High-speed decoder based on non-binary LDPC code and decoding method thereof

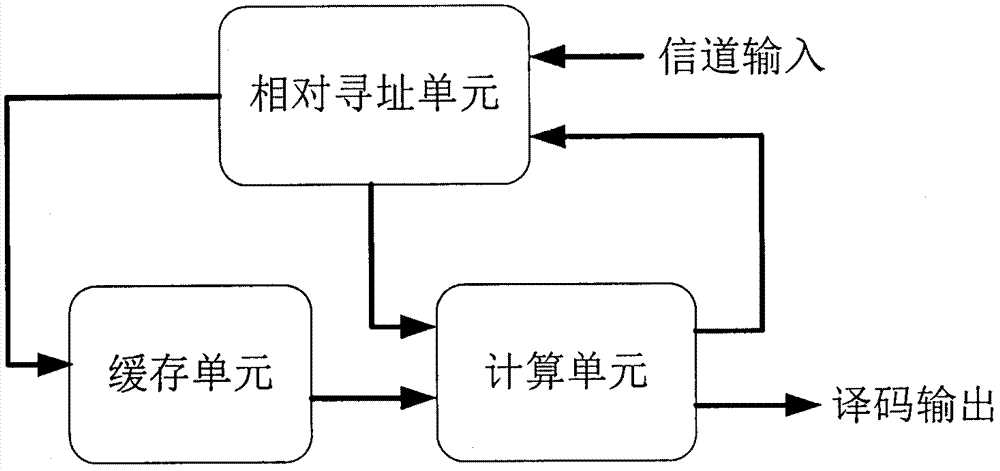

An LDPC code and multi-ary system technology, applied in the field of high-speed decoders, can solve the problems of affecting data throughput, low practicability, and large area consumption, so as to speed up decoding convergence speed, reduce decoding complexity, The effect of reducing the storage area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

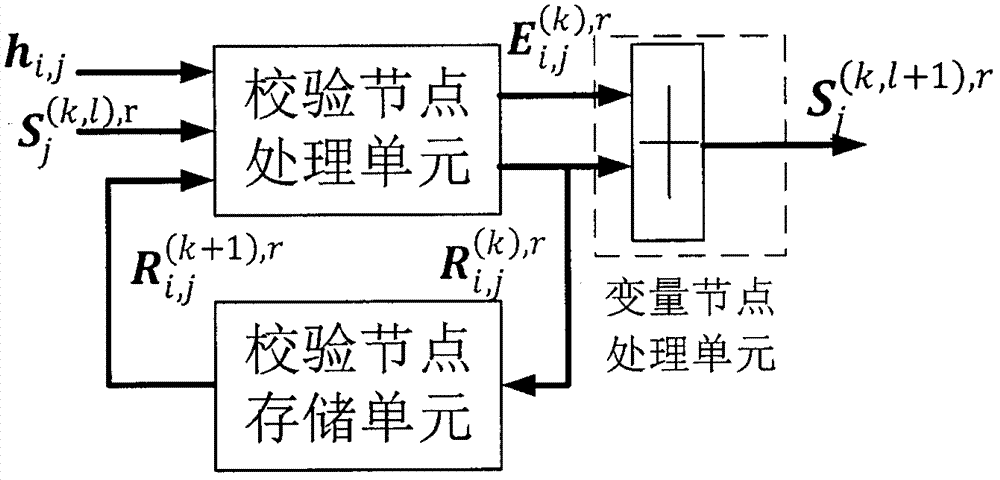

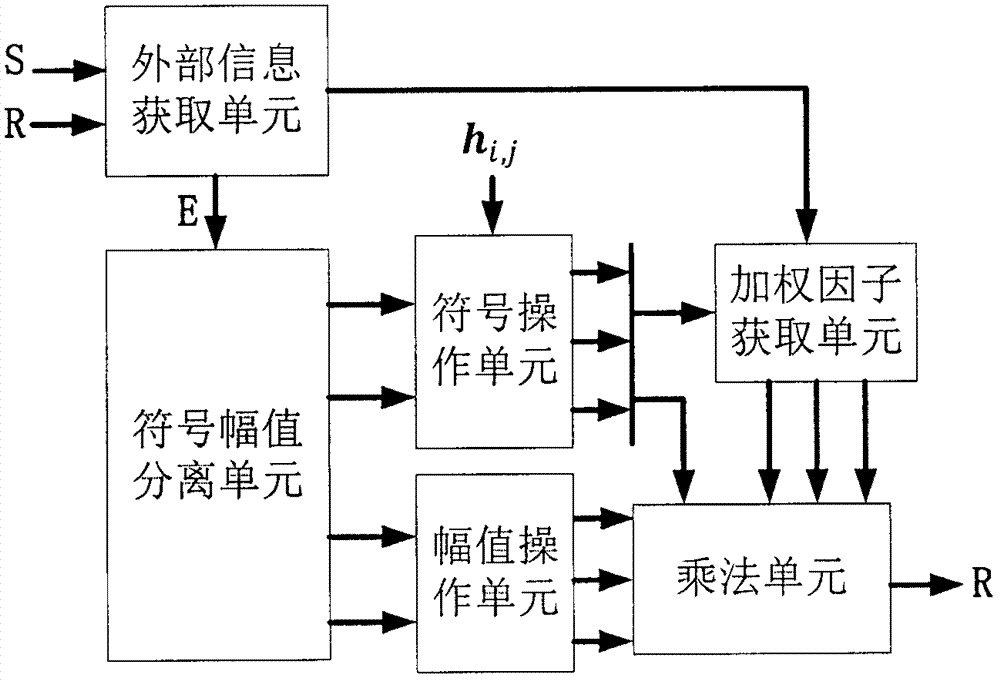

Method used

Image

Examples

Embodiment

[0080] Example: Pass the (837,726) multi-ary quasi-cyclic LDPC code through the AWGN channel, the row weight of the code is 27, the column weight is 4, the transmitting end uses BPSK modulation, and the receiving end is based on the above decoding architecture and methods, respectively Verilog language and C language are used for simulation realization, and the obtained FER performance simulation curve is as follows Figure 5 As can be seen from the figure, the decoding method takes a compromise between the hard decoding algorithm and the soft decoding algorithm; at the same time, the RTL based on the Verilog language is used to synthesize the Synopsys tool, and the process used is TSMC 90nm CMOS Process and comprehensive results show that under the condition of a frequency of 207.04Mhz, the total logic gate (the smallest unit is a NAND gate) is about 4.54M, and under the condition of a maximum number of iterations of 10, the total delay is only 40 clock cycles, and the throughpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More