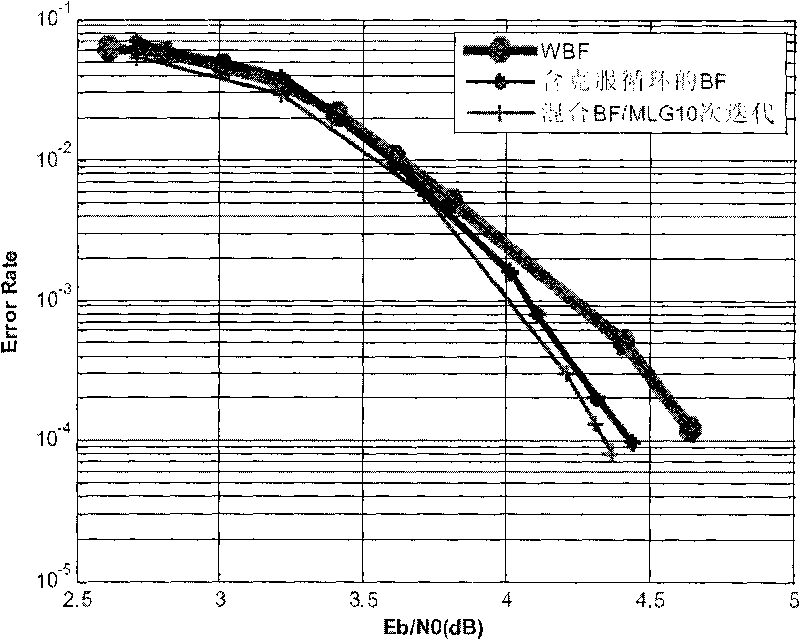

LDPC decoding method combining bit flipping (BF) and majority logic (MLG)

A large number logic and bit flip technology, which is applied in the field of LDPC decoding of mixed bit flip and large number logic, can solve the problems of complex calculation and poor decoding performance, and achieve simple calculation, reduced delay, and good decoding performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

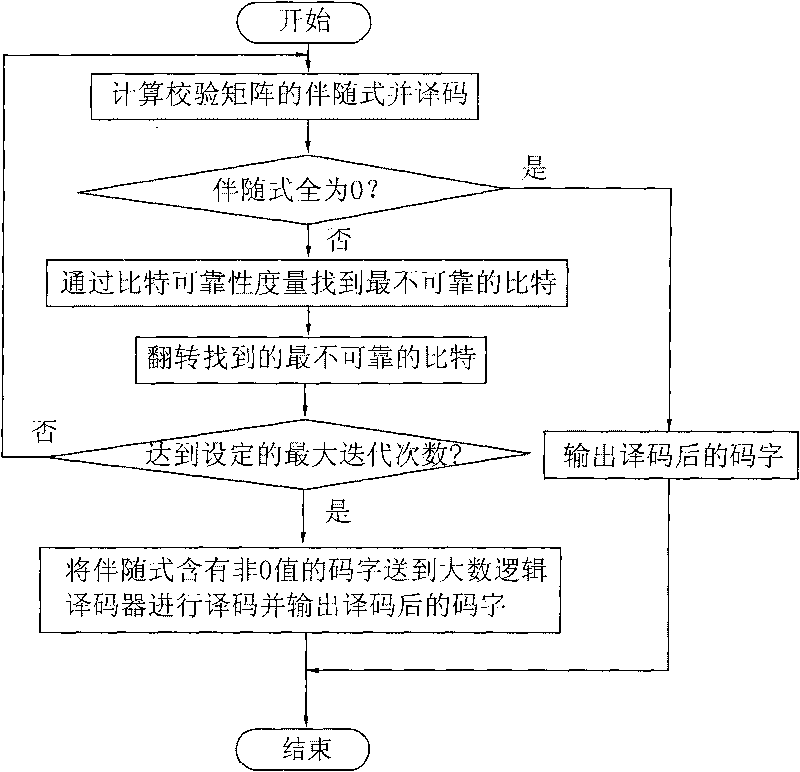

[0047] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

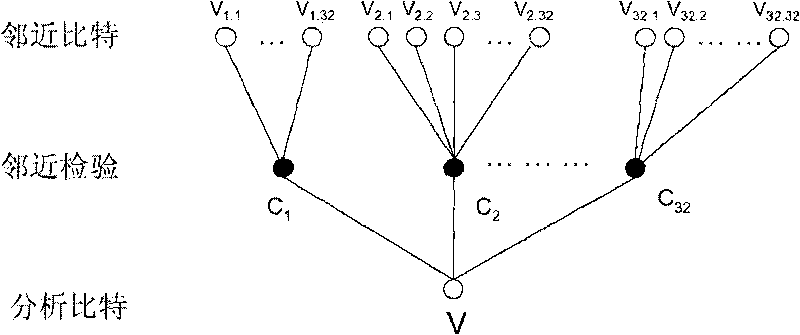

[0048] The present invention is a mixed decoding method using bit inversion and large number logic for FG-LDPC codes with orthogonal consistency check, now using the first type of Euclidean geometric low-density parity check code——(1023,781)EG - LDPC code as an example, where 781 represents the length of the input information bit, and 1023 represents the length of the code word output after error correction coding. Bit v participates in 32 checks, and each check contains 32 bits. Define U(v) to denote the number of invalid checksums containing bit v. The bipartite graph representation of the (1023, 781) EG-LDPC code is as follows figure 2 shown. Define D(a, b) to represent the distance between node a and node b in the bipartite graph, in figure 2 Among them, D(v, v 1.1 )=2,D(v,c 1 )=1.

[0049] According to the bipartite graph of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More