Patents

Literature

245 results about "On-die termination" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

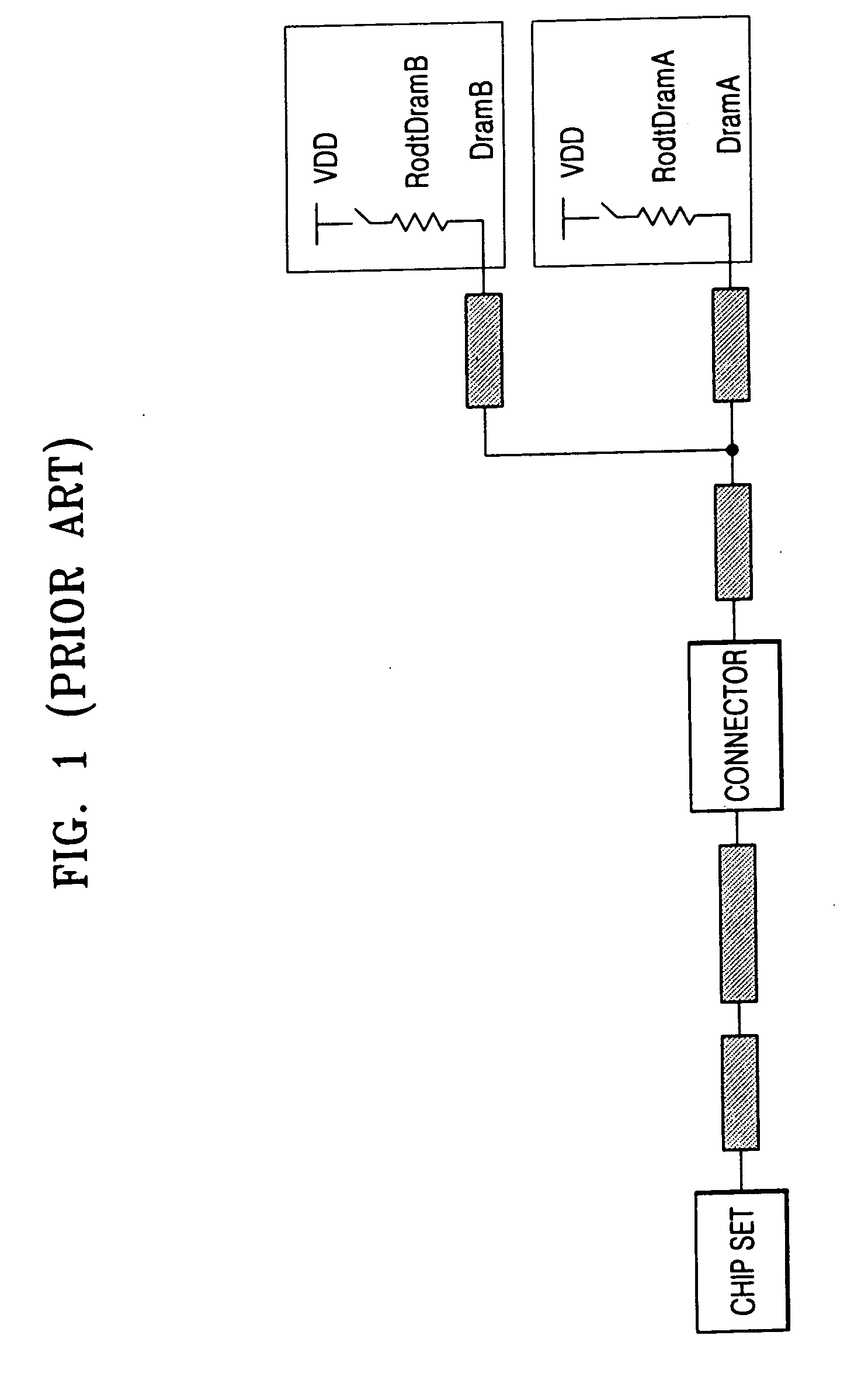

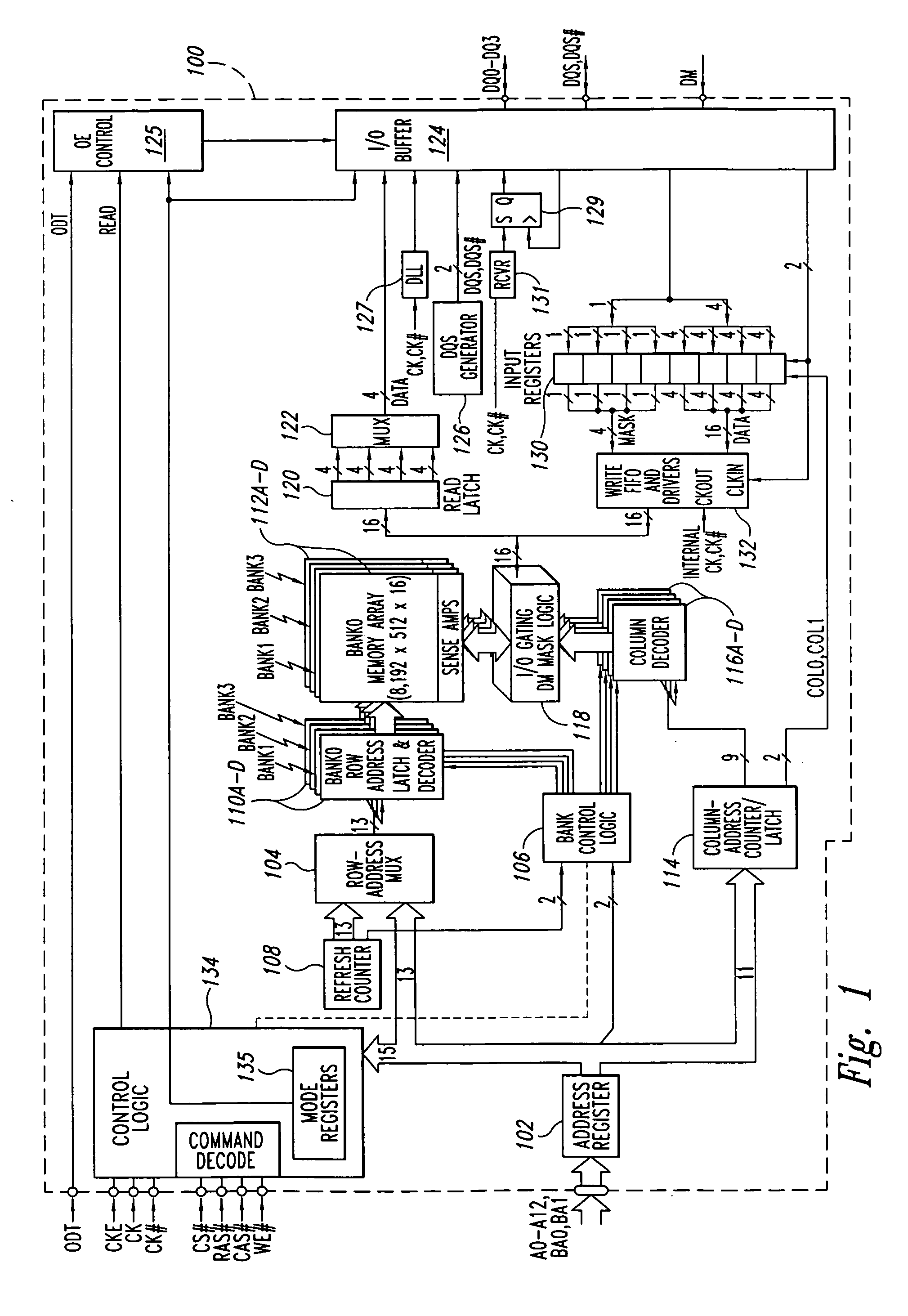

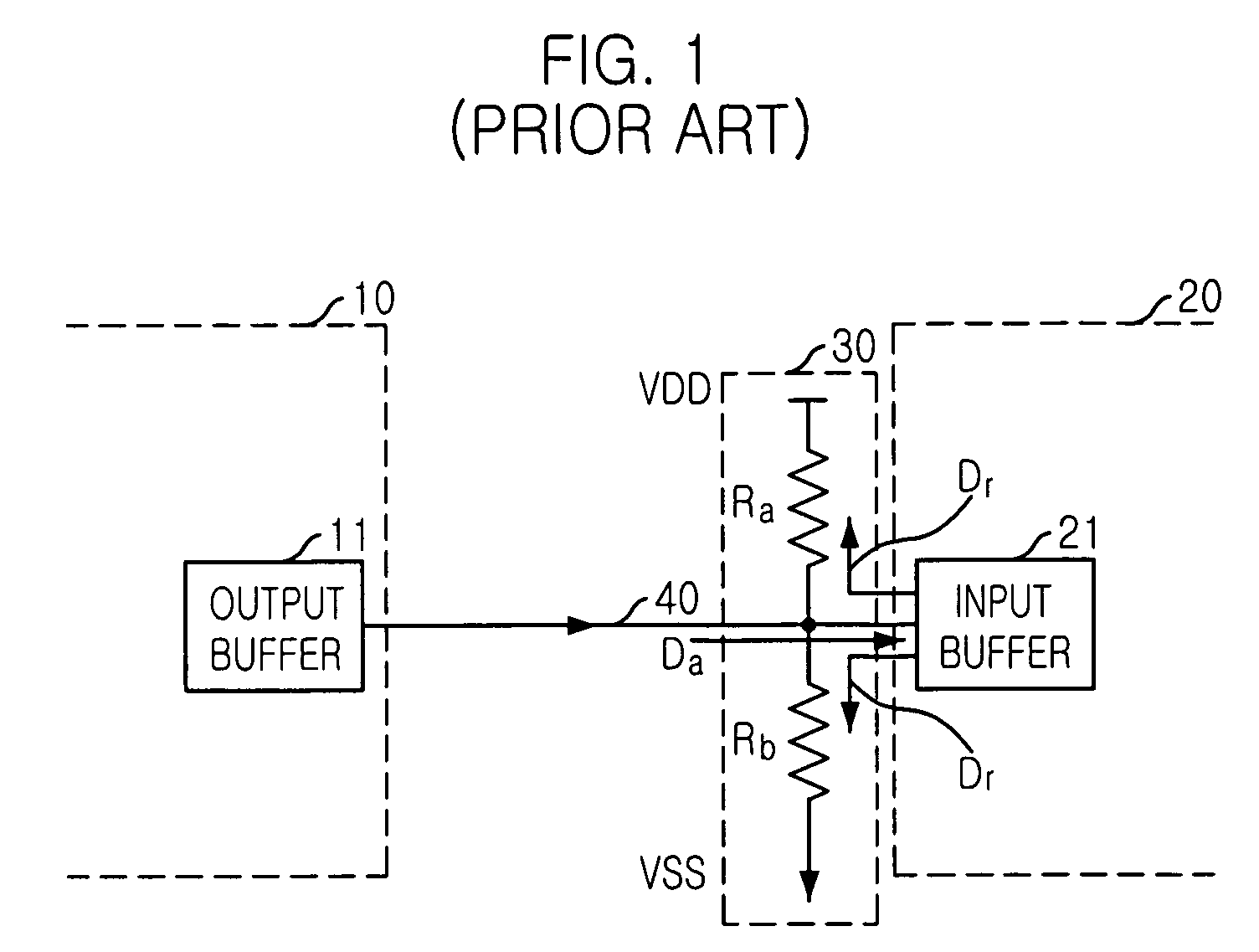

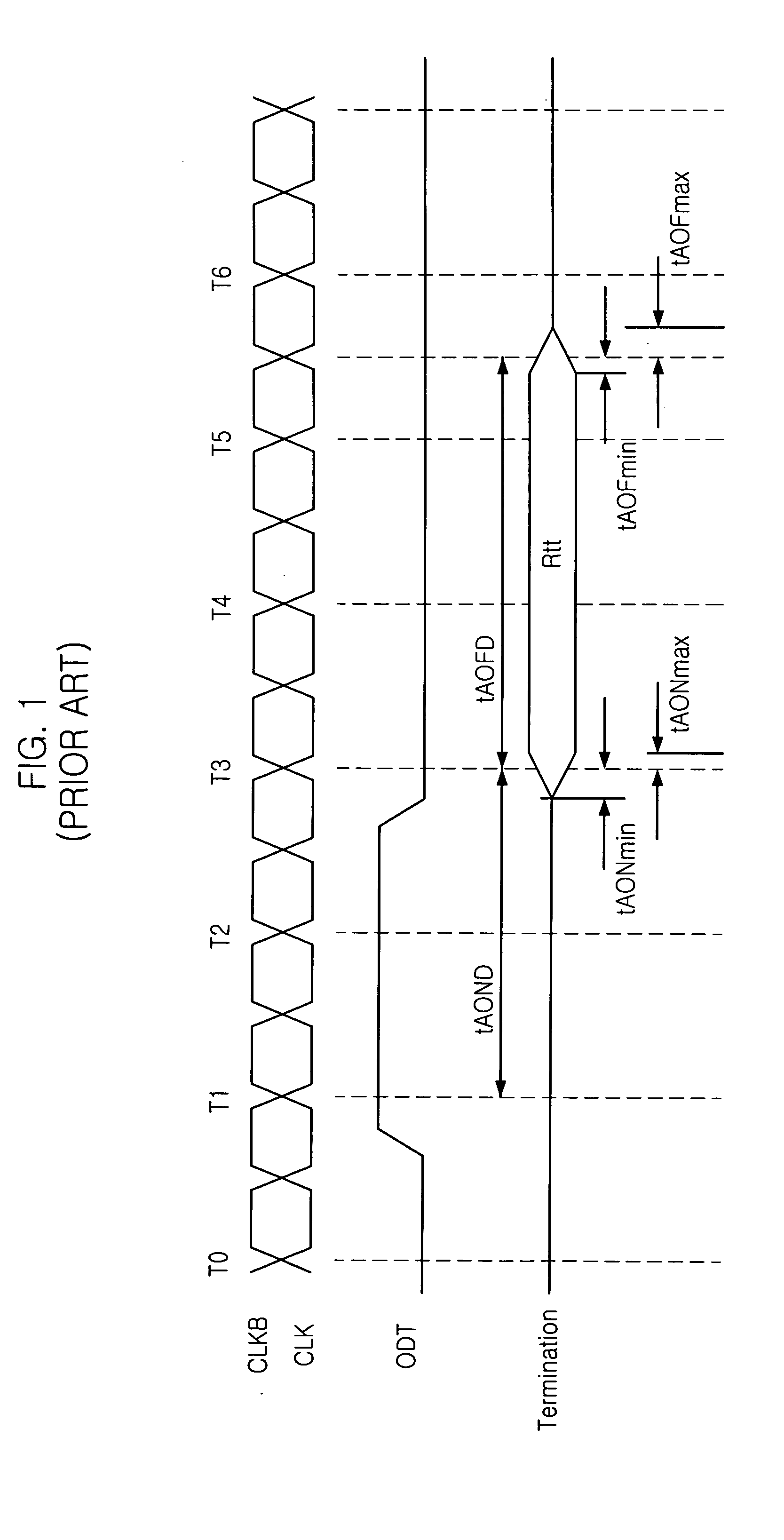

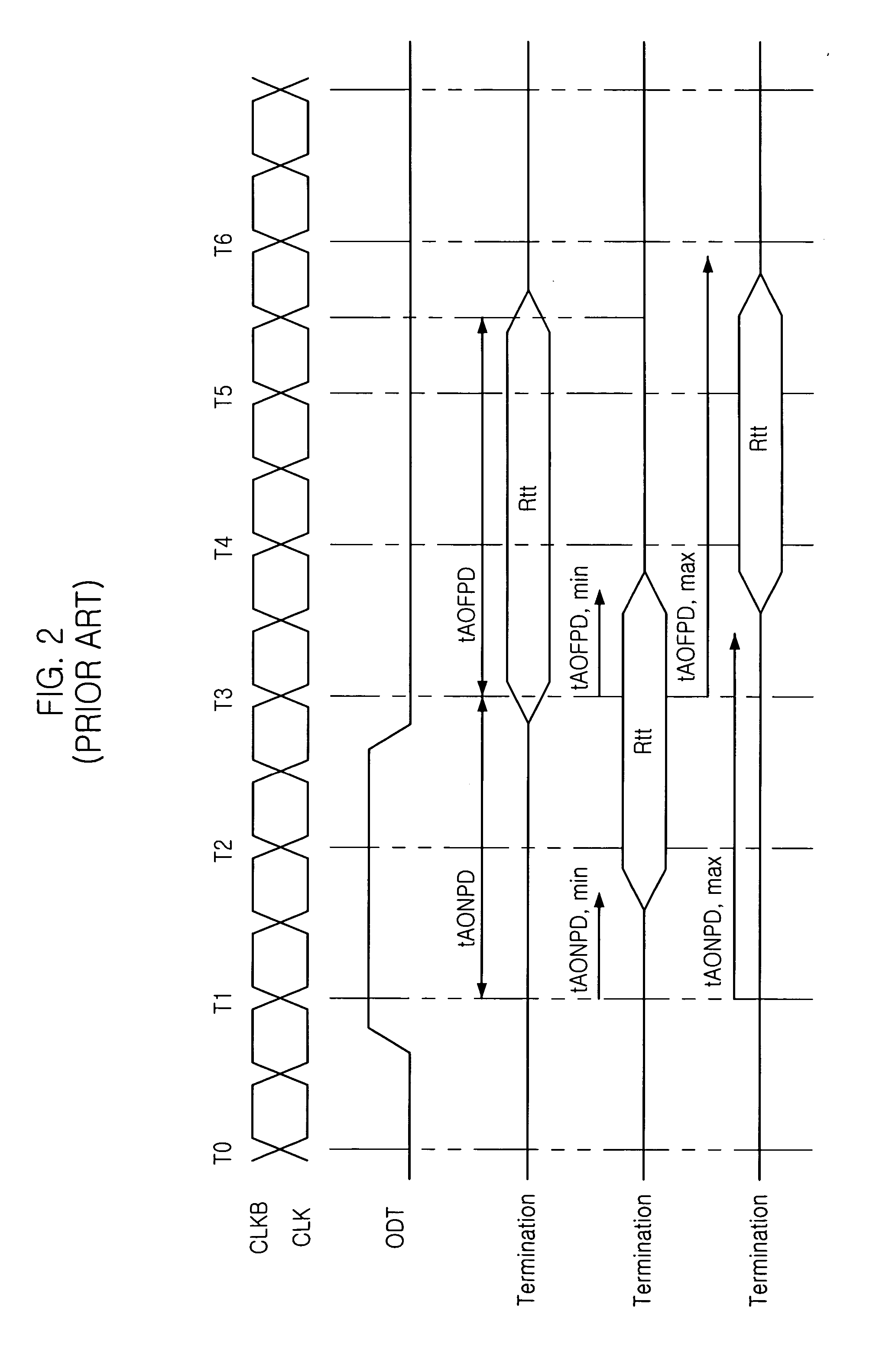

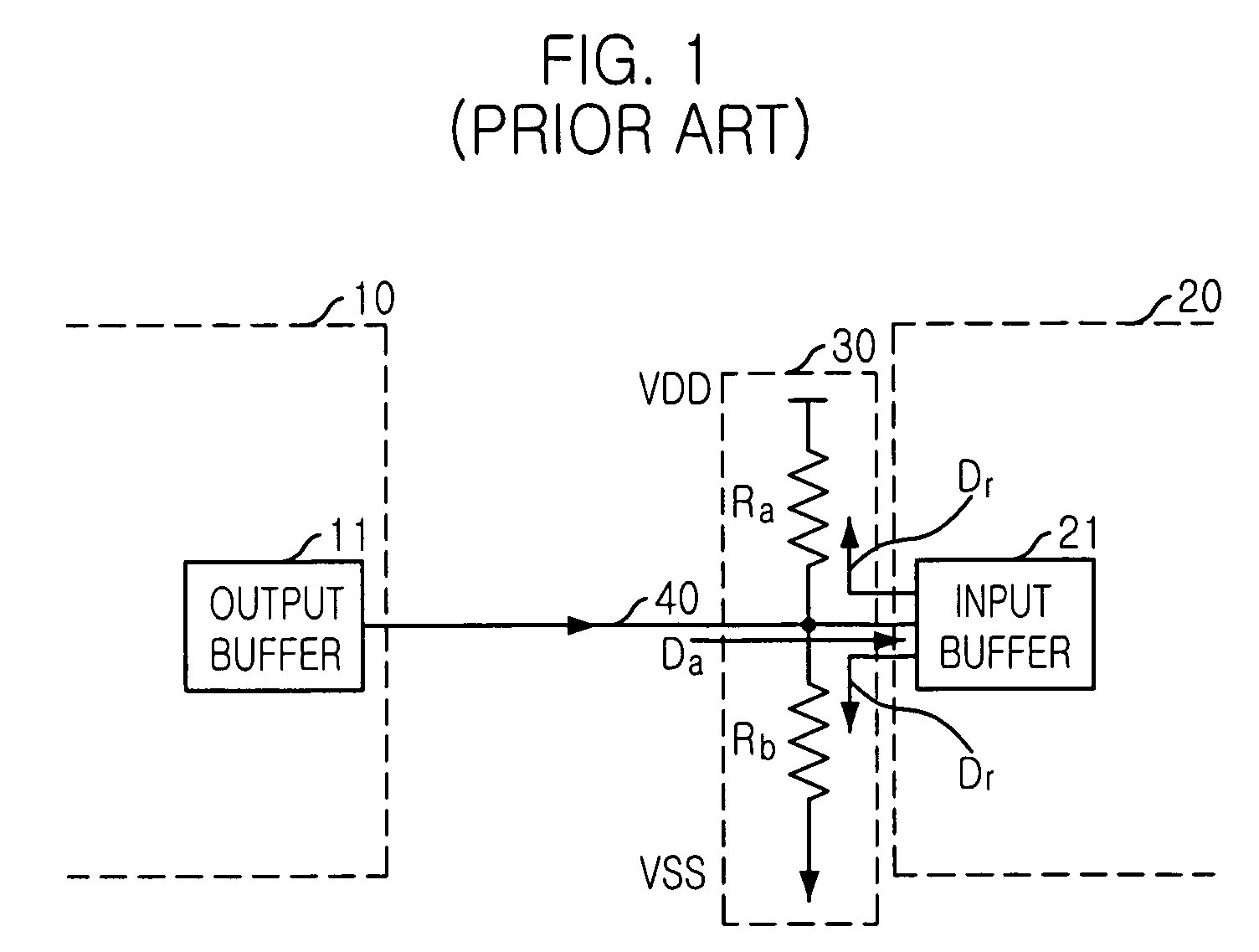

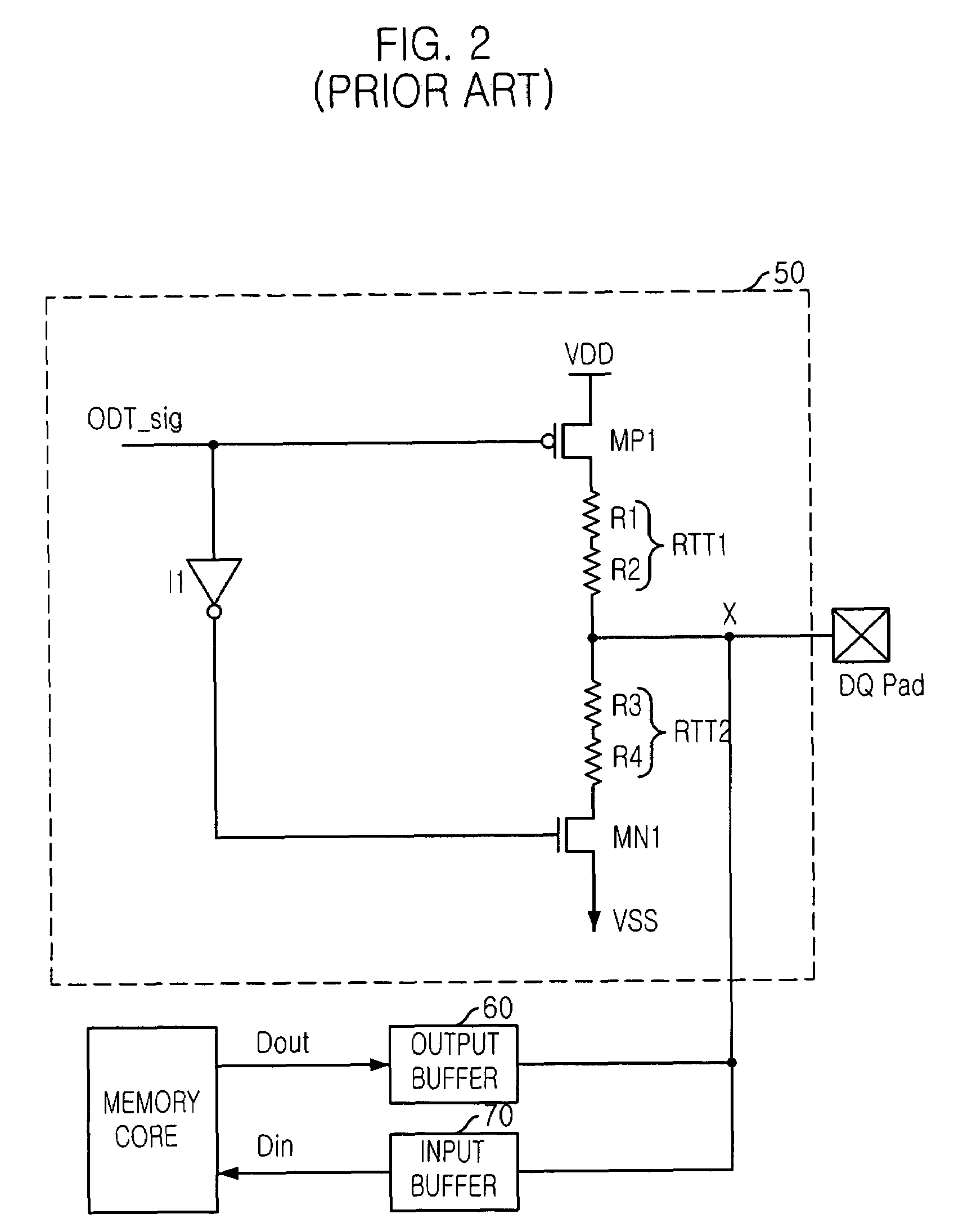

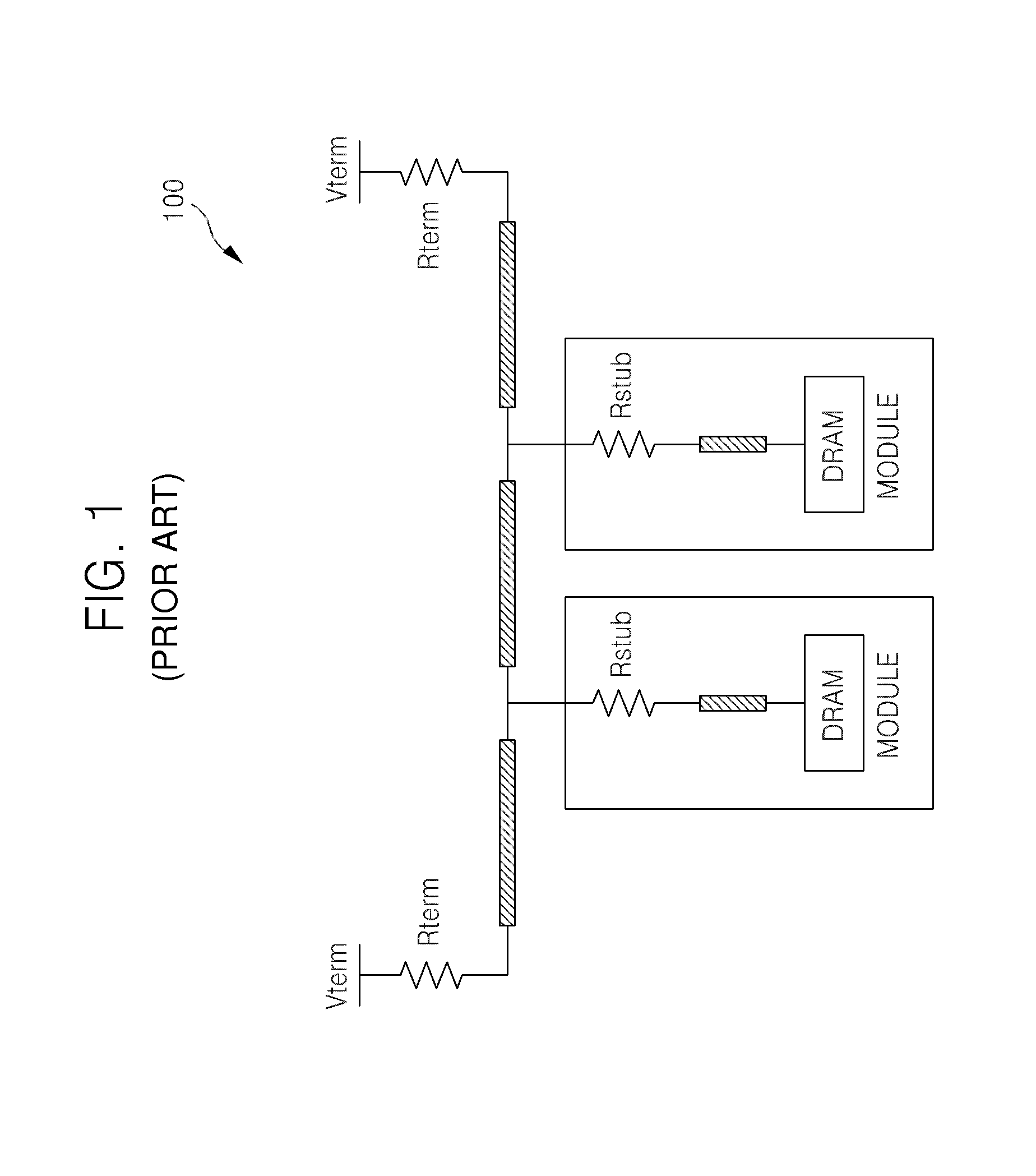

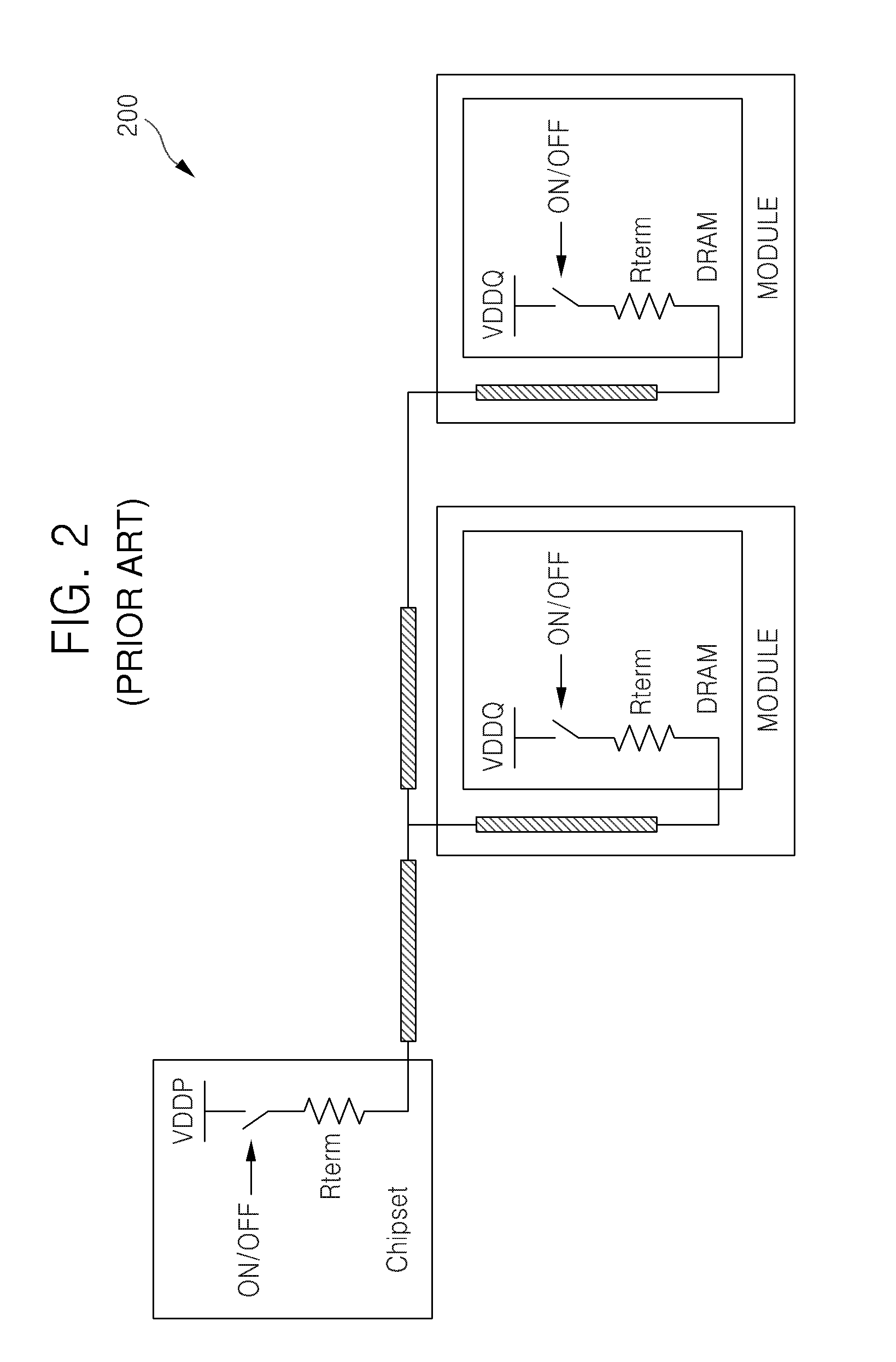

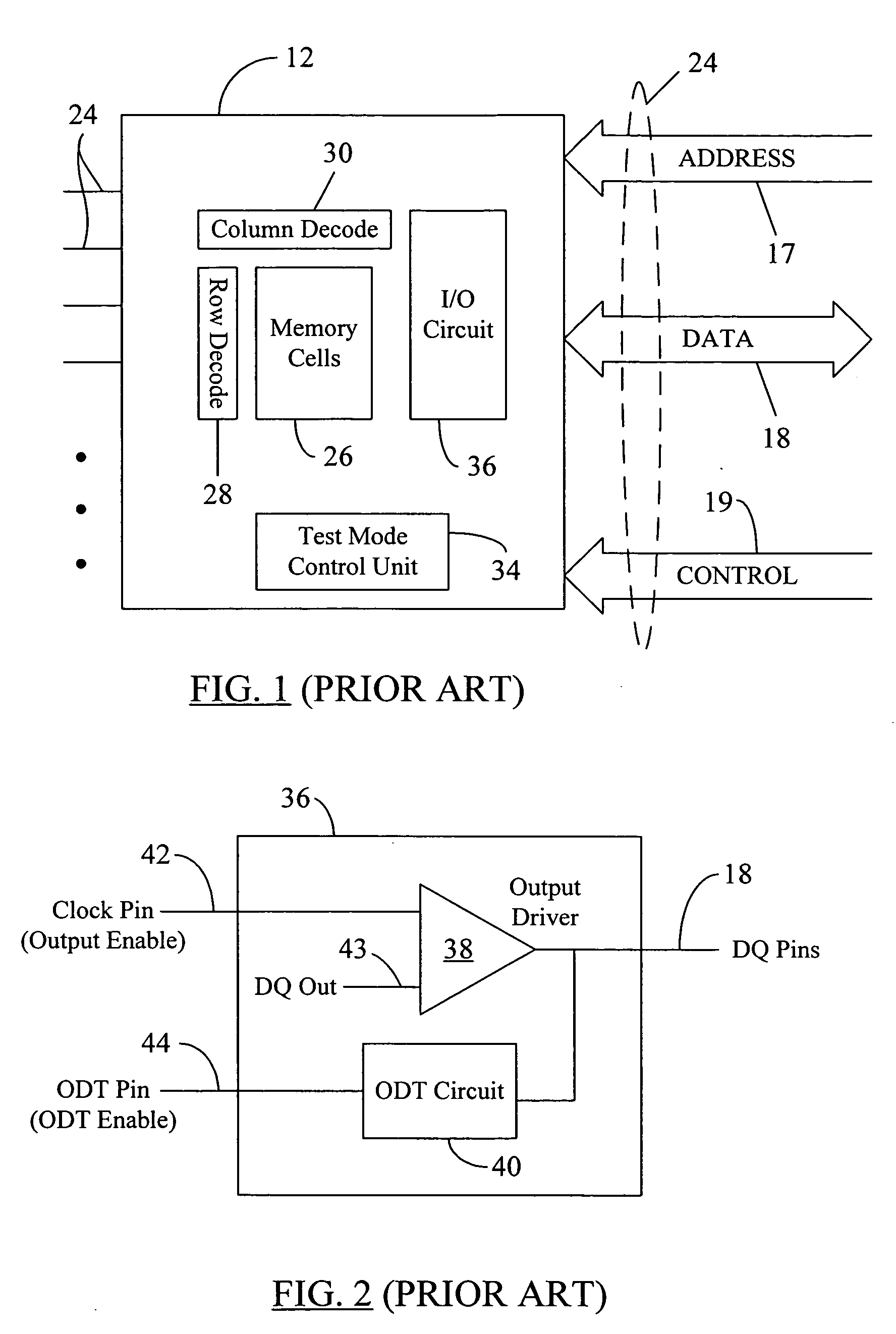

On-die termination (ODT) is the technology where the termination resistor for impedance matching in transmission lines is located inside a semiconductor chip instead of on a printed circuit board (PCB).

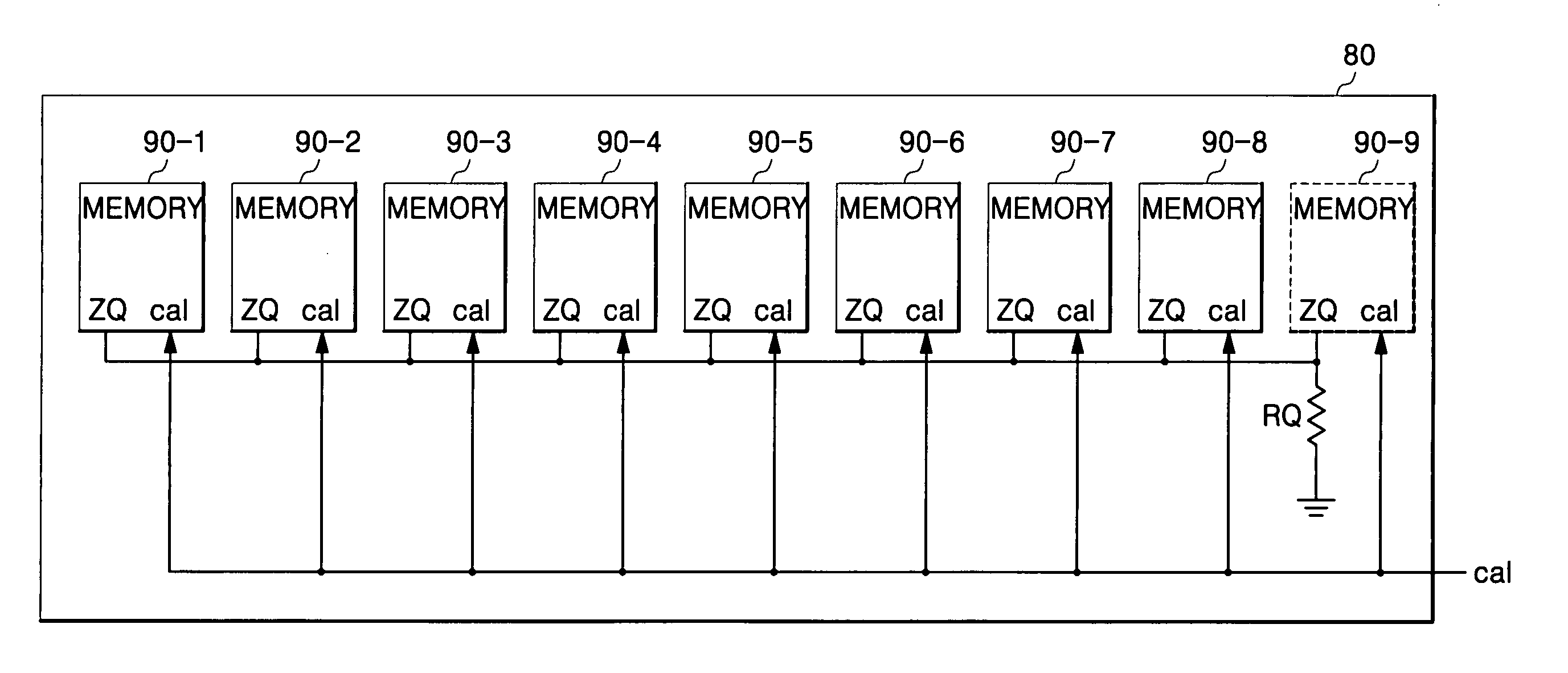

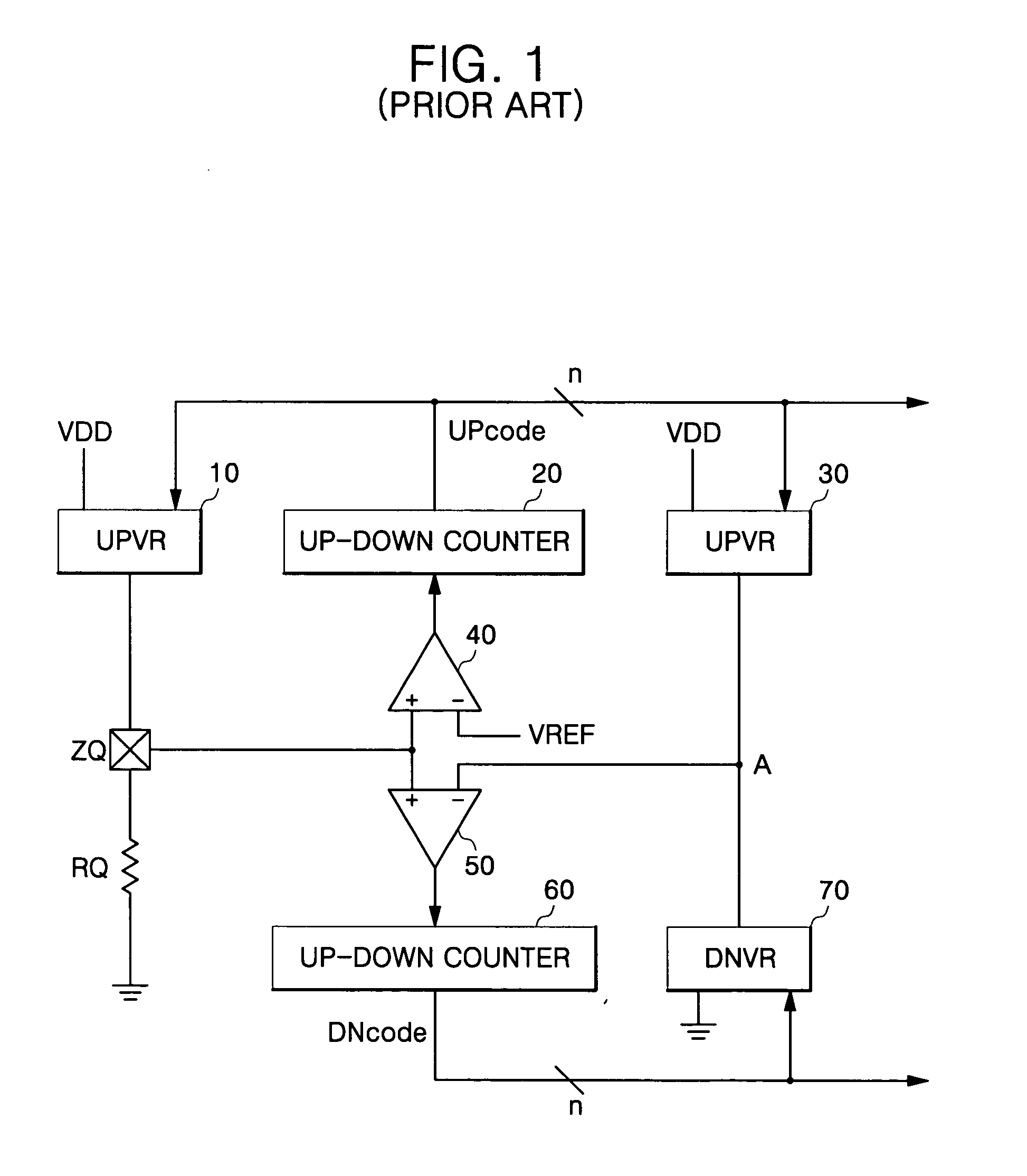

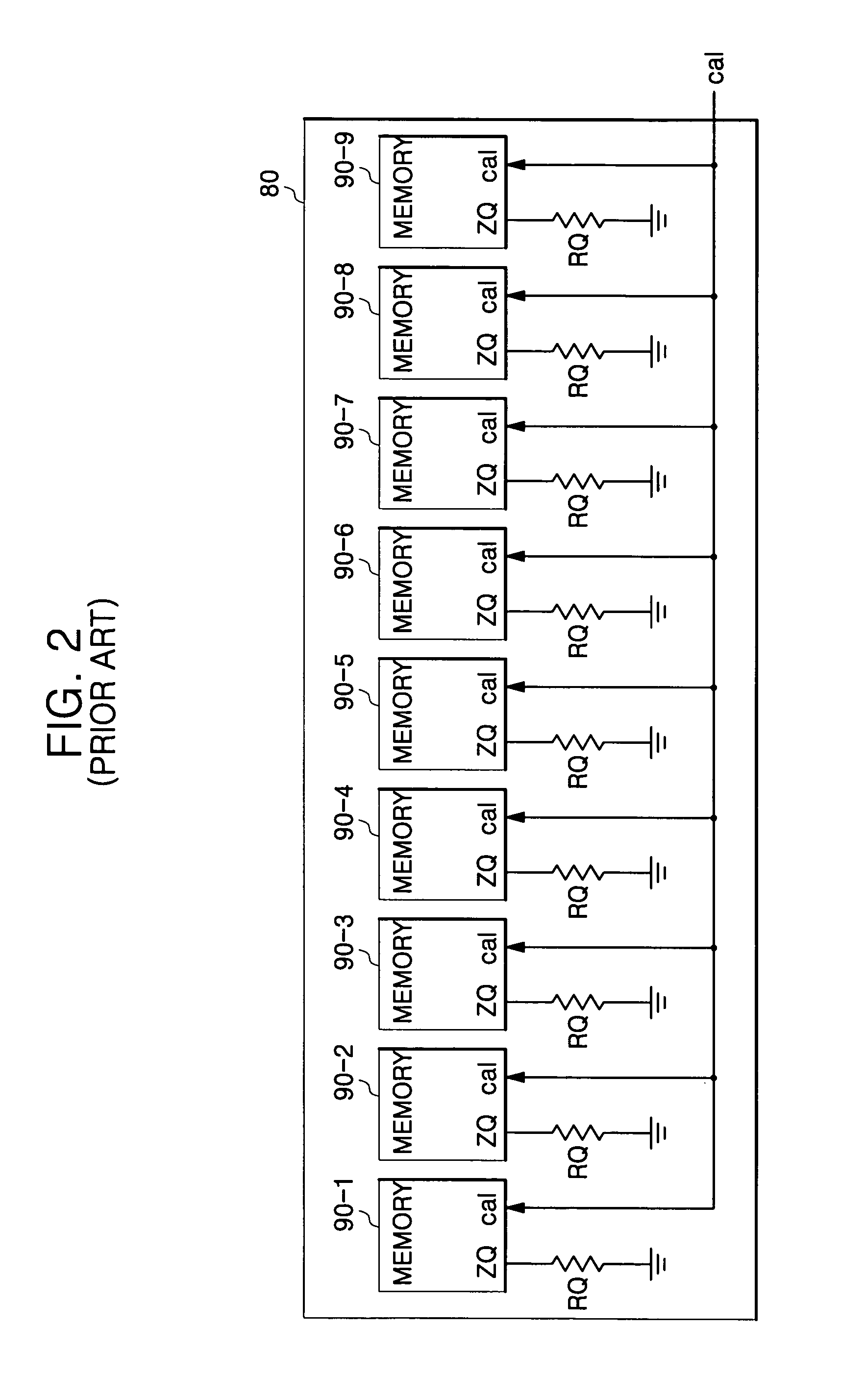

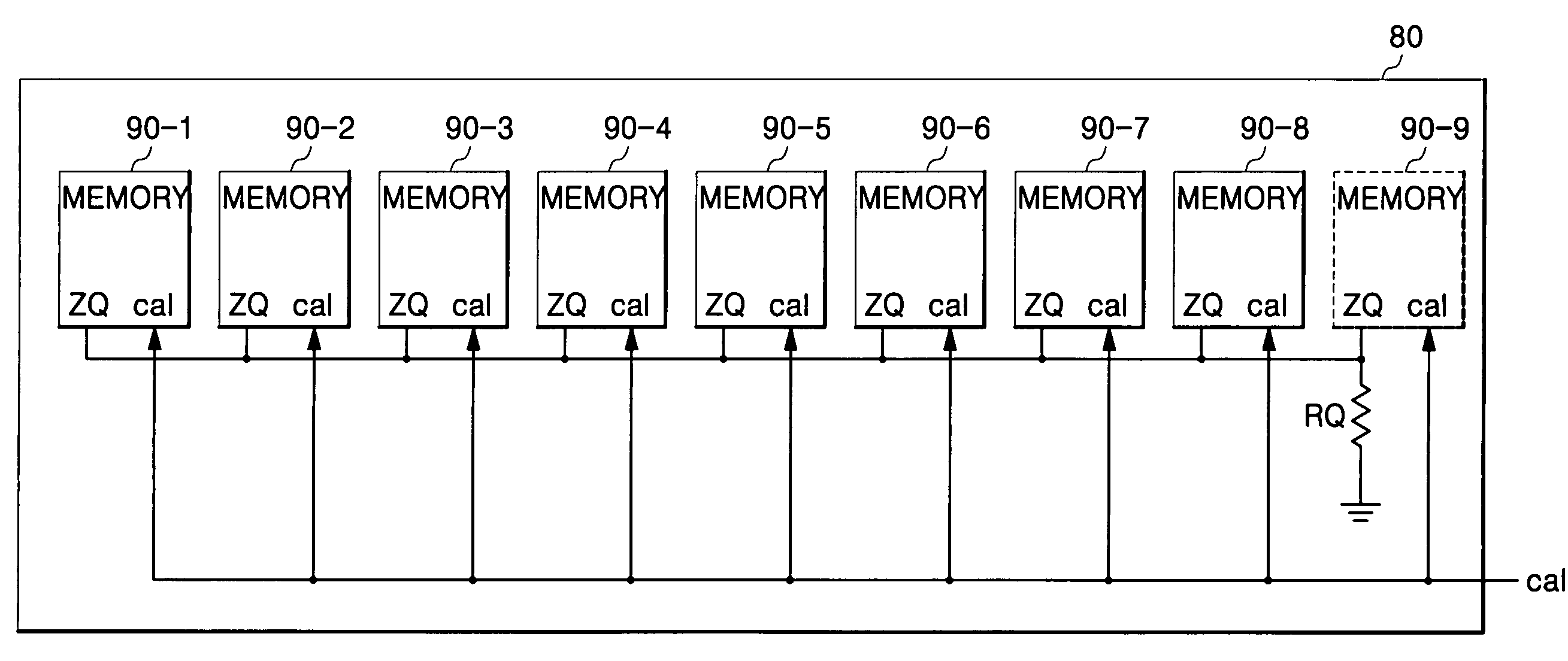

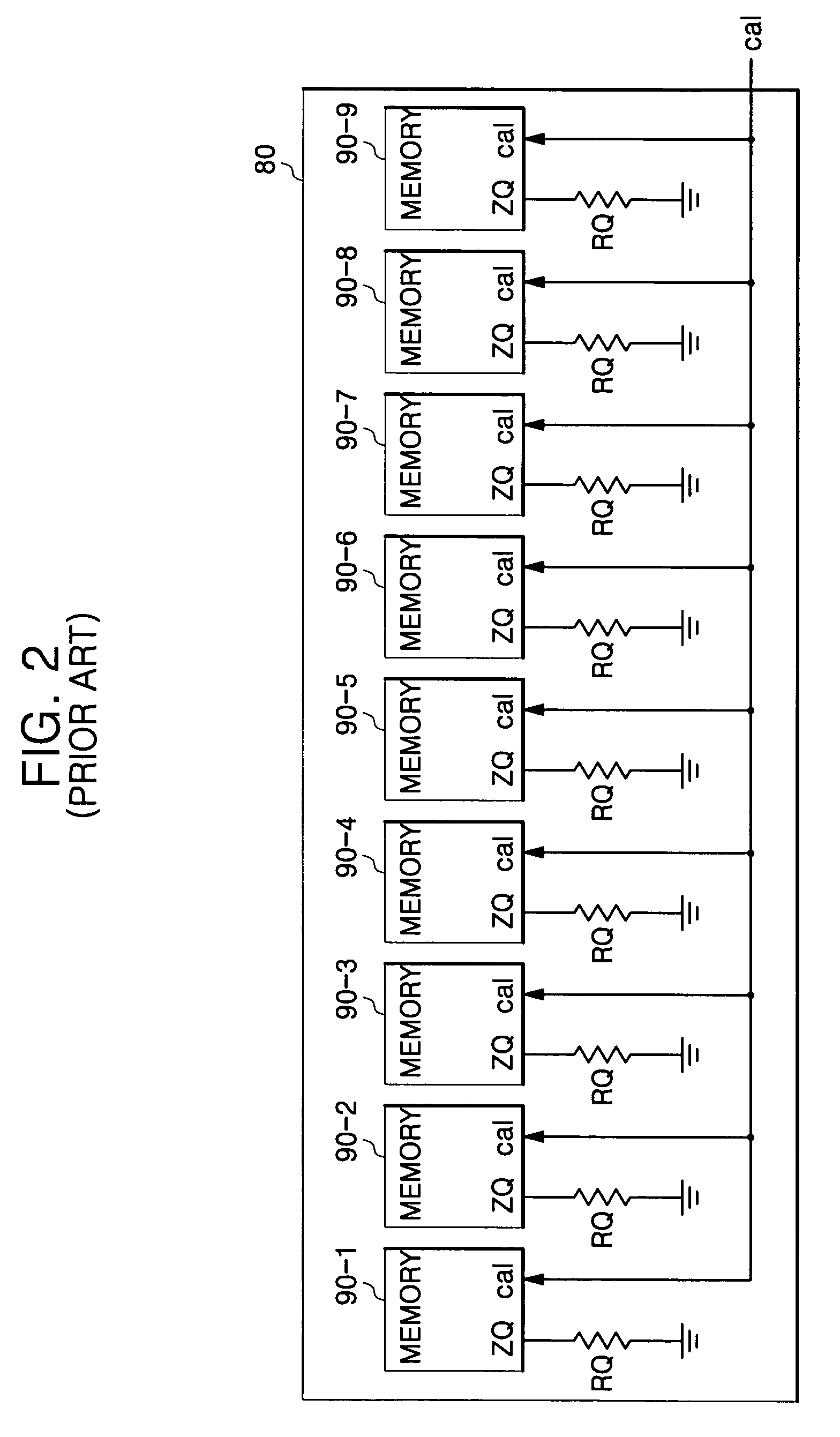

Memory module and impedance calibration method of semiconductor memory device

Disclosed is a memory module and a method of calibrating an impedance of a semiconductor memory device of the memory module, where the memory module includes semiconductor memory devices each having a separate terminal for calibrating impedance characteristics, and a reference resistor commonly connected to the separate terminals, such that the number of reference resistors used in calibration of impedance characteristics of an off-chip driver or an on-die termination circuit of the semiconductor memory device is reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

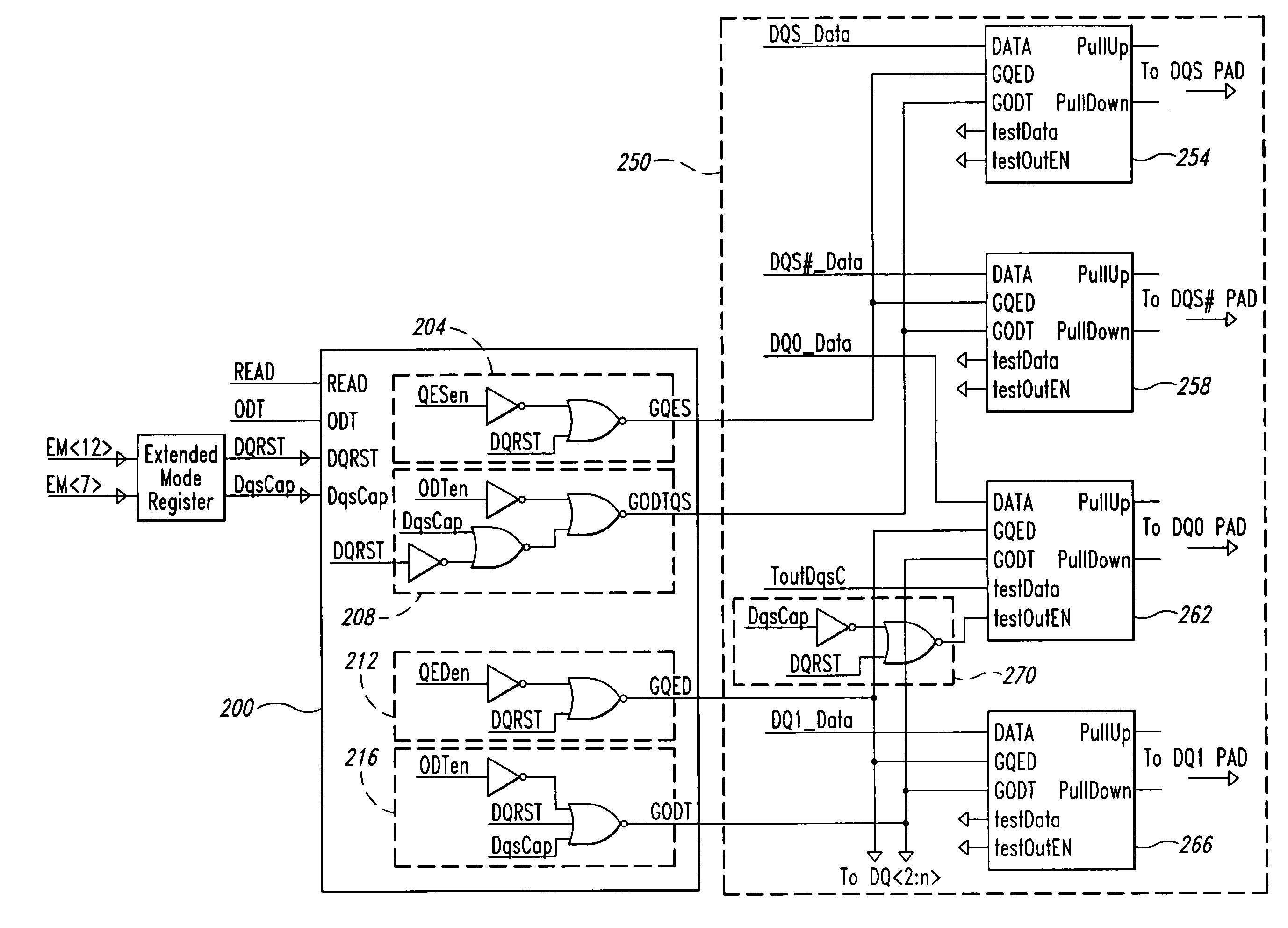

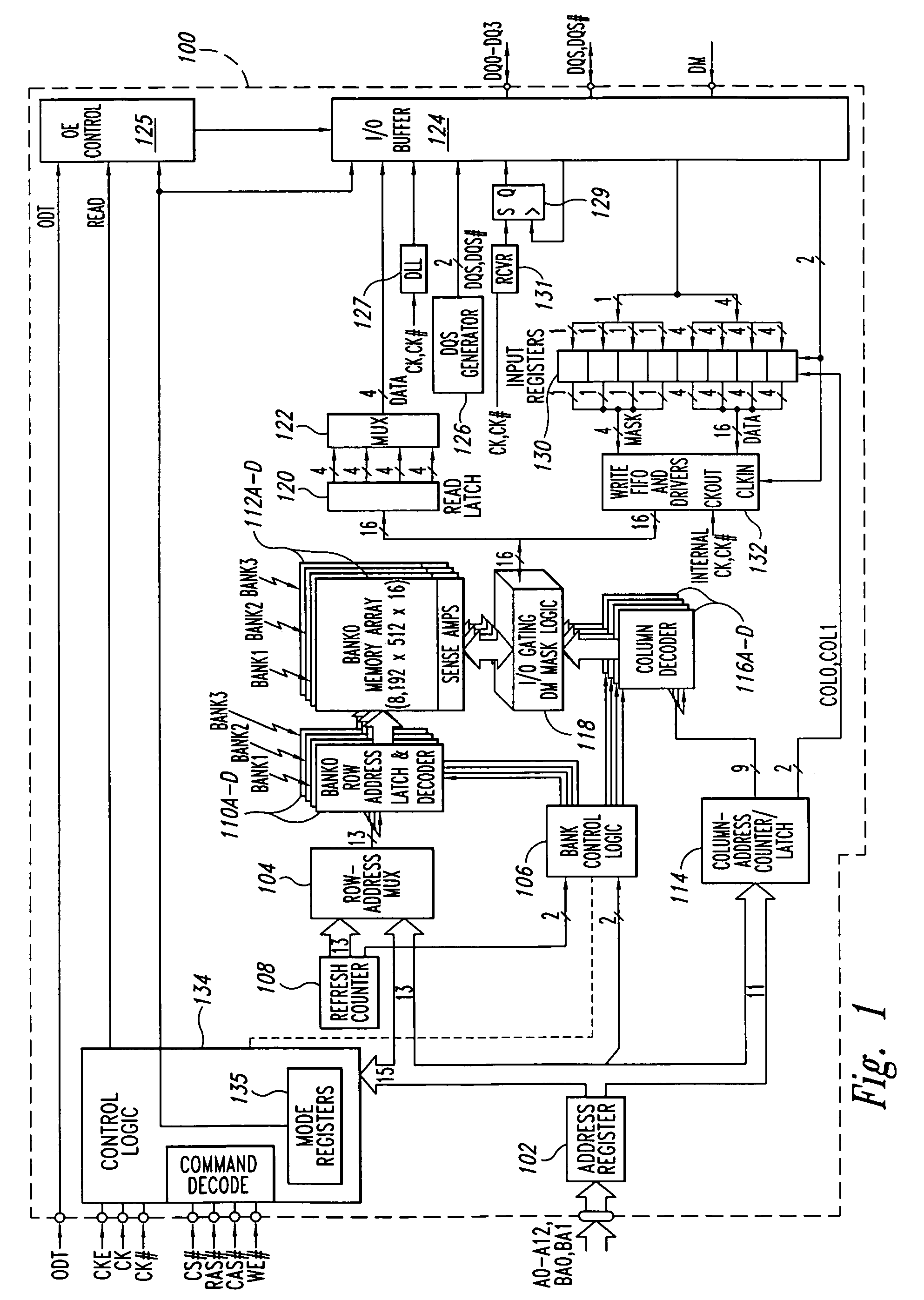

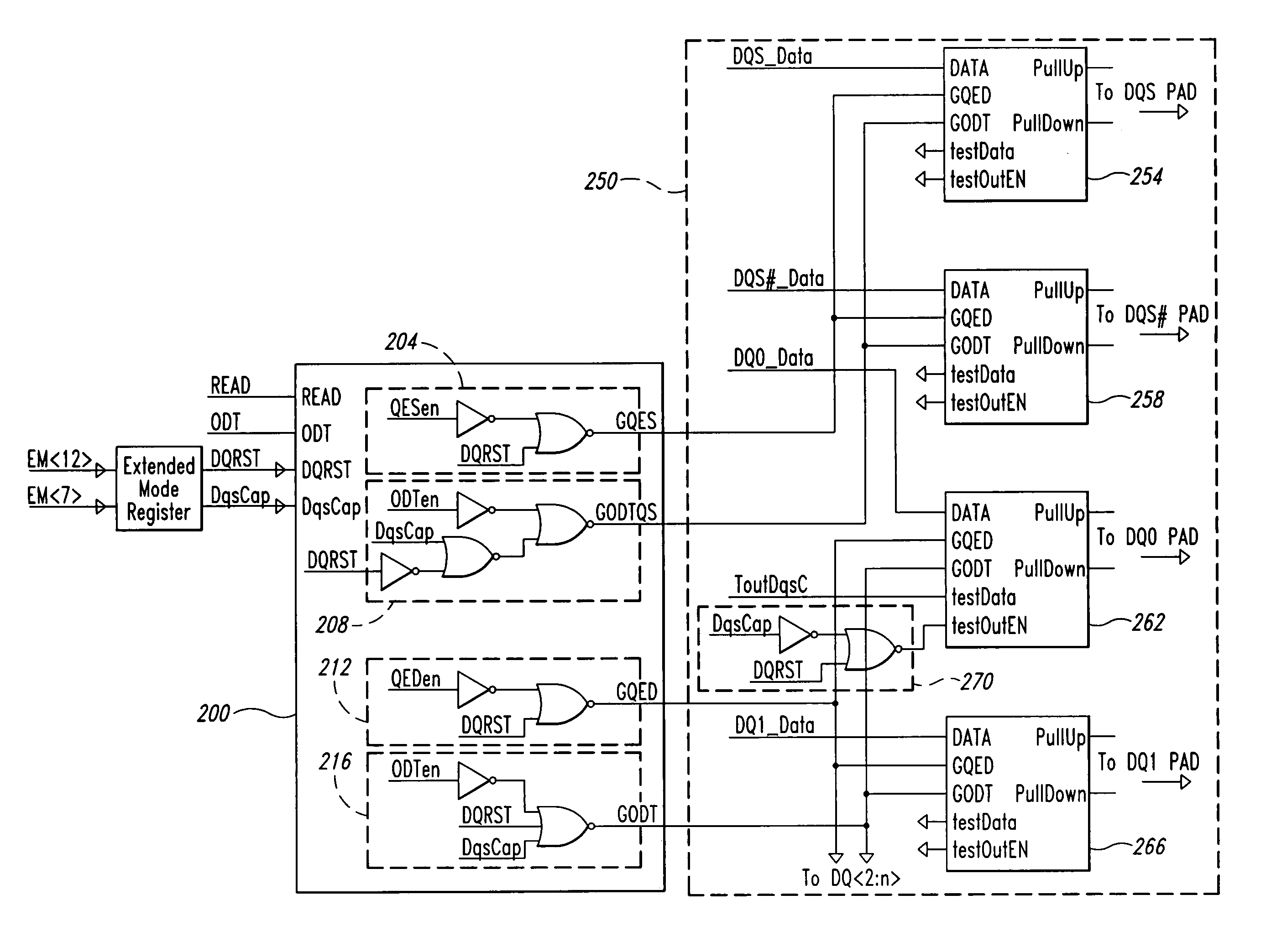

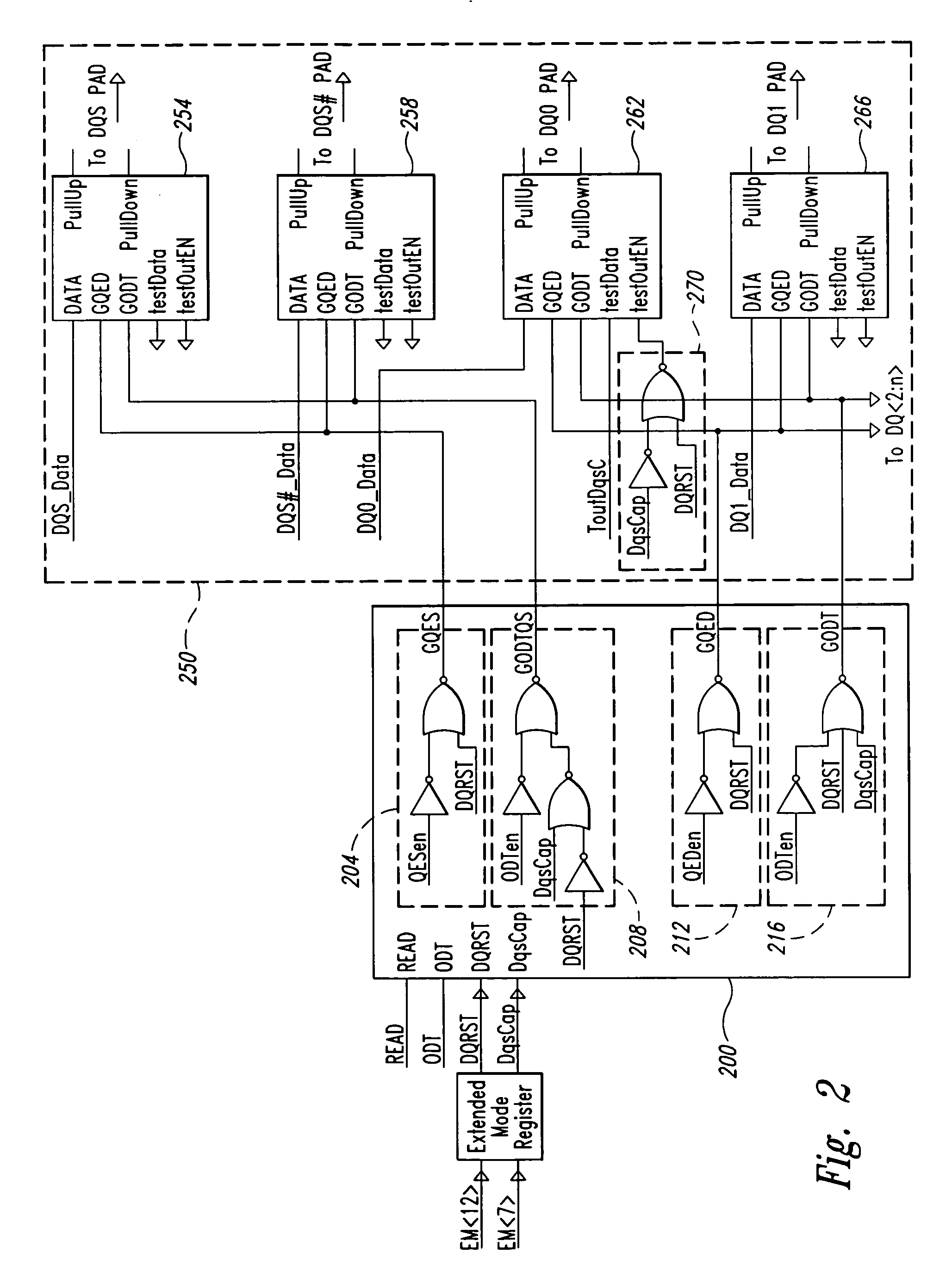

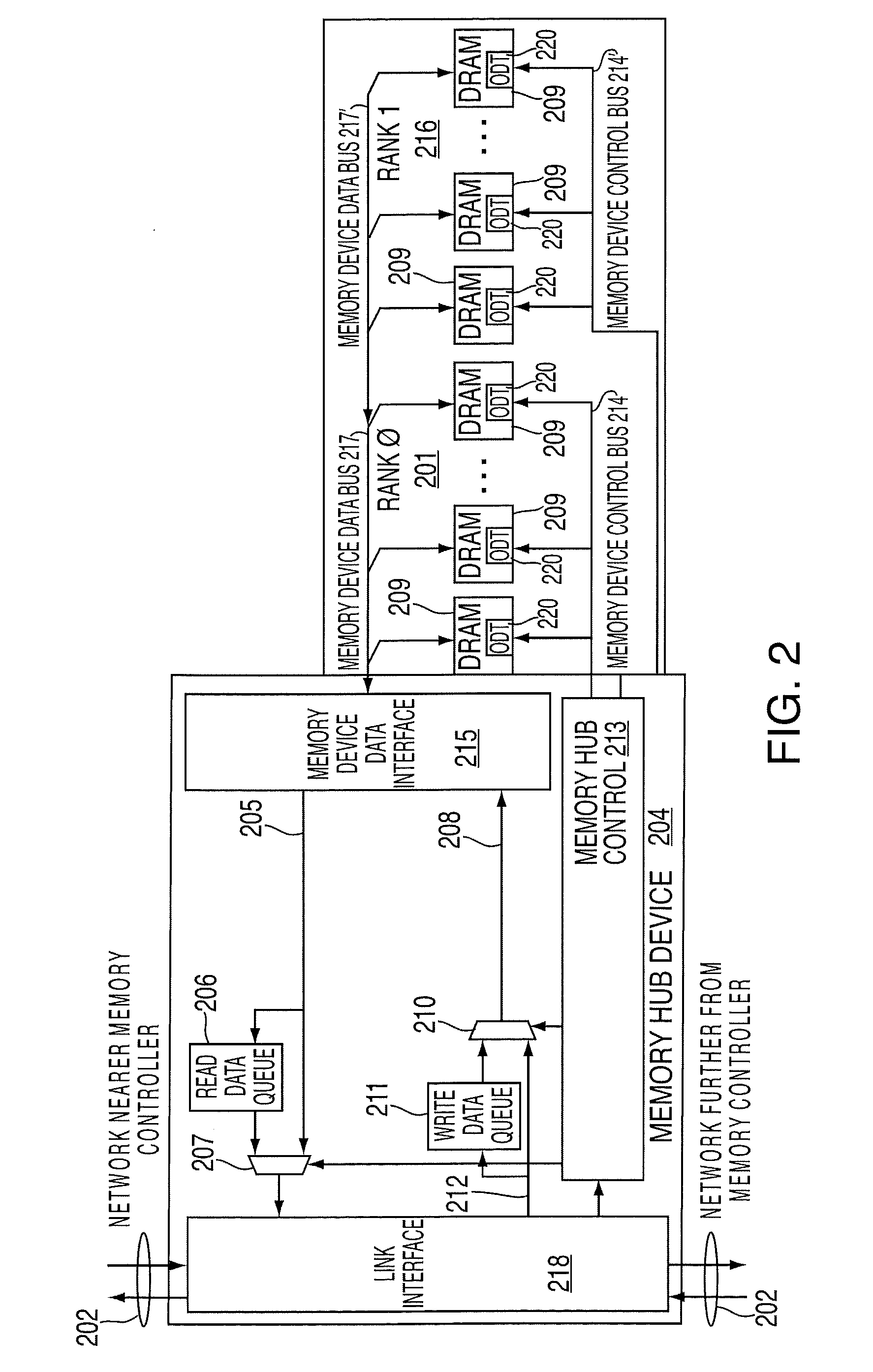

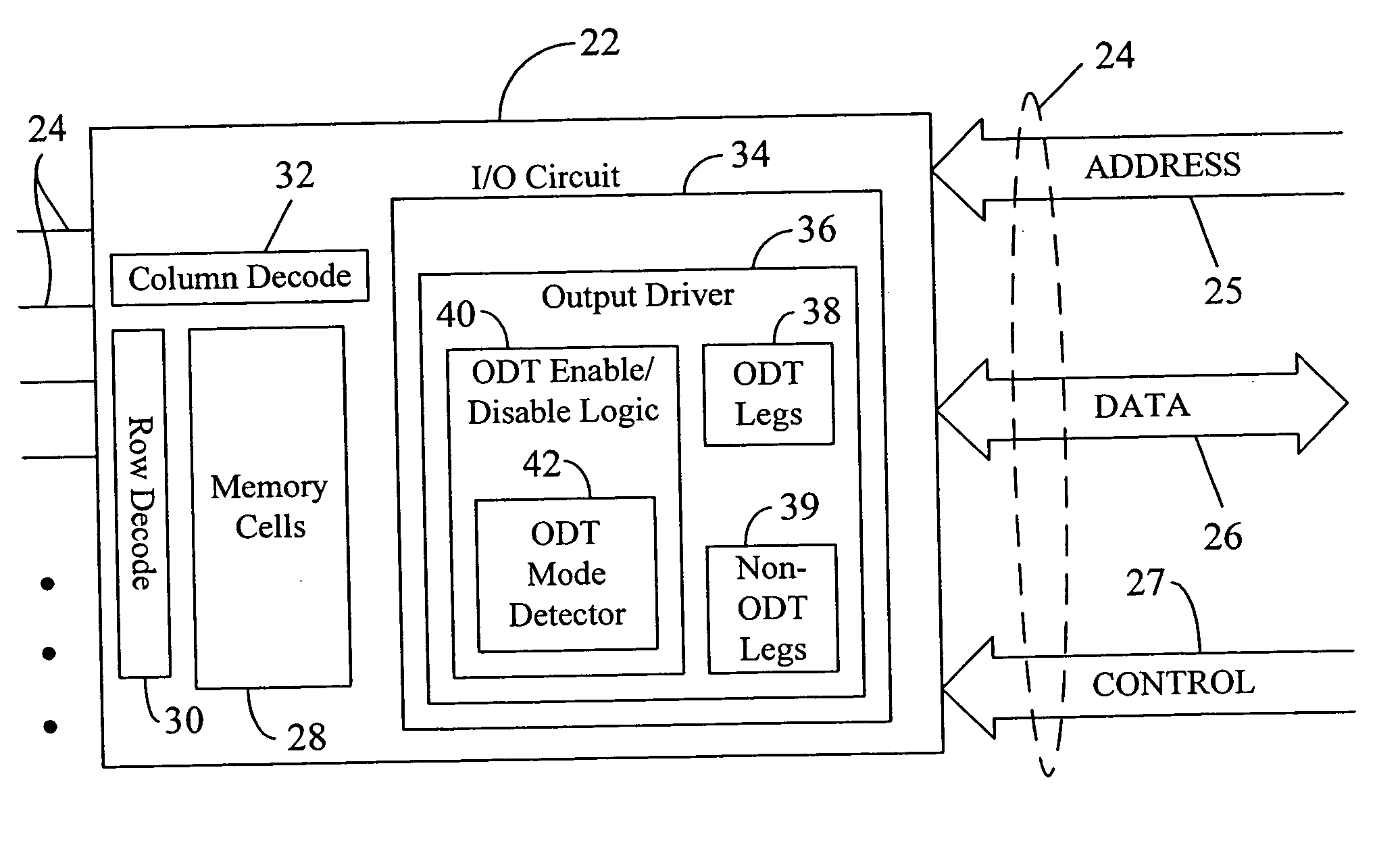

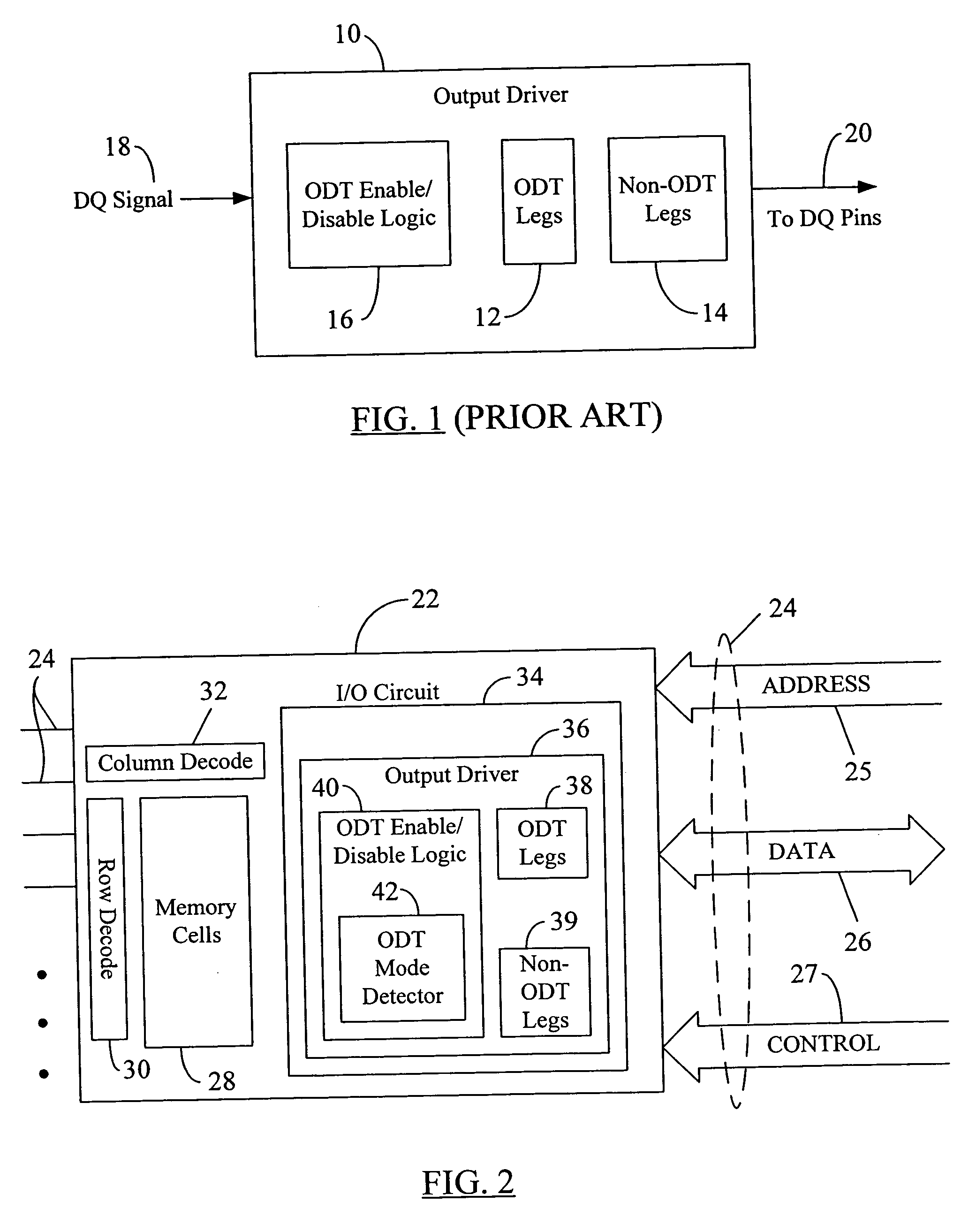

Apparatus and method for independent control of on-die termination for output buffers of a memory device

An apparatus and method providing independent control of on-die termination (ODT) of output buffers. The ODTs for the buffer circuits of an input / output (I / O) buffer can be enabled and disabled in response to an ODT control signal. Additionally, the ODTs for a first set of the buffer circuits can be enabled and disabled responsive to the ODT control signal and the ODT for at least one of a second set of the buffer circuits is disabled.

Owner:ROUND ROCK RES LLC

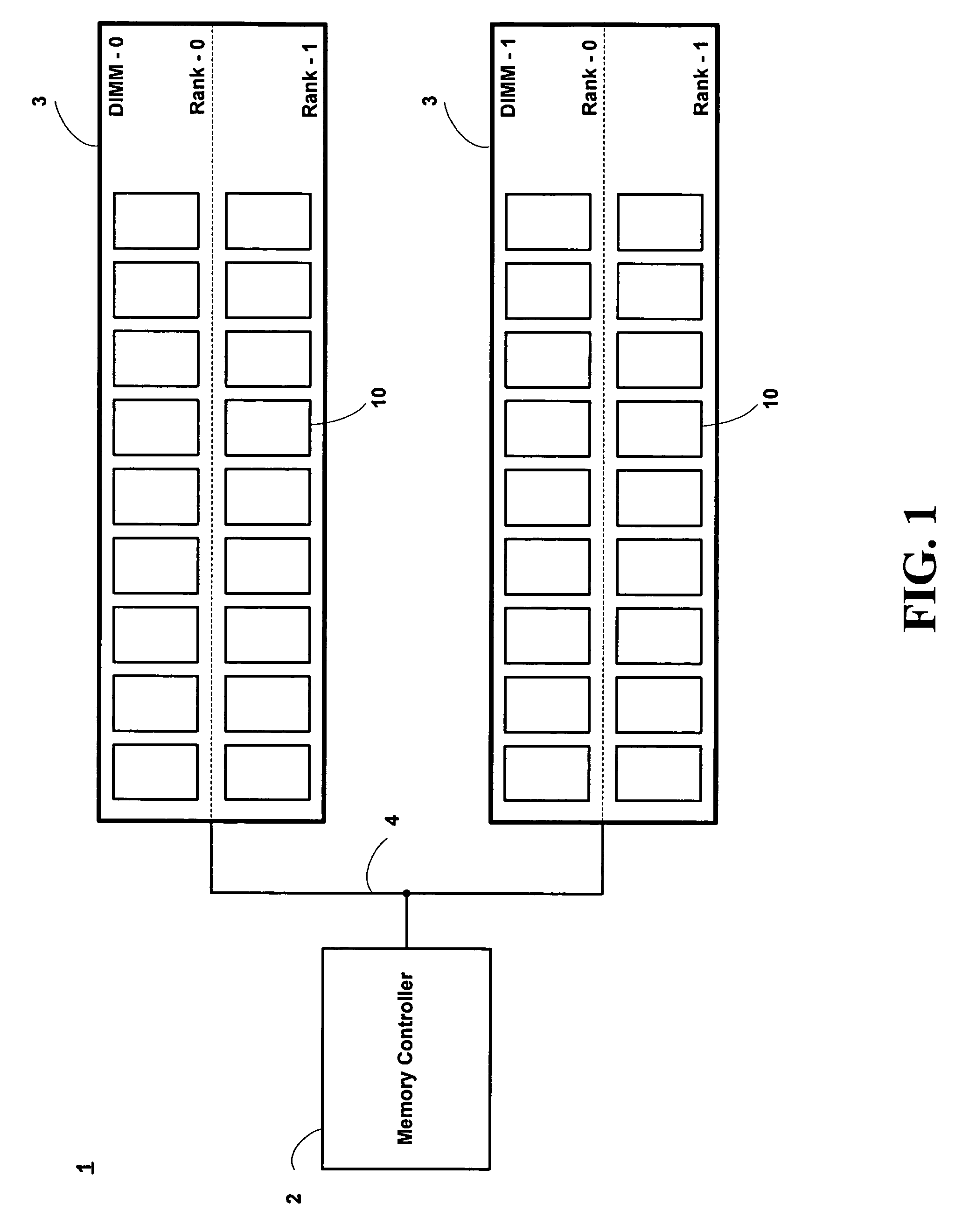

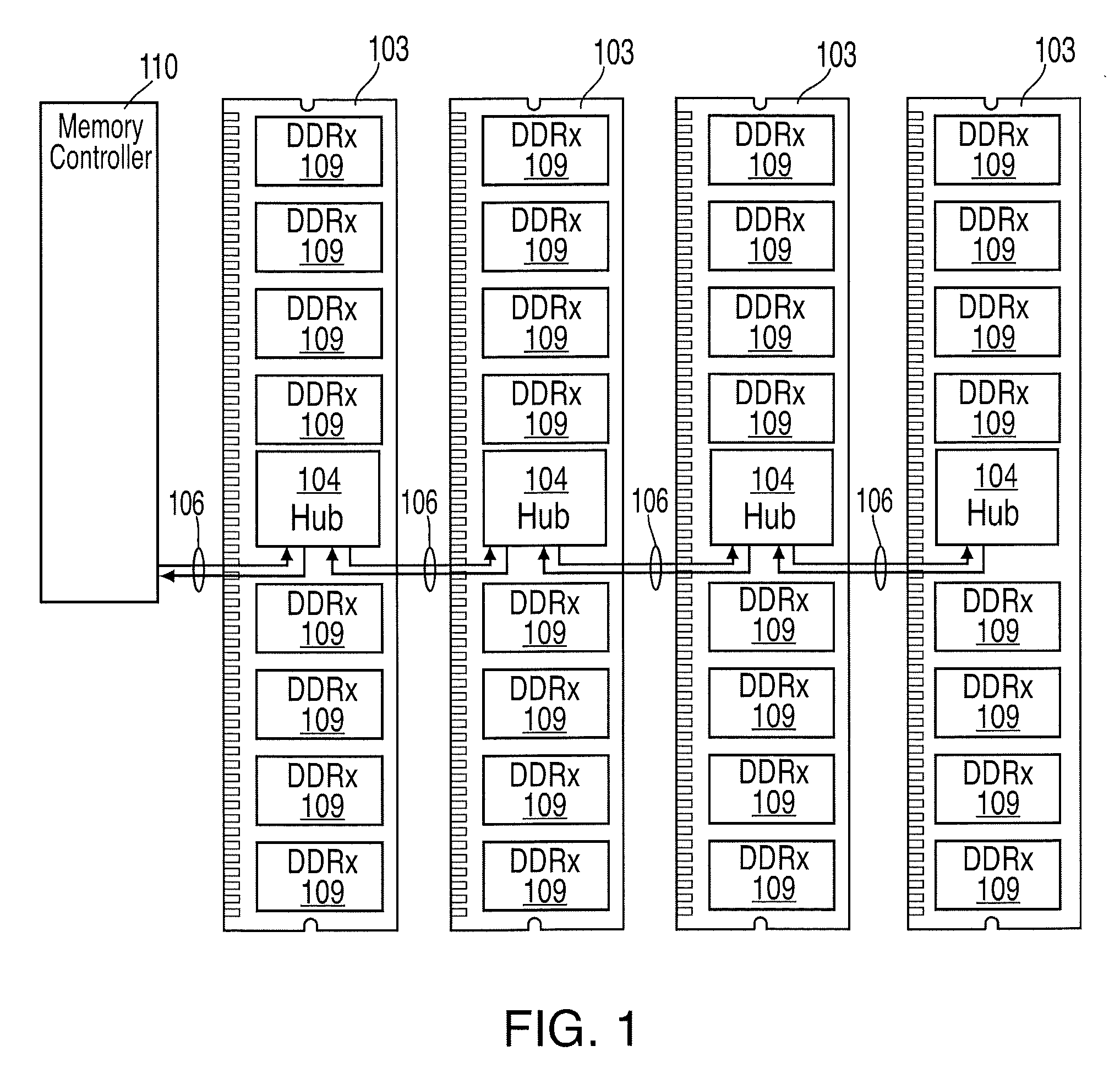

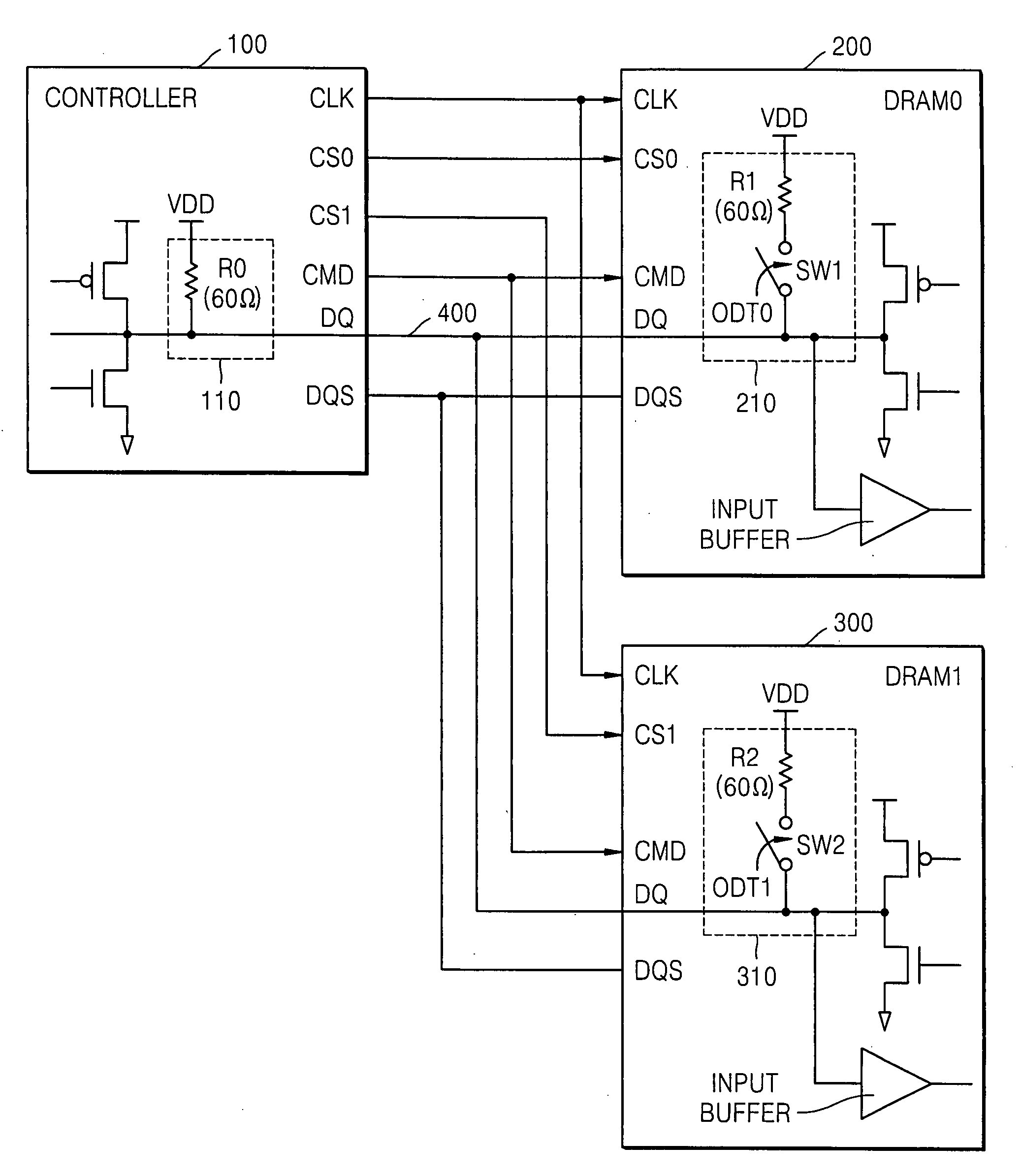

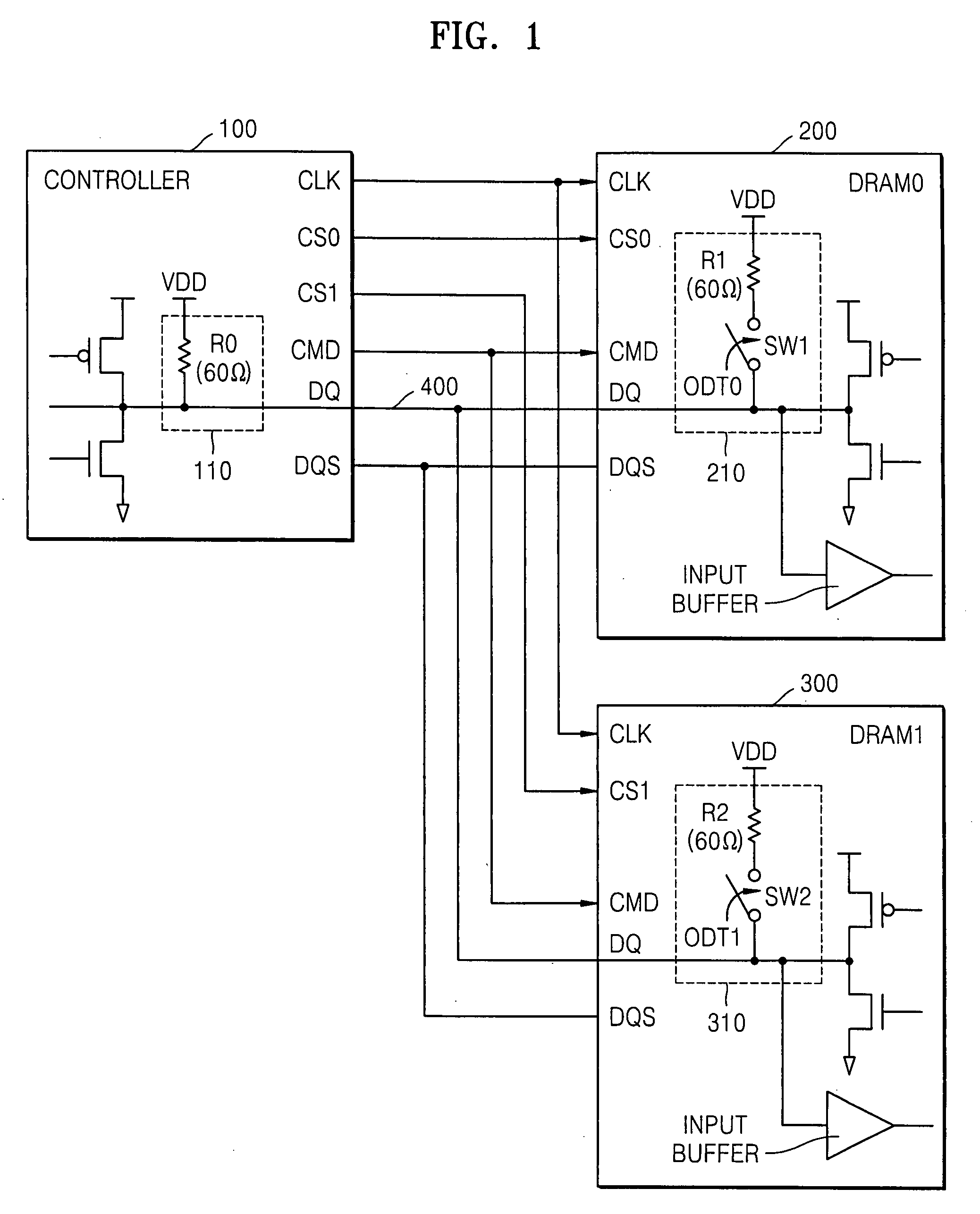

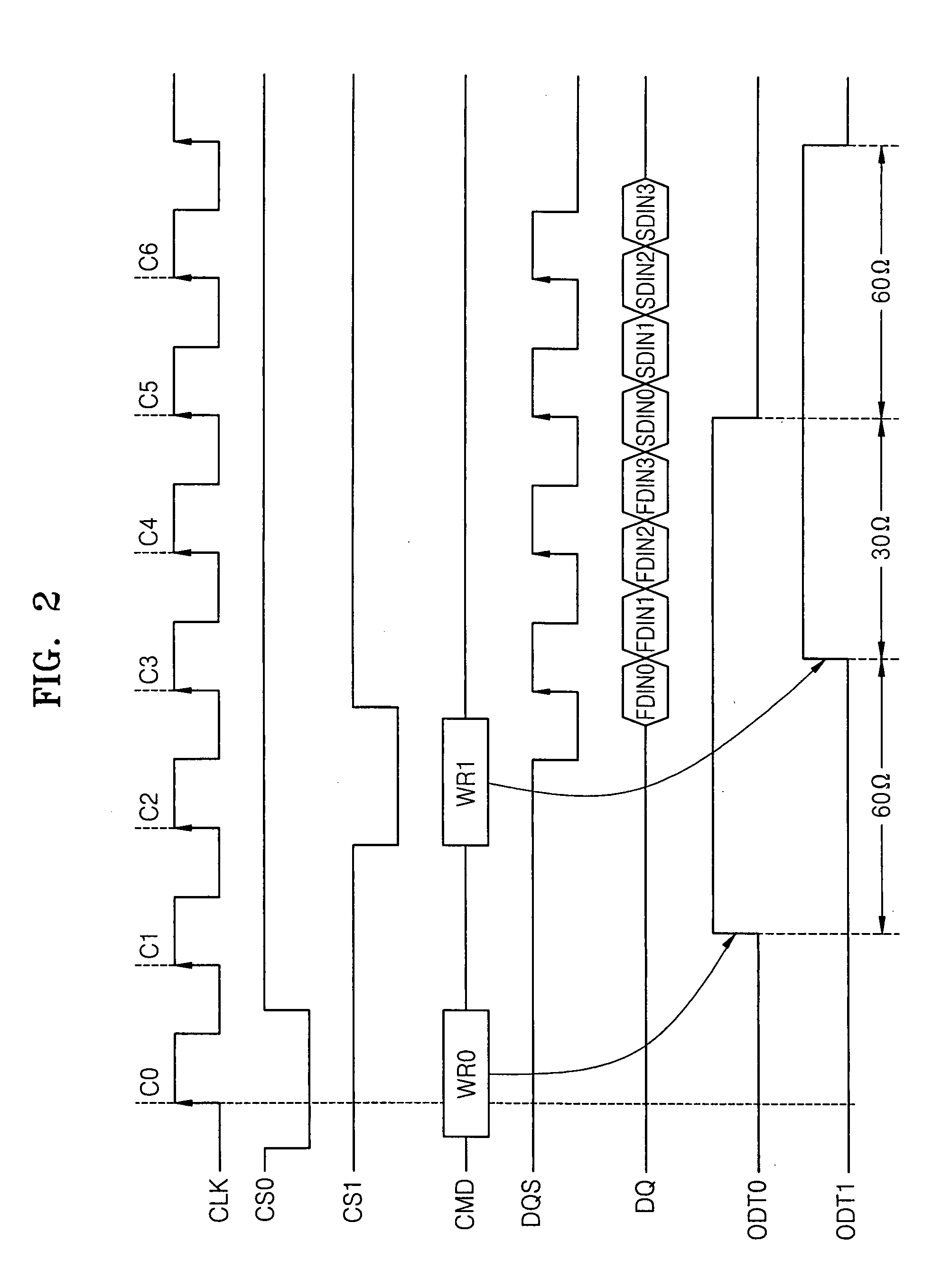

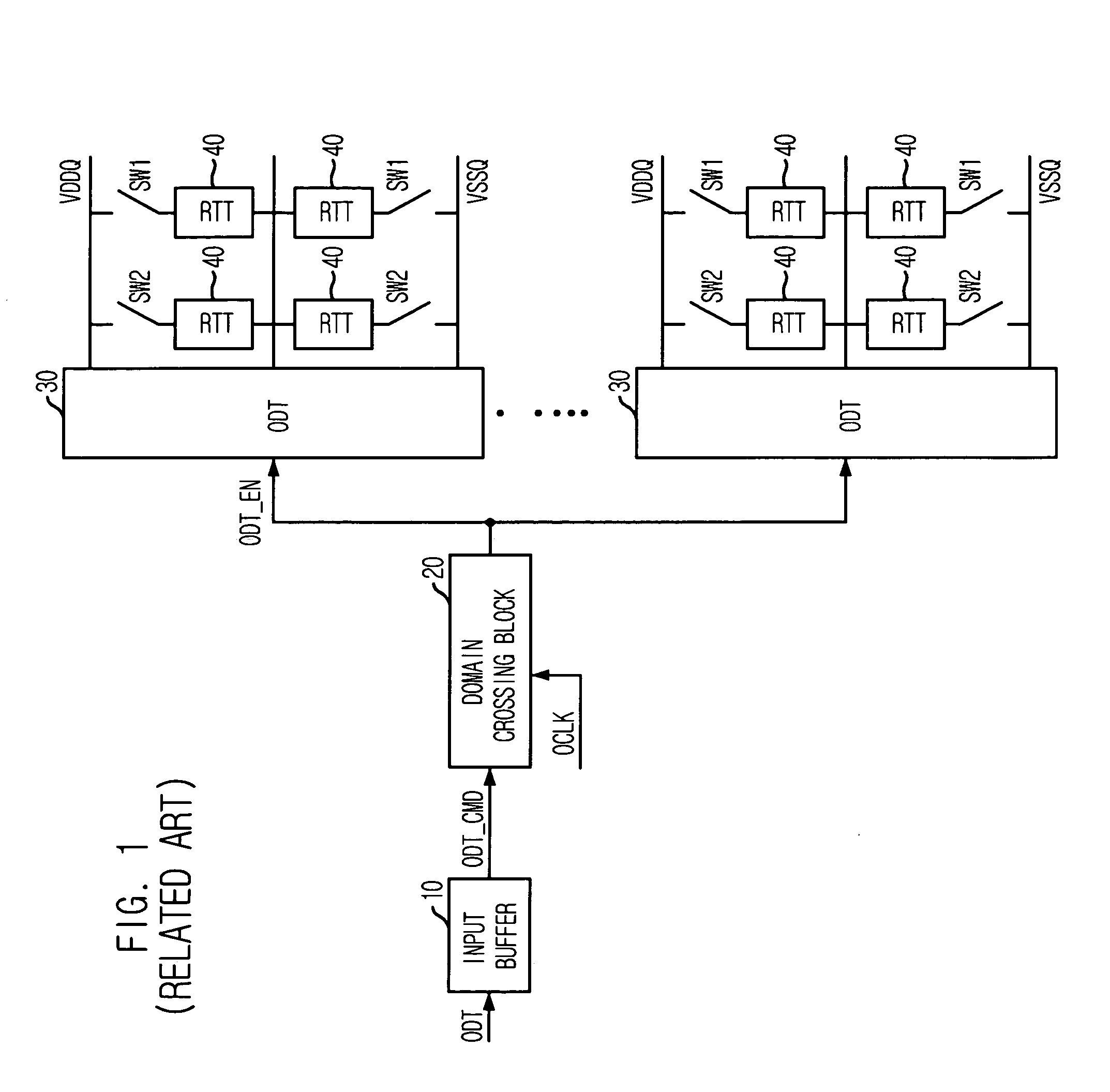

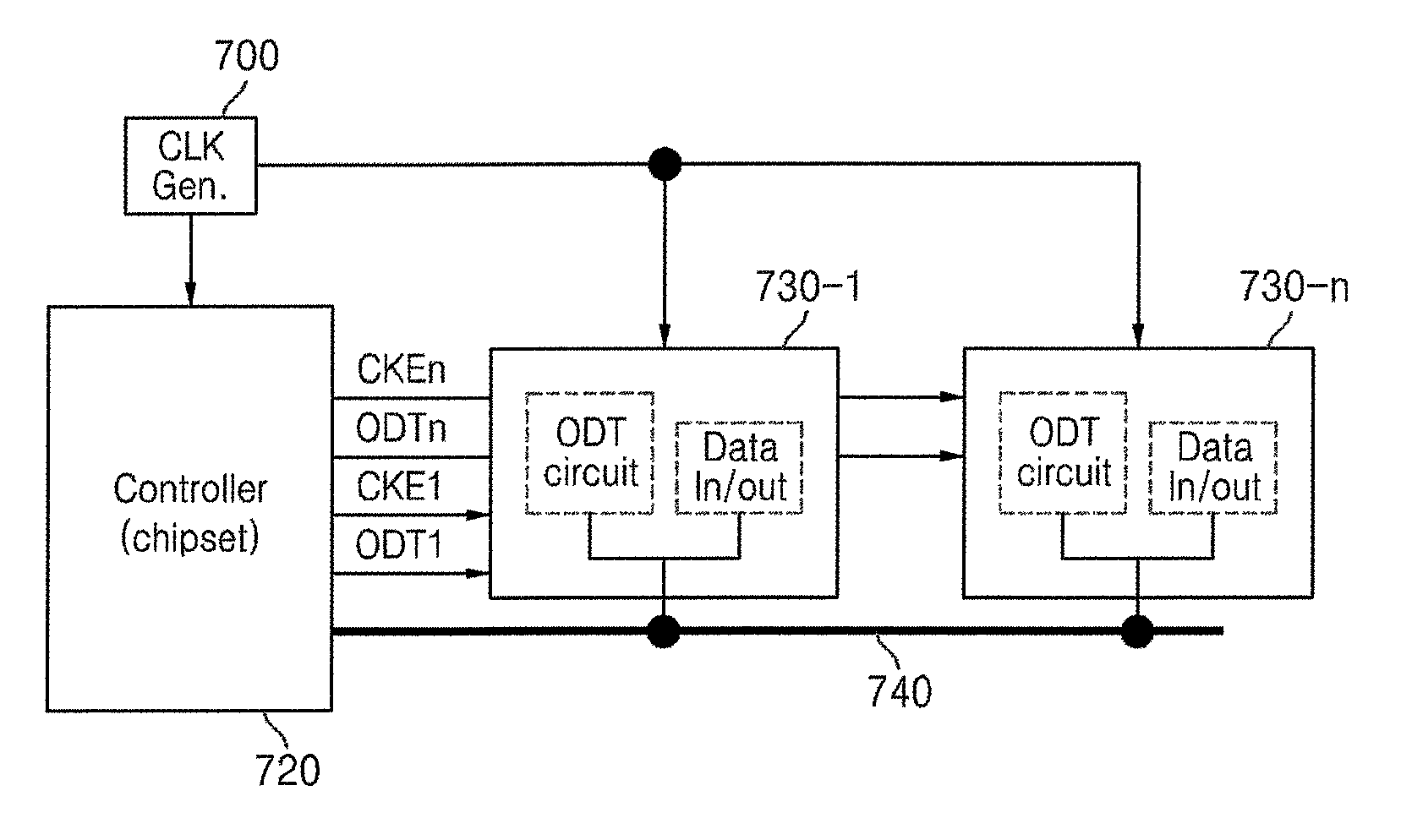

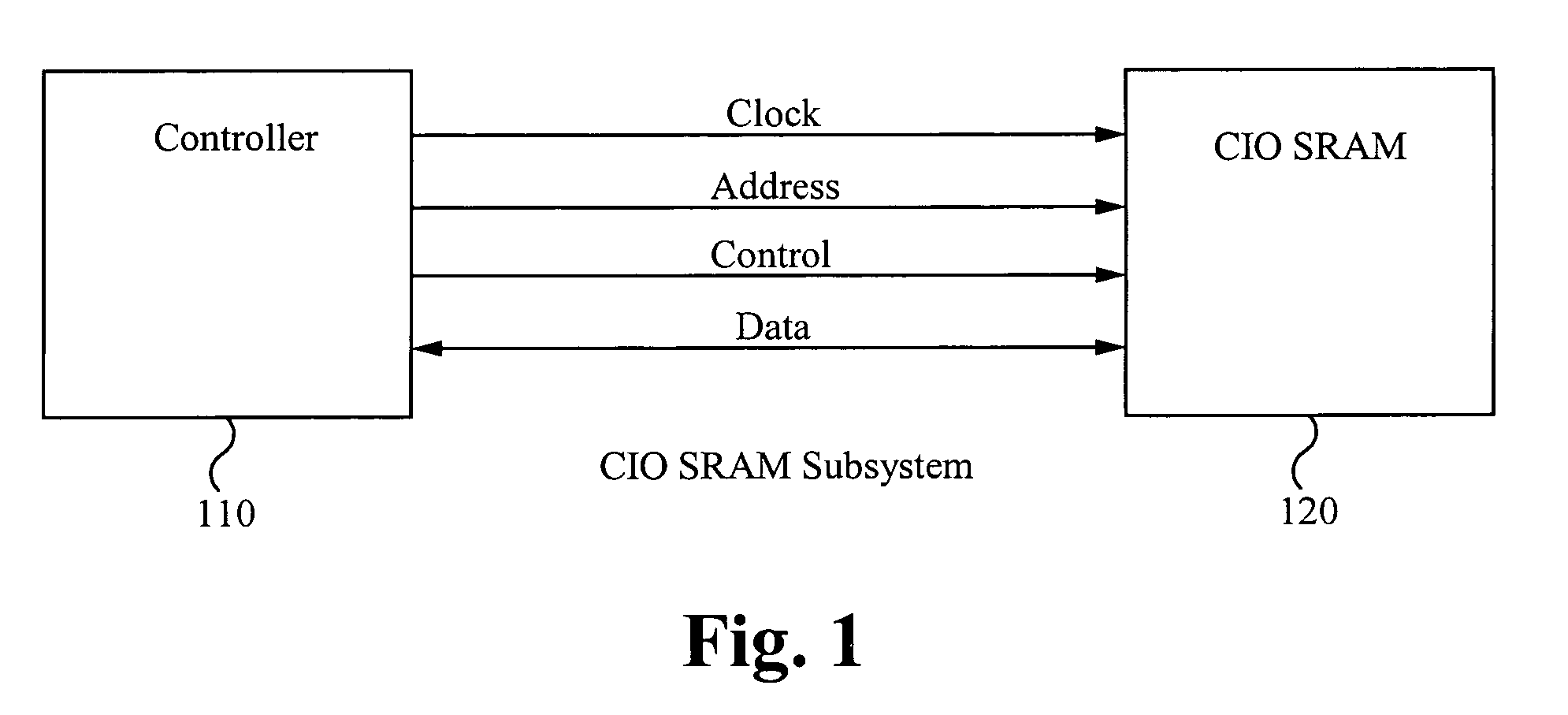

Memory module system with efficient control of on-die termination

ActiveUS20050212551A1Minimize power consumptionReliability increasing modificationsBaseband system detailsControl signalControl store

For ODT (on-die termination) control within a memory module system, just one pin from the memory controller is used for sending command signals indicating an activated one of the memory devices. The activated memory device includes components that are turned on for generating the ODT control signal for controlling an ODT circuit of inactivated memory device(s). The components for generating an ODT control signal within the inactivated memory devices are turned off for minimized power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

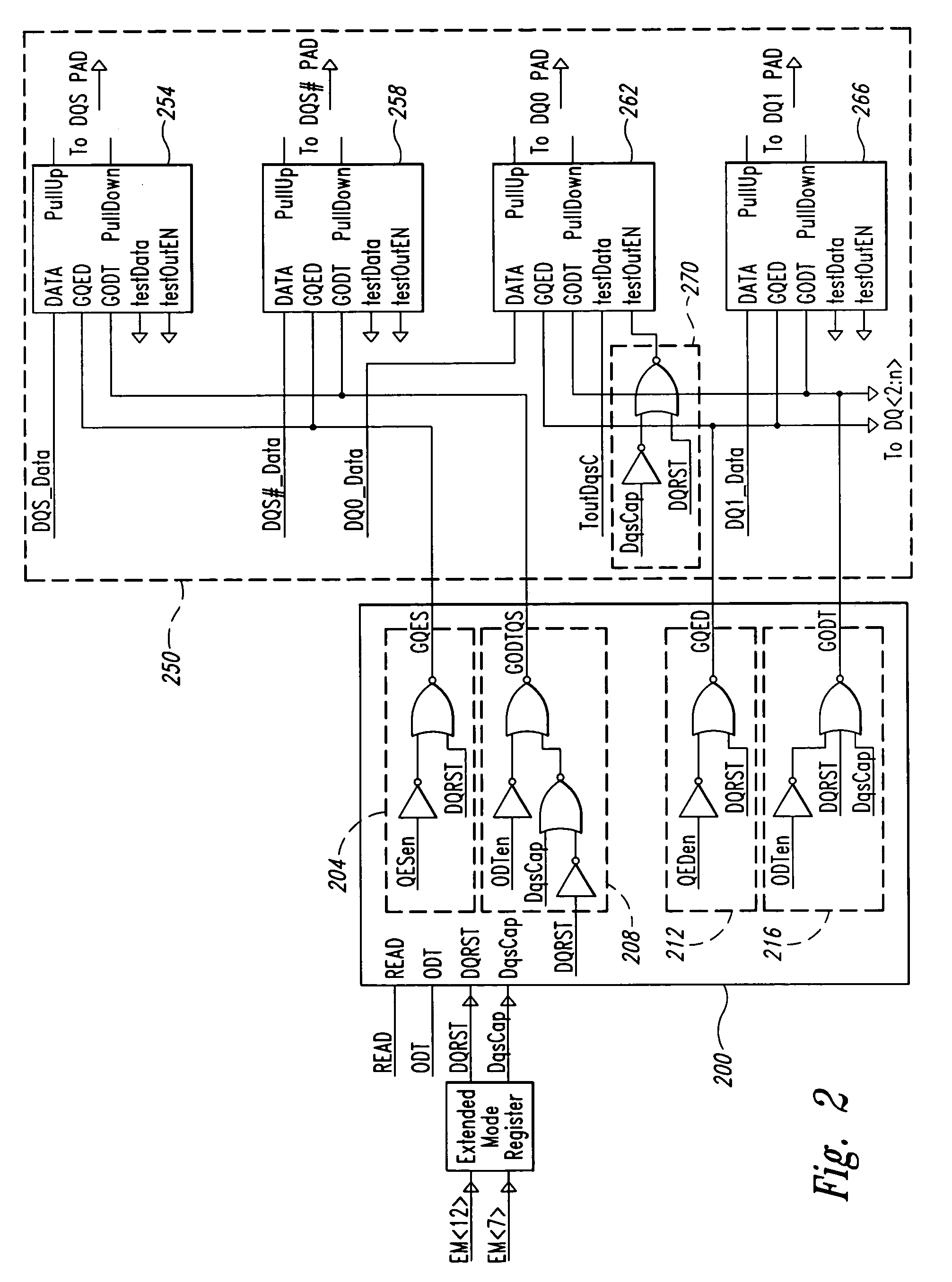

On-die termination snooping for 2T applications in a memory system implementing non-self-terminating ODT schemes

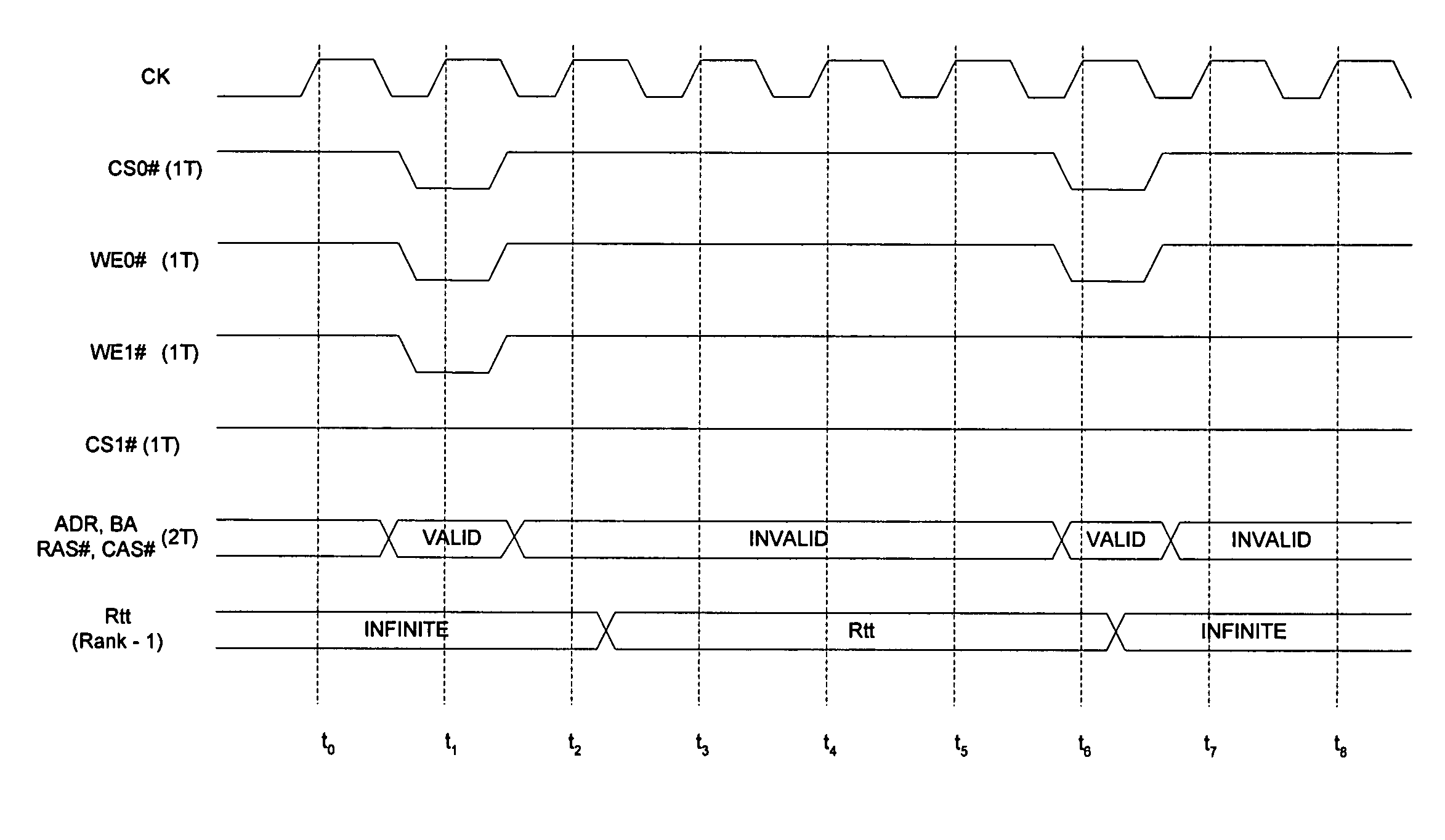

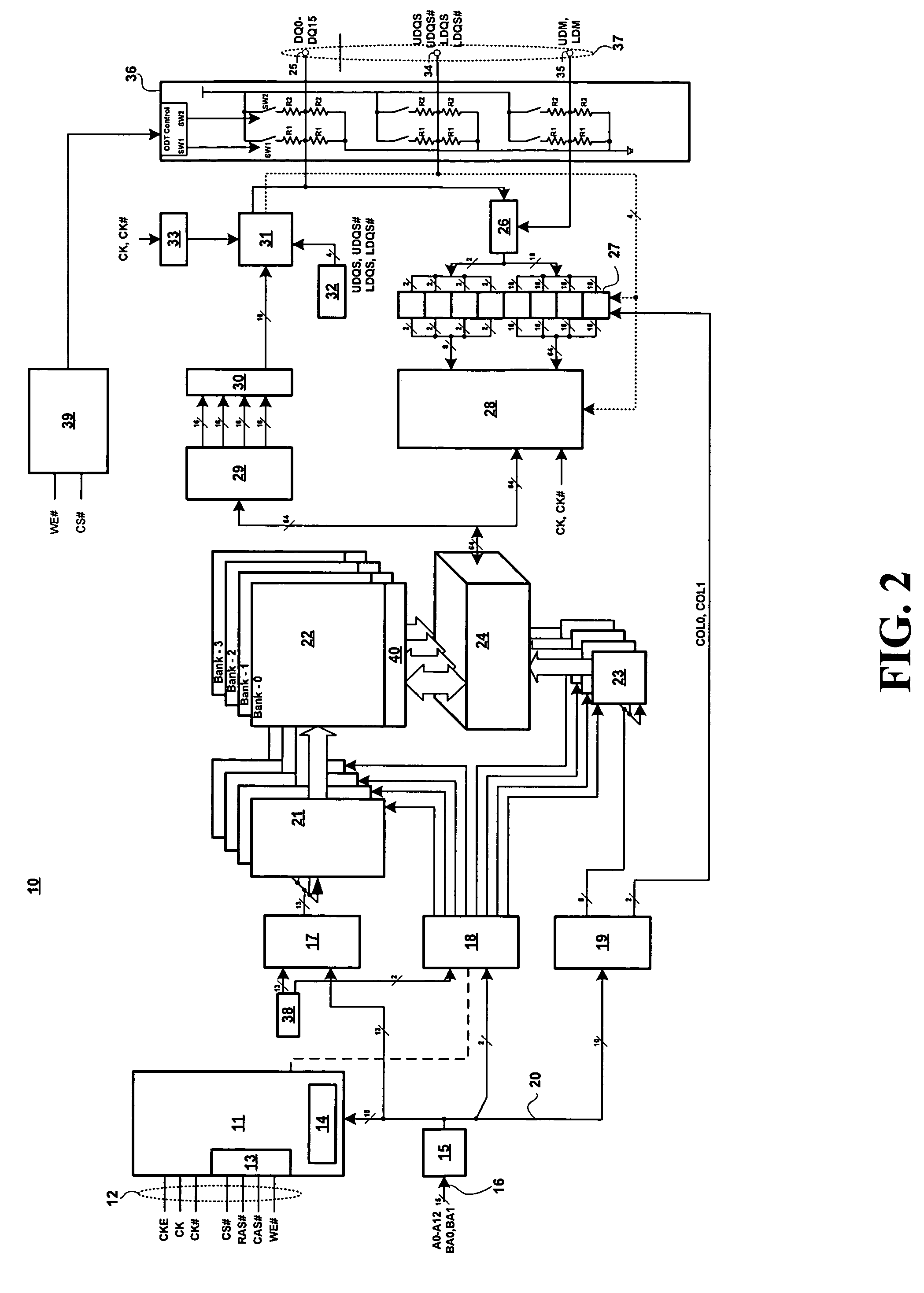

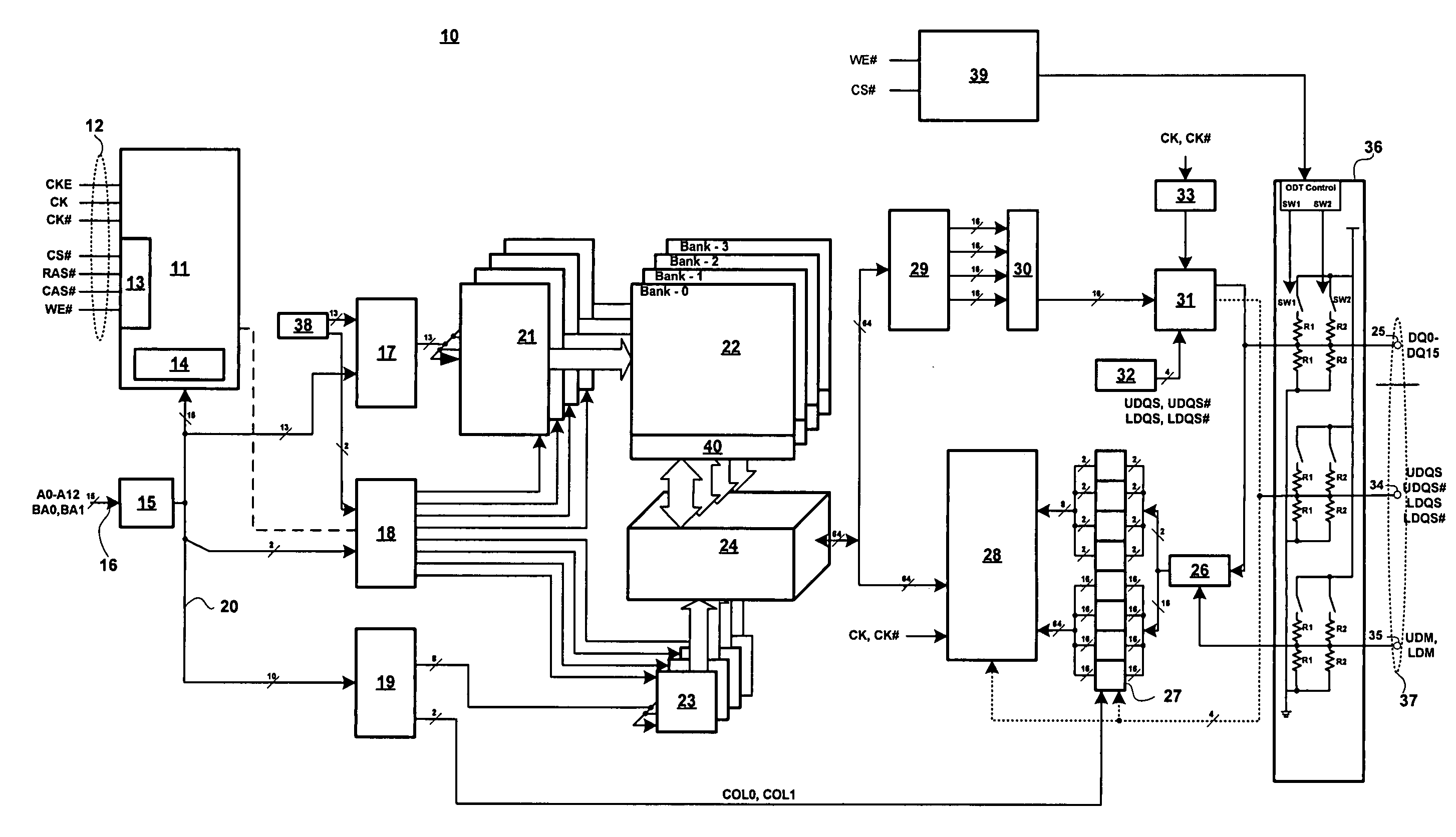

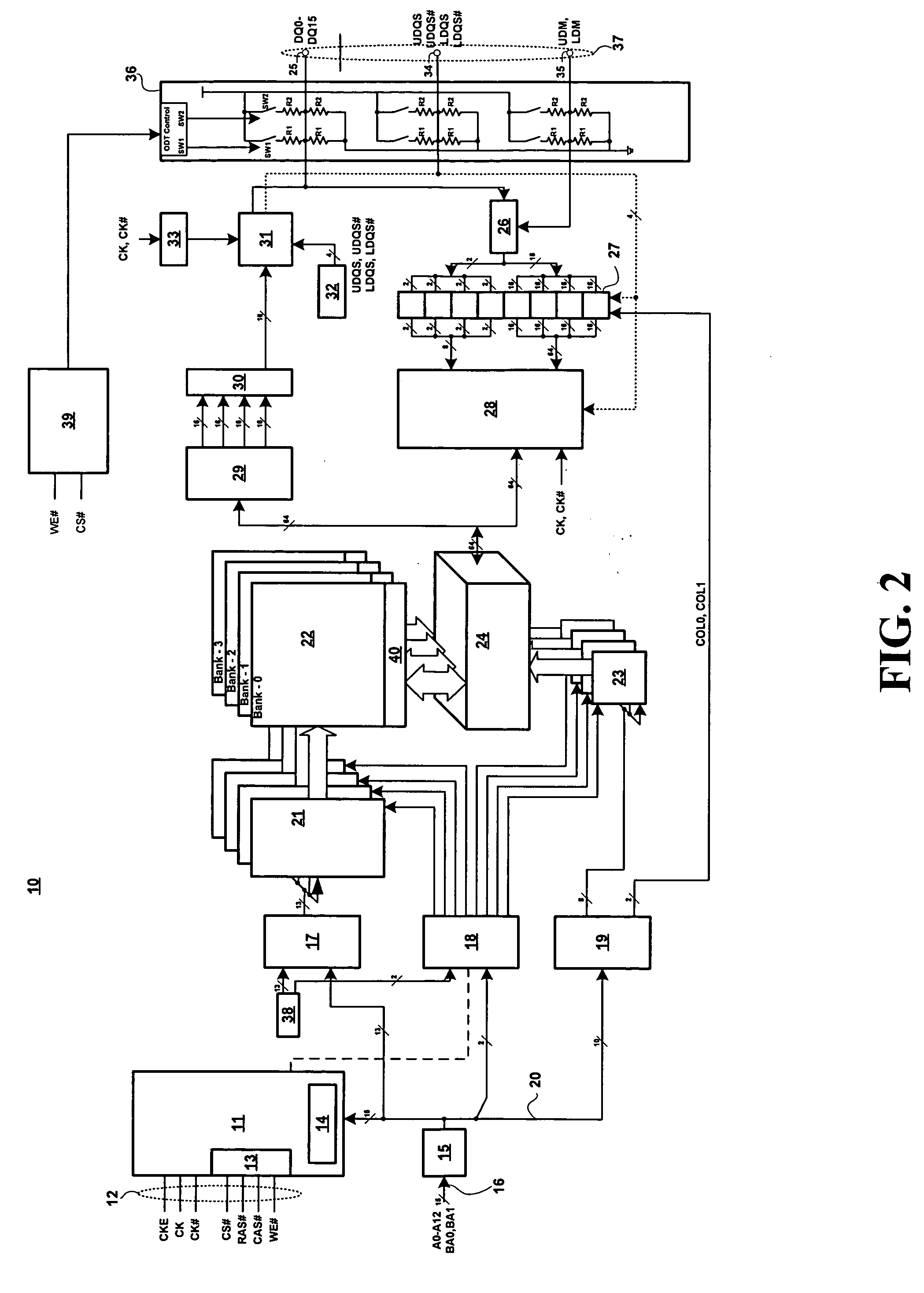

A method and apparatus for controlling the on-die termination of a memory system. The method comprises snooping a command bus in response to a first plurality of command signals clocked at 1T and enabling the on-die termination in response to a second plurality of command signals clocked at 2T and the first plurality of command signals. The apparatus may be a memory device comprising a memory array responsive to a plurality of command signals, a data bus having at least one of a data pad, a data strobe output pad, and an input data mask pad, an activation circuit responsive to certain of the plurality of command signals and operable to produce a control signal, and a termination circuit responsive to the control signal and operable to apply an effective resistance to at least one of the data pad, the data strobe output pad, and the input data mask pad.

Owner:MICRON TECH INC

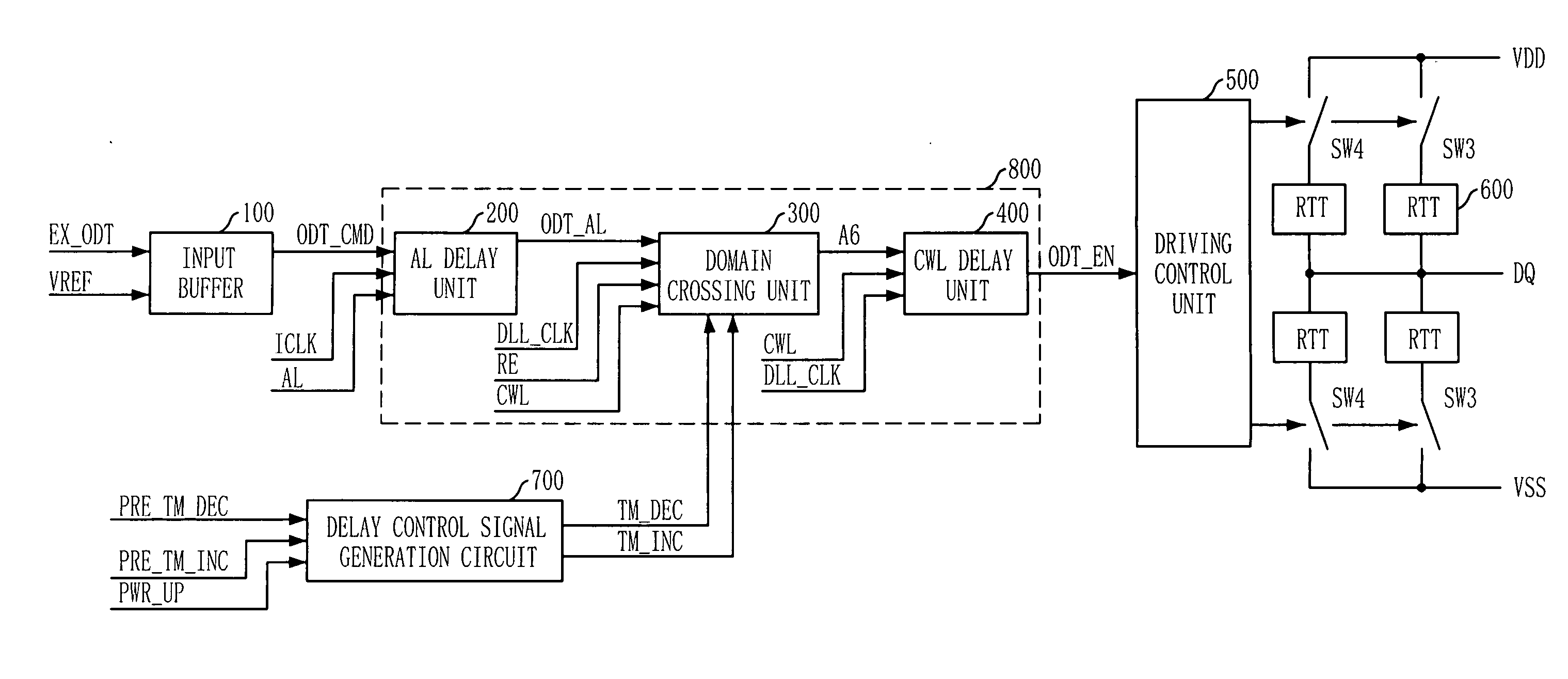

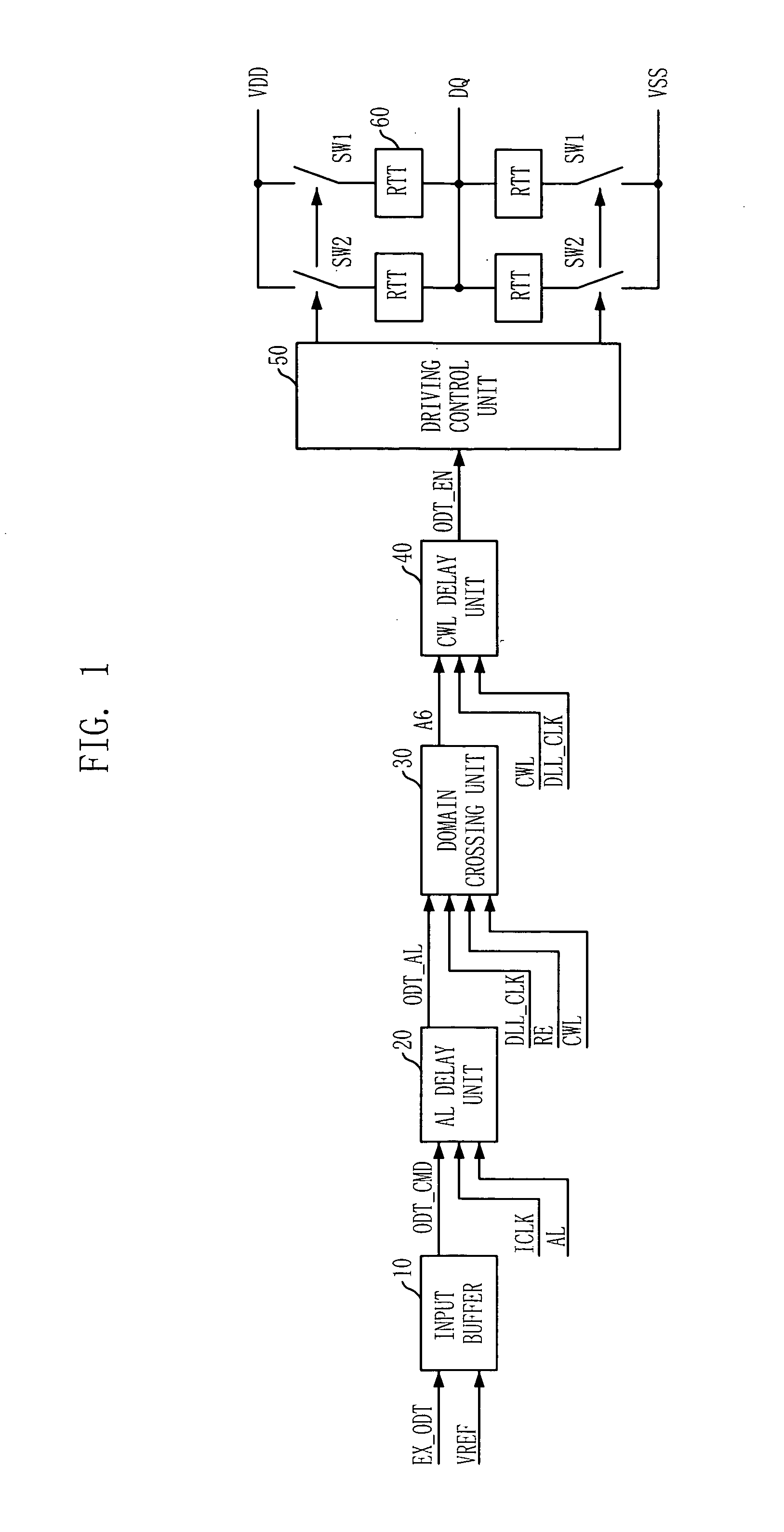

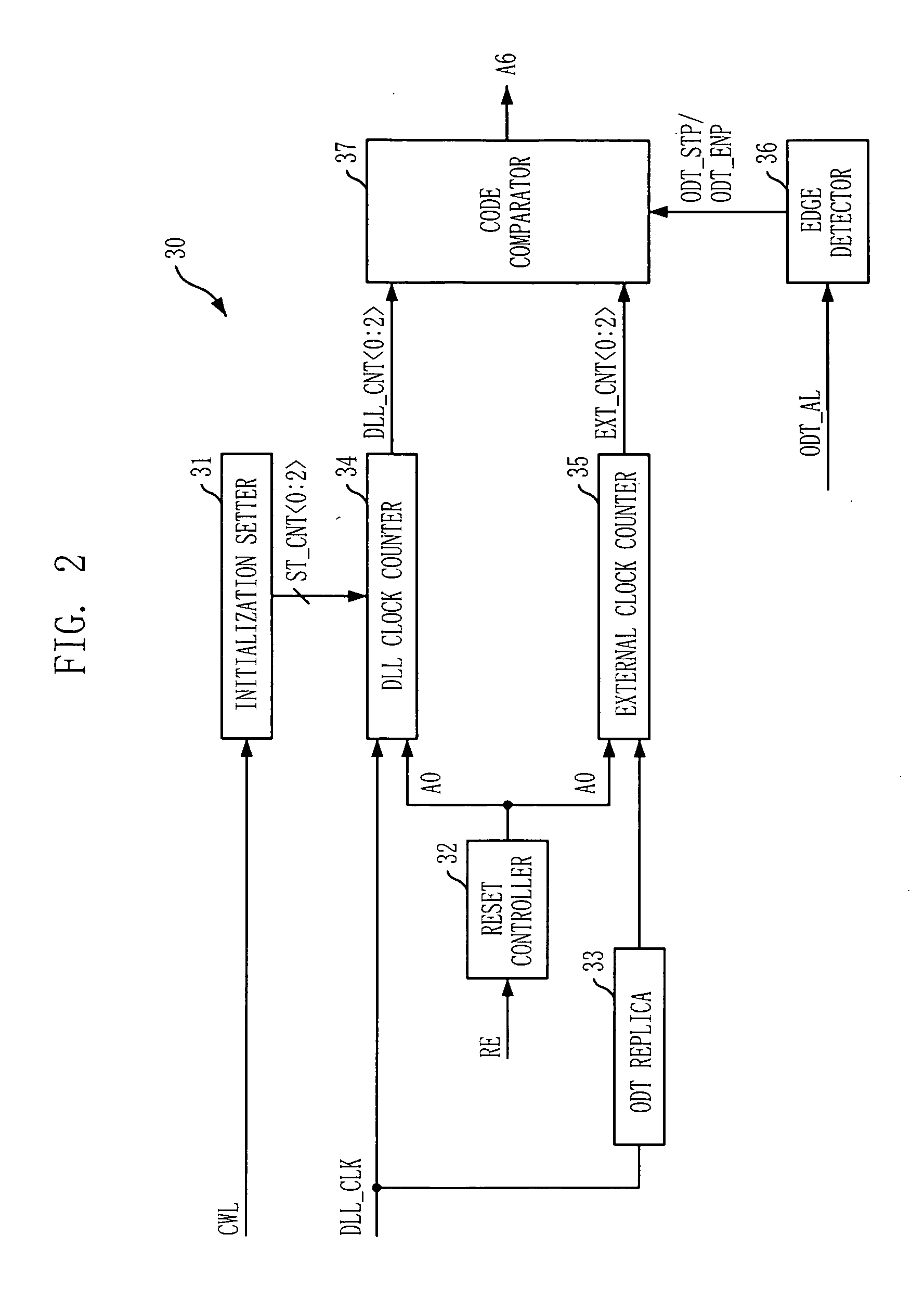

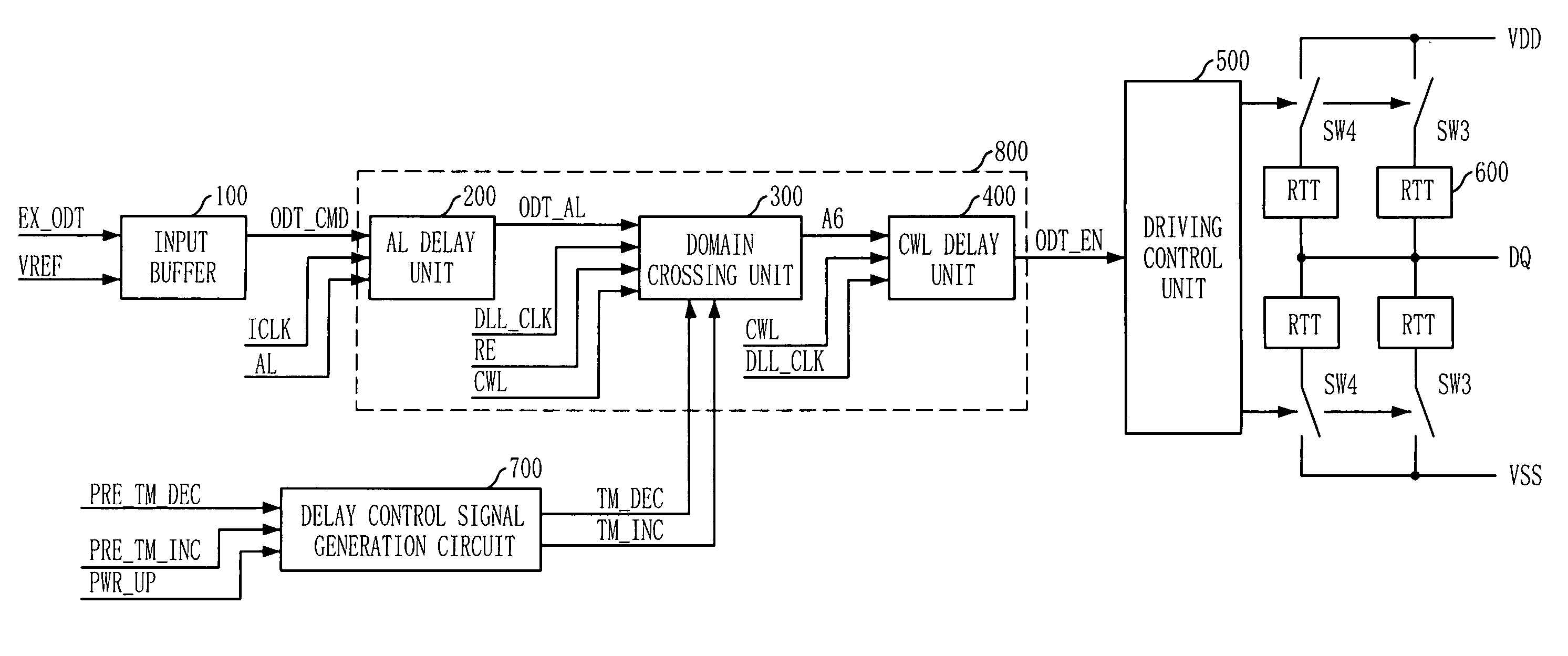

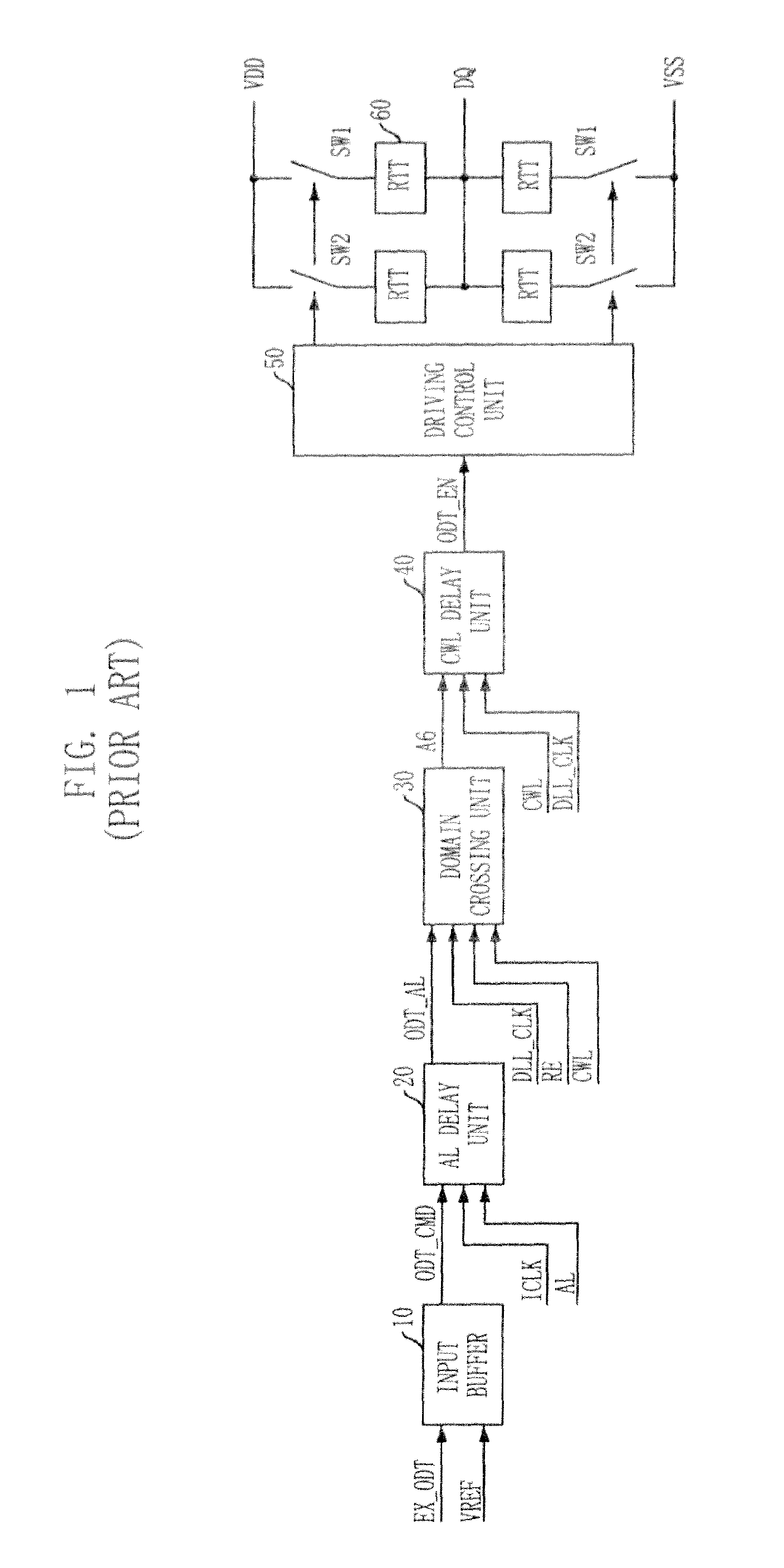

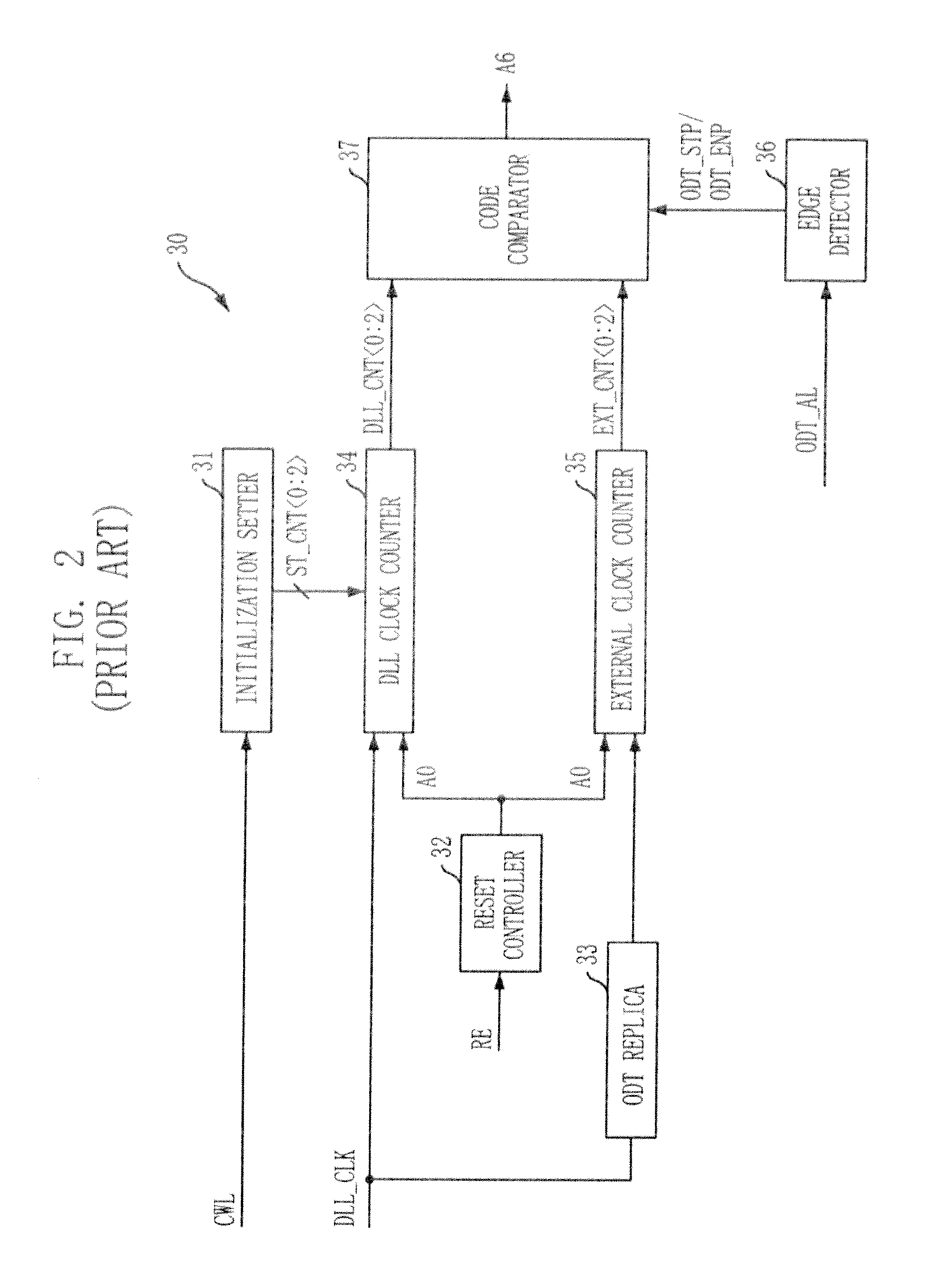

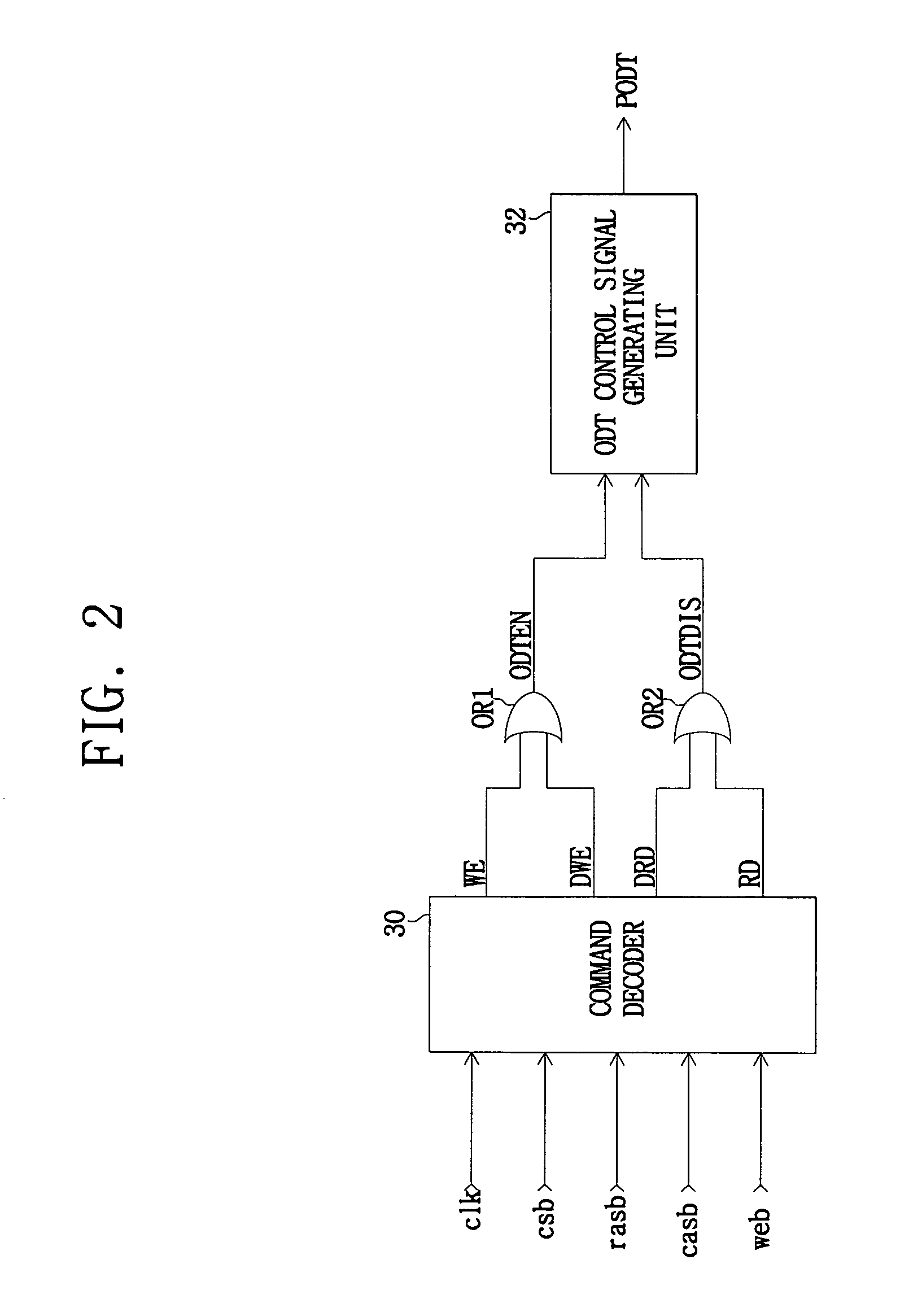

Semiconductor memory device having on-die-termination device and operation method thereof

ActiveUS20090016124A1Easy to fixLogic circuit coupling arrangementsDigital storageControl signalDelay-locked loop

A semiconductor memory device is capable of stably securing an on-die-termination (ODT) latency in spite of PVT variations and various operating speeds. The semiconductor memory device includes a plurality of termination resistors connected to an output pad in series and parallel, a drive controller, a delay path, and a delay control signal generator. The drive controller activates / inactivates the plurality of termination resistors in response to a driving control signal. The delay path delays a termination command by a delay time corresponding to an on-die-termination (ODT) latency to output the driving control signal, wherein the termination command is converted into a delay locked loop (DLL) clock domain signal. The delay control signal generator controls a conversion point of the termination command into the DLL clock domain signal.

Owner:SK HYNIX INC

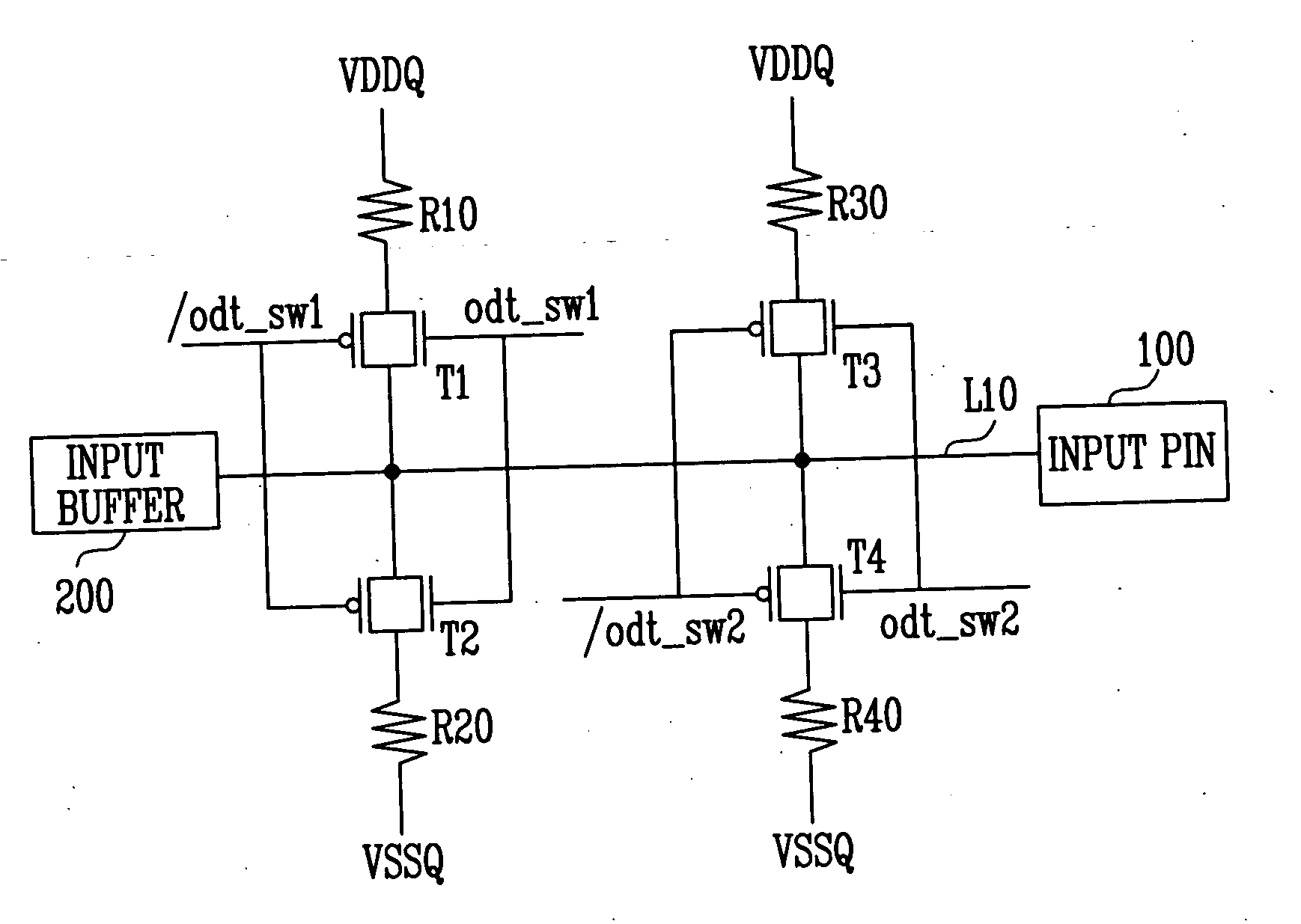

On die termination circuit

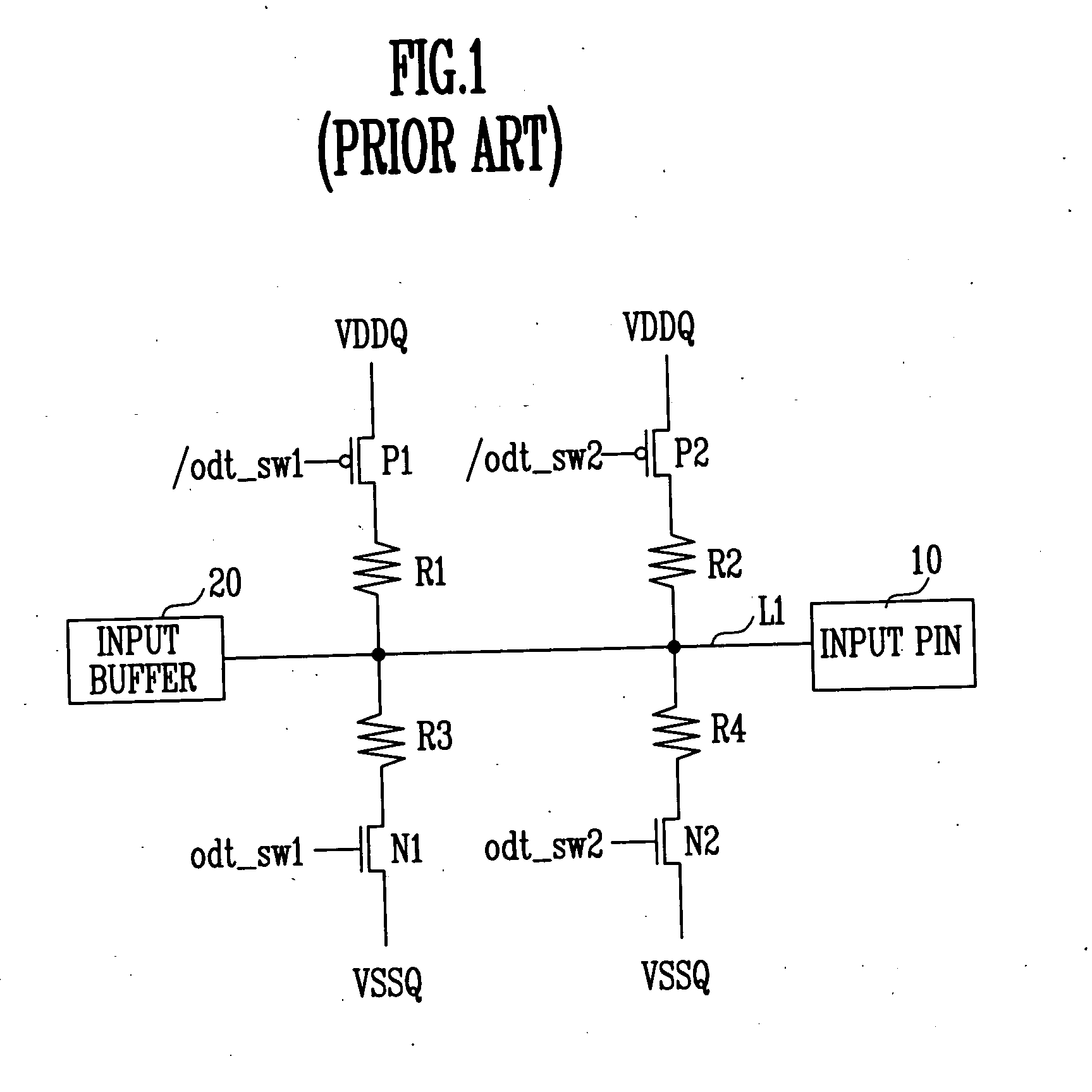

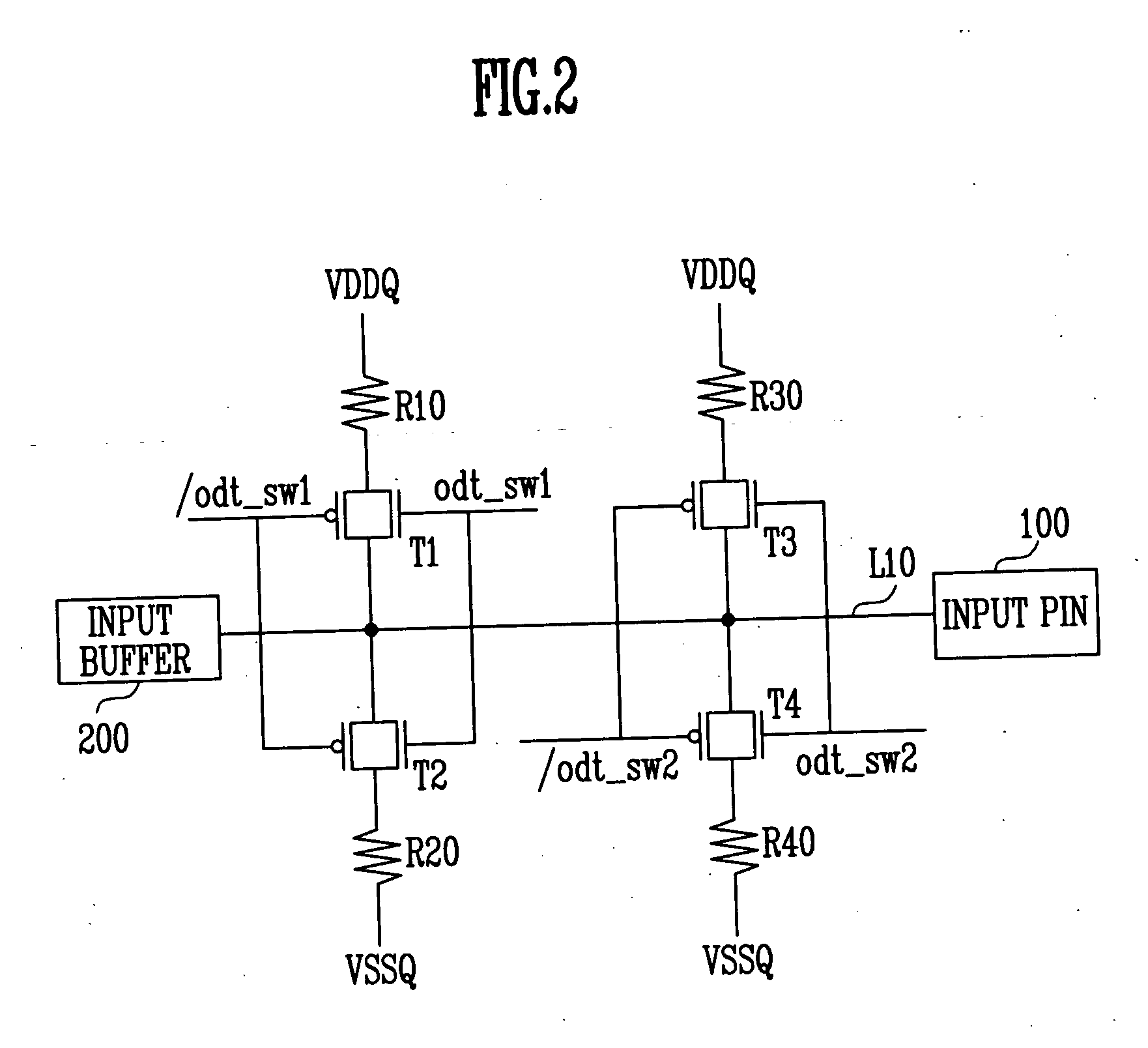

ActiveUS20050225353A1Constant voltage of an input pinEasy to operateReliability increasing modificationsLogic circuits characterised by logic functionTransmission gateOn-die termination

The present invention discloses an on die termination circuit. The on die termination circuit used in a DDR2 employs transmission gates as pull-up and pull-down switches, equalizes pull-up and pull-down resistance values by changing connection relations between switches and resistors, and maintains a constant voltage of an input pin.

Owner:SK HYNIX INC

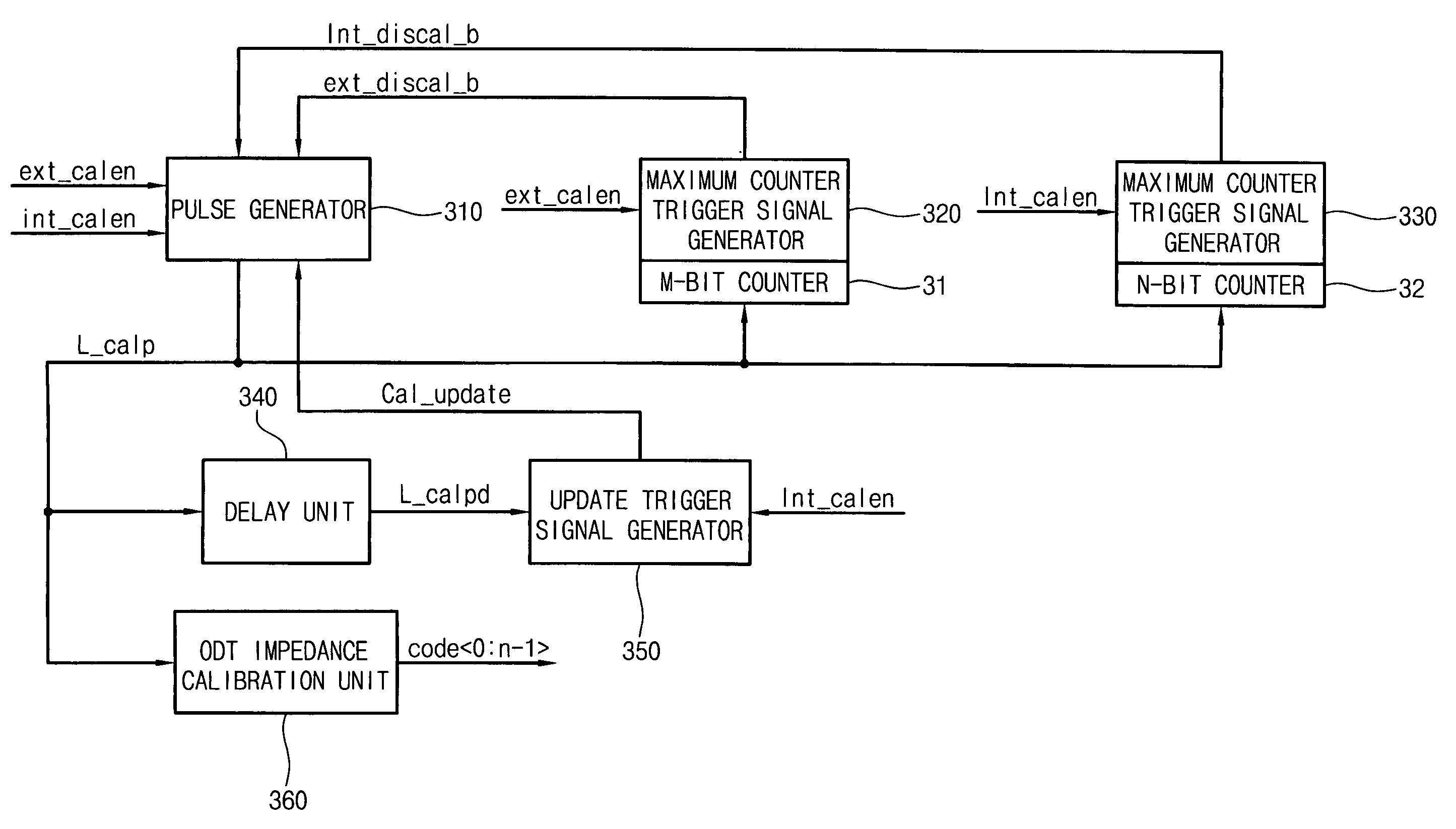

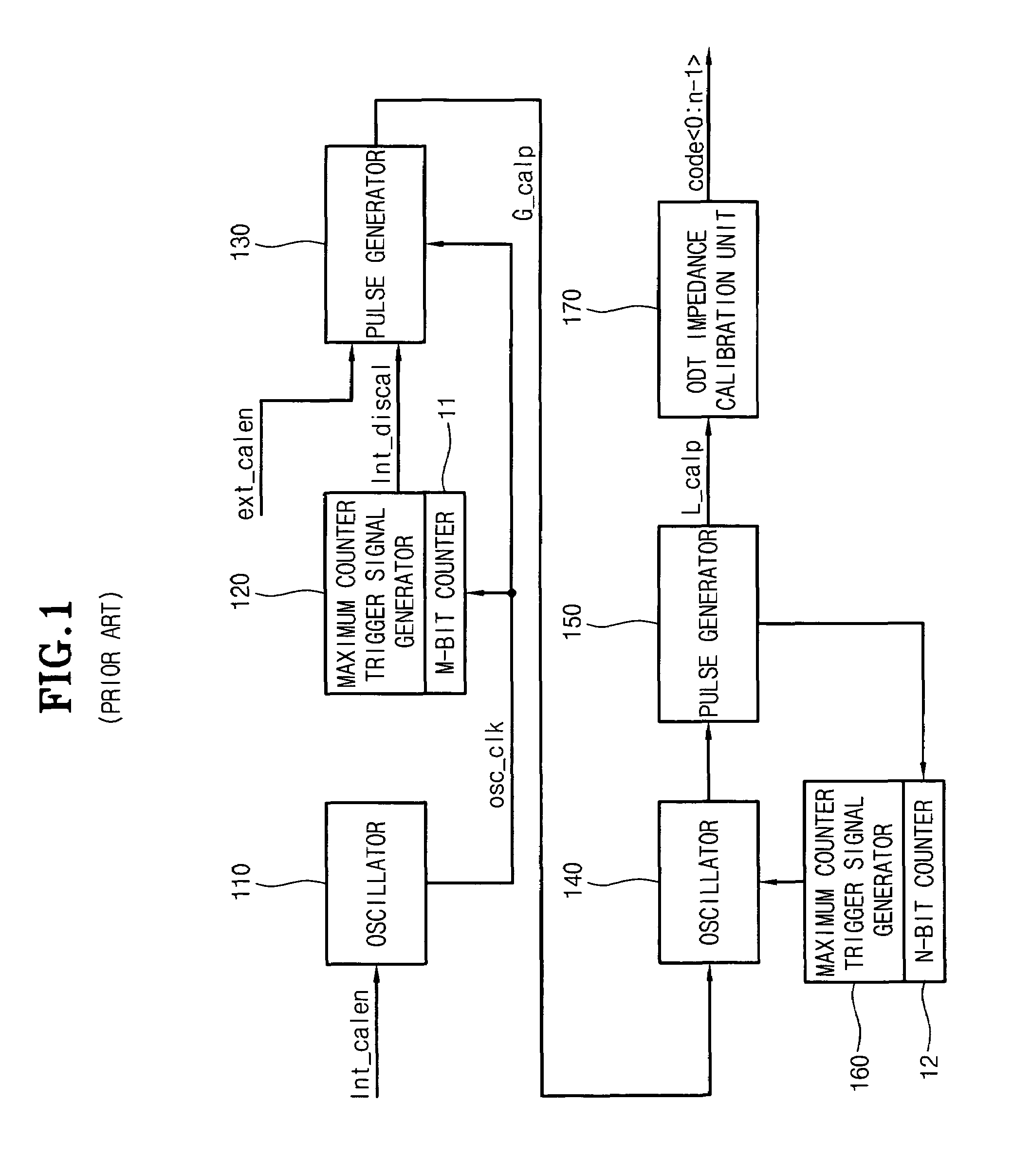

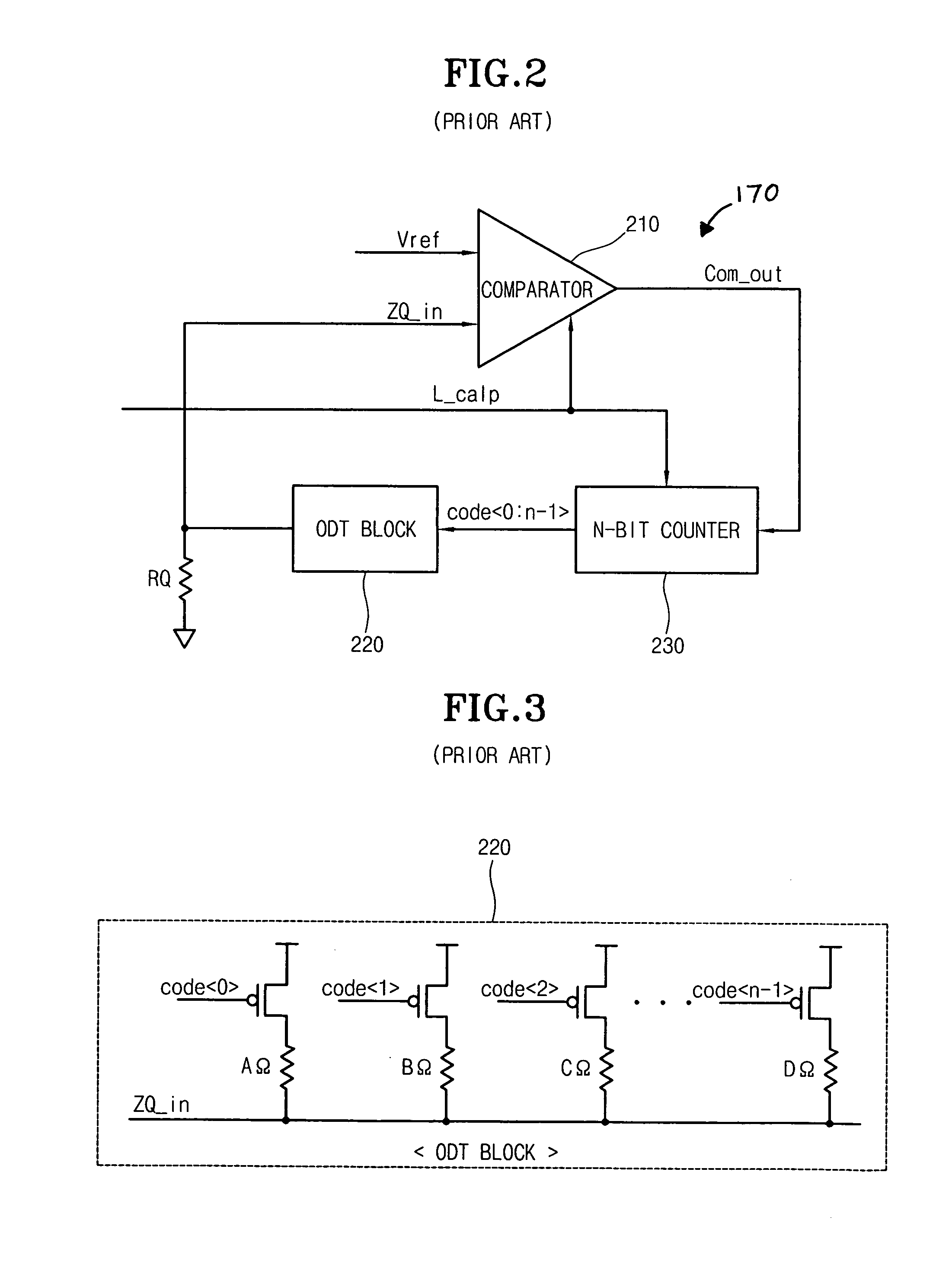

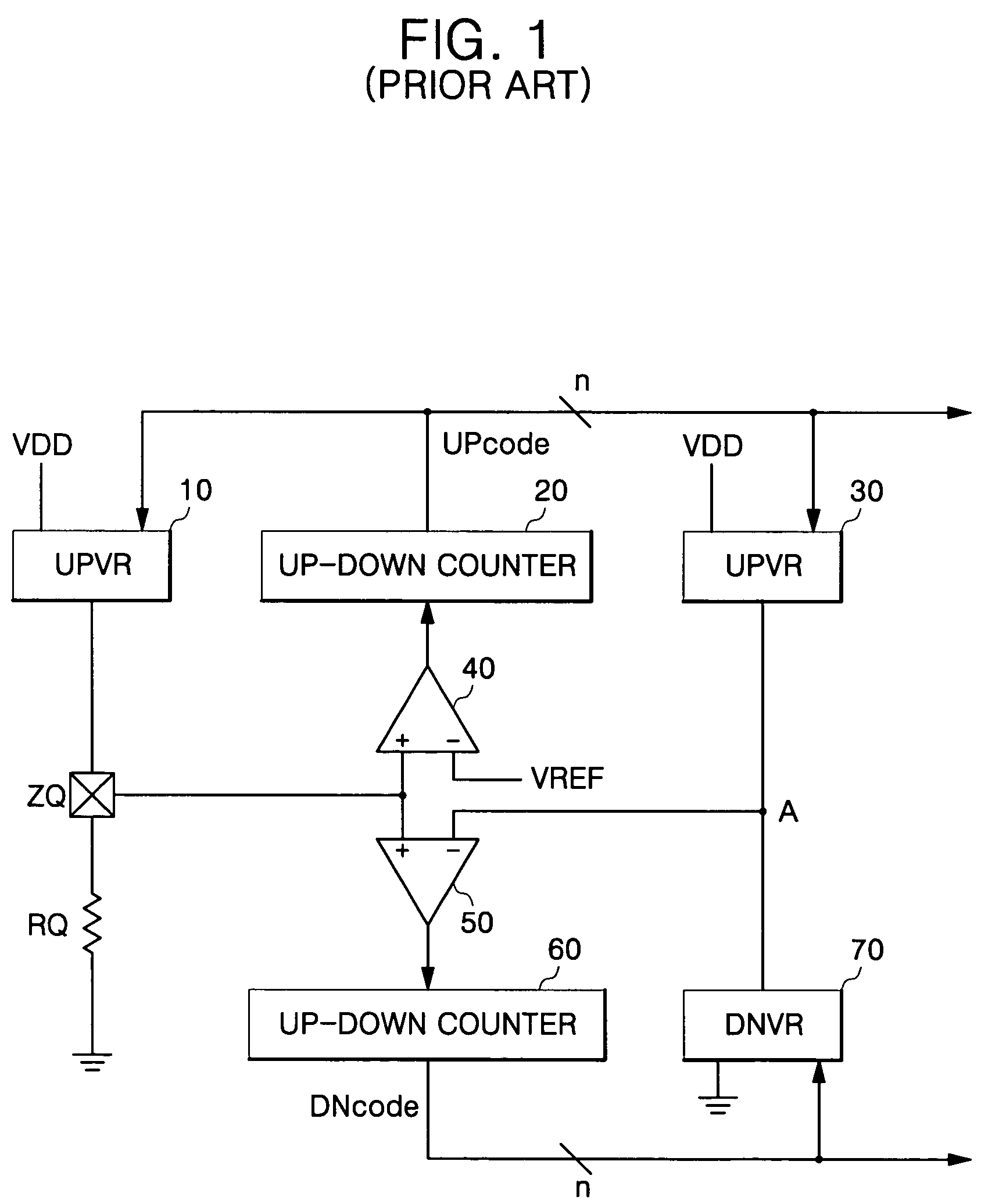

On-die termination impedance calibration device

InactiveUS7176711B2Multiple-port networksReliability increasing modificationsControl signalSignal generator

Disclosed is an on-die termination (‘ODT’) impedance calibration device. The ODT impedance calibration device comprises: a pulse generator for outputting a calibration signal of a pulse type for calibrating an ODT impedance; an M-bit counter for counting the number of pulses of the calibration signal; a first maximum counter trigger signal generator controlled by the M-bit counter; an N-bit counter for counting the number of pulses of the calibration signal; a second maximum counter trigger signal generator controlled by the N-bit counter; a delay unit for receiving a delay signal and outputting the delay signal after a predetermined period of time; an update trigger signal generator for outputting a pulse signal which is toggled according to an output signal of the delay unit; and an ODT impedance calibration unit for receiving the calibration signal and outputting a control signal for calibrating an ODT impedance.

Owner:SK HYNIX INC

Apparatus and method for independent control of on-die termination for ouput buffers of a memory device

An apparatus and method providing independent control of on-die termination (ODT) of output buffers. The ODTs for the buffer circuits of an input / output (I / O) buffer can be enabled and disabled in response to an ODT control signal. Additionally, the ODTs for a first set of the buffer circuits can be enabled and disabled responsive to the ODT control signal and the ODT for at least one of a second set of the buffer circuits is disabled.

Owner:ROUND ROCK RES LLC

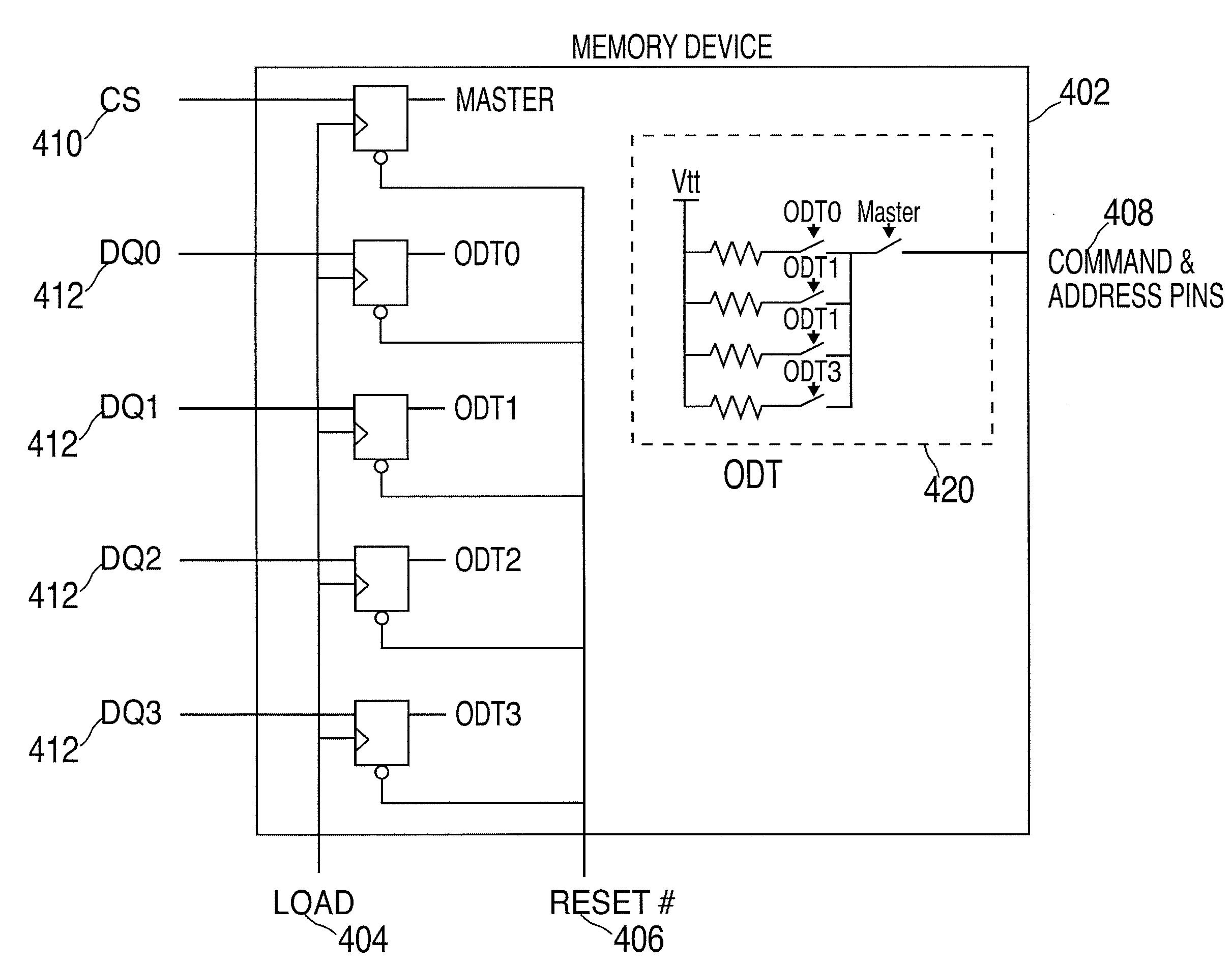

System for providing on-die termination of a control signal bus

ActiveUS20090273960A1Reliability increasing modificationsElectronic switchingControl signalControl bus

A system for providing on-die termination (ODT) of a control signal bus. The system includes a memory device that includes a plurality of data bus connectors, one or both of a load signal connector and a reset signal connector, a control bus connector, an ODT, and a mechanism. The ODT is in communication with the control bus connector, and the ODT provides a level of termination resistance to a control bus connected to the control bus connector. The mechanism latches data received via the data bus connectors in response to a signal received via one or both of the load signal connector and the reset signal connector. The data is utilized to set the level of termination resistance provided by the ODT.

Owner:GLOBALFOUNDRIES US INC

Semiconductor memory device having on-die-termination device and operation method thereof

ActiveUS7663946B2Easy to fixLogic circuit coupling arrangementsDigital storageControl signalDelay-locked loop

Owner:SK HYNIX INC

Memory module and impedance calibration method of semiconductor memory device

Disclosed is a memory module and a method of calibrating an impedance of a semiconductor memory device of the memory module, where the memory module includes semiconductor memory devices each having a separate terminal for calibrating impedance characteristics, and a reference resistor commonly connected to the separate terminals, such that the number of reference resistors used in calibration of impedance characteristics of an off-chip driver or an on-die termination circuit of the semiconductor memory device is reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

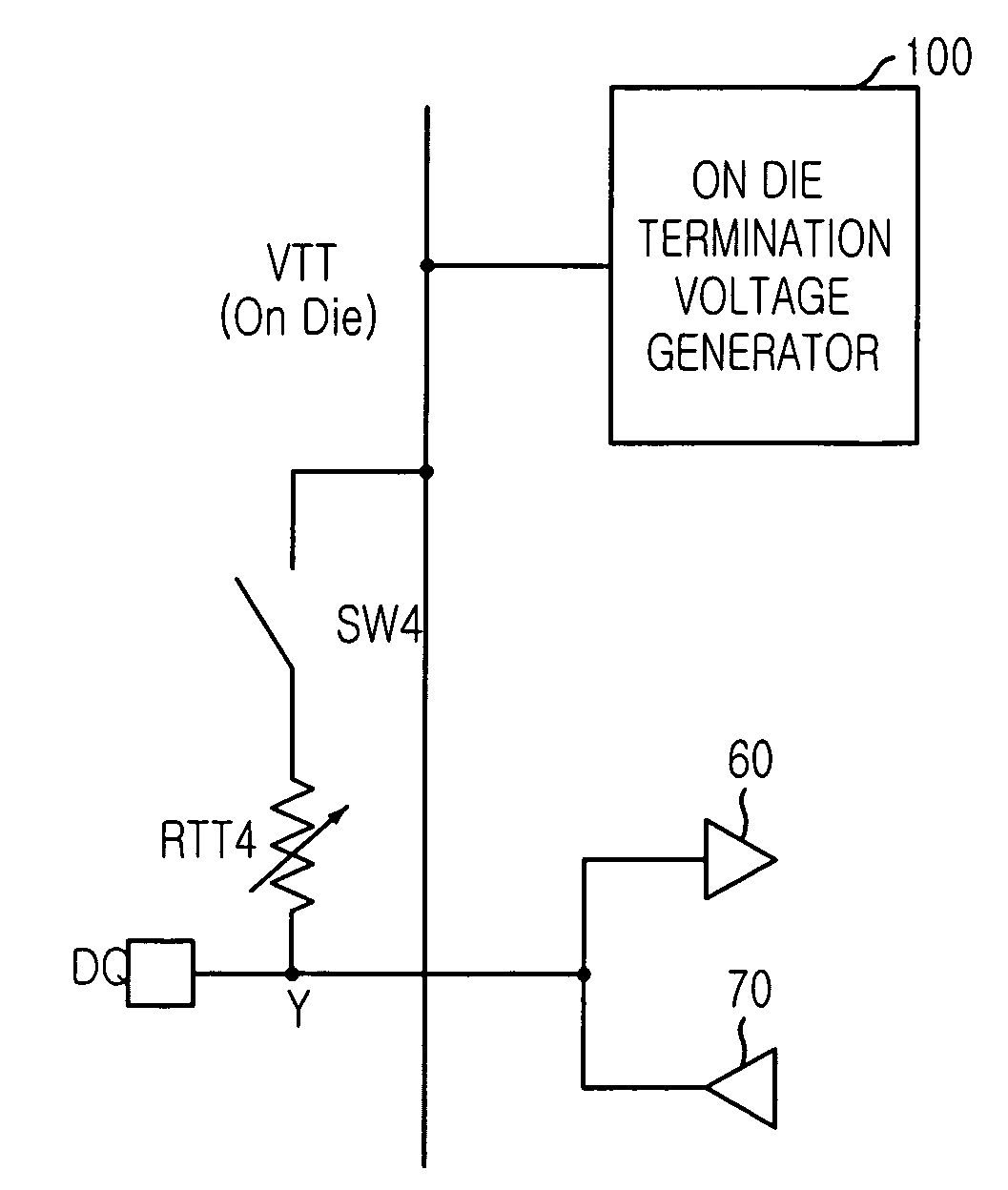

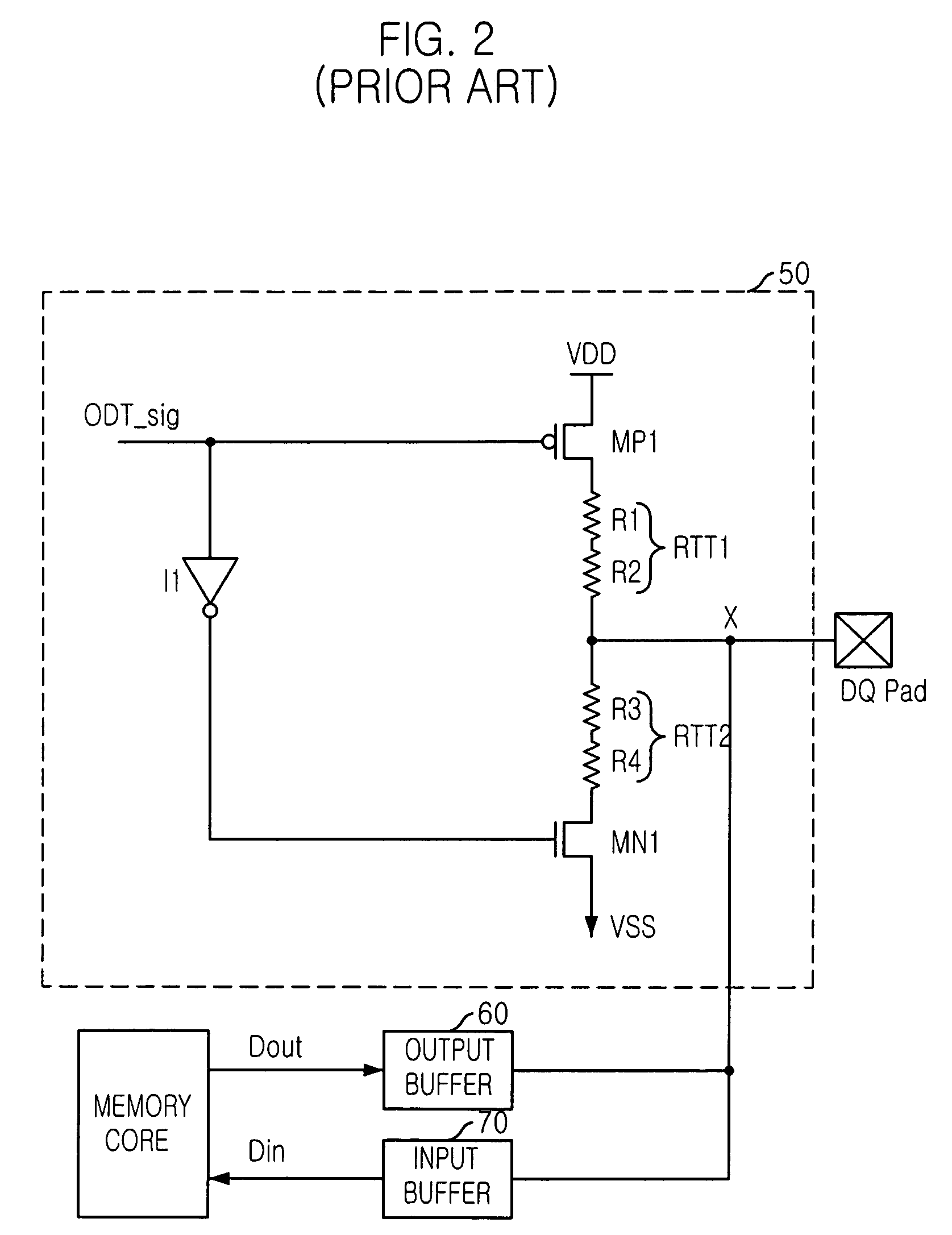

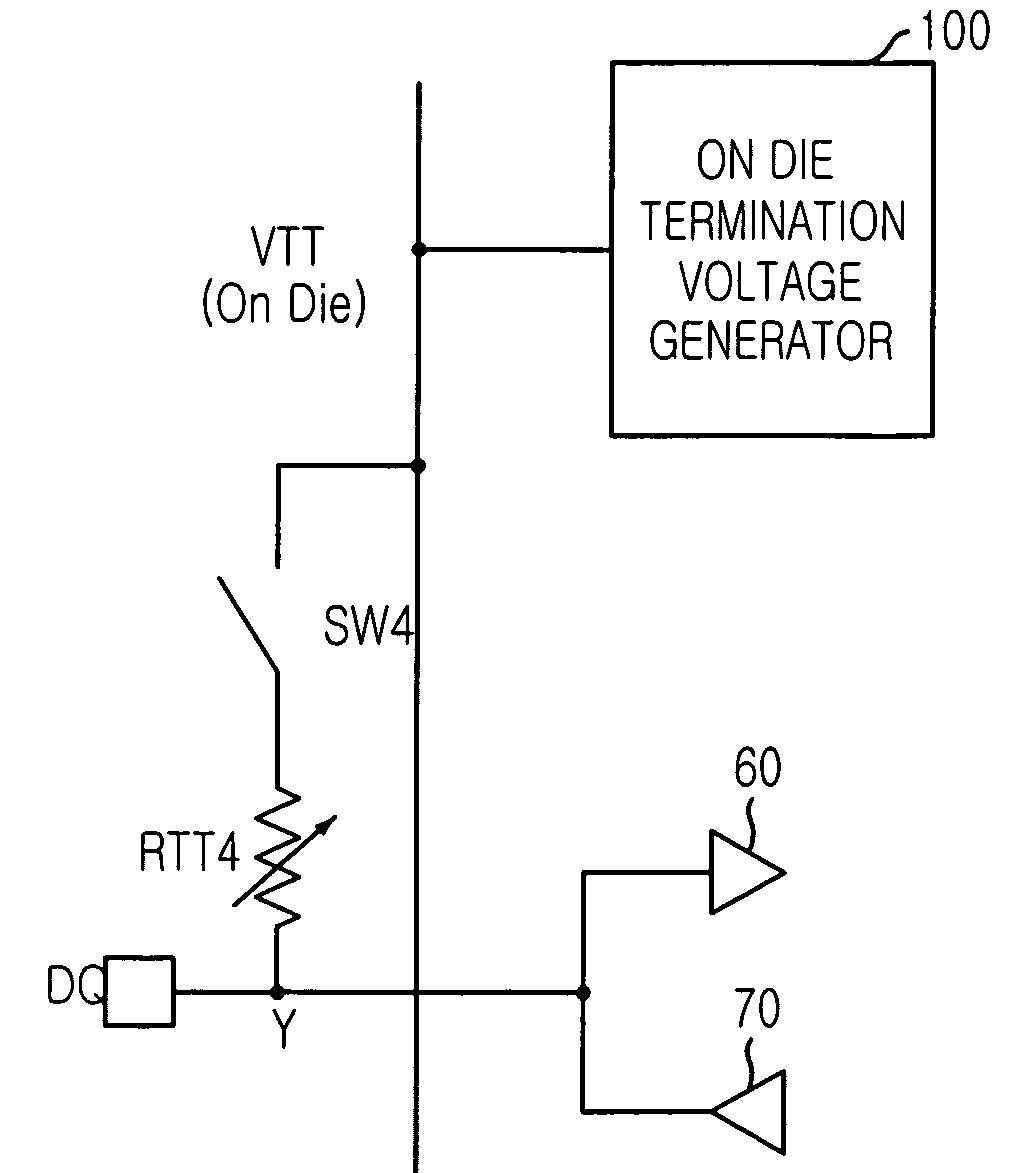

Semiconductor memory device with on die termination circuit

InactiveUS20060091900A1Reduce power consumptionReliability increasing modificationsElectronic switchingSemiconductorOn-die termination

A semiconductor memory device having a data input / output pad connected to a data input node includes: an on die termination resistor one end of which is connected to the data input node; and a switch one end of which is connected to the other end of the on die termination resistor for connecting / disconnecting the on die termination resistor with an on die termination voltage.

Owner:SK HYNIX INC

Method of controlling on-die termination of memory devices sharing signal lines

ActiveUS20080030221A1Input/output impedence modificationReliability increasing modificationsControl memoryOn-die termination

A method of controlling On-Die Termination (ODT) resistors of memory devices sharing signal lines is provided. The ODT controlling method comprises setting an ODT control enable signal of each of the memory devices and address / command or data termination information to a mode register of the corresponding memory device, and controlling resistances of ODT resistors of the signal lines in the memory devices in response to the address / command or data termination information and termination addresses. When only one of the memory devices is activated, ODT resistors of the activated memory device are set to a first resistance. When all the memory devices are activated, ODT resistors of the memory devices are set to a second resistance.

Owner:SAMSUNG ELECTRONICS CO LTD

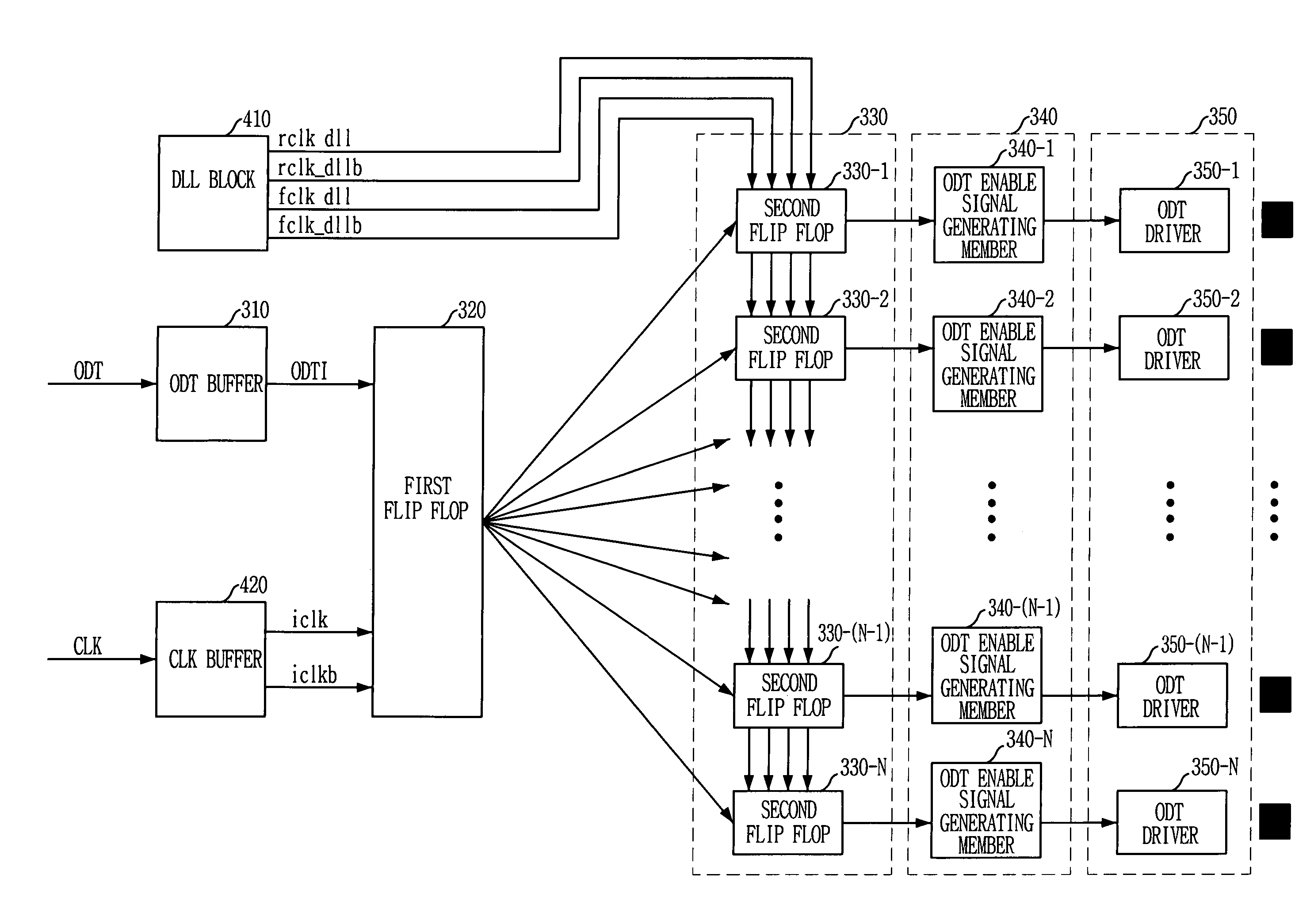

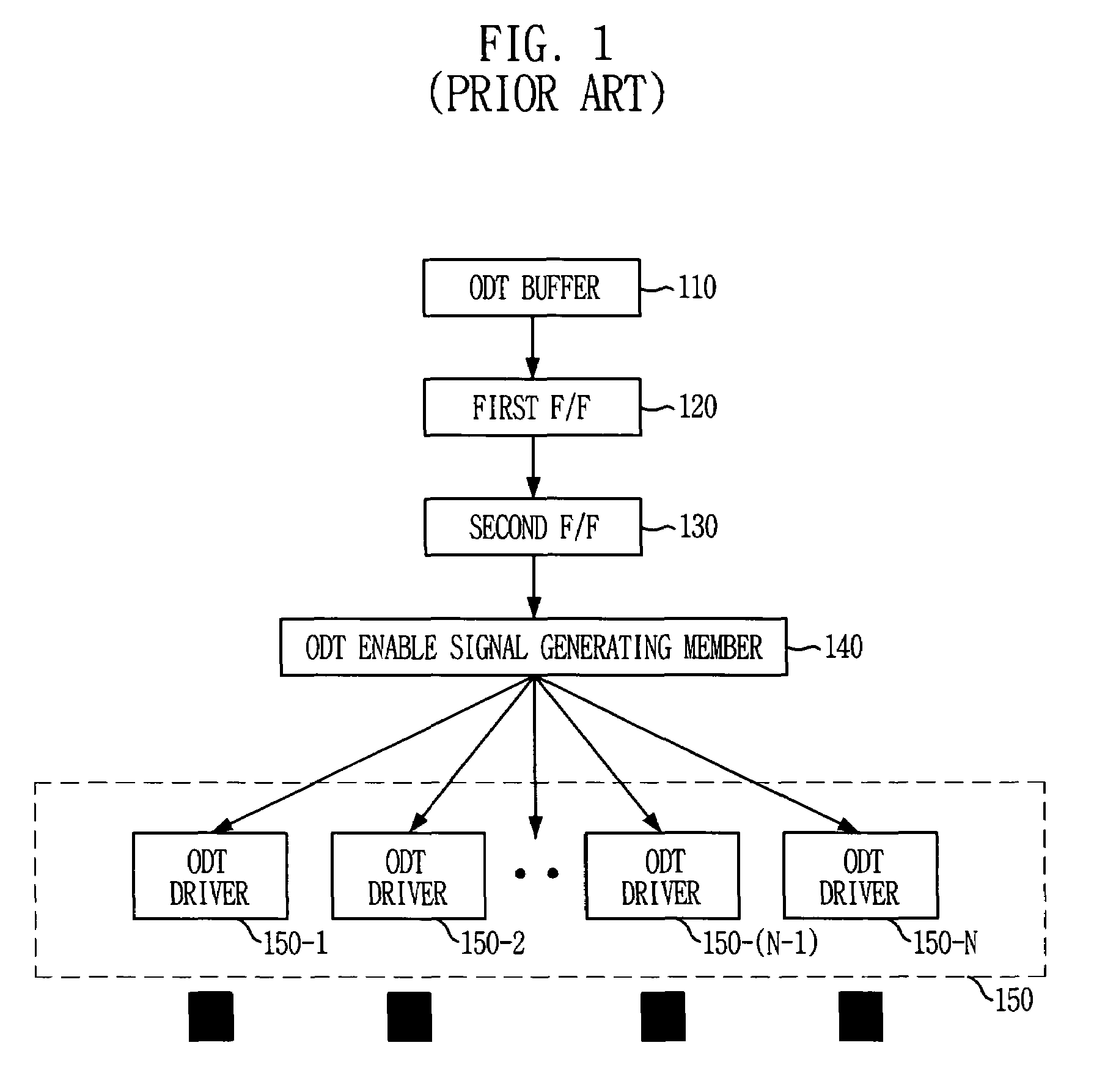

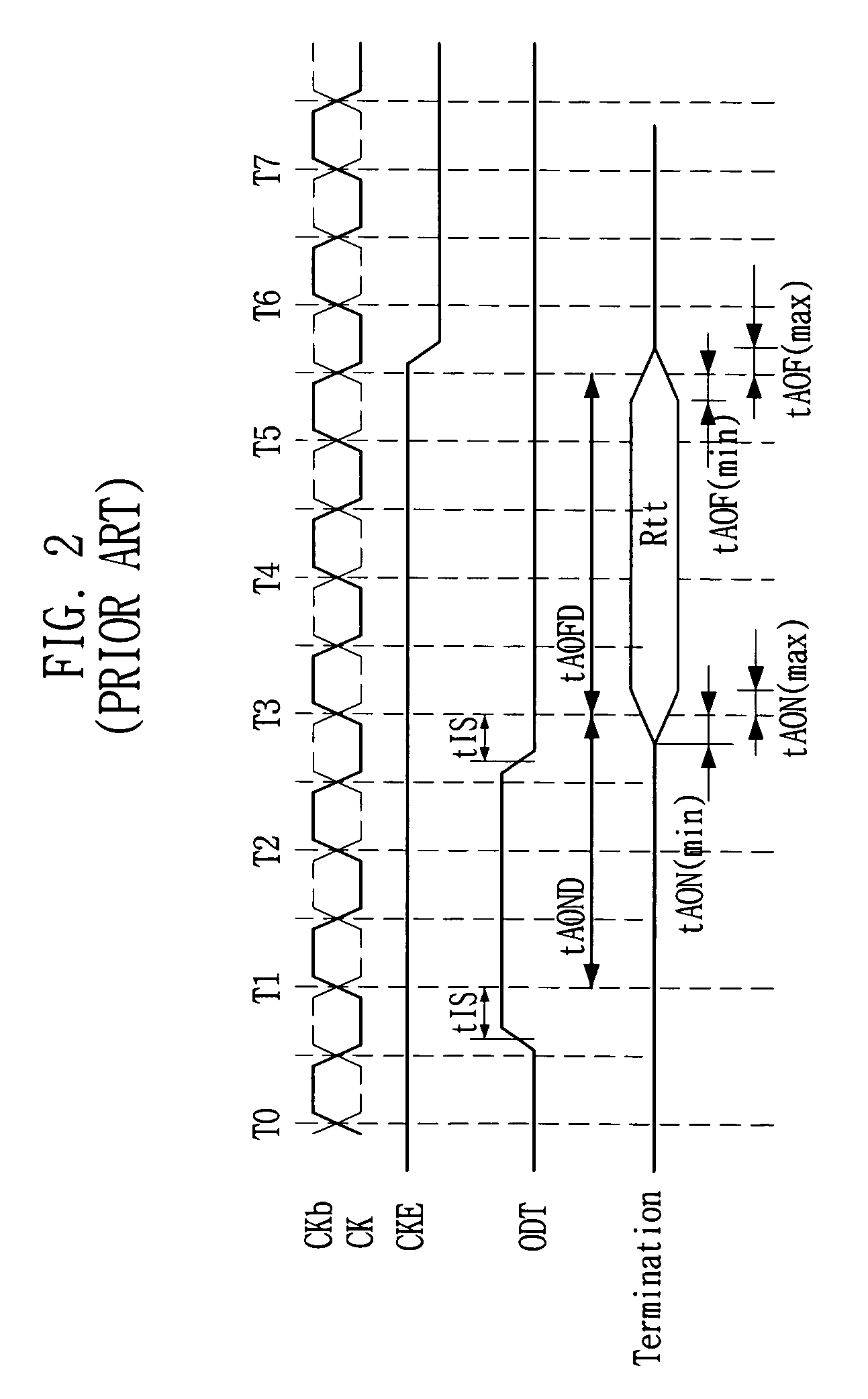

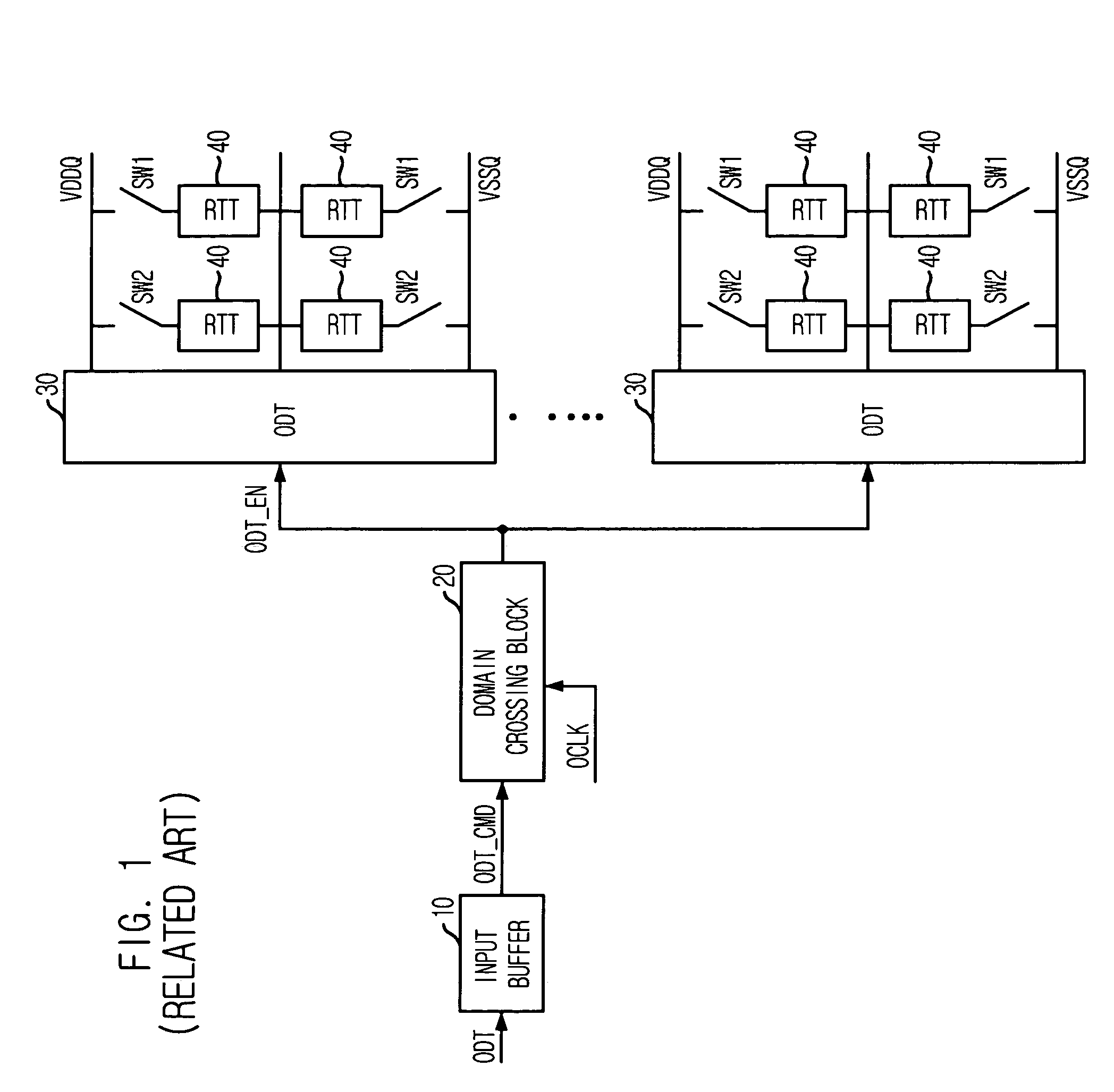

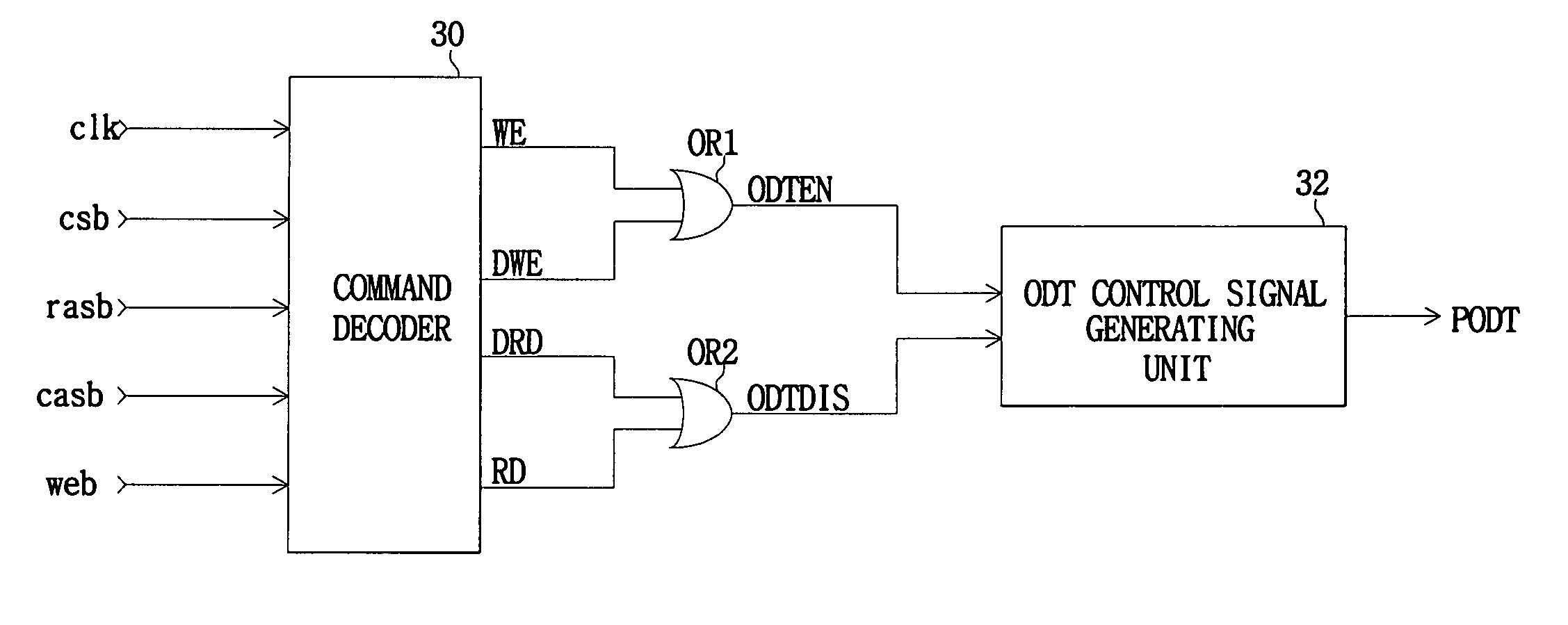

Circuit for performing on-die termination operation in semiconductor memory device and its method

InactiveUS7019555B2Minimizes effect of delayEasy to driveReliability increasing modificationsBaseband system detailsDelay-locked loopVoltage reference

A circuit for performing an on-die termination operation includes a clock buffer for outputting first and second buffered clocks using an external clock and an external inverting clock applied thereto externally; an on-die termination buffer for comparing each other an ODT signal and a reference voltage, which are applied thereto from an external chip set, to generate an on-die termination comparison signal; a first flip-flop member for transferring the on-die termination comparison signal as a plurality of parallel output signals based on the first and second buffered clocks outputted from the clock buffer; and a plurality of second flip-flop members, which corresponds to each of the parallel output signals outputted from the first flip-flop member, for transferring the parallel output signals outputted from the first flip-flop member based on delayed lock loop clocks outputted from a delayed lock loop.

Owner:SK HYNIX INC

On-die termination snooping for 2T applications in a dynamic random access memory device

ActiveUS20050268059A1Digital data processing detailsMemory systemsElectrical resistance and conductanceControl signal

A method and apparatus for controlling the on-die termination of a memory system. The method comprises snooping a command bus in response to a first plurality of command signals clocked at 1T and enabling the on-die termination in response to a second plurality of command signals clocked at 2T and the first plurality of command signals. The apparatus may be memory device comprising a memory array responsive to a plurality of command signals, a data bus having at least one of a data pad, a data strobe output pad, and an input data mask pad, an activation circuit responsive to certain of the plurality of command signals and operable to produce a control signal, and an termination circuit responsive to the control signal and operable to apply an effective resistance to at least one of the data pad, the data strobe output pad, and the input data mask pad.

Owner:MICRON TECH INC

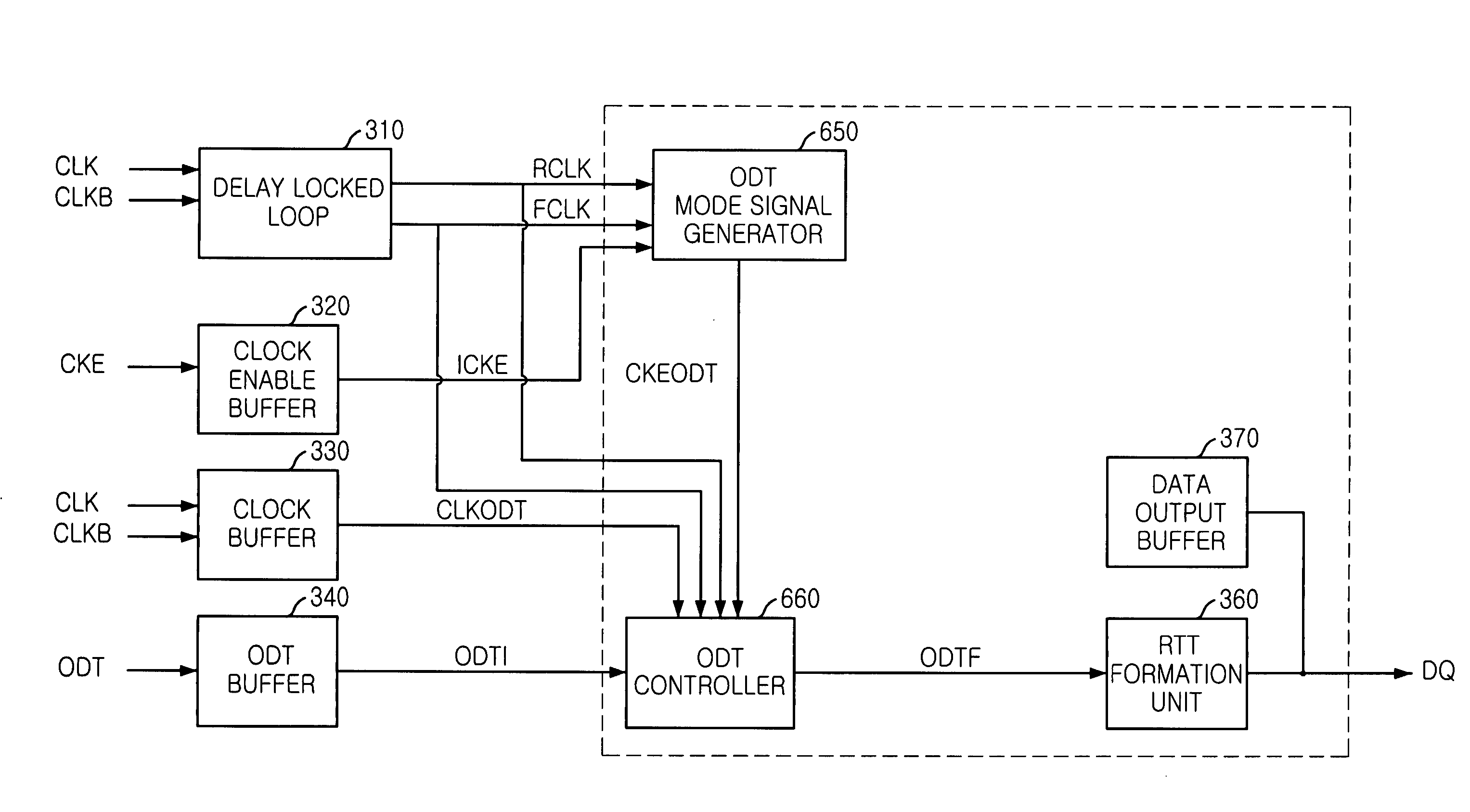

On die termination mode transfer circuit in semiconductor memory device and its method

ActiveUS20050180229A1Guaranteed uptimeDigital storageLogic circuit coupling/interface arrangementsDelay-locked loopOn-die termination

An on die termination (ODT) mode transfer circuit, for use in a semiconductor memory device, including: a delay locked loop (DLL) for receiving an external clock signal in order to generate a DLL clock signal according to a power down mode and an active-standby mode; an ODT mode signal generation means for generating an ODT mode signal in response to the DLL clock signal and a clock enable signal; and an ODT control means for generating a termination resistor (RTT) signal in response to an ODT signal and the ODT mode signal.

Owner:CONVERSANT INTPROP MANAGEMENT INC

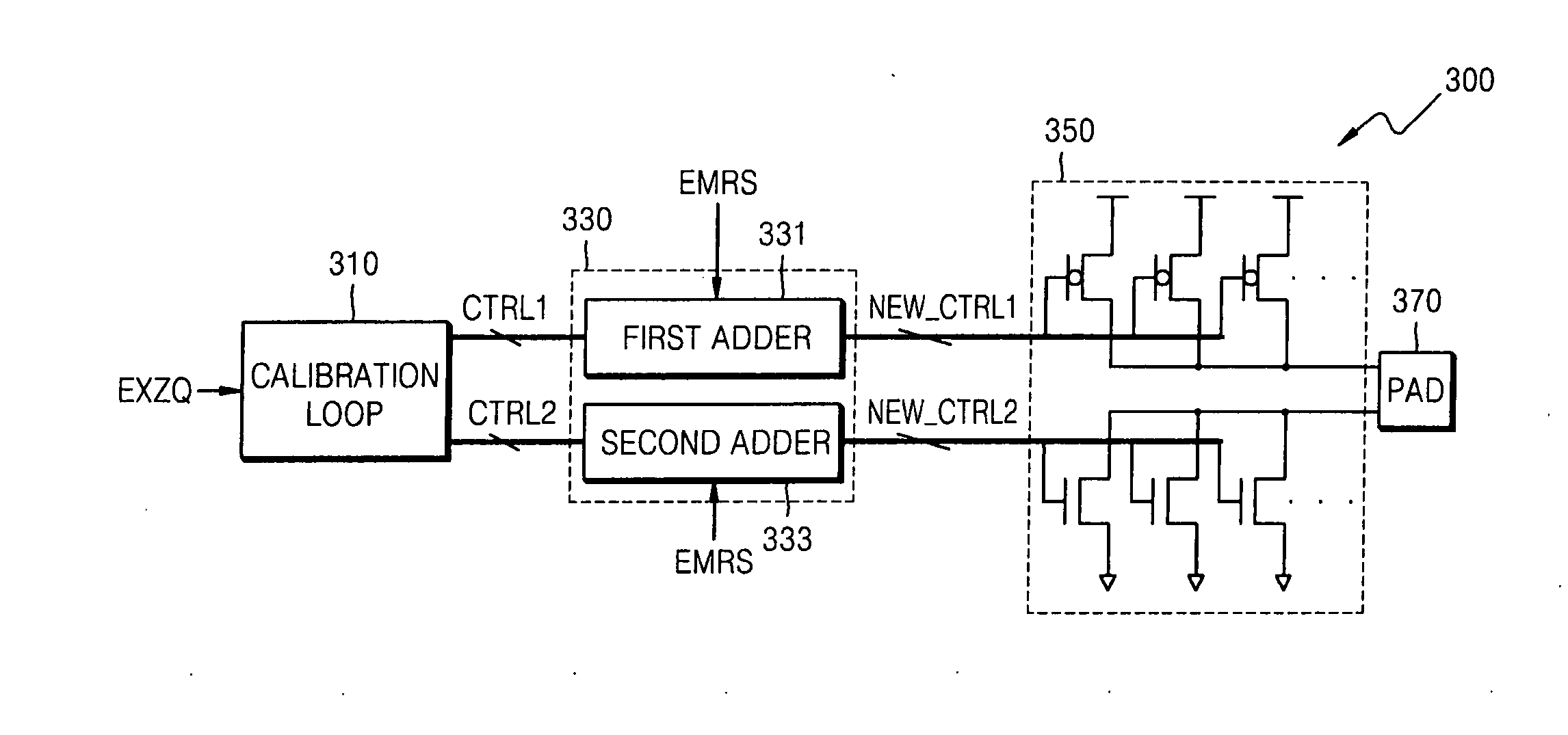

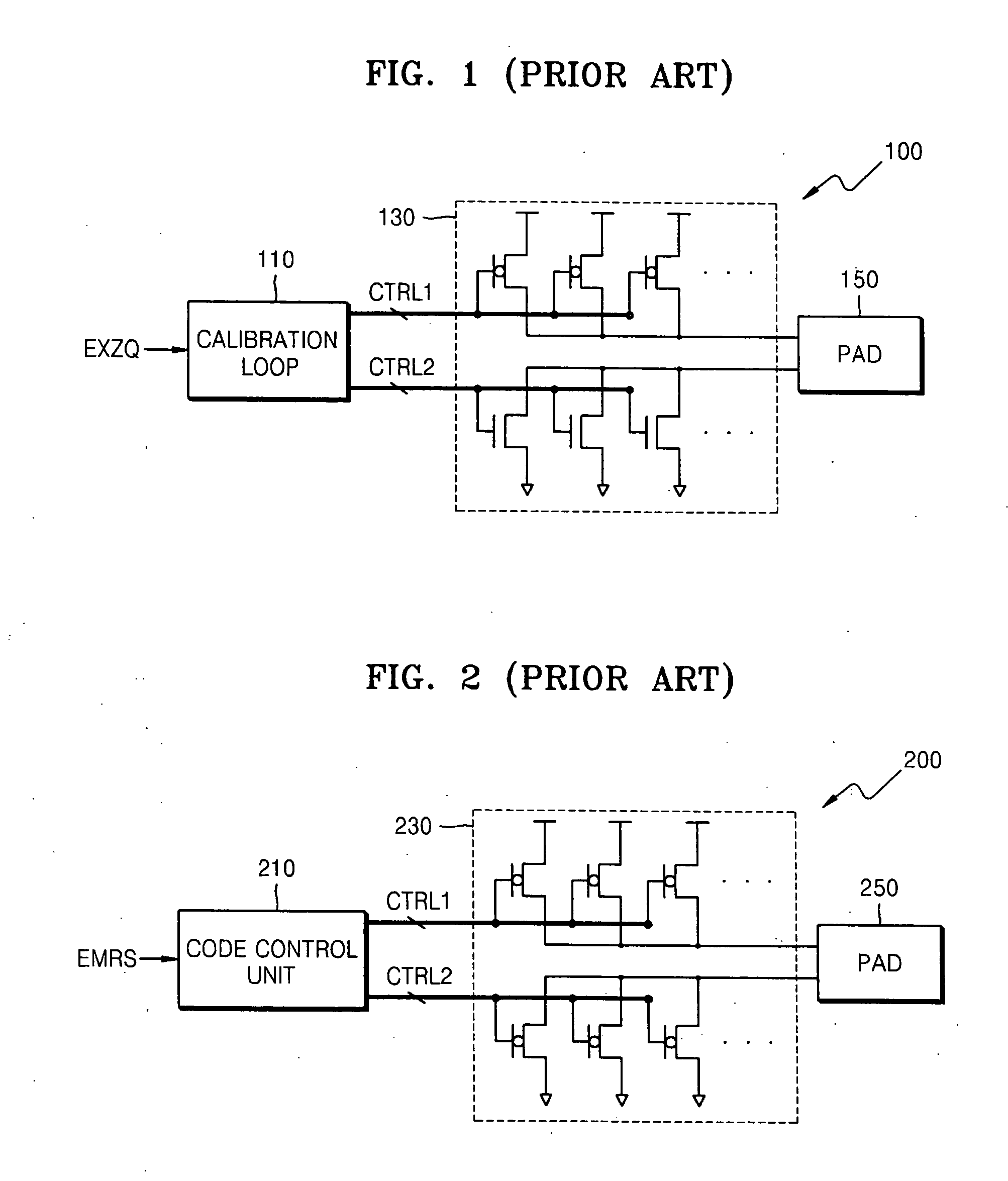

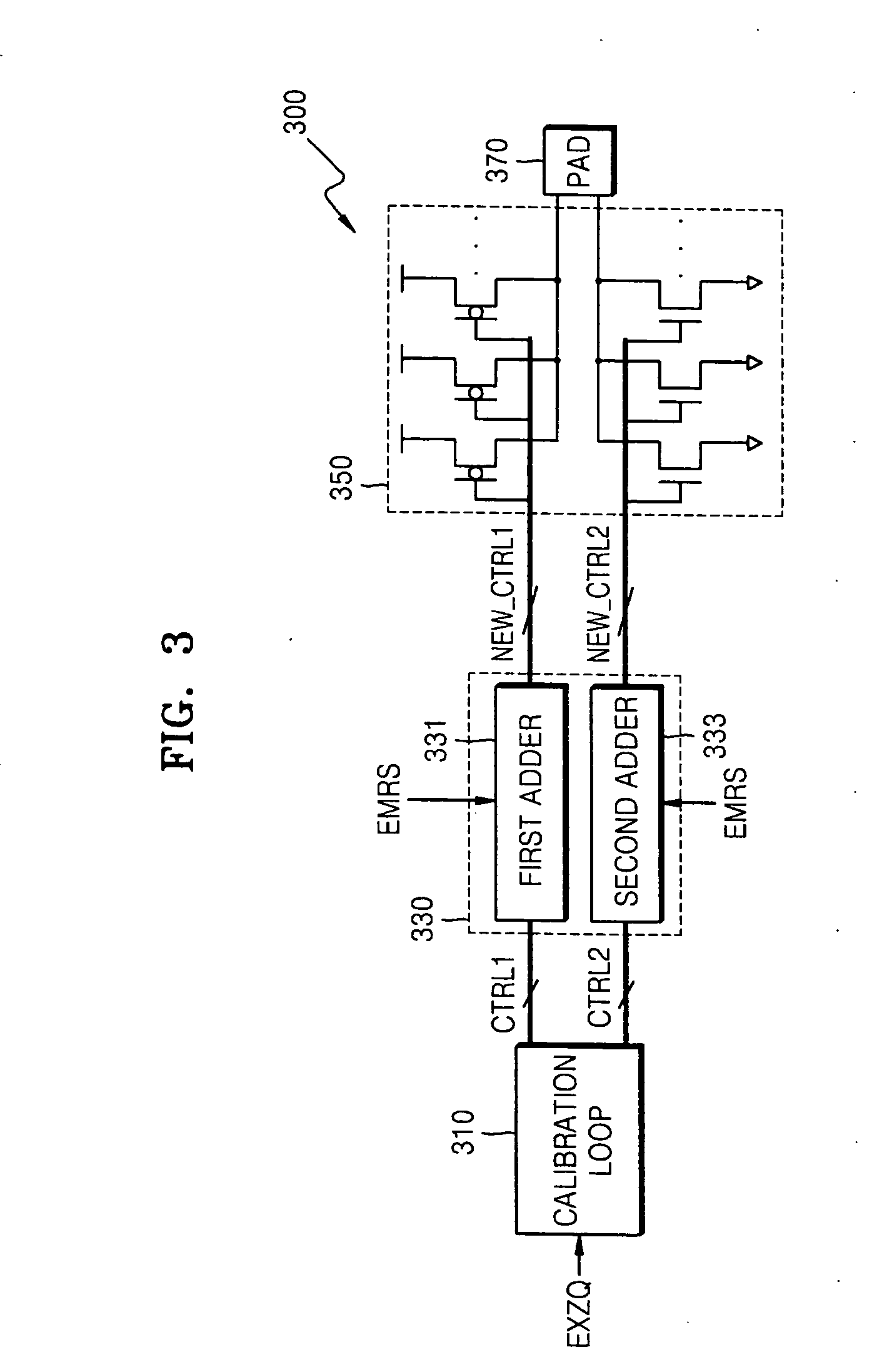

Semiconductor device capable of controlling OCD and ODT circuits and control method used by the semiconductor device

ActiveUS20060226868A1Input/output impedence modificationReliability increasing modificationsDevice materialControl signal

Provided is a semiconductor device capable of controlling an on-die-termination (ODT) circuit and an off-chip-driver (OCD) circuit and a control method used by the semiconductor device. The semiconductor device includes a control code generation unit generating a control code in response to a control signal, an addition unit adding an adjustment code to the control code to produce an adjusted control code, and an ODT circuit, wherein an impedance of the ODT circuit is adjusted in response to the adjusted control code. The semiconductor device can adjust the control code more precisely by adding or subtracting the adjustment code to or from the control code. Accordingly, the impedance of an OCD circuit or ODT circuit can be adjusted more precisely.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device with on die termination circuit

InactiveUS7161378B2Reduce power consumptionReliability increasing modificationsElectronic switchingEngineeringSemiconductor

A semiconductor memory device having a data input / output pad connected to a data input node includes: an on die termination resistor one end of which is connected to the data input node; and a switch one end of which is connected to the other end of the on die termination resistor for connecting / disconnecting the on die termination resistor with an on die termination voltage.

Owner:SK HYNIX INC

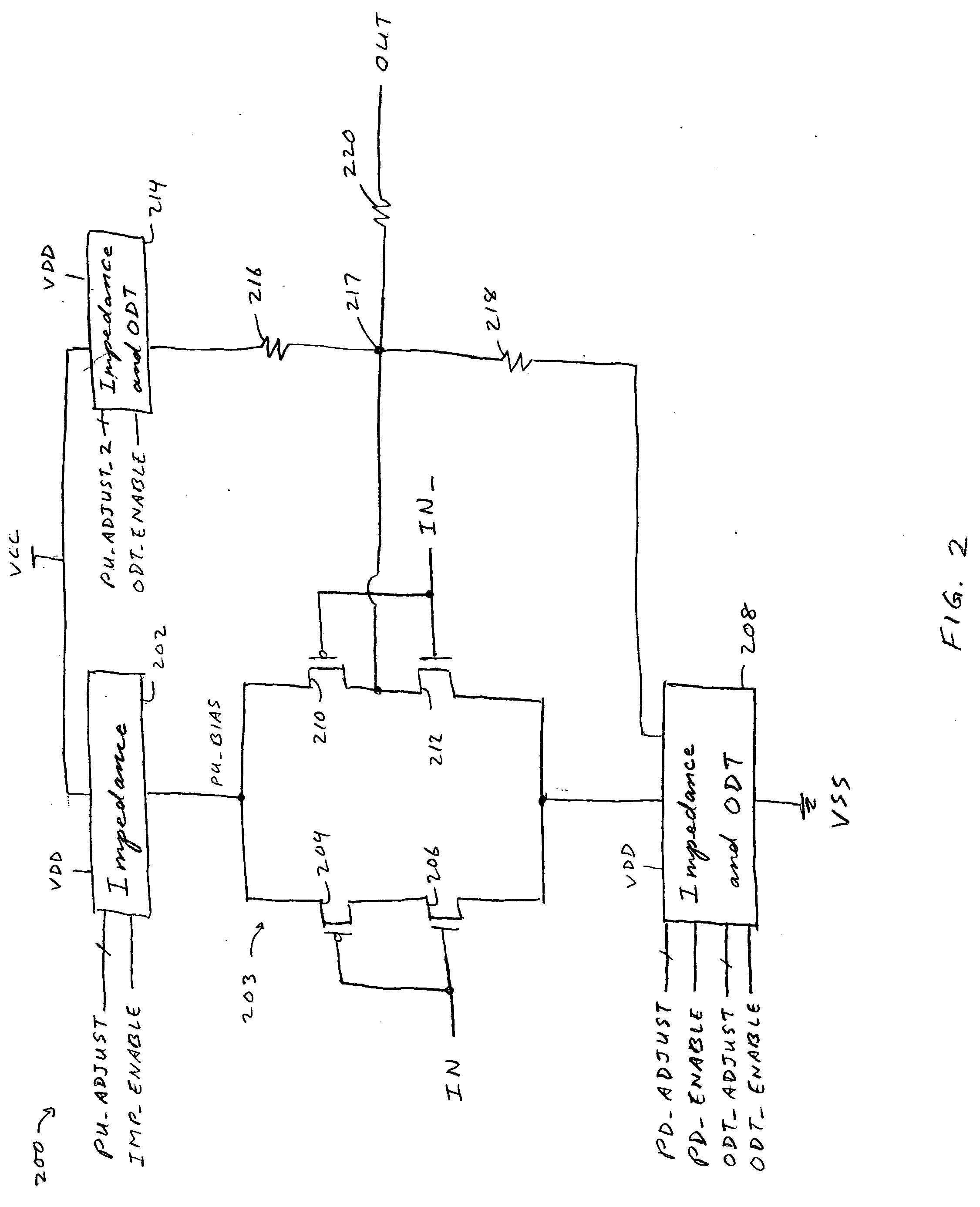

Pseudo-differential output driver with high immunity to noise and jitter

ActiveUS20060267633A1Improve immunityGood anti-noise performanceReliability increasing modificationsElectronic switchingCapacitanceLow voltage

Circuits and methods are provided for transmitting a pseudo-differential output signal with relatively high immunity to noise and jitter. The output driver of the invention receives two differential input signals and outputs a single output signal with low voltage transistors and programmable impedance and on-die termination circuits. The pseudo-differential output driver consumes little circuit area and has low output capacitance.

Owner:MICRON TECH INC

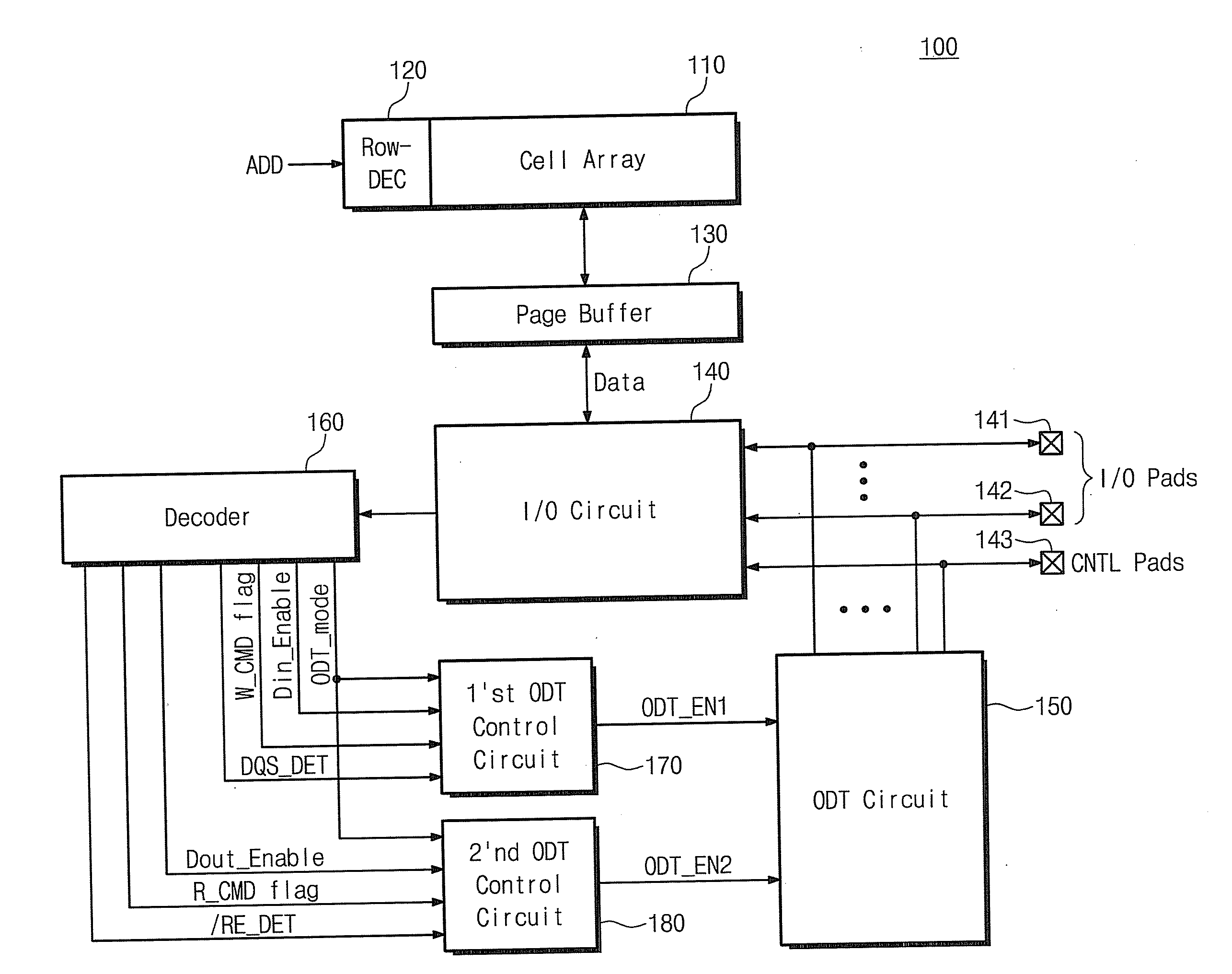

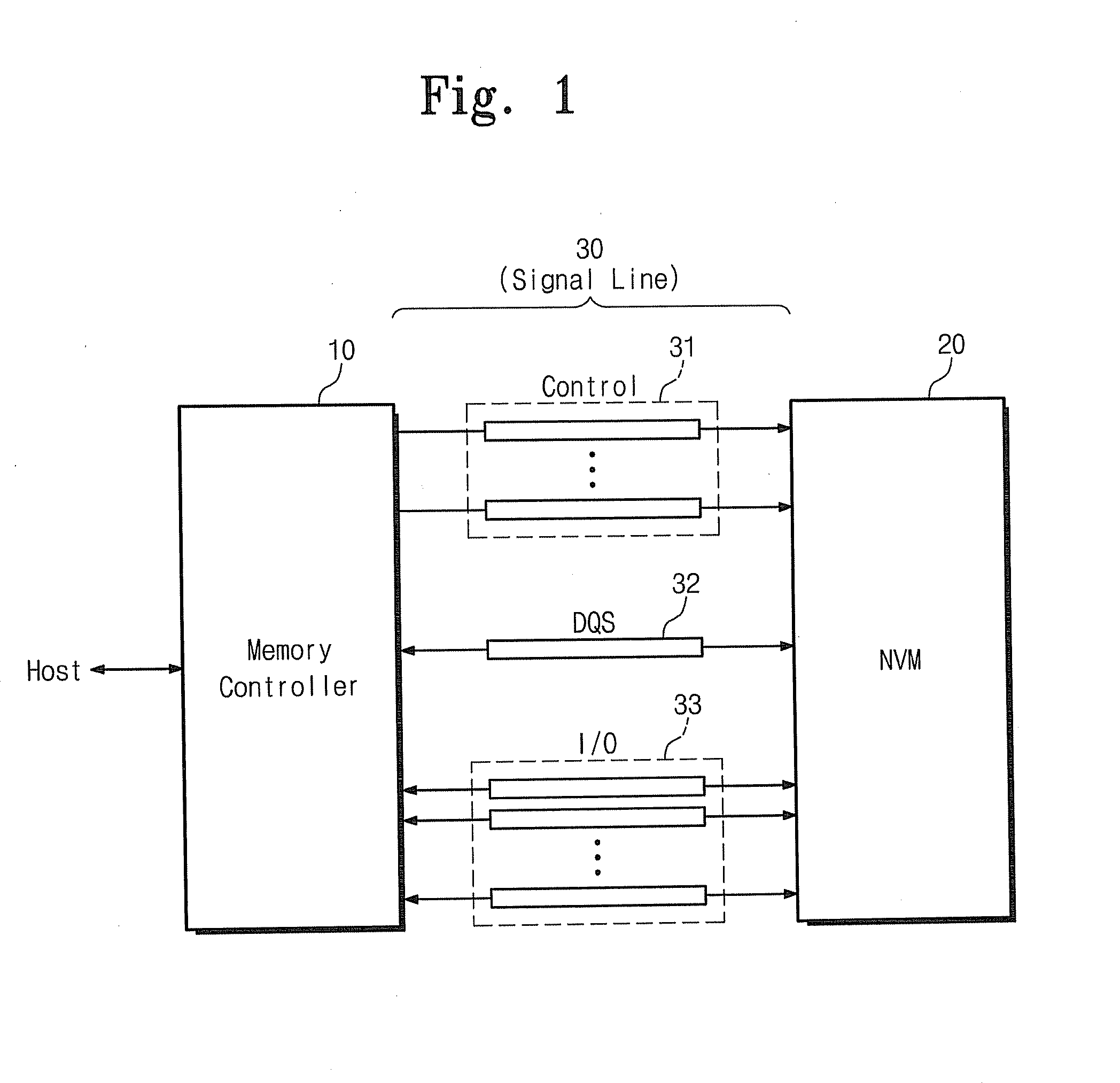

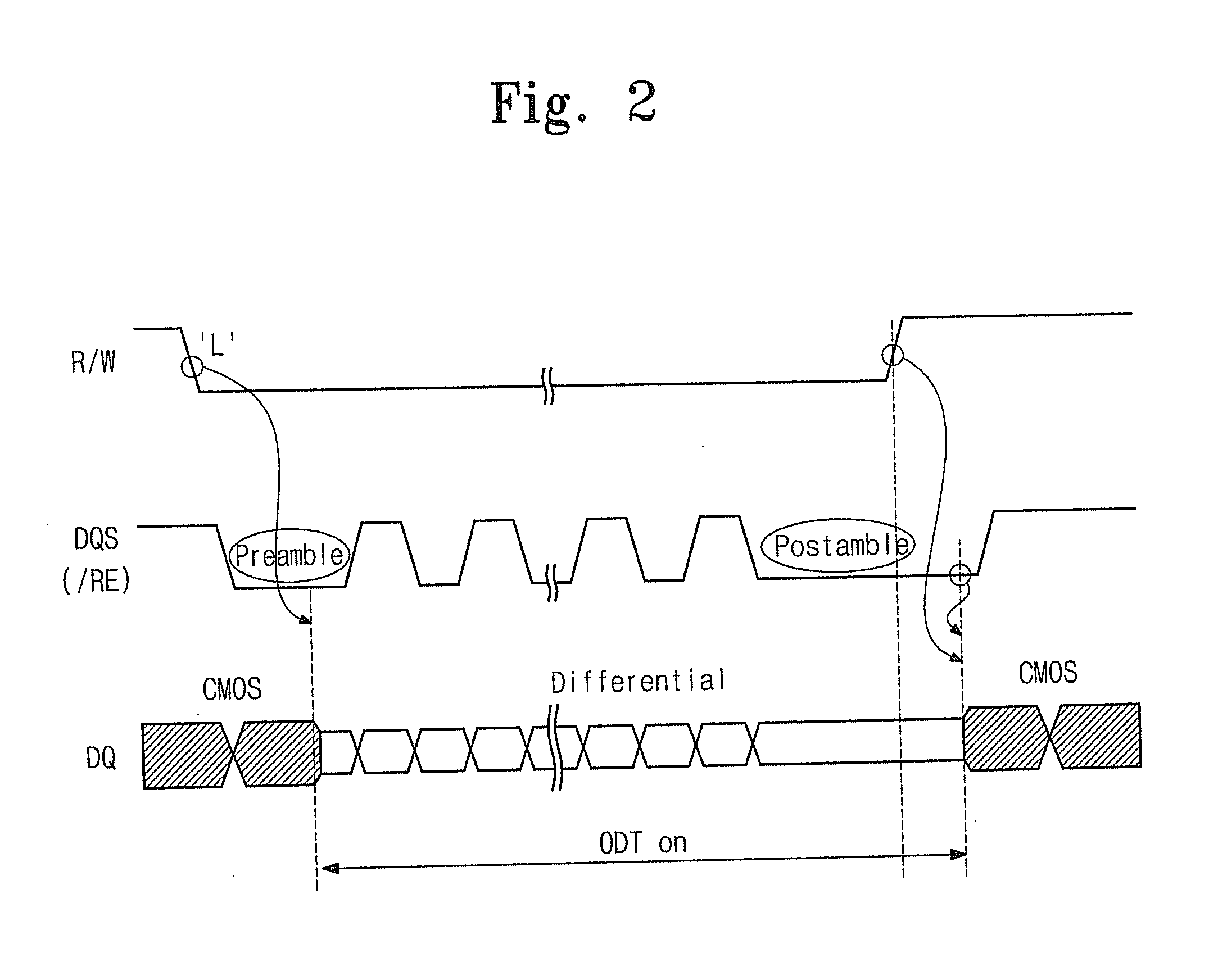

Nonvolatile Memory Devices With On Die Termination Circuits And Control Methods Thereof

ActiveUS20120113733A1Input/output impedence modificationReliability increasing modificationsControl signalCommand and control

Non-volatile memory devices including on-die termination circuits connected to an input / output circuit and an on-die termination control logic detecting a preamble of a strobe signal based on a command and a control signal and activating the on-die termination within the preamble period.

Owner:SAMSUNG ELECTRONICS CO LTD

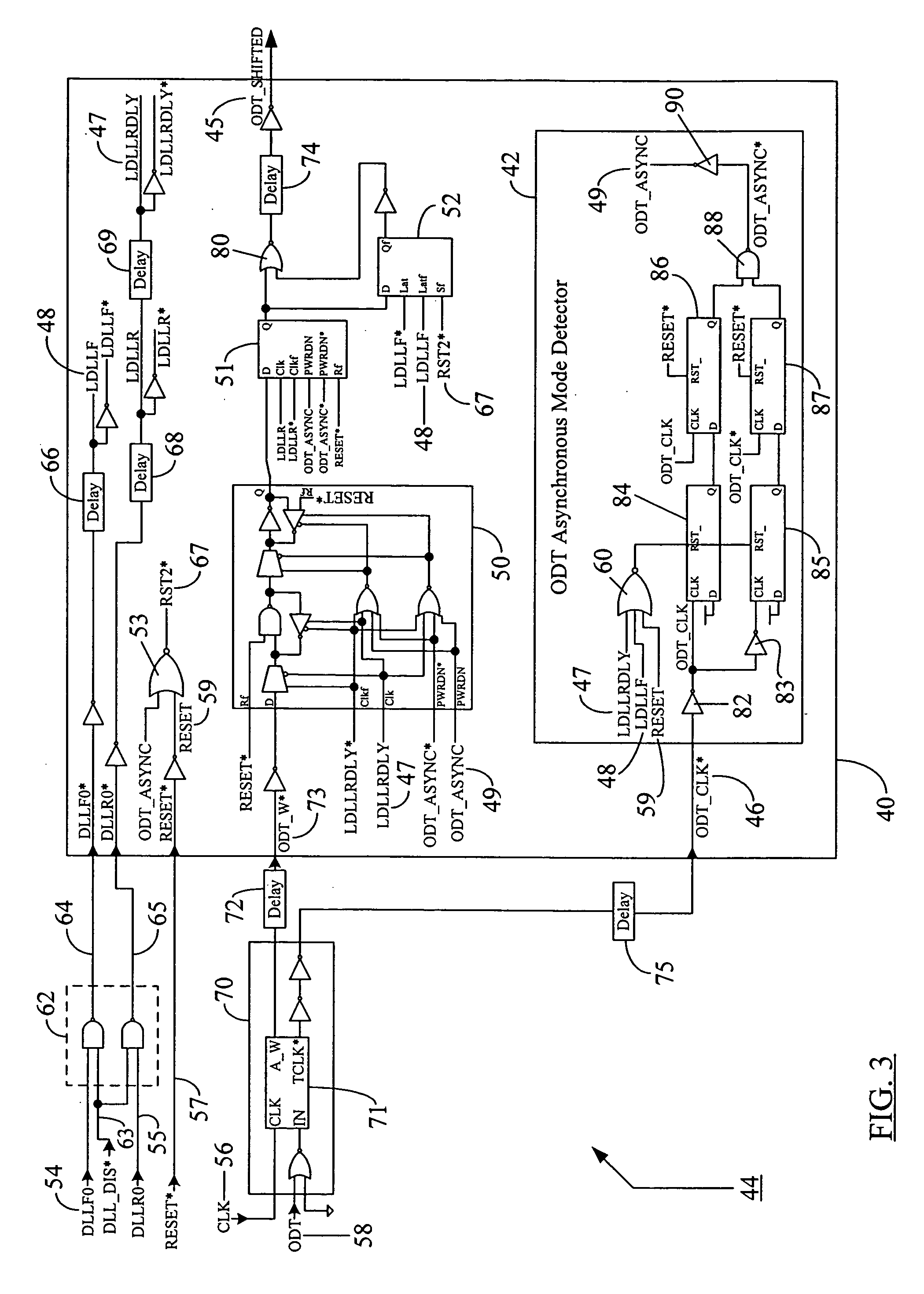

Method and apparatus for selecting an operating mode based on a determination of the availability of internal clock signals

ActiveUS20070030030A1Avoid utilizationEasy to useReliability increasing modificationsElectronic switchingDriver circuitMemory chip

A system and method to operate an electronic device, such as a memory chip, with an output driver circuit that is configured to include an ODT (On-Die Termination) mode detector detects whether there is sufficient internal clocking available to operate the ODT portion in the output driver in the synchronous mode of operation or to switch the operation to the asynchronous mode. The clock-sufficiency based determination of internal ODT mode of operation (synchronous vs. asynchronous) avoids utilization of complex and inflexible clock processing logic in an ODT control unit in the output driver. This enables the actual clocking to the ODT circuitry to be changed during various device operational modes (e.g., active, power down, etc.) without re-designing the ODT control logic for each of those modes. The simplicity and flexibility of the ODT mode detector design allows for efficient use of chip real estate without affecting the signal transfer speed of the output driver in the electronic device. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:MICRON TECH INC

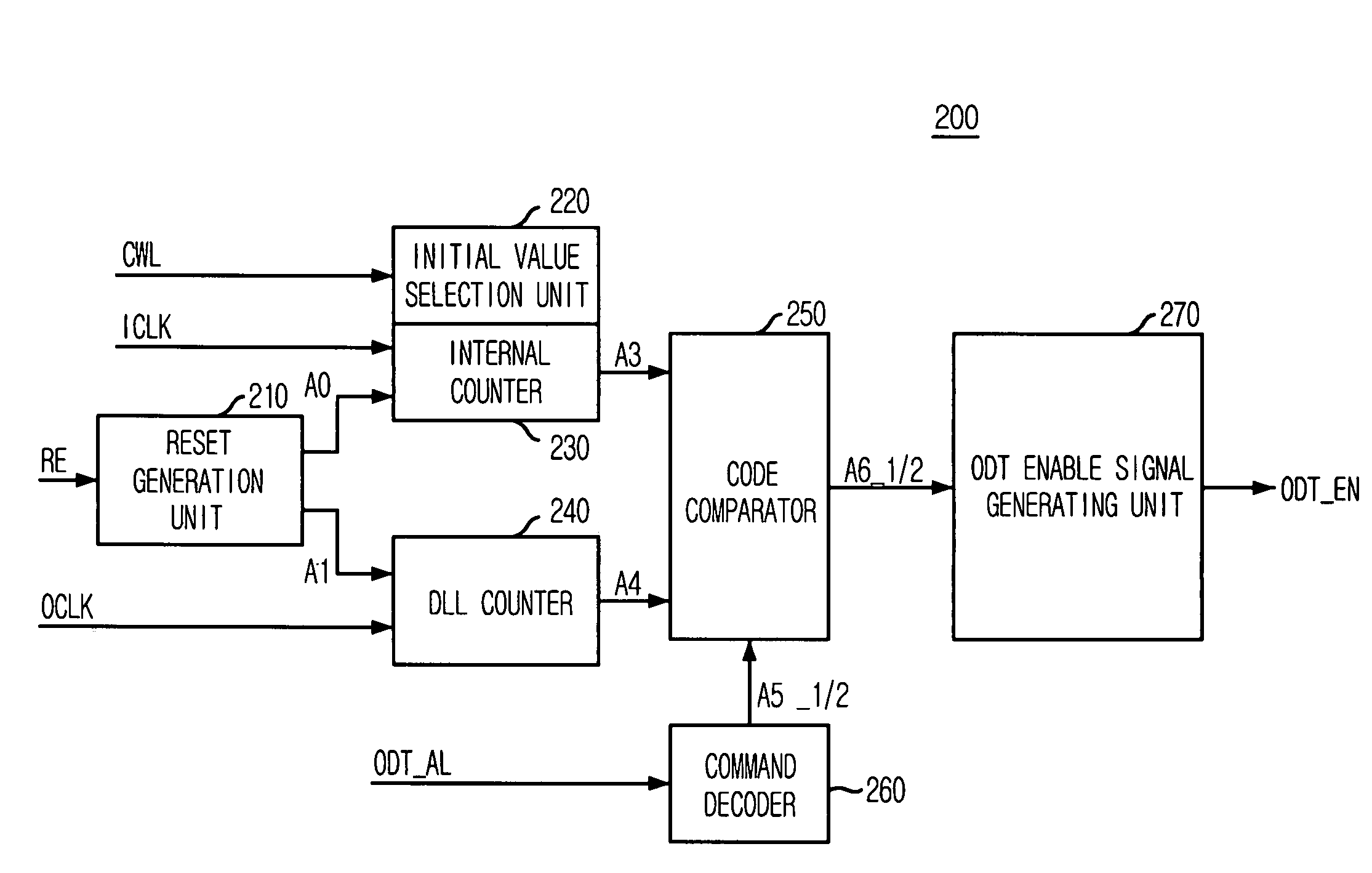

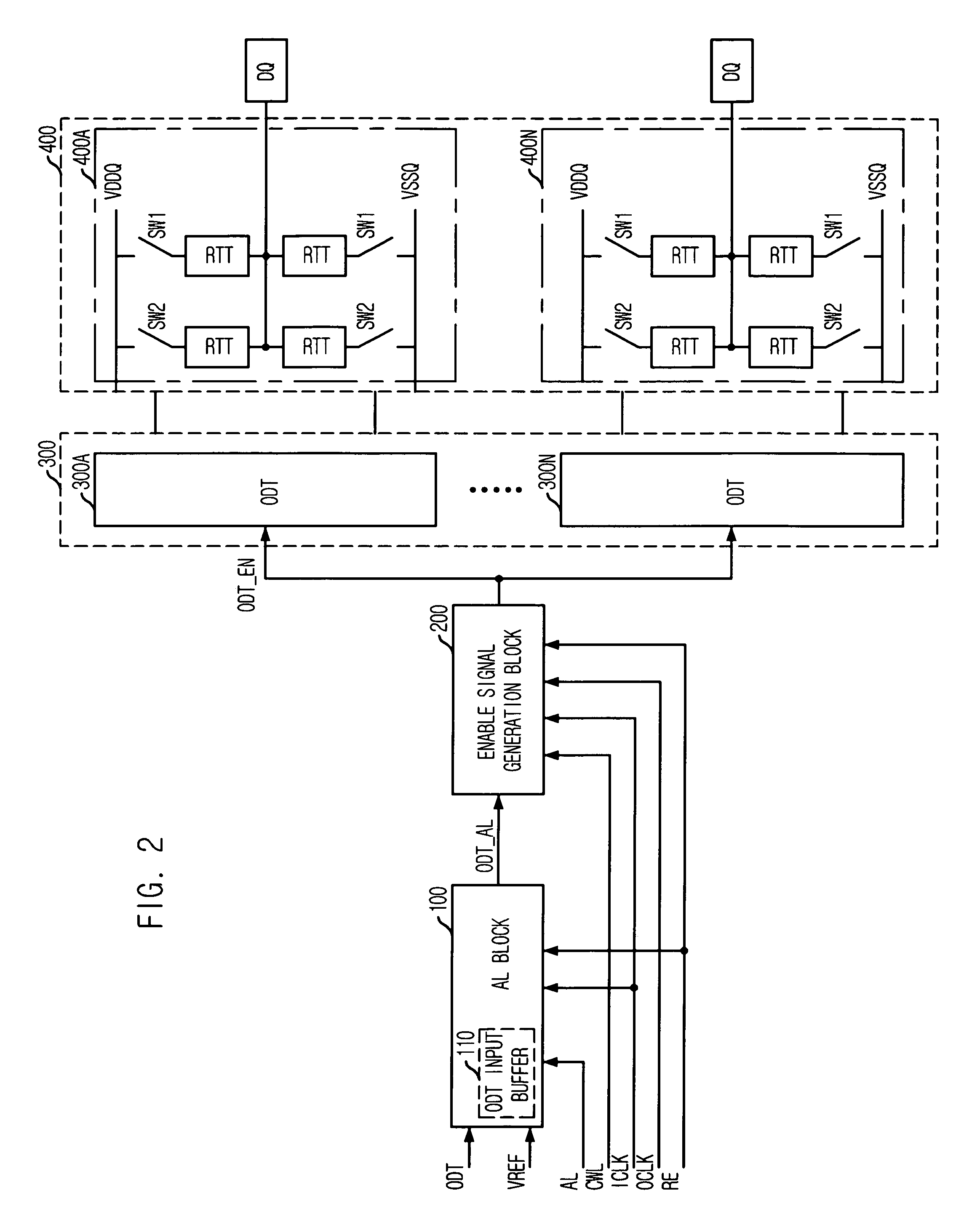

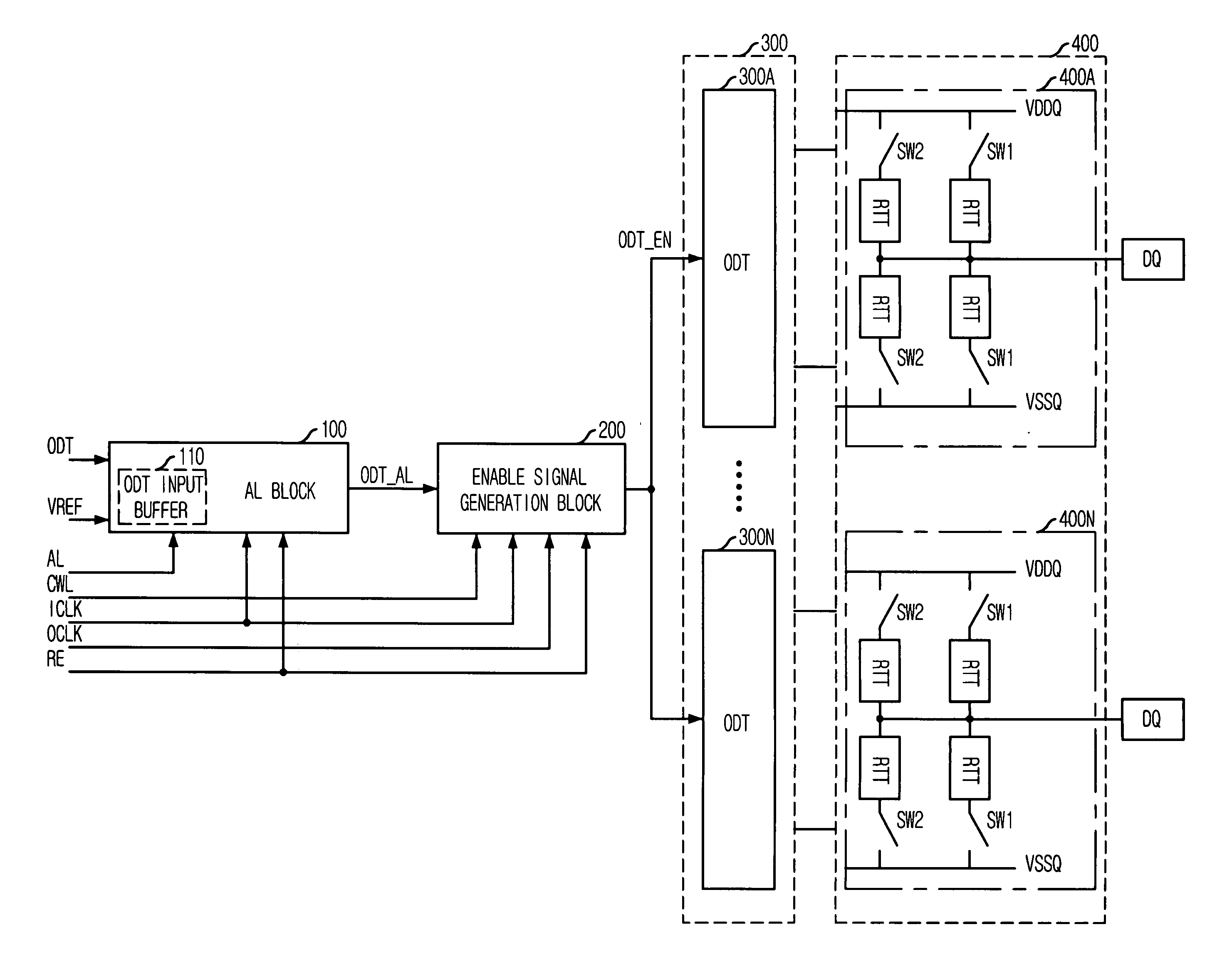

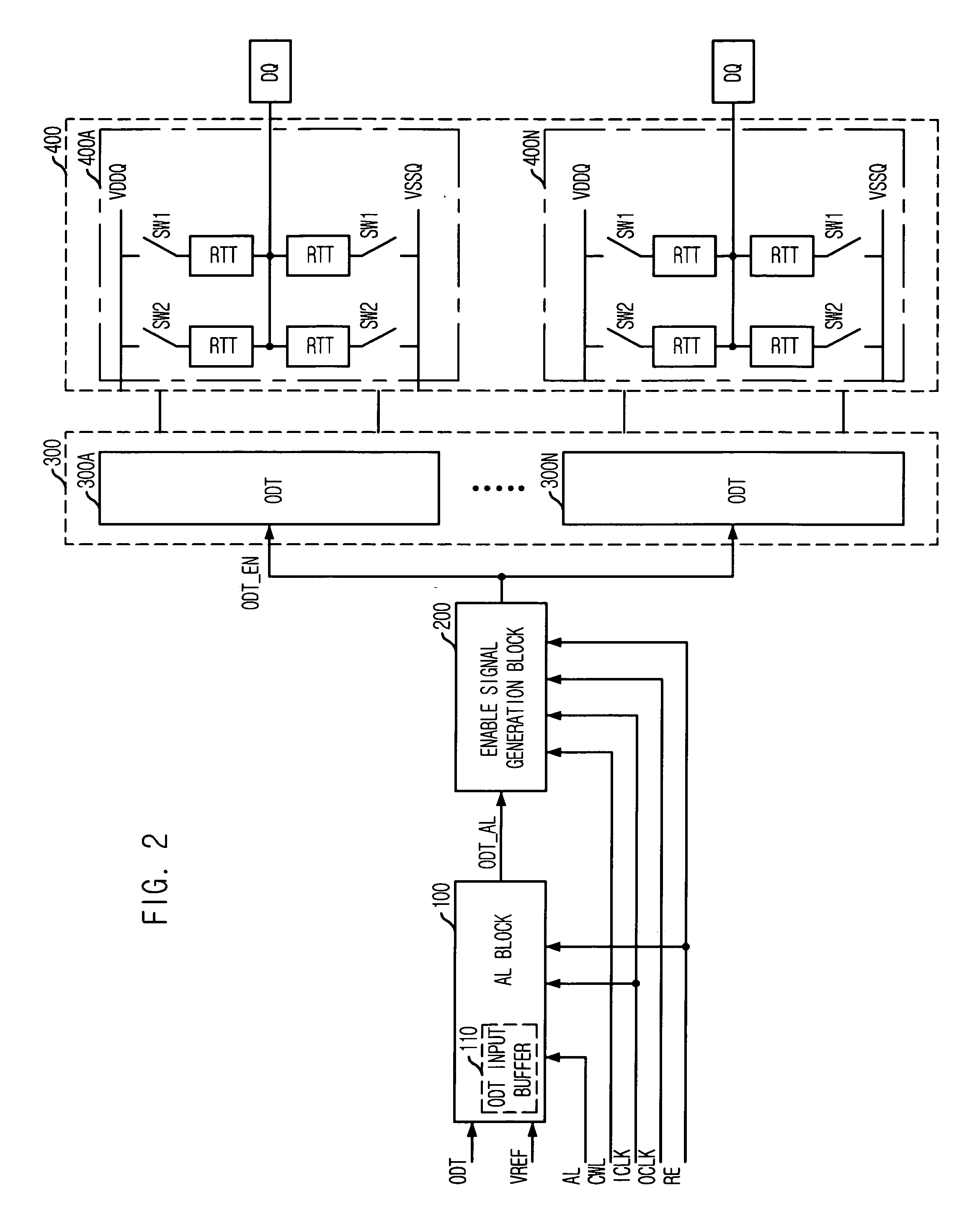

Device for controlling on die termination

ActiveUS7342412B2Control impedanceLogic circuit coupling arrangementsReliability increasing modificationsControl signalComputer science

An on die termination (ODT) control device includes a latency block for buffering an ODT control signal to output a latency control signal by selecting one of a plurality of intermediate control signals, which are generated by sequentially delaying the buffered ODT control signal in synchronization with an internal clock, based on first latency information; an enable signal generation block for comparing a first control signal with a second control signal in response to the latency control signal to thereby produce an ODT enable signal based on the compared result; and an ODT block for controlling a termination impedance based on the ODT enable signal.

Owner:SK HYNIX INC

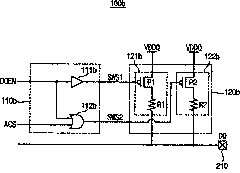

On-die termination circuit, memory device, memory module, and method of operating and training an on-die termination

A memory device comprises: a memory device having a memory core having a memory cell array; a data input / output pin connected to the memory core through a data buffer; and an on-die termination (ODT) circuit, comprising: a termination circuit configured to provide a termination impedance at the input / output data pin, the termination circuit having a switching device that selectively connects a termination impedance to the input / output data pin based on the presence of an asynchronous control signal (ACS), wherein the ACS is generated based on the presence of a memory WRITE command. The memory device may further comprise a training circuit comprising: an asynchronous signal delay configured to delay the signal path of the ACS signal to the termination circuit; and a comparing unit configured to compare a phase difference between the ACS signal and a reference signal, the comparing unit comprising a phase detector and a replica delay, wherein the replica delay is configured to delay the signal path of the ACS signal to the phase detector, and the phase detector is configured to output the phase difference as training result.

Owner:SAMSUNG ELECTRONICS CO LTD

Device for controlling on die termination

ActiveUS20070126468A1Flexible controlControl impedanceReliability increasing modificationsLogic circuit coupling arrangementsControl signalComputer science

An on die termination (ODT) control device includes a latency block for buffering an ODT control signal to output a latency control signal by selecting one of a plurality of intermediate control signals, which are generated by sequentially delaying the buffered ODT control signal in synchronization with an internal clock, based on first latency information; an enable signal generation block for comparing a first control signal with a second control signal in response to the latency control signal to thereby produce an ODT enable signal based on the compared result; and an ODT block for controlling a termination impedance based on the ODT enable signal.

Owner:SK HYNIX INC

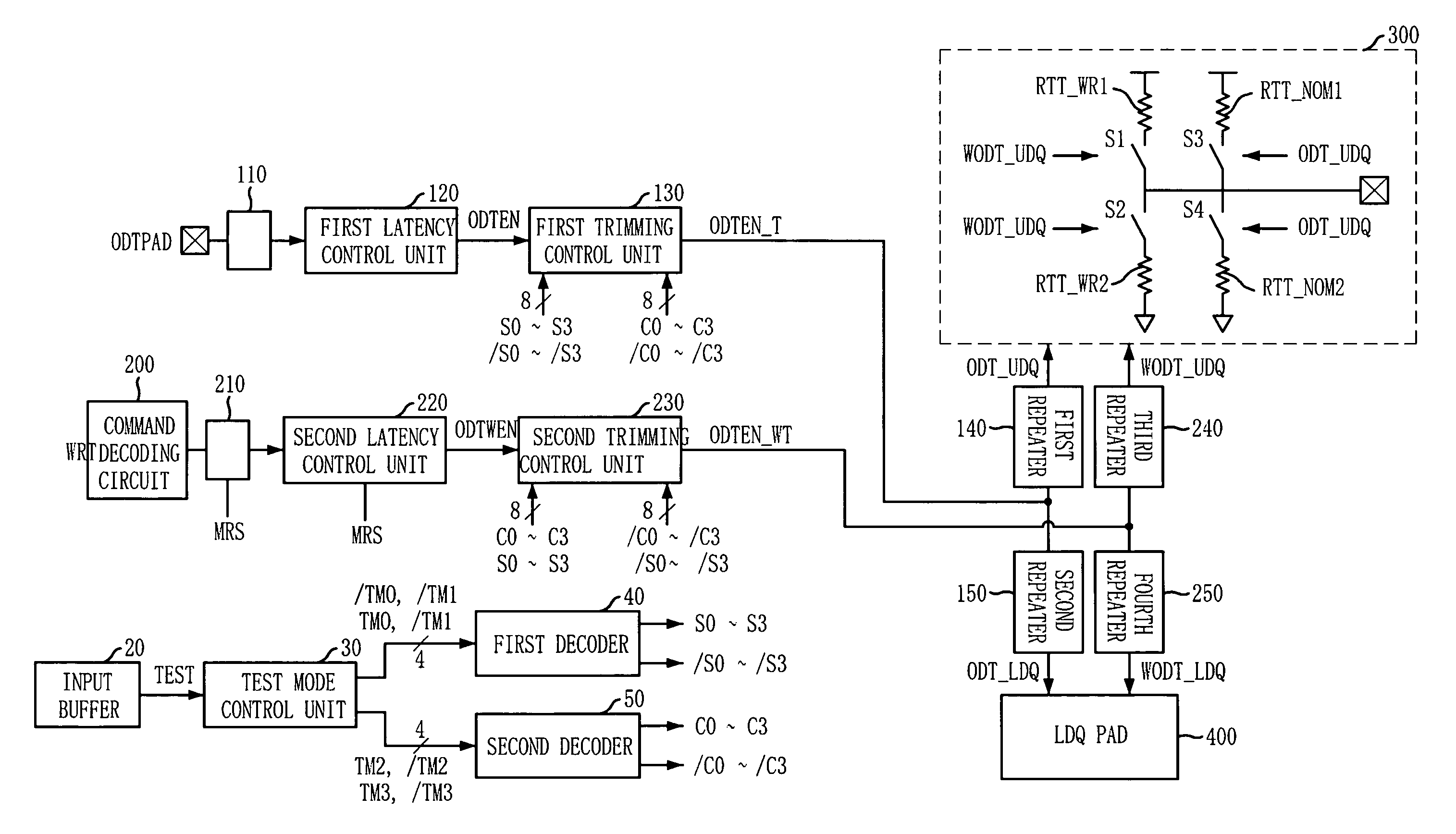

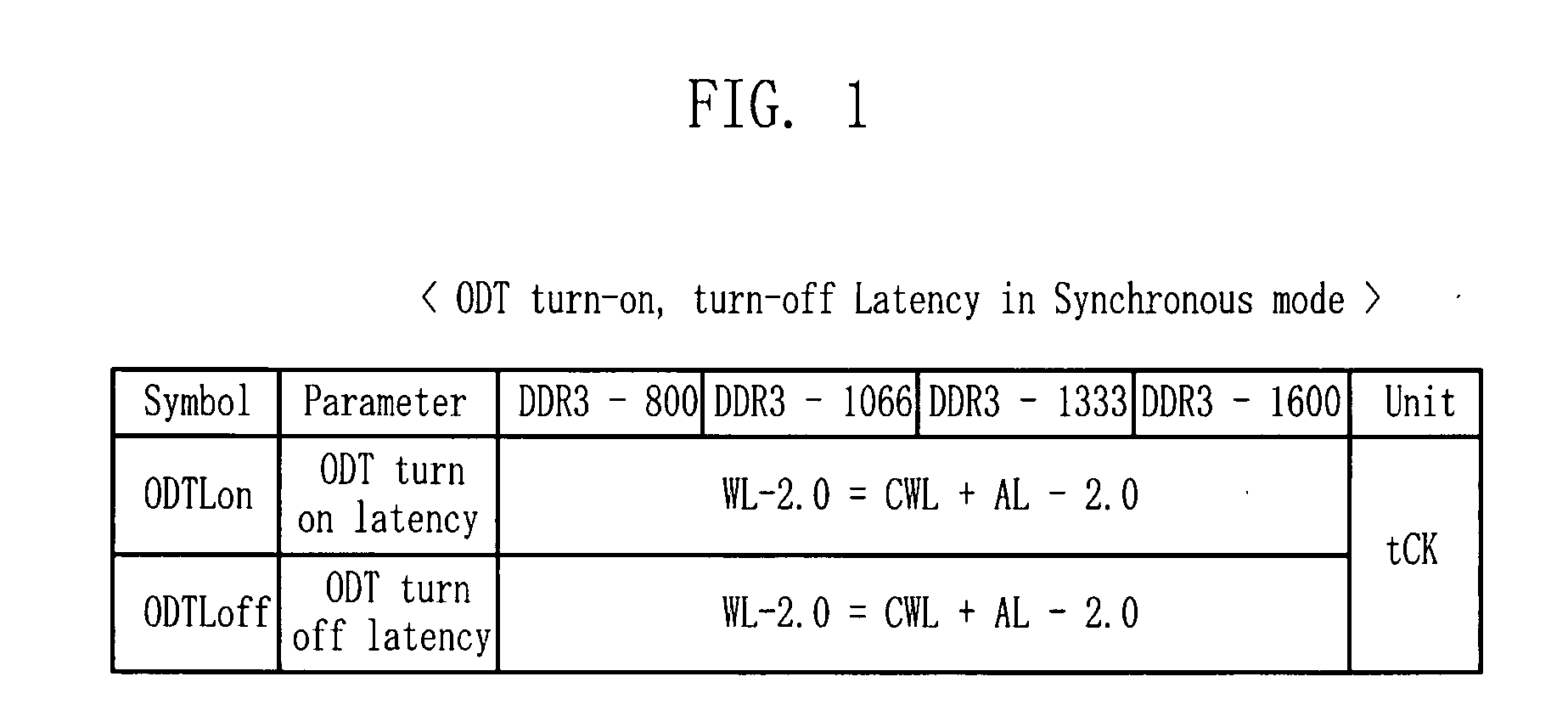

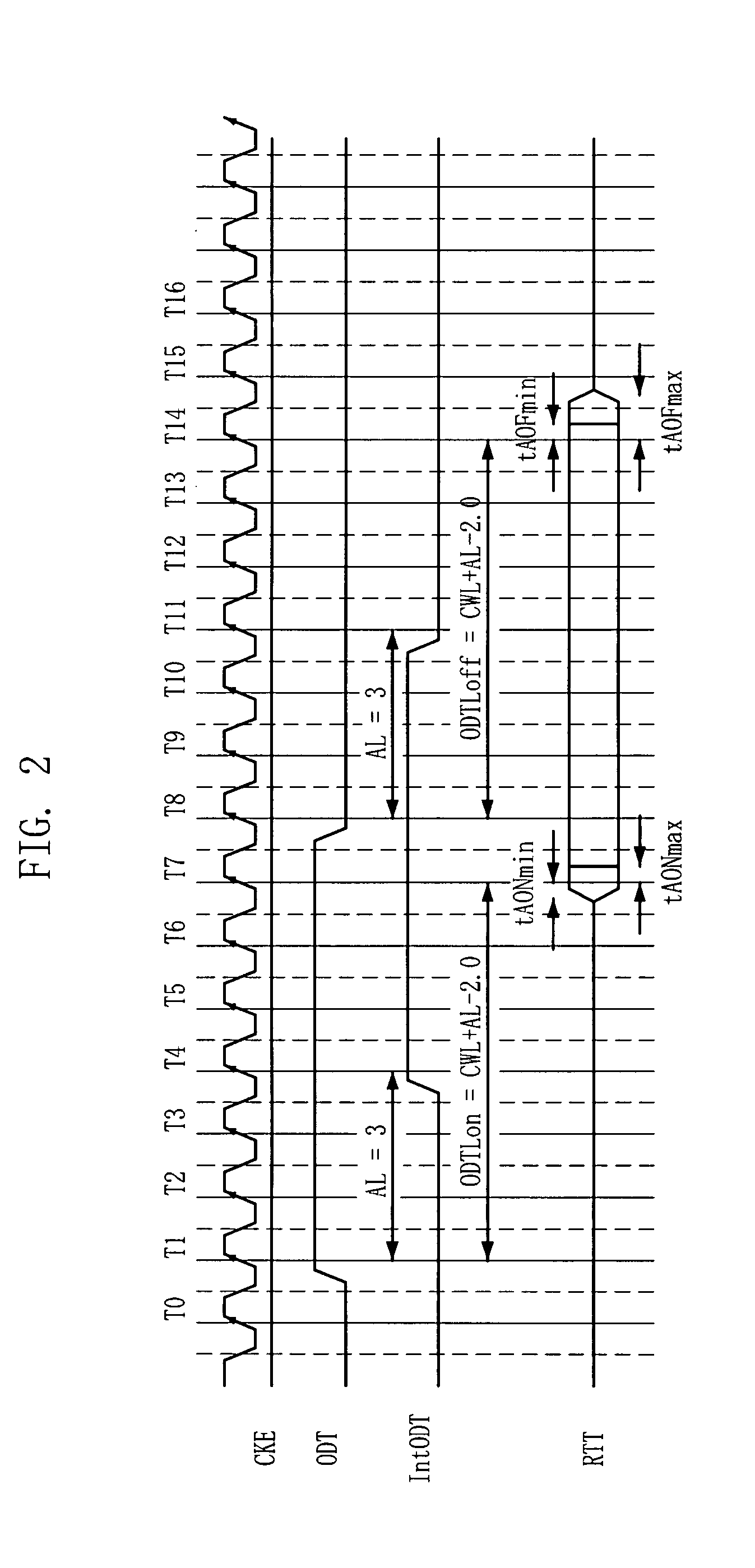

Semiconductor memory device with ability to effectively adjust operation time for on-die termination

ActiveUS20080164904A1Effectively adjust operation timeInput/output impedence modificationReliability increasing modificationsControl signalEngineering

A semiconductor memory device is effectively able to adjust operation time for on-die termination (ODT). The semiconductor memory device includes a latency control unit, a control signal generating unit, a trimming control unit, and a termination circuit. The latency control unit produces an ODT driving enable signal by delaying an ODT operation signal from an external circuit during a predetermined latency. The control signal generating unit produces control signals to control a change of waveform of the ODT driving enable signal. The trimming control unit changes the waveform of the ODT driving enable signal in response to the control signals, thereby outputting a ODT driving signal. The termination circuit connects a termination resistance to an impedance adjusting node in response to the ODT driving signal.

Owner:SK HYNIX INC

Memory systems, on-die termination (ODT) circuits, and method of ODT control

InactiveUS7786752B2Latency of operationLogic circuit coupling arrangementsReliability increasing modificationsPower modeDelay-locked loop

According to one aspect, an on-die termination (ODT) circuit is controlled during transition from a first power mode to a second power mode of a memory device. The transition from an asynchronous ODT circuit path to a synchronous ODT circuit path is delayed to compensate for an operational latency of a delay locked loop (DLL) circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

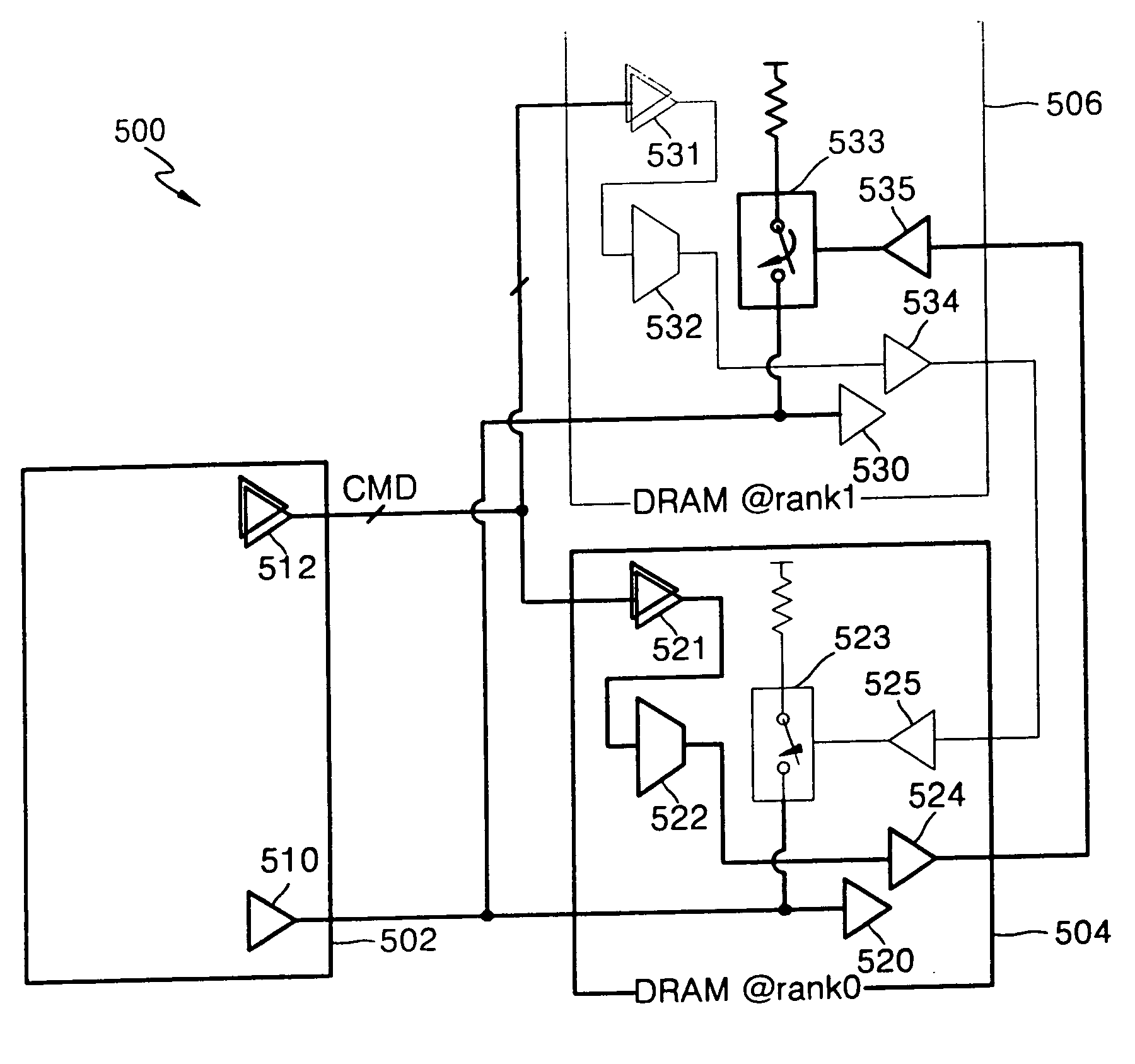

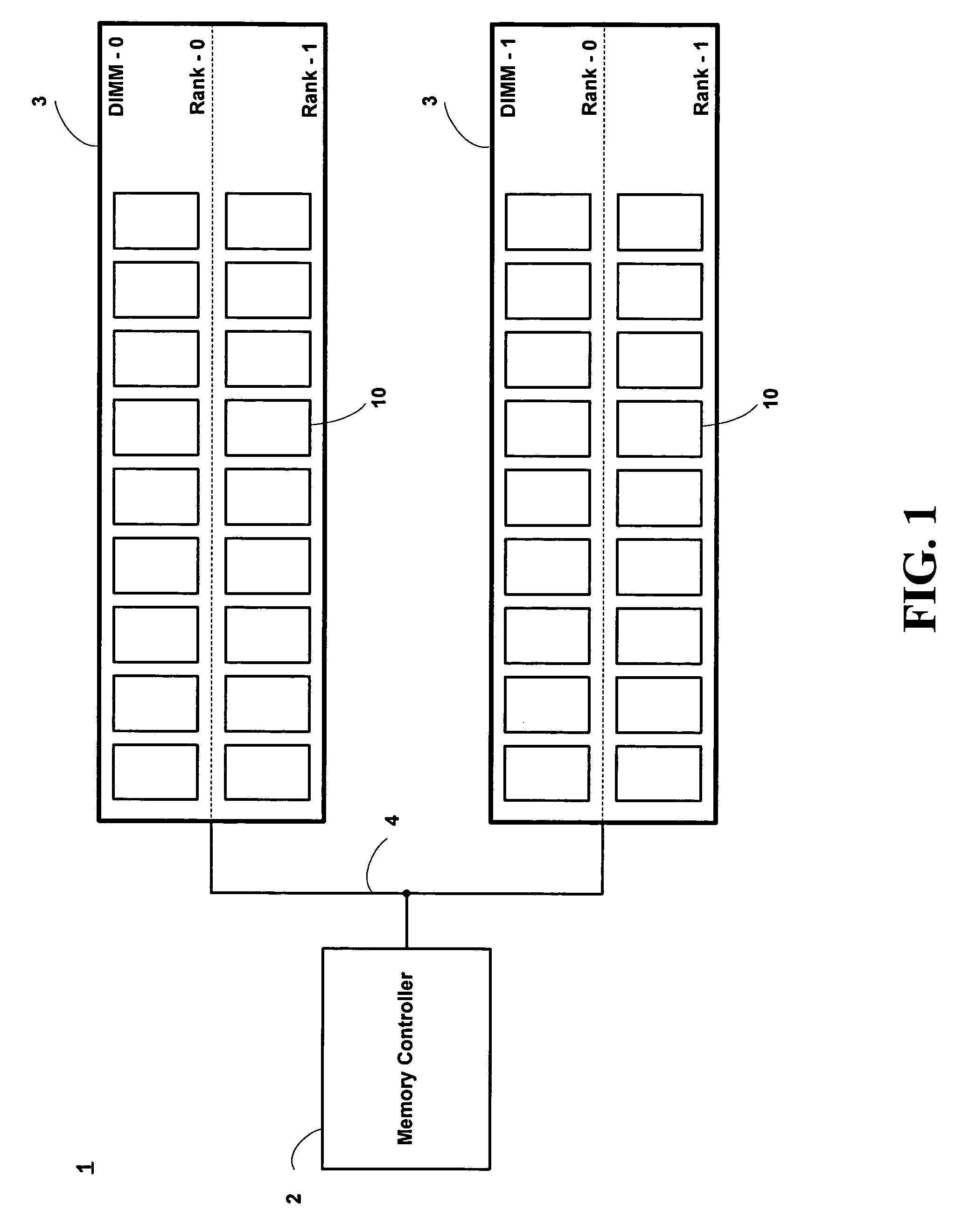

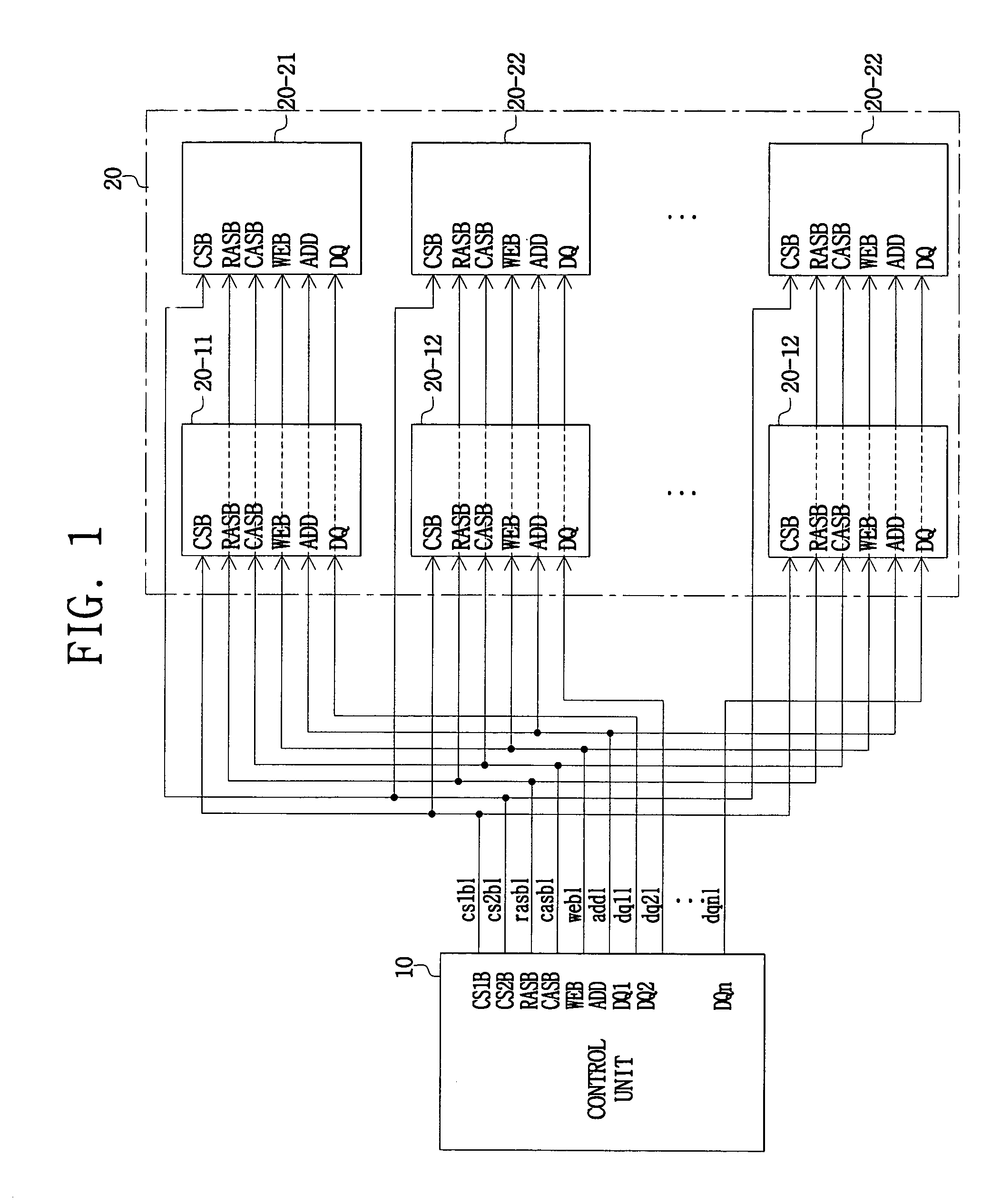

Memory devices, systems and methods using selective on-die termination

A memory system includes first and second memory devices having commonly connected data terminals and commonly connected memory control signal terminals, e.g., devices in respective first and second independently selectable memory banks that share common data lines and common memory control signal lines, such as column address strobe, row address strobe, write enable, and address signal lines. The first and second memory devices includes respective selective on-die termination (ODT) circuits configured to selectively provide first and second termination impedances at their respective data terminals responsive to a memory control signal at the commonly connected memory control signal terminals. The selective ODT circuits may produce the first termination impedance responsive to a memory write operation, and may produce the second termination impedance responsive to a memory read operation and / or expiration of a predetermined time interval following termination of the memory write operation. Preferably, the first termination impedance is less than the second termination impedance, and the selective ODT circuits provide the first termination impedance responsive to the memory write operation irrespective of which of the first and second memory devices is being written to.

Owner:SAMSUNG ELECTRONICS CO LTD

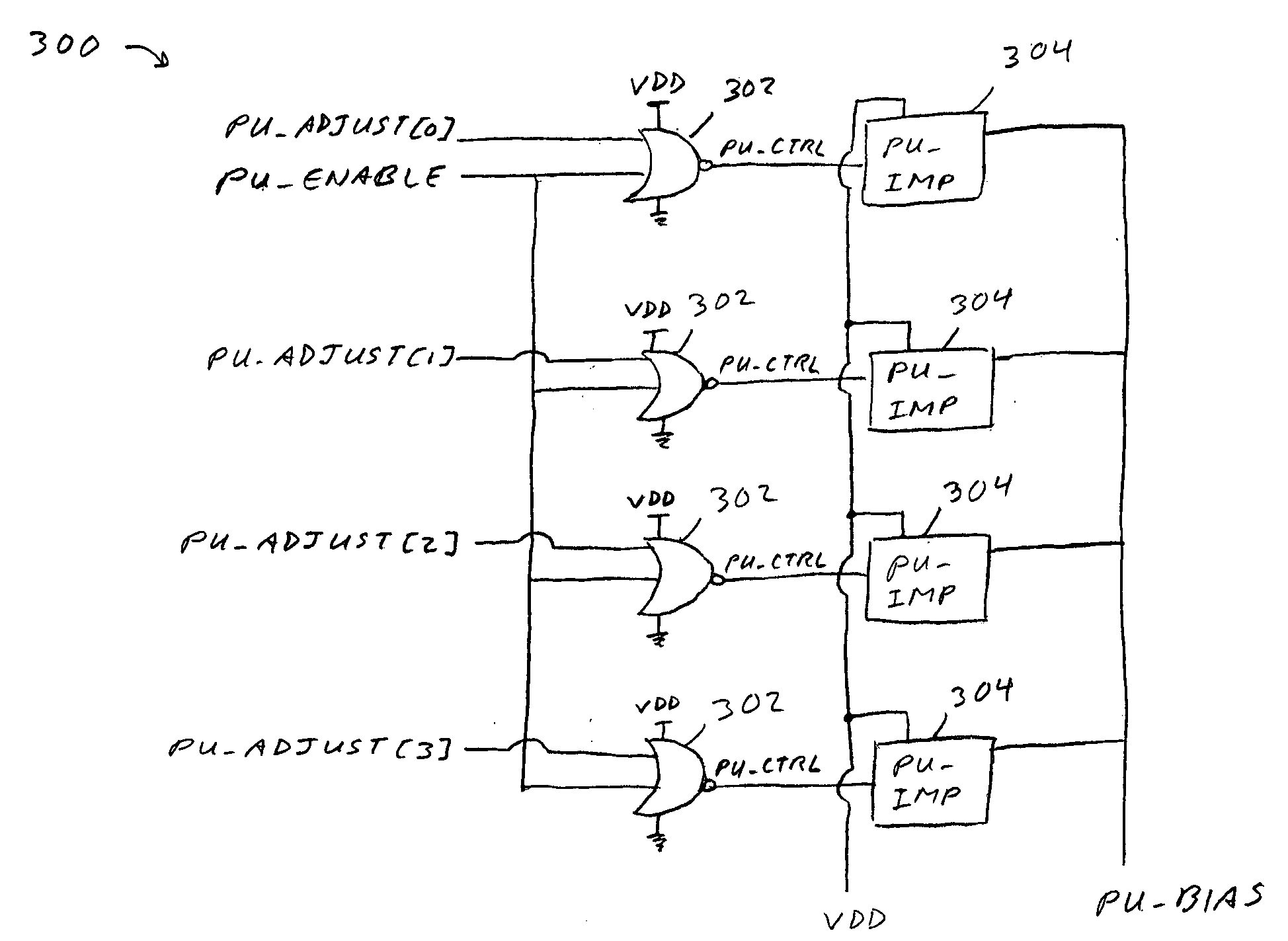

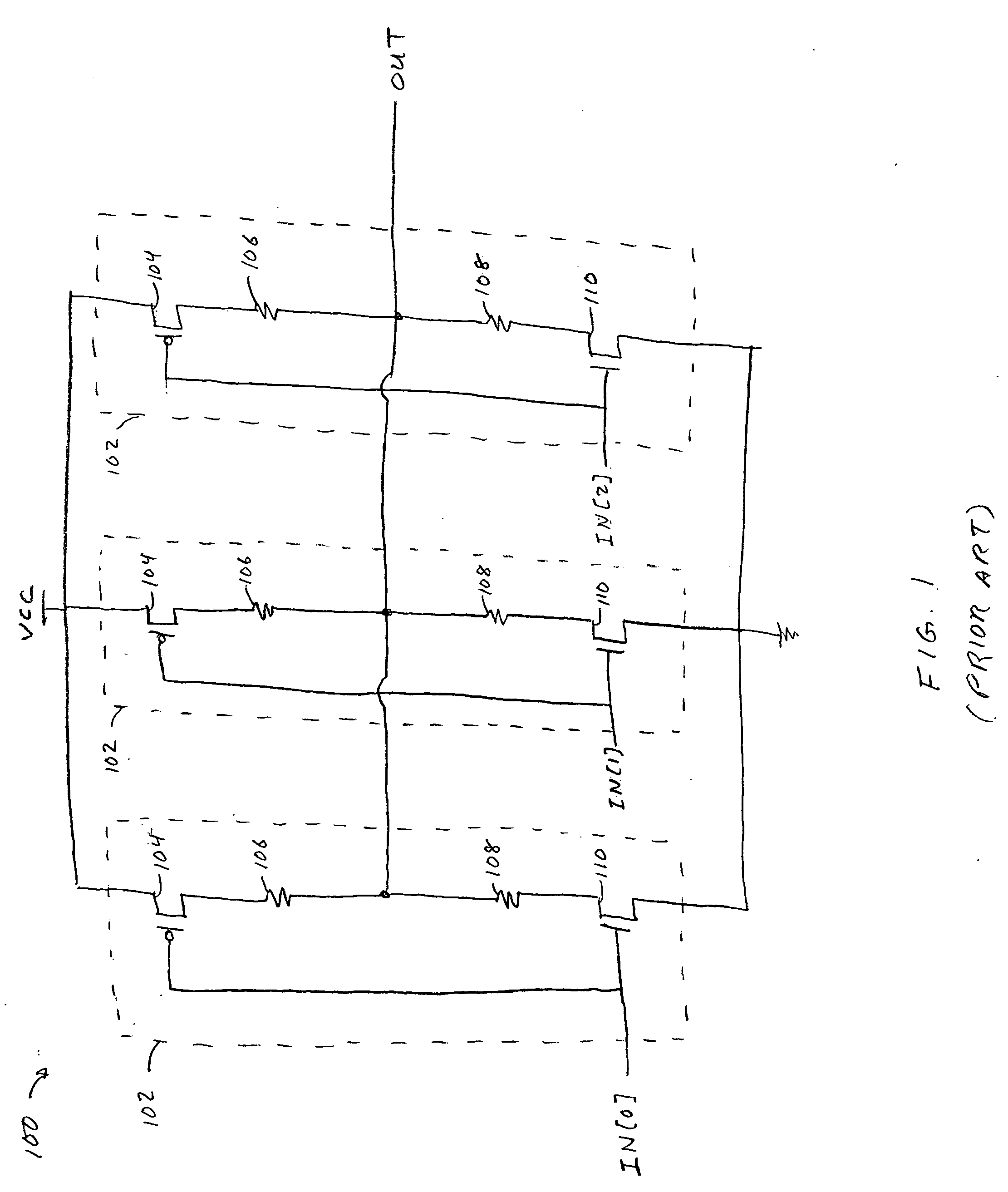

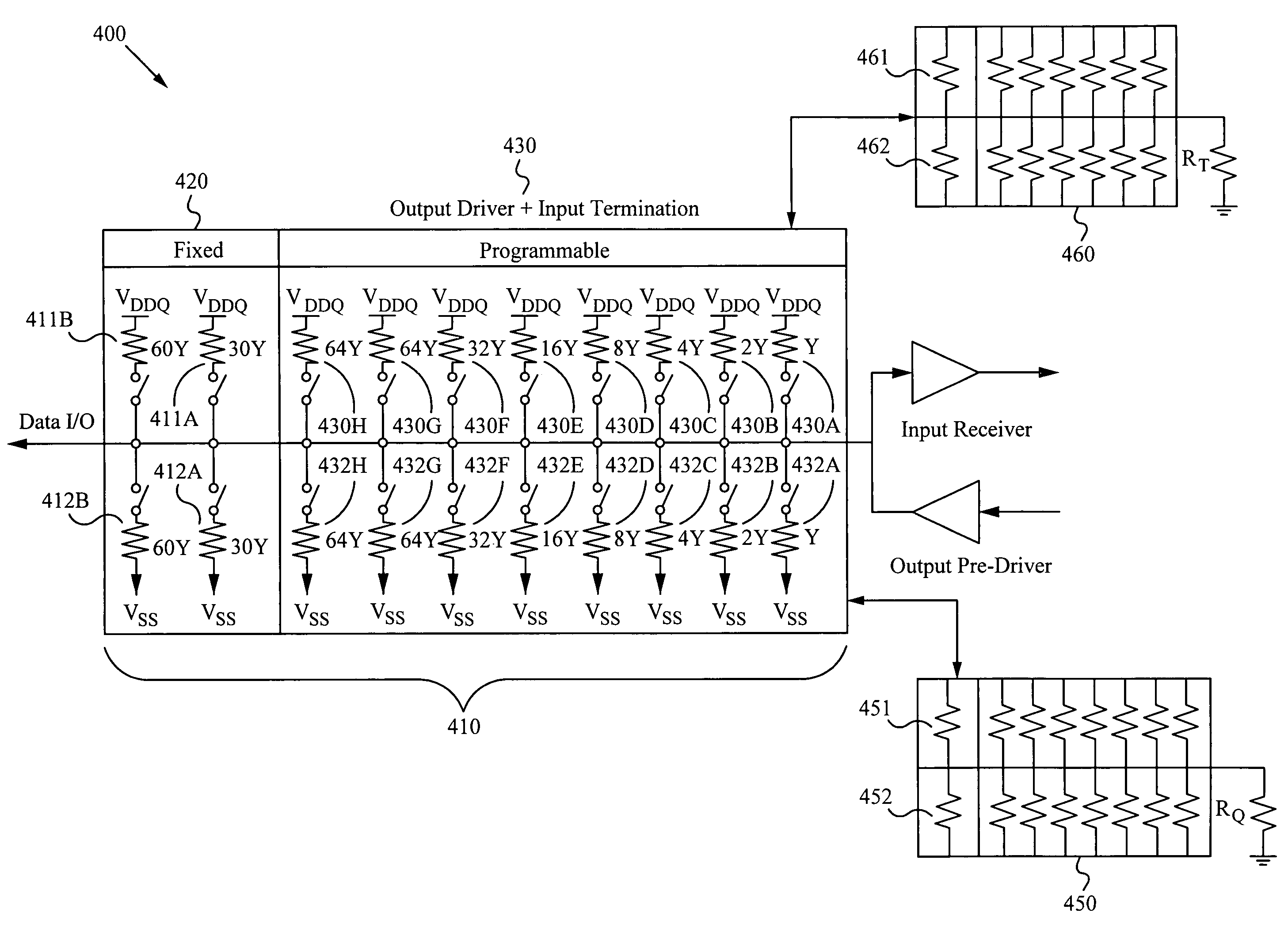

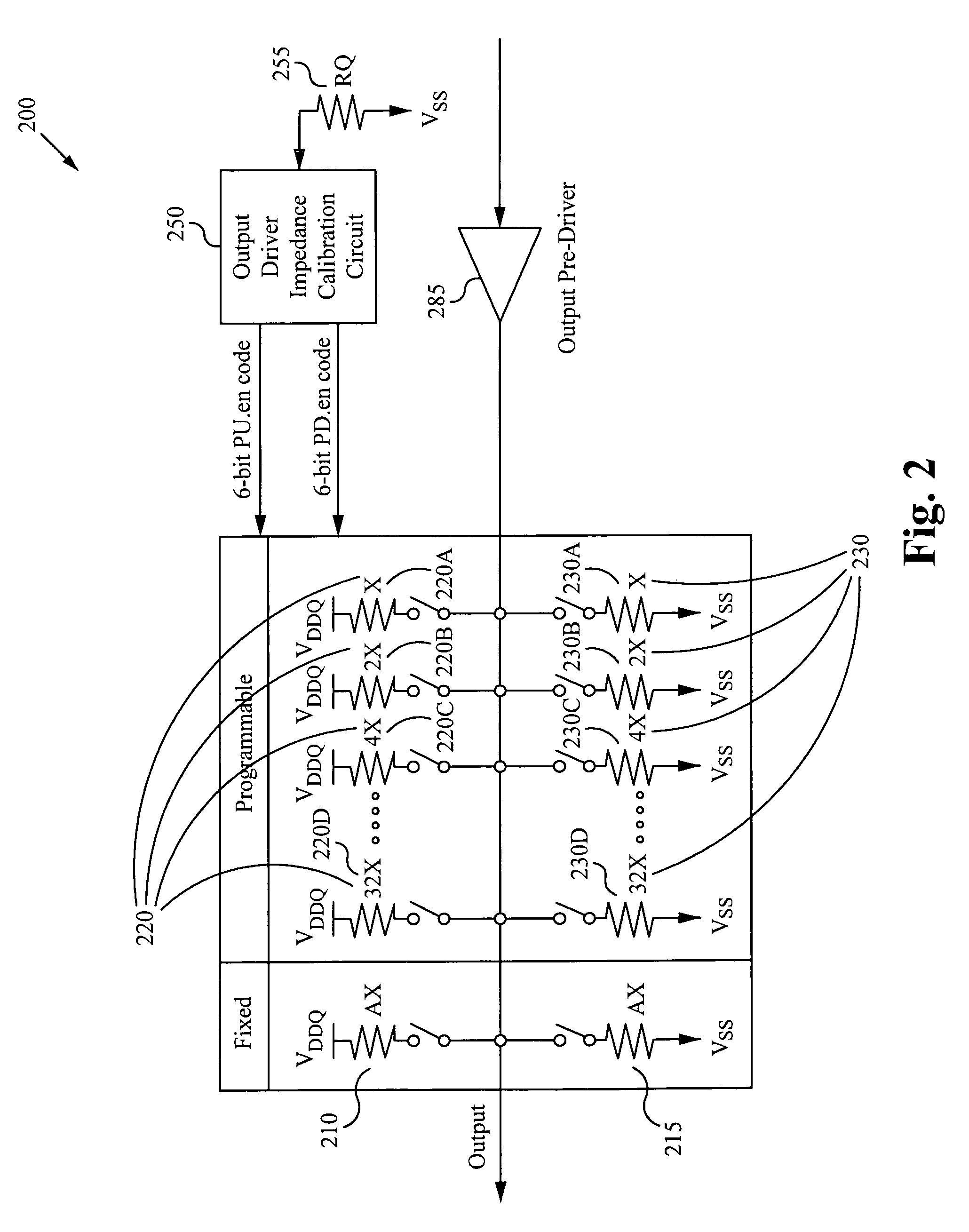

Efficient method for implementing programmable impedance output drivers and programmable input on die termination on a bi-directional data bus

ActiveUS7646215B2Input/output impedence modificationReliability increasing modificationsCapacitanceEngineering

A combined input and termination circuit comprises a fixed portion of impedance and a programmable portion of impedance. The fixed portion is able to be fixed in a driver mode and a termination mode. The programmable portion is able to be configured to have a desired impedance in a driver mode or a termination mode while maintaining minimum associated capacitance.

Owner:GSI TECH

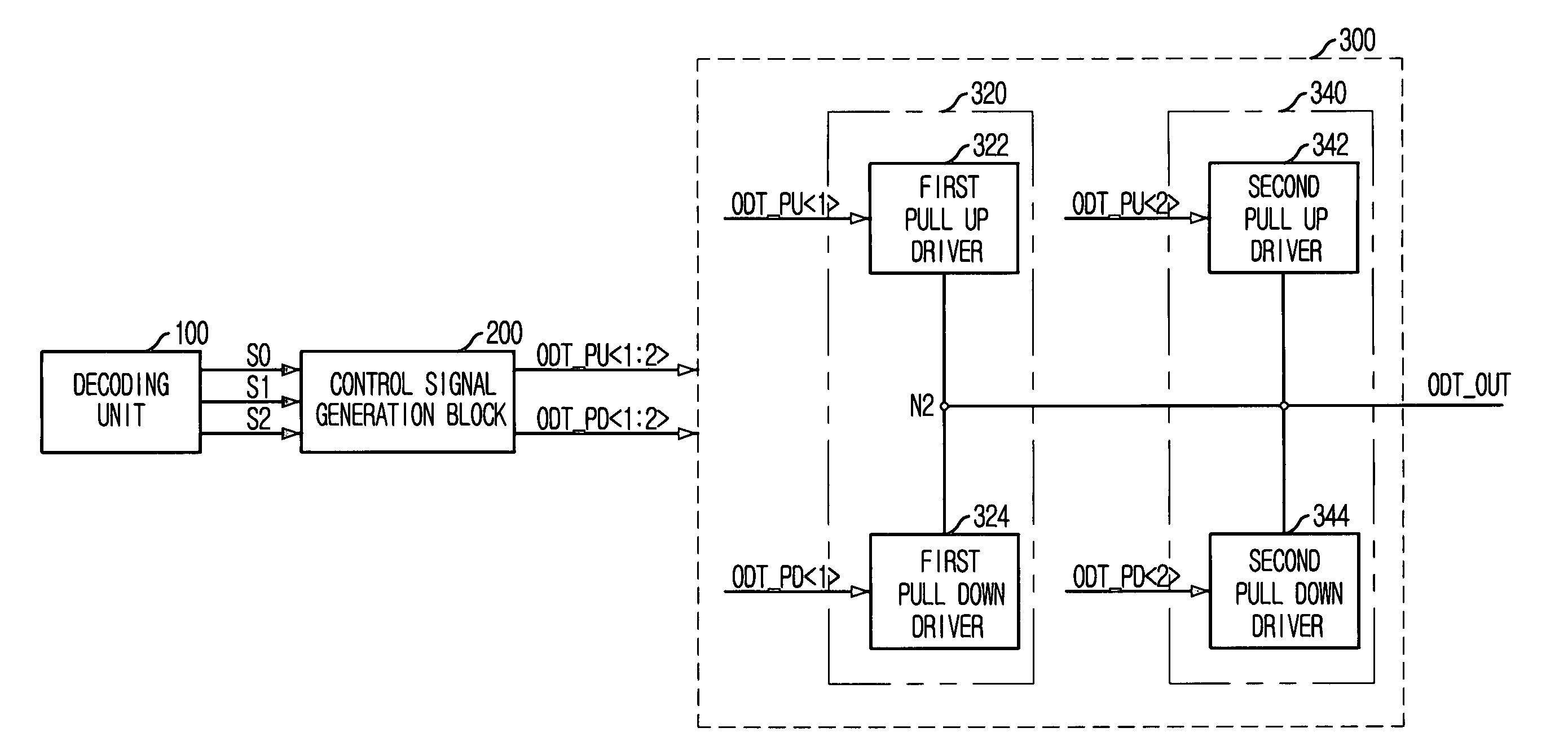

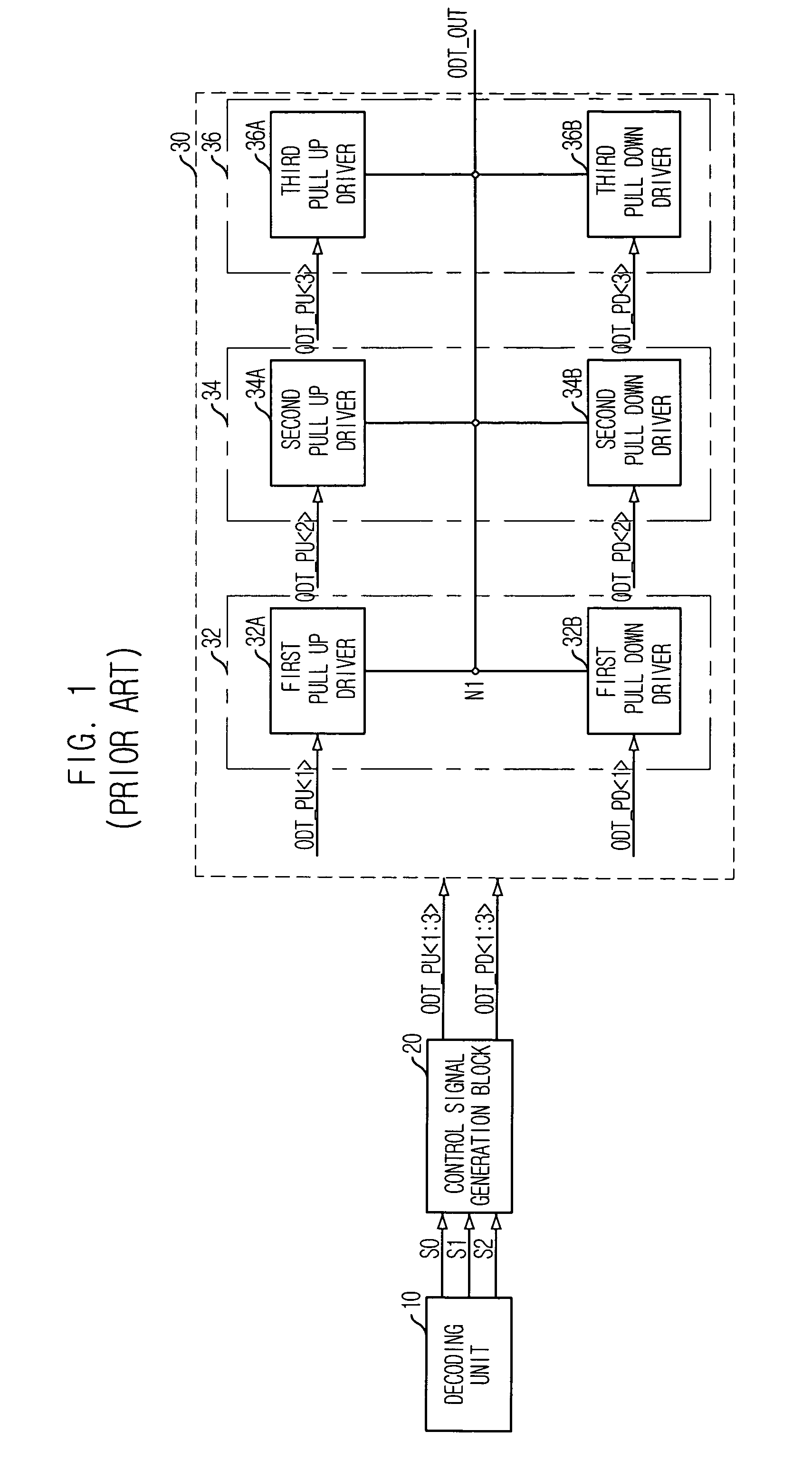

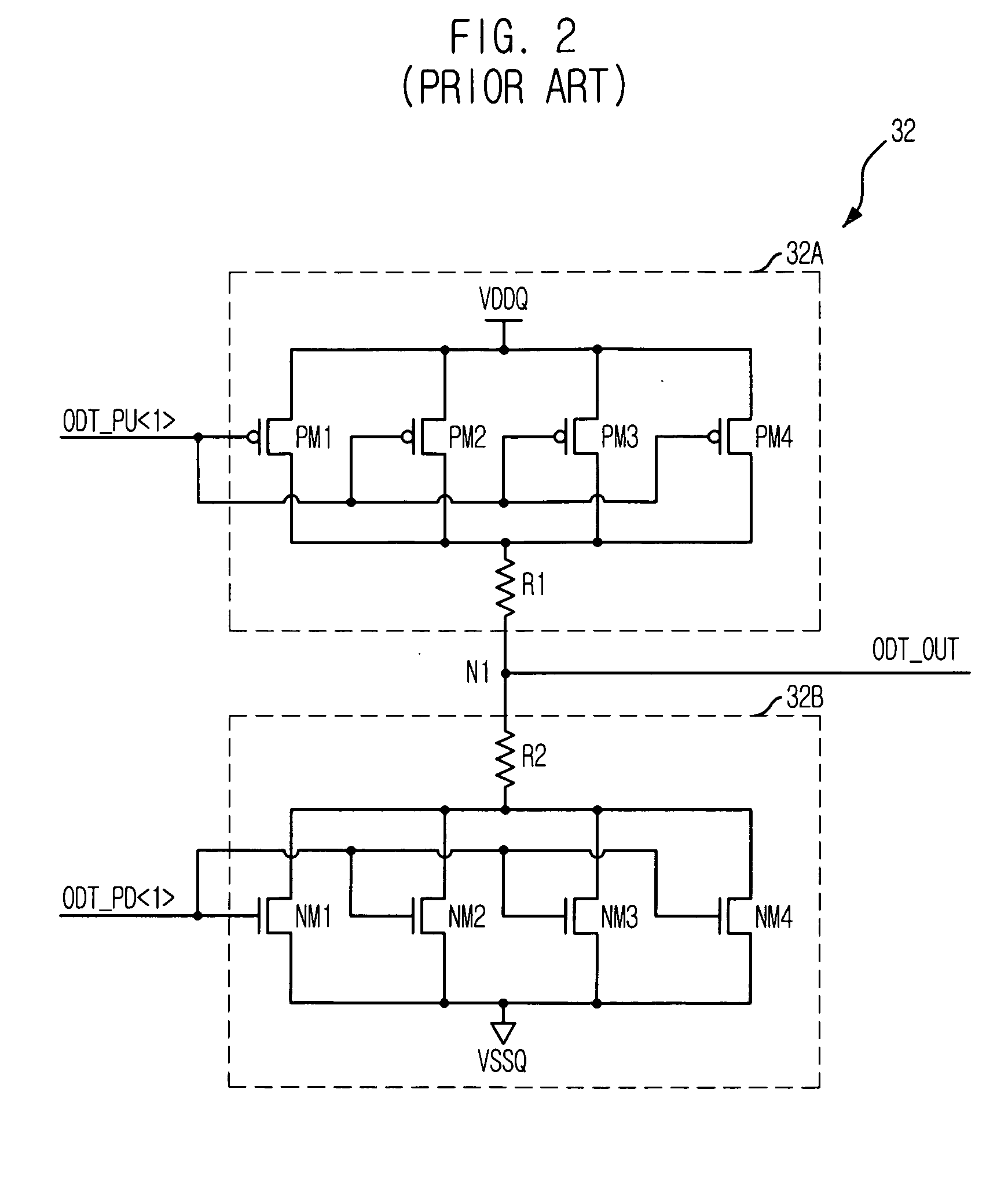

Semiconductor memory device with on-die termination circuit

ActiveUS20060091901A1Stable effective termination resistance valueEffective valueLogic circuit coupling arrangementsReliability increasing modificationsControl signalProcessor register

An on-die termination circuit with a stable effective termination resistance value and stabilized impedance mismatching. The on-die termination circuit includes: a decoding unit for decoding set values of an extended mode register set; an ODT output driver block including a plurality of output driver units connected in parallel with an output node for outputting an output signal and assigned with different resistance values; and a control signal generation block for generating a plurality of pull up and pull down control signals for turning on / off the plurality of output driver units in response to output signals of the decoding unit.

Owner:SK HYNIX INC

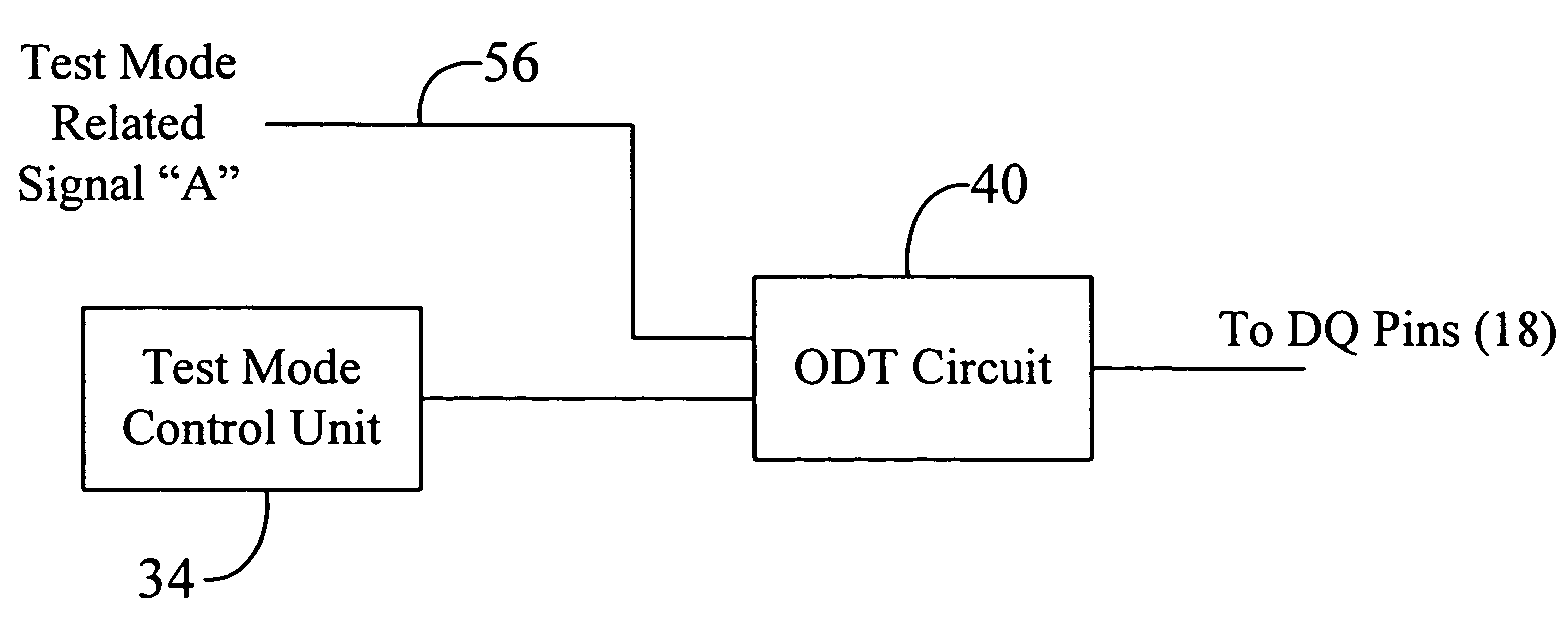

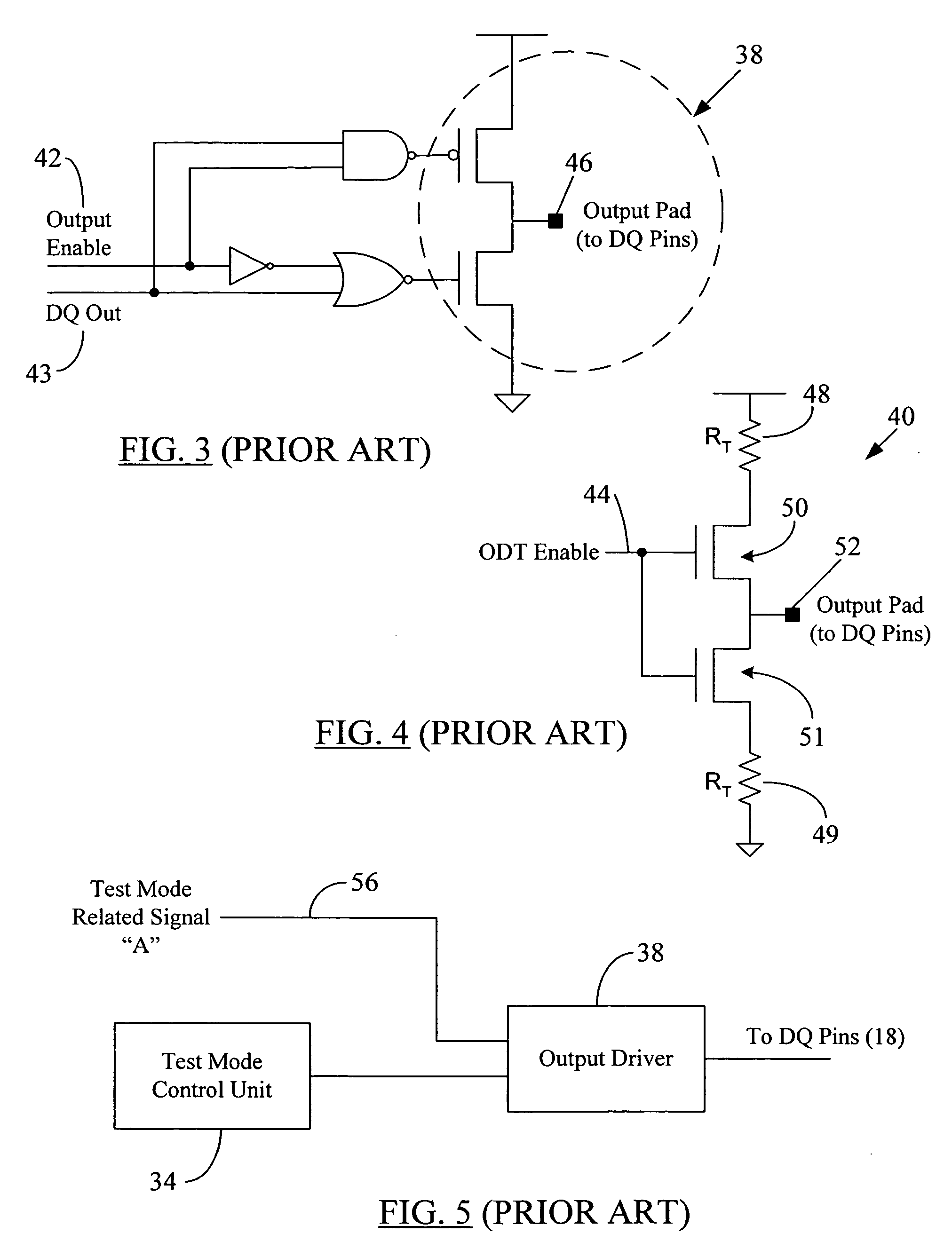

Real time testing using on die termination (ODT) circuit

InactiveUS20050283671A1Increase speedMaximize utilizationElectronic circuit testingError detection/correctionSystems designSignal quality

A system and method to operate an electronic device, such as a memory chip, in a test mode using the device's built-in ODT (on die termination) circuit is disclosed. One or more test mode related signals, which include on-die signals and other relevant information, may be transferred from the integrated circuit of the electronic device to an external processor using the device's ODT circuit instead of the output data signal driver circuit. Therefore, no capacitive loading of output drivers occurs during test mode operations. Thus the speed of the output data path (i.e., the circuit path propagating non-test mode related signals from the electronic device to other external units in the system) is not affected by test mode operations, allowing a system designer to increase the speed of the data output path as much as desired. Further, deterioration in the quality of signals output from the output drivers is also avoided. Also, the use of a minimal number of logic gates along with the existing ODT circuits to perform transmission of test mode related signals substantially maximizes chip real estate utilization without waste. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:MICRON TECH INC