Vertical double-diffusion metal oxide semiconductor device and manufacturing method thereof

An oxide semiconductor and vertical double-diffusion technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large reverse transmission capacitance, large gate coverage area, and reduced device withstand voltage, achieving Effects of reducing reverse capacitance, shortening switching time, and reducing reverse recovery time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

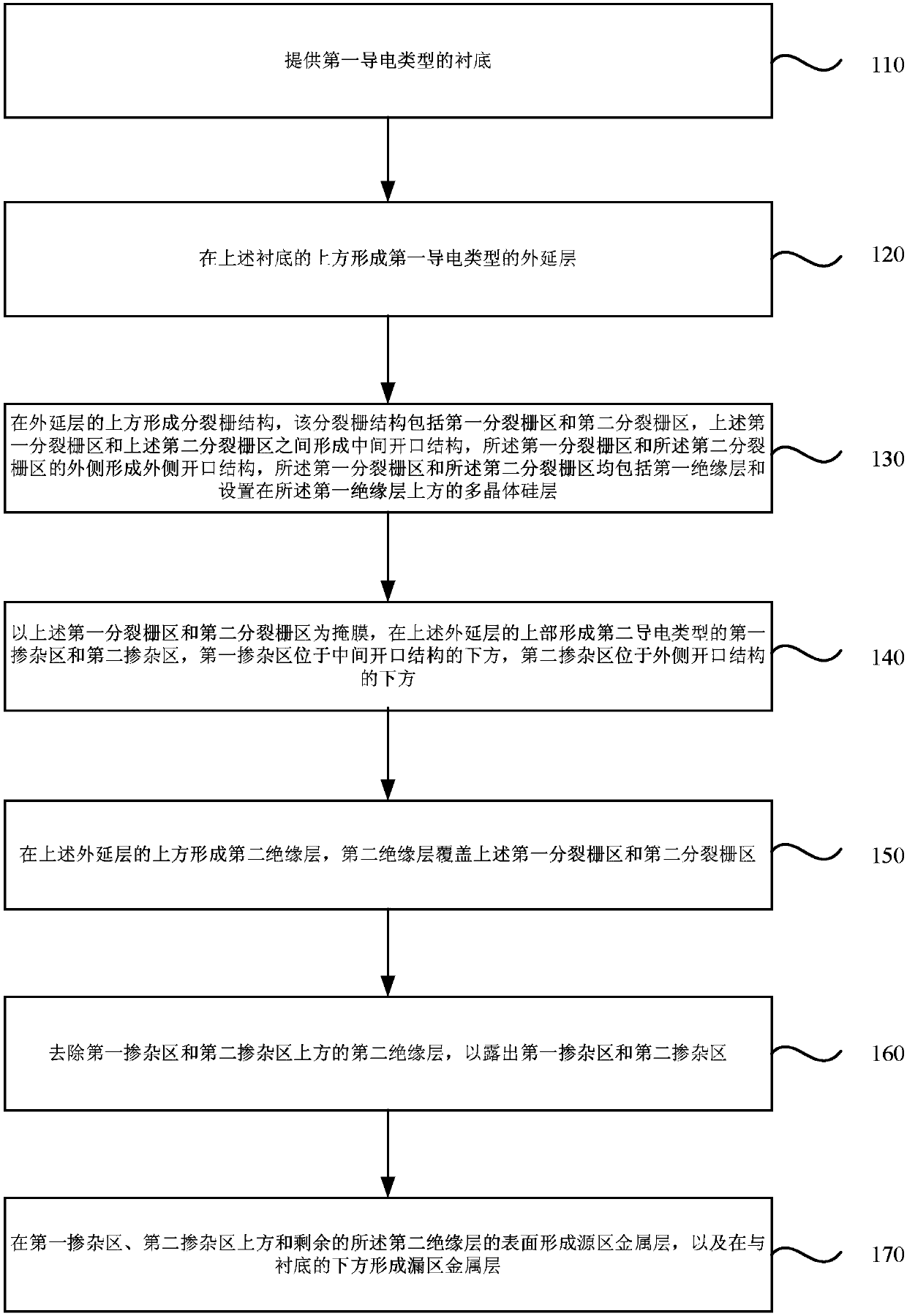

[0037] figure 1 It is a schematic flowchart of a method for fabricating a vertical double-diffused metal oxide semiconductor device provided in Embodiment 1 of the present invention. Figure 2a - FIG. 2m is a cross-sectional view corresponding to each step of a method for fabricating a vertical double-diffused metal oxide semiconductor device according to Embodiment 1 of the present invention.

[0038] see figure 1 , the present embodiment provides a method for fabricating a vertical double-diffused metal oxide semiconductor device, the method comprising the following steps:

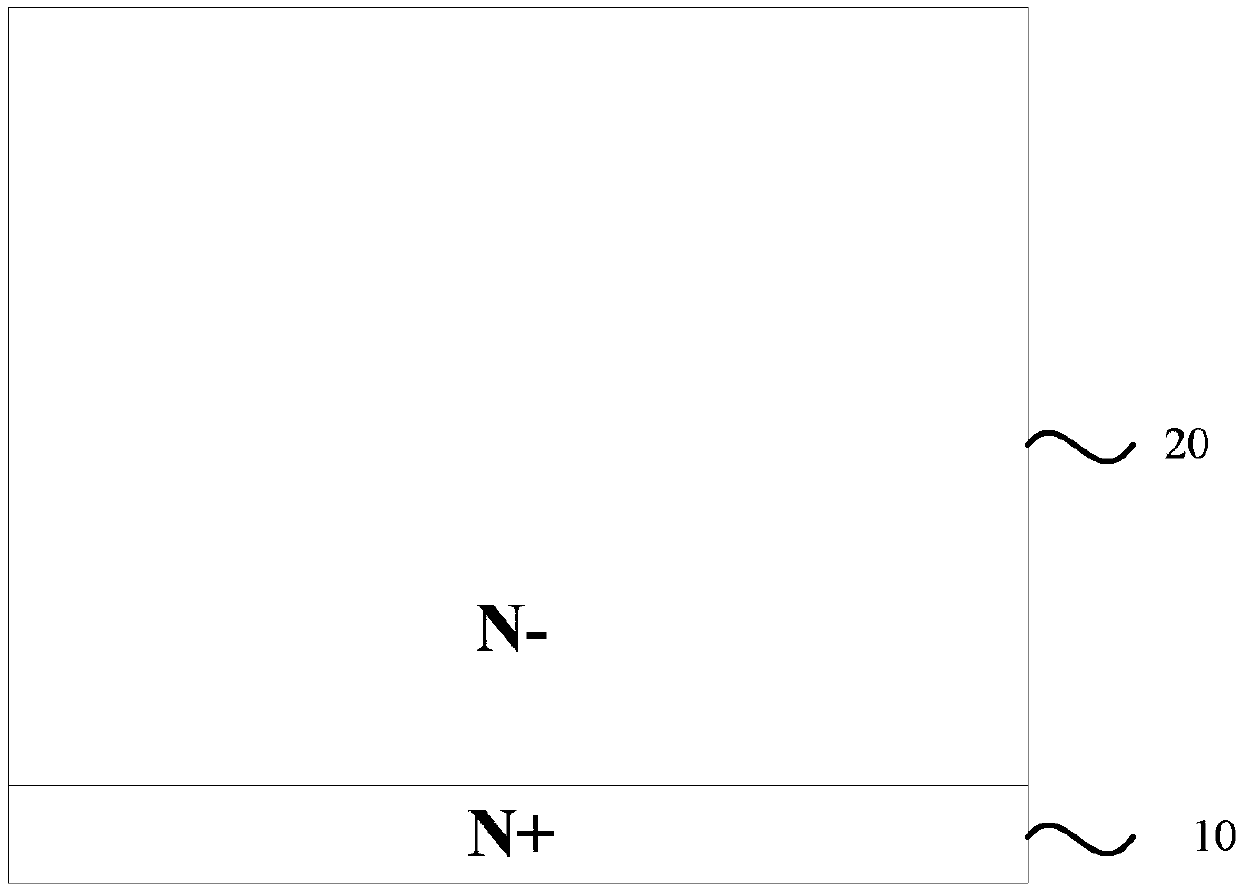

[0039] Step 110, providing a substrate of the first conductivity type.

[0040] Referring to 2a, this embodiment takes an N-channel VDMOS device as an example, where the first conductivity type is N-type, and this embodiment needs to provide an N-type substrate. In this embodiment, the single crystal silicon wafer is heavily doped with N-type ions, which can be represented by N+, and the N-type ions c...

Embodiment 2

[0068] Embodiment 2 of the present invention provides a vertical double-diffused metal oxide semiconductor device, which can be manufactured by the preparation method of Embodiment 1. Specifically, the vertical double-diffused metal oxide semiconductor device provided by the embodiment of the present invention includes :

[0069] A substrate of the first conductivity type.

[0070] The epitaxial layer of the first conductivity type is located above the substrate.

[0071] The split gate structure, located above the epitaxial layer, includes a first split gate region and a second split gate region, an intermediate opening structure is formed between the first split gate region and the second split gate region, and the first split gate region and the second split gate region The outer side of the split gate region is an outer opening structure, and both the first split gate region and the second split gate region include a first insulating layer and a polysilicon layer disposed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More