Patents

Literature

63results about How to "Reduce reverse current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Magnetic memory

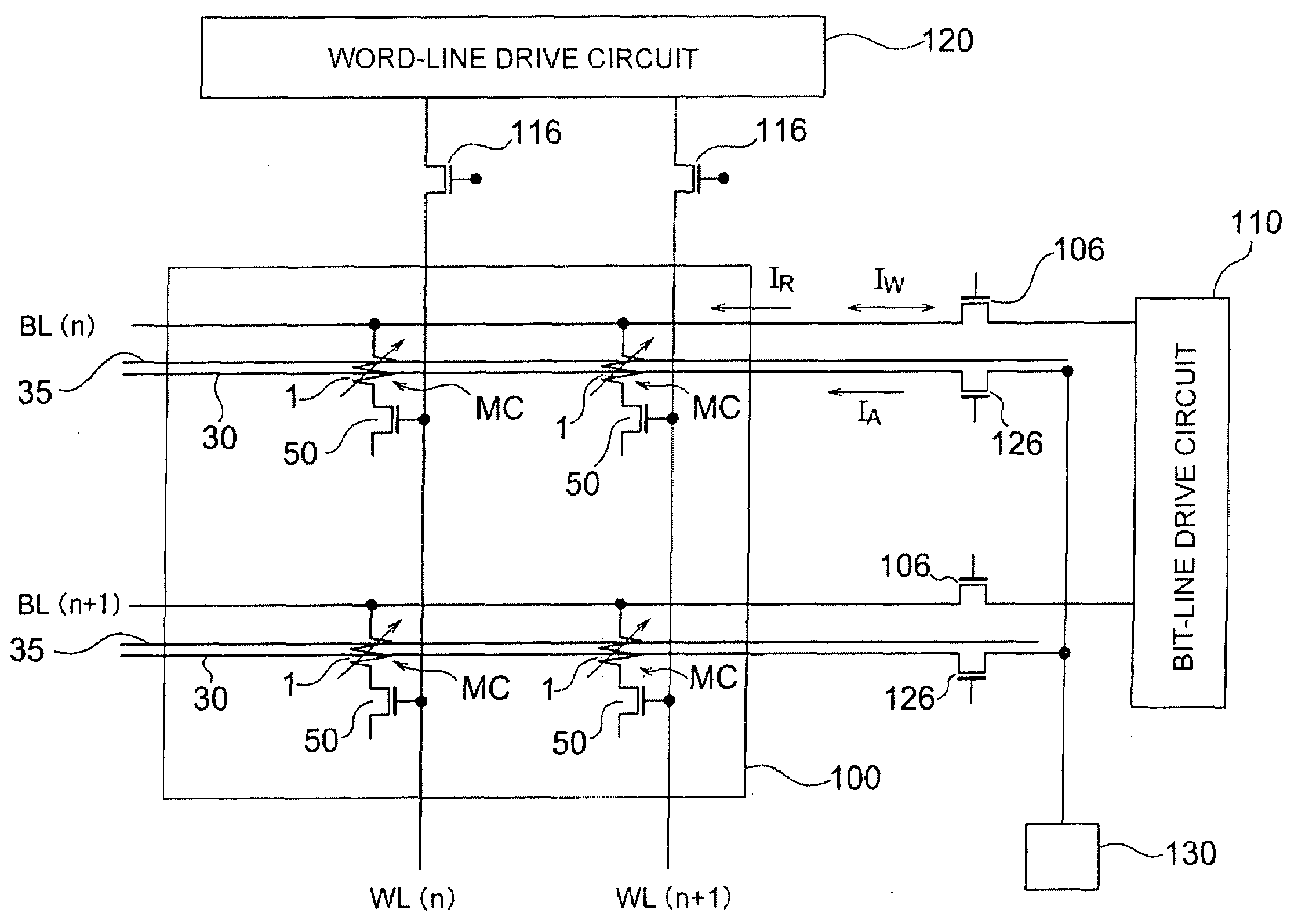

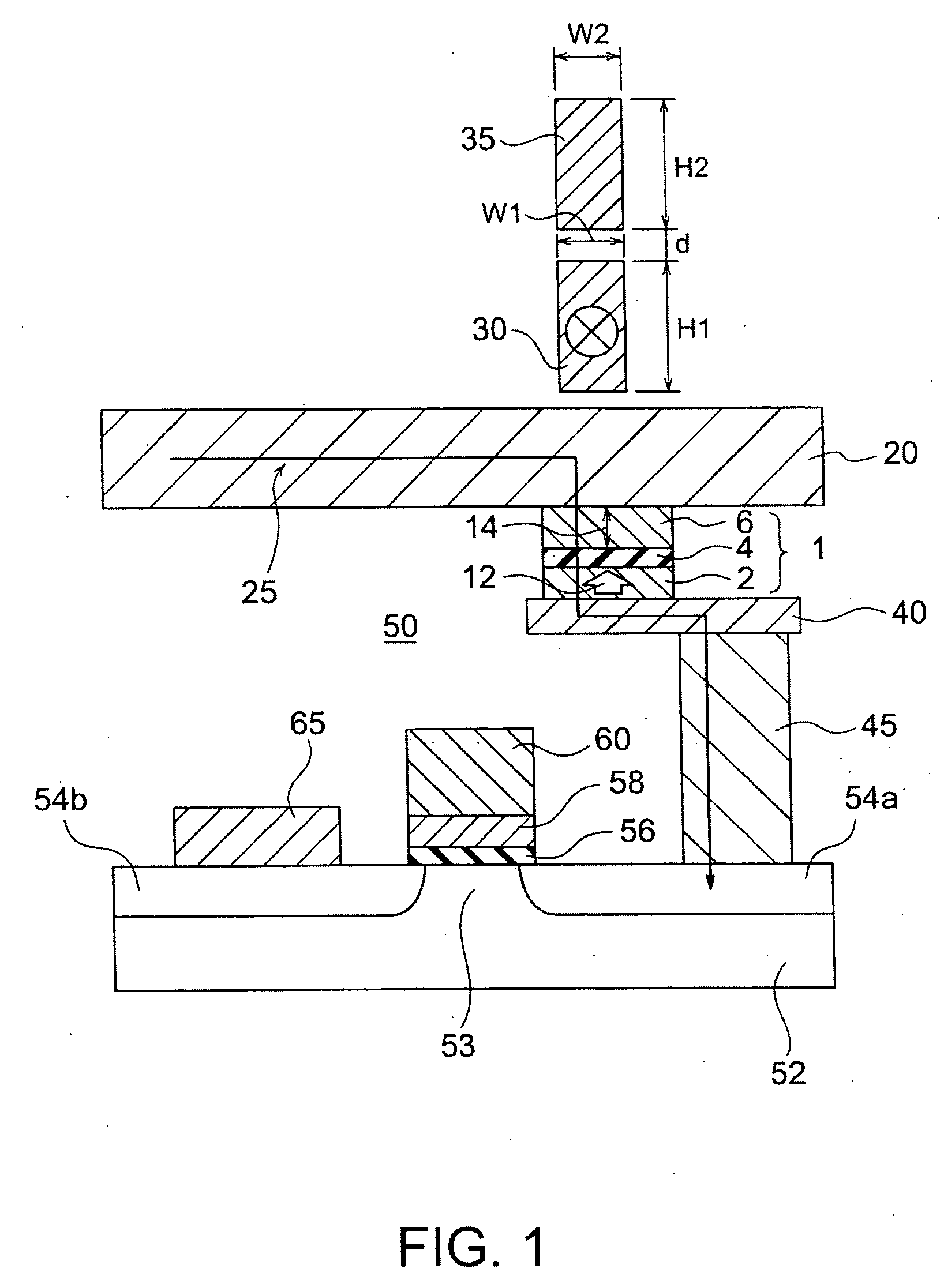

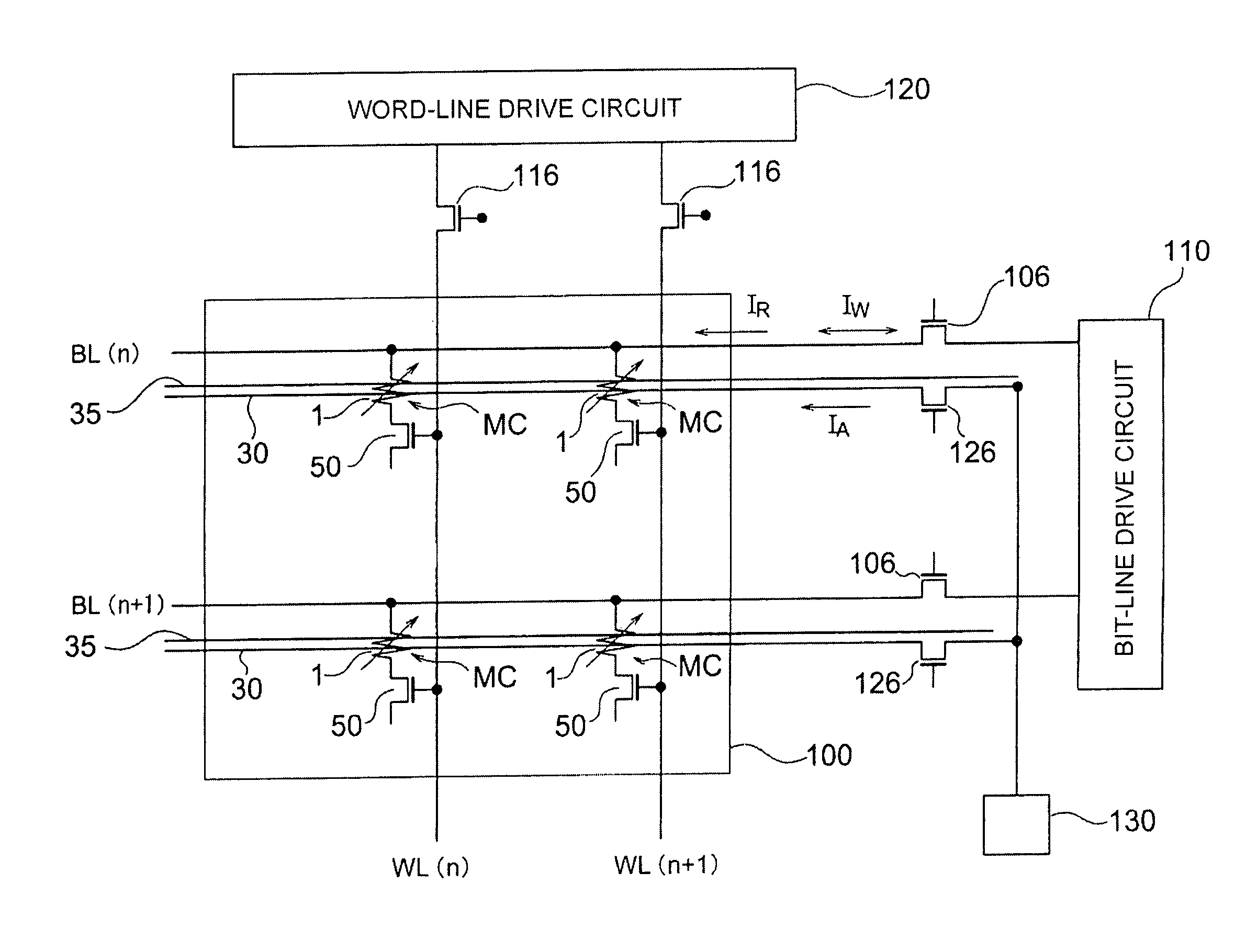

ActiveUS20090207724A1Reduce variationReduce reverse currentApparatus for flat record carriersSolid-state devicesMagnetizationMagnetic memory

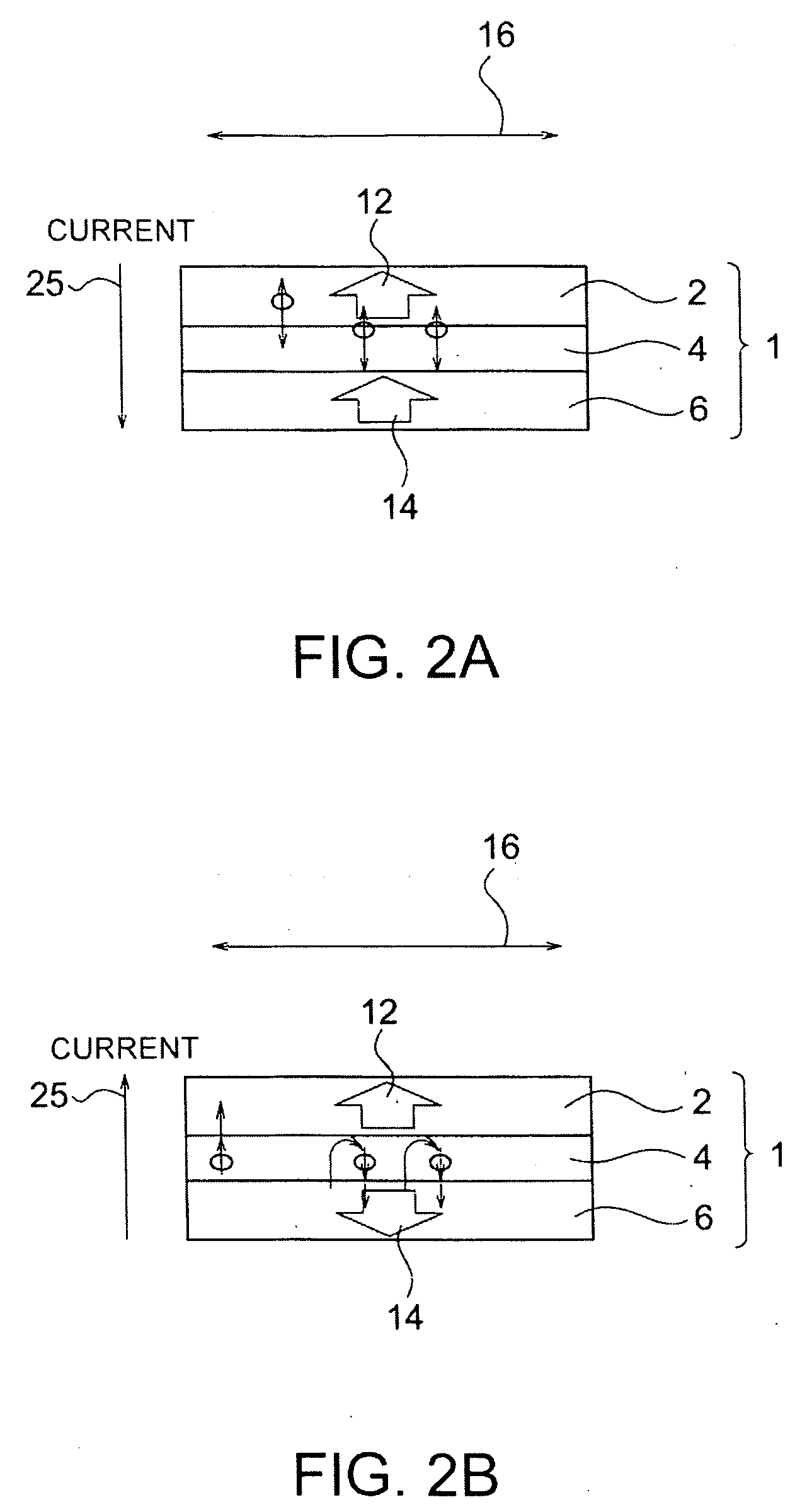

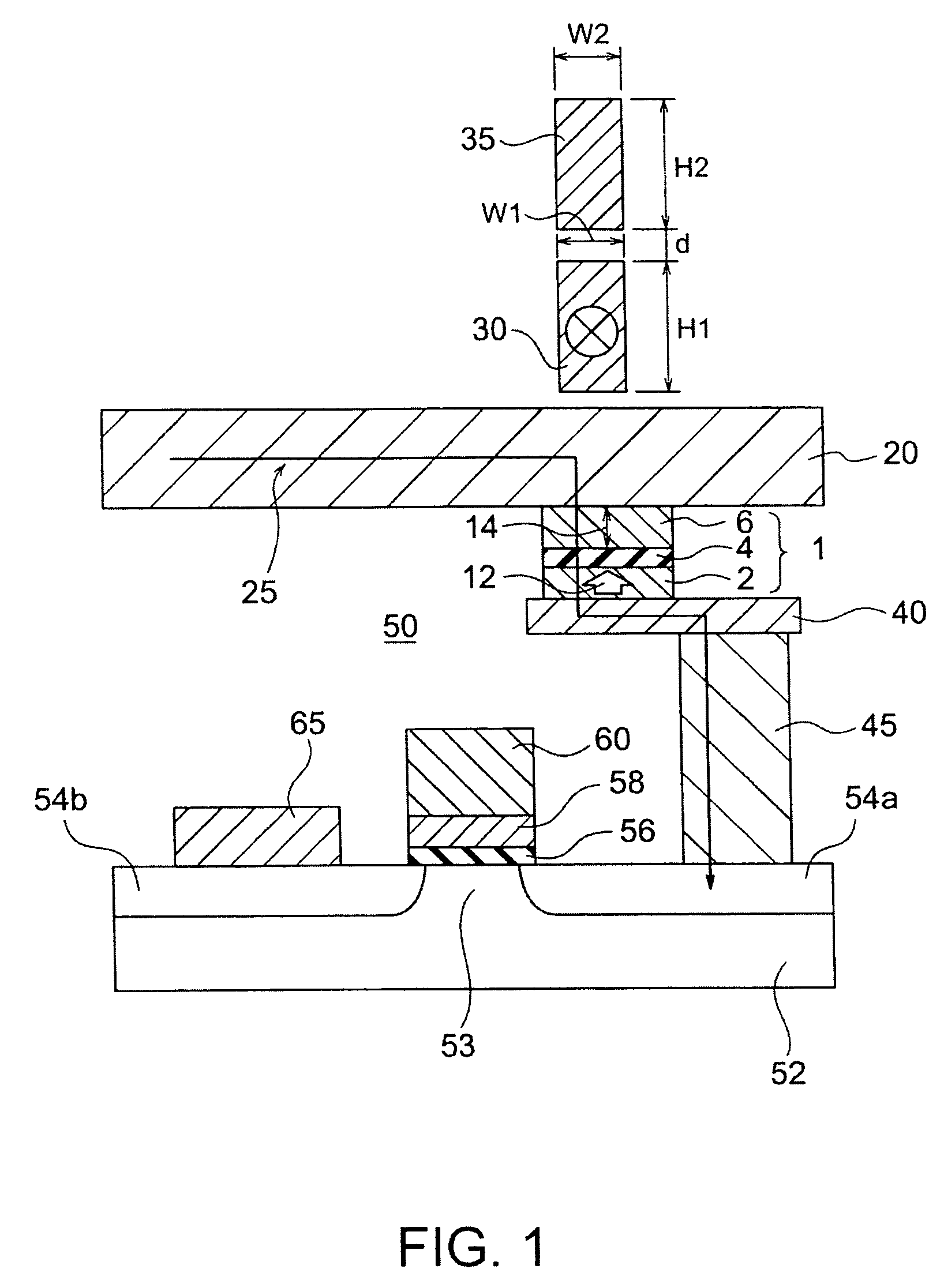

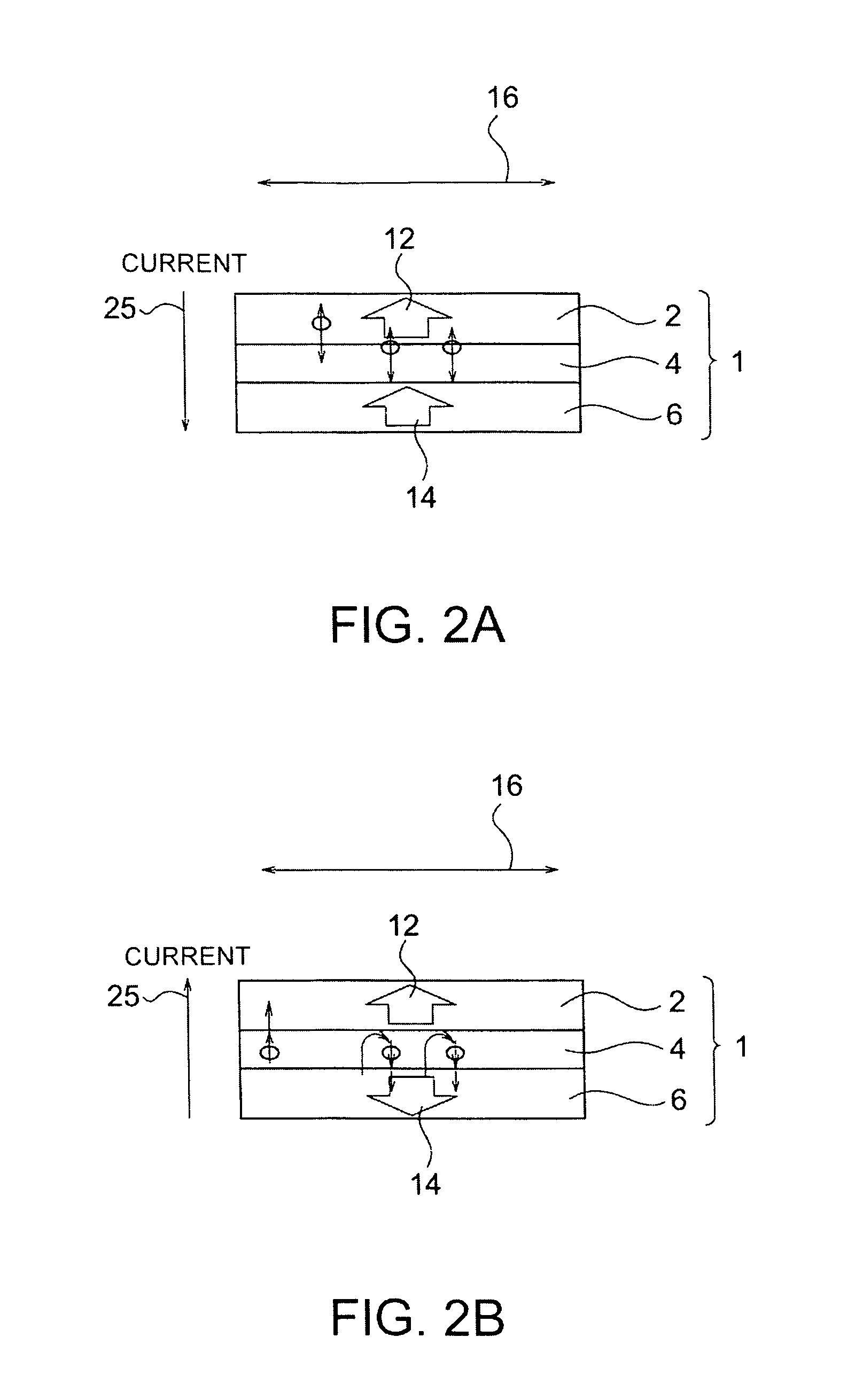

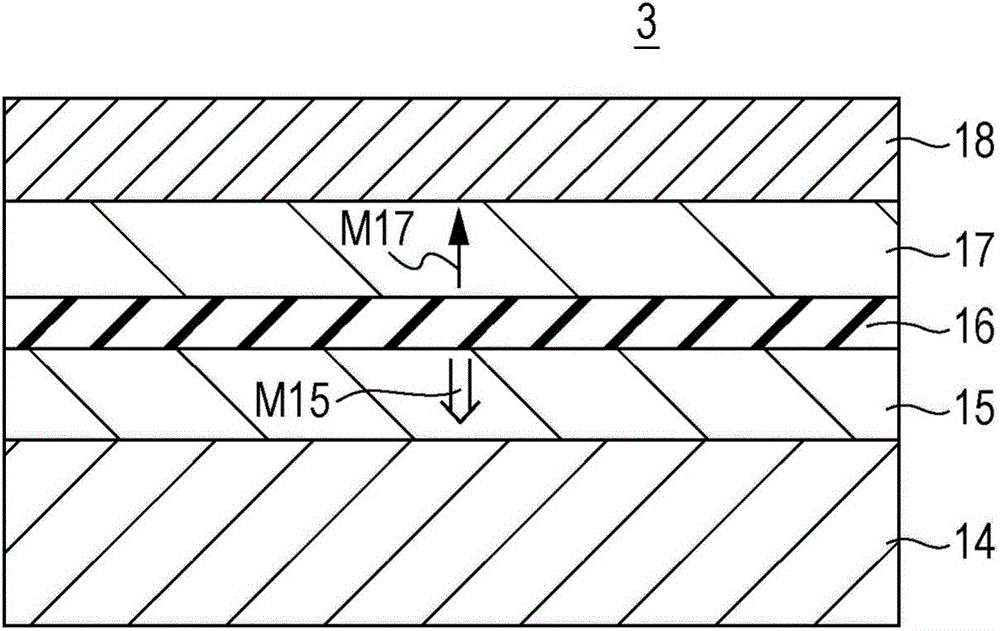

A magnetic memory is provided with a memory cell. The memory cell includes a magnetic recording element, an interconnection to generate a radio-frequency current-induced magnetic field and a ground line. The magnetic recording element is provided with a first magnetic layer whose magnetization direction is substantially fixed, a magnetic recording layer whose magnetization direction is substantially reversed by spin-polarized electrons passing through the magnetic recording layer and a first nonmagnetic layer provided between the first magnetic layer and the magnetic recording layer. The interconnection is provided above the magnetic recording element to generate a radio-frequency current-induced magnetic field acting in a direction substantially perpendicular to a magnetization easy axis of the magnetic recording layer. The ground line is provided on a side opposite to the magnetic recording element with respect to the interconnection.

Owner:KIOXIA CORP

Magnetic memory

ActiveUS8077509B2Reduce variationReduce reverse currentApparatus for flat record carriersMechanical record carriersMagnetizationMagnetic memory

A magnetic memory is provided with a memory cell. The memory cell includes a magnetic recording element, an interconnection to generate a radio-frequency current-induced magnetic field and a ground line. The magnetic recording element is provided with a first magnetic layer whose magnetization direction is substantially fixed, a magnetic recording layer whose magnetization direction is substantially reversed by spin-polarized electrons passing through the magnetic recording layer and a first nonmagnetic layer provided between the first magnetic layer and the magnetic recording layer. The interconnection is provided above the magnetic recording element to generate a radio-frequency current-induced magnetic field acting in a direction substantially perpendicular to a magnetization easy axis of the magnetic recording layer. The ground line is provided on a side opposite to the magnetic recording element with respect to the interconnection.

Owner:KIOXIA CORP

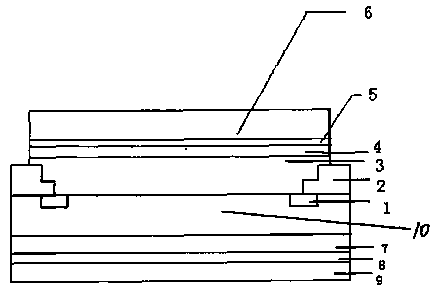

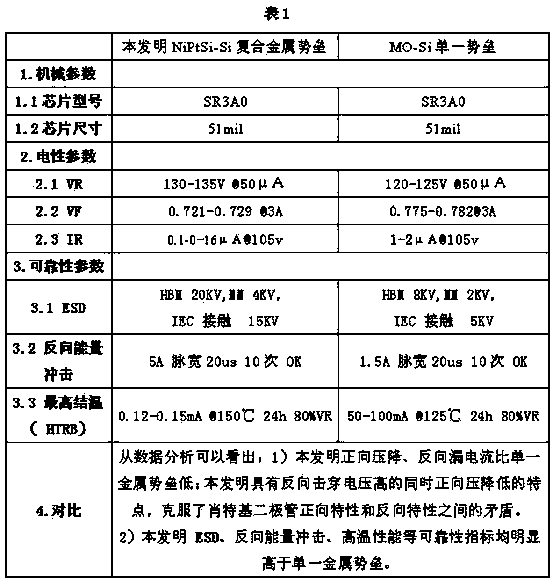

Schottky diode chip, Schottky diode device and manufacturing method for Schottky diode chip-composite barrier

ActiveCN103681885ABlocking mutual expansionImprove fatigue resistanceSemiconductor/solid-state device manufacturingDiodeSchottky barrierMetal silicide

The invention discloses a Schottky diode chip, a Schottky diode device and a manufacturing method for a Schottky diode chip-composite barrier. The Schottky diode chip comprises an N-type silicon semiconductor substrate; the obverse side of the semiconductor substrate is provided with a NiPtSi barrier layer, and the barrier layer makes direct contact with the semiconductor substrate to form a NiPtSi-Si barrier. The manufacturing method is simple, low in cost, practical and effective; NiPt alloy is adopted as Schottky barrier metal, and the composite metal silicide-silicon contact barrier (NiPtSi-Si) is formed; the obtained chip and the device eliminate the contradiction between forward voltage drop and reverse electric leakage with regard to a single-metal barrier, the reverse electric leakage and the forward voltage drop are both low, and meanwhile high-temperature resistant performance, antistatic performance, reverse energy impact performance and the like are well improved.

Owner:济南市半导体元件实验所

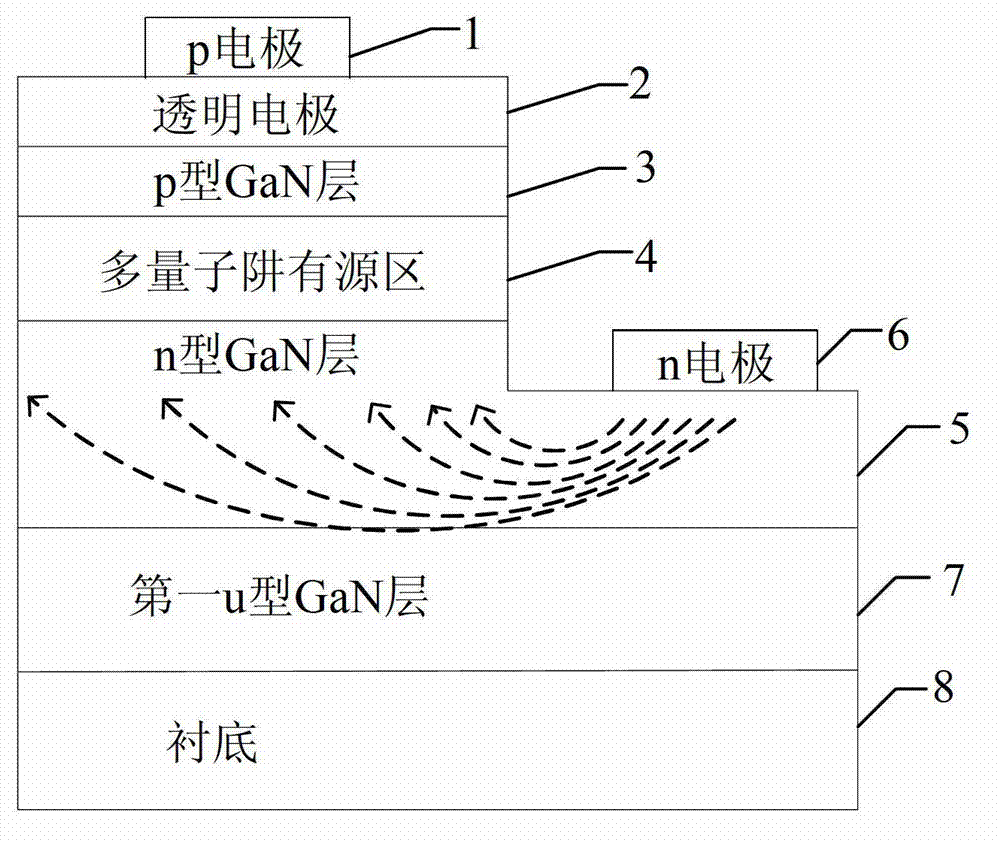

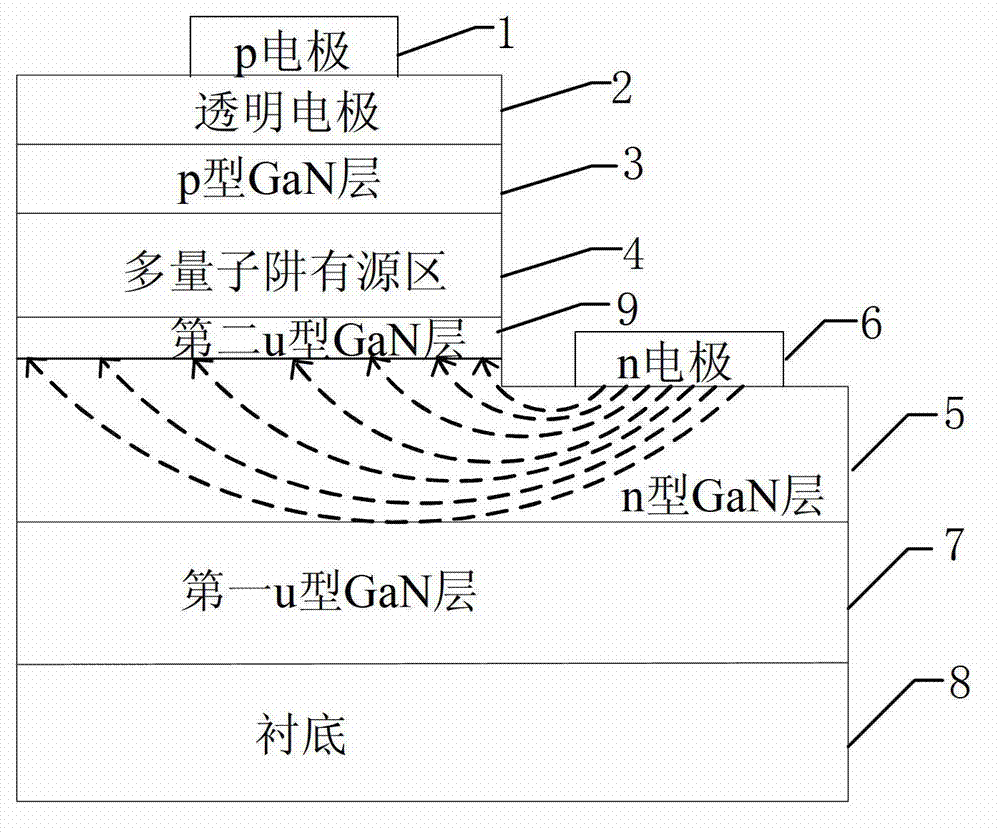

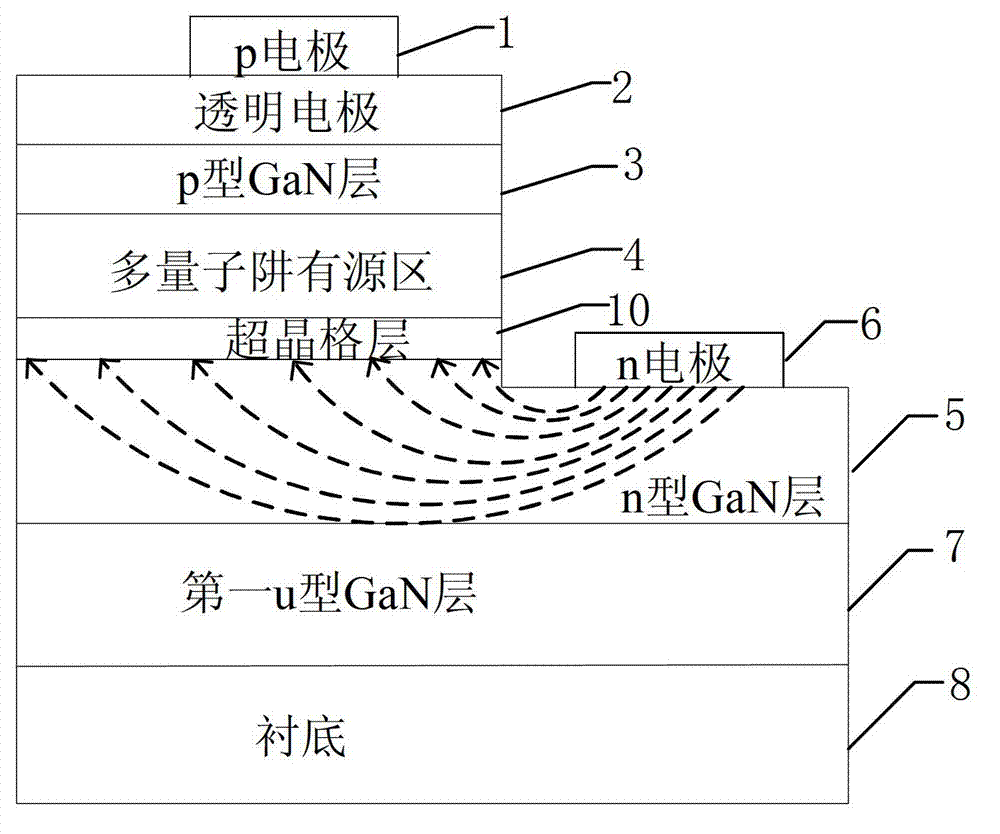

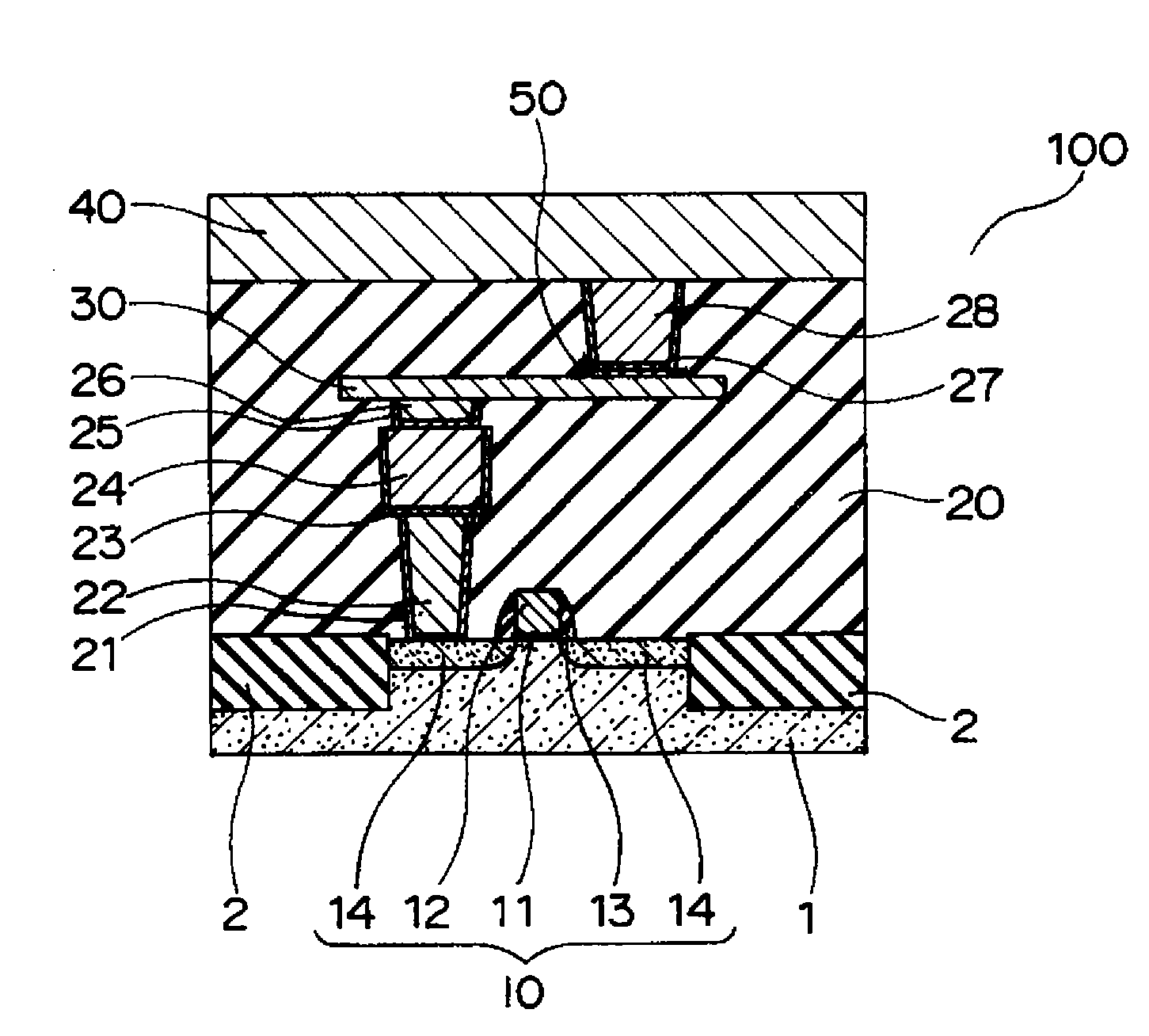

Gallium nitride (GaN) base light-emitting diode (LED) structure and method for improving photoelectric conversion efficiency thereof

InactiveCN103094441ALower forward voltageReduced resistance differenceSemiconductor devicesReverse currentGallium nitride

The invention relates to the field of photoelectric devices, in particular to a Gallium nitride (GaN) base light-emitting diode (LED) structure. The GaN base LED structure sequentially comprises a p electrode, a transparency electrode, a p type GaN layer, a multiple quantum well active area and an n type GaN layer from top to bottom. An n electrode, a first u type GaN layer and a substrate are etched on the n type GaN layer. A second u type GaN layer or a superlattice layer which is formed by a u type AlxGal-xN layer and low doping n type GaN in an alternate growing mode is inserted into between the multiple quantum well active area and the n type GaN layer. An x indicates the aluminous ingredient of the AlxGal-xN, and the value range of the x is that 0<=x<=1. Correspondingly, the invention further provides a method for improving the photoelectric conversion efficiency of the GaN base LED structure. Therefore, the transverse resistance difference of the GaN base LED structure is removed or reduced, so that currents can be expanded, forward voltages can be lowered, reverse currents are reduced, a luminous area is enlarged, and thus the photoelectric conversion efficiency of an LED is improved.

Owner:AQUALITE CO LTD

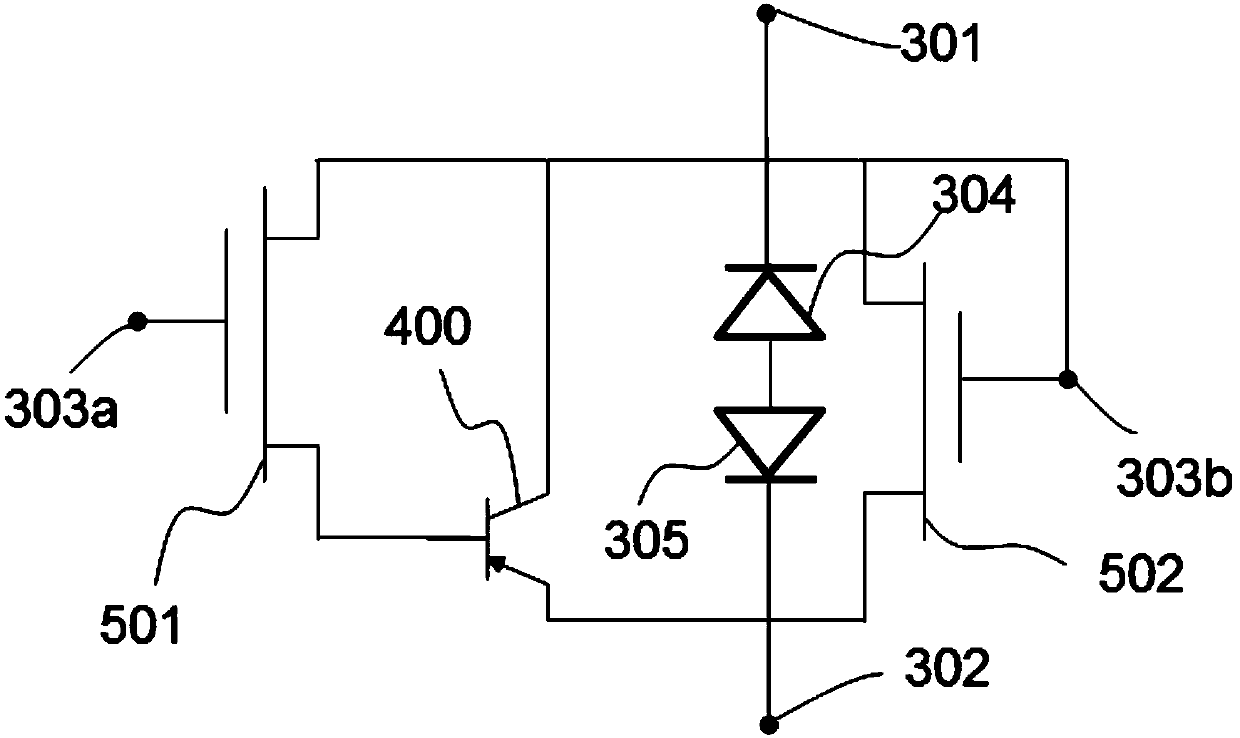

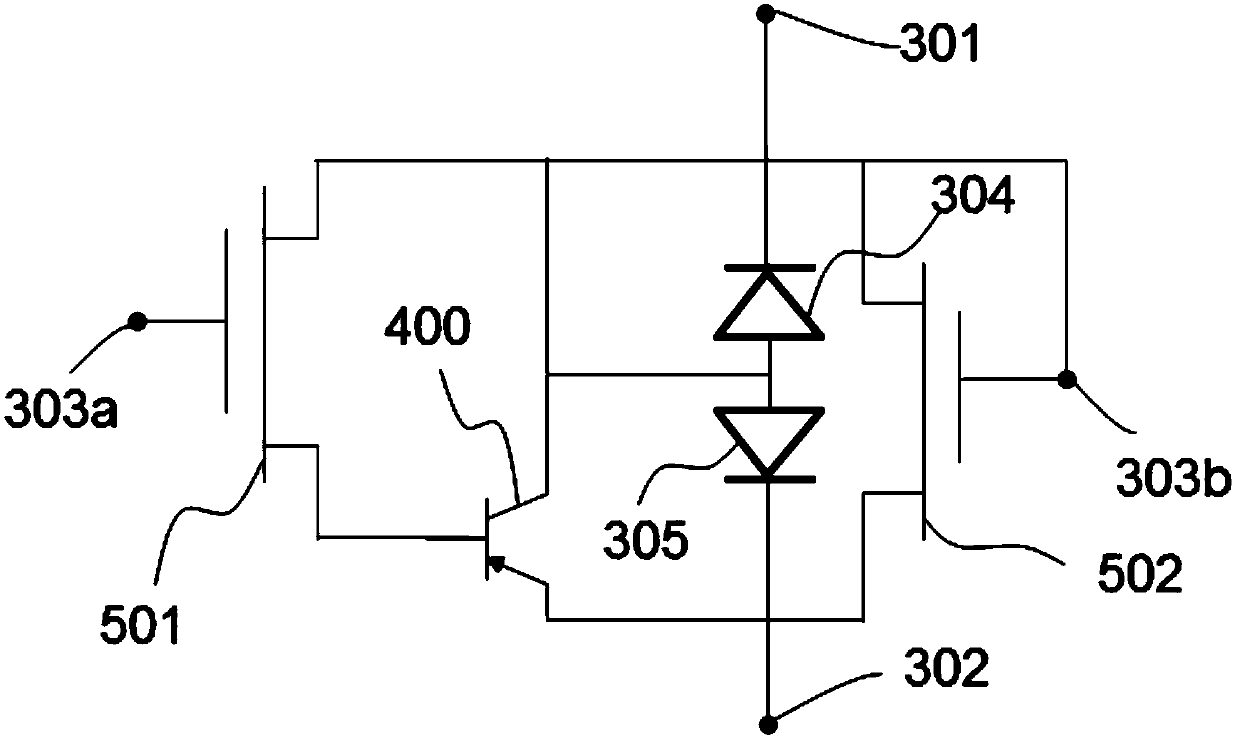

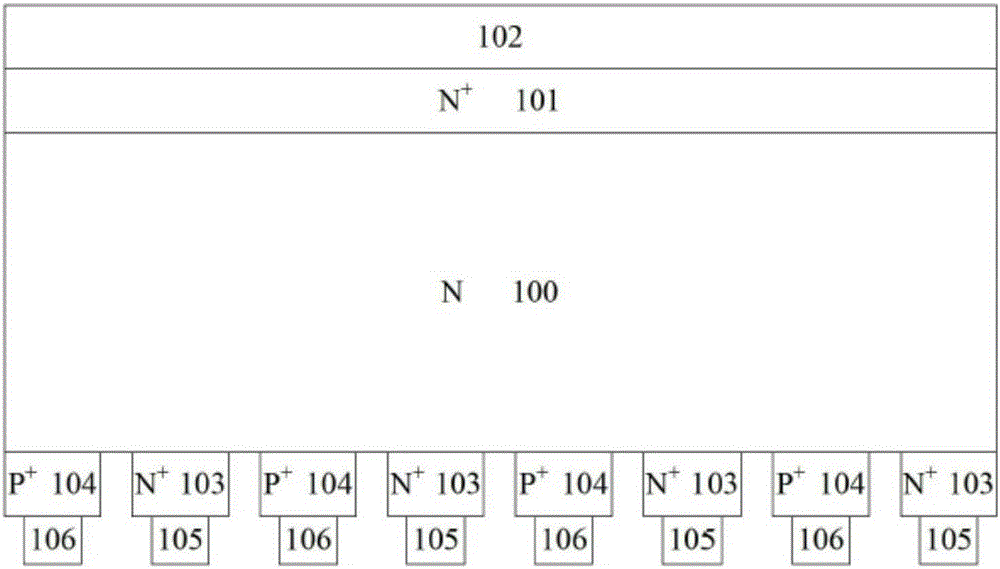

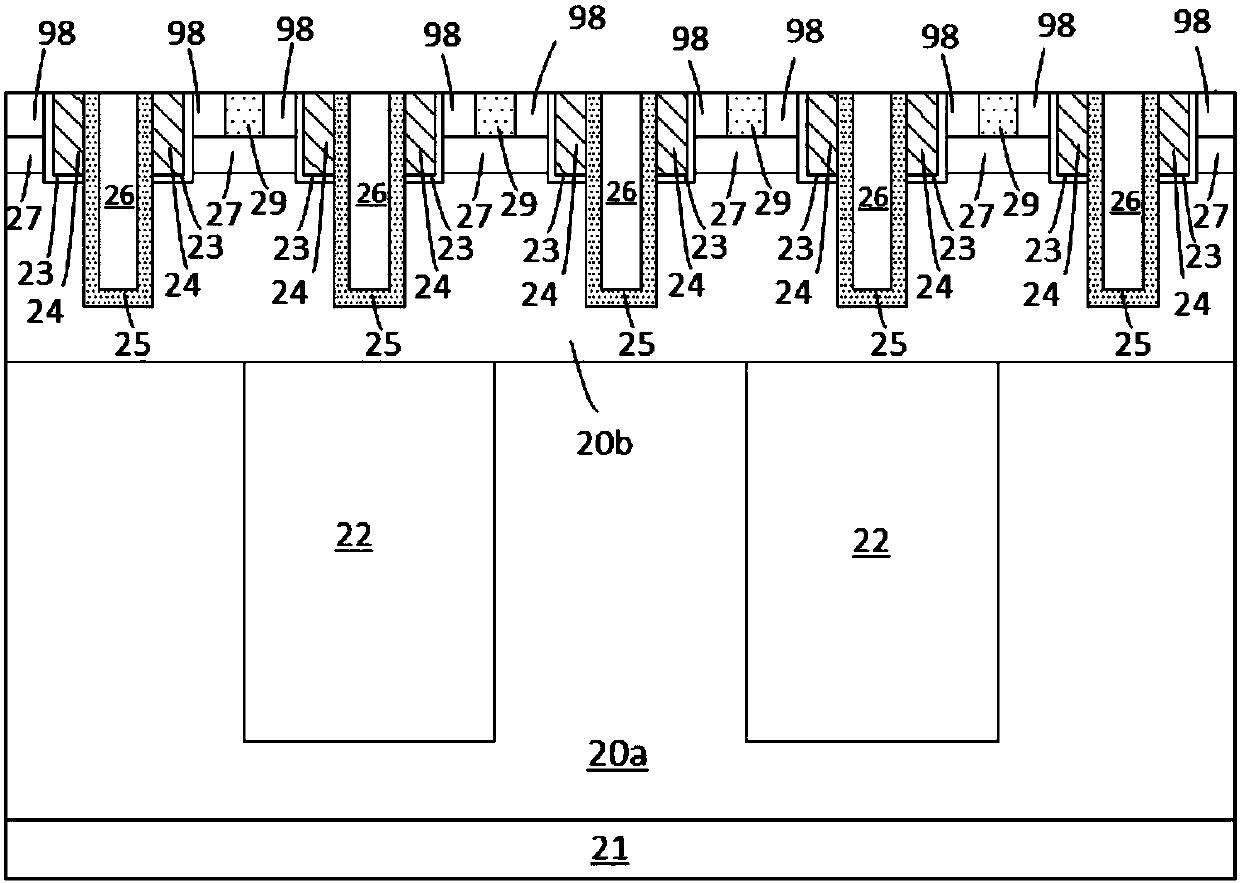

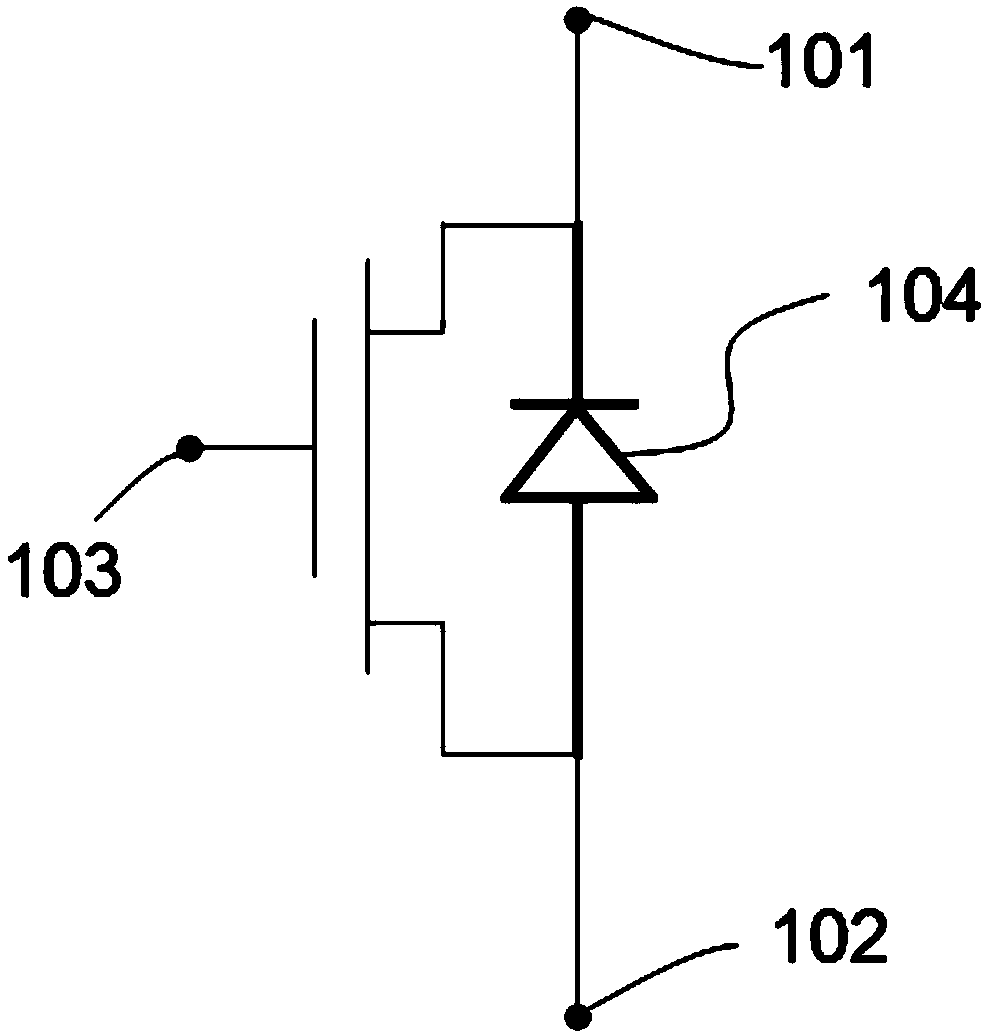

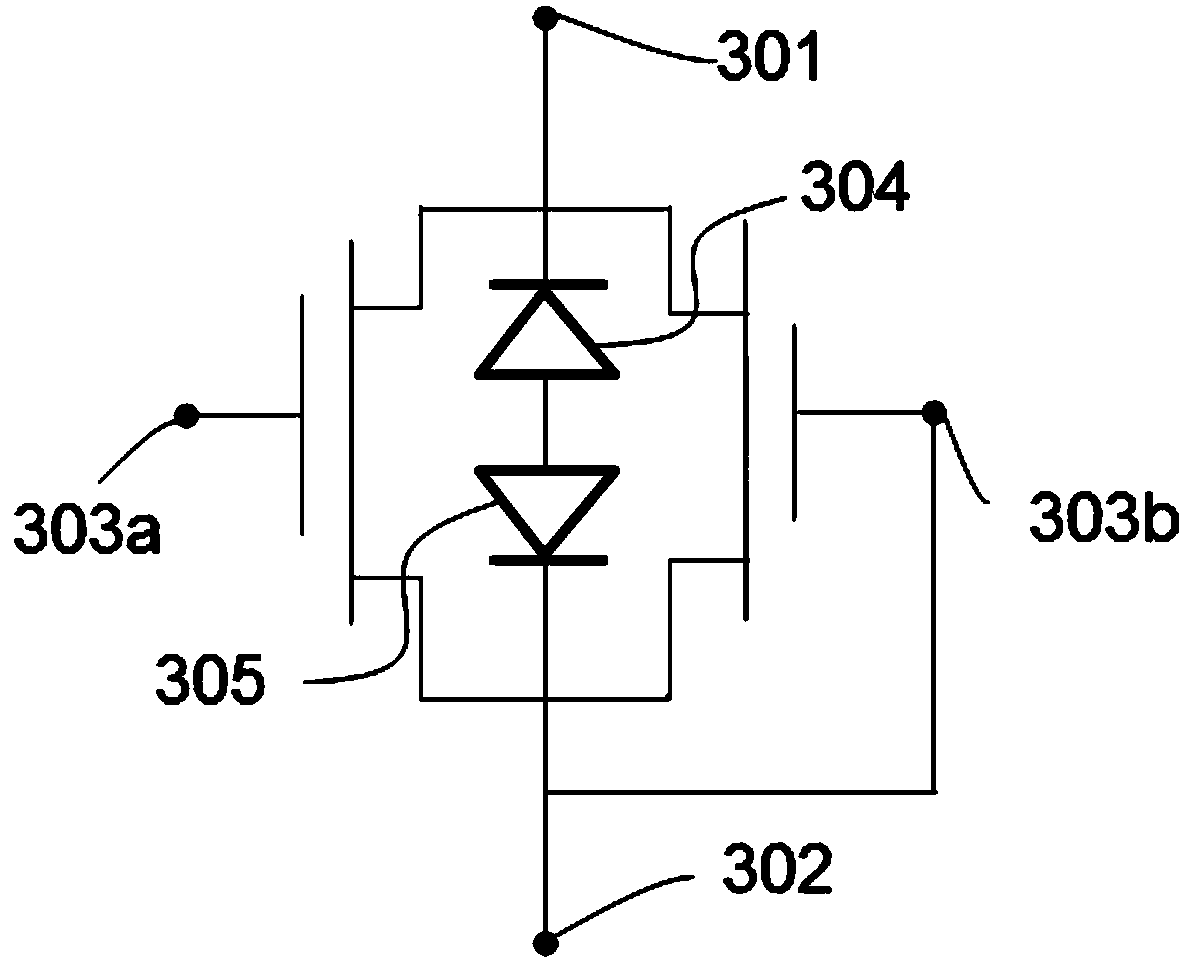

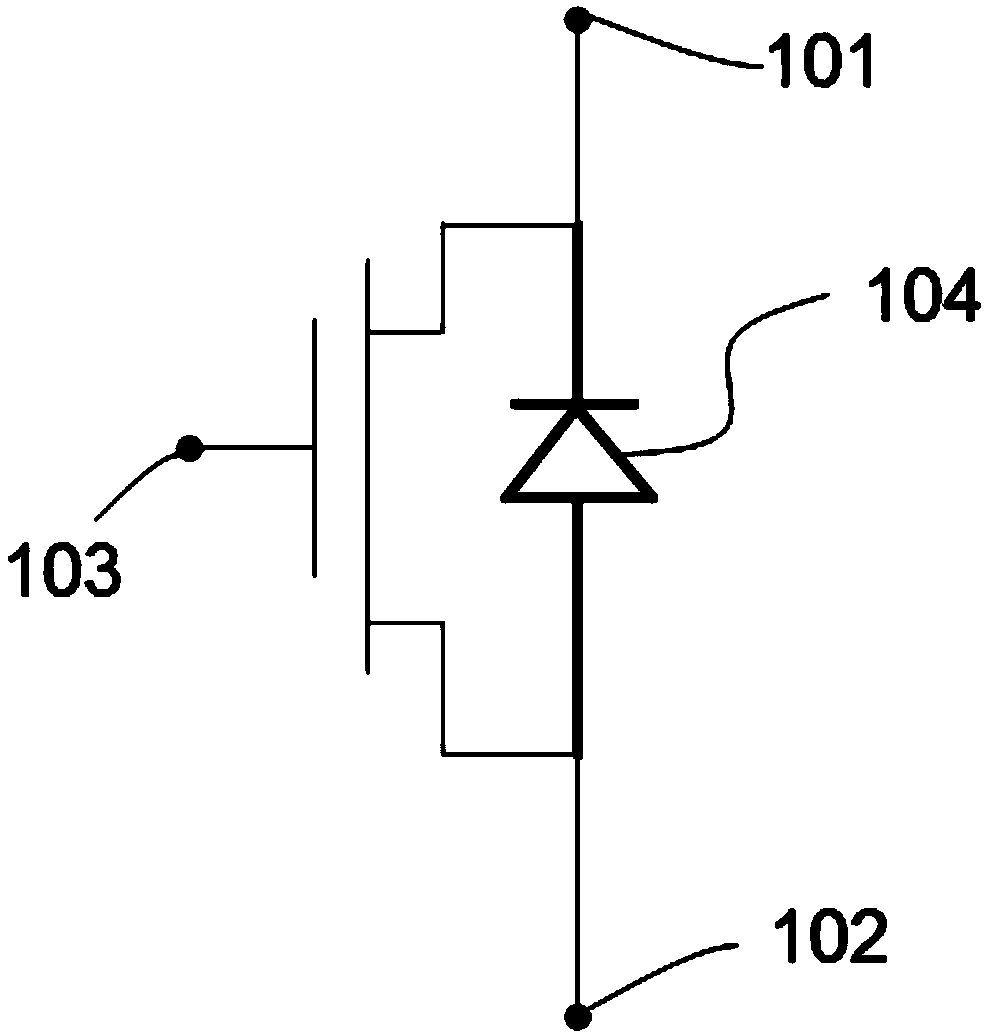

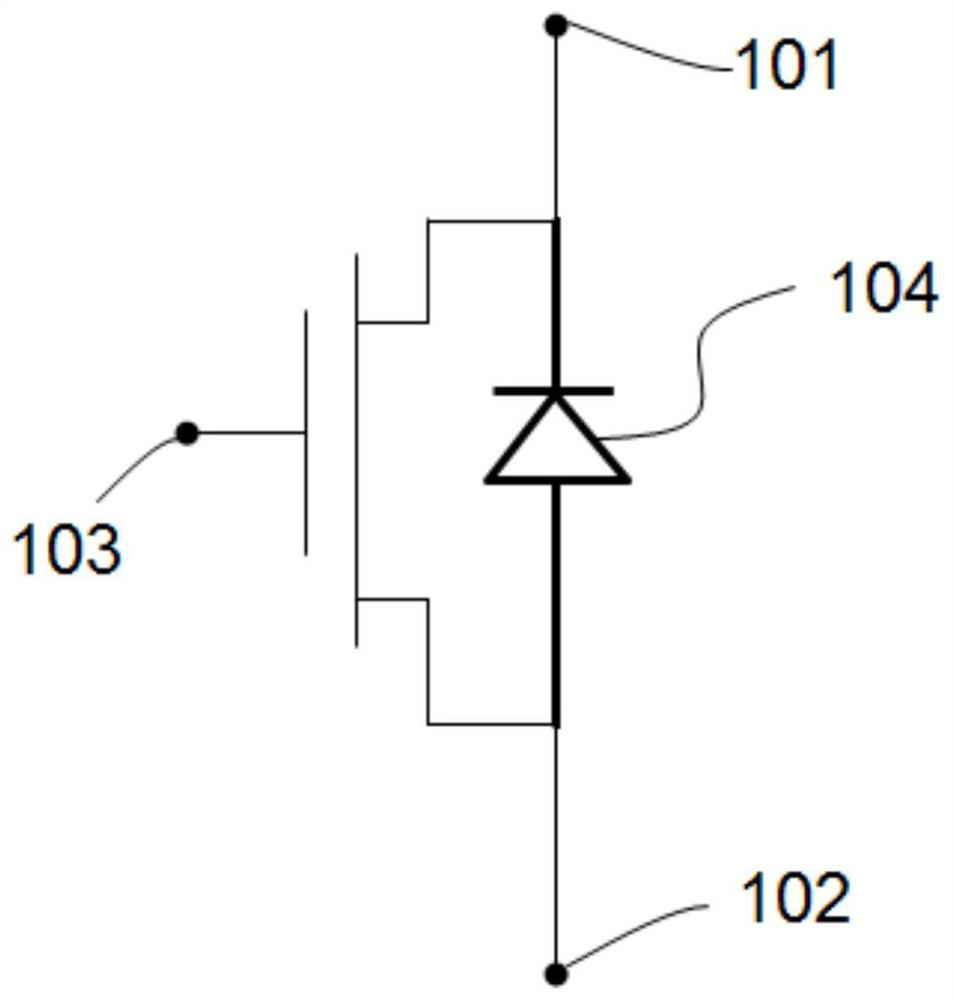

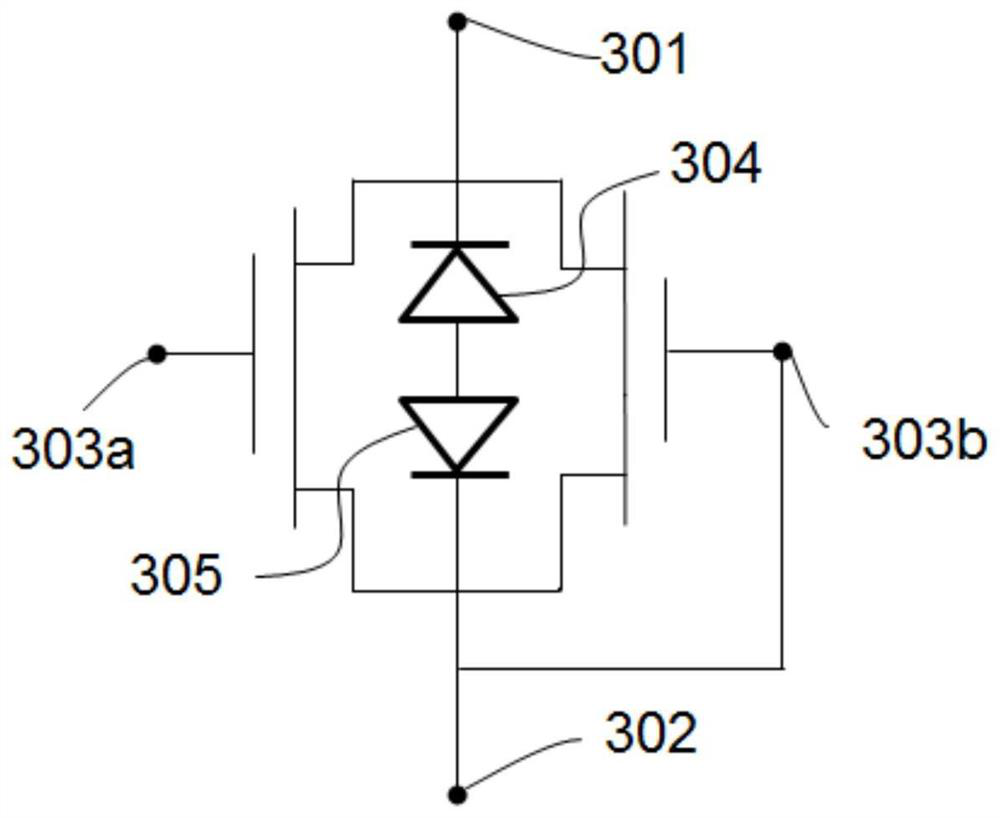

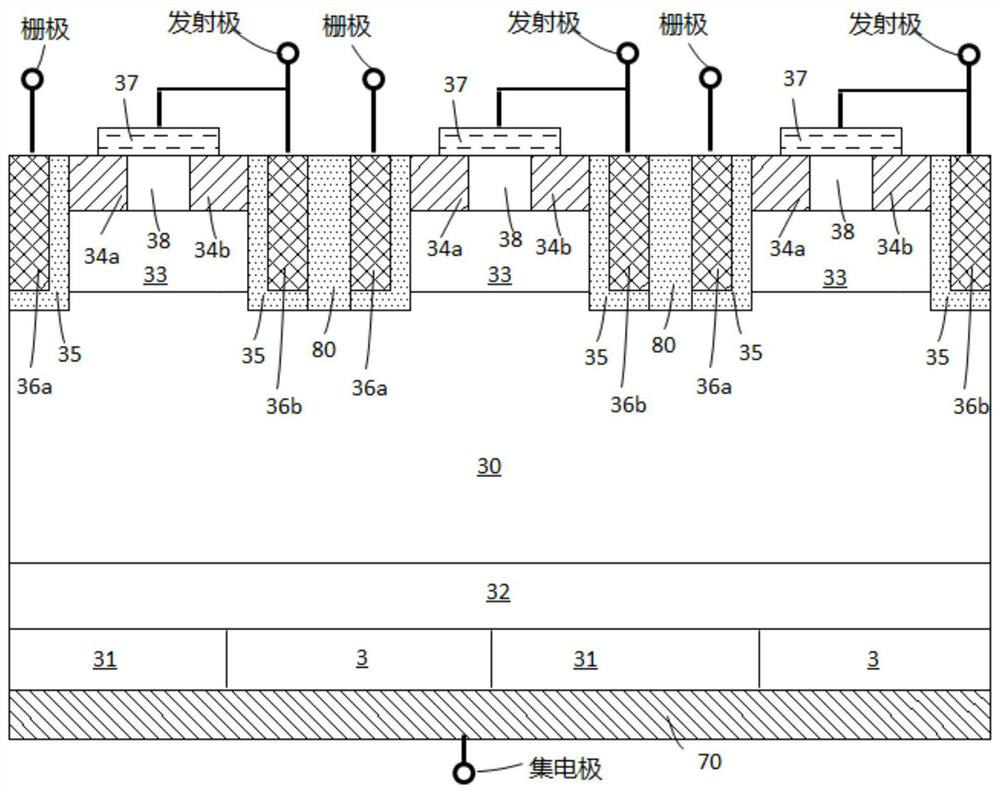

IGBT power device

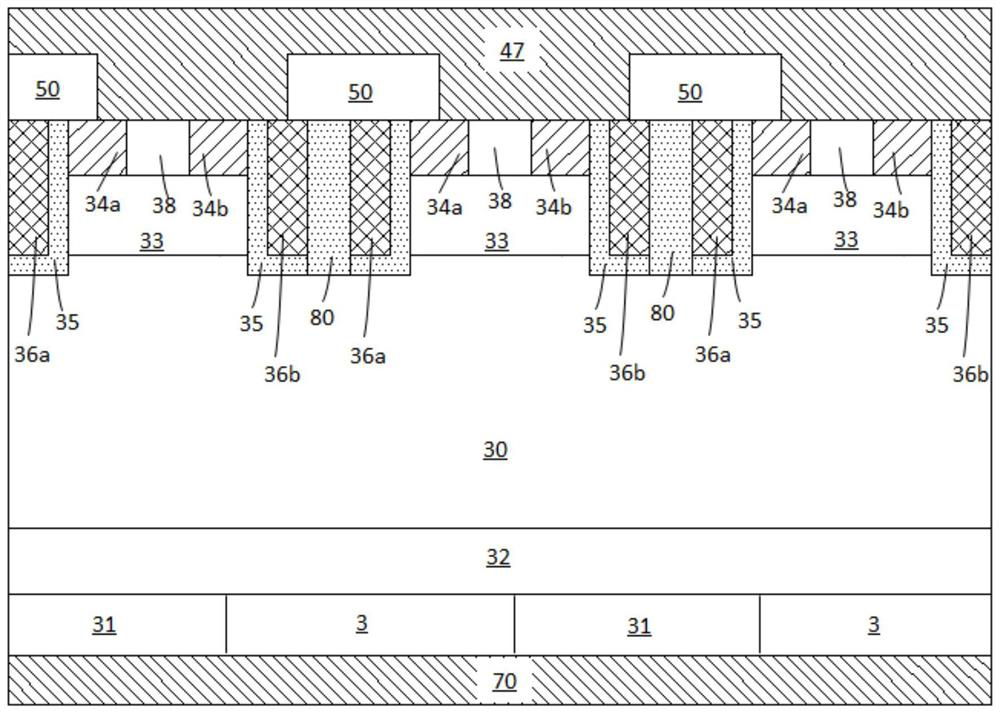

ActiveCN109755303AReduce reverse recovery chargeReduce reverse currentSemiconductor/solid-state device manufacturingSemiconductor devicesBody contactEngineering

An IGBT power device provided by an embodiment of the invention comprises a bipolar transistor, a first MOS transistor, a second MOS transistor, a body diode, and a body contact diode, wherein the anode of the body contact diode is connected to the anode of the body diode, and the cathode of the body contact diode is connected to the emitter of the bipolar transistor; the first gate of the first MOS transistor controls the first MOS transistor to be turned on or off through the gate voltage of the IGBT power device, the second gate of the second MOS transistor is connected to the emitter of the bipolar transistor, and the second gate of the second MOS transistor controls the second MOS transistor to be turned on or off through the emitter voltage of the IGBT power device.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

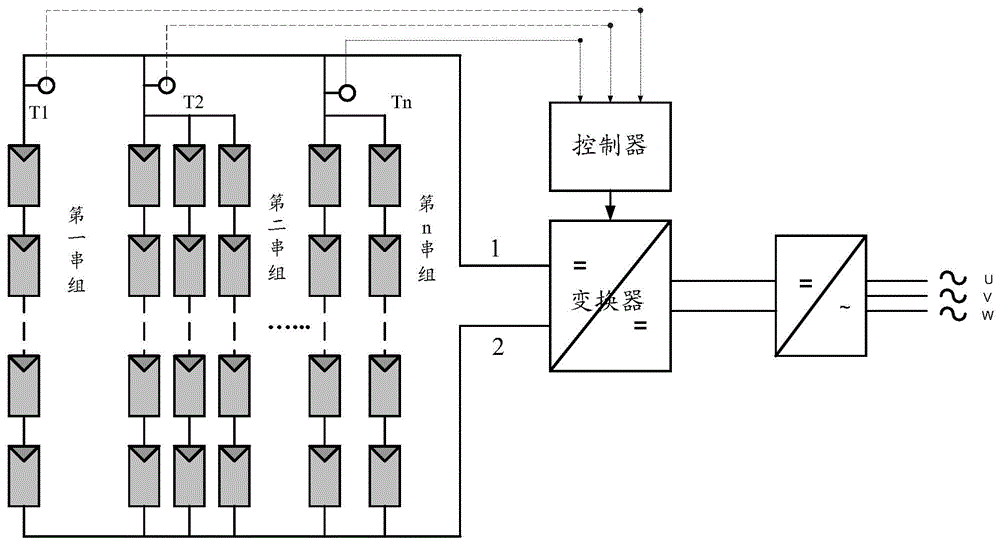

Photovoltaic system

ActiveCN105827179AReduce system voltageReduce reverse currentPhotovoltaic monitoringPV power plantsPower flowReverse current

The embodiment of the invention discloses a photovoltaic system comprising multiple photovoltaic cell strings, a converter, a controller, and buses. The multiple photovoltaic cell strings include at least one string group formed by connecting two or three photovoltaic cell strings in series and then connecting the photovoltaic cell strings to a current sensor. The at least one string group is connected to the converter through the buses after being connected in parallel. The controller is connected with the current sensor in each of the at least one string group. Each current sensor is used for detecting the total current of the corresponding string group and reporting to the controller whether there is reverse current in the corresponding string group. The controller is used for adjusting a control signal output to the converter when receiving a message indicating that there is reverse current in a target string group among the at least one string group reported by the current sensors. The converter is used for decreasing the system voltage between the buses according to the adjusted control signal so as to reduce the reverse current in the target string group. Photovoltaic cell protection is provided, and the equipment cost is reduced.

Owner:HUAWEI DIGITAL POWER TECH CO LTD

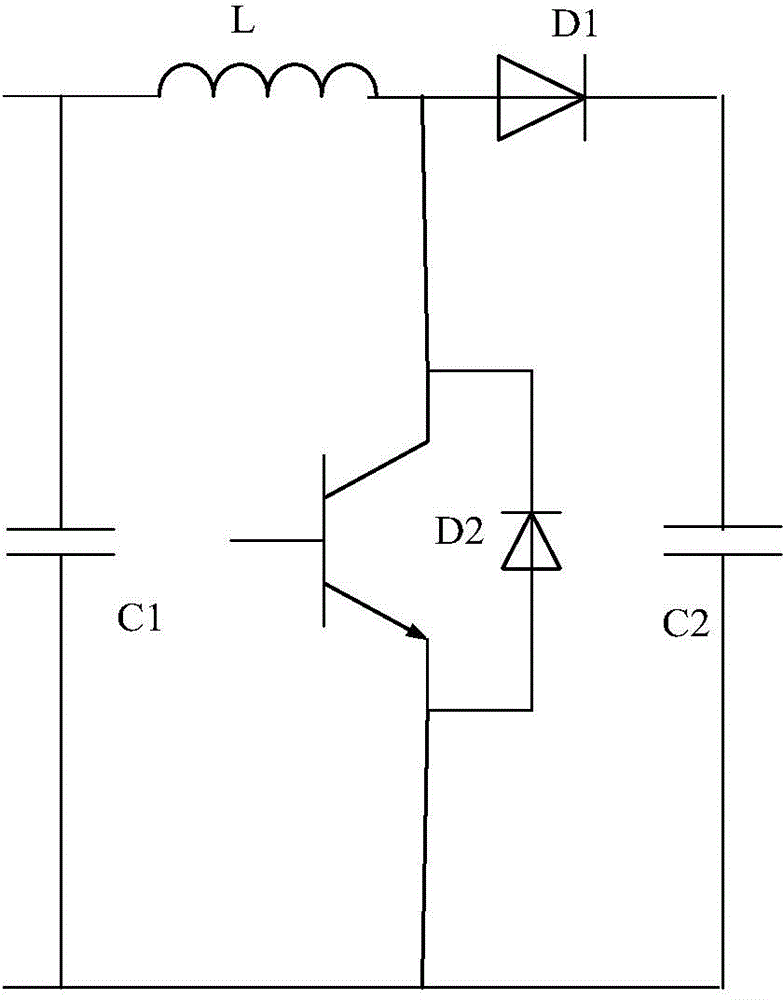

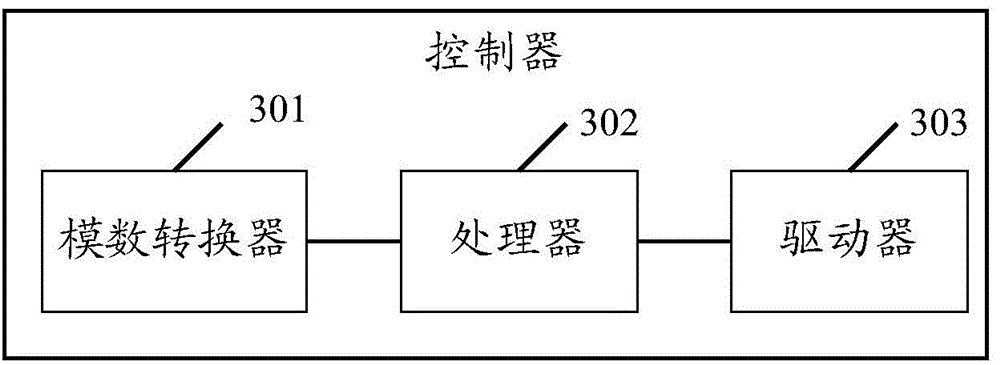

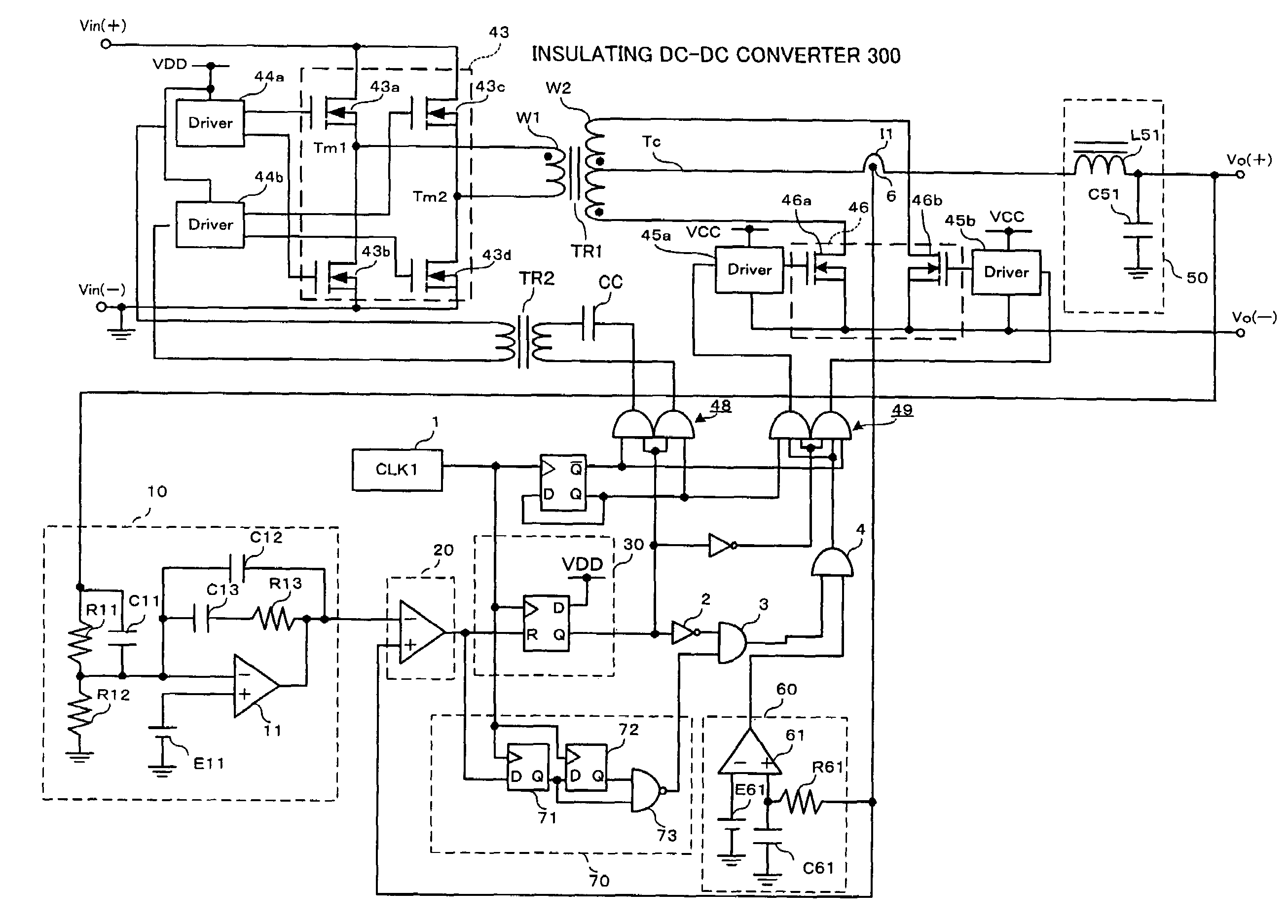

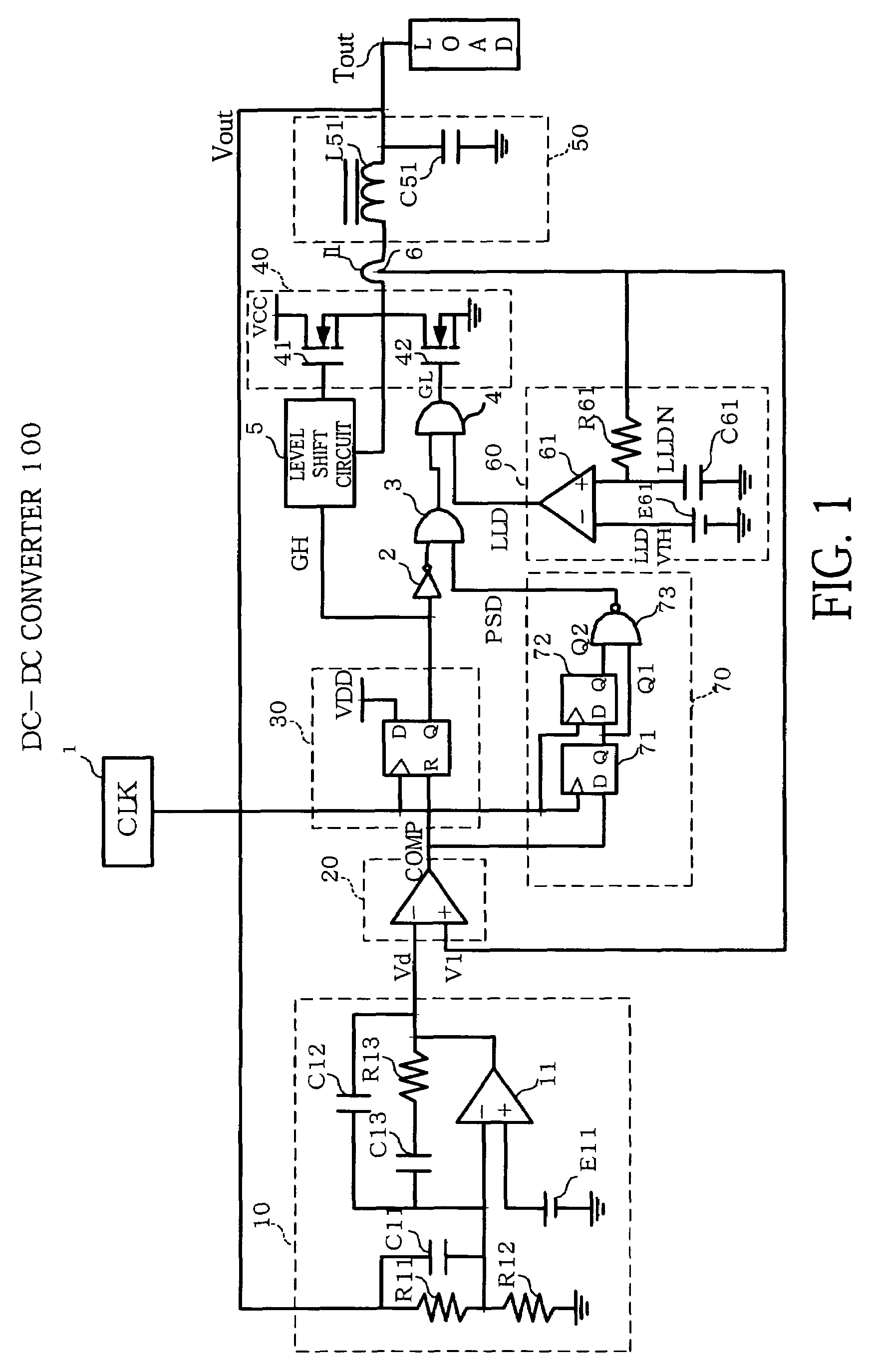

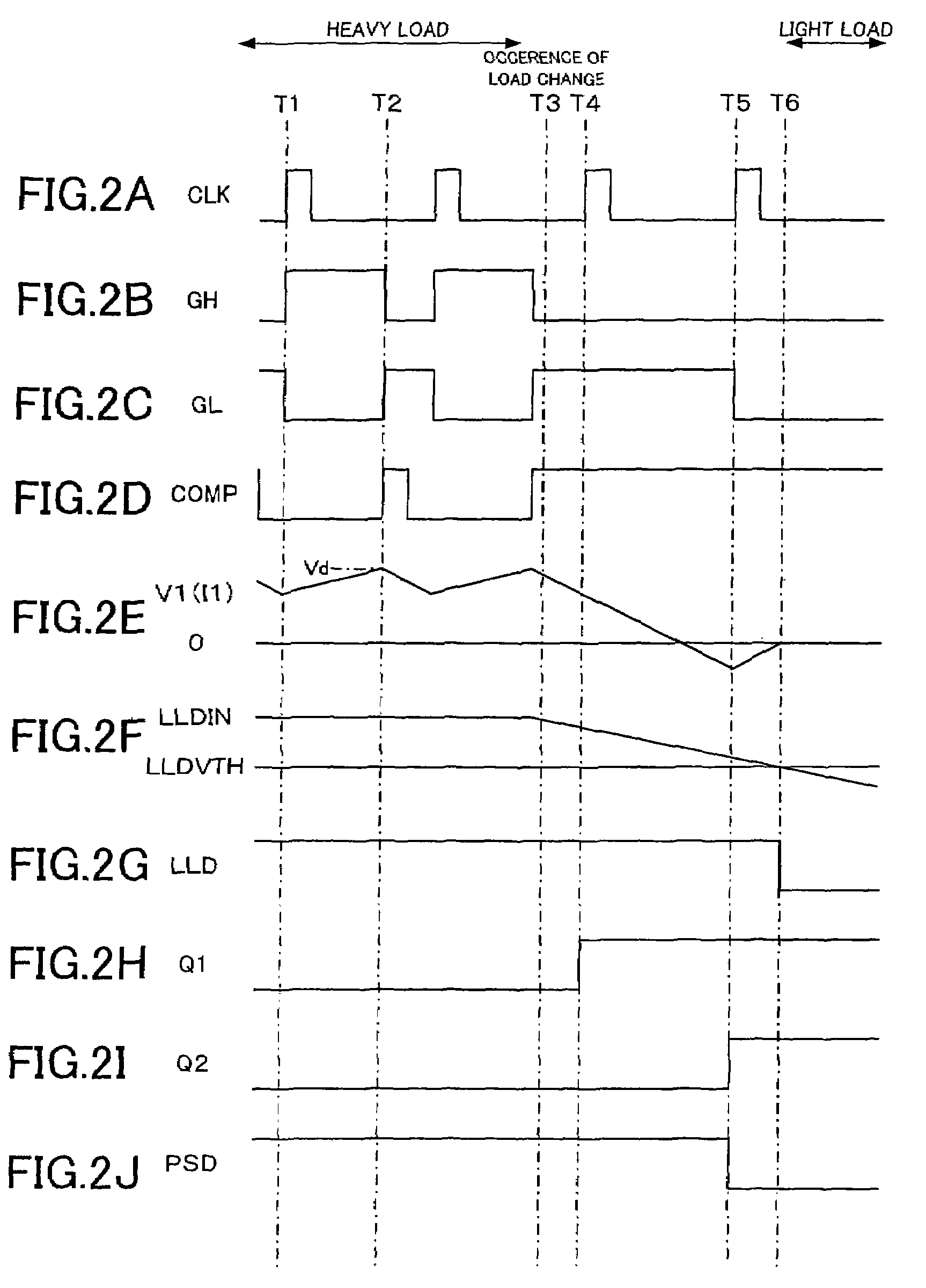

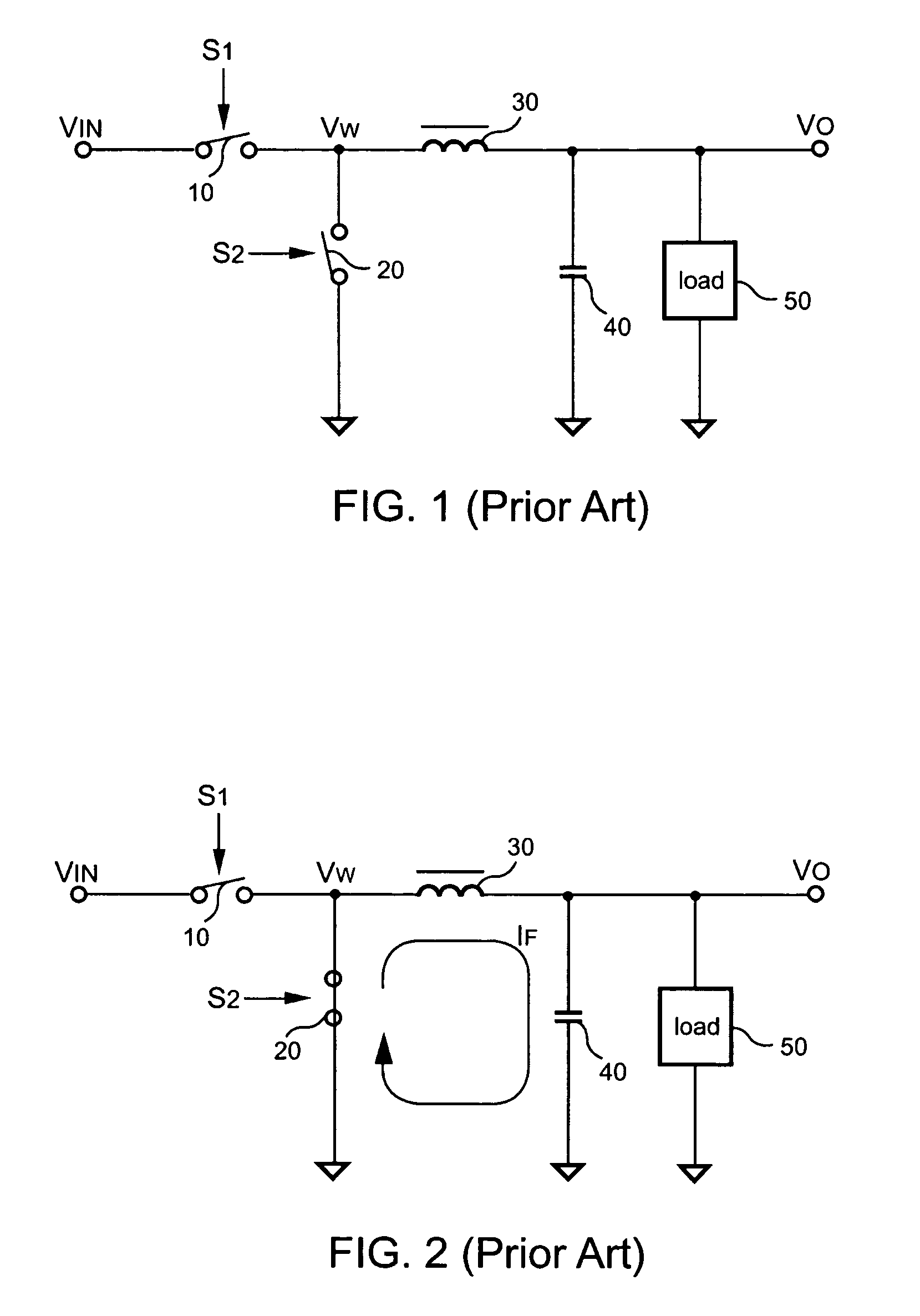

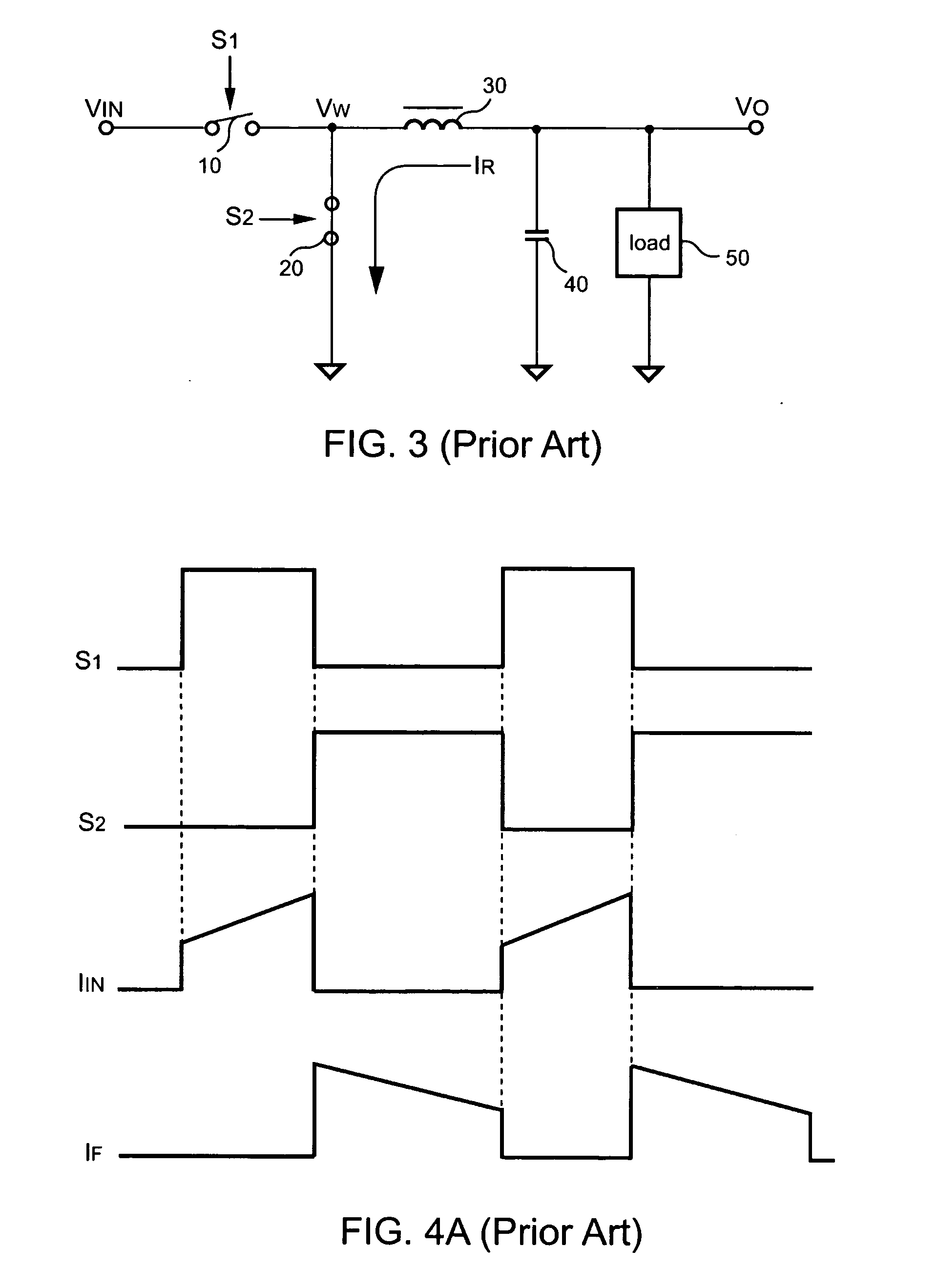

DC-DC converter and control method thereof

ActiveUS7660134B2Reduce reverse currentAdaptable to changeEfficient power electronics conversionEmergency protective circuit arrangementsDc dc converterInductor

A DC-DC converter has a switching circuit including switching elements at the high-side and at the low-side, an inductor connected to the output end of the switching circuit, a smoothing capacitor connected to the inductor, a switching control circuit for supplying a switching pulse to the switching elements, and a circuit. The circuit detects that a state that the switching element at the high side is switched off and the switching element at the low side is switched on is maintained for a predetermined period or longer. In this case, the circuit forcibly switches off the switching element at the low side.

Owner:TDK CORPARATION

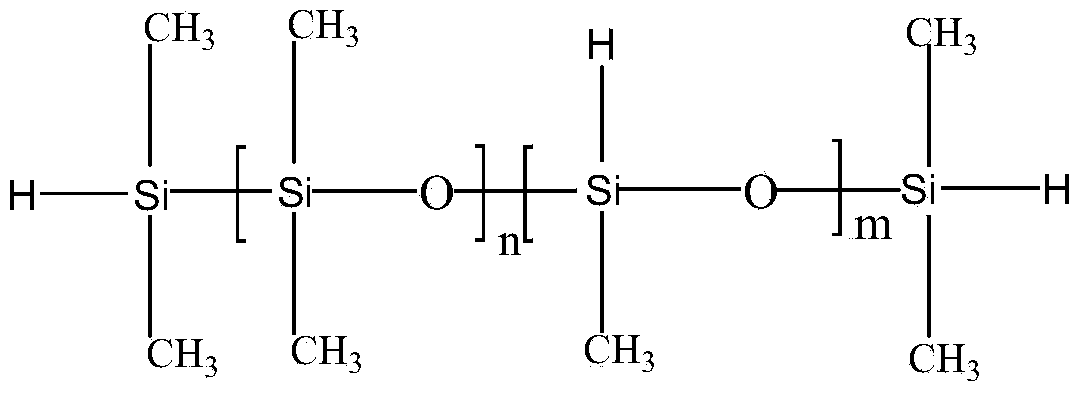

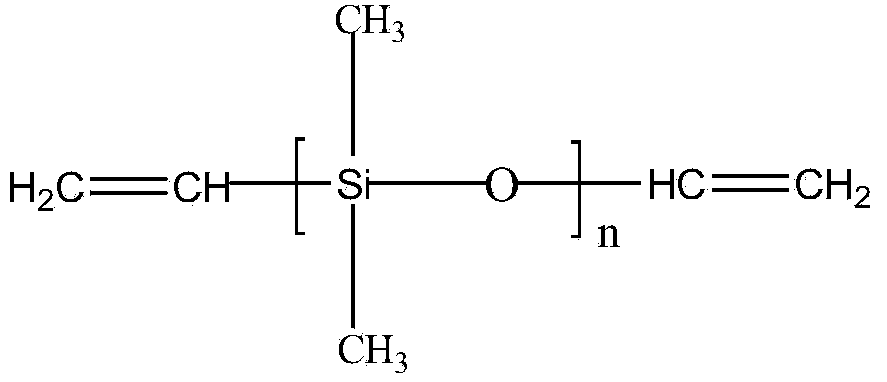

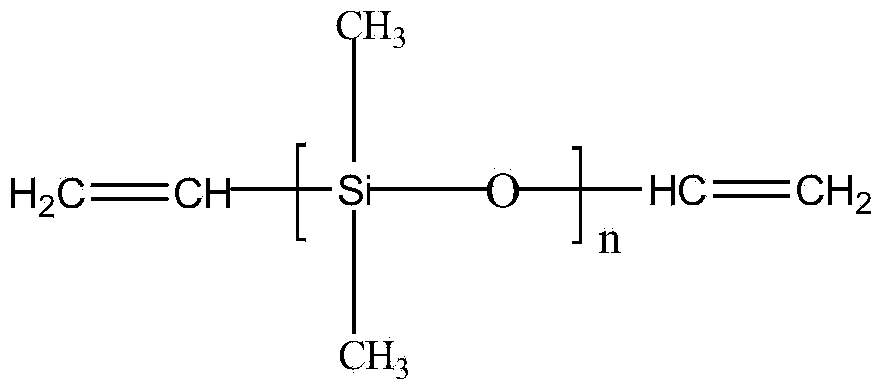

Addition silicone rubber compound for protecting diode chip

The invention discloses an addition silicone rubber compound for protecting a diode chip. The addition silicone rubber compound comprises the following raw materials in parts by weight: 100 parts of vinyl silicone oil, 20-300 parts of silicon dioxide, hydrogen-containing silicone oil of which the mass content of H is 0.5-1.5%, 5-100 parts of vinyl-containing MQ resin, 0.05-5 parts of stick relay promoter, 1,3-divinyl-1,1,3,3-tetramethyldisiloxane platinum complex, 0.01-10 parts of pigment, and 0.01-1 part of inhibitor, wherein the molar ratio of H-Si to vinyl contained in the silicon rubber compound is 0.6-2, and the dosage of the 1,3-divinyl-1,1,3,3-tetramethyldisiloxane platinum complex is 2-200PPm of the overall silicon rubber compound. The overall silicon rubber compound is stored at the temperature lower than 10 DEG C by adding the inhibitor while an organic silicon elastomer with a network structure is formed by addition reaction of vinyl silicone oil, vinyl-containing MQ resin and H-containing silicon oil at high temperature of 100-150 DEG C. The compound is applied to protection of the diode chip, and has the effect that countercurrent of the diode at normal temperature and high temperature is low.

Owner:MIANYANG WELLS ELECTRONICS MATERIAIS

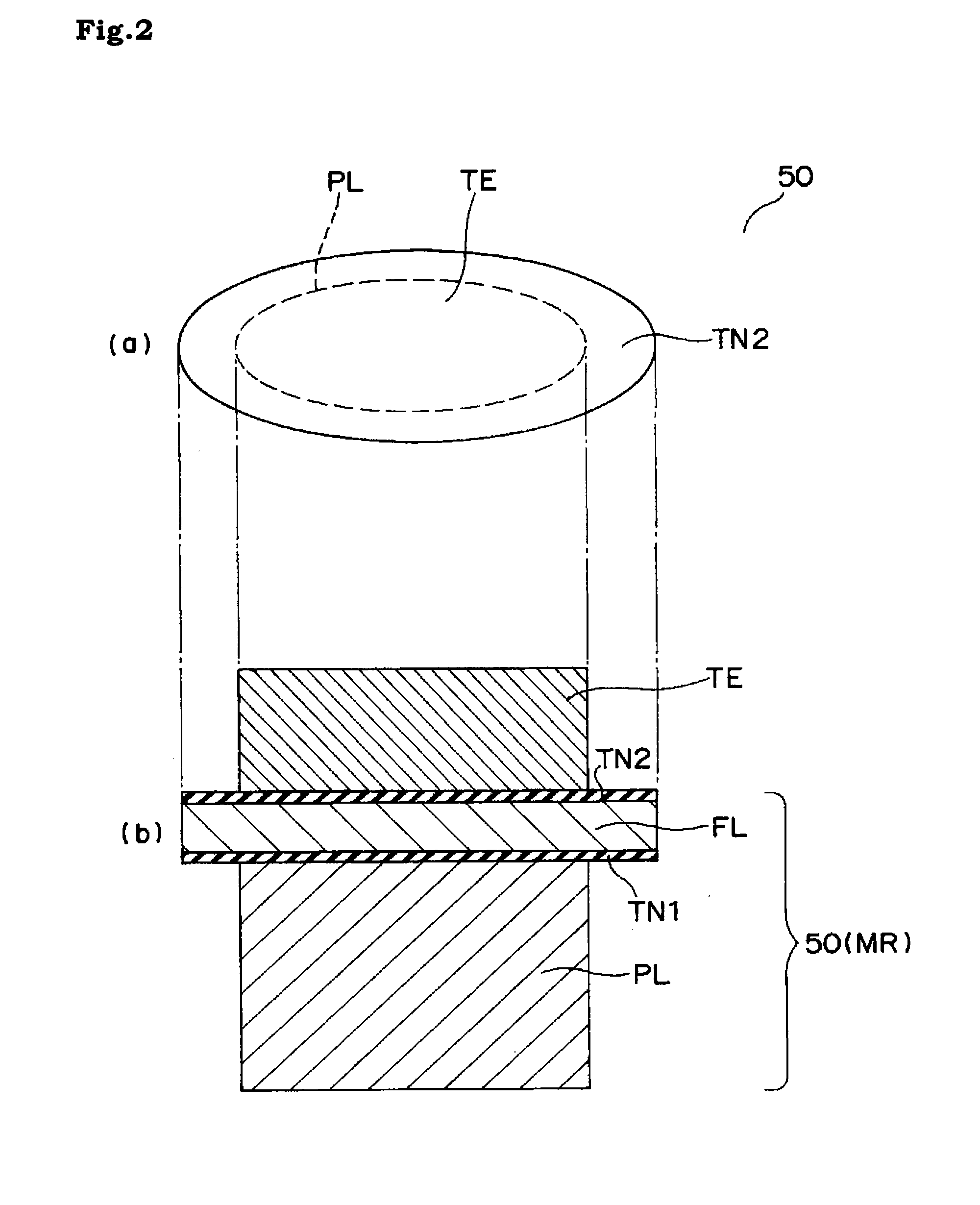

Magnetic memory element and magnetic memory device

ActiveUS20090261435A1Excellent magnetic propertiesReduce reverse currentMagnetic-field-controlled resistorsSolid-state devicesMagnetizationMagnetic memory

A magnetic memory element having a layer structure containing a fixing layer (pinned layer: PL) having a magnetization direction fixed unidirectionally, a nonmagnetic dielectric layer (TN1) in contact with the fixing layer (PL), and a memory layer (free layer: FL) having a first surface in contact with the nonmagnetic dielectric layer (TN1) and a second surface on the opposite to the first surface, the magnetization direction of the memory layer (FL) having a reversible magnetization direction in response to the current through the layer structure. The entire surface of the first surface of the memory layer (FL) is covered with the nonmagnetic dielectric layer (TN1) and in the joint surface of the nonmagnetic dielectric layer (TN1) and the fixing layer (PL), the first surface of the nonmagnetic dielectric layer (TN1) is exposed in a manner of surrounding the joint surface.

Owner:RENESAS ELECTRONICS CORP

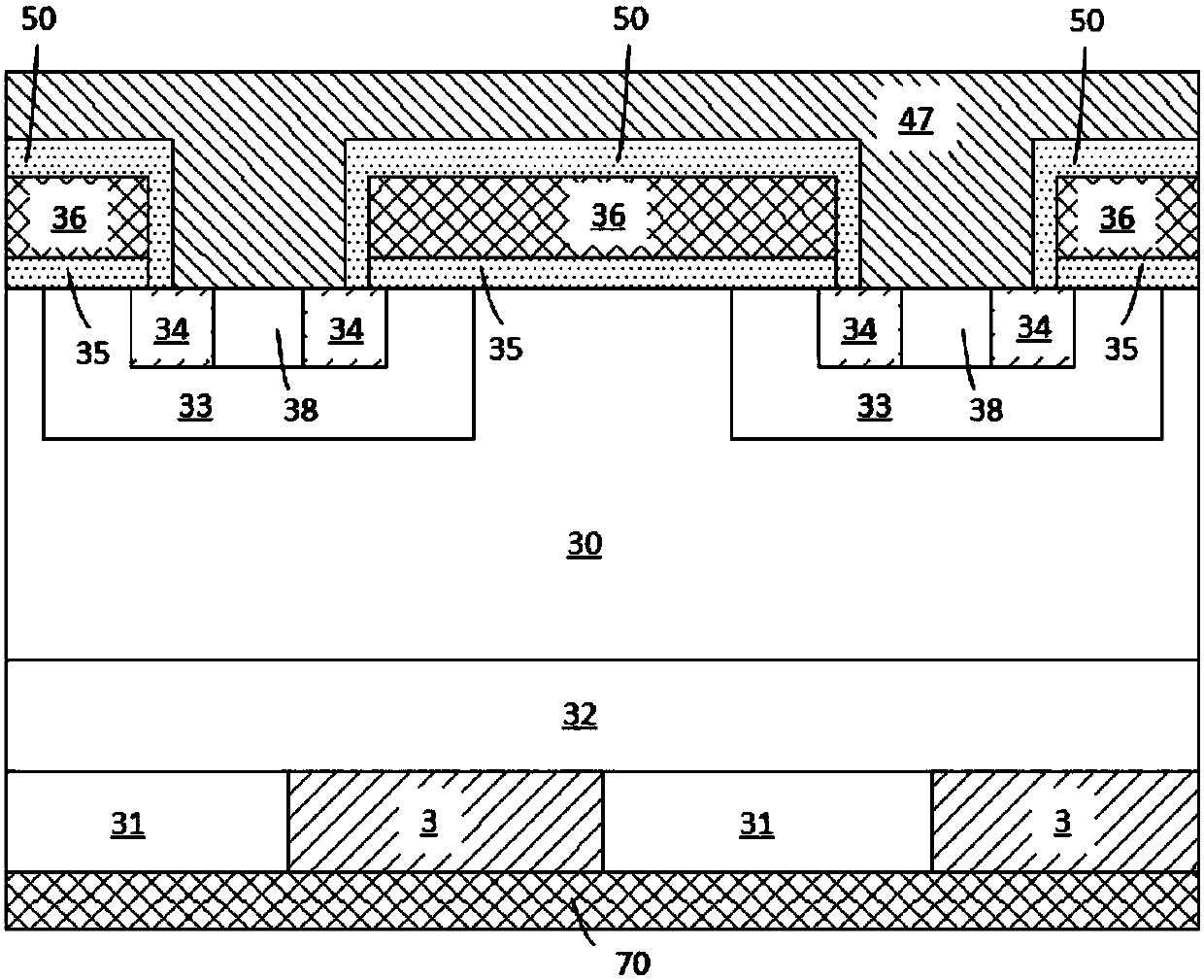

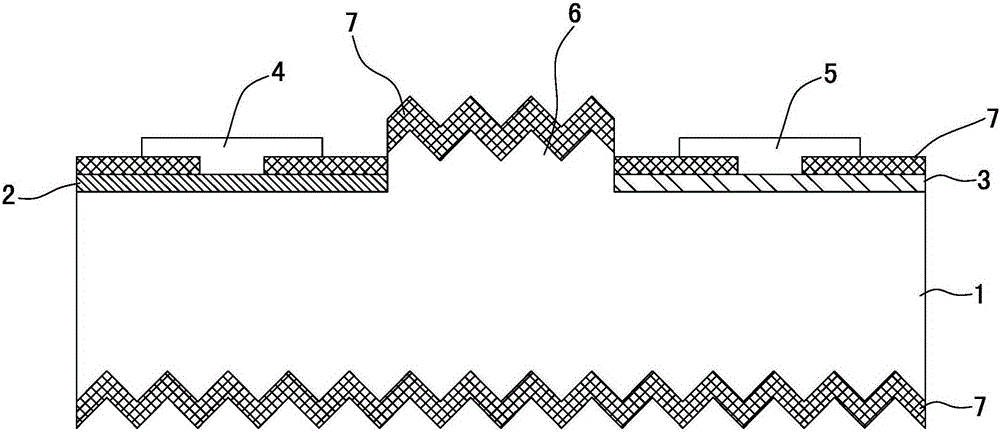

Back-contact solar cell and preparation method

ActiveCN105185849AImprove stabilitySolve the problem of printing biasFinal product manufacturePhotovoltaic energy generationSlurrySolar cell

The invention provides a back-contact solar cell and a preparation method. The back-contact solar cell comprises a silicon wafer substrate. The back side of the silicon wafer substrate is provided with an N+ first conductive area and a P+ second conductive area with an interval. The N+ first conductive area is provided with a first electrode, and the P+ second conductive area is provided with a second electrode. An isolation area is arranged between the N+ first conductive area and the P+ second conductive area. The top surfaces of the first electrode and the second electrode are on the same horizontal plane, and the top surface of the isolation area is higher than that of the first electrode and the second electrode. According to the back-contact solar cell, through arranging the isolation area between the N+ first conductive area and the P+ second conductive area, the electrodes are lower than the isolation area, the problem of electrode offset printing is solved well, the problem of positive electrode and negative electrode short circuit caused by metal slurry offset is solved, and the stability of the cell is improved greatly.

Owner:CSI CELLS CO LTD +1

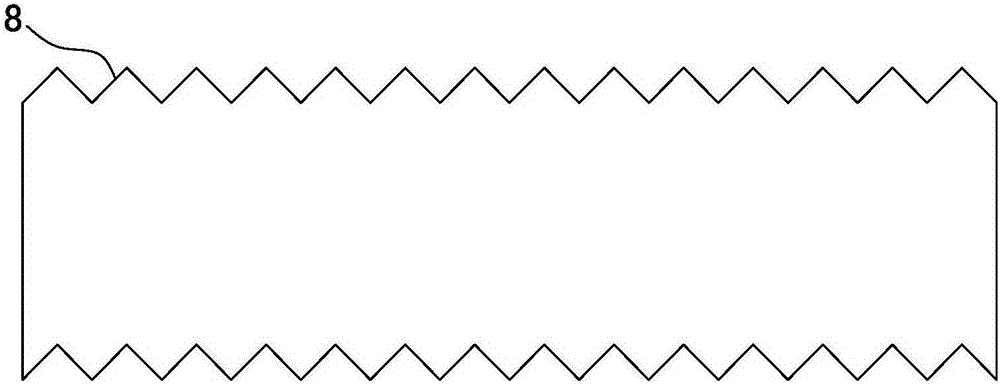

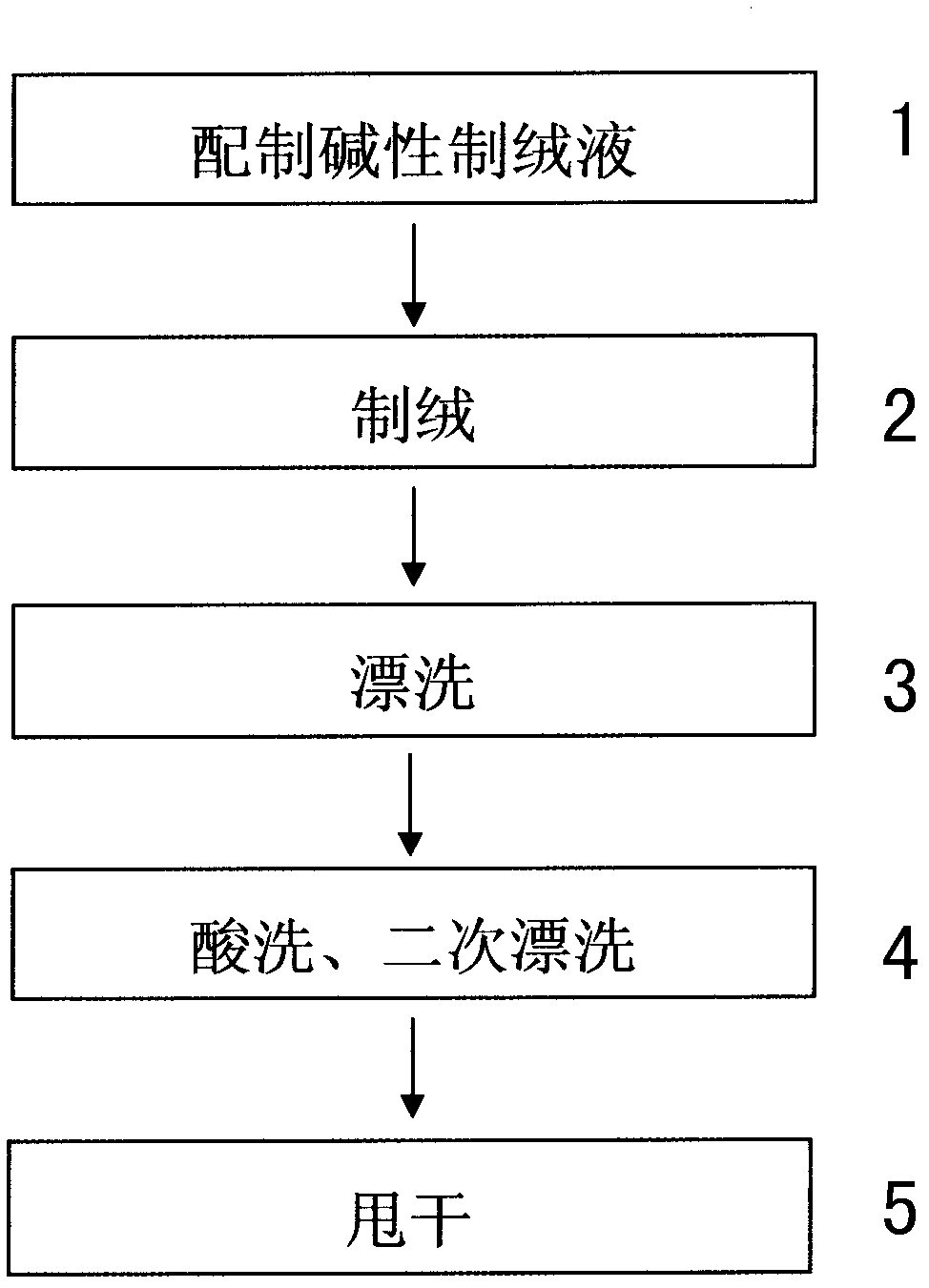

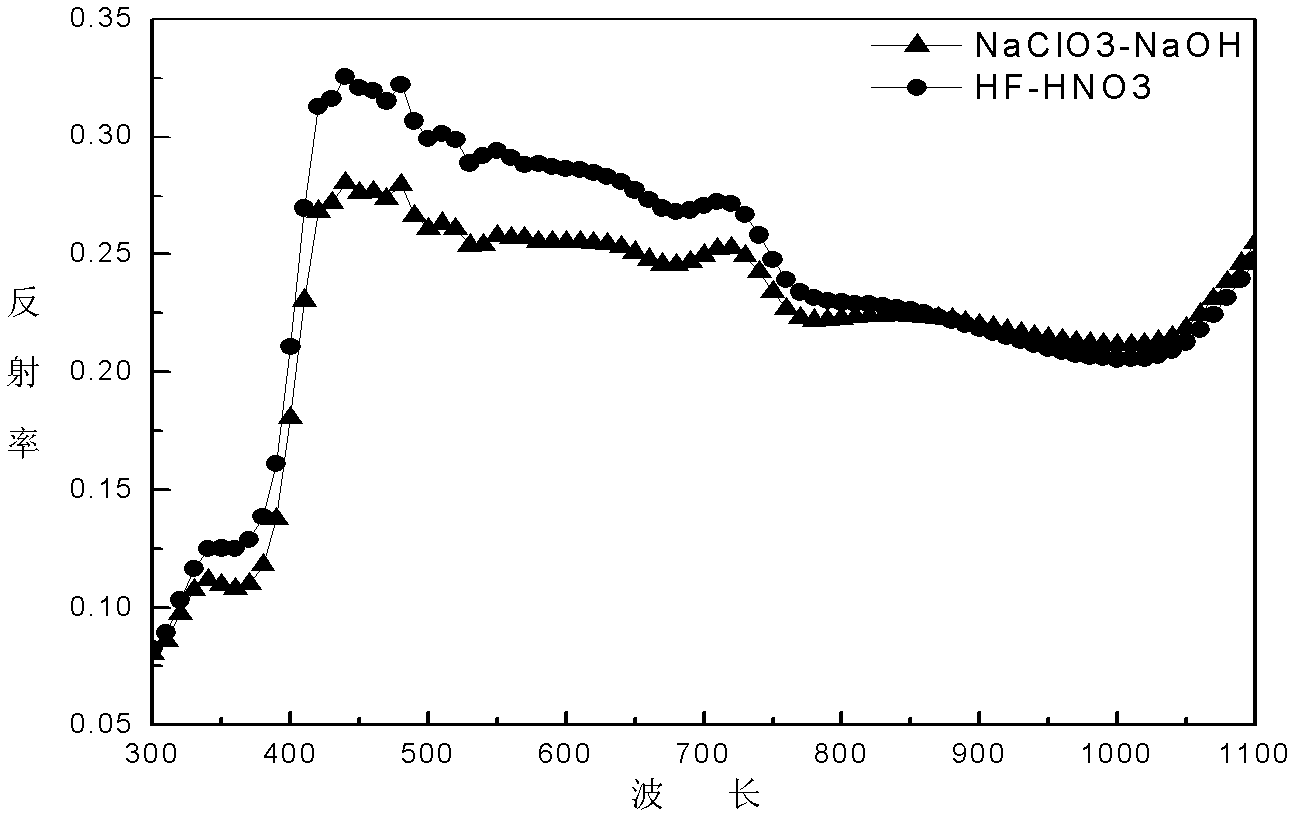

Polysilicon alkaline wool making method

InactiveCN102437044AReduce manufacturing costImprove trapping effectSemiconductor/solid-state device manufacturingPolycrystalline siliconPulp and paper industry

The invention relates to a polysilicon alkaline wool making method, which comprises the following steps that: 1) preparing alkaline wool making solution; 2) heating the well-prepared wool making solution, and soaking one piece of polysilicon into the wool making solution to make wool; 3) rinsing the wool-made polysilicon piece; 4) cleaning the rinsed polysilicon piece with acid, and performing the secondary rinsing; and 5) drying the polysilicon piece after the secondary rinsing to complete the polysilicon alkaline wool making procedures.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

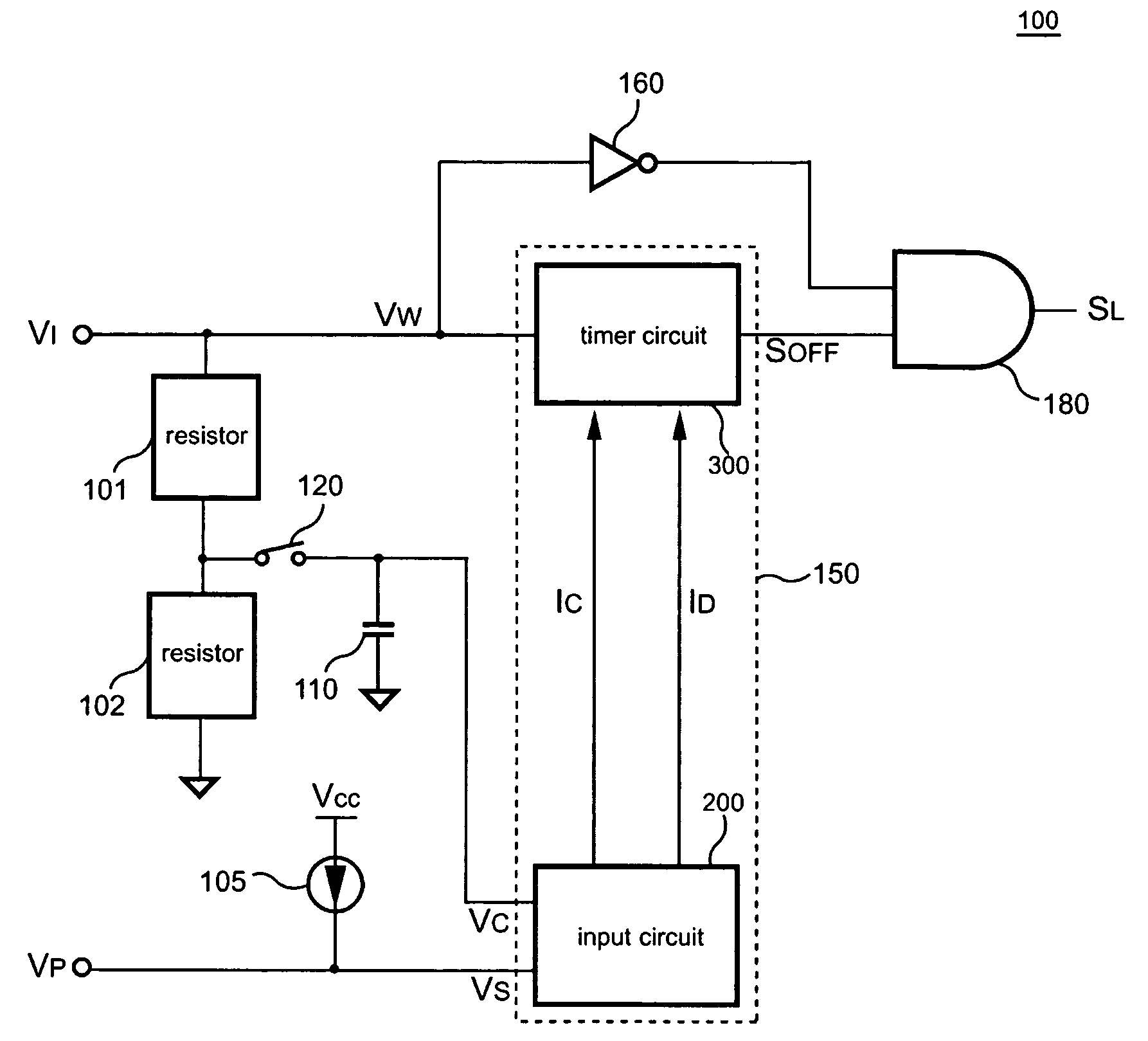

Control circuit to reduce reverse current of synchronous rectifier

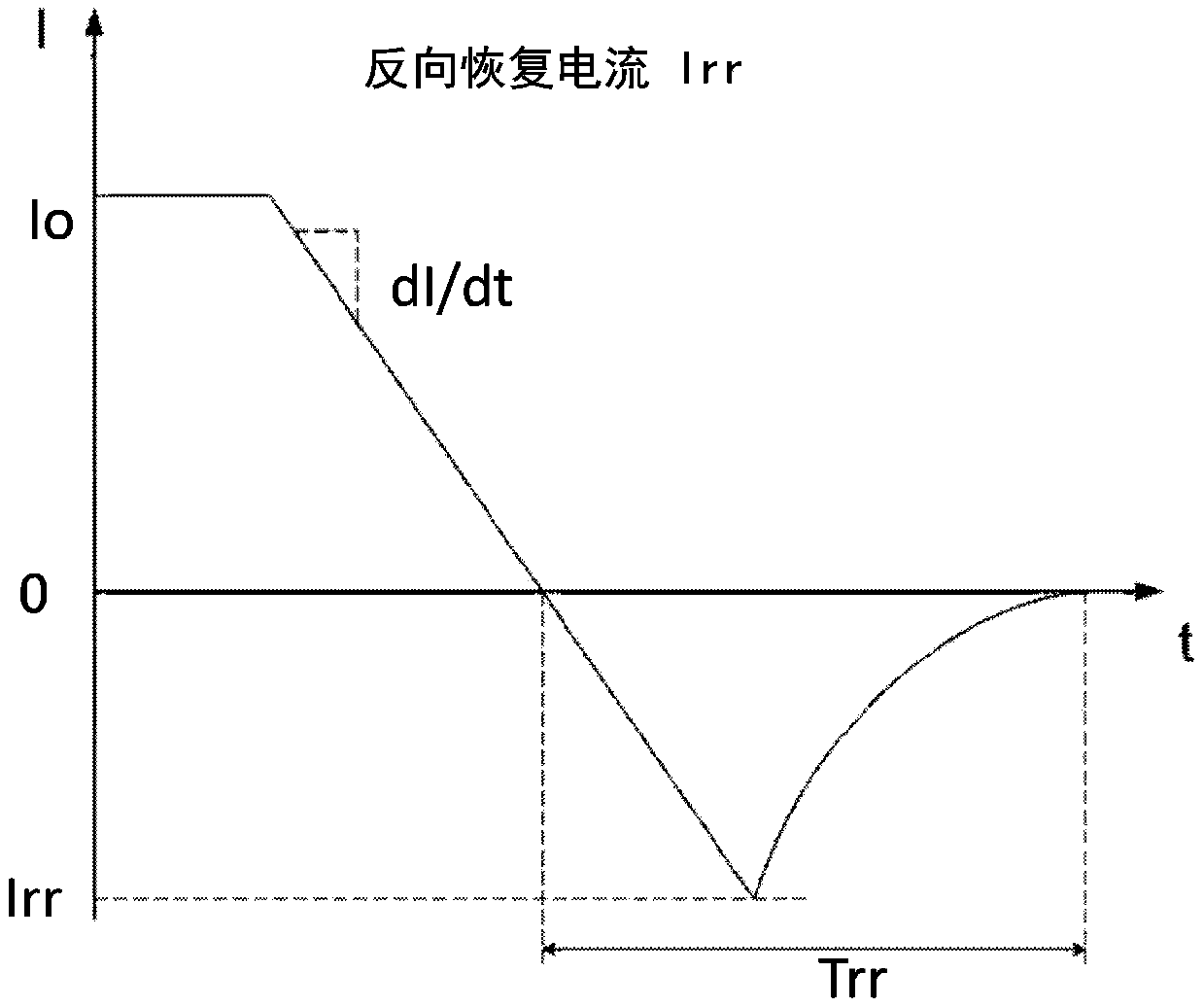

ActiveUS20070285070A1Reduce reverse currentShortening timing signalEfficient power electronics conversionDc-dc conversionReverse currentInductor

The present invention provides a control circuit to avoid a reverse current of a synchronous rectifier. A switching signal is applied to charge an inductor of a power converter. A predication circuit generates a timing signal in response to the switching signal. The timing signal is used to turn off the synchronous rectifier for preventing the reverse current occurred in light load and no load conditions.

Owner:SEMICON COMPONENTS IND LLC

Storage element and storage device

ActiveCN102800804AEasy to operateReduce consumptionNanomagnetismMagnetic-field-controlled resistorsSpinsNon magnetic

A storage element includes: a storage layer which retains information by a magnetization state of a magnetic substance; a magnetization pinned layer having magnetization which is used as the basis of the information stored in the storage layer; and an interlayer of a non-magnetic substance provided between the storage layer and the magnetization pinned layer. The storage element is configured to store information by reversing magnetization of the storage layer using spin torque magnetization reversal generated by a current passing in a laminate direction of a layer structure including the storage layer, the interlayer, and the magnetization pinned layer, and when the saturation magnetization of the storage layer and the thickness thereof are represented by Ms (emu / cc) and t (nm), respectively, (1489 / Ms)-0.593<t<(6820 / Ms)-1.55 holds.

Owner:SONY CORP

A transceiver unit for transmitting data via a differential bus

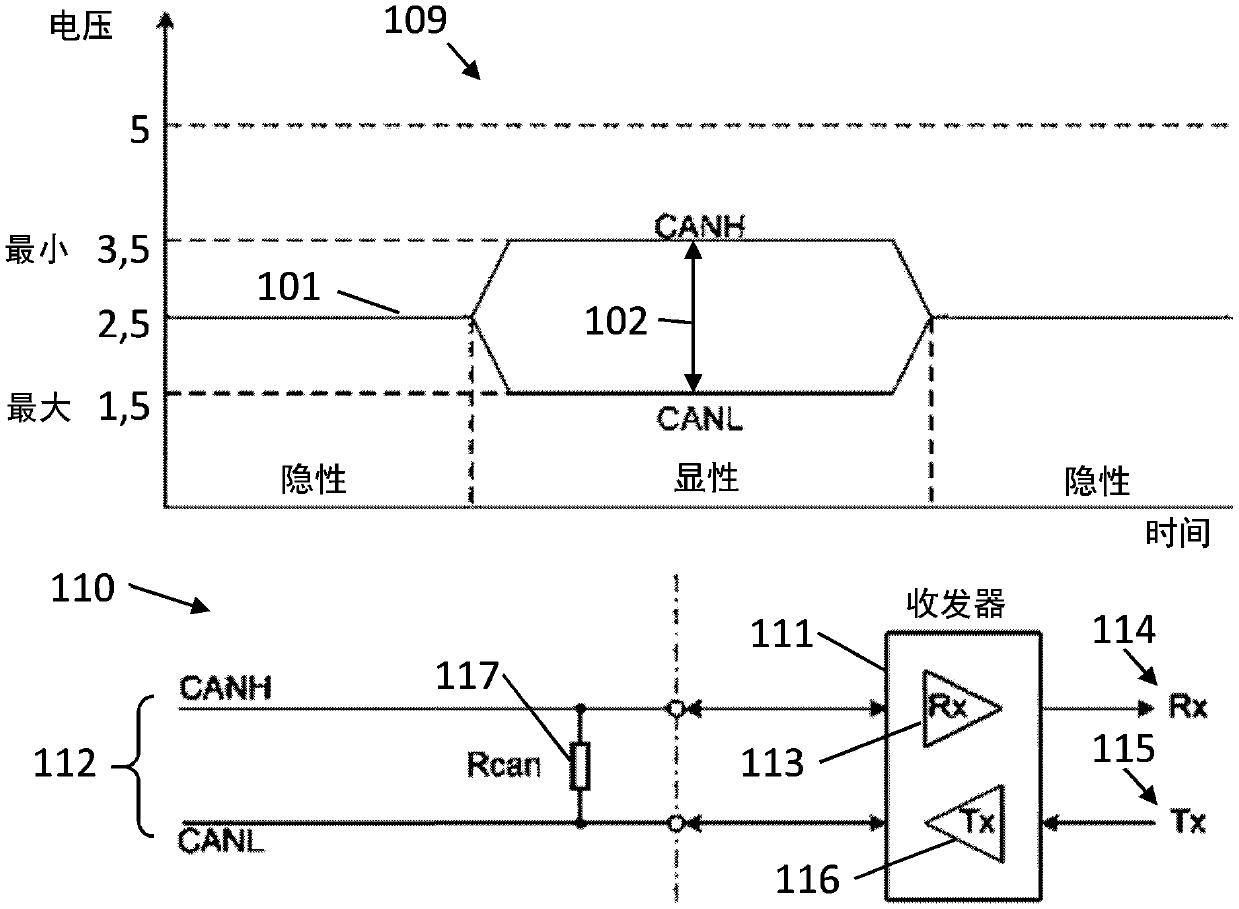

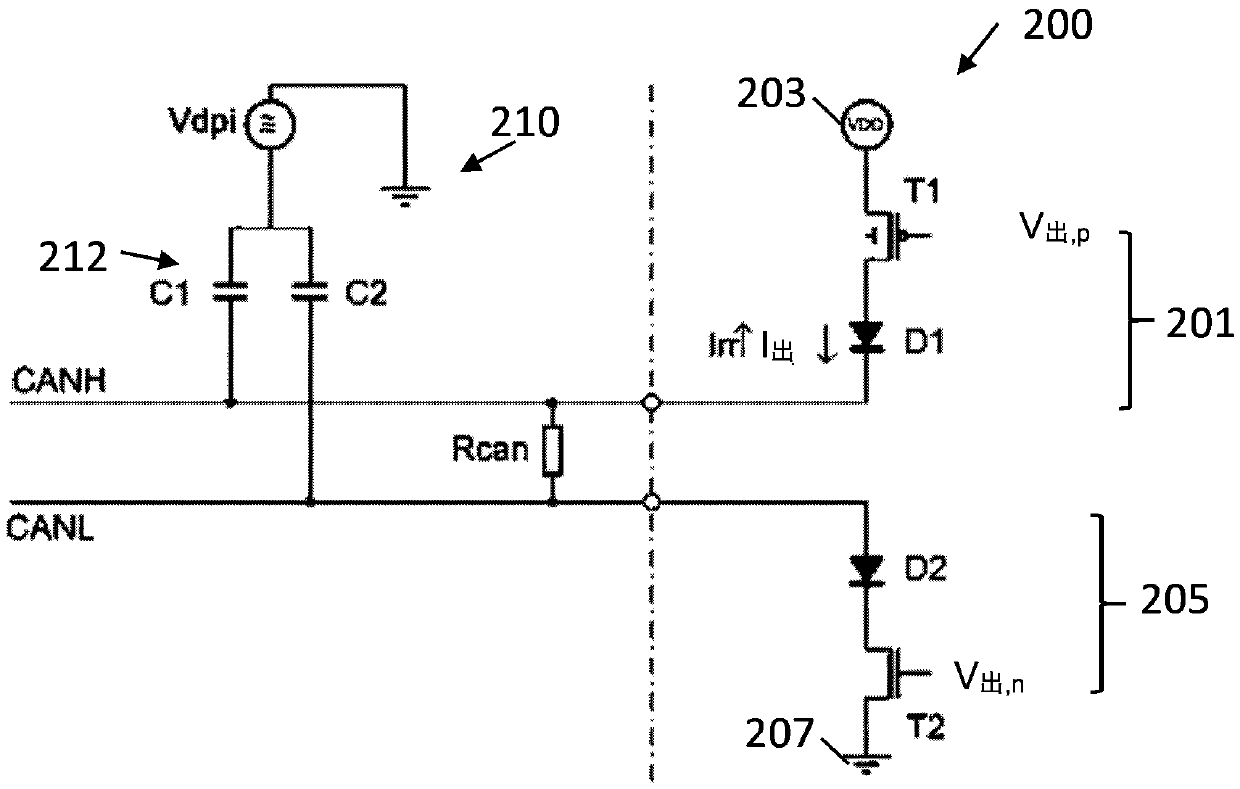

ActiveCN109714234AImprove shielding effectReduce reverse currentBaseband system detailsElectric digital data processingDriving currentTransceiver

A transmitter, for establishing communication between a device and a differential network bus, includes: current drivers connected to each line of the bus, through a conduction path of the transmitter; at least one unidirectional current regulator for extracting a current equal to a known ratio of a parasitic current circulating through the conduction path, inverse to the driving current through the conduction path connected to a first line; means for obtaining, from said current, a second current with a magnitude equal to the original magnitude of the parasitic current; means for introducingthe second current into the conduction path connected to the other line.

Owner:MELEXIS TECH NV

Schottky diode having a substrate p-n diode

InactiveUS20120187521A1Reduce reverse currentLower forward voltageSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialZener diode

A semiconductor device has a trench junction barrier Schottky diode that includes an integrated substrate p-n diode (TJBS-Sub-PN) as a clamping element, the trench junction barrier Schottky diode being suited, e.g., as a Zener diode having a breakdown voltage of approximately 20 V, for use in motor-vehicle generator systems. In this context, the TJBS-Sub-PN is made up of a combination of a Schottky diode, an epitaxial p-n diode and a substrate p-n diode, and the breakdown voltage of the substrate p-n diode (BV_pn) is less than the breakdown voltage of the Schottky diode (BV_schottky) and the breakdown voltage of the epitaxial p-n diode (BV_epi).

Owner:ROBERT BOSCH GMBH

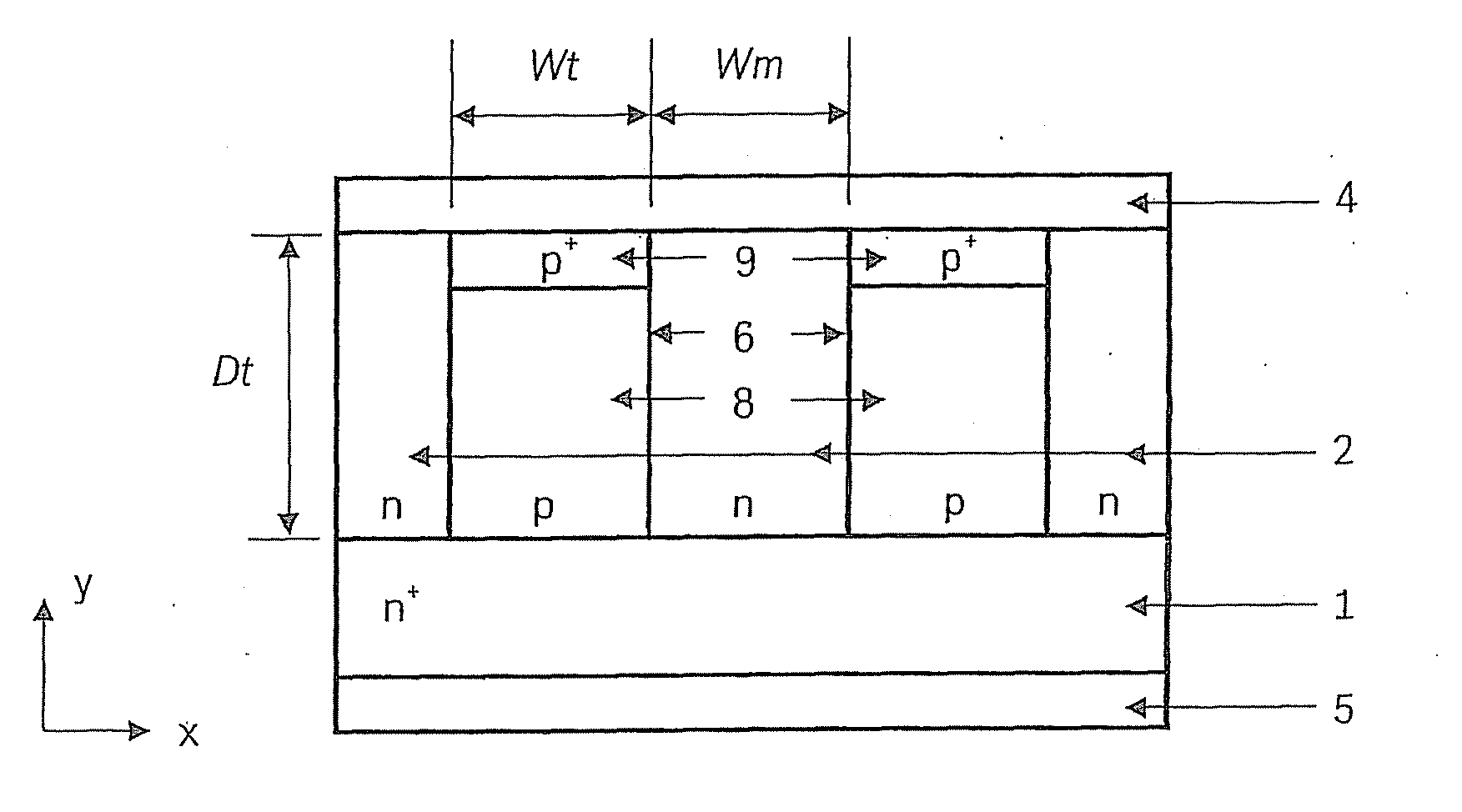

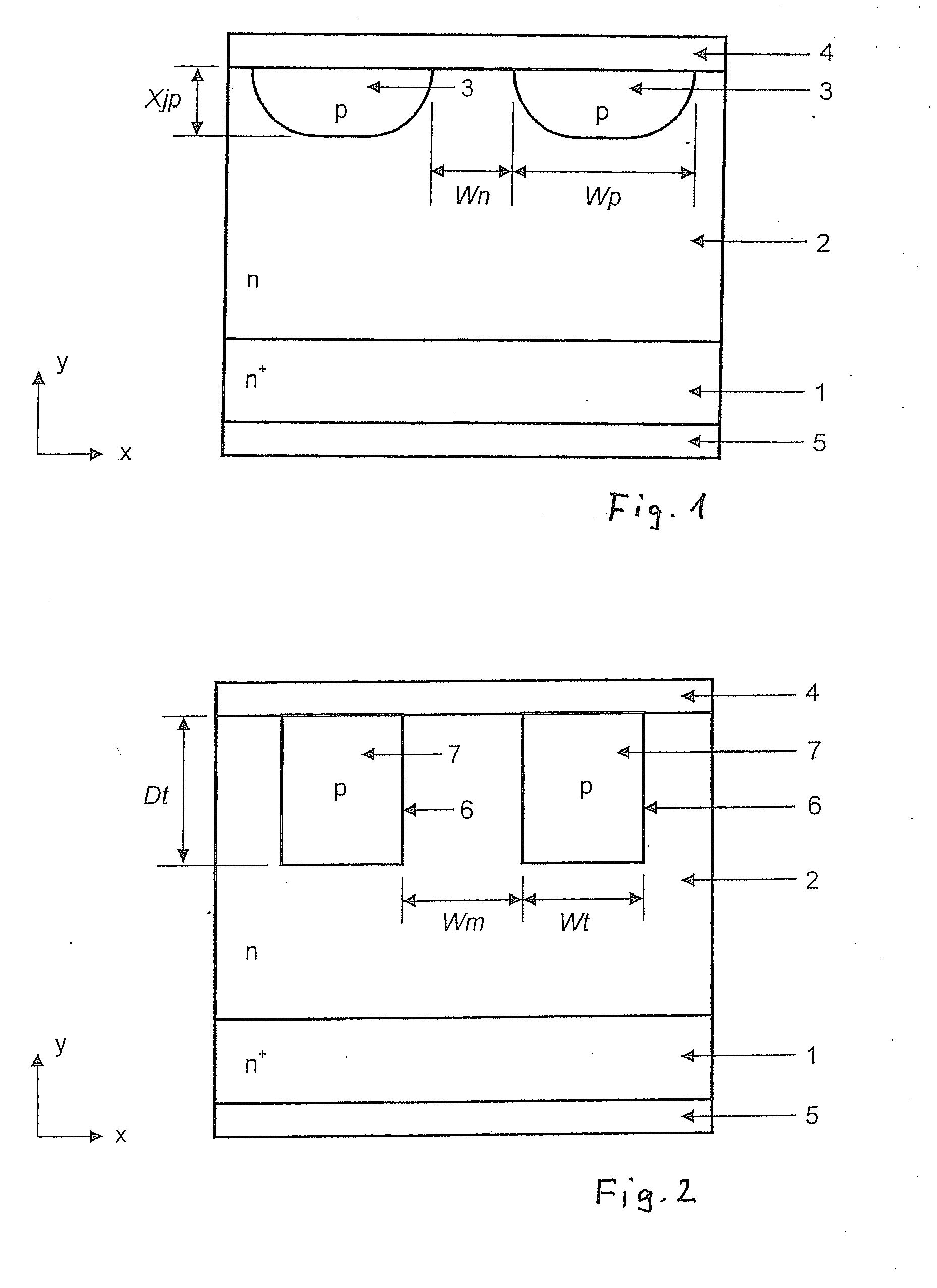

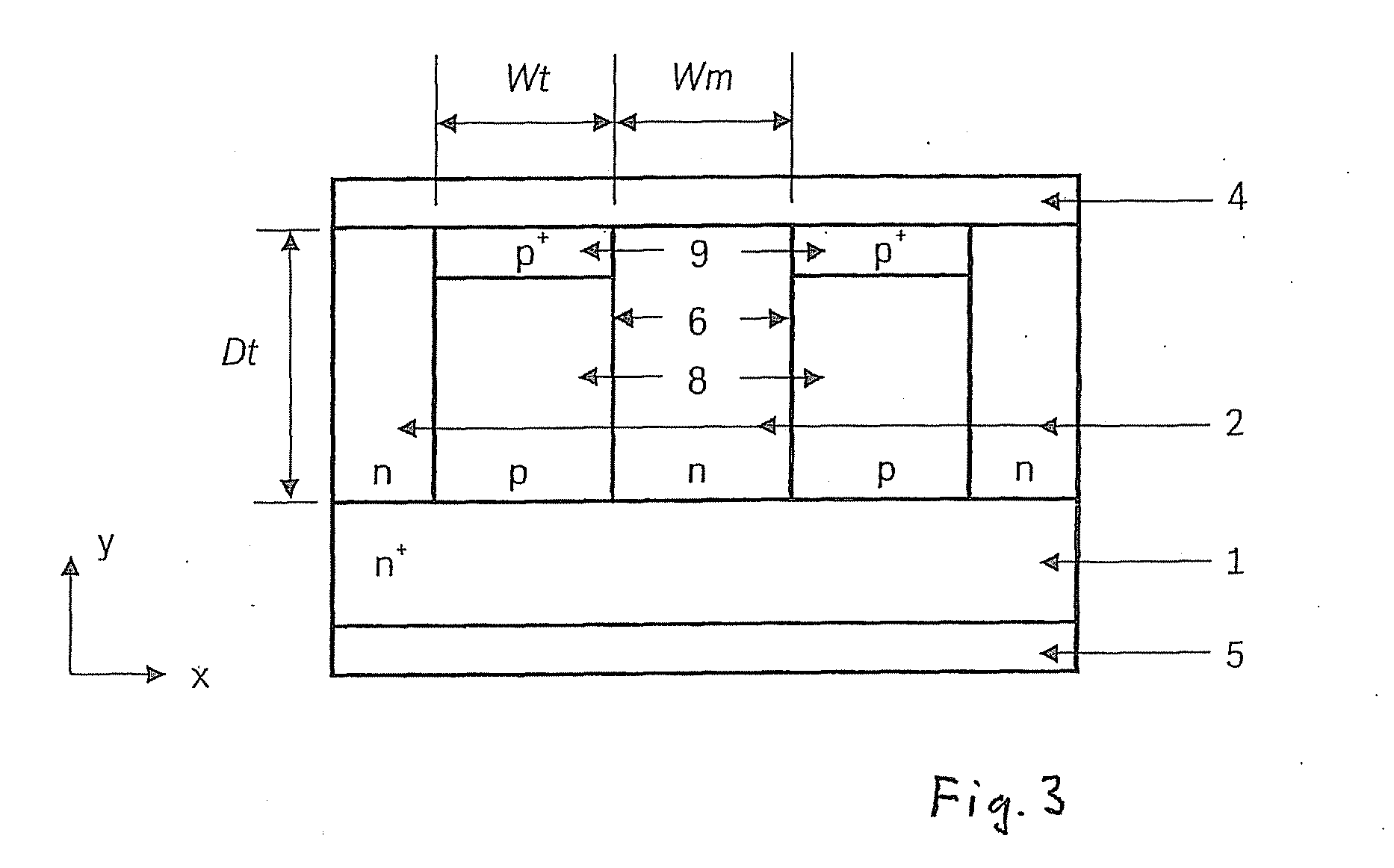

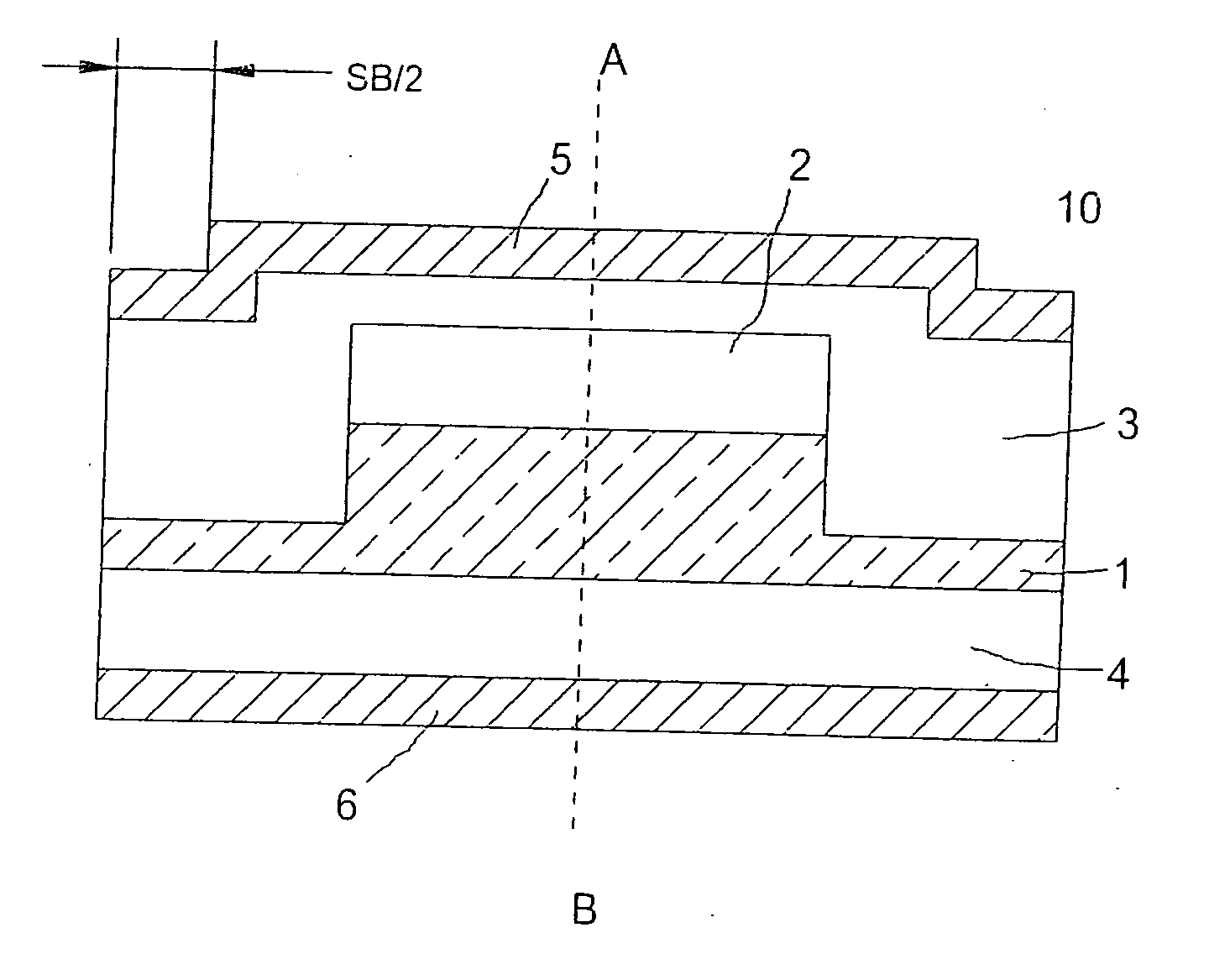

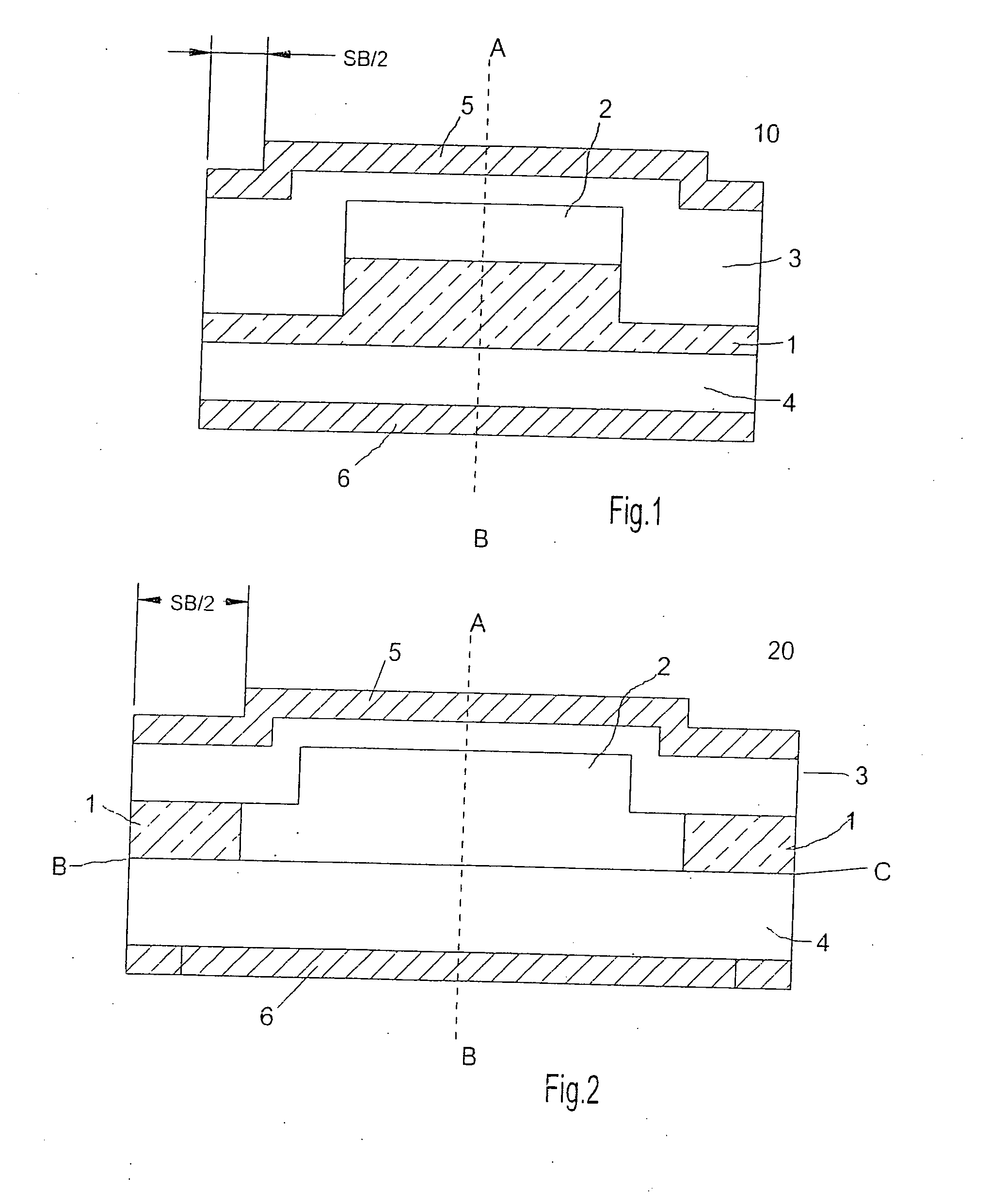

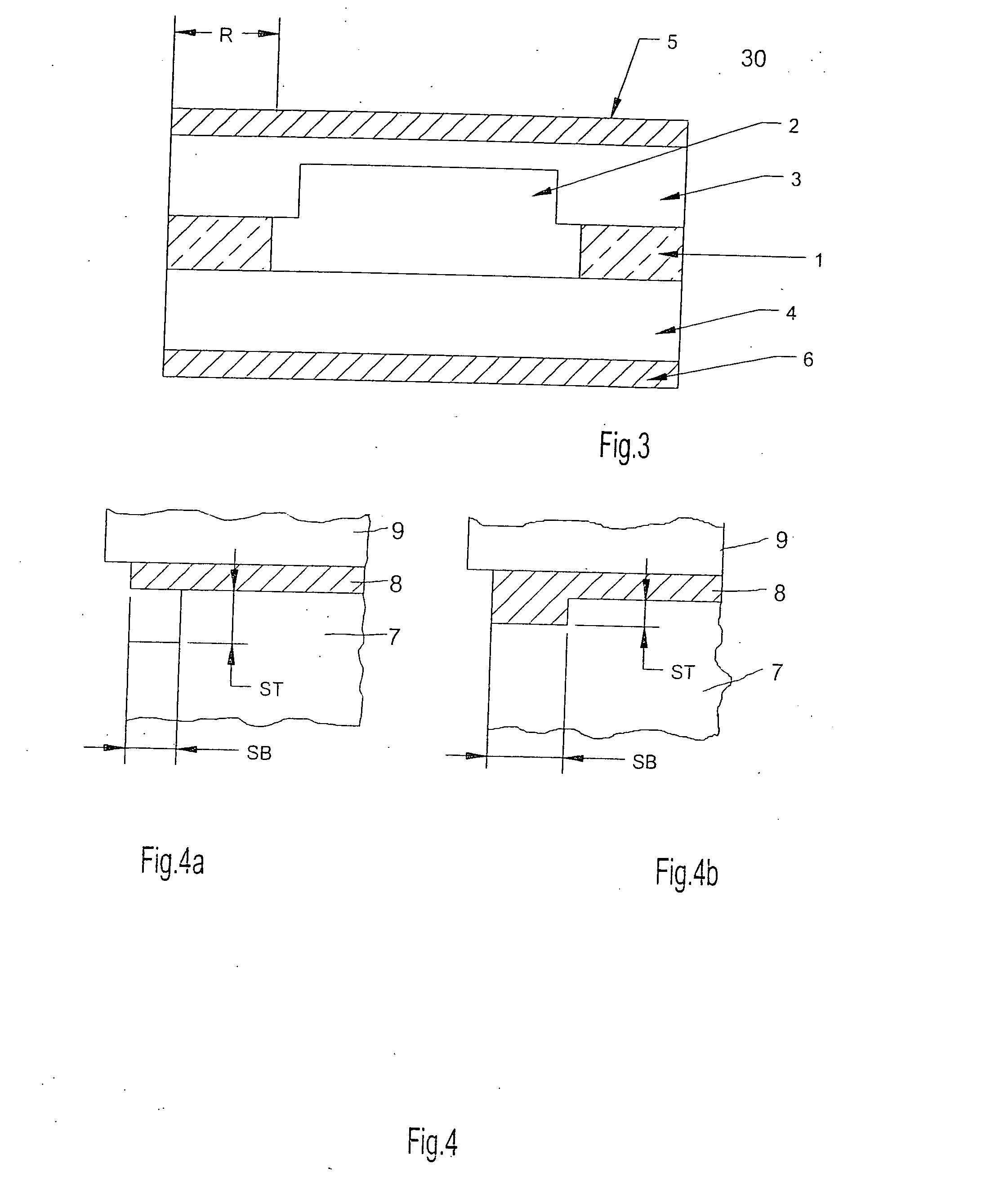

Semiconductor diode and method for the production thereof

In a semiconductor system 20 made up of multiple sublayers, a sublayer over the largest part of a cross-sectional area BC in the interior of the semiconductor system borders immediately on the first sublayer, while bordering on a second sublayer only in a comparatively narrow edge region of the cross-sectional area. The semiconductor system is characterized by a low bulk resistance and a high breakdown voltage in the edge region. In addition, a method for manufacturing this semiconductor system is specified.

Owner:ROBERT BOSCH GMBH

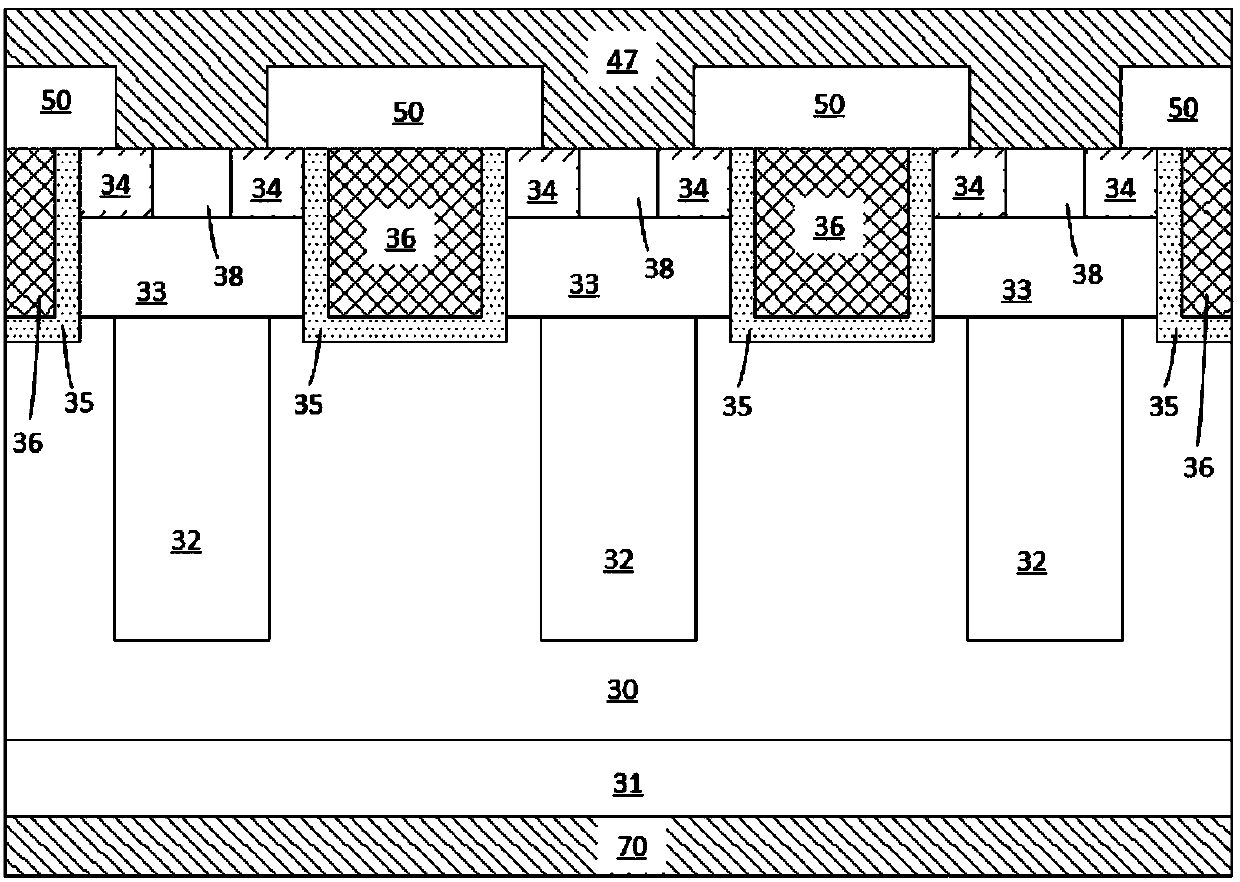

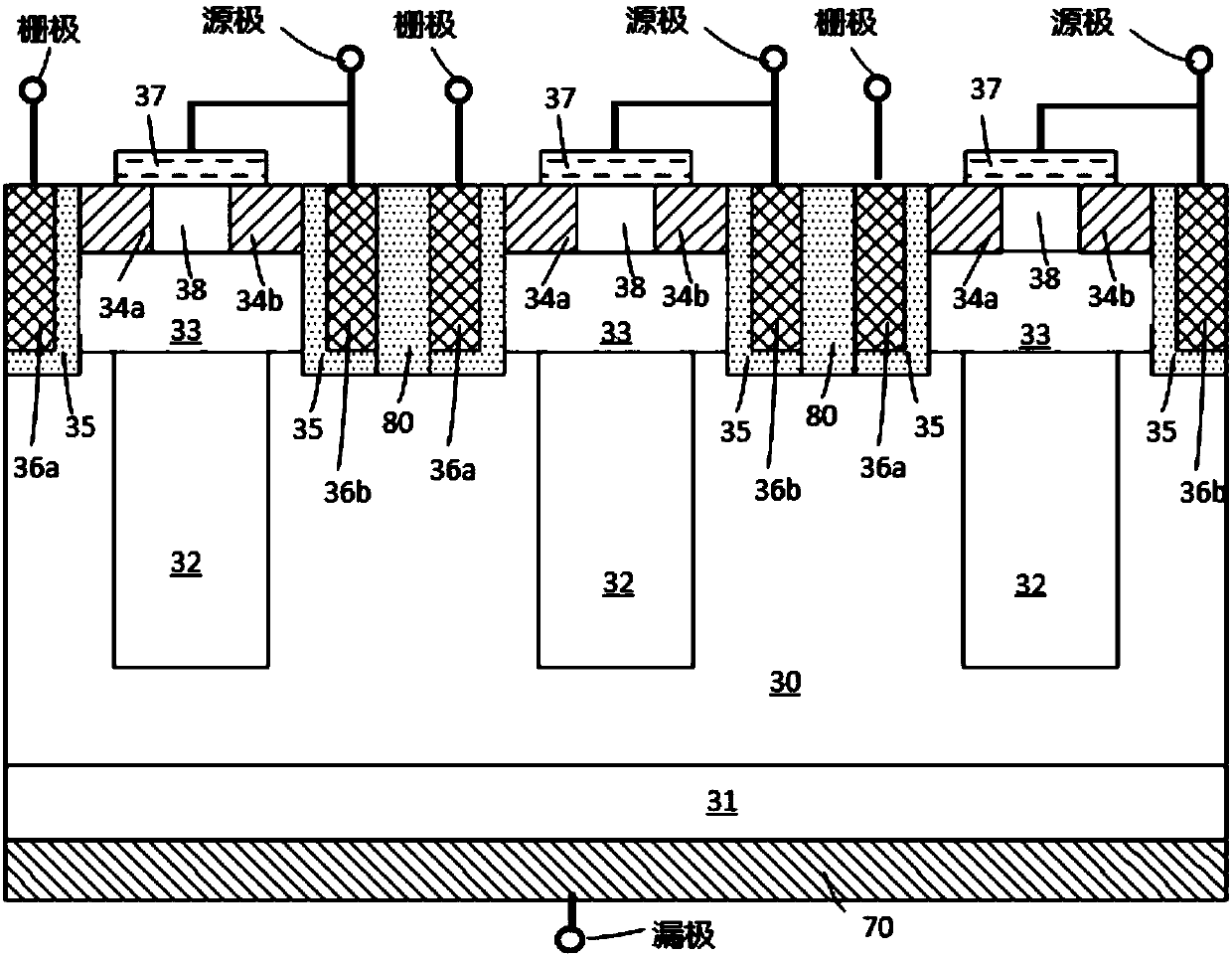

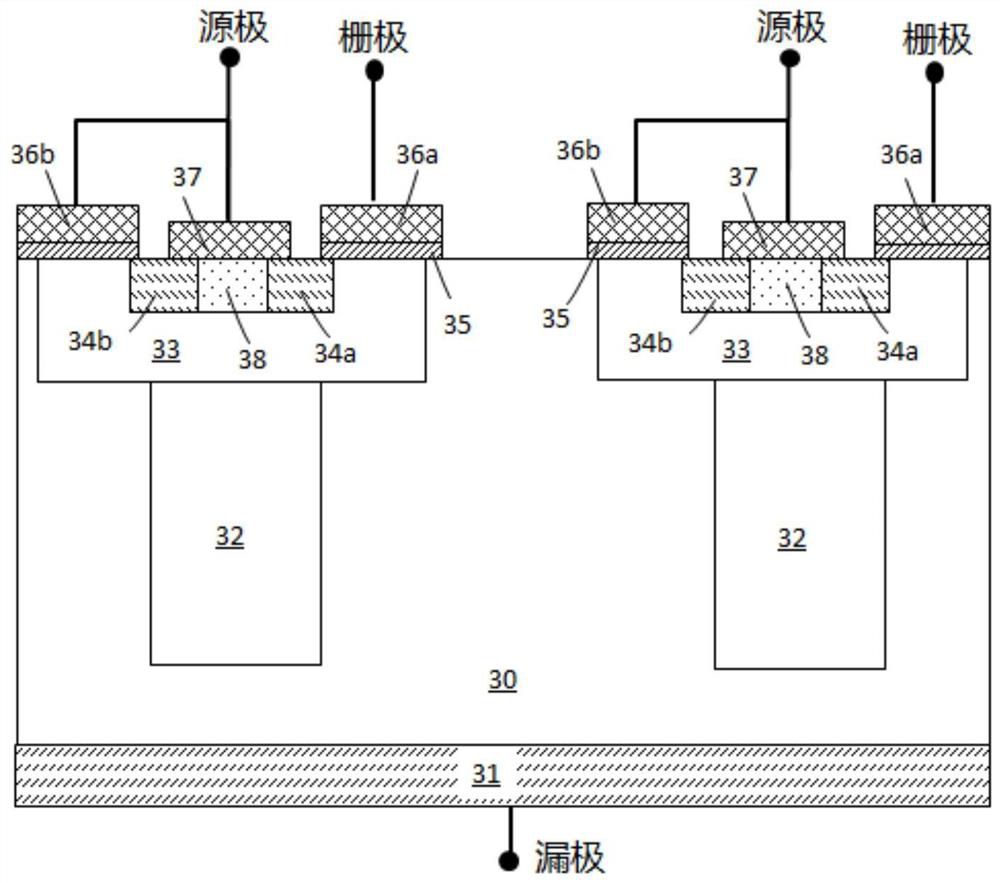

Super junction power device of split gate structure

ActiveCN109755238AReduce reverse recovery chargeReduce reverse recovery timeSolid-state devicesSemiconductor devicesCurrent channelBody contact

Embodiments of the invention disclose a super junction power device of a split gate structure. The device comprises a source, a drain, a first gate, a second gate, a third gate, a body diode and a body contact diode, wherein the cathode of the body diode is connected to the drain, the anode of the body contact diode is connected to the anode of the body diode, the cathode of the body contact diodeis connected to the source, the first gate controls a first current channel between the source and the drain to be turned on or off through the gate voltage, the second gate and a third gate are connected to the source, the second gate controls a second current channel between the source and the drain to be turned on or off through the source voltage, the third gate is a shield gate, and the source voltage is used to increase the withstand voltage of the super junction power device of the split gate structure.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

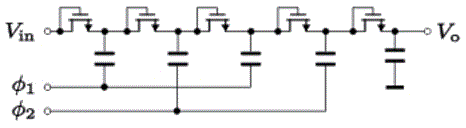

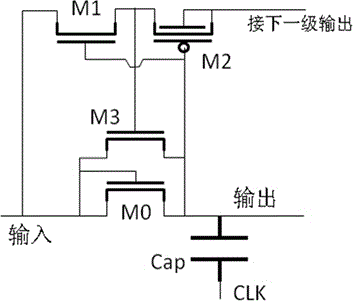

Charge pump circuit suitable for low voltage operation

ActiveCN104811033AAvoiding Parasitic Bipolar Transistor EffectsGood continuityApparatus without intermediate ac conversionLow voltageEngineering

The invention relates to a charge pump circuit, wherein each level charge pump subunit is provided with four NMOS (N-channel metal oxide semiconductor) transistors and a pair of phase complementary two-phase clock signals. The charge pump circuit suitable for low voltage operation is characterized in that a drain electrode of the first transistor is connected to the input end of the level of charge pump subunit, and a source electrode is connected to the output end of level of charge pump subunit; a drain electrode of the second transistor is connected to the input end of the level of charge pump subunit; a drain electrode and a grid electrode of the third transistor are connected to the source electrode of the second transistor; a source electrode of the third transistor is connected with the grid electrode of the first transistor; a drain electrode and a grid electrode of the fourth transistor are connected to the grid electrode of the first transistor; the source electrode of the fourth transistor is connected to the input end of the level of charge pump subunit; the first-phase clock signal is connected to the output end of the level of charge pump subunit through a first capacitor and is connected to a second source electrode of the second transistor through a third capacitor; the second-phase clock signal is connected to the grid electrode of the first transistor through a second capacitor. The charge pump circuit suitable for low voltage operation can improve the voltage of the grid electrodes of NMOS transistor switches and reduce the side effect of the substrate bias effect.

Owner:GIANTEC SEMICON LTD

Grooved super junction power device

ActiveCN109755289AReduce reverse recovery chargeReduce reverse recovery timeSemiconductor devicesCurrent channelPower flow

The embodiment of the invention provides a grooved super junction power device. The device comprises sources, a drain, first gates, second gates, body diodes, and p-body contact diodes, wherein each body diode is connected in series with the corresponding p-body contact diode; each first gate controls the on / off of a corresponding first current channel, which is controlled by the first gate, through a gate voltage; and each second gate is connected with the corresponding source, and controls the on / off of a corresponding second current channel, which is controlled by the second gate, through asource voltage. The grooved super junction power device provided by the invention has the advantages that when the device is off, reverse currents flowing through the body diodes can be greatly reduced, so that the number of minority carriers in the body diodes can be greatly decreased, and the grooved super junction power device can achieve a rapid reverse recovery function.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

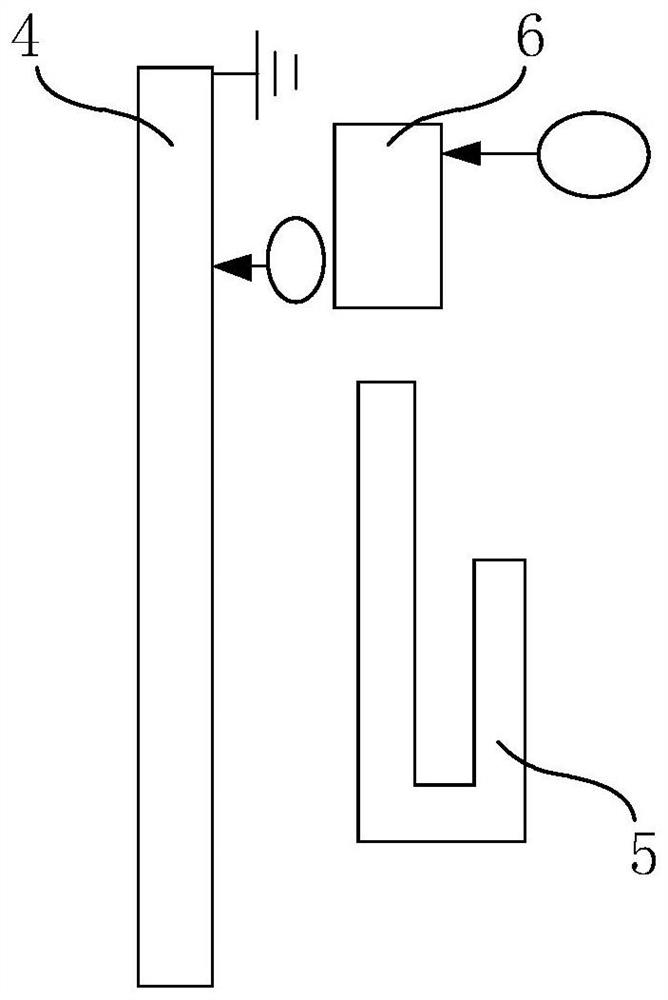

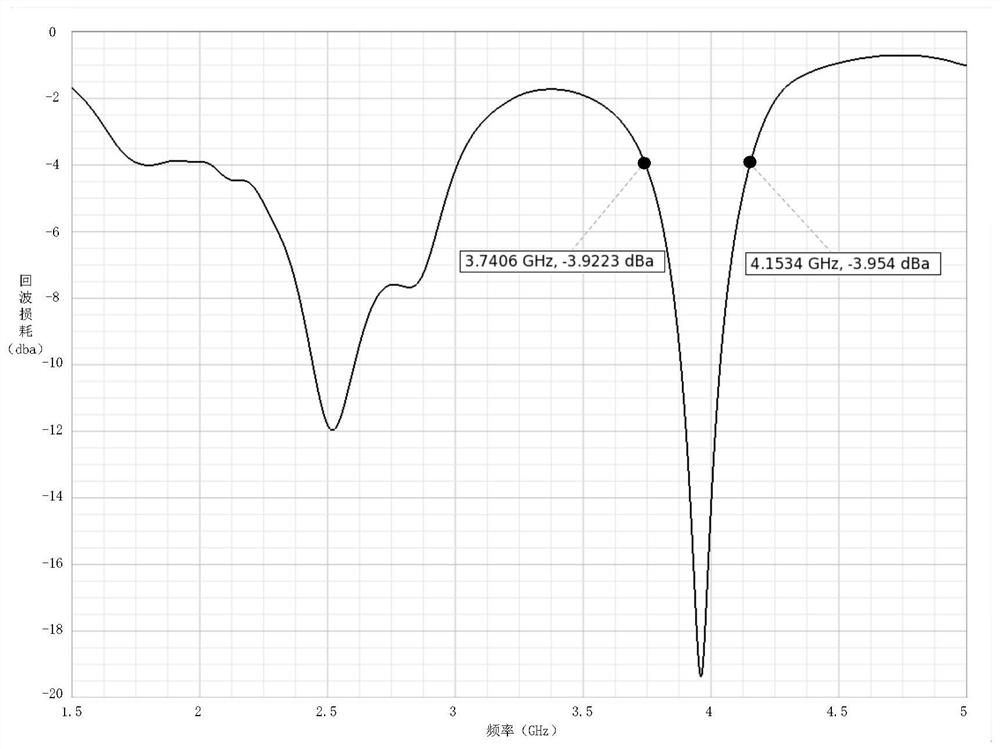

Antenna and mobile terminal

InactiveCN111613905AImprove performanceImprove communication performanceAntenna supports/mountingsAntenna adaptation in movable bodiesFrequency bandReverse current

The invention provides an antenna and a mobile terminal. The antenna comprises a first sub-antenna and a second sub-antenna, and radiators of the first sub-antenna and the second sub-antenna share a first branch, and the radiators of the first sub-antenna and the second sub-antenna further comprise a second branch. At setting, the second branch is electrically connected with the first branch, thesecond branch and the first branch are intersected at a set angle, and the ratio of the length of the second branch to the wavelength of a specific working frequency is within a set threshold value, wherein the specific working frequency is within the working frequency band of the second sub-antenna. The second branch is arranged to be electrically connected with the first branch and intersect with the first branch at the set angle, at the same time, the length of the second branch is limited, so that the resonance formed by the second branch is compatible with a half mode of the first branch,the frequency band width of the antenna is broadened. Moreover, a reverse current between the first branch and the second branch can be reduced, an efficiency pit is shallow, and further the performance of the antenna is improved, and the communication effect of the antenna is improved.

Owner:HUAWEI TECH CO LTD

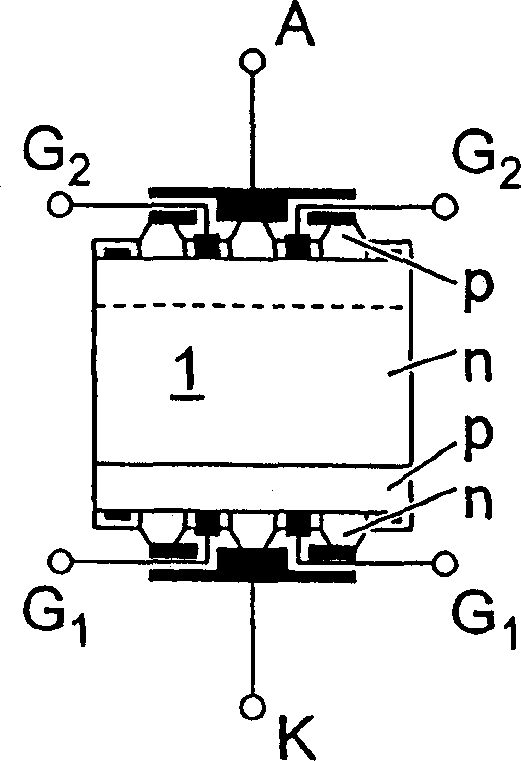

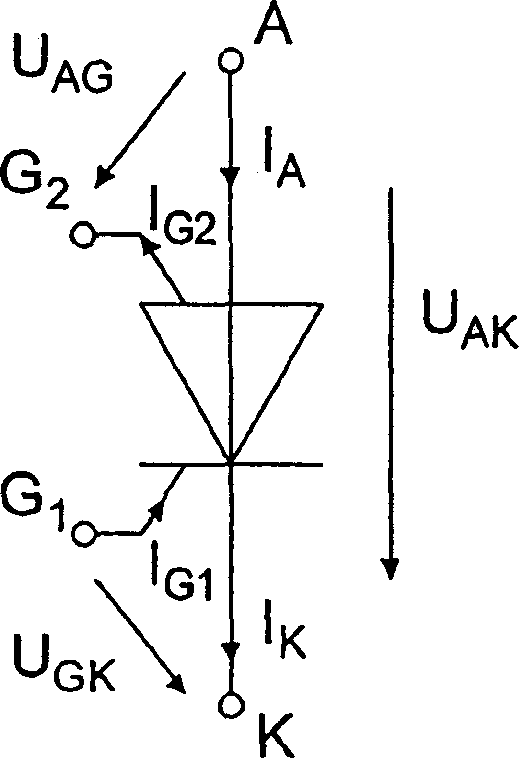

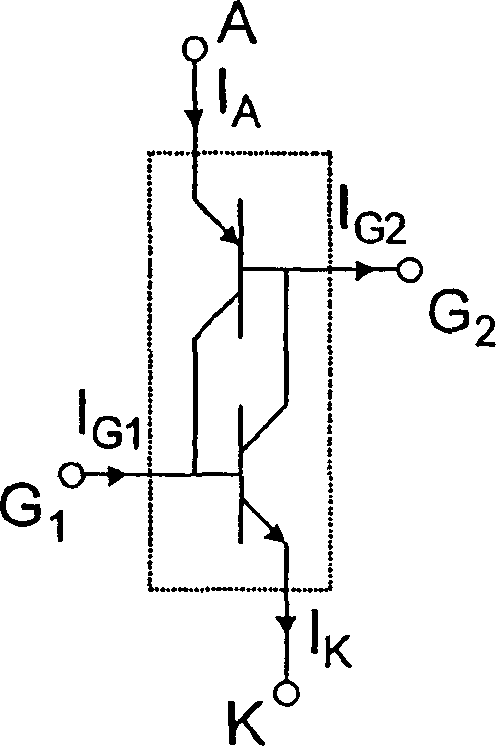

Method for driving power semiconductor element

InactiveCN1254015CReduced turn-off lossReduce lossThyristorElectronic switchingPower semiconductor deviceLow inductance

The integrated gate double transistor (IGDT) has two controllable gates (G 1 , G 2 ), the first gate (G 1 ) is placed on the cathode side and is driven by the first gate current through the low inductance first gate connection, while the second gate (G 2 ) is placed on the anode side and driven by the second gate current through the low inductance second gate connection. During the IGDT cut-off operation, the rate of rise of the voltage on the IGDT is limited by the two gates. Limiting the rate of rise of the voltage across the IGDTs prevents voltage growth at different rates in the series-connected IGDT circuit and thus prevents overheating and destruction of individual IGDTs due to uneven loading.

Owner:ABB (SCHWEIZ) AG

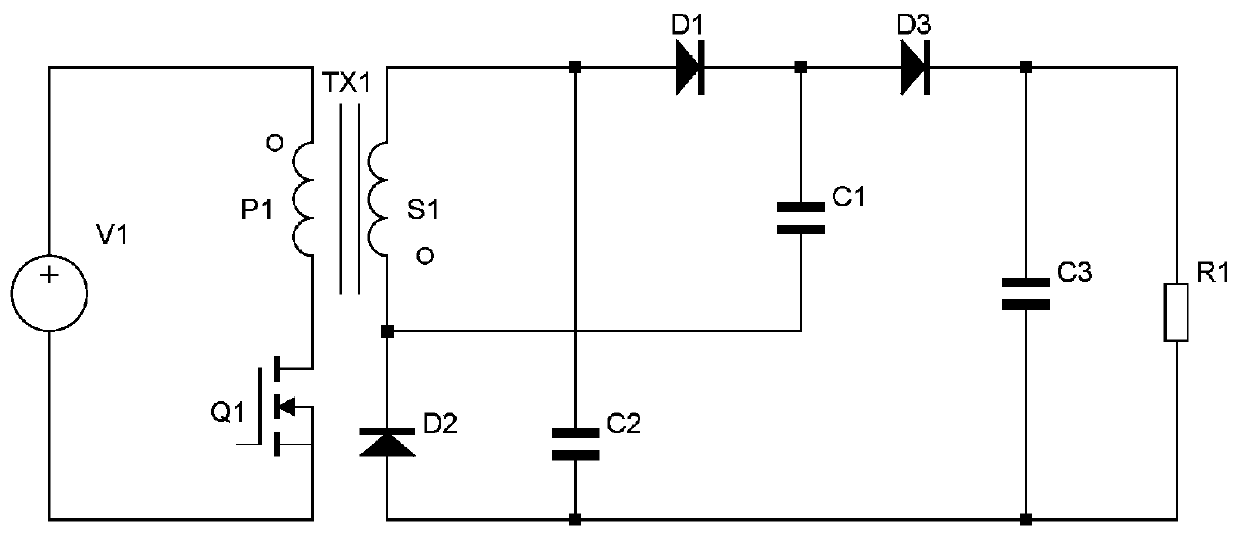

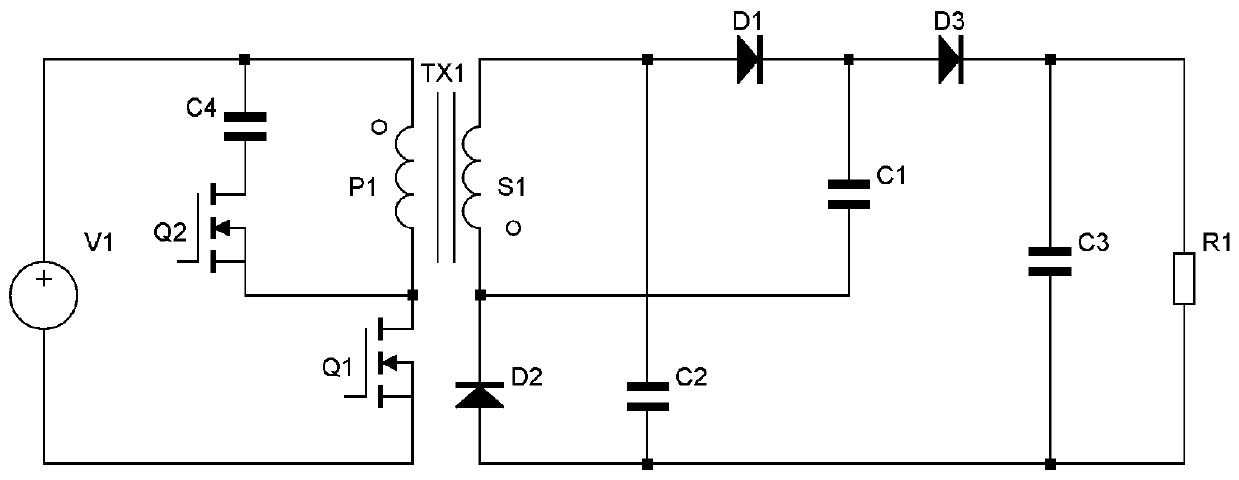

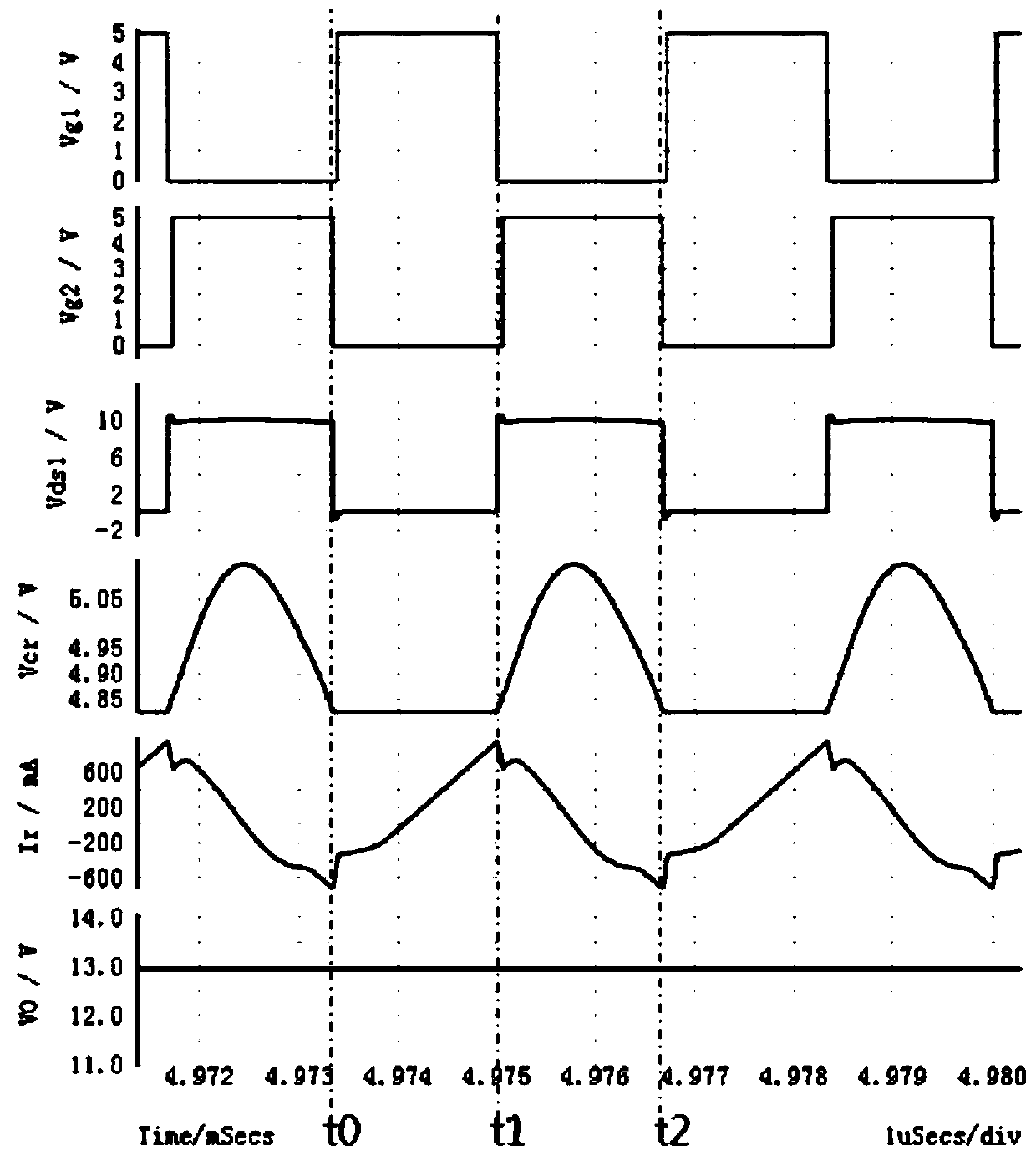

High-voltage output converter

InactiveCN111030460AImprove transmission efficiencyReduce lossEfficient power electronics conversionDc-dc conversionCapacitanceTransformer

The invention provides a high-voltage output converter which uses a positive flyback circuit and comprises an input positive end, an input negative end, a transformer TX1, an MOS transistor Q1, an MOStransistor Q2, a diode D1, a diode D2, a diode D3, a capacitor C1, a capacitor C2, a capacitor C3, a capacitor C4, an output positive end and an output negative end. According to the connection relation, the input positive end, the dotted terminal of the primary winding of the transformer TX1, the drain electrode of the MOS transistor Q1 and the input negative end are connected in sequence; the capacitor C2 and the MOS transistor Q2 are connected in series and then are connected in parallel to two ends of the primary winding; the synonym end of the secondary winding of the transformer TX1, the diodes D1 and D3 and the output positive end are connected in series; the output negative end, the diode D2 and the dotted terminal of the secondary winding of the transformer TX1 are sequentially connected in series; the capacitor C1 is connected in parallel between the cathode of the diode D1 and the dotted terminal of the secondary winding of the transformer TX1, the capacitor C2 is connectedin parallel between the synonym terminal of the secondary winding of the transformer TX1 and the anode of the diode D2, and the capacitor C3 is connected in parallel between the output positive terminal and the output negative terminal. High-voltage output can be realized, and main power is ensured to realize ZVS in a full-load range.

Owner:MORNSUN GUANGZHOU SCI & TECH

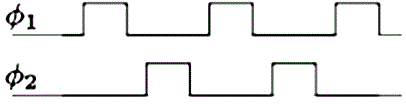

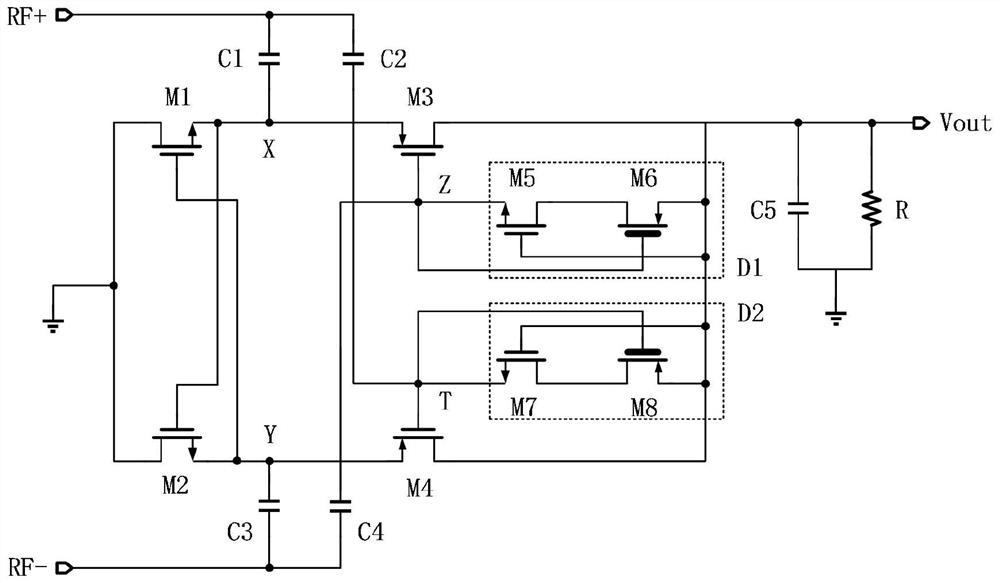

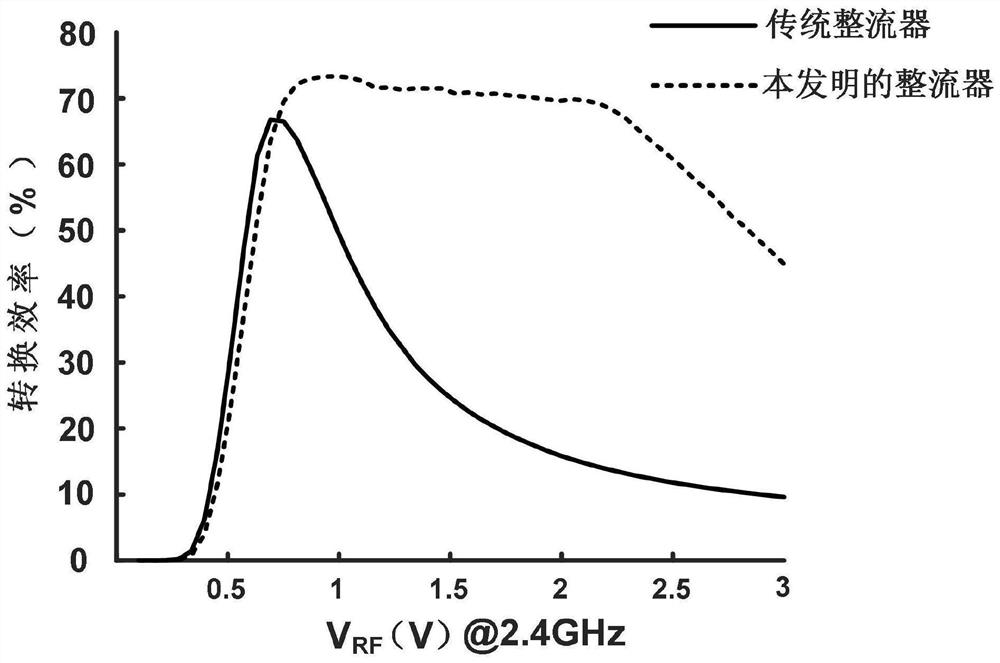

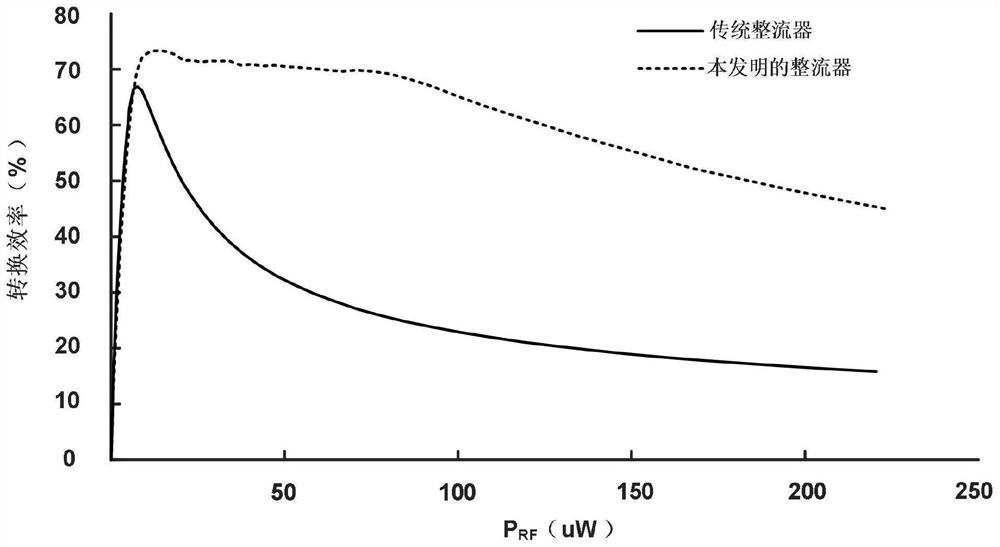

Self-biased differential drive rectifier circuit with wide dynamic range

ActiveCN112542956ALarge dynamic rangeReduce reverse currentNear-field transmissionAc-dc conversionCapacitanceHemt circuits

The invention discloses a self-biased differential drive rectifier circuit with a wide dynamic range. The differential drive rectifier circuit is composed of a differential drive rectifier composed ofa first NMOS transistor (M1), a second NMOS transistor (M2), a first PMOS transistor (M3) and a second PMOS transistor (M4), and a diode of a special structure composed of a first diode (D1) and a second diode (D2). Input signals are RF+ and RF- and are connected with the input end of the differential drive rectifier through the first capacitor (C1) and the second capacitor (C2), the output end of the differential drive rectifier is connected with the first diode (D1) and the second diode (D2) which are connected in parallel, and the output ends of the first diode (D1) and the second diode (D2) are output signals Vout. Feedback is introduced from an output port through a diode, so that bias is provided for a grid electrode of an output PMOS of the differential drive rectifier, and the grid voltage of the differential drive rectifier is controlled. Under the condition of high input power, the reverse current of the differential drive rectifier is effectively reduced, and the dynamic range of high-efficiency output of the differential drive rectifier circuit is widened.

Owner:SOUTHEAST UNIV

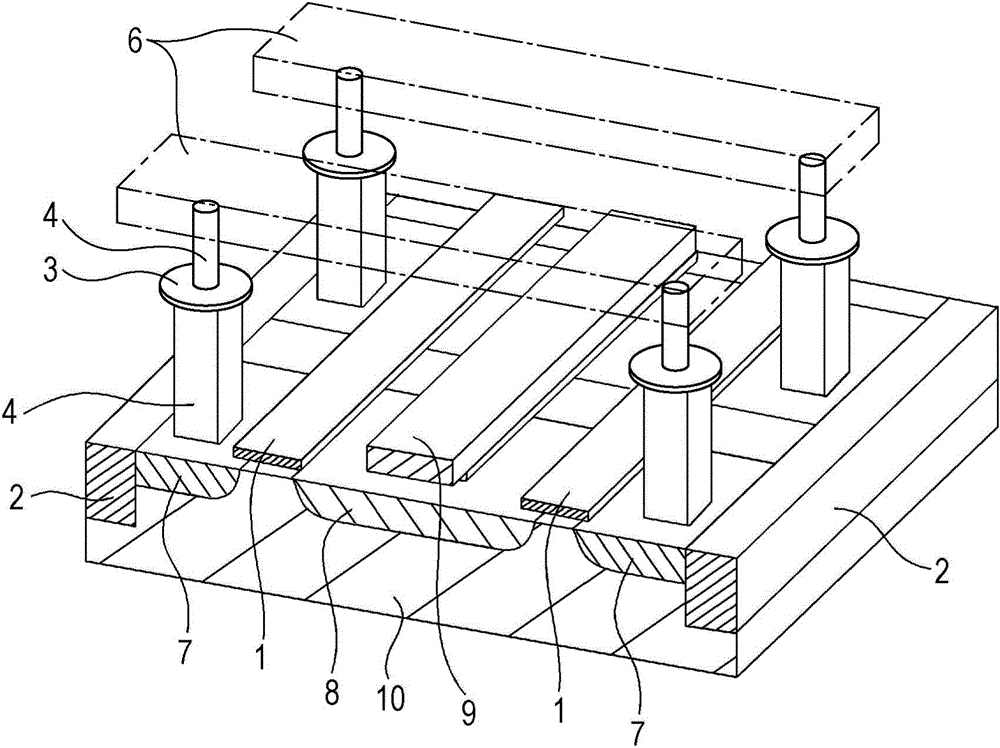

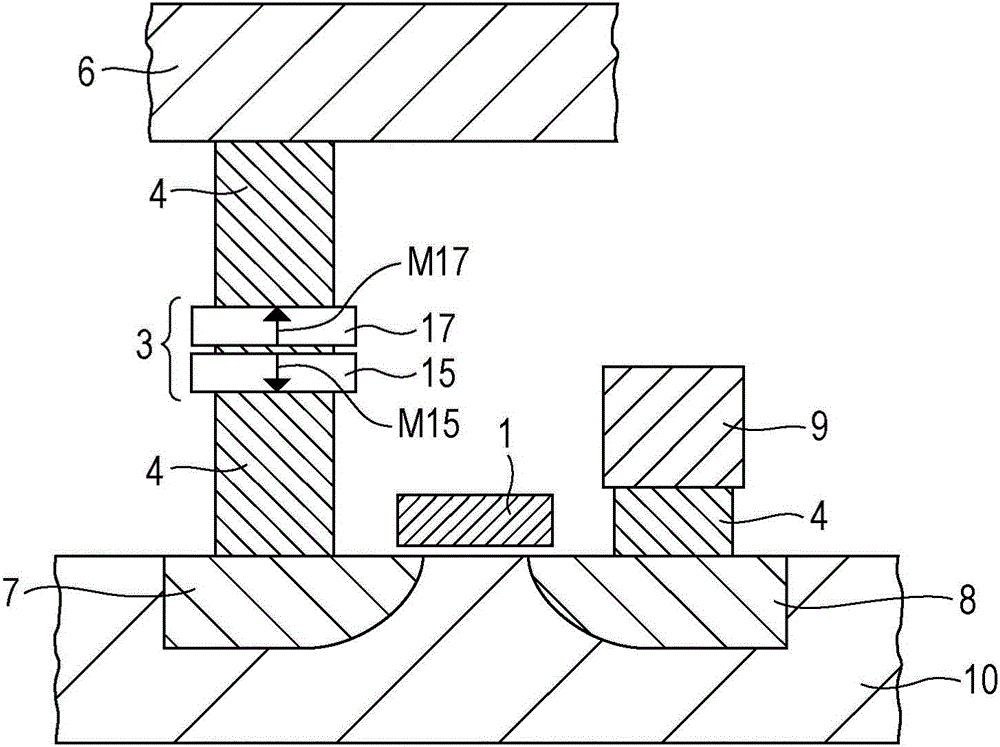

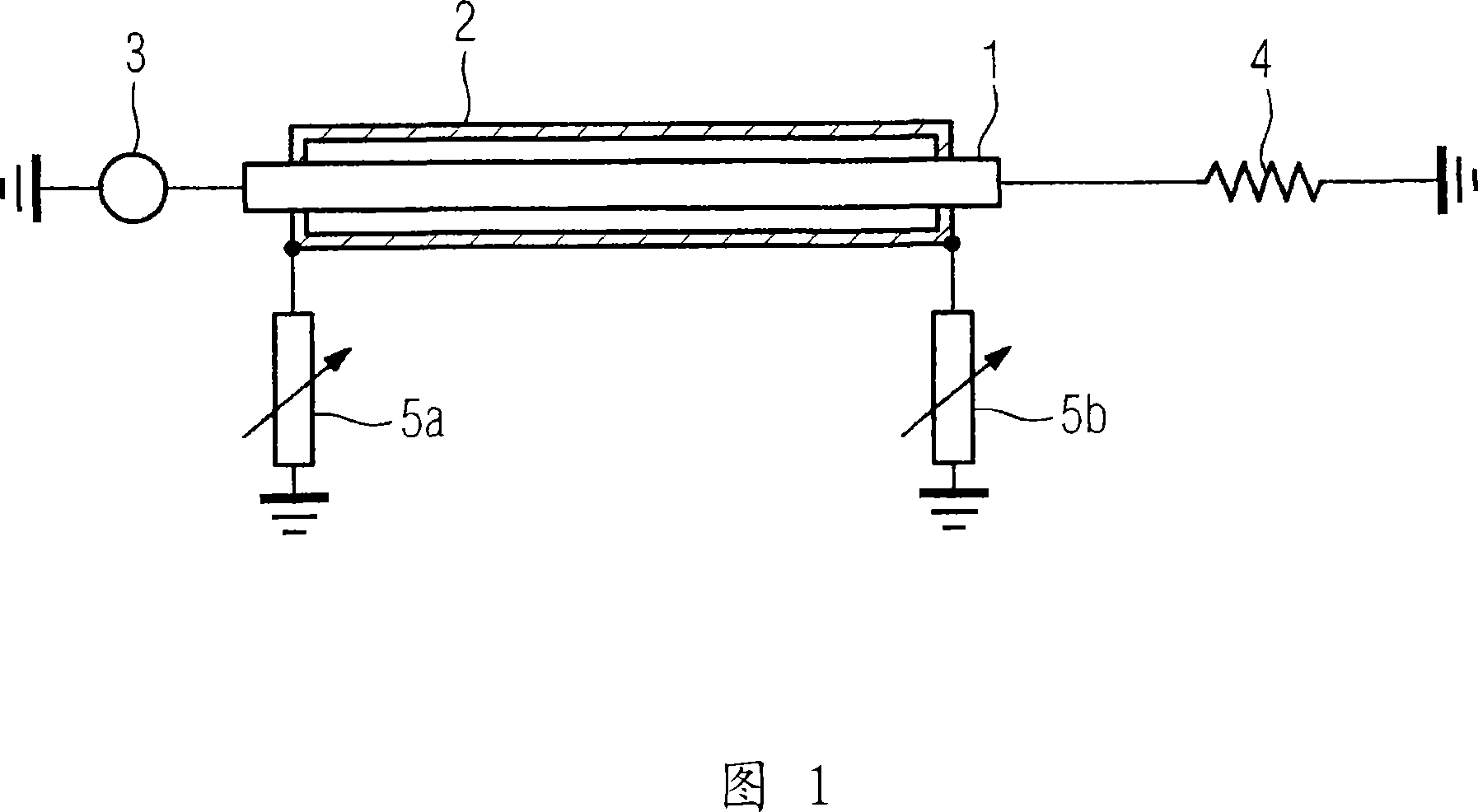

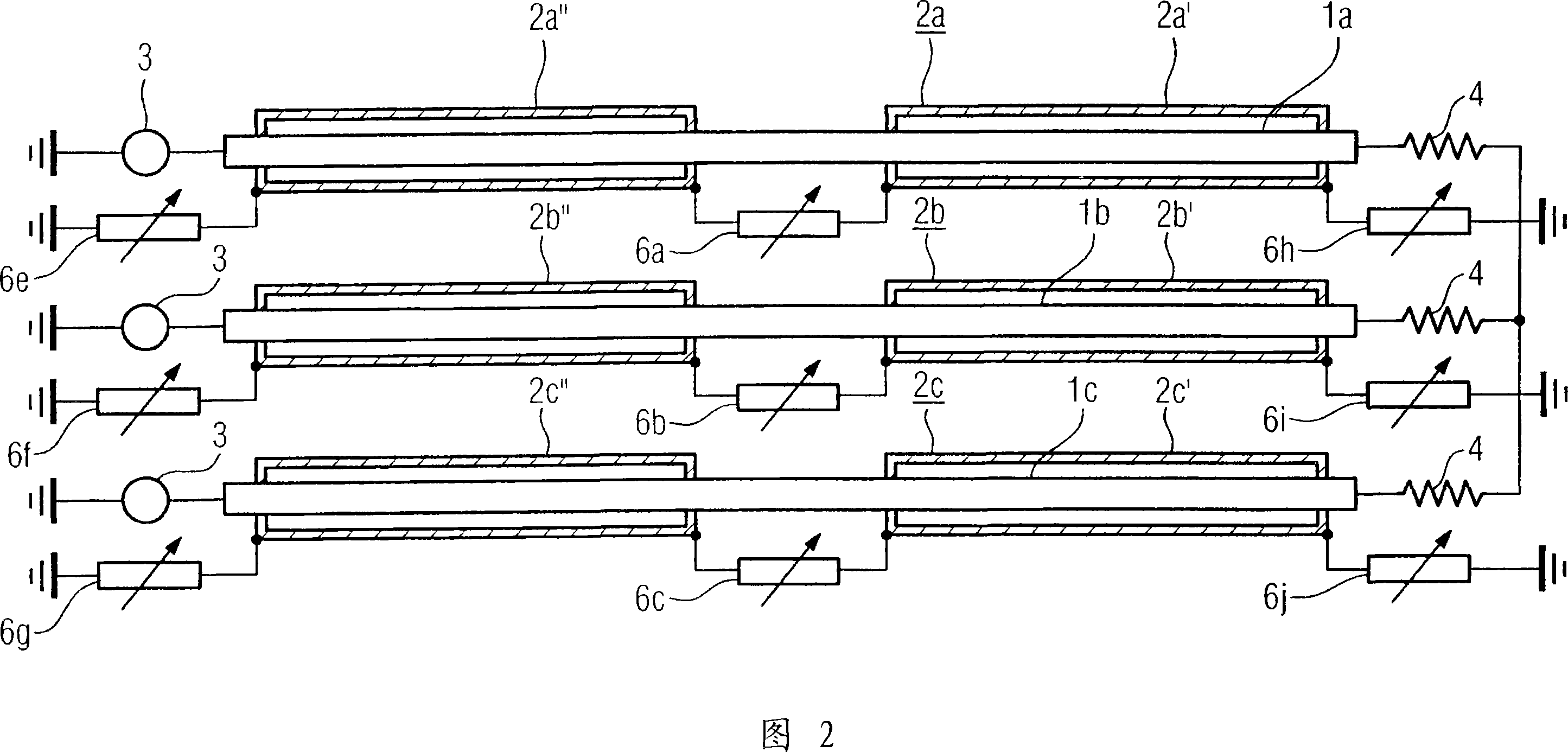

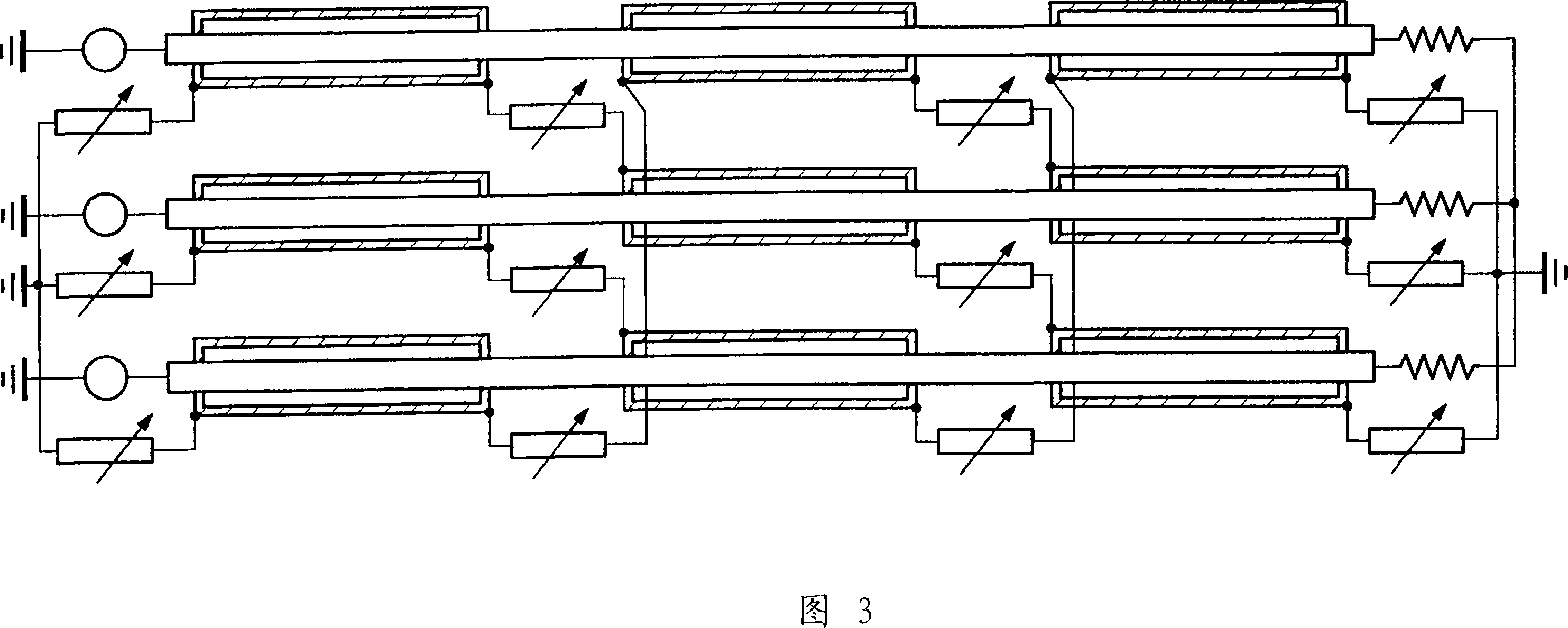

Electric energy transmitting device with a phase conductor and an screen conductor

InactiveCN101006627AReduce reverse currentIncrease running inductanceTotally enclosed bus-bar installationsCable fittings in presence of gas/oilElectrical conductorEngineering

An electric energy transmitting device comprises a phase conductor (1, 1a, 1b, 1c). The phase conductors (1, 1a, 1b, 1c) are each surrounded by an external conductor (2, 2a, 2b, 2c). The external conductors (2, 2a, 2b, 2c) are subdivided into sections (2a', 2a'', 2b', 2b'', 2c', 2c''). The individual sections (2a', 2a'', 2b', 2b'', 2c', 2c'') can be electrically connected by inserting a module with variable impedances (6a, 6b, 6c). A grounding of individual sections of the external conductor (2) ensues via a module with a variable impedance (6e, 6f, 6g, 6h, 6i, 6j, 5a, 5b).

Owner:SIEMENS AG

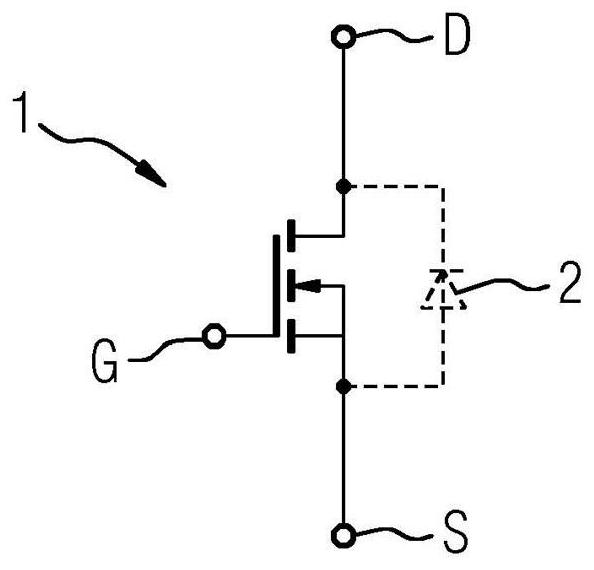

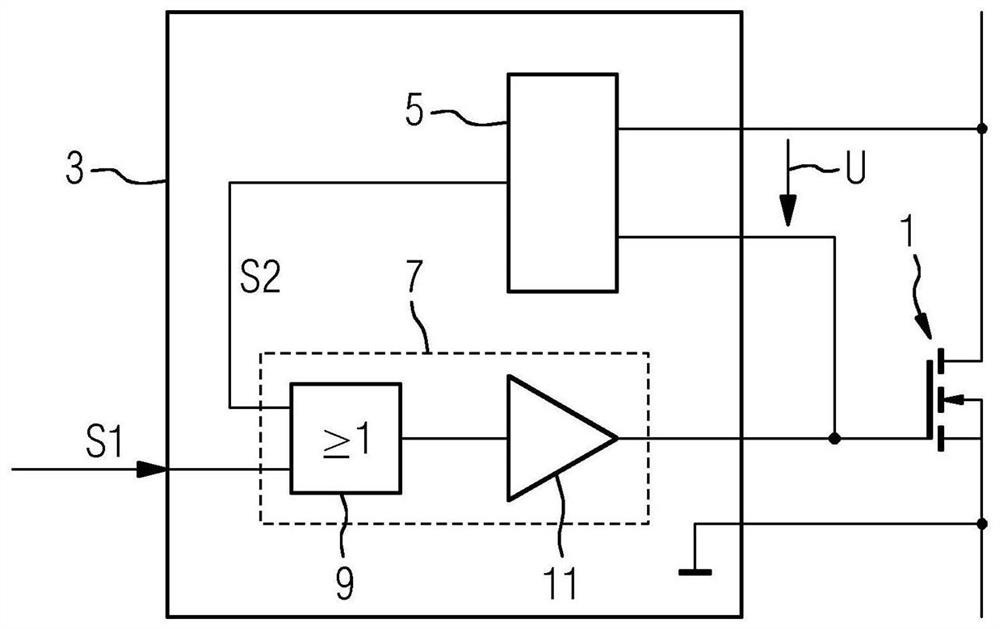

Actuating a metal-oxide semiconductor field-effect transistor

PendingCN112204865ANormal protection schemes are not affectedFunction increaseTransistorEfficient power electronics conversionMOSFETElectrical resistance and conductance

The invention relates to a method and an actuation assembly (3) for actuating a MOSFET (1), in particular a MOSFET (1) based on a semiconductor with a wide band gap. According to the invention, a monitoring process is carried out to determine whether the body diode (2) of the MOSFET (1) is electrically conductive. If the body diode (2) is electrically conductive, the MOSFET (1) is activated, and if the body diode (2) is electrically blocking, the MOSFET is actuated on the basis of an actuation signal (S1).

Owner:SIEMENS AG

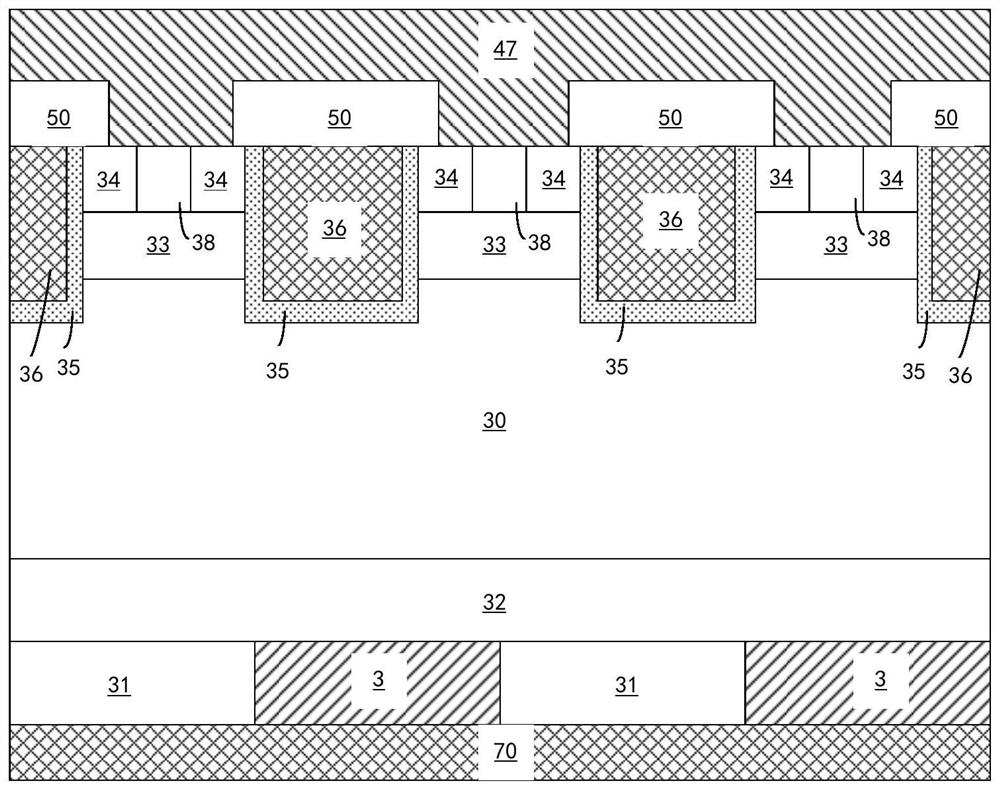

Semiconductor super junction power device

ActiveCN112864221AImprove reverse recovery speedSmall currentTransistorSolid-state devicesMOSFETCapacitance

A semiconductor super junction power device provided by the embodiment of the invention comprises a super junction MOSFET unit array composed of a plurality of super junction MOSFET units, wherein each super junction MOSFET unit comprises a p-type body region located at the top of an n-type drift region, a p-type columnar doped region located below the p-type body region, an n-type source region located in the p-type body region, a grid dielectric layer located on the p-type body region, and a grid electrode and the n-type floating grid located on the grid dielectric layer, in the transverse direction, the grid electrode is located on the side close to the n-type source region, the n-type floating grid is located on the side close to the n-type drift region, and the grid electrode acts on the n-type floating grid through capacitance coupling; and an opening positioned in the grid dielectric layer, wherein the n-type floating grid is in contact with the p-type body region through the opening to form a p-n junction diode. According to the embodiment of the invention, the reverse recovery speed of the semiconductor super junction power device is improved.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

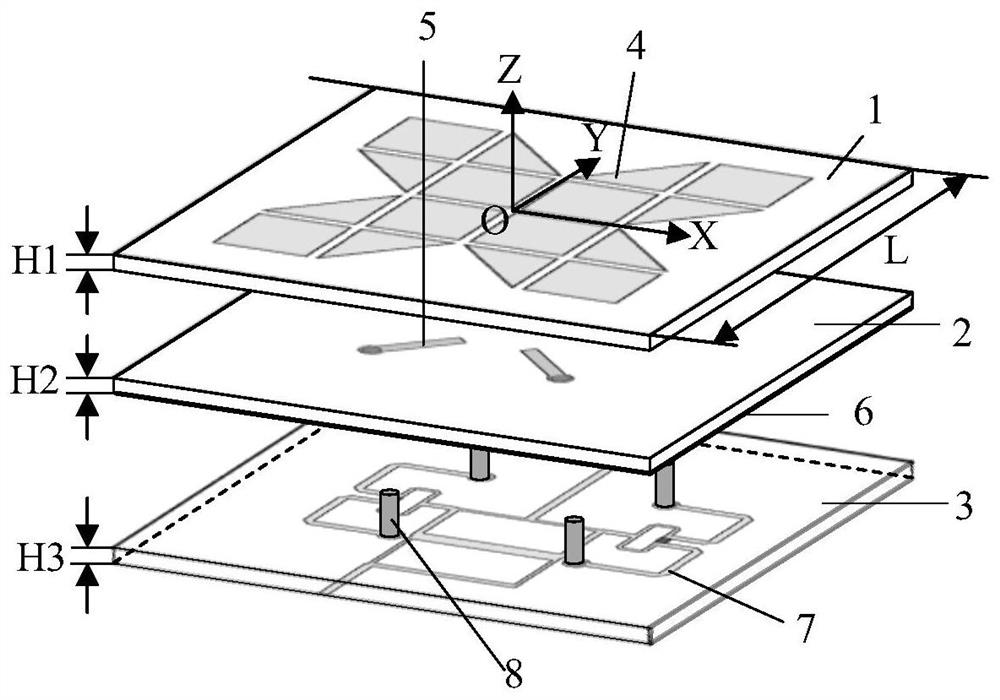

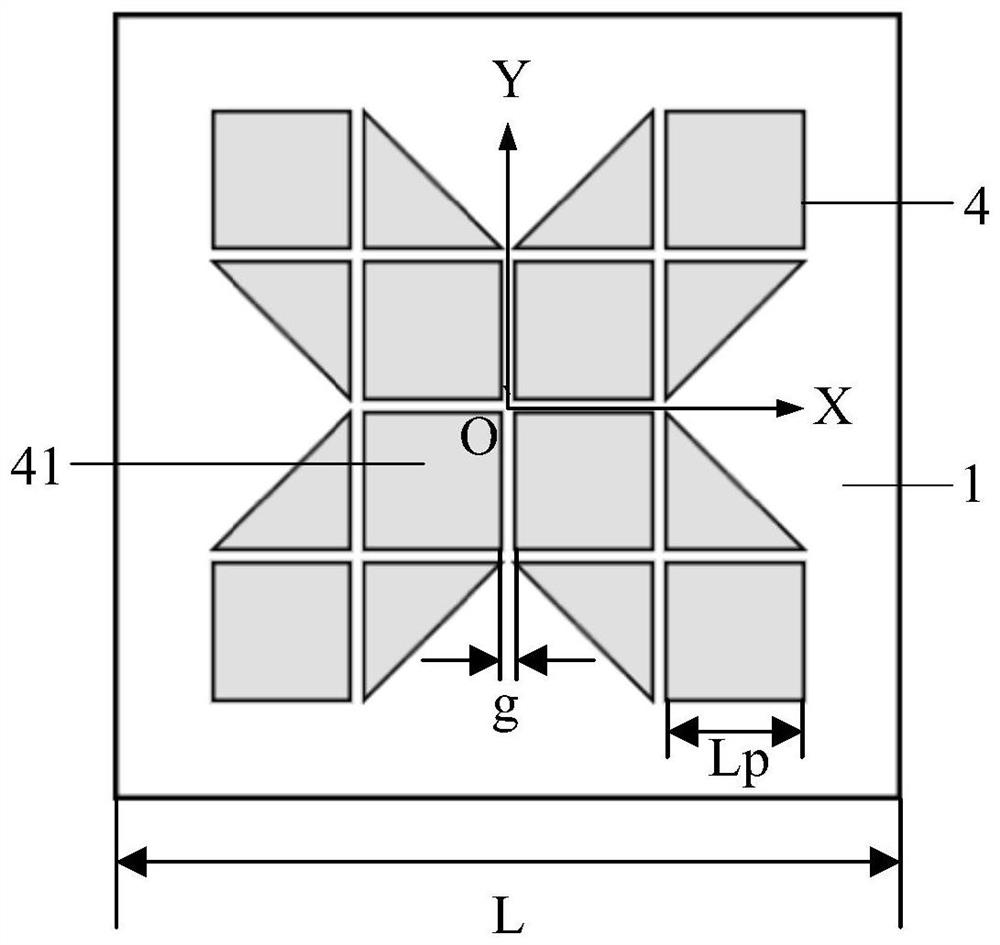

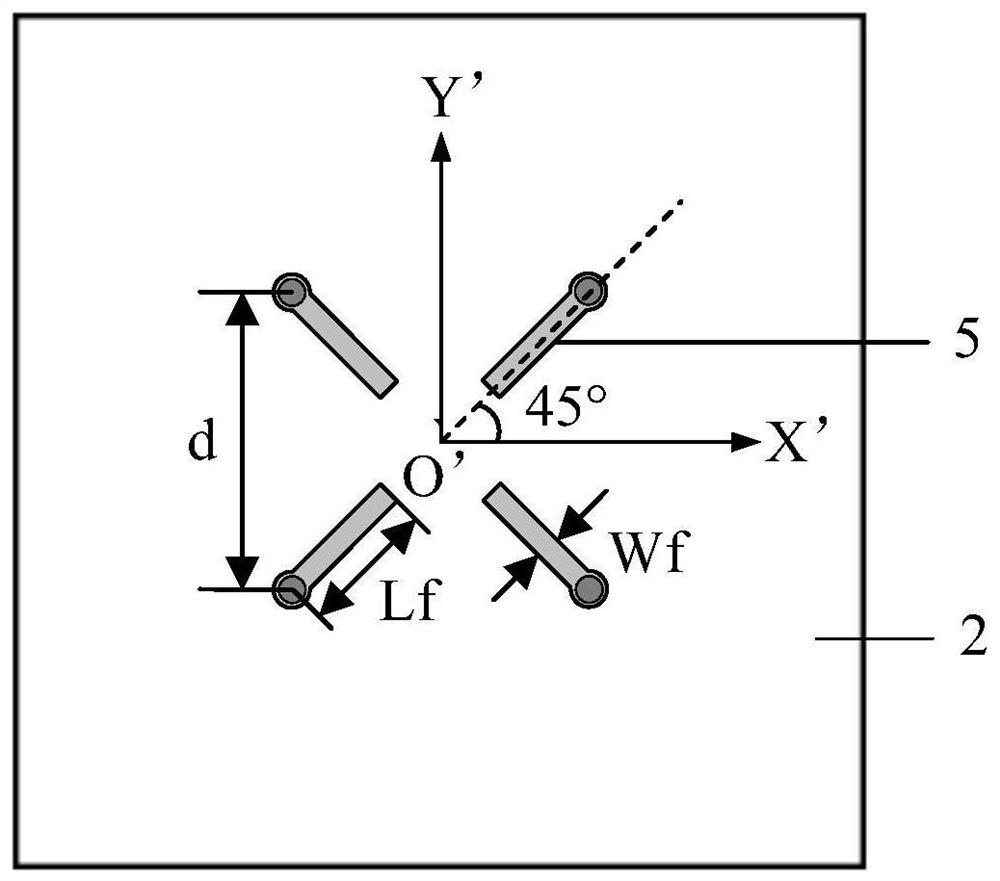

Metasurface-Based Low-Profile Broadband Pattern Diversity Antennas

ActiveCN111769358BBroaden VSWR bandwidthReduce section heightRadiating elements structural formsAntenna earthingsCommunications systemAntenna bandwidth

Owner:XIDIAN UNIV

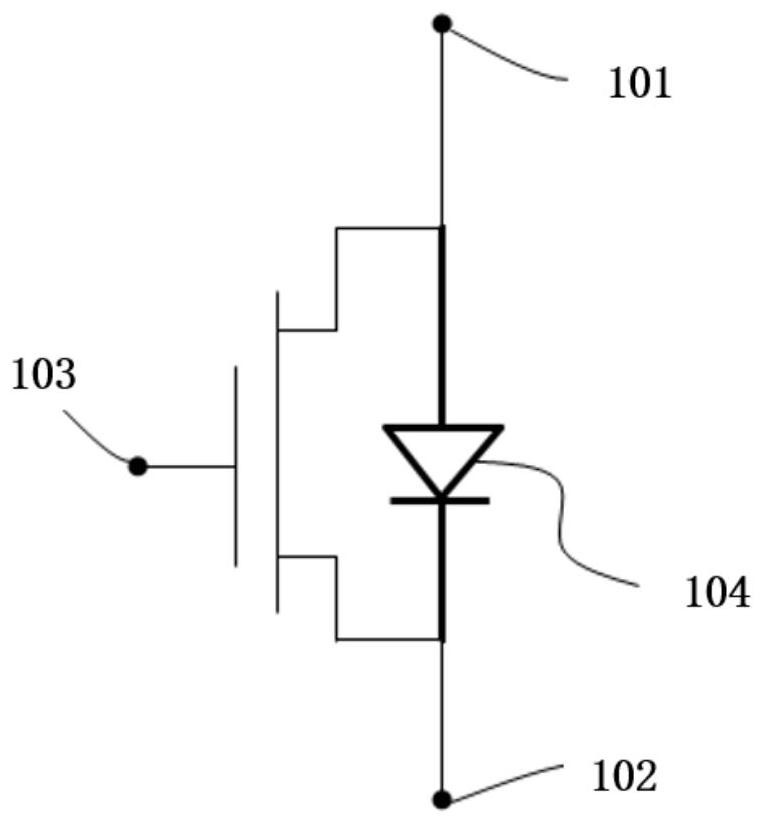

A power mosfet device

ActiveCN109755241BReduce reverse recovery chargeFast reverse recovery functionSolid-state devicesSemiconductor devicesEngineeringPower MOSFET

The present invention provides a power MOSFET device, comprising a source, a drain, a first gate, a second gate, a body diode and a body contact diode, the source, the drain, and the first gate form a first MOSFET structure, the source, drain, and second gate form a second MOSFET structure, the cathode of the body diode is connected to the drain, and the anode of the body contact diode is connected to the anode of the body diode , the cathode of the body contact diode is connected to the source, the first gate controls the opening and closing of the first current channel of the first MOSFET structure through the gate voltage, and the second The gate is connected to the source, and the second gate controls the opening and closing of the second current channel of the second MOSFET structure through the source voltage.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

A trench type igbt power device

ActiveCN109755298BReduce reverse recovery chargeFast reverse recovery functionSemiconductor devicesReverse recoveryReverse current

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

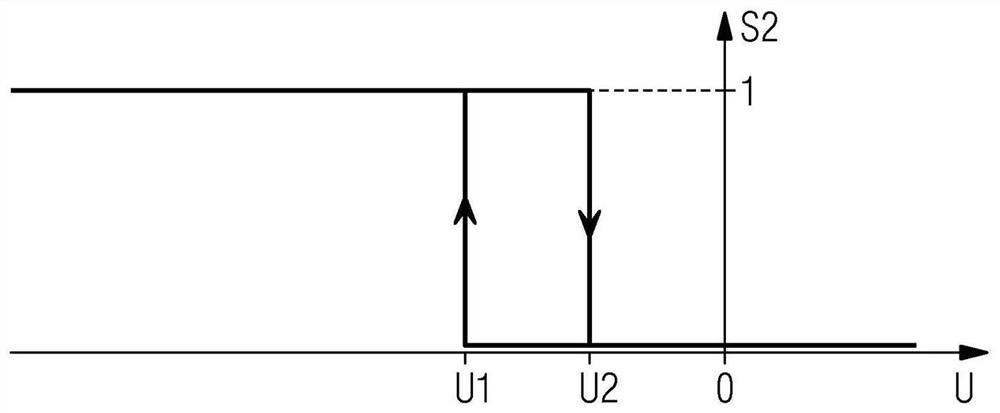

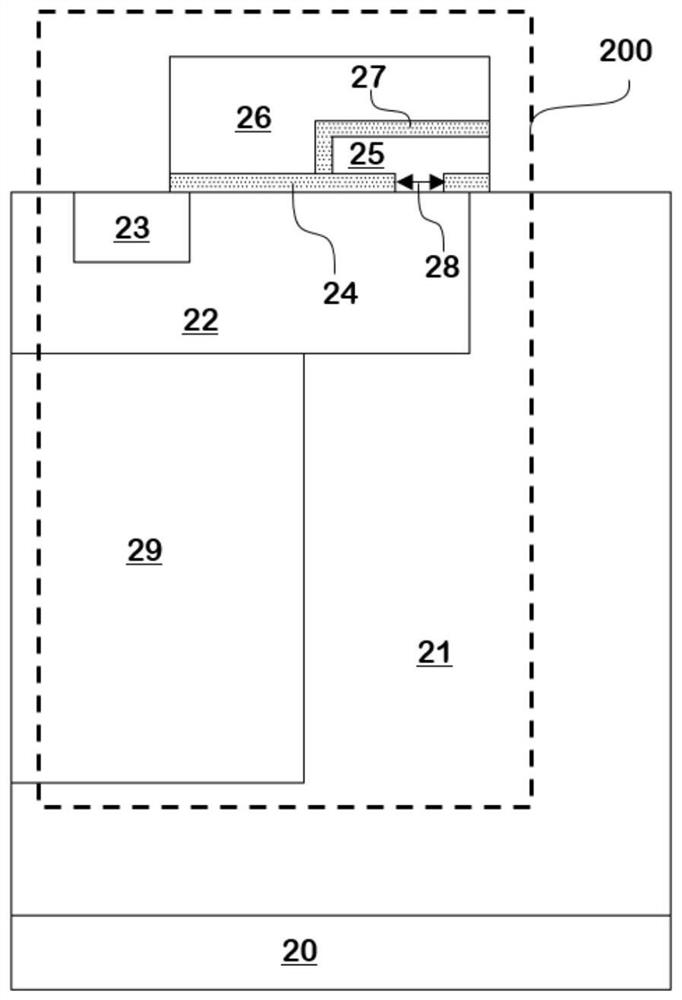

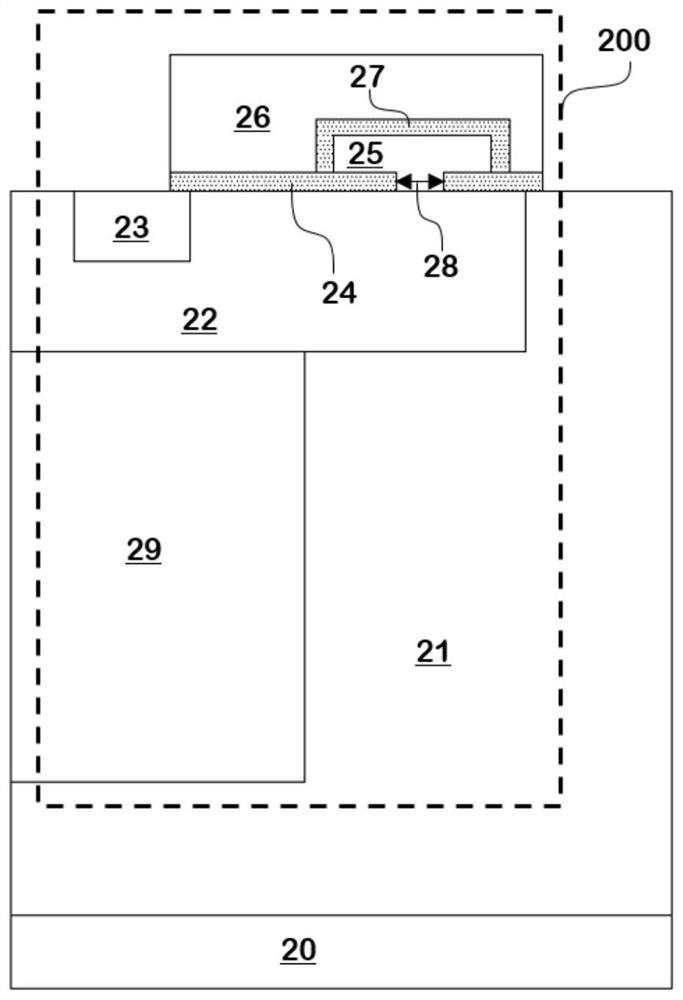

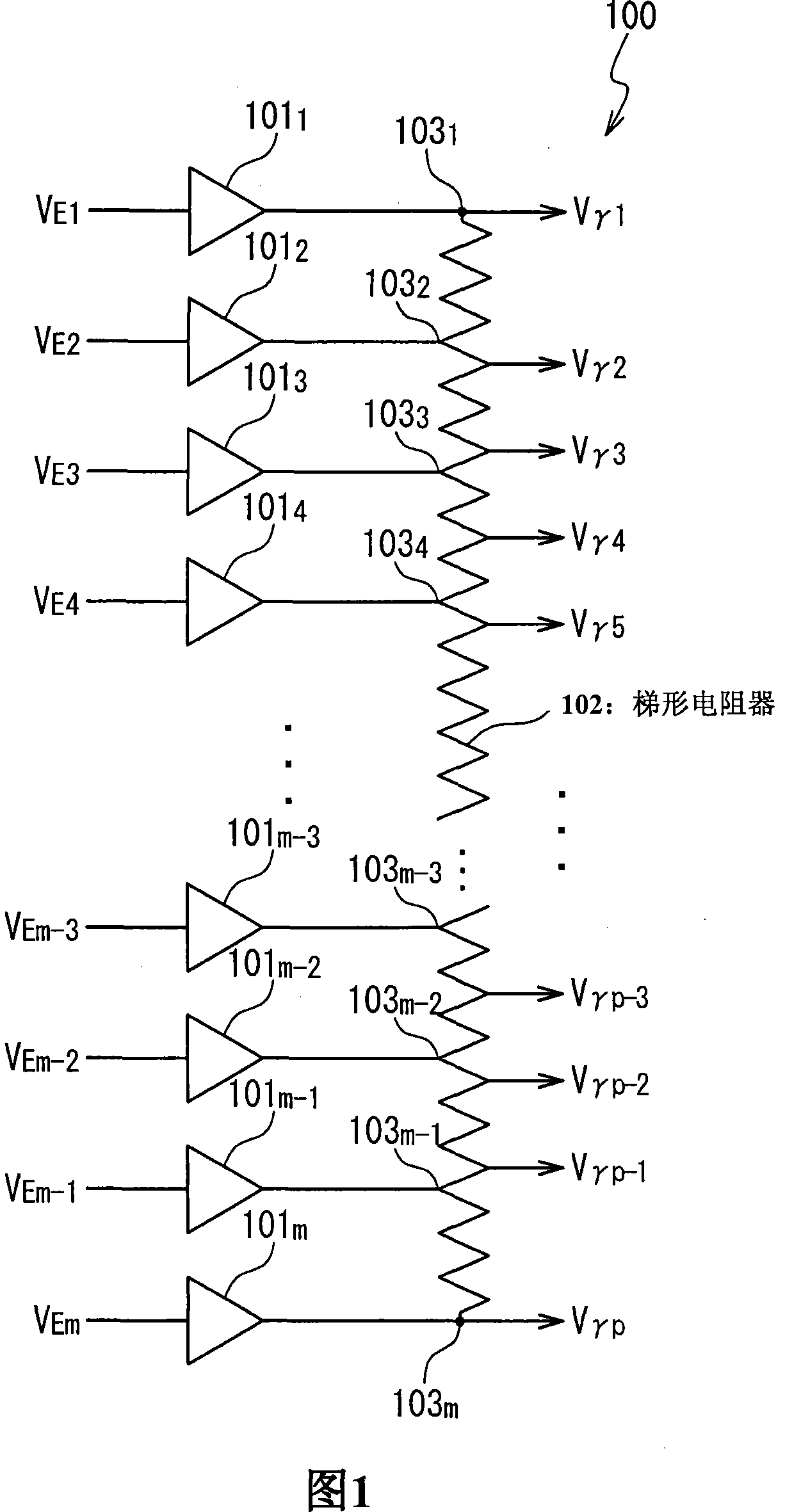

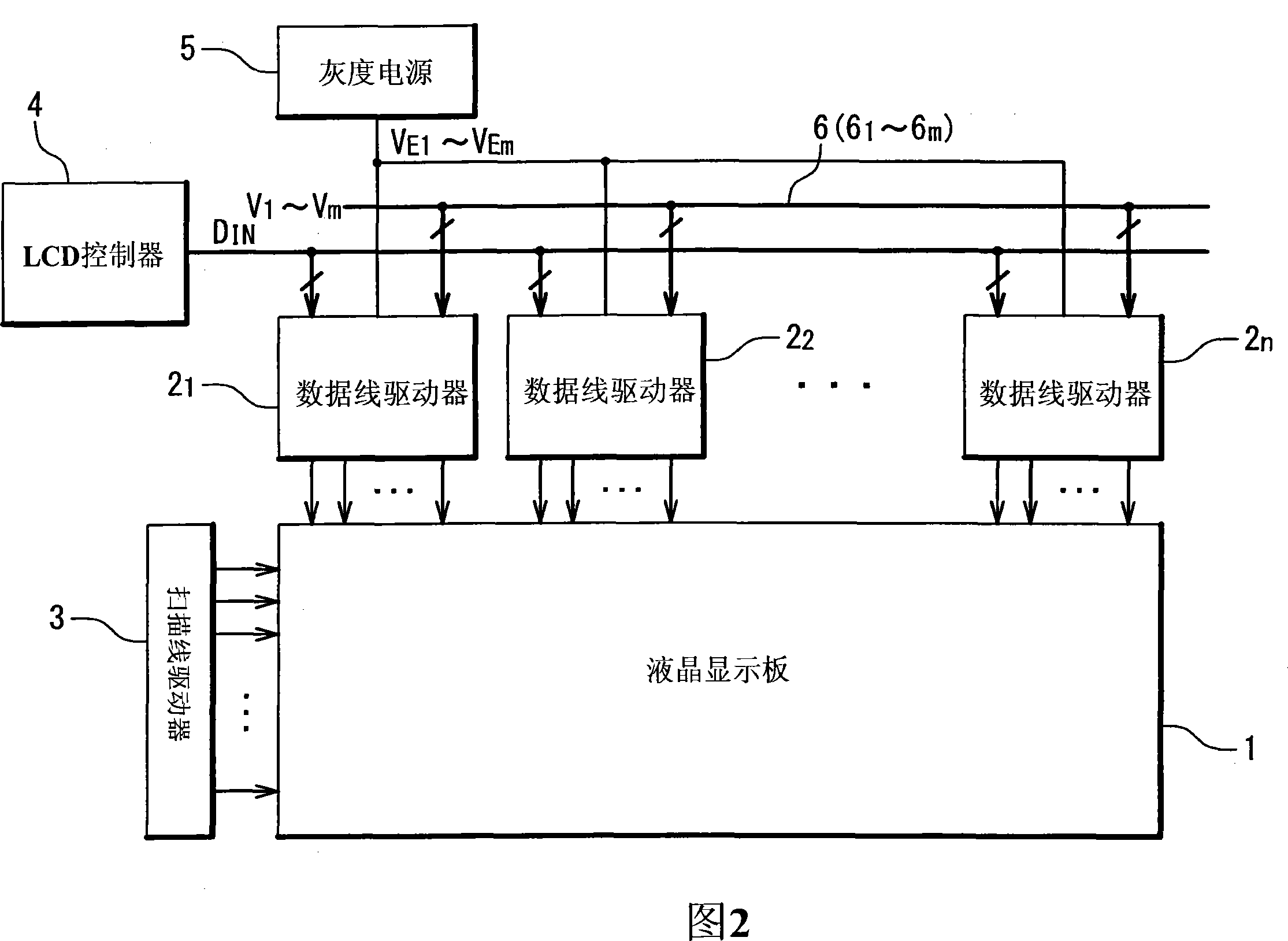

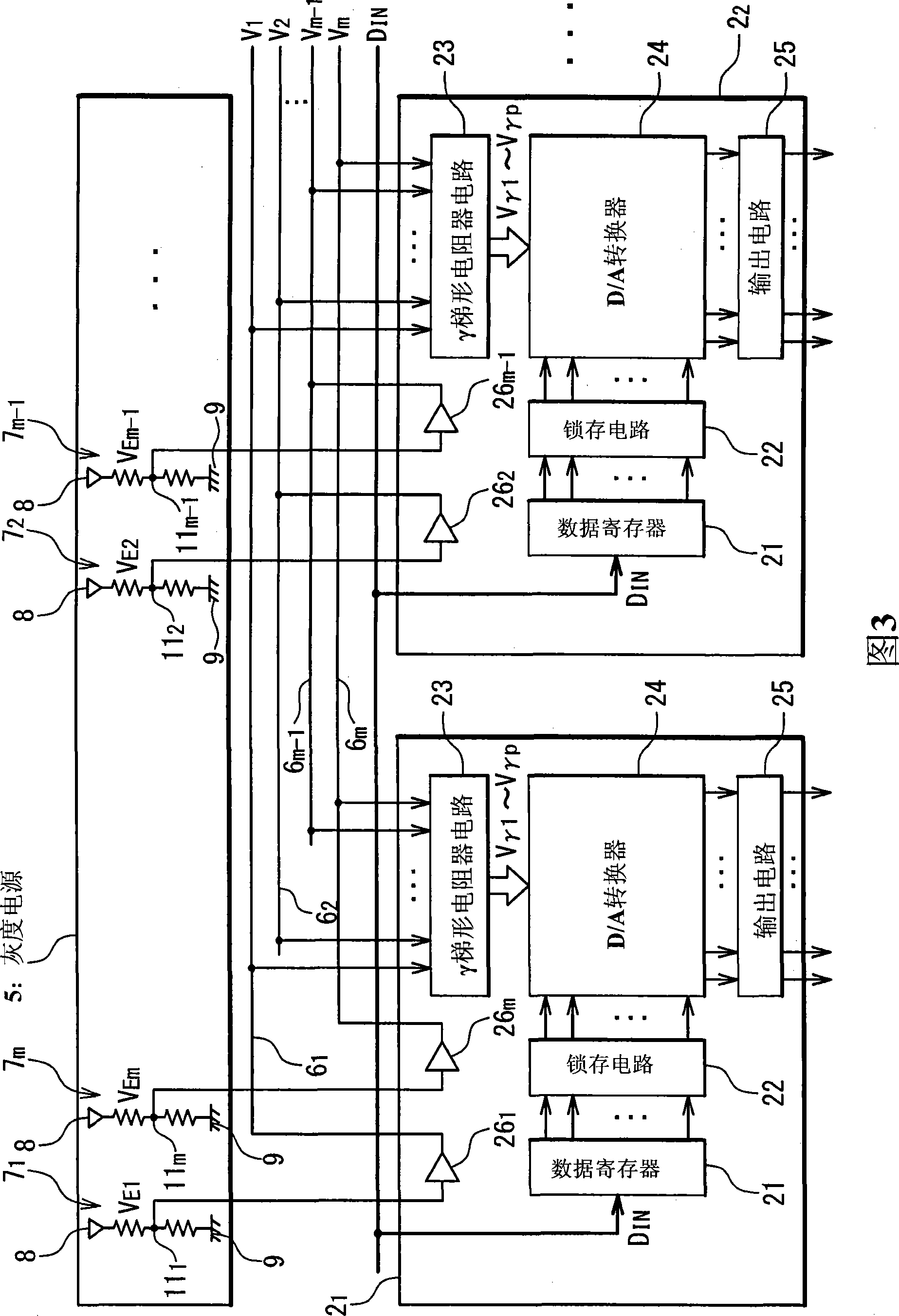

Display device and display panel driver using grayscale voltages which correspond to grayscales

InactiveCN101169915BImproved PSRR (Power Supply Rejection Ratio) characteristicsStable outputStatic indicating devicesApparatus without intermediate ac conversionDriver circuitAudio power amplifier

A display device includes: a display panel (1); at least one data-line driver (2); and a plurality of operational amplifiers (26 1 to 26 m-1). The plurality of operational amplifiers is integrated in any of the at least one data-line driver and generates a plurality of reference voltages, respectively. The data-line driver includes: a driving circuit, a maximum grayscale voltage wiring, and a resistance ladder. The driving circuit drives the display panel. The maximum grayscale voltage wiring receives a maximum reference voltage in the plurality of reference voltages from a first operational amplifier in the plurality of operational amplifiers and supplies the maximum reference voltage to the driving circuit as a maximum grayscale voltage. The resistance ladder receives the plurality of reference voltages except the maximum reference voltage from the plurality of operational amplifiers except the first operational amplifier, respectively, and generates a plurality of grayscale voltages lower than the maximum grayscale voltage. The driving circuit (24, 25) drives data lines of the display panel (1) by using the maximum grayscale voltage and the plurality of grayscale voltages. The maximum grayscale voltage wiring (27) is isolated from the resistance ladder (28).

Owner:RENESAS ELECTRONICS CORP