Patents

Literature

78results about How to "Reduced resistance difference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

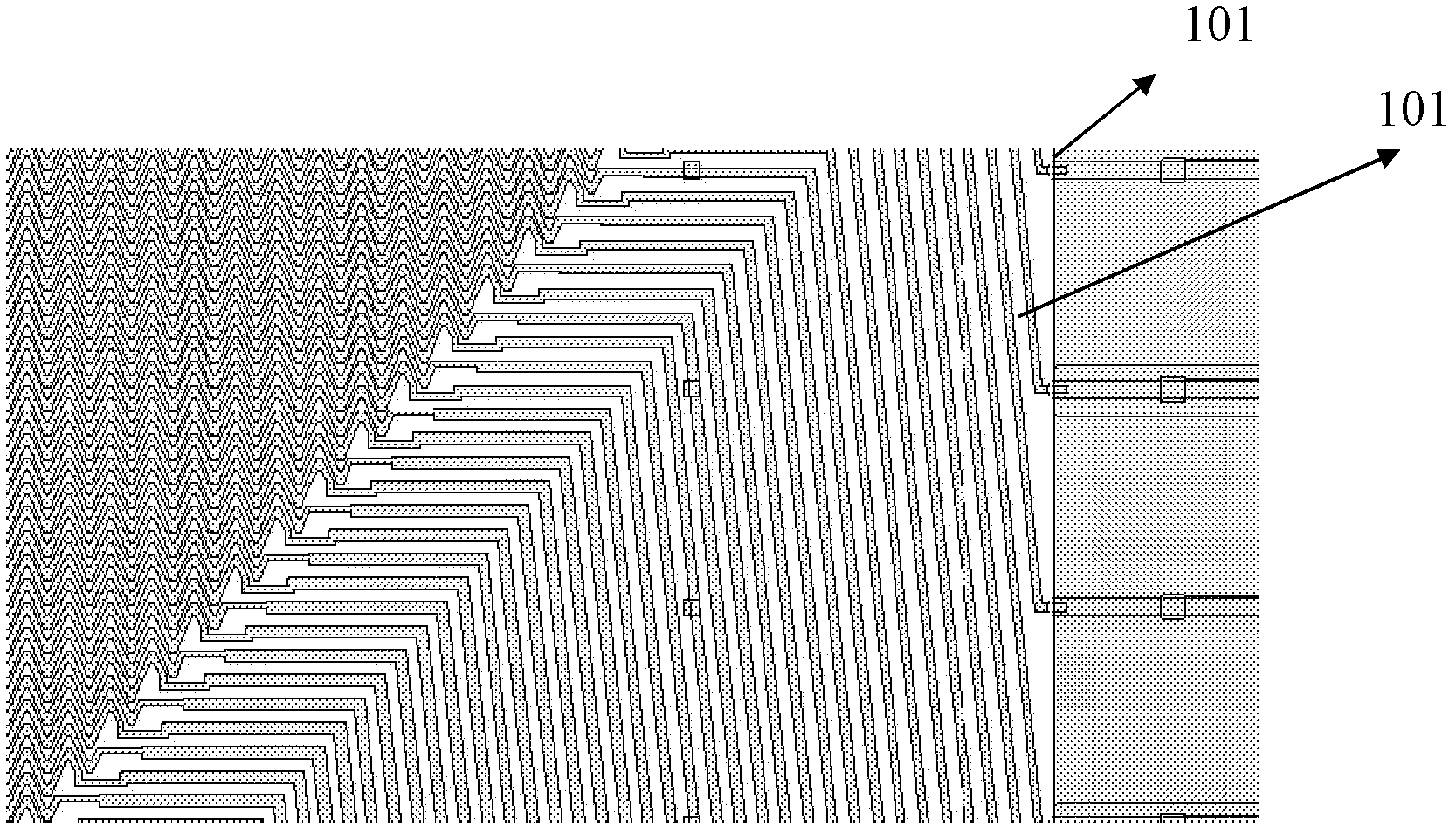

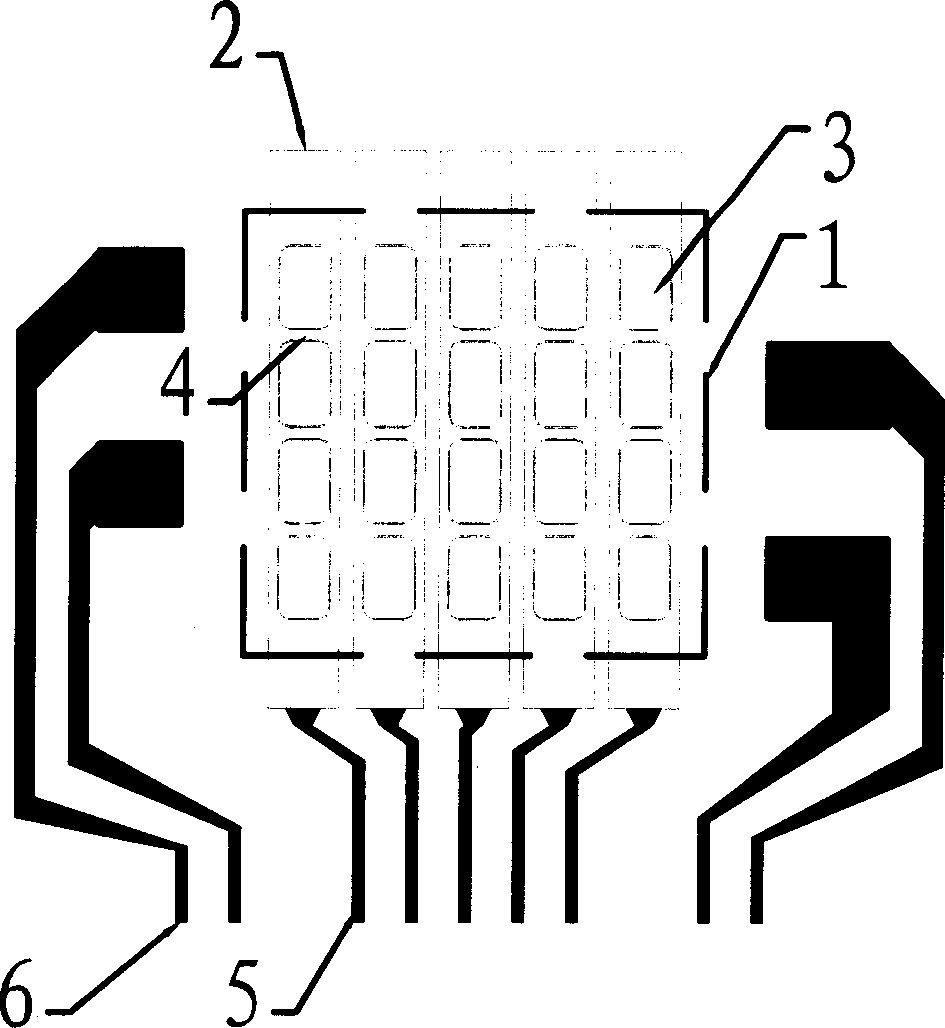

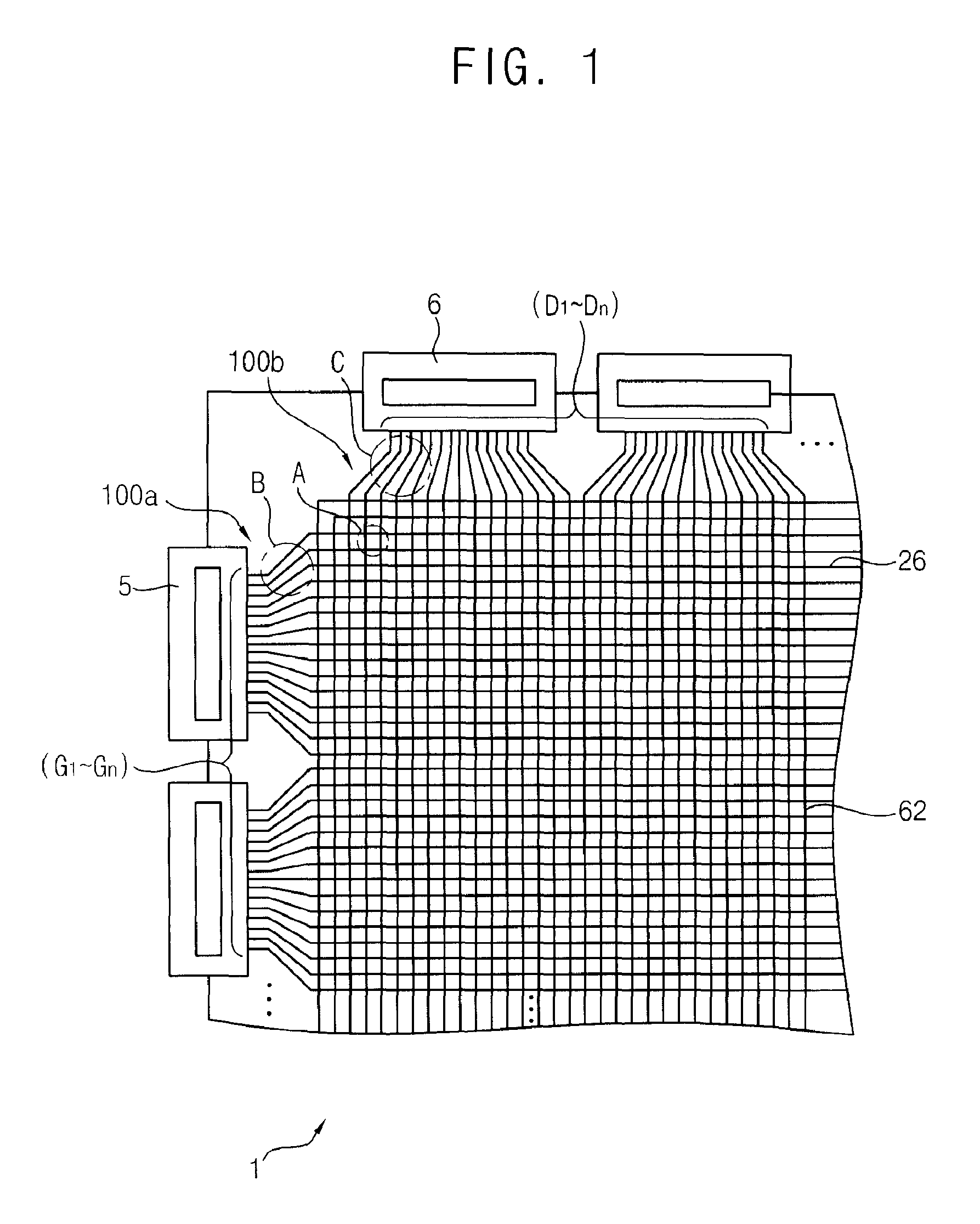

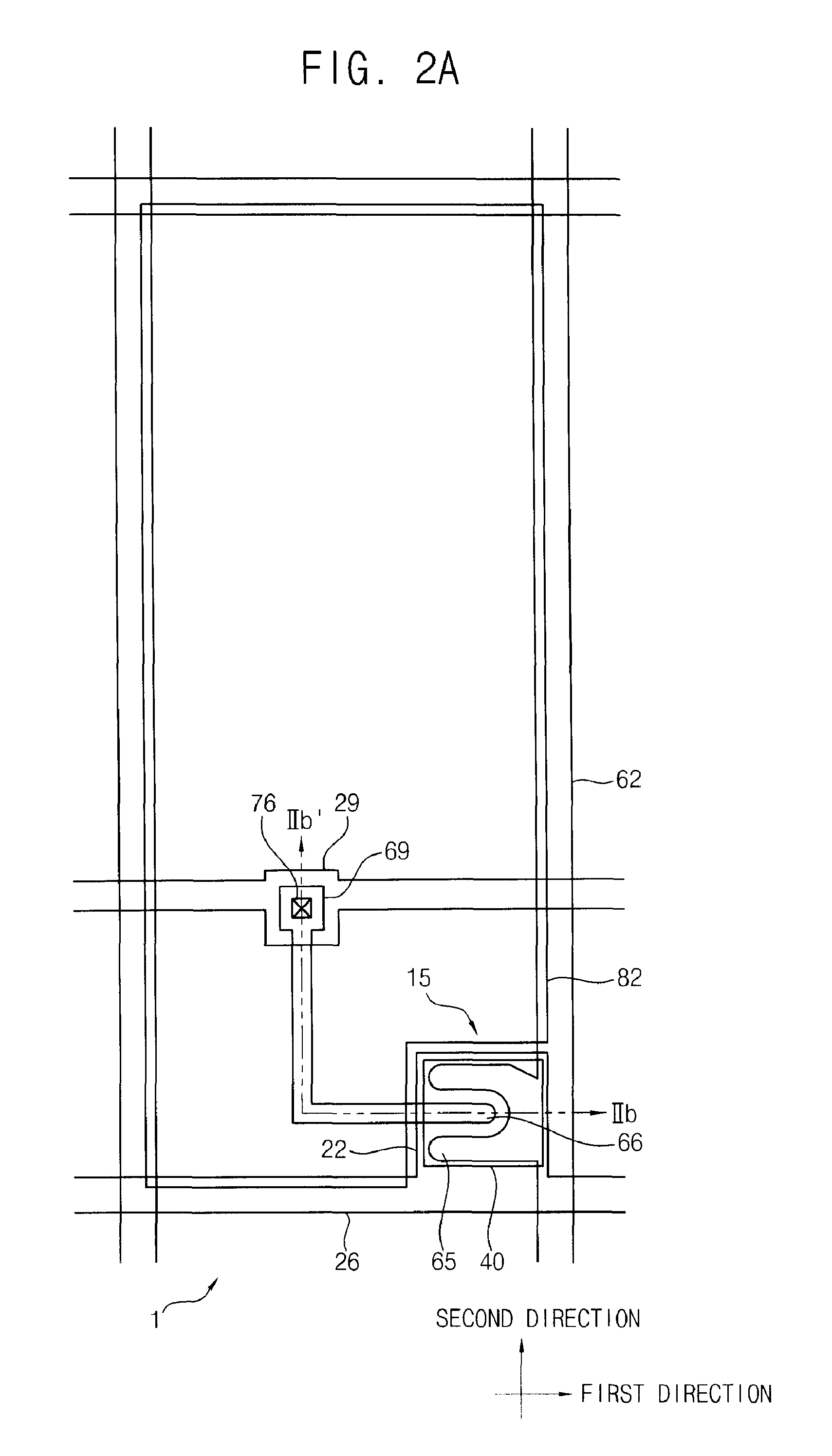

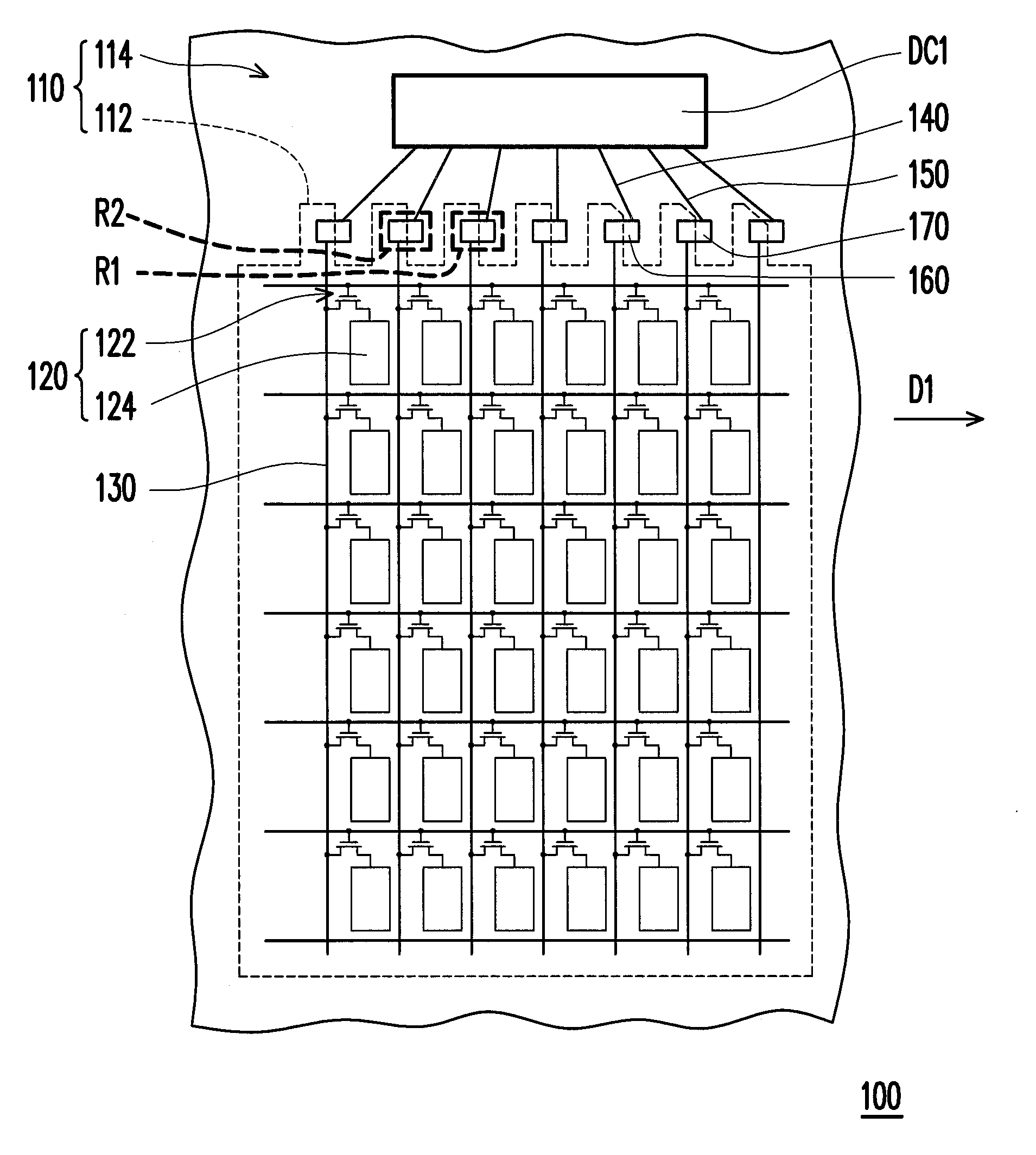

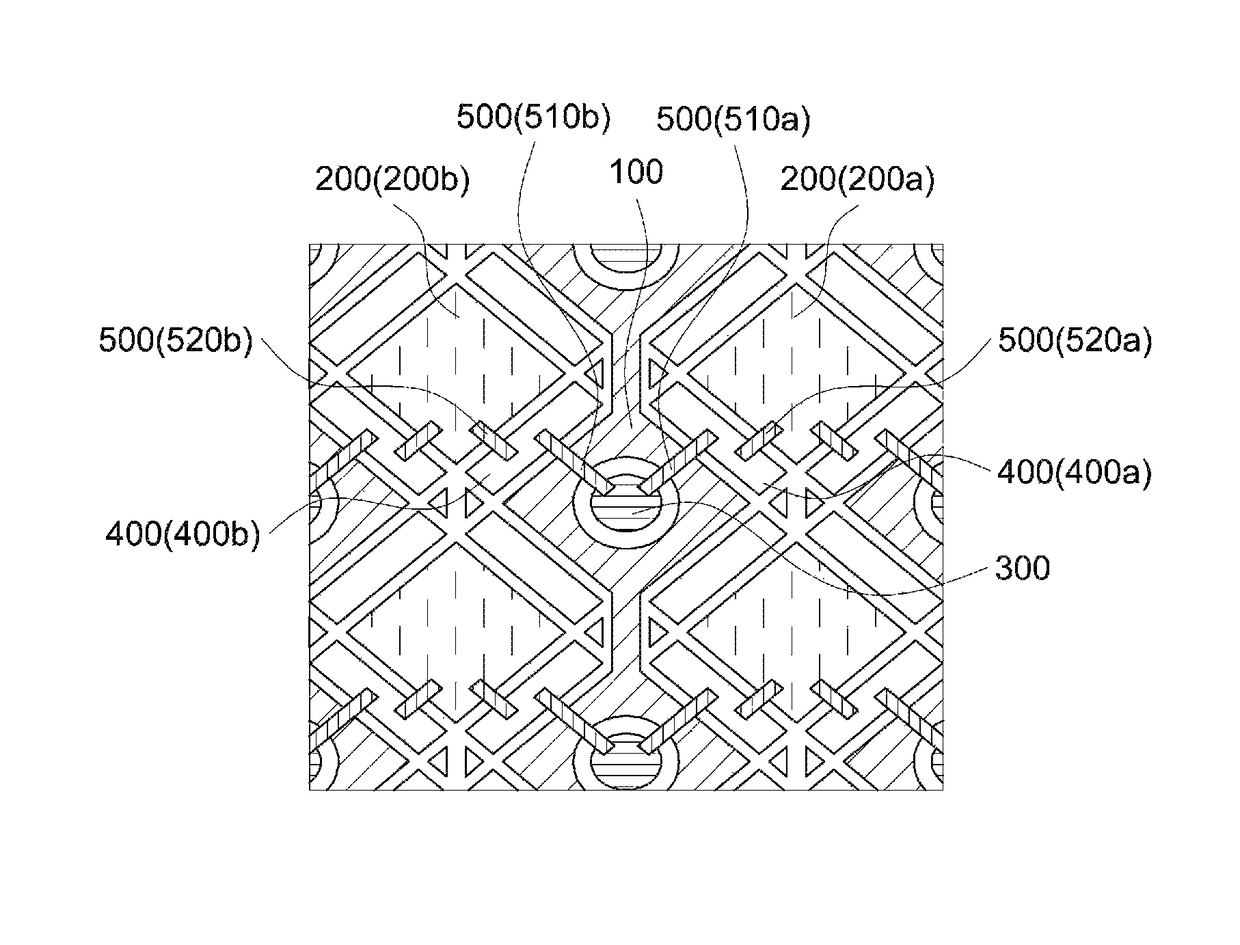

Electro-luminescence display apparatus

ActiveUS20170125506A1Improve uniformityReduced resistance differenceStatic indicating devicesSolid-state devicesCommon lineElectroluminescence

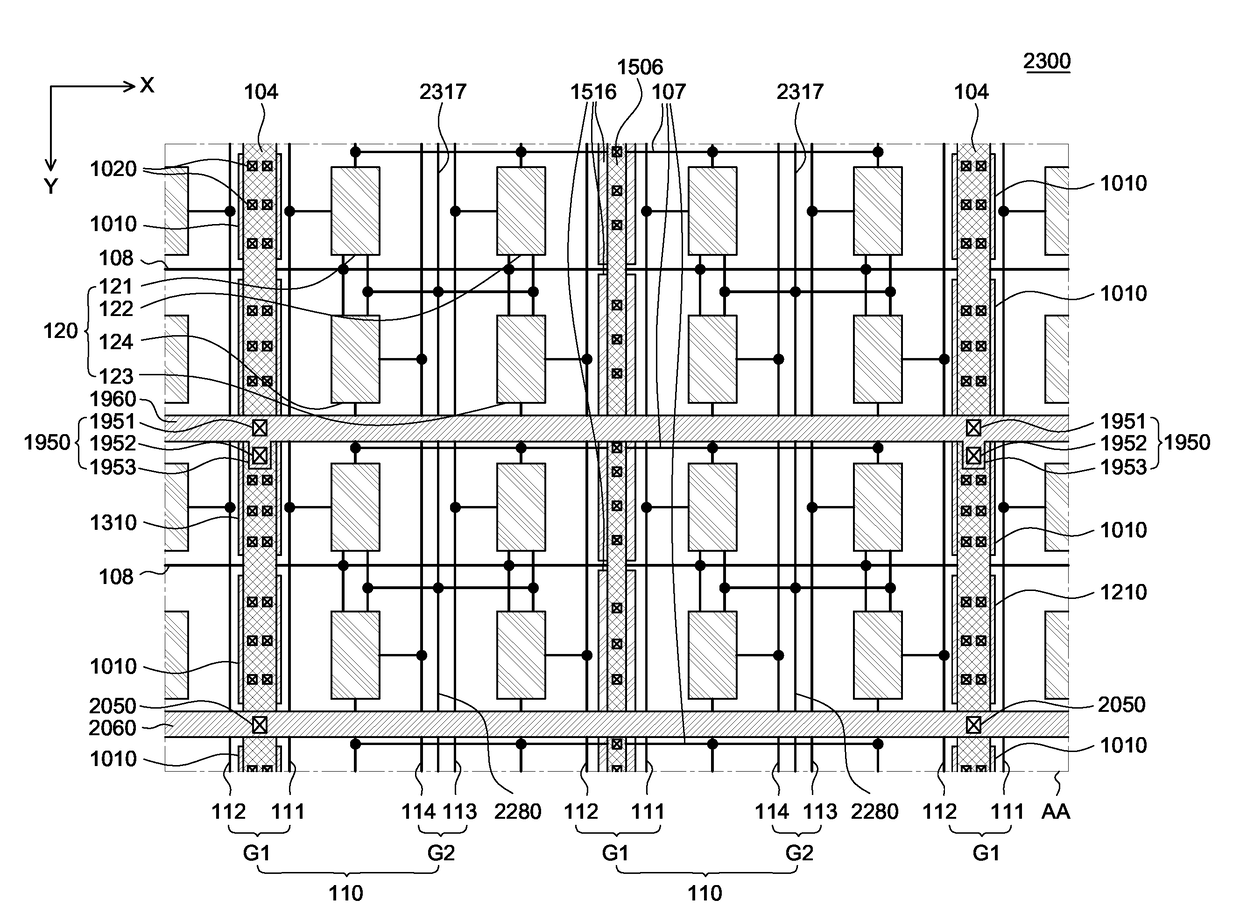

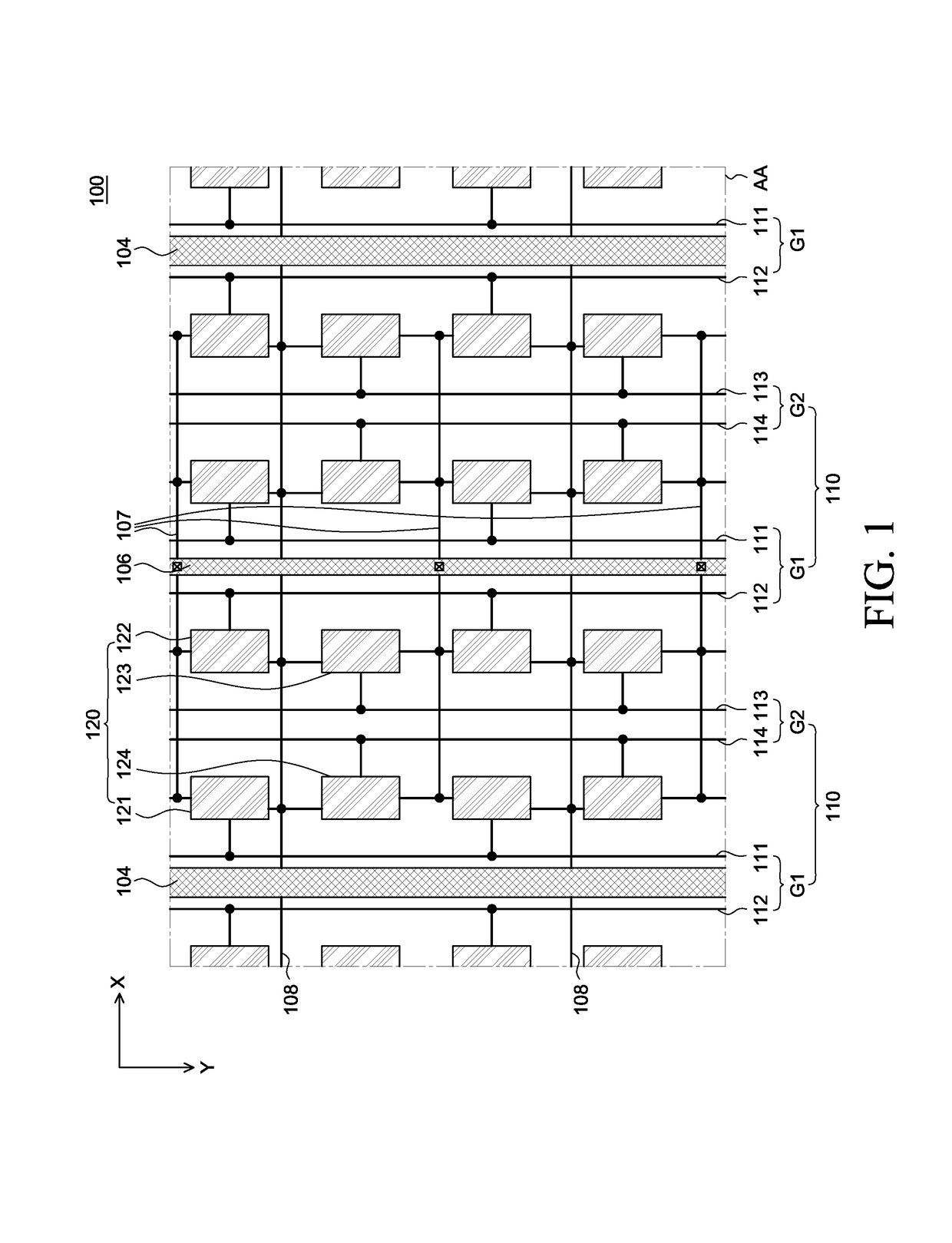

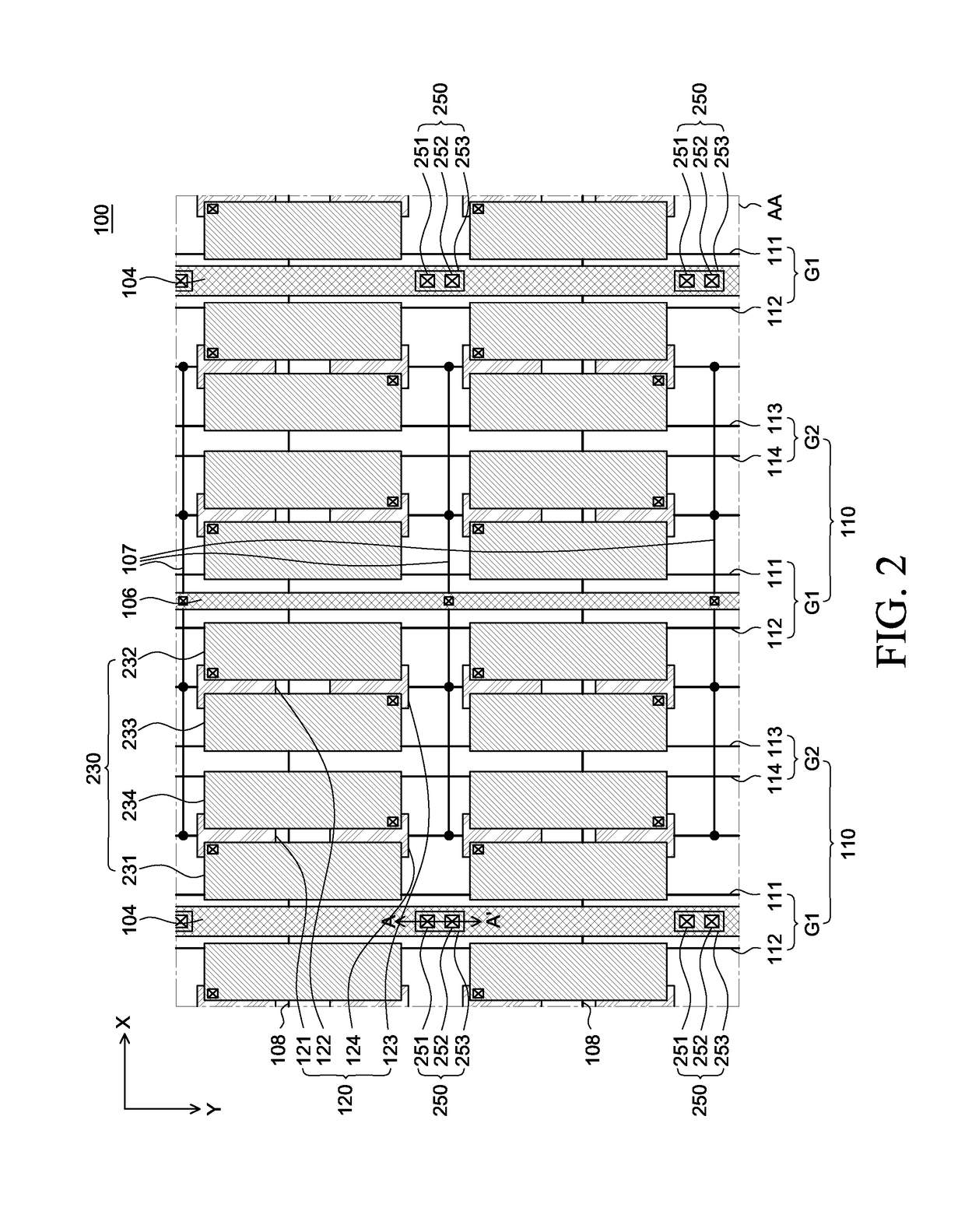

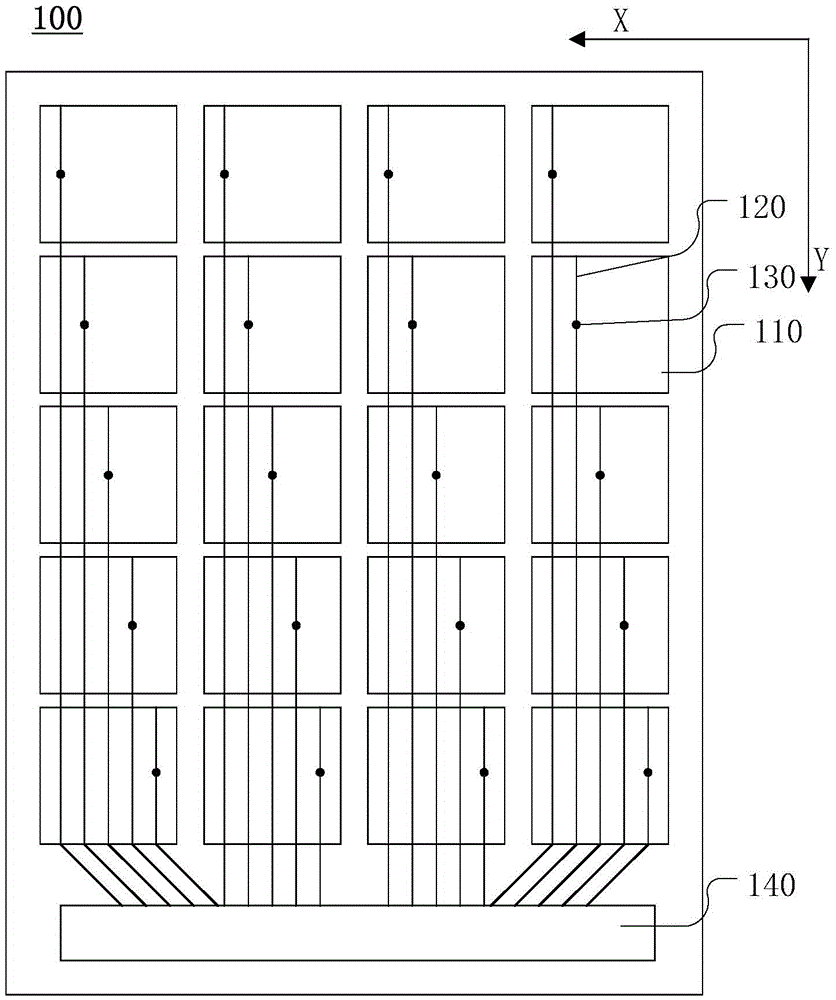

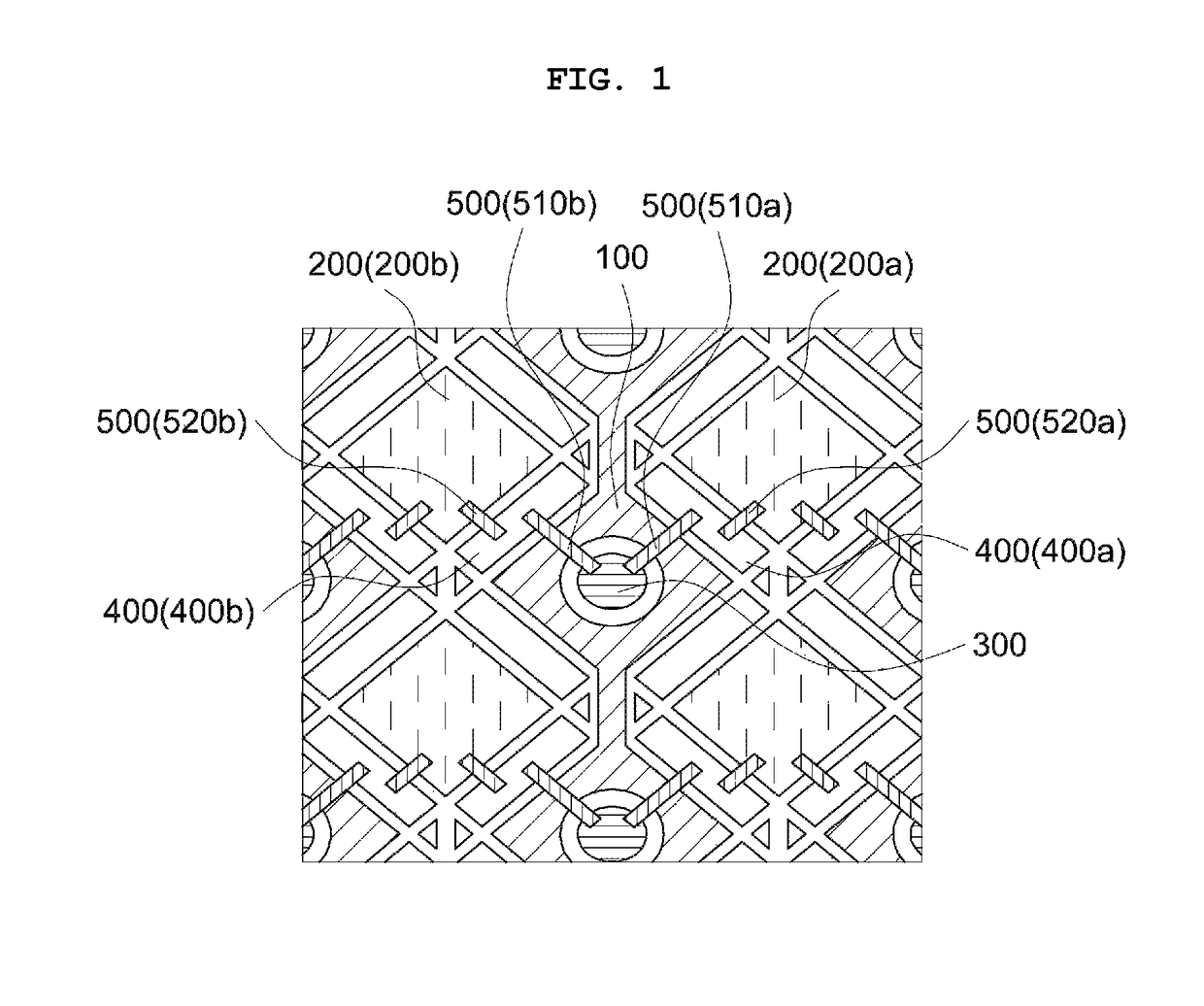

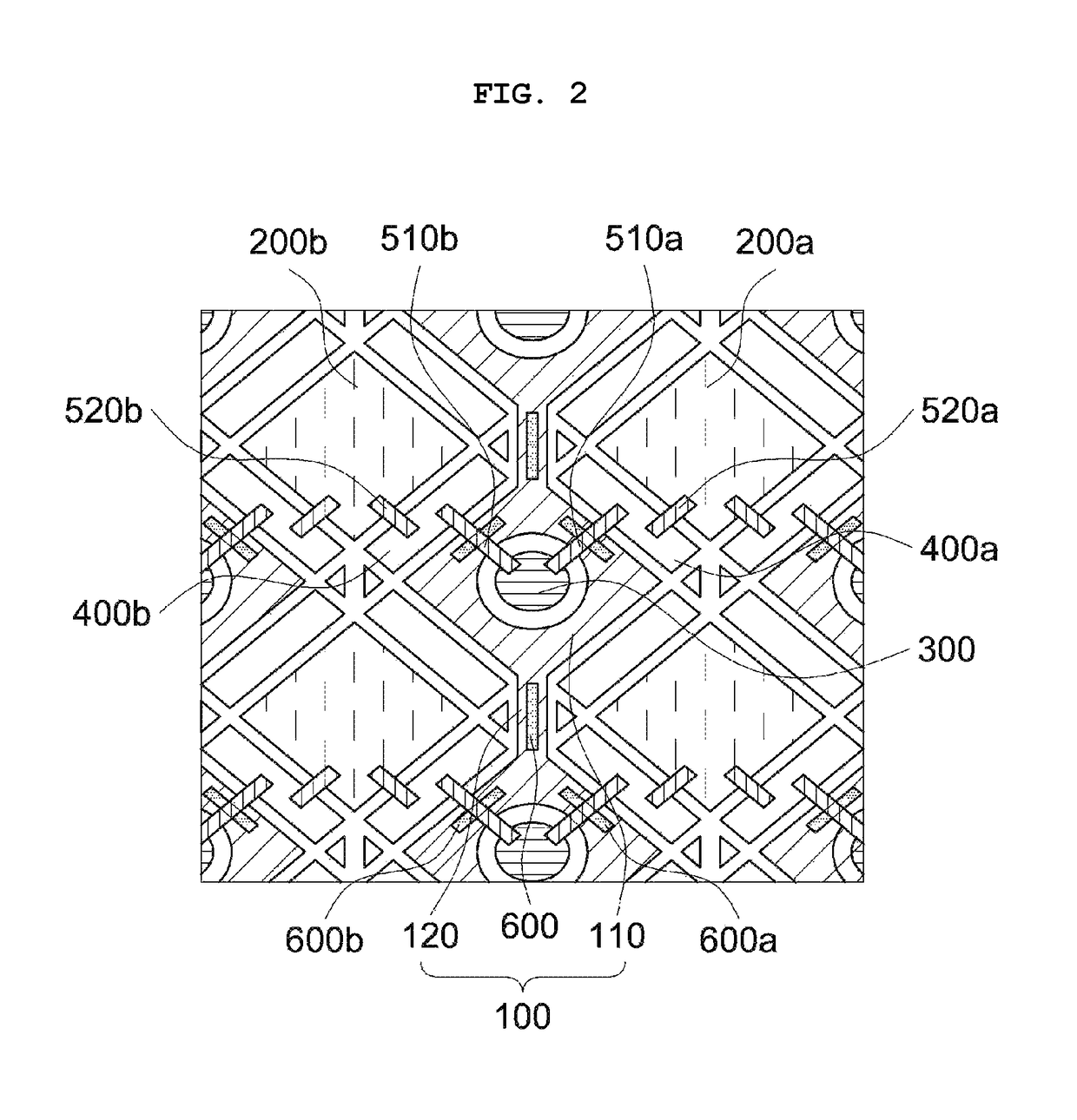

Described herein is an electroluminescence display apparatus comprising: at least one quad-type pixel circuit unit comprising a plurality of sub-pixel circuit units; at least one gate line disposed between the plurality of sub-pixel circuit units and extending along a first direction; at least one first data line group comprising a first pair of data lines disposed at both sides of the at least one pixel circuit unit and extending along a second direction; at least one second data line group comprising a second pair of data lines disposed between the sub-pixel circuit units and extending along the second direction; and at least one common line and at least one anode line disposed between the first pair of data lines of the first data line group and disposed along the first direction, the at least one gate line crosses with the at least one first data line group and the at least one second data line group.

Owner:LG DISPLAY CO LTD

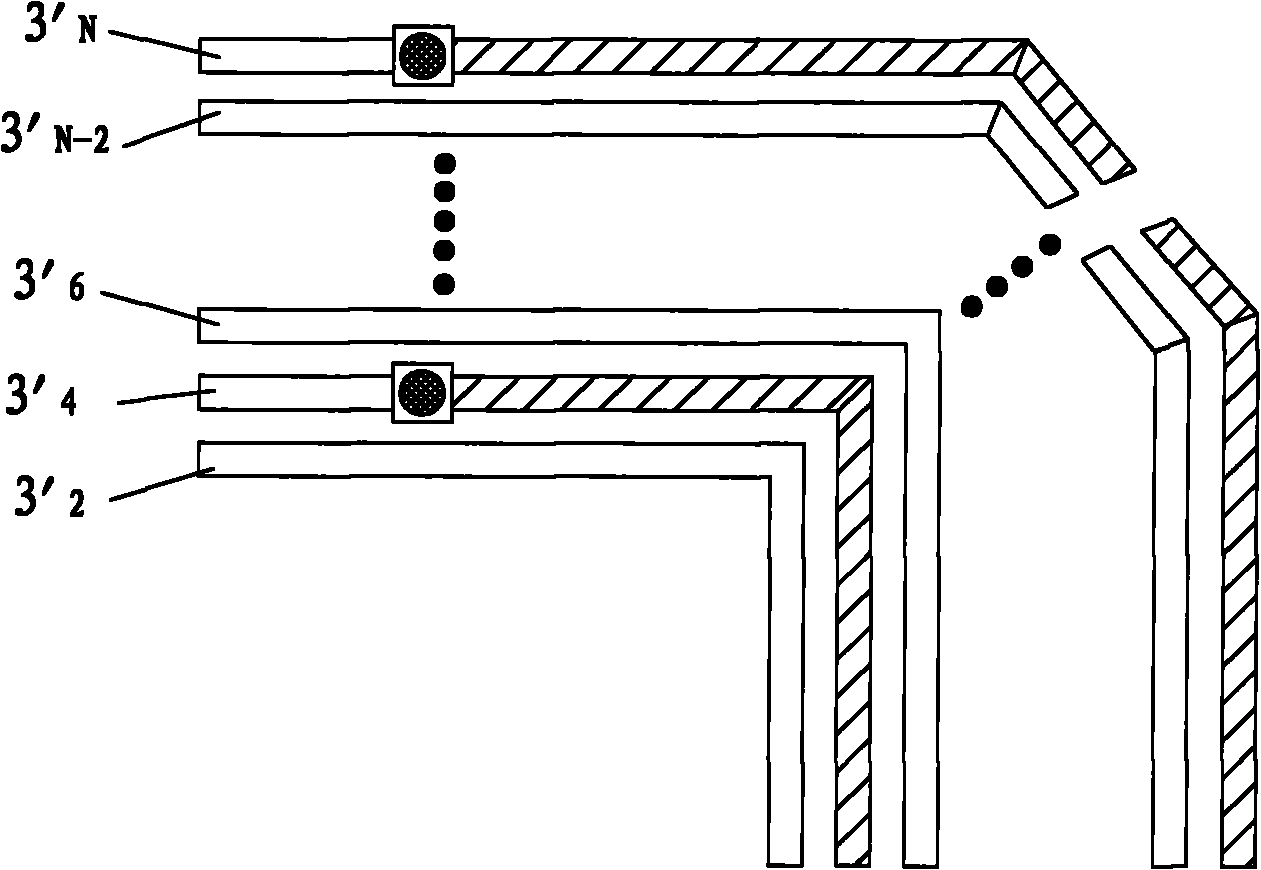

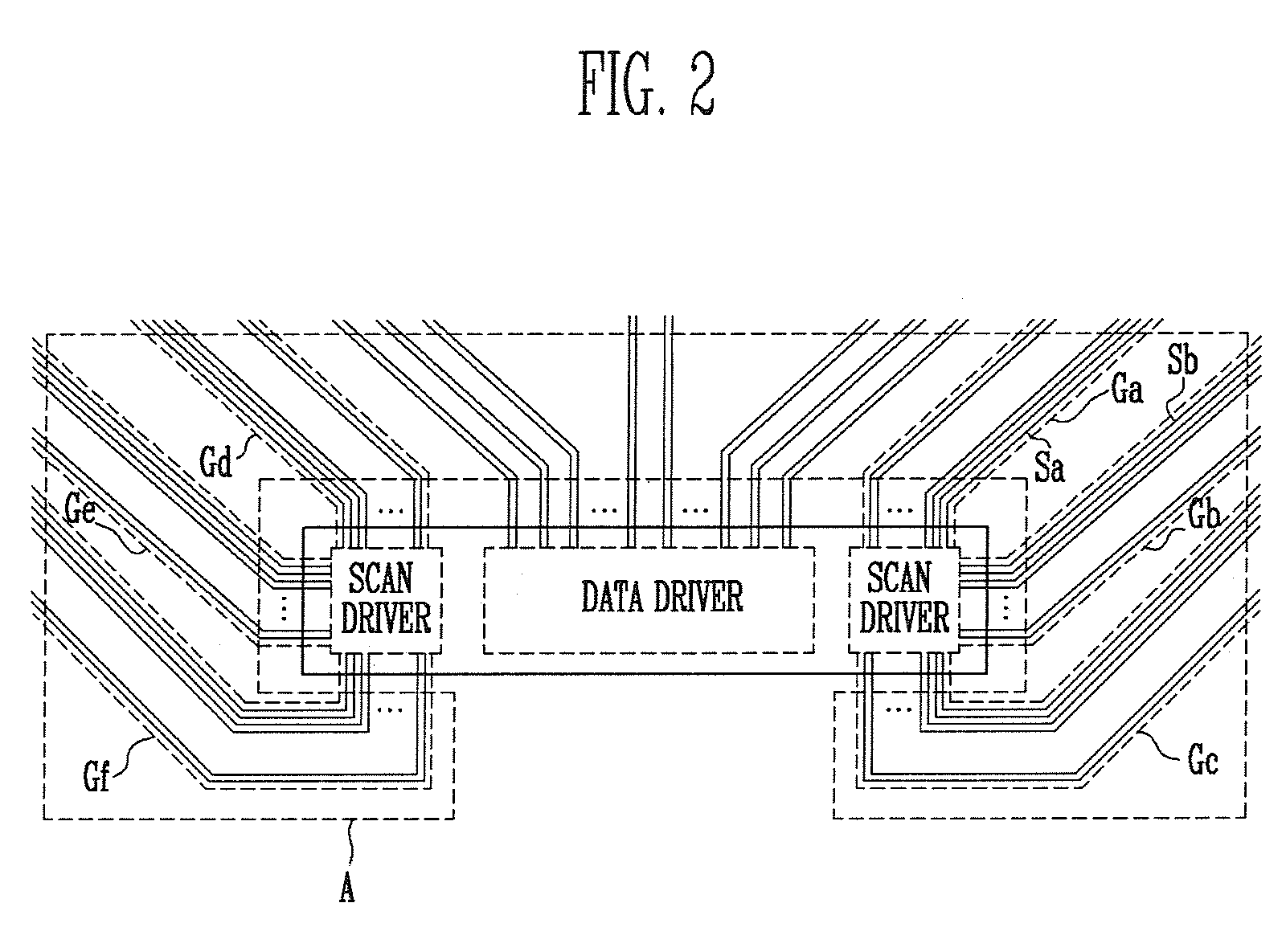

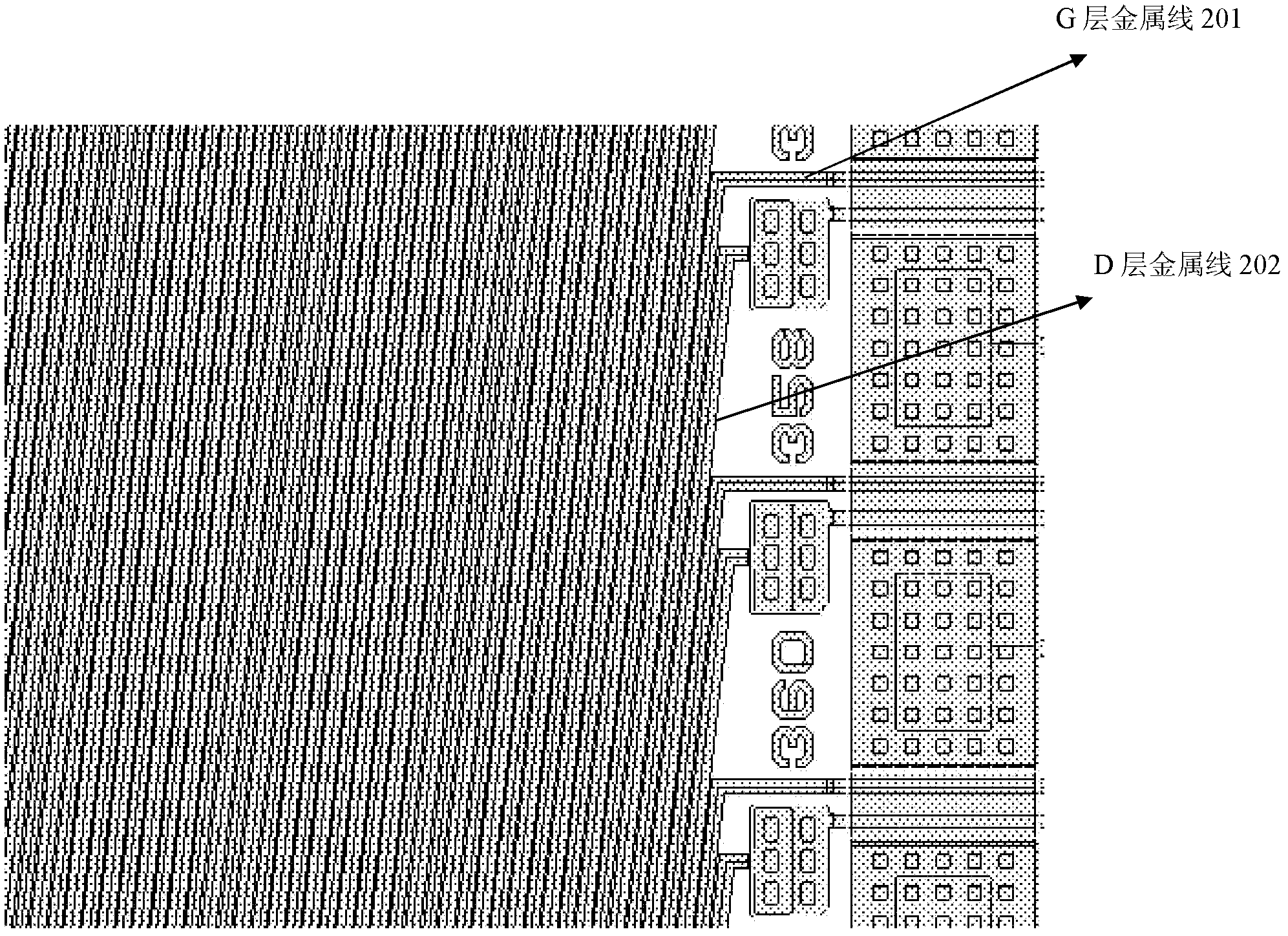

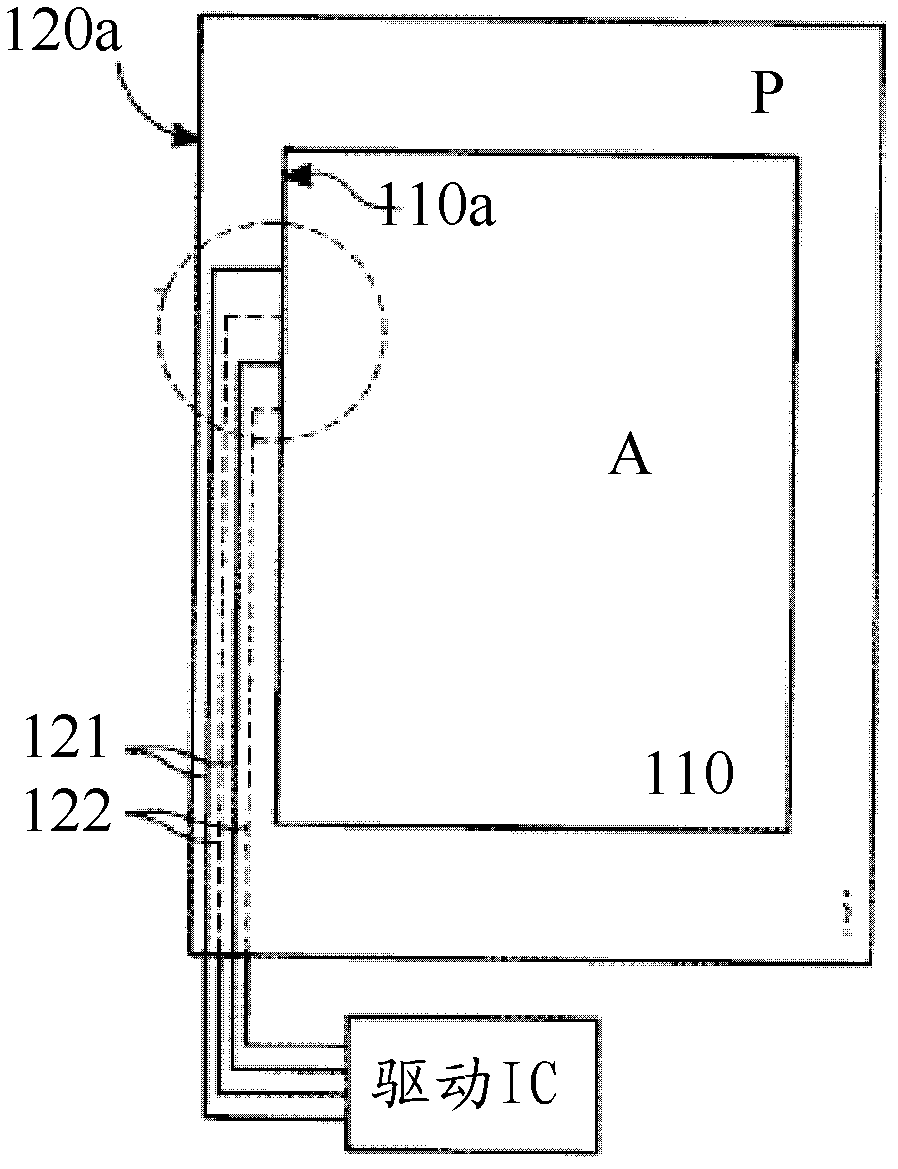

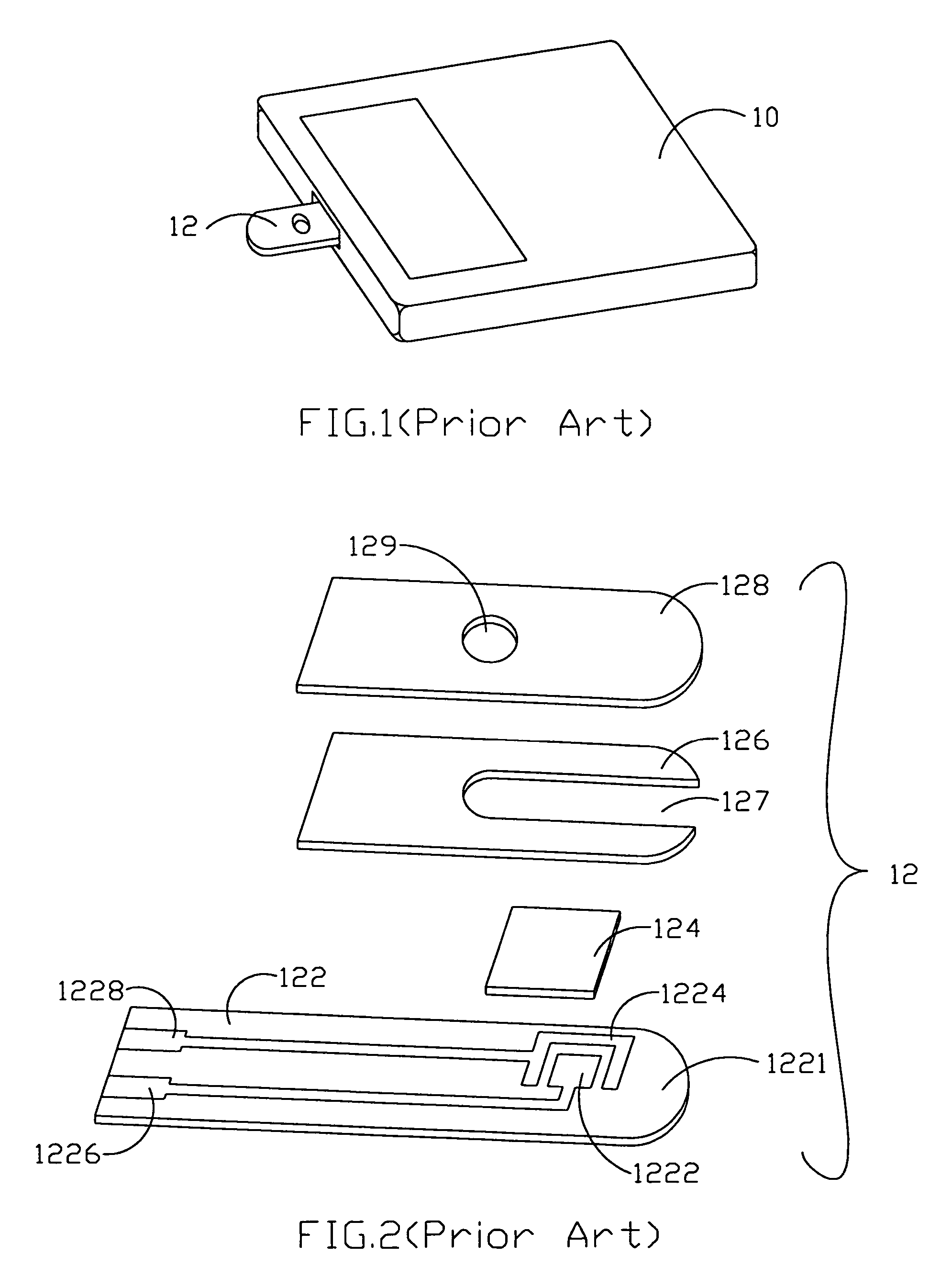

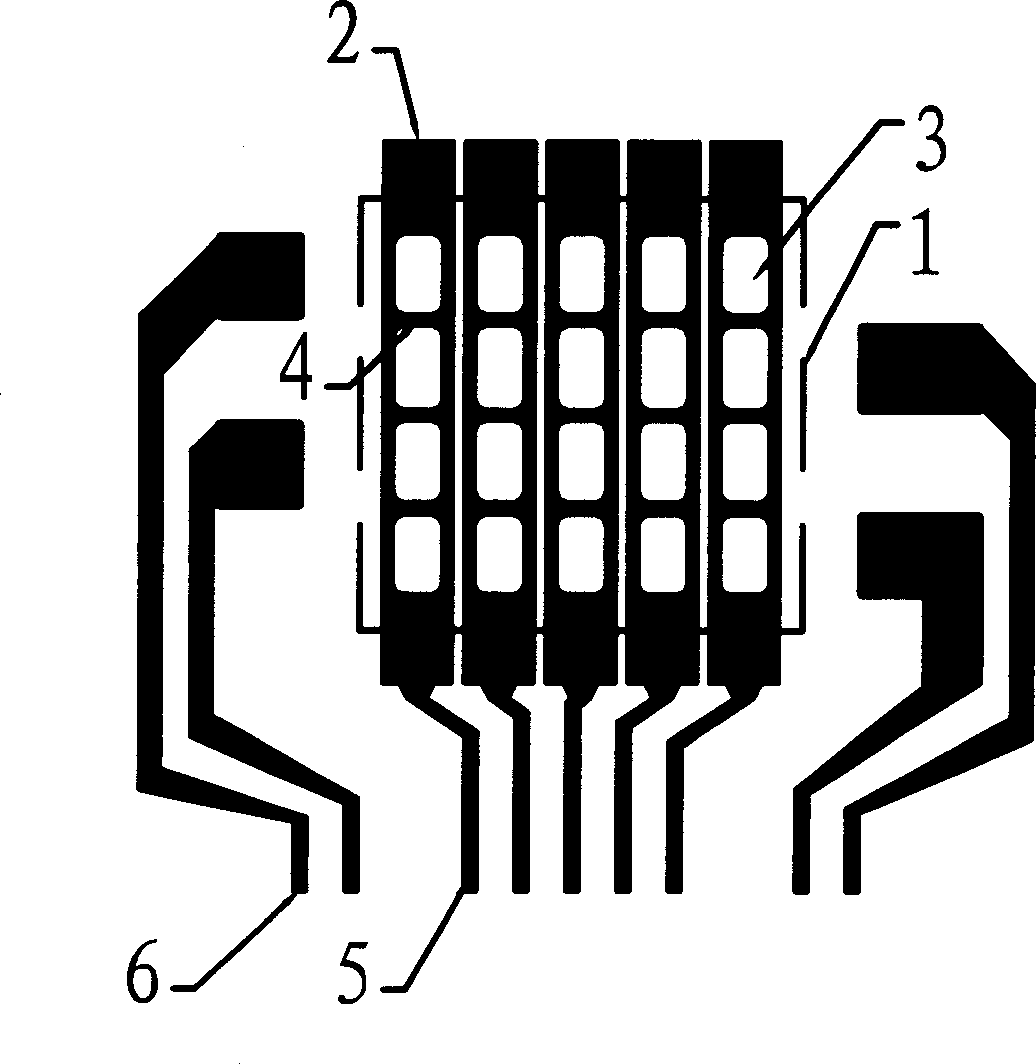

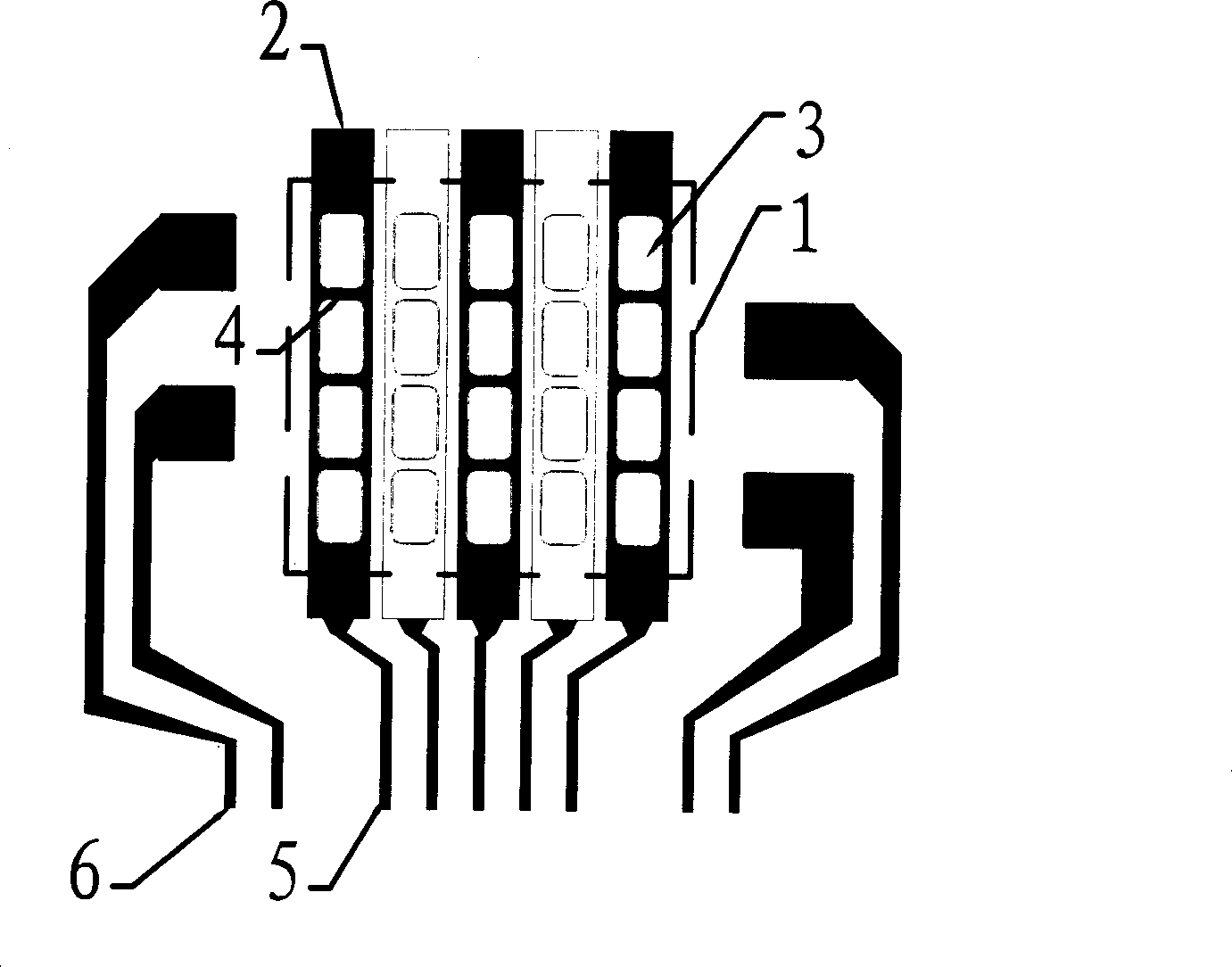

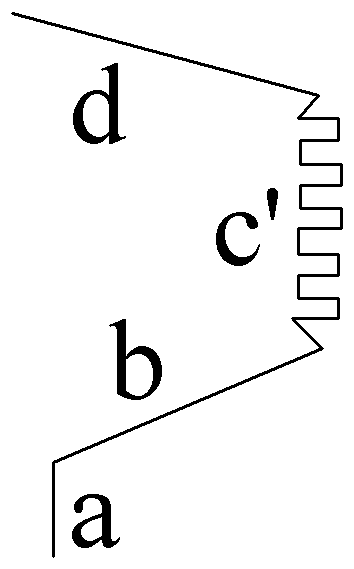

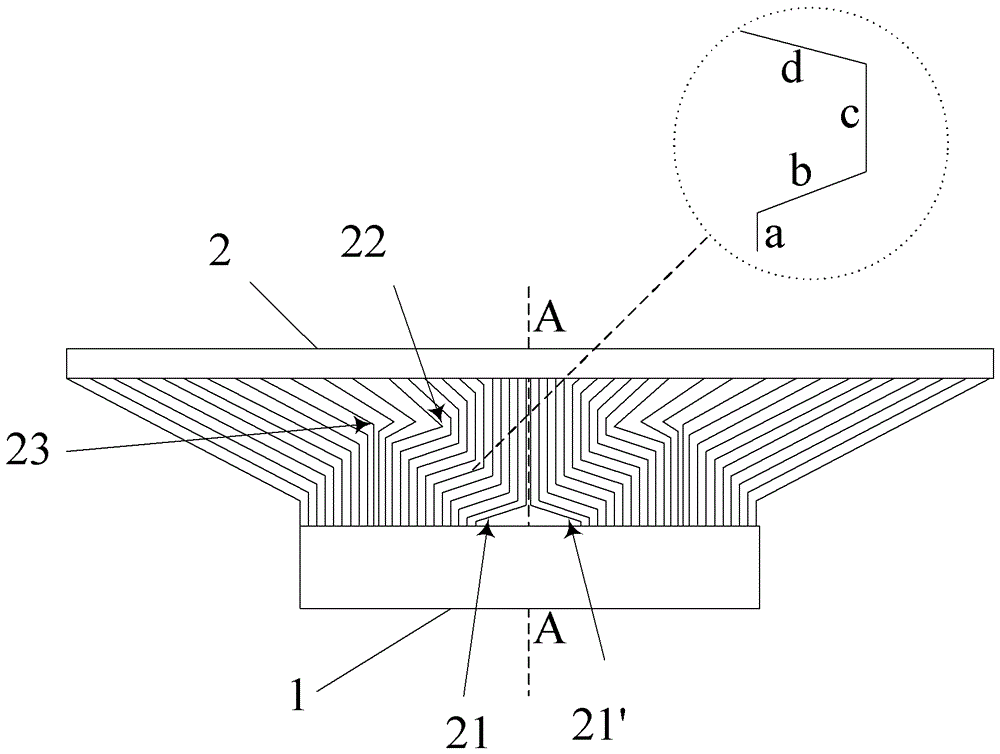

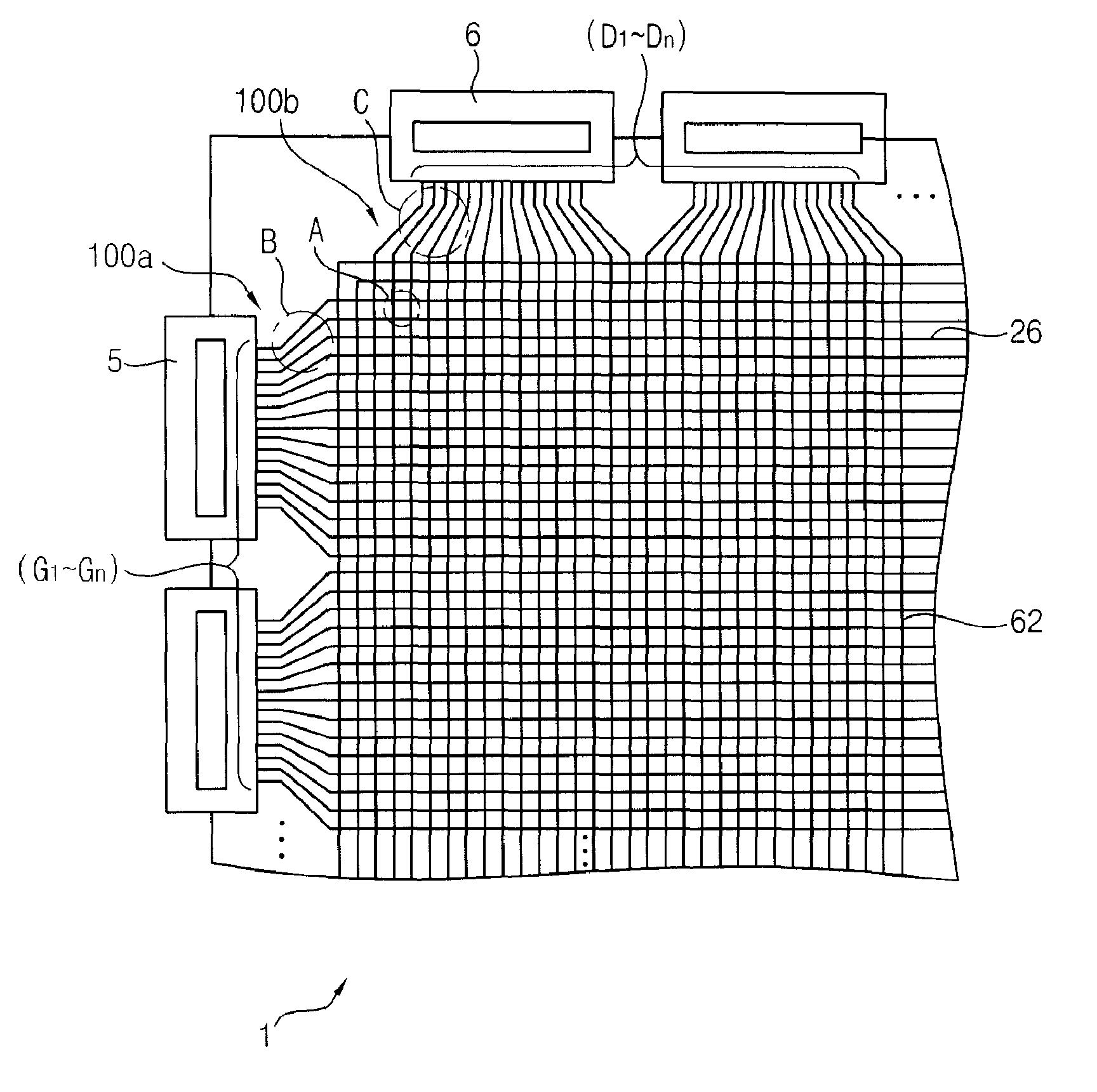

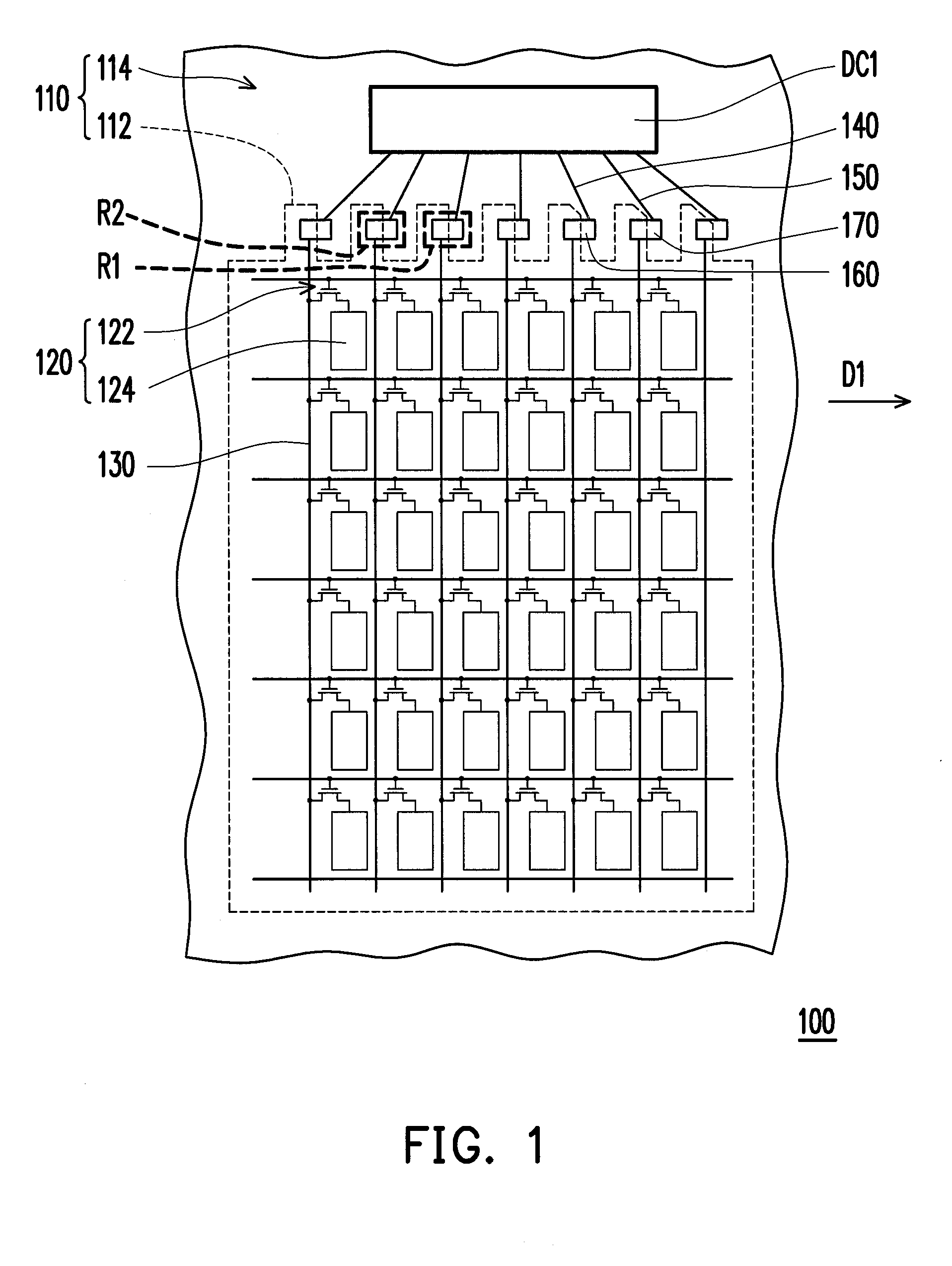

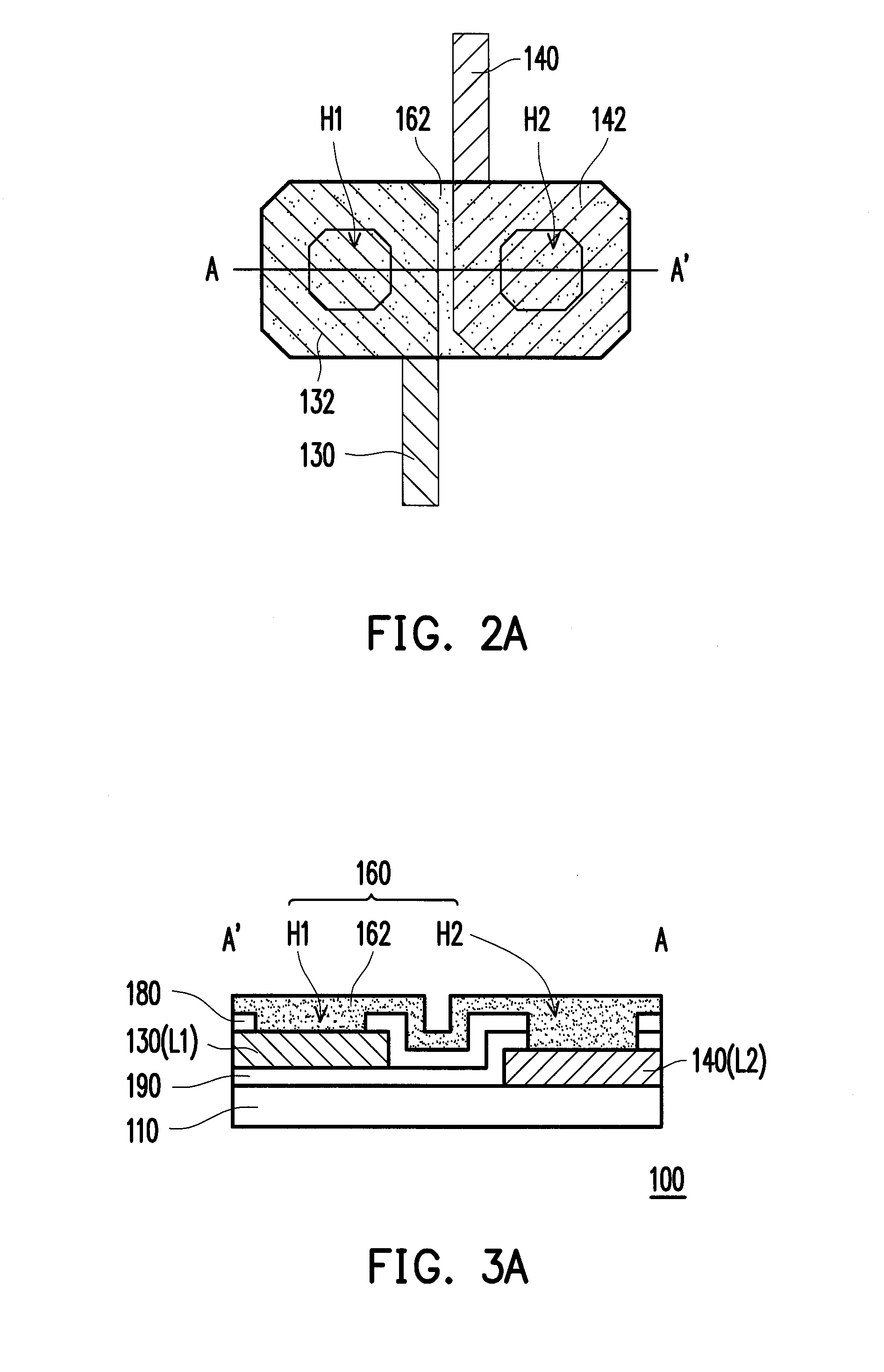

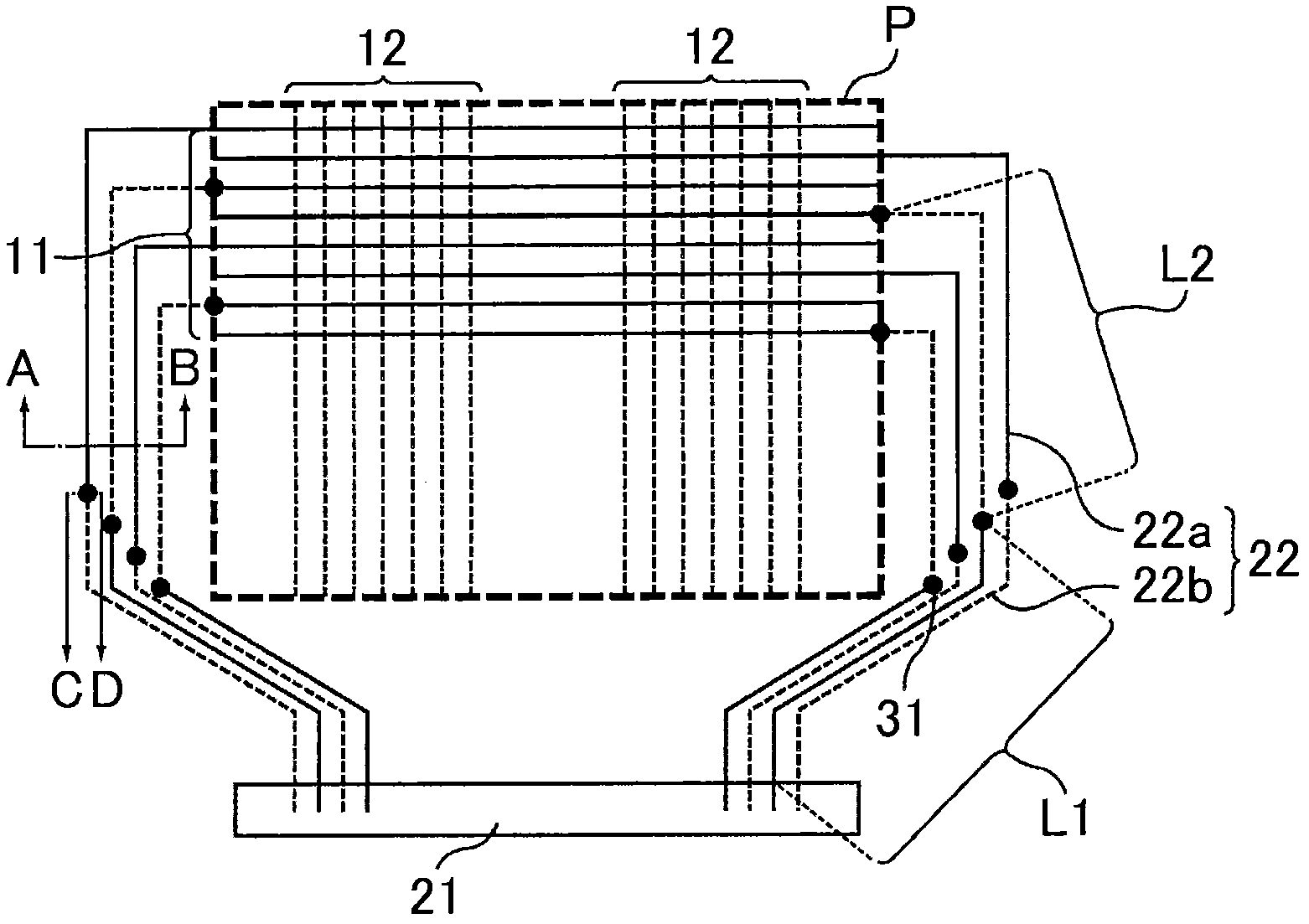

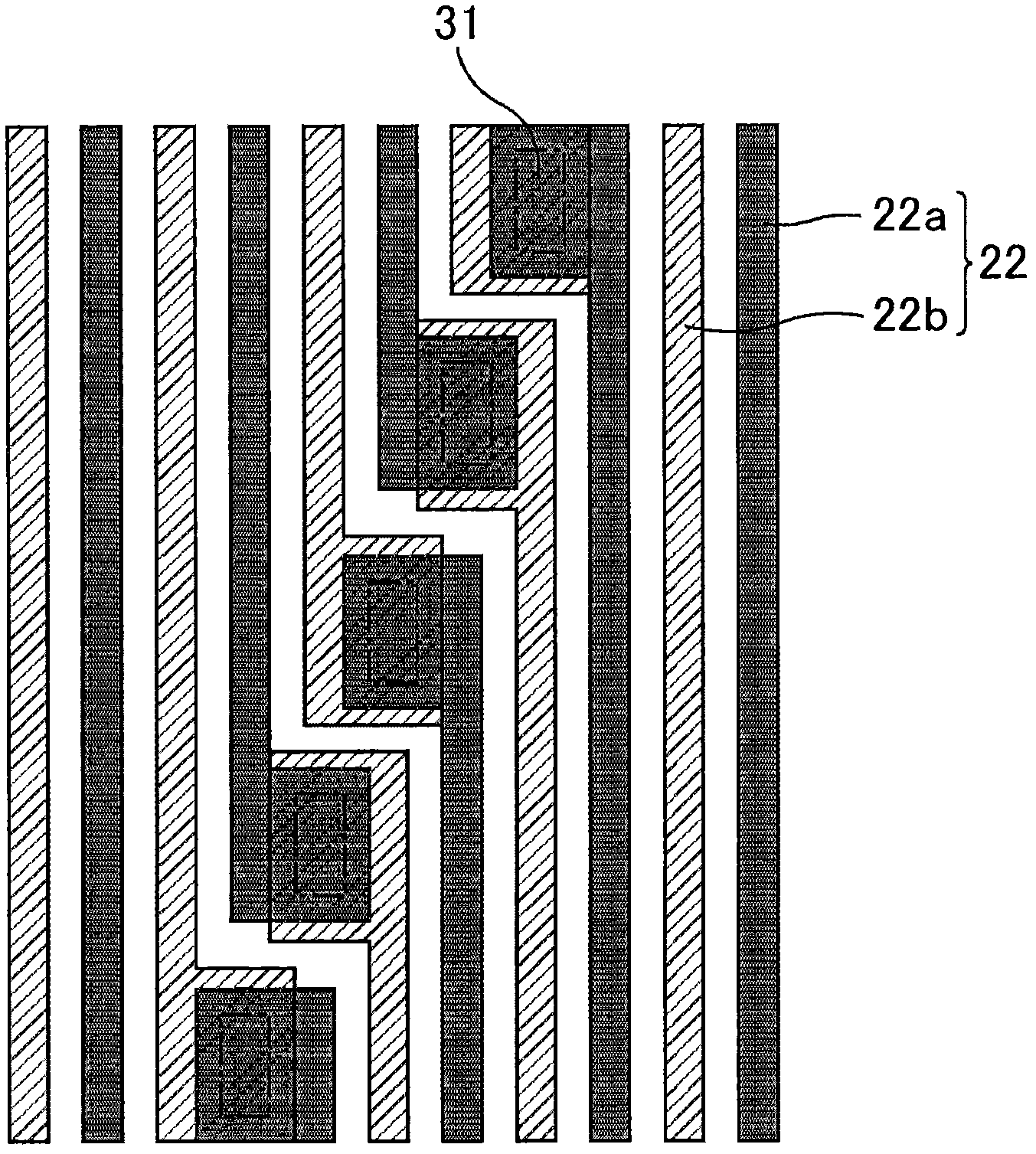

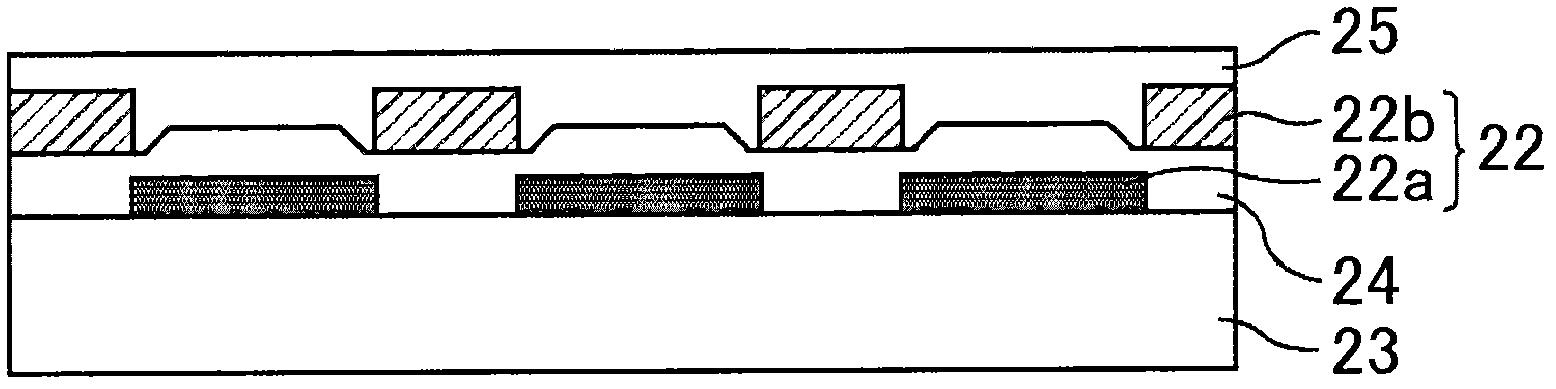

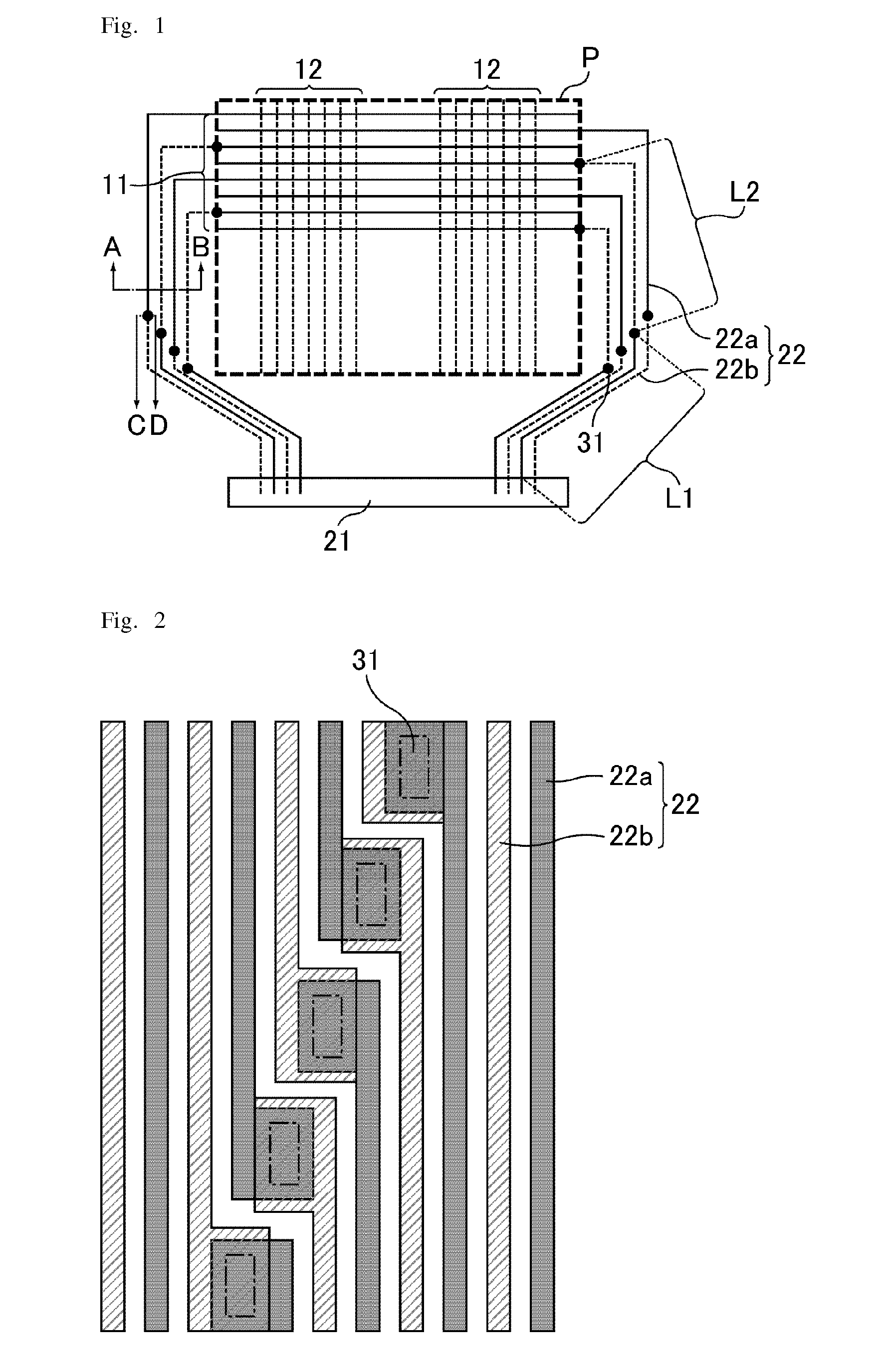

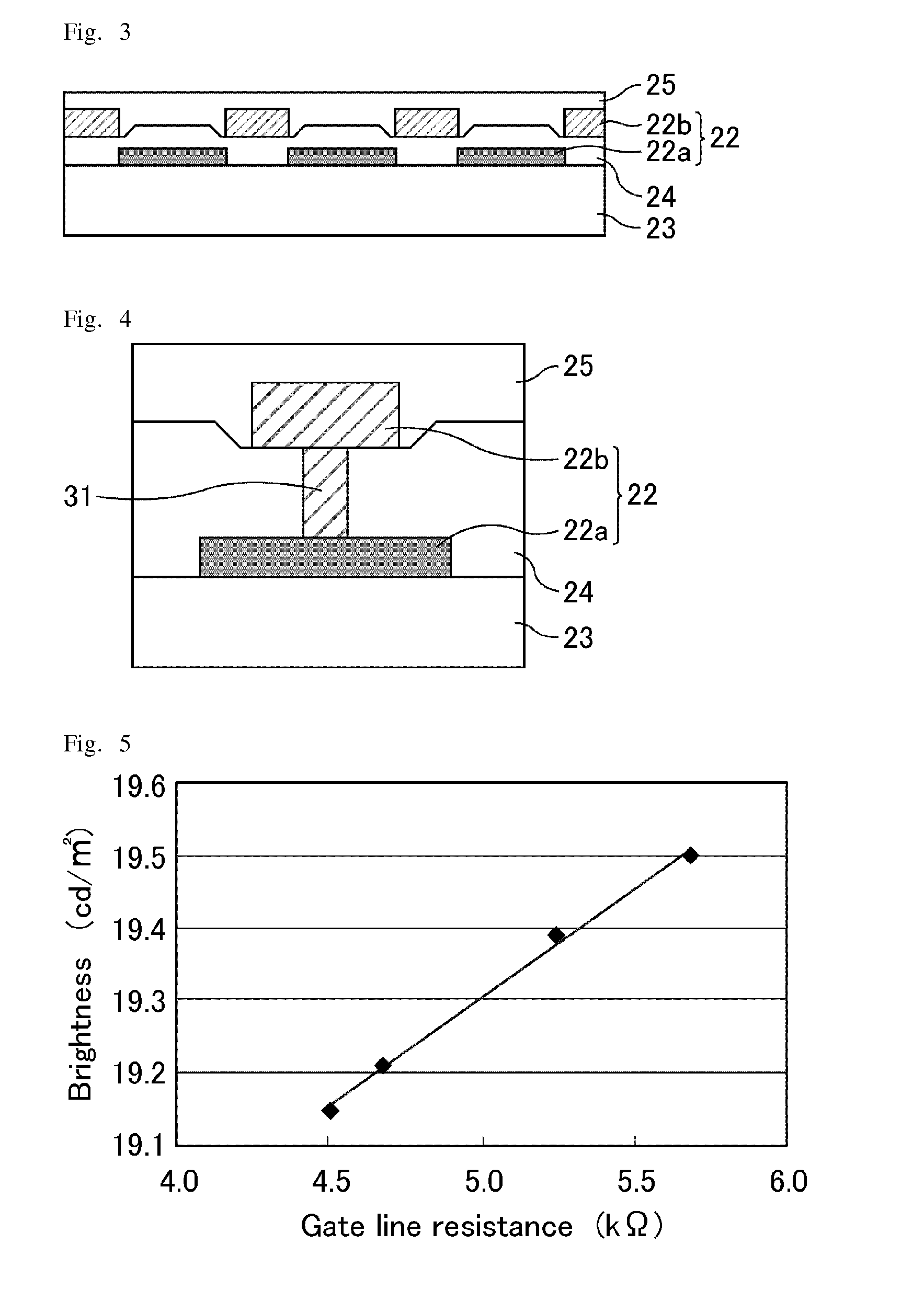

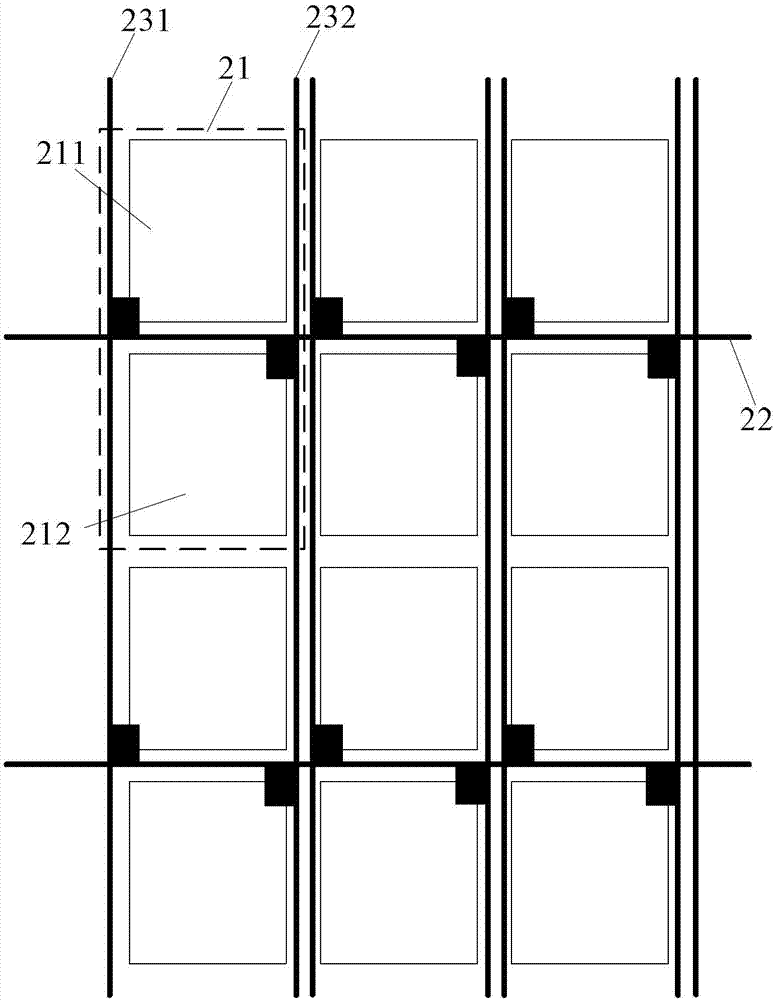

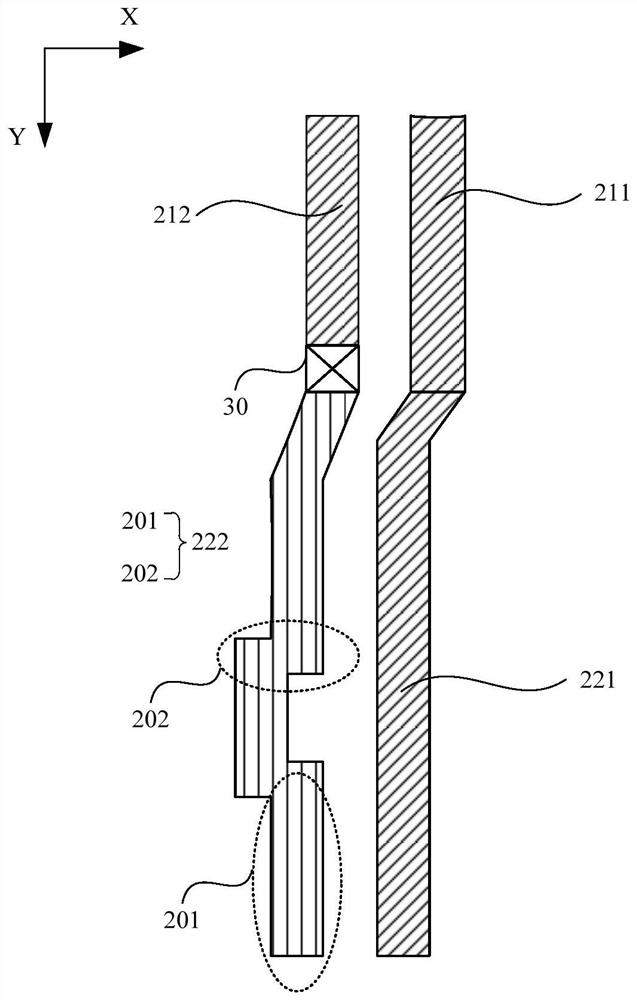

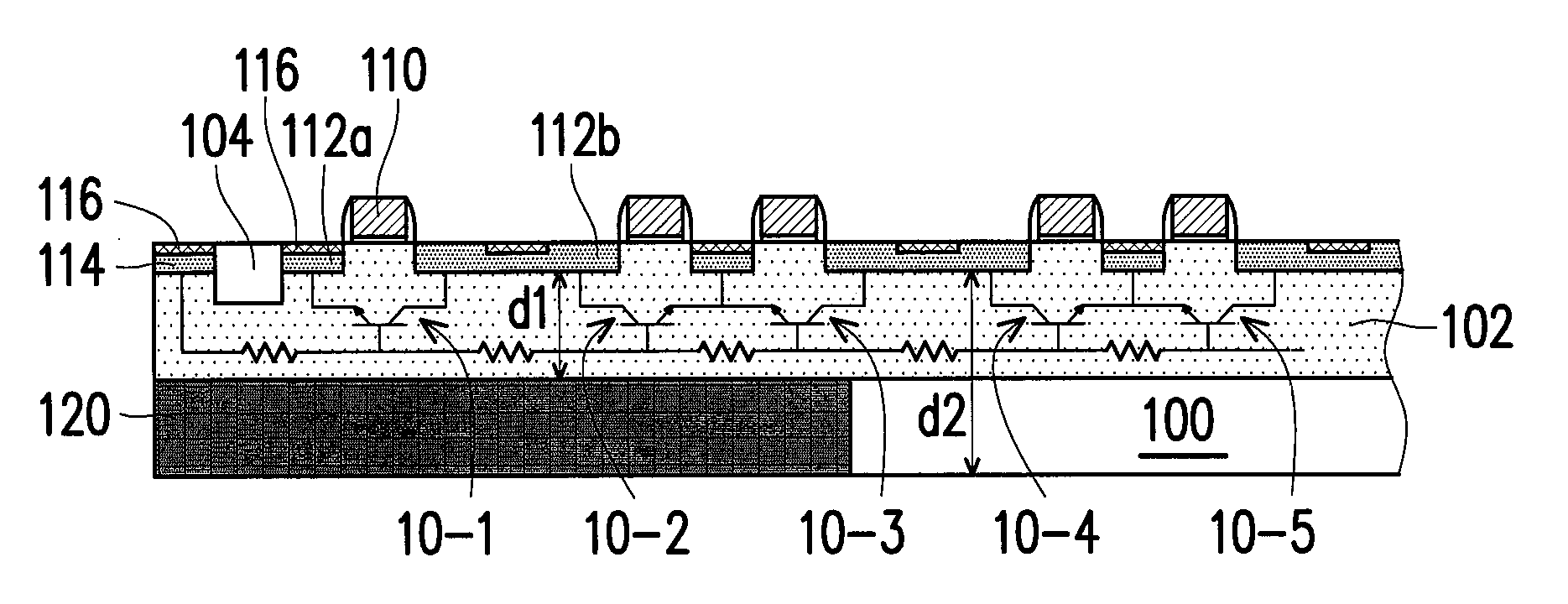

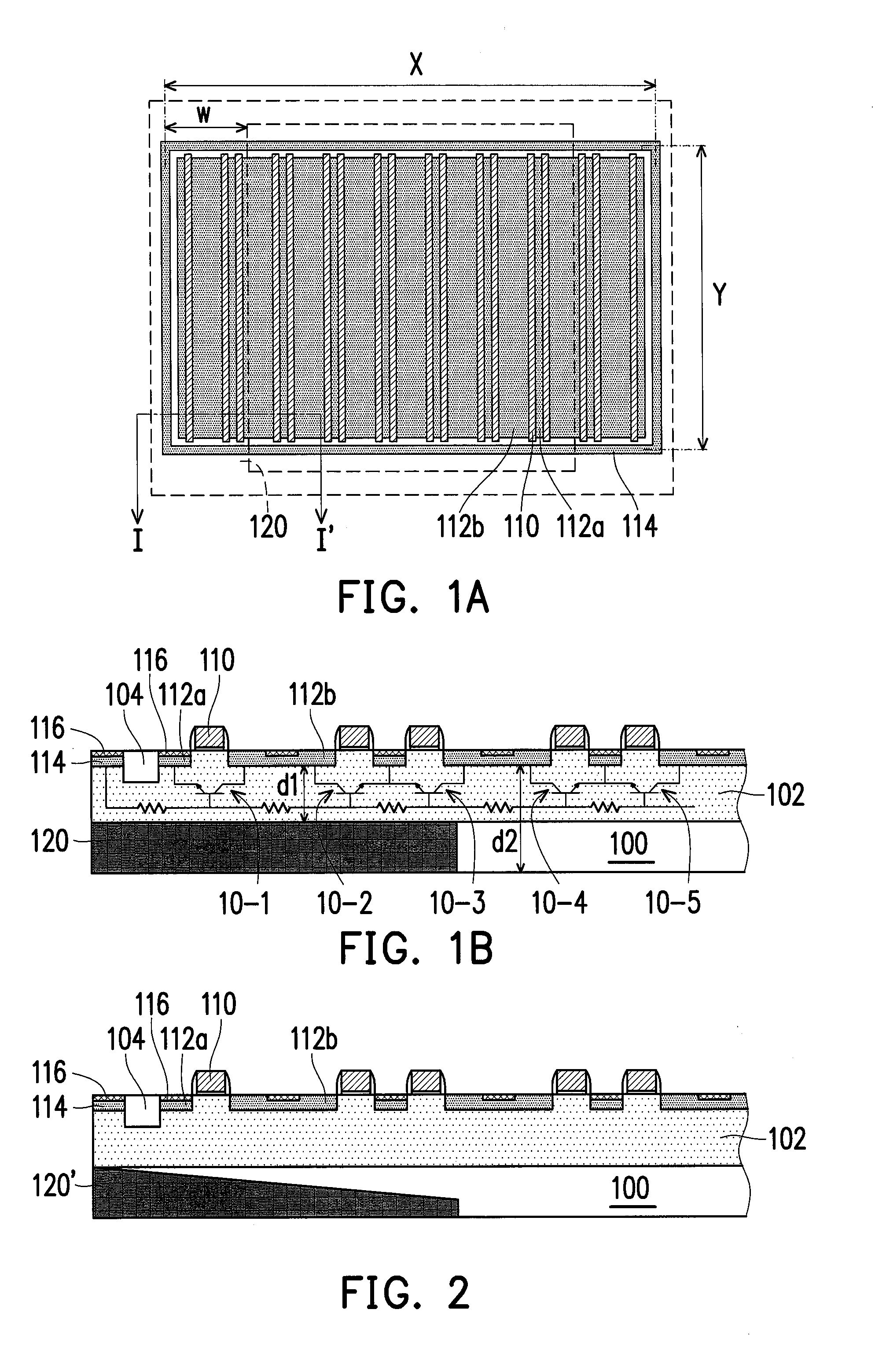

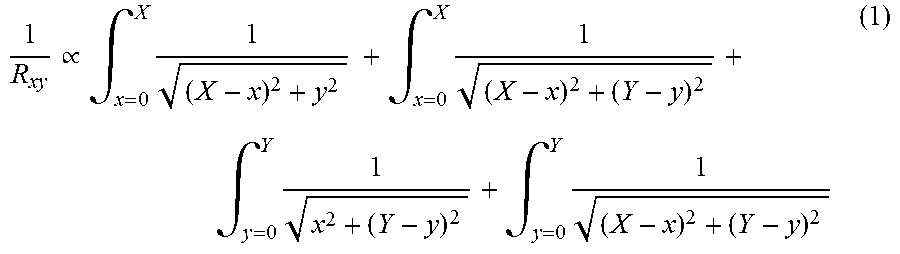

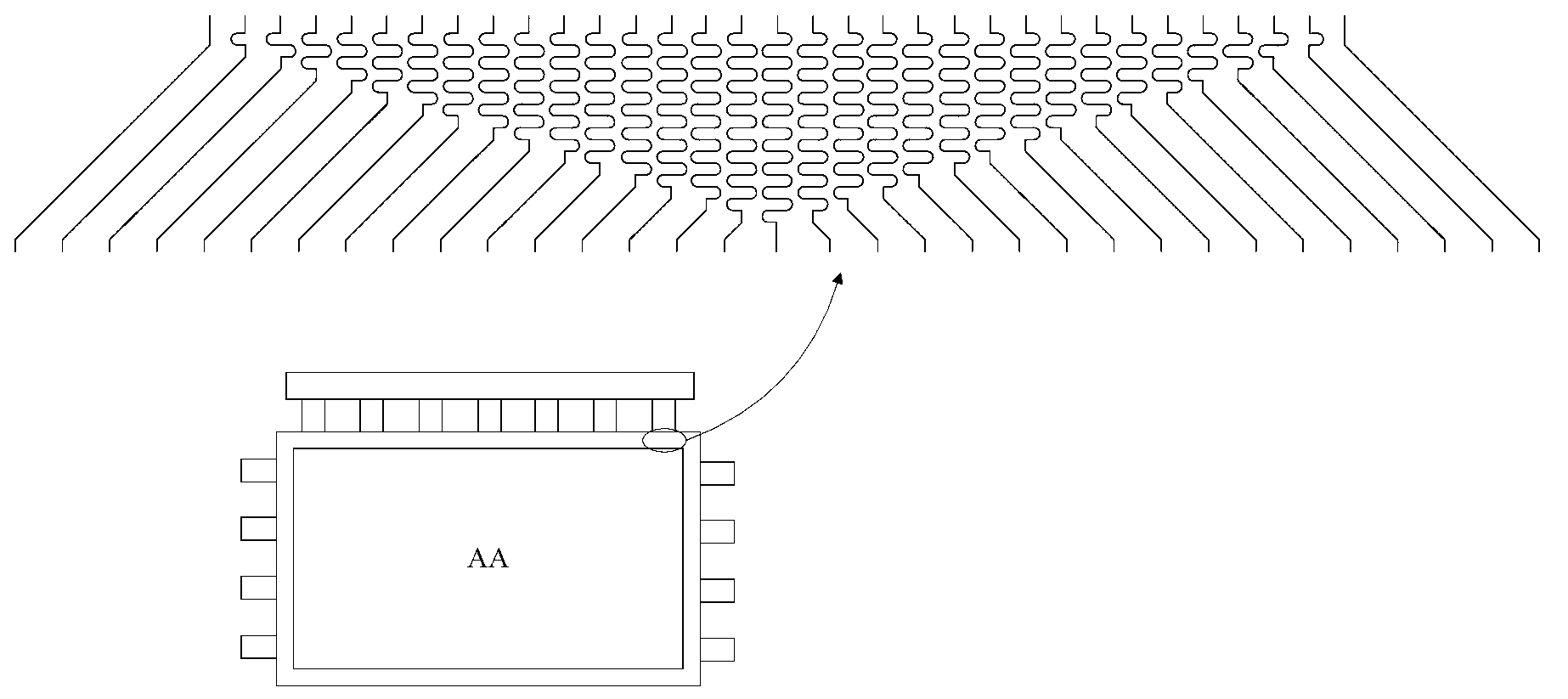

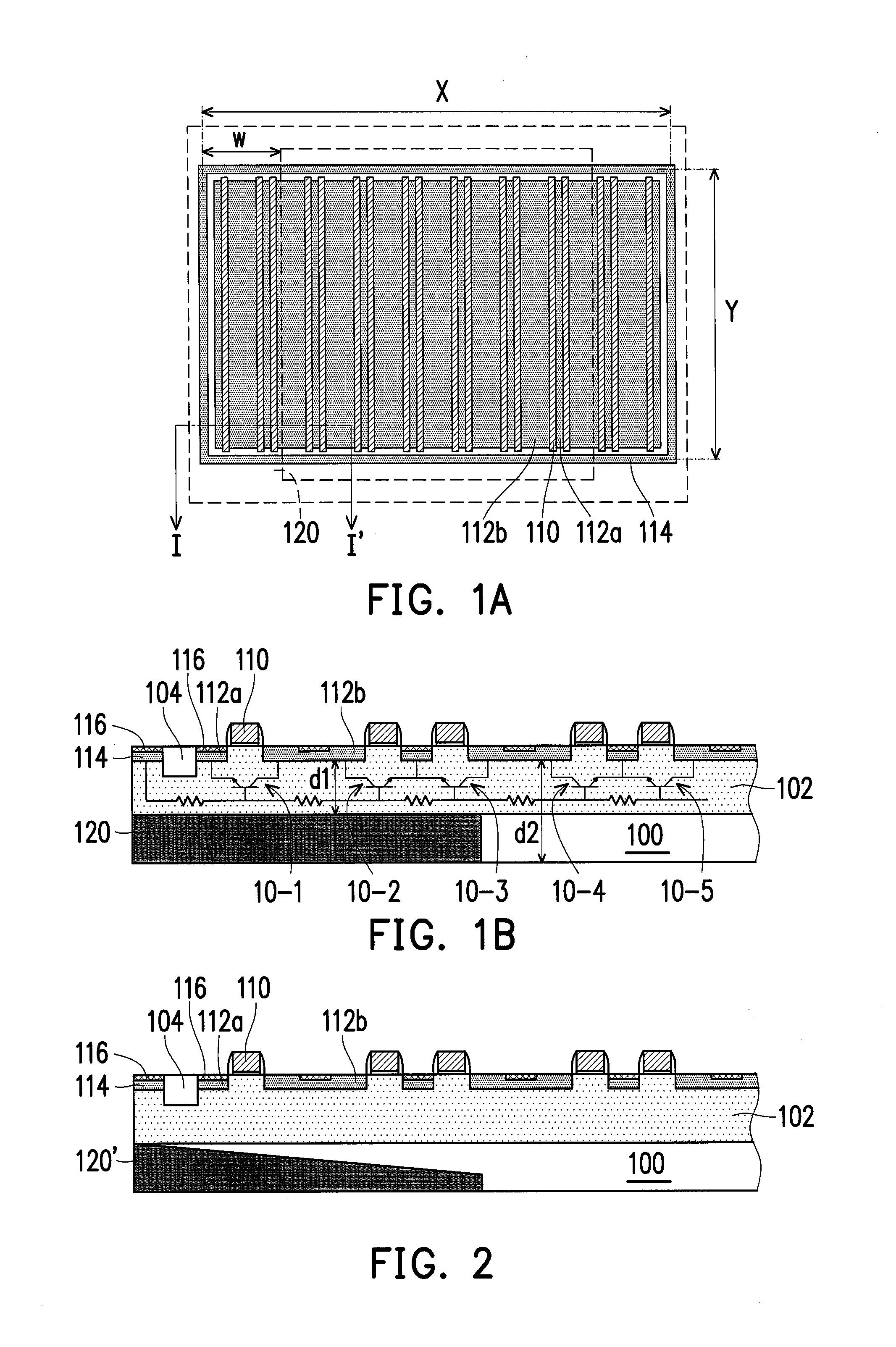

Fan-out, display substrate having the same and method for manufacturing the display substrate

ActiveUS20080157364A1Reduced resistance differenceSemiconductor/solid-state device detailsSolid-state devicesTransistorElectrical and Electronics engineering

A display substrate having a fan-out and a method for manufacturing the display substrate are disclosed. The fan-out includes an insulating substrate, a first line, a second line, a resistance control pattern, and first and second detour pattern. The first line is disposed on the insulating substrate and is connected to a pad. The second line is formed from the same layer as the first line and is connected to a thin-film transistor (TFT). The resistance control pattern is formed from a different layer than the first and second lines. The first and second detour patterns are formed from a different layer than the first and second lines and the resistance control pattern, and connect the first and second lines with the resistance control pattern, respectively.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

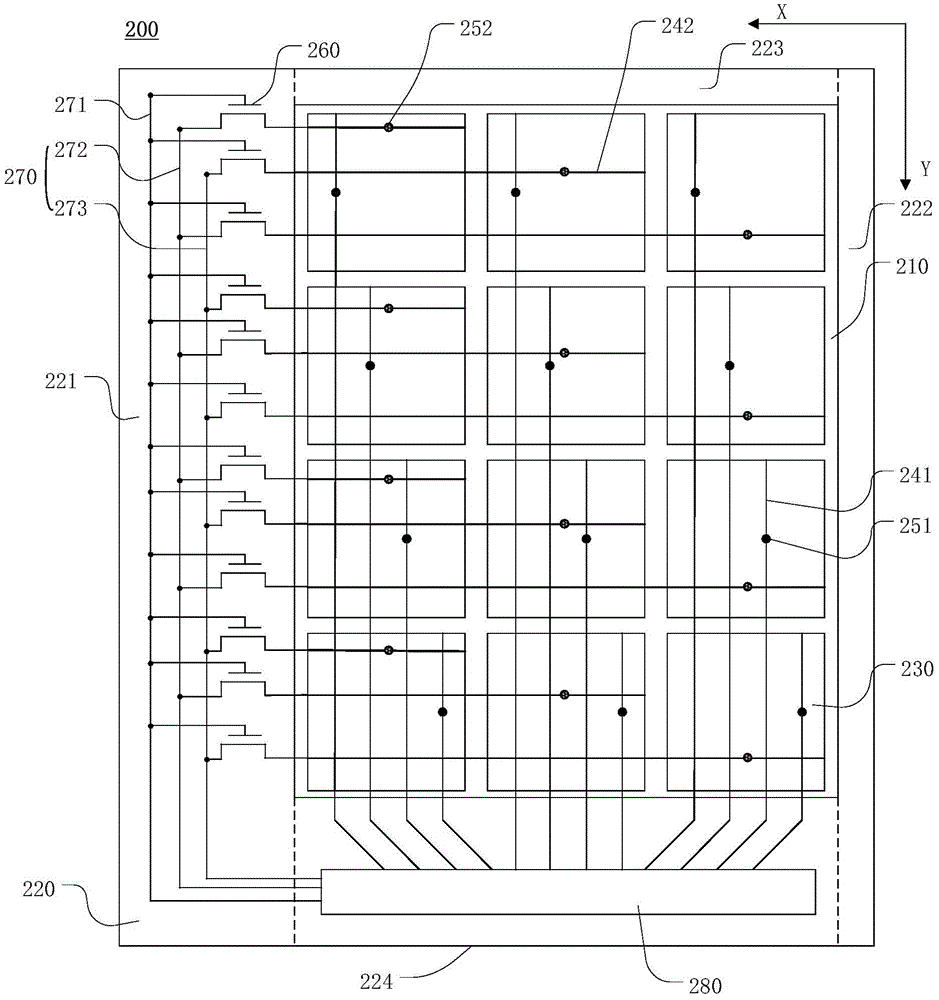

Array substrate and display panel

ActiveCN105549792AImprove test accuracyImprove the display effectNon-linear opticsInput/output processes for data processingElectricityPhysics

The invention provides an array substrate and a display panel. The array substrate comprises a display region and a frame region surrounding the display region, wherein a public electrode layer, a touch control wiring layer and a grid layer are arranged in the display region; the public electrode layer comprises multiple public electrode units; the touch control wring layer comprises multiple first touch control wires electrically connected with the public electrode units; the grid layer comprises multiple grid wires extending in the first direction. The display region further comprises multiple second touch control wires, wherein the second touch control wires are parallel with the grid wires, and each public electrode unit is electrically connected with the corresponding second touch control wire through a via hole; multiple first switches and test leads extending in the second direction are arranged in the frame region, at least one end of each second touch control wire is electrically connected with one corresponding first switch, and the test leads are electrically connected with the first switches. With the adoption of the array substrate and the display panel, the display effect is improved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

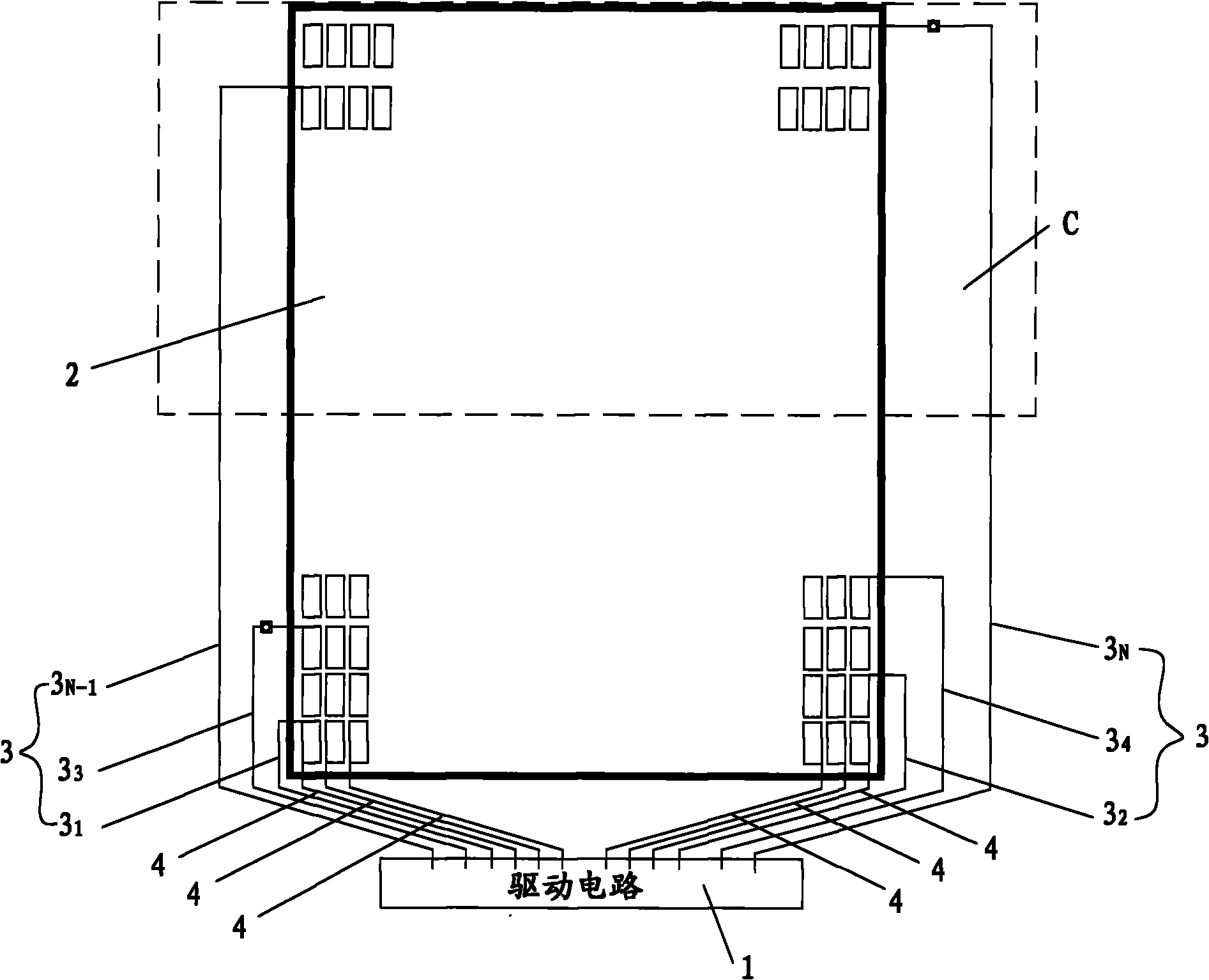

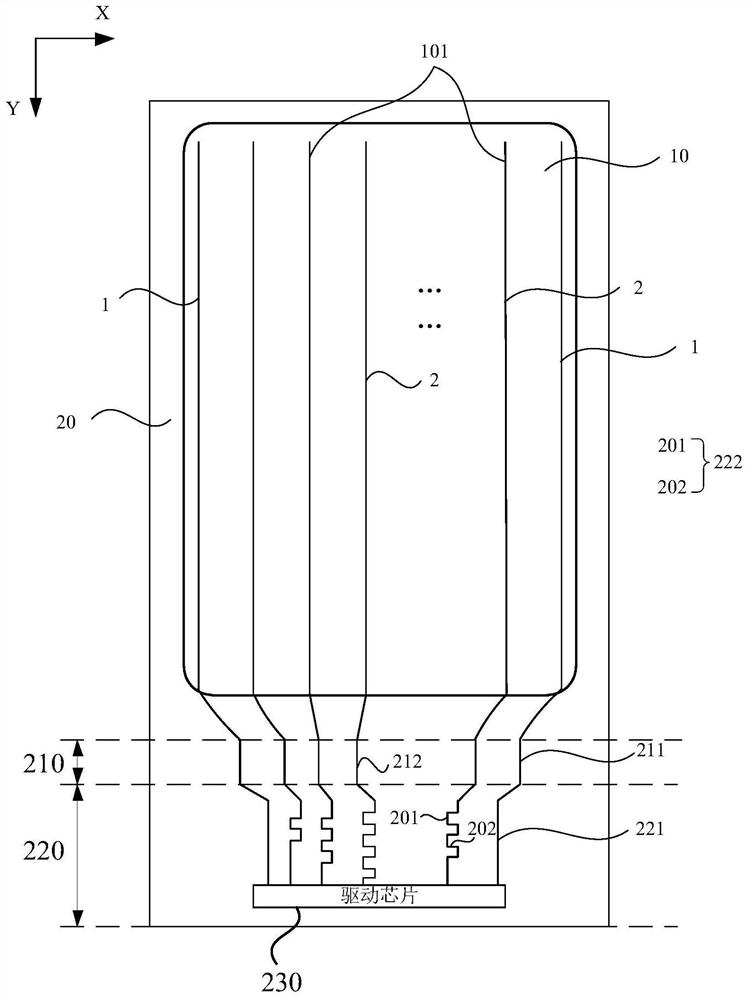

Liquid crystal display panel and liquid crystal display device

ActiveCN102314003AReduced resistance differenceSmall sizeStatic indicating devicesSemiconductor/solid-state device detailsLiquid-crystal displayEngineering

The invention discloses a liquid crystal display panel and a liquid crystal display device. The liquid crystal display panel comprises a driving circuit, a pixel array and a plurality of connecting wires, wherein the pixel array comprises a plurality of driving wires; each connecting wire at least consists of a first metal layer and a second metal layer; one end of each connecting wire is connected with the driving circuit, and the other ends of the connecting wires are connected with the plurality of driving wires respectively; and in the plurality of connecting wires, one section of at least one part of the connecting wires consists of the first metal layers, and the other section of the at least one part of the connecting wires consists of the second metal layers. By the liquid crystal display panel and the liquid crystal display device, resistance differences among the connecting wires can be reduced, so that the problem of non-uniform blinking of the liquid crystal display panel is solved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

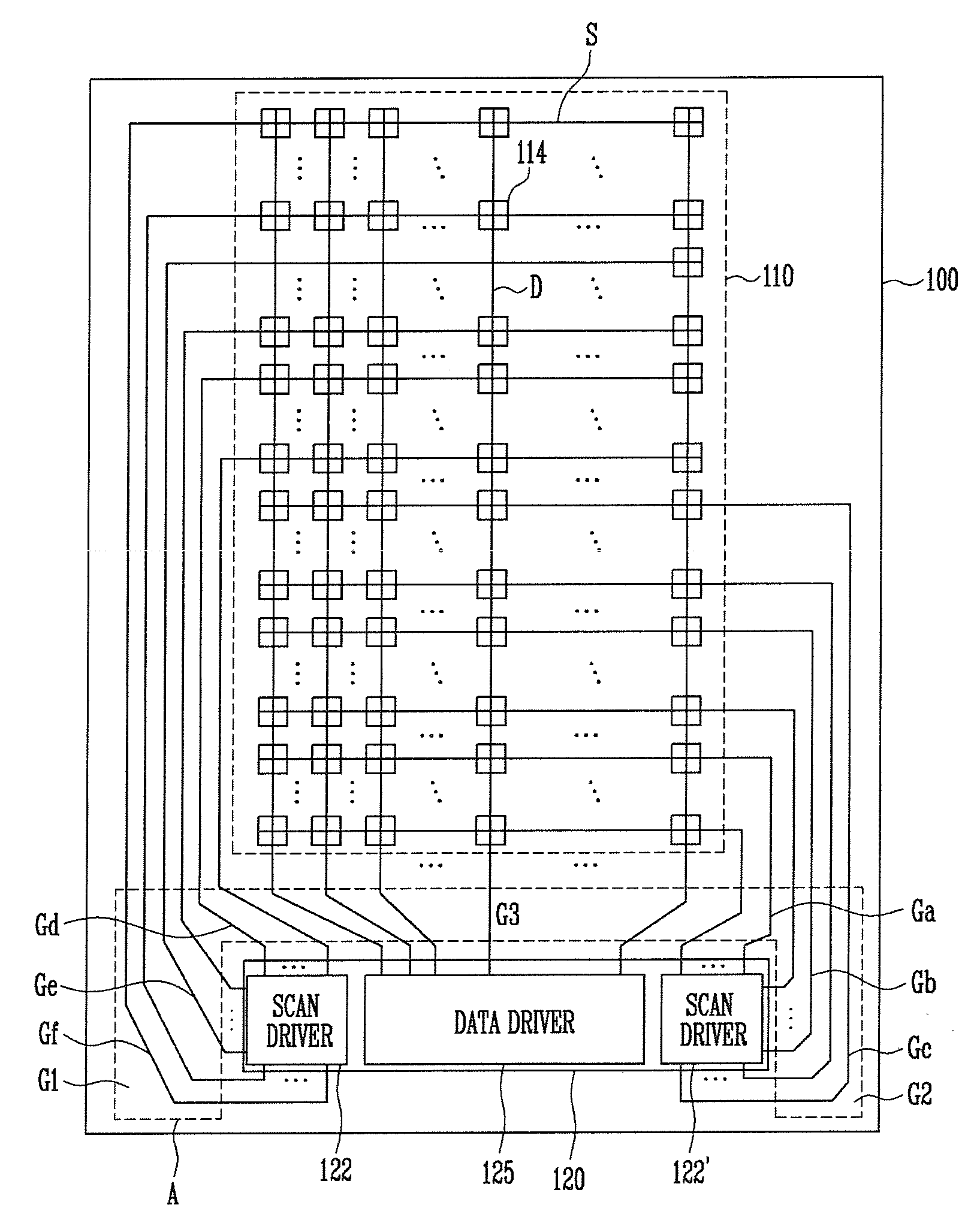

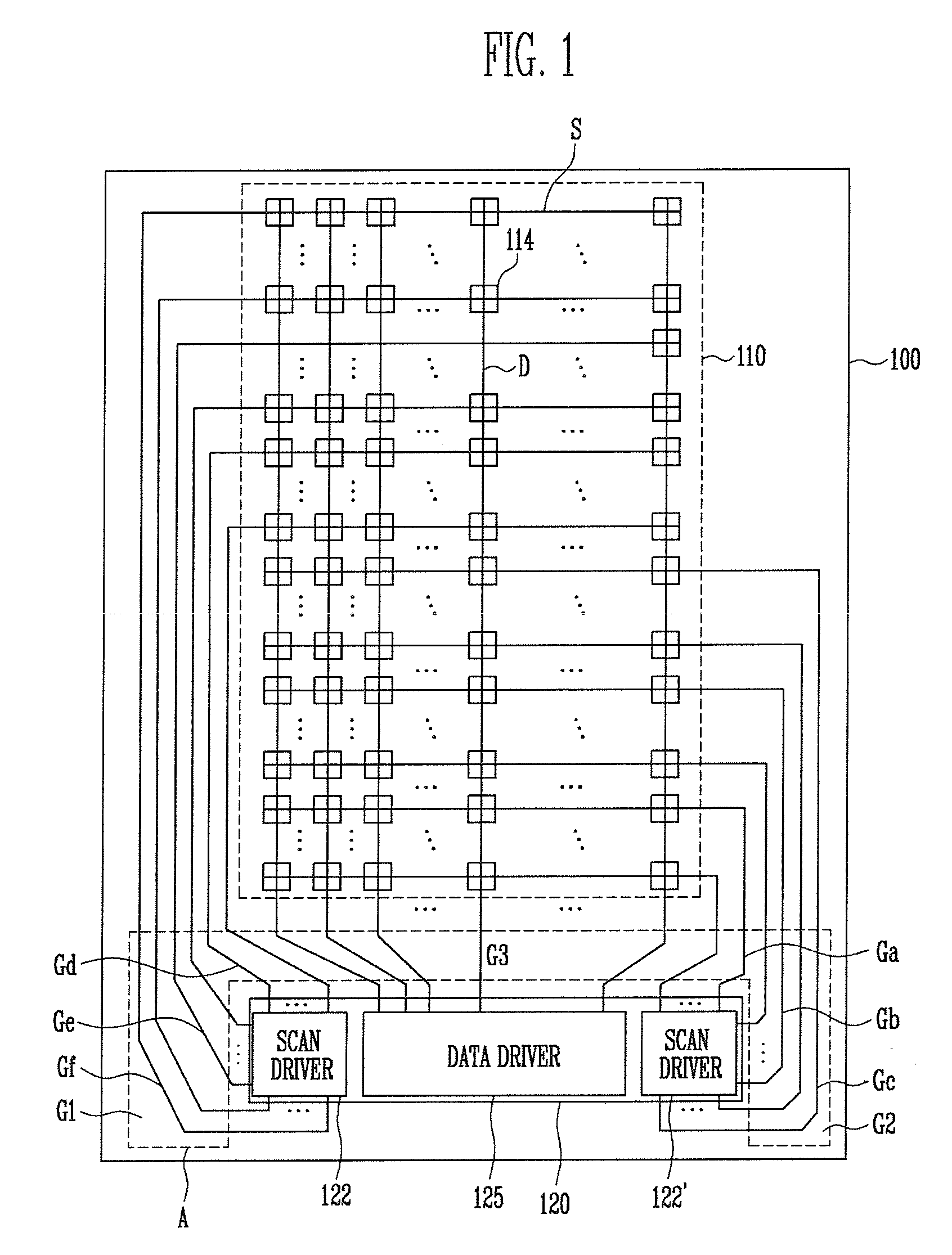

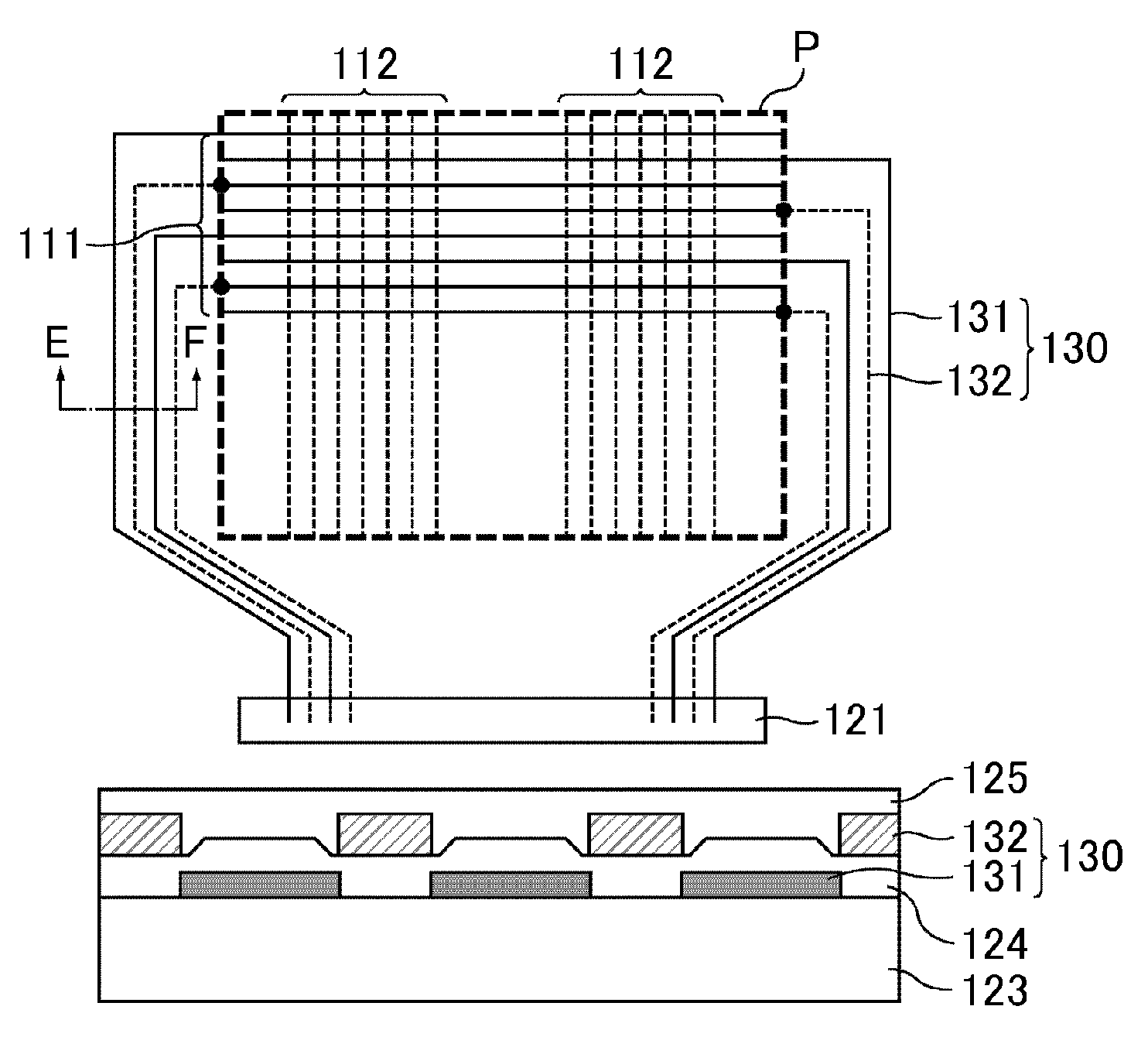

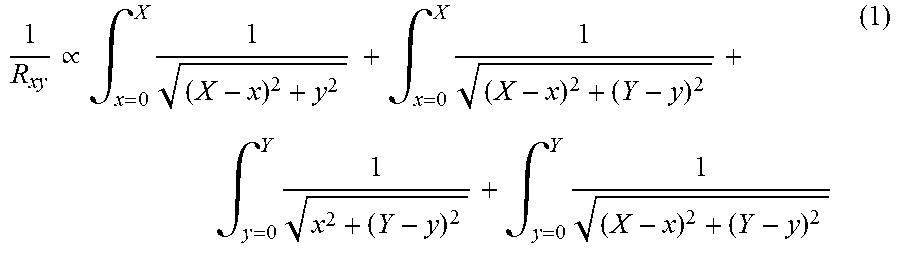

Flat panel display device

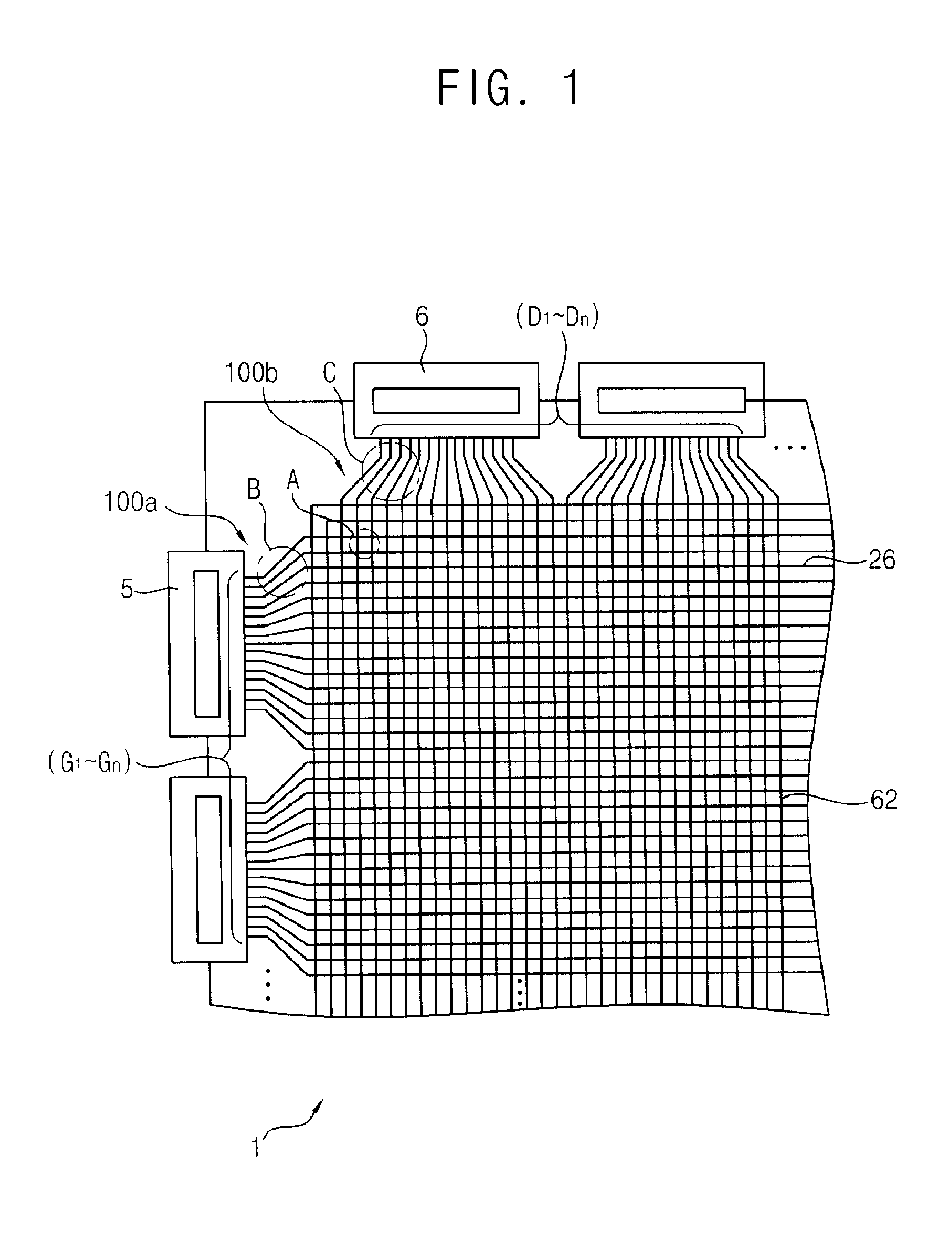

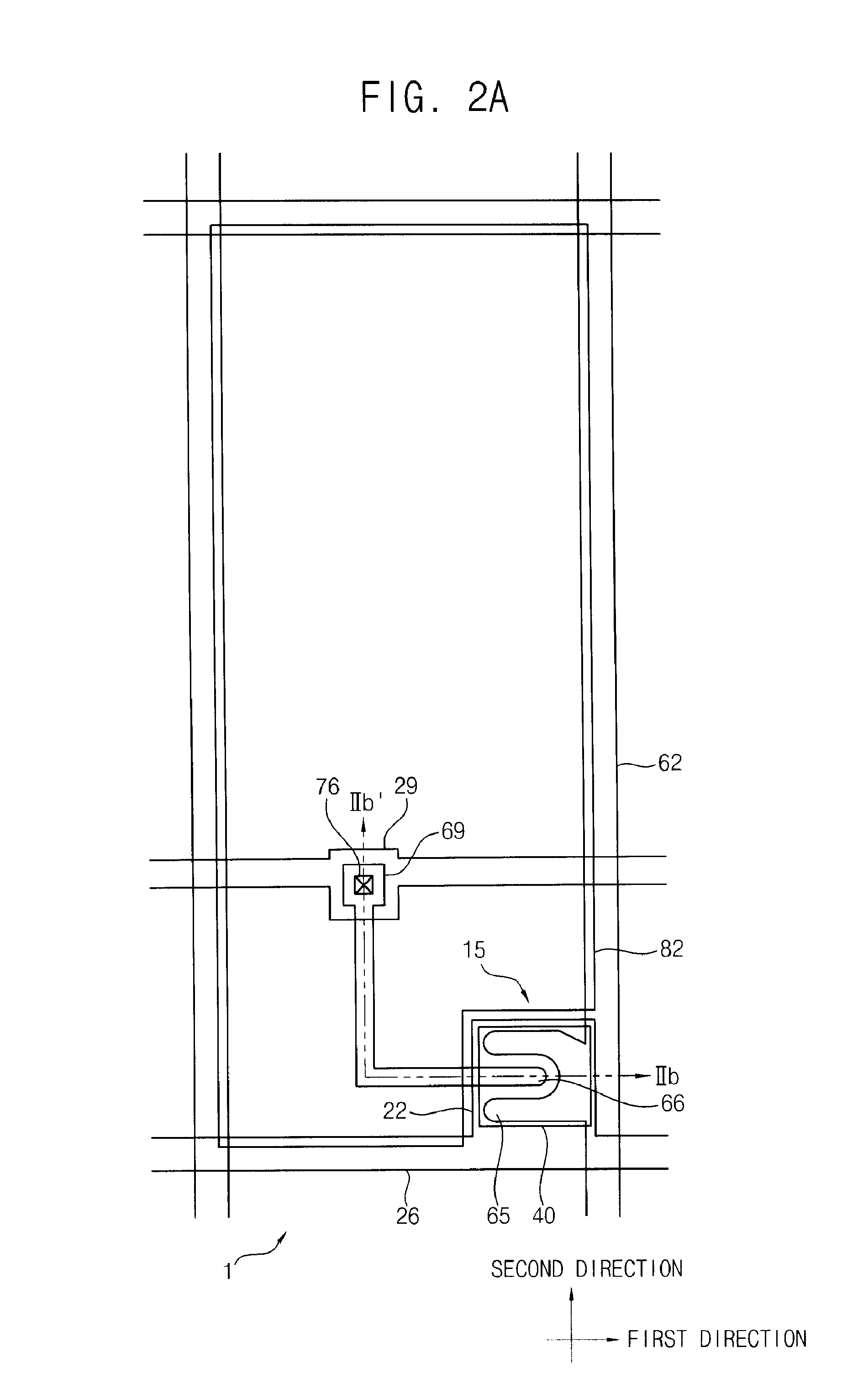

ActiveUS20080303776A1Reduced resistance differenceElectrical apparatusStatic indicating devicesElectrical resistance and conductanceEngineering

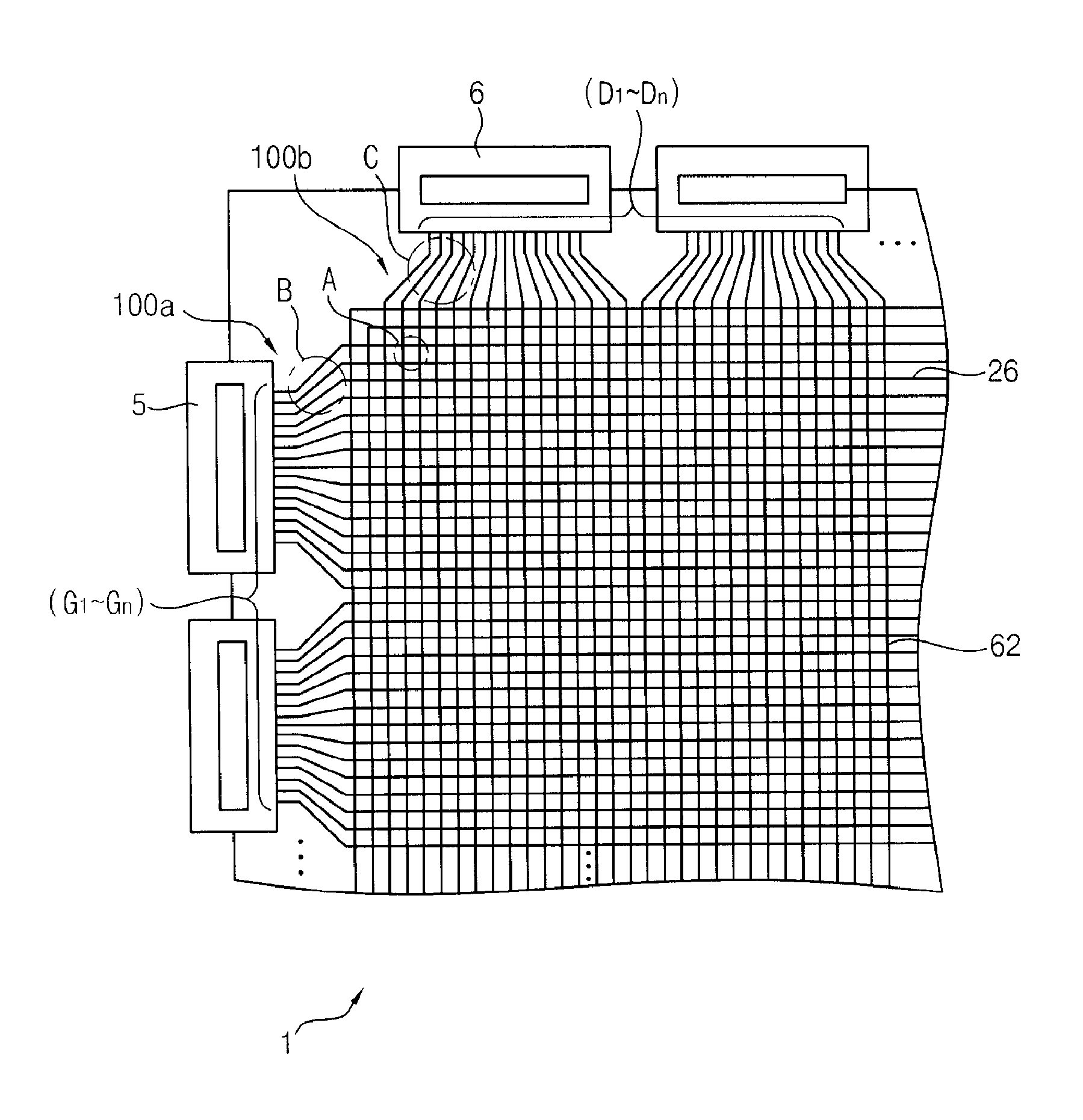

A flat panel display device is capable of reducing a resistance difference according to the lengths of signal lines and has a stably designed resistance value of the signal lines arranged in edges of wire groups diverging from a driving circuit unit. The flat panel display device includes a display unit including a plurality of pixels arranged in intersecting regions of signal lines; a driving circuit unit to supply drive signals to the signal lines; and a divergence region having the signal lines diverge into at least two wire groups to connect the driving circuit unit to the pixels, wherein a resistance difference per unit length between the signal lines arranged in a boundary of two wire groups is set to a value that is intermediate of average resistance differences between the adjacent signal lines in the two wire groups.

Owner:SAMSUNG DISPLAY CO LTD

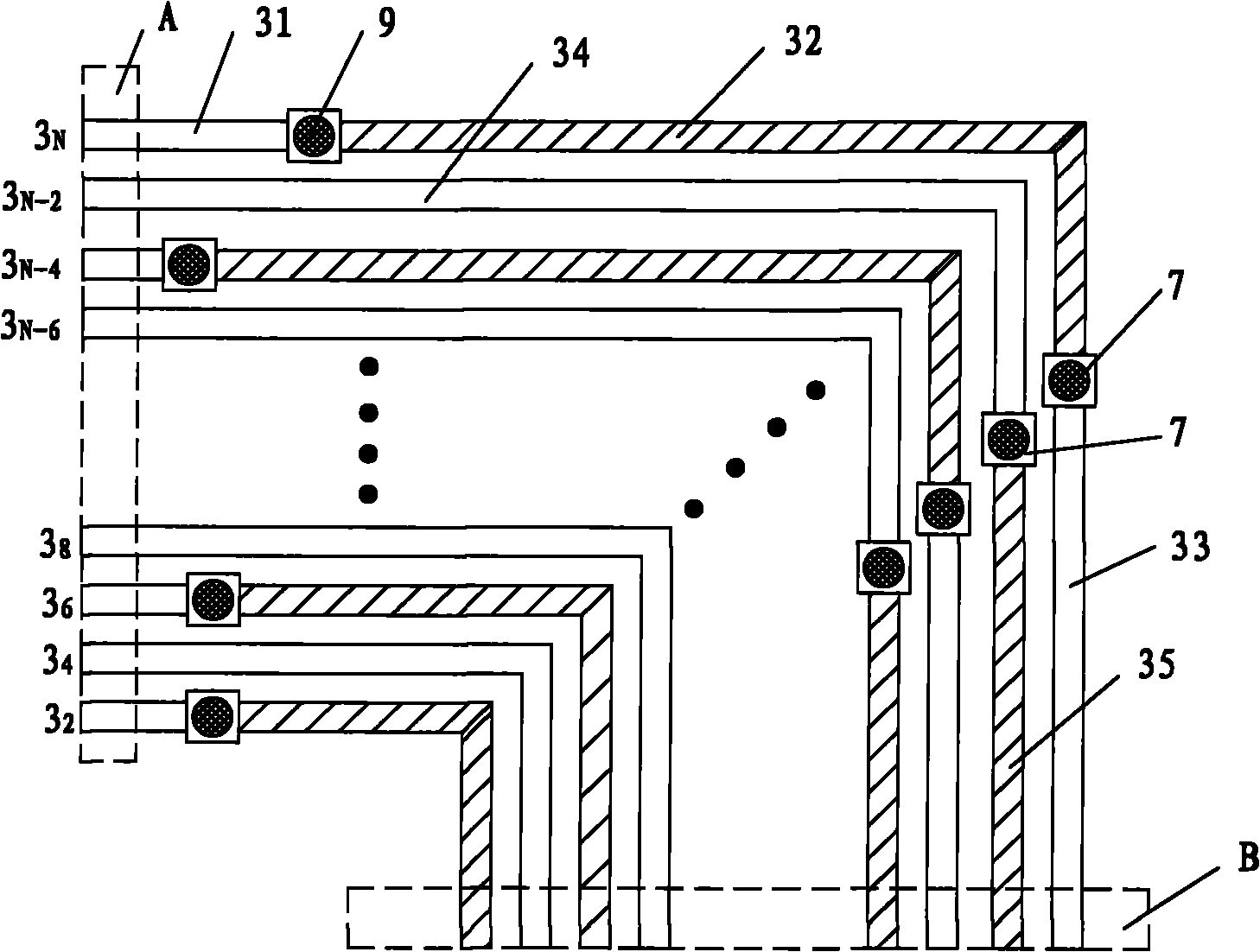

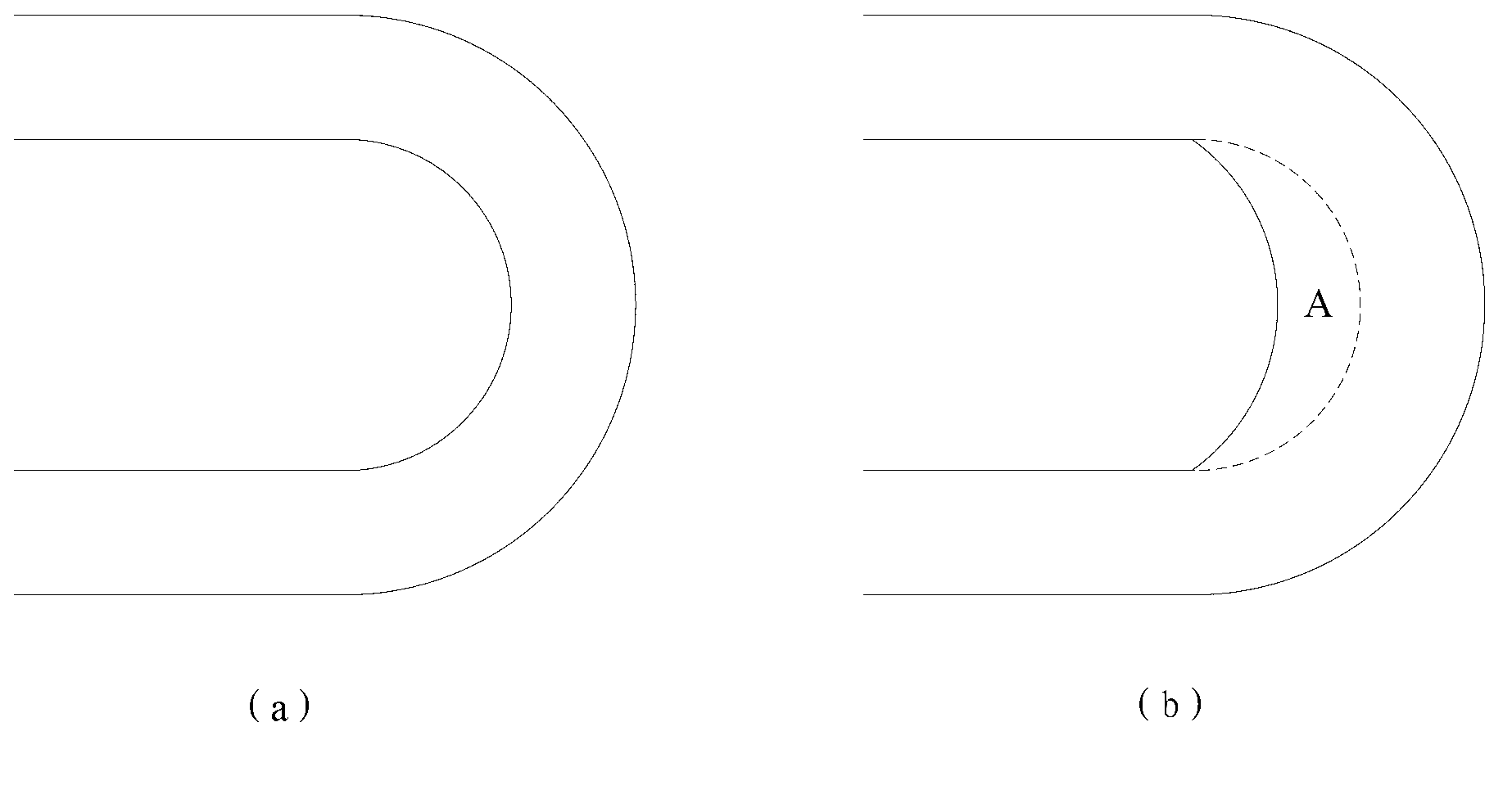

Array substrate of liquid crystal display and scanning line structure of array substrate

InactiveCN103185999AImprove the display effectReduced resistance differenceNon-linear opticsElectrical resistance and conductanceLiquid-crystal display

The invention discloses an array substrate of a liquid crystal display and a scanning line structure of the array substrate. The scanning line structure in an AA region and a non display region outside the AA region particularly comprises a first scanning line and a second scanning line which are alternately arranged in the non display region in sequence and positioned in different metal layers; a third scanning line in the AA region extends to the middle in the edge of the non display region; contact holes are formed in the first scanning line, the second scanning line and the third scanning line which are positioned on the two sides in the middle; and the first scanning line and the second scanning line are electrically connected with the third scanning line through the contact holes by transparent electrodes respectively. Through the structure, the resistance difference between adjacent wire harnesses in the dual-layer wiring process can be reduced, the width of each fan-shaped wire harness is reduced at the same time, the center and the edge in a fan section of each fan-shaped wire harness are wired in an equal-resistance way, the probability of causing horizontal stripes is reduced, and the purpose of improving the displaying effect of the whole liquid crystal display is achieved.

Owner:BEIHAI HKC OPTOELECTRONICS TECH CO LTD

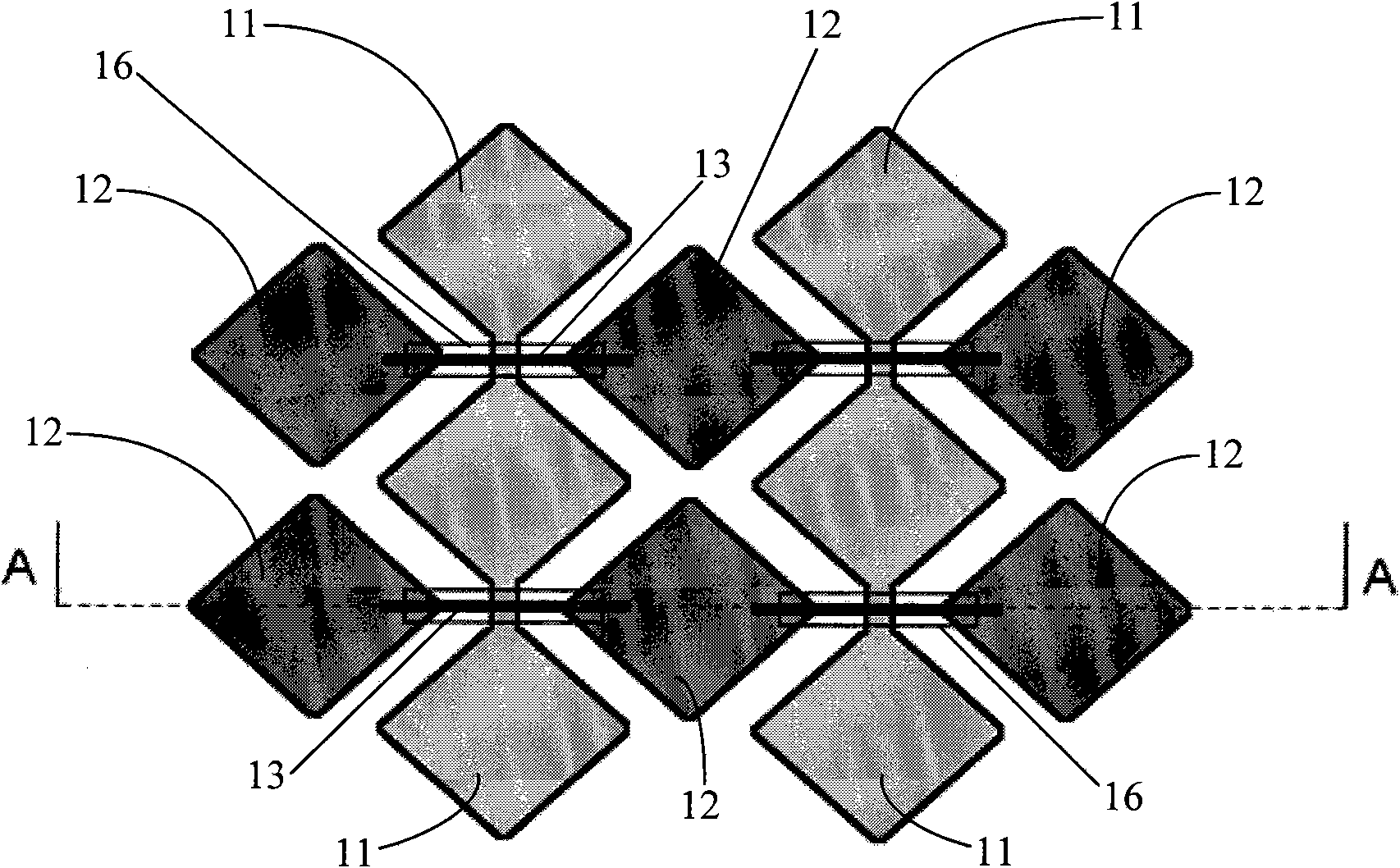

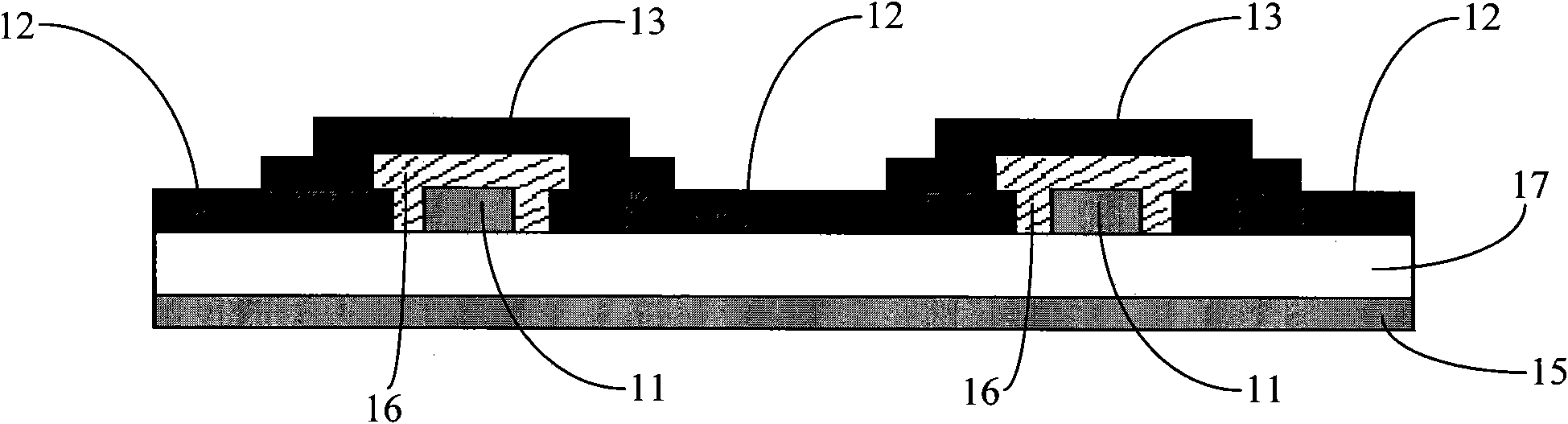

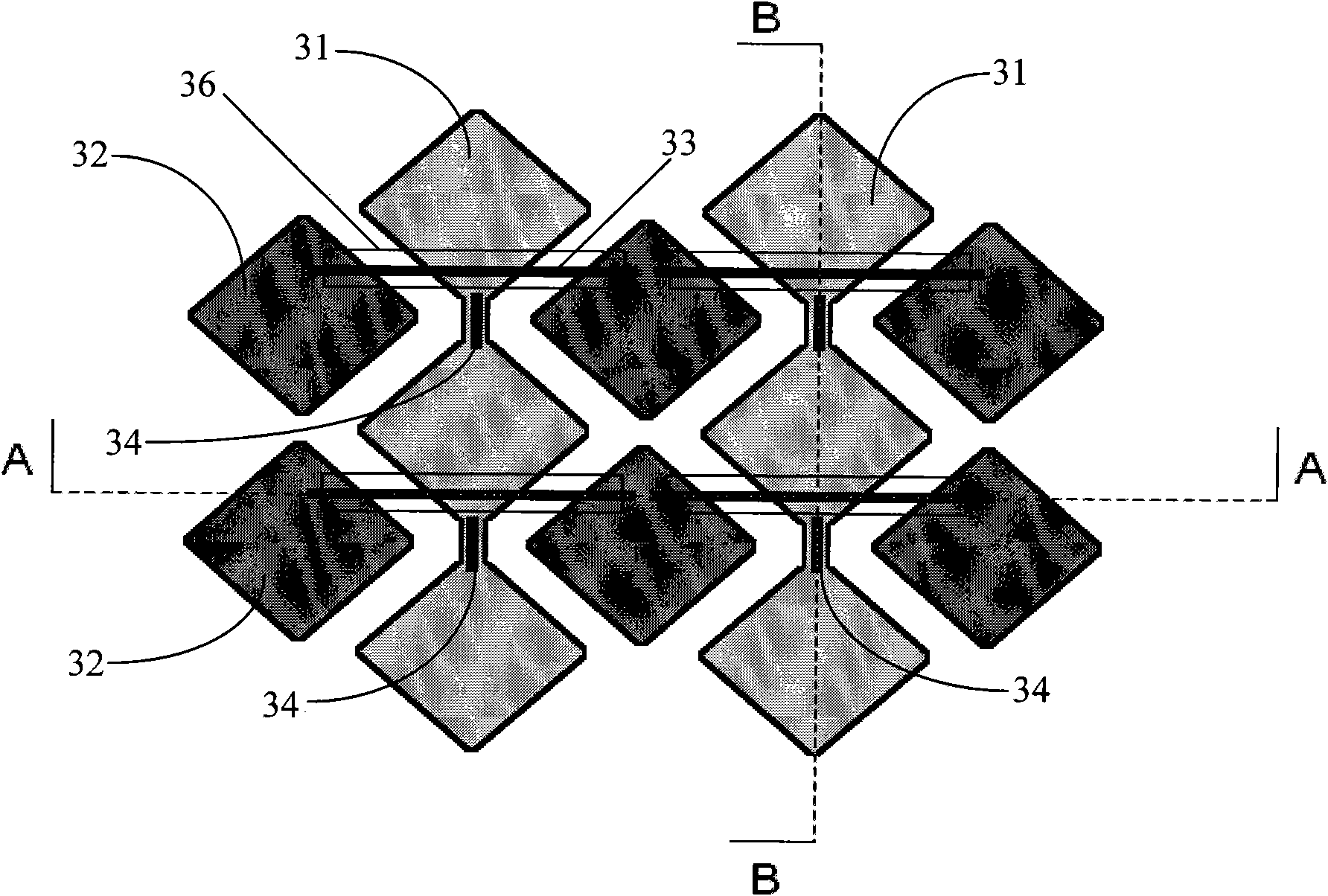

Touch pad of capacitive touch screen and manufacturing method thereof

InactiveCN101957700AImprove touch precisionImprove touch performanceInput/output processes for data processingTouchscreenLow resistance

The invention provides a touch pad of a capacitive touch screen and a manufacturing method thereof. The touch pad of the capacitive touch screen comprises a first group of conductive film lines and a second group of conductive film lines which are distributed on a substrate. Insulating film lines are arranged at intersections of the first and second groups of conductive film lines, wherein the upper surfaces of the insulating film lines are provided with a third group of conductive film lines which connects the second group of conductive film lines; and the narrowest part of the first group of conductive film lines is provided with a fourth group of conductive film lines. Compared with the prior art, the touch pad greatly reduces the resistance of the first group of conductive film lines by arranging the fourth group of conductive film lines on the narrowest part of the first group of conductive film lines, and greatly reduces the resistance of the second group of conductive film lines by adopting the third group of conductive film lines with low resistance to bridge the second group of conductive film lines. Therefore, the resistance of the first and second groups of conductive film lines is effectively reduced, a resistance difference between the first and second groups of conductive film lines is simultaneously reduced, and the touch performance of the touch screen is improved.

Owner:深圳市中显微电子有限公司

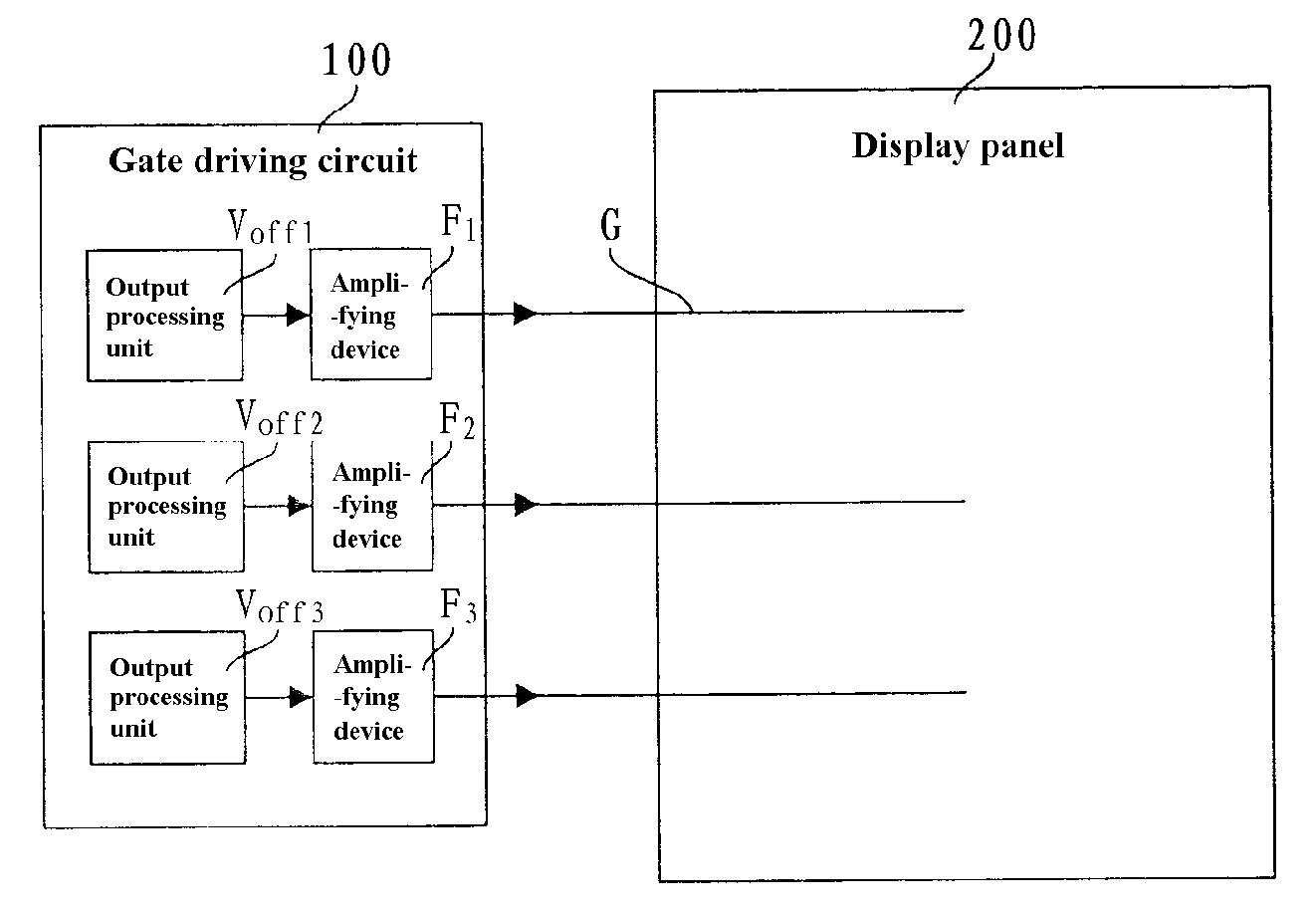

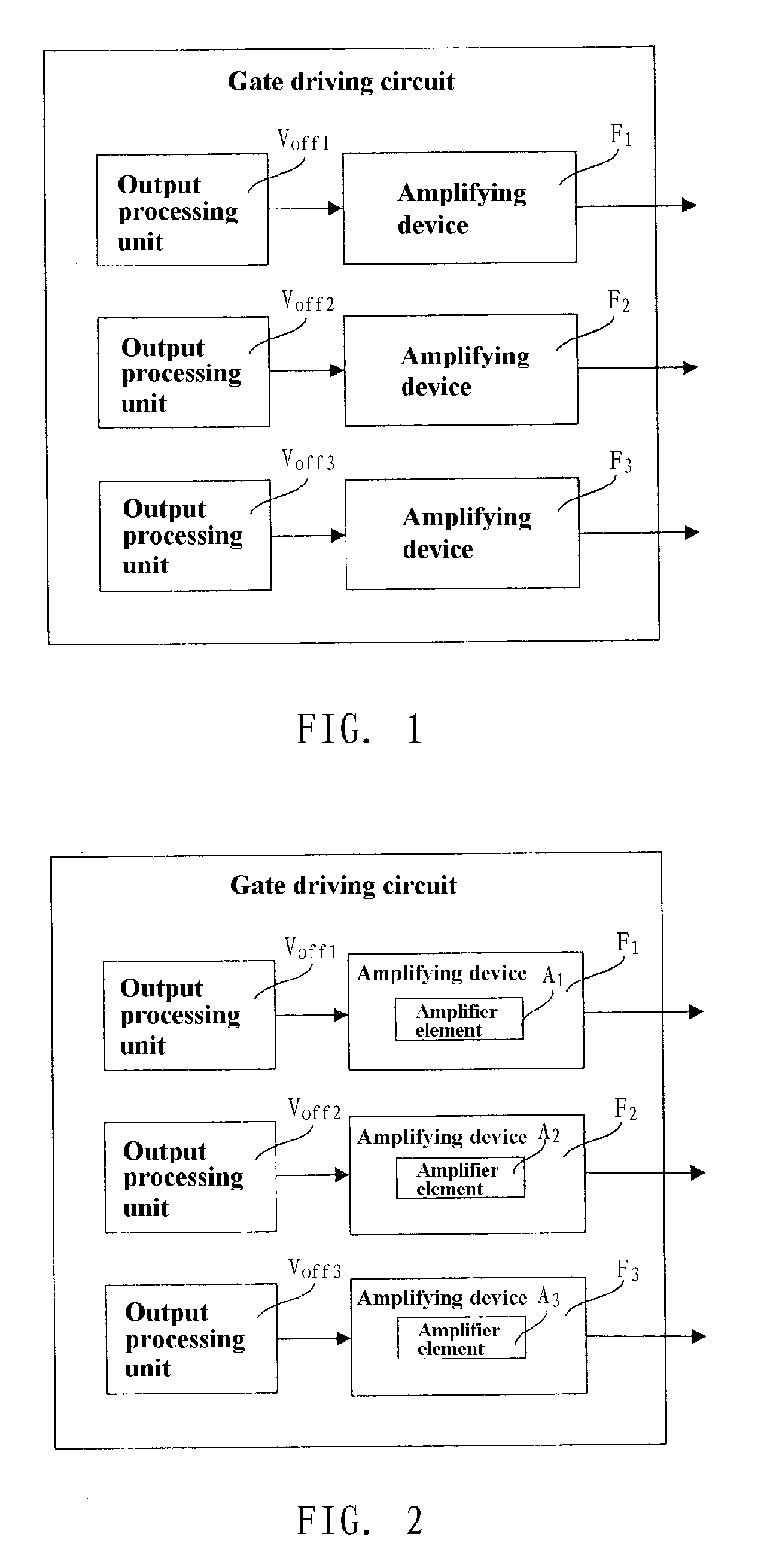

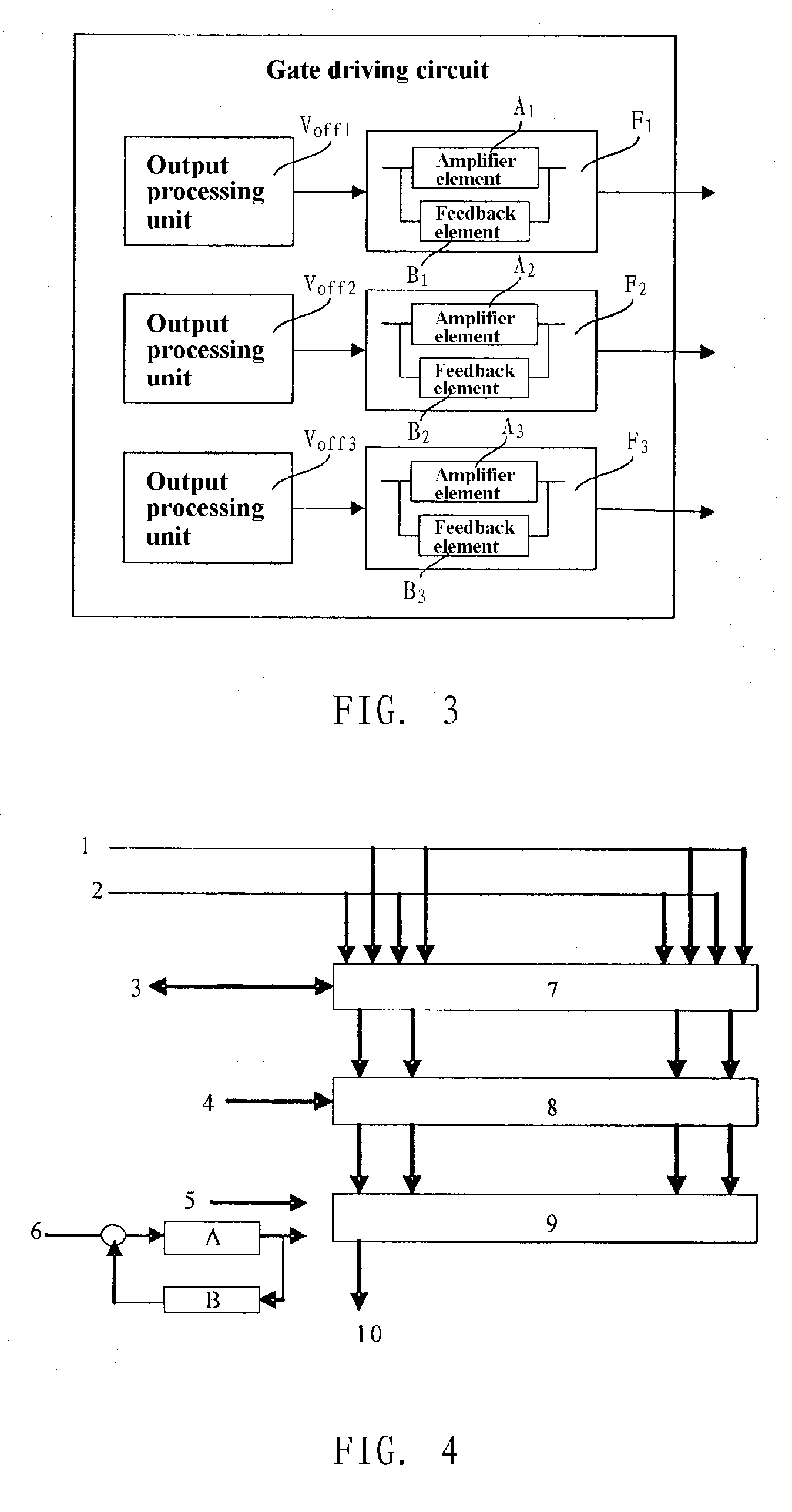

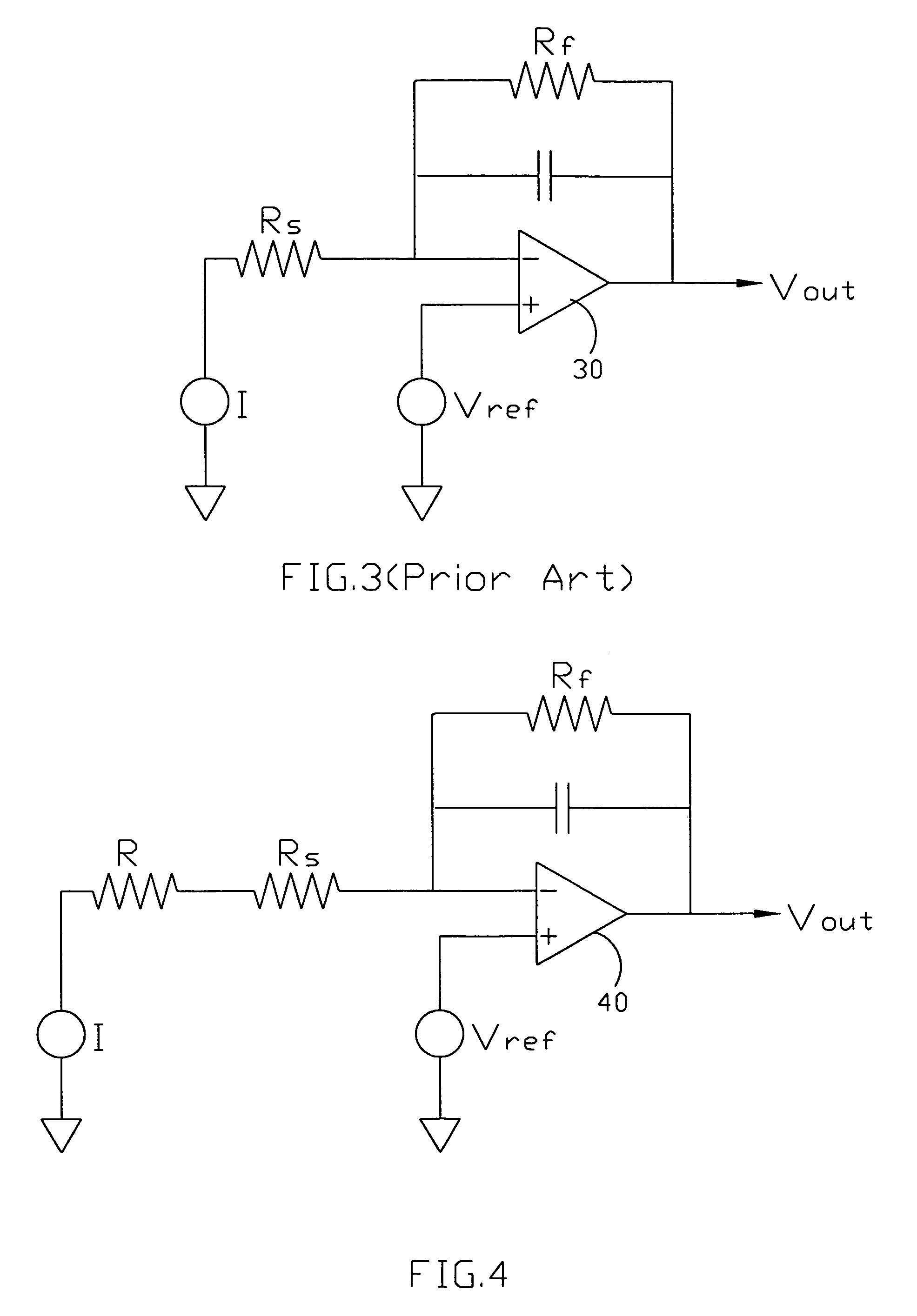

Gate driving circuit and liquid crystal display

ActiveUS20080259010A1Reduce output varianceUniformity of gate driving signalStatic indicating devicesLiquid-crystal displayEngineering

The present invention relates to a gate driving circuit comprising at least an output processing unit, and further comprising an amplifying device correspondingly connected to the output processing unit, said amplifying device being used to process a signal output from the output processing unit and then output a driving signal. The present invention also relates to a liquid crystal display, including a gate driving circuit and a display panel, said gate driving circuit comprising at least an output processing unit, and said display panel comprising a gate line, wherein said gate driving circuit further comprises an amplifying device correspondingly connected to the output processing unit, said amplifying device is used to process a signal output from the output processing unit and then output a driving signal; said amplifying device is correspondingly connected to an end of the gate line. The invention decreases the difference of output signals of the gate driving circuit at difference positions, improves overall uniformity of the gate driving signals, thus decreasing display deviation on the display panel and improving imaging effect.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

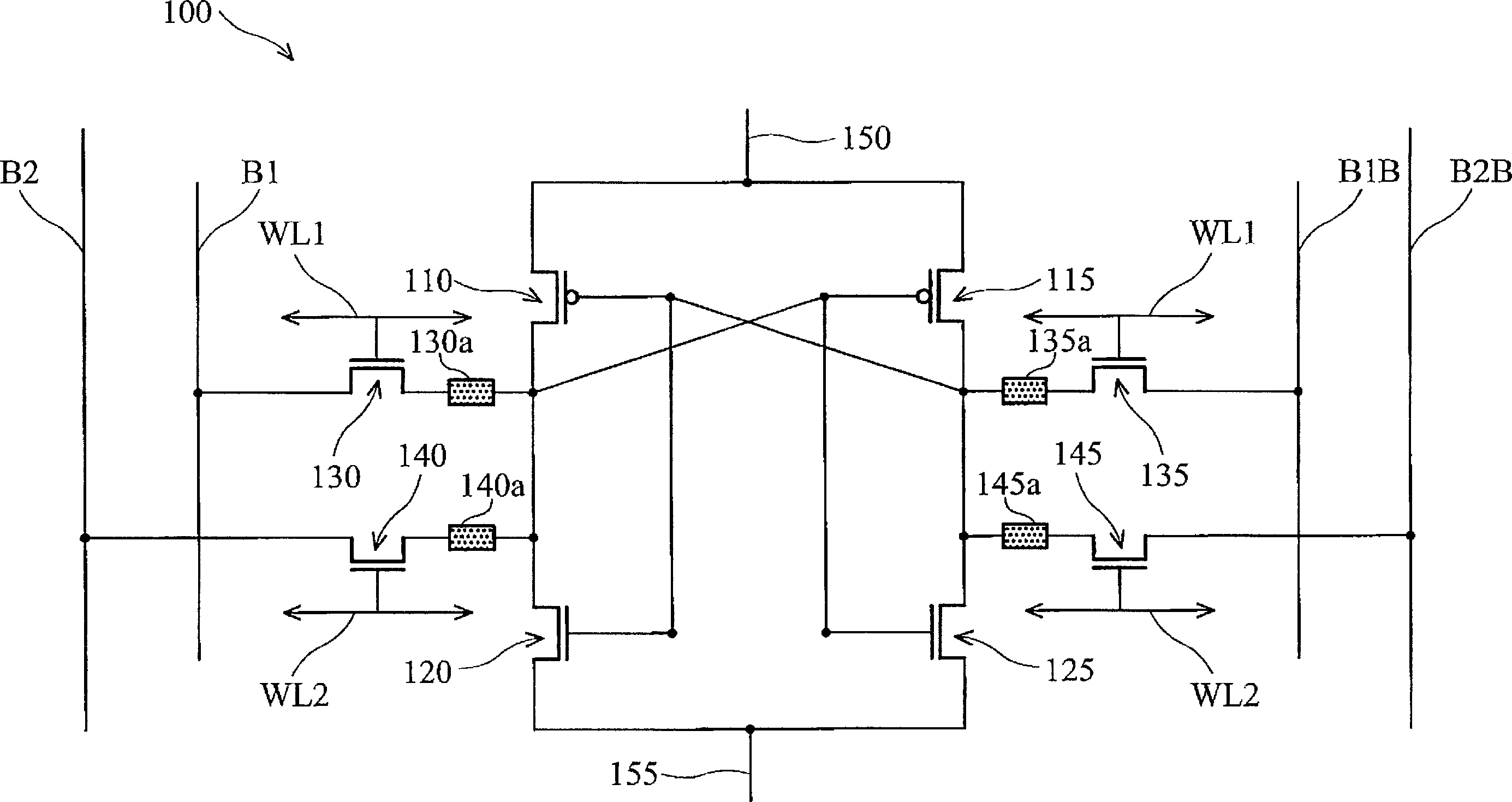

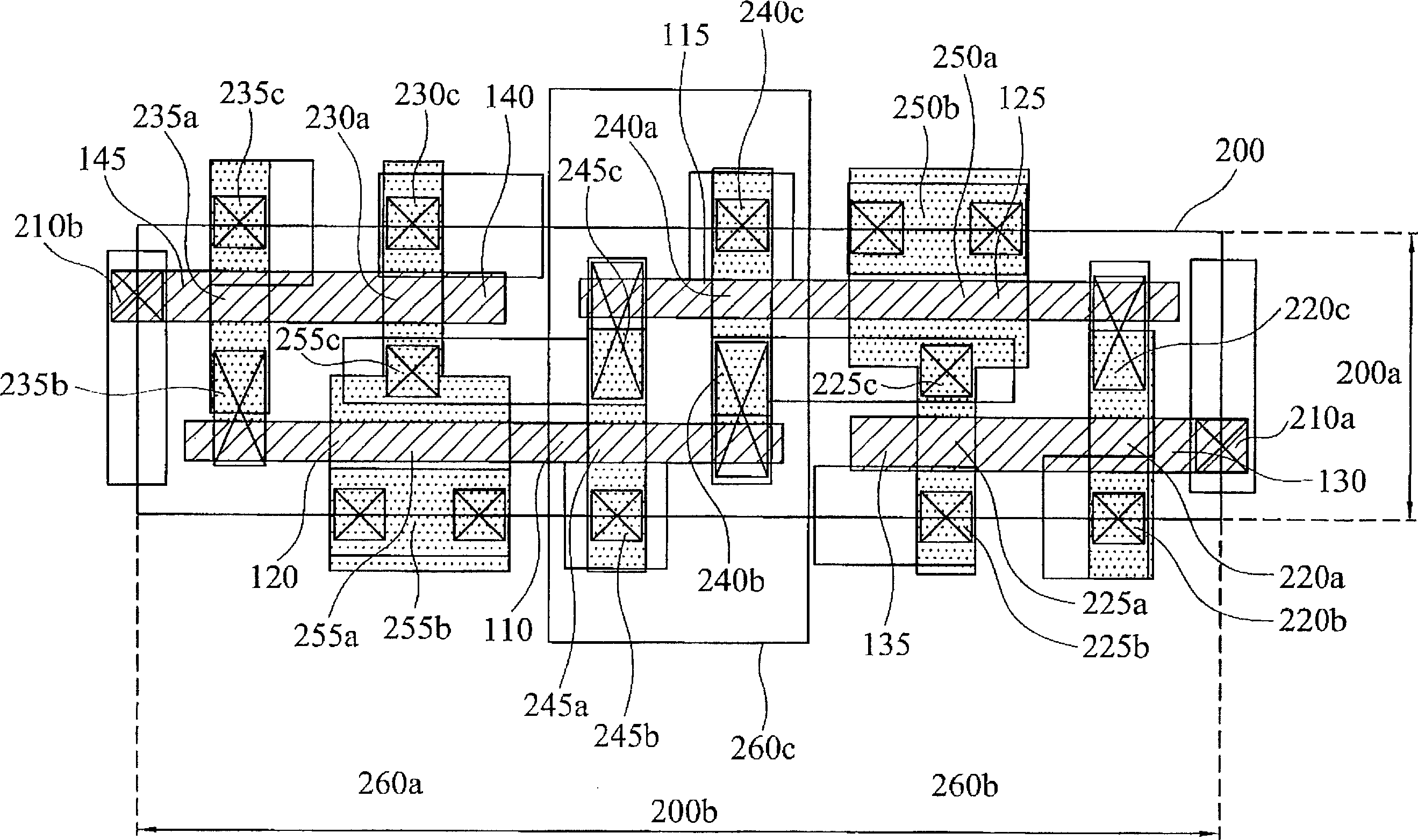

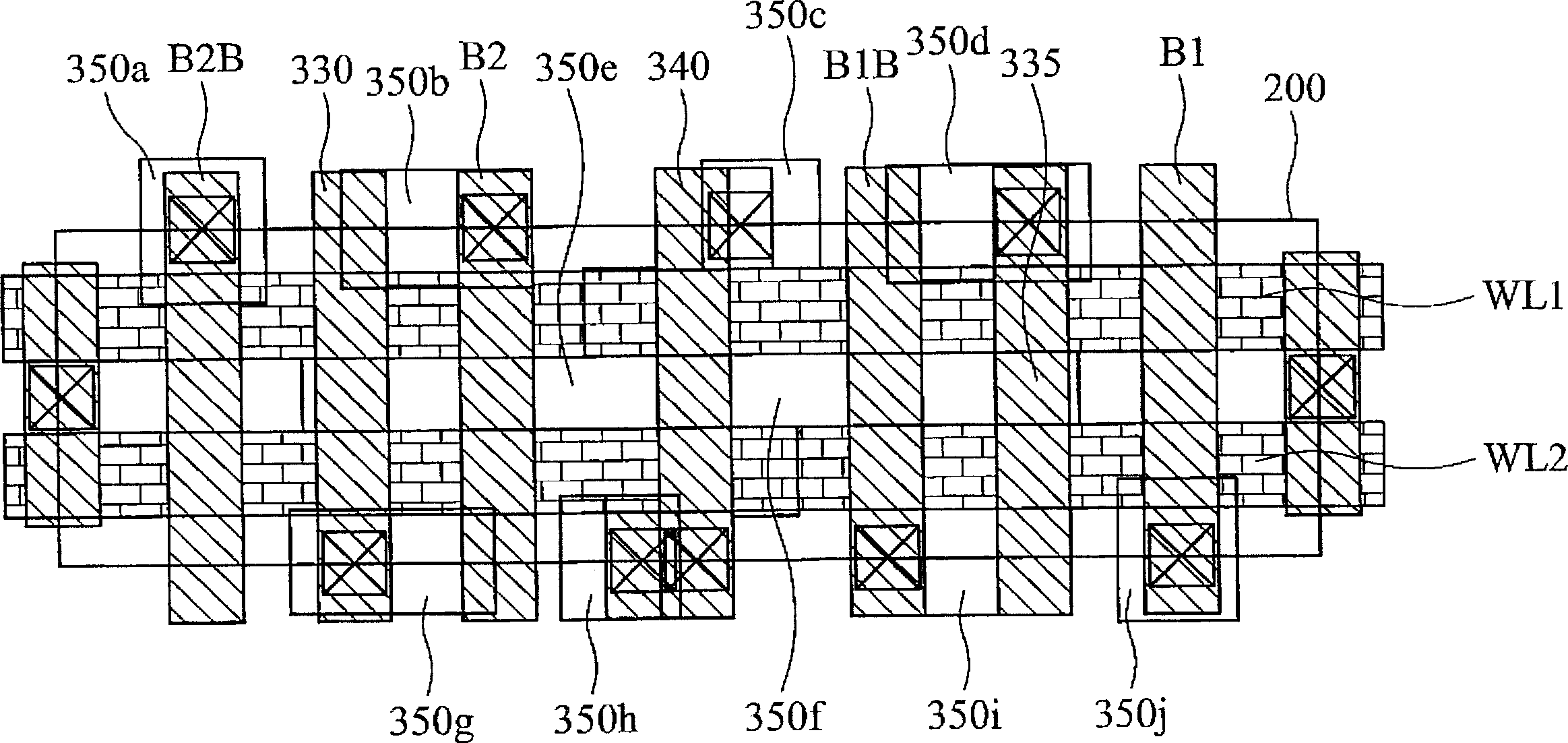

Memory device and dual port static RAM

ActiveCN1905063AReduce areaReduced resistance differenceTransistorSolid-state devicesElectricitySignal lines

Disclosed is a memory device and dual port static RAM. The memory device comprises a memory cell arrays, at least two signal lines and a interleaving region. The memory cell arrays comprise a plurality of memorizers arranged in lines or in rows wherein each line or row is provided with several memorizers. The signal lines extend along one line of the memorizers, and are electrically connected with the first end and the second end of each memorizers. The interleaving region is associated with each line, and the second signal line in the first line crosses the first interleaving region. The memory device and dual port static RAM according to the invention can reduce the resistance difference and circuit area, improve the efficiency and mass production.

Owner:TAIWAN SEMICON MFG CO LTD

LCD (liquid crystal display) panel and manufacturing method thereof

InactiveCN102360145AImprove the display effectAvoid display unevennessSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayDielectric layer

The invention discloses an LCD (liquid crystal display) panel and a manufacturing method thereof. The LCD panel comprises a first border scanning line, a first dielectric layer and a second border scanning line, wherein the first border scanning line is manufactured in a border area, the first border scanning line and gate lines are formed in a same photoetching step, and the first border scanning line is connected with part of thin-film transistors by a corresponding grid line; the first dielectric layer covers the first border scanning line; the second border scanning line is arranged on the surface of the first dielectric layer, and connected with the gate electrodes of remaining thin-film transistors by remaining gate lines; and the first border scanning line and the second border scanning line are made of a same metal material. In the invention, the widths and thicknesses of the two layers of scanning lines can be designed to be same, and because the developing and photoetching conditions are same, the widths of the two layers of scanning lines subjected to photoetching are more consistent, so that the resistances of the two layers of scanning lines are closer, thereby avoiding the occurrence of a situation that horizontal stripes are displayed non-uniformly; and under the premise of narrowing a border of the LCD panel, the display effect of the LCD panel is improved.

Owner:TRULY SEMICON

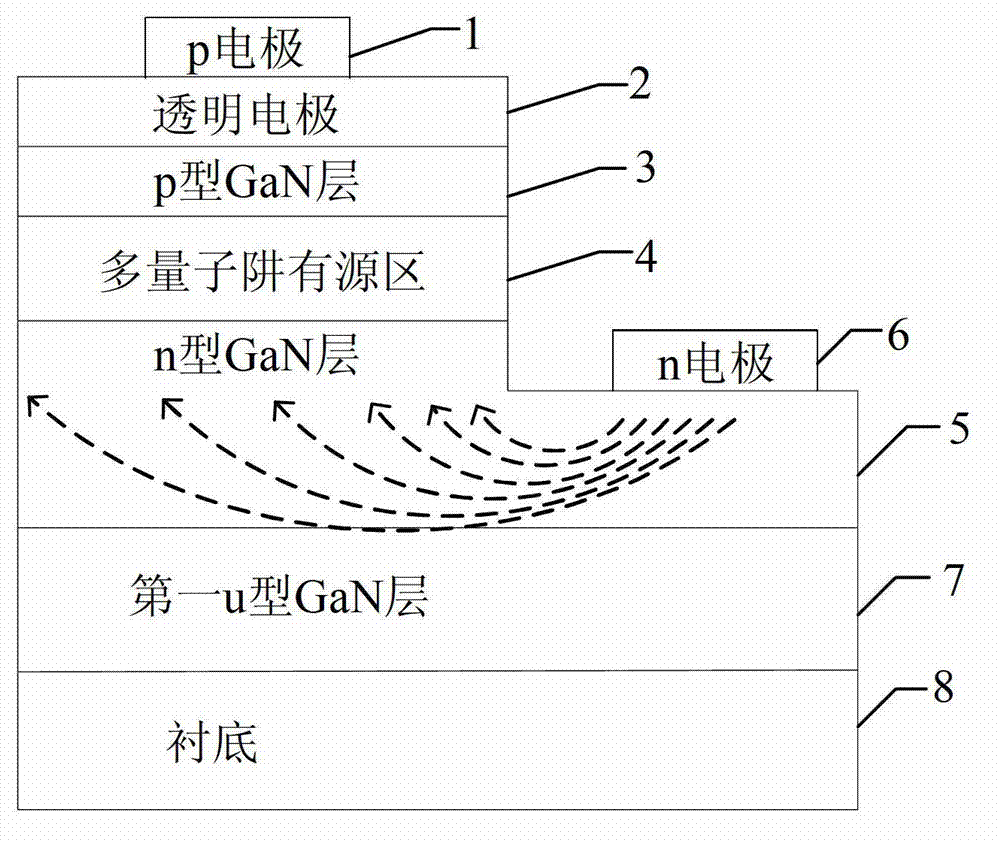

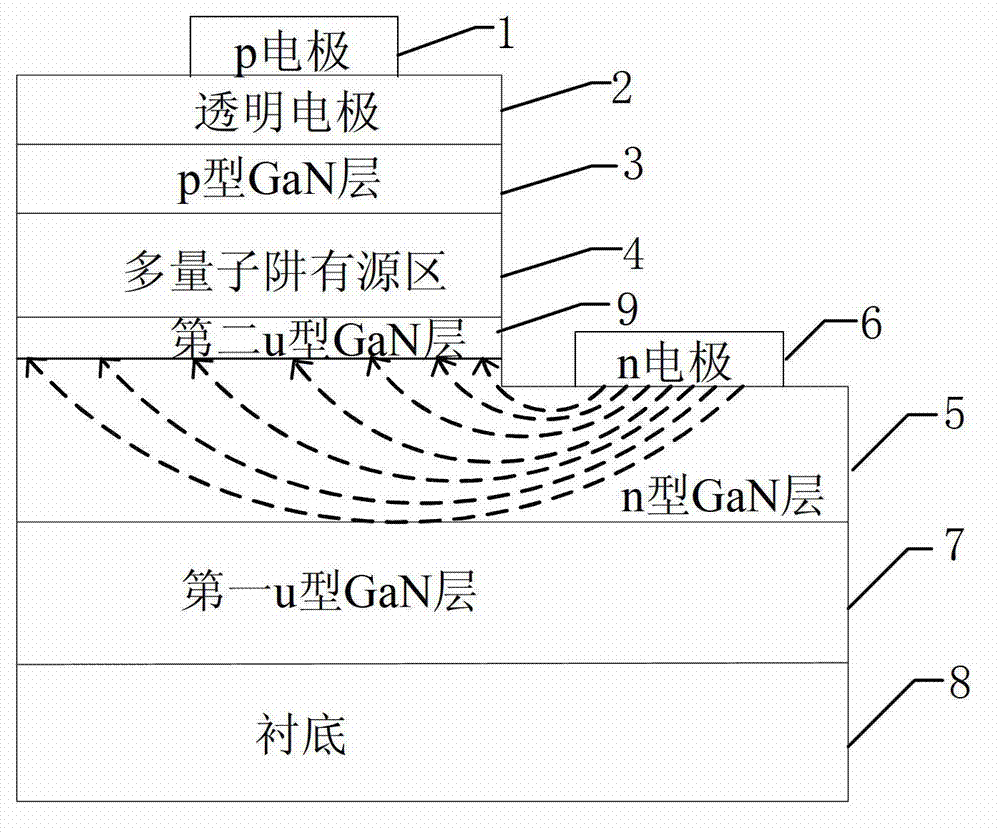

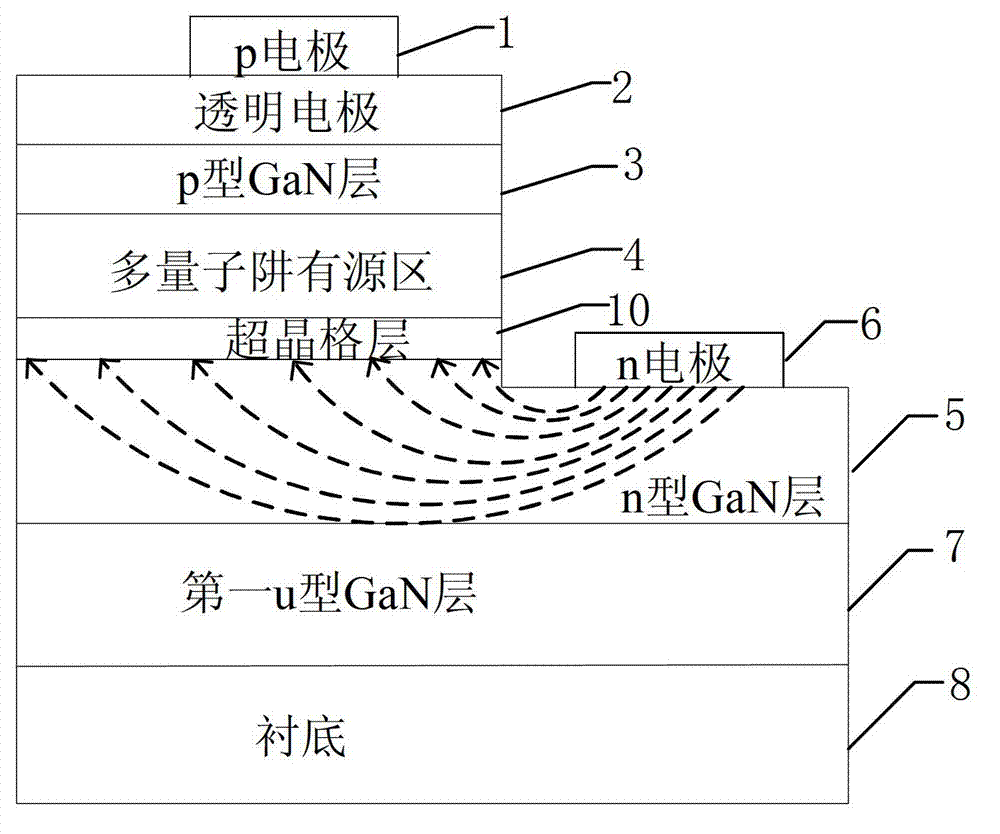

Gallium nitride (GaN) base light-emitting diode (LED) structure and method for improving photoelectric conversion efficiency thereof

InactiveCN103094441ALower forward voltageReduced resistance differenceSemiconductor devicesReverse currentGallium nitride

The invention relates to the field of photoelectric devices, in particular to a Gallium nitride (GaN) base light-emitting diode (LED) structure. The GaN base LED structure sequentially comprises a p electrode, a transparency electrode, a p type GaN layer, a multiple quantum well active area and an n type GaN layer from top to bottom. An n electrode, a first u type GaN layer and a substrate are etched on the n type GaN layer. A second u type GaN layer or a superlattice layer which is formed by a u type AlxGal-xN layer and low doping n type GaN in an alternate growing mode is inserted into between the multiple quantum well active area and the n type GaN layer. An x indicates the aluminous ingredient of the AlxGal-xN, and the value range of the x is that 0<=x<=1. Correspondingly, the invention further provides a method for improving the photoelectric conversion efficiency of the GaN base LED structure. Therefore, the transverse resistance difference of the GaN base LED structure is removed or reduced, so that currents can be expanded, forward voltages can be lowered, reverse currents are reduced, a luminous area is enlarged, and thus the photoelectric conversion efficiency of an LED is improved.

Owner:AQUALITE CO LTD

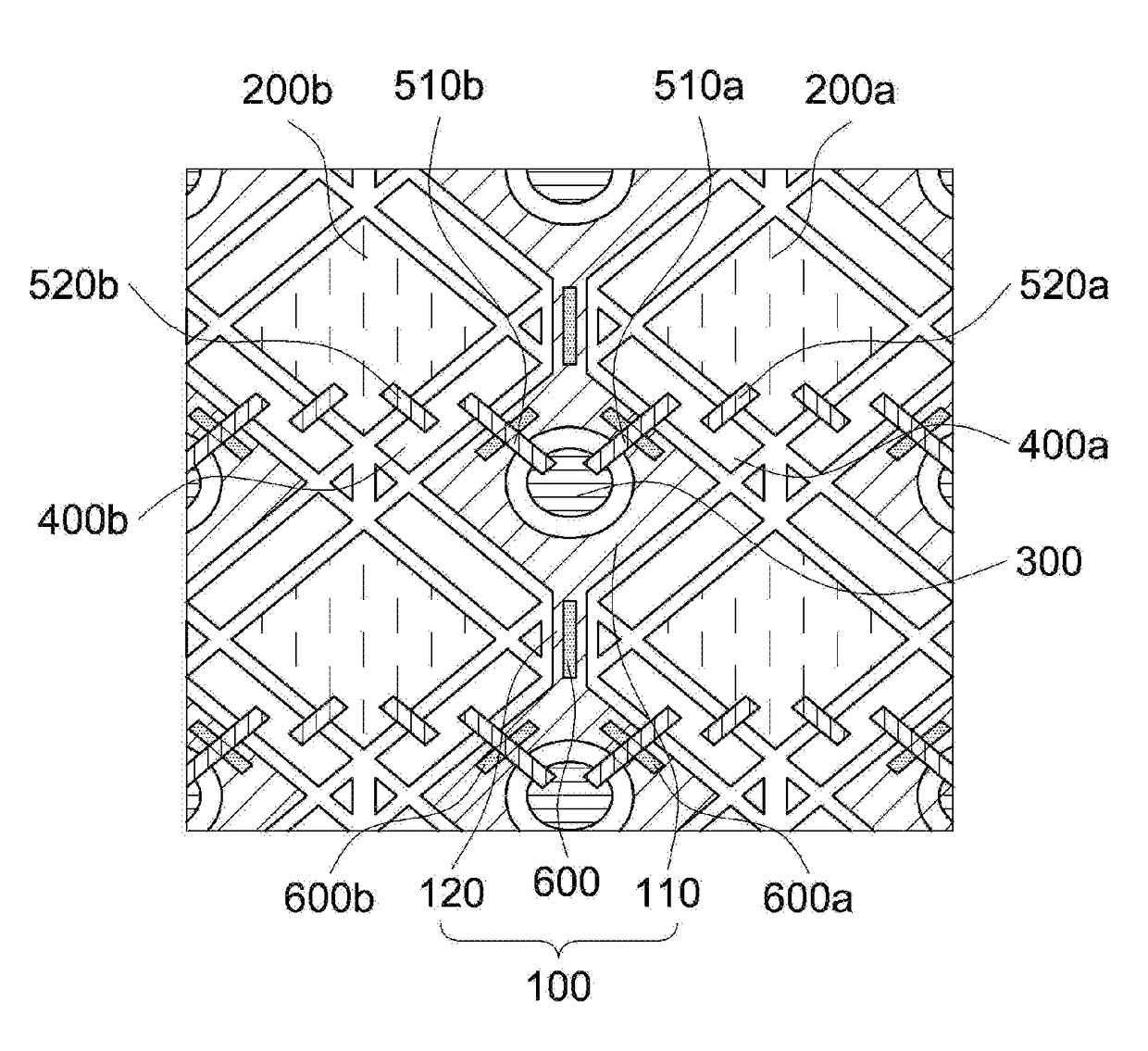

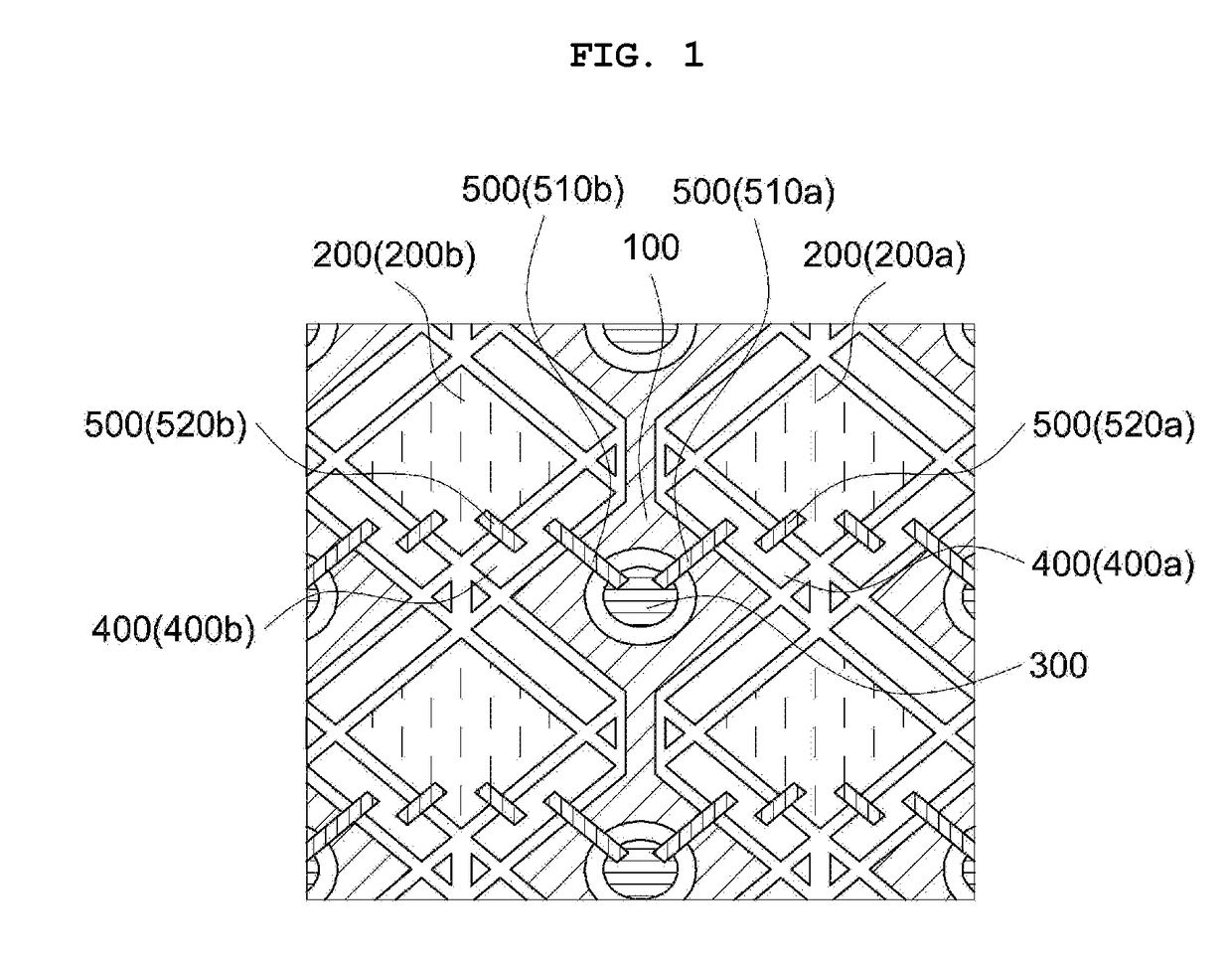

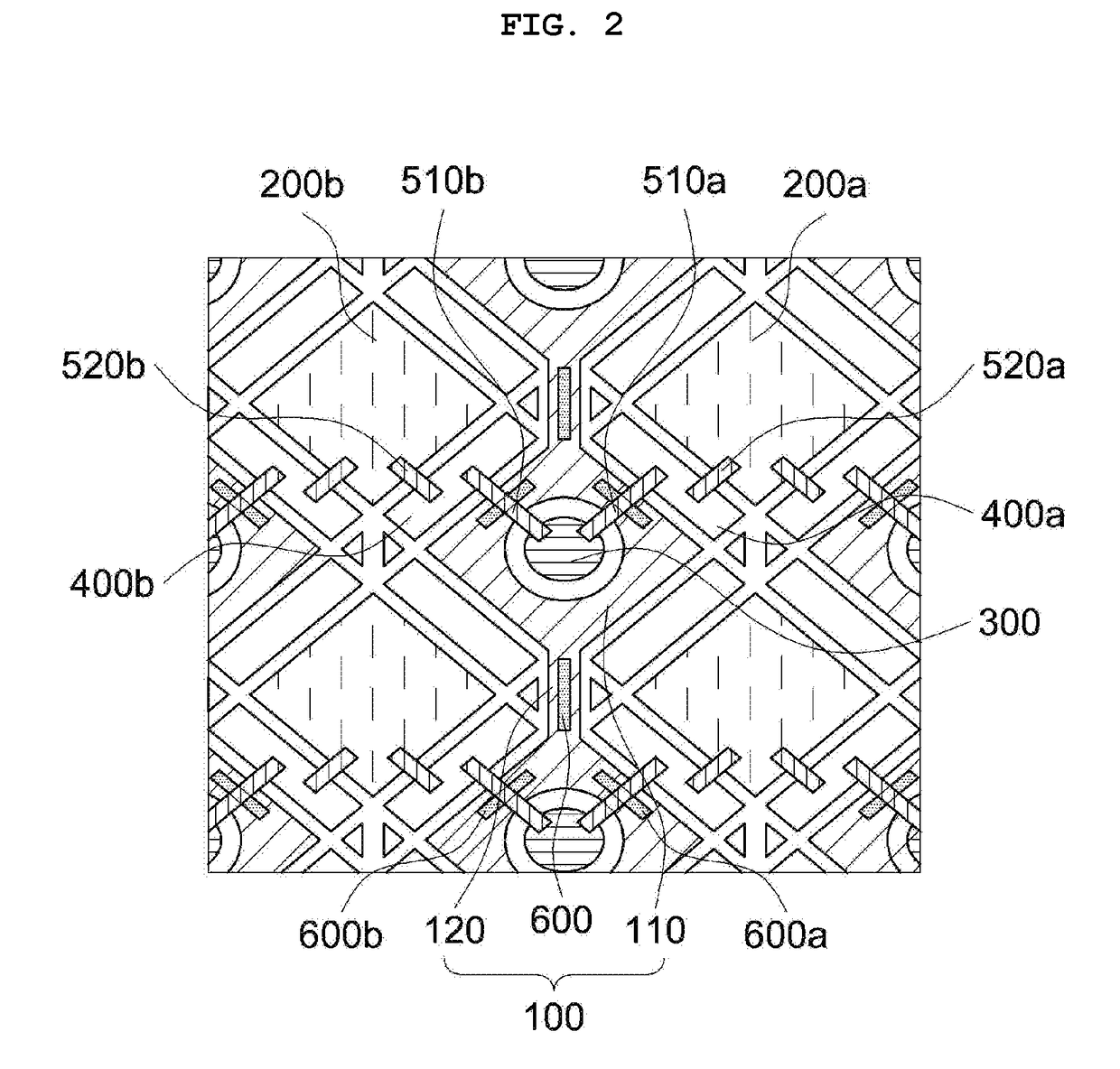

Touch panel and image display device including the same

ActiveUS20170147132A1Reduce resistance deviationMaintain electrical connectionInput/output processes for data processingTouch panelEngineering

A touch panel comprises a substrate and a touch sensing electrode formed on at least one surface of the substrate. The touch sensing electrode includes a first sensing pattern formed in a first direction, a second sensing pattern formed in a second direction, a first relay pattern formed at an inside of the first sensing pattern in an island form, a second relay pattern formed between the first sensing pattern and the second sensing pattern, and a connection pattern which electrically connect separated unit patterns of the second sensing pattern via the first relay pattern and the second relay pattern. The connection pattern includes a first connection pattern which connects the first relay pattern and the second relay pattern, and a second connection pattern which connects the second relay pattern and the unit pattern of the second sensing pattern.

Owner:DONGWOO FINE CHEM CO LTD

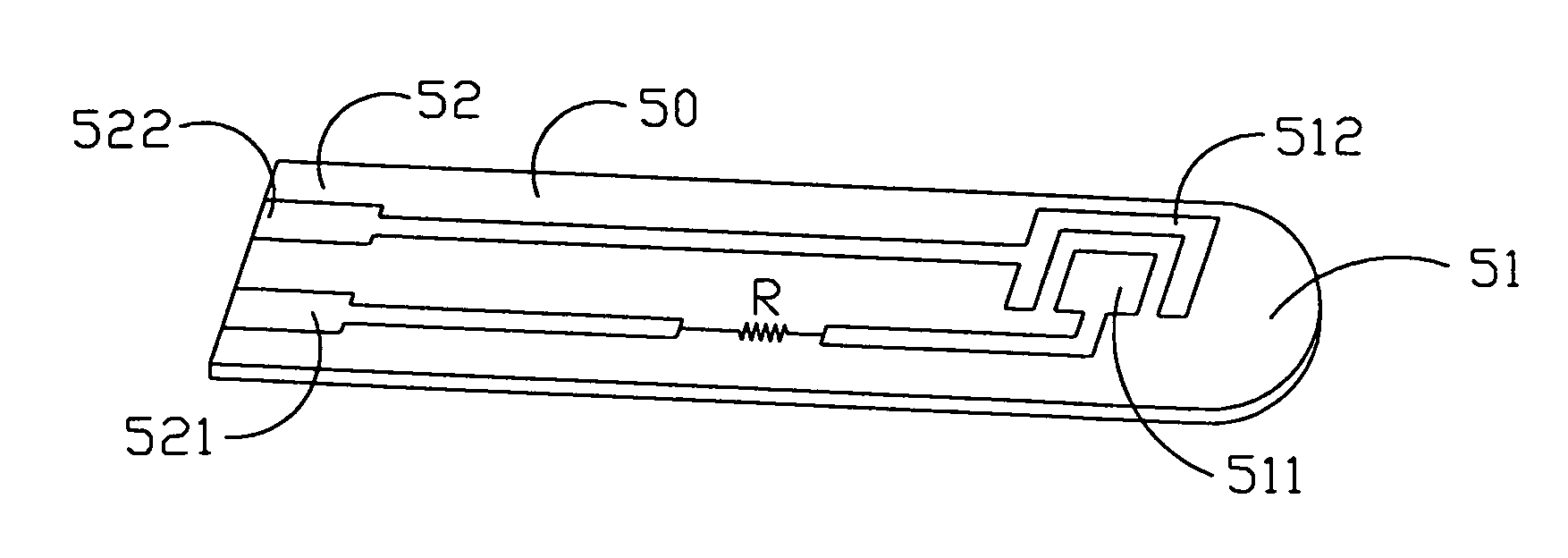

Chip with measuring reliability and a method thereof

ActiveUS7374721B2Improve chip reliabilityImprove measurement reliabilityImmobilised enzymesBioreactor/fermenter combinationsElectrical resistance and conductanceResistor

A chip with measuring reliability and a method thereof are provided. The present invention serially connects a resistor having a resistance equal to or a little more than a maximum resistance of the chip itself to the resistor Rs of the chip so as to compensate the resistance differences among chips. A noise to signal (N / S) ratio of the chip is decreased, and a measuring reliability of the chip is improved.

Owner:INTELLECTUAL VENTURES I LLC

Organic electroluminescent display, and prepartion method

ActiveCN1917227ALower column lead resistanceImproved display brightness and display uniformityElectroluminescent light sourcesSolid-state devicesOrganic electroluminescenceAuxiliary electrode

The display includes transparent substrate, first electrode, organic functional layer, second electrode, and auxiliary electrode setup on first electrode. The auxiliary electrode includes the covering metal layer in low resistance on column lead wire and row lead wire of transparent electrode outside zone of luminosity. Characters are that the auxiliary electrode further includes the covering metal layer in low resistance inside gap area of luminescence pixels on first electrode inside zone of luminosity. Resistance of the metal in low resistance is smaller than resistance of first electrode. The first electrode is a transparent electrode. Reducing difference of resistance between resistance of column lead wire and resistance of different area inside zone of luminosity effectively, the disclosed display of organic electroluminescence improves display brightness and display evenness.

Owner:KUNSHAN VISIONOX DISPLAY TECH

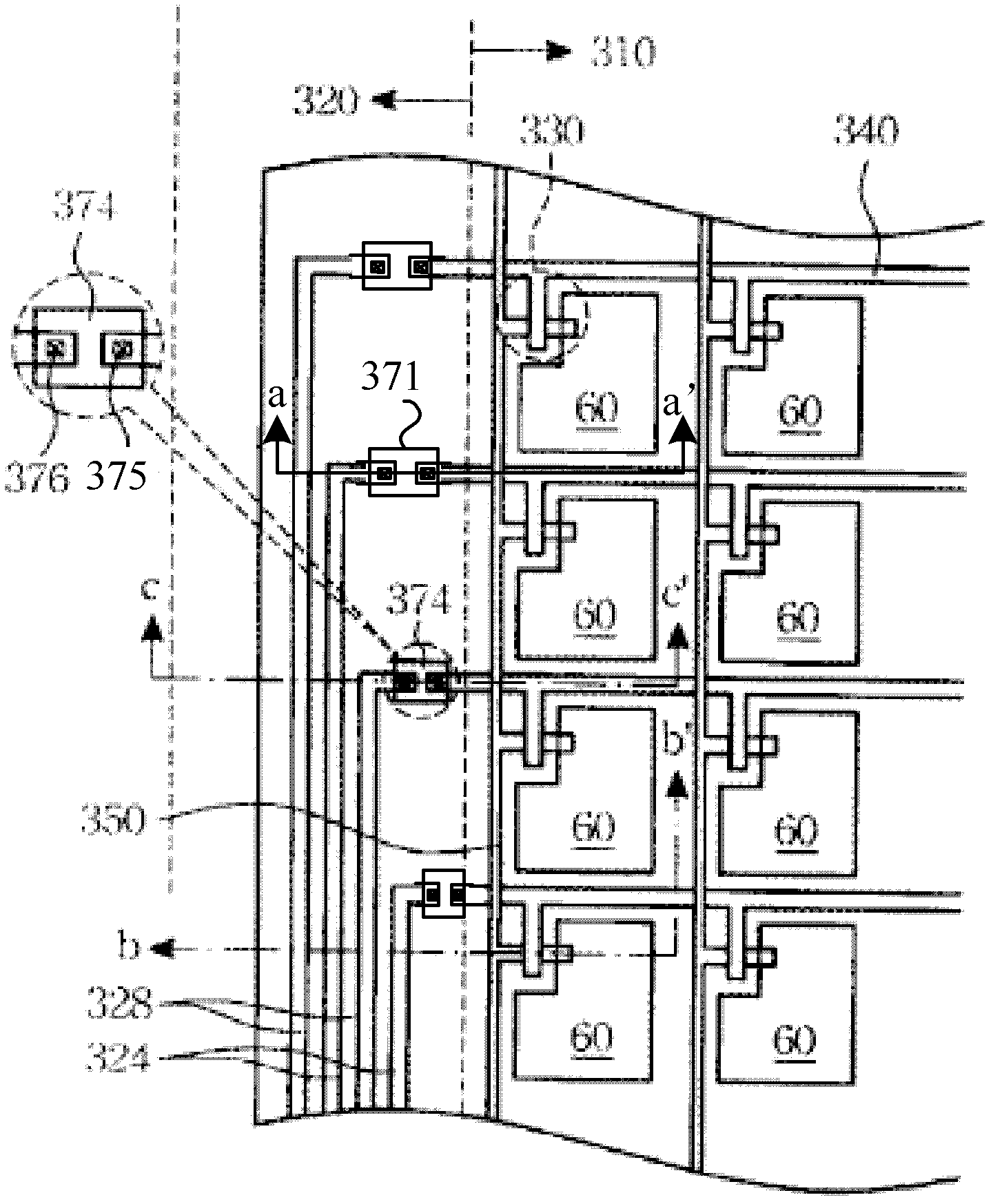

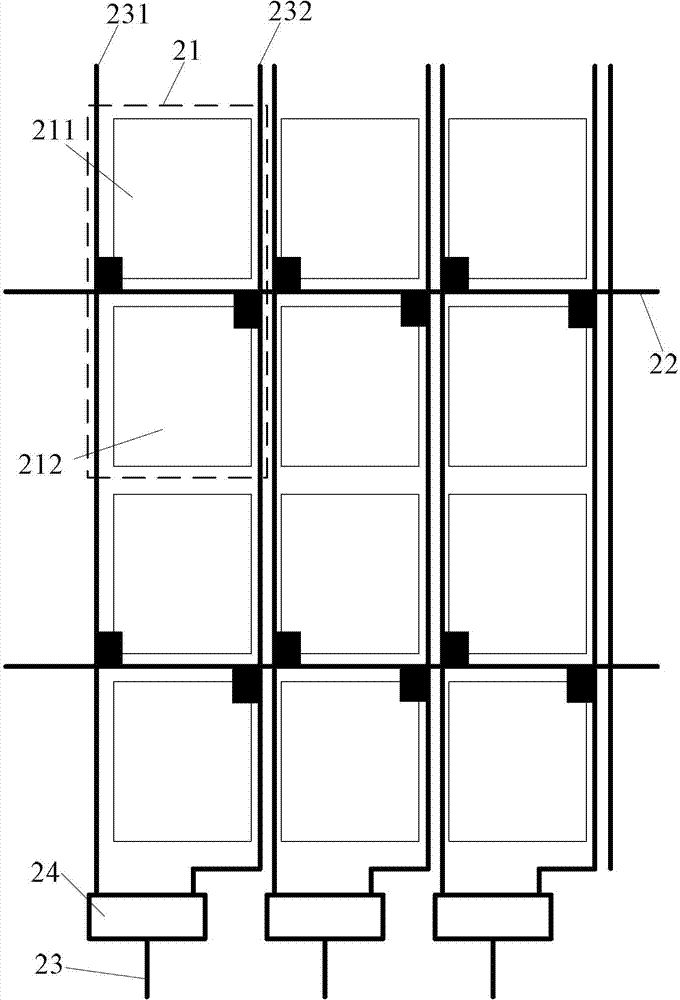

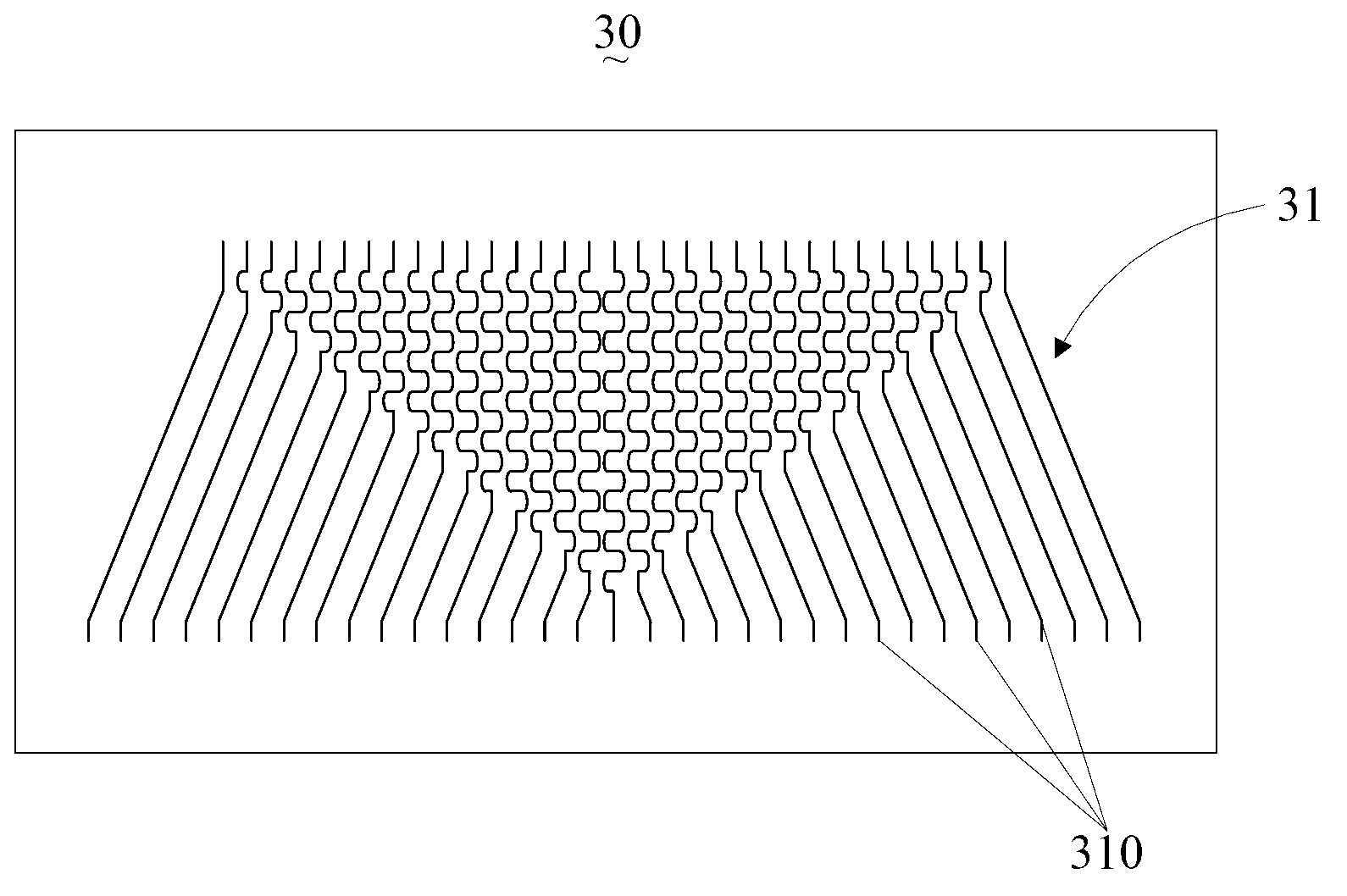

Fan-out line structure, display apparatus comprising same, and fan-out line wiring method

InactiveCN106169456ASave wiring spaceReduced resistance differenceSemiconductor/solid-state device detailsSolid-state devicesLine structureSignal delay

The invention relates to a fan-out line structure, a display apparatus comprising the same, and a fan-out line wiring method. The fan-out line structure provided by the embodiments of the invention is used for signal connection between a first function area and a second function area, an intermediate-section channel at a channel wire outlet end of the first function area is a suspended channel, in the fan-out line structure, a wire from an effective signal channel closes to the suspended channel, of the first function area to the second function area extends to a center normal area of the suspended channel and then extends in the center normal area along the direction of a center normal. The fan-out line structure can reduce wiring space and reduces signal delay differences between wires.

Owner:BOE TECH GRP CO LTD +1

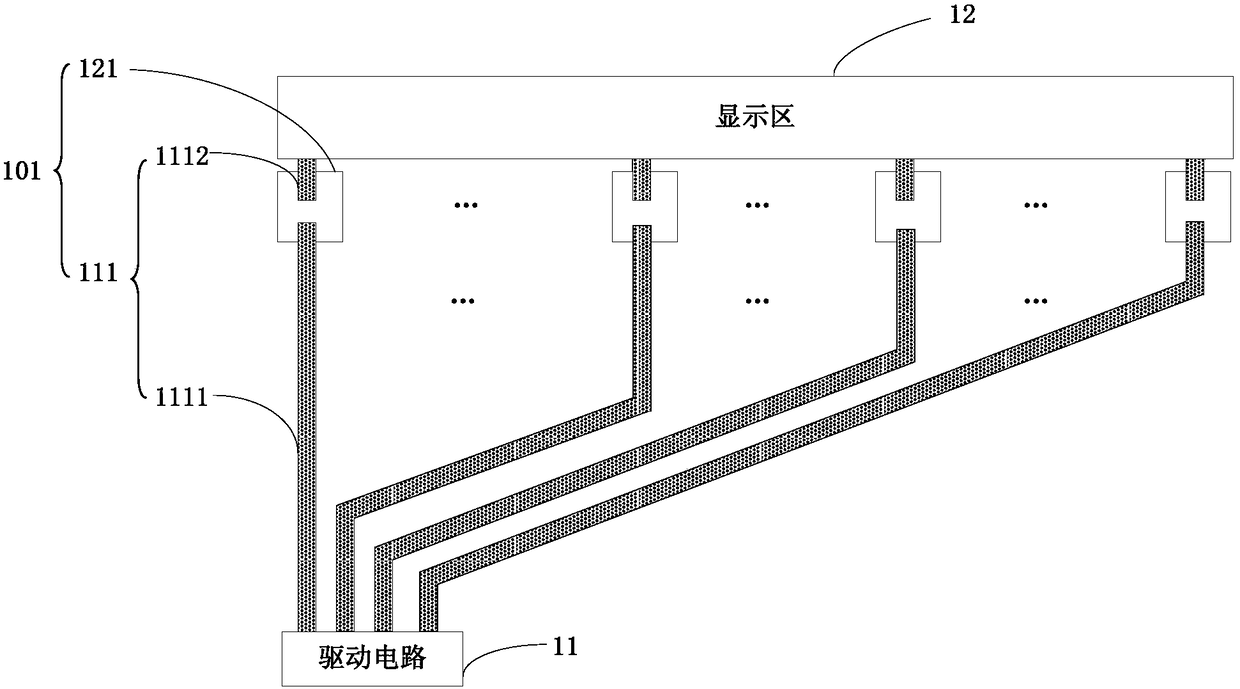

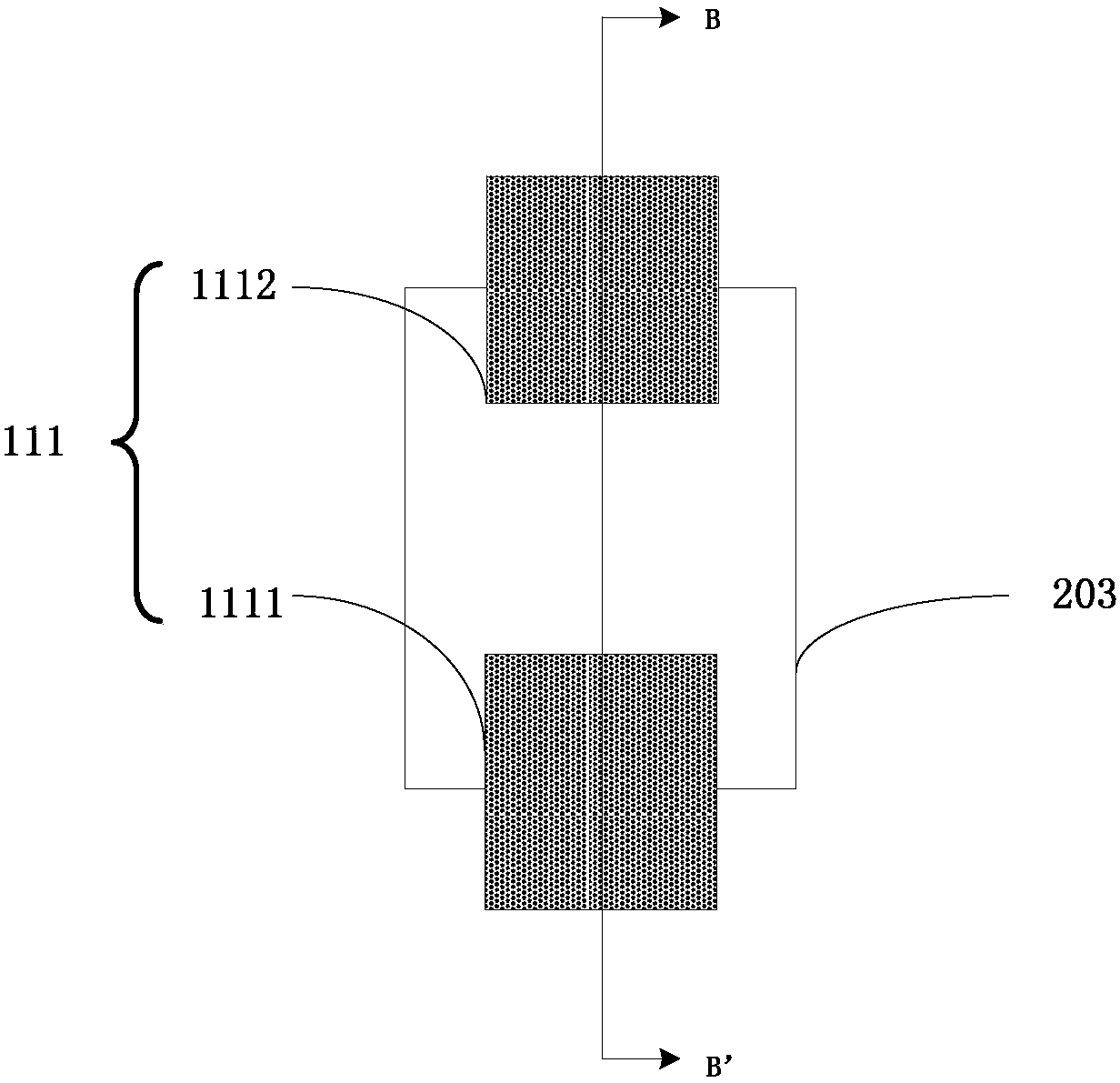

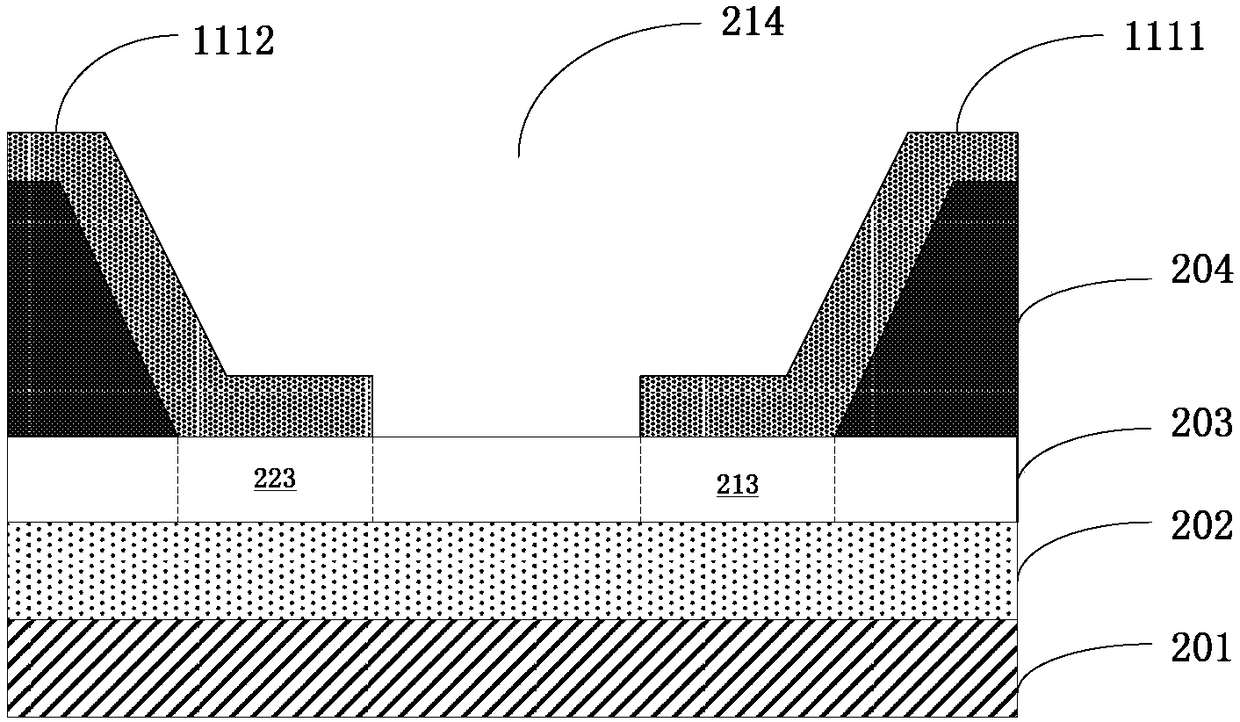

Fan-out structure and manufacturing method thereof and display panel

ActiveCN108258025AReduced resistance differenceSimple designSolid-state devicesSemiconductor/solid-state device manufacturingDriving circuitElectrical and Electronics engineering

The invention provides a fan-out structure and a manufacturing method thereof and a display panel, and relates to the technical field of display. The fan-out structure comprises multiple fan-out unitsused for connecting a driving circuit with a display area, wherein each fan-out unit comprises a fan-out line, at least one part of the fan-out units comprise resistance regulation units connected with the corresponding fan-out lines, and the resistance regulation units are configured to make resistance different values between the different fan-out units smaller than a first threshold value.

Owner:BOE TECH GRP CO LTD +1

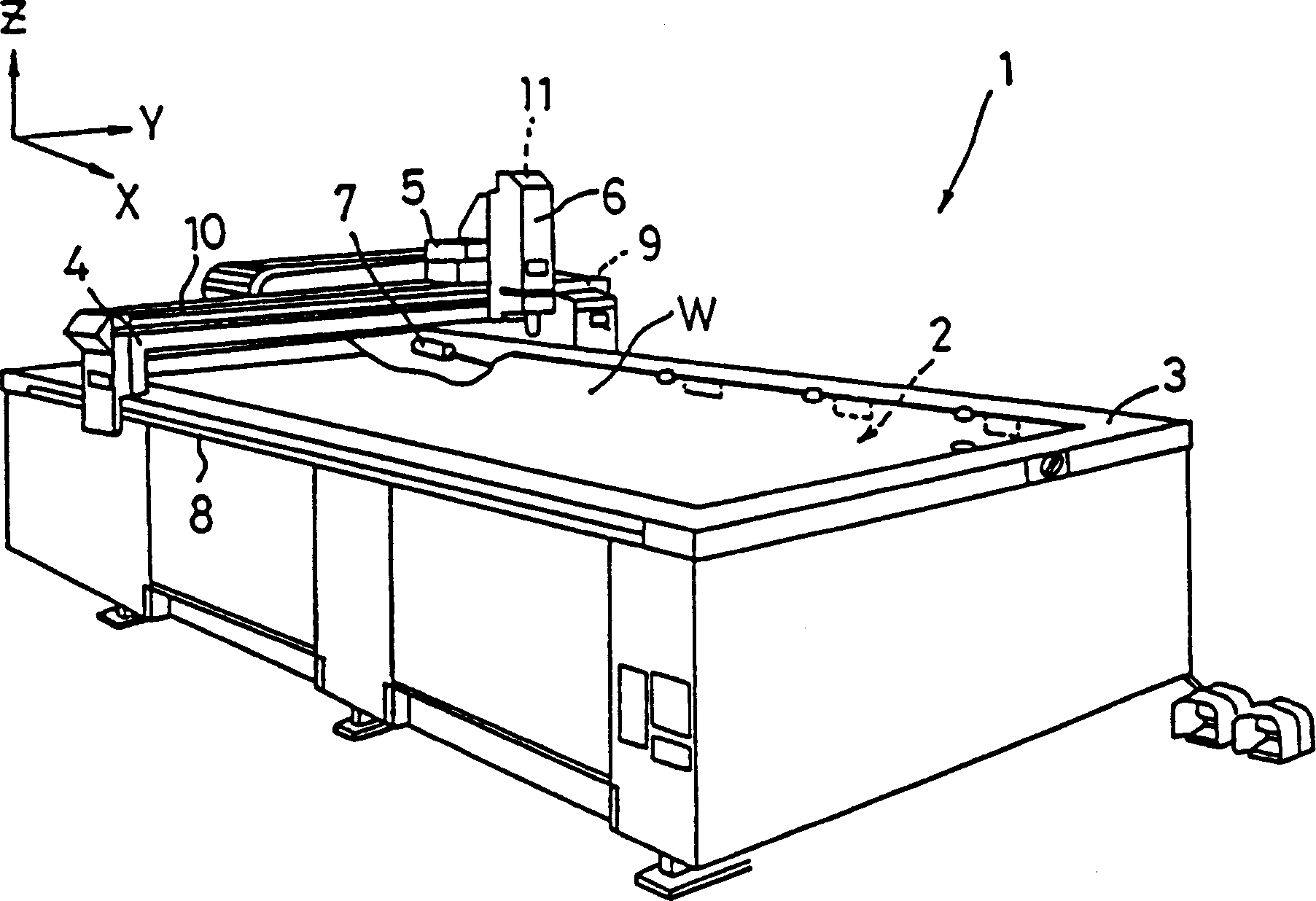

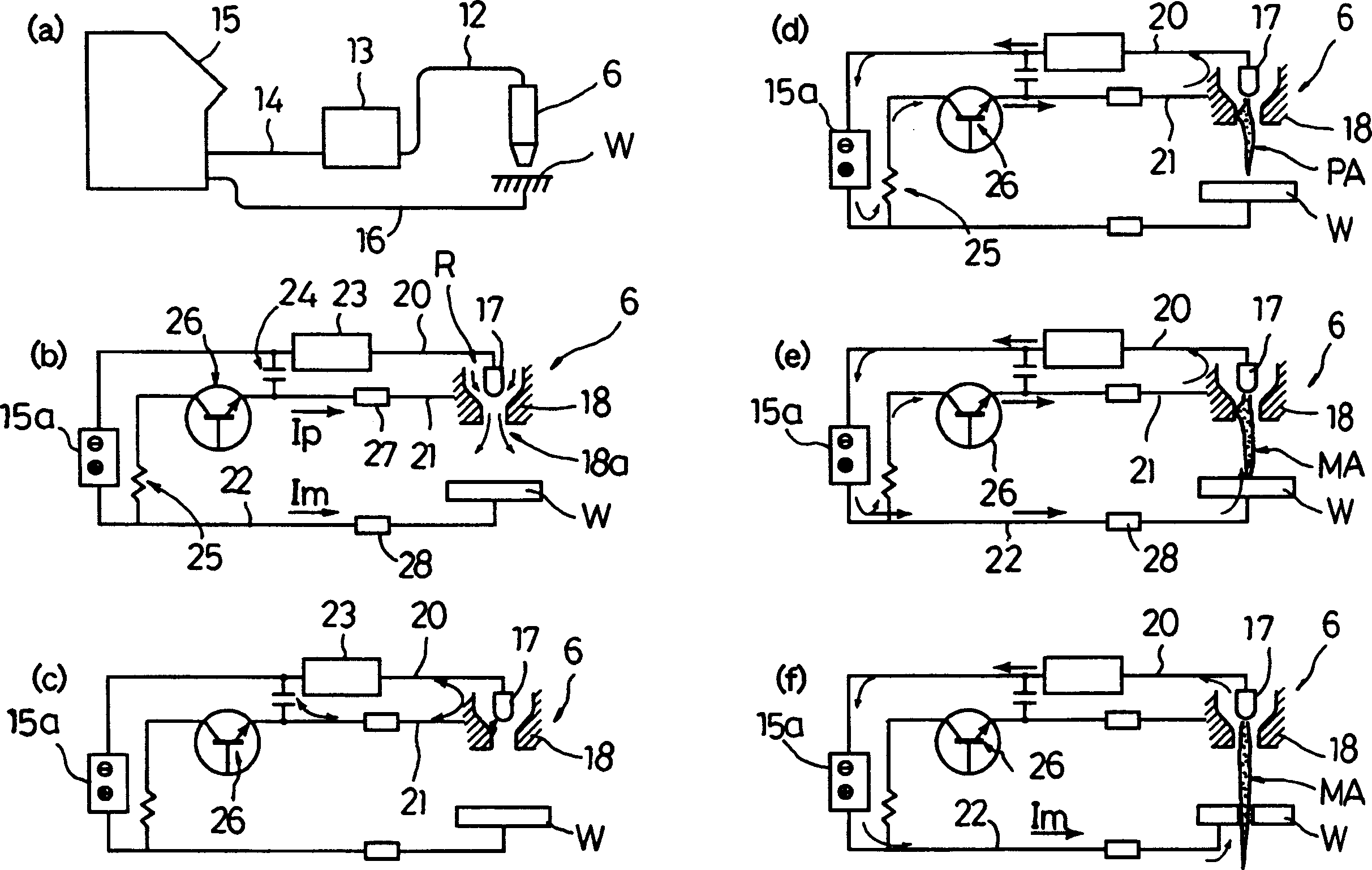

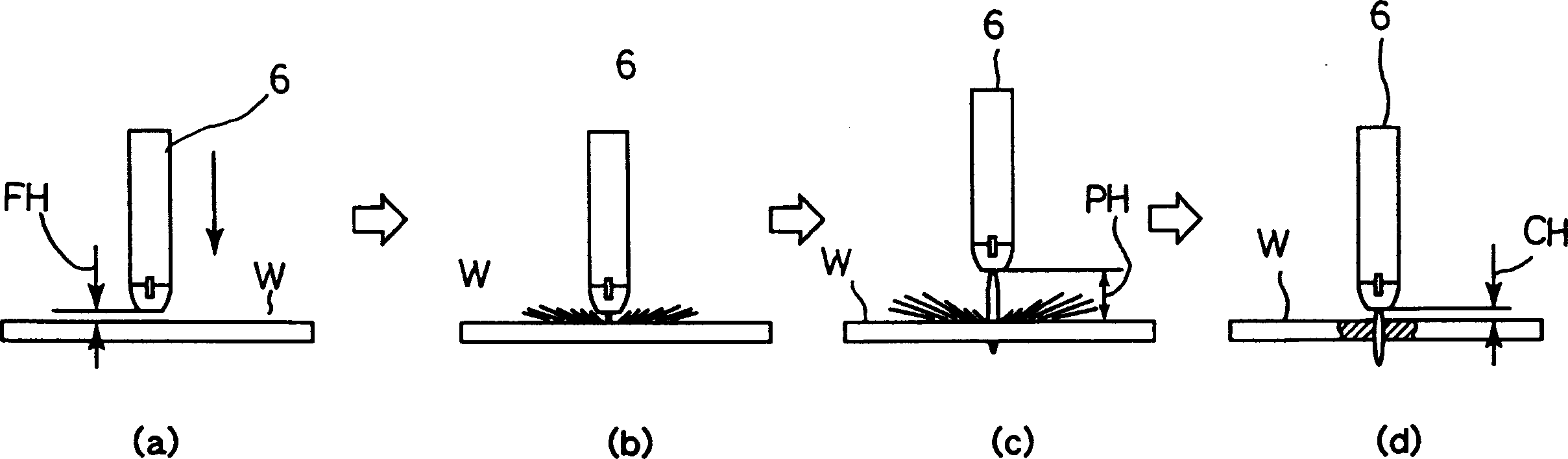

Plasma processing method

InactiveCN1507973AReduced resistance differenceInhibit deteriorationPlasma welding apparatusPlasma techniqueEngineeringPlasma processing

The plasma torch is positioned at an initial level which is the distance between the plasma torch and a steel plate when generating a plasma arc to start piercing operation and which has been set equal to a cutting level which is the distance between the plasma torch and the steel plate when carrying out cutting operation. After generation of the plasma arc, the plasma torch is immediately raised to a piercing level which is more distant from the steel plate W than the initial level and piercing operation is performed at the piercing level. After completion of the piercing operation, the plasma torch is lowered to the cutting level to start cutting operation. Just after transfer from a pilot arc into a main arc, a pilot current is cut off by turning a transistor off. Not only damage to a nozzle caused by spatter generated during piercing is prevented but also the deterioration of the nozzle owing to a pilot arc is restrained, whereby the service life of the nozzle is significantly increased.

Owner:KOMATSU SANKI

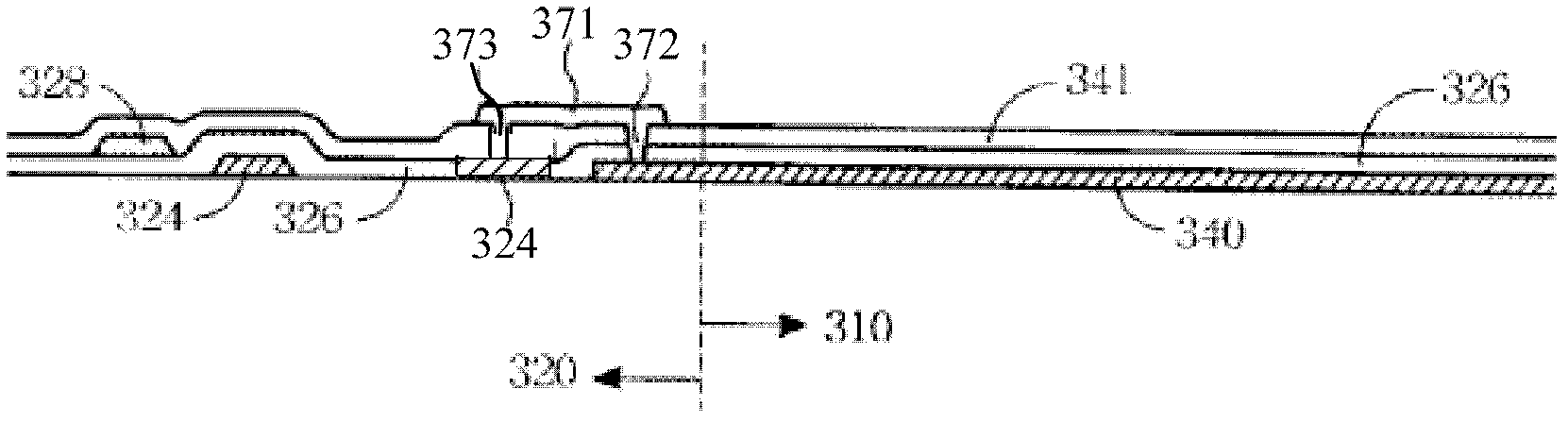

Fan-out, display substrate having the same and method for manufacturing the display substrate

ActiveUS8008665B2Reduced resistance differenceSemiconductor/solid-state device detailsSolid-state devicesTransistorElectrical and Electronics engineering

A display substrate having a fan-out and a method for manufacturing the display substrate are disclosed. The fan-out includes an insulating substrate, a first line, a second line, a resistance control pattern, and first and second detour pattern. The first line is disposed on the insulating substrate and is connected to a pad. The second line is formed from the same layer as the first line and is connected to a thin-film transistor (TFT). The resistance control pattern is formed from a different layer than the first and second lines. The first and second detour patterns are formed from a different layer than the first and second lines and the resistance control pattern, and connect the first and second lines with the resistance control pattern, respectively.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

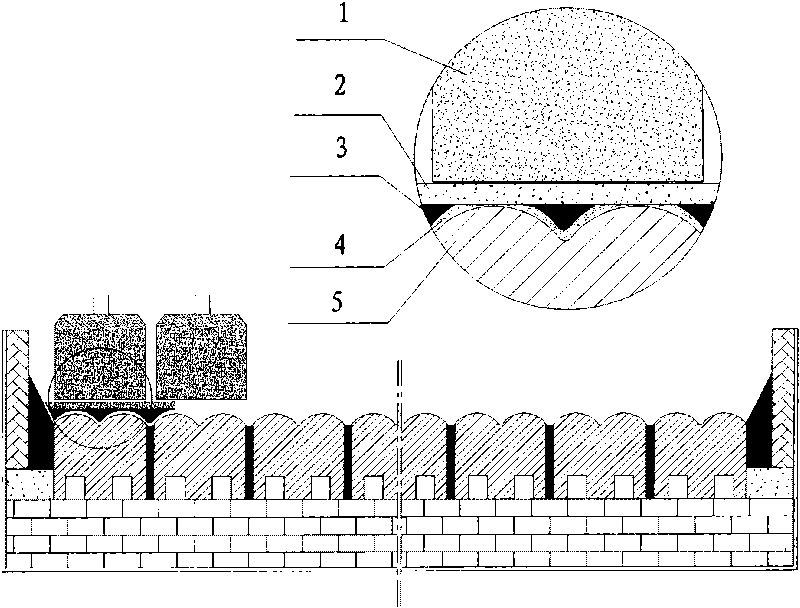

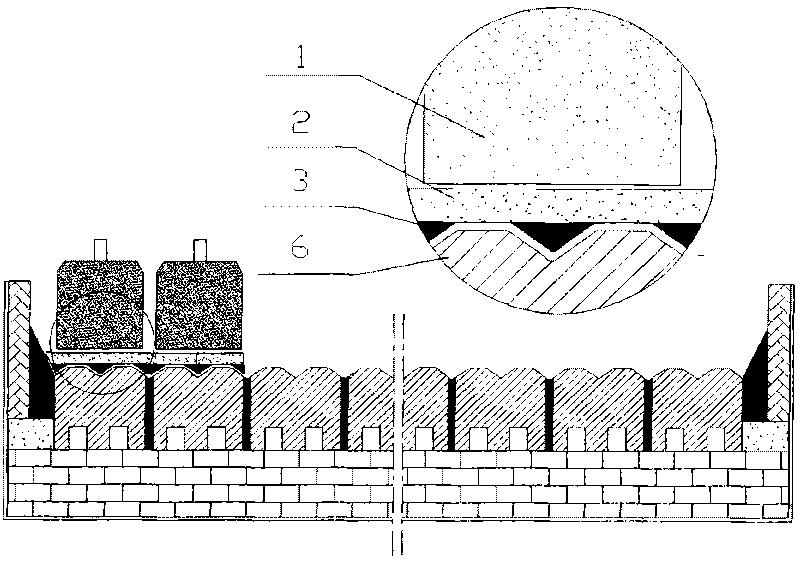

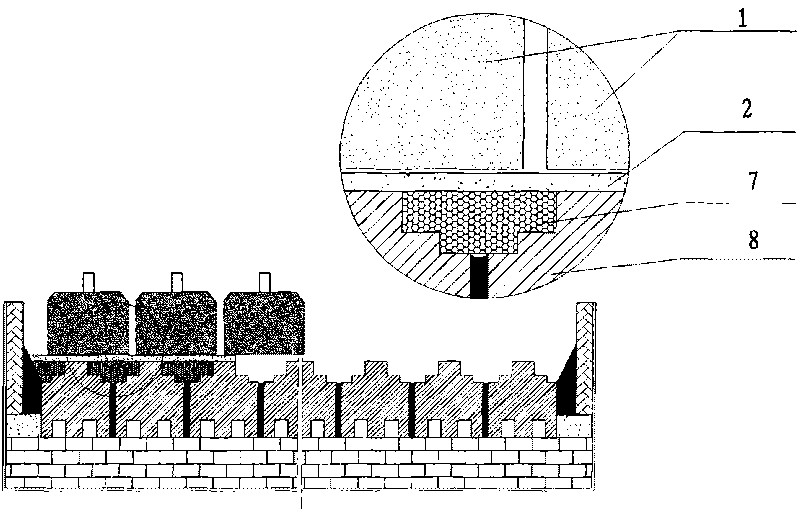

Method for roasting aluminum electrolytic bath with polymorphic structure cathode

InactiveCN101724859AAvoid thermal shockSolve the problem of uneven distribution of cathode currentThermal shockElectrolyte

The invention discloses a method for roasting an aluminum electrolytic bath with a polymorphic structure cathode, which comprises the following steps of: filling a concave part on the surface of the polymorphic structure cathode with aluminum powder or aluminum blocks with shapes corresponding to that of the concave part to ensure that the filled surface and a convex surface of the polymorphic cathode are in the same horizontal plane; paving a layer of coke particles on a plane of the cathode; hanging an anode on the layer of the coke particles, and electrifying and roasting the aluminum electrolytic bath until 60 to 70 percent of the area of the surface of the cathode reaches or exceeds 900 DEG C; and when over 60 percent of the area in the electrolytic bath has a fused electrolyte with the thickness of 10 centimeters, infusing the electrolyte into the electrolytic bath to perform a wet method or adopt a dry method to start the roasting. The aluminum block / powder-coke particle composite roasting technique is favorable for the even distribution of the current and the temperature on the surface of the cathode and the reduction of heat vibration, thereby not only preventing an aluminum liquid roasting method from performing thermal shock on an inner lining of the cathode, but also solving the problems of uneven distribution of the current of the cathode and the like caused by large differences of the coke particle thickness when the aluminum electrolytic bath with the polymorphic structure cathode singly adopts coke particle roasting, and improving the roasting quality of the inner lining of the cathode.

Owner:CENT SOUTH UNIV

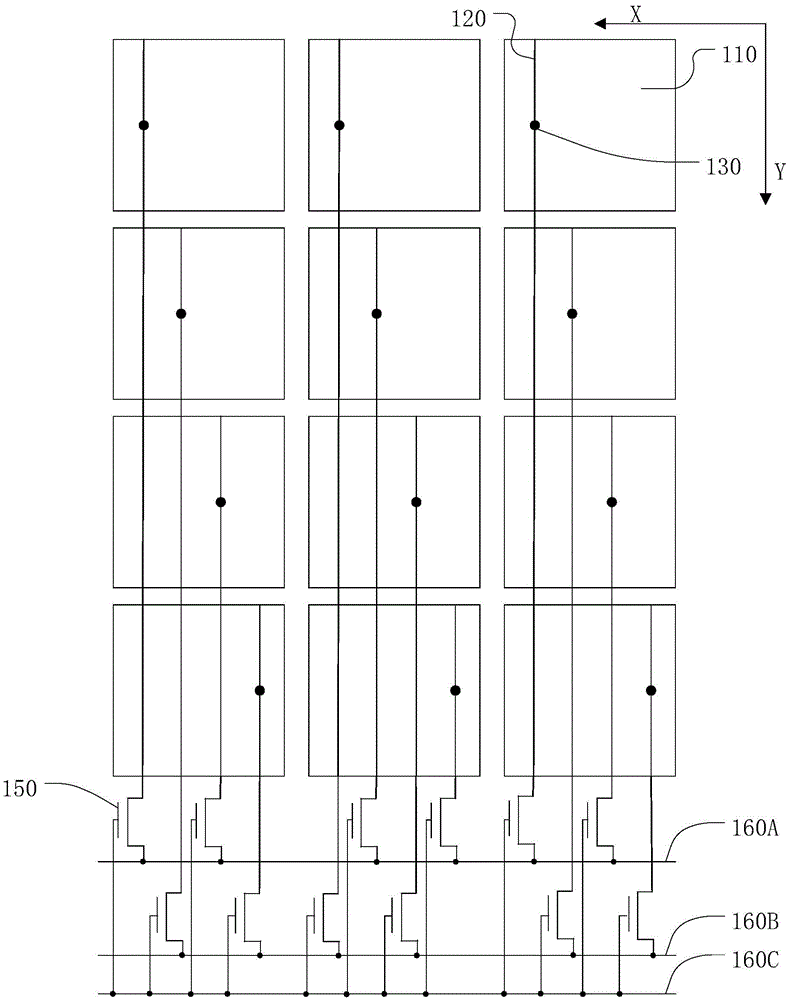

Pixel array substrate and display panel

InactiveUS20120306350A1Easy to optimizeReduced resistance differenceEngagement/disengagement of coupling partsDischarge tube luminescnet screensPixel arrayElectrical and Electronics engineering

A pixel array substrate includes a substrate, a plurality of pixel structures, a plurality of signal lines, a plurality of first traces, a plurality of second traces, a plurality of first conductive structures, and a plurality of second conductive structures. The pixel structures are arranged in array in a display region of the substrate. The signal lines are disposed in the display region and are formed in a first conducting wire layer and are electrically connected to the pixel structures. The first traces and the second traces are disposed in a periphery circuit region of the substrate and are respectively formed in a second conducting wire layer and the first conducting wire layer. A part of the signal lines are electrically connected to the first traces by the first conductive structures. Another of the signal lines are electrically connected to the second traces by the second conductive structures.

Owner:CHUNGHWA PICTURE TUBES LTD

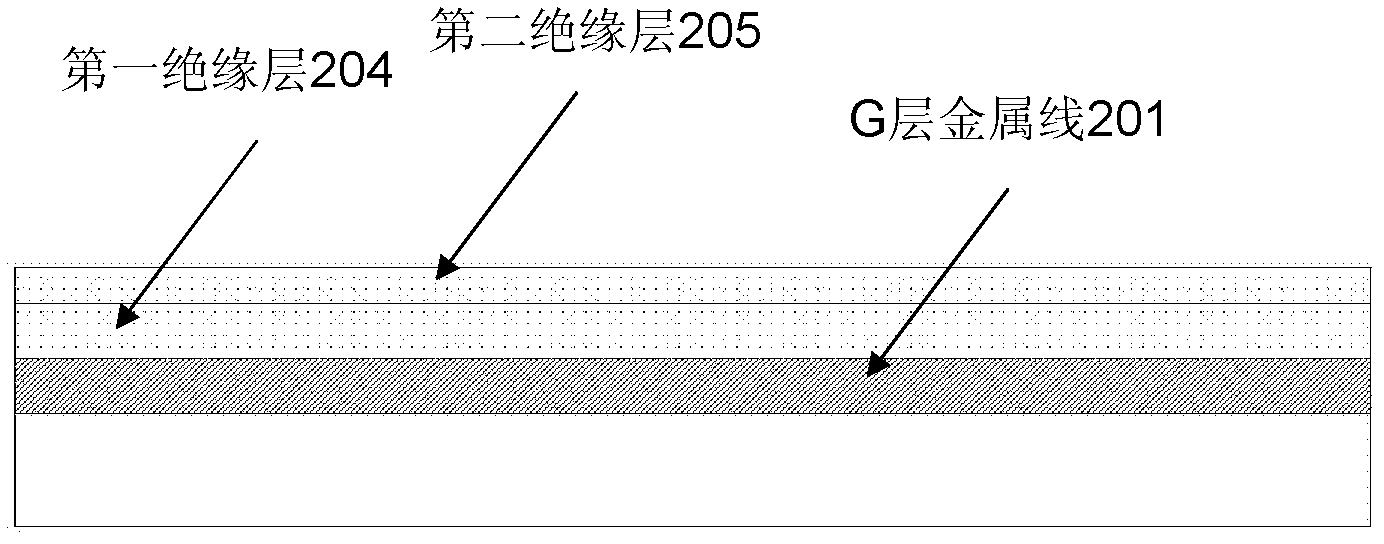

Wiring board and display apparatus

InactiveCN102667897AReduced resistance differenceStatic indicating devicesPrinted circuit aspectsEngineeringGate driver

Disclosed is a wiring board wherein the resistance difference among a plurality of drawn wiring lines is reduced. The wiring board has: a control region, which includes a plurality of gate wiring lines extending in the row direction, and a plurality of source wiring lines extending in the column direction; and a peripheral region, which includes a gate driver connected to the gate wiring lines, a source driver connected to the source wiring lines, and a plurality of drawn wiring lines, which are drawn along the outer periphery of the control region and connect the gate driver and the gate wiring lines. Each of the drawn wiring lines has a gate metal portion configured of the material of the gate wiring lines, and a source metal portion configured of the material of the source wiring lines. An insulating layer is disposed between the gate metal portion and the source metal portion, and the gate metal portion and the source metal portion are connected to each other through a contact section that penetrates the insulating layer.

Owner:SHARP KK

Wiring board and display apparatus

ActiveUS9078363B2Reduced resistance differenceStatic indicating devicesPrinted circuit aspectsEngineeringGate driver

Owner:SHARP KK

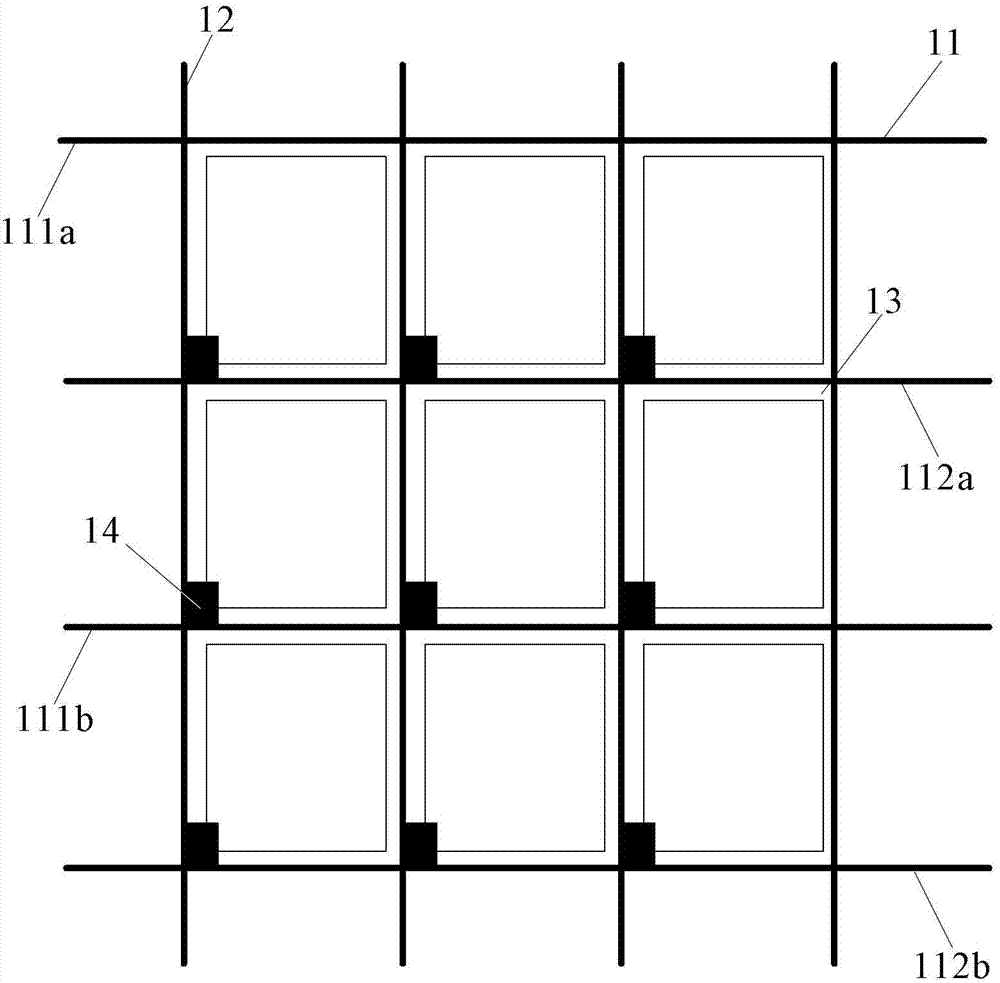

Array substrate, drive method of array substrate and display device of array substrate

ActiveCN103091920AAvoid bad phenomenaReduce the amount of wiringStatic indicating devicesSolid-state devicesDisplay deviceData lines

The invention provides an array substrate, a drive method of the array substrate and a display device of the array substrate, and relates to the technical field of display. The array substrate, the drive method of the array substrate and the display device of the array substrate are capable of avoiding that a horizontal line is poor, and improving yield of products of the display device of the array substrate. The array substrate comprises a plurality of pixel groups which are arranged in an matrix mode, a plurality of grid lines which correspond to the pixel groups and are transversely arranged, a plurality of columns of first data lines and a plurality of columns of second data lines, wherein the first data lines and the second data lines are lengthways arranged. Each pixel group comprises a first pixel unit and a second pixel unit. The first pixel unit and the second pixel unit are arranged on two adjacent lines. A grid line is respectively connected with a first pixel unit and a second pixel unit in a corresponding pixel group. A first data line is connected with the first pixel unit of the corresponding pixel group so as to provide data signals for the first pixel unit. A second data line is connected with the second pixel unit of the corresponding pixel group so as to provide data signals for the second pixel unit. The grid lines on the periphery of pixel units are formed by the same layer of metal.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

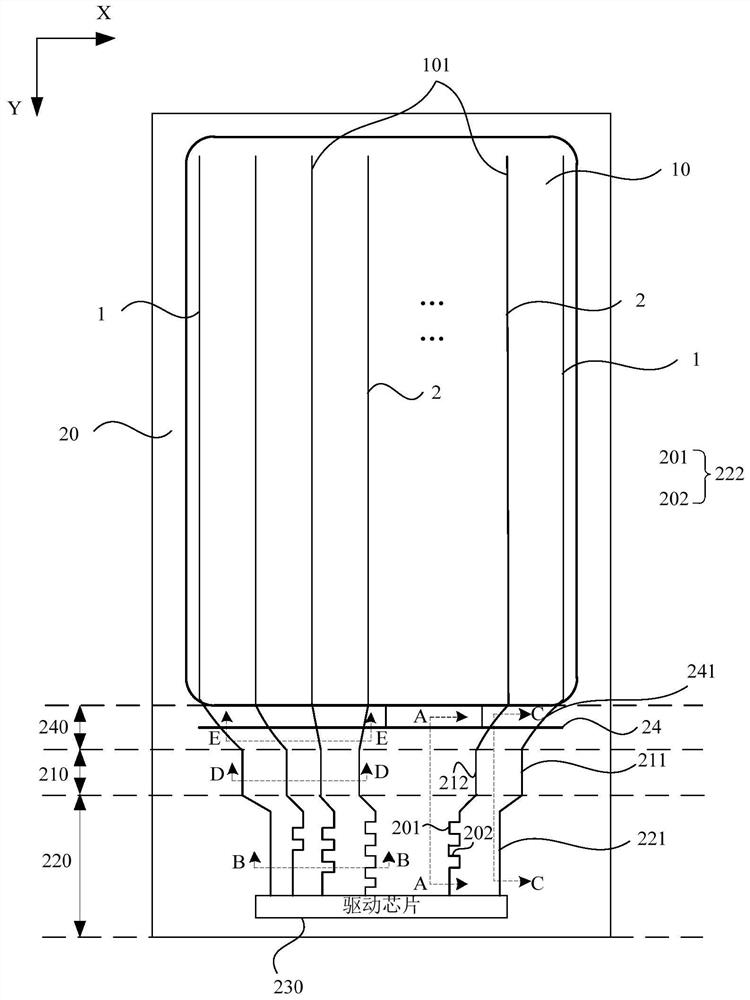

Display panel and display device

InactiveCN112071209AUniform resistanceReduced resistance differenceIdentification meansDisplay deviceEngineering

The embodiment of the invention discloses a display panel and a display device. The display panel comprises a plurality of data lines extending from a fan-out area to a display area through a bendingarea, the data lines comprise a plurality of first wires and a plurality of second wires, and the areas where the first wires are located are distributed on the two sides of the areas where the secondwires are located; each first wire comprises a first metal section located in the fan-out area and a second metal section located in the bending area; each second wire comprises a third metal sectionlocated in the fan-out area and a fourth metal section located in the bending area; and the length of each third metal section is larger than that of the corresponding first metal section, and the resistivity of each third metal section is larger than that of the corresponding first metal section. According to the technical scheme, the resistance difference between the data lines on the edge of the display panel and the data lines in the center area can be reduced, so that charging is more uniform, and then the display effect of the display panel is improved.

Owner:YUNGU GUAN TECH CO LTD

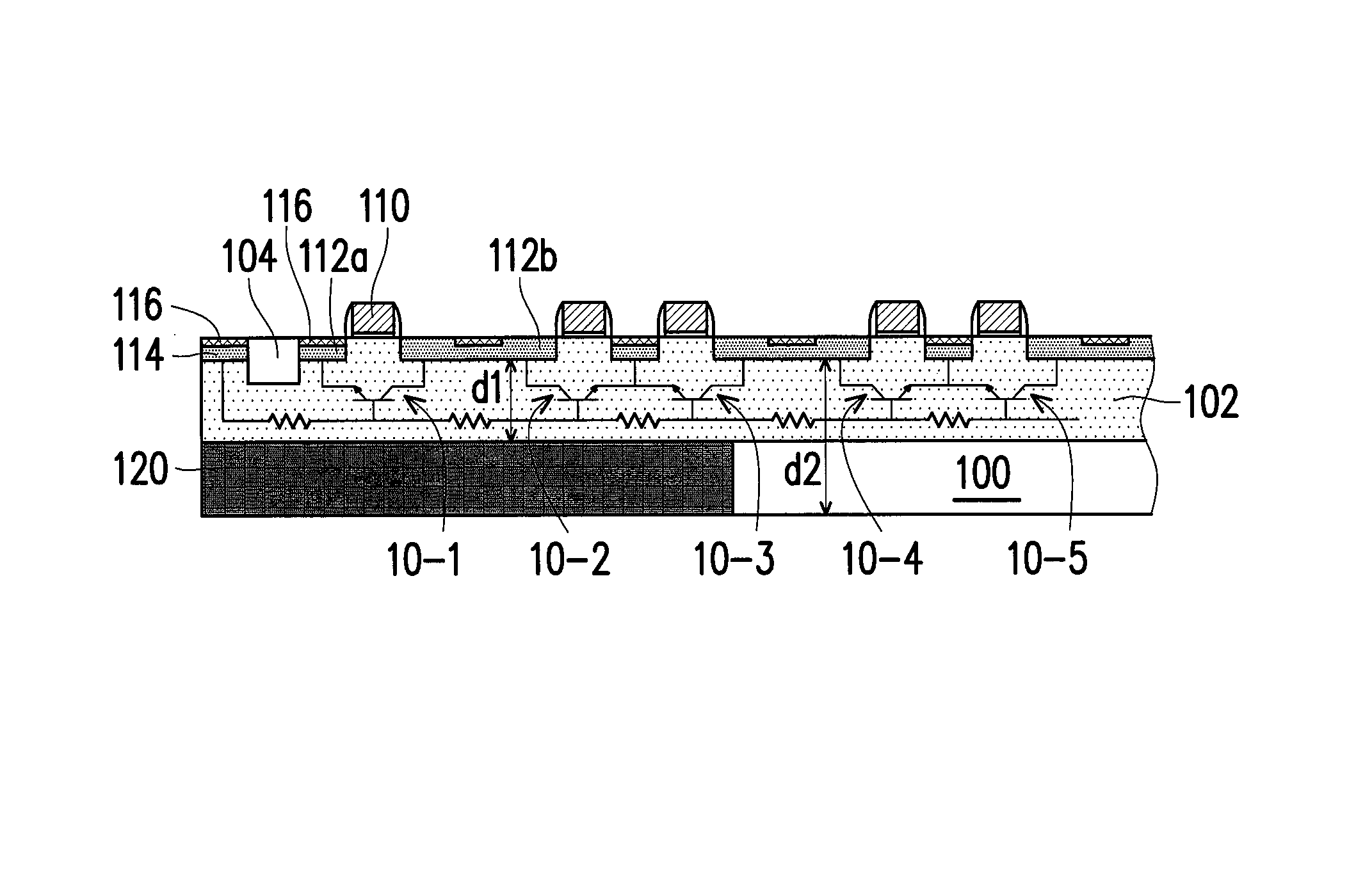

Semiconductor device

ActiveUS20150137255A1Decrease base resistance differenceReduced resistance differenceTransistorSolid-state devicesElectrically conductiveSi substrate

A semiconductor device is described, including a substrate including a first area and a second area, a first MOS element of a first conductivity type in the first area, and a second MOS element of the first conductivity type in the second area. The first area is closer to a pick-up region of the substrate than the second area. The substrate has a second conductivity type. The bottom depth of a first electrical conduction path in the substrate in the first area is smaller than that of a second electrical conduction path in the substrate in the second area.

Owner:UNITED MICROELECTRONICS CORP

Touch panel and image display device including the same

ActiveUS9886127B2Reduced resistance differenceResistance deviationInput/output processes for data processingTouch SensesDisplay device

A touch panel comprises a substrate and a touch sensing electrode formed on at least one surface of the substrate. The touch sensing electrode includes a first sensing pattern formed in a first direction, a second sensing pattern formed in a second direction, a first relay pattern formed at an inside of the first sensing pattern in an island form, a second relay pattern formed between the first sensing pattern and the second sensing pattern, and a connection pattern which electrically connect separated unit patterns of the second sensing pattern via the first relay pattern and the second relay pattern. The connection pattern includes a first connection pattern which connects the first relay pattern and the second relay pattern, and a second connection pattern which connects the second relay pattern and the unit pattern of the second sensing pattern.

Owner:DONGWOO FINE CHEM CO LTD

Liquid discharge head

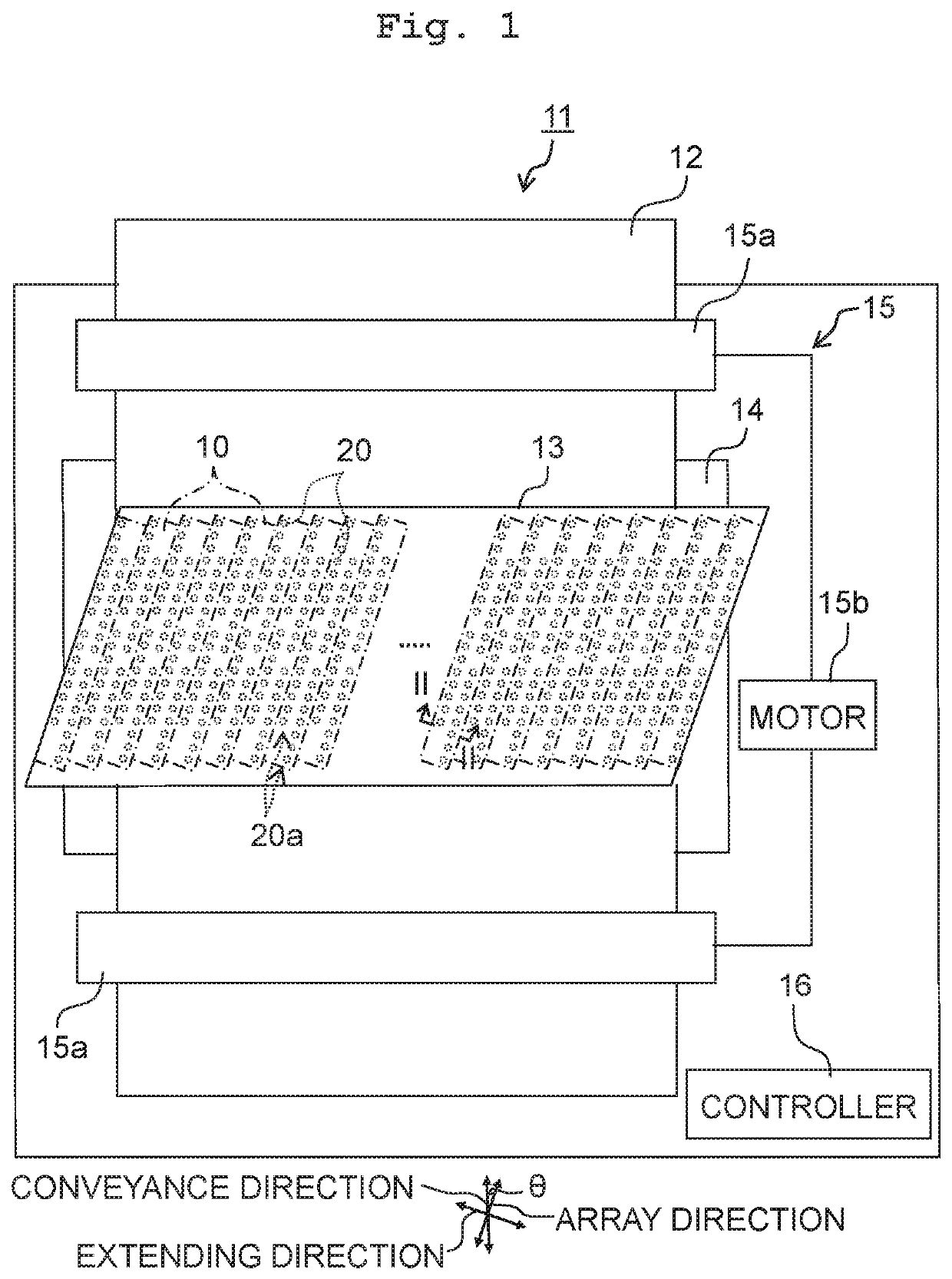

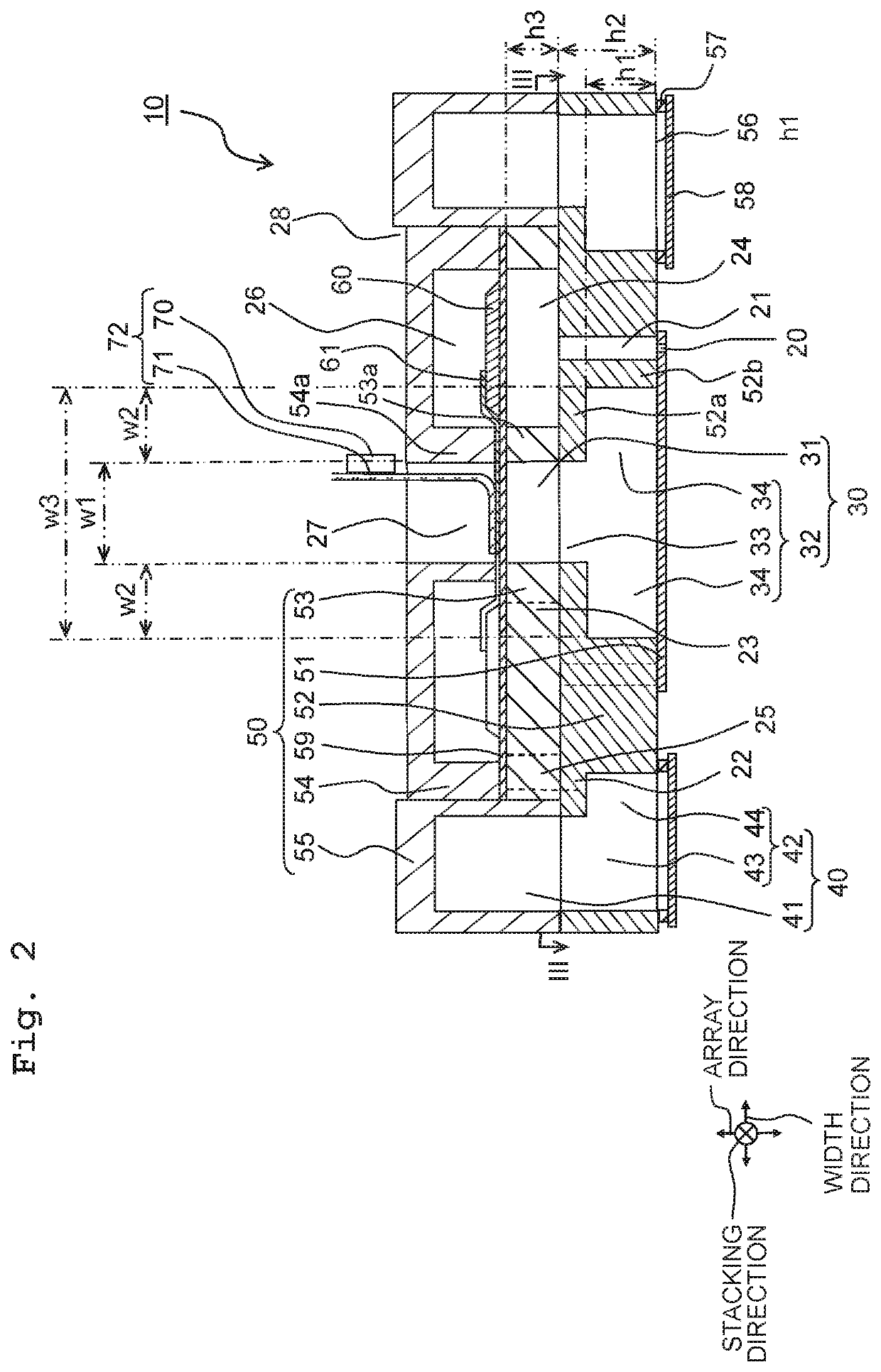

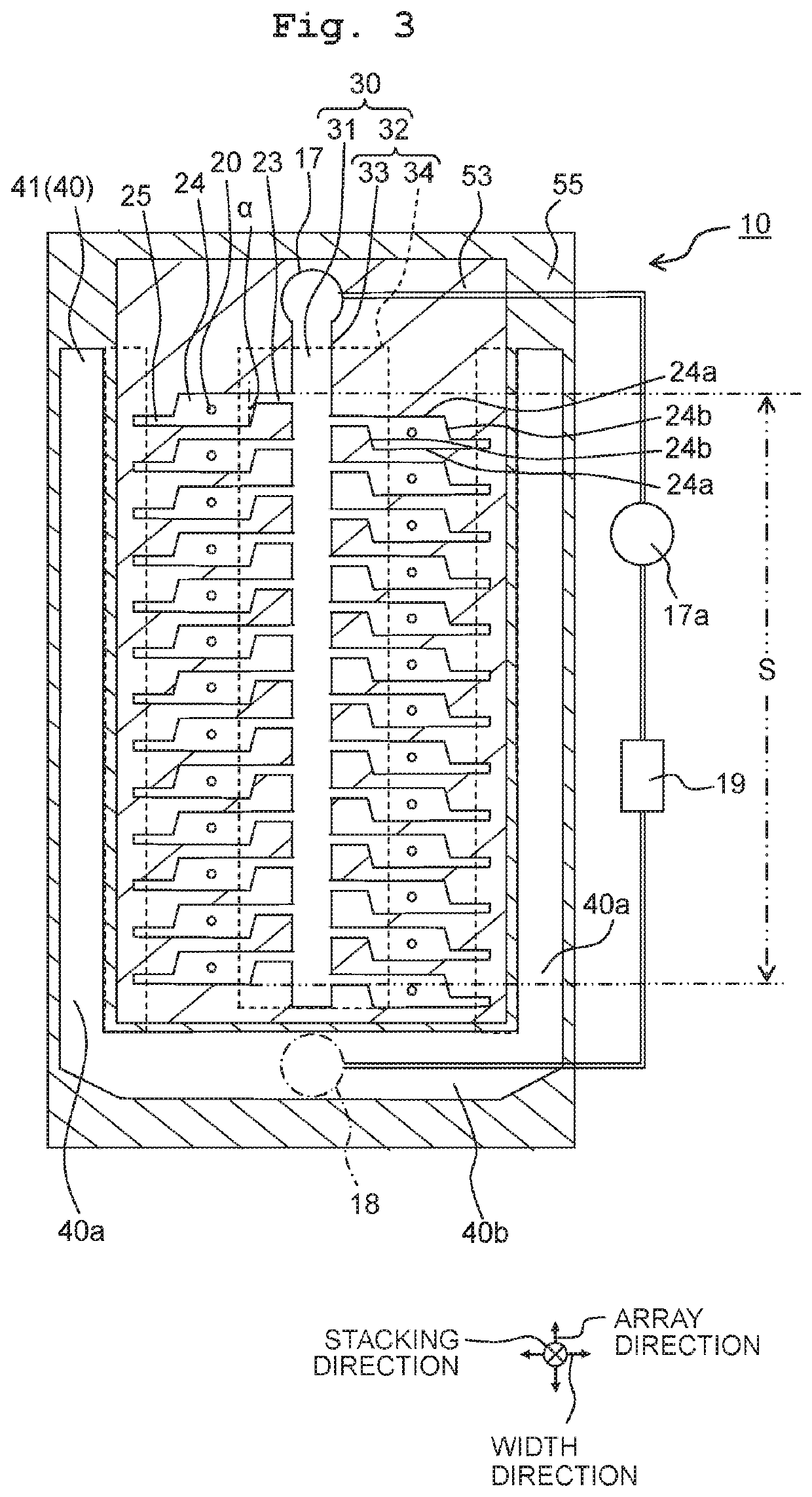

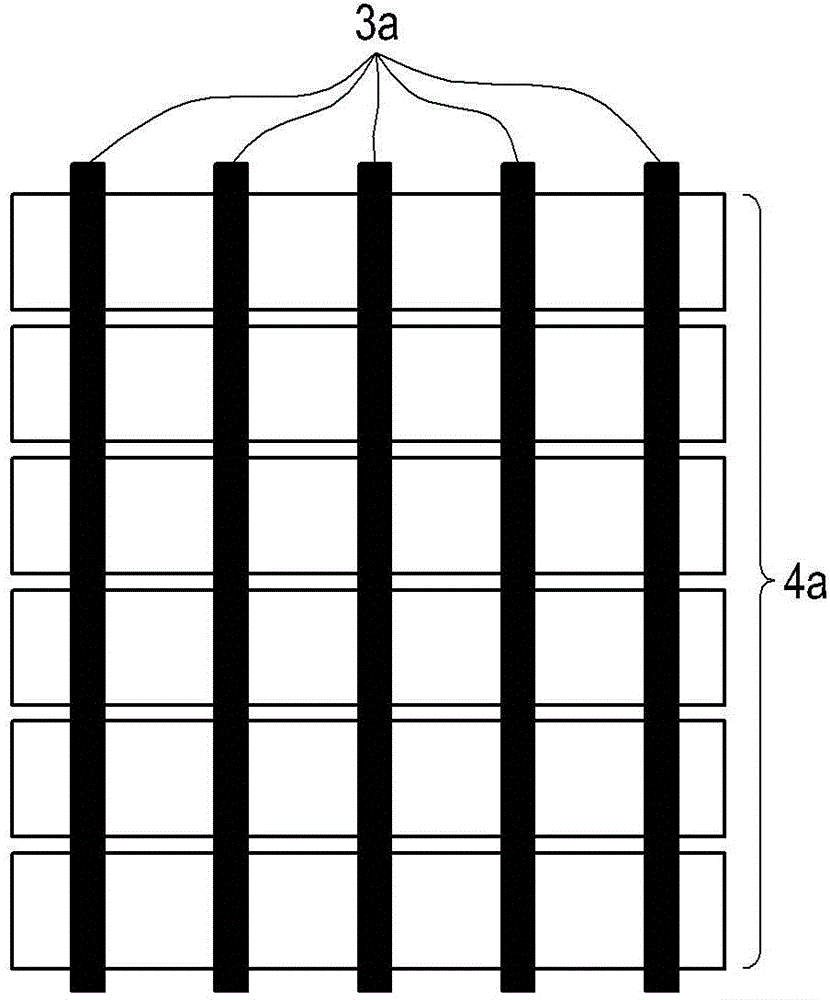

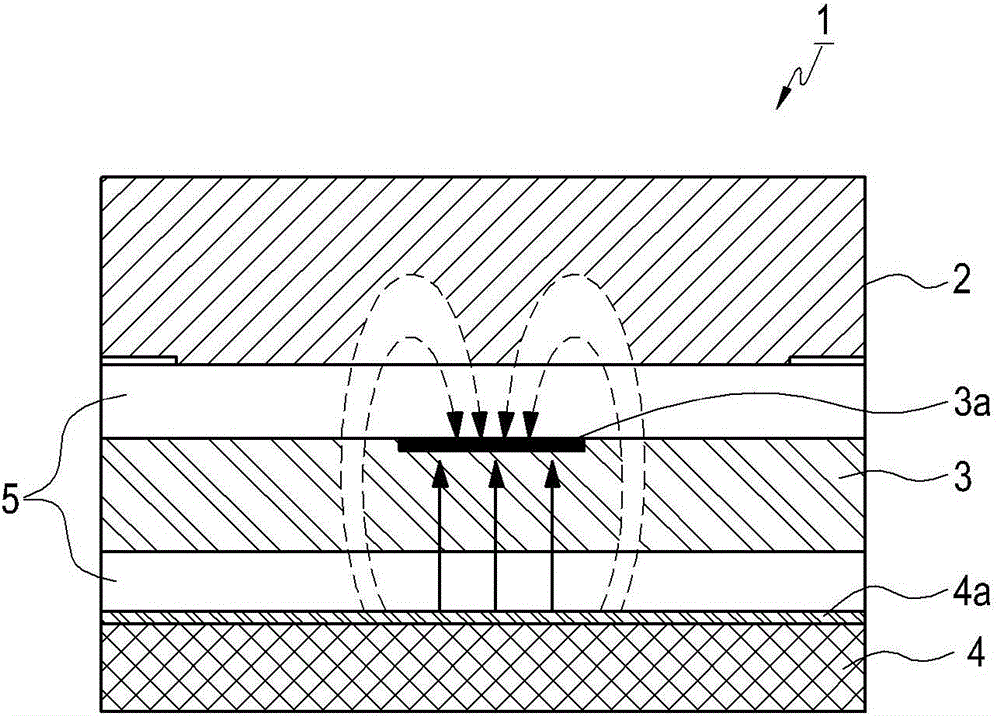

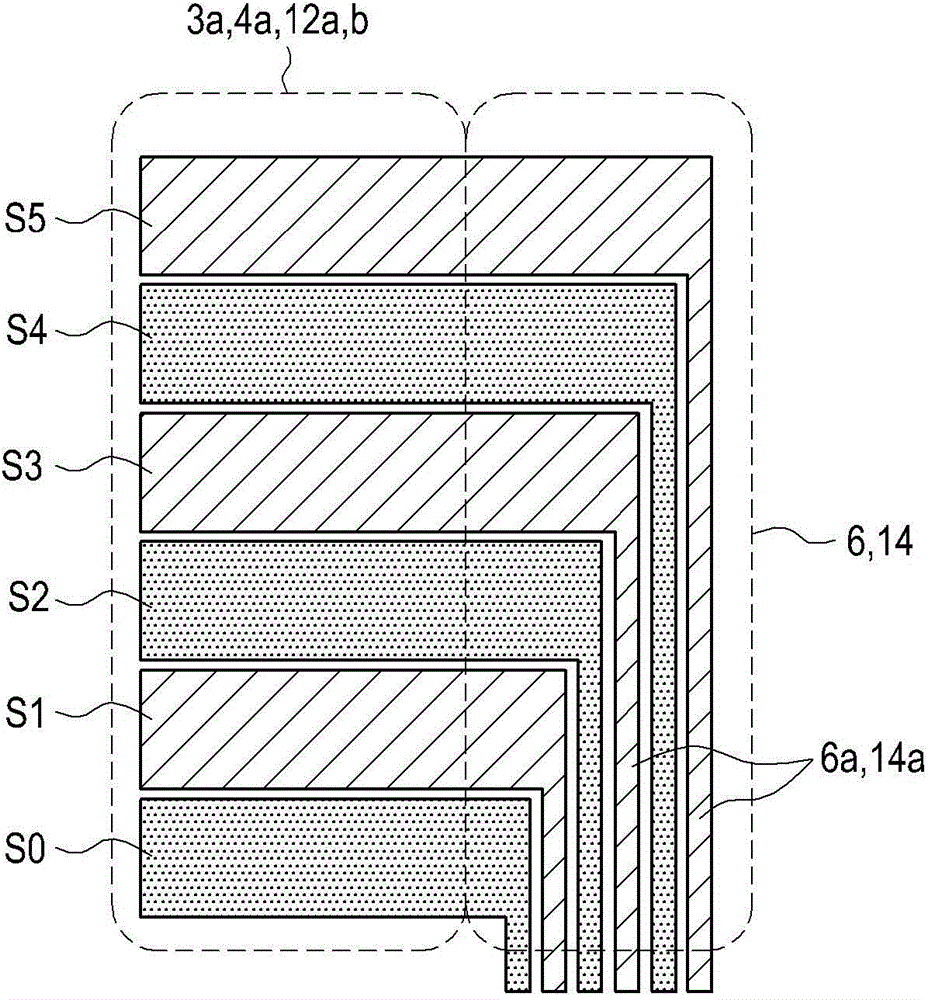

There is provided a liquid discharge head including: a communication plate formed with a descender connected to a nozzle, a pressure chamber plate including a plurality of pressure chambers aligning in an array direction, a piezoelectric element, and a discharge common channel. The discharge common channel extends in the array direction, is connected to the plurality of pressure chambers, and has a first discharge portion and a second discharge portion. The discharge common channel is configured to discharge liquid toward one side in the array direction. The second discharge portion includes an expansion portion to expand beyond the first discharge portion in a width direction orthogonal to the stacking direction and to the array direction.

Owner:BROTHER KOGYO KK

Wiring apparatus for touch screen panel

InactiveCN104035612AReduced resistance differenceHigh precisionInput/output processes for data processingEngineeringTouchscreen

Owner:SAMSUNG ELECTRONICS CO LTD

Mask plate and manufacture method of array base plate

ActiveCN103324035AReduced resistance differenceEliminate display unevennessSolid-state devicesSemiconductor/solid-state device manufacturingElectrical and Electronics engineering

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Semiconductor device

ActiveUS9564436B2Reduced resistance differenceAvoid damageTransistorSolid-state devicesPower semiconductor deviceElectrical conduction

A semiconductor device is described, including a substrate including a first area and a second area, a first MOS element of a first conductivity type in the first area, and a second MOS element of the first conductivity type in the second area. The first area is closer to a pick-up region of the substrate than the second area. The substrate has a second conductivity type. The bottom depth of a first electrical conduction path in the substrate in the first area is smaller than that of a second electrical conduction path in the substrate in the second area.

Owner:UNITED MICROELECTRONICS CORP