Memory device and dual port static RAM

A static random access and memory technology, applied in static memory, digital memory information, information storage, etc., can solve problems such as component performance that has to be considered

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the above-mentioned purposes, features and advantages of the present invention more obvious and understandable, a preferred embodiment is specifically cited below, and in conjunction with the accompanying drawings, the detailed description is as follows:

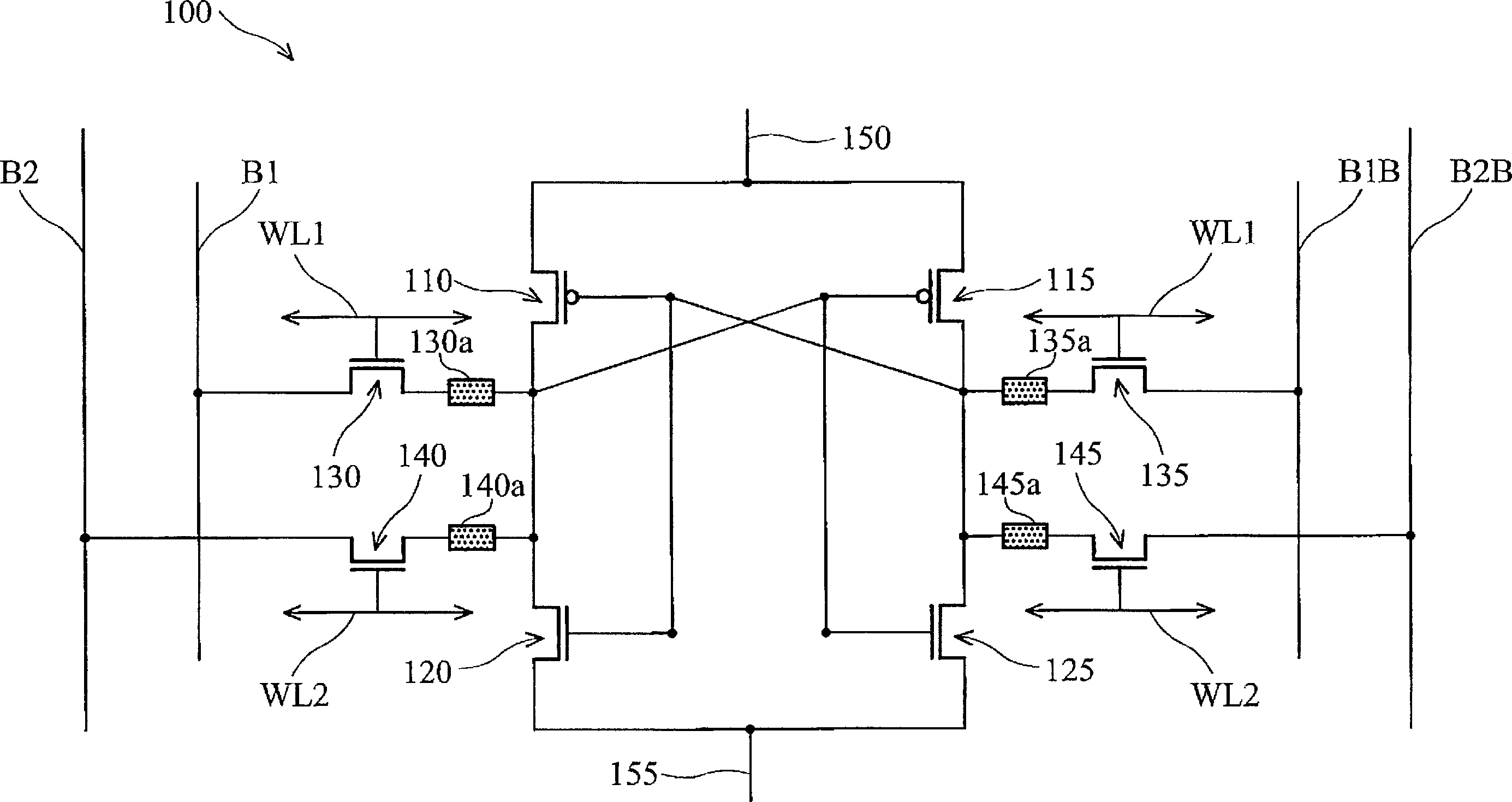

[0028] figure 1 A circuit diagram of a memory is shown. This circuit diagram is a circuit embodiment of a dual-port SRAM cell with eight transistors, denoted by symbol 100 . These eight transistors constitute two interlocked complementary metal-oxide-semiconductor field effect transistors (complementary metal-oxide-semiconductor field effect transistors, CMOSFET) inverters (inverters), and four transfer gate (passgate) transistors ( It is also called pass transistor, access transistor, active transistor). Cell 100 has pull-up transistors 110 and 115 , and pull-down transistors 120 and 125 , as well as pass-gate transistors 130 , 135 , 140 and 145 . In this specification, the pull-up transistor may ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More