Patents

Literature

60results about How to "Improve critical dimensions" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method of depositing thin film and method of manufacturing semiconductor device

ActiveUS20190115206A1Good shape retentionAvoid damageElectric discharge tubesSemiconductor/solid-state device manufacturingReactive gasEngineering

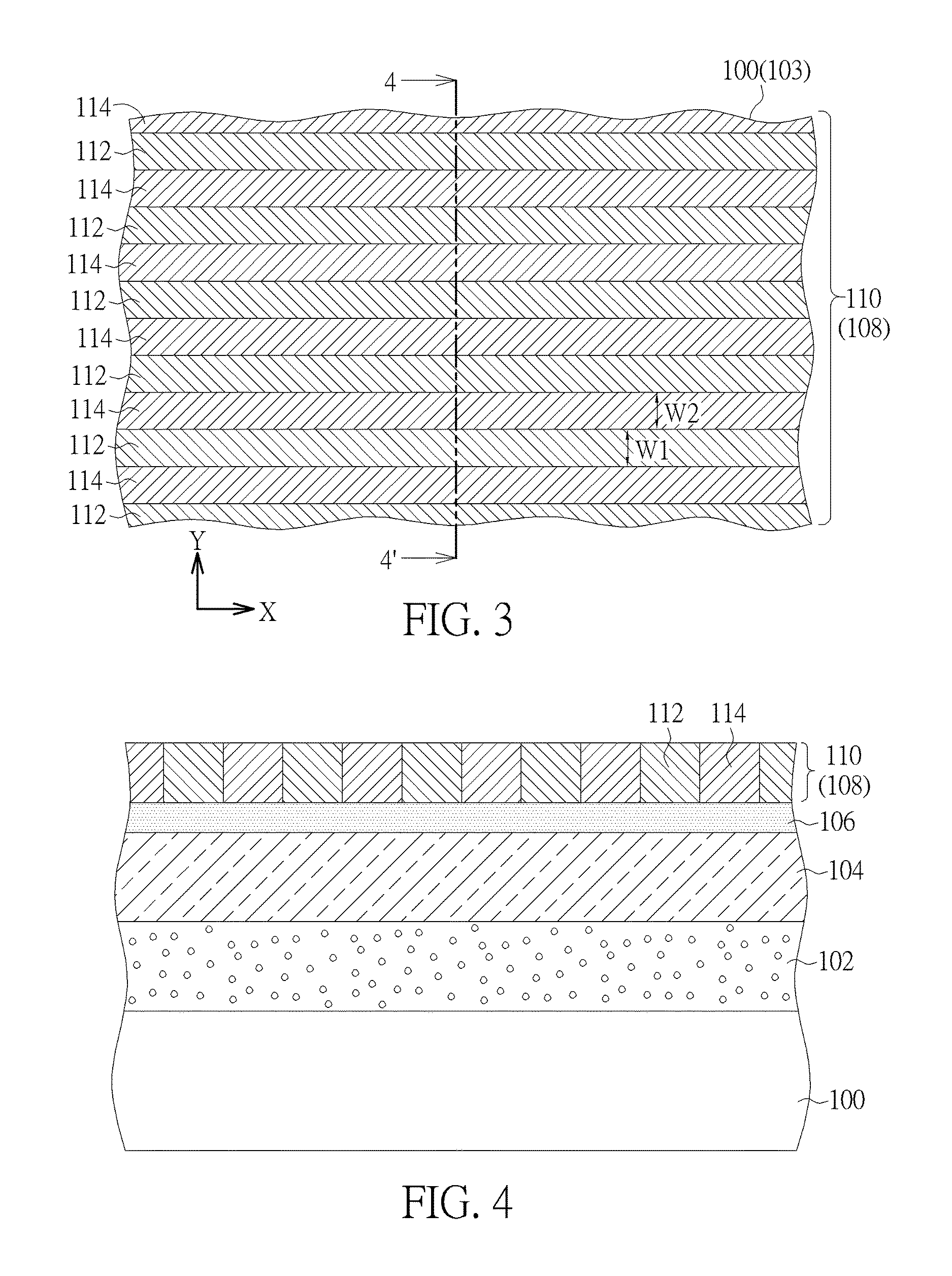

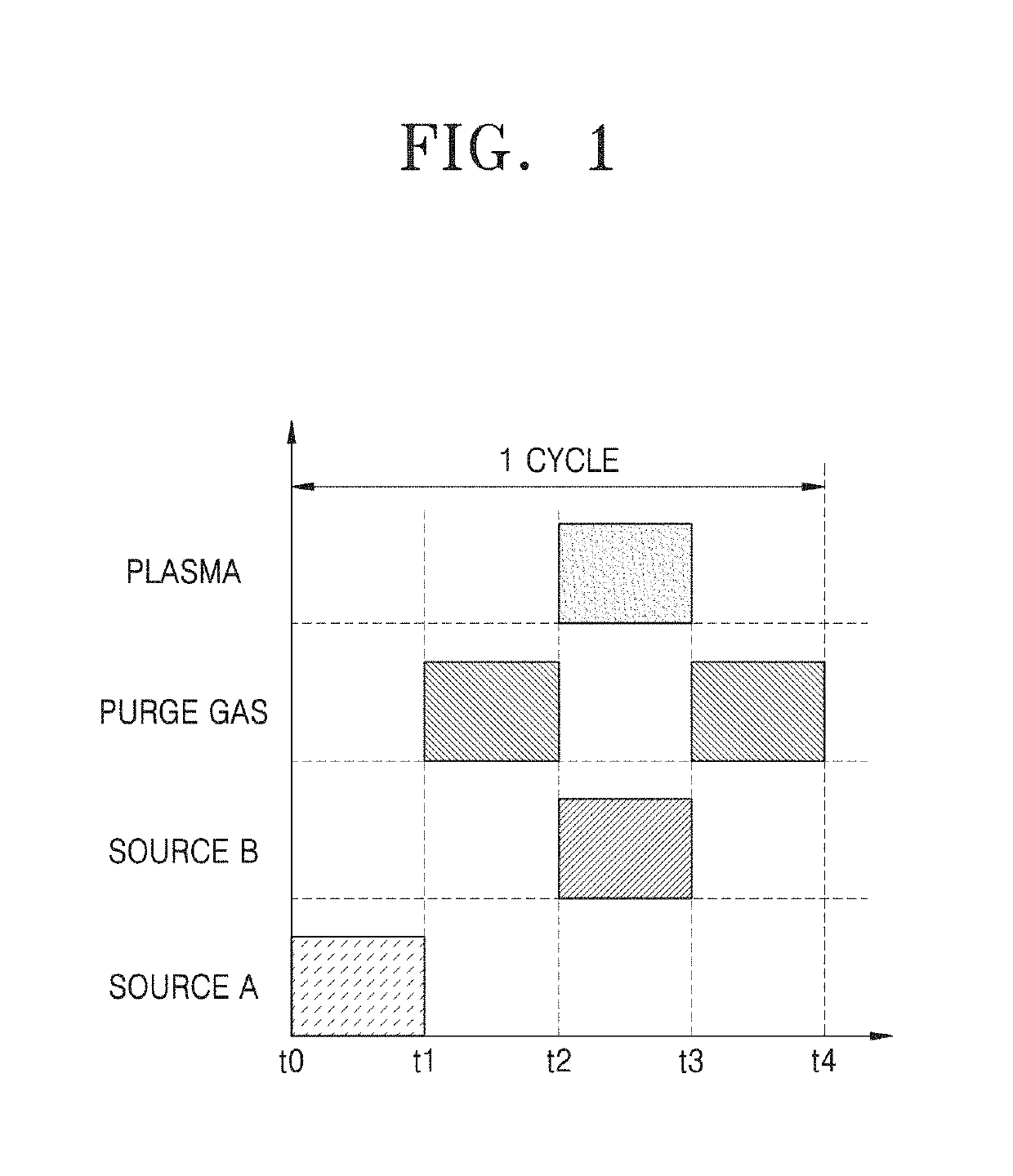

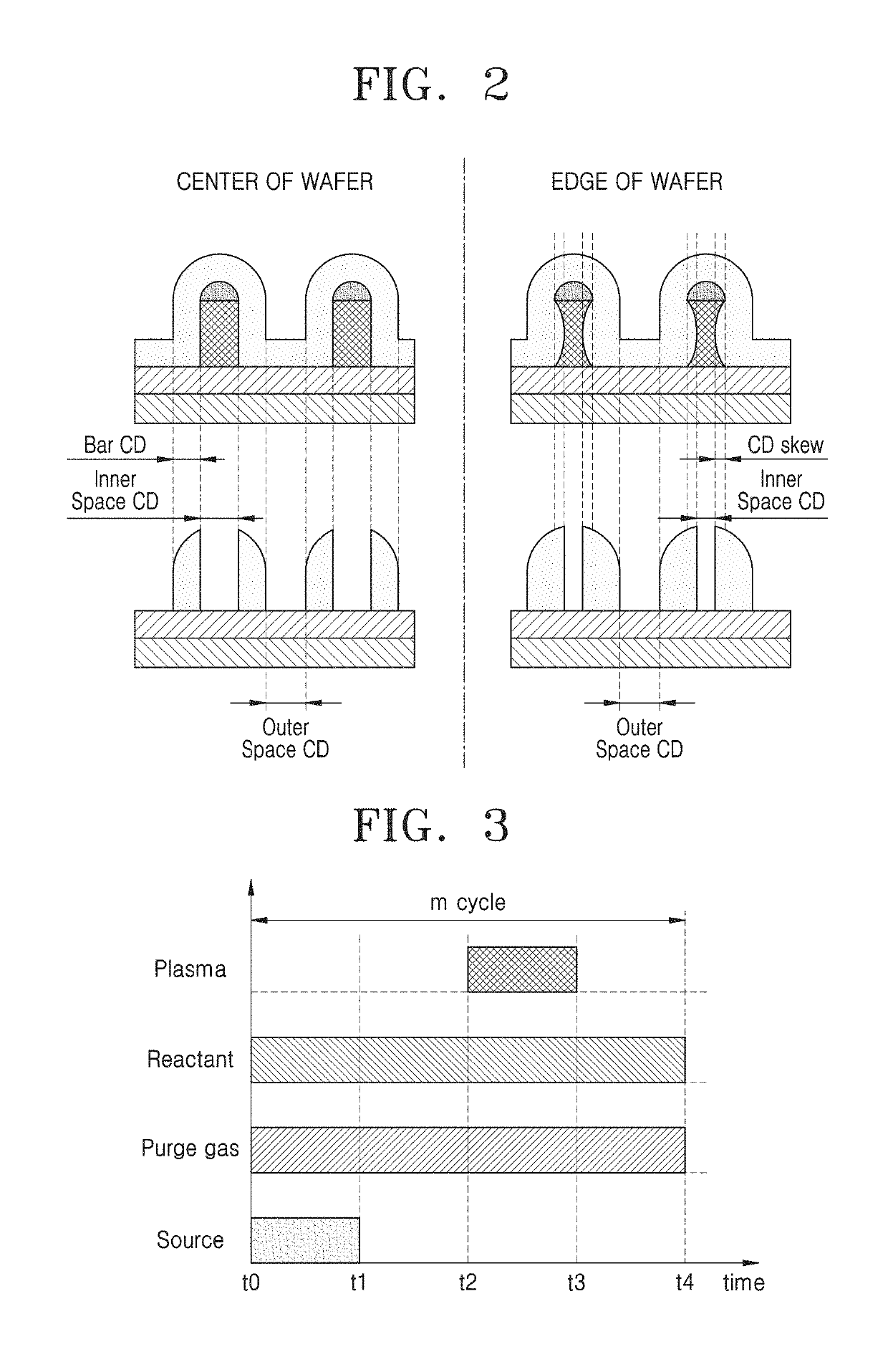

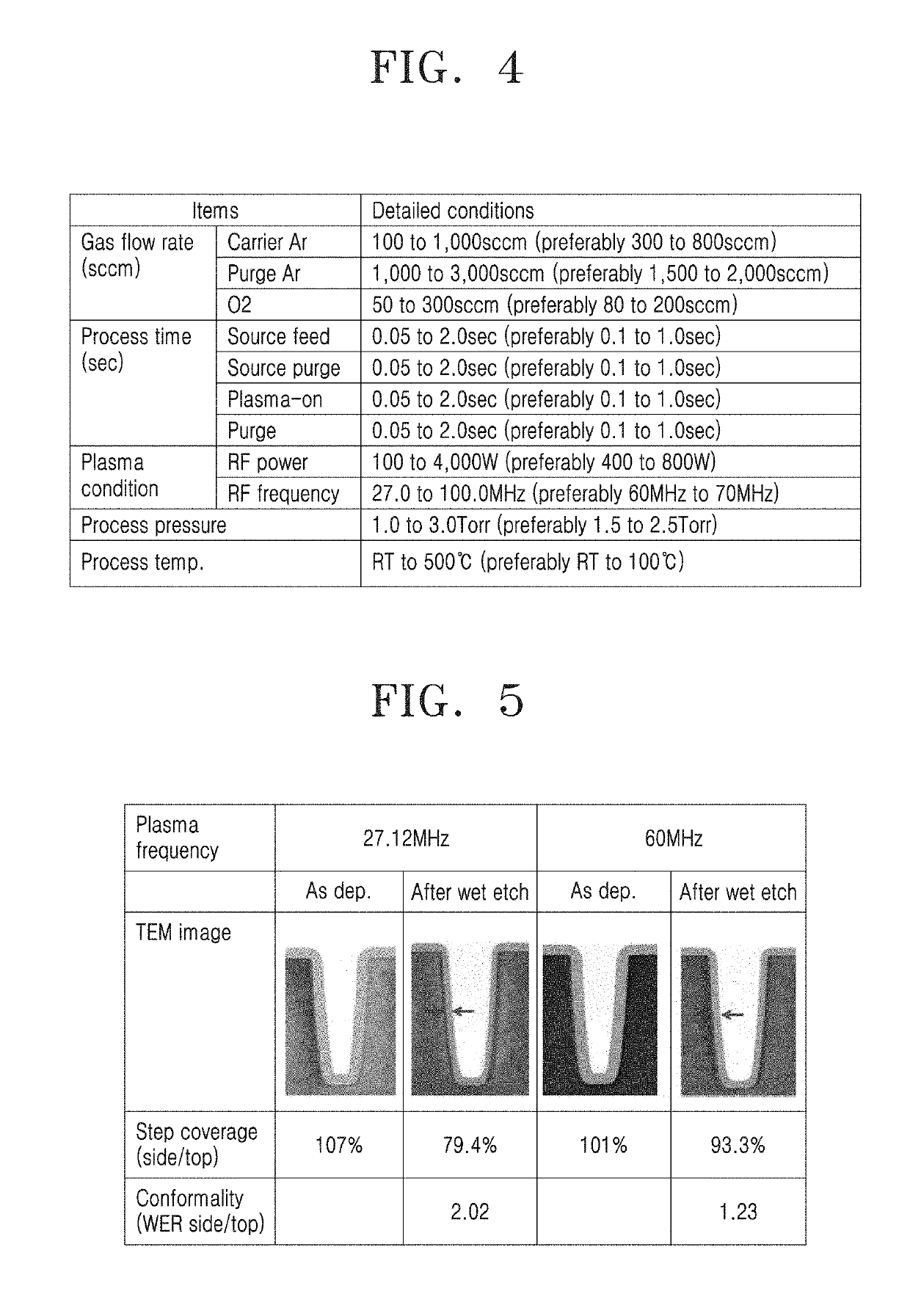

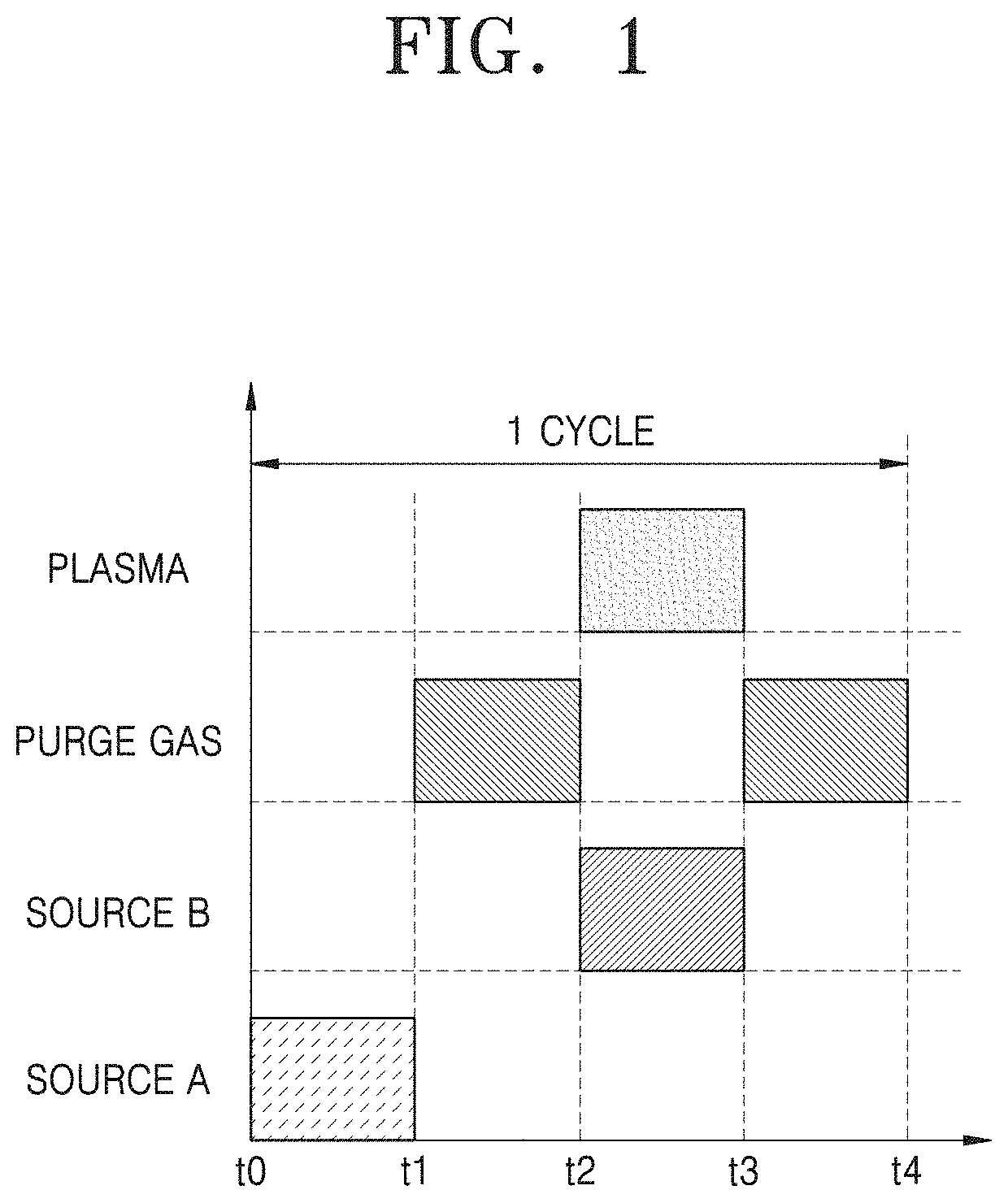

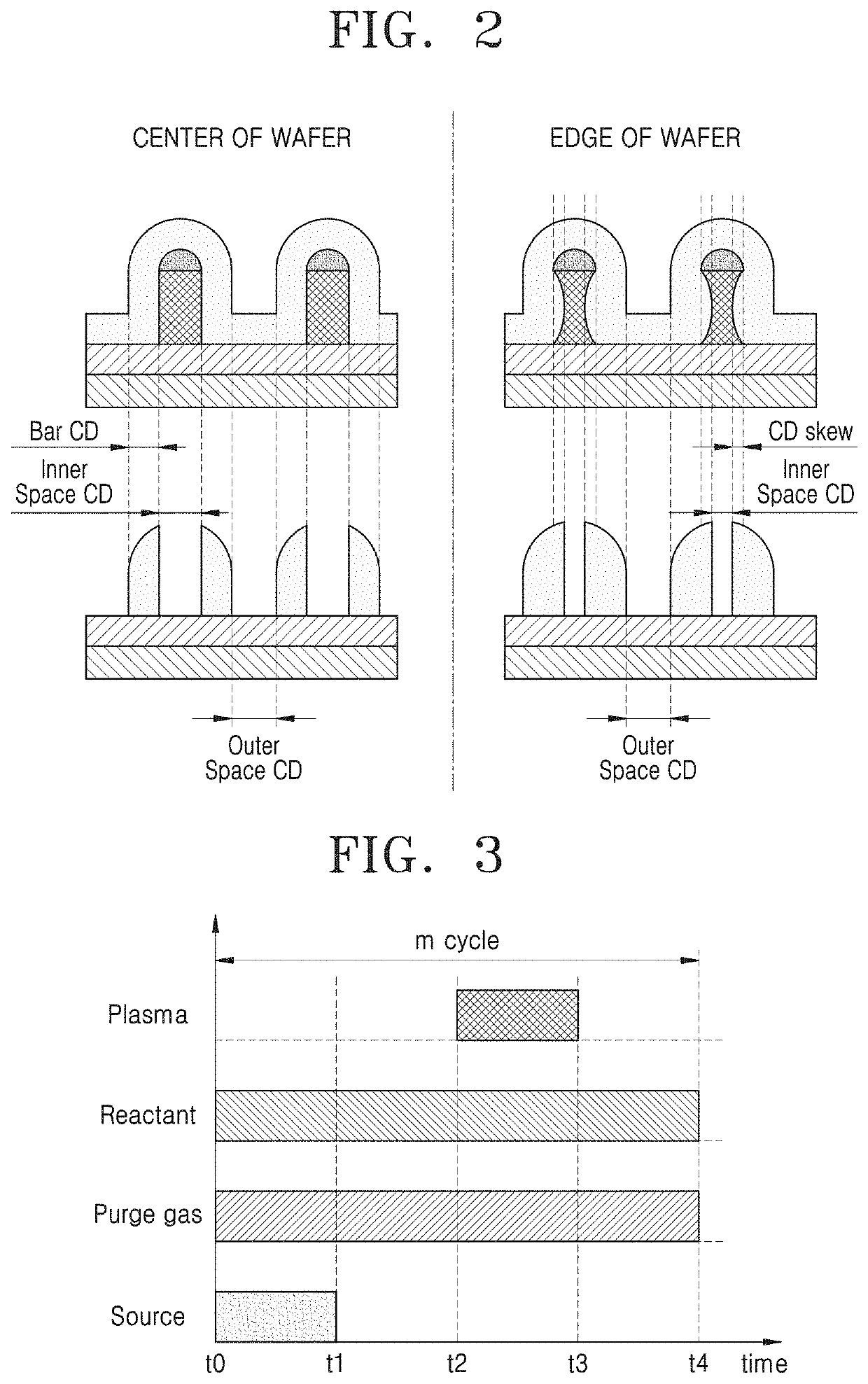

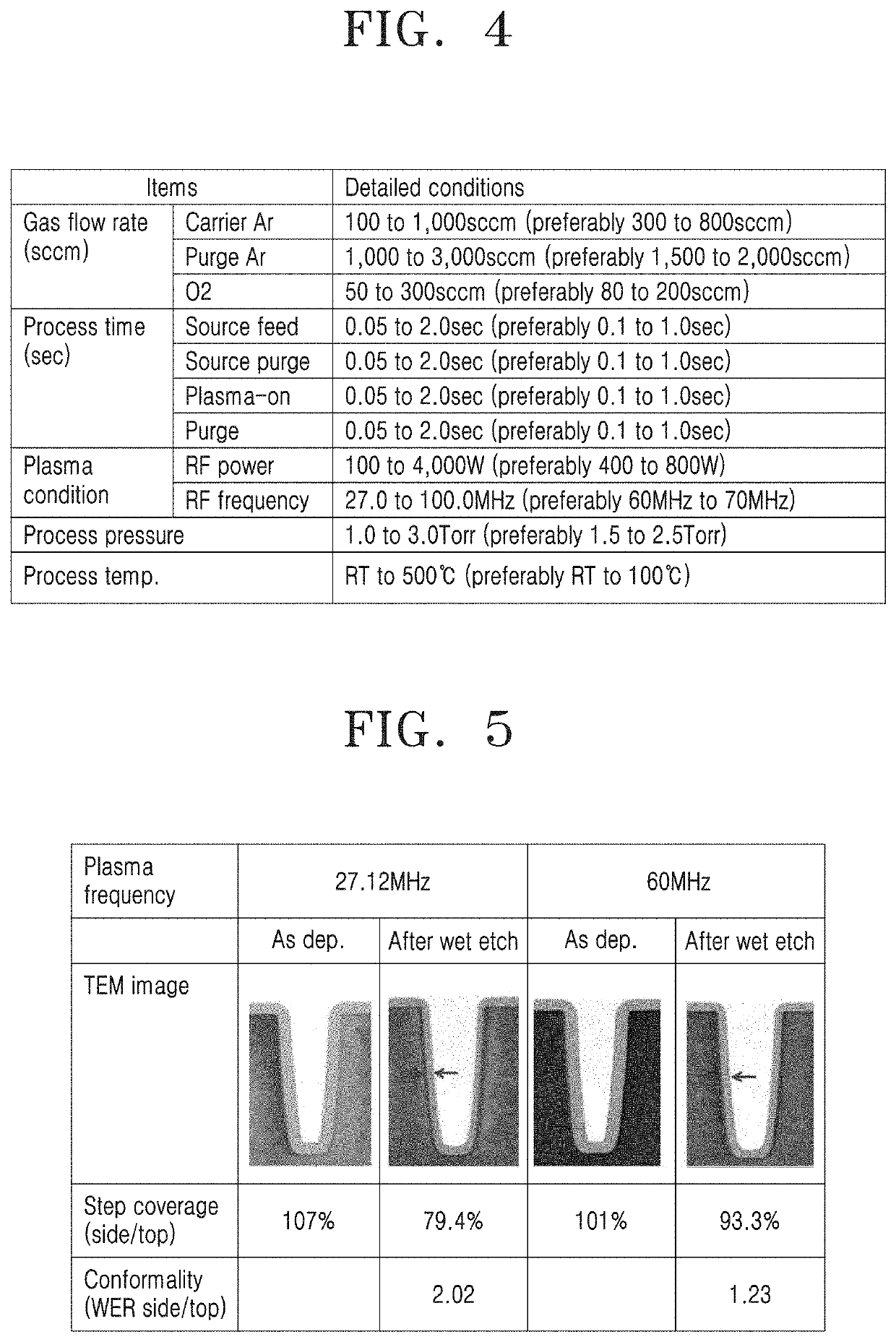

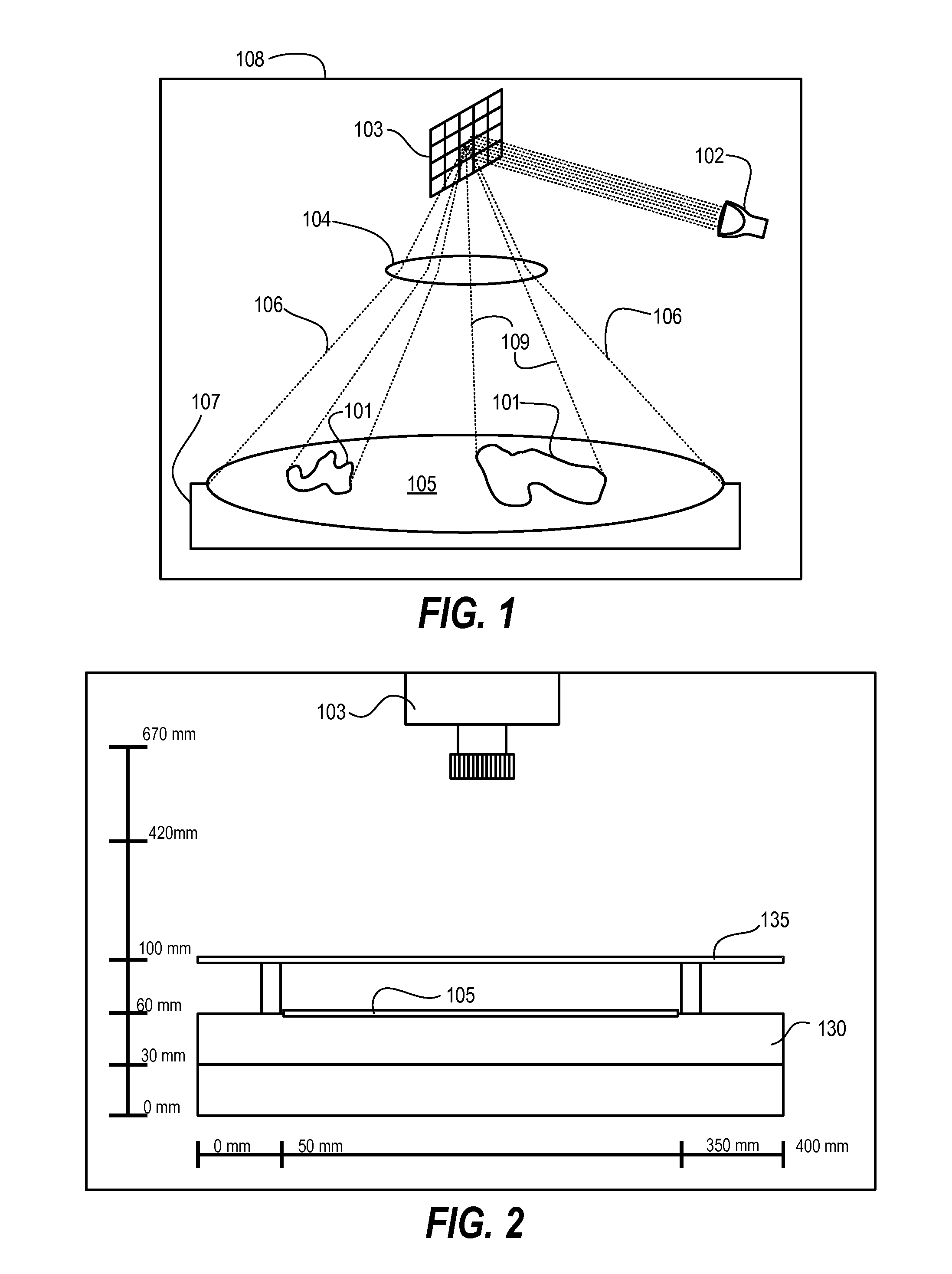

Provided is a method of depositing a thin film on a pattern structure of a semiconductor substrate, the method including (a) supplying a source gas; (b) supplying a reactive gas; and (c) supplying plasma, wherein the steps (a), (b), and (c) are sequentially repeated on the semiconductor substrate within a reaction space until a desired thickness is obtained, and a frequency of the plasma is a high frequency of 60 MHz or greater.

Owner:ASM IP HLDG BV

Method of depositing thin film and method of manufacturing semiconductor device

ActiveUS10714335B2Good shape retentionAvoid damageElectric discharge tubesSemiconductor/solid-state device manufacturingDevice materialReactive gas

Provided is a method of depositing a thin film on a pattern structure of a semiconductor substrate, the method including (a) supplying a source gas; (b) supplying a reactive gas; and (c) supplying plasma, wherein the steps (a), (b), and (c) are sequentially repeated on the semiconductor substrate within a reaction space until a desired thickness is obtained, and a frequency of the plasma is a high frequency of 60 MHz or greater.

Owner:ASM IP HLDG BV

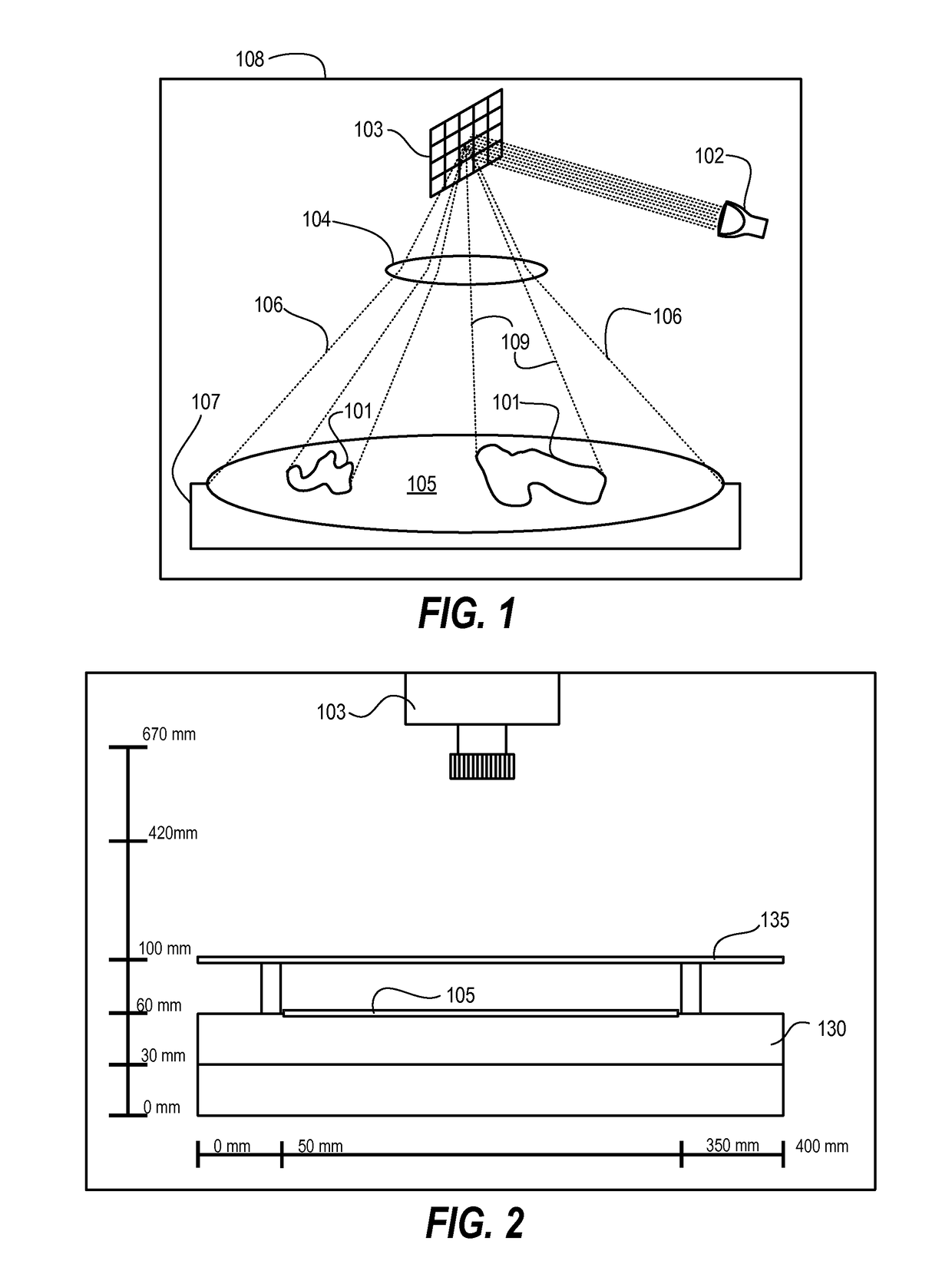

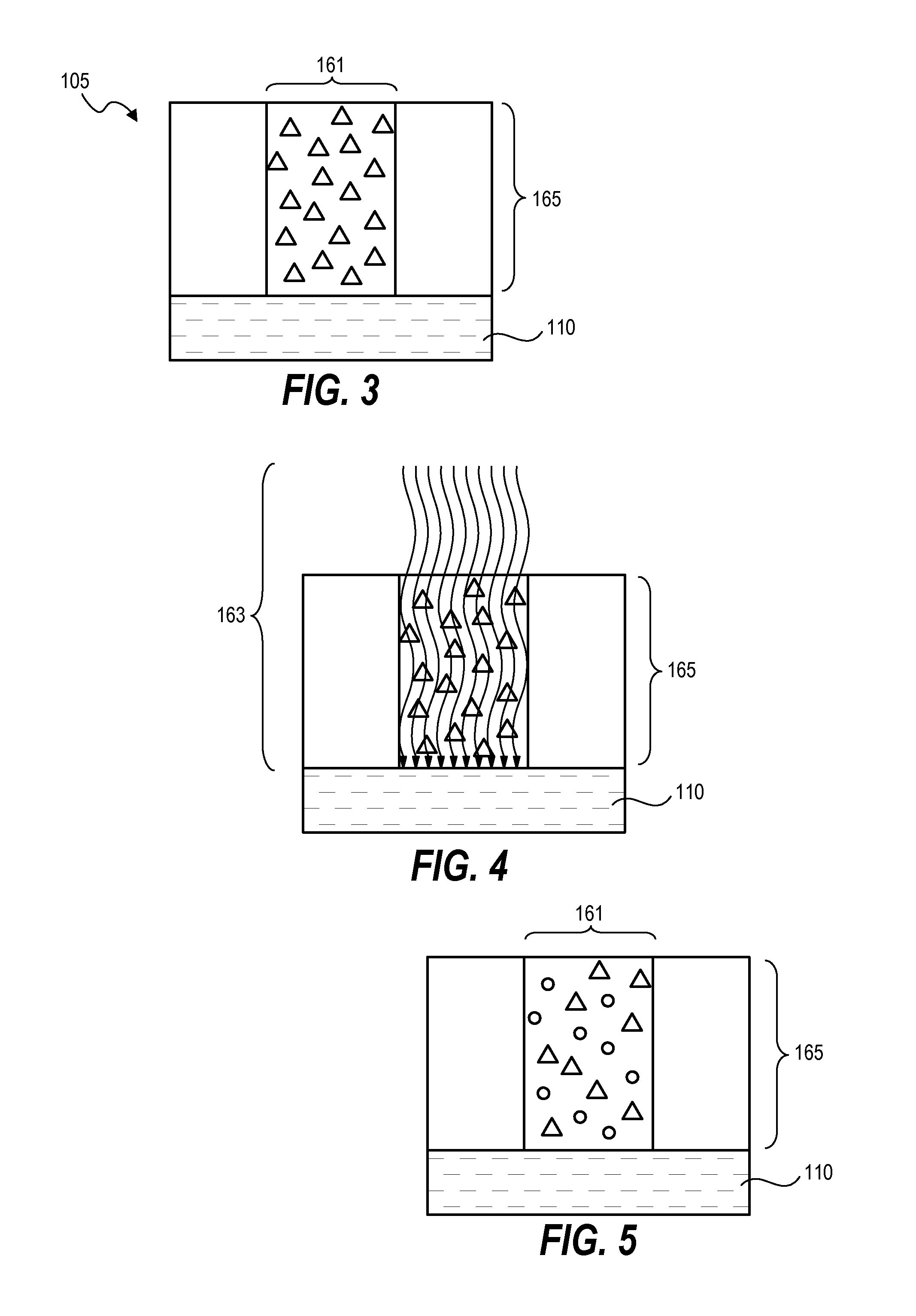

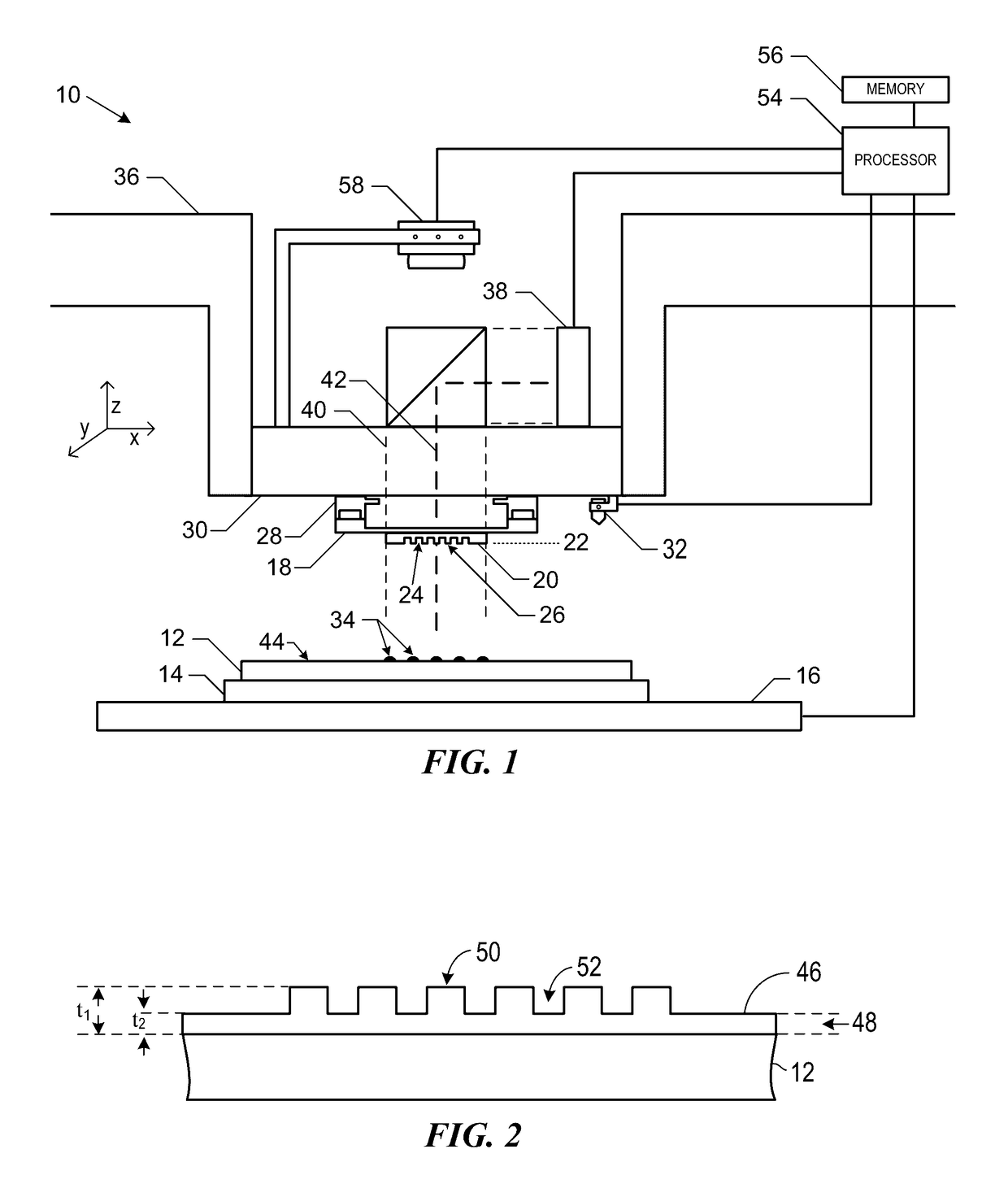

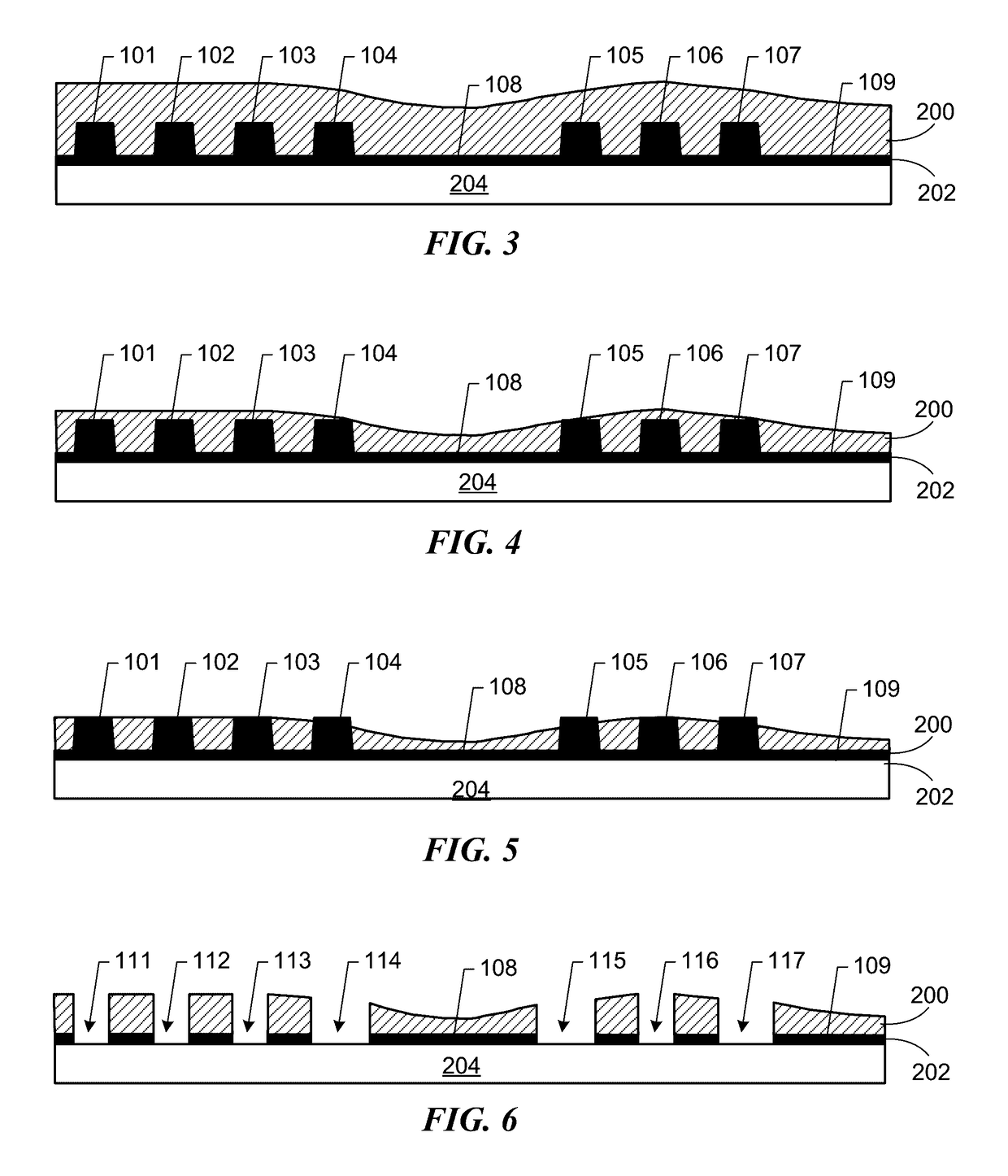

System and Method for Shifting Critical Dimensions of Patterned Films

ActiveUS20150212421A1Improve uniformityIncrease productionPhotosensitive material processingOriginals for photomechanical treatmentMarking outProjection system

Techniques herein include systems and methods that provide a spatially-controlled projection of electromagnetic radiation, such as light, onto a substrate as a mechanism of controlling or modulating critical dimensions of various features and structures being micro-fabricated on a substrate. Combining such spatial light projection with photolithographic exposure can achieve significant improvements in critical dimension uniformity across a surface of a substrate. In general, methods herein include patterning processes that identify or receive a critical dimension signature that spatially characterizes critical dimension values that correspond to the substrate. A pattern of electromagnetic radiation is projected onto a patterning film coated on substrate using a digital pixel-based projection system. A conventional photolithographic exposure process is executed subsequent to, or prior to, the pixel-based projection. The patterning film can then be developed to yield a relief pattern having critical dimensions shaped by both exposure processes.

Owner:TOKYO ELECTRON LTD

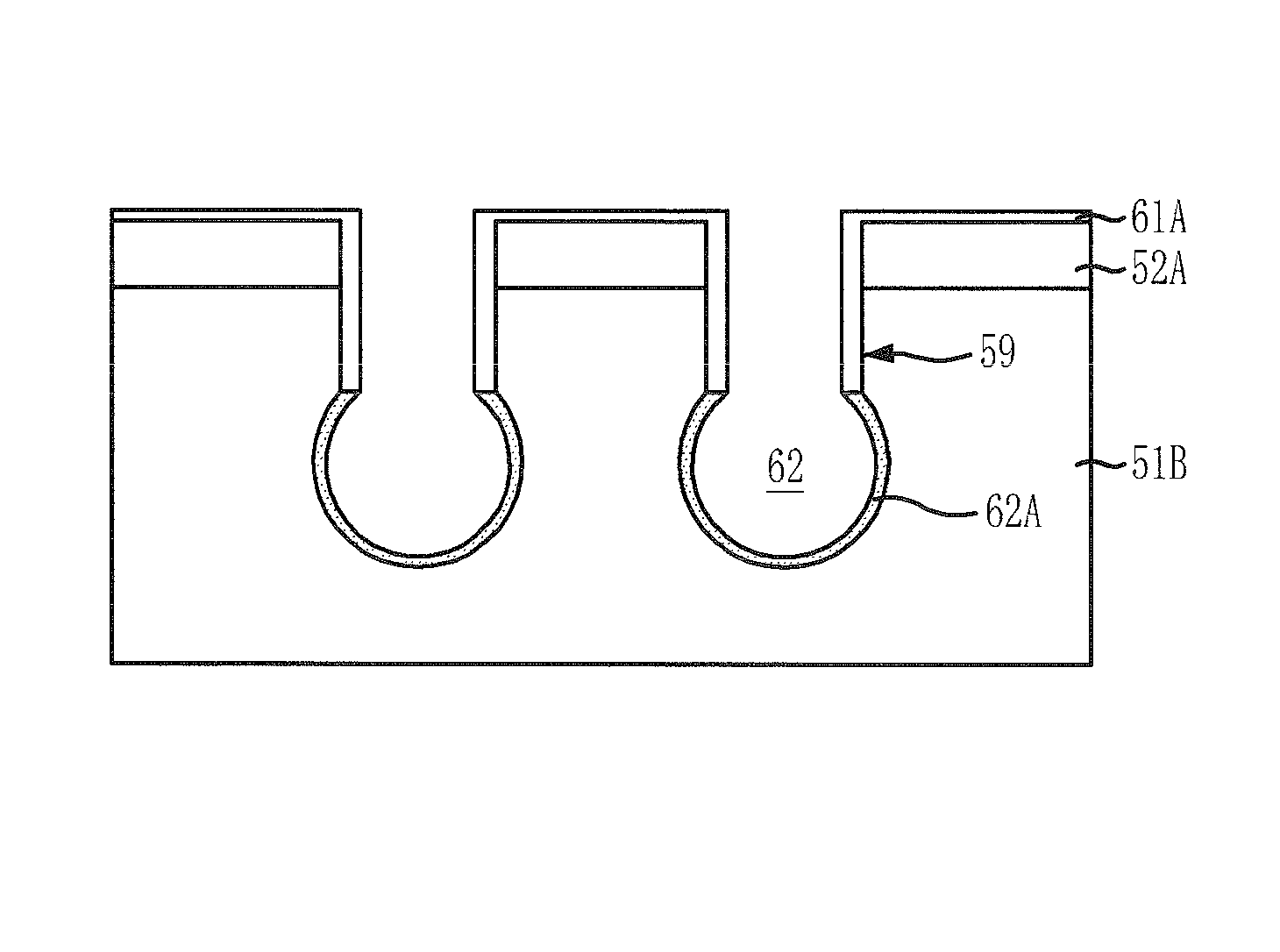

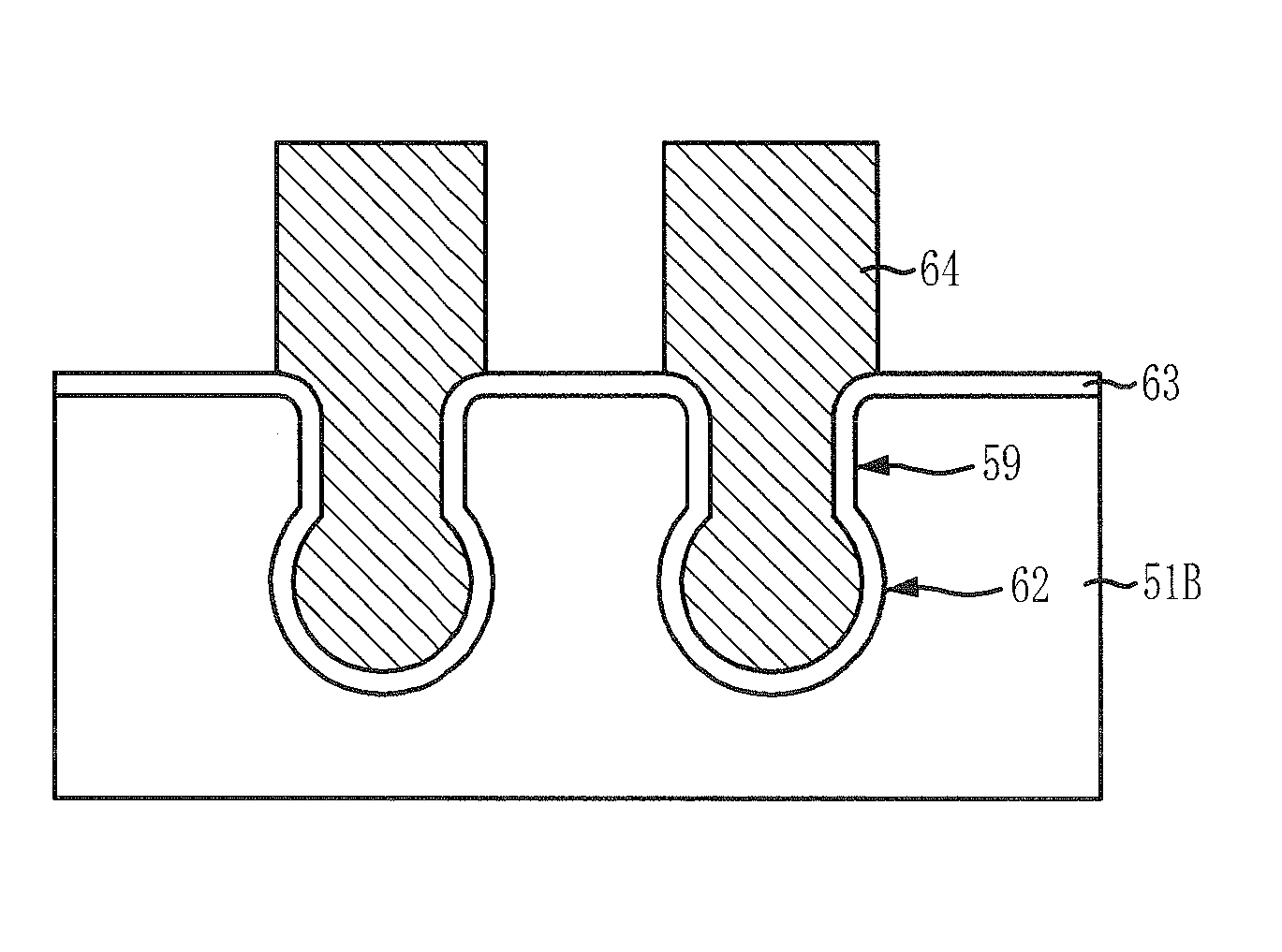

Method for fabricating bulb-shaped recess pattern

InactiveUS20080160766A1Improve critical dimensionsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHard mask

A method for fabricating a bulb-shaped recess pattern includes: forming an etch barrier layer over a substrate; forming a hard mask pattern in which a first polymer is attached to sidewalls of the hard mask pattern over the etch barrier layer; sequentially etching the etch barrier layer and the substrate to form a recess pattern in which a second polymer is attached to sidewalls of the recess pattern; removing the first and second polymers and the hard mask pattern; forming a plurality of spacers exposing a bottom portion of the recess pattern; and etching the exposed bottom portion of the recess pattern to form a ball pattern.

Owner:SK HYNIX INC

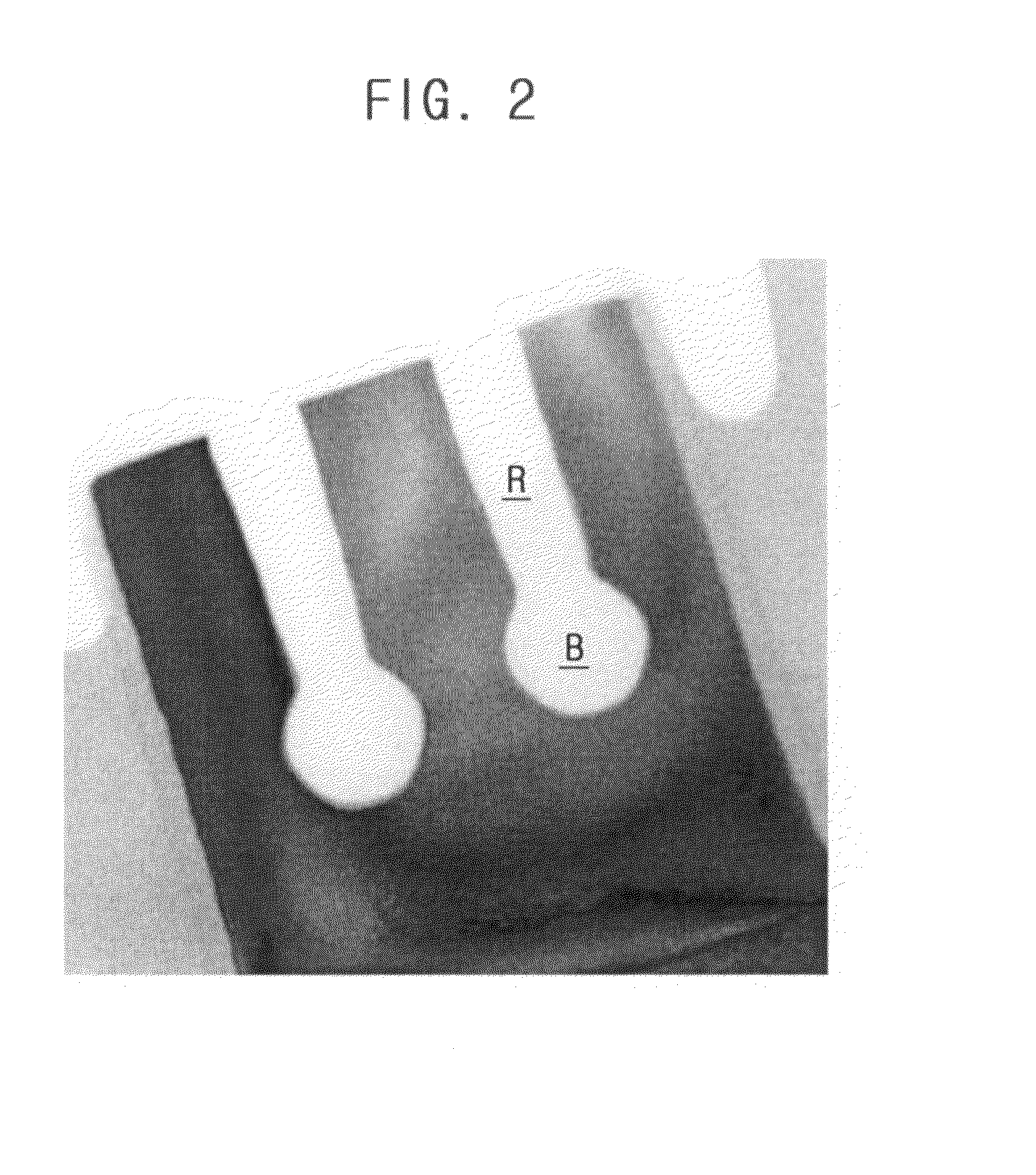

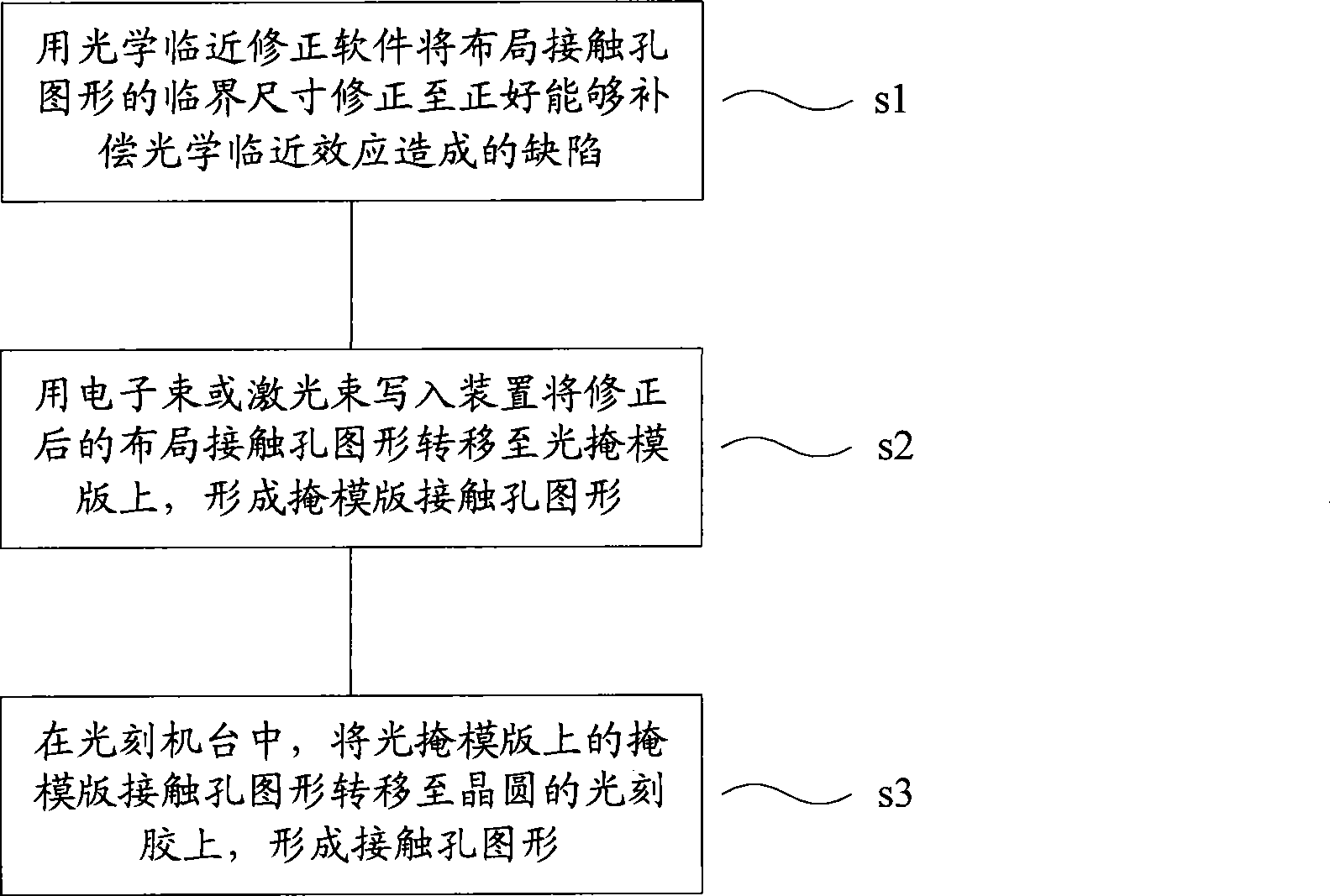

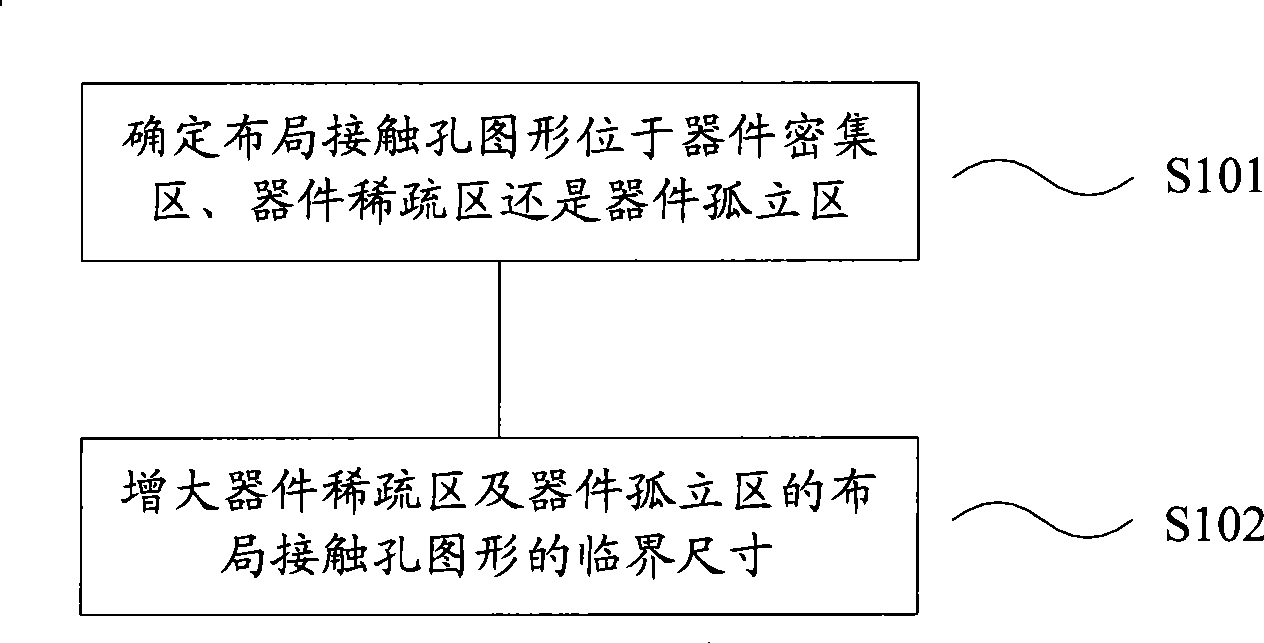

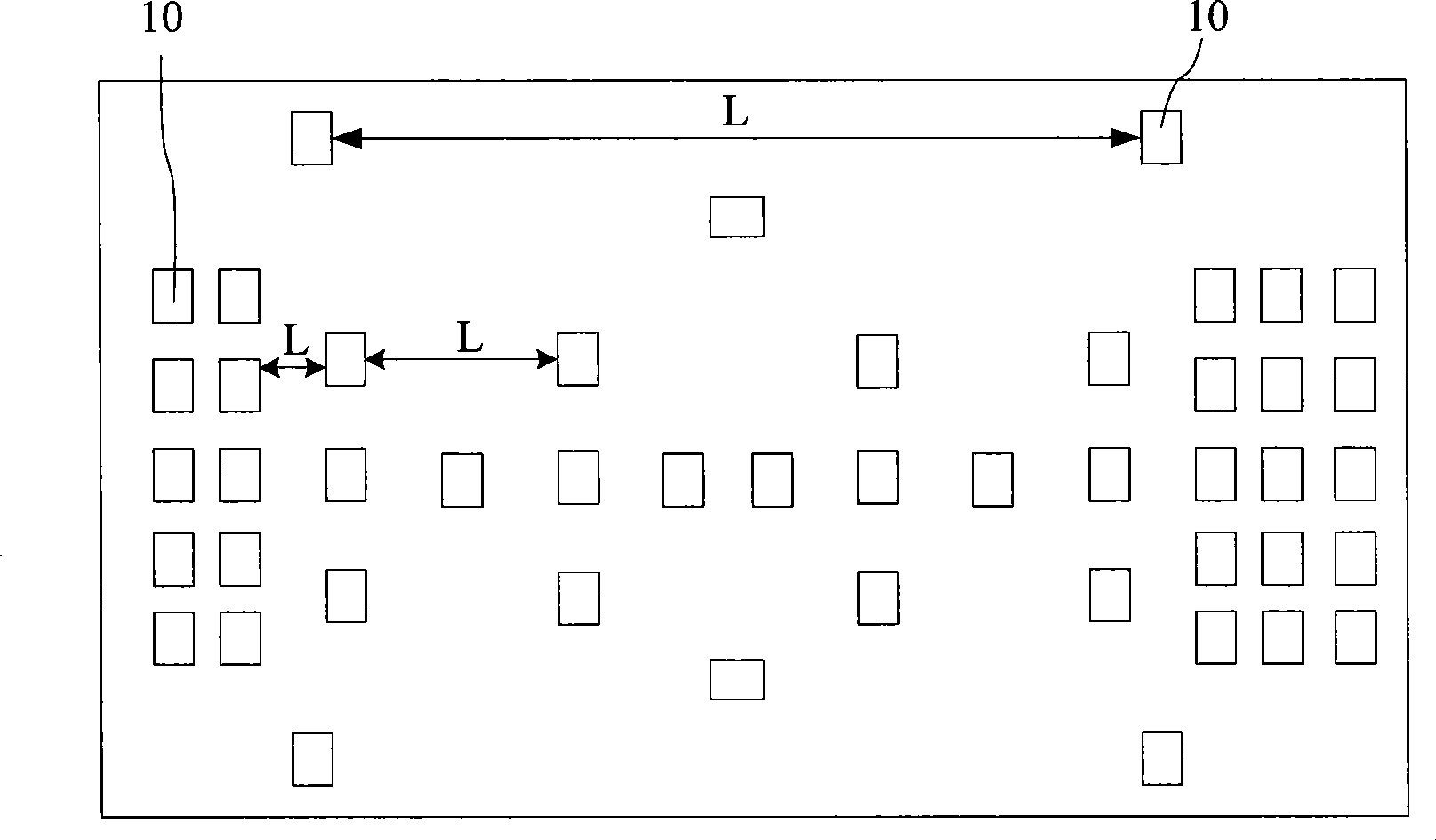

Optical approaching correction, photo mask production and graphic method

ActiveCN101458446AImprove critical dimensionsPrevent bridgingOriginals for photomechanical treatmentGraphicsCritical dimension

An optical approaching correction method comprises: determining that layout contact hole patterns are positioned in a device concentration area, a device sparse area and a device isolation area; and increasing critical dimensions of the layout contact hole patterns in the device sparse area and the device isolation area. The invention also provides a manufacturing method of a photomask plate and a graphical method thereof. The invention prevents bridge connection among the layout contact hole patterns caused by the concentration of devices and the increment of the critical dimensions, and further effectively solves short-circuit phenomenon among the devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor structure and process thereof

ActiveUS20160300755A1Short heightProcessing problemSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A semiconductor process includes the following step. A metal gate strip and a cap layer are sequentially formed in a trench of a dielectric layer. The cap layer and the metal gate strip are cut off to form a plurality of caps on a plurality of metal gates, and a gap isolates adjacent caps and adjacent metal gates. An isolation material fills in the gap. The present invention also provides semiconductor structures formed by said semiconductor process. For example, the semiconductor structure includes a plurality of stacked structures in a trench of a dielectric layer, where each of the stacked structures includes a metal gate and a cap on the metal gate, where an isolation slot isolates and contacts adjacent stacked structures at end to end, and the isolation slot has same level as the stacked structures.

Owner:MARLIN SEMICON LTD

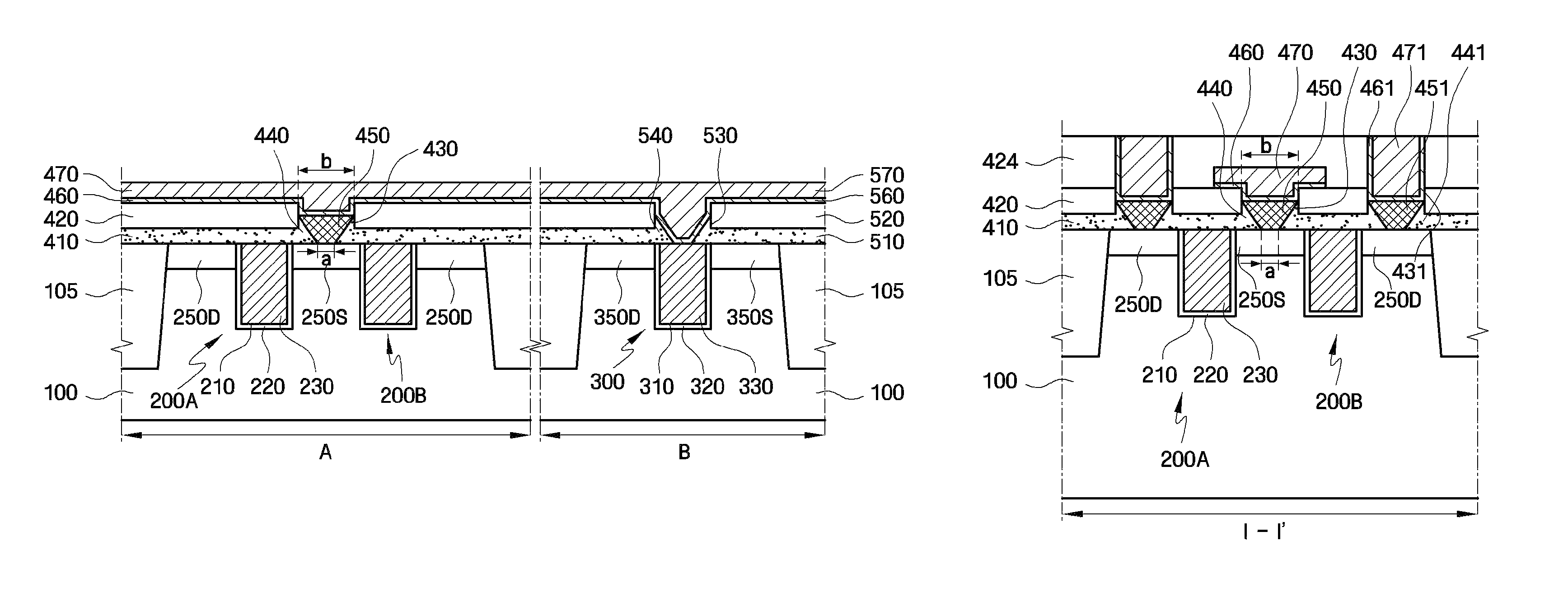

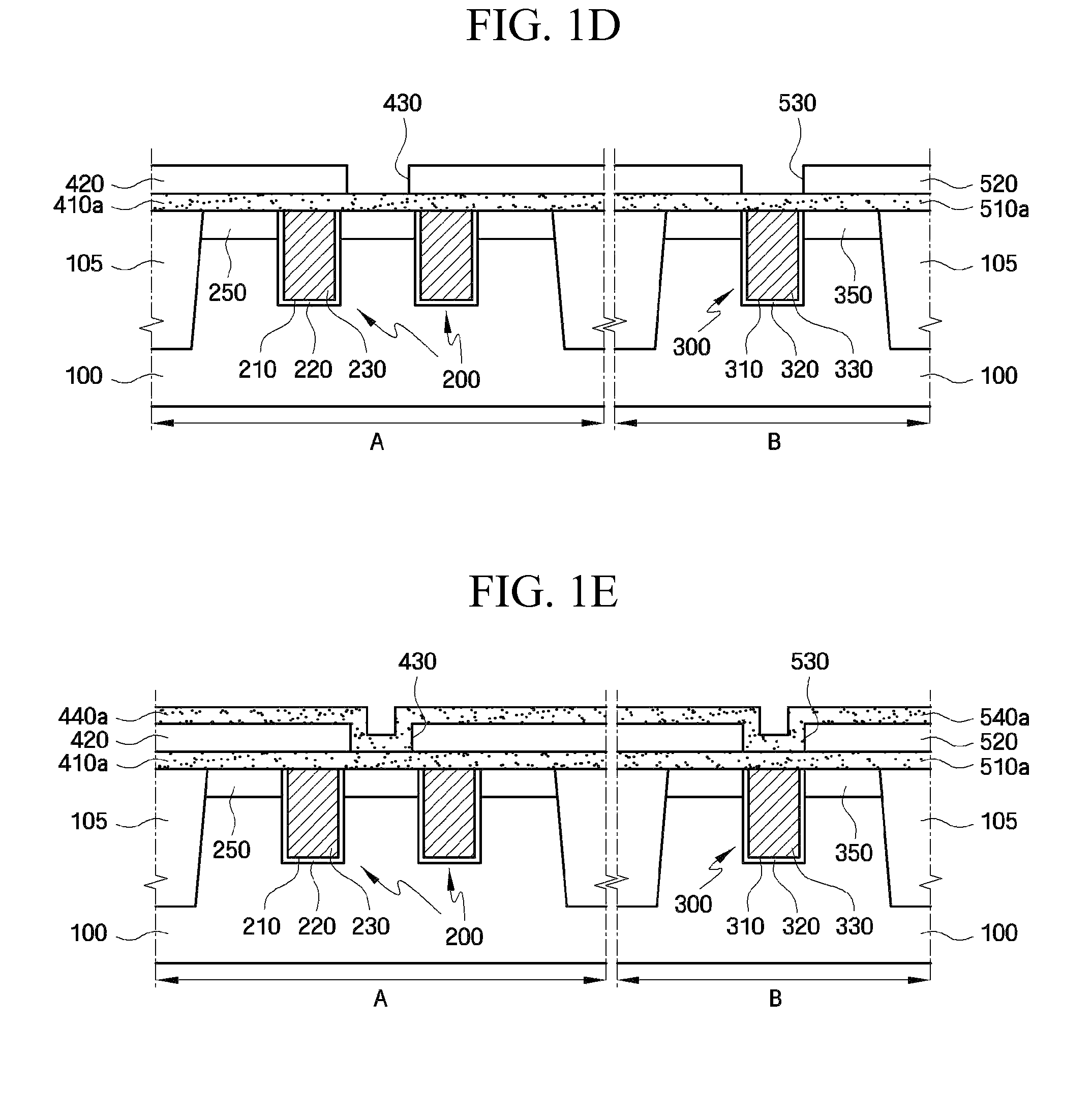

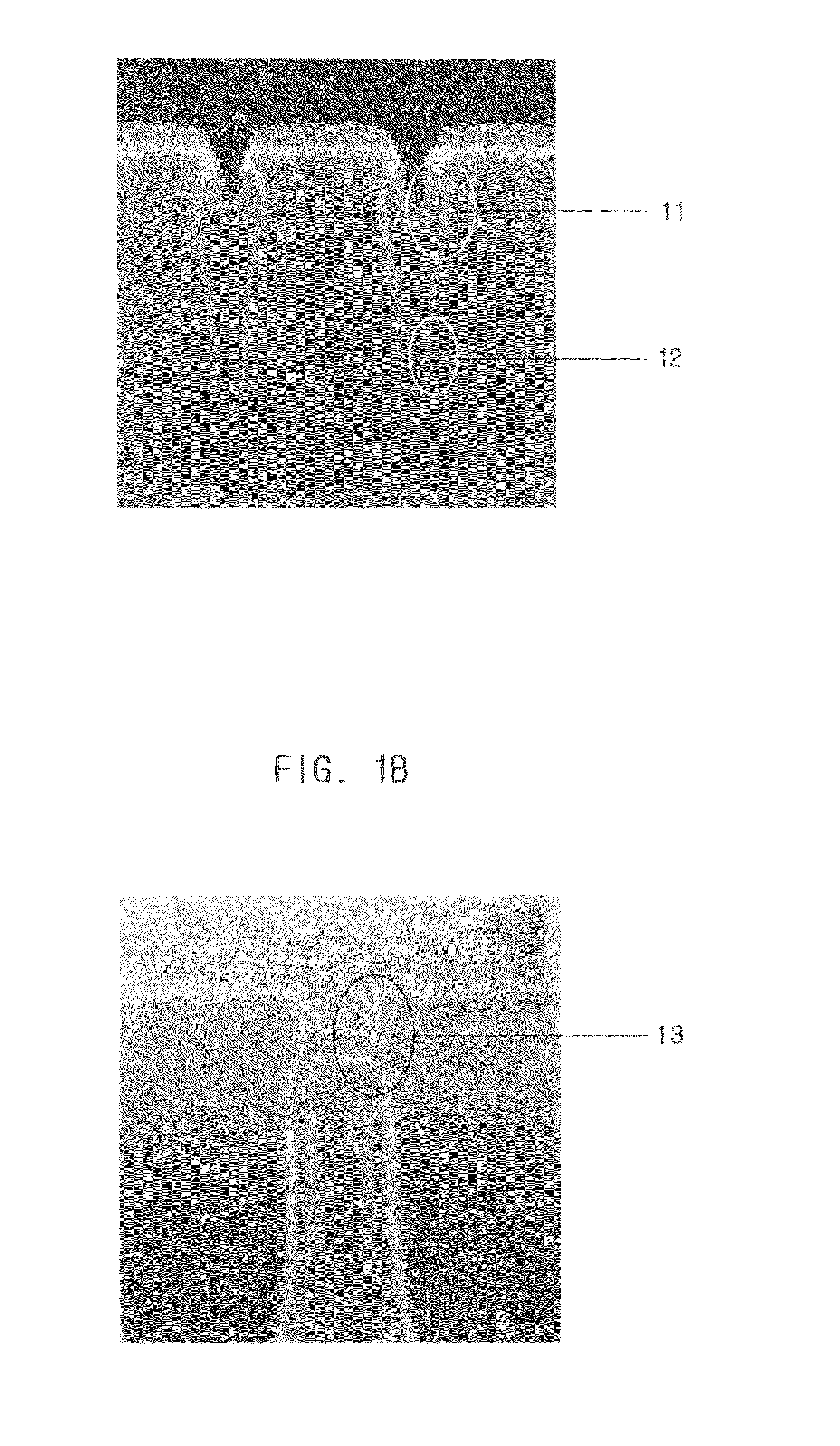

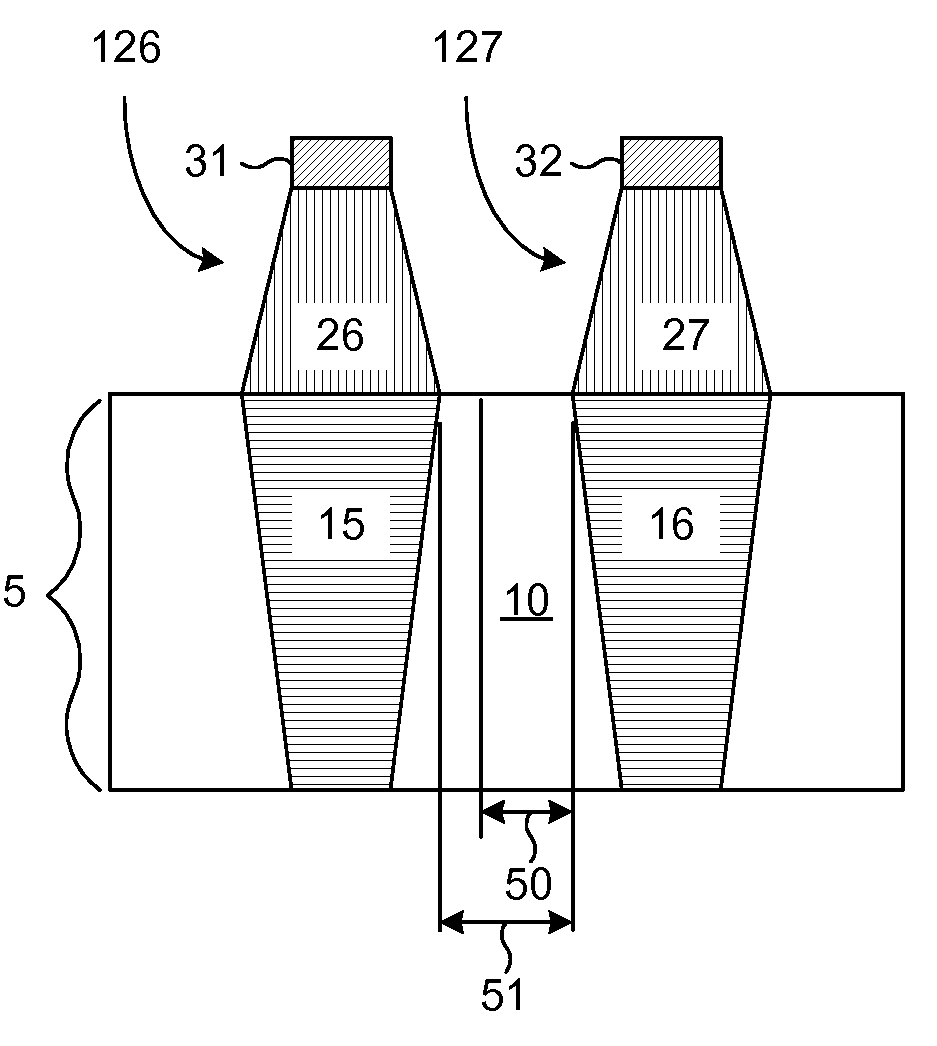

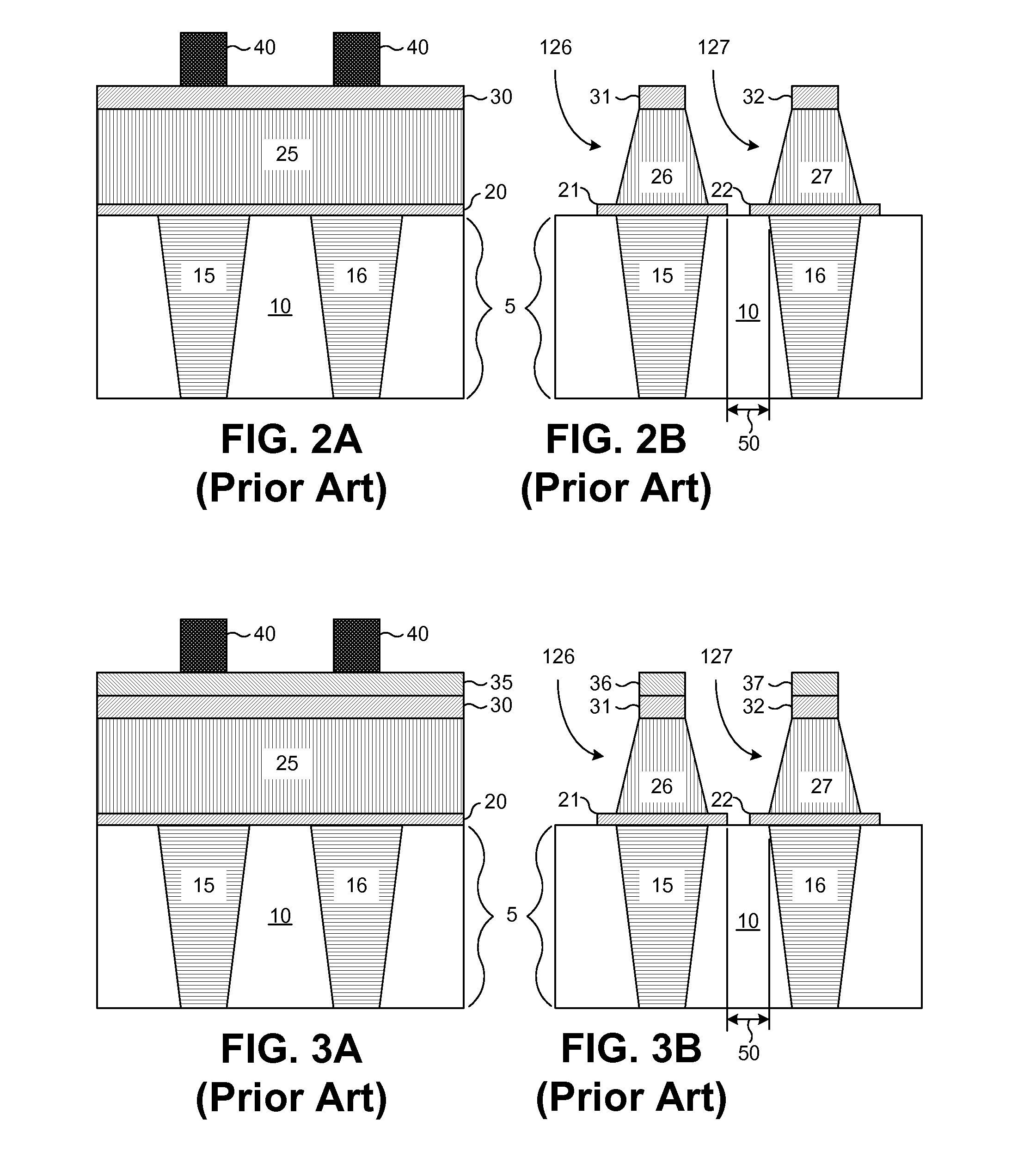

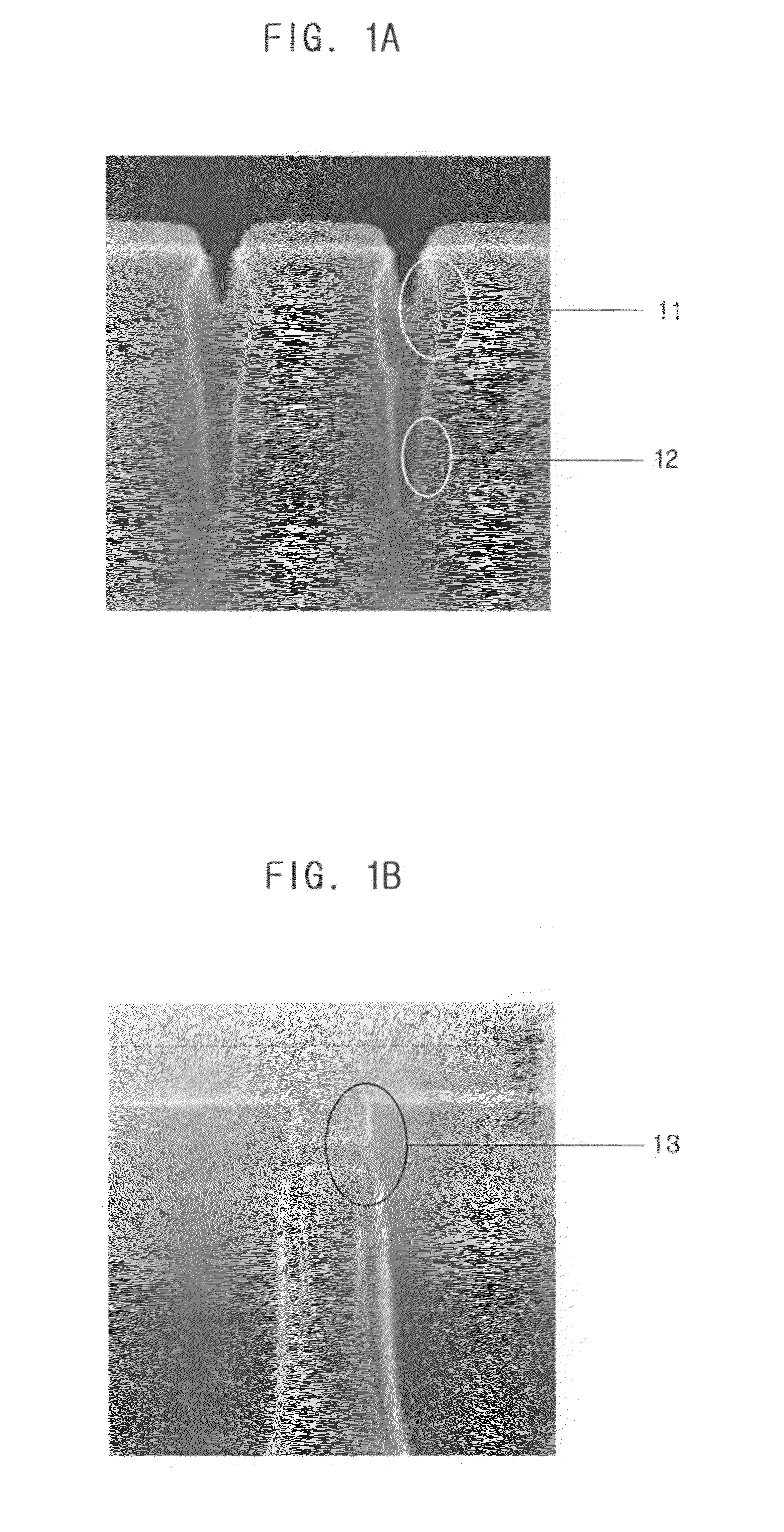

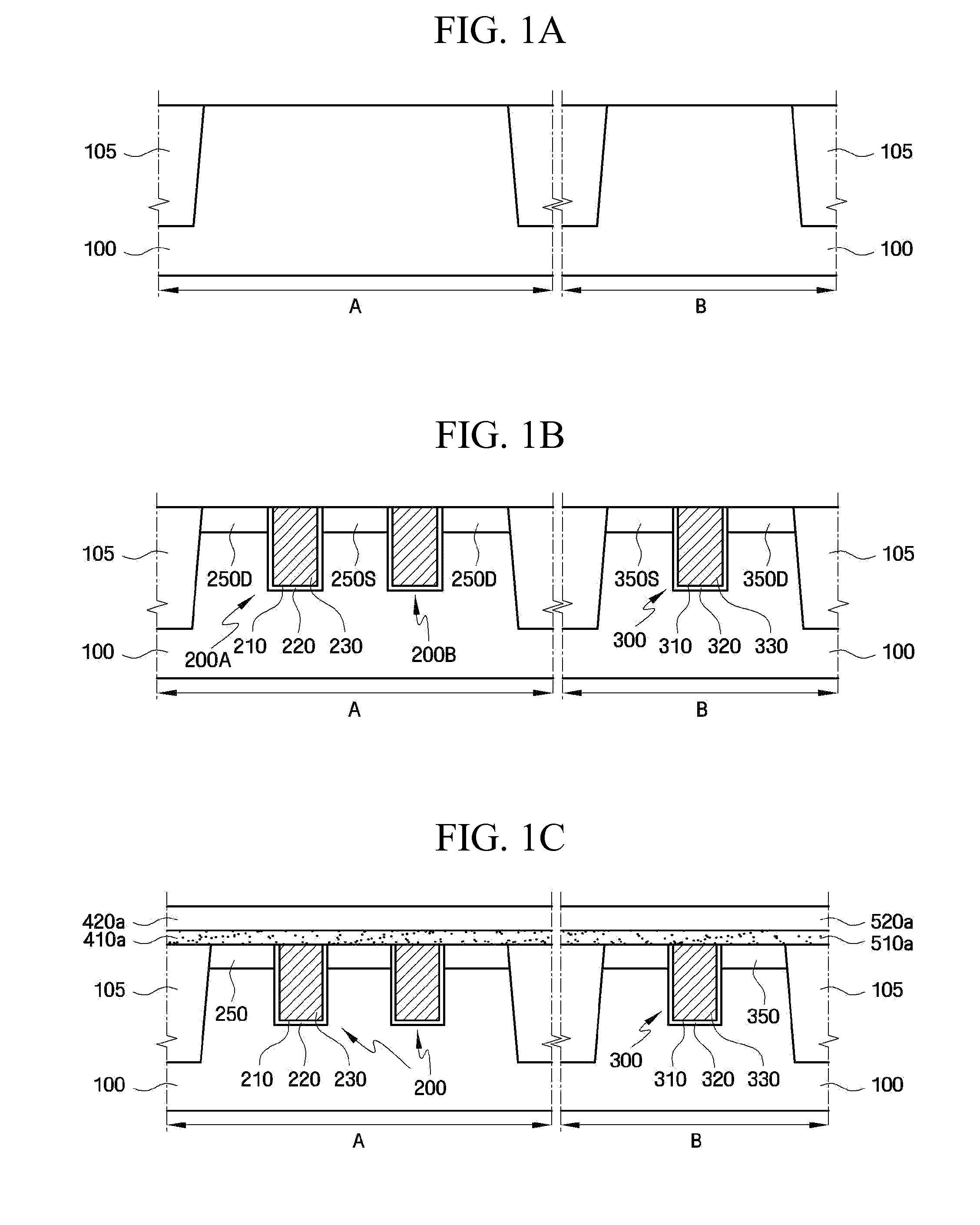

Semiconductor integrated circuit devices and fabrication methods thereof

ActiveUS20090020808A1Easy to separateImprove critical dimensionsTransistorSolid-state devicesInsulation layerEngineering

A memory cell of memory device, comprises an active region of a memory cell defined in a semiconductor substrate, and a conductive gate electrode in a trench of the active region. The gate electrode is isolated from the semiconductor substrate. An insulation layer is on the active region and on the conductive gate electrode. A conductive contact is in the insulation layer on the active region at a side of the gate electrode and isolated from the gate electrode. The contact has a first width at a top portion thereof and a second width at a bottom portion thereof, the first width being greater than the second width. The contact is formed of a single-crystal material.

Owner:IMBERATEK LLC

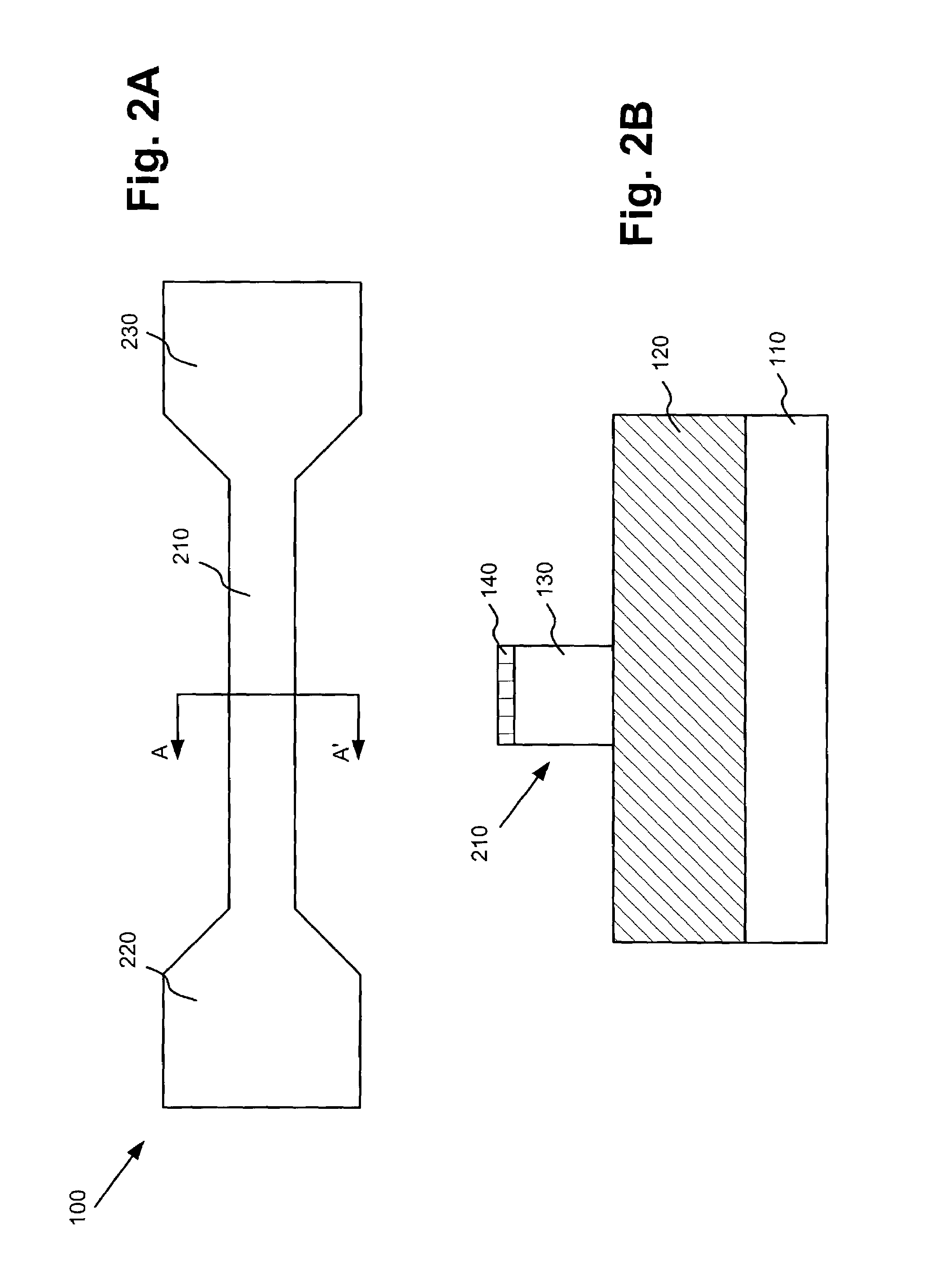

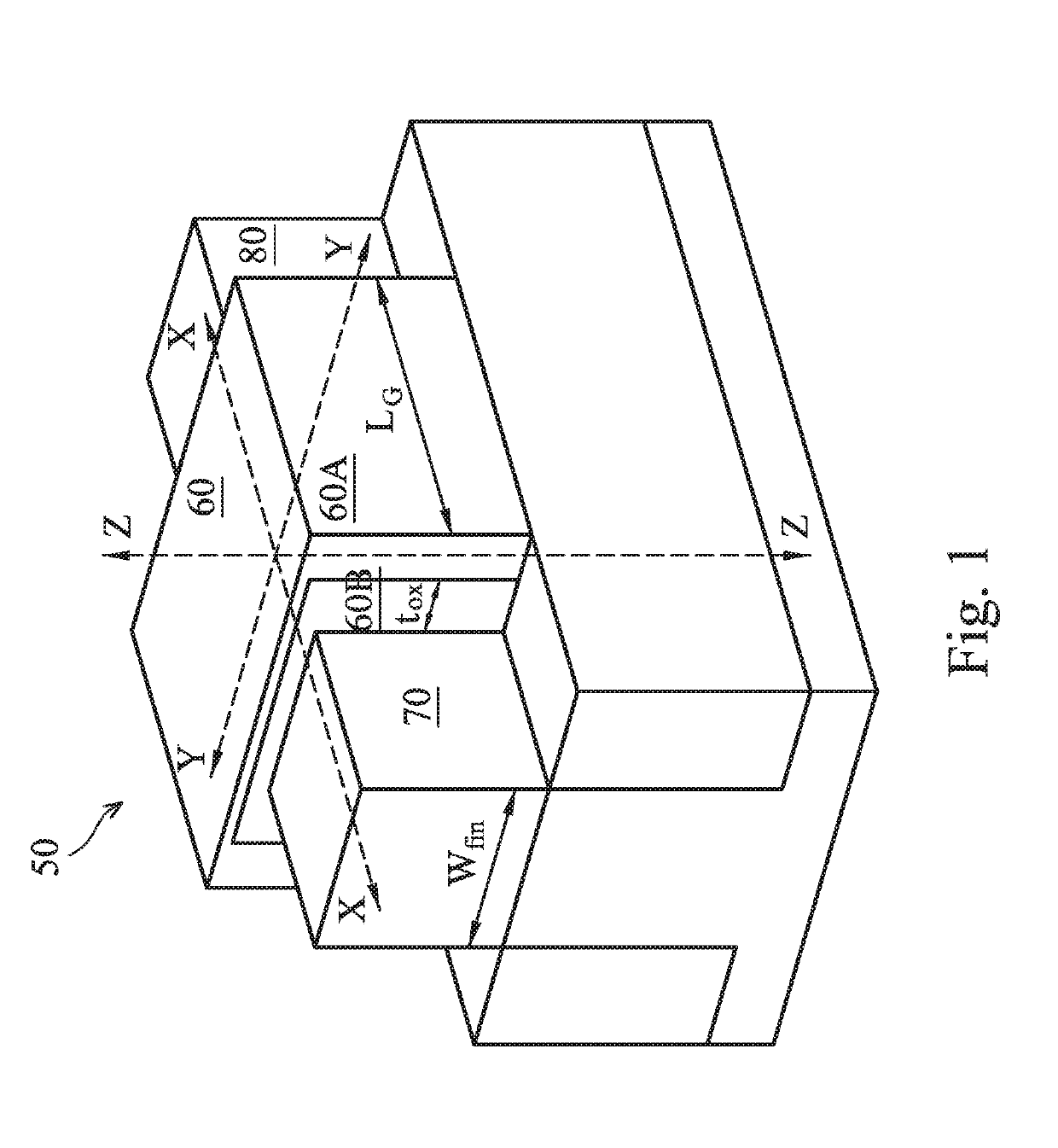

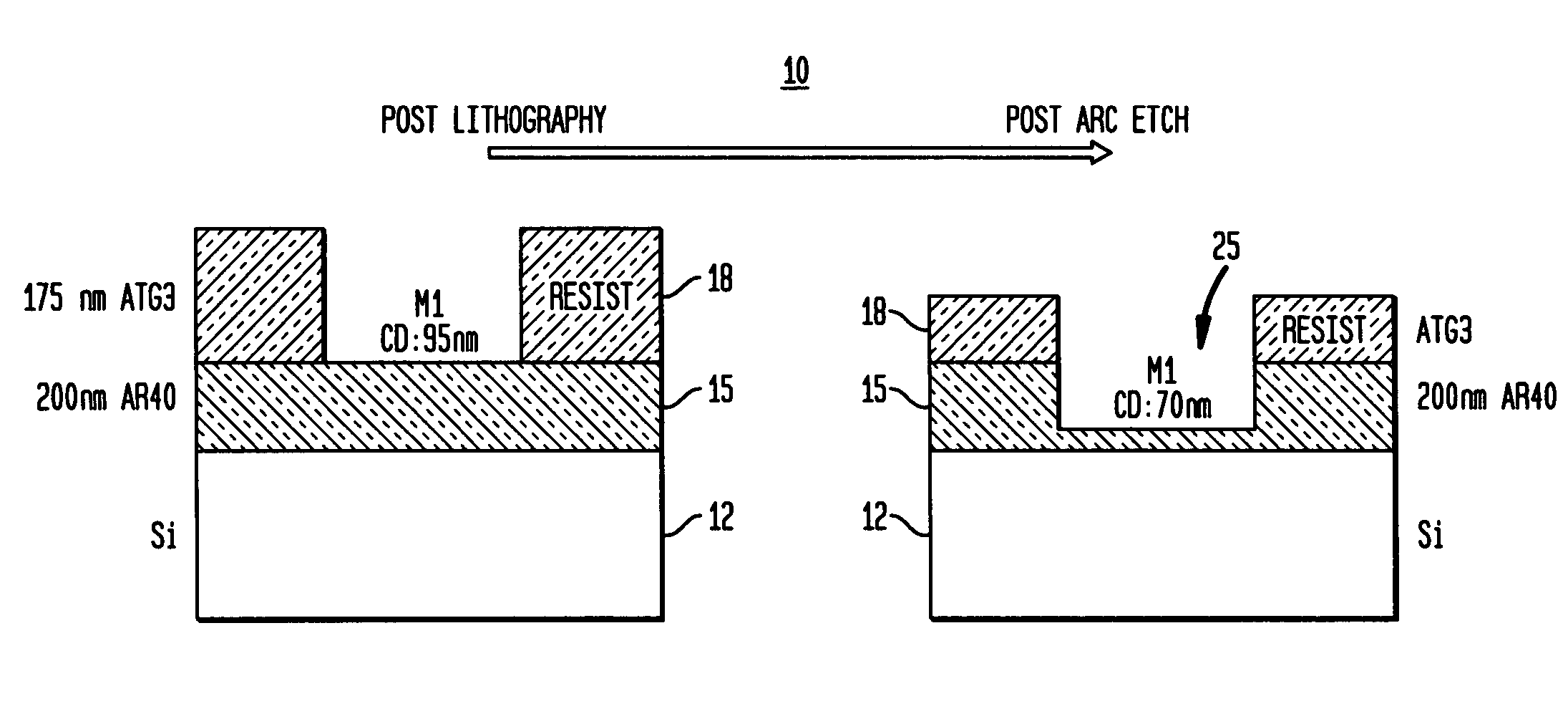

Planarizing sacrificial oxide to improve gate critical dimension in semiconductor devices

InactiveUS7091068B1Improve critical dimensionsSemiconductor/solid-state device manufacturingSemiconductor devicesCritical dimensionSemiconductor

A method of manufacturing a semiconductor device may include forming a fin structure on an insulator and depositing a gate material over the fin structure. The method may also include forming a sacrificial material over the gate material and planarizing the sacrificial material. An antireflective coating may be deposited on the planarized sacrificial material. A gate structure may then be formed by etching the gate material.

Owner:ADVANCED MICRO DEVICES INC

FinFET Devices with Embedded Air Gaps and the Fabrication Thereof

ActiveUS20190148215A1Minimizes “ footing ” profileGood yieldTransistorSolid-state devicesEngineeringSemiconductor

A semiconductor device includes a first gate structure disposed over a substrate. The first gate structure extends in a first direction. A second gate structure is disposed over the substrate. The second gate structure extends in the first direction. A dielectric material is disposed between the first gate structure and the second gate structure. An air gap is disposed within the dielectric material.

Owner:TAIWAN SEMICON MFG CO LTD

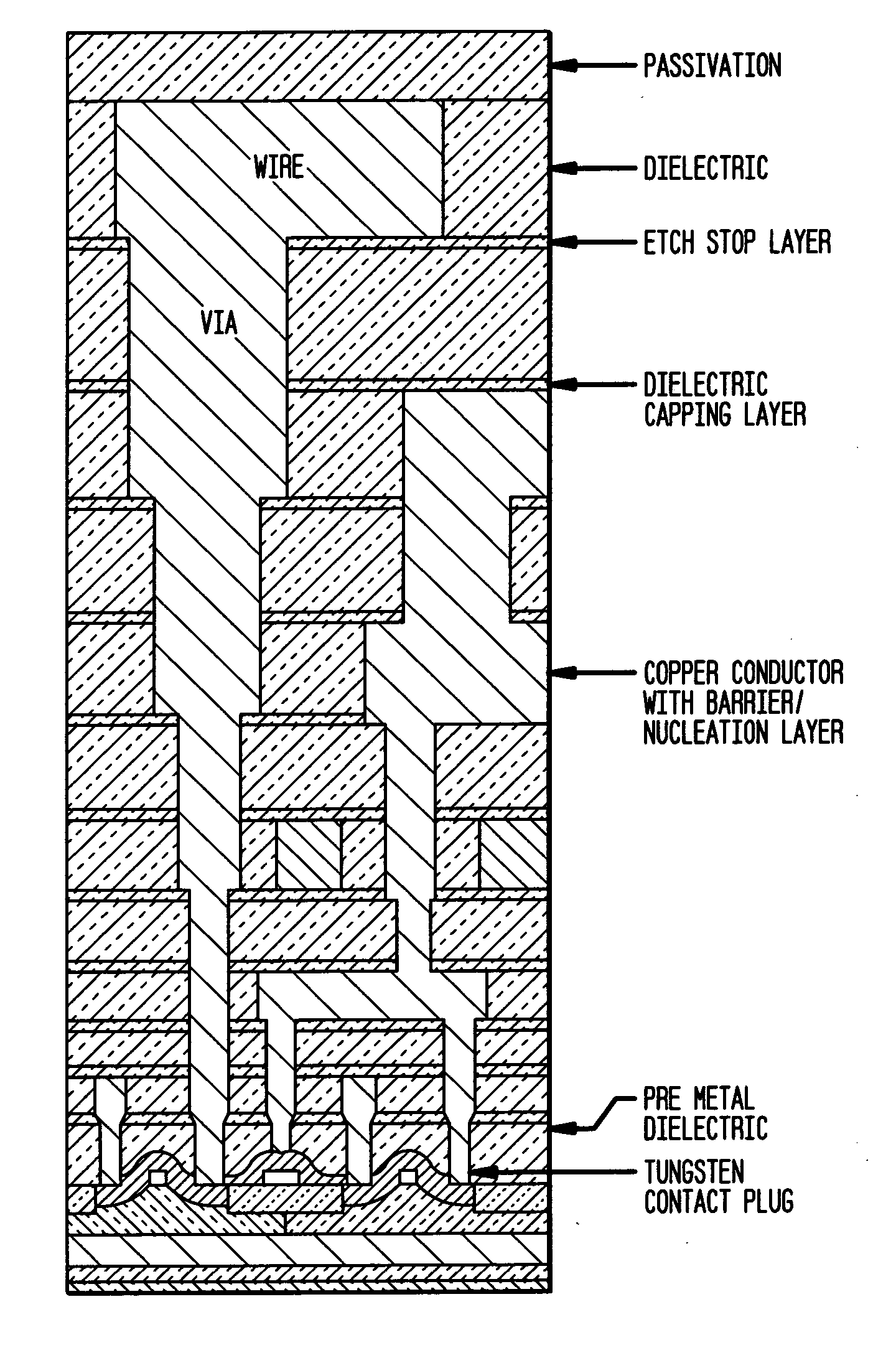

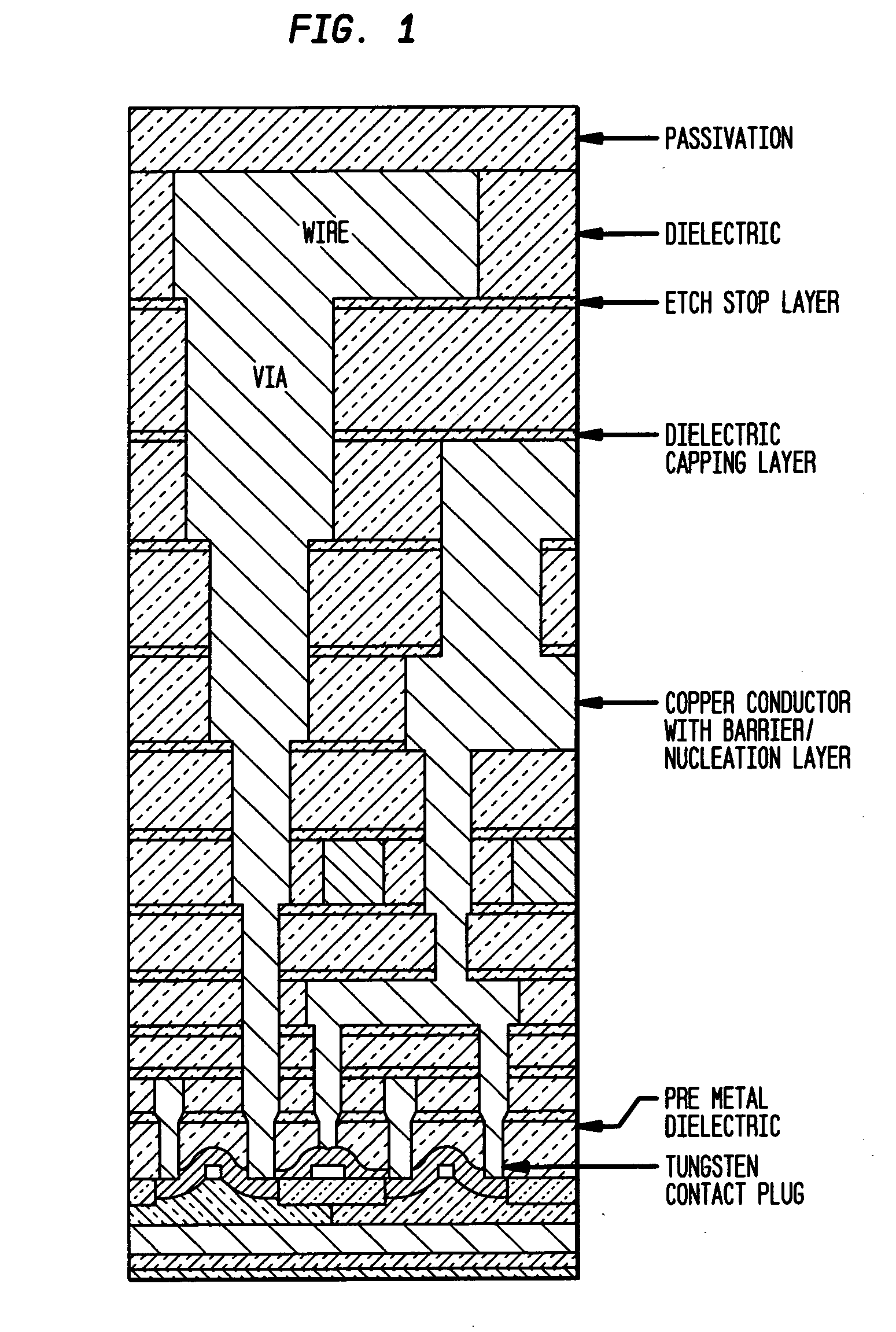

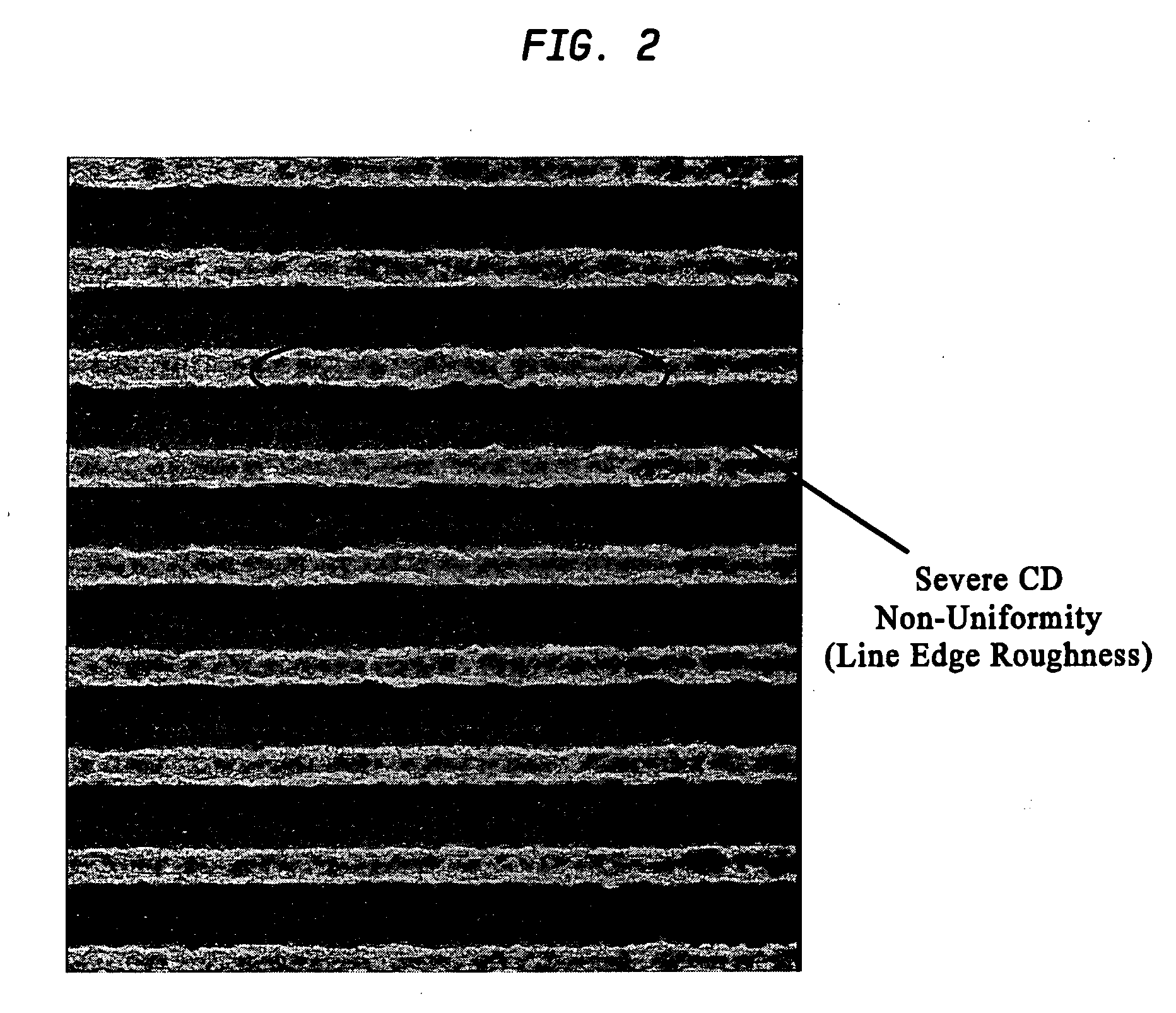

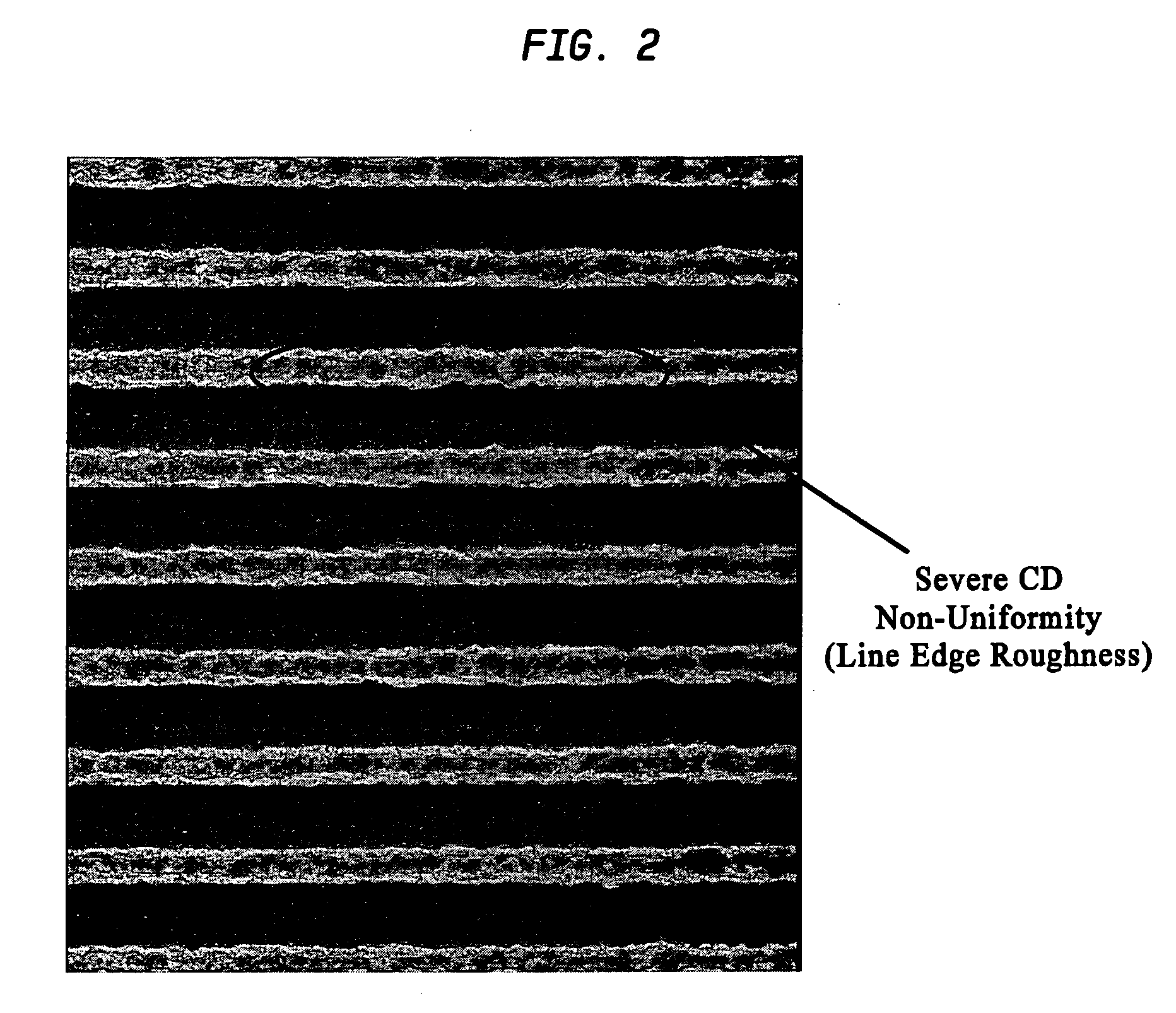

System and method for plasma induced modification and improvement of critical dimension uniformity

ActiveUS20060099816A1Reduce post lithographic CD non-uniformity LEREnhanced linerSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesDevice materialEngineering

Novel interconnect structures possessing a OSG or polymeric-based (90 nm and beyond BEOL technologies) in which advanced plasma processing is utilized to reduce post lithographic CD non-uniformity (“line edge roughness”) in semiconductor devices. The novel interconnect structure has enhanced liner and seed conformality and is therefore capable of delivering improved device performance, functionality and reliability.

Owner:GLOBALFOUNDRIES US INC

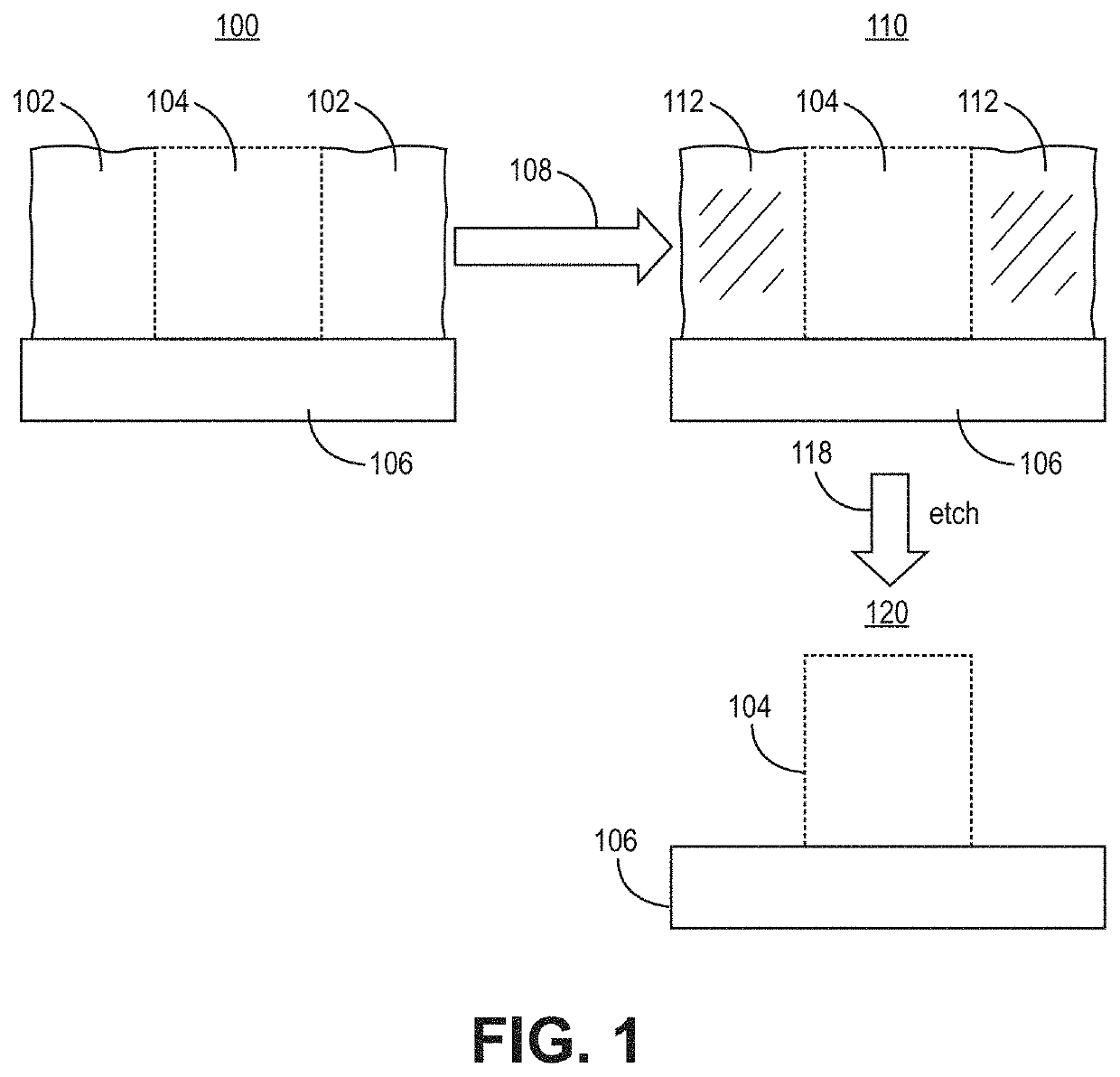

Method of reverse tone patterning

ActiveUS20170140921A1Improve critical dimensionsMinimizes variabilityPhotomechanical apparatusSemiconductor/solid-state device manufacturingCritical dimensionComputer science

Methods of reversing the tone of a pattern having non-uniformly sized features. The methods include depositing a highly conformal hard mask layer over the patterned layer with a non-planar protective coating and etch schemes for minimizing critical dimension variations.

Owner:CANON KK

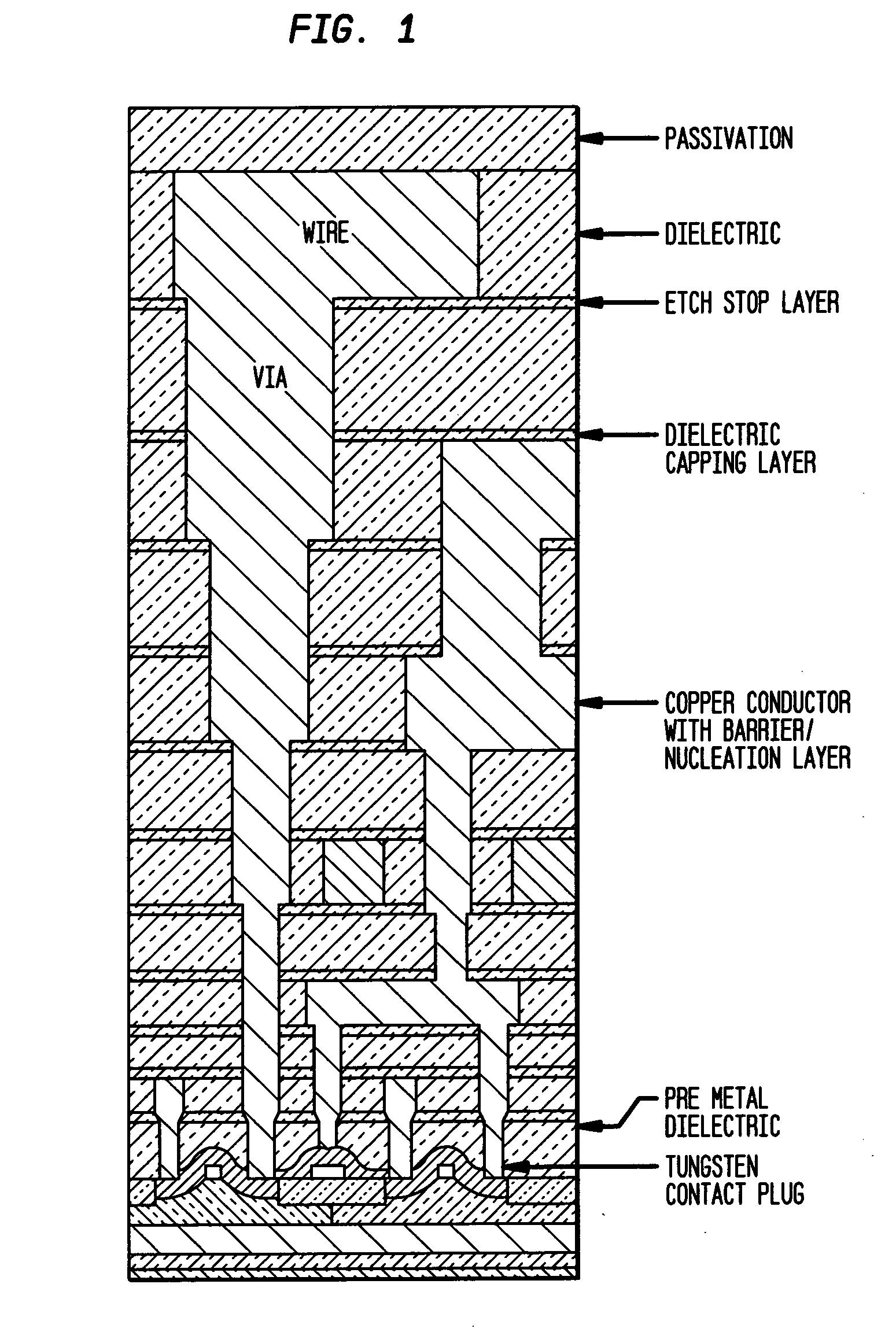

System and method for plasma induced modification and improvement of critical dimension uniformity

ActiveUS7196014B2Reduce unevennessImproved liner and seed conformalitySemiconductor/solid-state device manufacturingBulk negative resistance effect devicesEngineeringCritical dimension

Novel interconnect structures possessing a OSG or polymeric-based (90 nm and beyond BEOL technologies) in which advanced plasma processing is utilized to reduce post lithographic CD non-uniformity (“line edge roughness”) in semiconductor devices. The novel interconnect structure has enhanced liner and seed conformality and is therefore capable of delivering improved device performance, functionality and reliability.

Owner:GLOBALFOUNDRIES U S INC

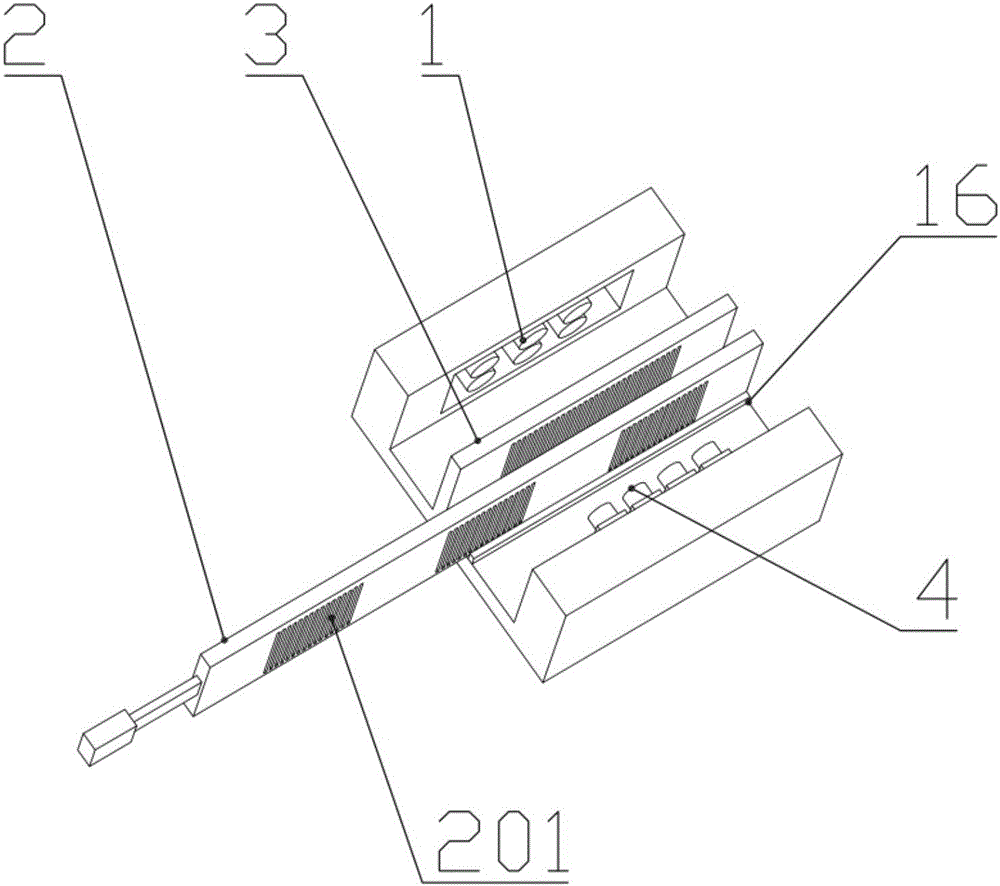

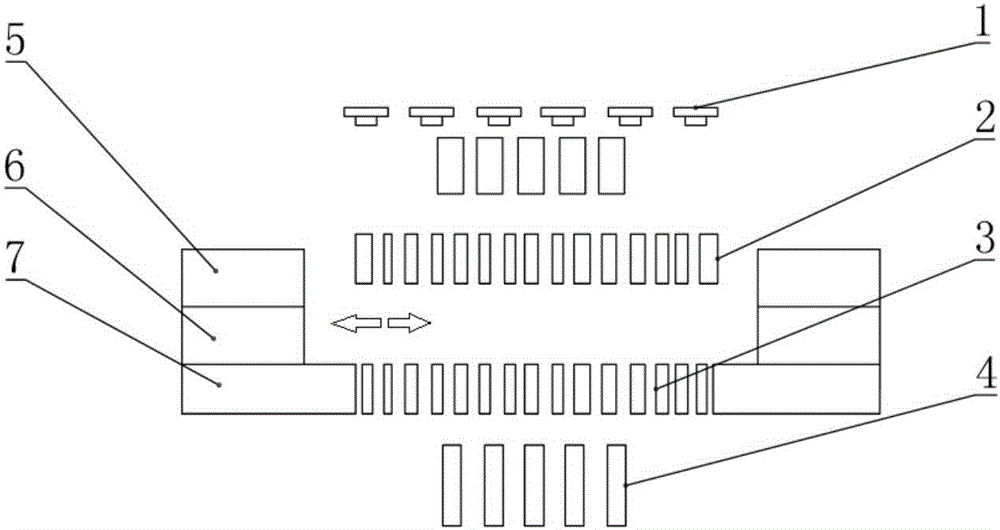

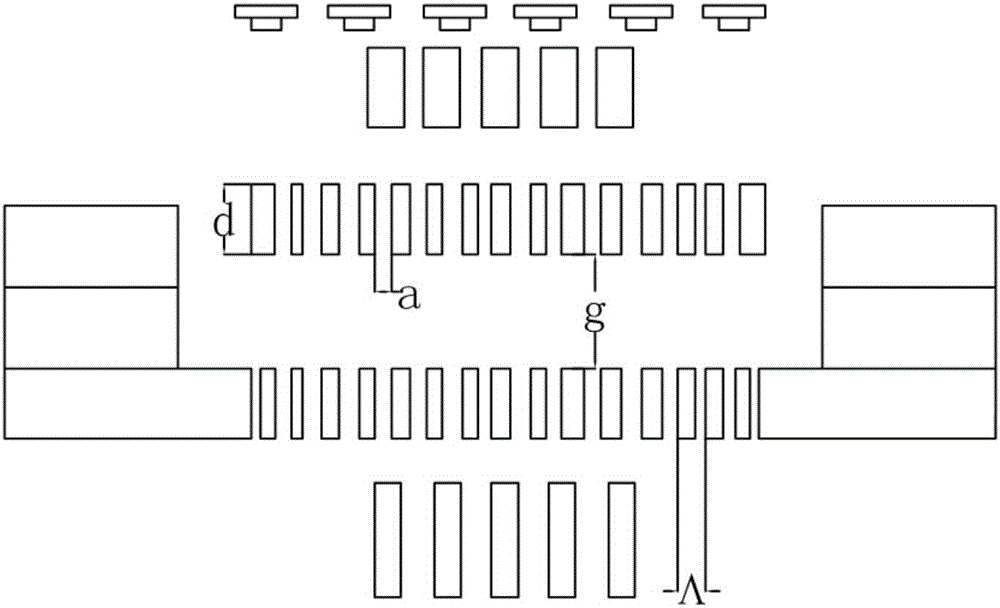

High-accuracy wide-range double-layer nano-grating micro displacement detection device

ActiveCN106524921ASmall grating periodHigh precisionUsing optical meansPhotodetectorPhotovoltaic detectors

The present invention relates to a high-accuracy wide-range double-layer nano-grating micro displacement detection device. The micro displacement detection device includes a displacement sensing module, a processing unit and a display unit; the displacement sensing module is connected with the display unit through the processing unit; the displacement sensing module comprises double nano-grating layers which can move relative to each other; the double nano-grating layers include a movable nano-grating array and fixed nano-gratings; a plurality of nano-grating regions are spliced to form the movable nano-grating array; certain intervals are left between the plurality of nano-grating regions; the processing unit includes a subdividing circuit; and the subdividing circuit can improve the resolution of the output signals of a photodetector array. The grating period of the micro displacement detection device is smaller than the grating period of an existing micrometer-scale device, and therefore, the micro-displacement detection precision of the gratings is improved; the grating regions of the movable nano-grating array are spliced, so that the range of the micro displacement detection device is wider. The micro displacement detection device has the advantages of compact overall structure, high miniaturization degree and higher practicality.

Owner:ZHONGBEI UNIV

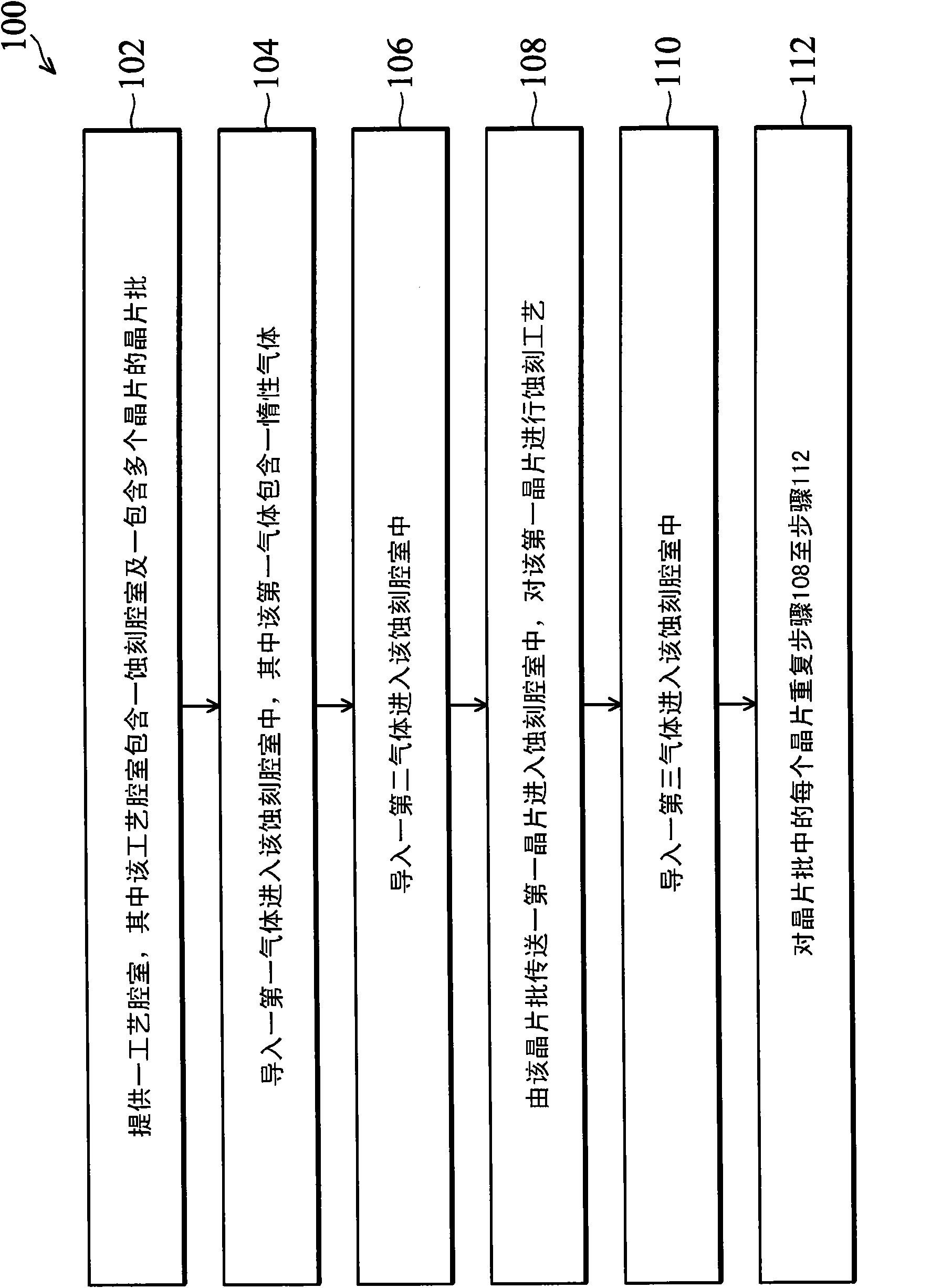

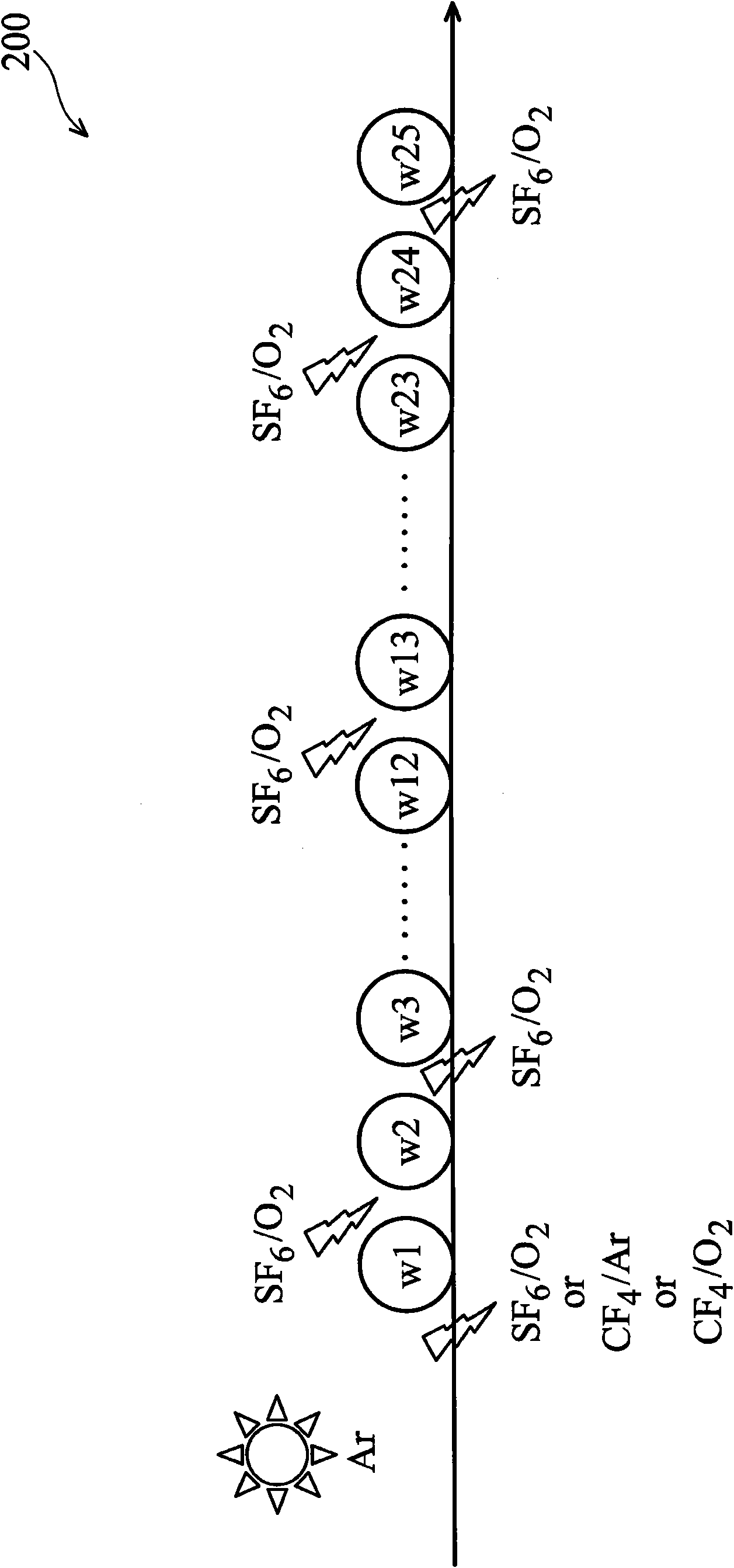

Method for pre-conditioning and stabilizing an etching chamber and method for cleaning an etching chamber

ActiveCN101685771AImprove critical dimensionsImproved variation of key dimensionsElectric discharge tubesSemiconductor/solid-state device manufacturingPre conditioningCleaning methods

A method for pre-conditioning and stabilizing an etching chamber and a method for cleaning an etching chamber are provided. The method for cleaning an etching chamber comprises providing an etching chamber; introducing a first gas comprising an inert gas into the etching chamber for a first period of time; and transporting a first wafer into the etching chamber after the first period of time, wherein the first wafer undergoes an etching process. The embodiment has one or a plurality of advantages of (1) reducing the pollutants and impurities in the chamber; (2) reducing wafer effect of head pieces; (3) improving the critical size of the wafer; (4) minimizing the damage due to the long-term use of chamber; (5) reducing the average time of cleaning; (6) lowering the cost of technical processing of wafer; and (7) increasing the quantity of the wafer that can be processed per hour.

Owner:TAIWAN SEMICON MFG CO LTD

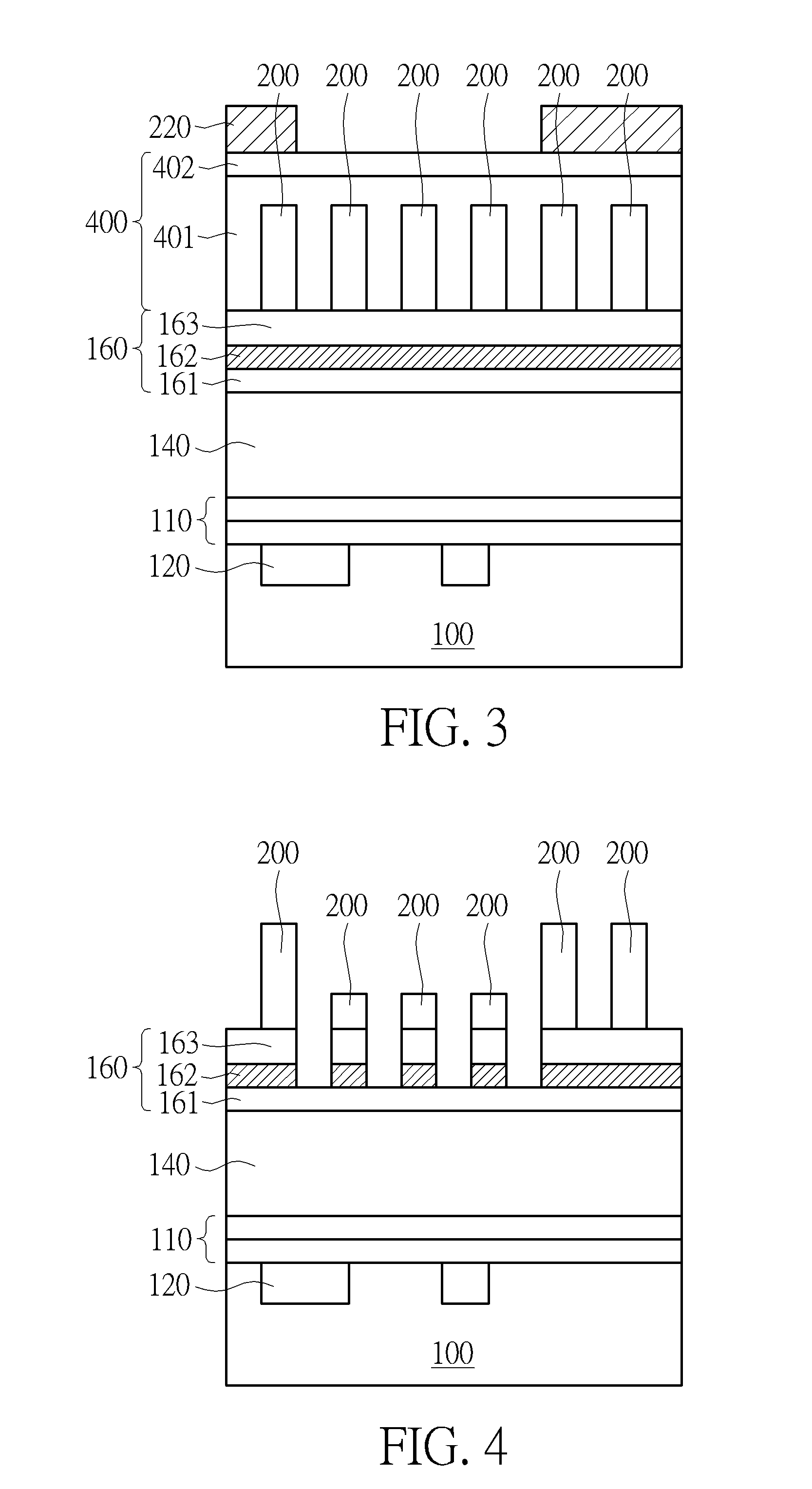

Image sensor and formation method thereof

InactiveCN108470740AImprove critical dimensionsGuaranteed performanceSolid-state devicesSemiconductor/solid-state device manufacturingCarbon layerInsulation layer

The technical scheme discloses an image sensor and a formation method thereof; the image sensor forming method comprises the following steps: providing a semiconductor substrate; forming a discrete photodiode and a deep trench isolation structure in the semiconductor substrate, wherein the deep trench isolation structure is located between the photodiode; forming an interlayer dielectric layer onthe surface of the semiconductor substrate so as to cover the photodiode and the deep trench isolation structure; forming an amorphous form carbon layer on the interlayer dielectric layer; etching theamorphous form carbon layer so as to expose the interlayer dielectric layer surface, thus forming a groove; forming an insulation layer on the surface of the amorphous form carbon layer, and the sidewalls and the bottom of the groove; forming a metal layer on the surface of the insulation layer; etching the metal layer and the insulation layer so as to expose the interlayer dielectric layer surface, thus forming discrete metal grids; removing the amorphous form carbon layer. When the key dimensions of the formed metal grids are small enough, collapse conditions cannot happen.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

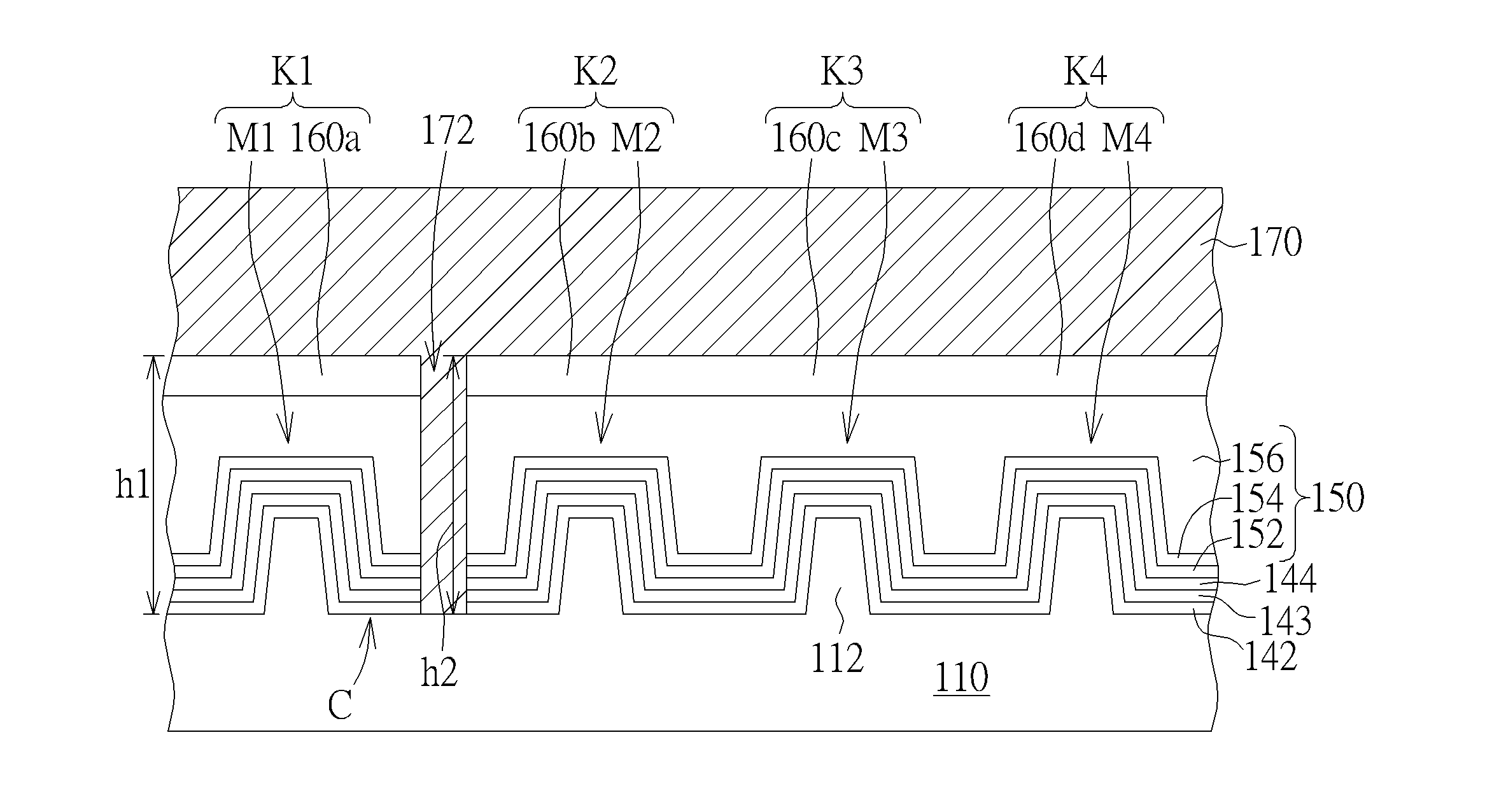

Plug structure and process thereof

ActiveUS20140264481A1Improve performanceAdhesionSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

A plug structure including a first dielectric layer, a second dielectric layer, a barrier layer and a second plug is provided. The first dielectric layer having a first plug therein is located on a substrate, wherein the first plug physically contacts a source / drain in the substrate. The second dielectric layer having an opening exposing the first plug is located on the first dielectric layer. The barrier layer conformally covers the opening, wherein the barrier layer has a bottom part and a sidewall part, and the bottom part is a single layer and physically contacts the first plug while the sidewall part is a dual layer. The second plug fills the opening and on the barrier layer. Moreover, a process of forming a plug structure is also provided.

Owner:UNITED MICROELECTRONICS CORP

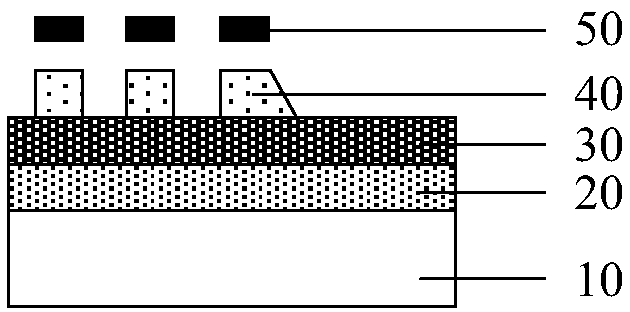

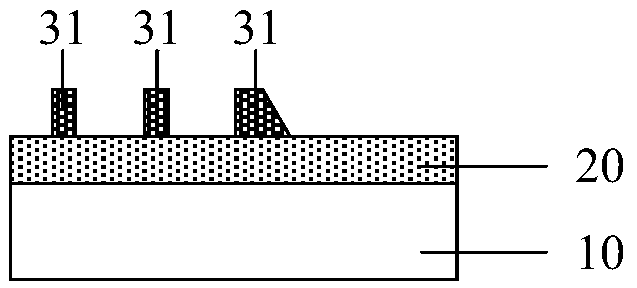

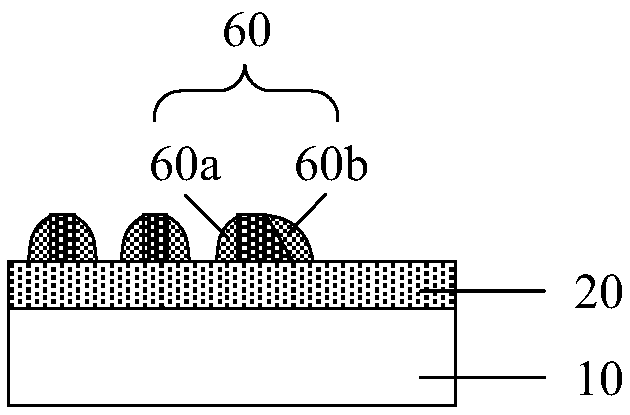

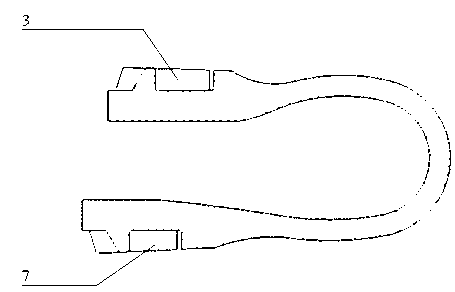

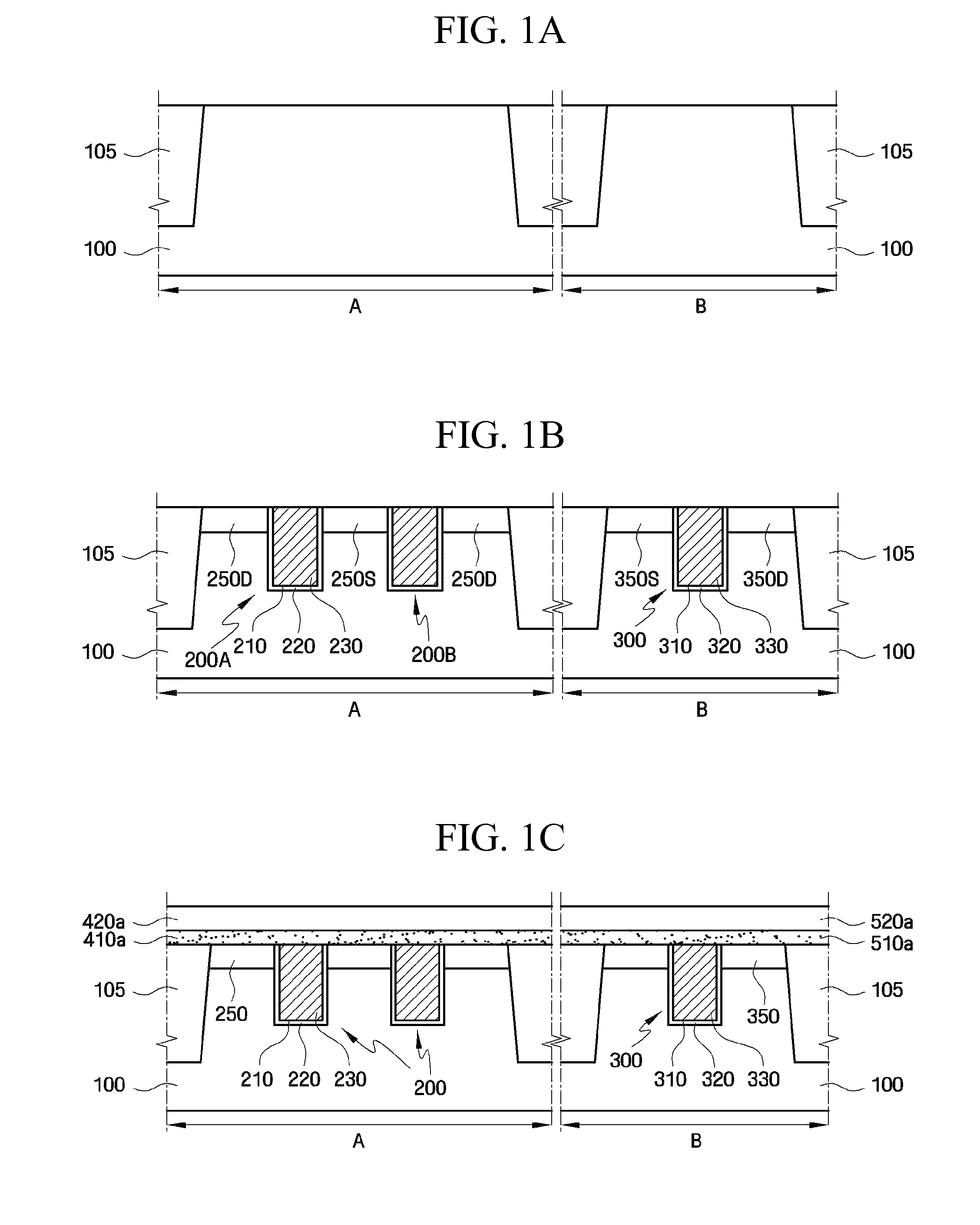

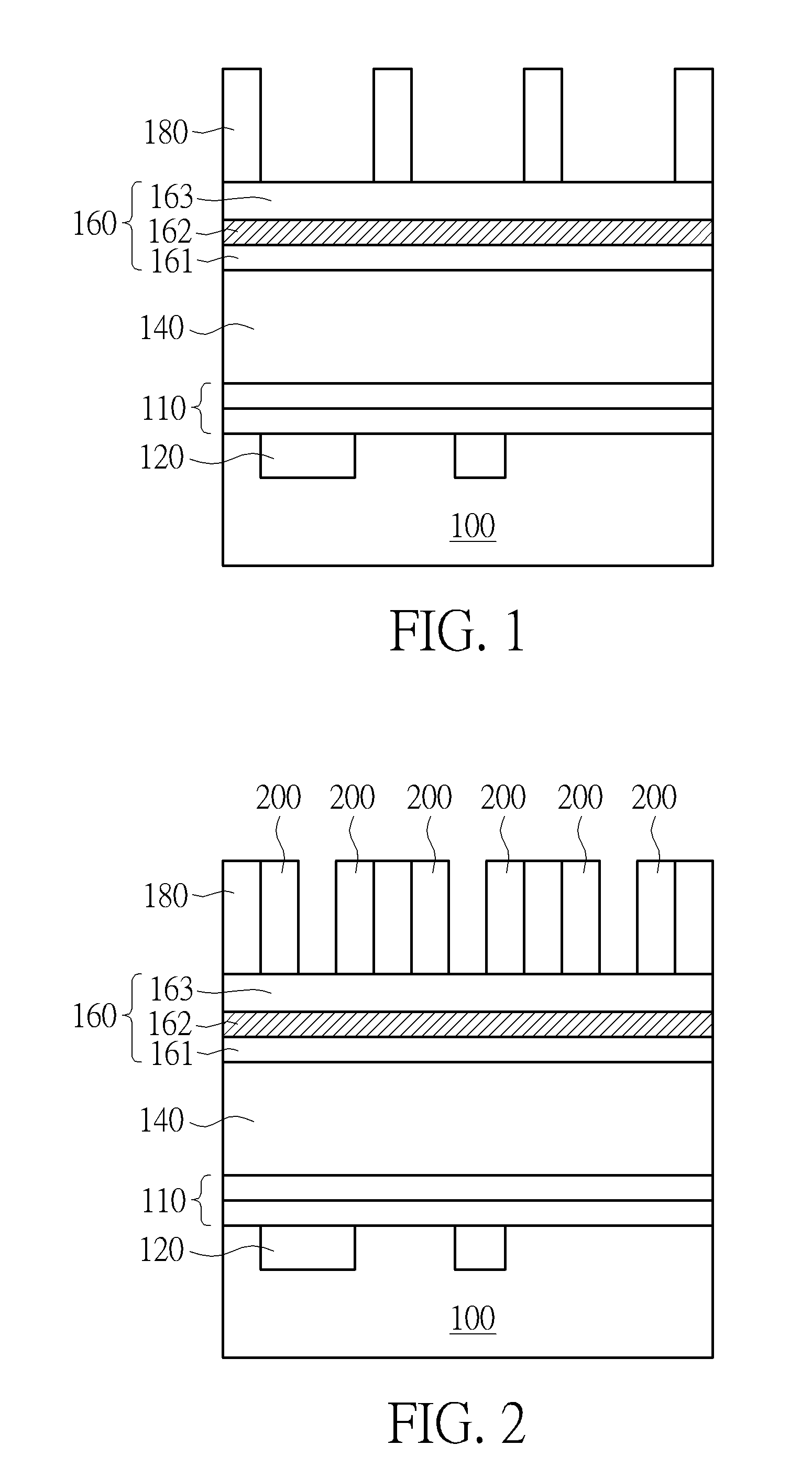

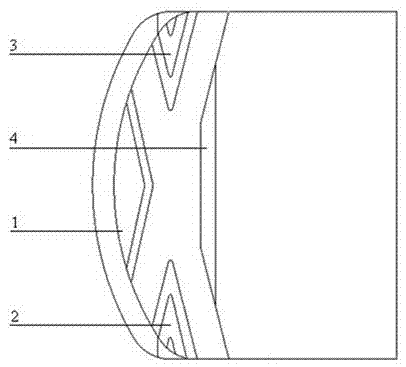

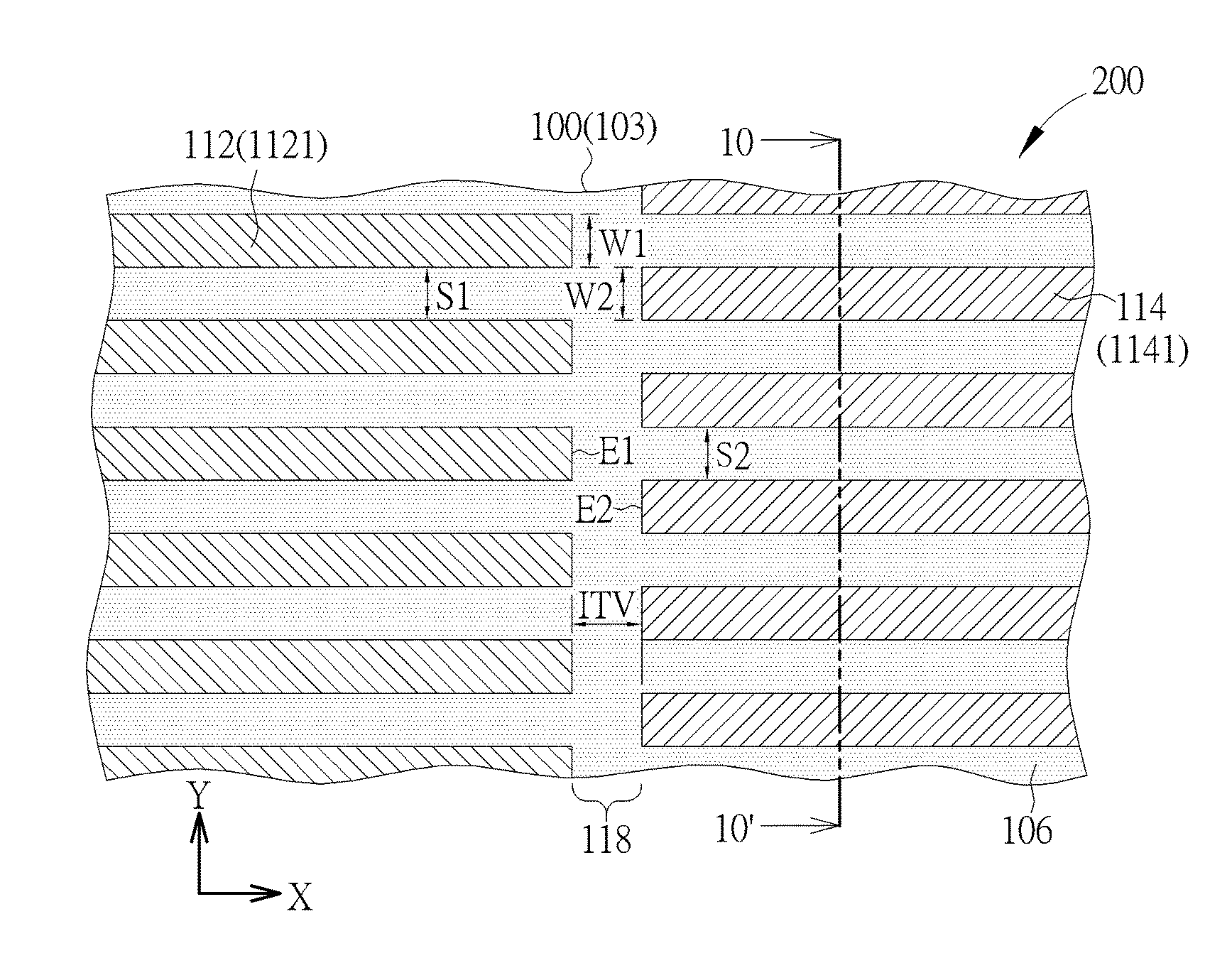

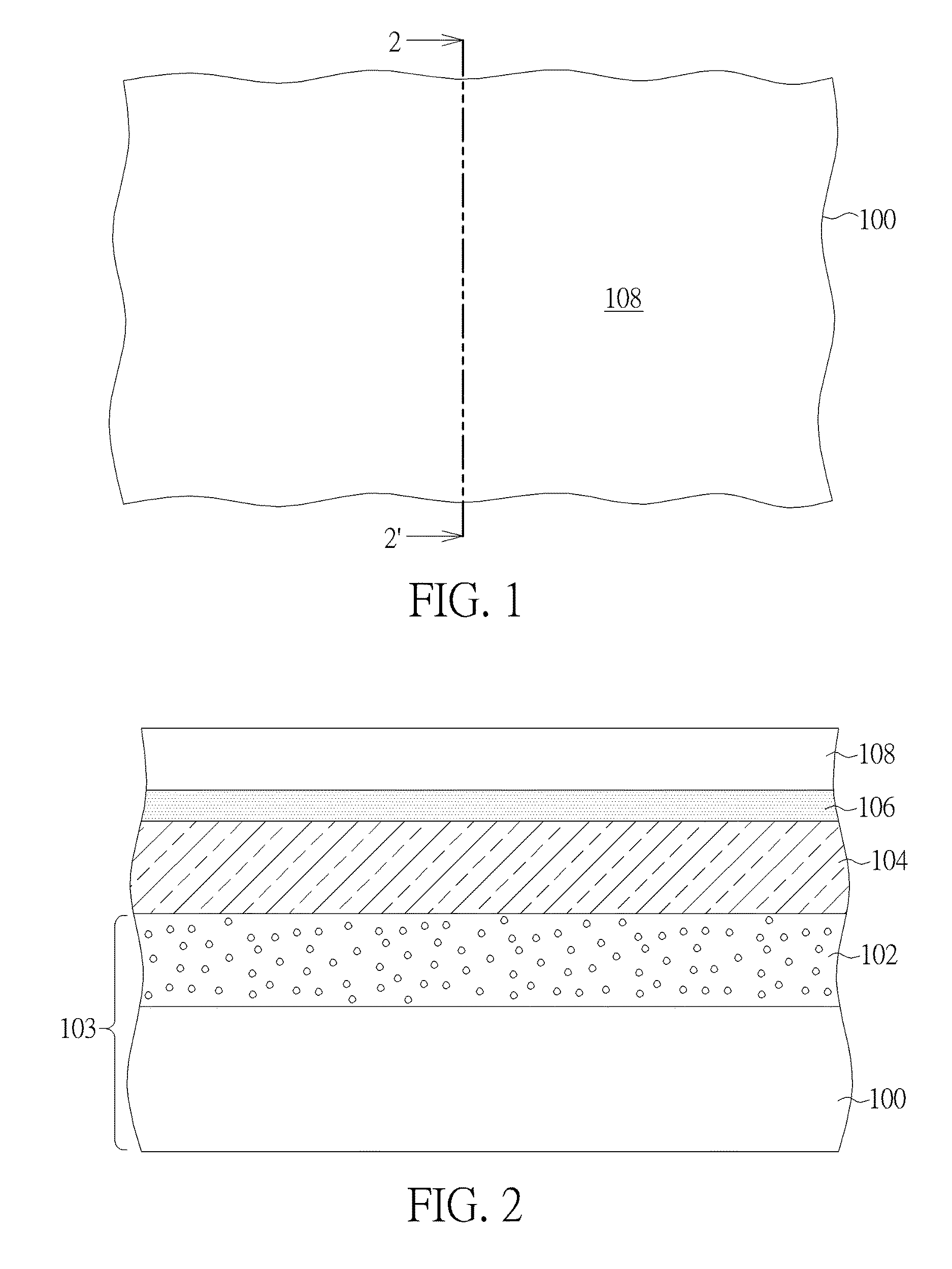

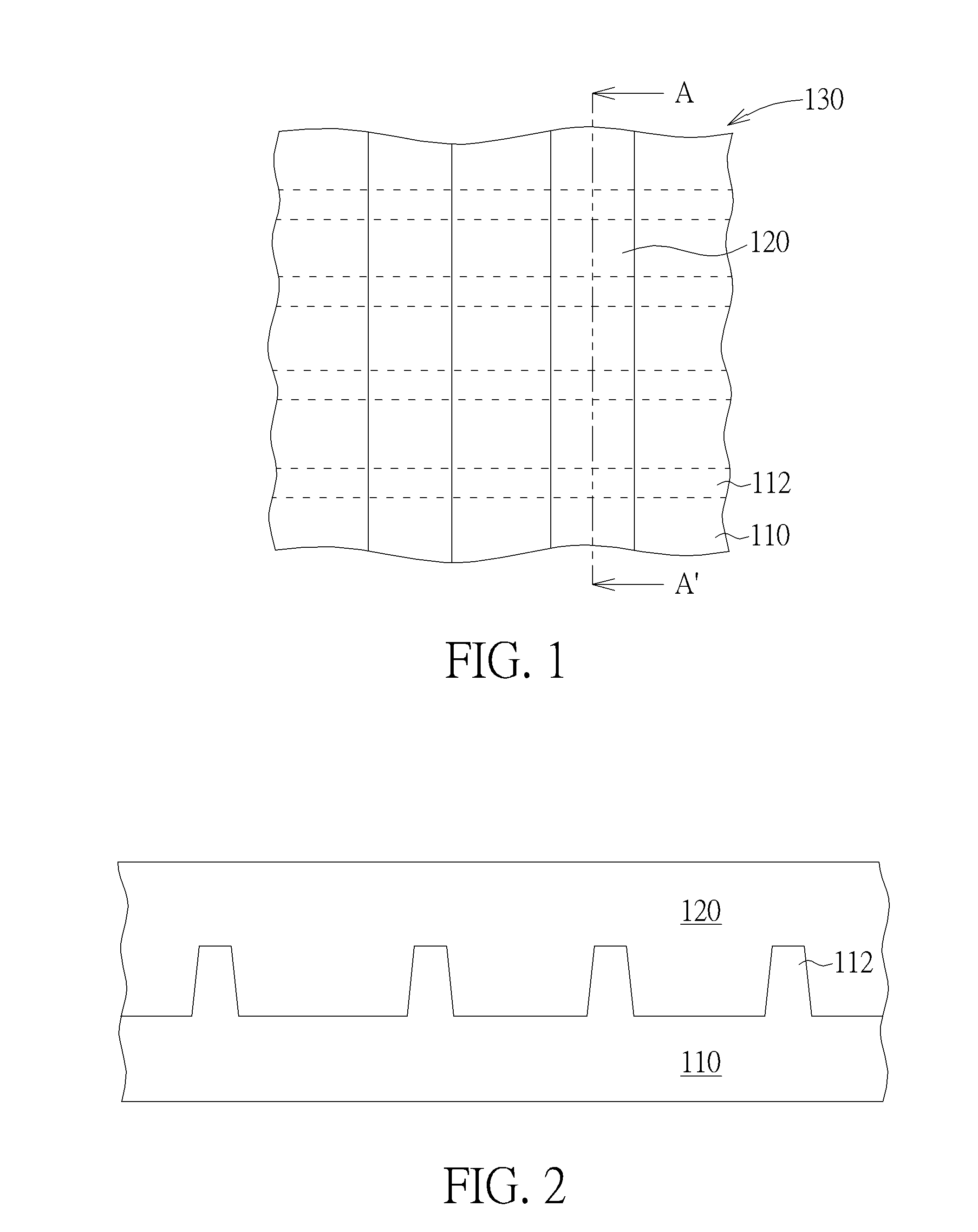

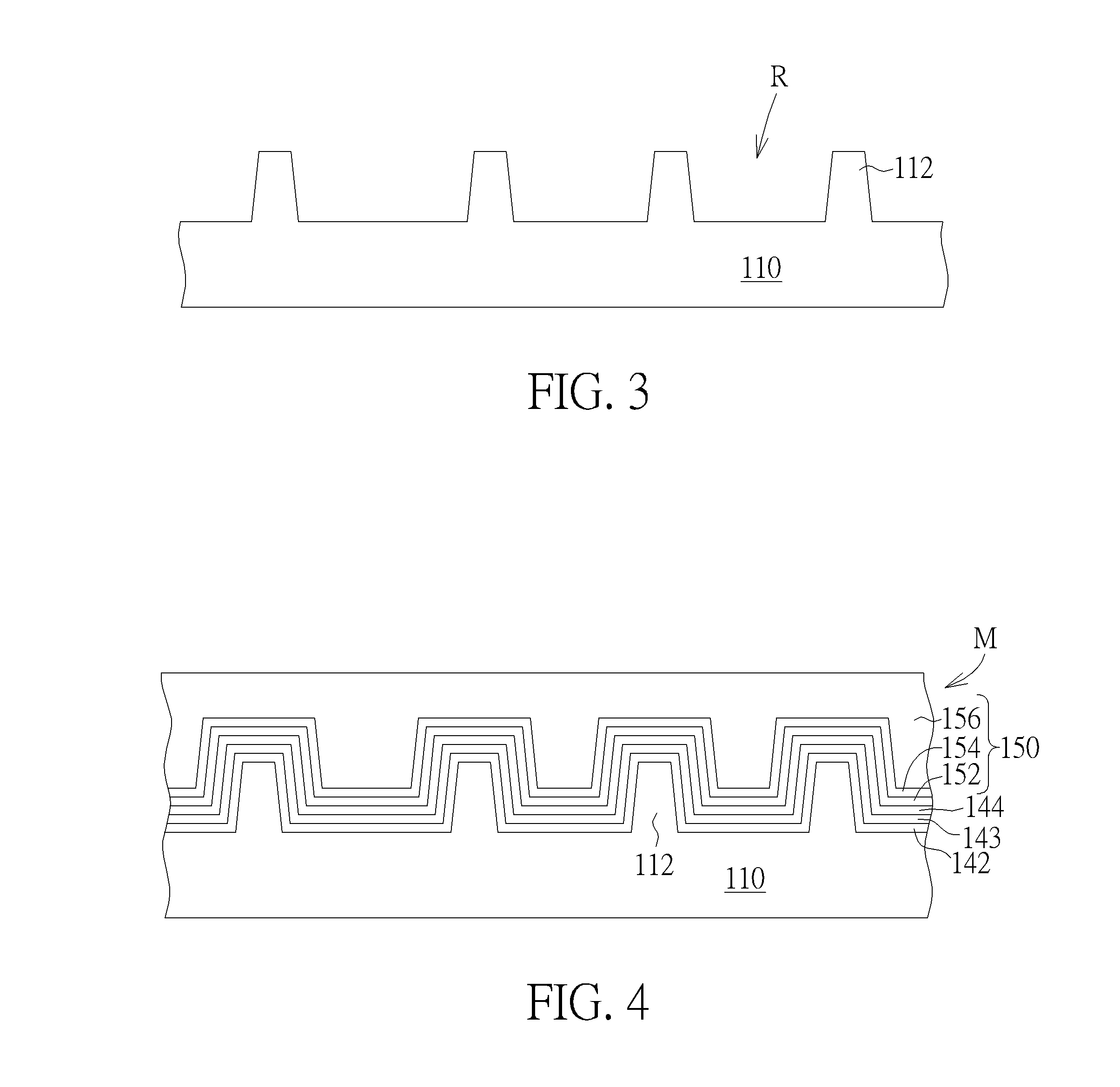

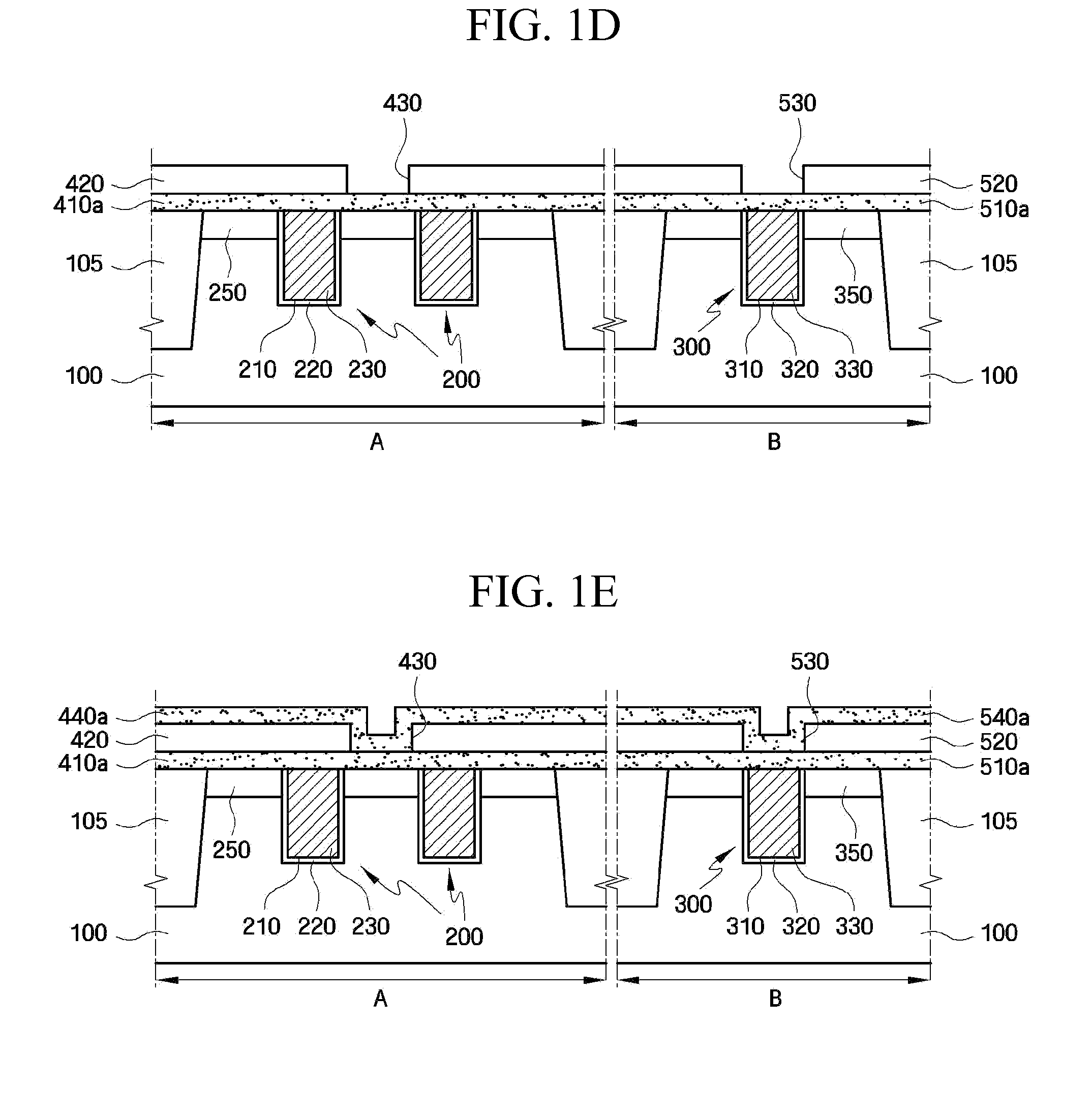

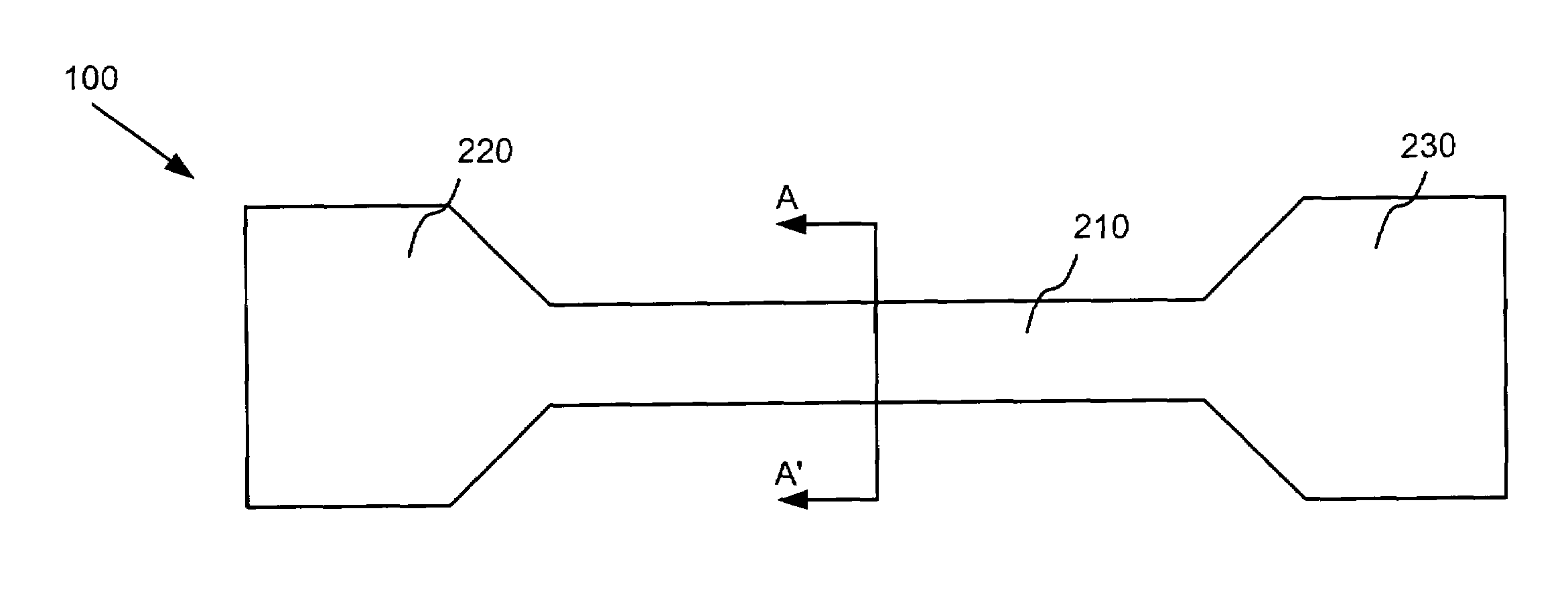

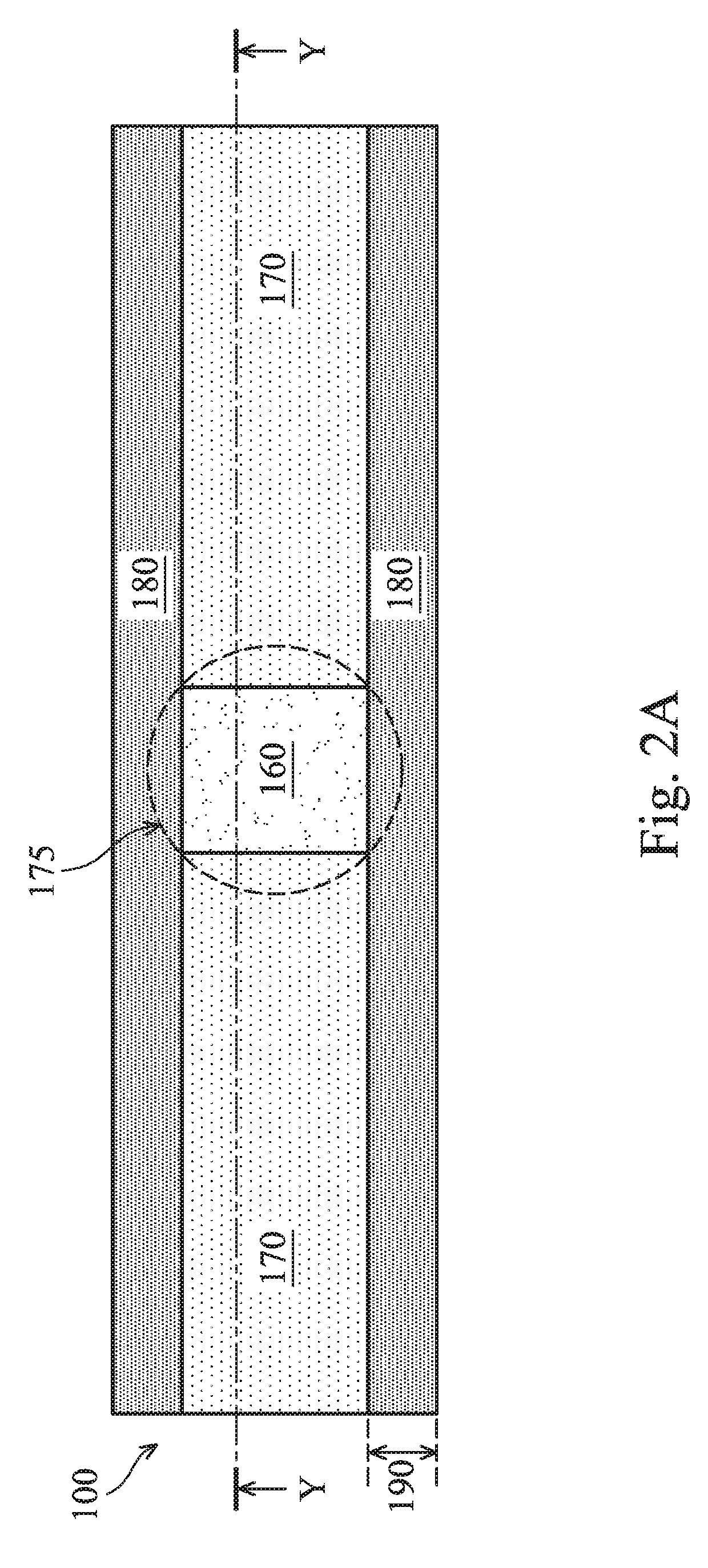

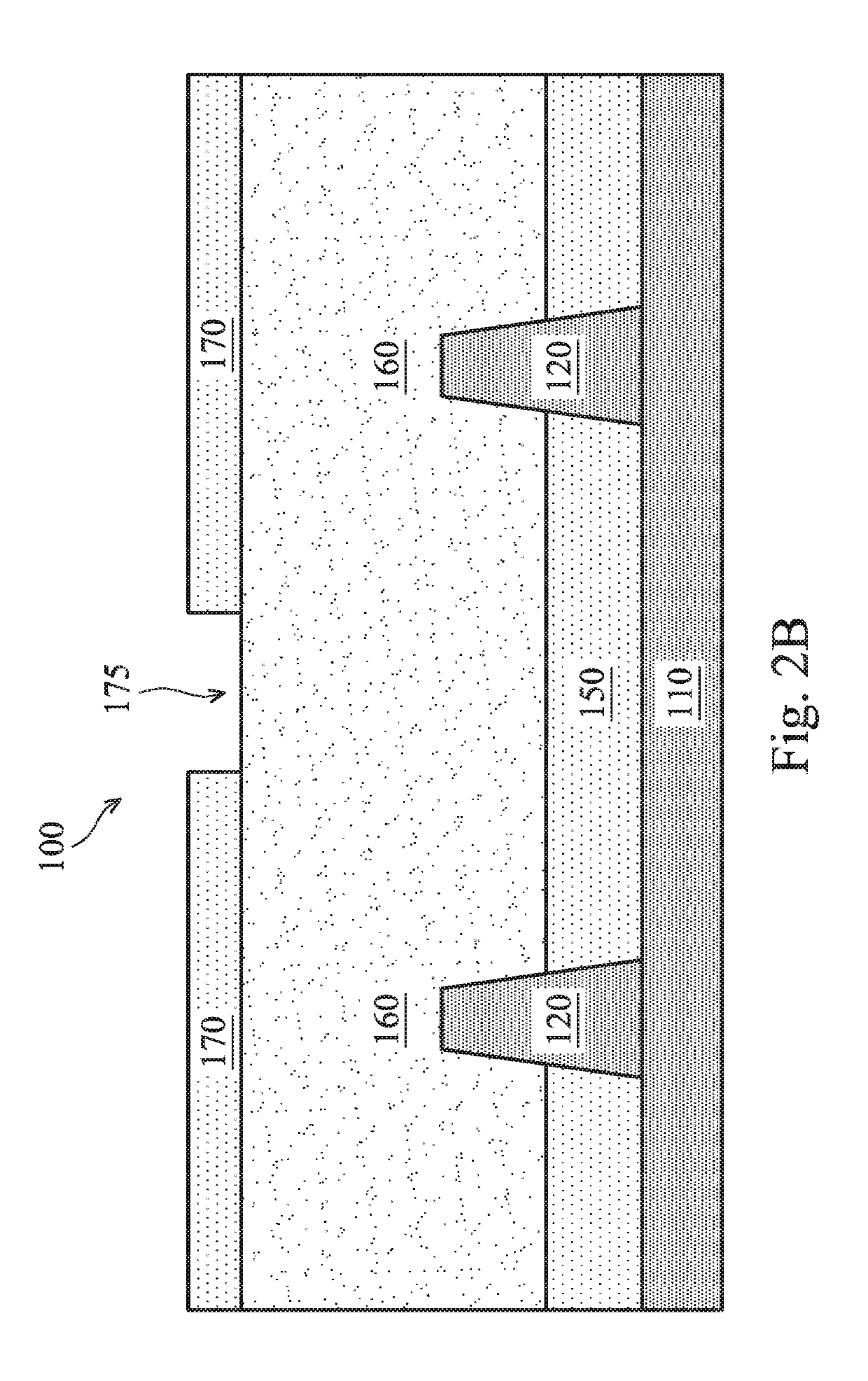

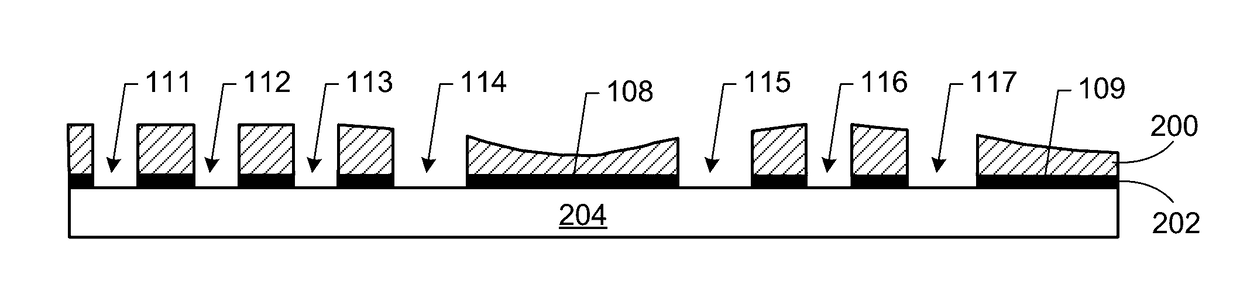

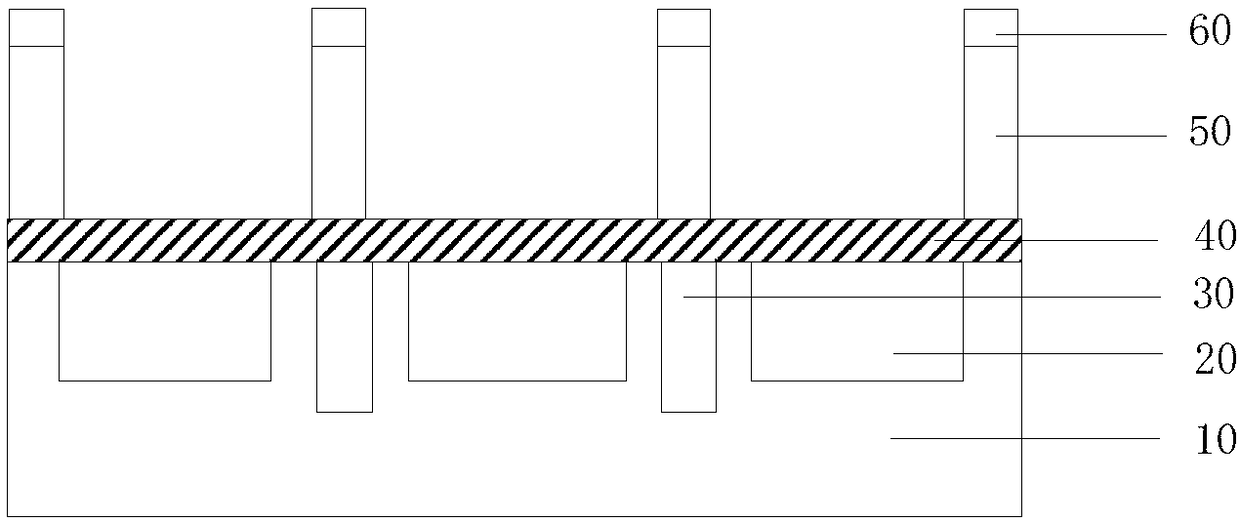

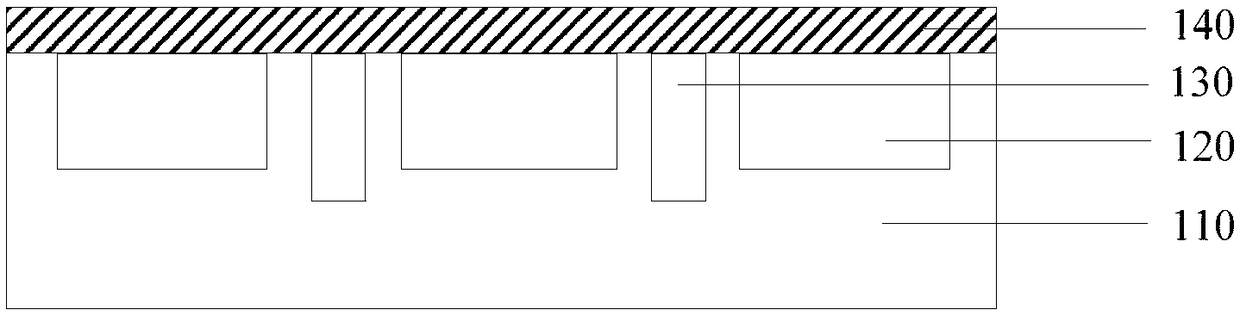

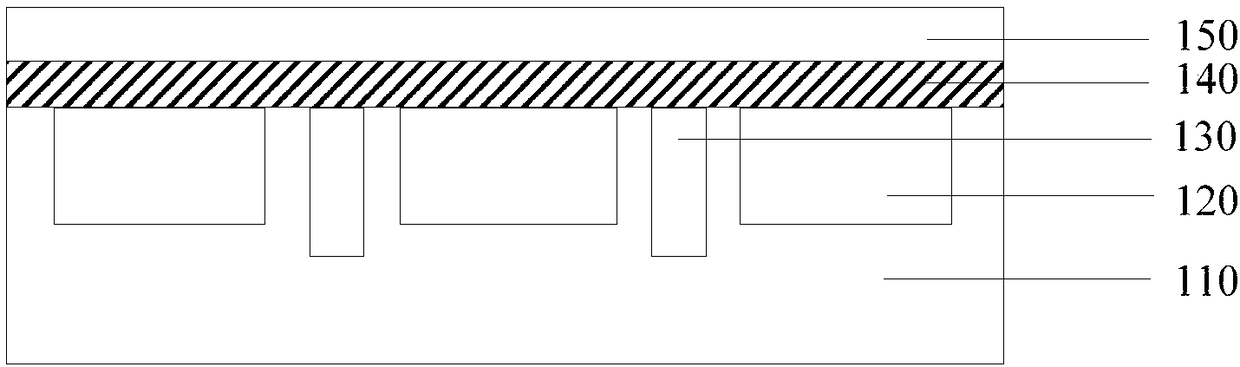

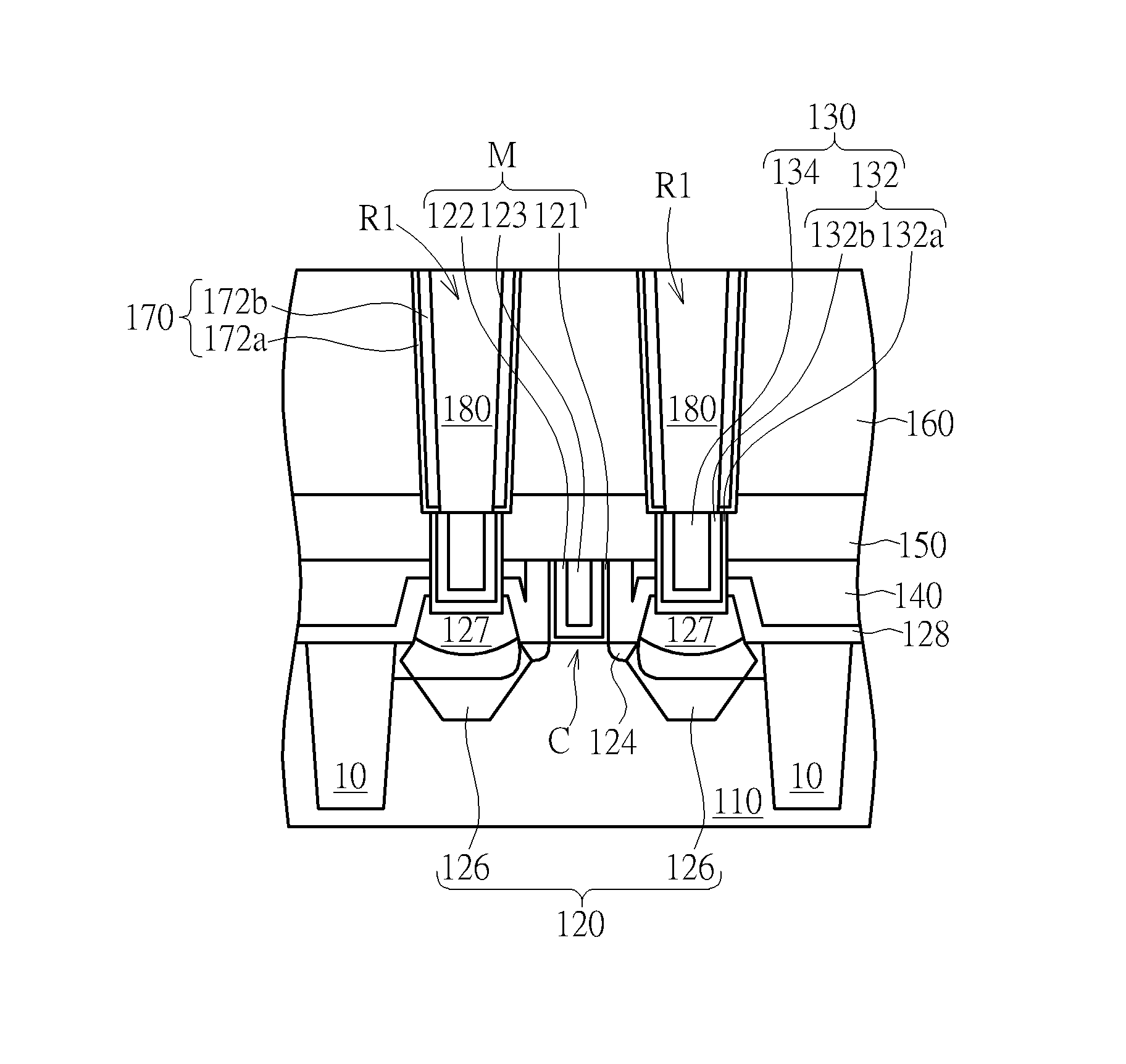

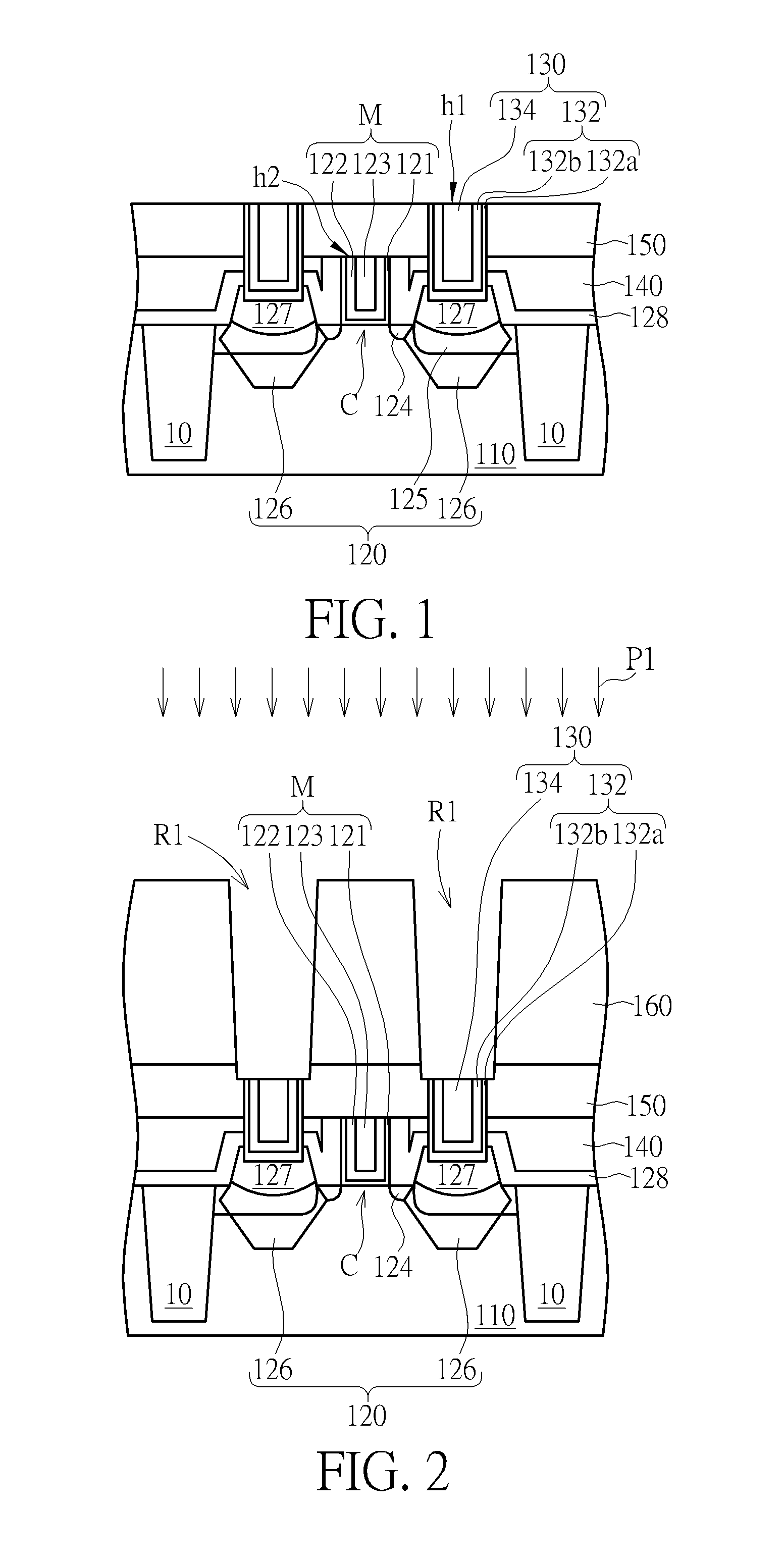

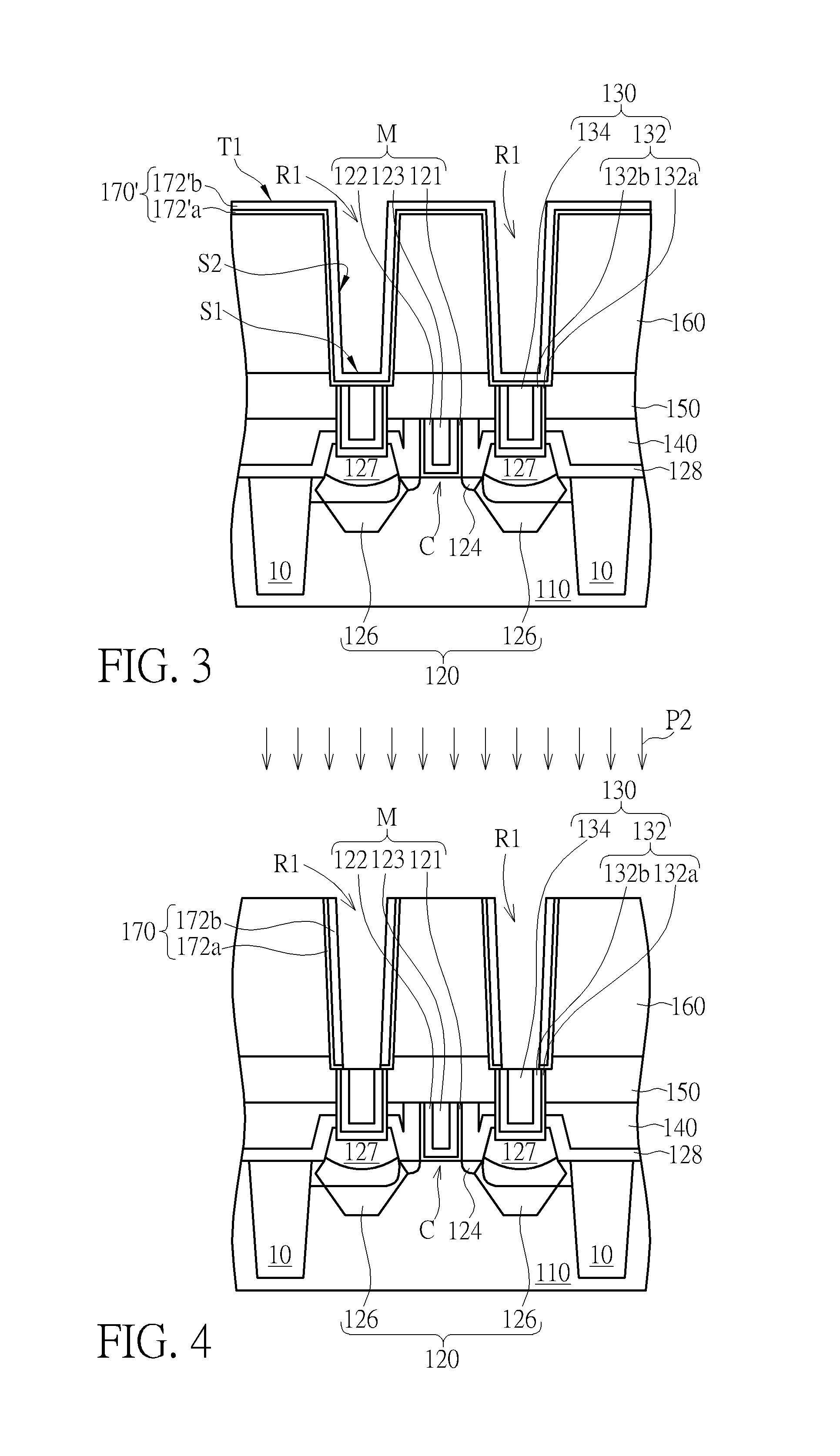

[structure applied to a photolithographic process and method for fabricating a semiconductor device]

ActiveUS20050148166A1Reduce the amount of lightReduce the amount requiredSemiconductor/solid-state device manufacturingAnti-reflective coatingDevice material

A structure applied to a photolithographic process is provided. The structure comprises at least a film layer, an optical isolation layer, an anti-reflection coating and a photoresist layer sequentially formed over a substrate. In the photolithographic process, the optical isolation layer stops light from penetrating down to the film layer. Since the optical isolation layer is set up underneath the photoresist layer, light emitted from a light source during photo-exposure is prevented from reflecting from the substrate surface after passing through the film layer. Thus, the critical dimensions of the photolithographic process are unaffected by any change in the thickness of the film layer.

Owner:MACRONIX INT CO LTD

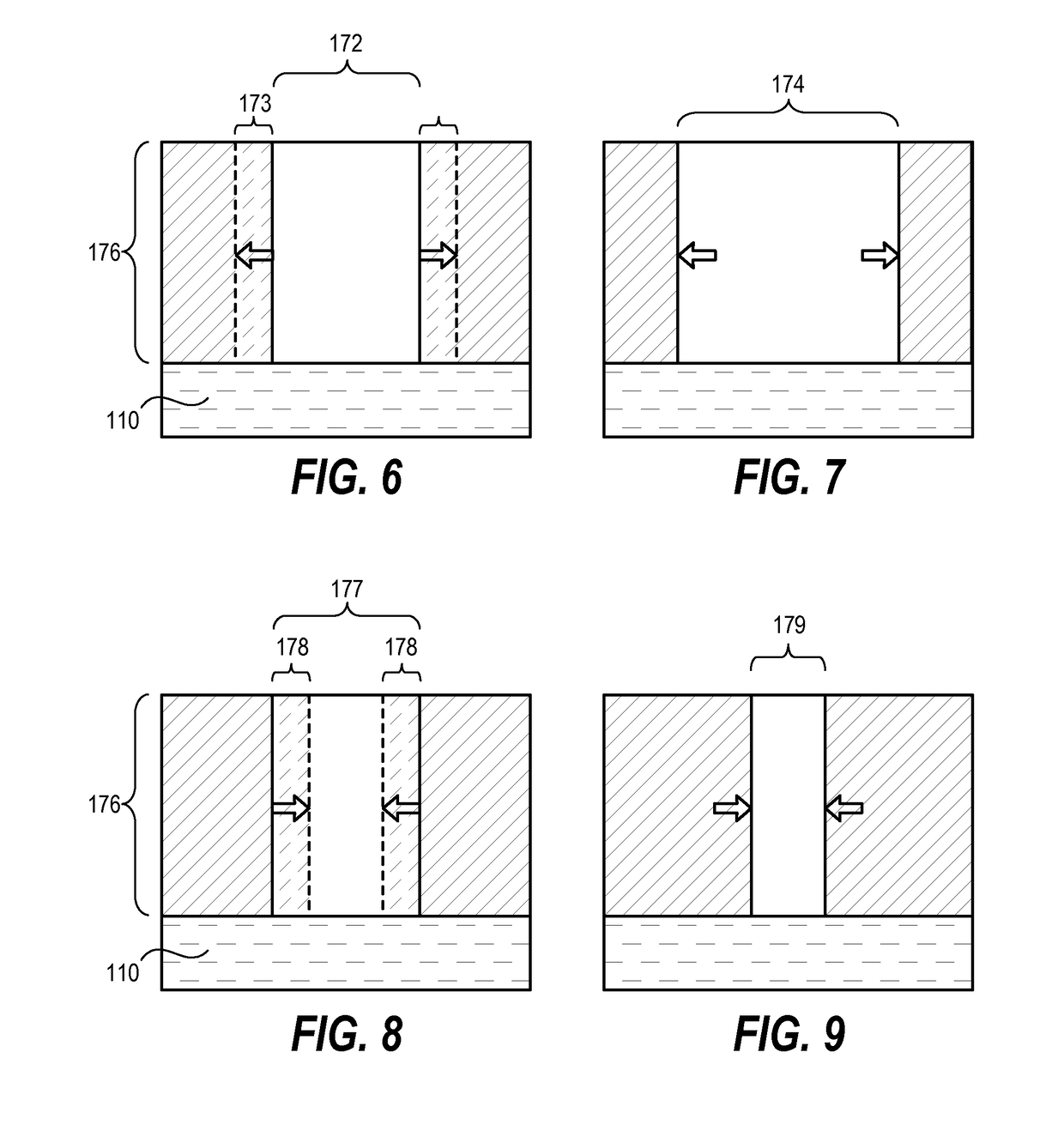

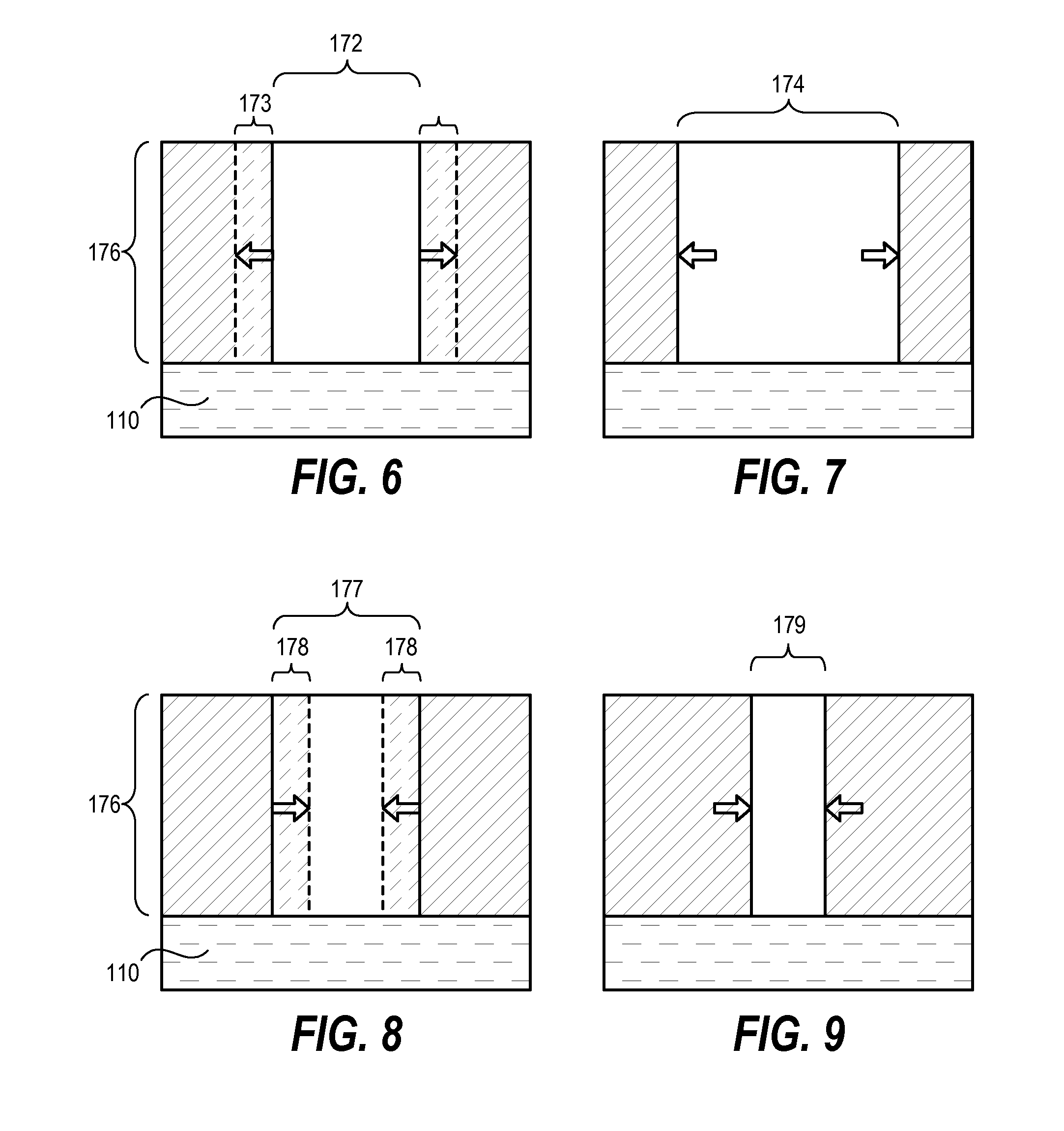

Correction method for self-aligned dual patterning process and semiconductor device thereof

ActiveCN109103074AImprove critical dimensionsGood lookingSemiconductor/solid-state device manufacturingPhotoresistCorrection method

The invention provides a correction method for a self-aligned dual patterning process and semiconductor device thereof. The method comprises: forming an etching film layer, a core layer and a photoresist layer on a substrate. The photoresist layer is photolithographically etched after the core layer mask is added with a mask structure to form a patterned photoresist structure; the core layer is etched on the basis of the patterned photoresist structure to form the core pattern structure. Spacers are deposited on the core pattern structure and etched to form spacer layers on both sides of the core pattern structure; the core graphics structure are removed and the spacer layer is kept; a photoresist is applied on the spacer layer; on the peripheral mask, after the position of the peripheraletching film structure to be etched and the edge spacer layer with irregular shape are formed and covered, the photoresist is photolithographically etched to form the peripheral photoresist structure;a modified etched film structure is formed by etching the etched film layer with a spacer layer and a peripheral photoresist structure as a mask. The invention can improve the uniformity and the morphology of the key dimensions of the etched film.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

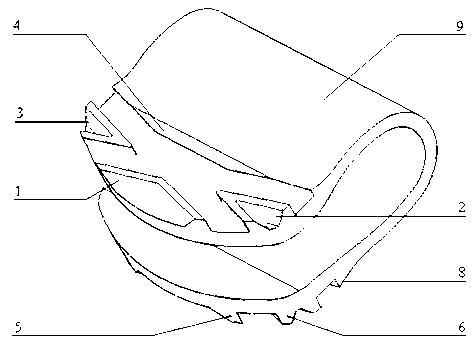

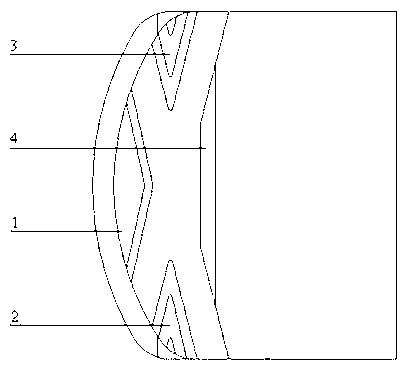

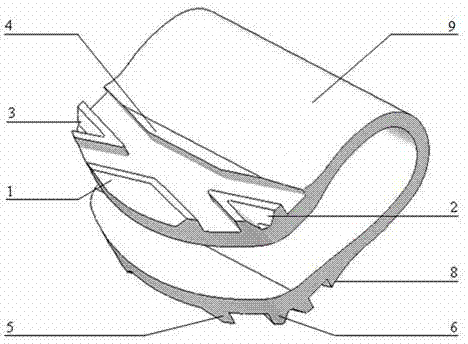

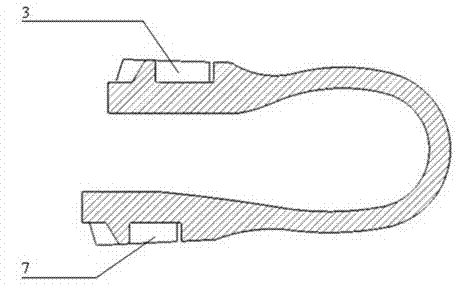

Omega-shaped artificial cervical disc implantation prosthesis with inverted-V-shaped two-way stopping inverted teeth

InactiveCN103315830AImprove surface stress stateRecovery and maintenanceSpinal implantsIntervertebral discEngineering

The invention relates to an omega-shaped artificial cervical disc implantation prosthesis with inverted-V-shaped two-way stopping inverted teeth. The omega-shaped artificial cervical disc implantation prosthesis with the inverted-V-shaped two-way stopping inverted teeth comprises a body and is characterized in that the body is an omega-shaped non-contacting elastic structure with integral upper and lower end plates, the outer surfaces of the upper end plate and the lower end plate are provided with the inverted-V-shaped two-way stopping inverted teeth in a symmetrical mode, the length of the lower end plate of the body is 10-16mm, the length of the upper end plate is 1 mm shorter than that of the lower end plate, the distance between the upper end plate and the lower end plate is 2-3.5 mm, and the thickness of the bending section of the back end of the body is 0.6-1.2 mm. The omega-shaped artificial cervical disc implantation prosthesis with the inverted-V-shaped two-way stopping inverted teeth is stable in space after being implanted, is supported by elastic force and does not need to be fixed with screws, avoids direct friction and abrasion between the upper end plate and the lower end plate fundamentally, and can meet the performance requirements of long service life and anti-fatigue effect of an implantation prosthesis. By means of the omega-shaped artificial cervical disc implantation prosthesis with the inverted-V-shaped two-way stopping inverted teeth, the range of motion of the anteflexion and the range of motion of the lateroflexion of a cervical vertebra segment reaches 30%-60% of the range of motion of the anteflexion and the range of motion of a normal cervical vertebra after a patient is subjected to operation, and the range of motion of the posterior extension reaches 70%-80% of the range of motion of the posterior extension of the normal cervical vertebra.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

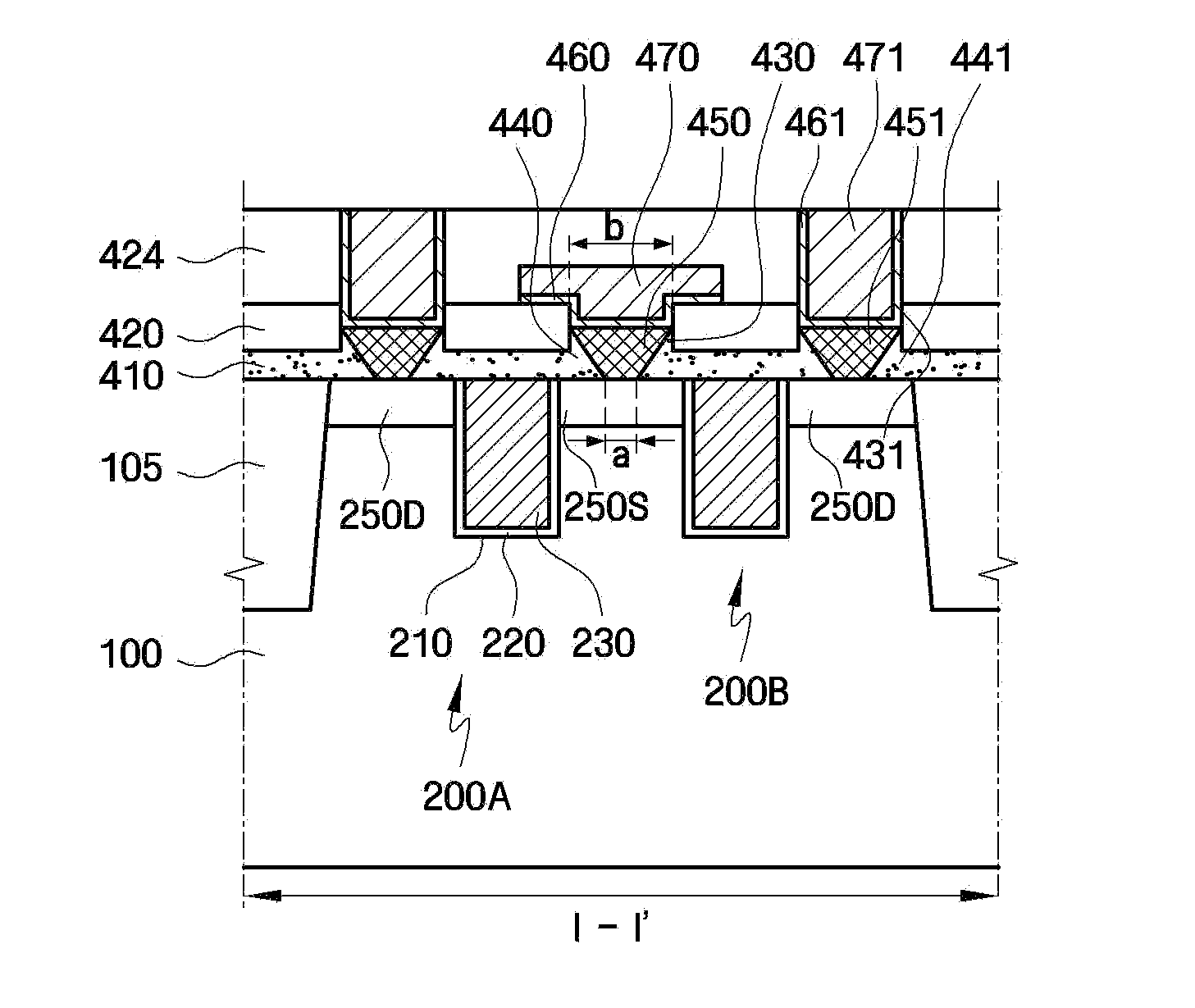

Semiconductor integrated circuit devices having contacts formed of single-crystal materials

ActiveUS8053831B2Easy to separateImprove critical dimensionsTransistorSolid-state devicesInsulation layerSingle crystal

A memory cell of memory device, comprises an active region of a memory cell defined in a semiconductor substrate, and a conductive gate electrode in a trench of the active region. The gate electrode is isolated from the semiconductor substrate. An insulation layer is on the active region and on the conductive gate electrode. A conductive contact is in the insulation layer on the active region at a side of the gate electrode and isolated from the gate electrode. The contact has a first width at a top portion thereof and a second width at a bottom portion thereof, the first width being greater than the second width. The contact is formed of a single-crystal material.

Owner:IMBERATEK LLC

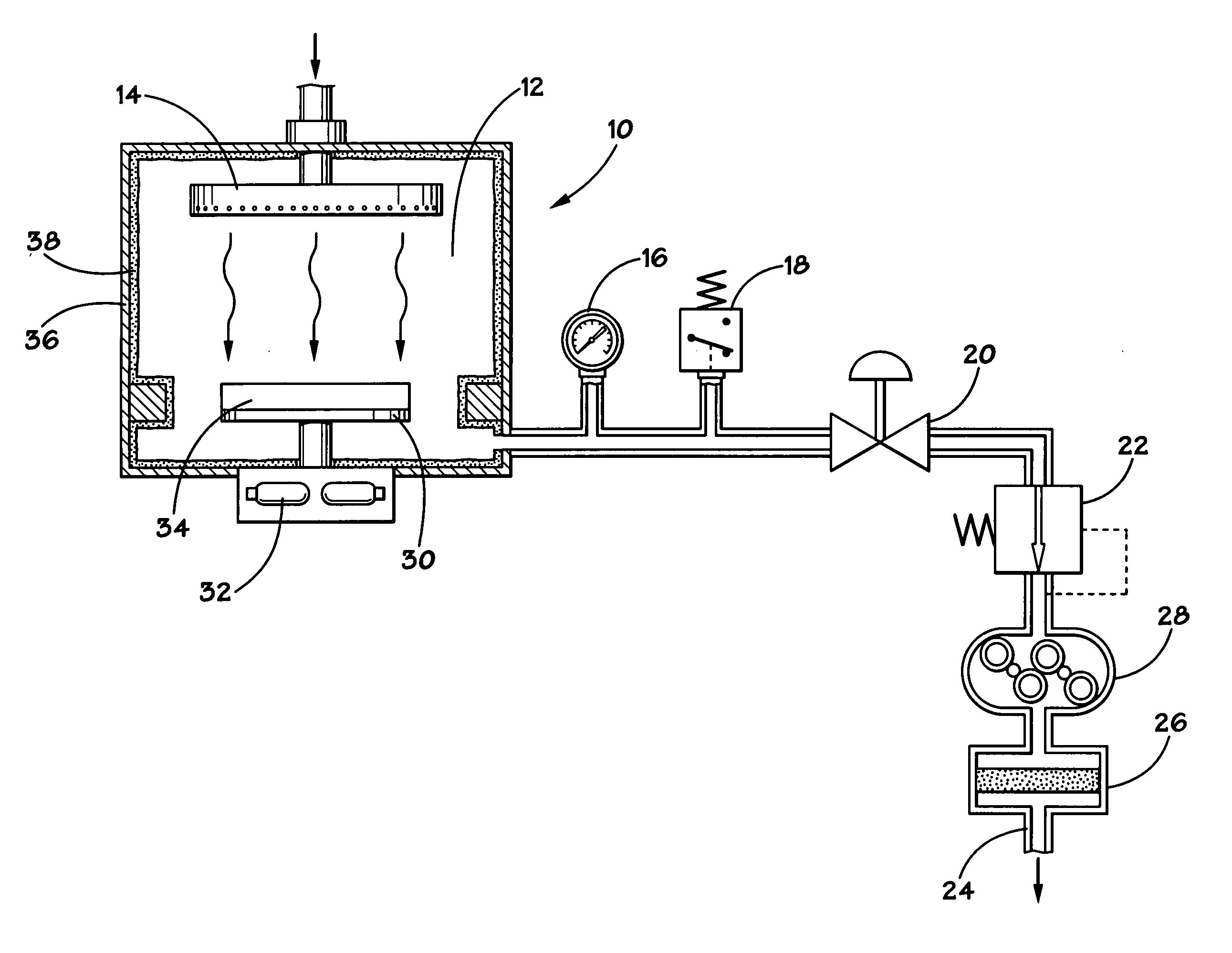

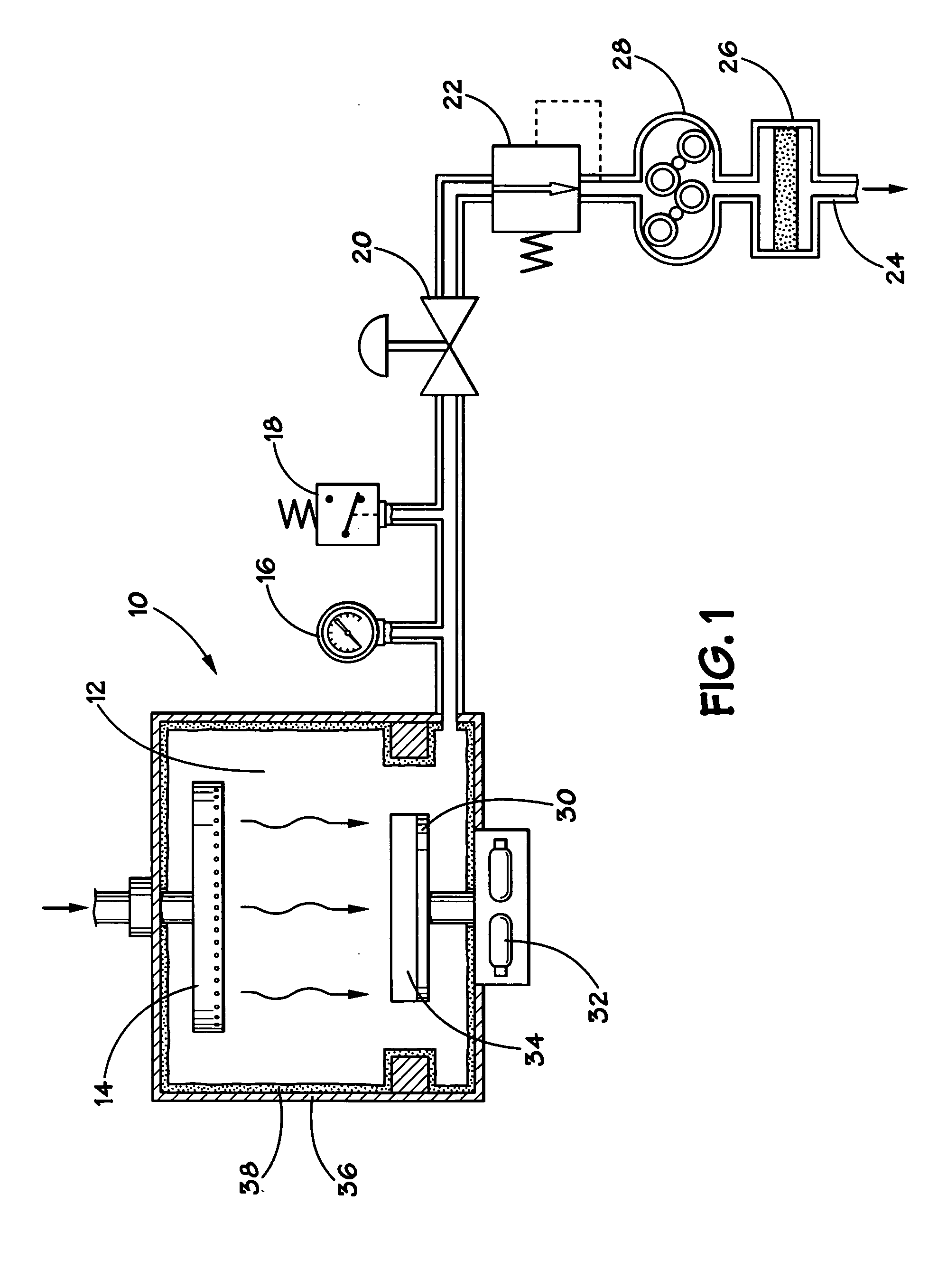

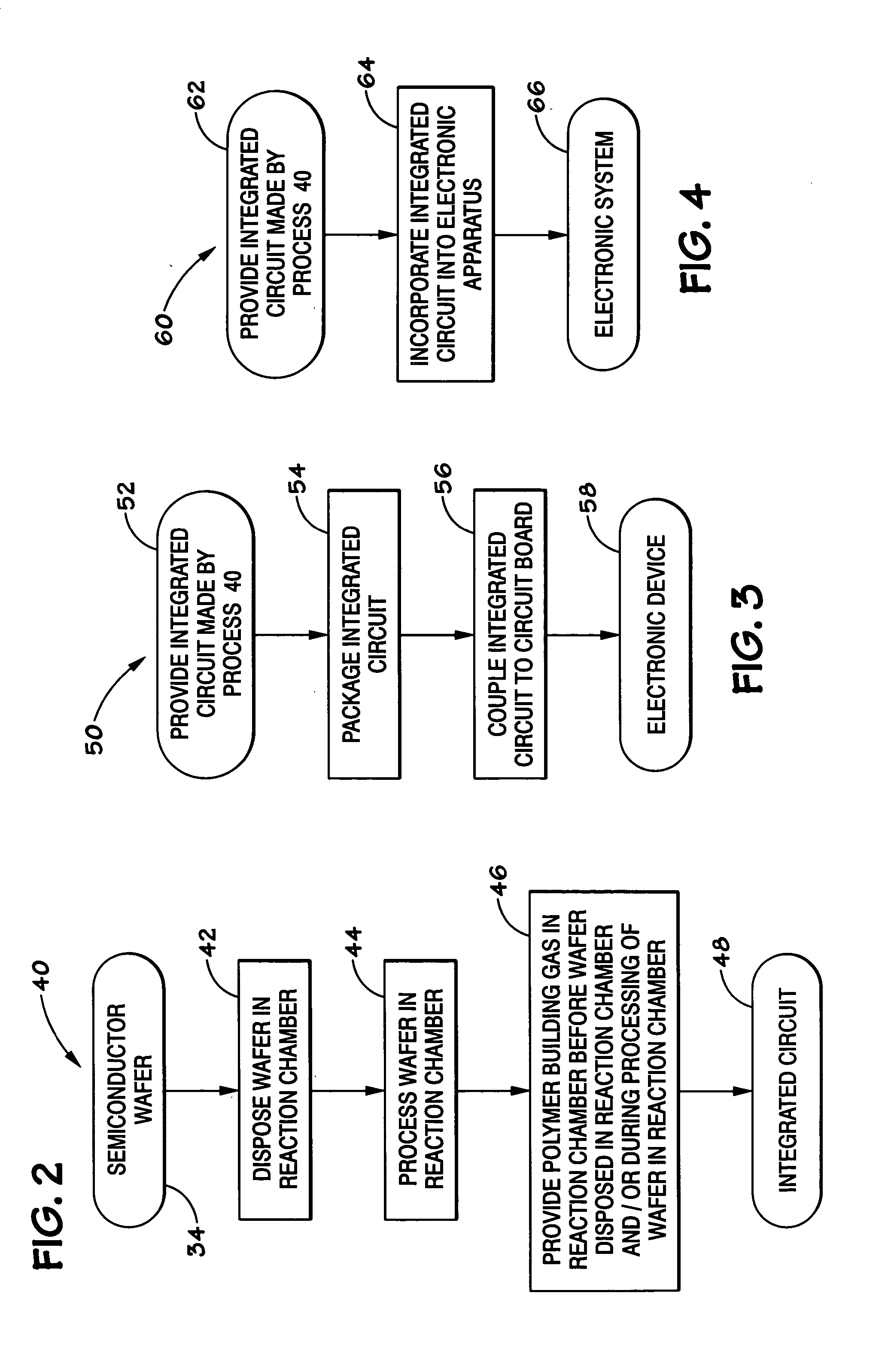

Conditioning of a reaction chamber

InactiveUS20050106891A1Increase of standard deviationAchieve consistencyDecorative surface effectsSemiconductor/solid-state device manufacturingElectronic systemsForming gas

A method is provided for forming polymer on an interior surface of a reaction chamber. A polymer-forming gas is introduced into the chamber and the environment is regulated to form the polymer on the interior surface of the chamber. Methods for the manufacture of integrated circuits, electronic devices, and electronic systems, are also provided.

Owner:MICRON TECH INC

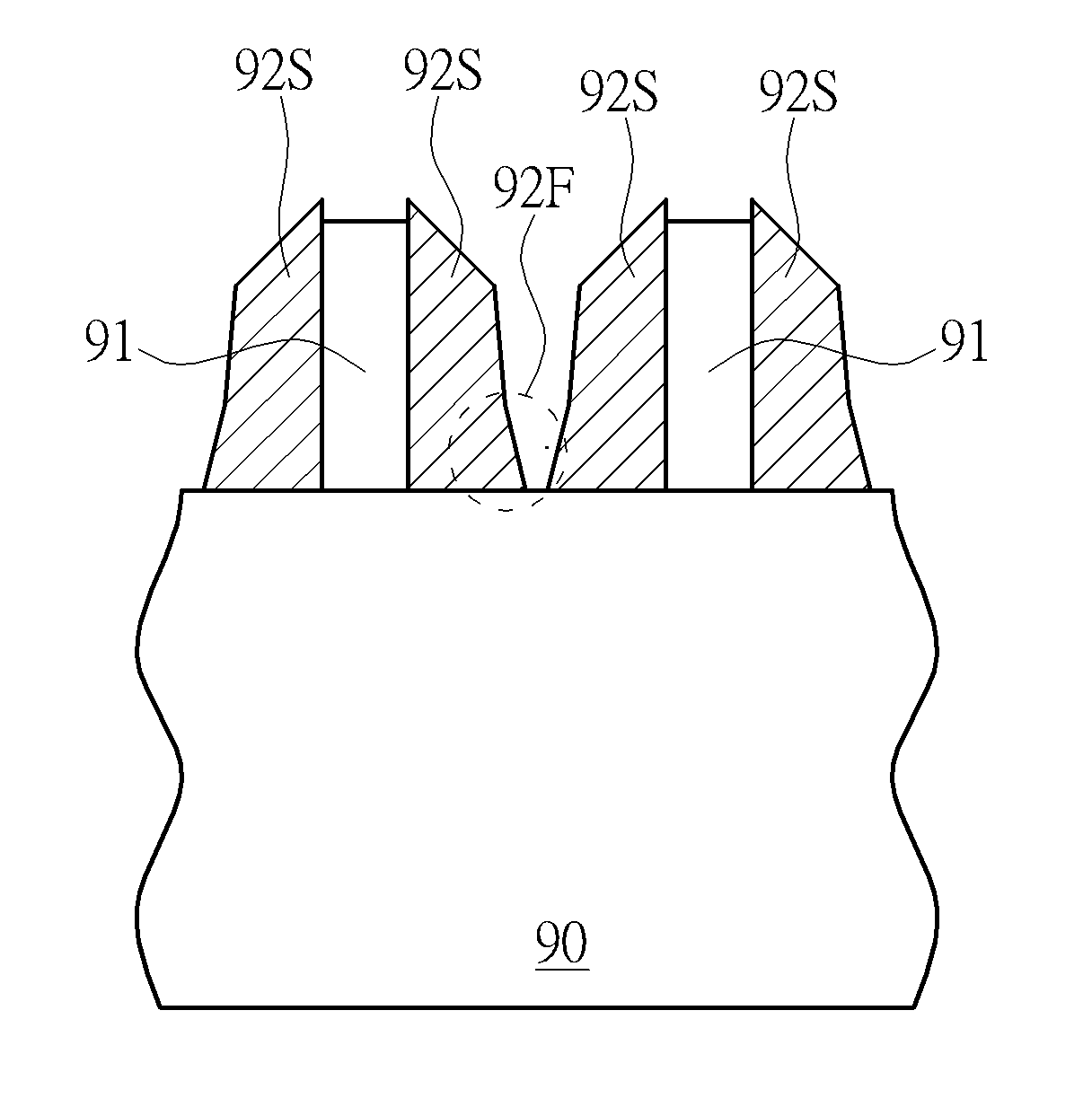

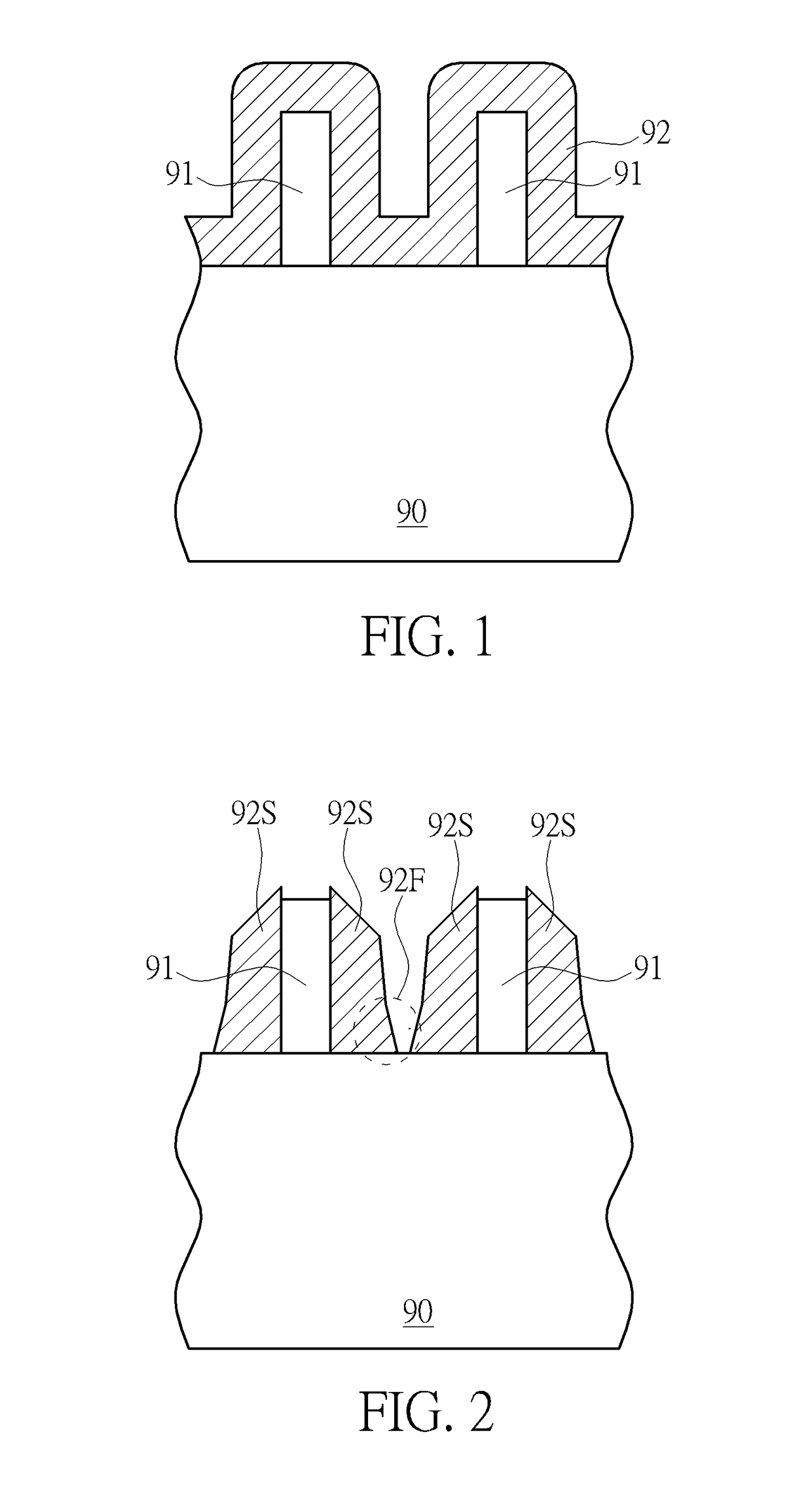

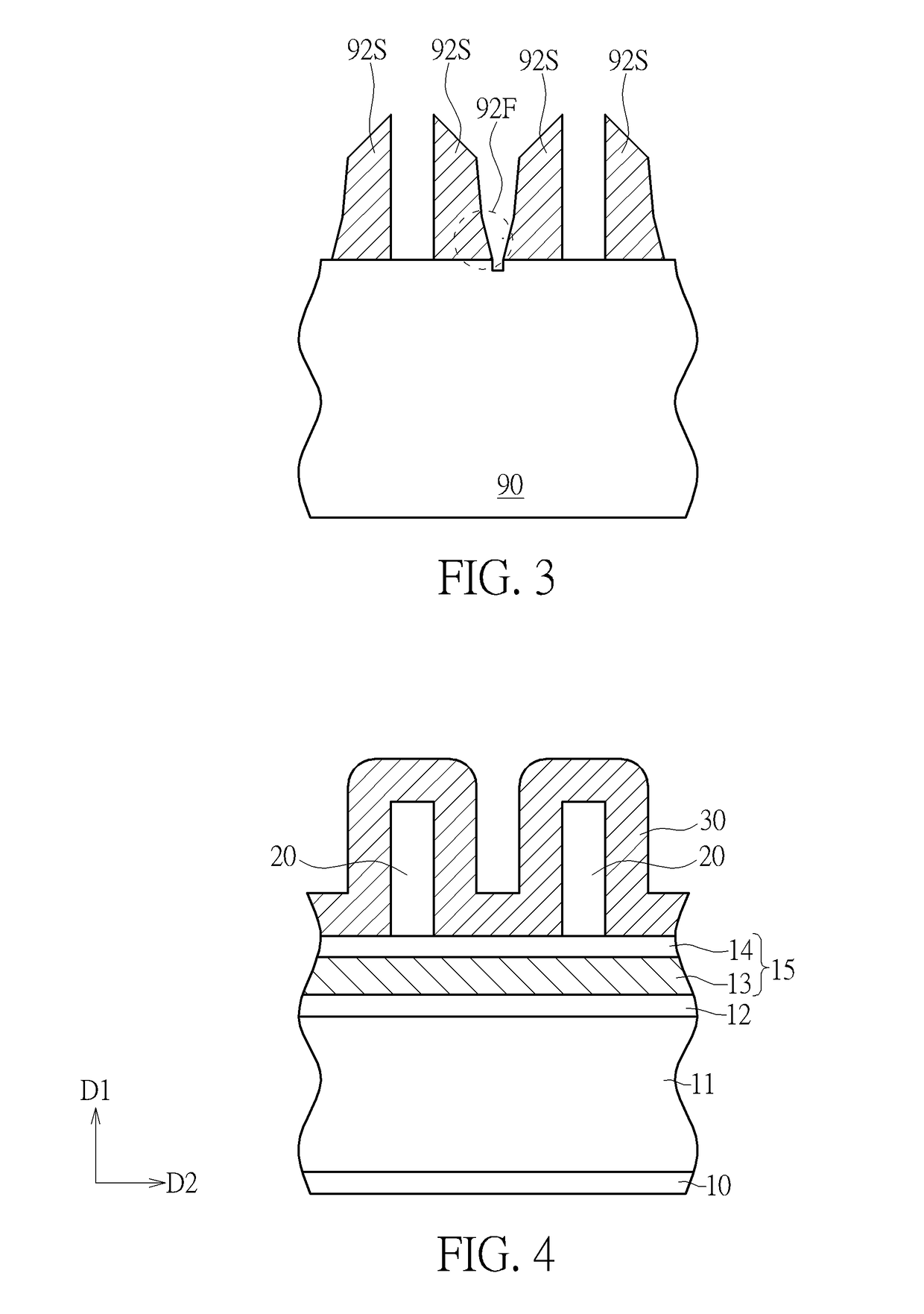

Method of forming patterned mask layer

ActiveUS9779942B1Improve critical dimensionsImprove critical dimension uniformitySemiconductor/solid-state device manufacturingEngineeringMask layer

A method of forming a patterned mask layer includes the following steps. A plurality of support features is formed on a mask layer. A plurality of spacers is formed on side walls of the support features. A patterned protection layer is formed on the support features and top surfaces of the spacers. At least a part of side surfaces of the spacers are not covered by the patterned protection layer, and the patterned protection layer is formed in a process environment containing methane (CH4). A trimming process is then performed to remove a part of each of the spacers. Tapered parts of the spacers may be removed by the trimming process before the step of etching the mask layer with the spacers as a mask, and the critical dimension uniformity of the patterned mask layer may be improved accordingly.

Owner:UNITED MICROELECTRONICS CORP

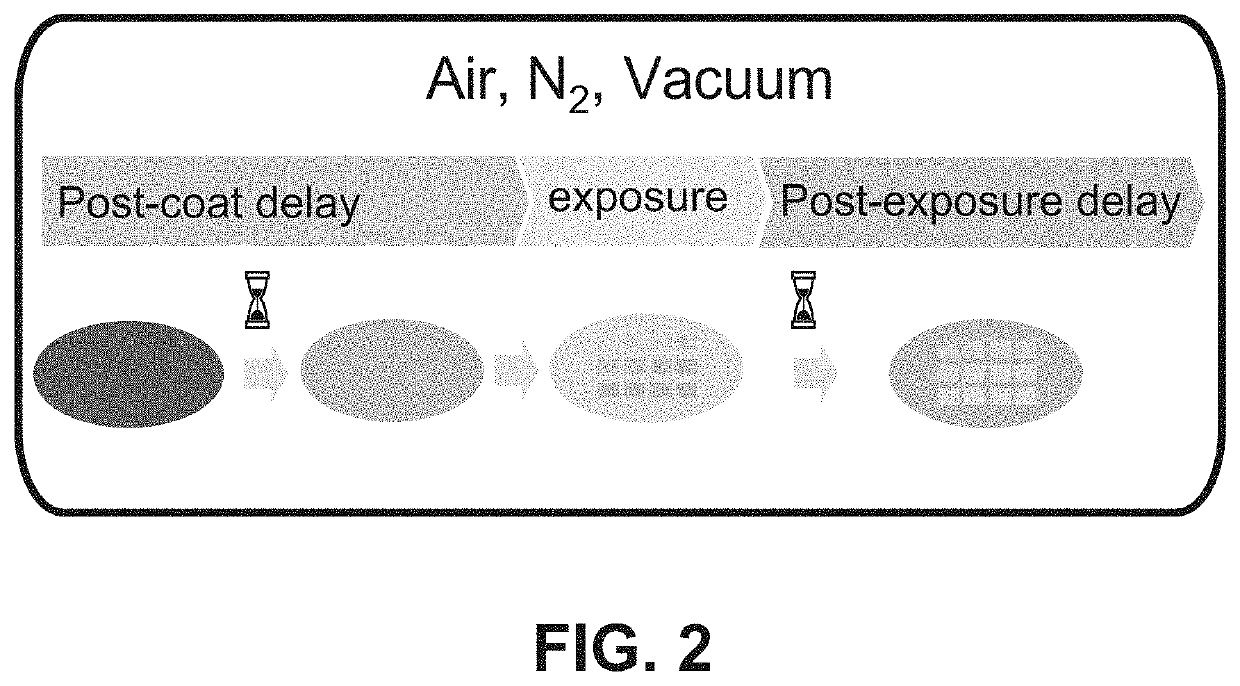

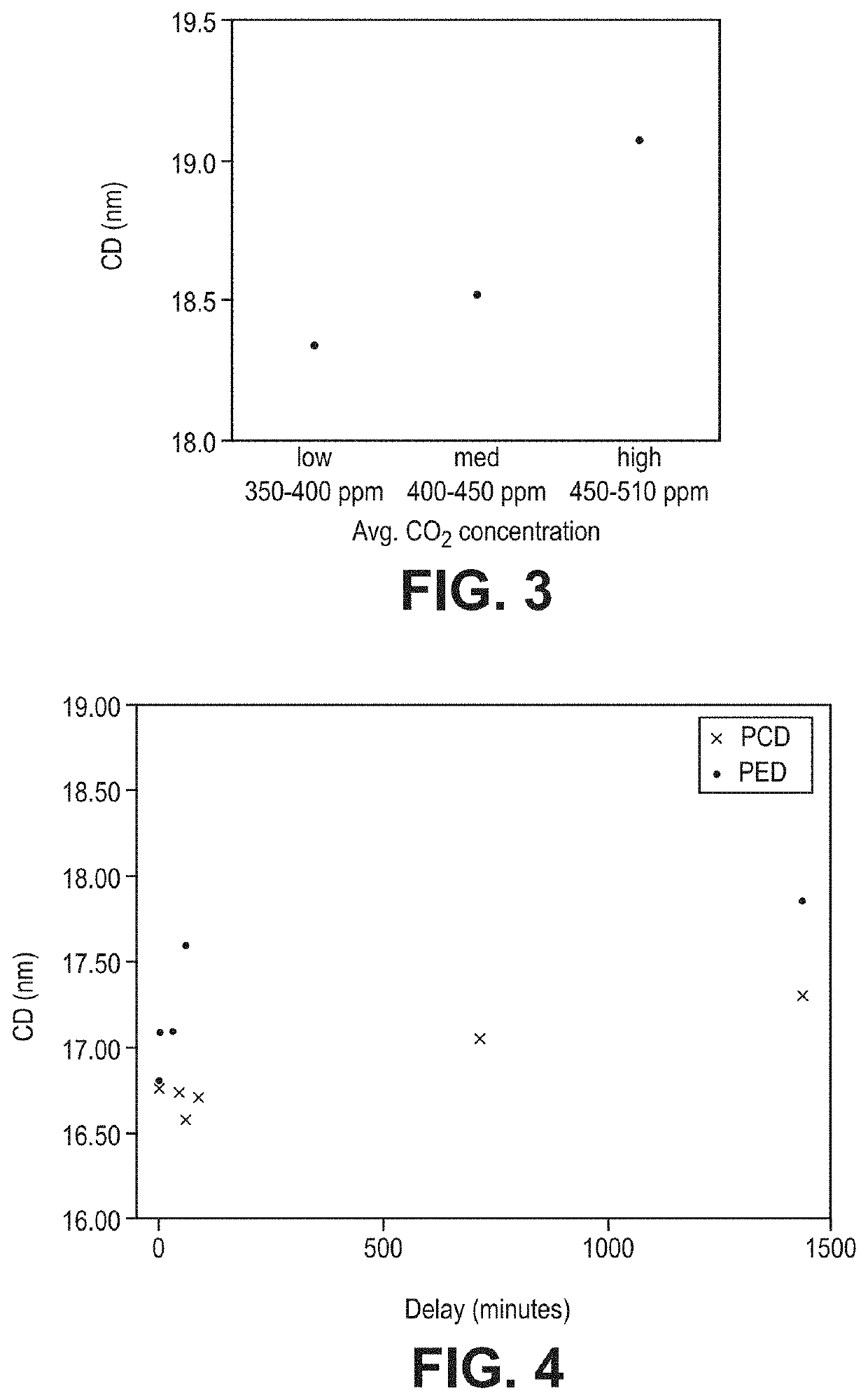

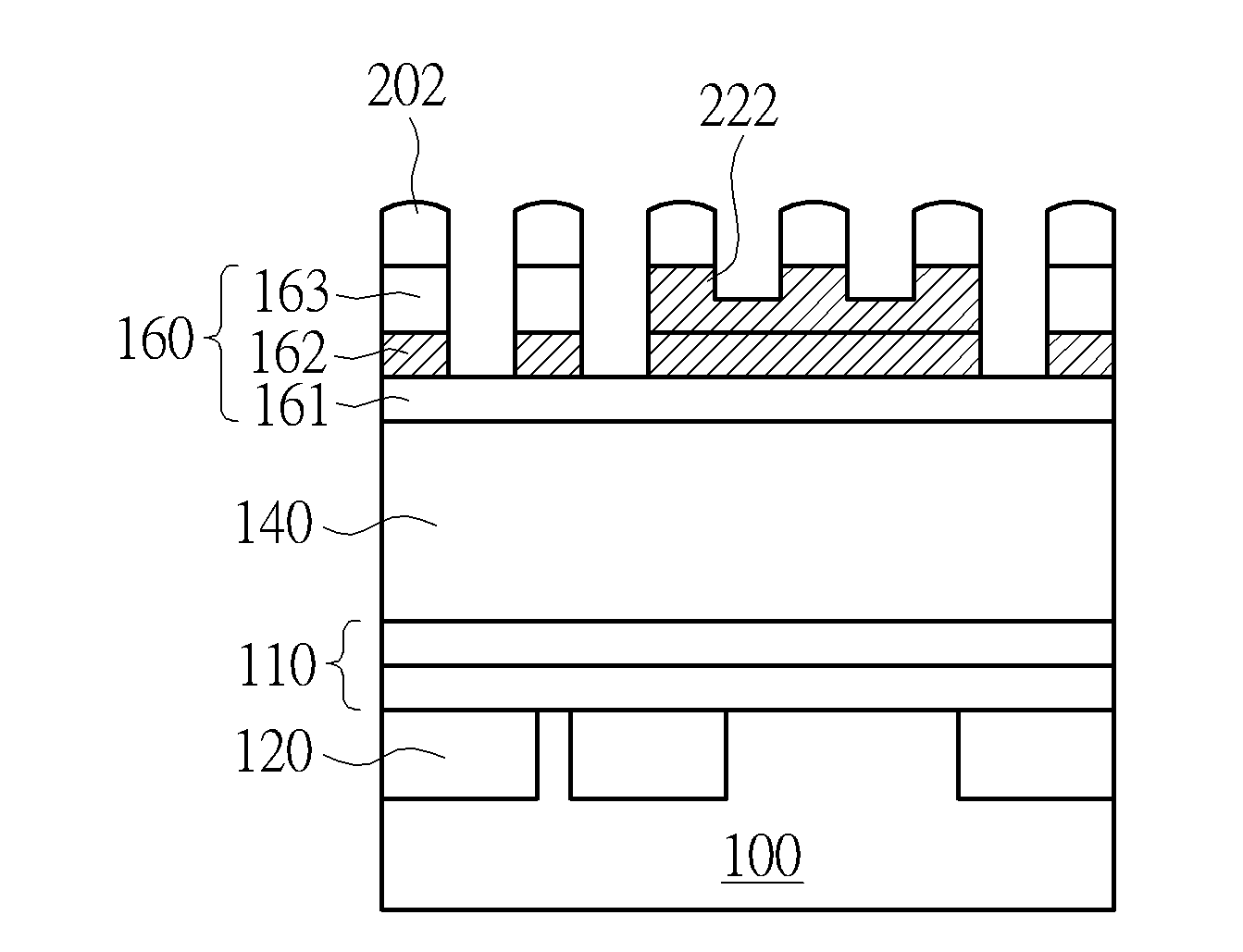

Process environment for inorganic resist patterning

PendingUS20210271170A1Increase variabilitySpeed up the processPhotosensitive material processingPhotosensitive materials for photomechanical apparatusWaferingReactive gas

The processing of radiation patternable organometallic coatings is shown to be improved through the appropriate selection of post processing conditions between coating and development of the pattern. In particular, a coated wafer can be subjected to process delays to allow aging of the coating at various process points, in particular following irradiation. Process delays can be combined and interspersed with heating steps. The atmosphere above the coated wafer at various process steps can be adjusted to obtain desired improvements in the development of the pattern. Reactive gases can be beneficial with respect to improvement of coating properties.

Owner:TOKYO ELECTRON LTD

Method of fabricating semiconductor device

ActiveUS20170025519A1Layout specificationImprove critical dimensionsSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor device and a method of fabricating the same, the semiconductor device includes a hard mask layer and a plurality of spacers. The hard mask layer is disposed on a target layer and has a first material and a second material. The spacers are disposed on the hard mask layer, wherein a first portion of the spacers is disposed on the first material, and a second portion of the spacers is disposed on the second material.

Owner:UNITED MICROELECTRONICS CORP

System and method for shifting critical dimensions of patterned films

ActiveUS9977339B2Improve critical dimensionsImprove uniformityPhotomechanical exposure apparatusMicrolithography exposure apparatusMarking outProjection system

Techniques herein include systems and methods that provide a spatially-controlled projection of electromagnetic radiation, such as light, onto a substrate as a mechanism of controlling or modulating critical dimensions of various features and structures being micro-fabricated on a substrate. Combining such spatial light projection with photolithographic exposure can achieve significant improvements in critical dimension uniformity across a surface of a substrate. In general, methods herein include patterning processes that identify or receive a critical dimension signature that spatially characterizes critical dimension values that correspond to the substrate. A pattern of electromagnetic radiation is projected onto a patterning film coated on substrate using a digital pixel-based projection system. A conventional photolithographic exposure process is executed subsequent to, or prior to, the pixel-based projection. The patterning film can then be developed to yield a relief pattern having critical dimensions shaped by both exposure processes.

Owner:TOKYO ELECTRON LTD

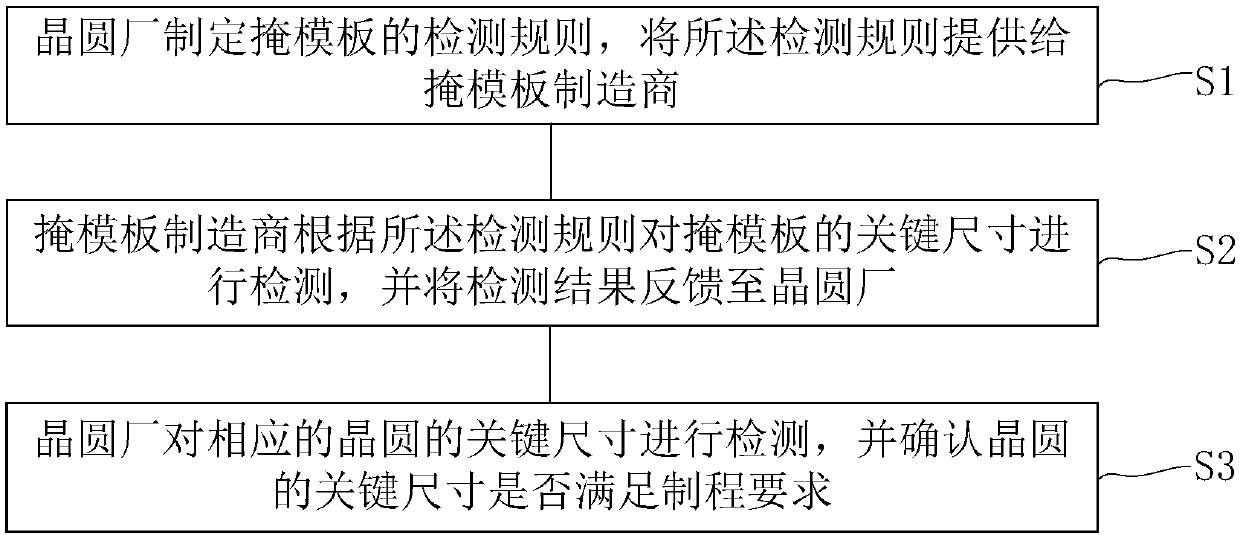

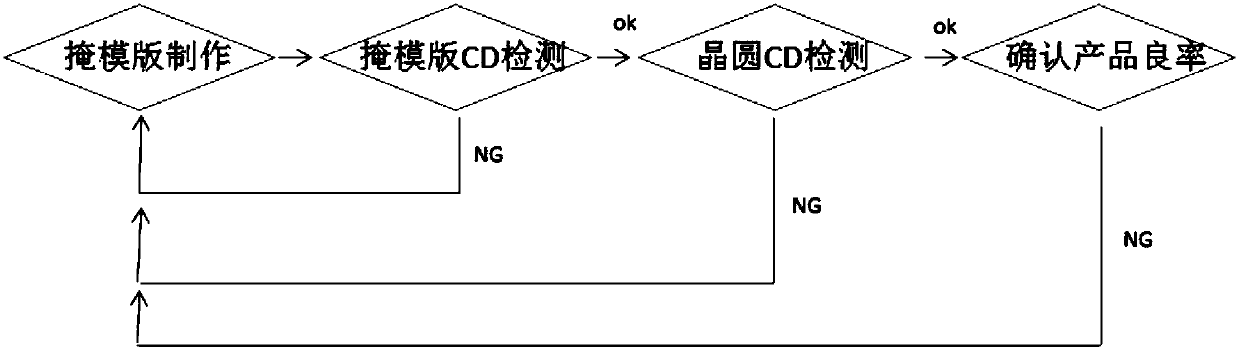

Method for monitoring critical sizes of mask plates

InactiveCN107643655AImprove critical dimensionsImprove uniformityPhotomechanical exposure apparatusMicrolithography exposure apparatusEngineeringWafer Product

The invention provides a method for monitoring critical sizes of mask plates. The method includes formulating detection rules for the mask plates by the aid of wafer factories and providing the detection rules to mask plate manufacturers; detecting the critical sizes of the mask plates by the aid of the mask plate manufacturers according to the detection rules and feeding detection results to thewafer factories; detecting critical sizes of corresponding wafers by the aid of the wafer factories and confirming whether the critical sizes of the wafers meet requirements of manufacture proceduresor not. The method has the advantages that the uniformity of the global and local critical sizes of the mask plates can be effectively monitored and improved by the aid of the method, so that the uniformity of critical sizes of wafer products can be ultimately improved, and the yield of the products can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for fabricating bulb-shaped recess pattern

InactiveUS7749912B2Improve critical dimensionsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHard mask

A method for fabricating a bulb-shaped recess pattern includes: forming an etch barrier layer over a substrate; forming a hard mask pattern in which a first polymer is attached to sidewalls of the hard mask pattern over the etch barrier layer; sequentially etching the etch barrier layer and the substrate to form a recess pattern in which a second polymer is attached to sidewalls of the recess pattern; removing the first and second polymers and the hard mask pattern; forming a plurality of spacers exposing a bottom portion of the recess pattern; and etching the exposed bottom portion of the recess pattern to form a ball pattern.

Owner:SK HYNIX INC

Fabrication of metal film stacks having improved bottom critical dimension

ActiveUS20100276807A1Improve critical dimensionsSemiconductor/solid-state device detailsSolid-state devicesAdverse effectMetal

A method of fabricating metal film stacks is described that reduces or eliminates adverse effects of photolithographic misalignments. A bottom critical dimension is increased by removal of a bottom titanium nitride barrier.

Owner:MACRONIX INT CO LTD

Omega-shaped artificial cervical disc implantation prosthesis with inverted-V-shaped two-way stopping inverted teeth

InactiveCN103315830BImprove surface stress stateRecovery and maintenanceSpinal implantsIntervertebral discDentistry

The invention relates to an omega-shaped artificial cervical disc implantation prosthesis with inverted-V-shaped two-way stopping inverted teeth. The omega-shaped artificial cervical disc implantation prosthesis with the inverted-V-shaped two-way stopping inverted teeth comprises a body and is characterized in that the body is an omega-shaped non-contacting elastic structure with integral upper and lower end plates, the outer surfaces of the upper end plate and the lower end plate are provided with the inverted-V-shaped two-way stopping inverted teeth in a symmetrical mode, the length of the lower end plate of the body is 10-16mm, the length of the upper end plate is 1 mm shorter than that of the lower end plate, the distance between the upper end plate and the lower end plate is 2-3.5 mm, and the thickness of the bending section of the back end of the body is 0.6-1.2 mm. The omega-shaped artificial cervical disc implantation prosthesis with the inverted-V-shaped two-way stopping inverted teeth is stable in space after being implanted, is supported by elastic force and does not need to be fixed with screws, avoids direct friction and abrasion between the upper end plate and the lower end plate fundamentally, and can meet the performance requirements of long service life and anti-fatigue effect of an implantation prosthesis. By means of the omega-shaped artificial cervical disc implantation prosthesis with the inverted-V-shaped two-way stopping inverted teeth, the range of motion of the anteflexion and the range of motion of the lateroflexion of a cervical vertebra segment reaches 30%-60% of the range of motion of the anteflexion and the range of motion of a normal cervical vertebra after a patient is subjected to operation, and the range of motion of the posterior extension reaches 70%-80% of the range of motion of the posterior extension of the normal cervical vertebra.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

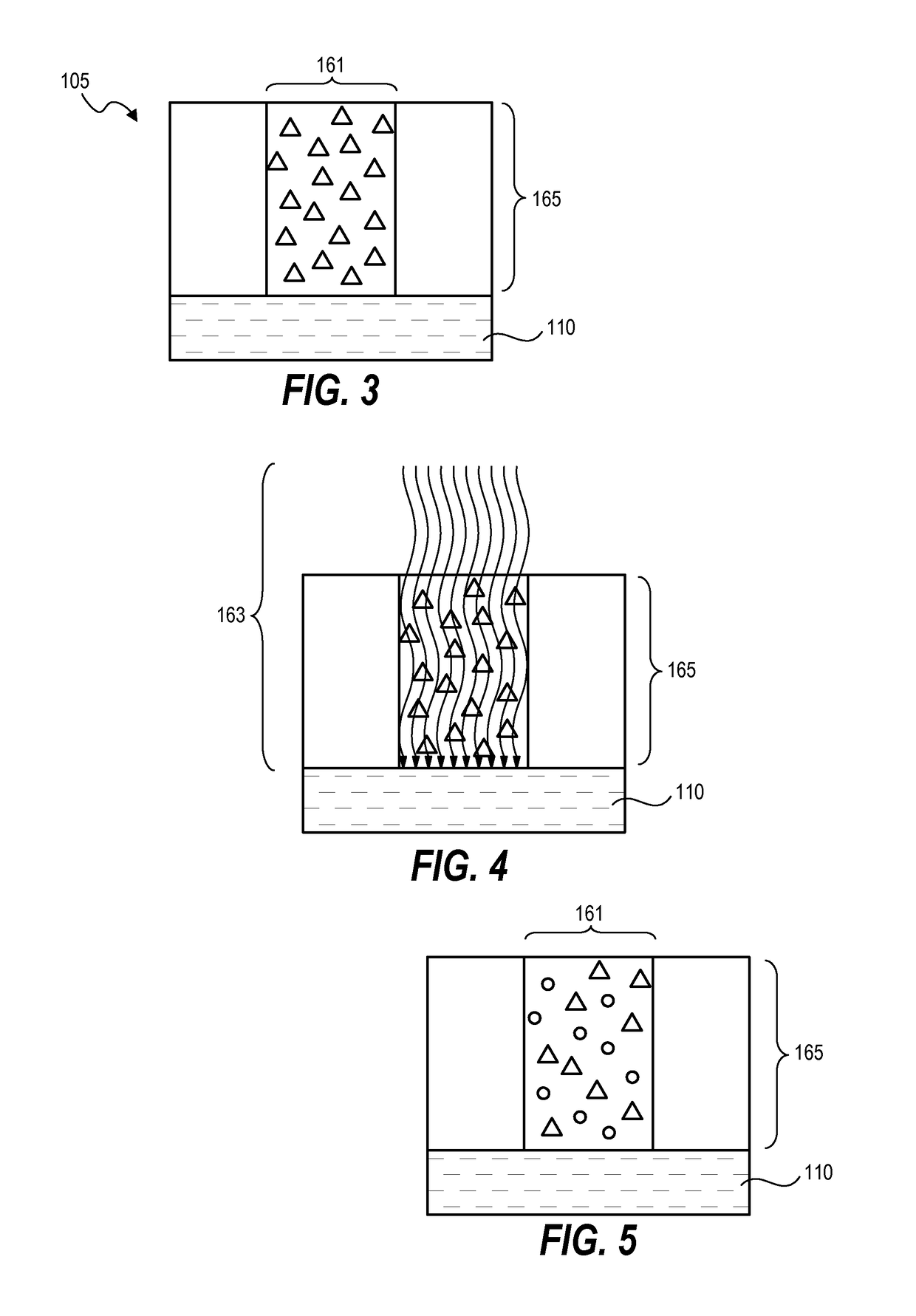

Method of forming non-continuous line pattern and non-continuous line pattern structure

ActiveUS9583343B2Improve critical dimensionsSemiconductor/solid-state device detailsSolid-state devicesEngineeringPolymer architecture

A method of forming a non-continuous line pattern includes forming a DSA material layer on a substrate, performing a phase separation of the DSA material layer to form an ordered periodic pattern including a plurality of first polymer structures and the second polymer structures arranged alternately, forming a first mask to cover a first portion of the ordered periodic pattern, performing a first etching process to remove a portion of the first polymer structures exposed by the first mask, removing the first mask, forming a second mask to cover a second portion of the ordered periodic pattern, with an interval to the first portion of the ordered periodic pattern, performing a second etching process to remove a portion of the second polymer structures exposed by the second mask, and removing the second mask. The remaining first polymer structures and the remaining second polymer structures are not connected to each other.

Owner:UNITED MICROELECTRONICS CORP

![[structure applied to a photolithographic process and method for fabricating a semiconductor device] [structure applied to a photolithographic process and method for fabricating a semiconductor device]](https://images-eureka.patsnap.com/patent_img/0ecb7c9f-1063-40d1-b4d0-57c470bf79d1/US20050148166A1-20050707-D00000.png)

![[structure applied to a photolithographic process and method for fabricating a semiconductor device] [structure applied to a photolithographic process and method for fabricating a semiconductor device]](https://images-eureka.patsnap.com/patent_img/0ecb7c9f-1063-40d1-b4d0-57c470bf79d1/US20050148166A1-20050707-D00001.png)

![[structure applied to a photolithographic process and method for fabricating a semiconductor device] [structure applied to a photolithographic process and method for fabricating a semiconductor device]](https://images-eureka.patsnap.com/patent_img/0ecb7c9f-1063-40d1-b4d0-57c470bf79d1/US20050148166A1-20050707-D00002.png)