Plug structure and process thereof

a technology of plug and socket, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., to achieve the effect of enhancing the adhesion between the first contact plug and the second contact plug

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

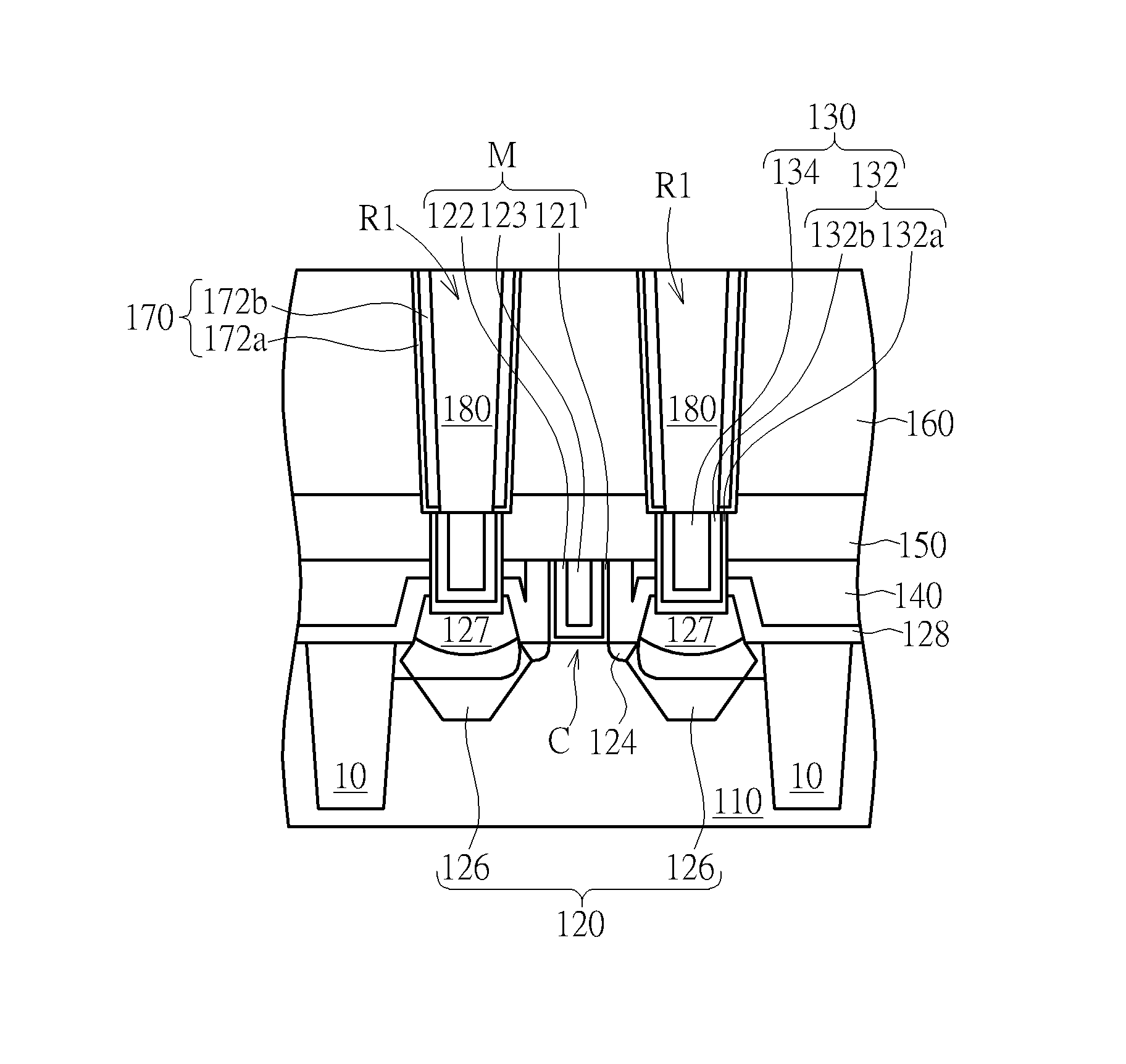

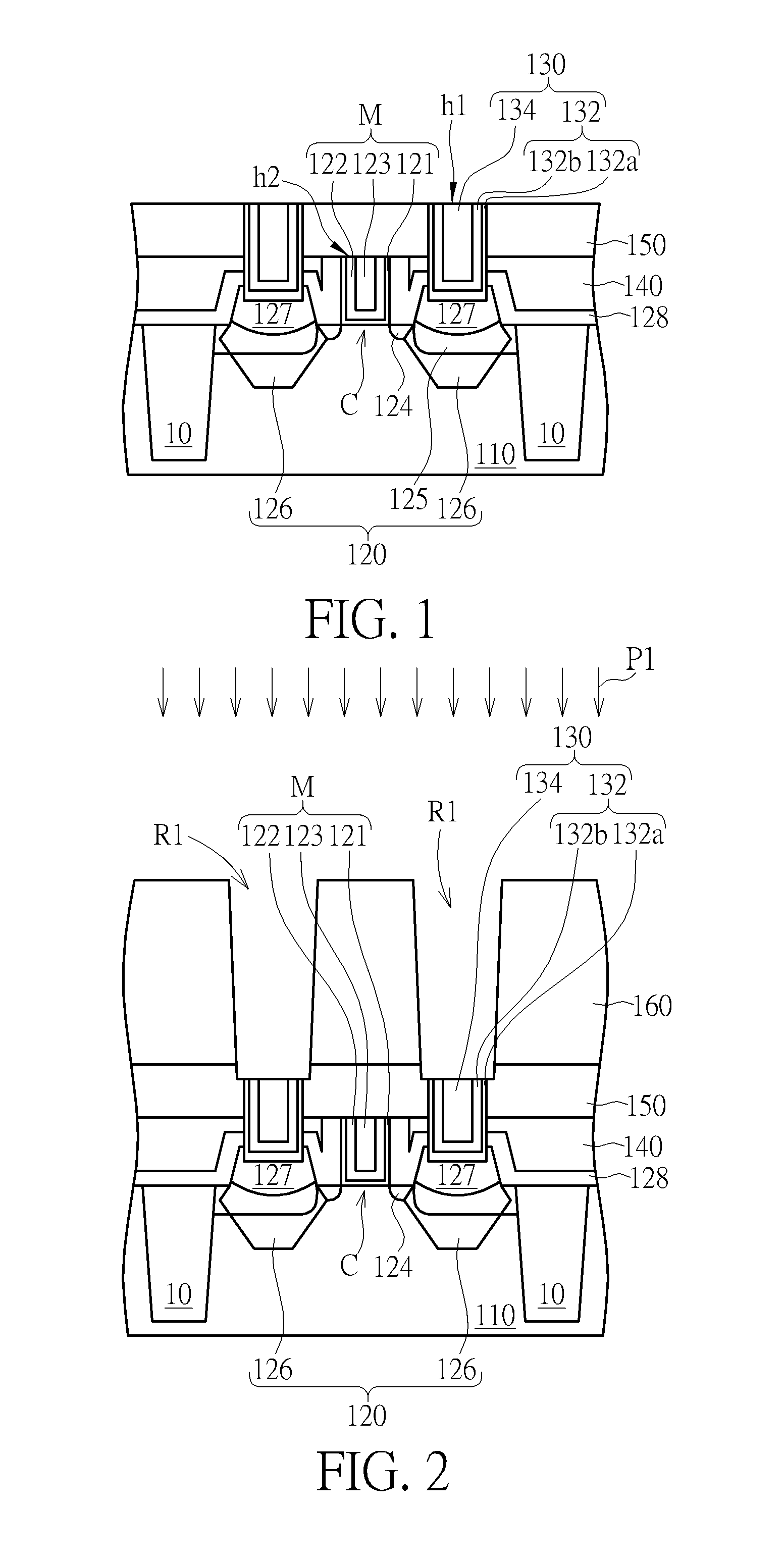

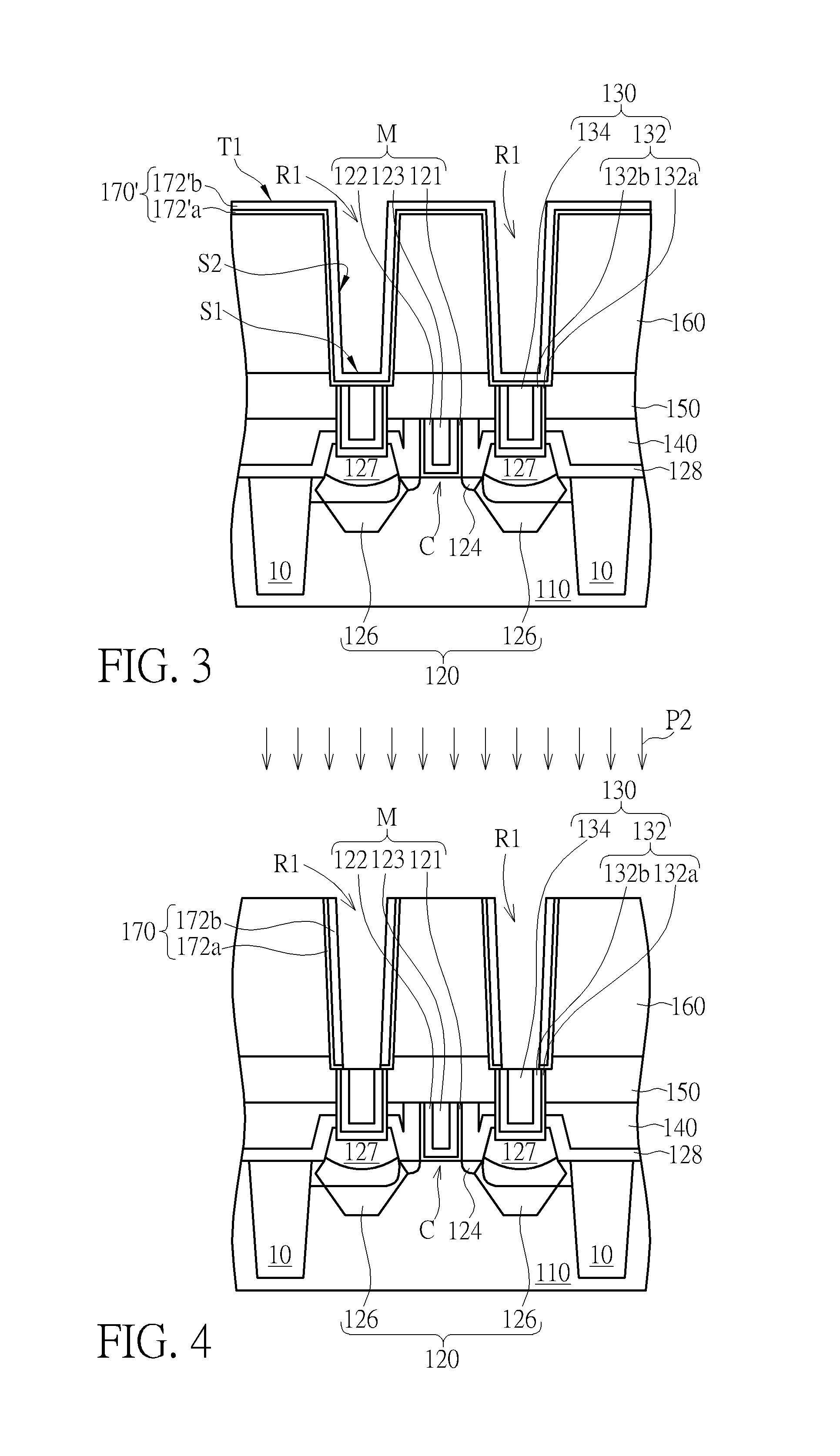

[0014]FIGS. 1-6 schematically depict cross-sectional views of a method of forming a plug structure according to a first embodiment of the present invention. As shown in FIG. 1, a substrate 110 is provided. The substrate 110 may be a semiconductor substrate such as a silicon substrate, a silicon containing substrate, a III-V group-on-silicon (such as GaN-on-silicon) substrate, a graphene-on-silicon substrate or a silicon-on-insulator (SOI) substrate. Isolation structures 10 are formed in the substrate 110 to electrically isolate each MOS transistor. A MOS transistor 120 is formed on / in the substrate 110. The MOS transistor 120 may include a metal gate M on the substrate, and the metal gate M may includes a stacked structure including a dielectric layer 121, a work function layer 122 and a low resistivity material 123 sequentially from bottom to top; a lightly doped source / drain 124, a source / drain 125 and an epitaxial structure 126 are formed in the substrate 110 beside the metal gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More