Correction method for self-aligned dual patterning process and semiconductor device thereof

A double patterning and self-alignment technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as uneven key dimensions, tilted morphology, and poor etched film structure morphology, achieving Consistent critical dimension uniformity and improved morphology, the effect of improving critical dimensions and morphology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention is described in detail below in conjunction with accompanying drawing:

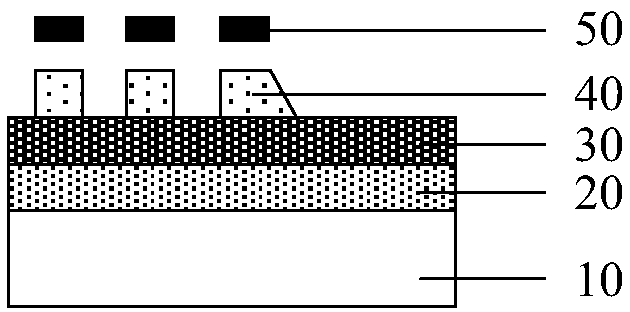

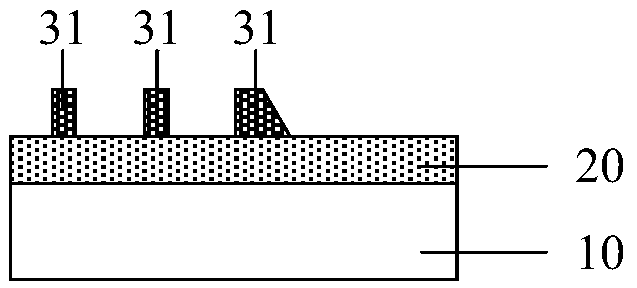

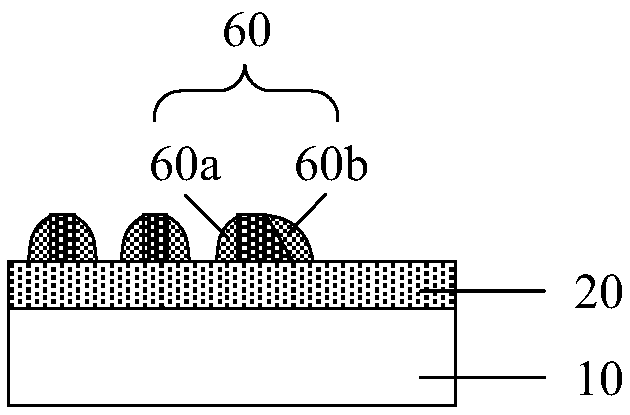

[0026] Please refer to Figure 14 , an embodiment of the present invention provides a method for correcting a self-aligned double patterning process, comprising the following steps:

[0027] Step 901, please refer to Figure 7 , providing a substrate 100 .

[0028] Step 902, please refer to Figure 7 , forming an etching film layer 110 on the substrate 100 .

[0029] Step 903, please refer to Figure 7 , forming a core layer 120 on the etched film layer 110 . The material of the core layer is, for example, oxides such as silicon dioxide.

[0030] Step 904, please refer to Figure 7 , coating a photoresist layer 130 on the core layer 120 .

[0031] Step 905, please refer to Figure 7, set a core layer mask (core mask) 140, and add a group of mask structures 141 with the same specification next to the position of the core layer mask 140 corresponding to the core pattern...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More