Patents

Literature

45results about How to "Improve critical dimension uniformity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

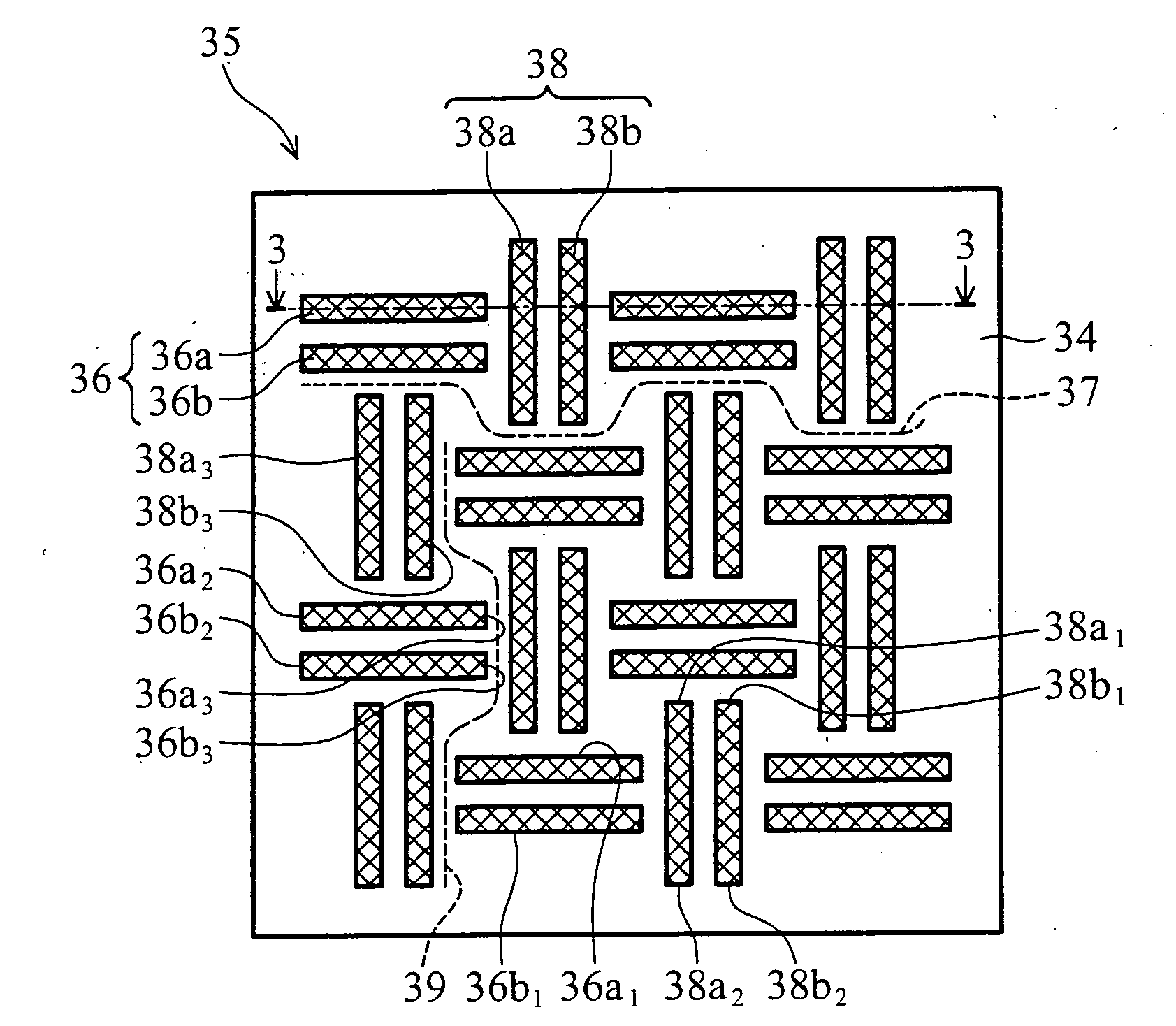

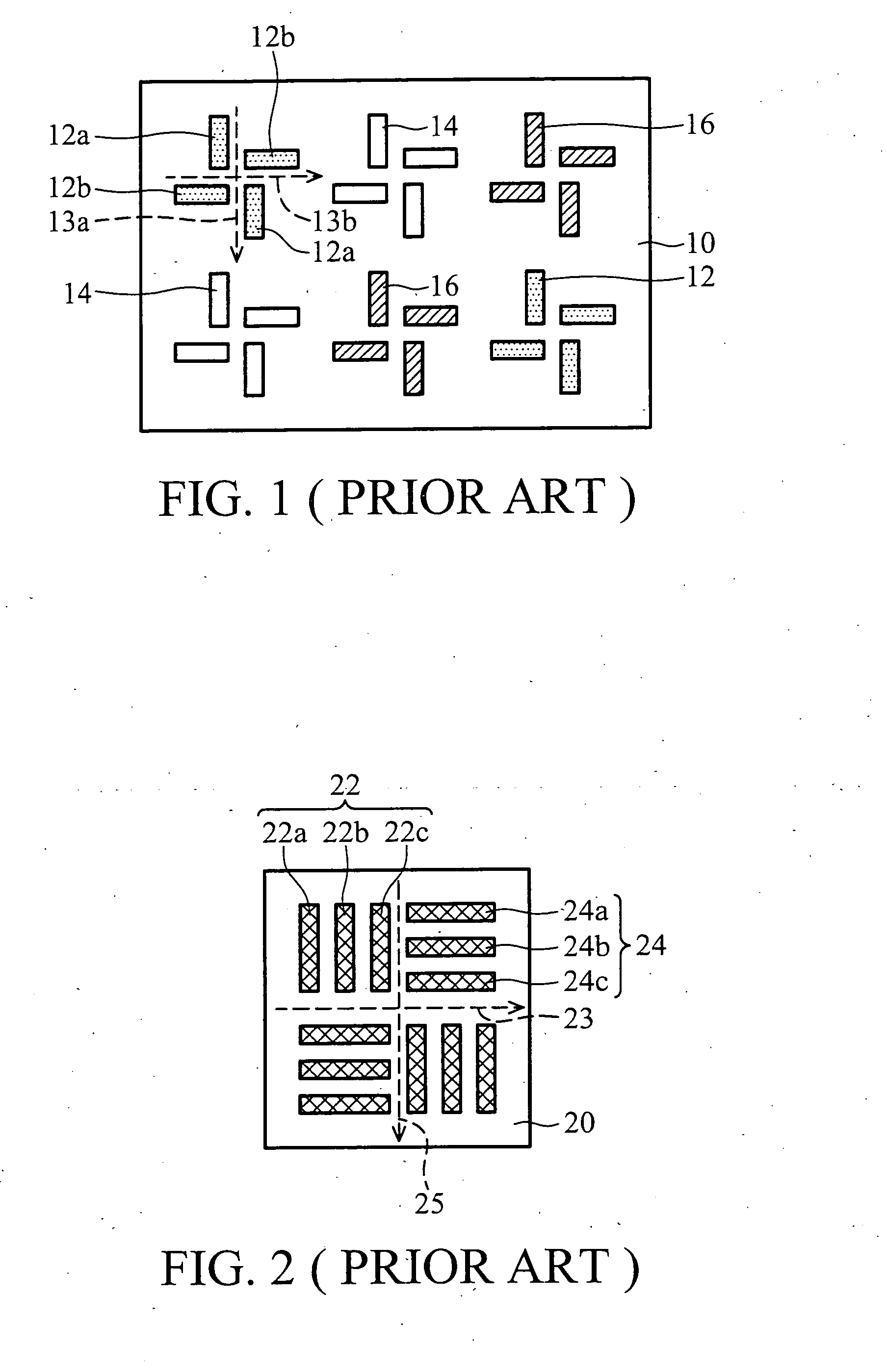

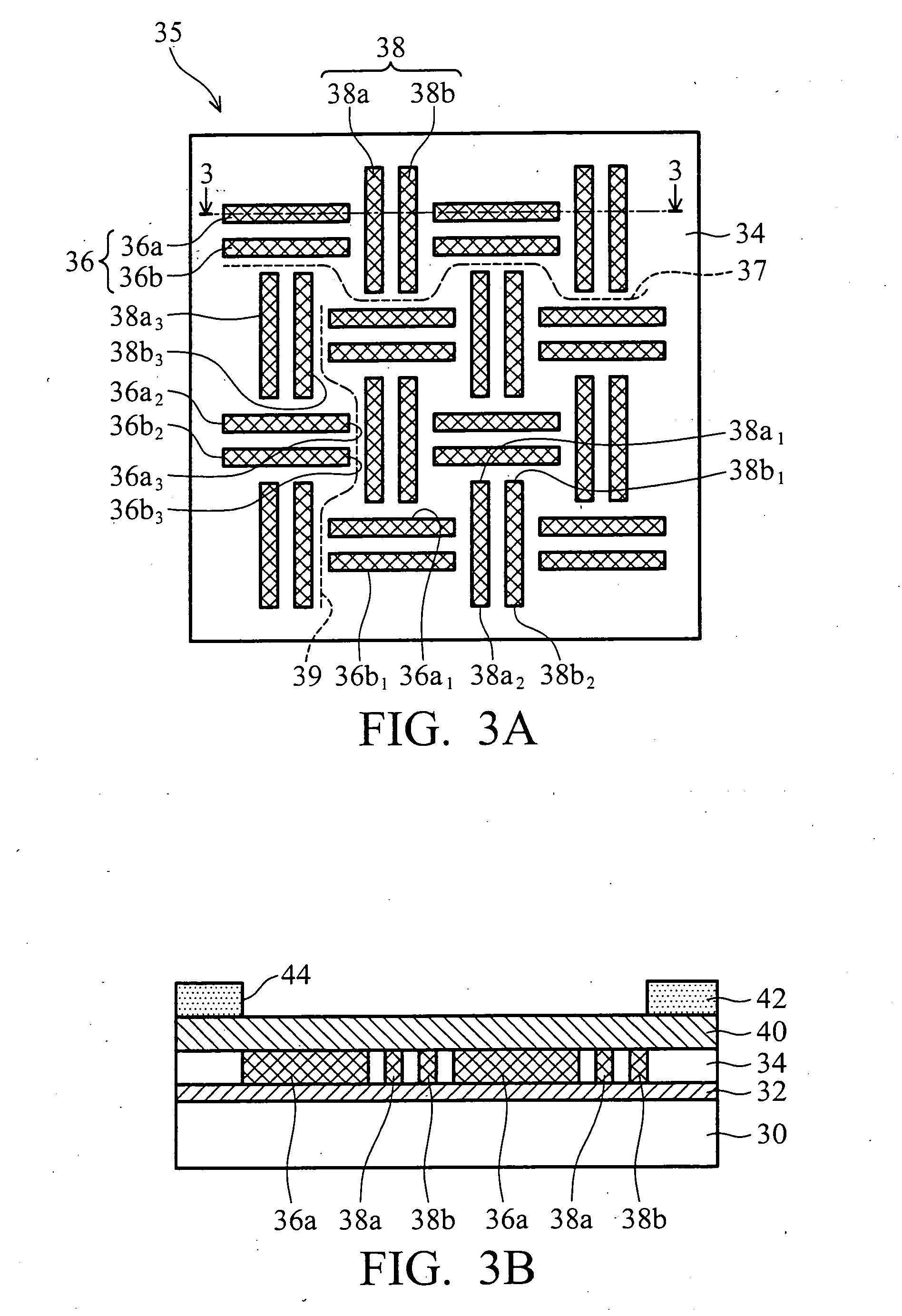

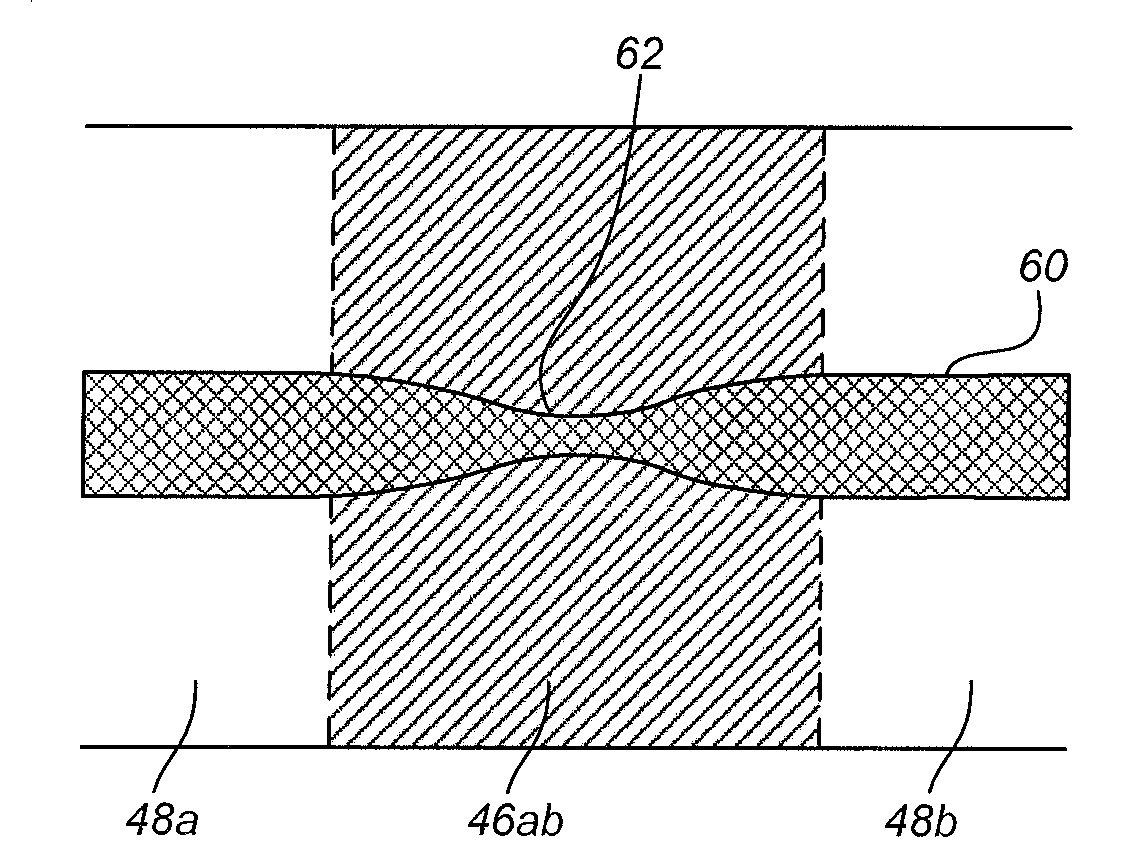

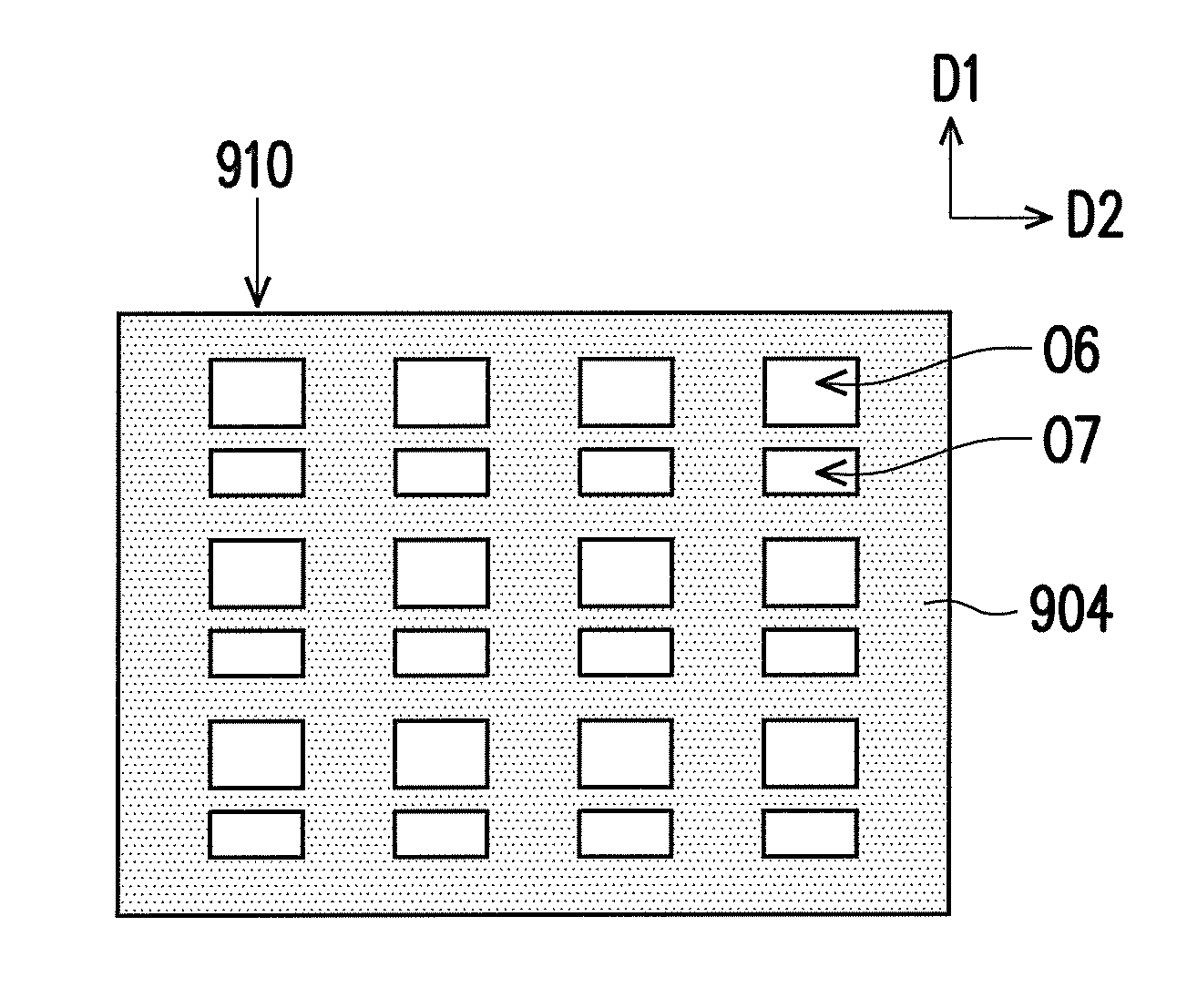

Via layout with via groups placed in interlocked arrangement

ActiveUS20070290361A1Improve critical dimension uniformityImprove thickness uniformitySemiconductor/solid-state device detailsSolid-state devicesEngineeringA domain

Via layout with via groups placed in an interlocked arrangement for suppressing the crack propagation along the domain boundary between the via groups. A structure has a metal via pattern located in a dielectric layer and having a first via group and a second via group adjacent to each other. The first via group has at least two first line vias extending in a first direction, and the second via group has at least two second line vias extending in a second direction. The first via group and the second via group are placed in an interlocked arrangement, and a domain boundary along the first direction or the second direction between the first via group and said second via group is not straight.

Owner:TAIWAN SEMICON MFG CO LTD

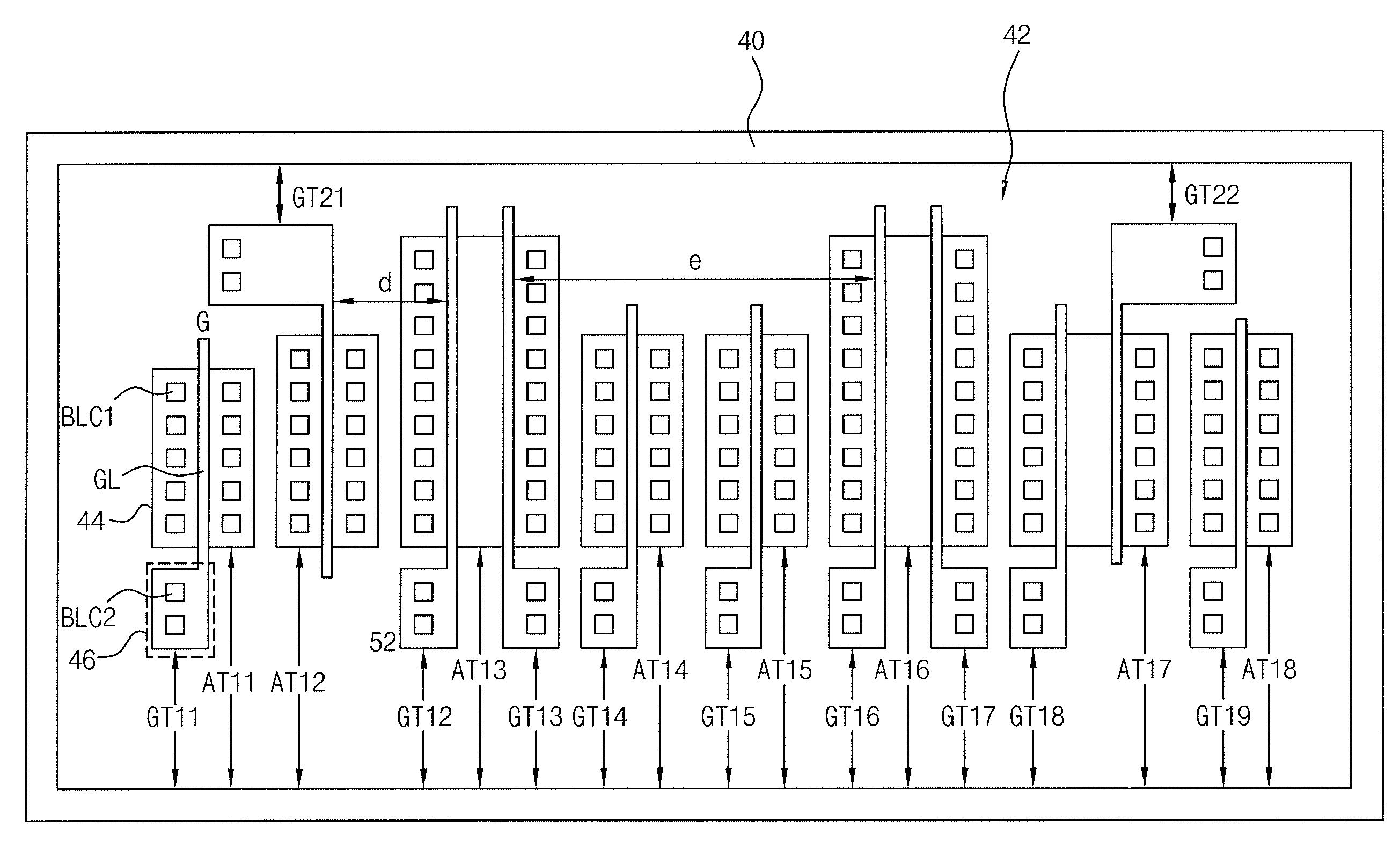

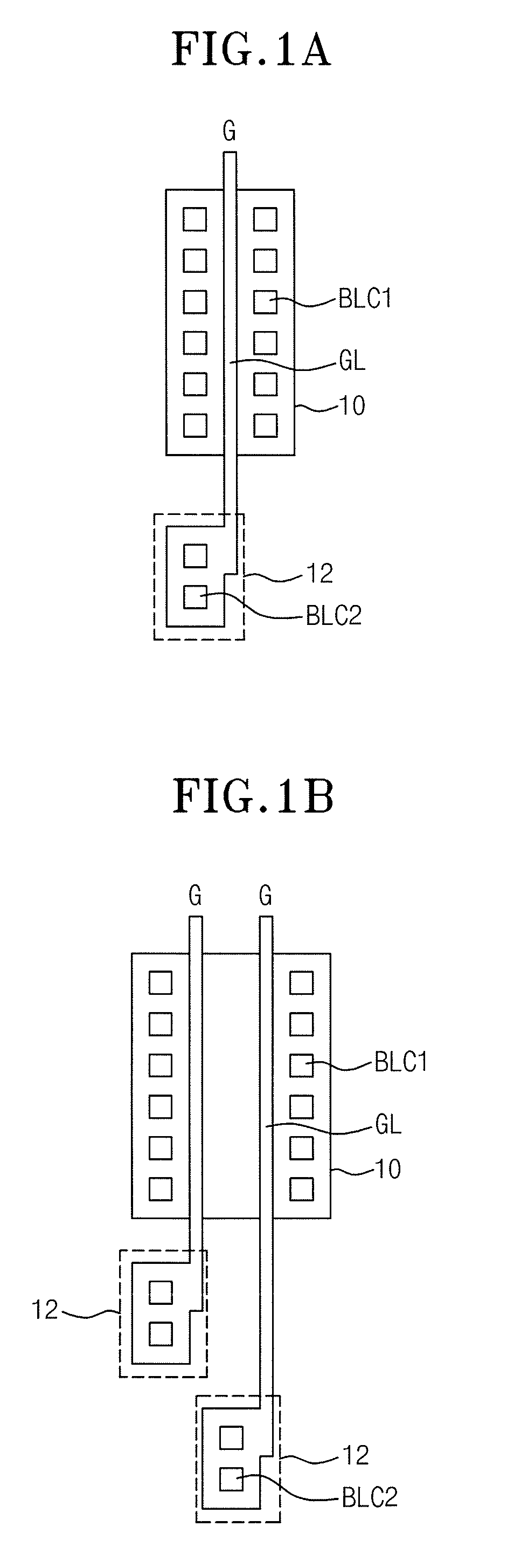

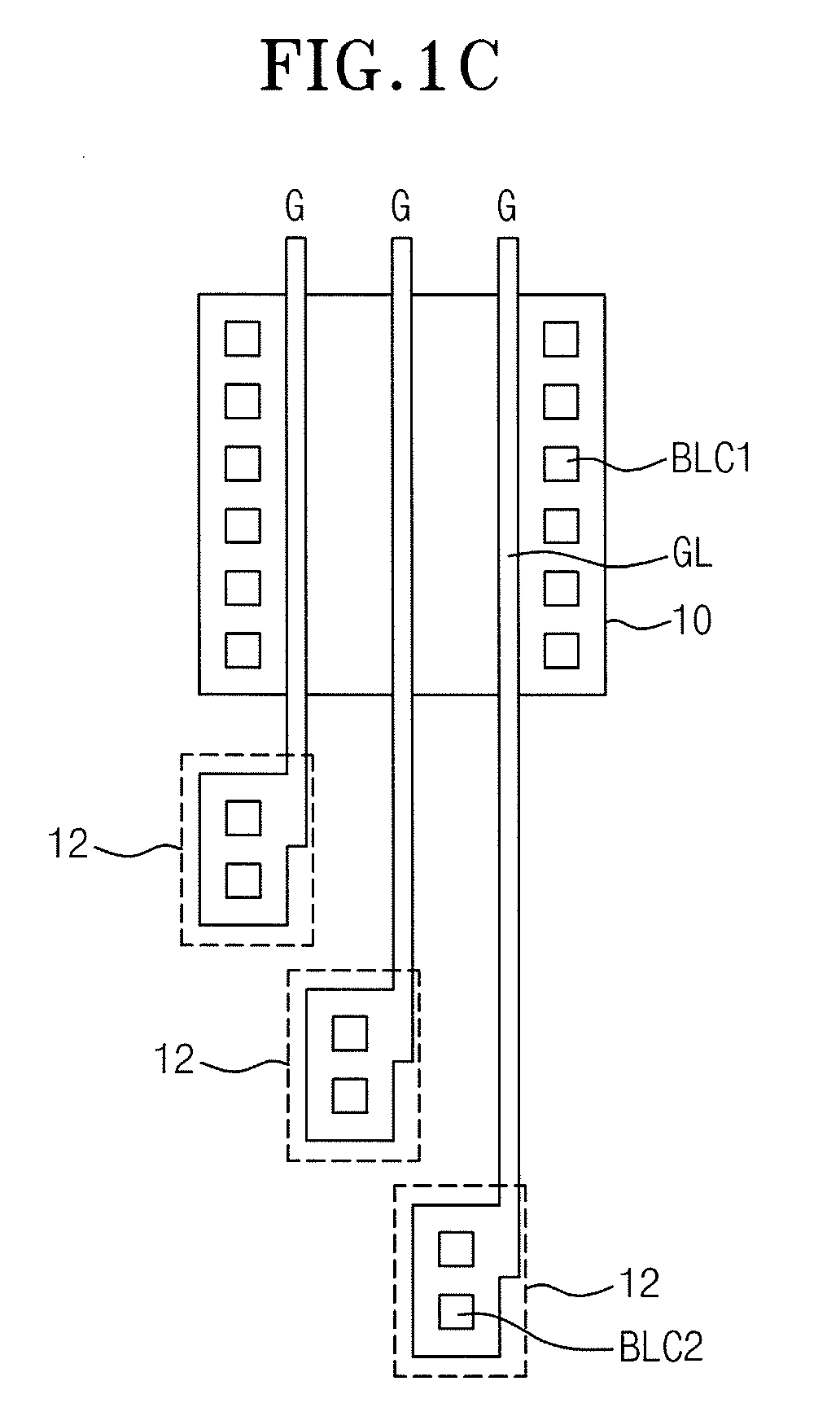

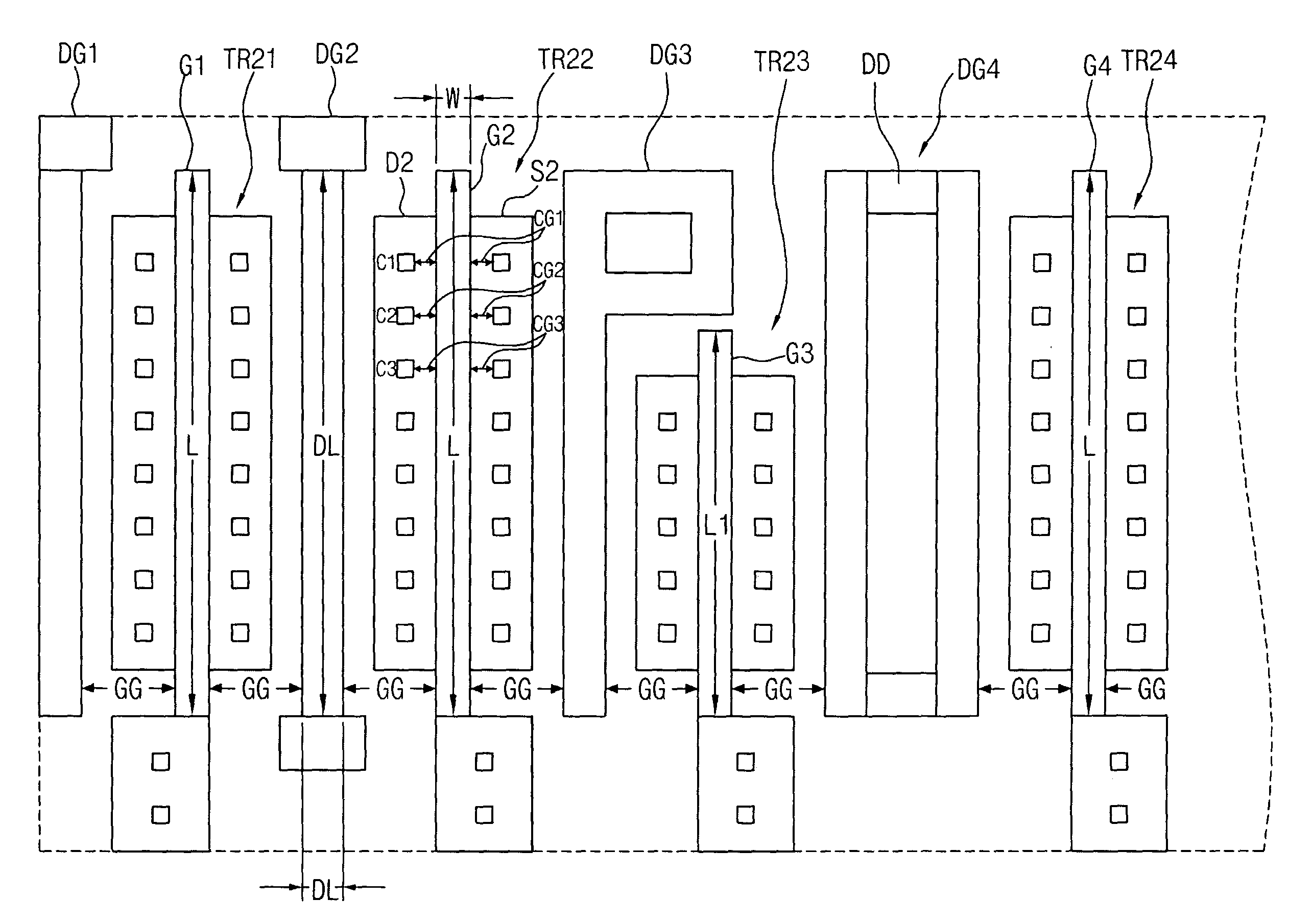

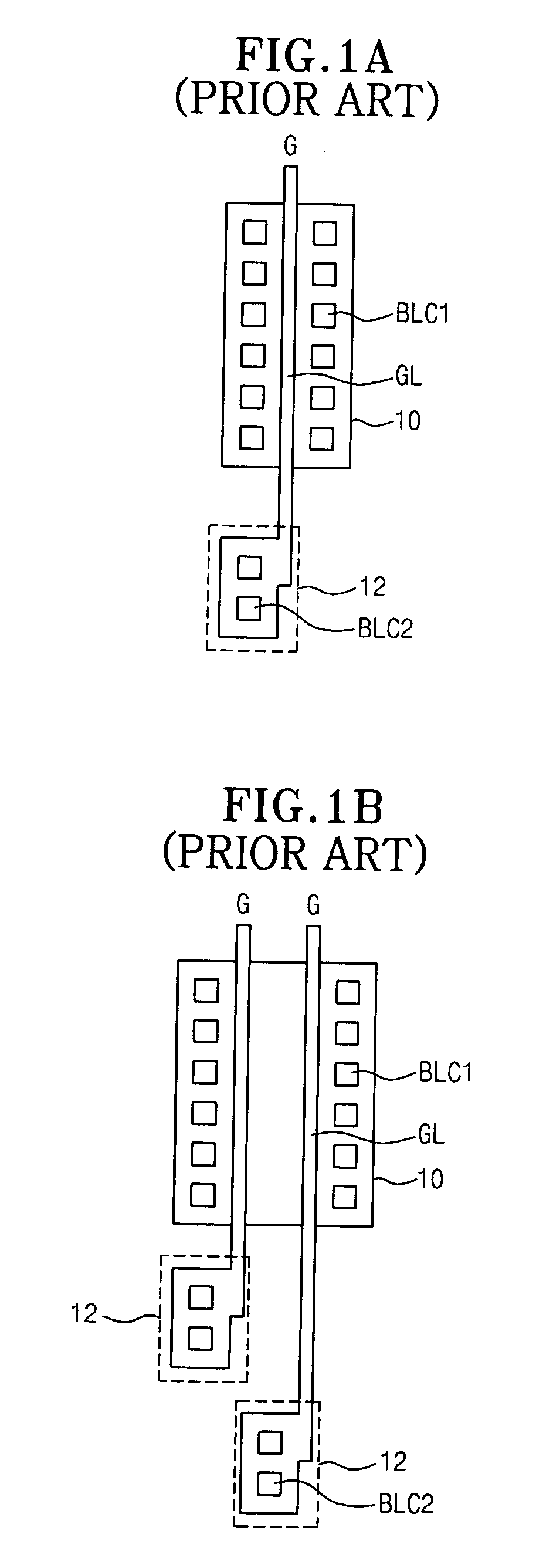

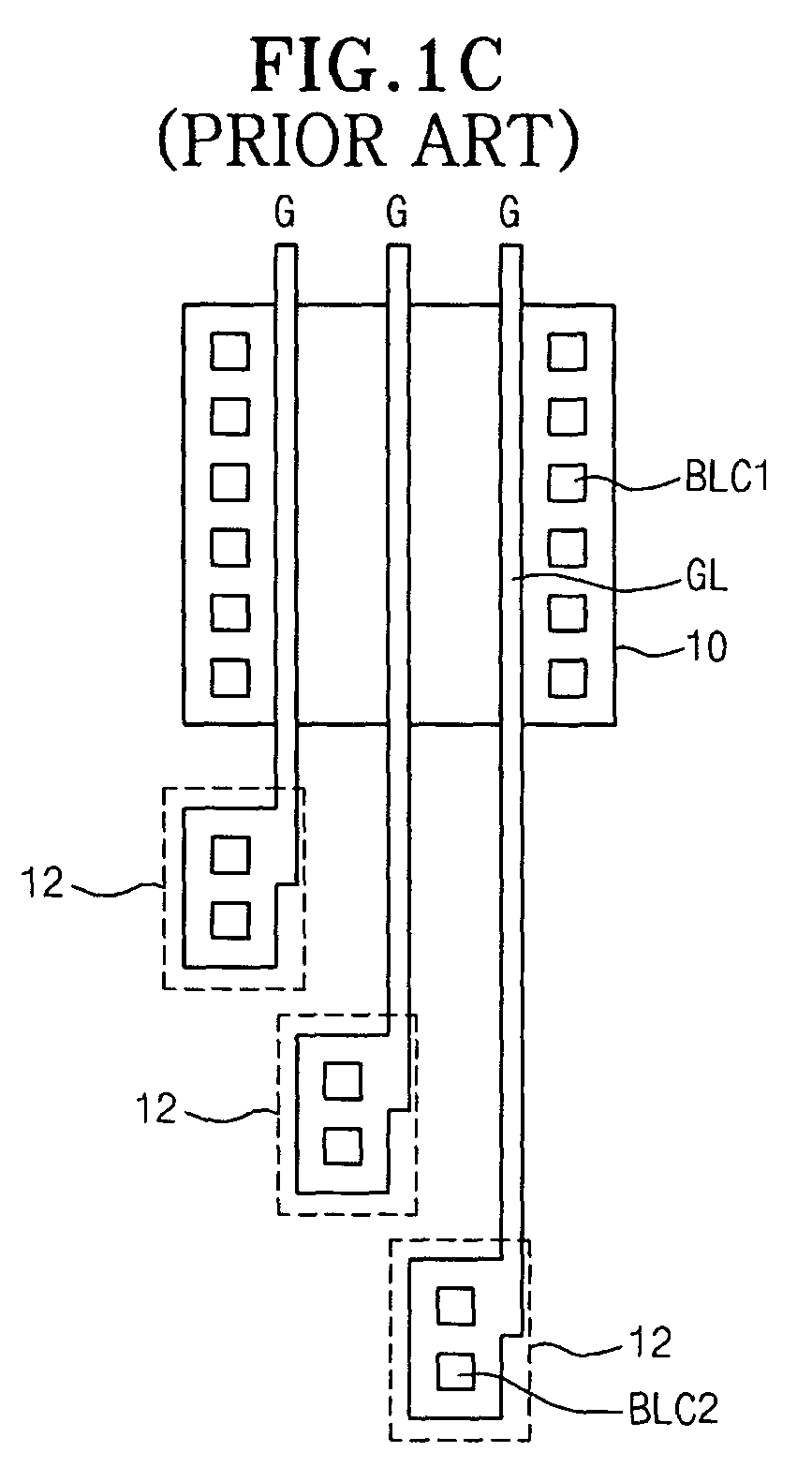

Semiconductor device and method of forming gate and metal line thereof

InactiveUS20080265335A1Reduce formationImprove critical dimension uniformityTransistorSemiconductor/solid-state device detailsChannel couplingEngineering

A gate in a semiconductor device is formed to have a dummy gate pattern that protects a gate. Metal lines are formed to supply power for a semiconductor device and transfer a signal. A semiconductor device includes a quad coupled receiver type input / output buffer. The semiconductor device is formed with a gate line that extends over an active region, and a gate pad located outside of the active region. The gate line and the gate pad are adjoined such that the gate line and a side of the gate pad form a line. Dummy gates may also be applied. The semiconductor device includes a first metal line patterns supplying power to a block having a plurality of cells, a second metal line pattern transferring a signal to the cells, and dummy metal line patterns divided into in a longitudinal direction.

Owner:SK HYNIX INC

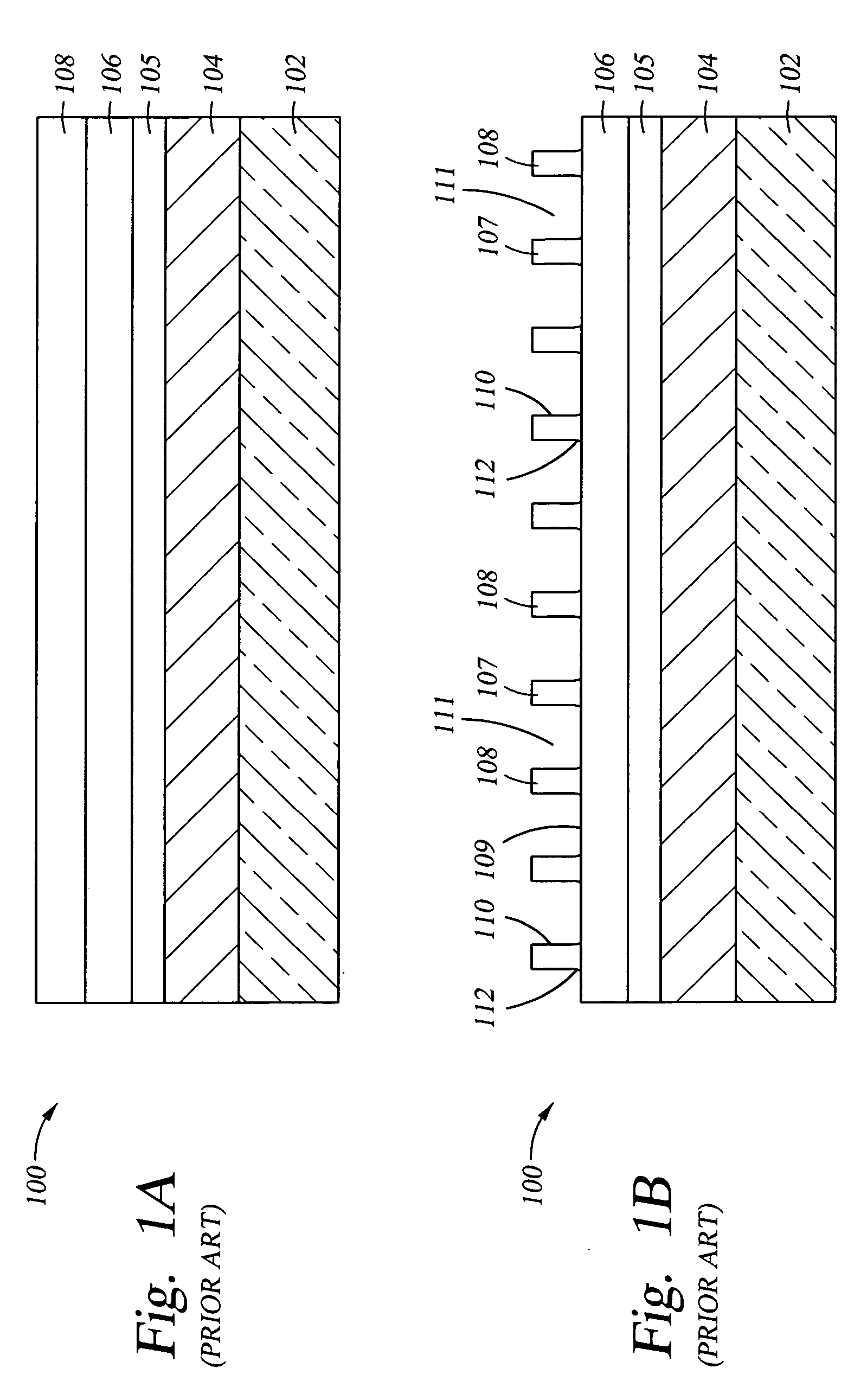

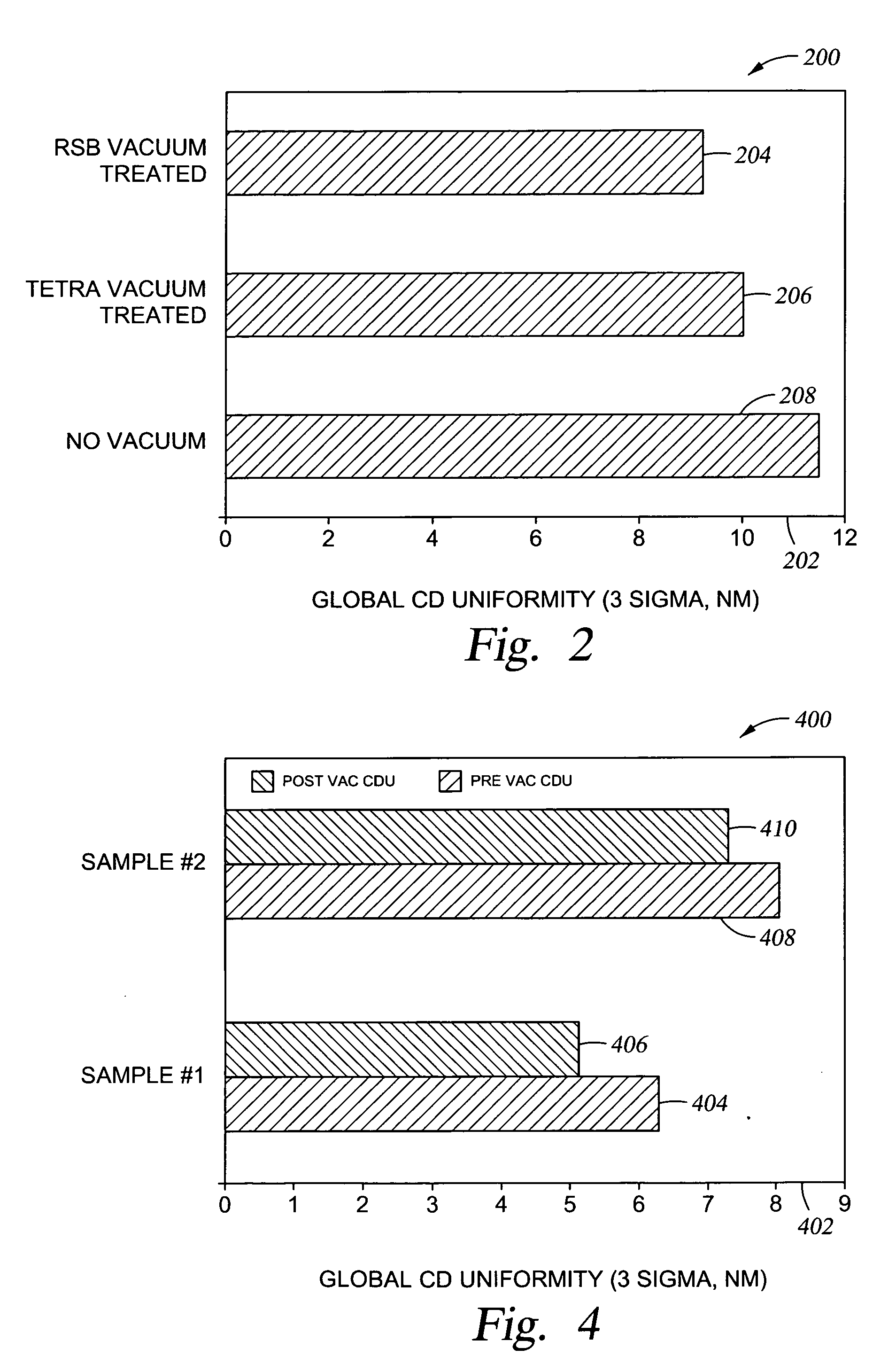

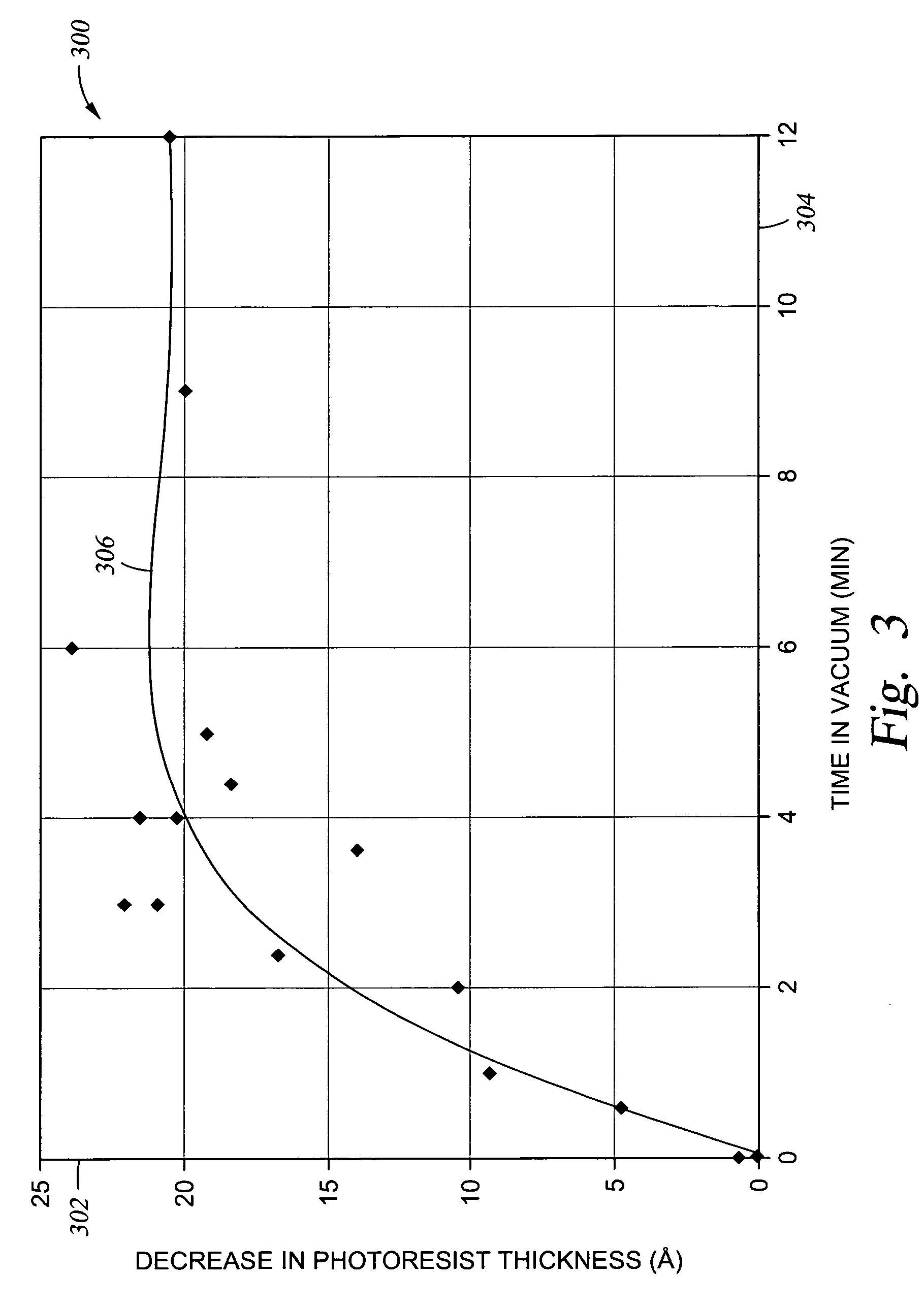

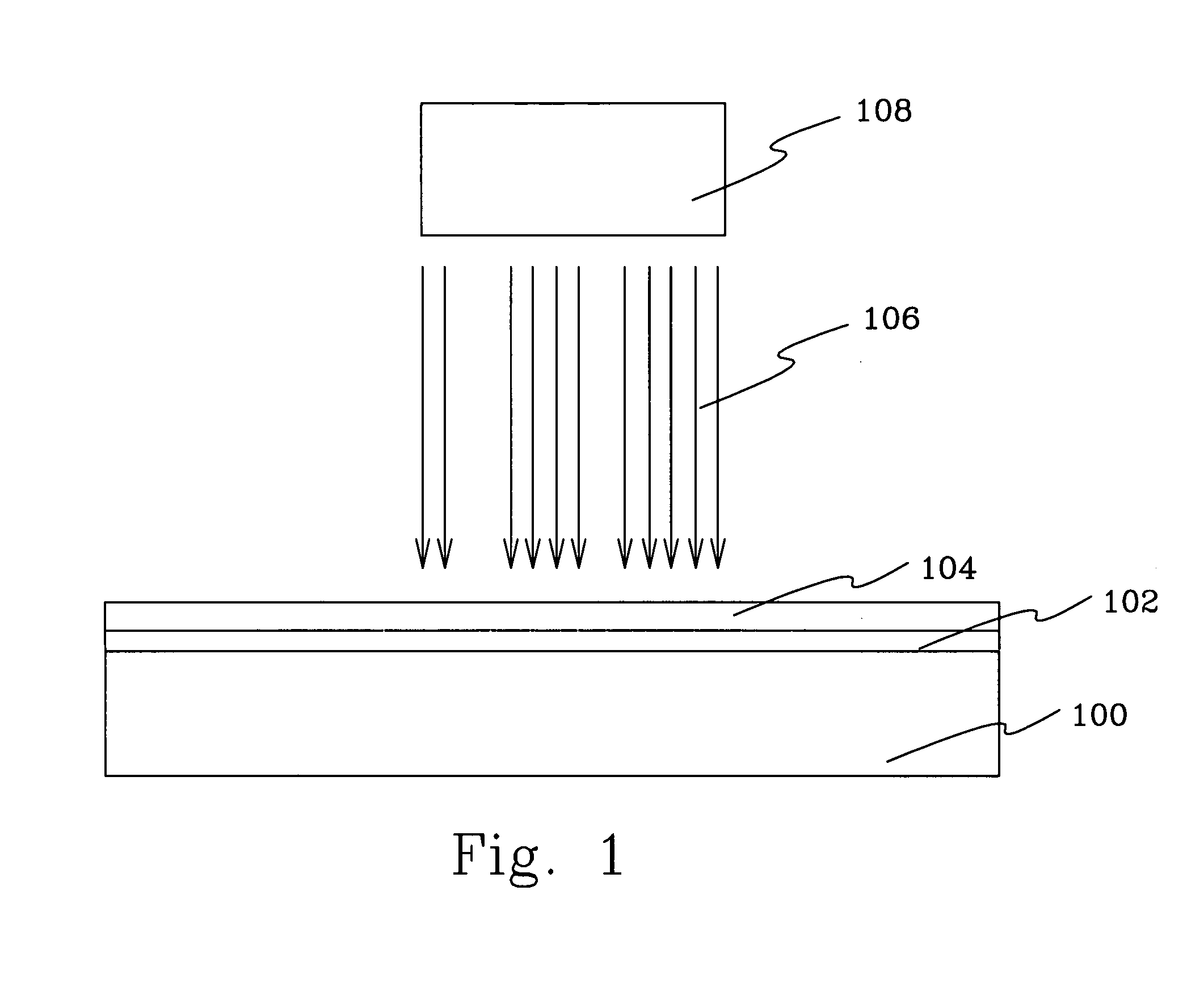

Method of improving the uniformity of a patterned resist on a photomask

InactiveUS20050221019A1Increased line edge roughnessSmooth out sidewall roughnessPhotosensitive material processingPhotographic processesPhysicsPhotoresist

We have discovered that exposure of a photoresist on a photomask substrate to a vacuum after the photoresist has been exposed to imaging radiation results in improved critical dimension uniformity of the developed photoresist. Exposure of the imaged photoresist to vacuum is performed for a period of time sufficient to allow pattern critical dimensions to reach equilibrium across the photoresist. The vacuum treatment process of the invention is typically performed prior to the performance of a post-exposure bake process and prior to development of the photoresist. We have also discovered that exposure of a photoresist on a photomask substrate to a vacuum after the photoresist has been developed results in an improvement in the line edge roughness of pattern openings that have been formed through the photoresist layer thickness.

Owner:APPLIED MATERIALS INC

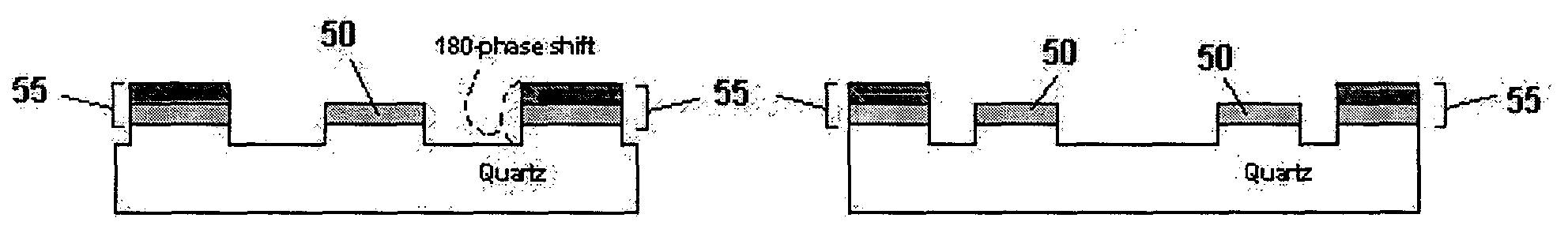

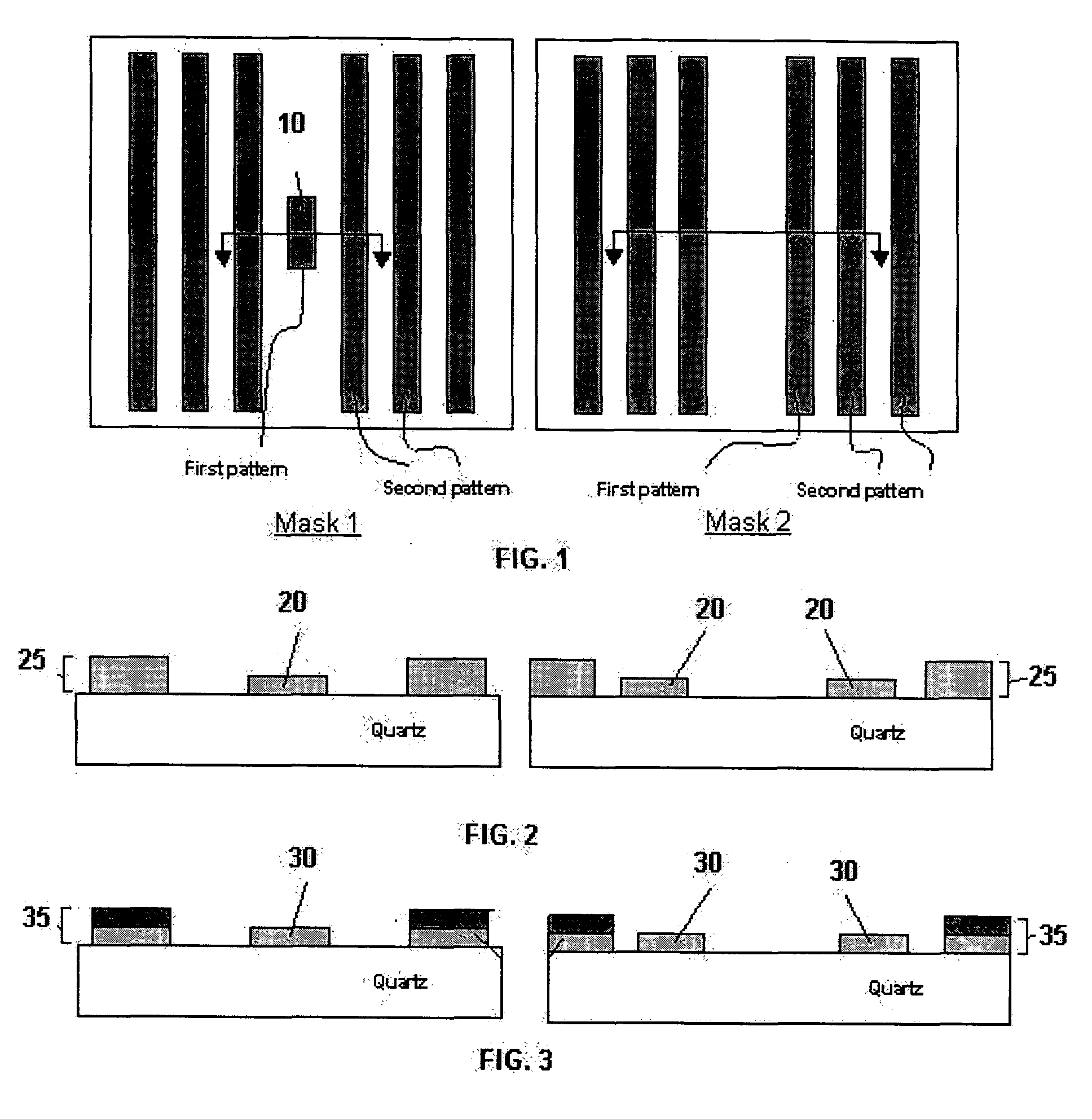

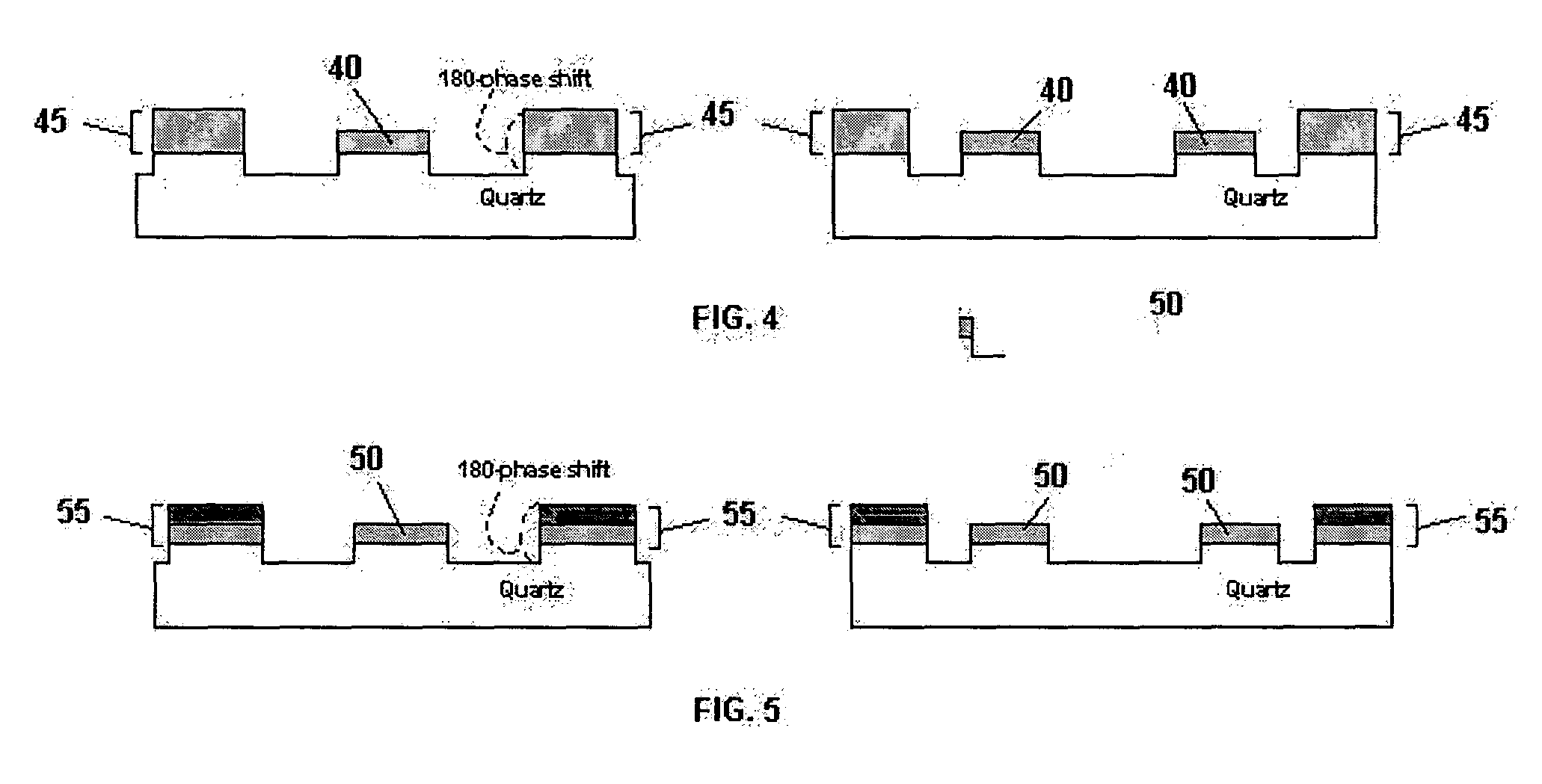

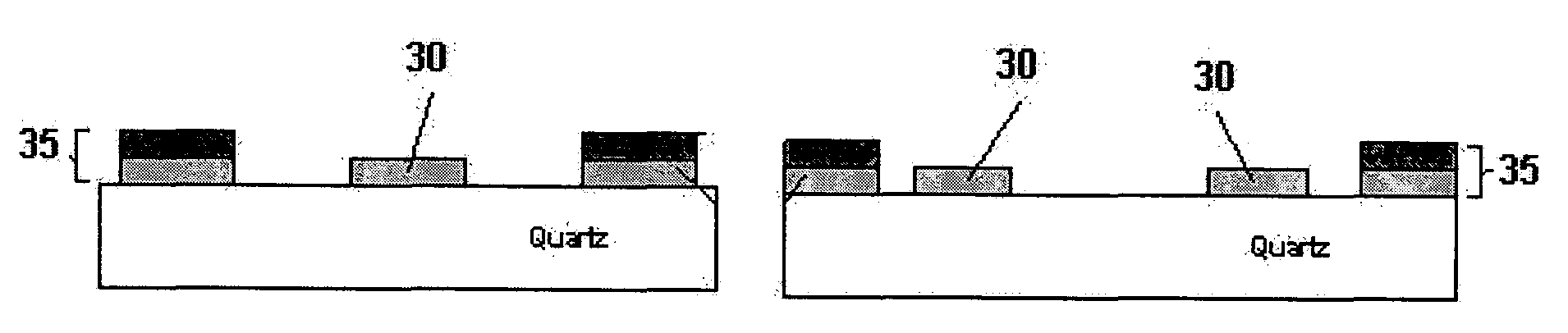

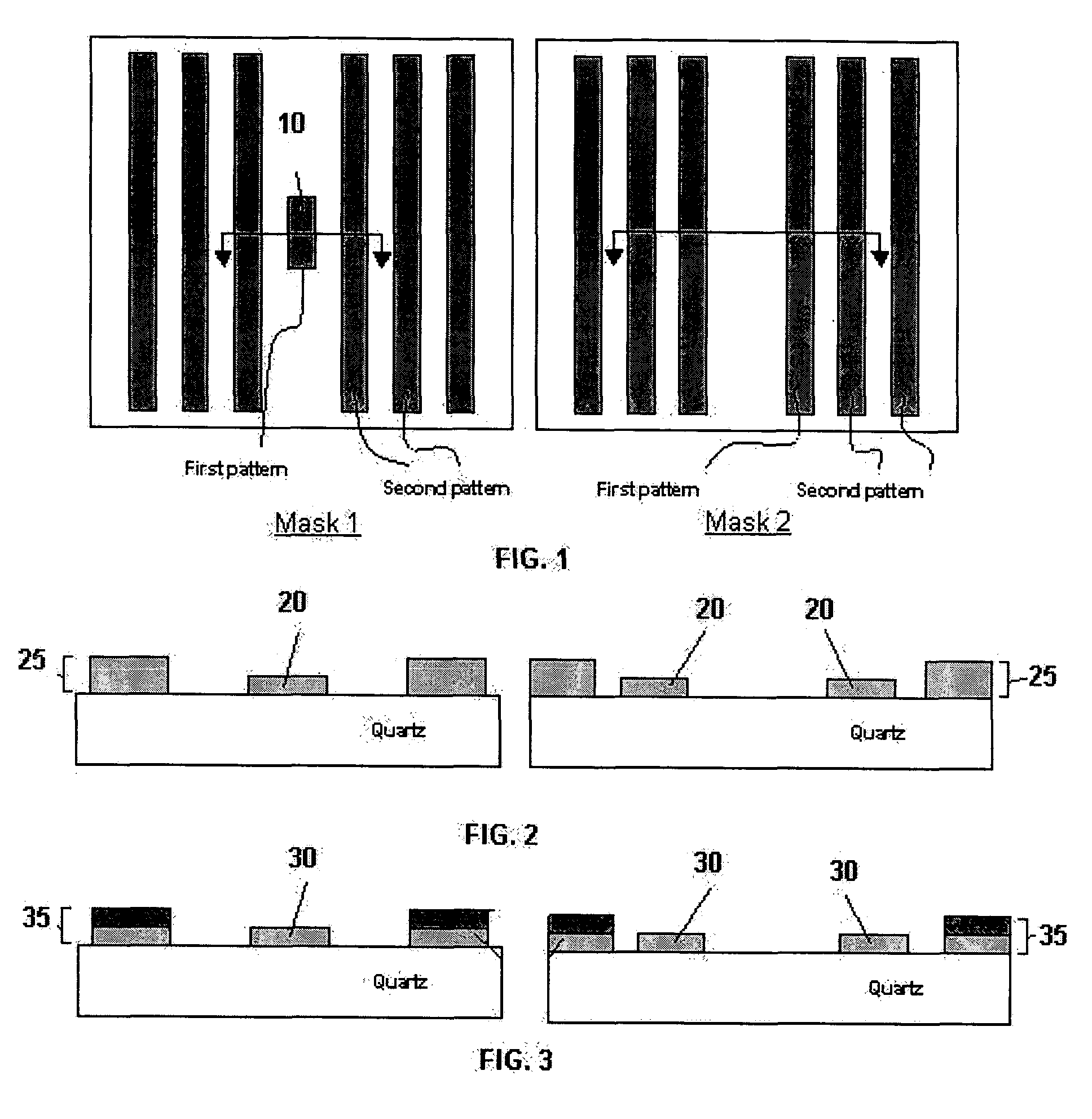

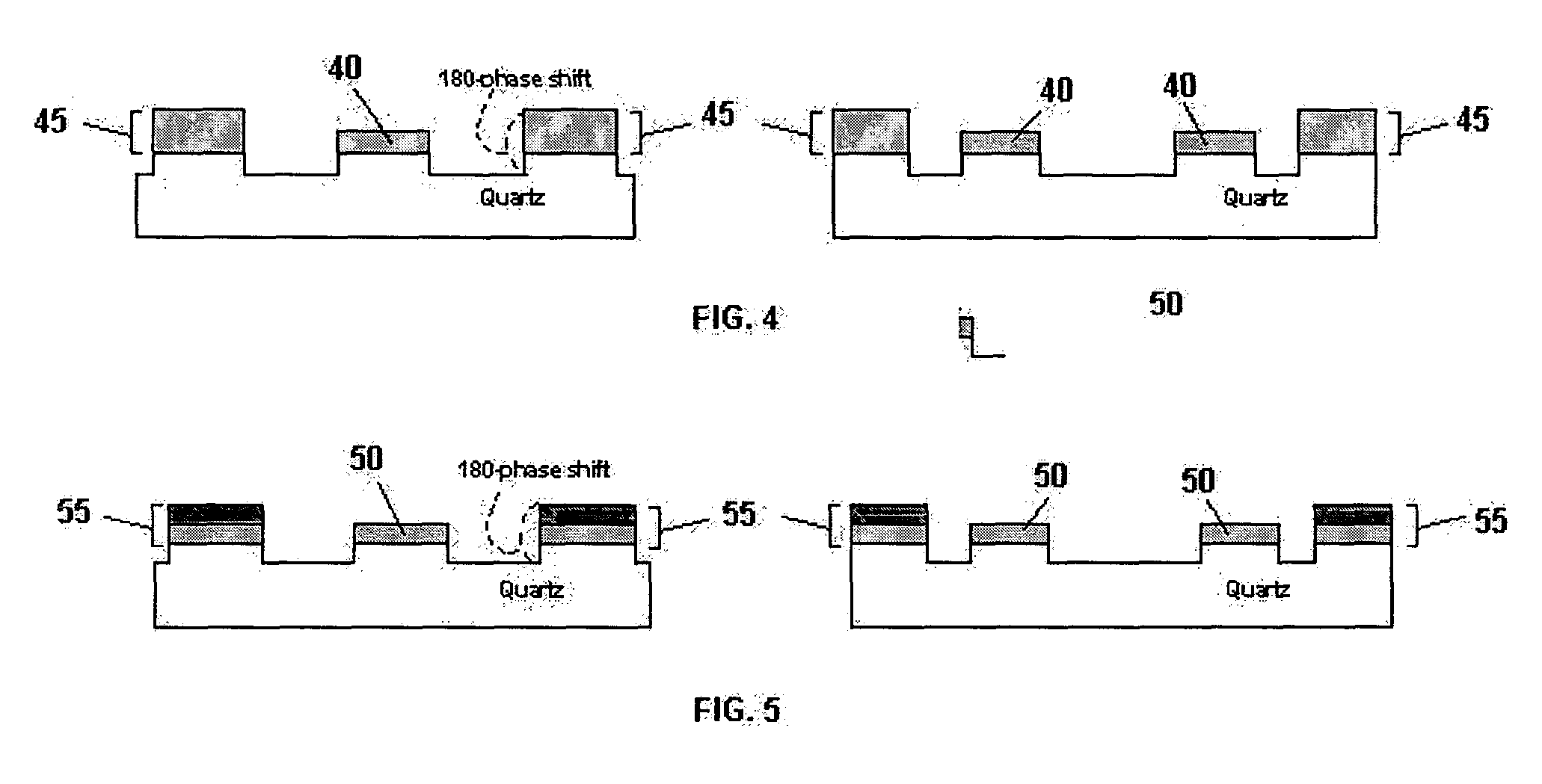

Mask for improving lithography performance by using multi-transmittance photomask

ActiveUS20050048377A1Efficient and effectiveEfficiently and effectively reduce issueOriginals for photomechanical treatmentPhotographic processesPhase shiftedLithographic artist

Materials and methods for fabricating multi-transmittance halftone phase shift masks (HTPSM) are disclosed. The masks include patterns having regions of different transmittance for the purpose of reducing one or more of line edge shortening, iso-to-dense bias, and edge-to-dense bias. The masks employ at least one halftone material in forming the patterns that have different transmittances. Regions of denser or longer lines are constructed to have a lower transmittance than regions of isolated lines. The patterns may include a single halftone material of different thicknesses for different regions or may include two halftone materials applied singly and doubly to different regions.

Owner:MACRONIX INT CO LTD

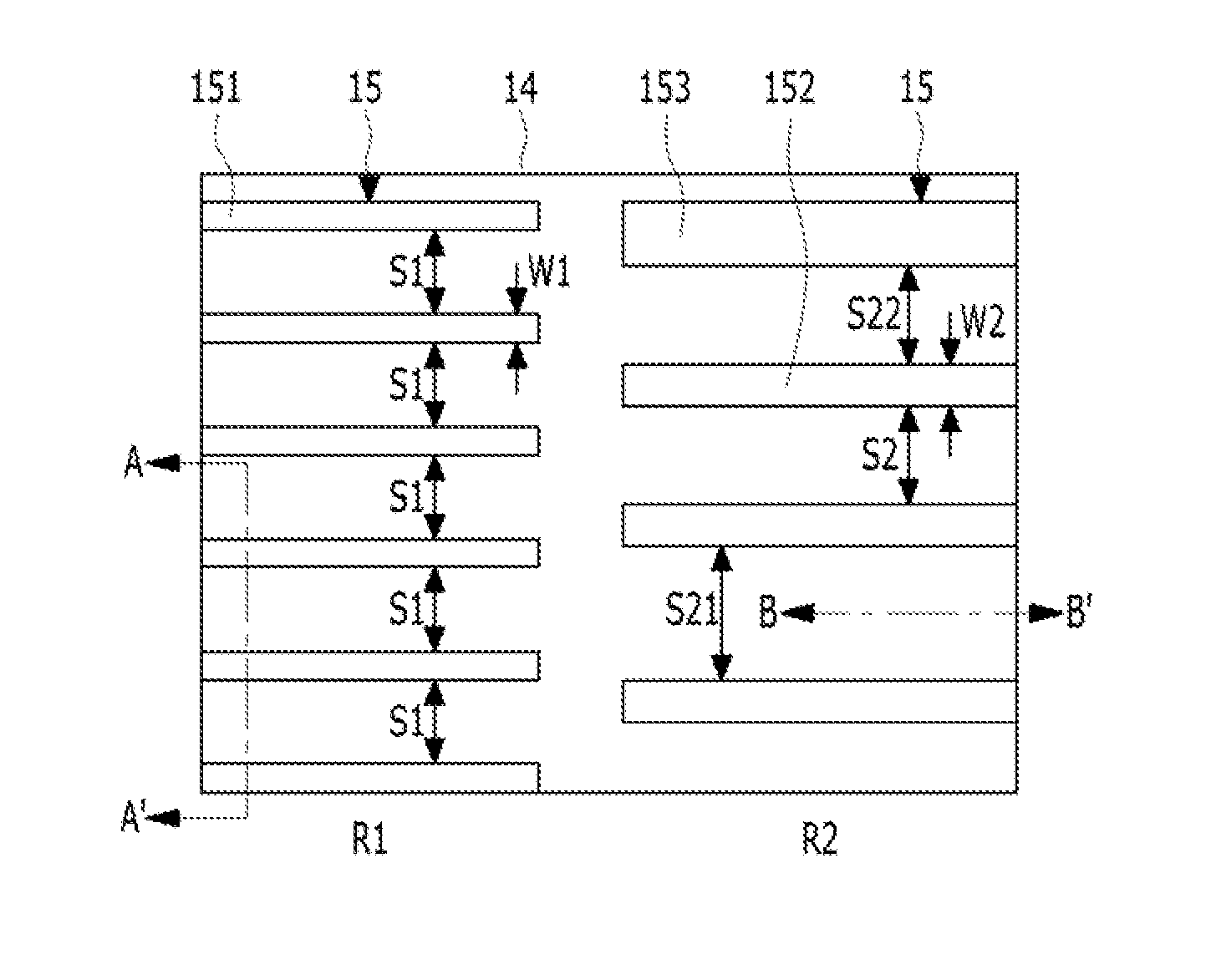

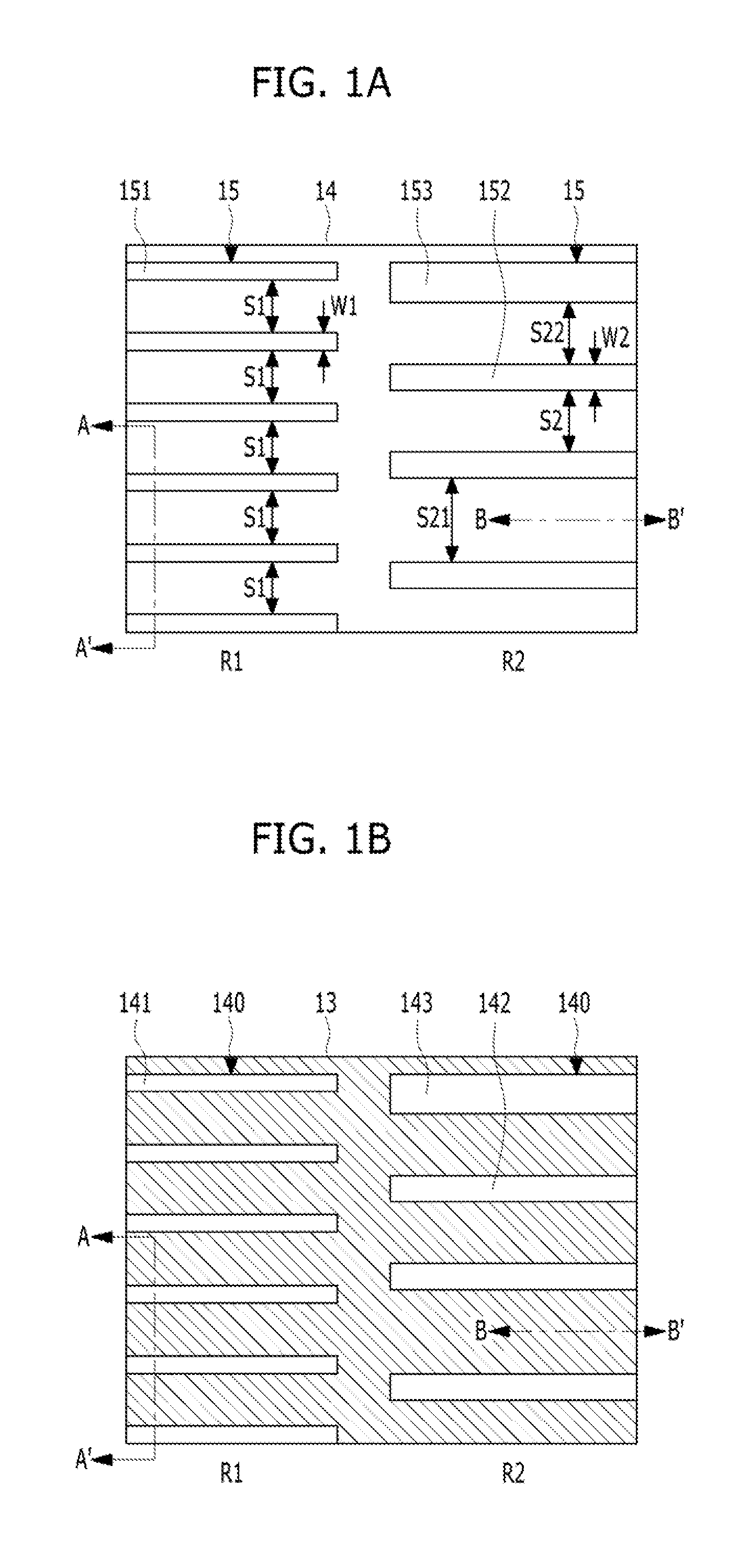

Semiconductor device and method of forming gate and metal line thereof with dummy pattern and auxiliary pattern

InactiveUS8053346B2Reduce formationImprove critical dimension uniformityTransistorSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor

A gate in a semiconductor device is formed to have a dummy gate pattern that protects a gate. Metal lines are formed to supply power for a semiconductor device and transfer a signal. A semiconductor device includes a quad coupled receiver type input / output buffer. The semiconductor device is formed with a gate line that extends over an active region, and a gate pad located outside of the active region. The gate line and the gate pad are adjoined such that the gate line and a side of the gate pad form a line. Dummy gates may also be applied. The semiconductor device includes a first metal line patterns supplying power to a block having a plurality of cells, a second metal line pattern transferring a signal to the cells, and dummy metal line patterns divided into in a longitudinal direction.

Owner:SK HYNIX INC

Enhanced stitching by overlap dose and feature reduction

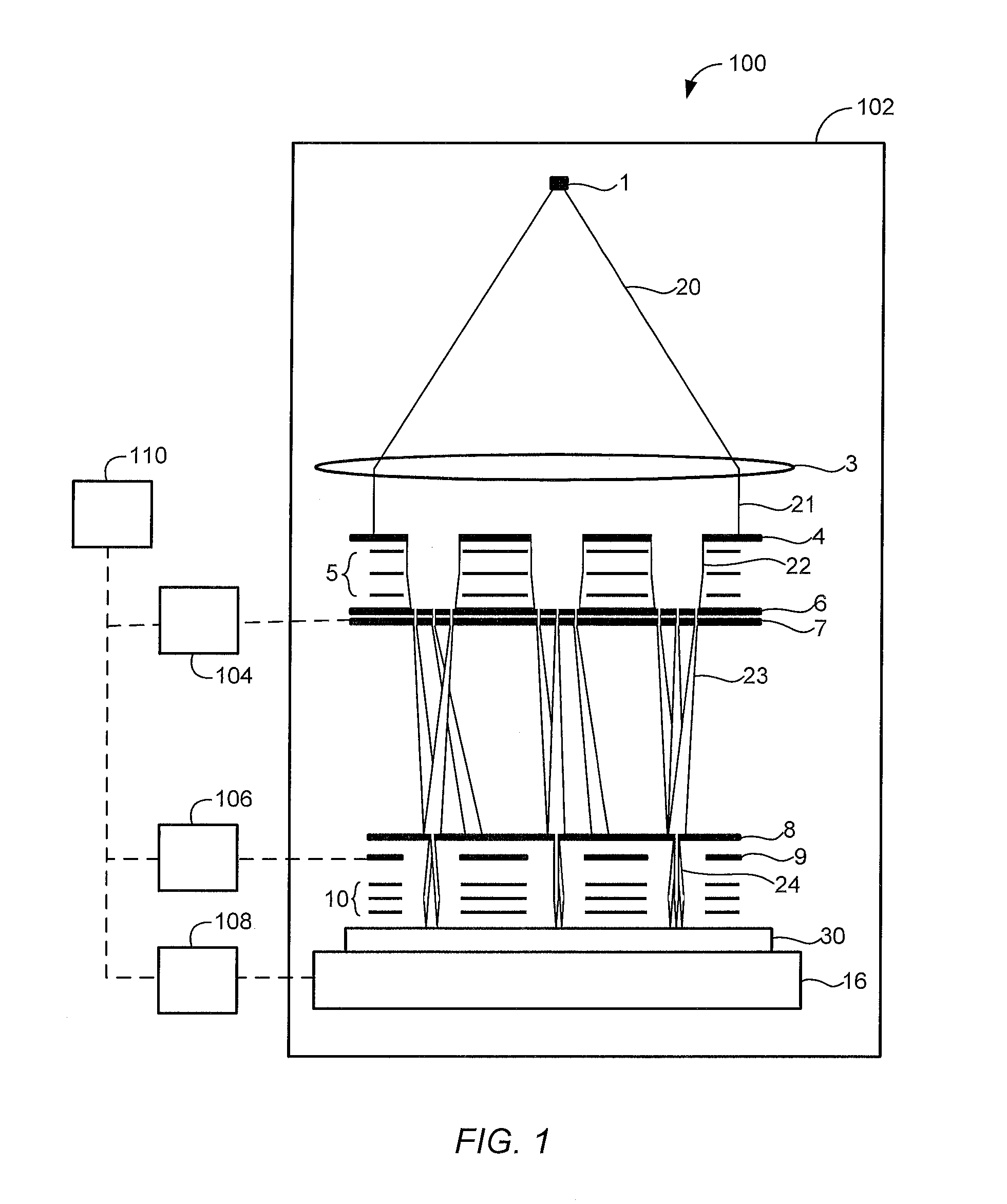

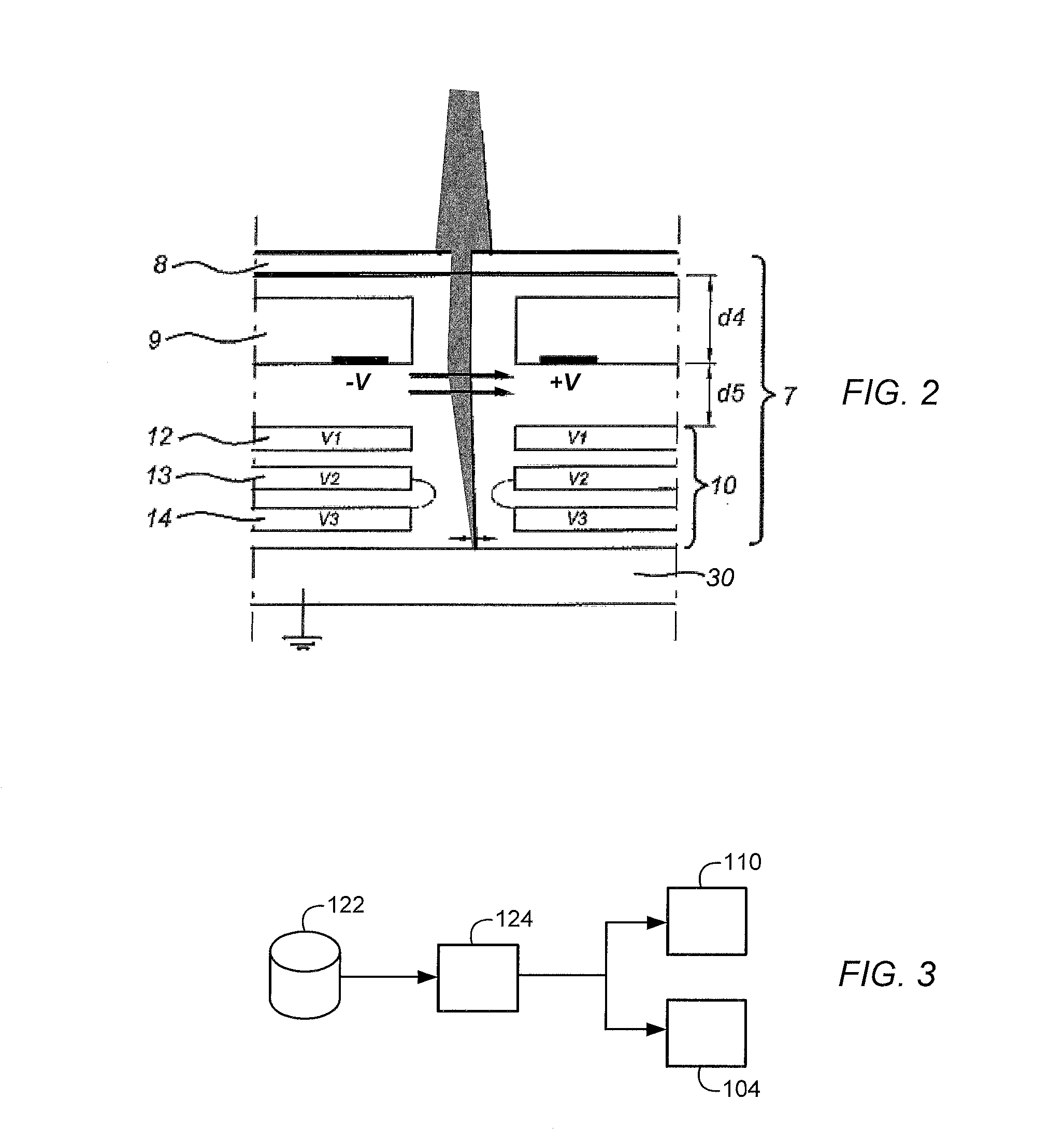

ActiveUS20150242563A1Improve critical dimension uniformityIncrease exposureElectric discharge tubesPhotomechanical apparatusMedicineMaximum dose

A method for processing exposure data (40) for exposing a pattern on a target (30) using a plurality of charged particle beams (24), the exposure data comprising pattern data (42) representing one or more features (60) to be written on the target (30) and exposure dose data (52) describing exposure dose of the charged particle beams. The method comprises setting one or more dose values of the exposure dose data (52) such that a sum of dose values corresponding to a position in an overlap area (36) of the target exceeds a maximum dose value for the non-overlap areas (38) of the target where adjacent sub-areas (34) do not overlap, and dividing the pattern data (42) into a plurality of sub-sections (44), each of the sub-sections comprising pattern data describing a part of the pattern to be written in a corresponding sub-area (34) of the target (30), wherein the pattern data (42) comprises overlap pattern data (46) describing a part of the pattern to be written in a corresponding overlap area (36) of the target where adjacent sub-areas (34) overlap, and processing the overlap pattern data (46) to reduce a size of one or more features described by the overlap pattern data.

Owner:ASML NETHERLANDS BV

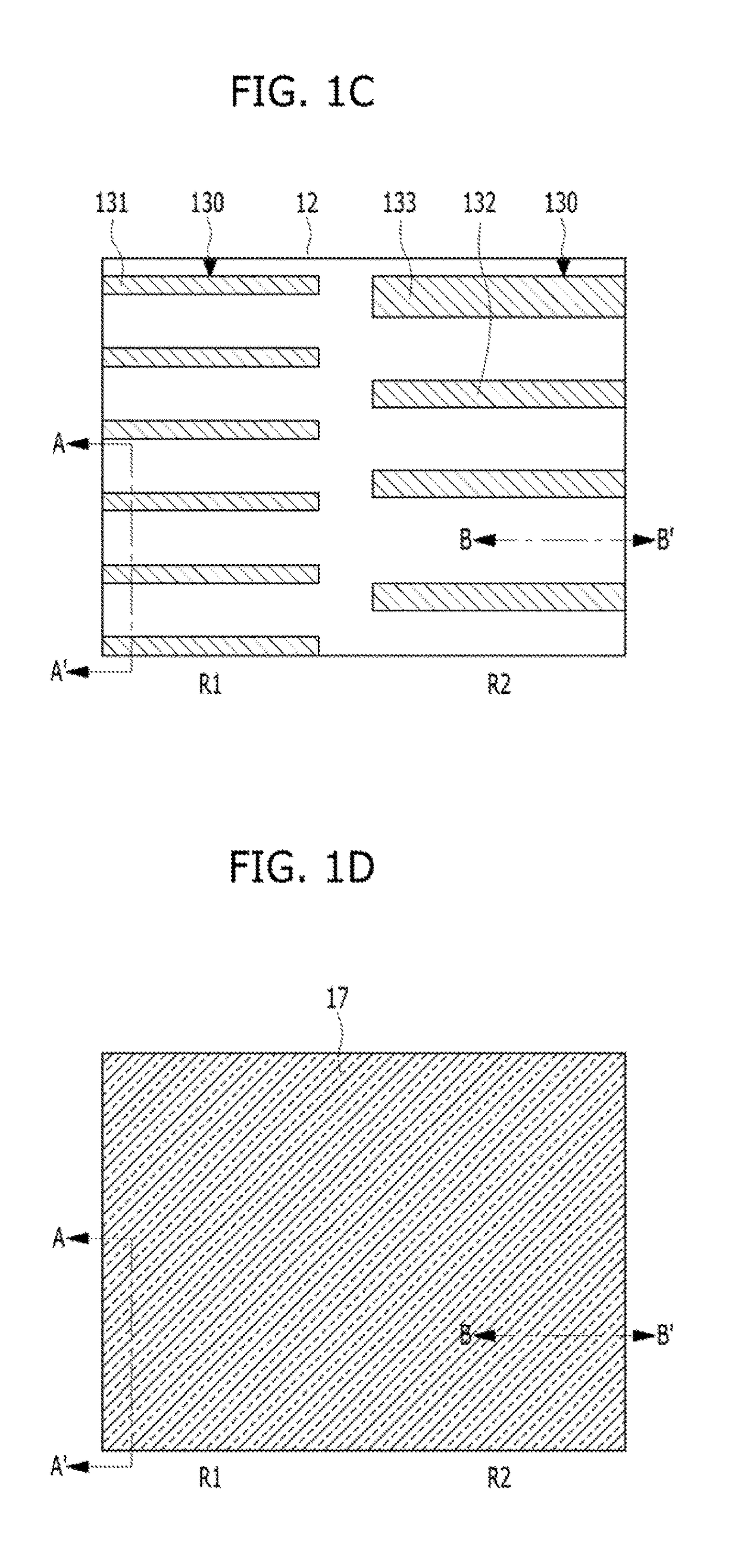

Method for forming patterns of semiconductor device

ActiveUS20170025284A1Improve critical dimension uniformityIncrease process marginSolid-state devicesSemiconductor/solid-state device manufacturingRandom arrayEngineering

A method for forming patterns of a semiconductor device includes preparing an etch target layer defined with a first region and a second region; forming a regular first feature which is positioned over the etch target layer in the first region and a random feature which is positioned over the etch target layer in the second region; forming a regular second feature over the regular first feature; forming first and second cutting barriers which expose a portion of the random feature, over the random feature; cutting the regular first feature using the regular second feature, to form a regular array feature; cutting the random feature using the first cutting barrier and the second cutting barrier, to form a random array feature; and etching the etch target layer by using the regular array feature and the random array feature, to form a regular array pattern and a random array pattern.

Owner:SK HYNIX INC

Method of forming trenches with targeted critical dimensions

InactiveCN102280403AImprove critical dimension uniformityImprove yield rateSolid-state devicesSemiconductor/solid-state device manufacturingLow-k dielectricEngineering

The invention discloses a method for forming a trench with a target critical dimension, comprising: providing a front-end device structure, an intermetallic dielectric layer having a trench is formed on the front-end device structure, and the intermetallic dielectric layer The material is an oxide with a low dielectric constant; and a reaction gas containing a reducing gas is introduced to adjust the actual critical dimension of the trench to the target critical dimension. According to the method of the invention, the critical dimension uniformity of different wafers or different batches of grooves can be effectively improved, and the yield rate can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

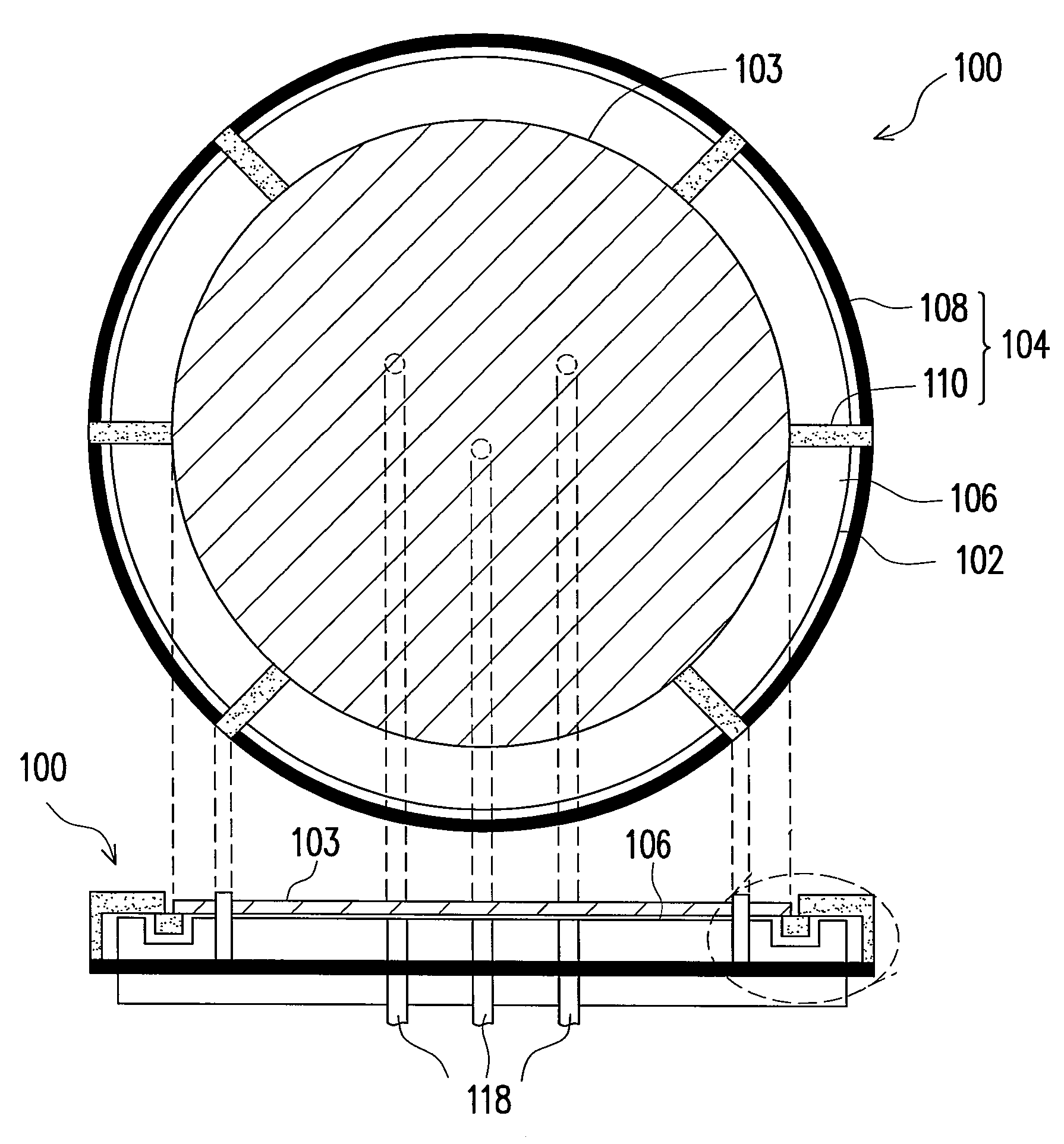

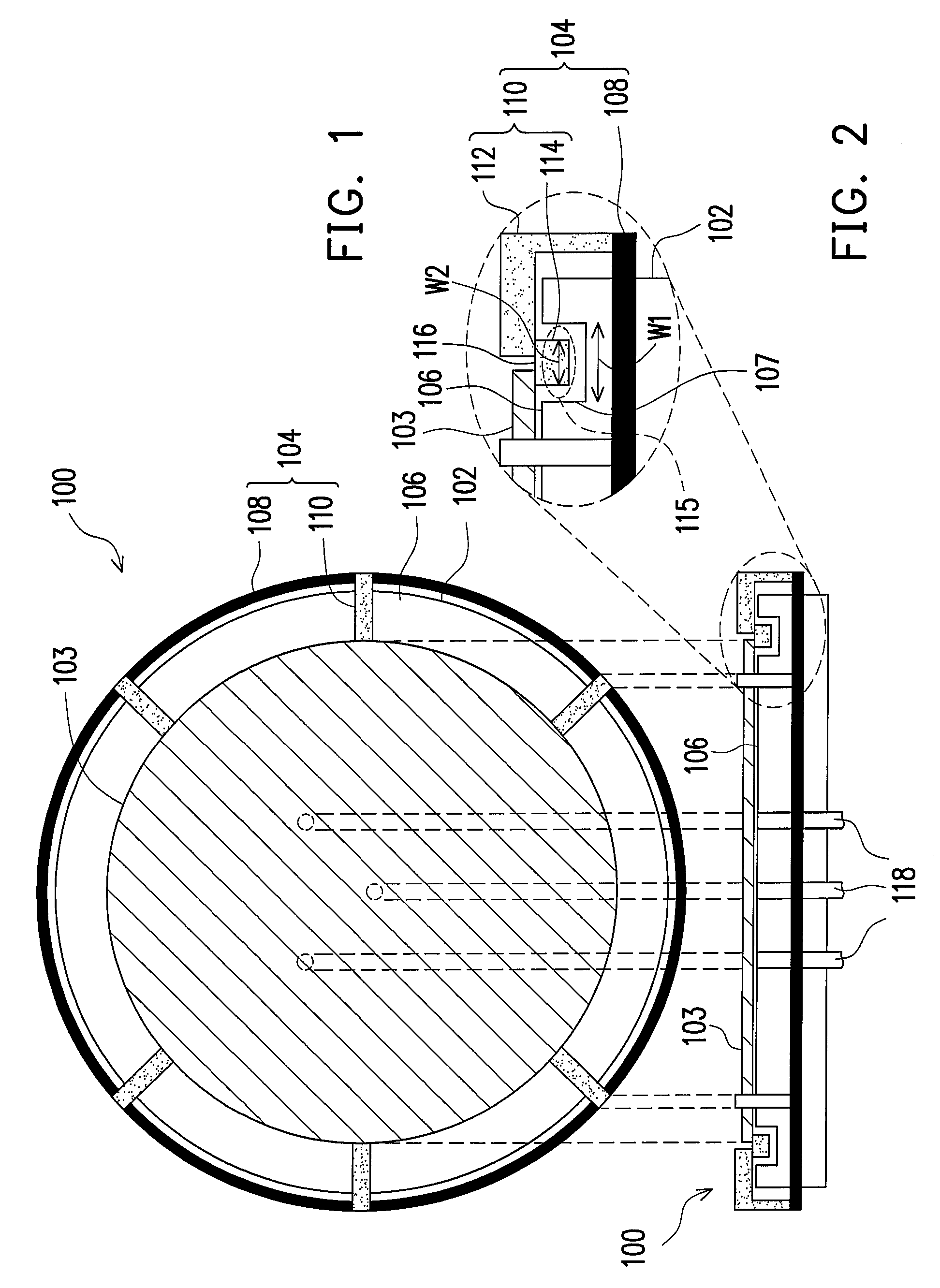

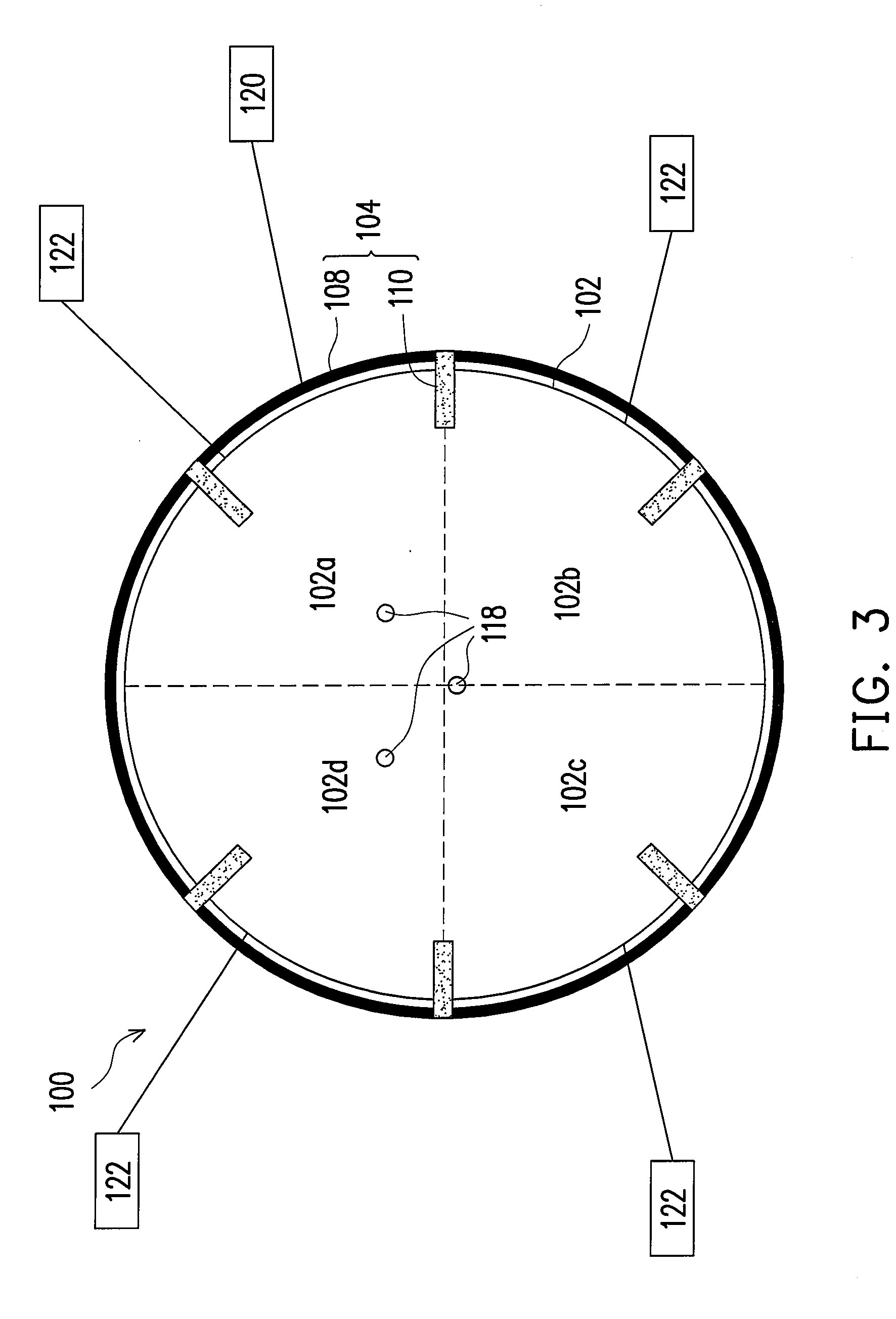

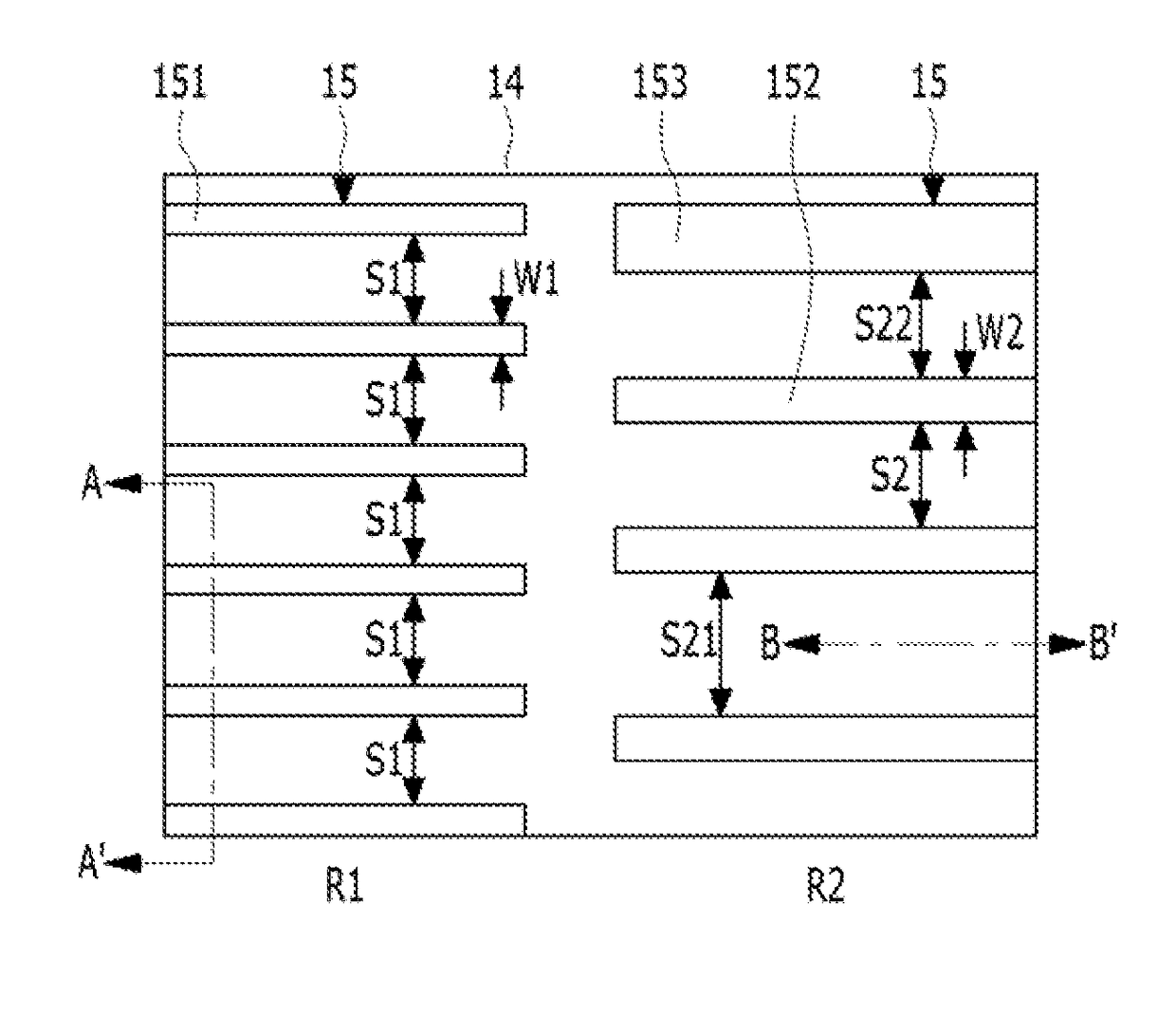

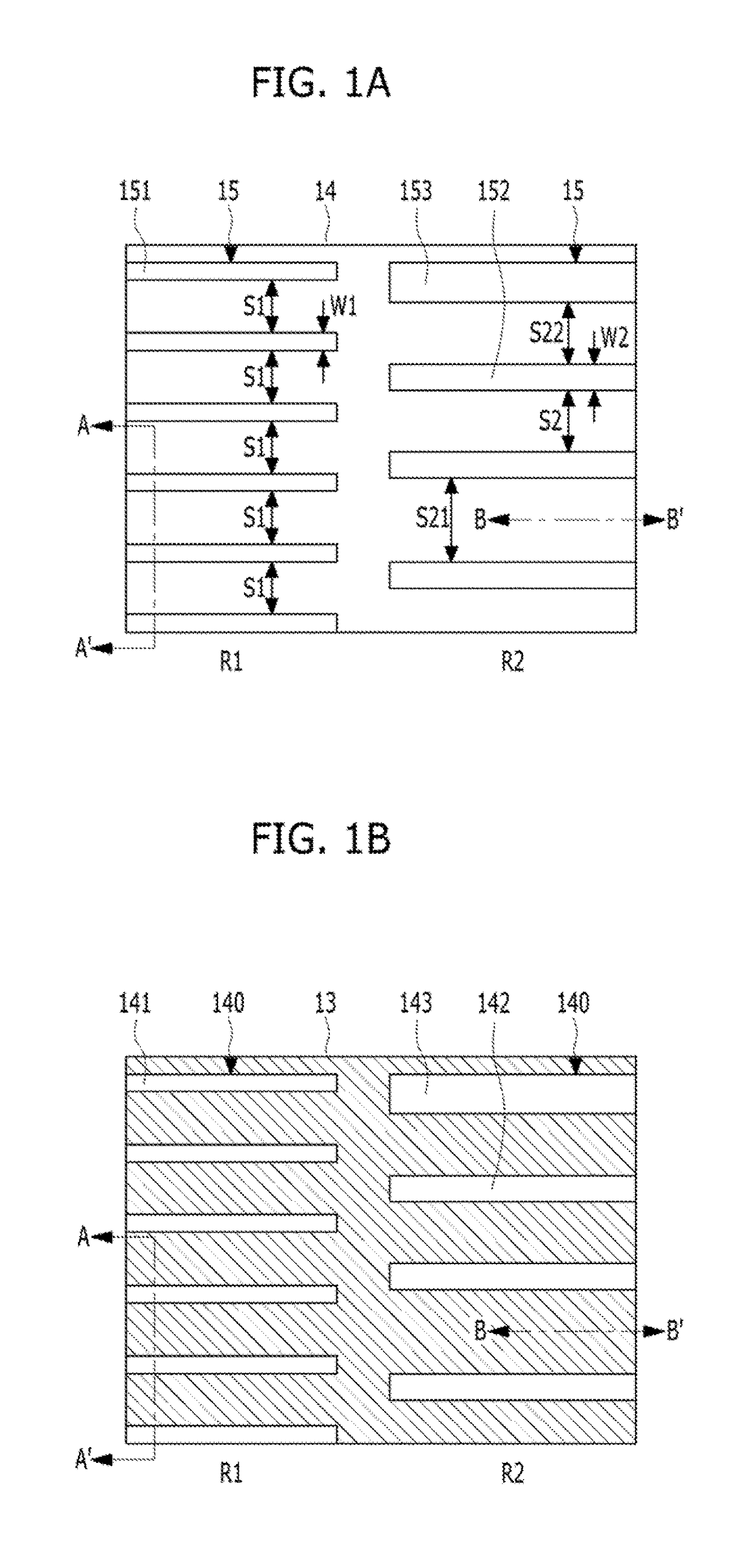

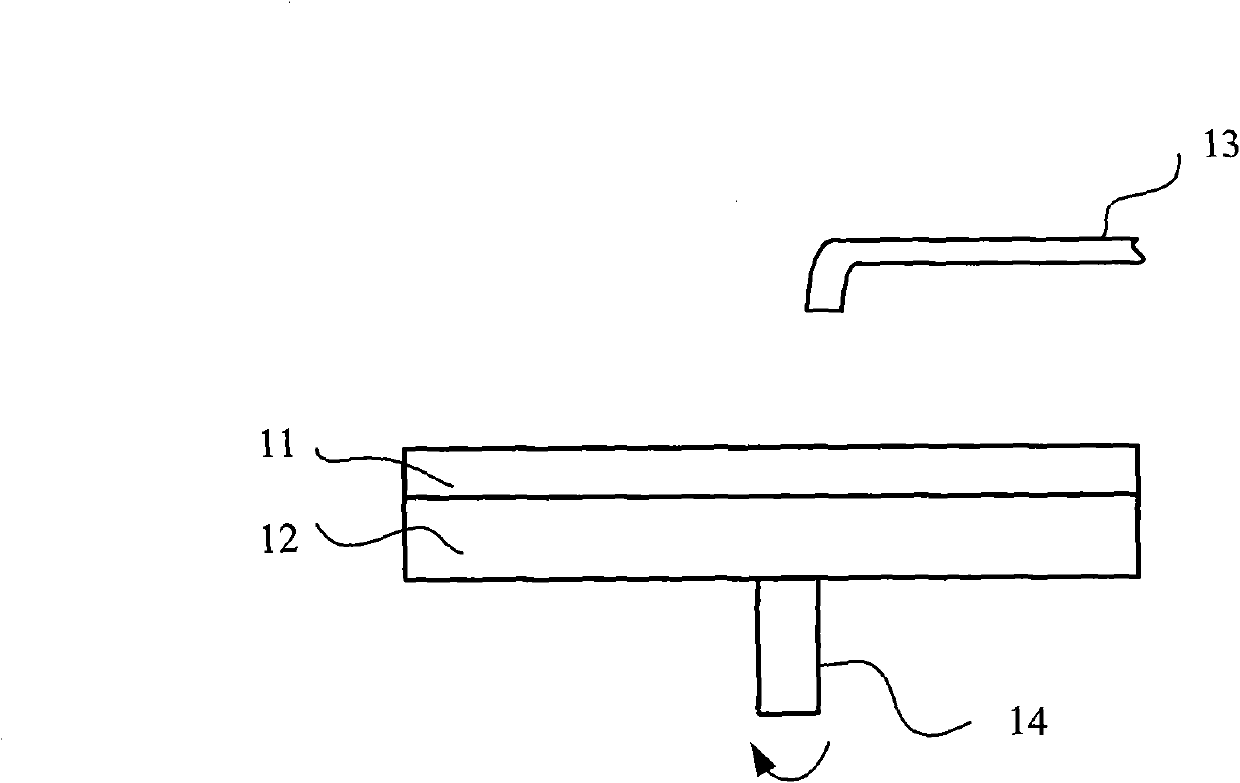

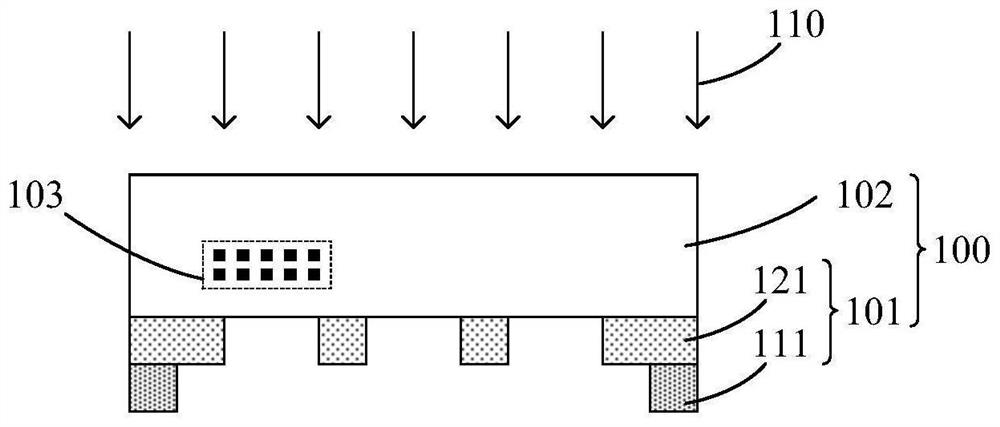

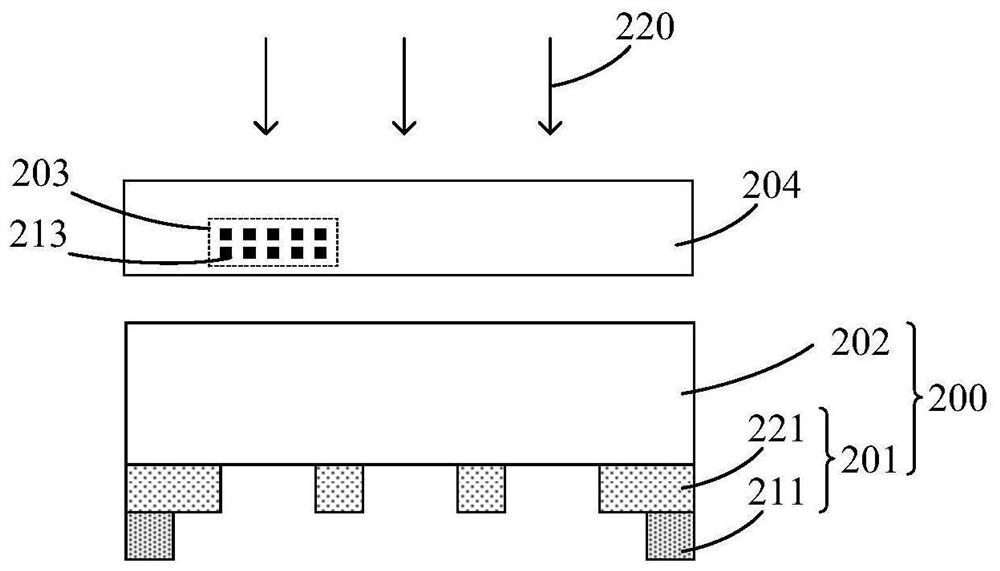

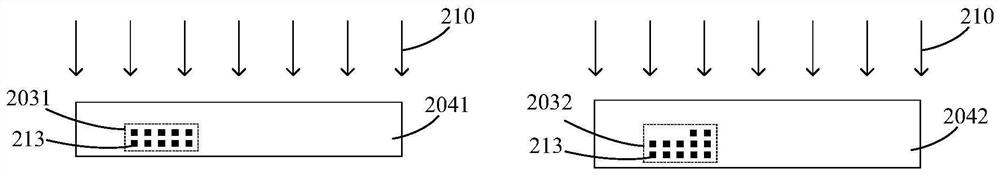

Baking apparatus, baking mehod and method of reducing gap width

ActiveUS20090286407A1Uniform temperature distributionImprove performancePhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringGap width

A baking apparatus including a hot plate and a substrate rotation member is provided. The hot plate has a heating surface. The substrate rotation member includes a rotation ring and a plurality of support arms. The rotation ring is configured to surround the hot plate. The support arms are disposed over the heating surface of the hot plate. Each of the support arms includes a connection part and a support part, wherein the connection part is configured to connect the rotation ring and the support part, and a supporting surface of the support part for supporting the substrate is higher than the heating surface of the hot plate.

Owner:MACRONIX INT CO LTD

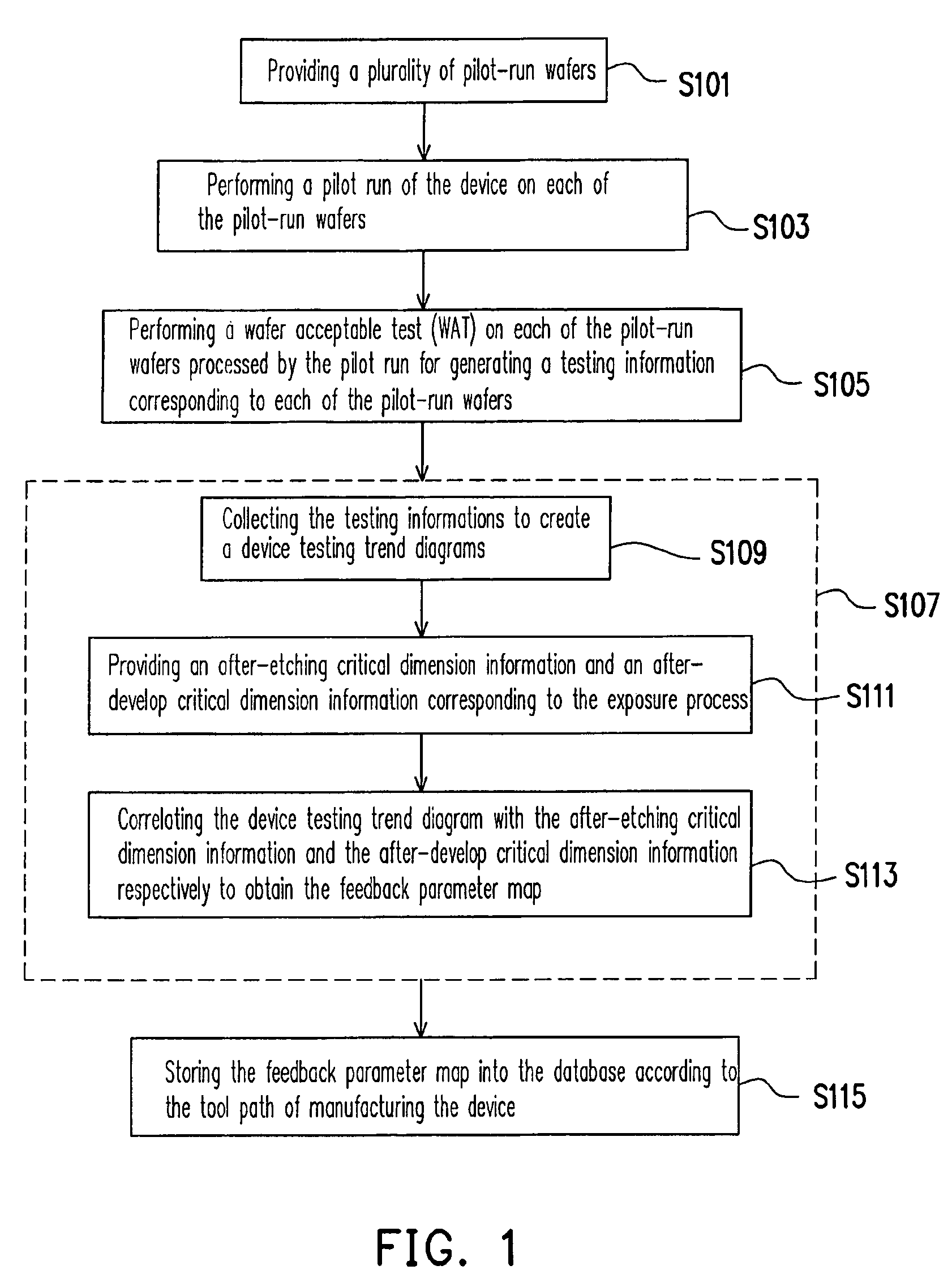

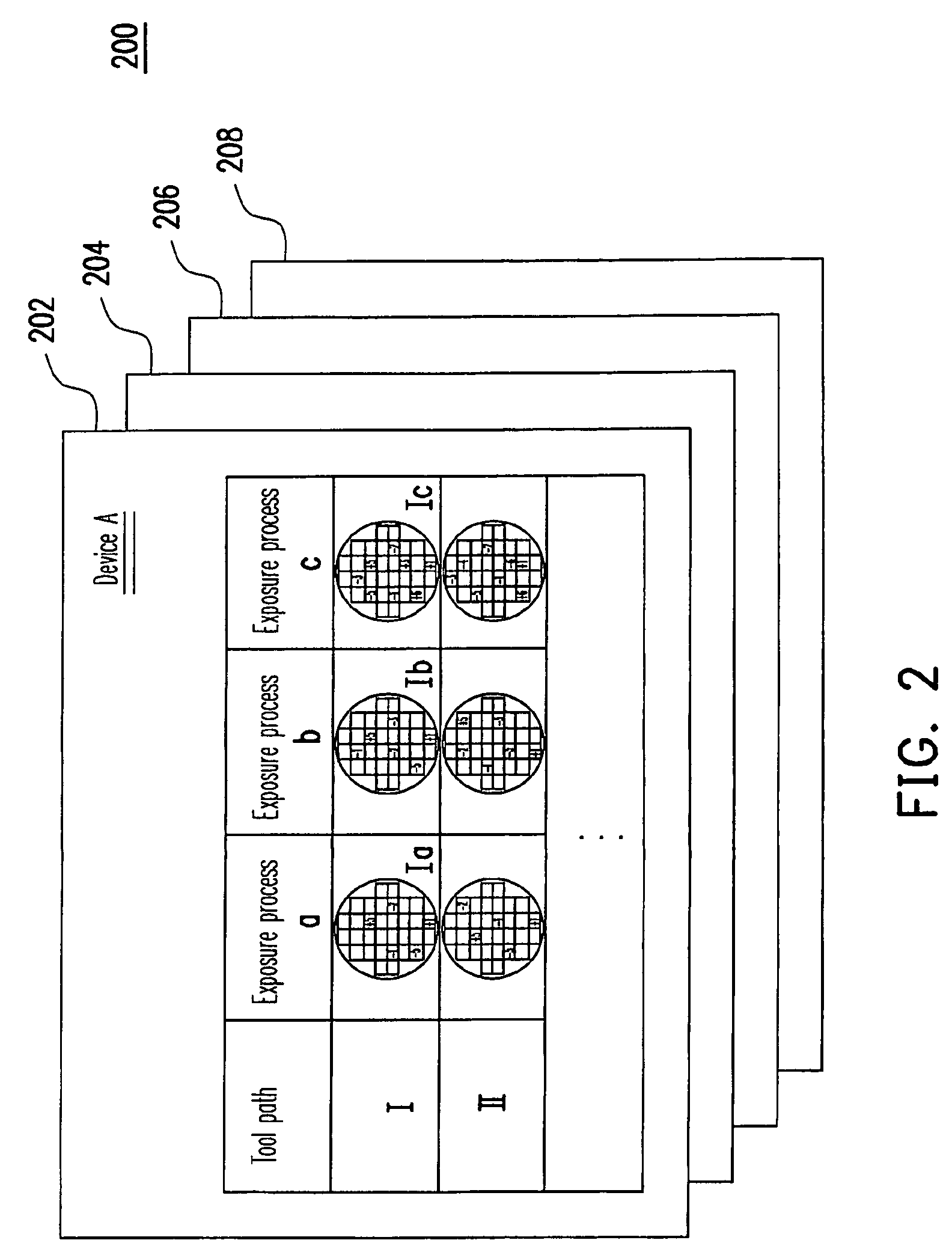

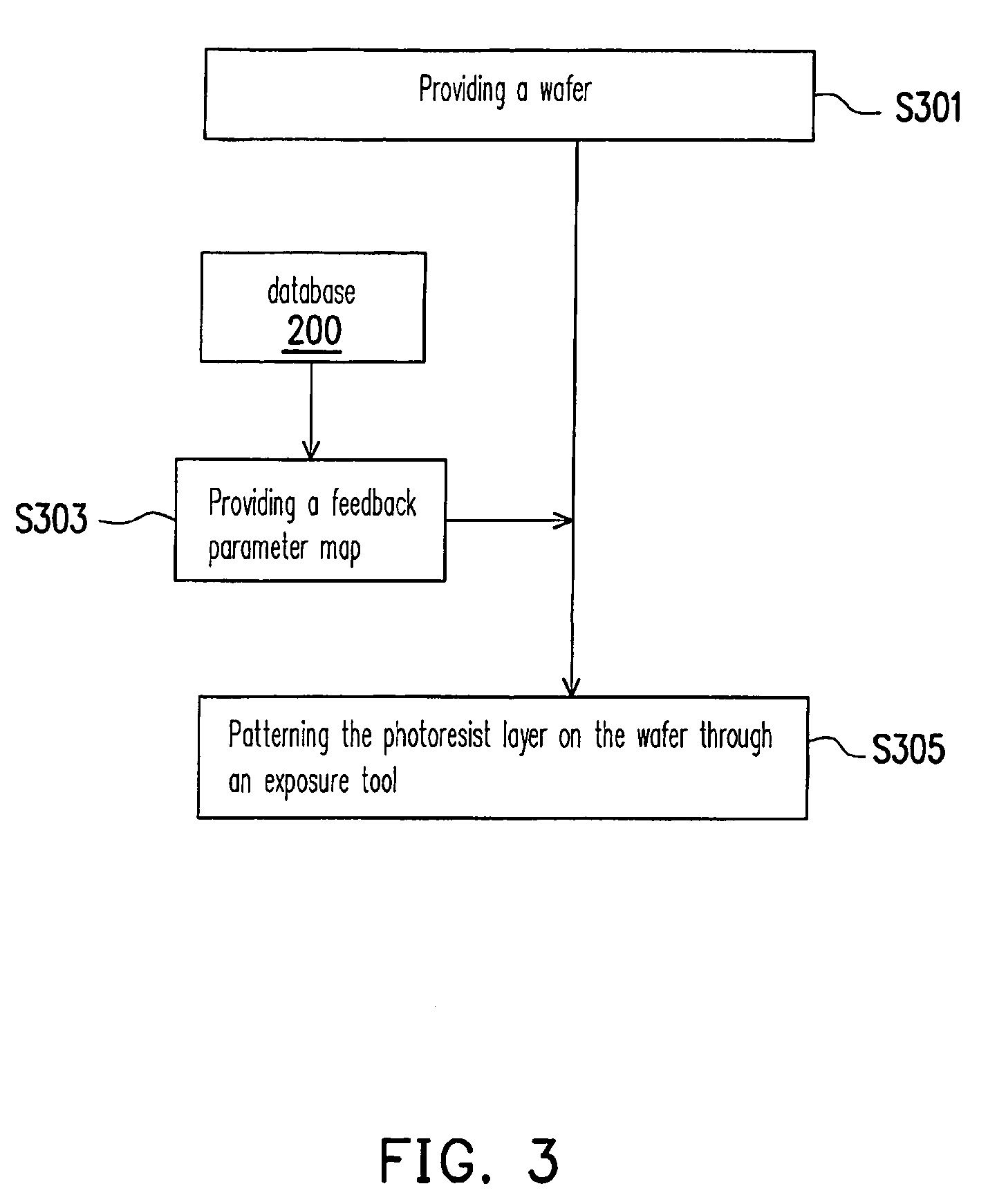

Exposure method

ActiveUS7871745B2Improve critical dimension uniformityEasy alignmentPhotomechanical apparatusCharacter and pattern recognitionEngineeringPhotoresist

The invention provides an exposure method for manufacturing a device. The method includes providing a wafer having several exposure regions with a photoresist layer covering thereon. A feedback parameter map with several exposure-region feedback parameter sets respectively corresponds to the exposure regions of the wafer. At least one of the exposure-region feedback parameter sets is different from the rest of the exposure-region feedback parameter sets. According to the feedback parameter map, an exposure process is sequentially performed on each of the exposure regions of the wafer through an exposure tool to pattern the photoresist layer on the wafer. While the exposure tool performs the exposure process on each of the exposure regions, an exposure process parameter set of the exposure tool is adjusted based on the exposure-region feedback parameter sets corresponding to the exposure region in the feedback parameter map.

Owner:UNITED MICROELECTRONICS CORP

Mask for improving lithography performance by using multi-transmittance photomask

ActiveUS7008735B2Improve performanceImprove critical dimension uniformityOriginals for photomechanical treatmentPhotographic processesPhase shiftedLithographic artist

Materials and methods for fabricating multi-transmittance halftone phase shift masks (HTPSM) are disclosed. The masks include patterns having regions of different transmittance for the purpose of reducing one or more of line edge shortening, iso-to-dense bias, and edge-to-dense bias. The masks employ at least one halftone material in forming the patterns that have different transmittances. Regions of denser or longer lines are constructed to have a lower transmittance than regions of isolated lines. The patterns may include a single halftone material of different thicknesses for different regions or may include two halftone materials applied singly and doubly to different regions.

Owner:MACRONIX INT CO LTD

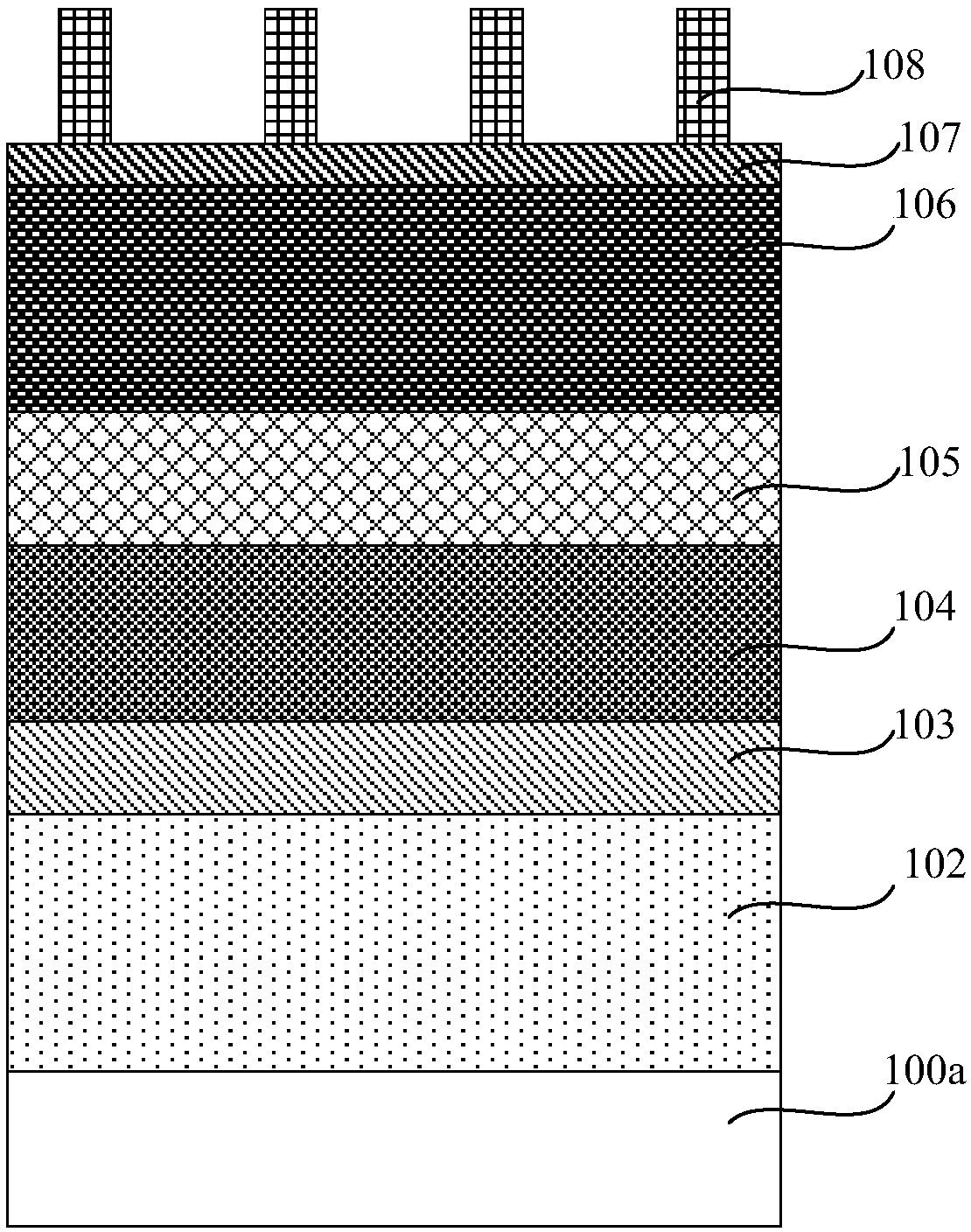

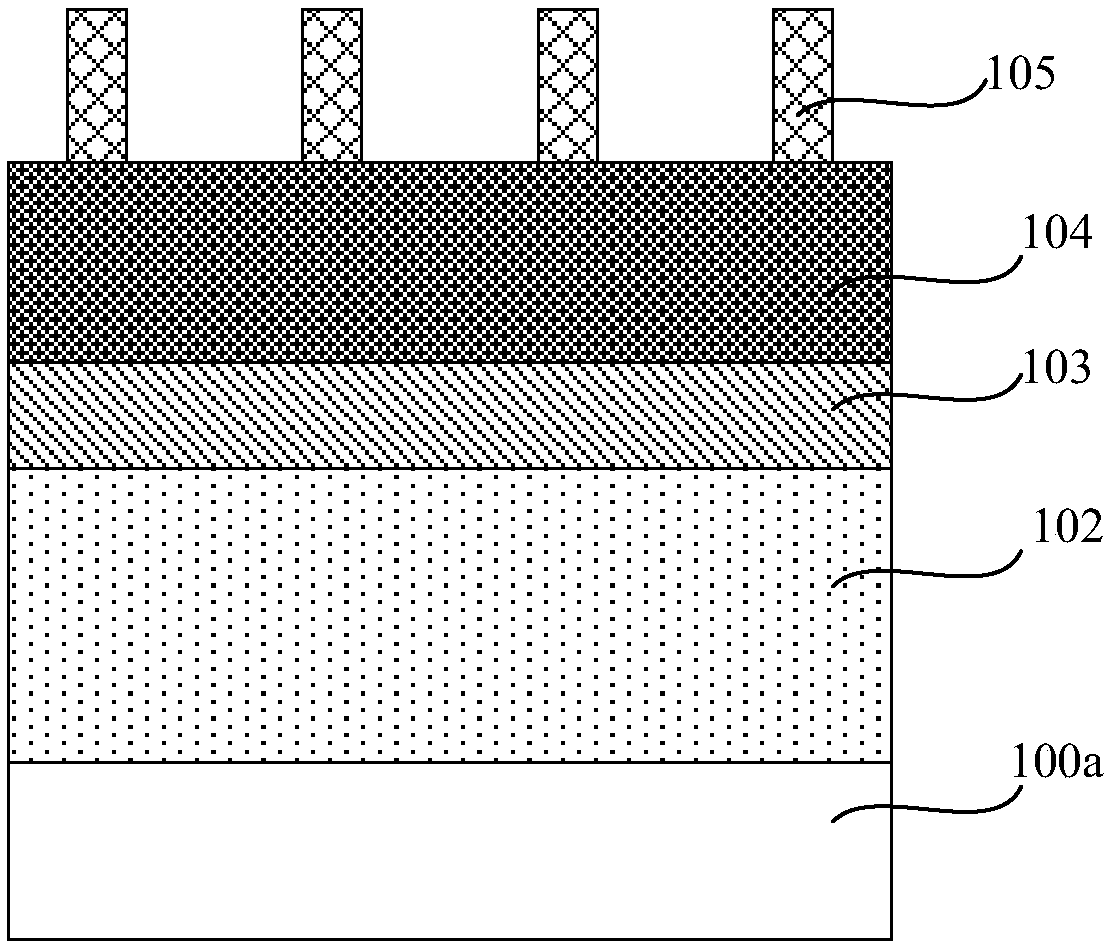

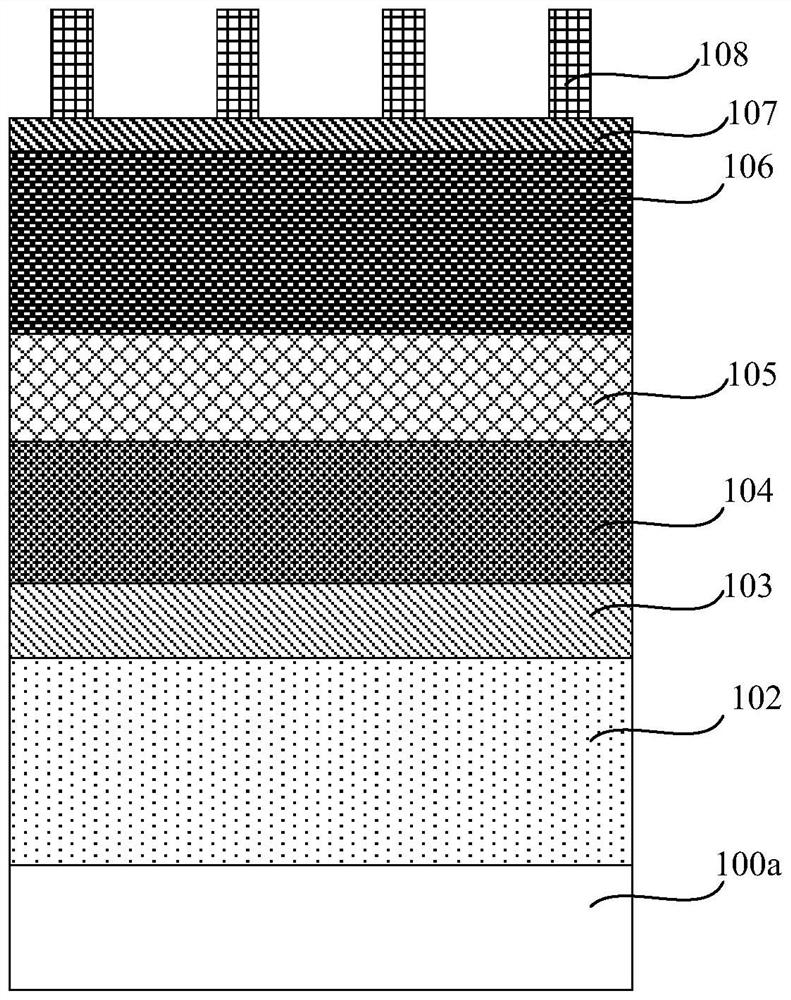

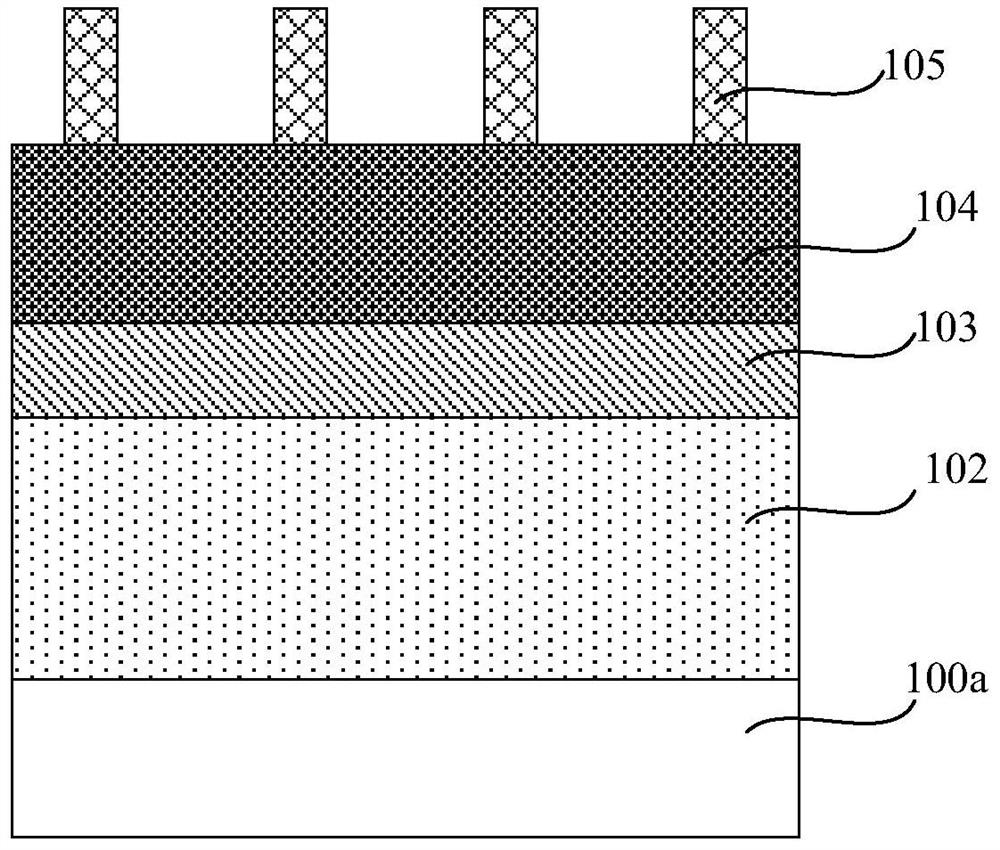

Method for manufacturing self-aligned double pattern and method for manufacturing semiconductor device

ActiveCN110571139AImprove critical dimension uniformityImprove uniformitySemiconductor/solid-state device manufacturingEngineeringProtection layer

The invention provides a method for manufacturing a self-aligned double pattern and a method for manufacturing a semiconductor device. In consideration of the negative impact of a process of forming atarget etching layer on a semiconductor substrate, data such as the thickness of the formed target etching layer is fed back to a subsequent process of etching the target etching layer, so as to control the etching effect of the target etching layer more accurately, thereby improving the uniformity of the key dimensions of the pattern obtained on the target etching layer and improving the performance and the yield of the manufactured semiconductor device. Further, in consideration of the negative impact of a photolithography process, a photolithography process condition is adjusted in time according to the key dimensions after photolithography and the thicknesses of the etch protection layer, an cover layer and the like, thereby improving the shape of a finally formed core mold, and further improving the uniformity of the key dimensions of the patterns obtained on the target etching layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

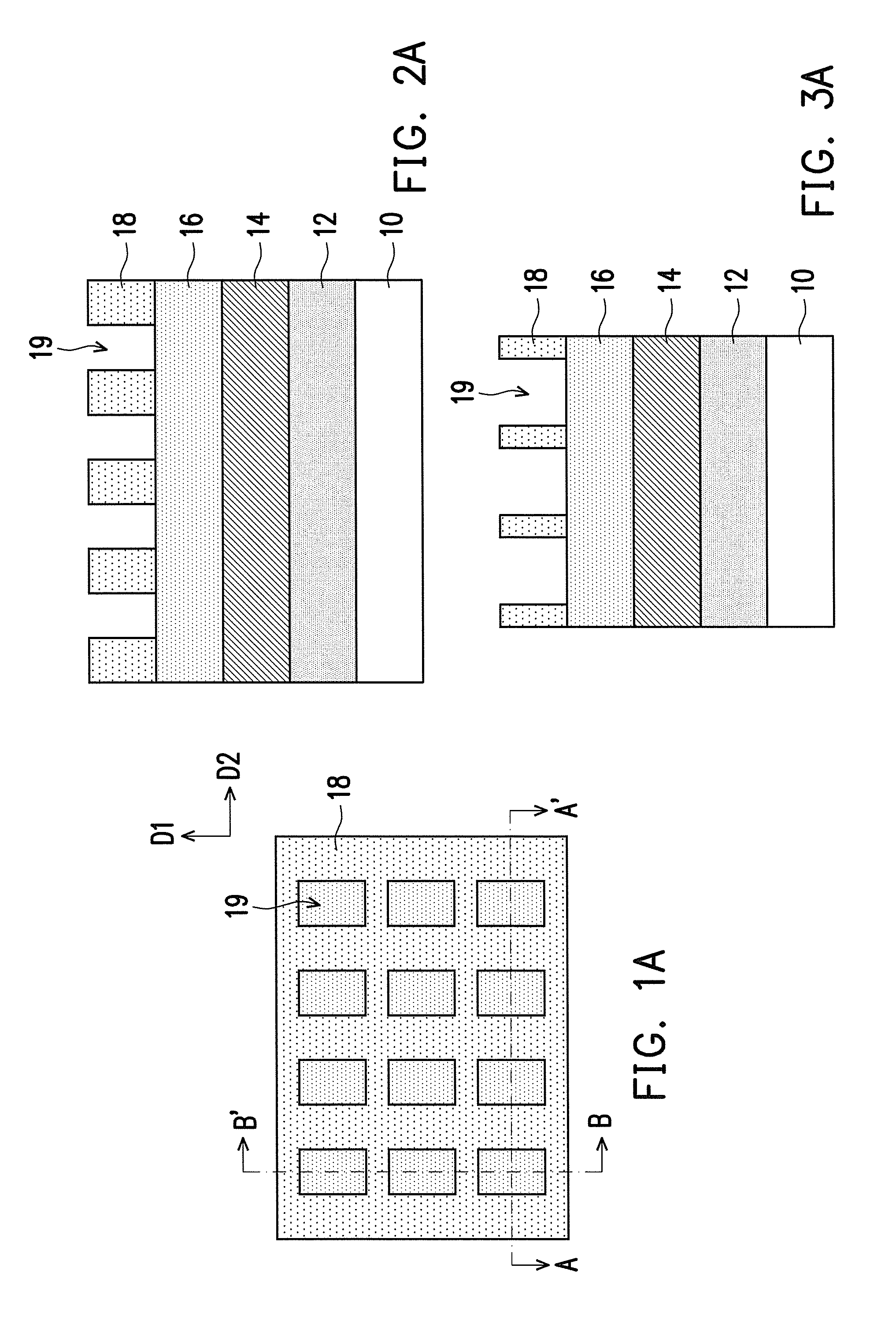

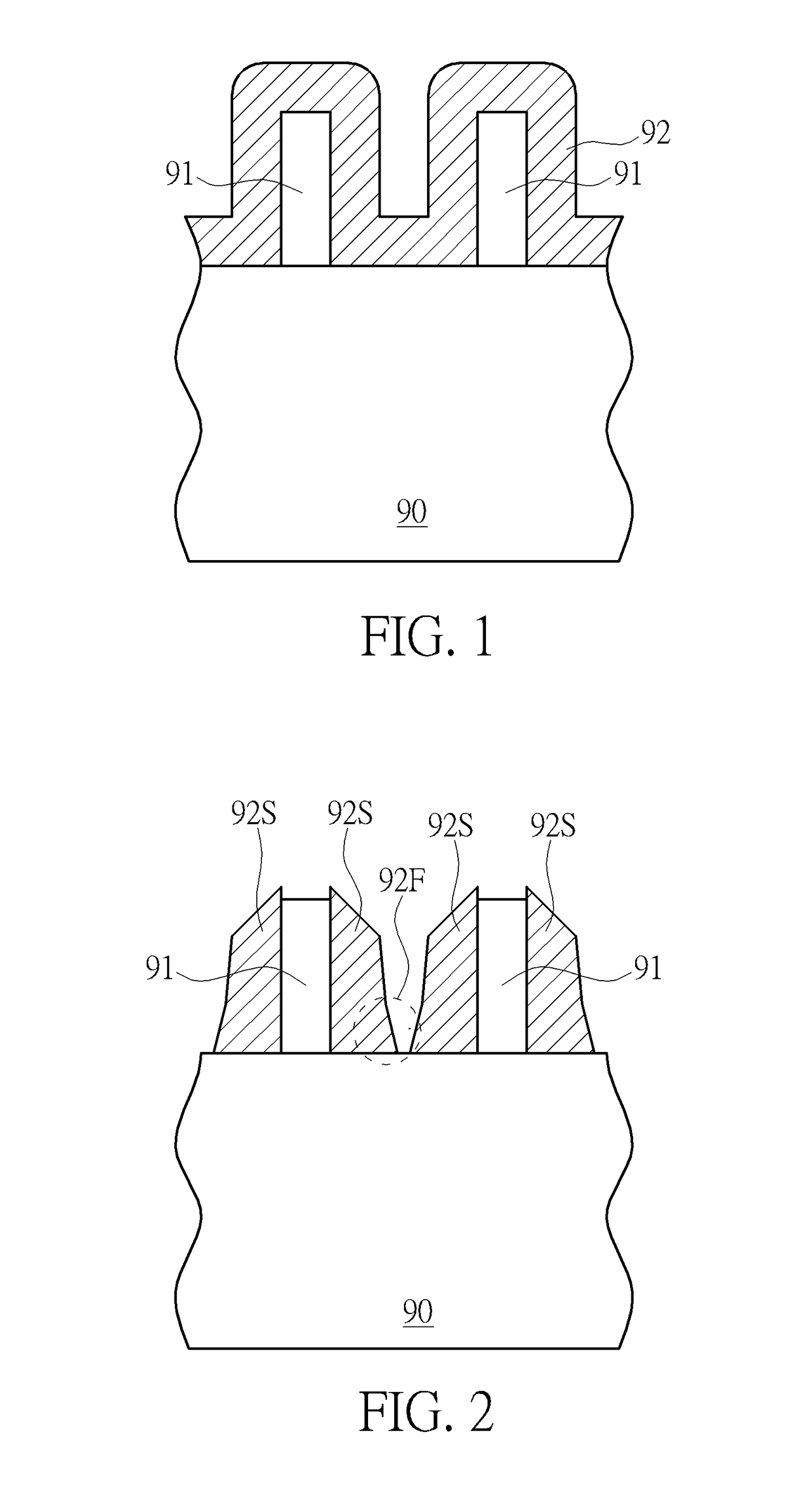

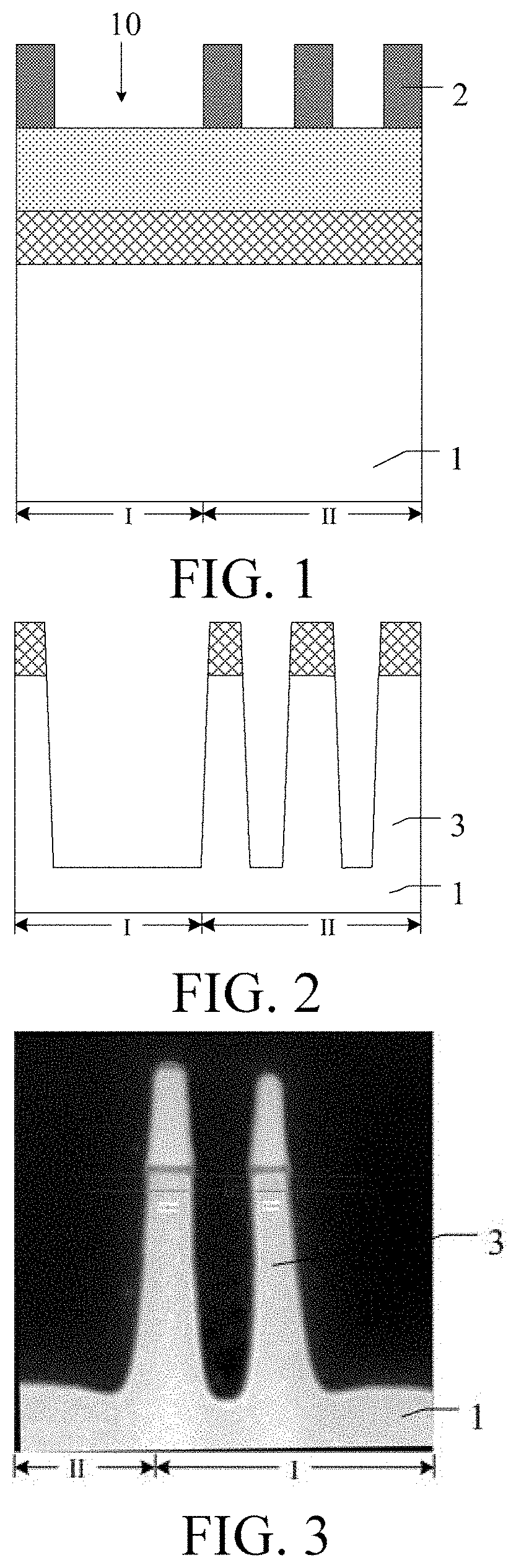

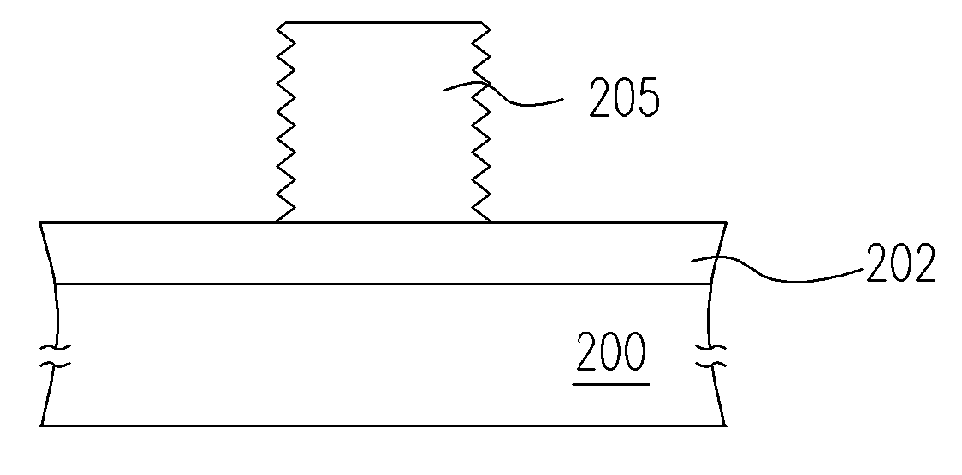

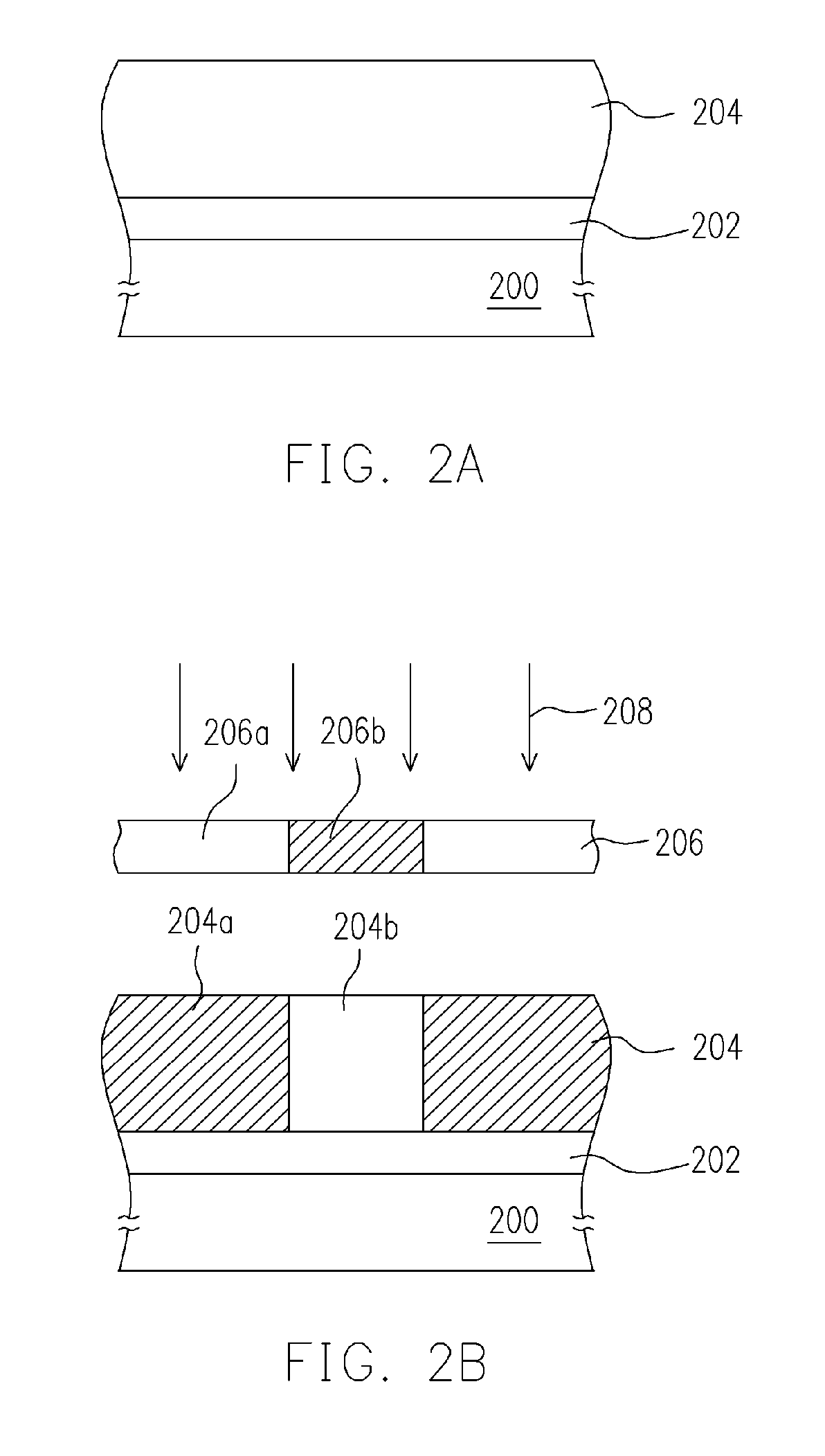

Patterning method and semiconductor structure

ActiveUS20160086809A1Improve critical dimension uniformityOvercoming misalignmentSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A patterning method is provided. A substrate including a material layer thereon is provided. A patterned hard mask layer, having a plurality of first holes, is formed on the material layer. Afterward, a mask layer, including a plurality of line pattern masks extending in a direction and dividing each first hole into a second hole and a third hole, is formed. The material layer is patterned using the patterned hard mask layer and the mask layer as masks to form a patterned material layer having a plurality of fourth and fifth holes. Furthermore, a semiconductor structure is provided.

Owner:MACRONIX INT CO LTD

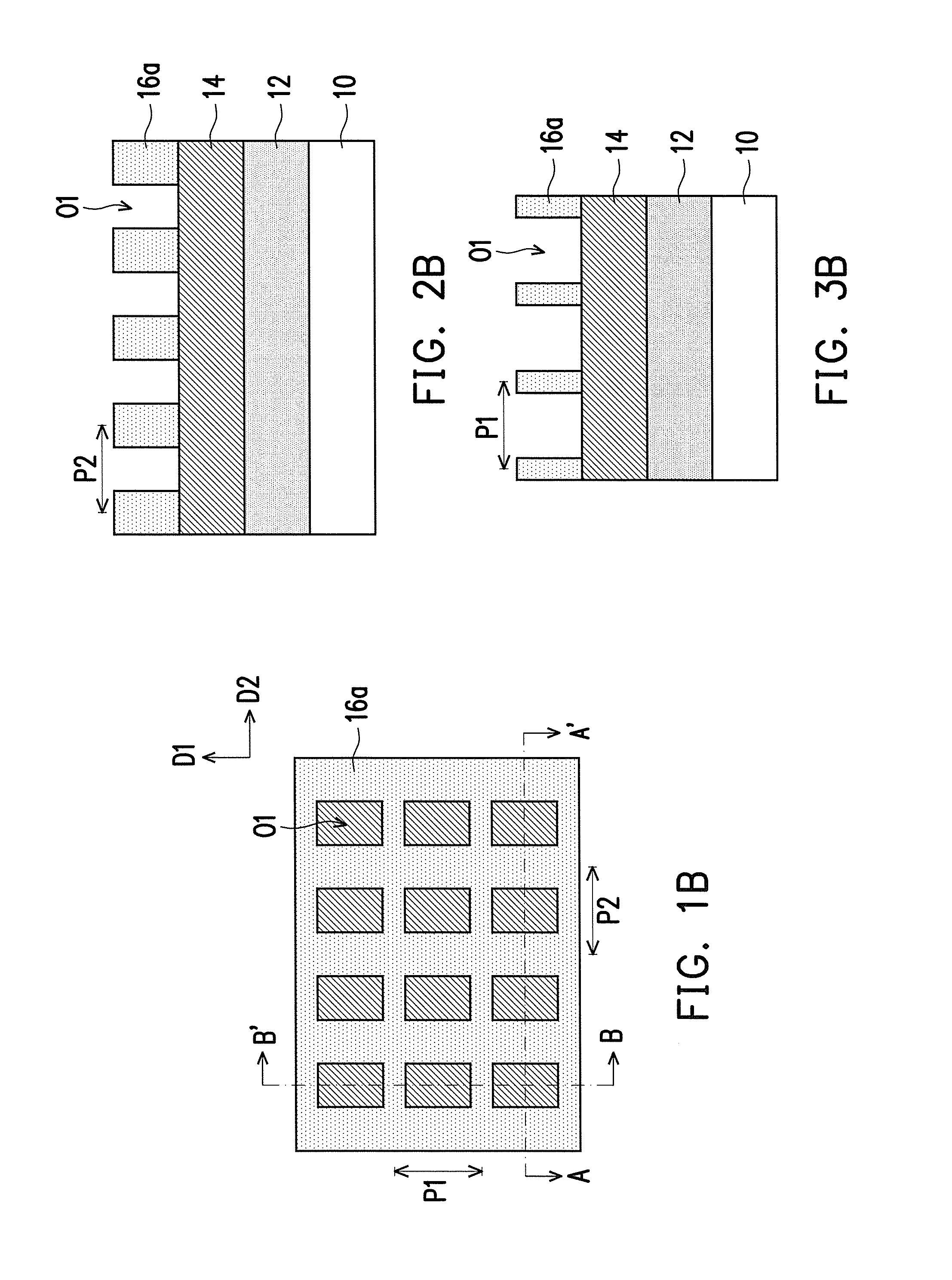

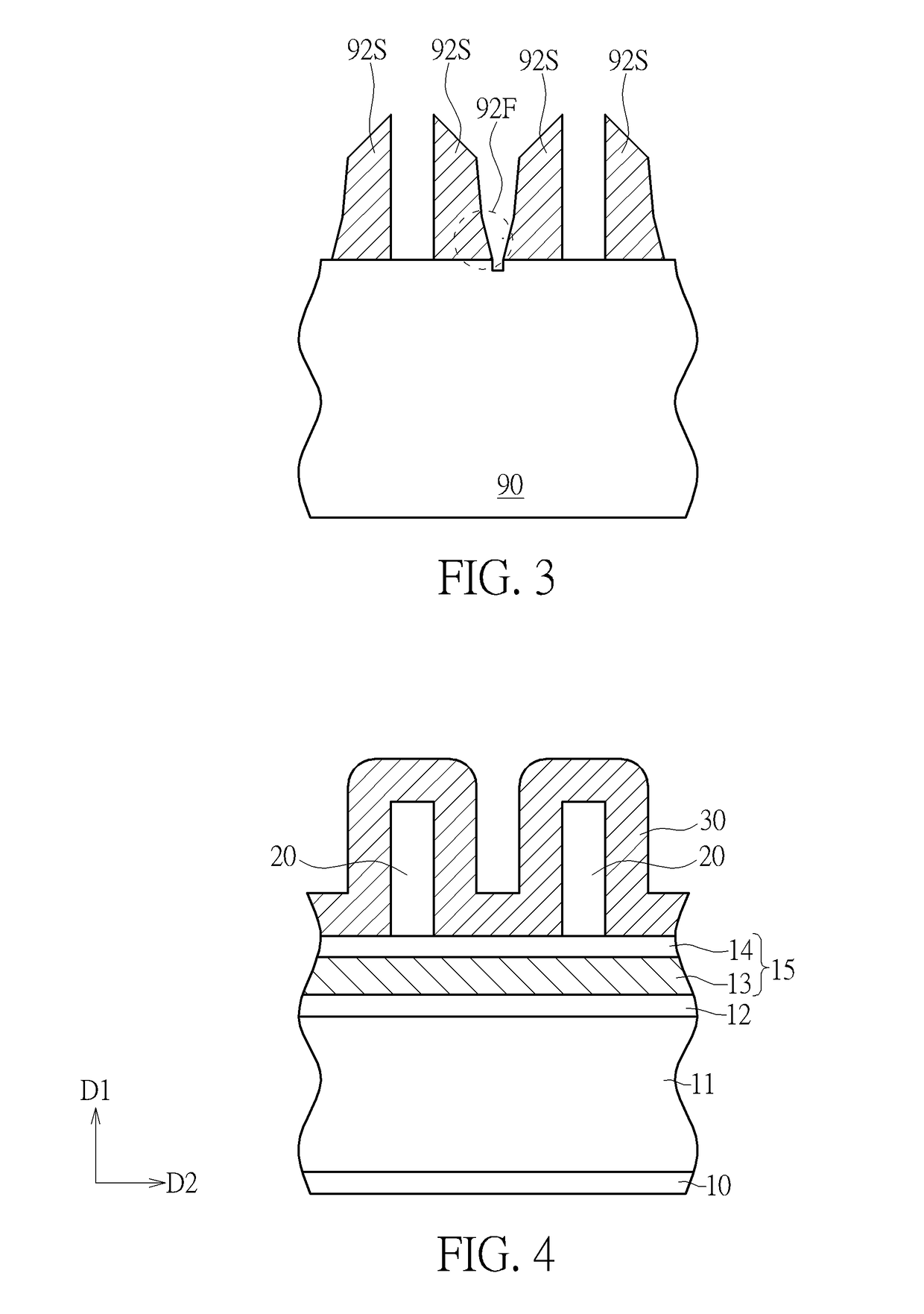

Method of forming patterned mask layer

ActiveUS9779942B1Improve critical dimensionsImprove critical dimension uniformitySemiconductor/solid-state device manufacturingEngineeringMask layer

A method of forming a patterned mask layer includes the following steps. A plurality of support features is formed on a mask layer. A plurality of spacers is formed on side walls of the support features. A patterned protection layer is formed on the support features and top surfaces of the spacers. At least a part of side surfaces of the spacers are not covered by the patterned protection layer, and the patterned protection layer is formed in a process environment containing methane (CH4). A trimming process is then performed to remove a part of each of the spacers. Tapered parts of the spacers may be removed by the trimming process before the step of etching the mask layer with the spacers as a mask, and the critical dimension uniformity of the patterned mask layer may be improved accordingly.

Owner:UNITED MICROELECTRONICS CORP

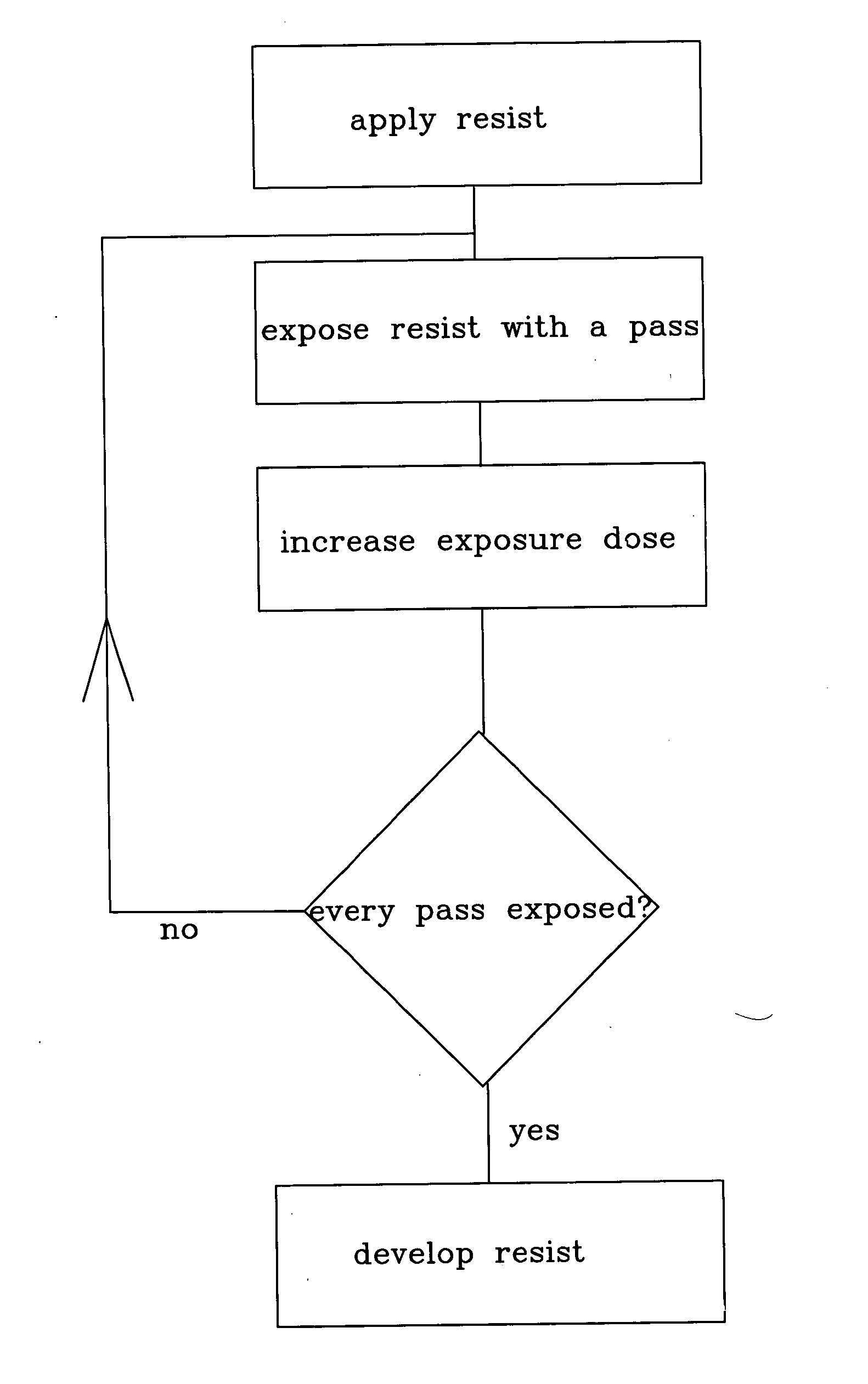

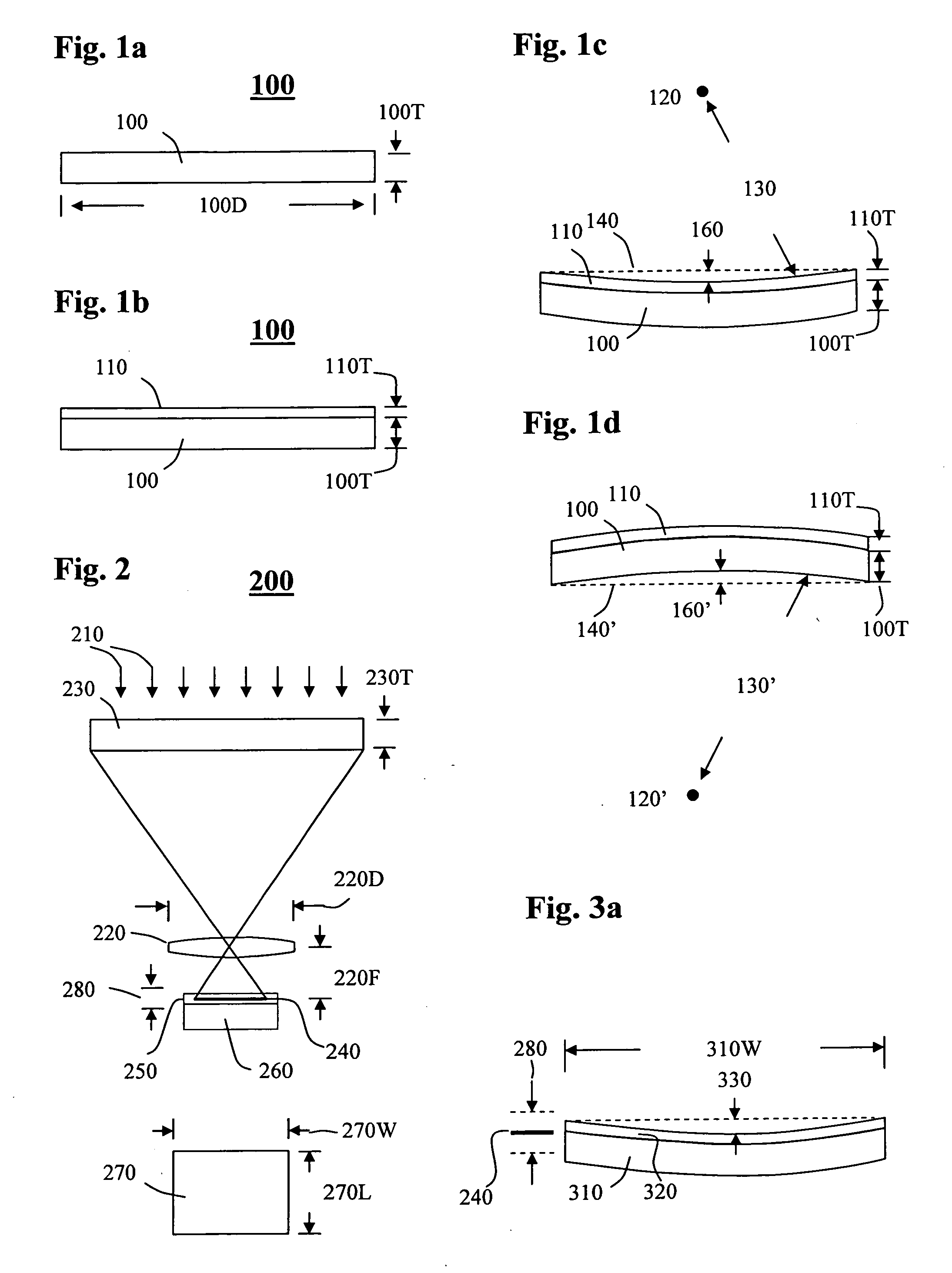

Method to pattern a substrate

ActiveUS20050032002A1Precise critical dimensionPrecise DimensionsSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusLithographic artistElectromagnetic radiation

An aspect of the present invention includes a method of lithography to enhance uniformity of critical dimensions of features patterned onto a workpiece. Said workpiece is coated with a coating sensitive to electromagnetic radiation. An electromagnetic radiation source having an illumination intensity is provided. At least one object pixel of electromagnetic radiation is created. A predetermined pattern is exposed, by using said at least one object pixel, on at least a portion of said workpiece in a first exposure pass with a first dose to provide less than full exposure of said coating sensitive to electromagnetic radiation. Said exposing action is repeated at least until said portion of said coating sensitive to electromagnetic radiation is fully exposed, wherein said dose is increased for every following pass. Said fully exposed coating sensitive to electromagnetic radiation is developed.

Owner:MICRONIC LASER SYST AB

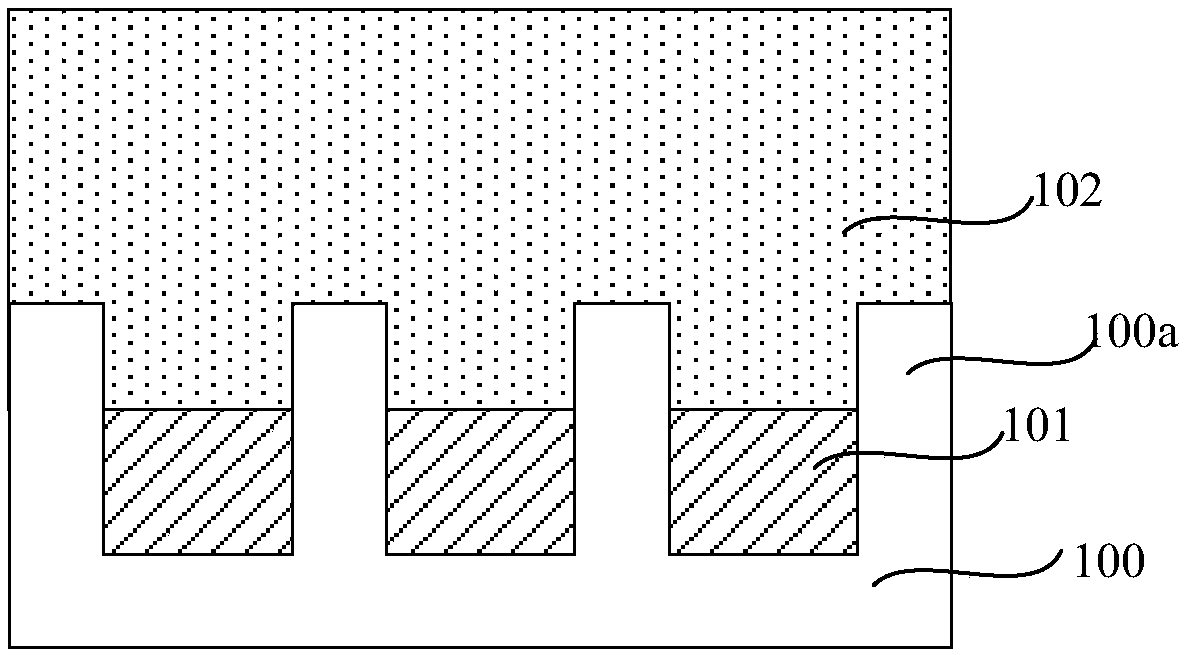

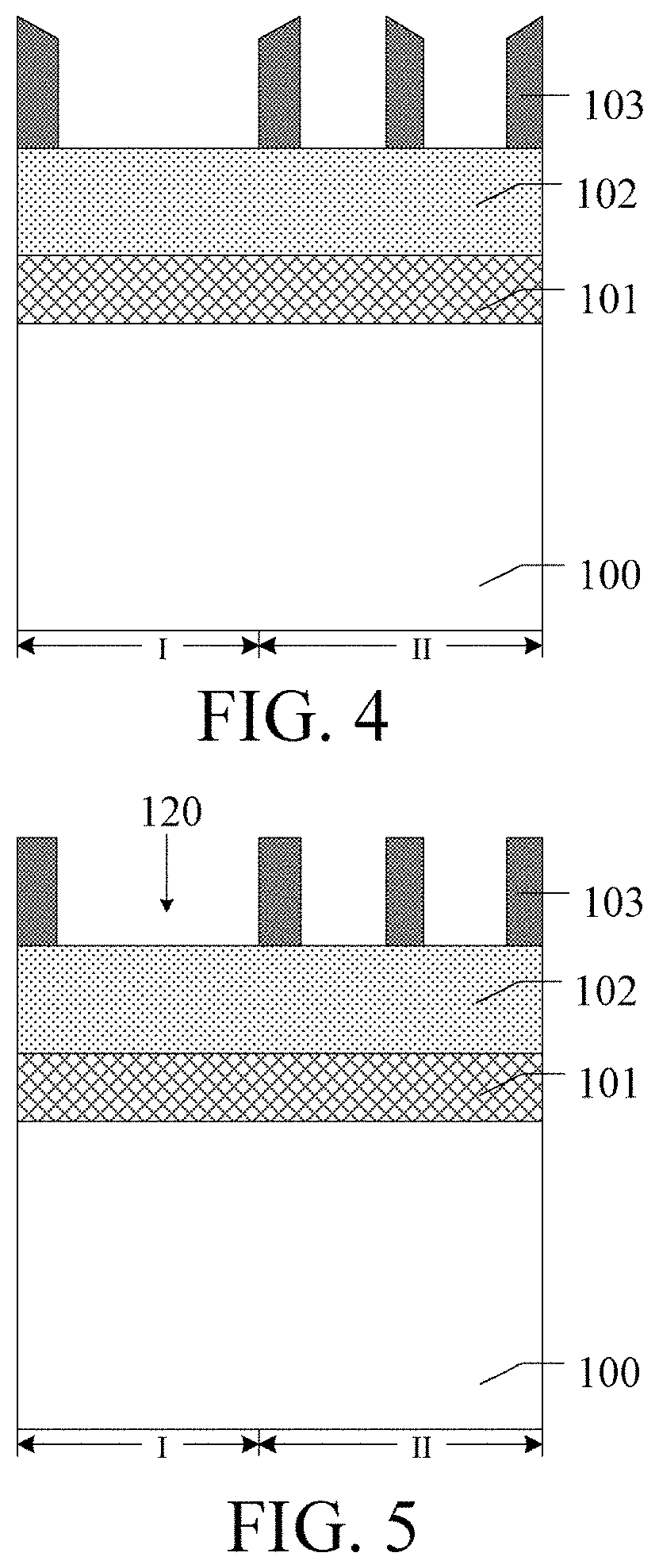

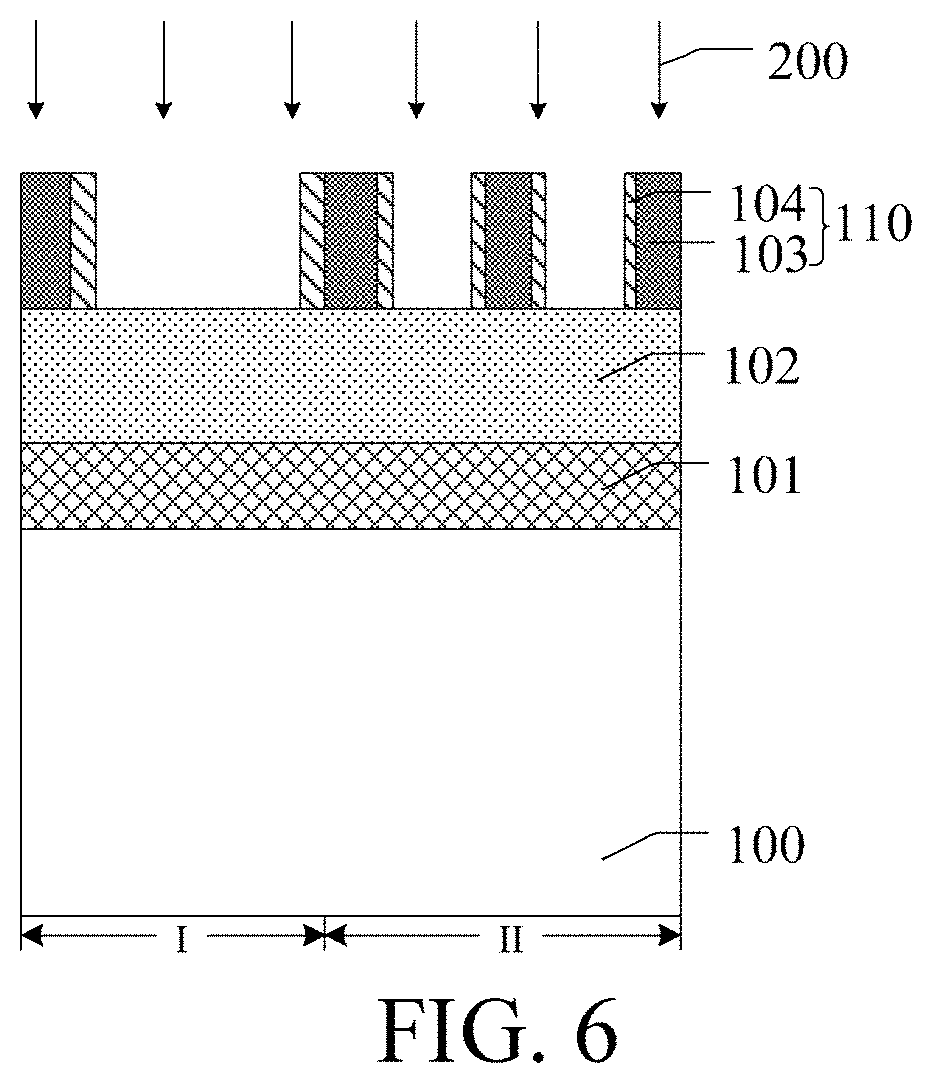

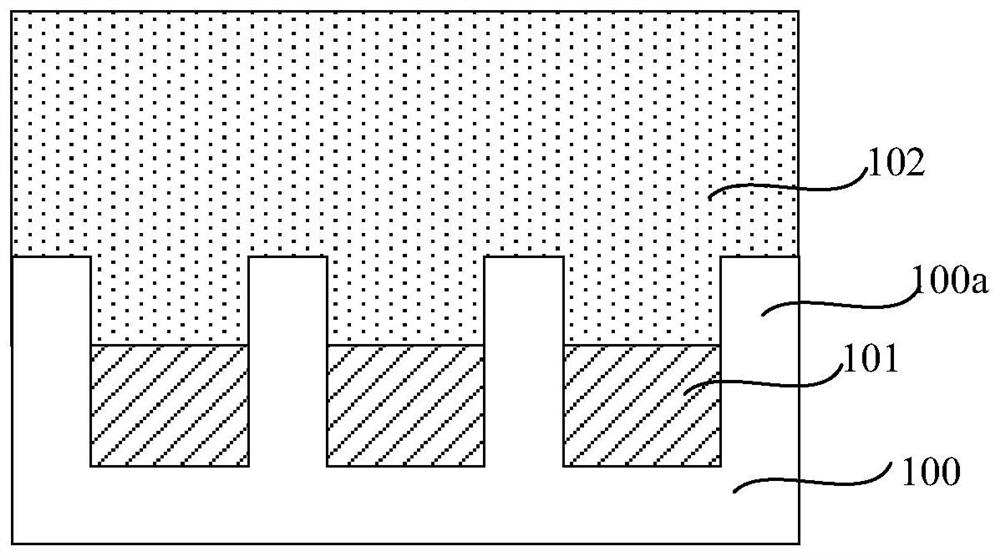

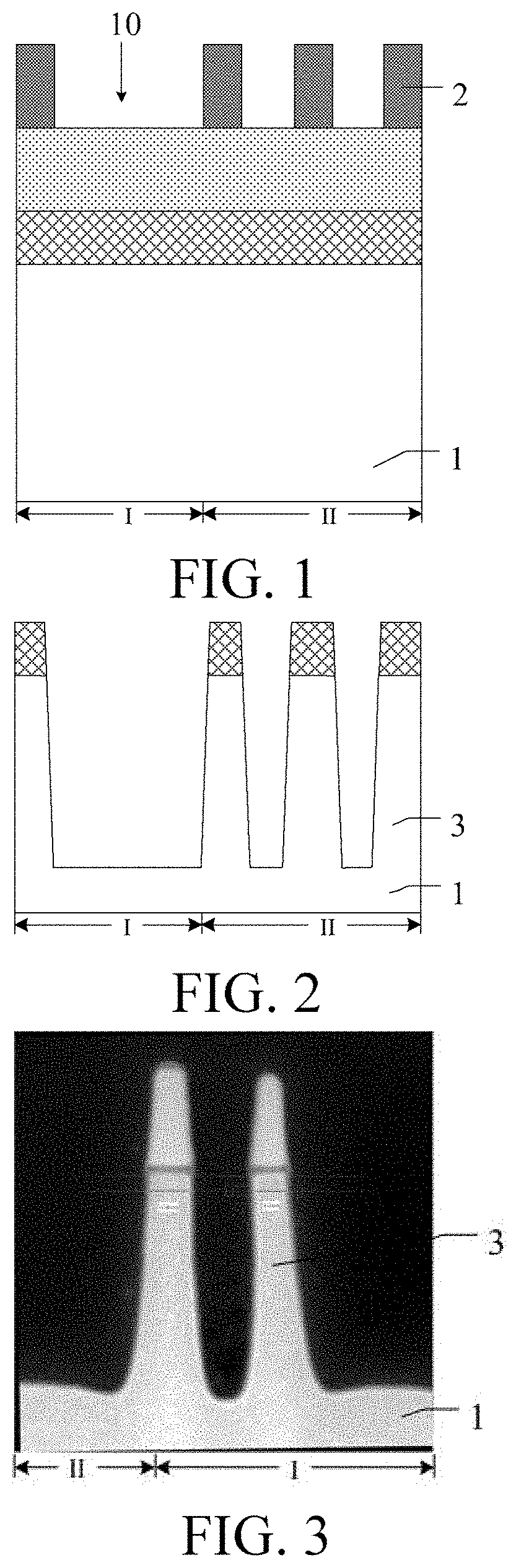

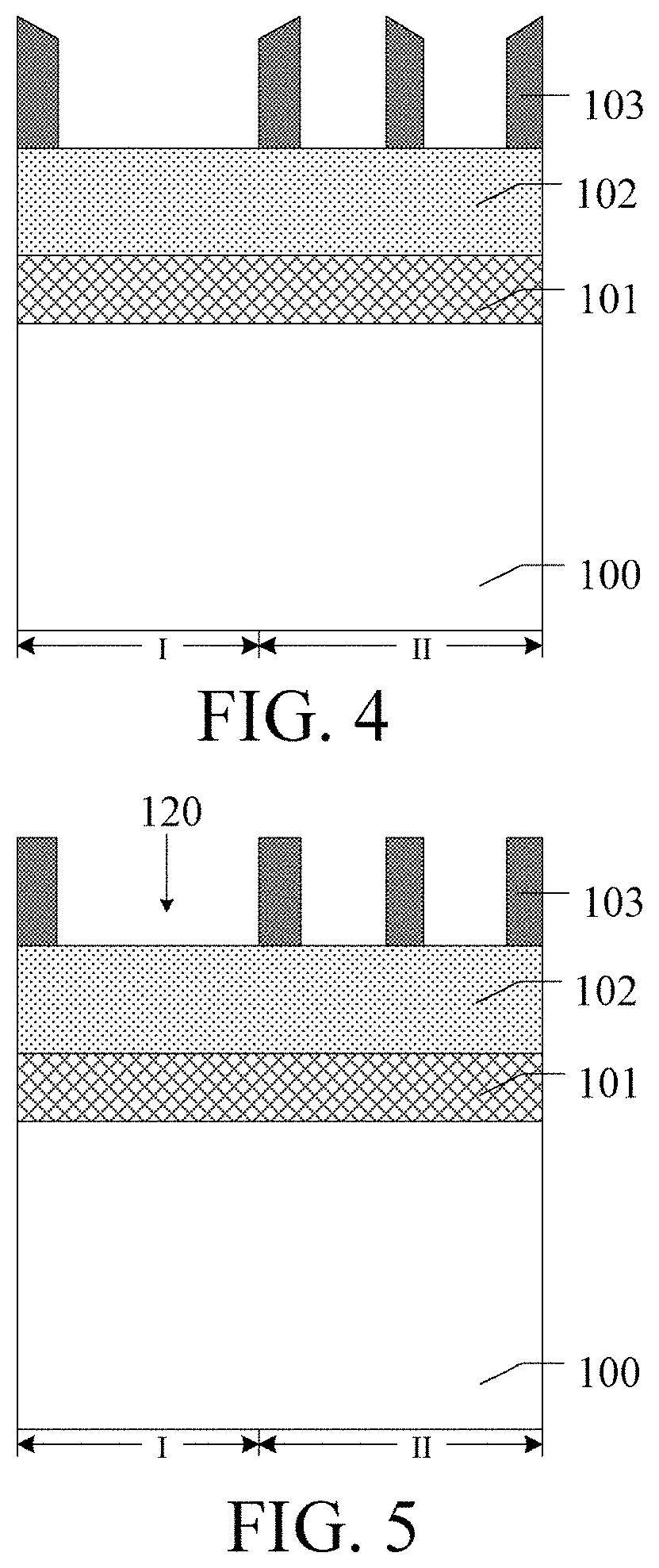

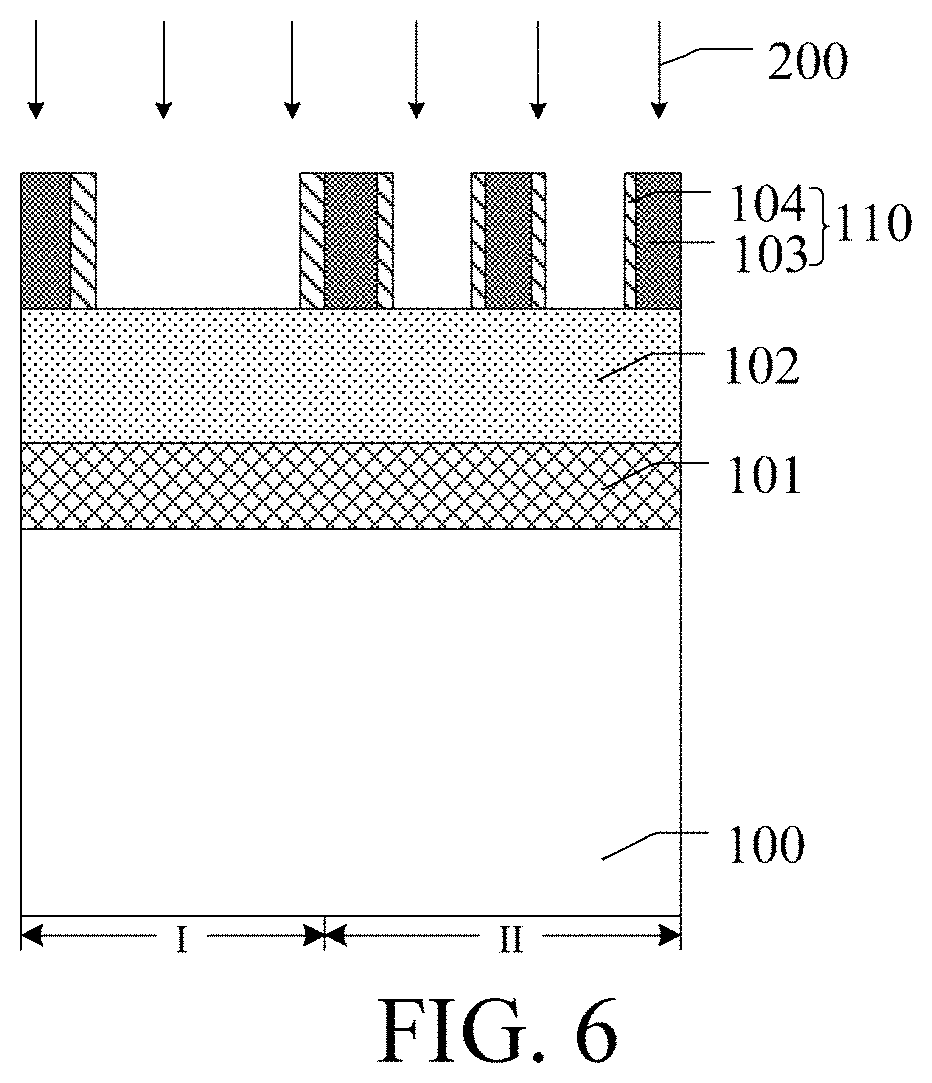

Semiconductor structure and formation method thereof

ActiveUS20200279748A1Reduce width sizeReduce opening widthSemiconductor/solid-state device manufacturingSemiconductor devicesCrystallographySemiconductor structure

A semiconductor structure and a formation method thereof are provided. The formation method includes: providing a base, the base including a pattern dense region and a pattern isolated region; forming a plurality of separate hard mask layers on the base, where adjacent hard mask layers and the base define an opening, and an opening of the pattern isolated region is wider than an opening of the pattern dense region; forming a trimming layer at least on a side wall of the opening of the pattern isolated region, the trimming layer and the hard mask layer constituting a mask structure layer; and etching, using the mask structure layer as a mask, a portion of the thickness of the base exposed by the opening to form a plurality of target pattern layers protruding from the remaining base. Embodiments and implementations of the present disclosure are advantageous for improving a critical dimension uniformity of a target pattern layer in each region.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

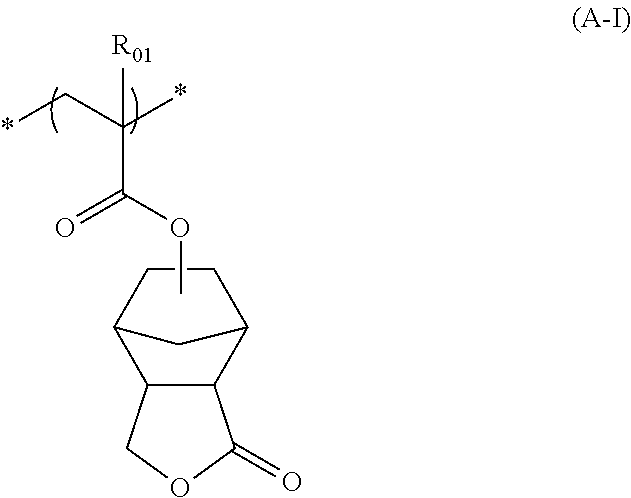

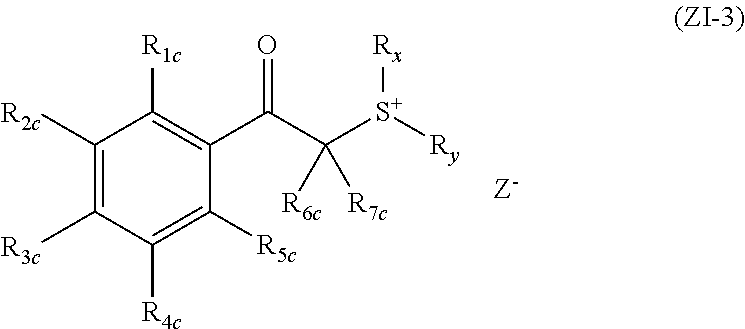

Actinic-ray-sensitive or radiation-sensitive resin composition, and resist film and pattern forming method using the same

InactiveUS20120164573A1Improve critical dimension uniformityImprove uniformityPhotosensitive materialsPhotomechanical exposure apparatusActinic RaysRadiation sensitivity

An actinic-ray-sensitive or radiation-sensitive resin composition capable of forming a pattern having excellent critical dimension uniformity (CDU) in the line width, and a pattern forming method using the same are provided.The actinic-ray-sensitive or radiation-sensitive resin composition of the present invention includes (A) a resin containing a repeating unit having a specific lactone structure and a repeating unit having a specific monocyclic alicyclic structure, which increases a solubility in an alkaline developer by the action of an acid, and (B) a compound having a specific structure, which generates an acid upon irradiation with an actinic-ray or a radiation.

Owner:FUJIFILM CORP

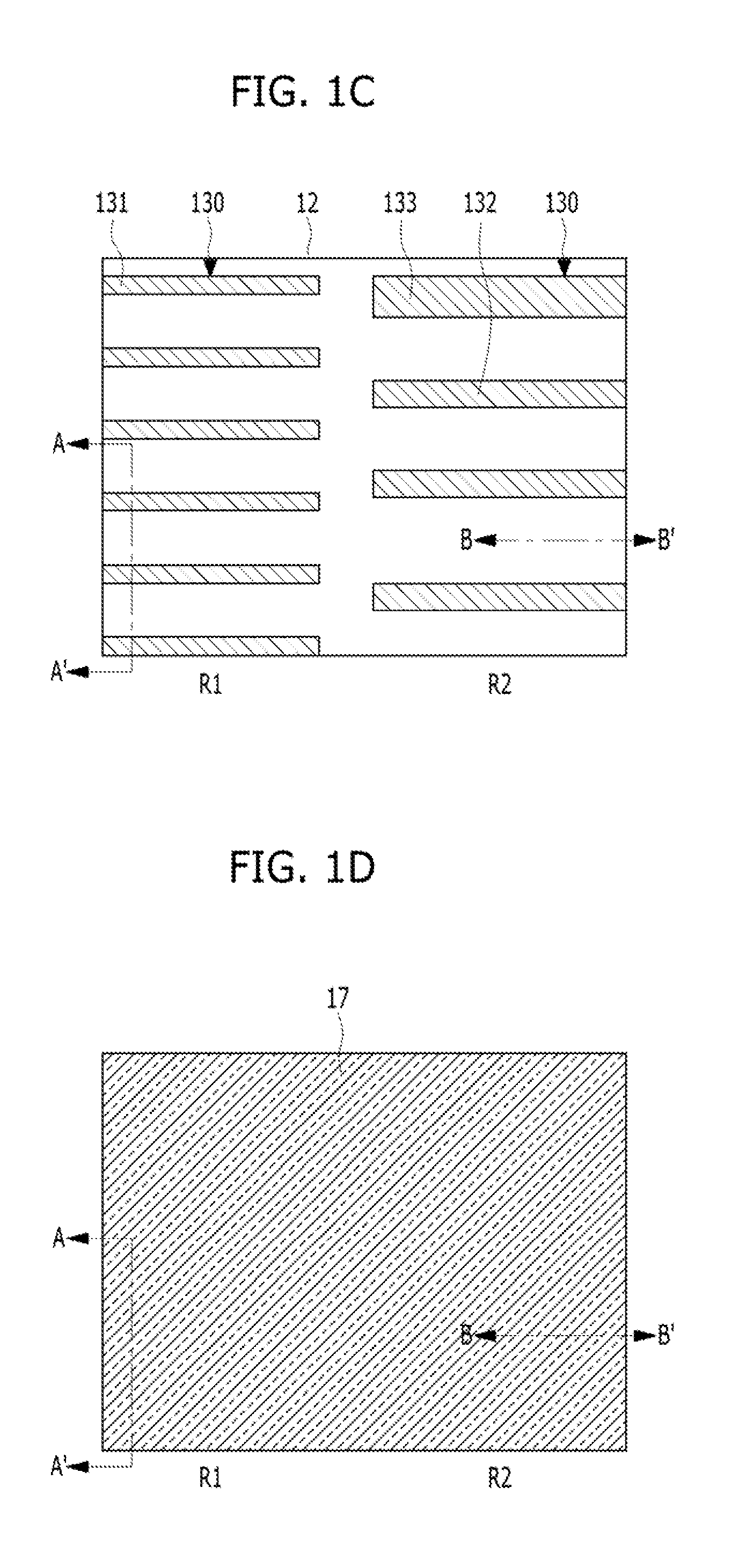

Method for forming patterns of semiconductor device

ActiveUS9847227B2Improve critical dimension uniformityIncrease process marginSolid-state devicesSemiconductor/solid-state device manufacturingRandom arrayDevice material

A method for forming patterns of a semiconductor device includes preparing an etch target layer defined with a first region and a second region; forming a regular first feature which is positioned over the etch target layer in the first region and a random feature which is positioned over the etch target layer in the second region; forming a regular second feature over the regular first feature; forming first and second cutting barriers which expose a portion of the random feature, over the random feature; cutting the regular first feature using the regular second feature, to form a regular array feature; cutting the random feature using the first cutting barrier and the second cutting barrier, to form a random array feature; and etching the etch target layer by using the regular array feature and the random array feature, to form a regular array pattern and a random array pattern.

Owner:SK HYNIX INC

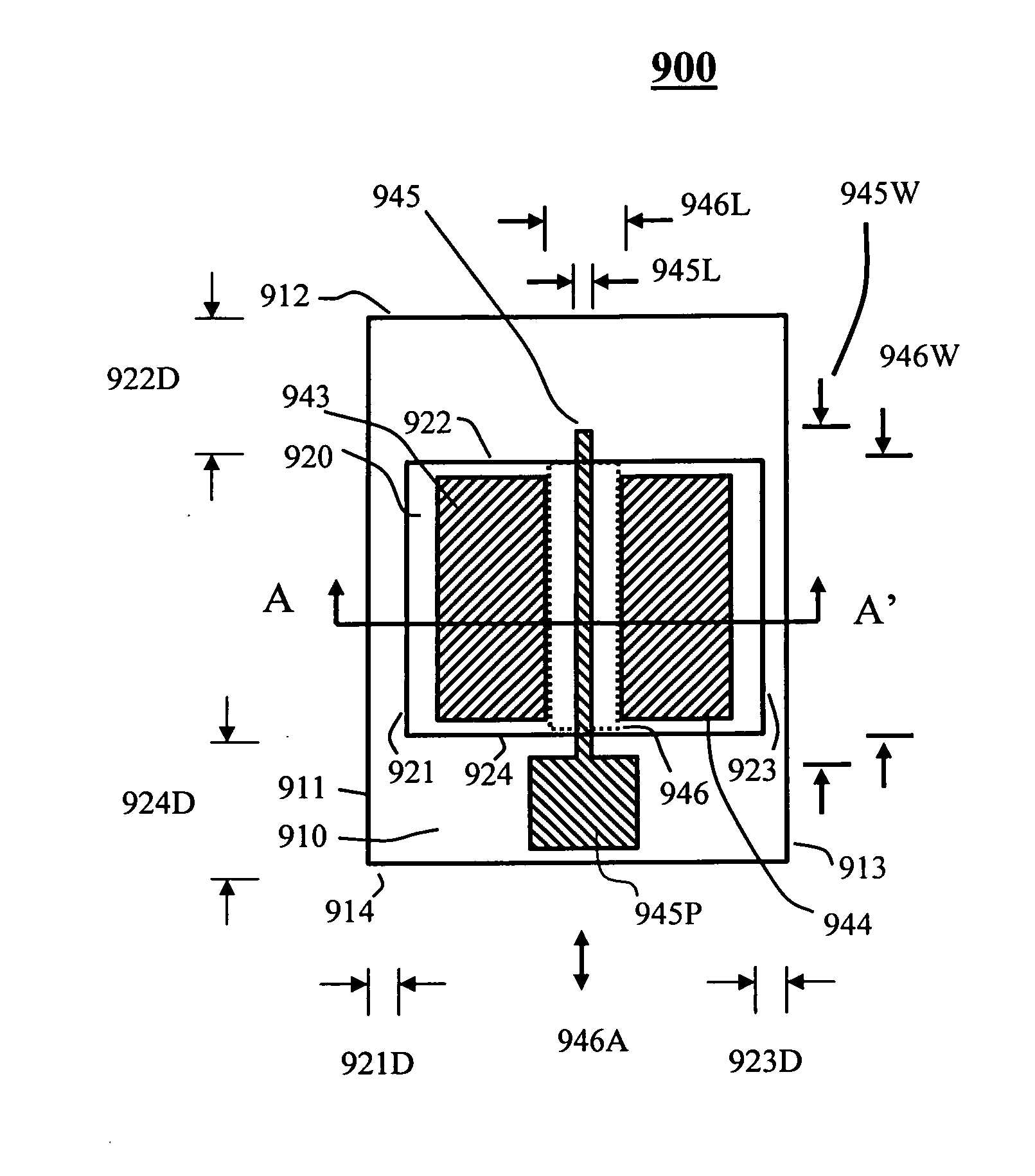

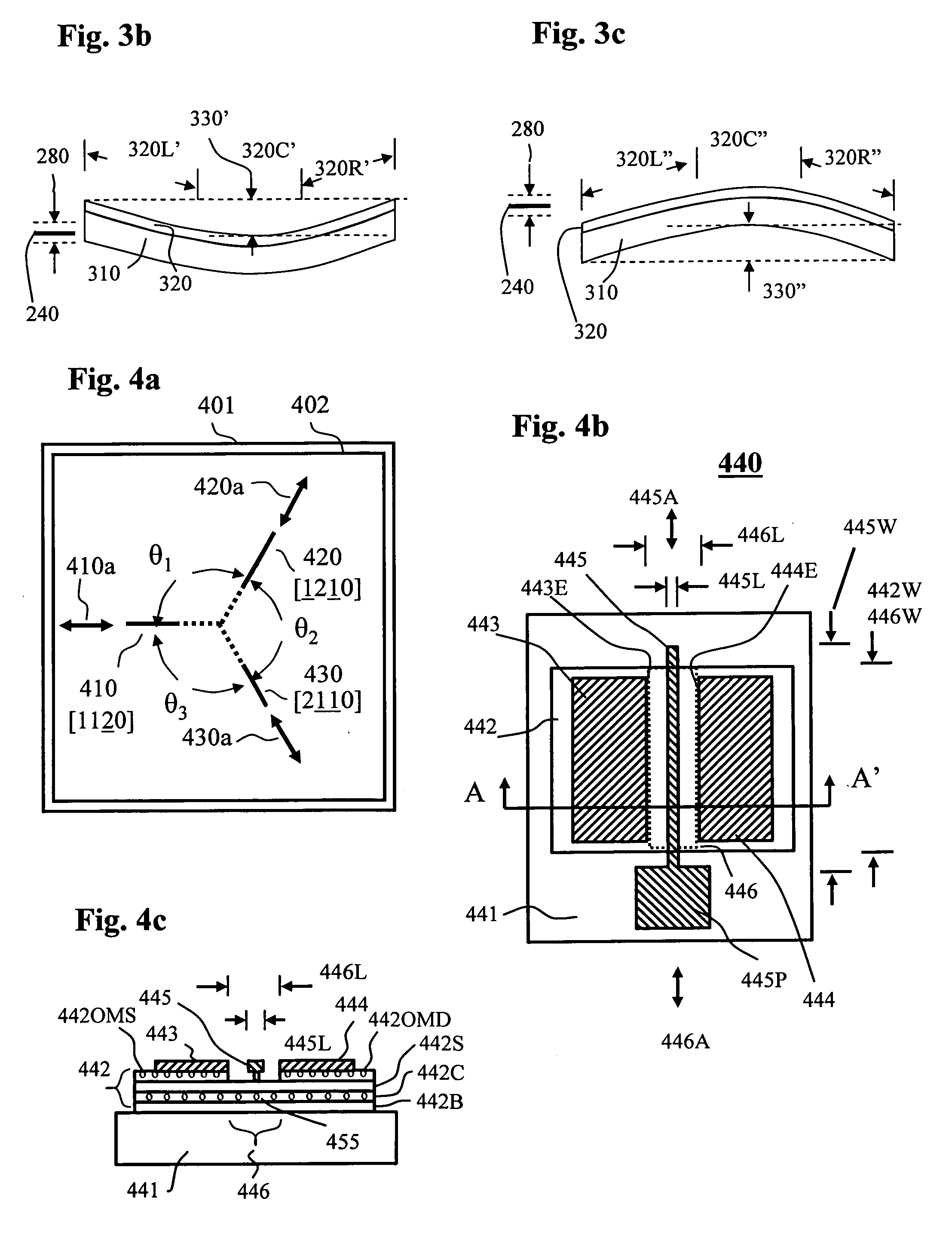

High Electron Mobility Transistors and Integrated Circuits with Improved Feature Uniformity and Reduced defects for Microwave and Millimetre Wave Applications

InactiveUS20150372096A1Improve critical dimension uniformityReduce defectTransistorSolid-state devicesPhysicsIntegrated circuit

High mobility transistors and microwave integrated circuits with an improved uniformity of the width of the smallest of features, an increased lithographic yield and reduced defects in the active components are provided. Before and during fabrication, a first grooving process is performed to partially or completely remove composite epitaxial layers in the field lanes to reduce the initial bow to be smaller than DOF range and to improve the uniformity of the critical dimension. A second grooving process may also be performed to remove composite epitaxial layers in the dicing lanes to further improve the uniformity of the width of the smallest features for the devices and circuits to be made.

Owner:SHIH ISHIANG +3

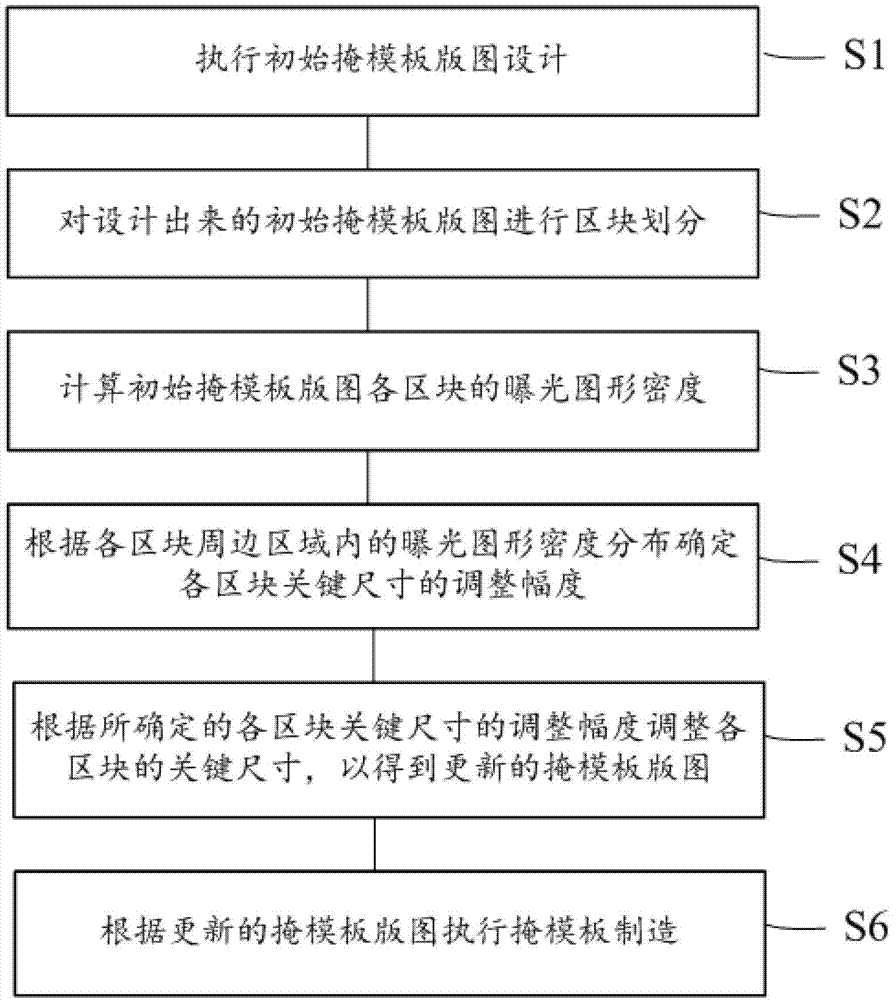

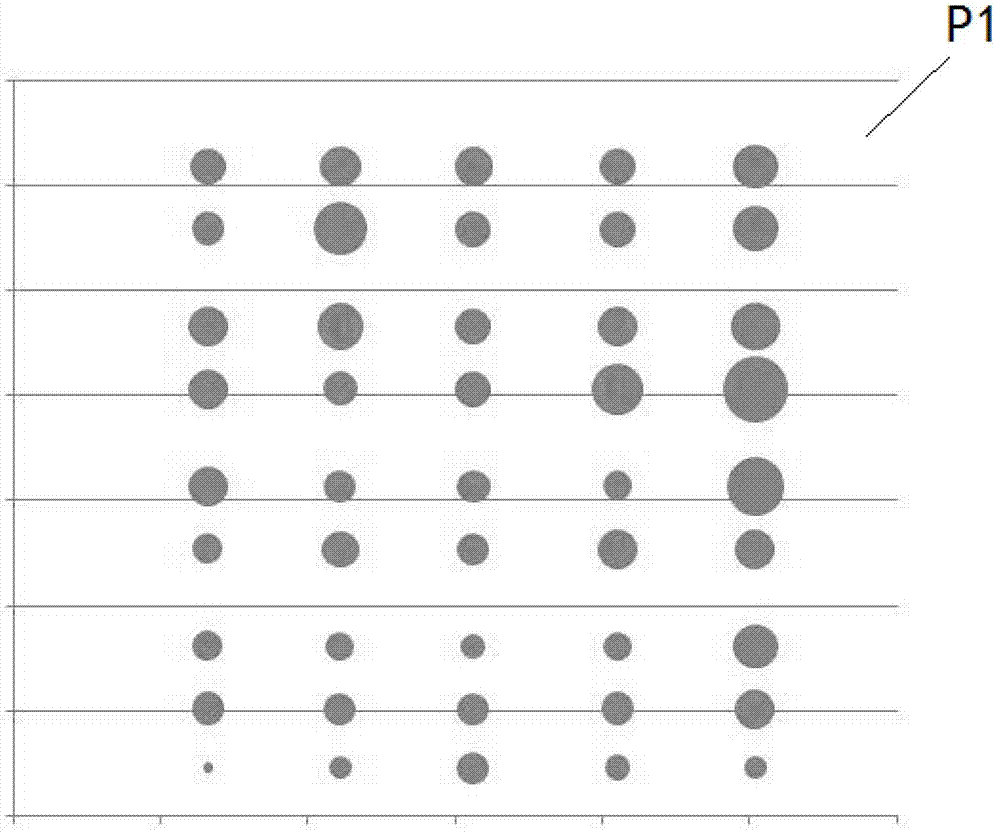

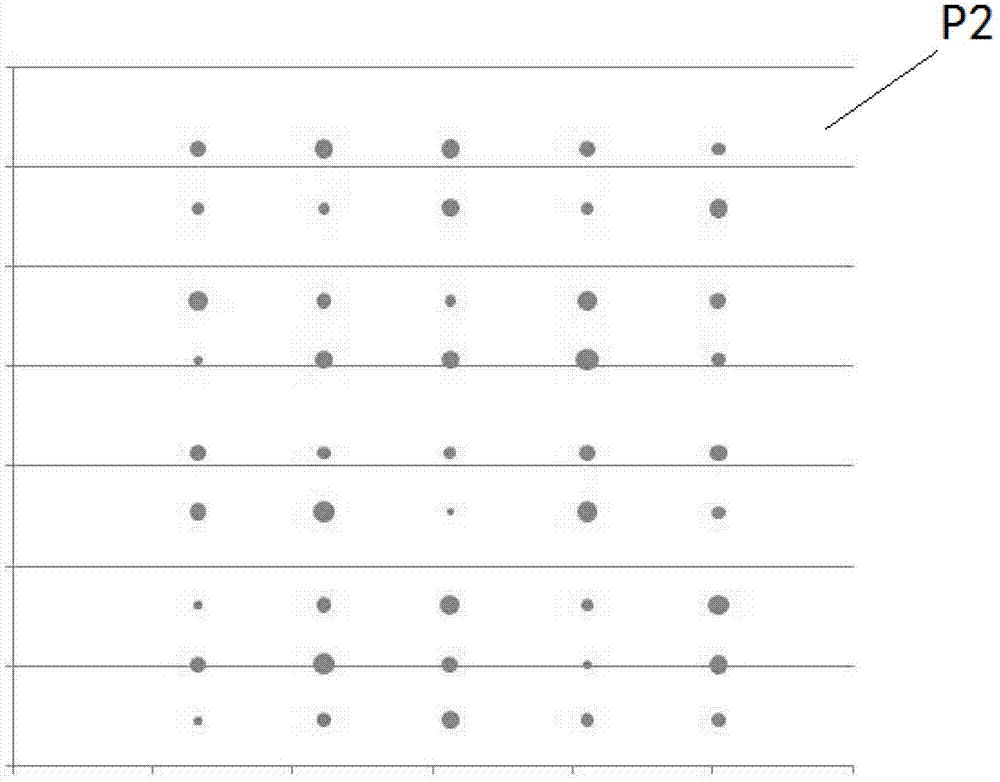

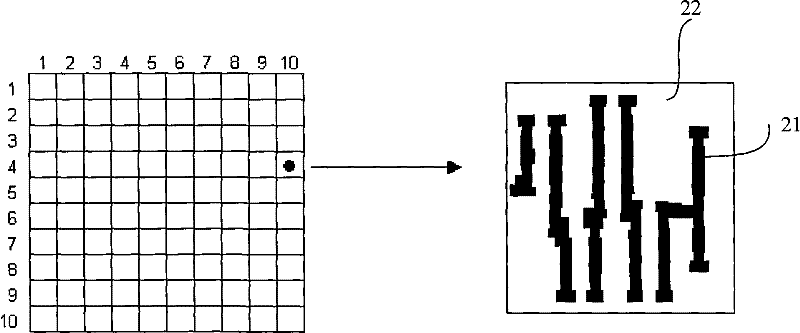

Method for improving homogeneity of critical dimension of photomask

InactiveCN103091976AIncrease critical sizeImprove critical dimension uniformityOriginals for photomechanical treatmentDensity distributionCritical dimension

The invention provides a method for improving homogeneity of critical dimension of a photomask. The method comprises the steps of: firstly, carrying out initial mask layout design; secondly, dividing the designed initial mask layout to blocks; thirdly, calculating the density of an exposure figure of each block of the initial mask layout; fourthly, determining the adjustment range of the critical dimension of each block according to the density distribution of the exposure figure in the peripheral area of each block; fifthly, adjusting the critical dimension of each block according to the determined adjustment range of the critical dimension of each block, thereby obtaining an updated mask layout; and sixthly, manufacturing a mask according to the updated mask layout.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

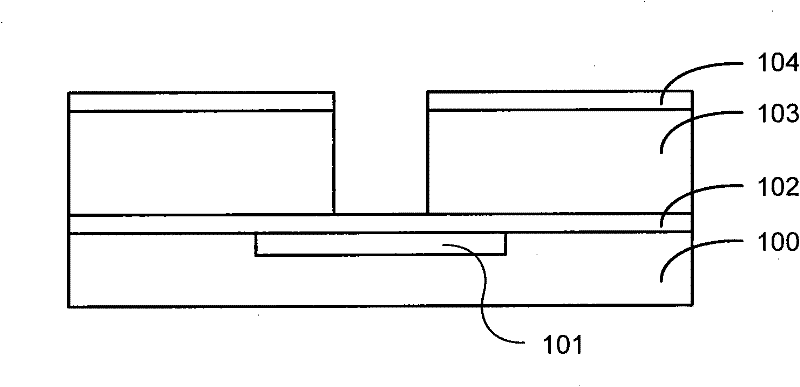

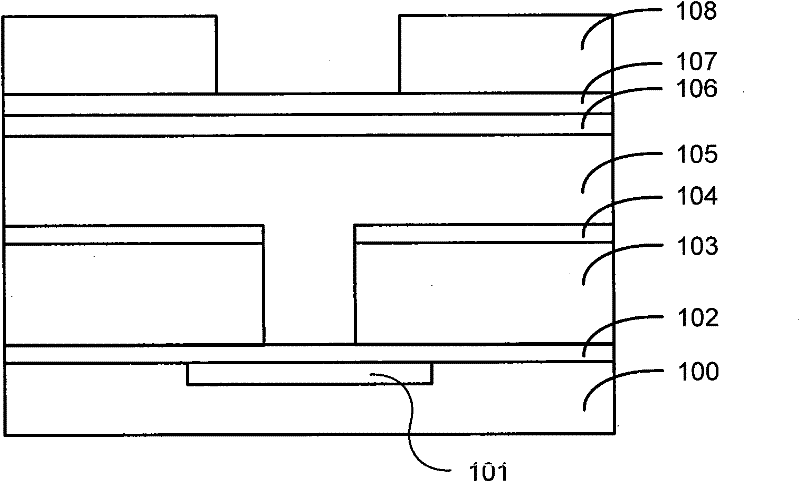

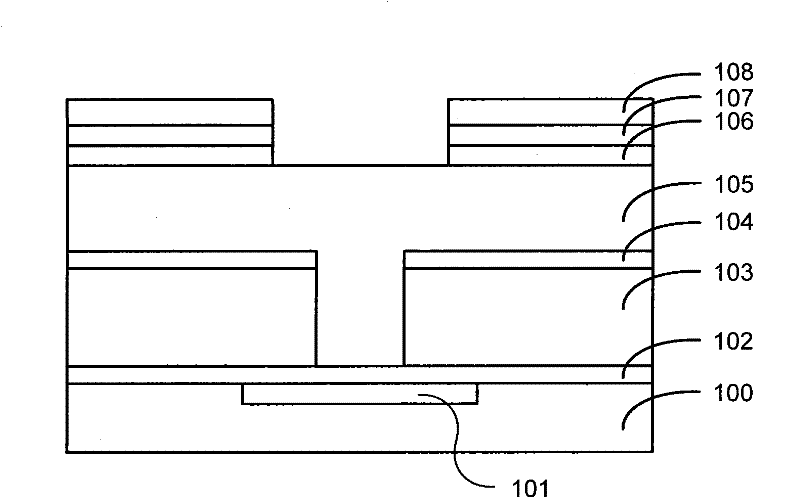

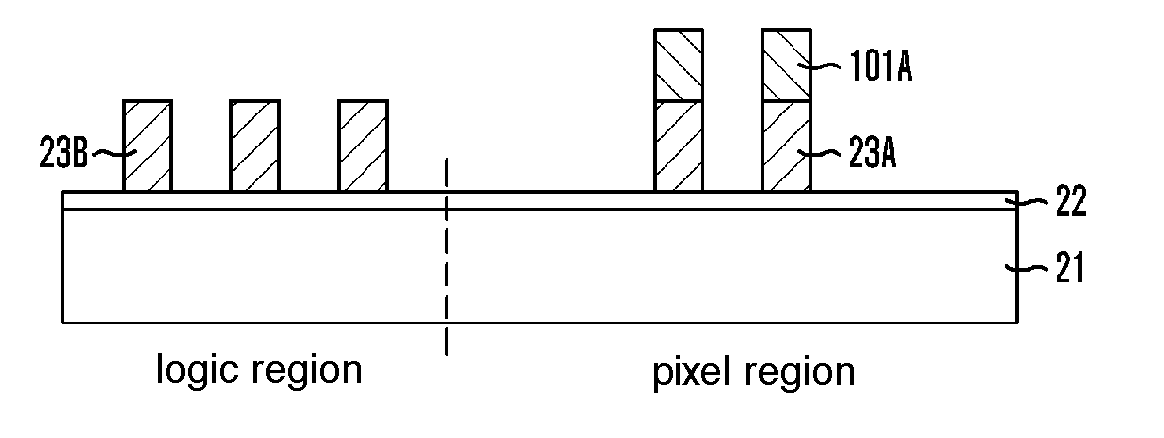

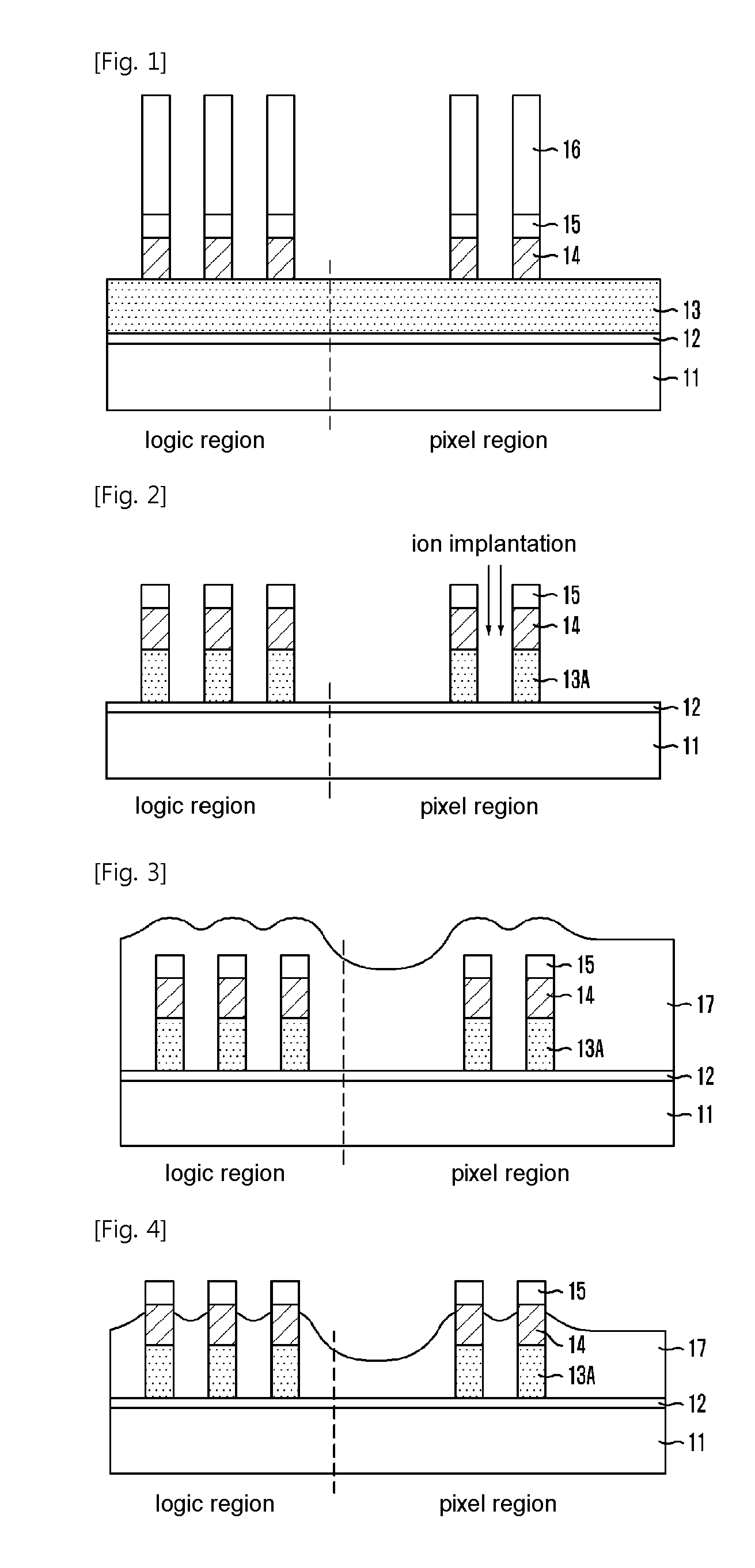

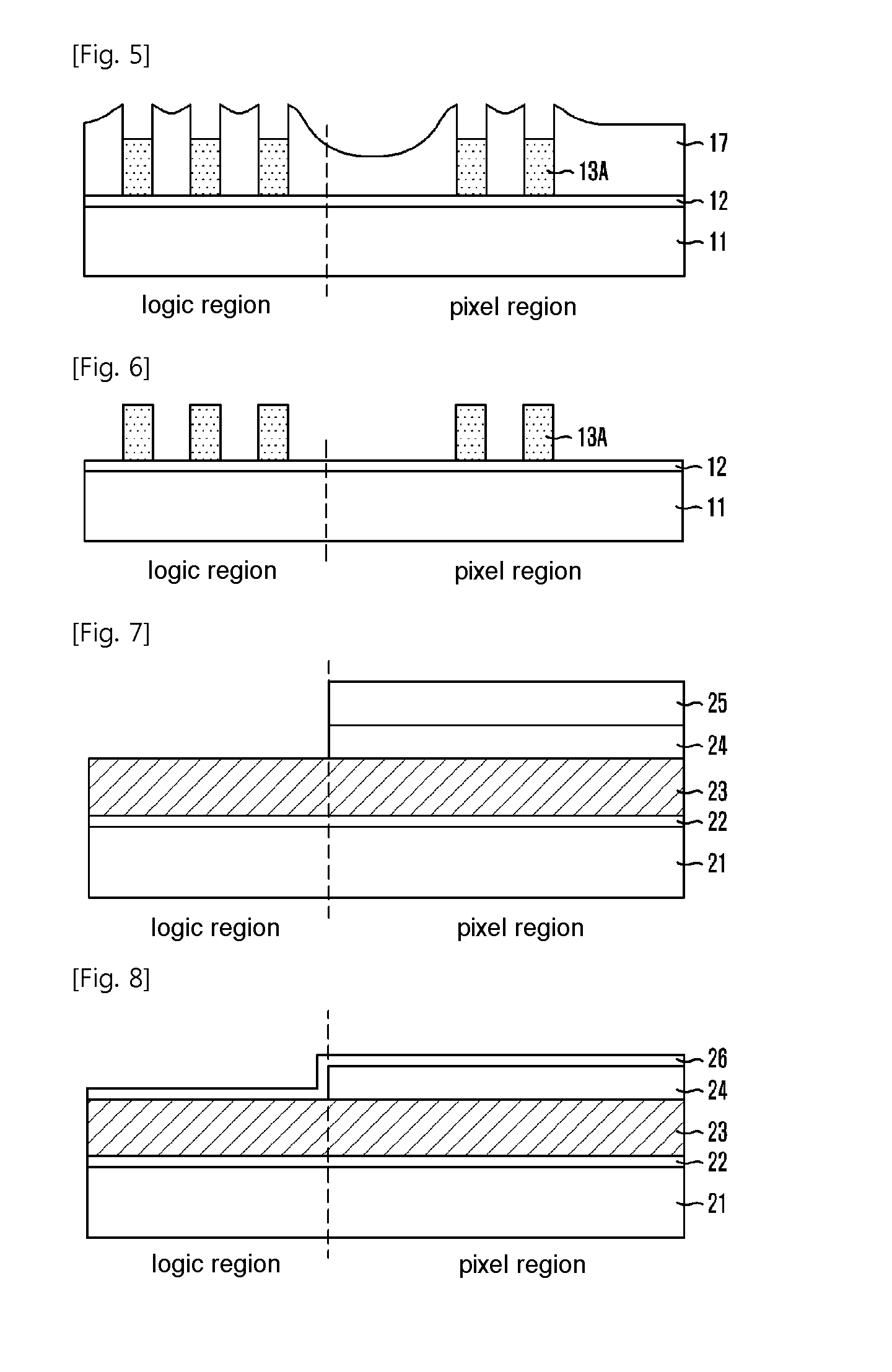

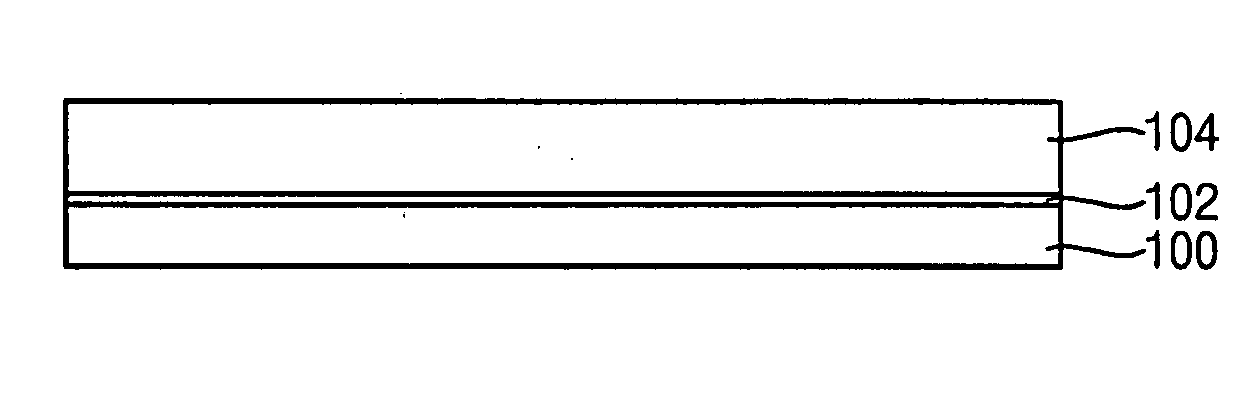

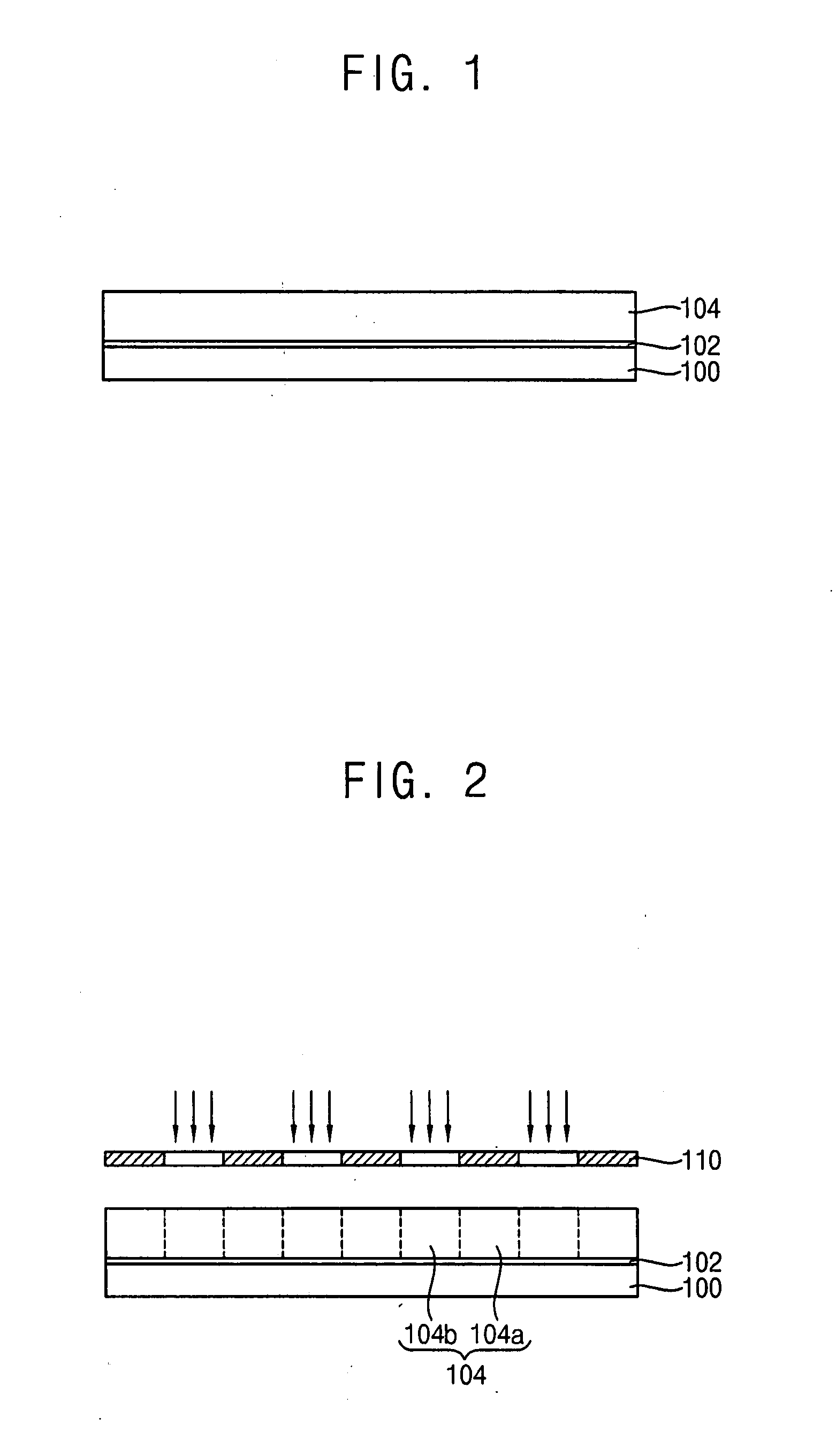

Method of manufacturing CMOS image sensor using double hard mask layer

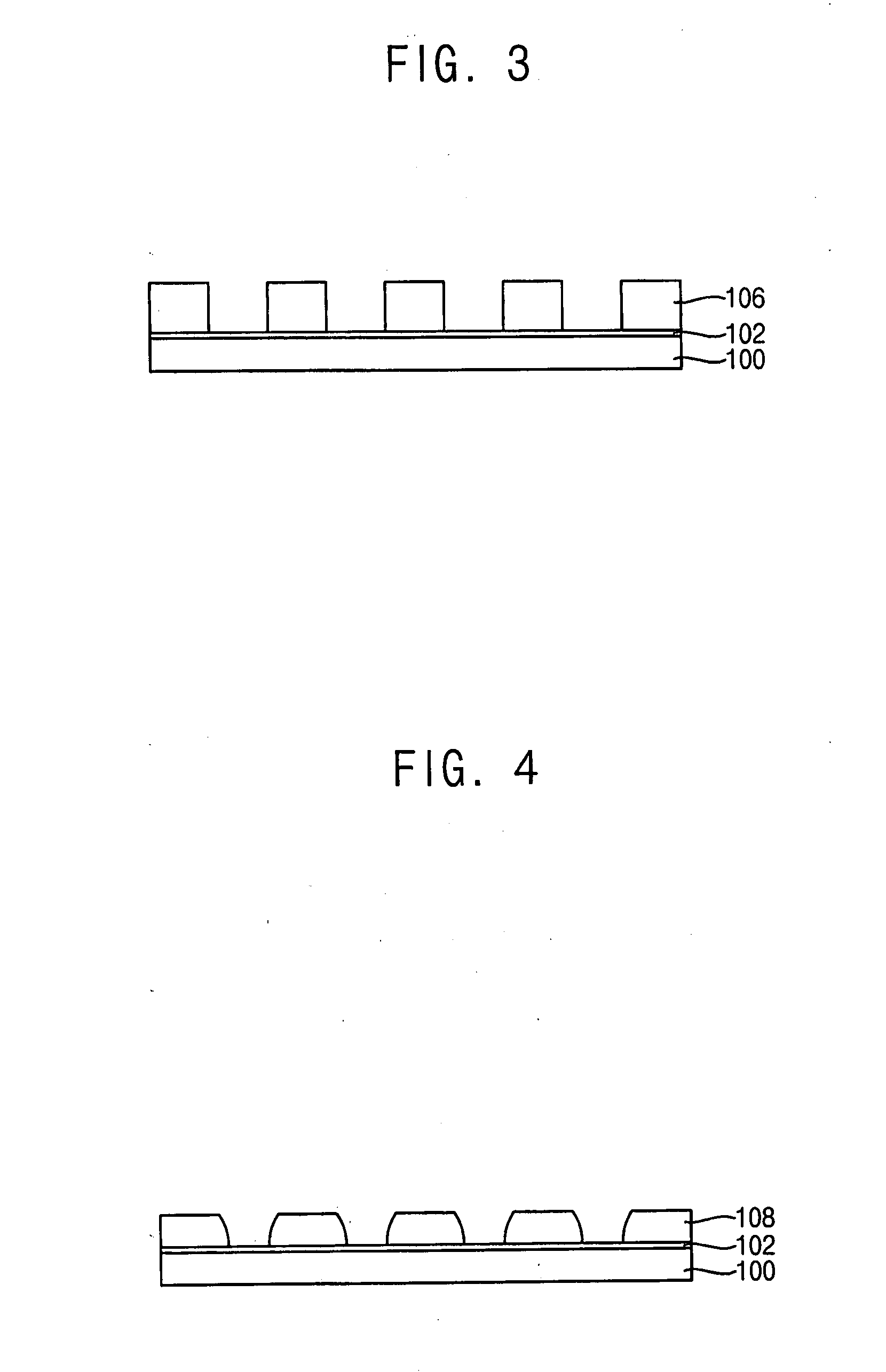

InactiveUS20110164161A1Easy to controlThin thicknessTelevision system detailsTelevision system scanning detailsSalicideCMOS

Disclosed is a method of manufacturing a CMOS image sensor, capable of forming silicide in a logic region and facilitating ion implantation into a pixel region while keeping a hard mask layer in a thin thickness without performing a process for removing the hard mask layer. The critical dimension is easily controlled when forming a gate pattern and the uniformity in the critical dimension of a gate photoresist pattern is improved. The method includes the steps of forming a gate conductive layer on a substrate on which a pixel region and a logic region are defined; forming a hard mask pattern on the gate conductive layer in such a manner that a thickness of the hard mask pattern in the pixel region is thicker than a thickness of the hard mask pattern in the logic region; forming a gate pattern in the pixel region and the logic region by etching the gate conductive layer using the hard mask pattern as an etching barrier; removing the hard mask pattern remaining in the logic region; and forming silicide in the logic region.

Owner:INTELLECTUAL VENTURES II

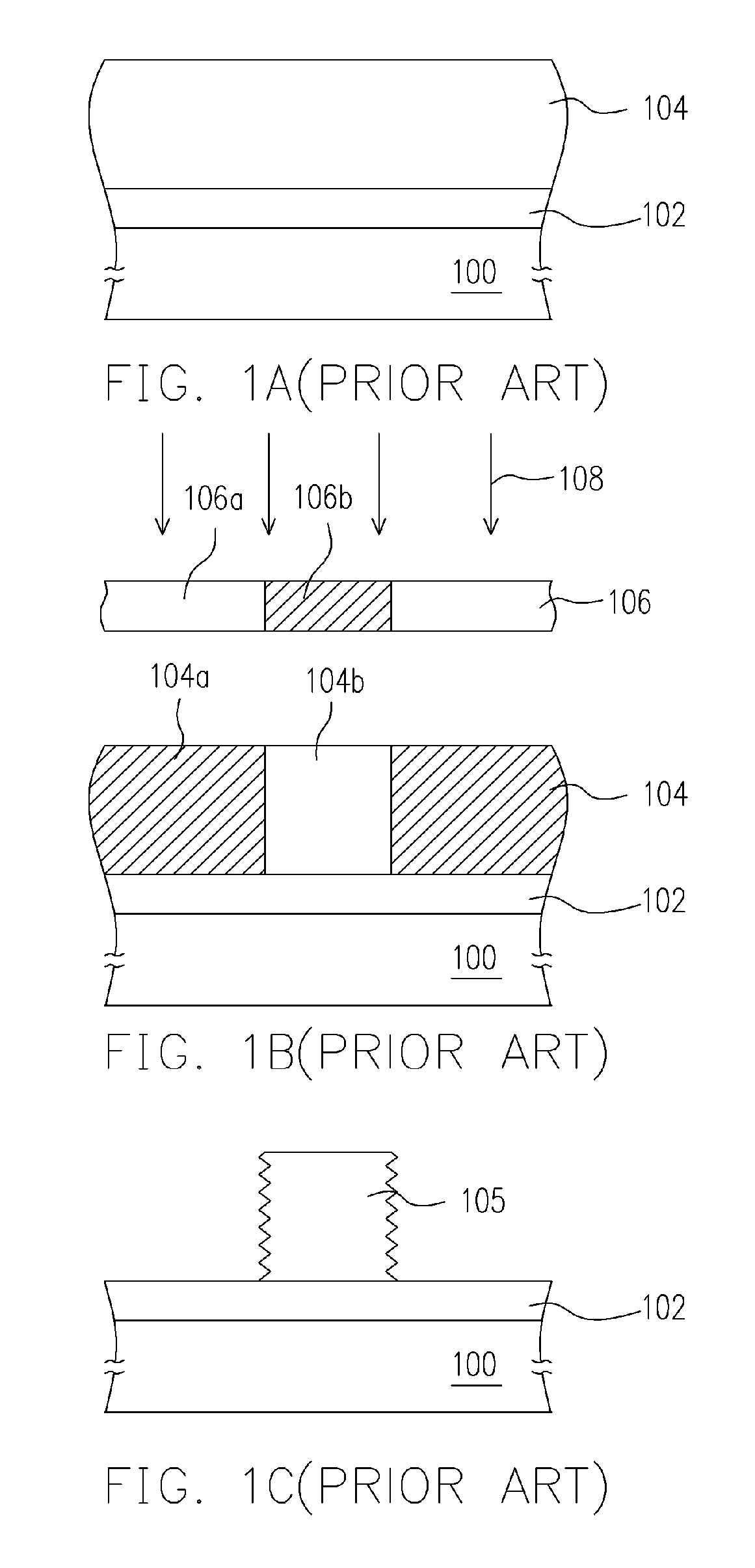

Method for forming photoresist pattern and method for triming photoresist pattern

InactiveUS20060127820A1Improve smoothnessAccurate layeringPhotosensitive material processingOriginals for photomechanical treatmentSolution treatmentCritical dimension

A method for forming a photoresist pattern is described. A photoresist layer is first formed over a substrate, and then an exposure process and a development process are performed to pattern the photoresist layer so as to form a patterned photoresist layer. Next, a multiple-trimming process is performed to trim the patterned photoresist lay to form a photoresist pattern. The multiple-trimming process includes at least one step of alkaline solution treatment and / or at least one step of neutral solution treatment. The method is applicable for improving properties of smoothness of the surface, and uniformity and minification of critical dimensions of the photoresist patterns.

Owner:UNITED MICROELECTRONICS CORP

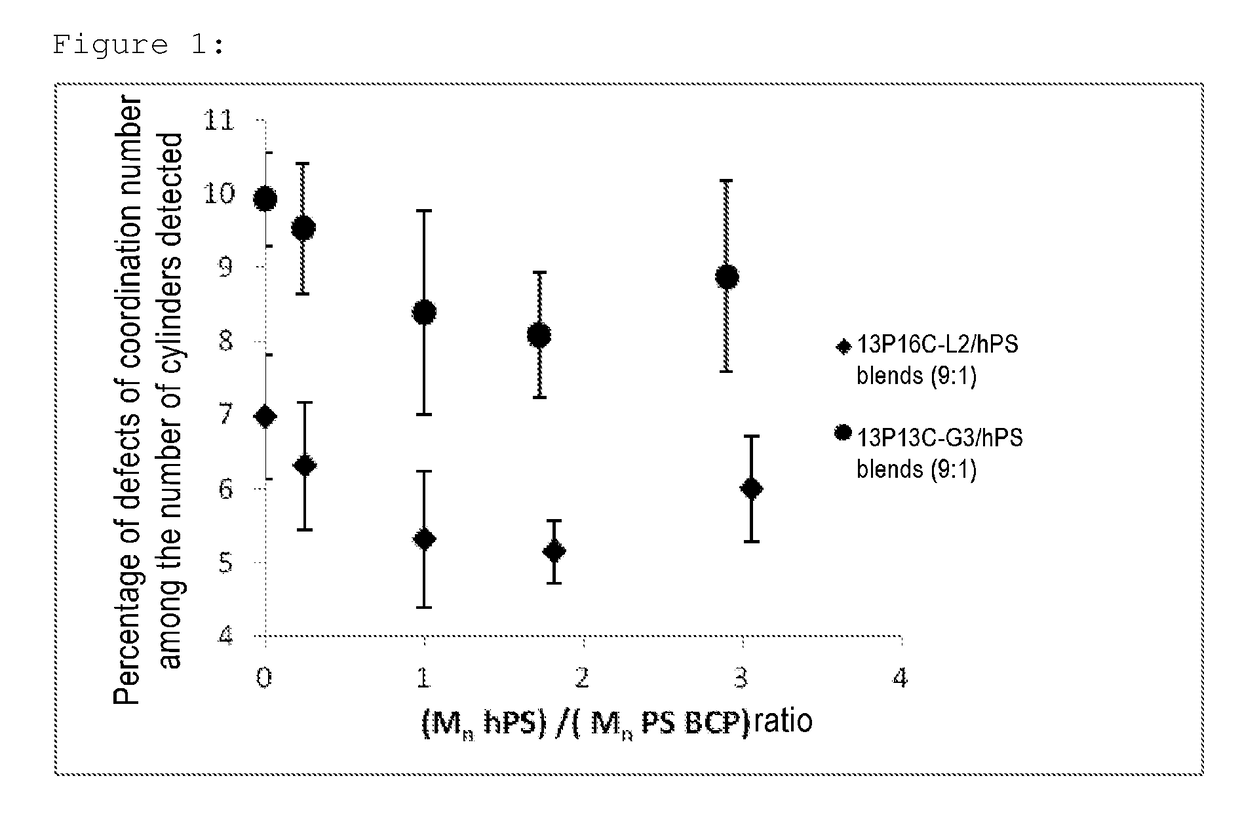

Method for controlling the level of defects in films obtained with blends of block copolymers and polymers

InactiveUS20170307973A1Reduce defectsGreat massPhotomechanical apparatusPretreated surfacesPolymer scienceMonomer

The present invention relates to a method for controlling the level of defects in films obtained using a composition comprising a blend of block copolymers and polymers deposited on a surface. The polymers comprise at least one monomer identical to those present in one or other block of the block copolymers.

Owner:ARKEMA FRANCE SA

Photoresist compositions and methods of forming a pattern using the same

InactiveUS20080102403A1Reduce and suppress hydrogen bondingLower glass transition temperaturePhotosensitive materialsPhotosensitive material processingPolymer sciencePhotoacid

A photoresist-composition includes about 4 to about 20 percent by weight of an acrylate copolymer; about 0.1 to about 0.5 percent by weight of a photoacid generator; and a solvent. The acrylate copolymer includes about 28 to about 38 percent by mole of a first repeating unit represented by Formula (1), about 28 to about 38 percent by mole of a second repeating unit represented by Formula (2), about 0.5 to about 22 percent by mole of a third repeating unit represented by Formula (3) and about 4 to about 42 percent by mole of a fourth repeating unit represented by Formula (4),wherein R1, R2, R3 and R4 independently represent a hydrogen atom or a C1-C3 alkyl group, X is a blocking group including an alkyl-substituted adamantane or an alkyl-substituted tricycloalkane, Y is a blocking group including a lactone, Z1 is a blocking group including a hydroxyl-substituted adamantane, and Z2 is a blocking group including an alkoxy-substituted adamantane.

Owner:SAMSUNG ELECTRONICS CO LTD

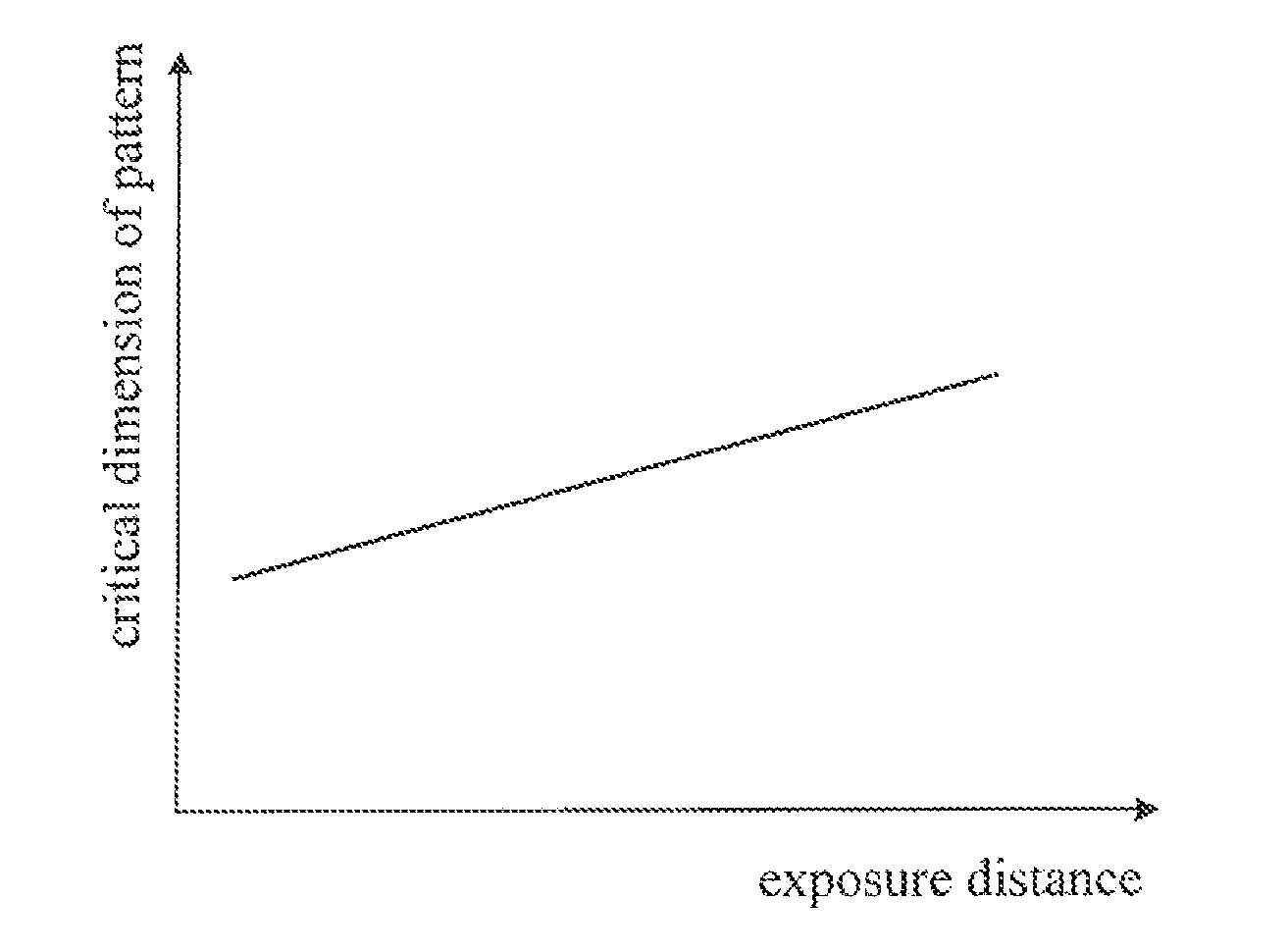

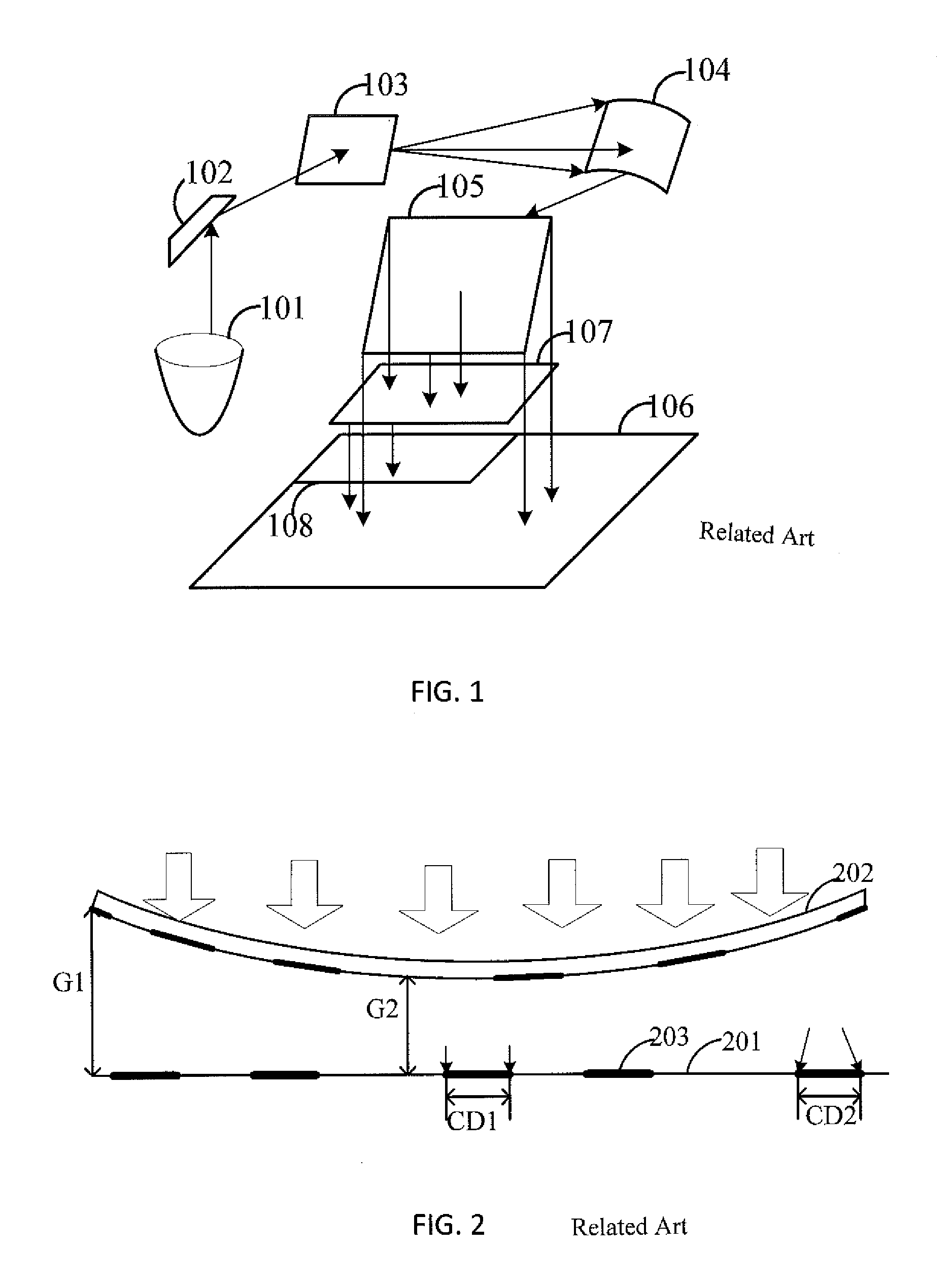

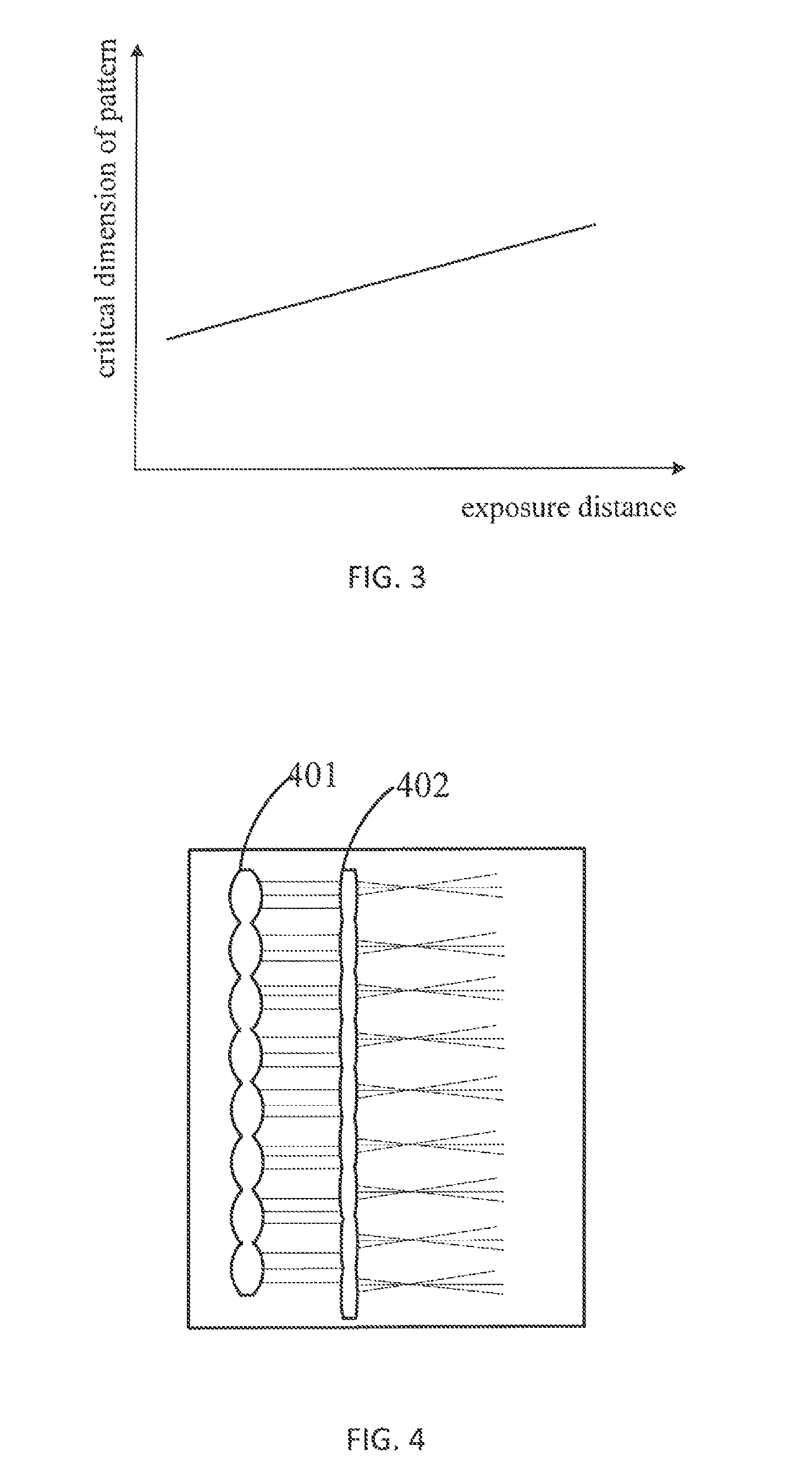

Fly eye lens and proximity exposure machine optical system

ActiveUS9274433B2Improve transmittanceReduce transmittancePhotomechanical exposure apparatusMicrolithography exposure apparatusIlluminanceLight beam

An embodiment of the present invention provides a fly eye lens which is applied to a proximity exposure machine optical system. The fly lens includes a first lens assembly and a second lens assembly, wherein the first lens assembly includes a plurality of lenses which form a first lens face, and the second lens assembly includes a plurality of lenses which form a second lens face. The first lens face is used to split an incident broad light beam into narrow light beams and then refract the narrow light beams onto the second lens face, and the second lens face is used to dispersively refract the received narrow light beams onto a concave mirror in the optical system. A lens closer to a center of the second lens face has a higher transmittivity, and a lens farther from the center of the second lens face has a lower transmittivity. According to the embodiment of the present invention, since different lenses on the second lens face have different transmittivities, the illuminances of light radiated to different regions of a mask plate through the fly eye lens are different, and thus the uniformity of the critical dimensions of the exposed patterns can be improved to a certain extent.

Owner:BOE TECH GRP CO LTD +1

Method for manufacturing self-aligned double pattern and method for manufacturing semiconductor device

ActiveCN110571139BImprove critical dimension uniformityImprove uniformitySemiconductor/solid-state device manufacturingGraphicsEtching

The invention provides a method for manufacturing a self-aligned double pattern and a method for manufacturing a semiconductor device. Considering the negative influence of the process of the target etching layer formed on the semiconductor substrate, the data such as the thickness of the formed target etching layer is fed back In the subsequent process of etching the target etching layer, the etching effect of the target etching layer can be more accurately controlled, thereby improving the uniformity of the key dimensions of the pattern obtained on the target etching layer, and improving the obtained The performance and yield of the semiconductor device; further, considering the negative impact of the lithography process, the lithography process conditions are adjusted in time according to the critical dimensions after lithography and the thickness of the etch protection layer and cover layer, thereby improving the final core. The morphology of the mold is further improved to further improve the uniformity of the critical dimension of the pattern obtained on the target etching layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

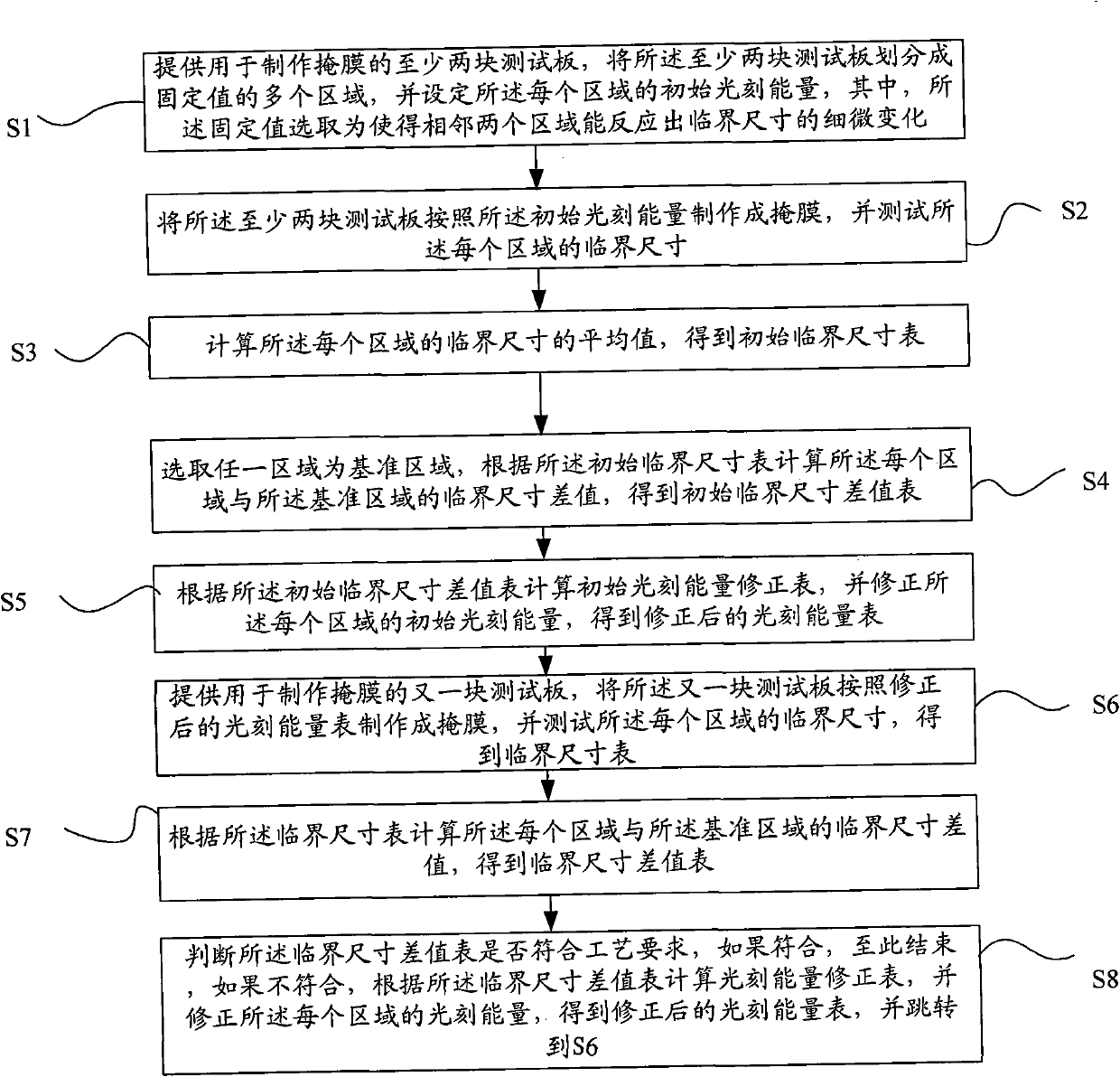

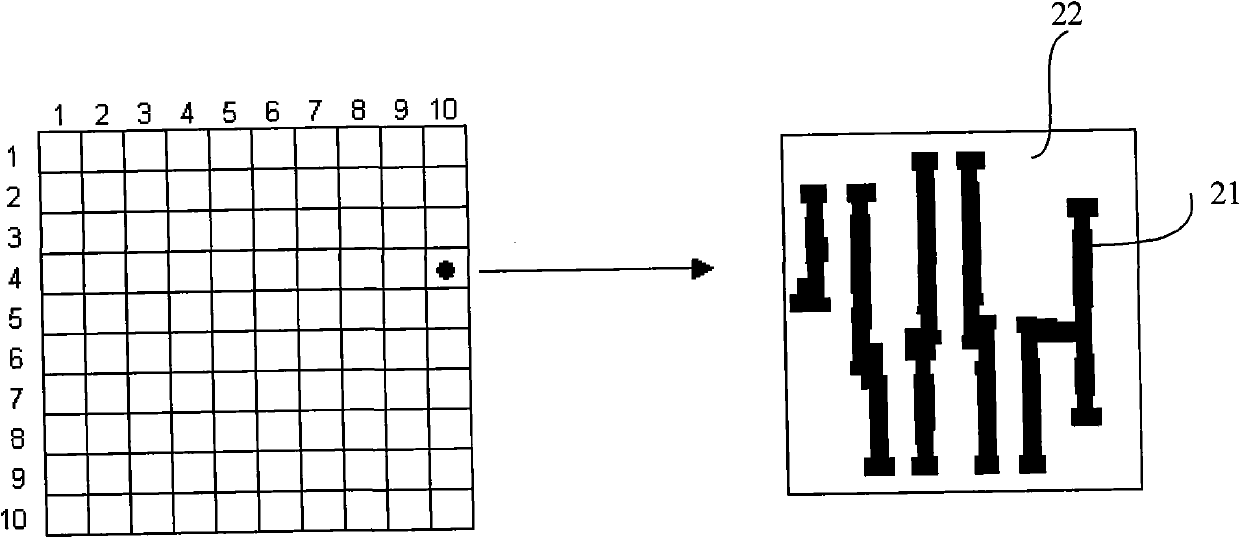

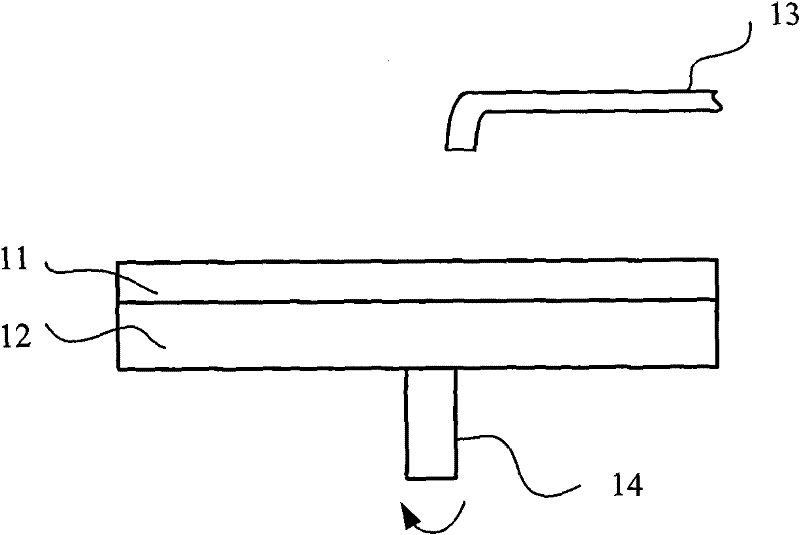

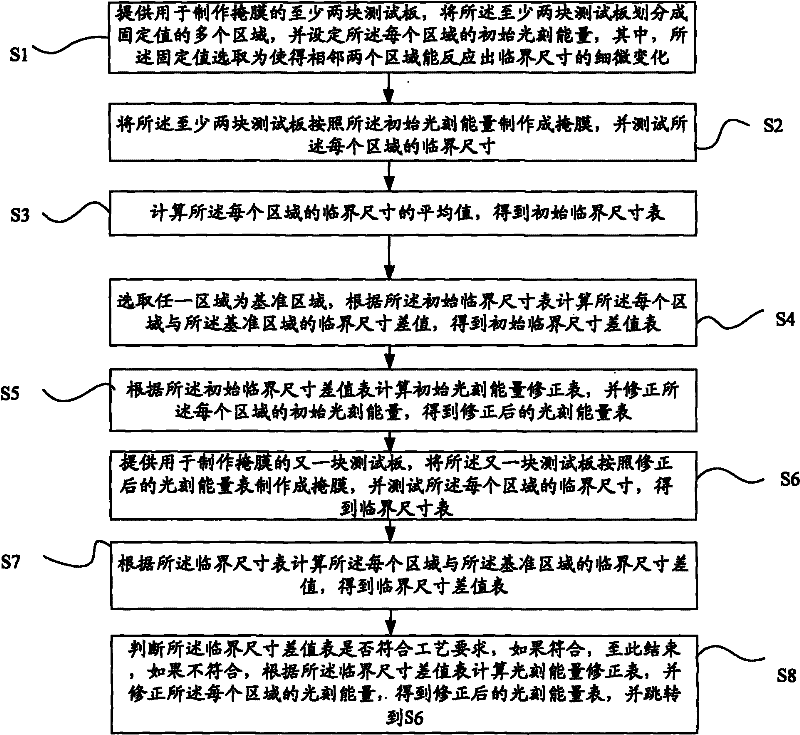

Method for improving critical dimension uniformity of mask

InactiveCN102023473AImprove critical dimension uniformityOriginals for photomechanical treatmentAgricultural engineeringCritical dimension

The invention provides a method for improving critical dimension uniformity of a mask. The differential distribution of critical dimension of the mask is fed back to a photoetching step in a mask manufacturing process, so that the photoetching energy distribution in the photoetching step is adjusted, and the aim of improving the critical dimension uniformity of the mask is fulfilled.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for improving critical dimension uniformity of mask

InactiveCN102023473BImprove critical dimension uniformityOriginals for photomechanical treatmentAgricultural engineeringCritical dimension

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor structure and formation method thereof

ActiveUS10957550B2Improve critical dimension uniformityCompensation differenceSemiconductor/solid-state device manufacturingSemiconductor devicesCrystallographySemiconductor structure

A semiconductor structure and a formation method thereof are provided. The formation method includes: providing a base, the base including a pattern dense region and a pattern isolated region; forming a plurality of separate hard mask layers on the base, where adjacent hard mask layers and the base define an opening, and an opening of the pattern isolated region is wider than an opening of the pattern dense region; forming a trimming layer at least on a side wall of the opening of the pattern isolated region, the trimming layer and the hard mask layer constituting a mask structure layer; and etching, using the mask structure layer as a mask, a portion of the thickness of the base exposed by the opening to form a plurality of target pattern layers protruding from the remaining base. Embodiments and implementations of the present disclosure are advantageous for improving a critical dimension uniformity of a target pattern layer in each region.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Method for obtaining compensation mask of photomask, exposure method and exposure system

PendingCN113655687AImprove critical dimension uniformityOriginals for photomechanical treatmentEngineeringExposure

The embodiment of the invention relates to the field of semiconductors, and provides a method for obtaining a compensation mask of a photomask, an exposure method and an exposure system. The method for obtaining the compensation mask of the photomask comprises the steps that: the photomask is provided, wherein the photomask comprises a photosensitive layer and a graphical shading layer, and the graphical shading layer is located on the surface of the photosensitive layer; a critical dimension deviation test is performed on the photomask by using an exposure machine to obtain a deviation area of the feature dimension of the photomask and a deviation value of the deviation area; and based on the deviation area and the deviation value, a compensation mask corresponding to the exposure machine table is formed, the compensation mask is internally provided with an attenuation area, the compensation mask is located between the photomask and an exposure light source in the exposure processing period through the photomask, and the attenuation area is right opposite to the deviation area, the attenuation area is used for attenuating the illumination intensity of light emitted by the exposure light source and reaching the deviation area through the attenuation area, and at least the critical dimension uniformity of the photomask can be improved.

Owner:CHANGXIN MEMORY TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com