Method for manufacturing self-aligned double pattern and method for manufacturing semiconductor device

A technology of dual graphics and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that are not good, affect the performance and yield of semiconductor devices, and achieve improved morphology, accurate graphic features, and precise effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

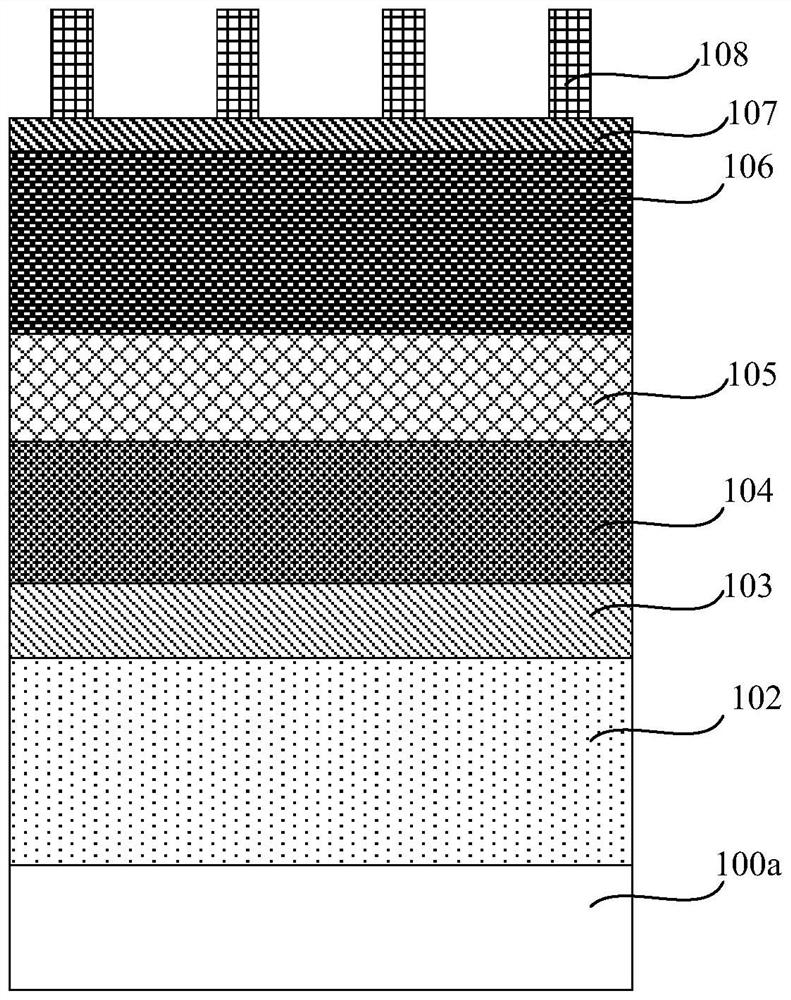

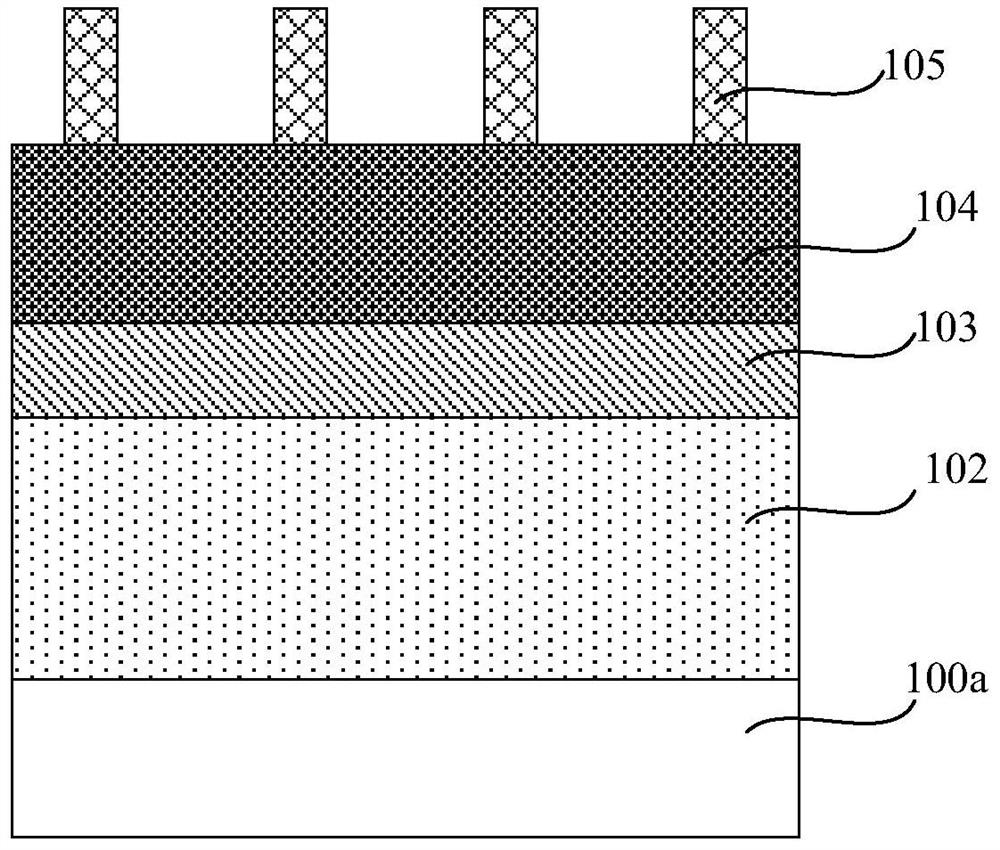

[0043] A method of manufacturing a polysilicon gate using self-aligned double patterning (SADP) technology, comprising the following steps:

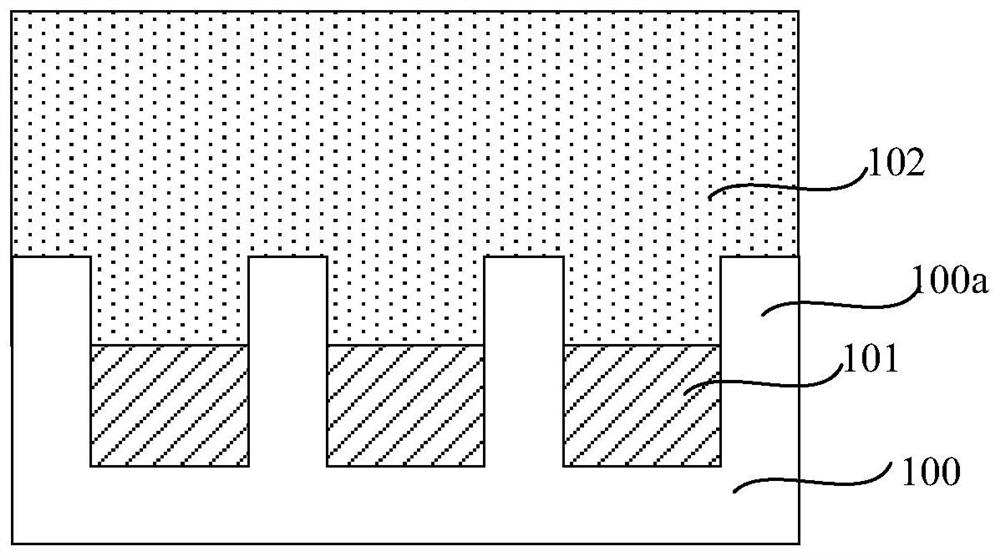

[0044] First, please refer to Figure 1A , providing a semiconductor substrate 100 having fins 100a and shallow trench isolation structures (STI) 101, the shallow trench isolation structures 101 are formed between adjacent fins 100a and the top of the shallow trench isolation structures 101 is lower than the fins On the top of the fin 100a, polysilicon (poly) is deposited on the surface of the fin 100a and the shallow trench isolation structure 101, the thickness of the deposited polysilicon layer is sufficient to fill the trench between adjacent fins 100a and between the fins having a sufficient thickness on top of the fin 100a, chemical mechanical planarization (CMP) is performed on the top of the deposited polysilicon to form a polysilicon layer 102 with a flat top surface and the desired thickness on top of the fin 100a;

[0045] Ne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More