Patents

Literature

39results about How to "Increase critical size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

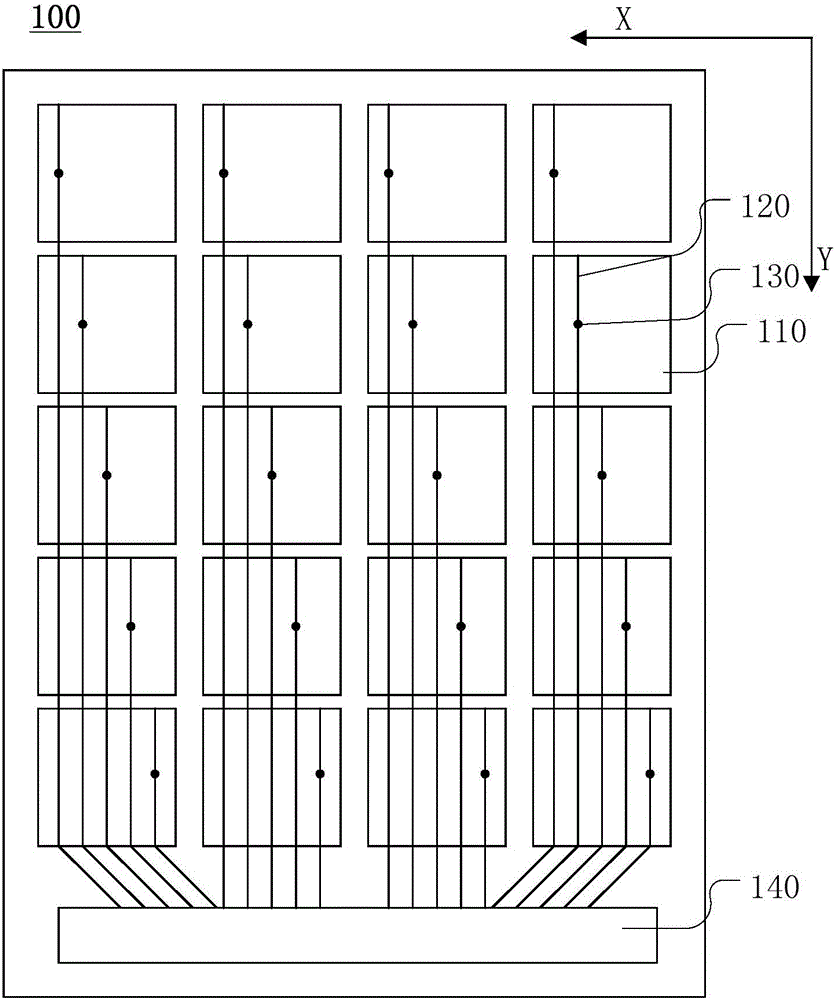

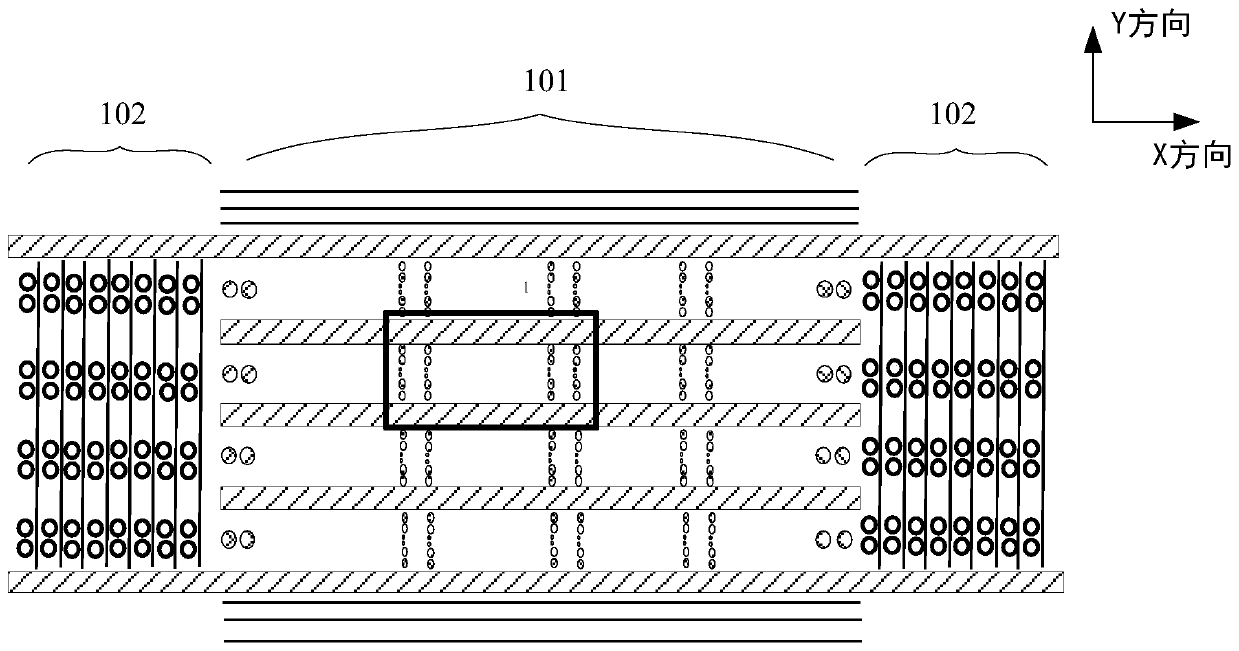

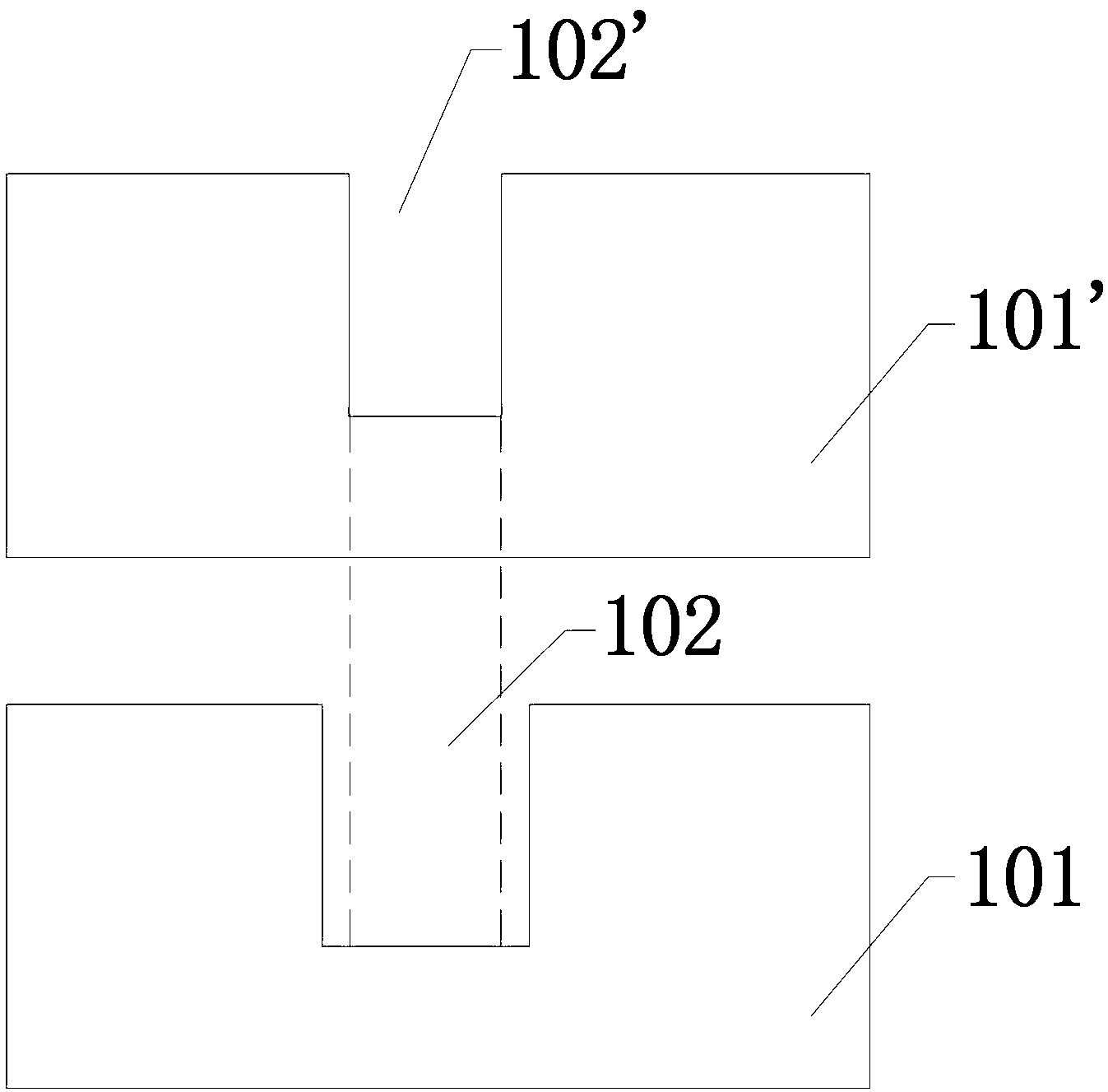

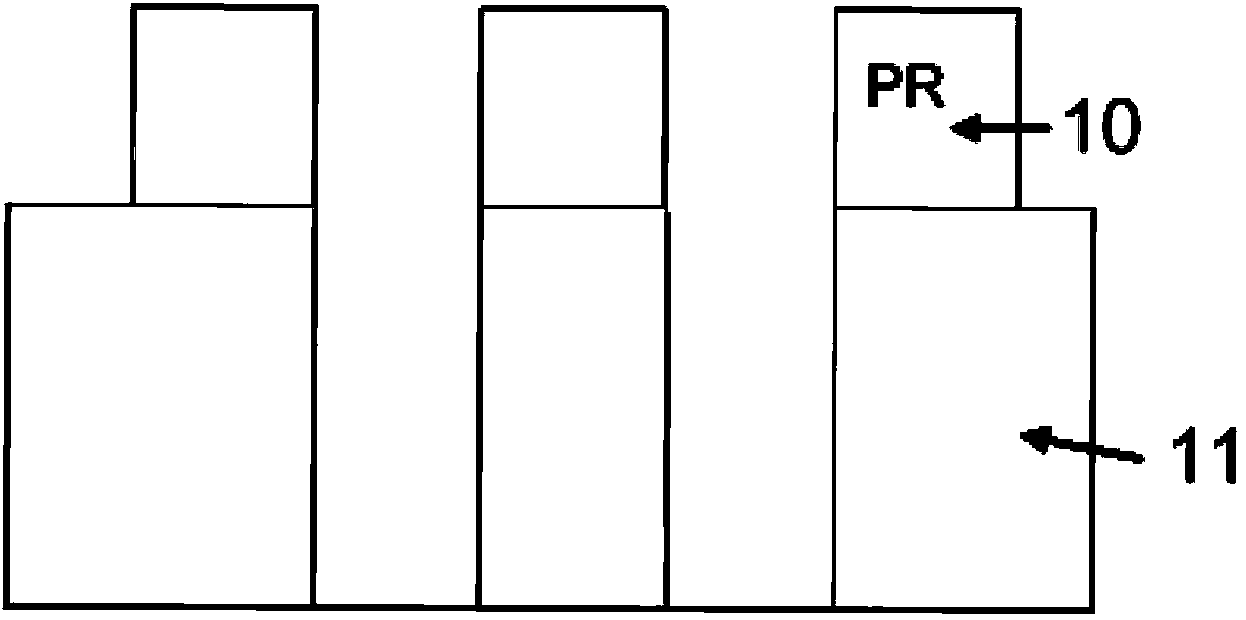

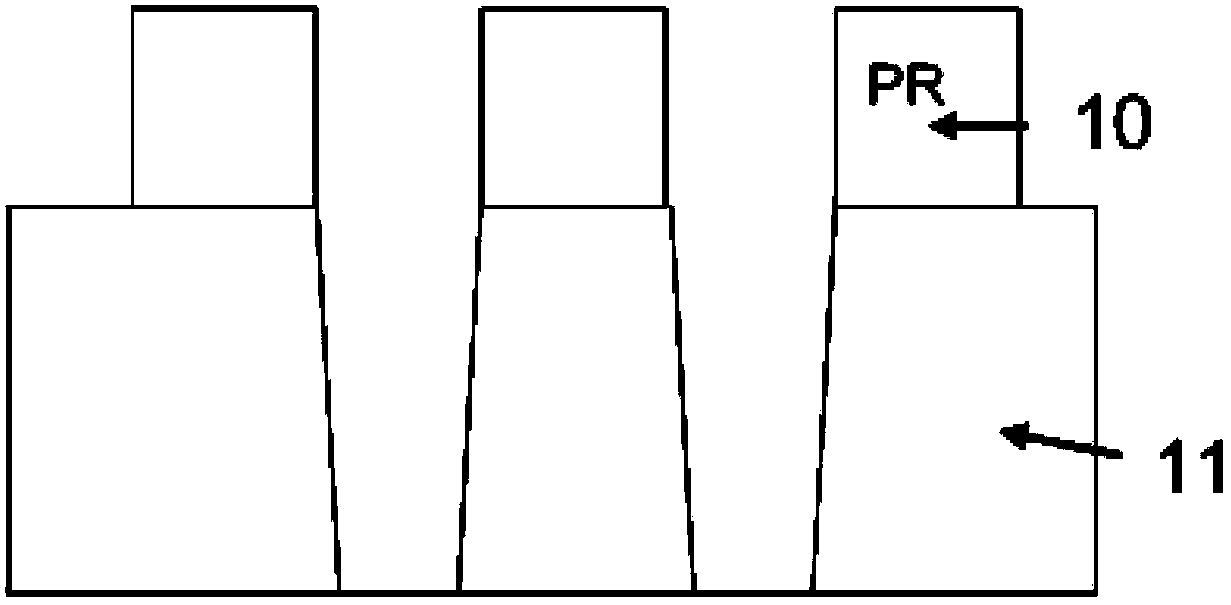

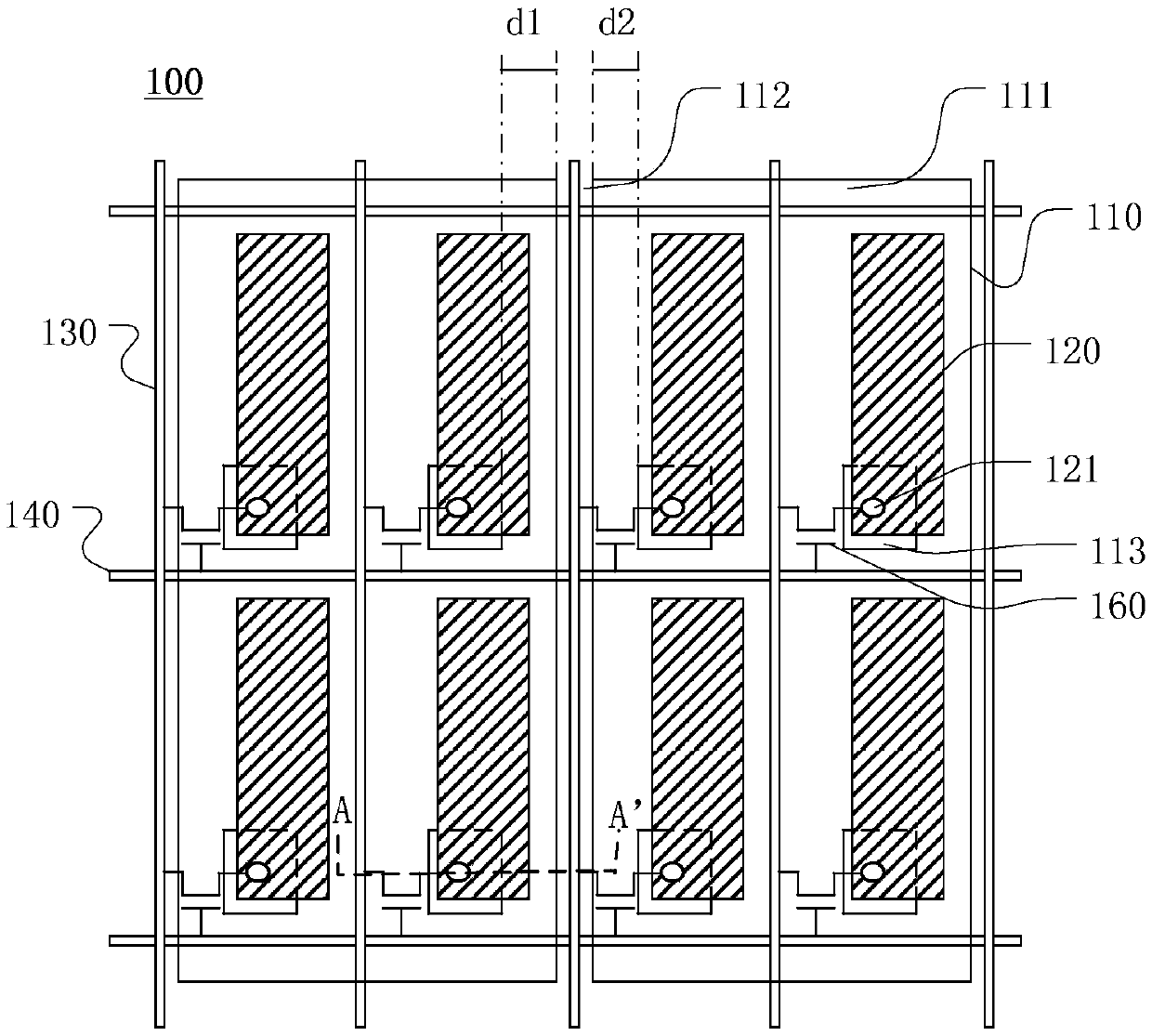

Design of fanout trace in TFT-LCD (thin film transistor-liquid crystal display) narrow frame design

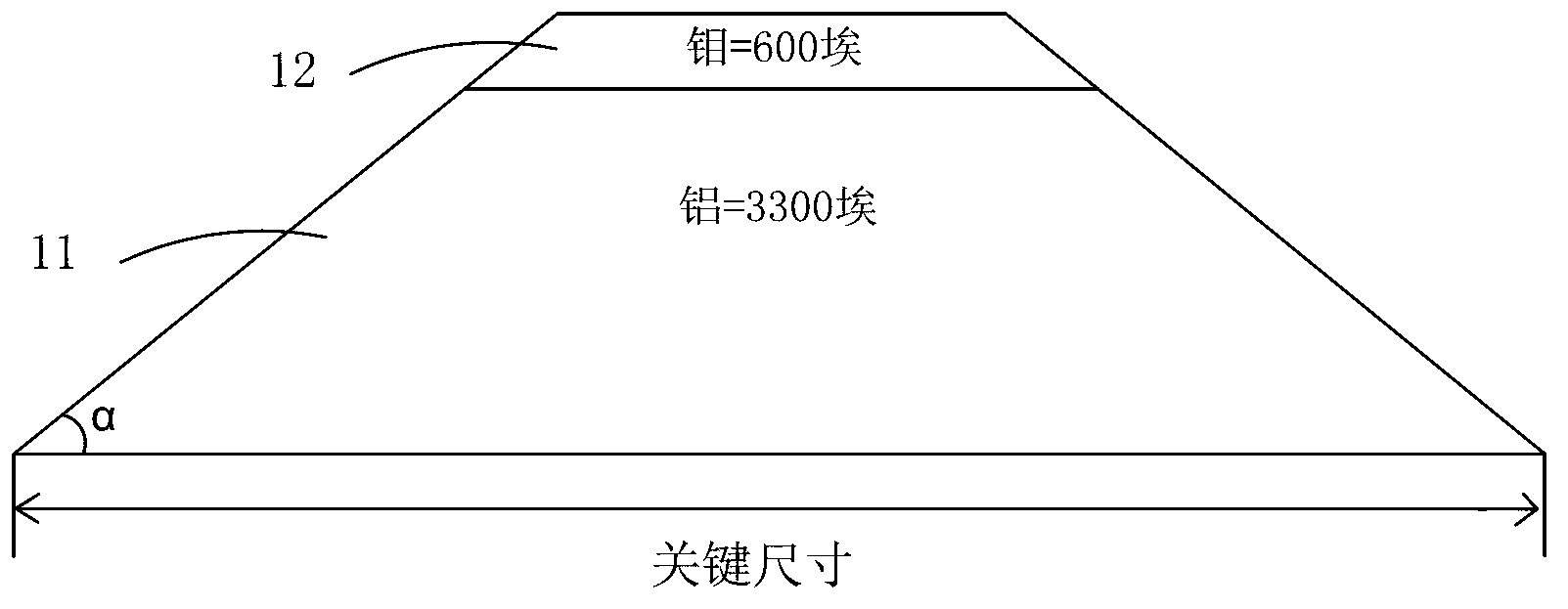

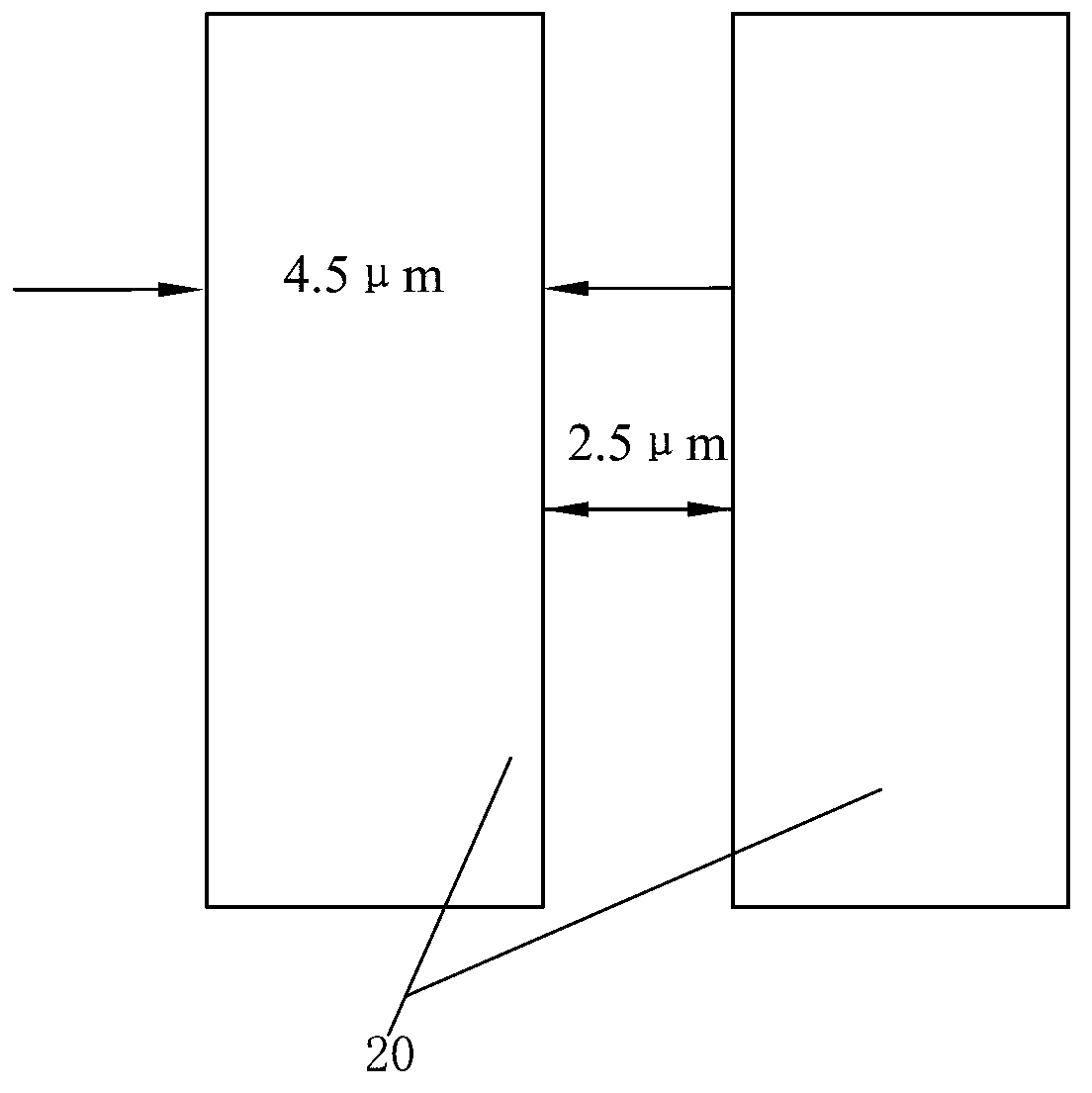

InactiveCN102799005AIncrease critical sizeReduce loadNon-linear opticsLiquid-crystal displayMicrometer

The invention relates to a design of fanout trace in a TFT-LCD (thin film transistor-liquid crystal display) narrow frame design. The design of the fanout trace mainly comprises a first metal layer of first fanout traces and a second metal layer of second fanout traces, wherein the first fanout traces are used for etching to form parallel arrangement; the second fanout traces are used for etching to form another parallel arrangement; the first metal layer and the second metal layer are configured in an up-down parallel manner and are opposite substantially; the width and the fanout pitch of the first fanout traces are equal to the width and the fanout space of the second fanout traces; and projections of the first fanout traces on the second metal layer are in parallel to the second fanout traces and are staggered with the second fanout traces at equal distances. By utilizing the design of the fanout trace in the TFT-LCD narrow frame design, the trace pitch can be less than or equal to 8 micrometers, the fanout height is reduced, metal critical dimensions are increased, the resistance load is reduced, and the narrow frame design is realized.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

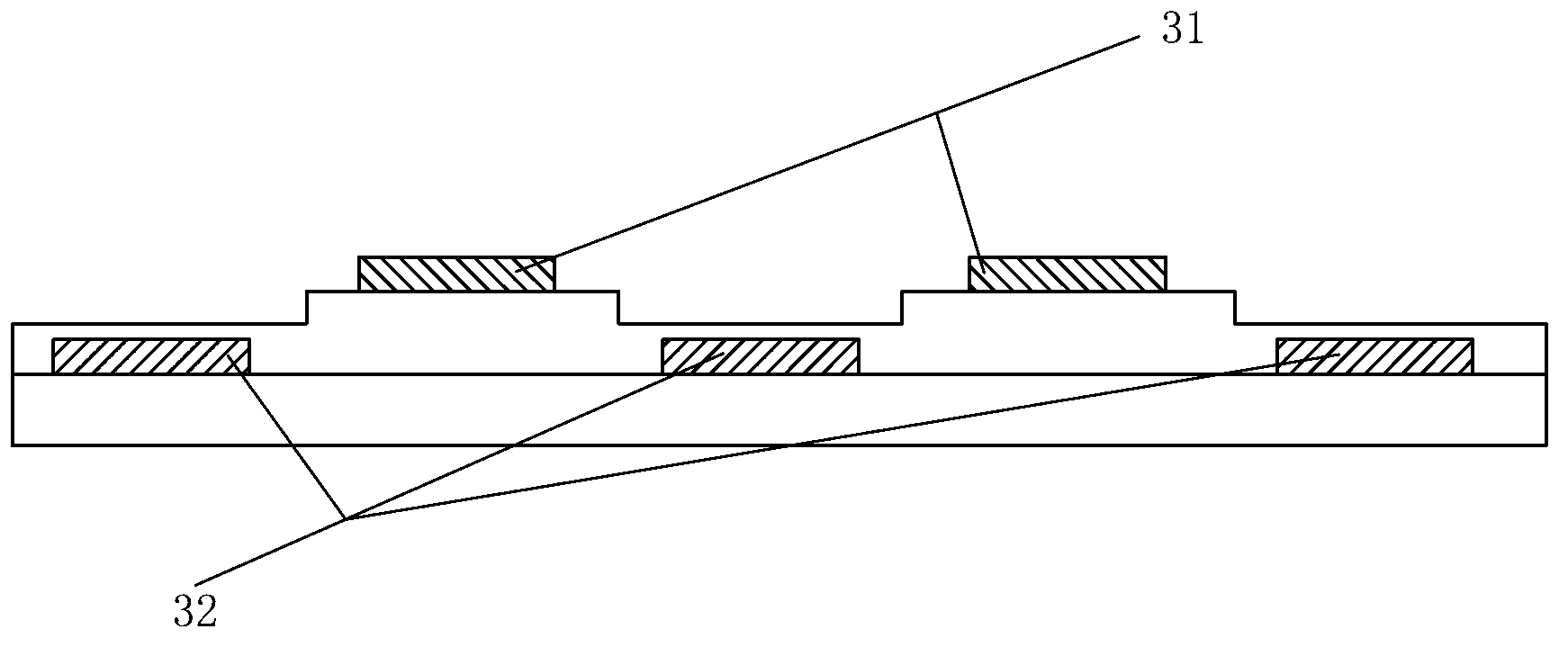

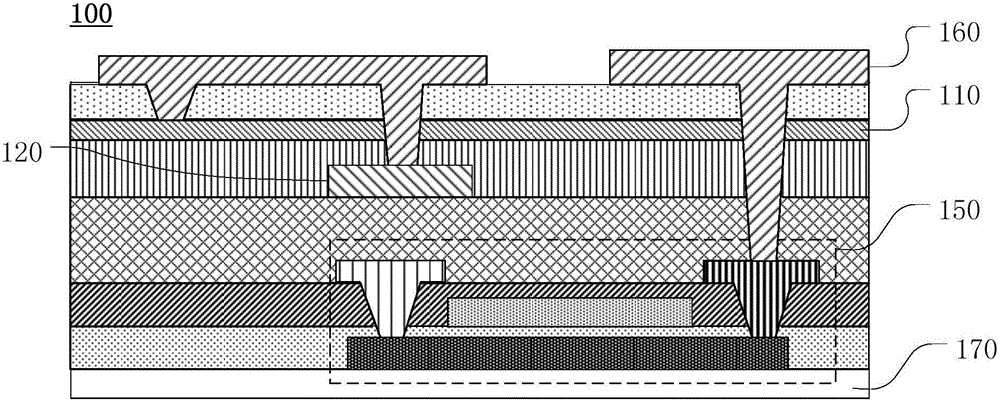

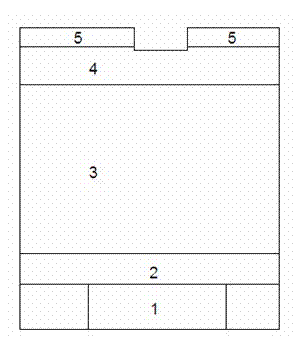

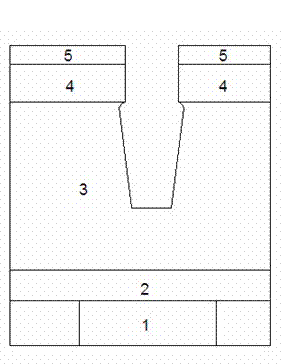

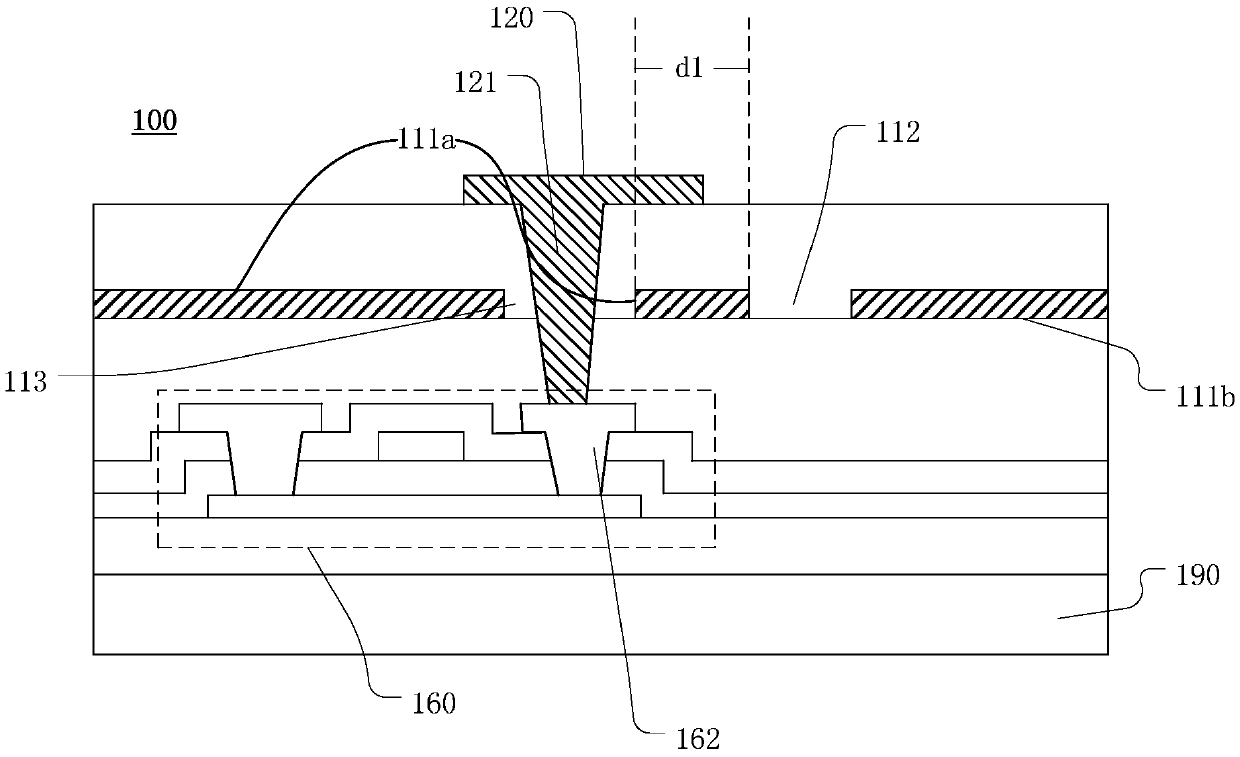

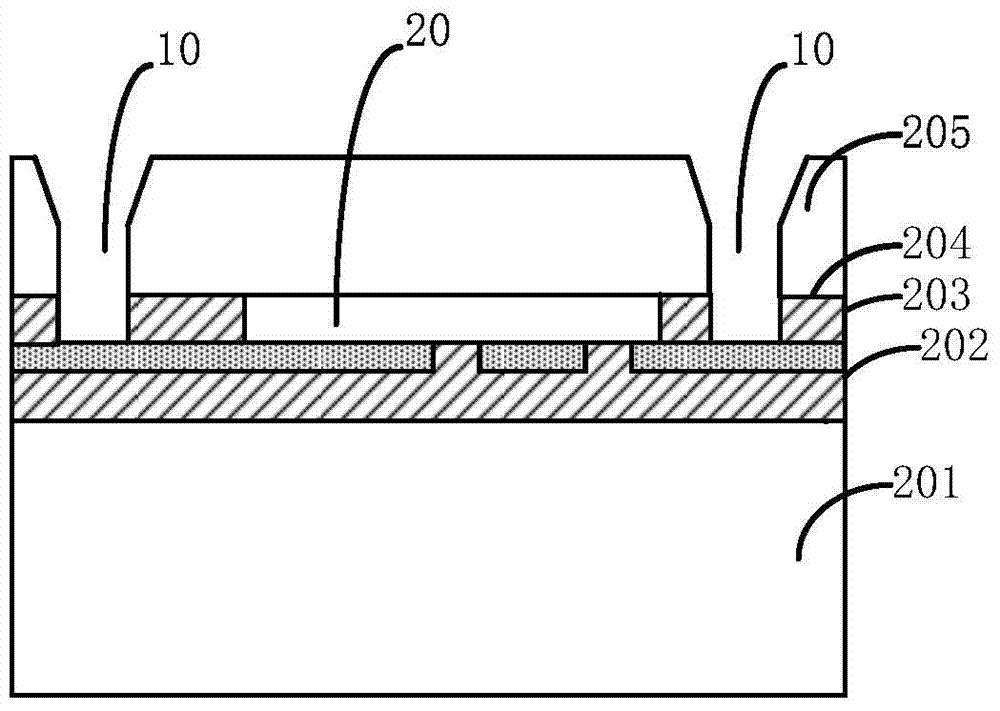

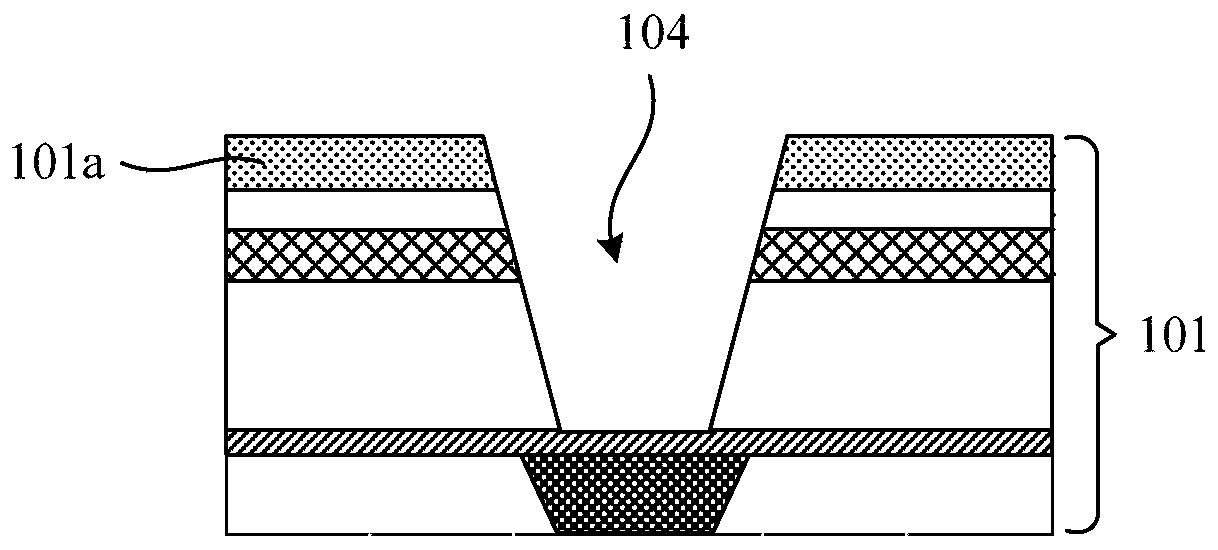

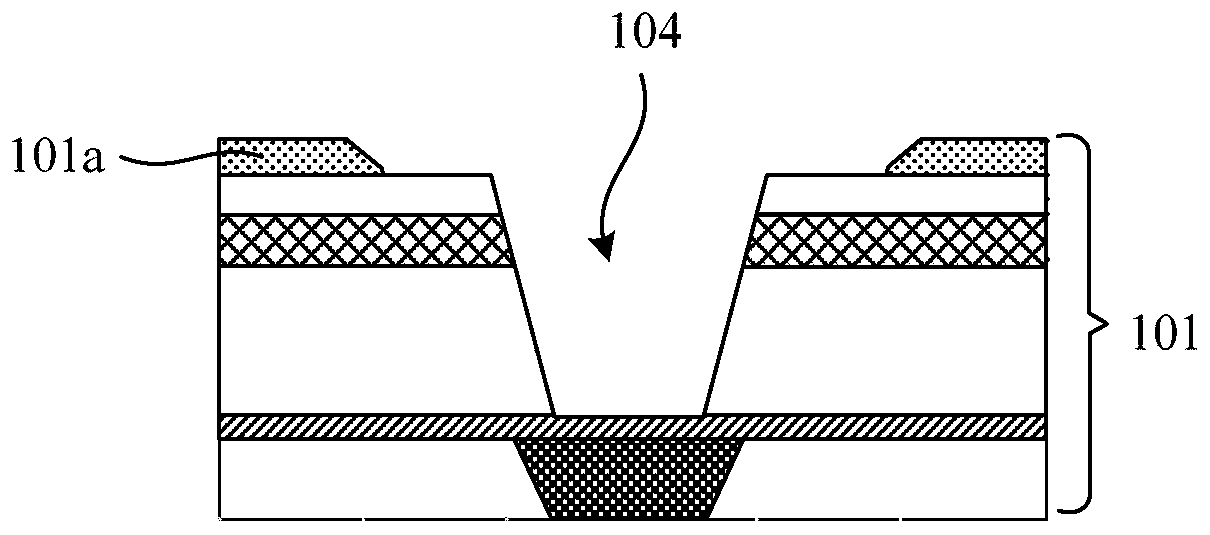

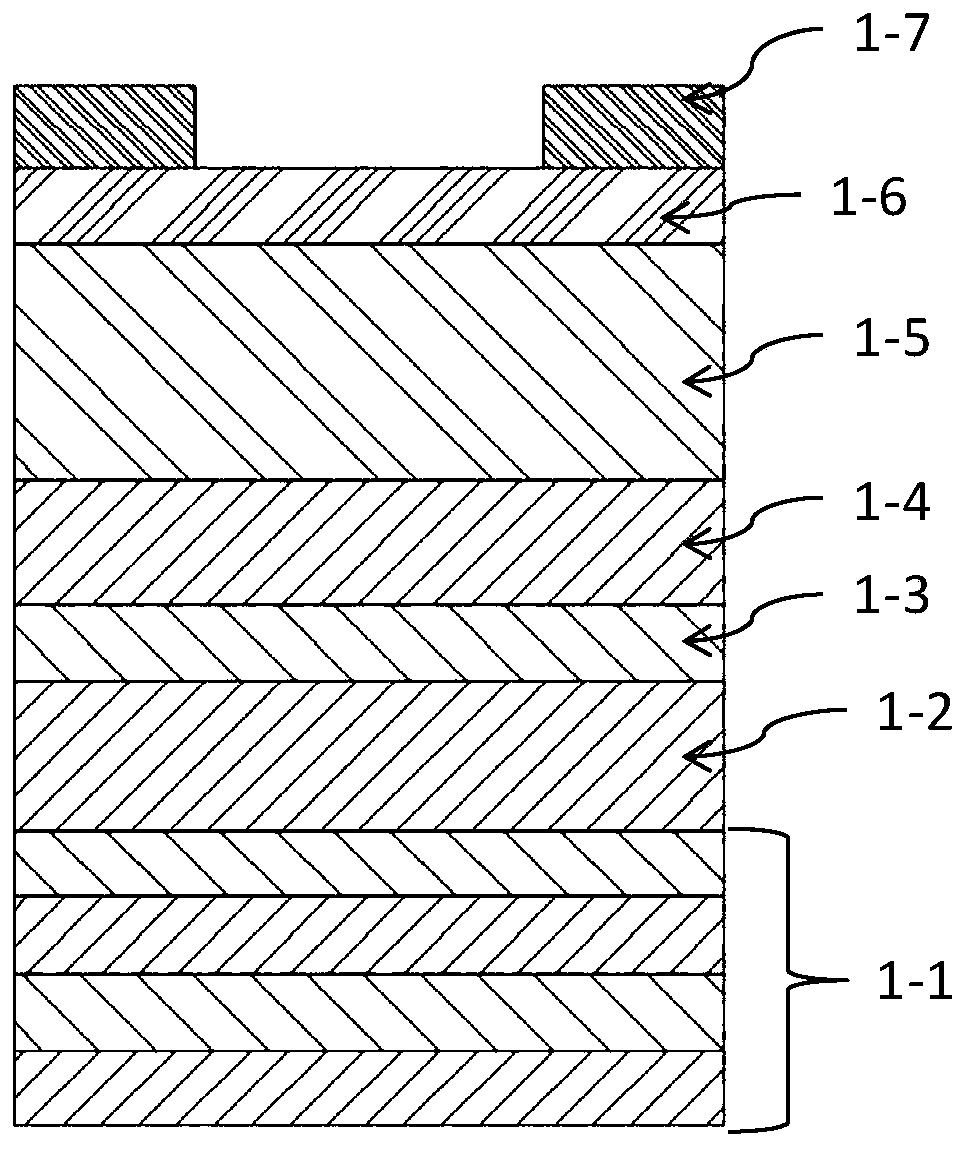

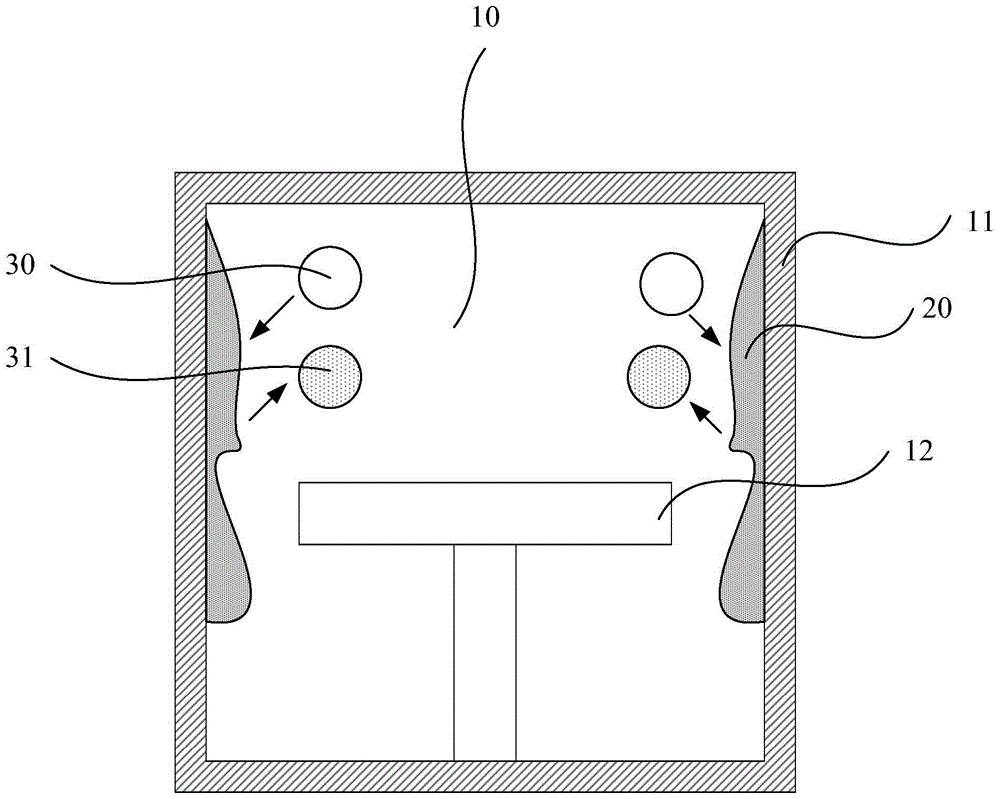

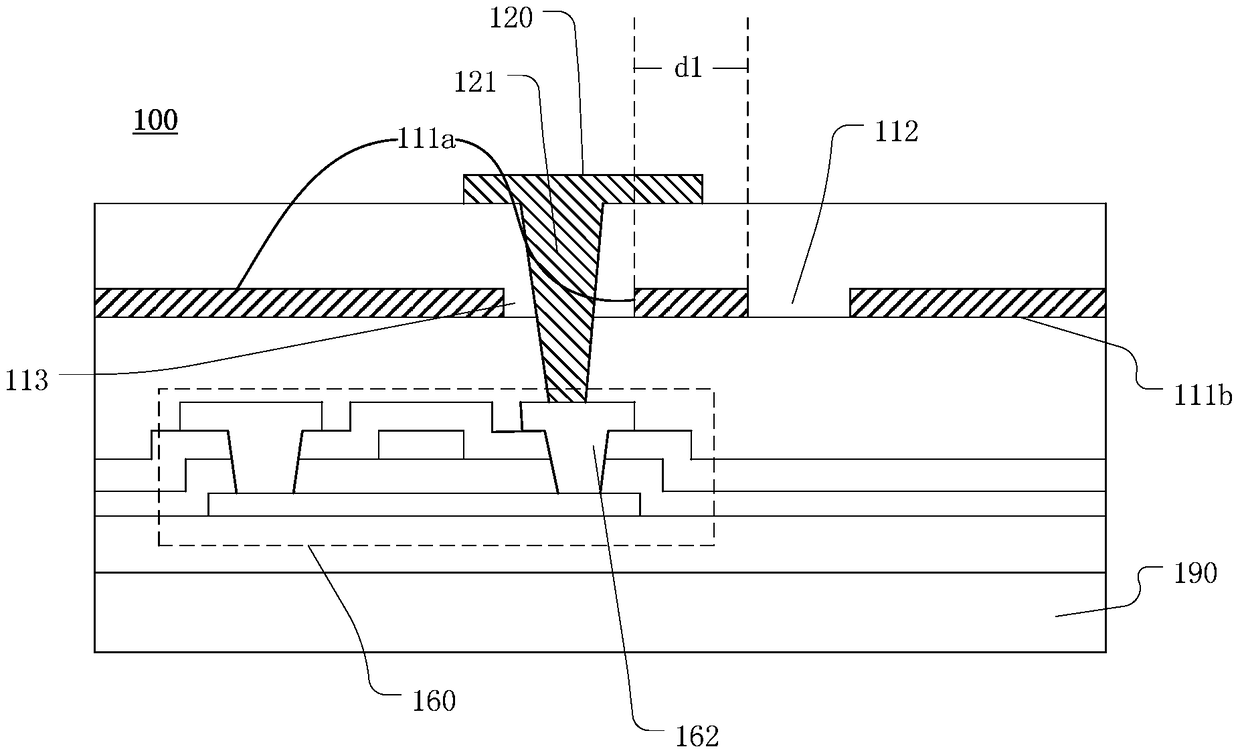

Array substrate and touch display panel

ActiveCN106020581AReduce color mixingLower resistanceInput/output processes for data processingInsulation layerEngineering

The invention provides an array substrate and a touch display panel comprising the array substrate. The array substrate comprises a substrate, multiple switch elements located above the substrate, a first insulation layer located above the switch elements and provided with an upper surface having at least one recess, a touch-control electrode layer located above the switch elements and provided with multiple touch-control electrodes, and a touch-control wiring layer located above the first insulation layer and provided with multiple touch-control wiring. Each touch-control wiring is electrically connected with each touch-control electrode correspondingly and used for connecting a corresponding touch-control electrode to a driving circuit. At least one touch-control wiring comprises at least one protrusion arranged in a corresponding recess. The array substrate and the touch display panel comprising the array substrate help improve display effect.

Owner:XIAMEN TIANMA MICRO ELECTRONICS +1

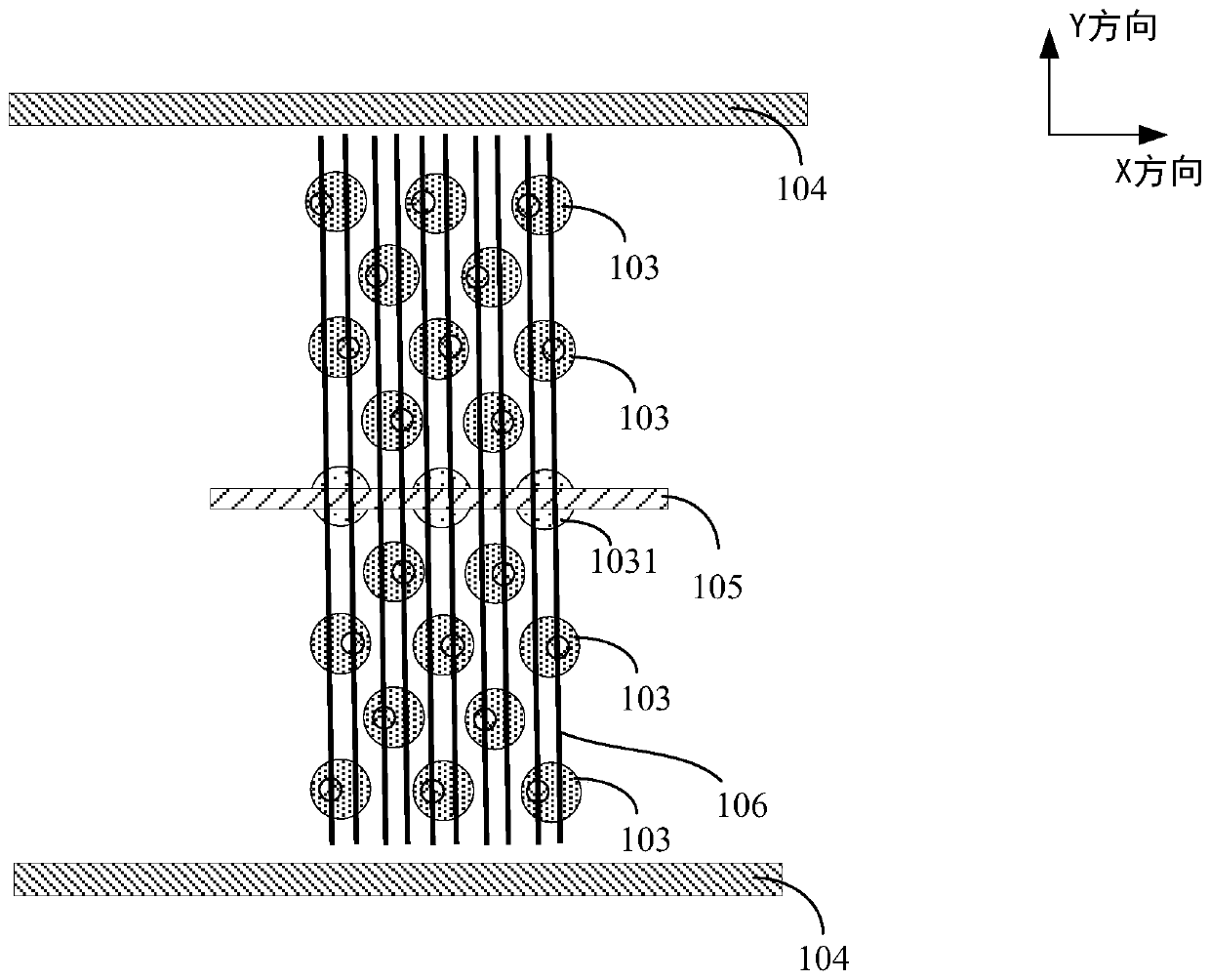

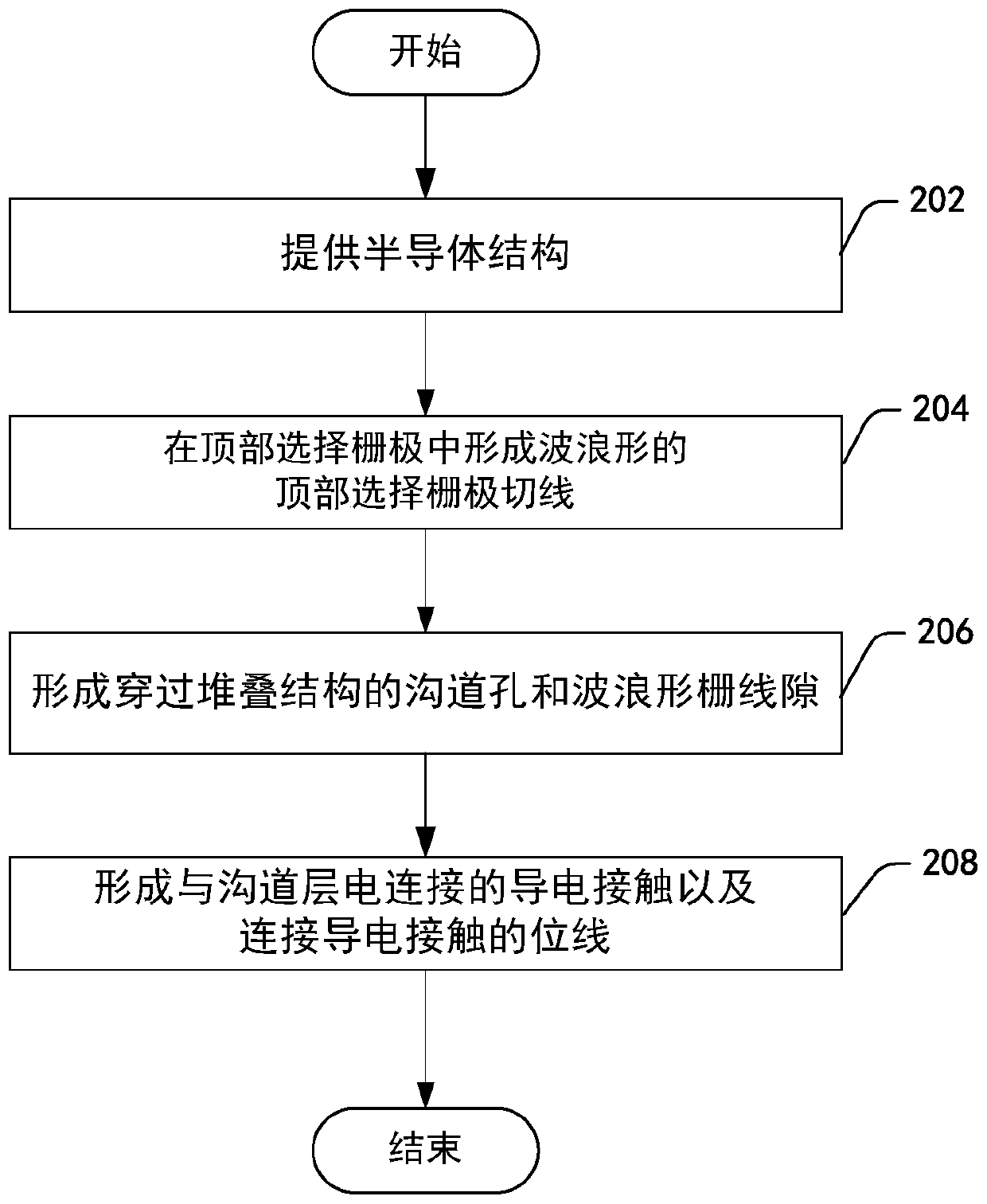

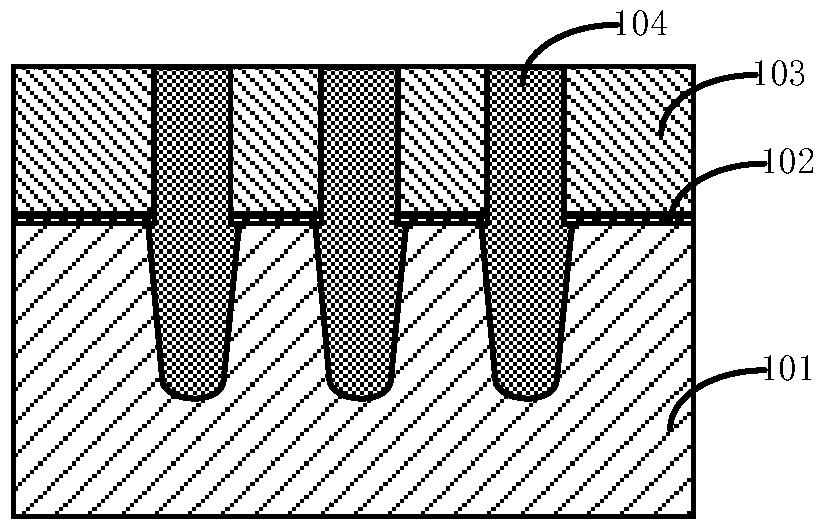

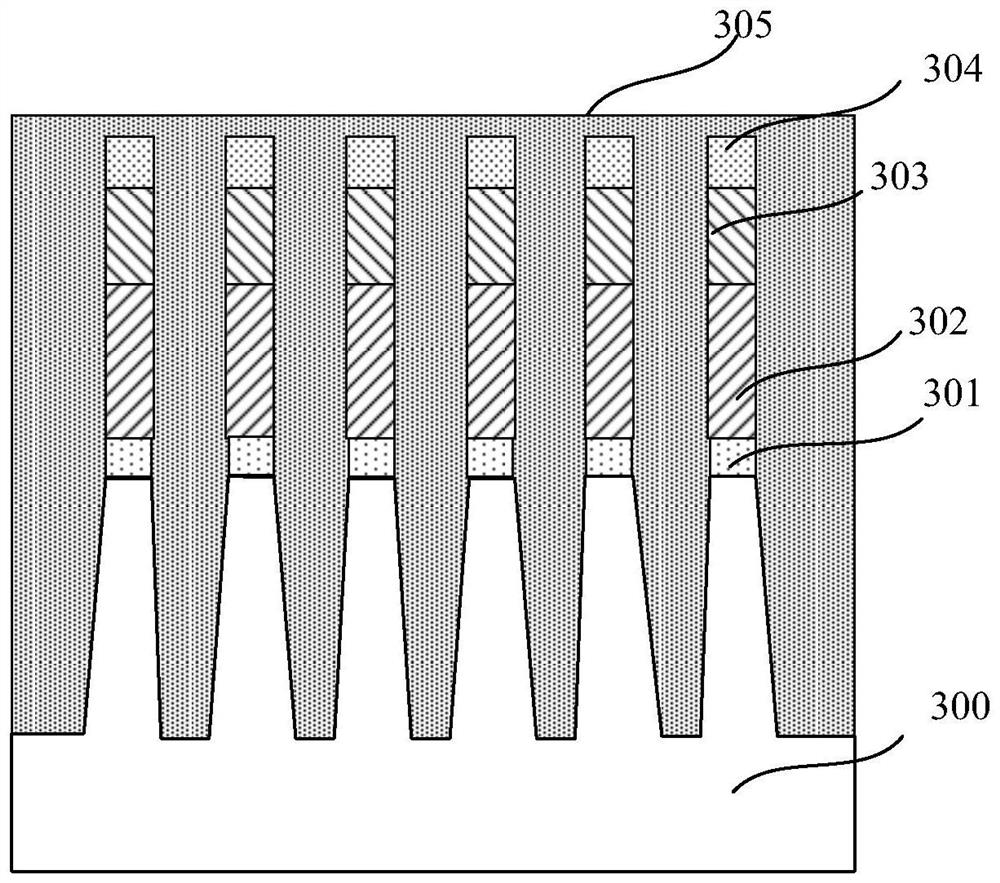

Method for forming three-dimensional memory and three-dimensional memory

InactiveCN109817627AImprove storage densityIncrease capacitySolid-state devicesSemiconductor devicesWave shapeSemiconductor structure

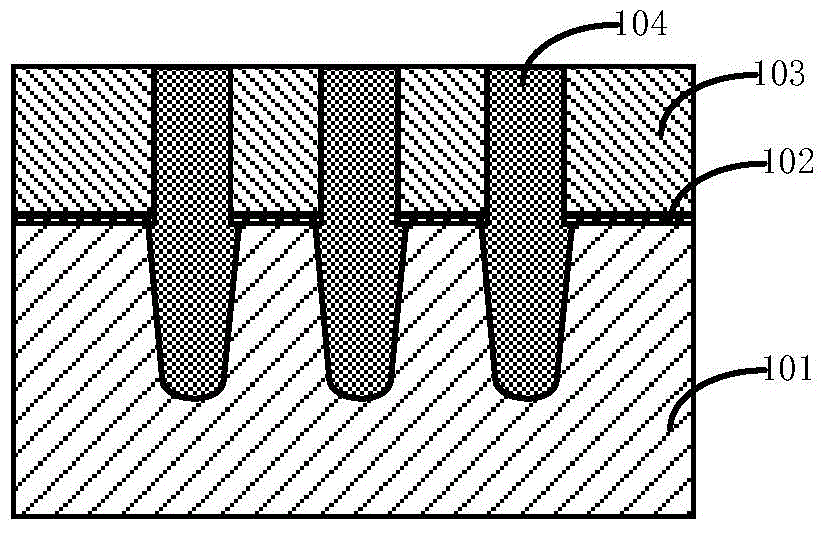

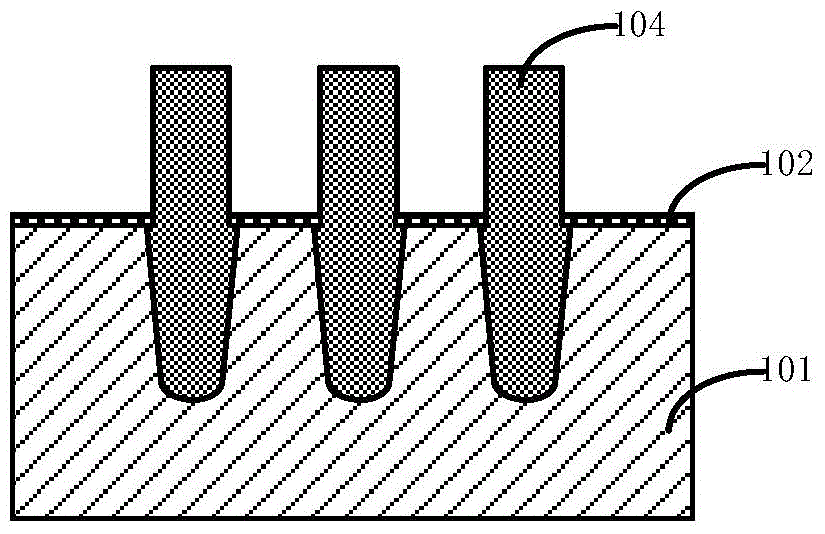

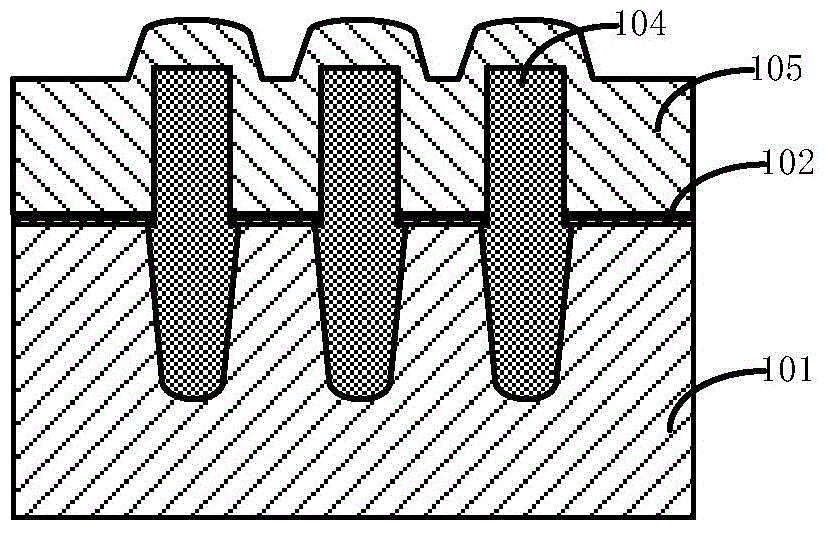

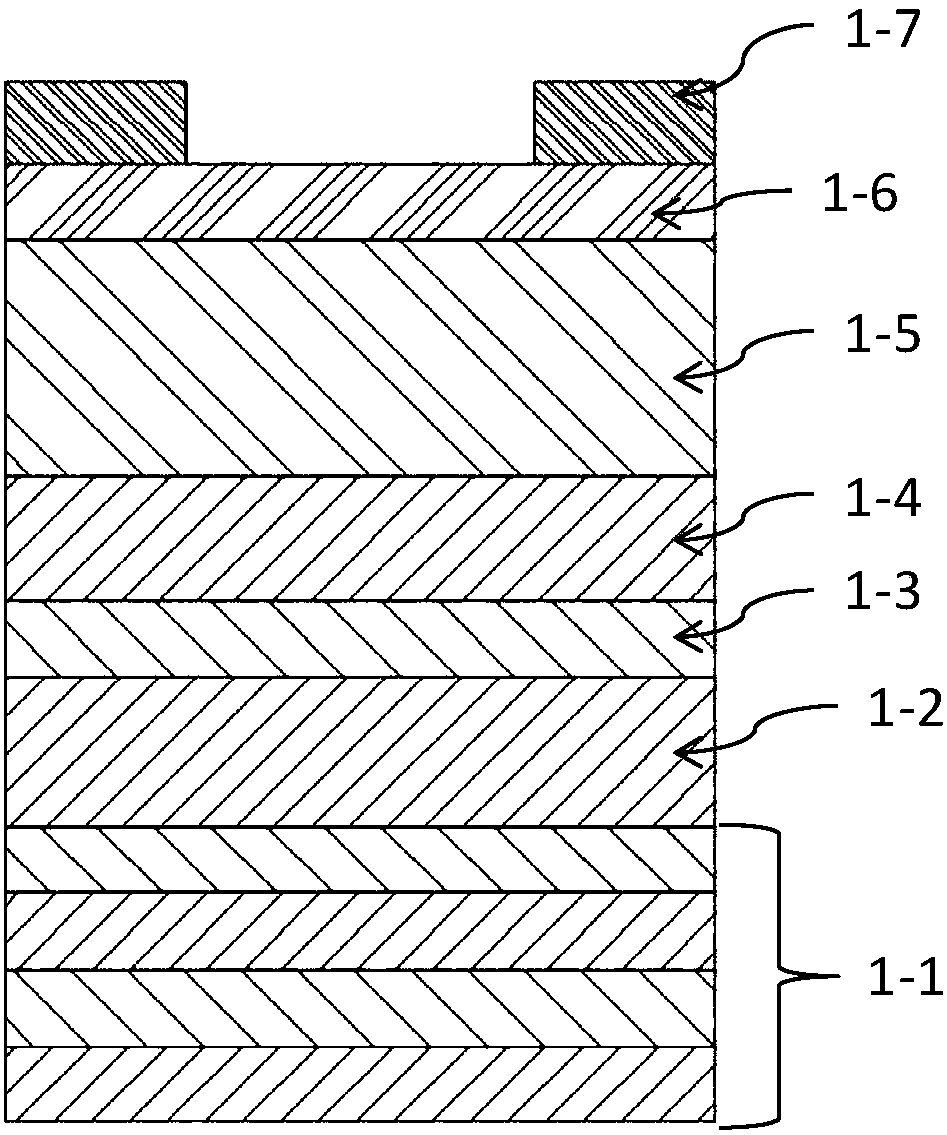

The invention provides a method for forming a three-dimensional memory, comprising: providing a semiconductor structure, wherein the semiconductor structure is provided with a substrate and a stackingstructure positioned on the substrate, and the stacking structure is provided with a top select gate; forming a wavy top select gate-cut in the top select gate, wherein the top select gate is dividedinto a plurality of mutually insulated regions by the top select gate-cut; and forming channel holes and wave-shaped grid line gaps penetrating through the stacking structure, filling the channel holes to form a vertical channel structure, and forming an array common source, wherein the top selection gate-cut is located between the channel holes of the adjacent regions.

Owner:YANGTZE MEMORY TECH CO LTD

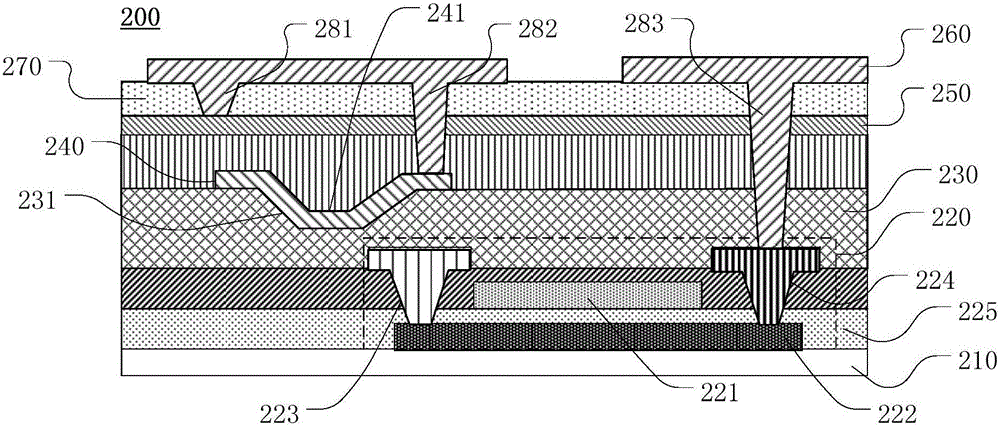

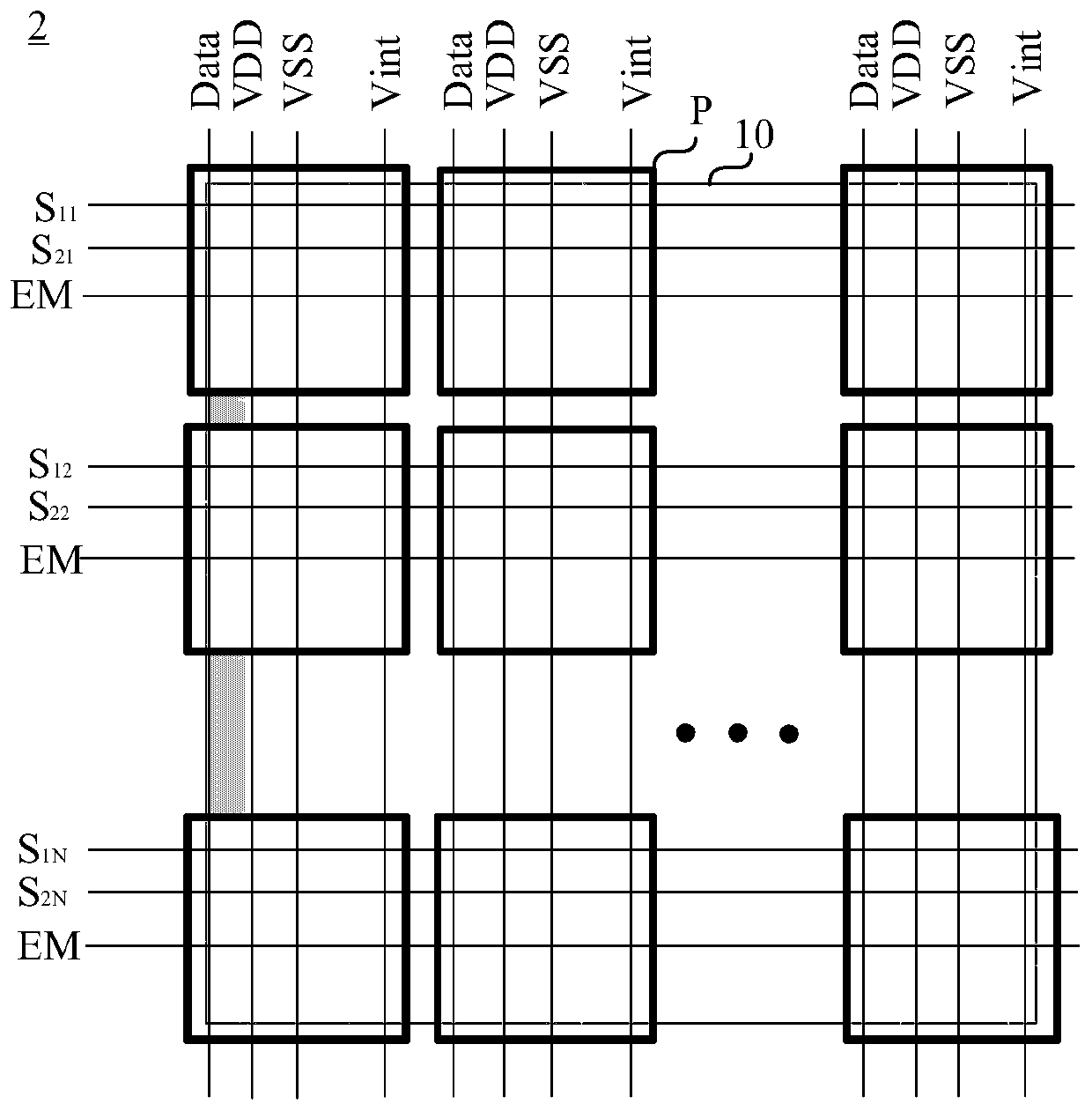

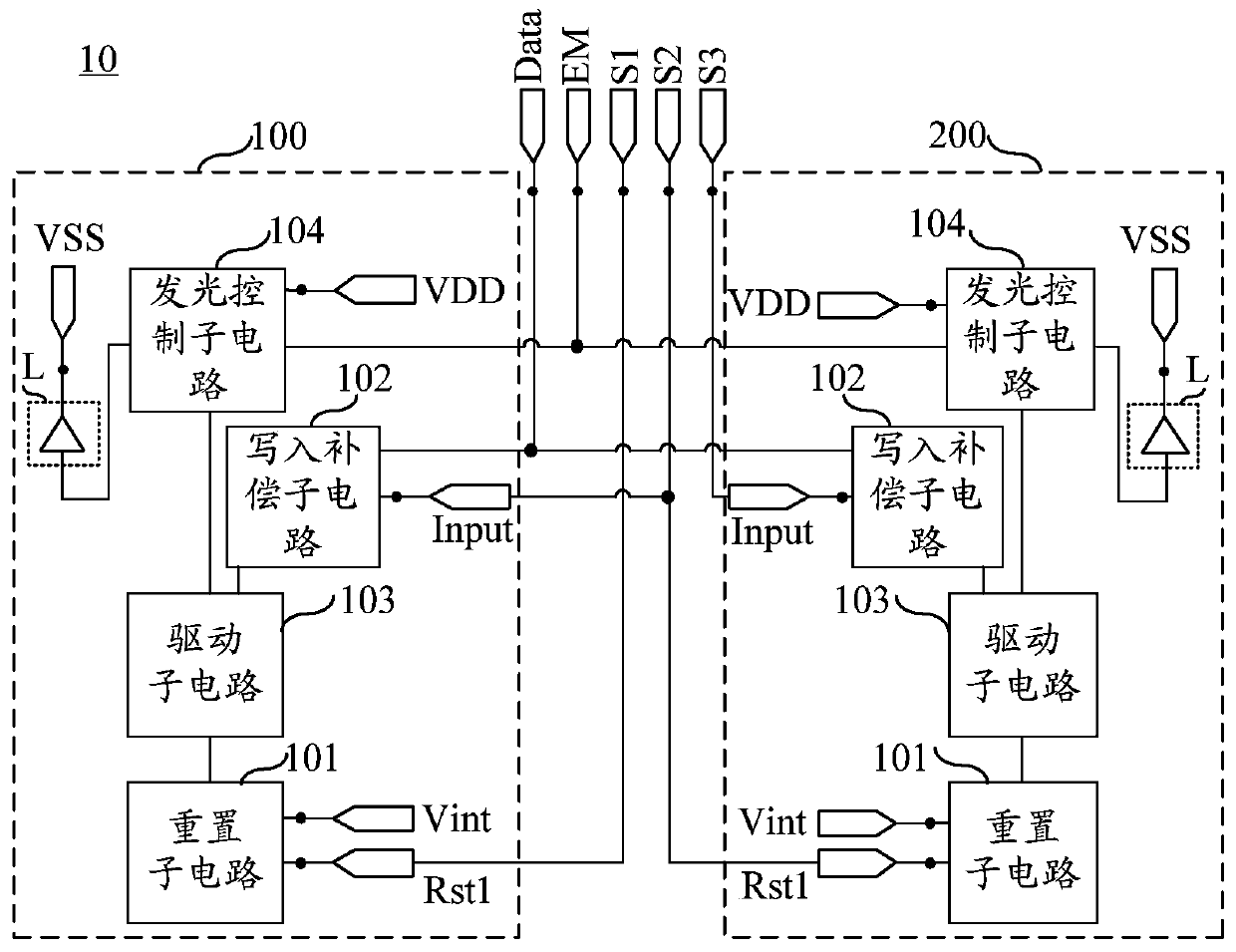

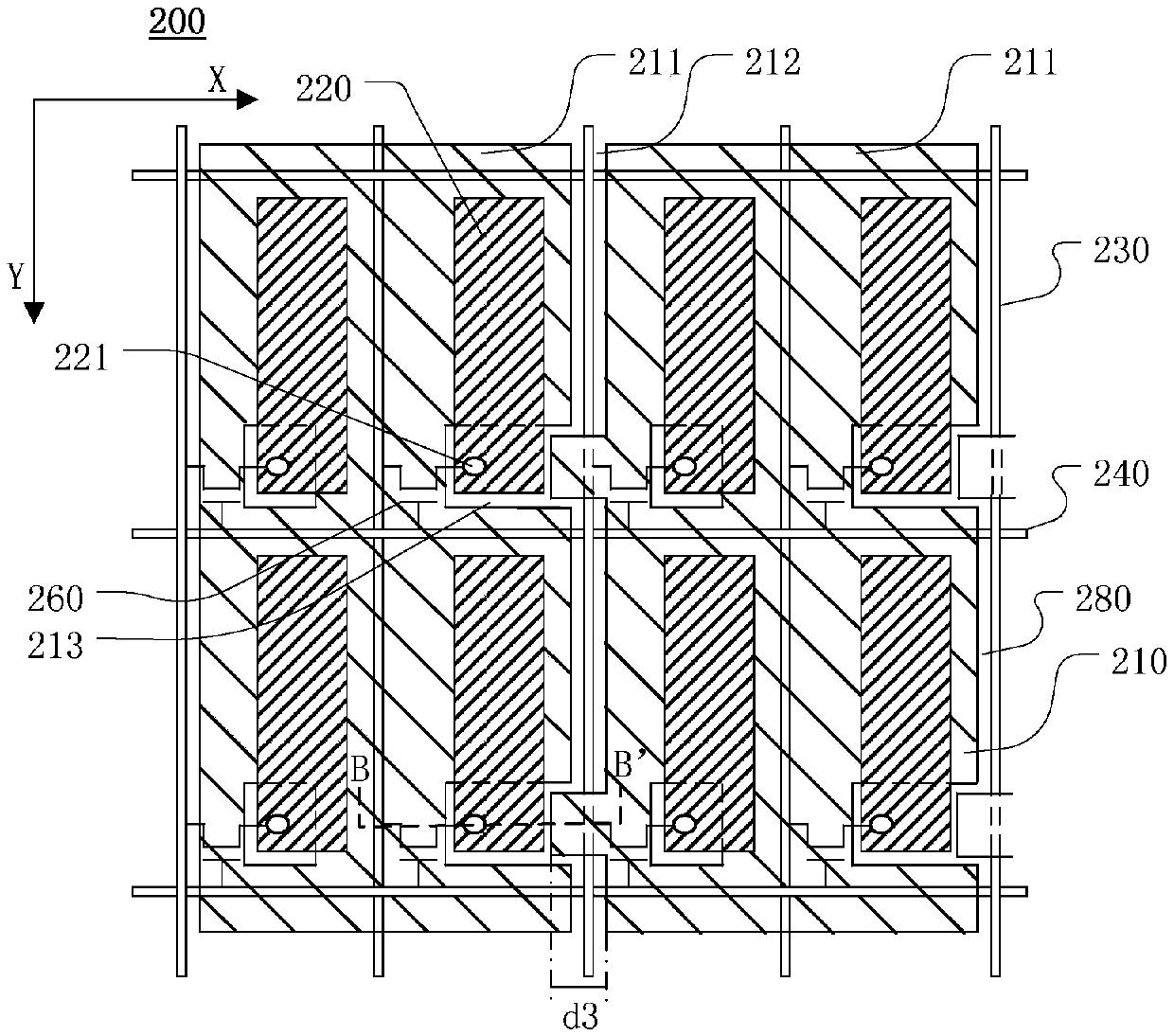

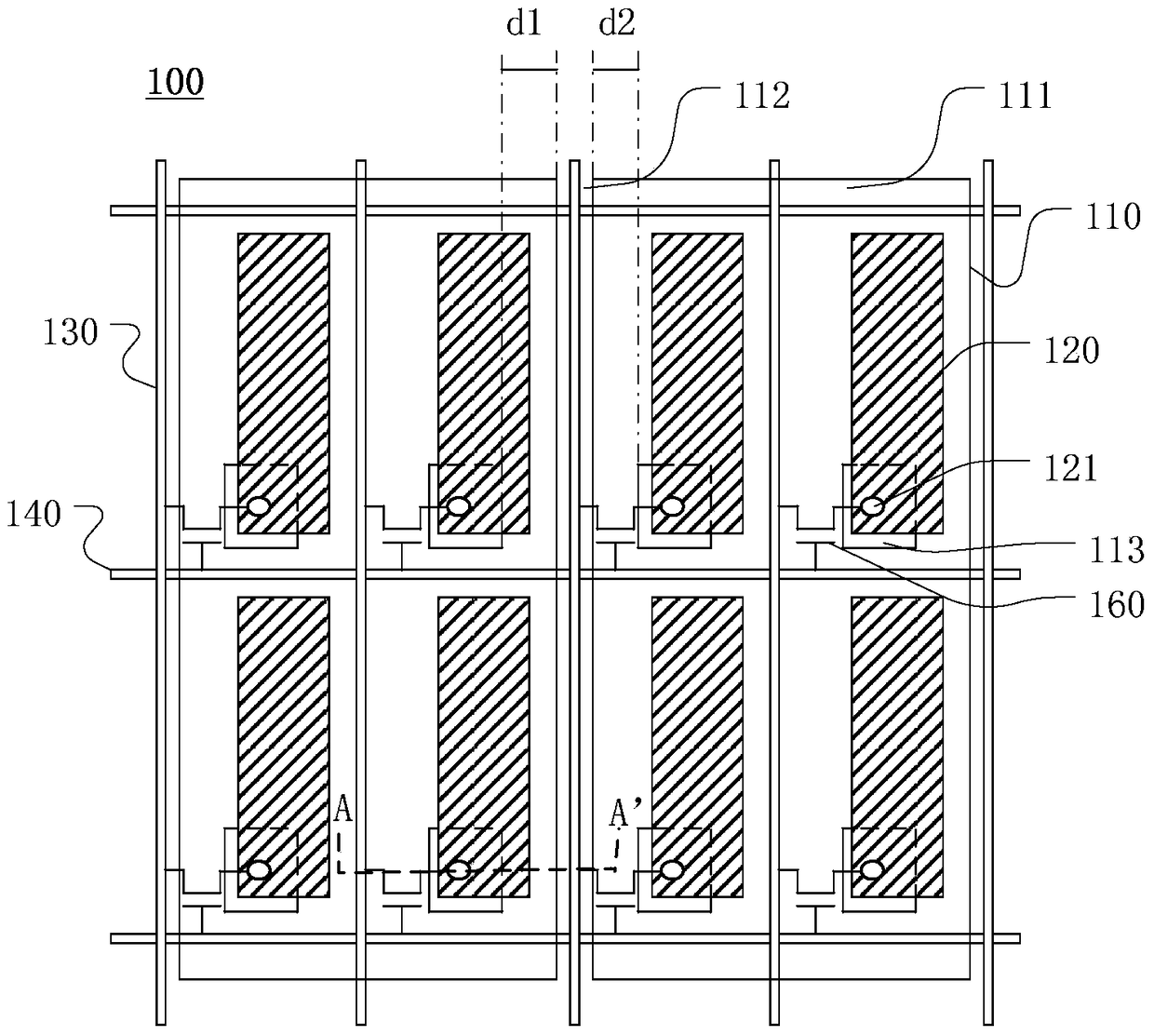

Pixel circuit and driving method thereof, array substrate and display device

PendingCN111063301AReduce in quantityIncrease critical sizeStatic indicating devicesComputer hardwareDriving current

The embodiment of the invention provides a pixel circuit and a driving method thereof, an array substrate and a display device, relates to the technical field of display, and can improve the display effect. The pixel circuit comprises a first sub-pixel circuit and a second sub-pixel circuit, each of the first sub-pixel circuit and the second sub-pixel circuit comprises a reset sub-circuit, a write-in compensation sub-circuit, a driving sub-circuit, a light-emitting control sub-circuit and a light-emitting device; the reset sub-circuit is configured to input the voltage provided by the initialvoltage end to the driving sub-circuit under the control of the first reset control end; the write-in compensation sub-circuit is configured to write a signal output by the data end into the driving sub-circuit under the control of the write-in control end so as to perform threshold voltage compensation on the driving sub-circuit; and the light-emitting control sub-circuit is configured to conducta current path between the first power supply voltage end and the second power supply voltage end under the control of the enabling end, and transmit the driving current provided by the driving sub-circuit to the light-emitting device.

Owner:BOE TECH GRP CO LTD +1

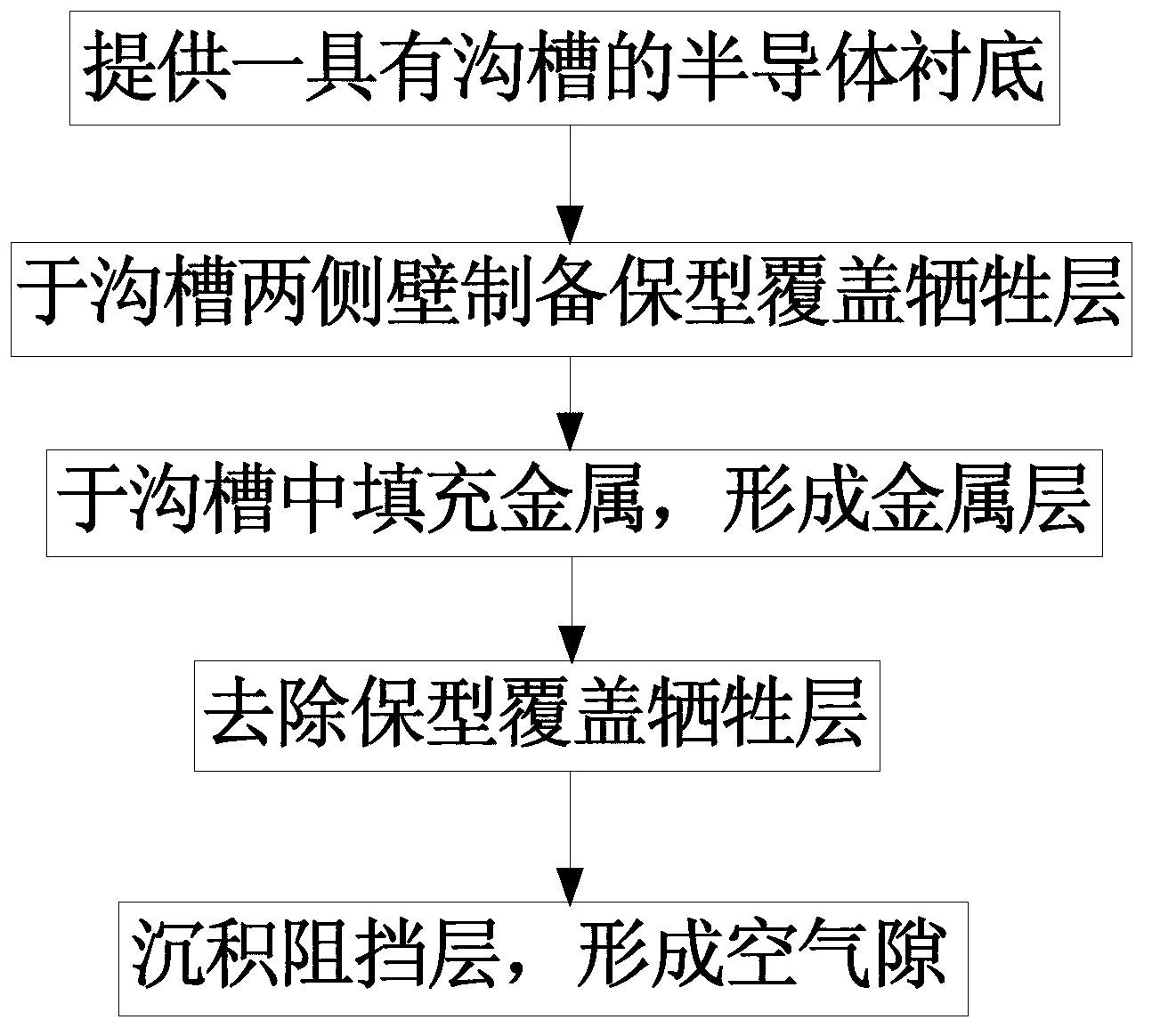

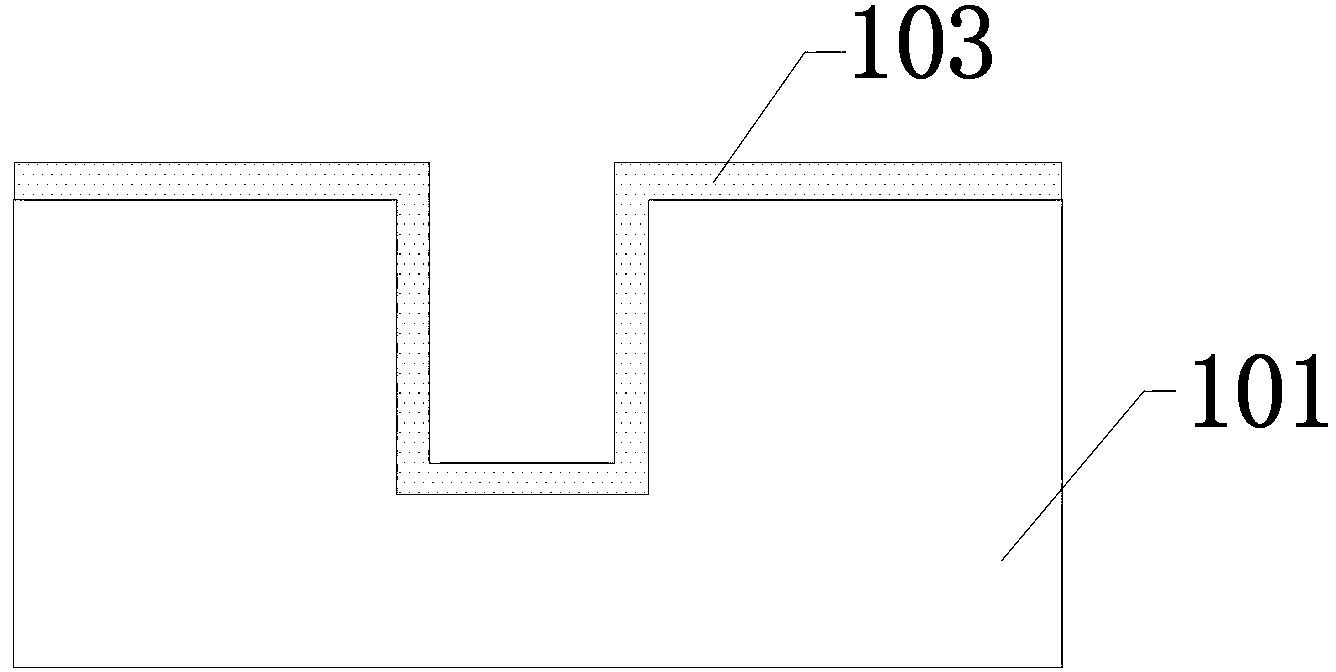

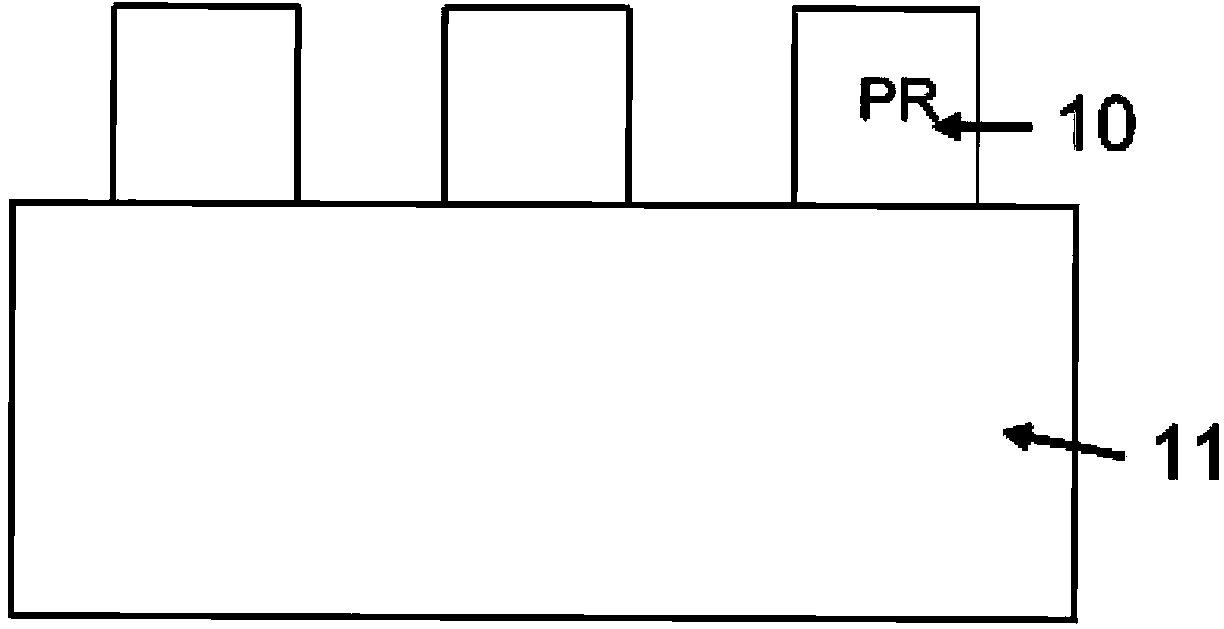

Air gap forming method

InactiveCN103325728AThe process steps are simpleLess consumablesSemiconductor/solid-state device manufacturingMaterial consumptionEngineering

The invention discloses an air gap forming method. According to the method, the critical size of a cannelure is required to be larger than the critical size required by technology requirements when technological design of the cannelure is carried out, a mould-keeping covering layer is deposited in the cannelure in a large critical size, a mould-keeping covering layer on the bottom of the cannelure and a mould-keeping covering layer on the upper surface of a semiconductor substrate are removed, a mould-keeping covering sacrificial layer is reserved, the subsequent filling process is continued, and finally the mould-keeping covering sacrificial layer is removed and a blocking layer is deposited on the top of the cannelure to obtain an air gap structure. According to the air gap forming method, the number of processing steps is small, material consumption is low, critical sizes of a through hole and the cannelure are increased during photoetching and etching while RC delay is improved, technological difficulty is reduced, production efficiency is improved, and production cost is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Etching method for silicon nitride high depth-to-width ratio hole

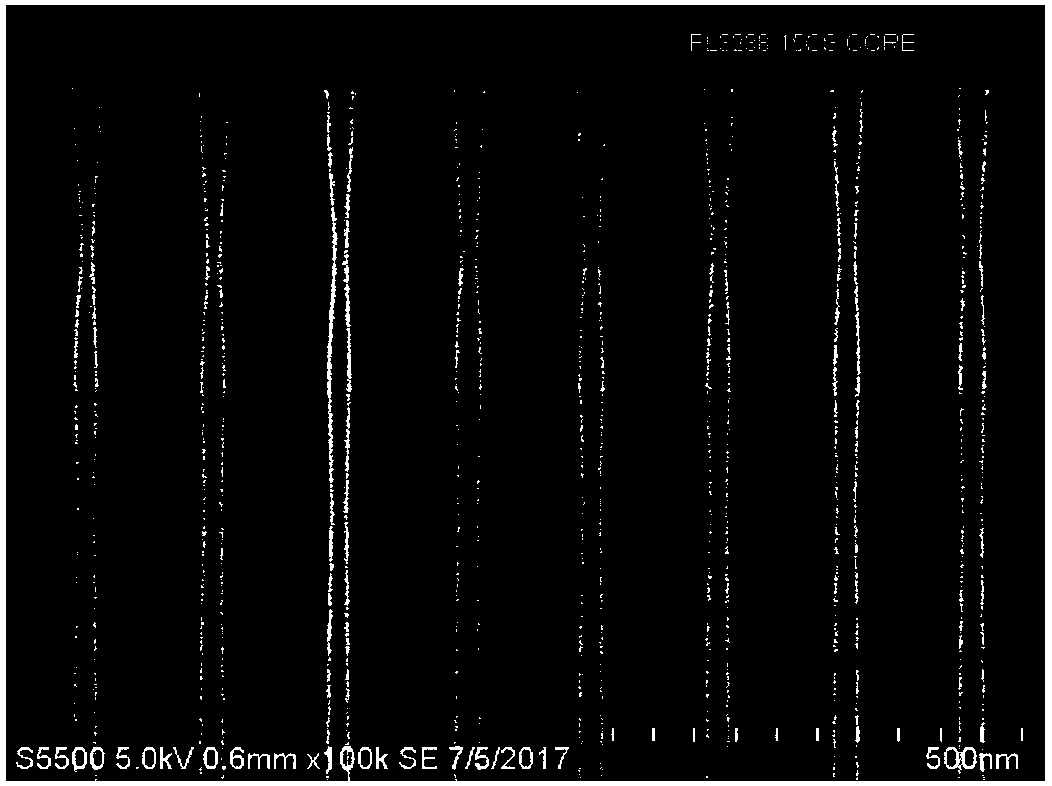

ActiveCN103531464AAchieve anisotropyAdjust etch topographySemiconductor/solid-state device manufacturingEtchingPlasma technology

The invention discloses an etching method for a silicon nitride high depth-to-width ratio hole. The method comprises: first of all, placing a semiconductor device of a silicon nitride film, already forming the graph needed by a semiconductor, into en etching cavity; then using a dry-method plasma technology, letting in a high carbon chain molecule fluorocarbon-based gas, an oxidizing gas, a dilution gas and a fluorocarbon-based gas containing hydrogen, adding radio frequency power and exciting plasma; and after a plasma stabilization step, performing etching of the silicon nitride film until the etching morphology, the hole diameter size and the depth of a high depth-to-width ratio hole reach requirements. According to the invention, the silicon nitride film is etched by using the unique fluorocarbon-based gas, through adjusting gas component and power size, the deposition amount of fluorocarbon polymers on the side wall of the deep hole can be controlled, the key dimensions of the hole can be prevented from becoming larger, and polymers already deposited at the bottom of the deep hole can be removed so as to ensure that the etching can be continued, thus the etching morphology of the hole can be adjusted.

Owner:SOI MICRO CO LTD

Method for improving etched via bottom critical dimension of 40 nm dual damascene structure

InactiveCN102881641AProtect the side wallsIncrease critical sizeSemiconductor/solid-state device manufacturingDielectricCritical dimension

The invention provides a method for improving etched via bottom critical dimension (VBCD) of a 40 nm dual damascene structure. The method comprises the following steps: etching a groove, forming a protective layer of side walls of a ULK (Ultra-low dielectric constant) layer, and forming vias of an exposed metal layer. According to the method provided by the invention, the side walls of the ULK layer can be protected, and the VBCD can be enlarged in the step for etching the groove in the 1*DD AIO (all in one) process.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

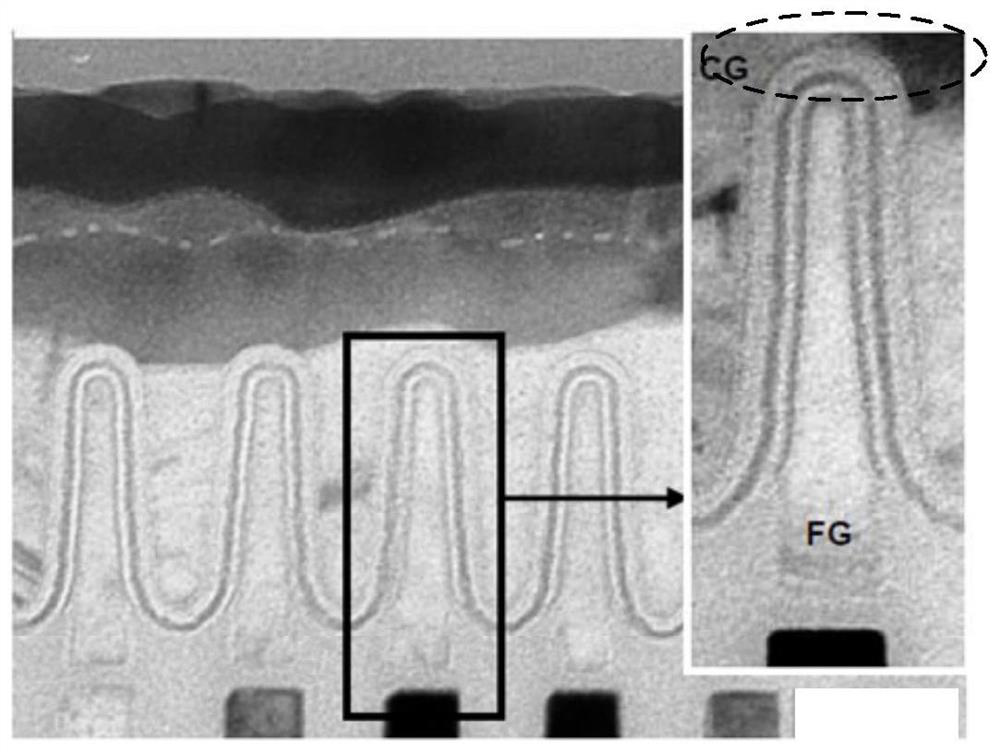

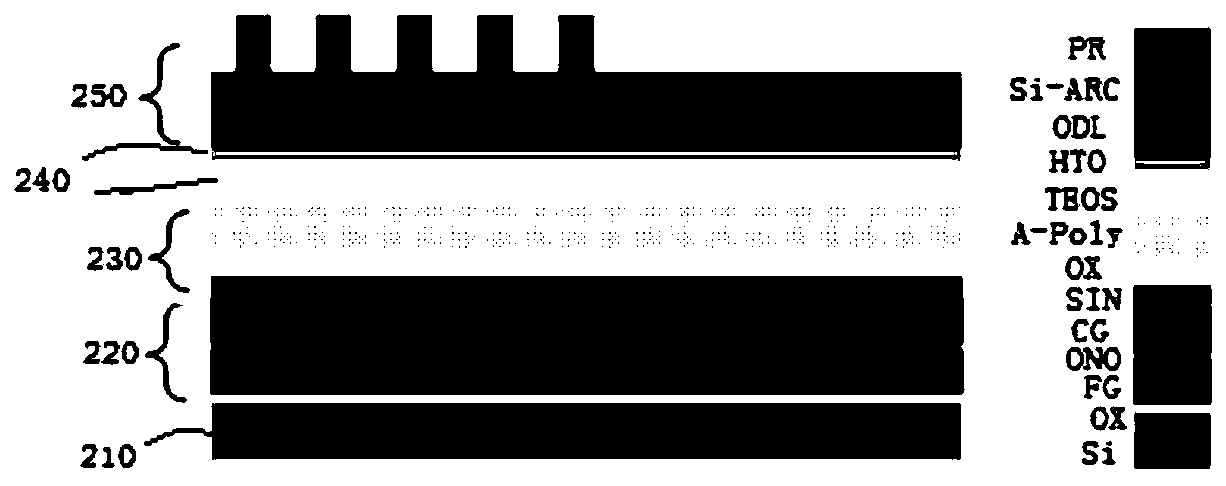

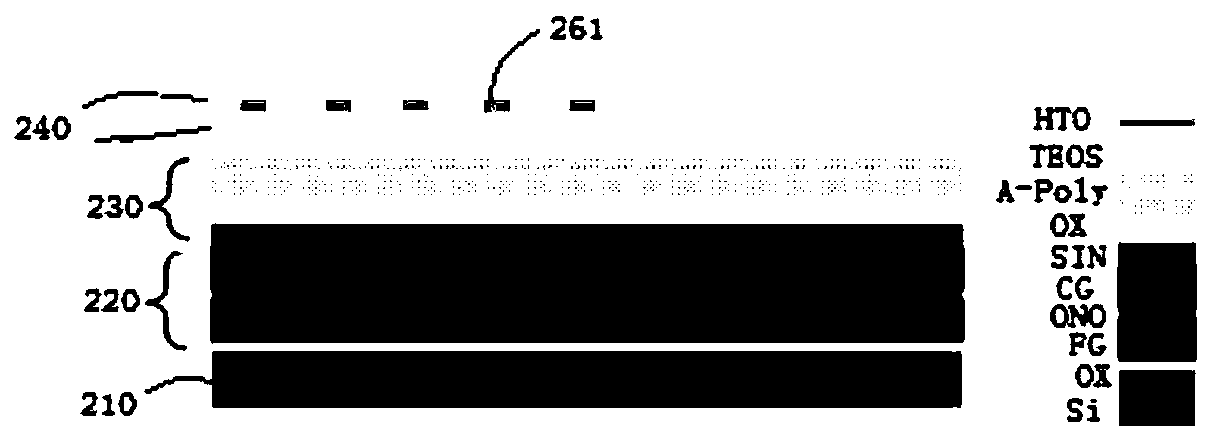

Embedded flash memory, preparation method thereof, and electronic device

ActiveCN105575968AAvoid it happening againIncreased process windowSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectron

The invention relates to an embedded flash memory, a preparation method thereof, and an electronic device. The method comprises that a substrate is provided, an active region isolated by a shallow trench isolation (STI) oxide is formed in the substrate, and the top of the STI oxide is higher than the surface of the substrate; a floating gate material layer is deposited to cover the active region and the STI oxide; the floating gate material layer is flattened to expose the surface of the STI oxide; the floating gate material layer is etched back to reduce the thickness of the floating gate material layer and expose the STI oxide of certain height; the exposed STI oxide is etched back to reduce the key size of the exposed STI oxide; the floating gate material layer is re-deposited till the top of the STI oxide to surround the STI oxide and flatten the floating material layer; and the part whose key size is reduced of the STI oxide is removed to form a T-shaped floating gate on the active region.

Owner:SEMICON MFG INT (SHANGHAI) CORP

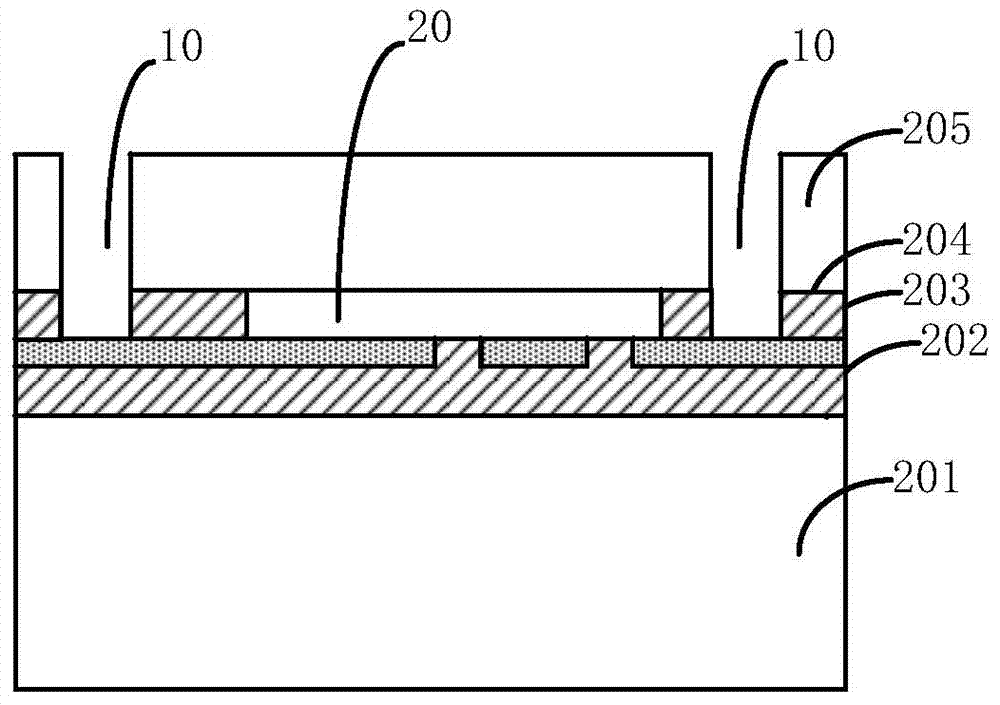

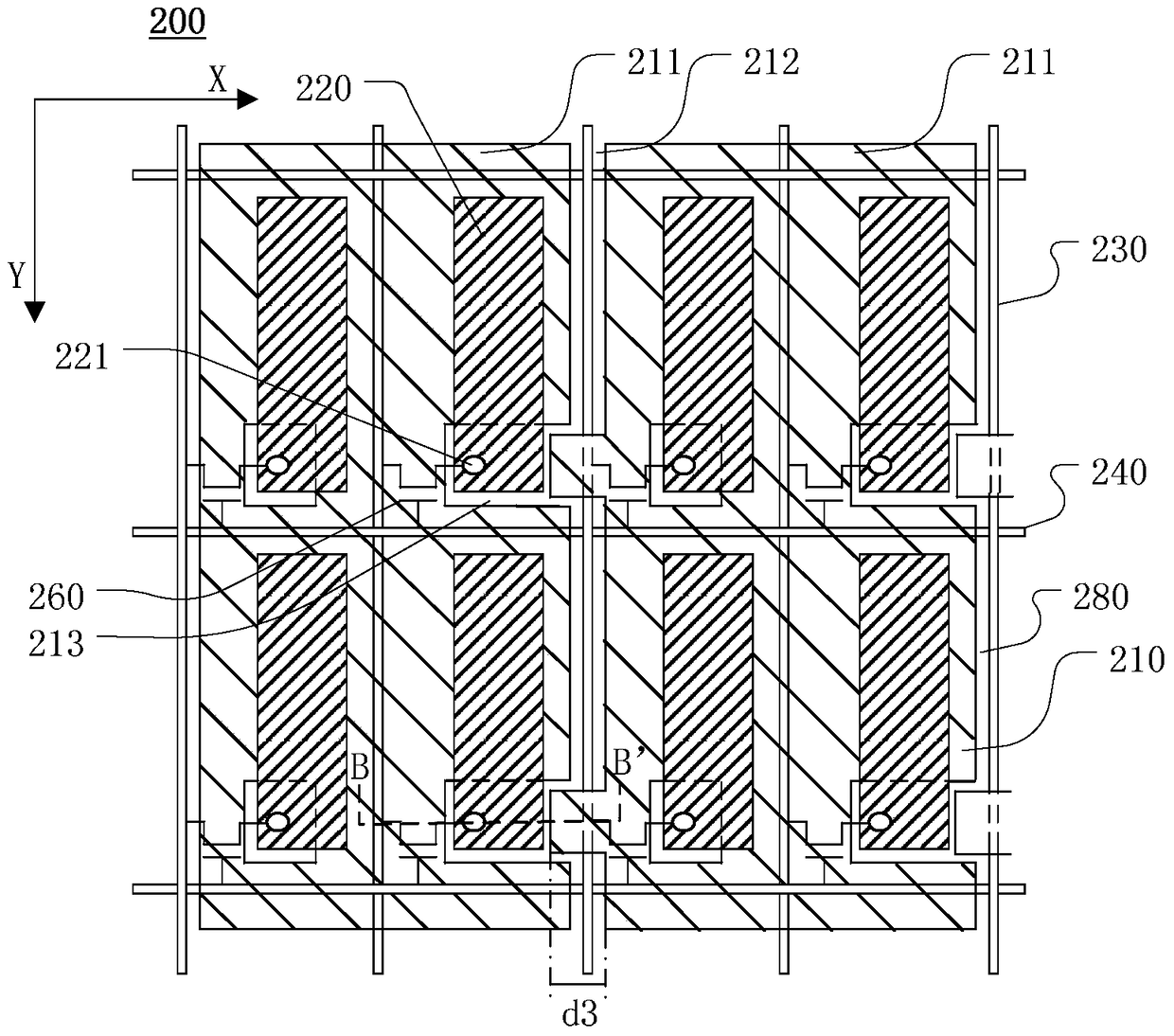

Touch display panel

ActiveCN105511707AEasy to detectImprove the display effectInput/output processes for data processingTransistorPhysics

The invention provides a touch display panel, which comprises a first substrate, a thin-film transistor, a pixel electrode layer and a common electrode layer, wherein the thin-film transistor is arranged on the first substrate; the pixel electrode layer is arranged on the thin-film transistor and is connected with a drain or a source of the thin-film transistor through a contact hole; the common electrode layer is arranged on the first substrate and below the pixel electrode layer, and is divided into a plurality of common electrodes; a slit is formed between each two adjacent common electrodes; and the slits are connected with contact holes in the slits. According to the touch display panel provided by the invention, the touch detection capability and the display effect are improved.

Owner:SHANGHAI AVIC OPTOELECTRONICS +1

Preparation method for motion sensor

ActiveCN104743501AIncrease critical sizeEasy to fillDecorative surface effectsChemical vapor deposition coatingCMOSInsulation layer

The invention relates to a preparation method for a motion sensor. The method includes: providing a base, on which a CMOS device is formed; forming a bottom electrode on the base and an MEMS substrate positioned above the bottom electrode, and forming a cavity between the bottom electrode and the MEMS substrate; etching the MEMS substrate to the bottom electrode to form a deep through hole, thereby exposing the bottom electrode; etching the top of the deep through hole to expand the key size of the deep through hole top opening; forming an insulation layer on the side wall of the deep through hole; and depositing a metal material in the deep through hole, and then conducting etching to remove the metal material deposited at the deep through hole top so as to maintain a large key size of the opening. According to the method provided by the invention, no hole is formed in the filling process, and the device yield is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

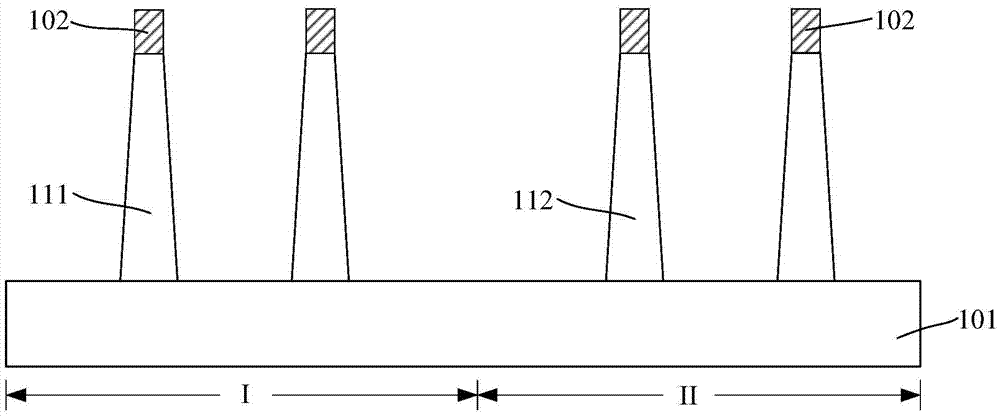

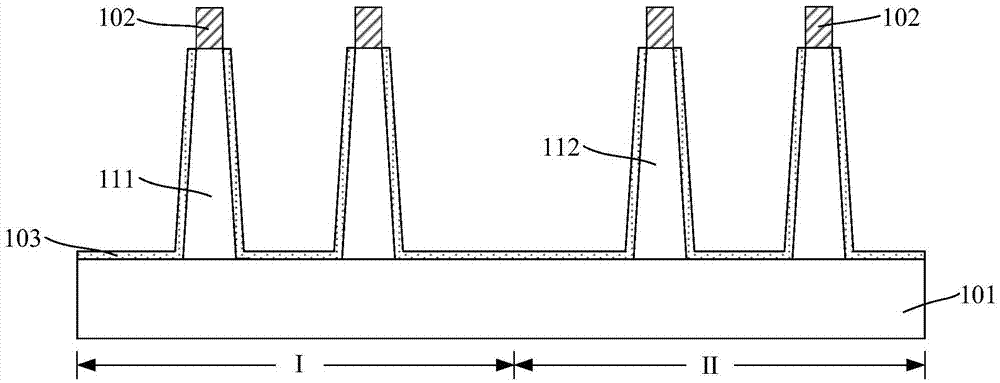

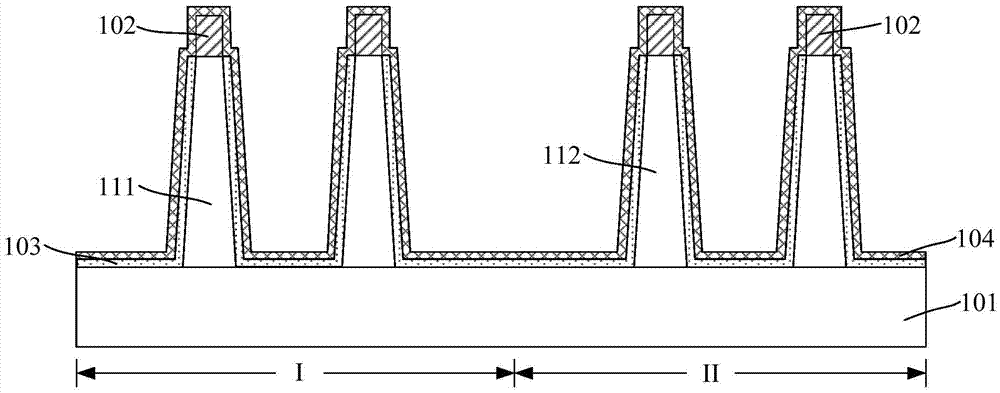

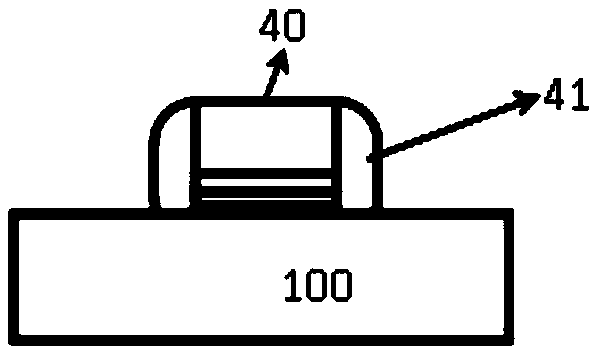

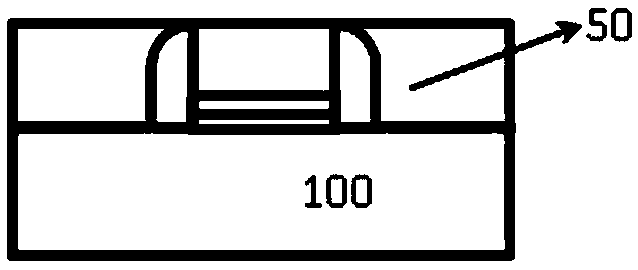

Formation method of fin field-effect transistor

ActiveCN106952873AImproved design redundancyPlay a blocking roleSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerIsolation layer

A formation method of a fin field-effect transistor comprises the steps of forming lining oxide layers on a surface, a surface of a side wall of a first fin part and a surface of a side wall of a second fin part; forming an insulation blocking layer on a surface of the lining oxide layer on a first region; depositing a precursor material layer on a surface of the insulation blocking layer and a surface of the lining oxide layer on a second region; performing curing and annealing on the precursor material layer under a H2O-containing atmosphere, and converting the precursor material layer to an insulation layer, wherein during the curing and annealing process, the side wall of the first fin part is oxidized to form a first oxide layer, the side wall of the second fin part is oxidized to form a second oxide layer, and the thickness of the first oxide layer is smaller than the thickness of the second oxide layer; and removing the insulation layer in a partial thickness to form an isolation layer, and also removing the lining oxide layer, the insulation blocking layer, the first oxide layer and the second oxide layer which are higher than the top of the isolation layer. After the isolation layer is formed, the critical dimension of the first fin part is larger than the critical dimension of the second fin part, and the process is simple in step.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

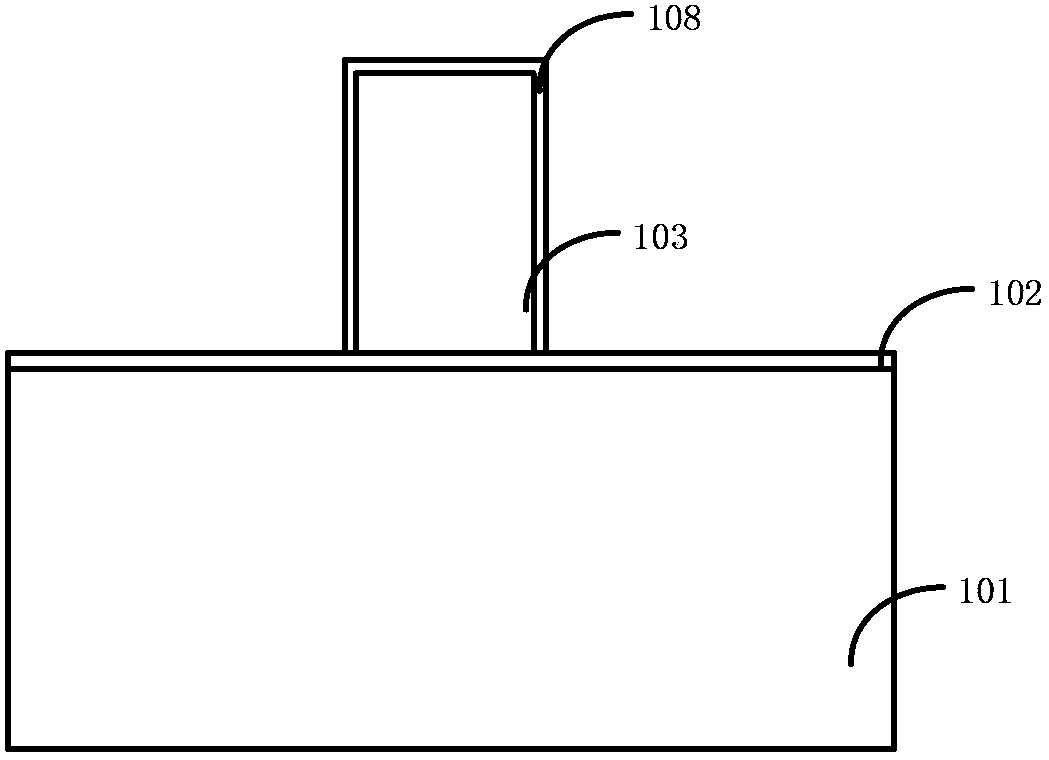

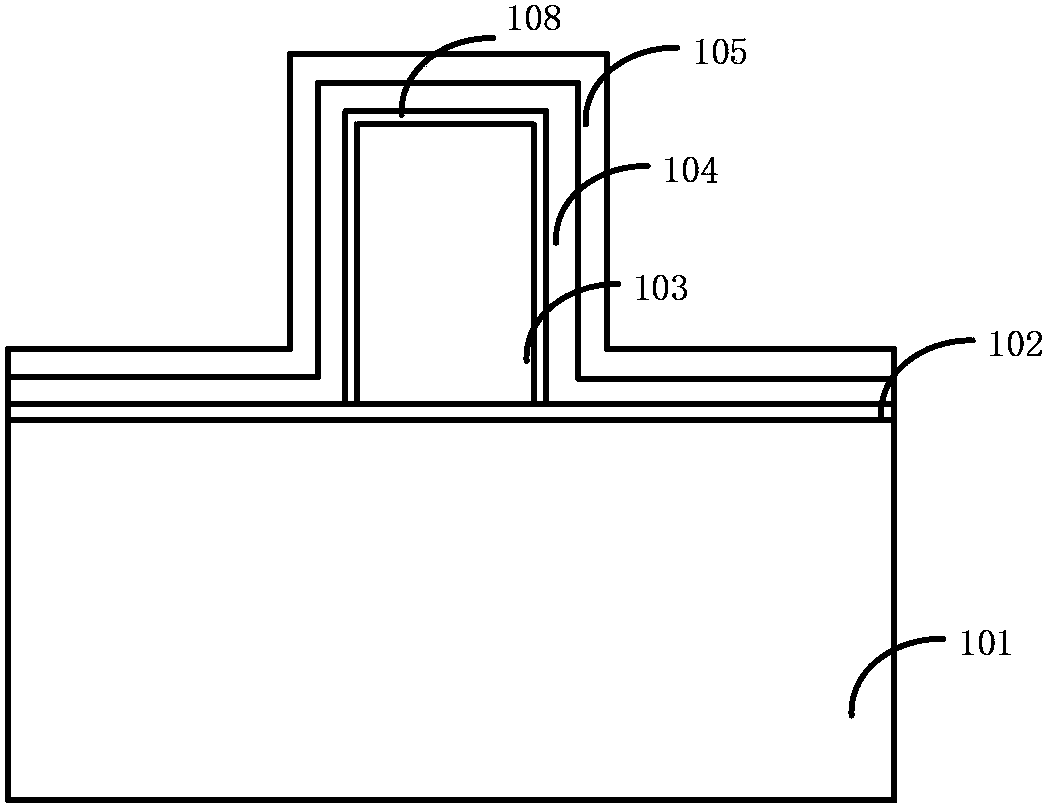

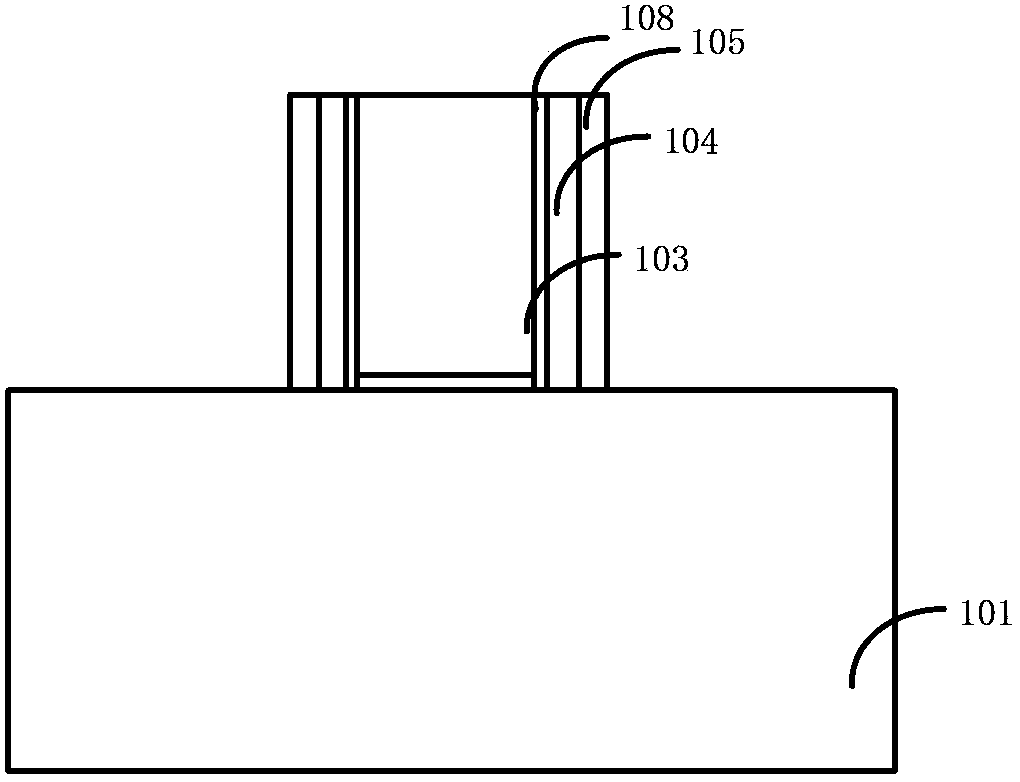

Preparation method of semiconductor device

ActiveCN104051245AImprove performanceIncrease critical sizeSemiconductor/solid-state device manufacturingSemiconductor devicesShadow effectOxide

The invention relates to a preparation method of a semiconductor device. The method comprises: providing a semiconductor substrate; forming a virtual gate on the semiconductor substrate; forming a first offset side wall and a second offset side wall at the side of the virtual gate; removing the virtual gate; and removing the first offset side wall to form a groove with the increased critical dimension. According to the invention, after the virtual gate is formed, a thermal treatment oxide layer, the first offset side wall, and the second offset side wall are formed on the virtual gate; and after LDD and source-drain ion injection are executed, the thermal treatment oxide layer and the first offset side wall are removed to form the groove, wherein the critical dimension of the groove is the critical dimension of the metal gate and the critical dimension of the metal gate is larger than that of the conventional metal gate. Moreover, the thermal treatment oxide layer and the first offset side wall are formed after the source-drain ion injection, so that the large critical dimension is obtained and the shadow effect can be avoided and thus the device performance is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

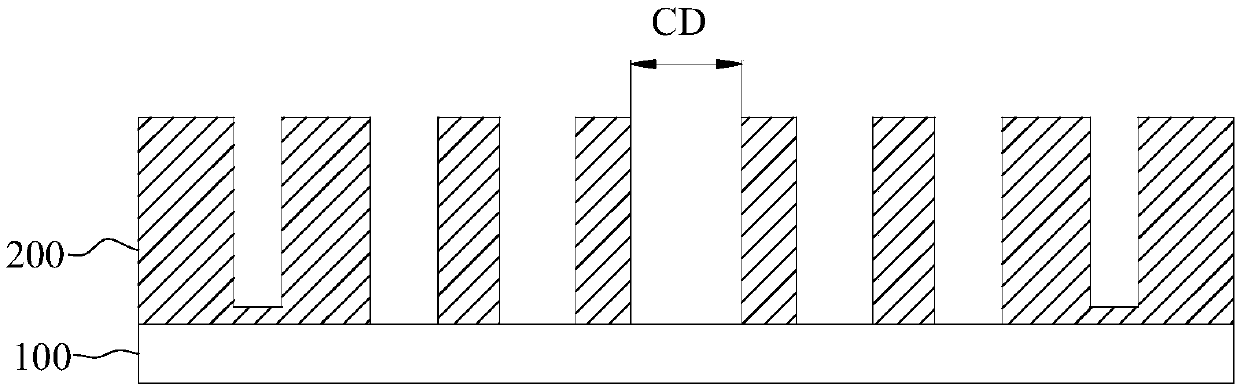

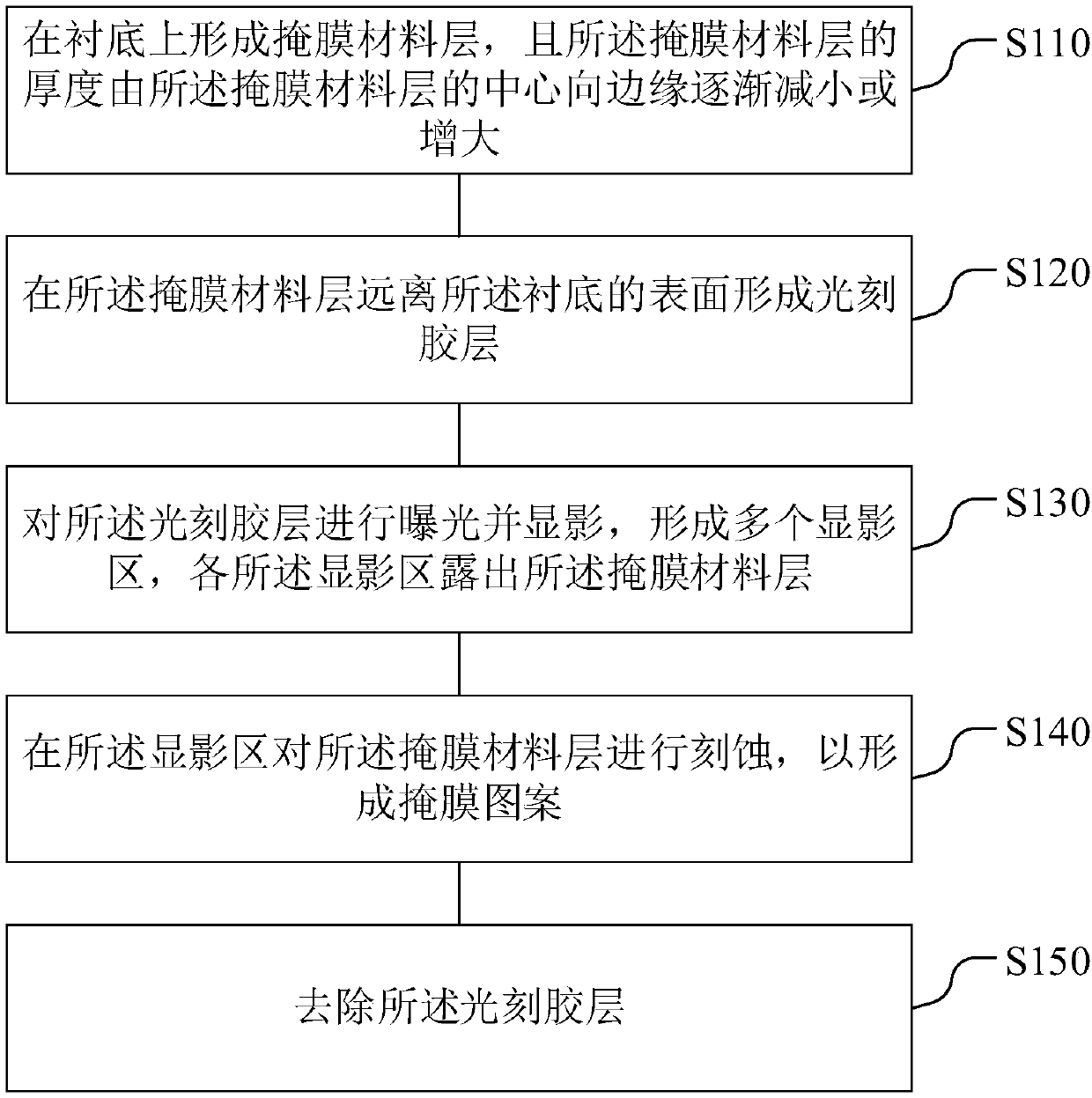

Semiconductor device, hard mask structure and manufacturing method thereof

InactiveCN110890273AIncrease critical sizeAvoid different degrees of etchingSemiconductor/solid-state device manufacturingDevice materialEngineering

The invention provides a semiconductor device, a hard mask structure and a manufacturing method of the hard mask structure, and relates to the technical field of semiconductors. The manufacturing method comprises the following steps: forming a mask material layer on a substrate, wherein the thickness of the mask material layer is gradually reduced or increased from the center to the edge of the mask material layer; forming a photoresist layer on the surface, far away from the substrate, of the mask material layer; exposing and developing the photoresist layer to form a plurality of developingareas, and exposing the mask material layer in each developing area; etching the mask material layer in the developing area to form a mask pattern; and removing the photoresist layer. According to themanufacturing method of the hard mask structure, the uniformity of the critical dimension can be improved.

Owner:CHANGXIN MEMORY TECH INC

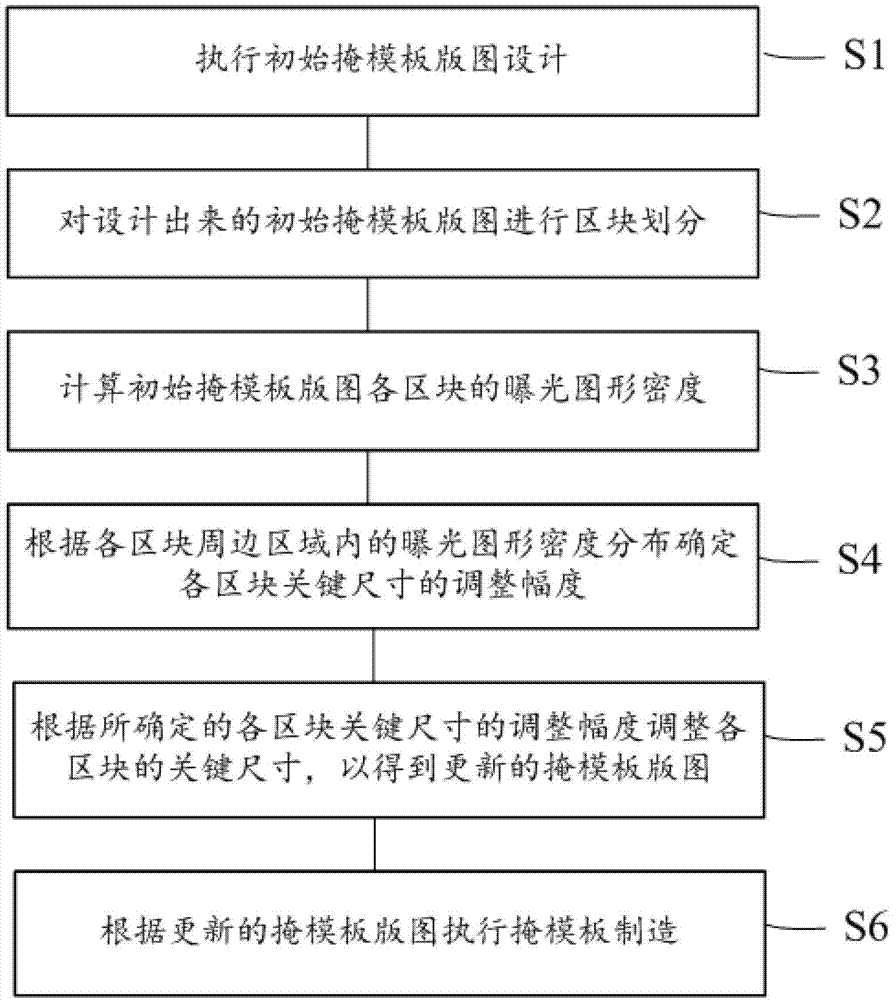

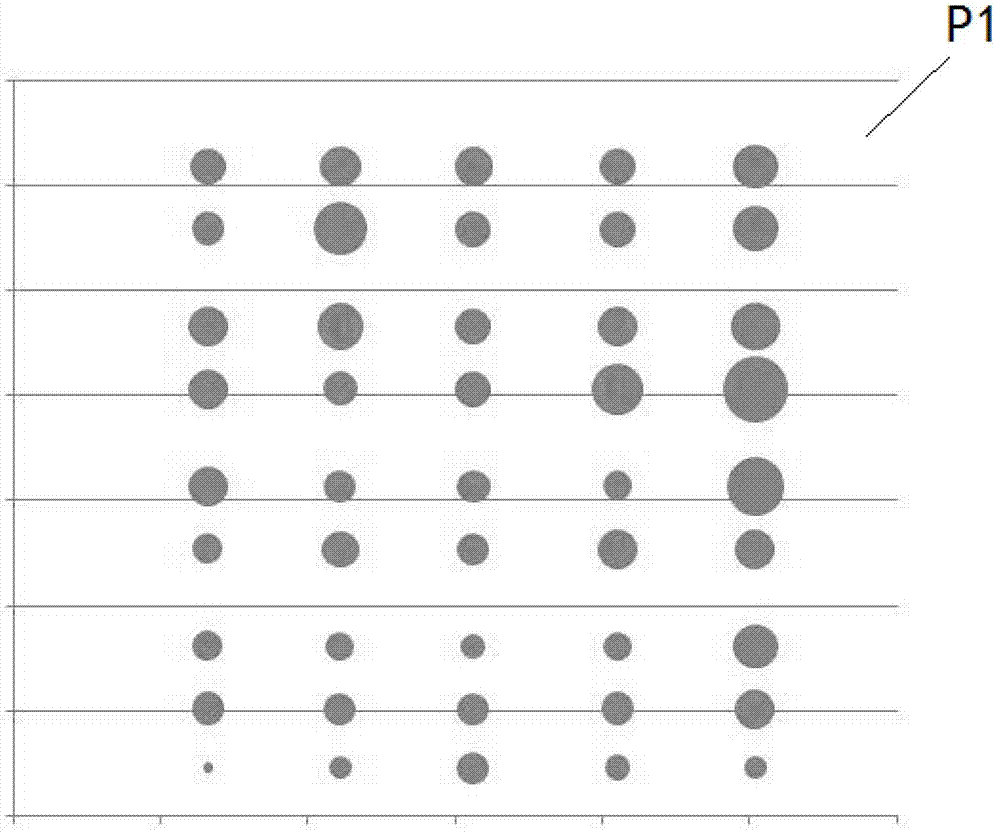

Method for improving homogeneity of critical dimension of photomask

InactiveCN103091976AIncrease critical sizeImprove critical dimension uniformityOriginals for photomechanical treatmentDensity distributionCritical dimension

The invention provides a method for improving homogeneity of critical dimension of a photomask. The method comprises the steps of: firstly, carrying out initial mask layout design; secondly, dividing the designed initial mask layout to blocks; thirdly, calculating the density of an exposure figure of each block of the initial mask layout; fourthly, determining the adjustment range of the critical dimension of each block according to the density distribution of the exposure figure in the peripheral area of each block; fifthly, adjusting the critical dimension of each block according to the determined adjustment range of the critical dimension of each block, thereby obtaining an updated mask layout; and sixthly, manufacturing a mask according to the updated mask layout.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

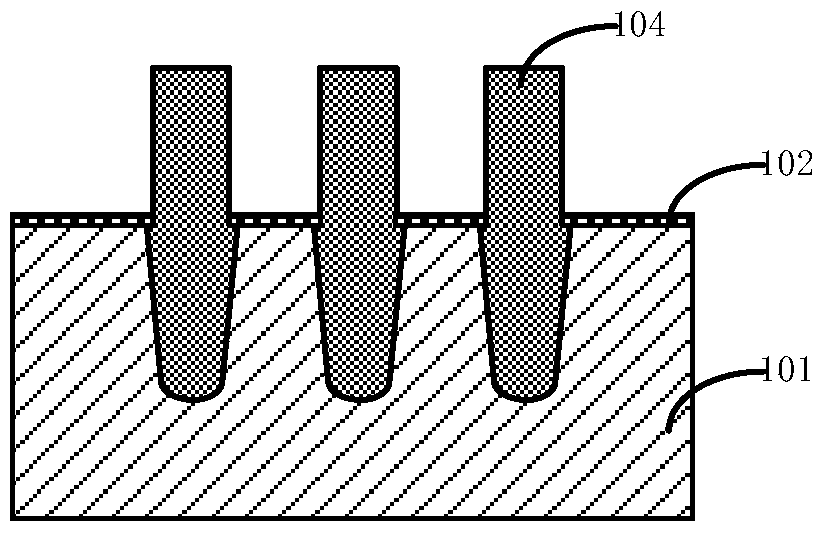

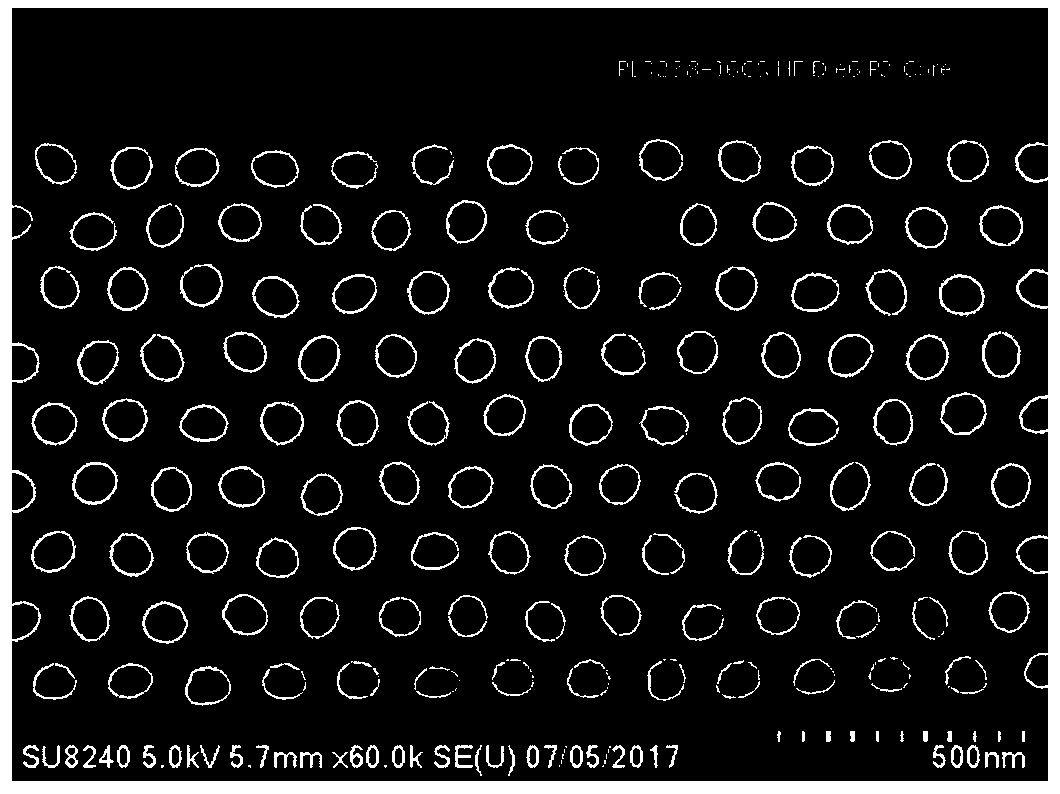

Channel hole etching technology adopting novel hard mask

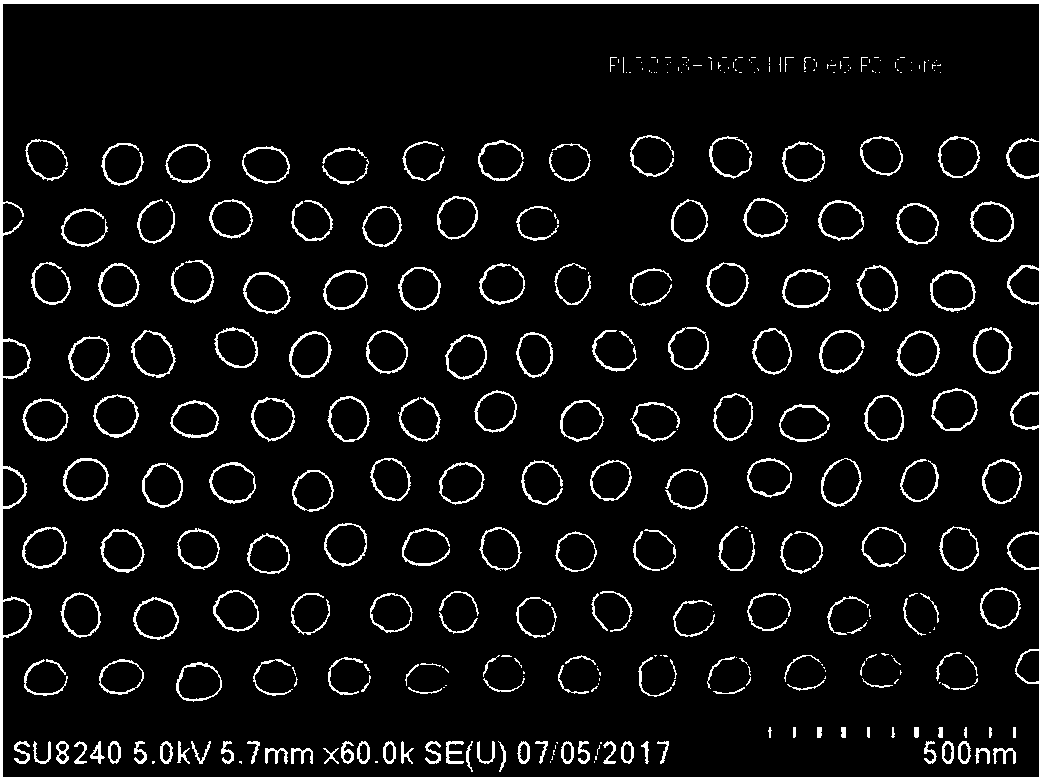

ActiveCN107731680ASo as not to damageSolve the deformationSemiconductor/solid-state device manufacturingEtchingChloride

The invention provides a channel hole etching technology adopting a novel hard mask. The technology comprises the steps that metal aluminum is adopted on a buffer oxide (buffer OX) on a stacking structure as a hard mask layer; the thickness of the metal aluminum hard mask layer is 500 , and before etching, chlorine (Cl2) is adopted for etching to open the metal aluminum hard mask layer; then, oxygen is adopted on the metal aluminum hard mask layer for perform short-time oxidation treatment to form an aluminum oxide (Al2O3) protective layer; then, channel hole etching is performed to form channel holes; finally, boron chloride (BCl3) is adopted for removing the Al2O3 protective layer. The metal aluminum hard mask is not damaged by etching, the thickness can be greatly lowered, and thereforethe problem that the channel hole deforms and some channel holes are closed or lost can be solved; the channel hole arc-shaped bent morphology is improved, and the bottom critical dimension (CD) is enlarged.

Owner:YANGTZE MEMORY TECH CO LTD

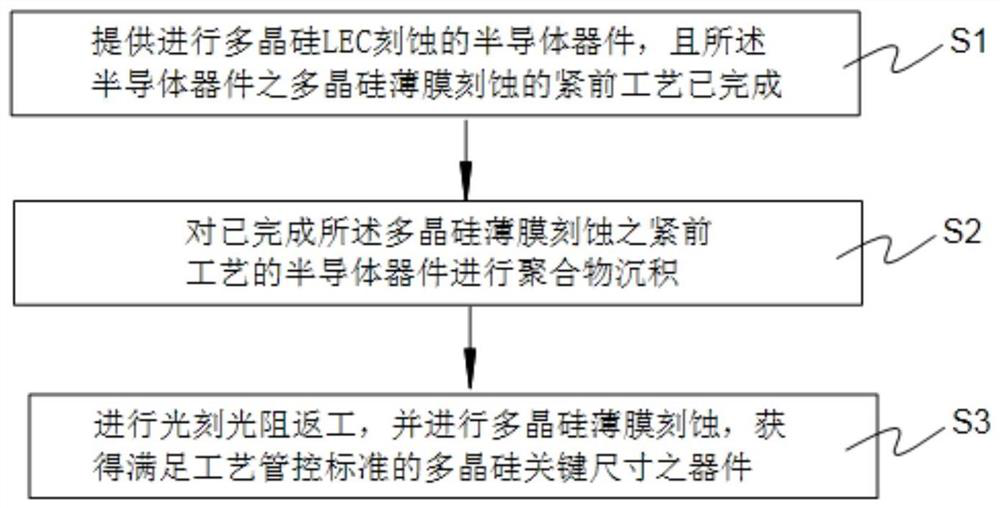

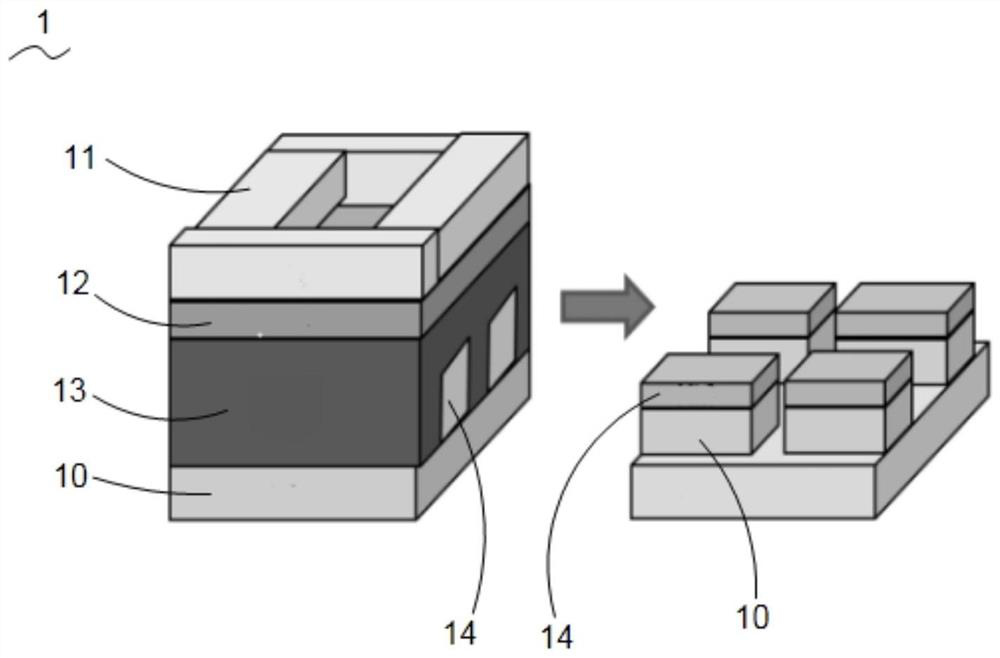

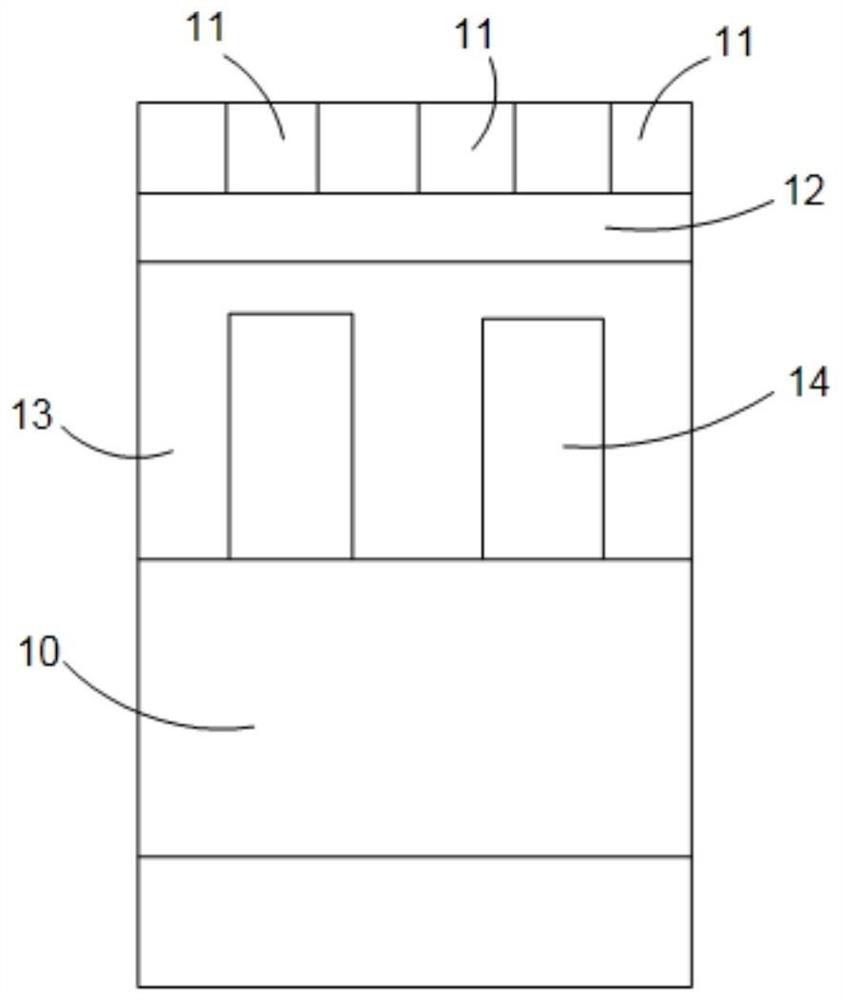

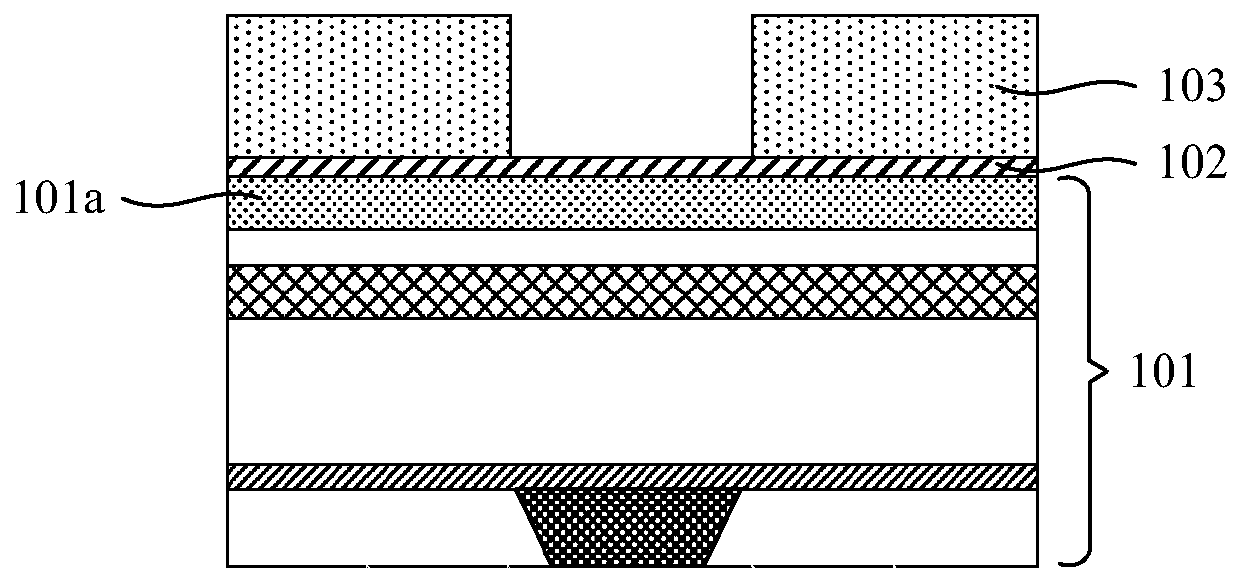

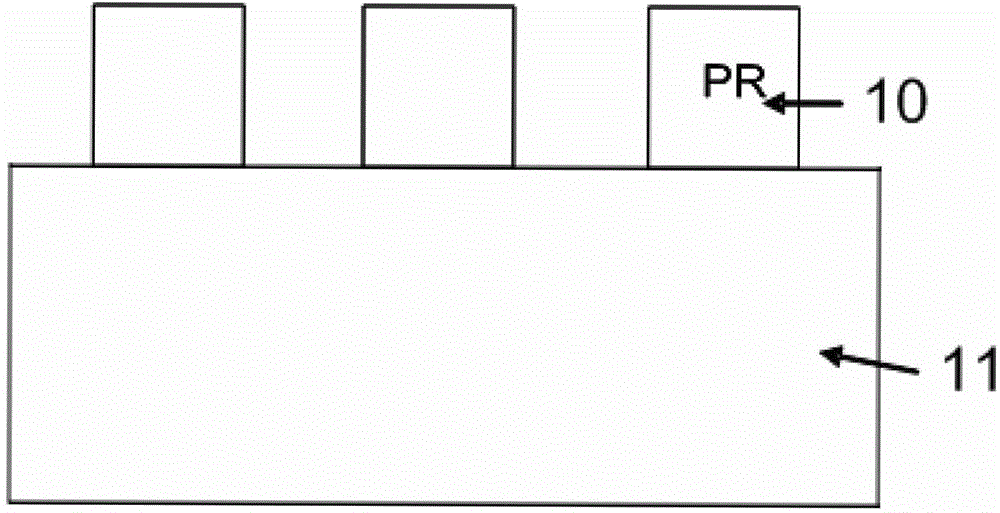

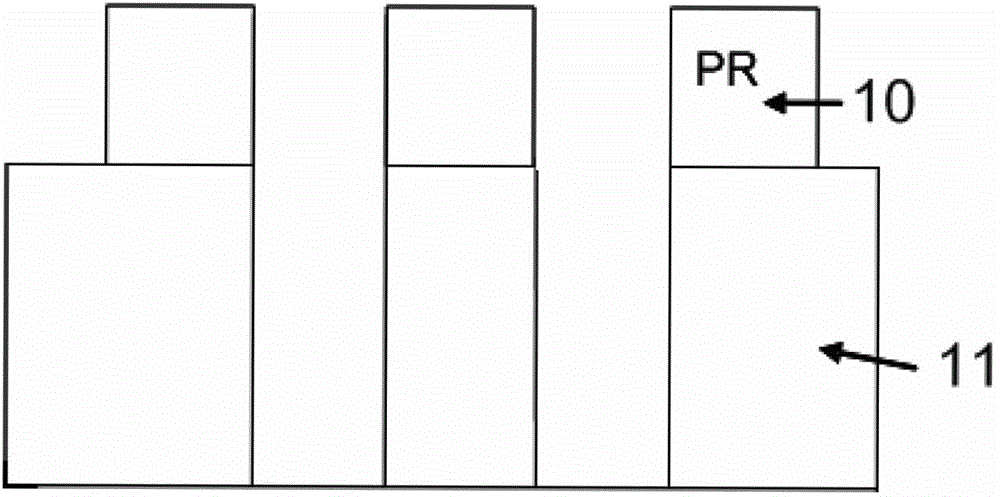

Method for reducing polycrystalline silicon critical dimension loss caused by photoetching photoresist reworking

PendingCN114005738AImprove the problem of key size reductionIncrease critical sizeSemiconductor/solid-state device manufacturingEtchingDevice material

The invention discloses a method for reducing polycrystalline silicon critical dimension loss caused by photoetching photoresist reworking, which comprises the steps of S1, providing a semiconductor device for polycrystalline silicon LEC etching, wherein the just preceding process of polycrystalline silicon thin film etching is completed; S2, carrying out polymer deposition; and S3, carrying out photoetching photoresist reworking, and carrying out polycrystalline silicon thin film etching to obtain a polycrystalline silicon critical dimension device meeting the process control standard. According to the method, polymer deposition is carried out on the semiconductor device which is subjected to the just preceding process of etching the polycrystalline silicon thin film, the critical dimension of a hard mask is increased, and under the condition that the pattern of the polycrystalline silicon thin film is not changed, the problem that the critical dimension of polycrystalline silicon is reduced can be effectively solved, the product yield is improved, and the production cost is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A kind of semiconductor structure and its manufacturing method

ActiveCN110379762BIncrease critical sizeSmall sizeSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The invention provides a semiconductor structure and a manufacturing method thereof, and the method comprises the following steps: providing a stacked structure, and forming a first recessed structurein the stacked structure, wherein the first recessed structure extends downwards into an insulating medium interlayer but does not penetrate through an insulating medium interlayer; etching the insulating medium interlayer by taking a first hard mask layer as a mask to obtain a second concave structure in the stacked structure, wherein the second concave structure extends to the surface of the etching barrier layer and has a vertical side wall; transversely trimming the second hard mask layer to enlarge the size of a top opening of the second hard mask layer; and etching the insulating mediuminterlayer by taking the second hard mask layer as a mask so as to enlarge the opening size of the first concave structure in the insulating medium interlayer. The method can adapt to dual damascenehole patterns, slit patterns or groove pattern structures with different film thicknesses, and is beneficial to enlarging a processing window of chemical mechanical polishing of an insulating layer ina preorder process and enlarging a processing window of a key size at the bottom of a dual damascene hole.

Owner:YANGTZE MEMORY TECH CO LTD

Etching Method of Silicon Nitride High Aspect Ratio Hole

ActiveCN103531464BAchieve anisotropyAdjust etch topographySemiconductor/solid-state device manufacturingEtchingHydrogen

The invention discloses an etching method for a silicon nitride high depth-to-width ratio hole. The method comprises: first of all, placing a semiconductor device of a silicon nitride film, already forming the graph needed by a semiconductor, into en etching cavity; then using a dry-method plasma technology, letting in a high carbon chain molecule fluorocarbon-based gas, an oxidizing gas, a dilution gas and a fluorocarbon-based gas containing hydrogen, adding radio frequency power and exciting plasma; and after a plasma stabilization step, performing etching of the silicon nitride film until the etching morphology, the hole diameter size and the depth of a high depth-to-width ratio hole reach requirements. According to the invention, the silicon nitride film is etched by using the unique fluorocarbon-based gas, through adjusting gas component and power size, the deposition amount of fluorocarbon polymers on the side wall of the deep hole can be controlled, the key dimensions of the hole can be prevented from becoming larger, and polymers already deposited at the bottom of the deep hole can be removed so as to ensure that the etching can be continued, thus the etching morphology of the hole can be adjusted.

Owner:SOI MICRO CO LTD

Semiconductor device, manufacturing method and mask

ActiveCN110571220BImprove performanceSmall density differenceSolid-state devicesSemiconductor devicesDevice materialEngineering

The invention provides a semiconductor device and its manufacturing method and mask plate. In the manufacturing method of the semiconductor device, after forming a patterned core layer with a core on the gate dense area and the gate sparse area, the A sidewall is formed on the sidewall of the core, and then the gate layer is etched using the sidewall as a mask to form a first gate on the gate-dense region and a second gate on the gate-sparse region. When the gate base structure is used, the etching load effect between the gate dense area and the gate sparse area can be reduced or even completely avoided, and the uniformity of the critical dimension of the first gate in the formed gate dense area can be improved. The shape of the first gate at the edge is ensured, and then the tops of a plurality of adjacent second gate infrastructure structures on the gate sparse region are connected to form a second gate by means of a connecting gate layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

An embedded flash memory, preparation method thereof, and electronic device

ActiveCN105575968BAvoid it happening againIncreased process windowSolid-state devicesSemiconductor devicesPhysical chemistryEngineering

The invention relates to an embedded flash memory, a preparation method thereof, and an electronic device. The method includes providing a substrate, in which an active area isolated by a shallow trench isolation oxide is formed, and the top of the shallow trench isolation oxide is formed. Higher than the surface of the substrate; deposit a floating gate material layer to cover the active area and the shallow trench isolation oxide; planarize the floating gate material layer to expose the surface of the shallow trench isolation oxide; etch back The floating gate material layer is used to reduce the thickness of the floating gate material layer to expose a portion of the shallow trench isolation oxide; the exposed shallow trench isolation oxide is etched back to reduce the exposed shallow trench isolation oxide. critical dimensions of the shallow trench isolation oxide; redeposit the floating gate material layer to the top of the shallow trench isolation oxide to surround the shallow trench isolation oxide, planarize the floating gate material layer; remove the shallow trench isolation oxide The trench isolates portions of the oxide with reduced critical dimensions to form a T-shaped floating gate over the active area.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A Trench Hole Etching Process Using Hard Mask

ActiveCN107731680BSo as not to damageImprove curved shapeSemiconductor/solid-state device manufacturingEtchingChloride

The invention provides a channel hole etching technology adopting a novel hard mask. The technology comprises the steps that metal aluminum is adopted on a buffer oxide (buffer OX) on a stacking structure as a hard mask layer; the thickness of the metal aluminum hard mask layer is 500 , and before etching, chlorine (Cl2) is adopted for etching to open the metal aluminum hard mask layer; then, oxygen is adopted on the metal aluminum hard mask layer for perform short-time oxidation treatment to form an aluminum oxide (Al2O3) protective layer; then, channel hole etching is performed to form channel holes; finally, boron chloride (BCl3) is adopted for removing the Al2O3 protective layer. The metal aluminum hard mask is not damaged by etching, the thickness can be greatly lowered, and thereforethe problem that the channel hole deforms and some channel holes are closed or lost can be solved; the channel hole arc-shaped bent morphology is improved, and the bottom critical dimension (CD) is enlarged.

Owner:YANGTZE MEMORY TECH CO LTD

Control Method of Critical Dimension Consistency After Ultra-Deep Hole Plasma Etching Process

ActiveCN104550132BAvoid/Mitigate Etch Rate Drift IssuesIncrease critical sizeCleaning processes and apparatusNitrogen gasCritical dimension

Owner:SEMICON MFG INT (SHANGHAI) CORP

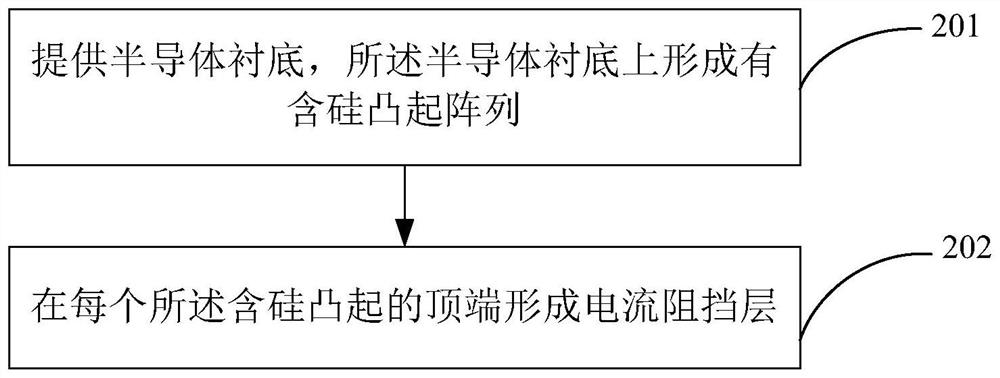

A kind of semiconductor device and its manufacturing method, electronic device

ActiveCN107785374BIncrease critical sizeReduce leakage currentSolid-state devicesSemiconductor devicesDevice materialEngineering

The present invention provides a semiconductor device, a manufacturing method thereof, and an electronic device. The manufacturing method includes: providing a semiconductor substrate on which an array of silicon-containing protrusions is formed; A current blocking layer is formed. The manufacturing method can form a current blocking layer on the top of the silicon-containing protrusion, thereby avoiding the formation of a conductive tip on the top of the silicon-containing protrusion, thereby relatively increasing the critical dimension of the conductive part at the top of the silicon-containing protrusion, reducing leakage current, and improving the performance of the silicon-containing protrusion. Device performance such as programming window, endurance, and data retention. The semiconductor device and electronic device have high performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

touch display panel

ActiveCN105511707BEasy to detectImprove the display effectInput/output processes for data processingOptoelectronicsTransistor

Owner:SHANGHAI AVIC OPTOELECTRONICS +1

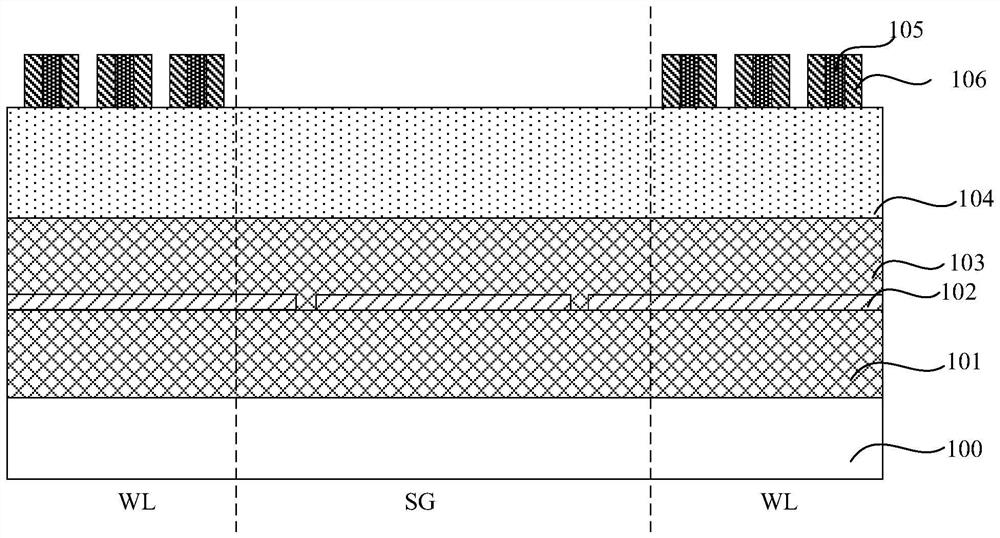

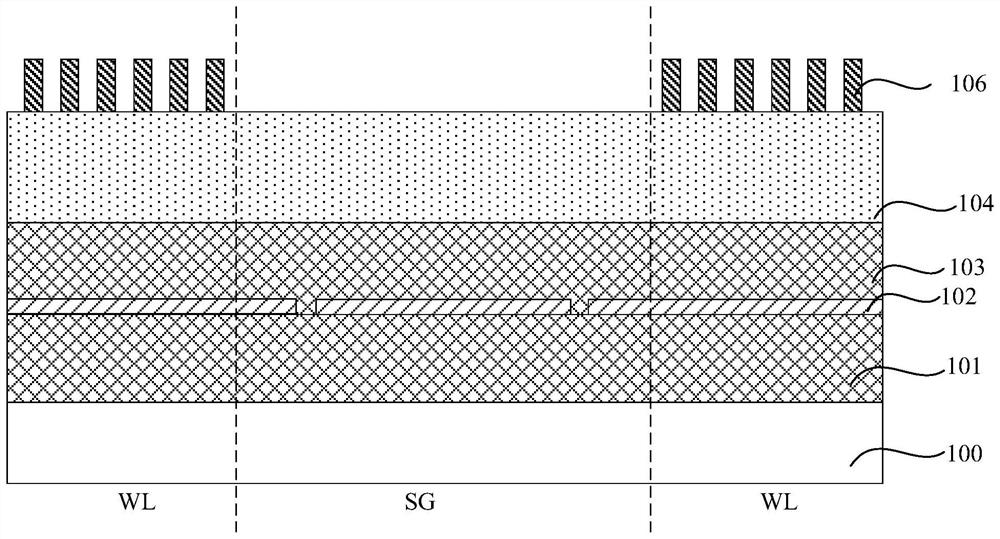

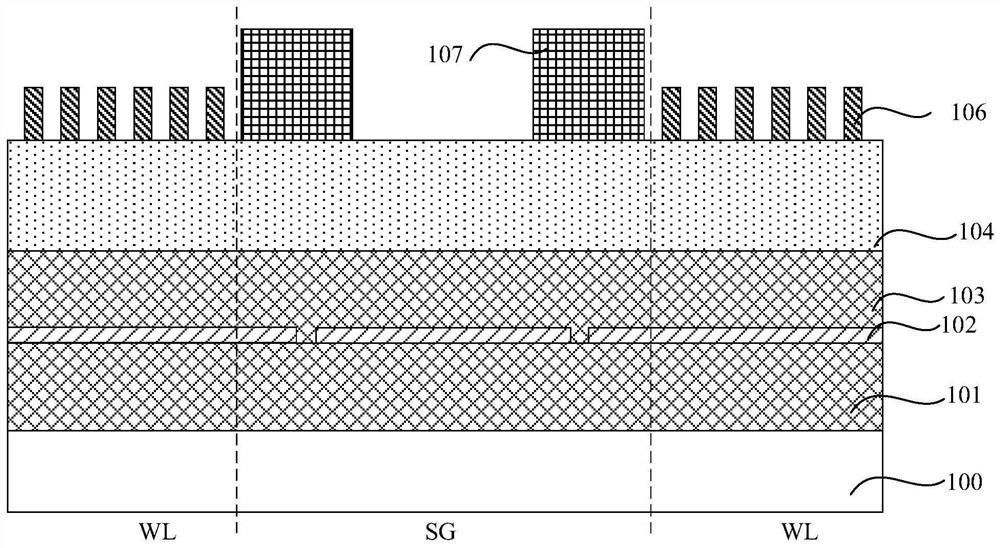

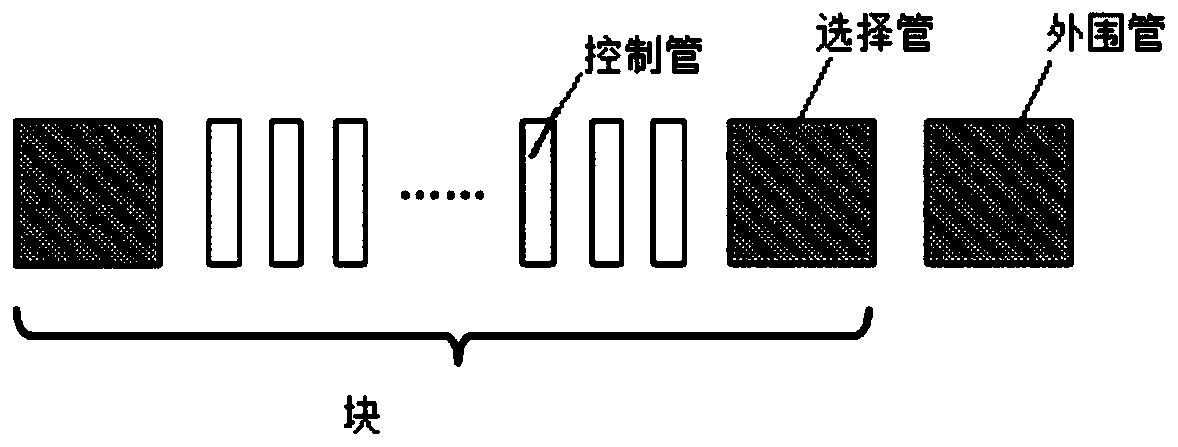

Method for forming gate structure of NAND memory, NAND memory and photomask

InactiveCN111106001AIncrease critical sizeTransistorSolid-state devicesIntegrated circuit manufacturingEtching

The invention relates to a gate structure forming method of an NAND memory, a NAND memory and a photomask, and relates to a semiconductor integrated circuit manufacturing process. The method comprisesthe steps of in the forming process of the gate structure of the NAND memory, forming a mandrel pattern shape for forming a control gate structure through a first photoetching exposure process, and forming a mandrel pattern morphology used for forming a peripheral gate structure and a selection gate structure; then, in the process of removing the mandrel pattern structure through a second photoetching exposure process, protecting an area for forming the peripheral gate and selection gate structures by using photoresist so as to remove the control gate mandrel film layer; in the subsequent etching of the gate structure, forming the control gate by the remaining side walls; and forming the peripheral gate and the selection gate by the side walls and the unremoved mandrel pattern structure together. The critical size of the side wall used for forming the outermost periphery of the control gate is not large, and the influence of interlayer registration deviation on the subsequent processis weakened.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

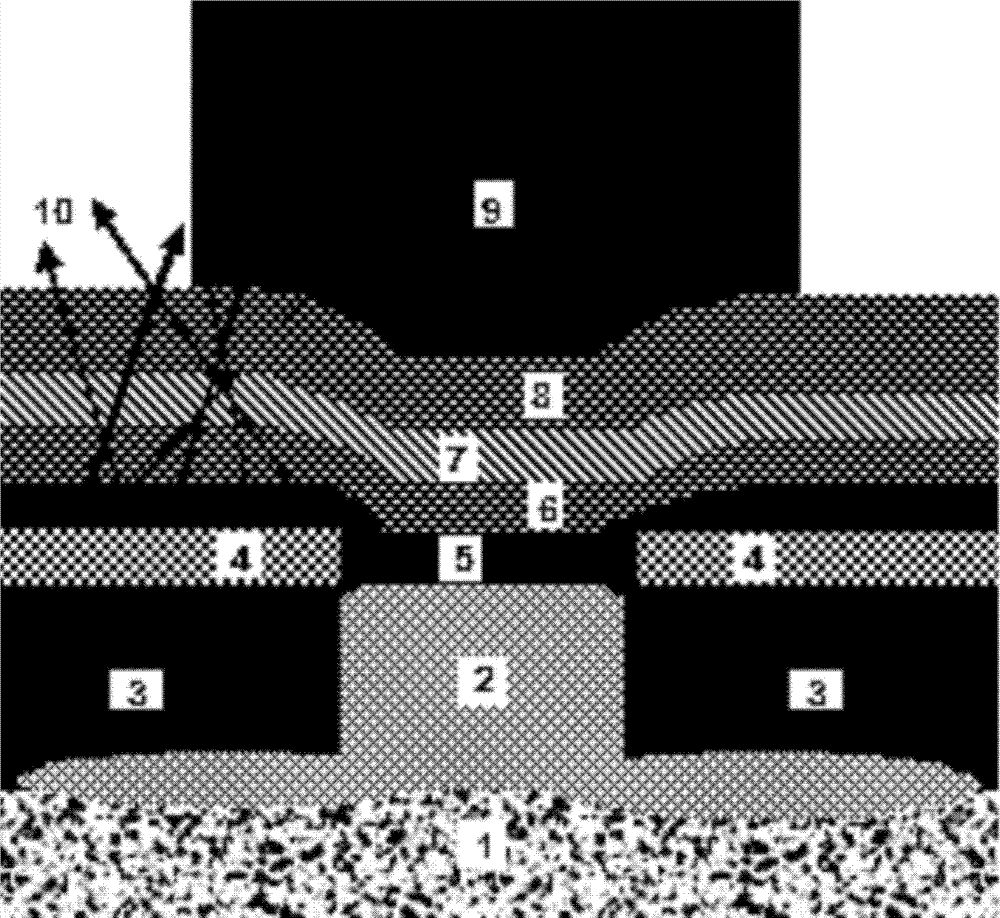

A hard mask film layer structure and manufacturing method of a silicon germanium triode base region

ActiveCN102842607BSmall sizeIncrease critical sizeTransistorSemiconductor/solid-state device manufacturingSilicon membraneDiffuse reflection

The invention discloses a germanium-silicon triode base region hard mask membrane layer structure, which comprises a silicon chip, wherein a collector region and a field isolation region are arranged on the silicon chip; a polycrystalline silicon layer and a germanium-silicon membrane layer are grown on the collector region and the field isolation region, and the germanium-silicon membrane layer is partially grown above the polycrystalline silicon layer; and an inorganic anti-reflection material layer and at least one hard mask membrane layer are grown above the germanium-silicon membrane layer. The invention further discloses a manufacturing method of the germanium-silicon triode base region hard mask membrane layer structure. Through adoption of the germanium-silicon triode base region hard mask membrane layer structure, the influence of a germanium-silicon membrane layer diffuse reflection beam to the appearance of the photoresist is reduced, the control acpability to key sizes in the production is improved, and photoetching patterns of small sizes are obtained.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

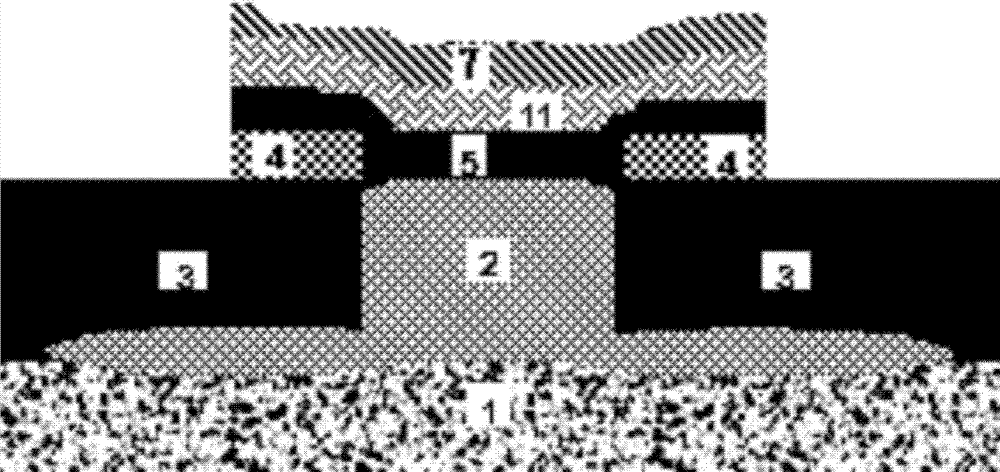

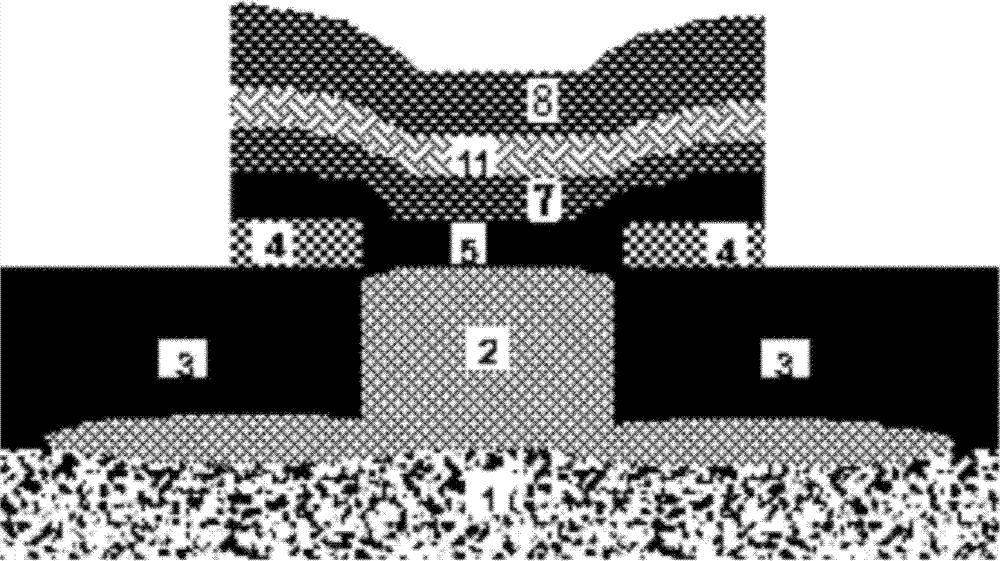

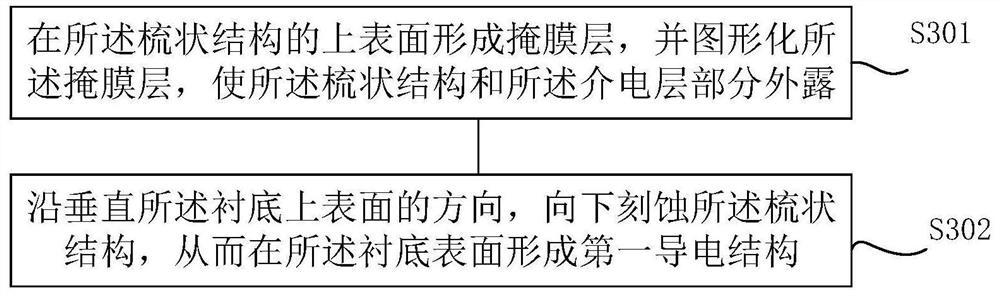

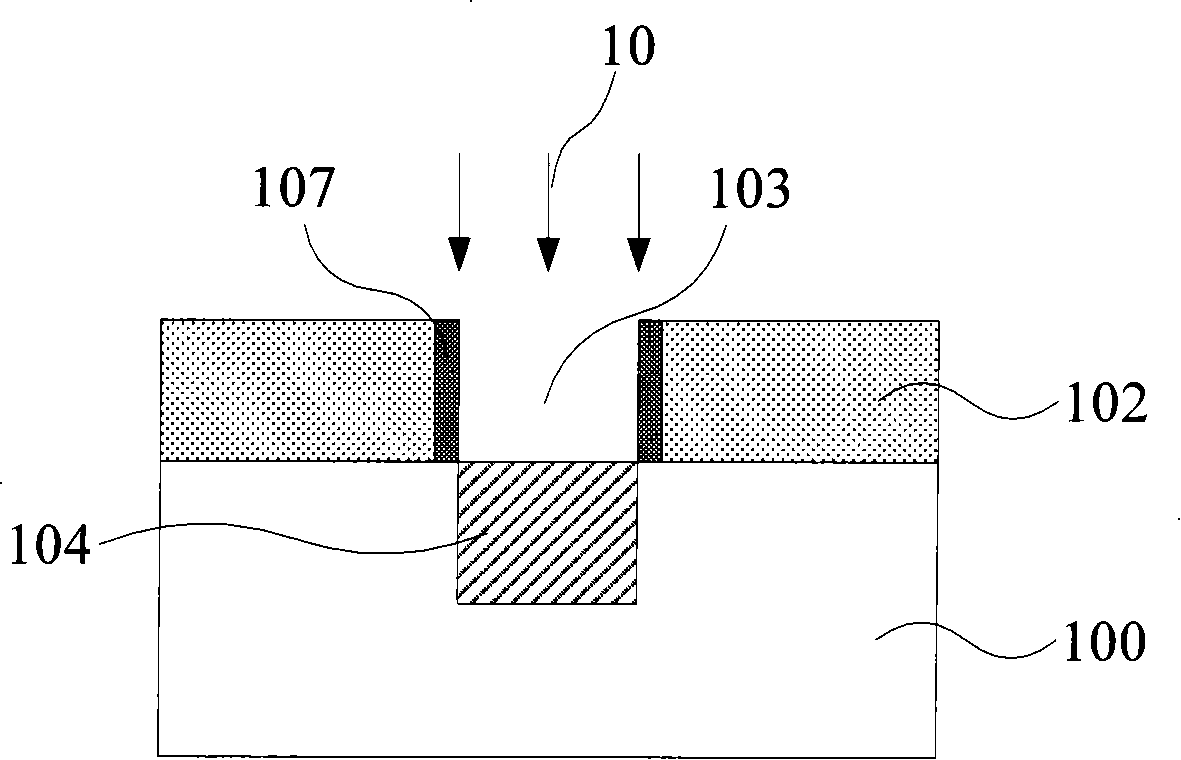

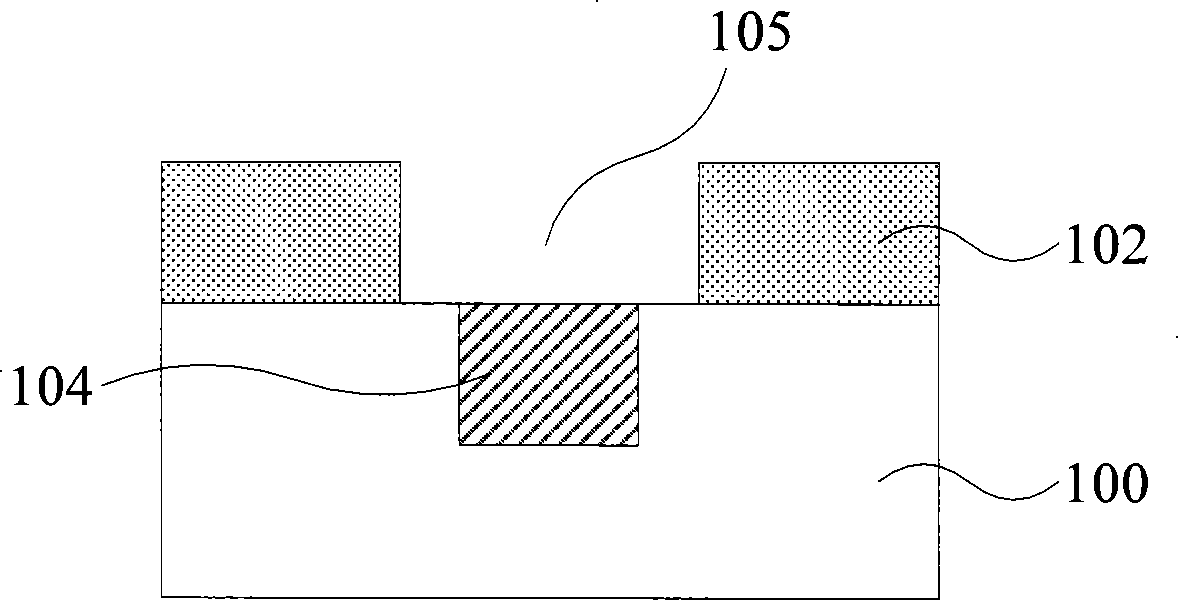

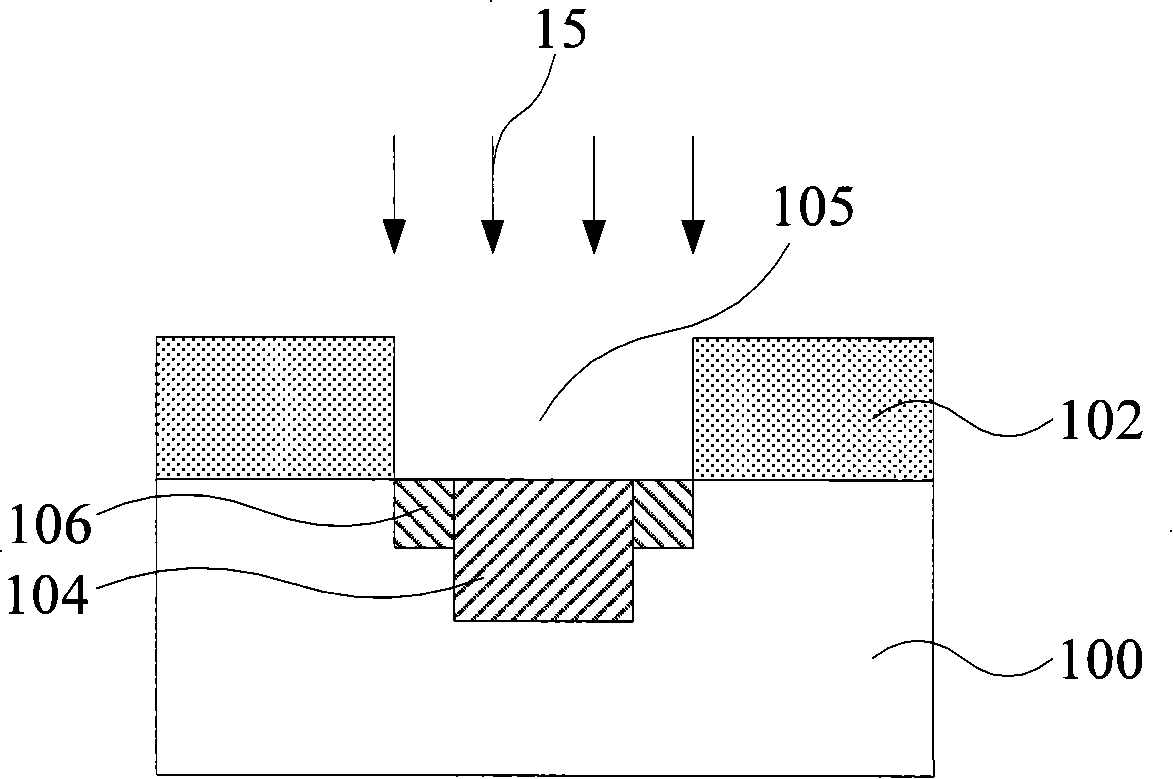

Semiconductor storage device and preparation method thereof

PendingCN114068404ALower impedanceIncrease critical sizeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor storage devicesSemiconductor

The invention discloses a semiconductor storage device and a preparation method thereof, which can meet the resolution requirement or the manufacturing process requirement for manufacturing micro line width patterns. The preparation method of the semiconductor storage device comprises the following steps of providing a substrate, wherein a conductive structure layer is formed on an upper surface; patterning the conductive structure layer to form a first conductive structure comprising a first pattern structure, the first pattern structure extending in a first direction and having a first width in a second direction perpendicular to the first direction, the first pattern structure further comprising a terminal conductive structure having a second width in a second direction perpendicular to the first direction, the terminal conductive structure comprising an inner side widening part and an outer side widening part which are sequentially arranged along the first direction, the inner side widening part and the outer side widening part being respectively used for extending the first pattern structure along the third direction and extending the first pattern structure along the fourth direction, and the third direction and the fourth direction being not parallel to the first direction.

Owner:FUJIAN JINHUA INTEGRATED CIRCUIT CO LTD

Method for forming dopant well and method for forming image sensor

InactiveCN101572249BIncrease critical sizeUniform controlSemiconductor/solid-state device manufacturingRadiation controlled devicesDopantSilicon oxide

The invention relates to a method for forming a dopant well and a method for forming an image sensor. The method for forming the dopant well comprises the following steps: forming a silicon oxide layer on a semiconductor substrate; etching a photoresist layer and a silicon oxide layer until the layers are exposed out of the semiconductor substrate after forming the photoresist layer on the siliconoxide layer, and defining the graphics of the dopant well; incinerating the photoresist layer until the layer is exposed out of the silicon oxide layer, and increasing the key dimension of the graphics of the dopant well; taking the photoresist layer and the silicon oxide layer as masks, implanting ions into the semiconductor substrate along the increased graphics of the dopant well, and formingthe dopant well of which the depth is in graded distribution; and removing the photoresist layer and the silicon oxide layer. The invention also provides the method for forming the image sensor. The invention can uniformly control the key dimension of the dopant well and simplifies processing steps.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

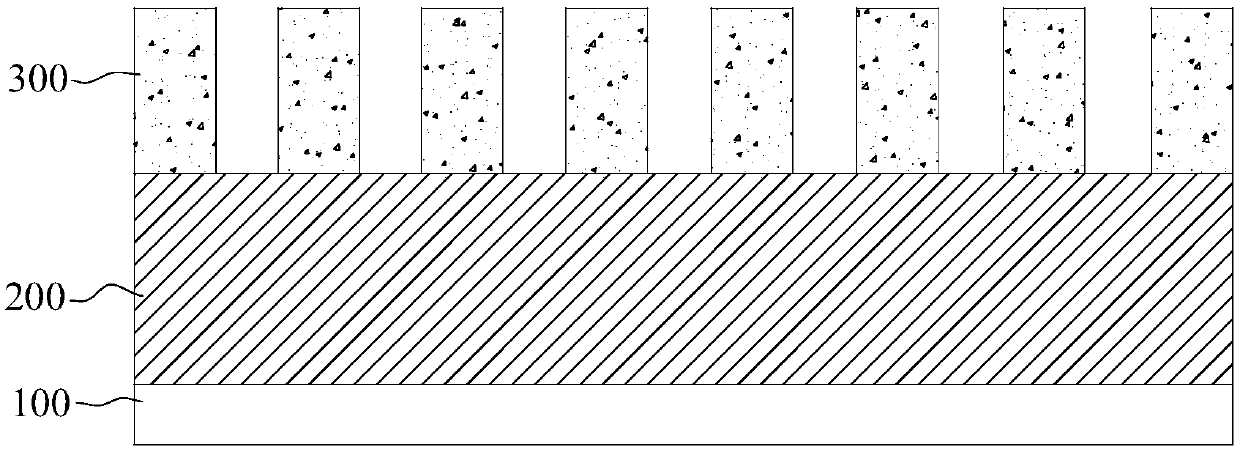

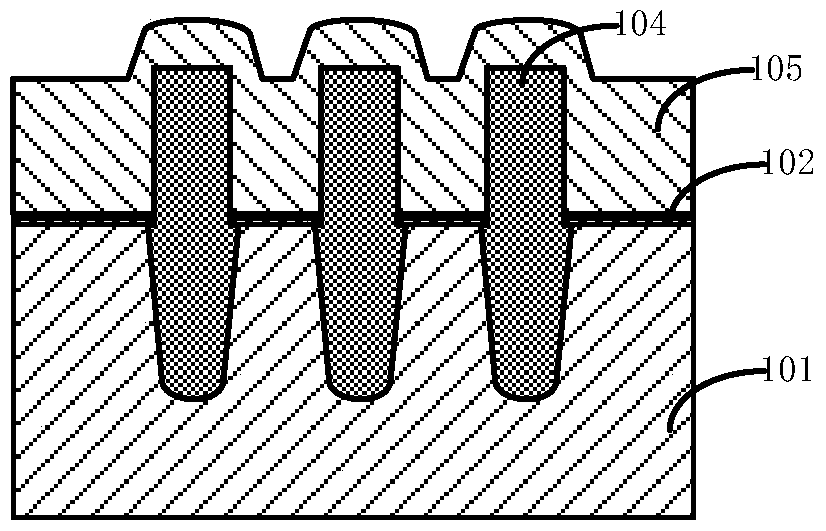

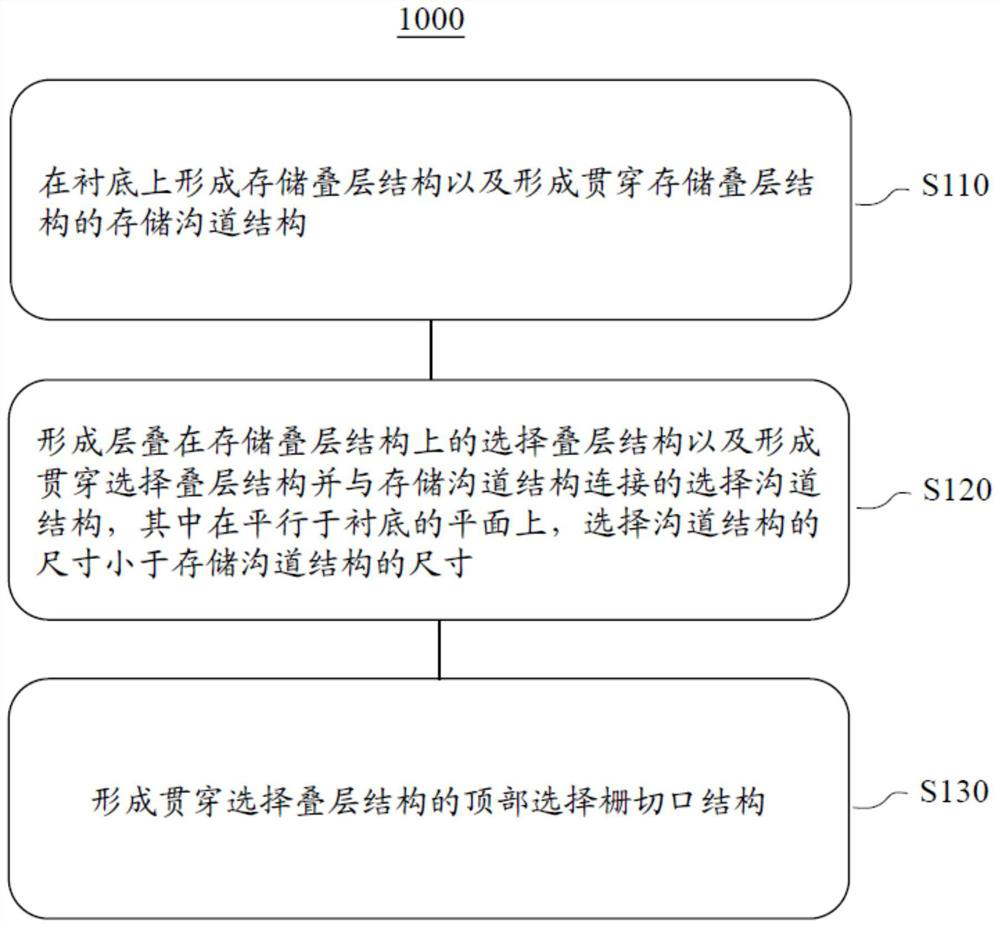

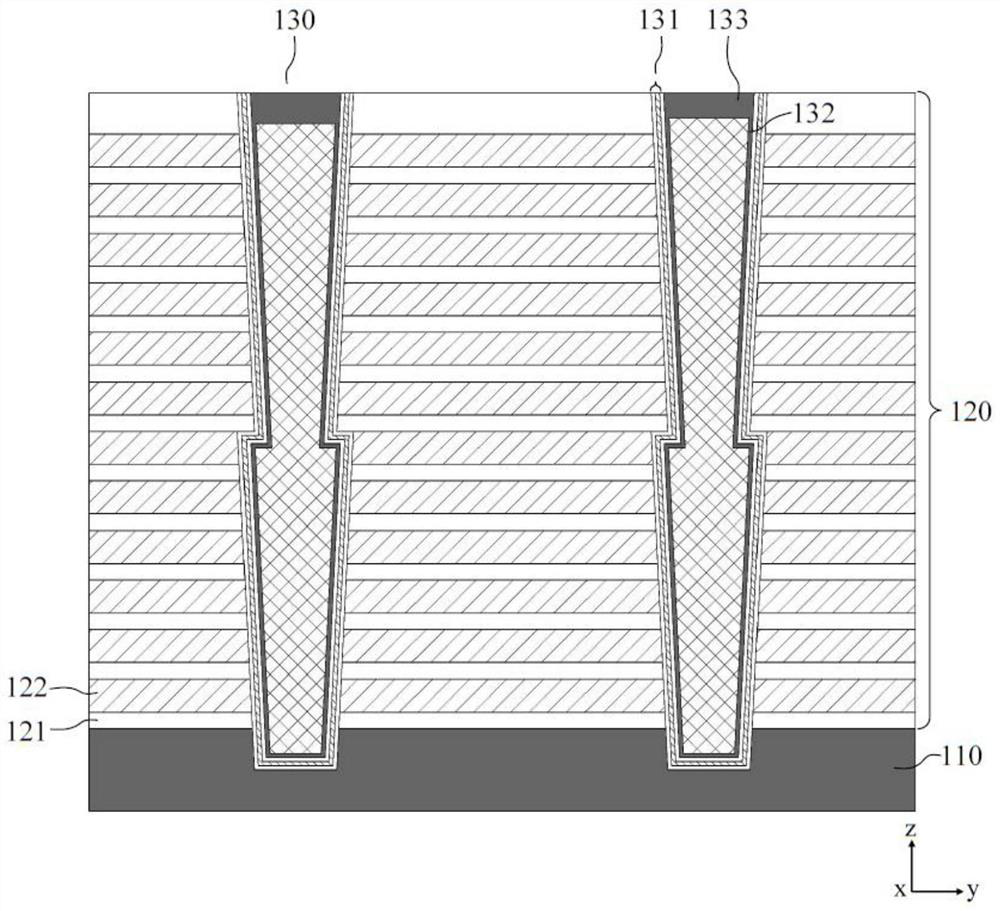

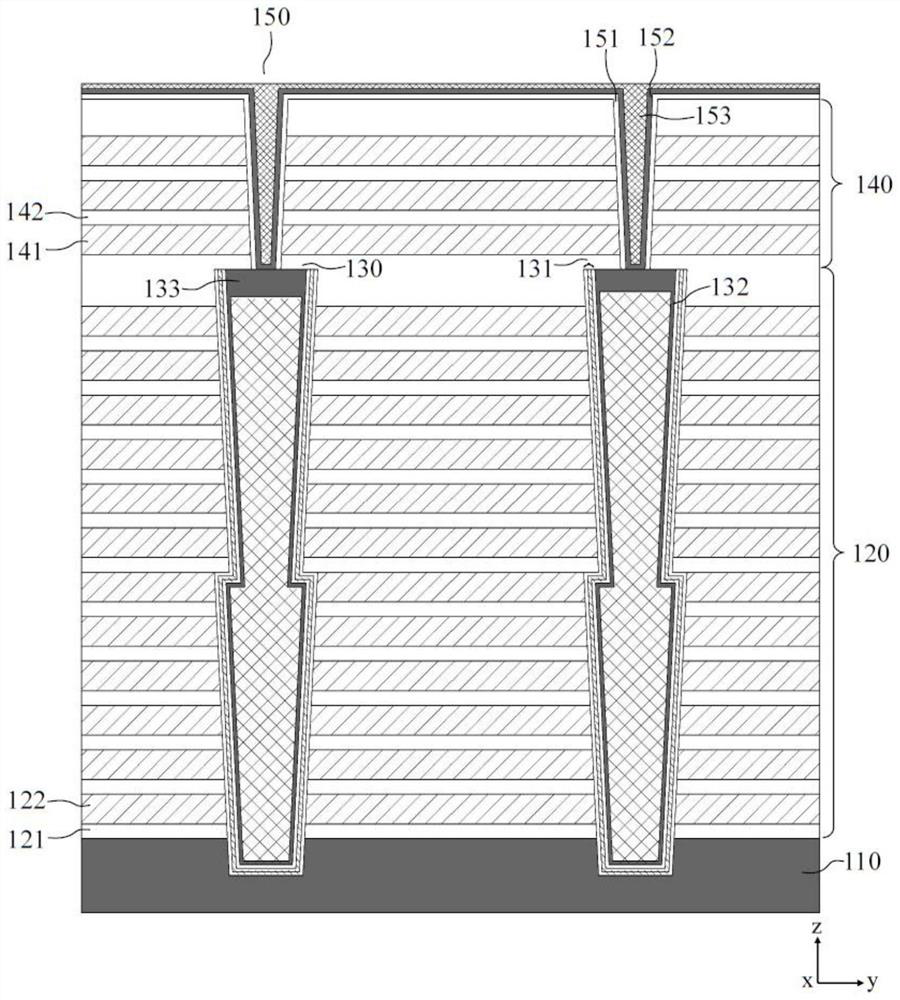

Three-dimensional memory and preparation method thereof

ActiveCN113410251AIncrease distanceIncrease critical sizeSolid-state devicesSemiconductor devicesStructural engineeringMechanical engineering

The invention provides a three-dimensional memory and a preparation method thereof. The method comprises the following steps: forming a storage laminated structure on a substrate and forming a storage channel structure penetrating through the storage laminated structure; forming a selection laminated structure laminated on the storage laminated structure and a selection channel structure penetrating through the selection laminated structure and connected with the storage channel structure, wherein the size of the selection channel structure is smaller than that of the storage channel structure on a plane parallel to the substrate; and forming a top selection gate cut structure penetrating through the selection laminated structure. According to the three-dimensional memory and the preparation method thereof, the process window of the top selection gate notch structure formed between the selection channel structures can be increased, and the unit memory density can be improved.

Owner:YANGTZE MEMORY TECH CO LTD

A kind of formation method of high-k metal gate

ActiveCN106298491BIncrease critical sizeSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsFiller metal

The invention provides a forming method of a high-K metal grid. The method comprises the following steps of step 1: sequentially forming an interlayer dielectric layer, a TiO2 film layer and a polycrystalline silicon layer on a substrate; step 2: performing patterning on the interlayer dielectric layer, the TiO2 film layer and the polycrystalline silicon layer so as to form a pseudo grid electrode structure; forming a grid electrode side wall at the side edge of the pseudo grid electrode structure; step 3: depositing the interlayer electric dielectric materials on the periphery of the pseudo grid electrode structure; flattening the interlayer electric dielectric materials; step 4: removing the top polycrystalline silicon layer in the pseudo grid electrode structure to form a groove; step 5: performing Hf ion injection on the TiO2 film layer in the pseudo grid electrode structure so as to form an HfTiO film layer; step 6: filling metal materials into the groove so as to form the metal grid.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP