A kind of semiconductor device and its manufacturing method, electronic device

A manufacturing method and semiconductor technology, applied in semiconductor devices, electric solid state devices, circuits, etc., can solve the problems of increased electron traps, large leakage current, limited key size, etc., to reduce leakage current, improve the programming window, and increase the key The effect of size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

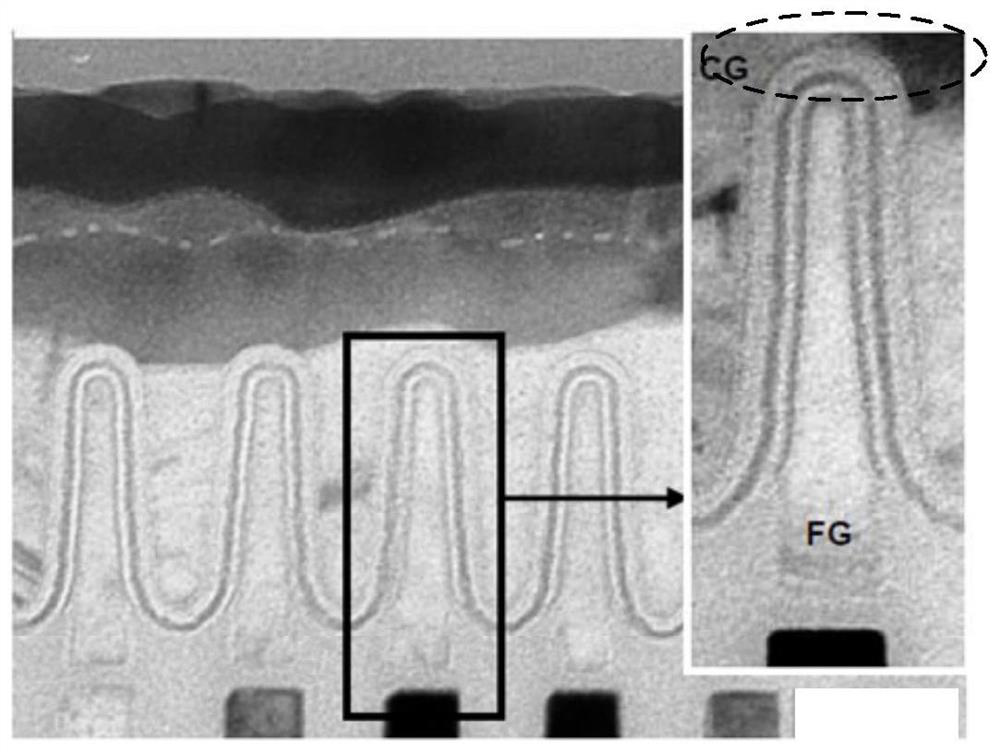

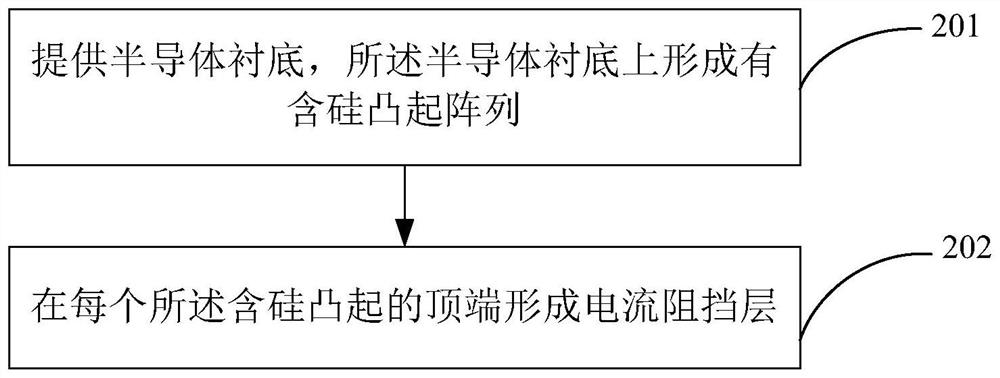

[0043] The following will refer to Figure 3A ~ Figure 3G as well as Figure 4 A method for fabricating a semiconductor device according to an embodiment of the present invention will be described in detail.

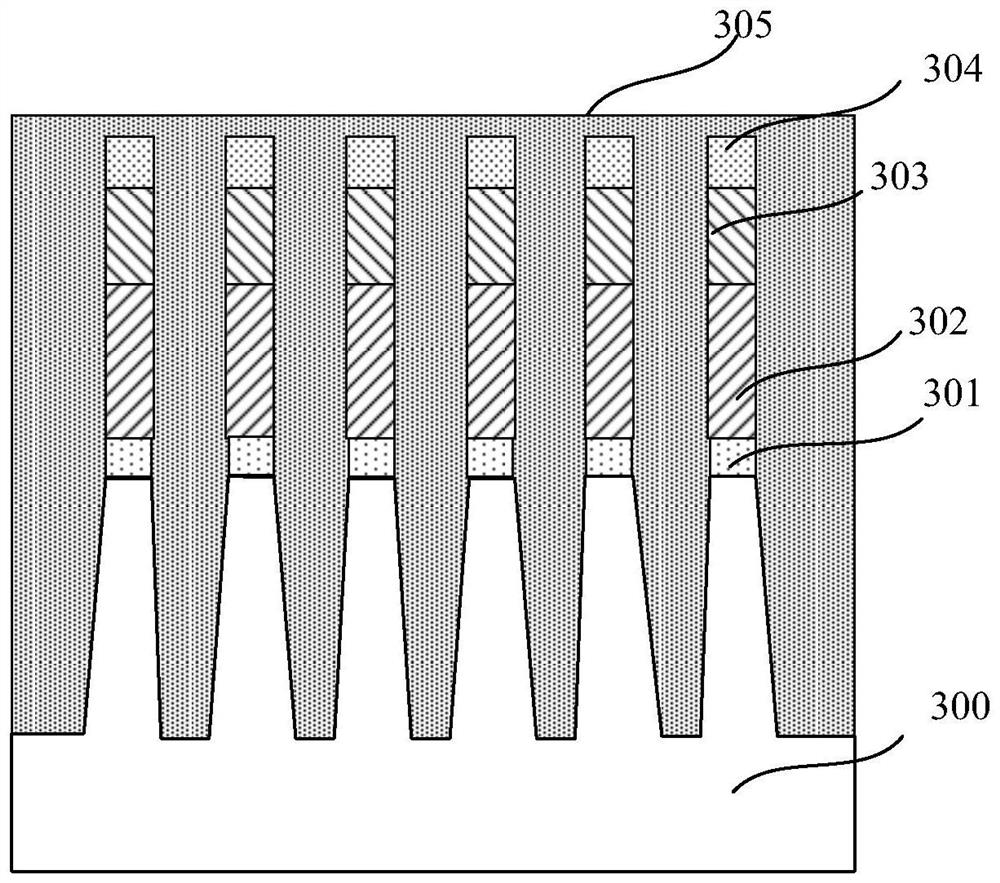

[0044] First, if Figure 3A As shown, a semiconductor substrate 300 is provided, a floating gate array 302 is formed on the semiconductor substrate 300, a trench forming an isolation structure is formed in the semiconductor substrate 300, and between the floating gate arrays 302 The gaps and the trenches are filled with isolation material 305 .

[0045] Wherein, the semiconductor substrate 300 can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, and also includes multiple semiconductors composed of these semiconductors. The layer structure or the like may be silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), silicon-germanium-on-insulator...

Embodiment 2

[0077] The present invention also provides a semiconductor device fabricated by the above method, such as Figure 5 As shown, the semiconductor device includes: a semiconductor substrate 500, an isolation structure 501 is formed in the semiconductor substrate 500, a gate oxide layer 502 is formed on the semiconductor substrate between the isolation structures, and between the gate oxide layer 502 A floating gate 503 is formed on it, a current blocking layer 504 is formed on the top of the floating gate 503 , and a gate dielectric layer 505 is formed on the sidewall of the floating gate 503 and the top of the current blocking layer 504 .

[0078] Wherein the semiconductor substrate 500 can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, and also includes multilayers composed of these semiconductors The structure or the like may be silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-...

Embodiment 3

[0085] Still another embodiment of the present invention provides an electronic device, including a semiconductor device and an electronic component connected to the semiconductor device. Wherein, the semiconductor device includes: a semiconductor substrate, an array of silicon-containing protrusions is formed on the semiconductor substrate, and a current blocking layer is formed on the top of each silicon-containing protrusion.

[0086] The semiconductor substrate can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, including multilayer structures composed of these semiconductors etc. or silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), silicon-germanium-on-insulator (SiGeOI), and germanium-on-insulator (GeOI). Devices, such as NMOS and / or PMOS, can be formed on the semiconductor substrate. Similarly, a conductive member may also be formed in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More