Semiconductor device, manufacturing method and mask

A manufacturing method and semiconductor technology, which are applied to semiconductor devices, electrical solid-state devices, electrical components, etc., can solve the problems of poor uniformity of key dimensions of word lines, etching load effects, abnormal contours and depths, etc. Erosion loading effect, improved device performance, improved uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

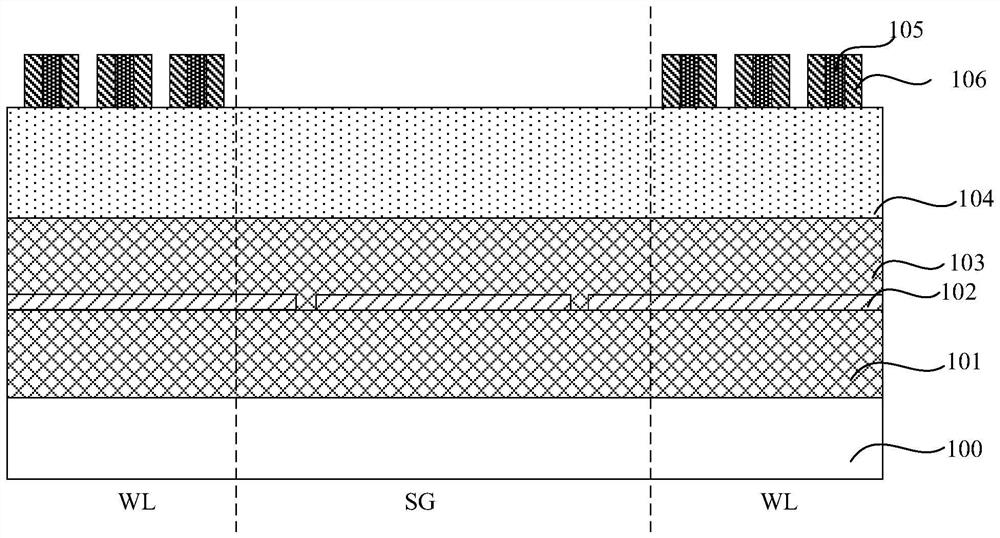

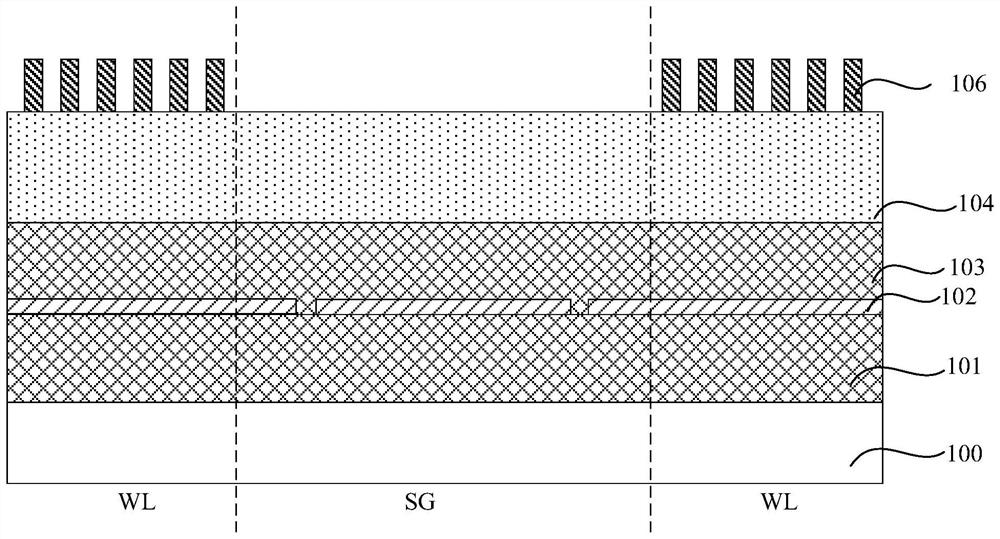

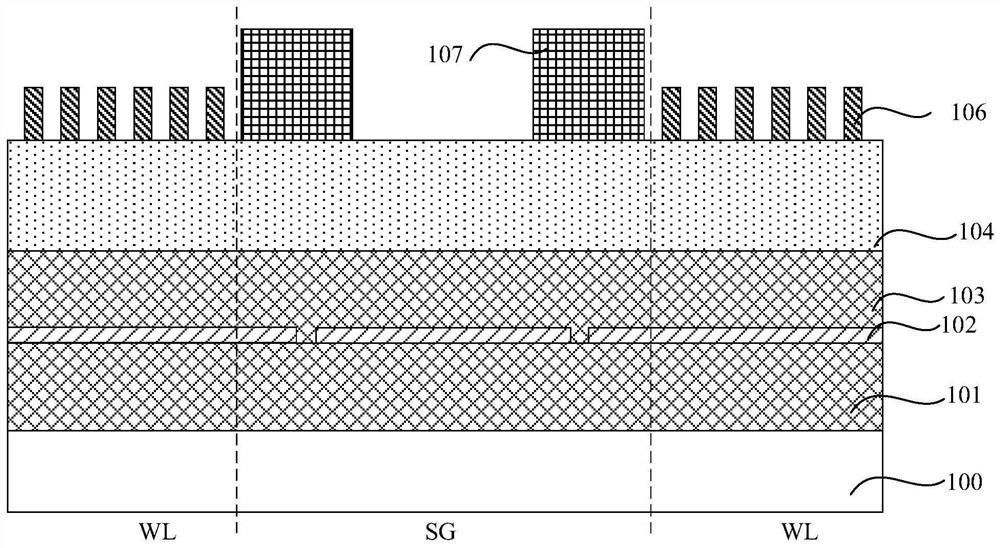

[0045] In the following, a NAND flash memory device is taken as an example to describe in detail the adverse effects of the sparse / dense loading effect of the gate on the performance of the device. Such as Figure 1E As shown, a NAND flash memory device may include: a selection gate (SG, that is, the gate of the selection transistor, the source or drain of the selection transistor is connected to the bit line) 103b and arranged outside the selection gate (SG) 103b A plurality of word lines (WL) 103a, the selection gate (SG) 103b and the word line 103a are formed by connecting the control gates (Control Gate, CG) of the memory cells on the same active area, the selection gate (SG), The word lines (WL) are arranged in parallel, and a corresponding charge storage structure can be provided between each word line 103a and each active area (ACT), so that each intersection of the word line 103a and the active area (ACT) Provide the corresponding storage unit. Usually, the distribut...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More