Embedded flash memory, preparation method thereof, and electronic device

An electronic device and embedded technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of holes, deposition of floating gates, holes, etc., and achieve the effect of good contour, avoiding holes, and good process window.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

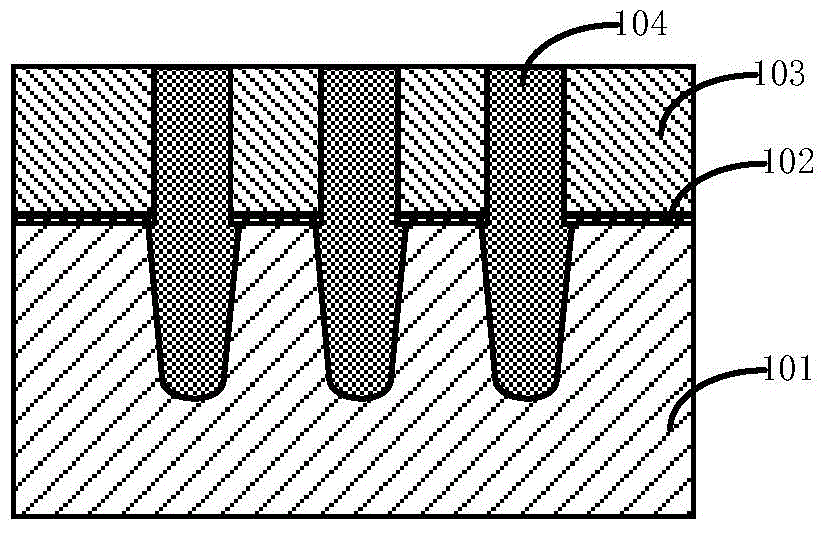

[0053] The preparation method of the embedded flash memory described in the prior art is as Figures 1a-1g As shown, first as Figure 1a As shown, a semiconductor substrate 101 is provided on which an oxide layer 102 and a nitride layer 103 are formed and patterned to form shallow trenches in the oxide layer 102 and the nitride layer 103 , choose shallow trench oxide 104 to fill the shallow trench, and obtain the following Figure 1a pattern shown.

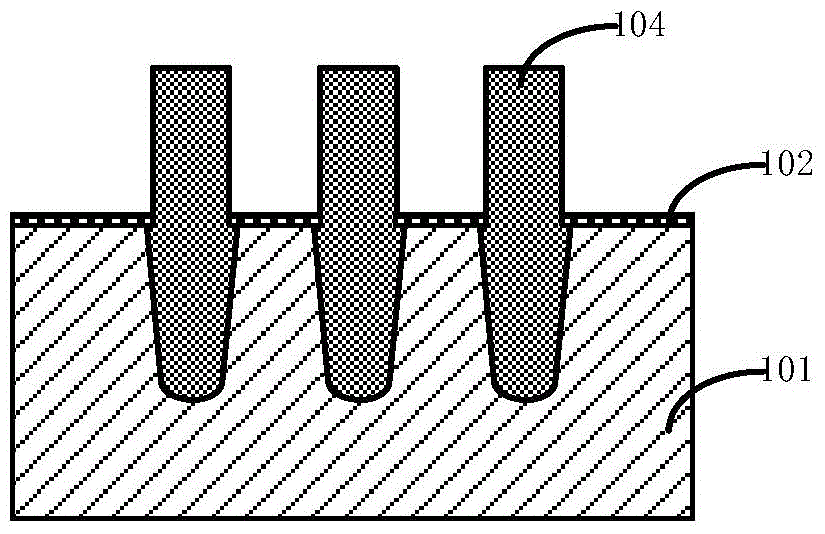

[0054] Then, the nitride layer 103 is removed to obtain Figure 1b structure shown.

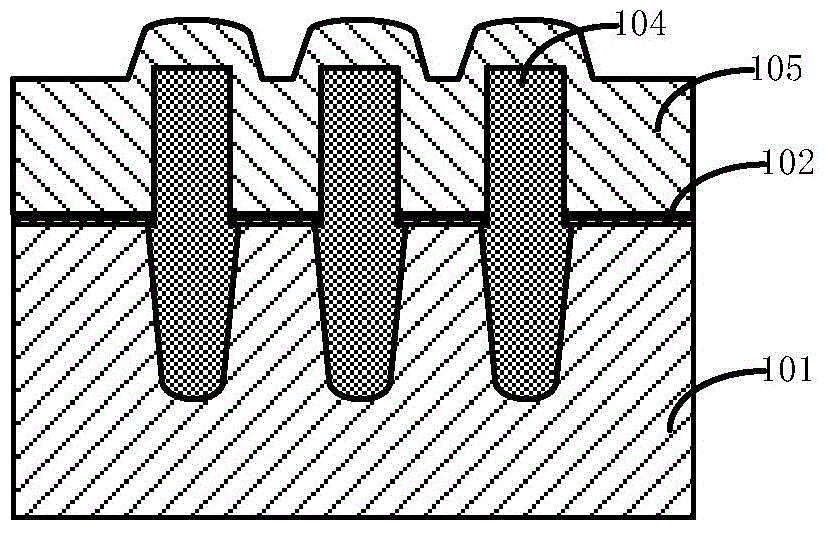

[0055] Next, a floating gate material layer 105 is deposited to cover the oxide layer 102 and the shallow trench oxide 104, to obtain the following Figure 1c structure shown.

[0056] planarizing the floating gate material layer 105 and the shallow trench oxide 104 to a smaller thickness, such as Figure 1d shown.

[0057] Etching back the shallow trench oxide 104 to the oxide layer 102 to form openings in the floating gate material layer...

Embodiment 1

[0062] Step 201 is executed to provide a substrate 201 in which a shallow trench isolation oxide 204 is formed.

[0063] Specifically, such as Figure 3a As shown, the base 201 includes at least a semiconductor substrate, and the semiconductor substrate can be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), stack-on-insulator Silicon germanium (S-SiGeOI), silicon germanium on insulator (SiGeOI) and germanium on insulator (GeOI), etc.

[0064] An oxide layer 202 and a nitride layer 203 are sequentially formed on a semiconductor substrate. The oxide layer 202 can be obtained by a high temperature oxidation method, and its thickness can be 100-200 angstroms. The oxide layer 202 may serve as an isolation layer to protect the semiconductor substrate from damage and contamination.

[0065] The nitride layer 203 may be formed by chemical vapor deposition (CVD), physical vapor deposition (PVD) or atomic layer depositi...

Embodiment 2

[0112] The present invention also provides an embedded flash memory, comprising:

[0113] base;

[0114] a shallow trench isolation structure, the bottom of which is embedded in the substrate;

[0115] active regions located in the substrate and isolated from each other by the shallow trench isolation structure;

[0116] T-shaped floating gates are arranged at intervals on the active region, and the horizontal part of the T-shaped floating gate covers part of the top of the shallow trench isolation structure.

[0117] Wherein, the critical dimension at the top of the T-shaped floating gate is 60-110 nm, and the critical dimension at the bottom is 50-75 nm.

[0118] The thickness of the shallow trench isolation structure is 100-1000 angstroms.

[0119] The thickness of the vertical part of the T-shaped floating gate is 60-300 angstroms.

[0120] The embedded flash memory further includes:

[0121] an isolation layer located above the T-shaped floating gate;

[0122] The c...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More