Formation method of fin field-effect transistor

A technology of fin field effect transistors and fins, which is applied to semiconductor devices, electrical components, circuits, etc., can solve complex problems, achieve the effects of saving production costs, improving device design redundancy, and simplifying the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] It can be seen from the background art that when the formed fins have different critical dimensions, the forming process of the fin field effect transistor provided by the prior art is complicated.

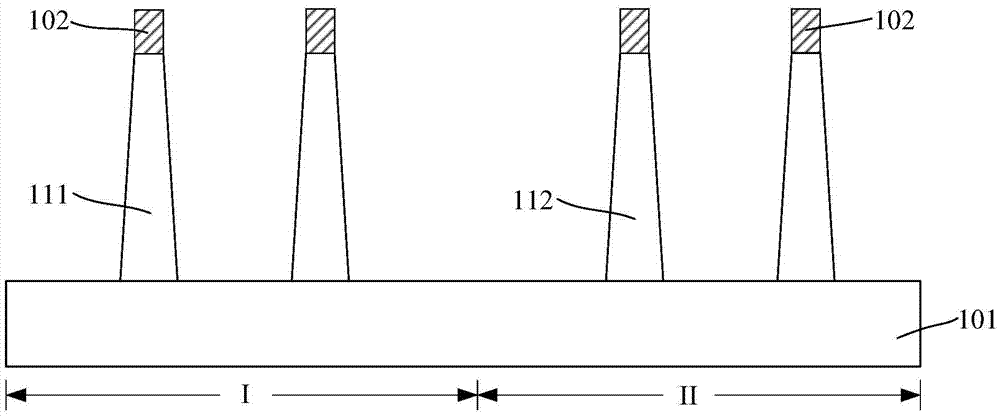

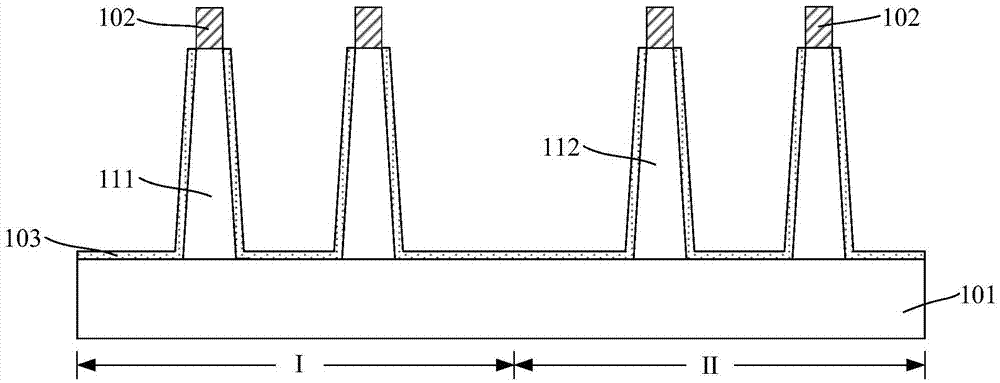

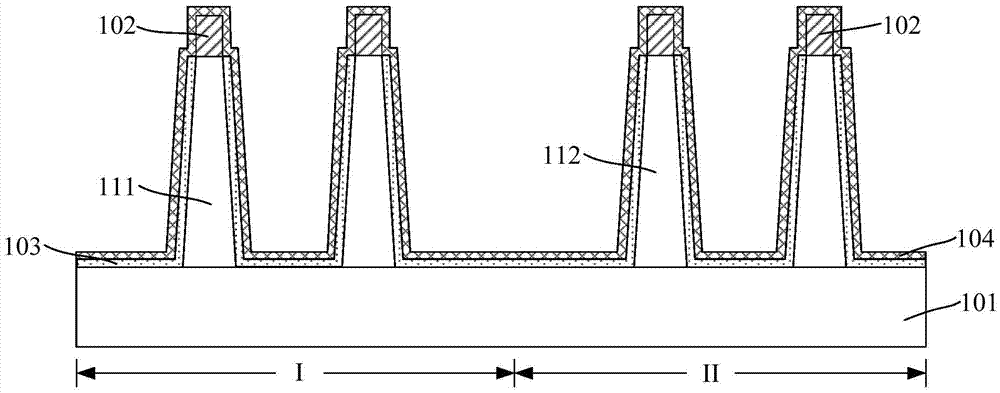

[0032] To this end, the present invention provides a method for forming a fin field effect transistor, providing a substrate including a first region and a second region, the substrate surface of the first region is formed with a first fin, and the second region A second fin is formed on the surface of the substrate, and the critical dimension of the first fin is the same as that of the second fin; forming a liner oxide layer on the surface of the wall; forming an insulating barrier layer on the surface of the liner oxide layer in the first region; A permanent precursor material layer, the top of the precursor material layer is higher than the top of the first fin and the top of the second fin; 2 Performing curing annealing treatment on the precursor material layer in an O...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More