Patents

Literature

187results about How to "Improve electrical isolation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

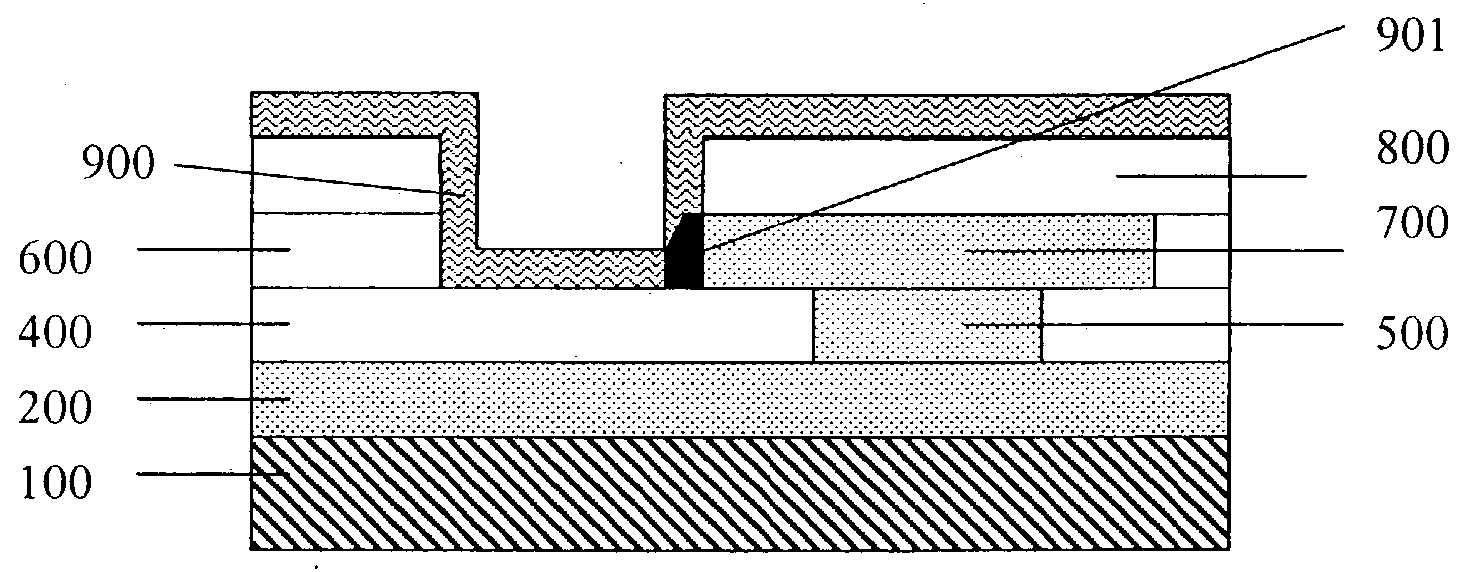

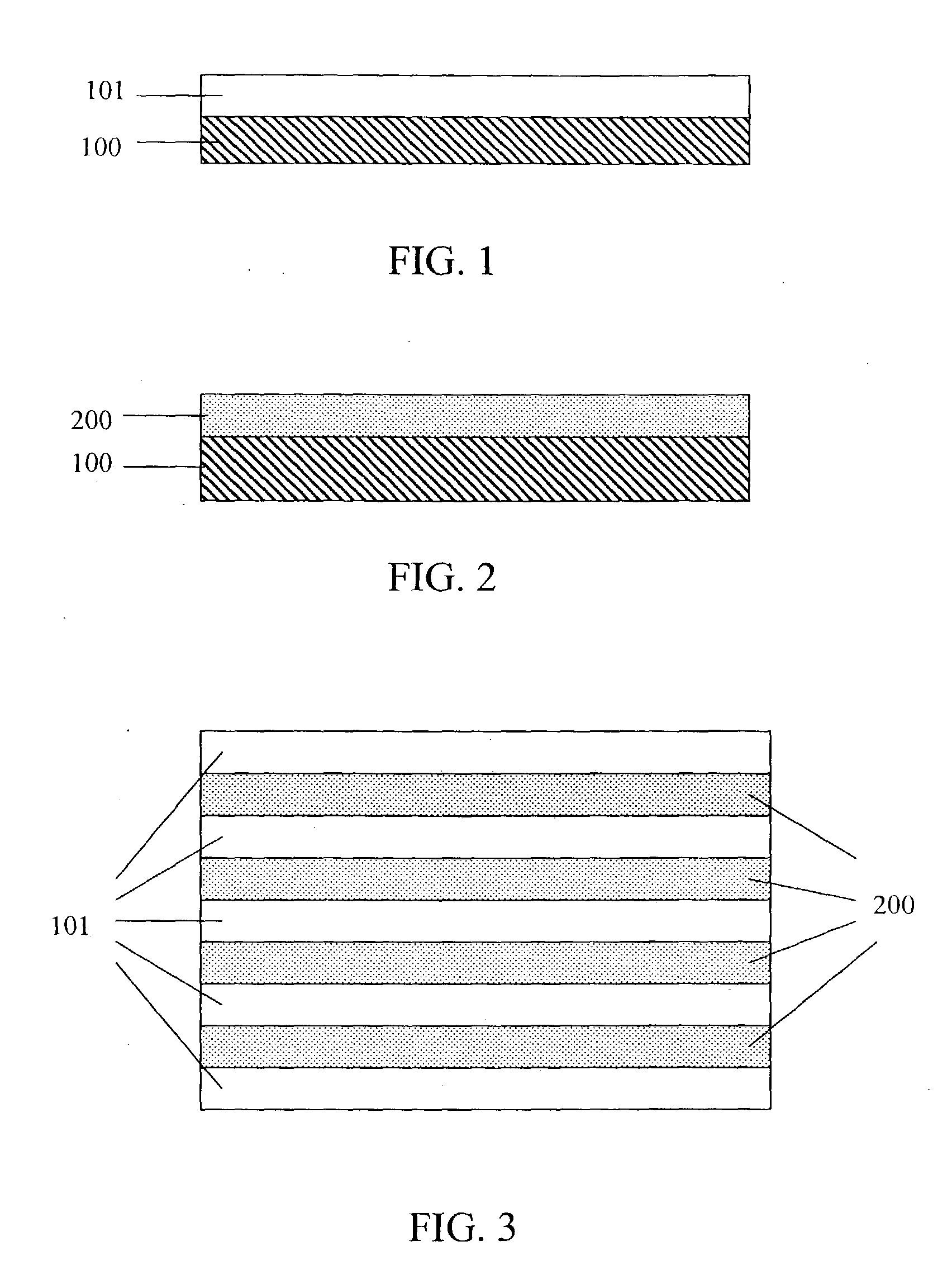

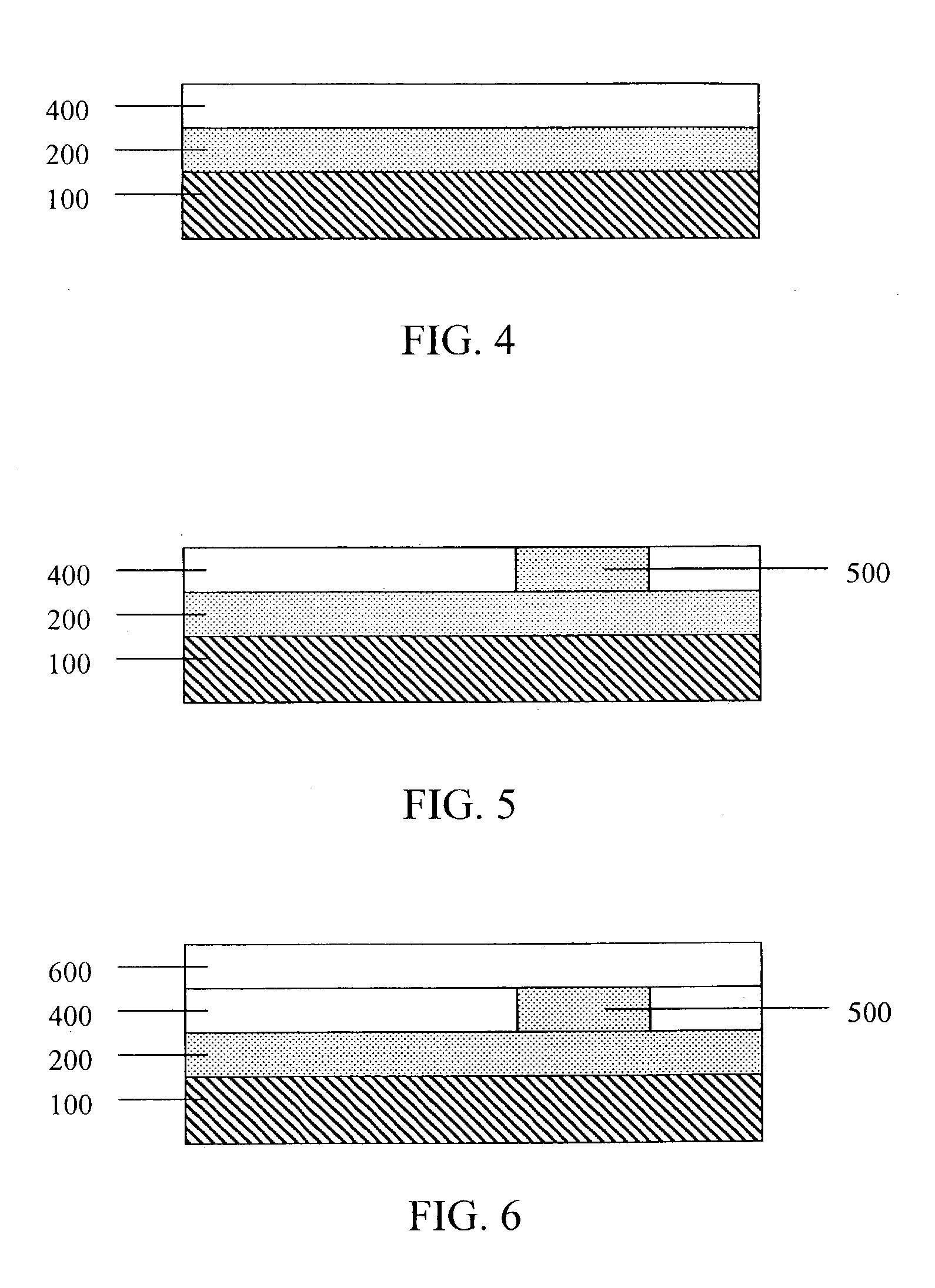

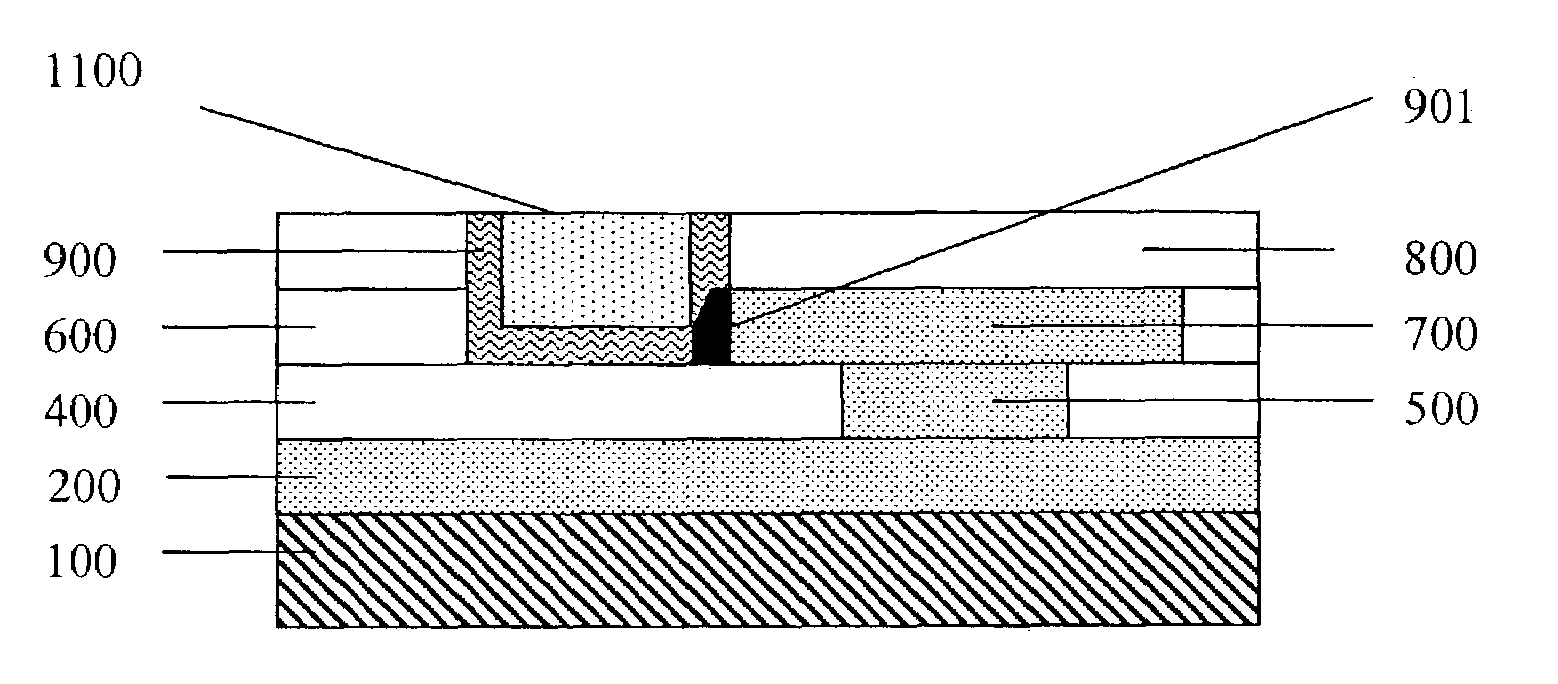

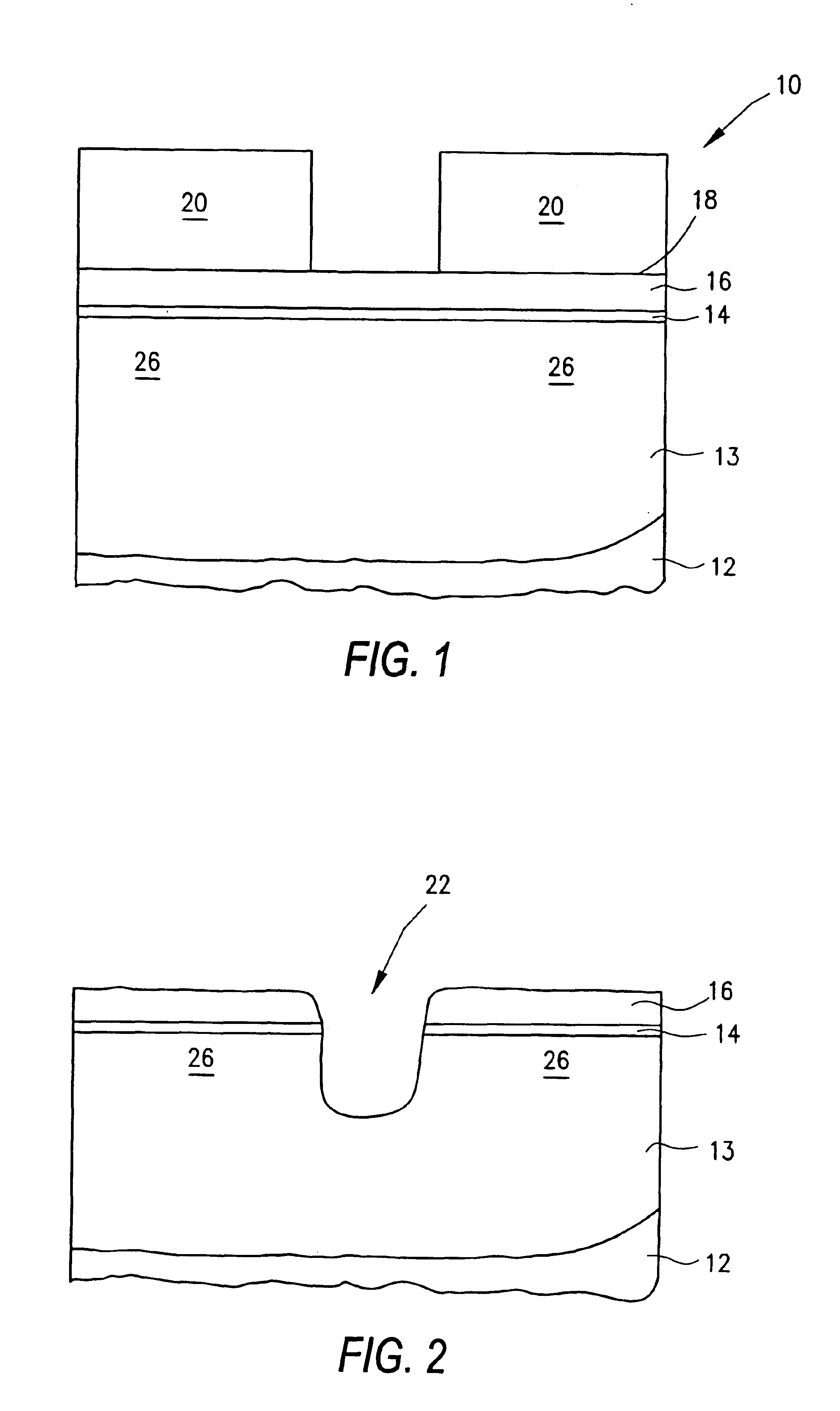

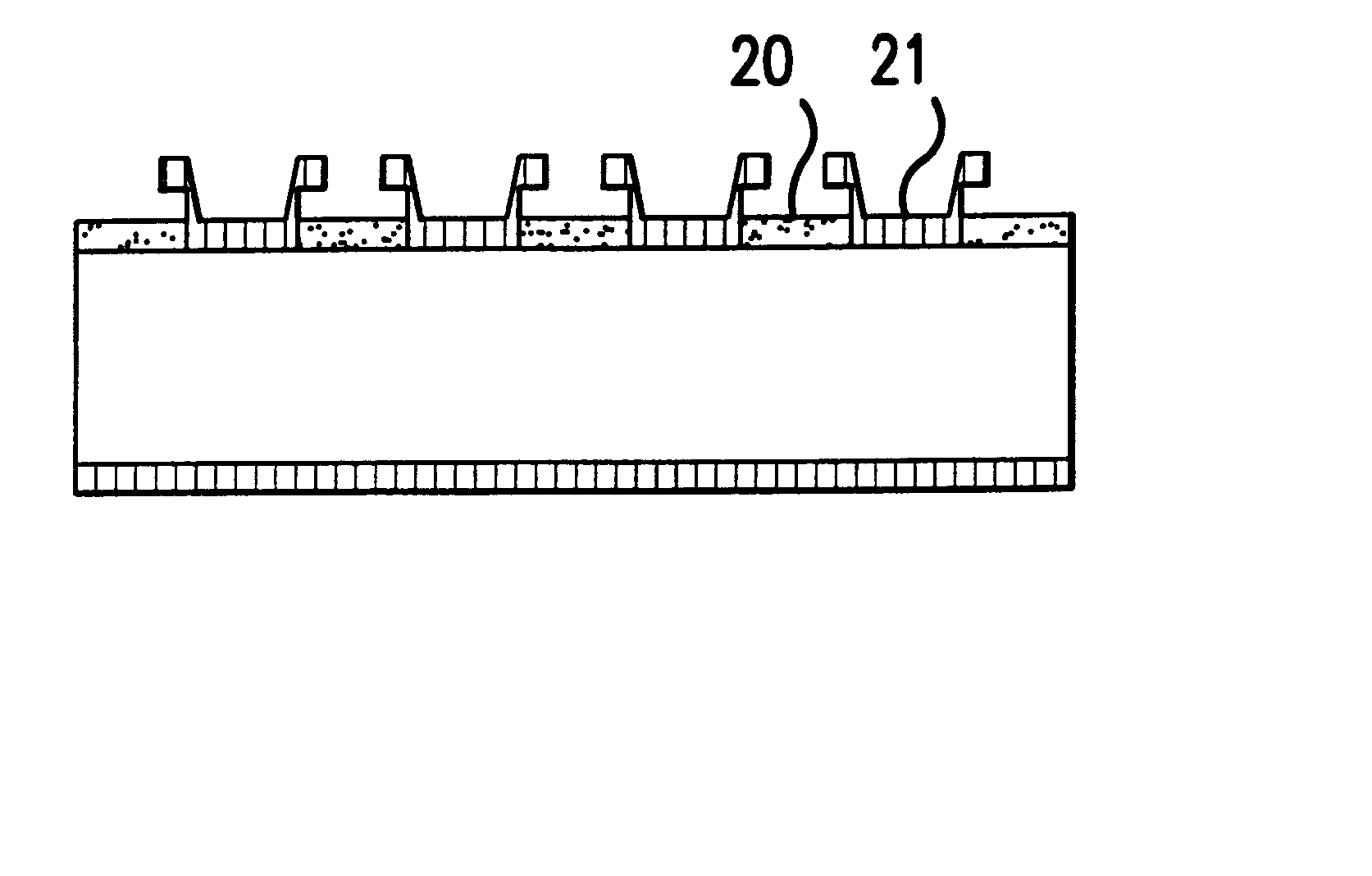

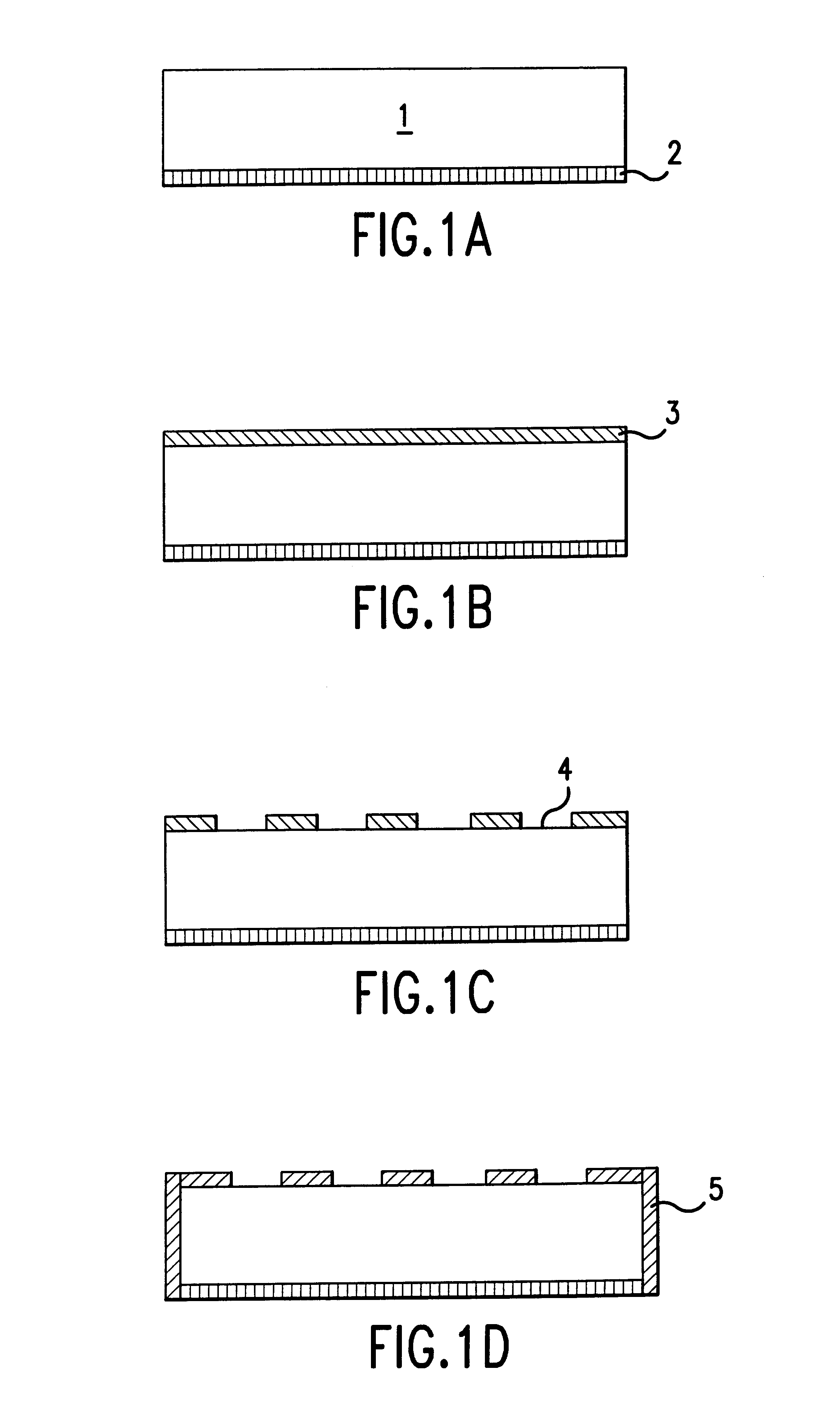

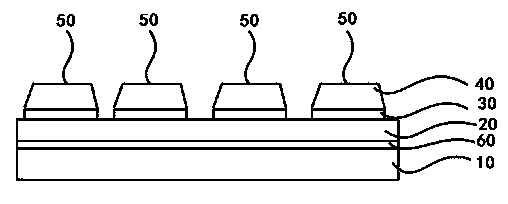

High density chalcogenide memory cells

ActiveUS20040248339A1Tight and repeatable controlImprove electrical isolationSolid-state devicesSemiconductor/solid-state device manufacturingHigh densityAlloy

A non-volatile memory cell is constructed from a chalcogenide alloy structure and an associated electrode side wall. The electrode is manufactured with a predetermined thickness and juxtaposed against a side wall of the chalcogenide alloy structure, wherein at least one of the side walls is substantially perpendicular to a planar surface of the substrate. The thickness of the electrode is used to control the size of the active region created within the chalcogenide alloy structure. Additional memory cells can be created along rows and columns to form a memory matrix. The individual memory cells are accessed through address lines and address circuitry created during the formation of the memory cells. A computer can thus read and write data to particular non-volatile memory cells within the memory matrix.

Owner:MACRONIX INT CO LTD

High density chalcogenide memory cells

InactiveUS7067865B2Tight and repeatable controlImprove electrical isolationTransistorSolid-state devicesHigh densityAlloy

A non-volatile memory cell is constructed from a chalcogenide alloy structure and an associated electrode side wall. The electrode is manufactured with a predetermined thickness and juxtaposed against a side wall of the chalcogenide alloy structure, wherein at least one of the side walls is substantially perpendicular to a planar surface of the substrate. The thickness of the electrode is used to control the size of the active region created within the chalcogenide alloy structure. Additional memory cells can be created along rows and columns to form a memory matrix. The individual memory cells are accessed through address lines and address circuitry created during the formation of the memory cells. A computer can thus read and write data to particular non-volatile memory cells within the memory matrix.

Owner:MACRONIX INT CO LTD

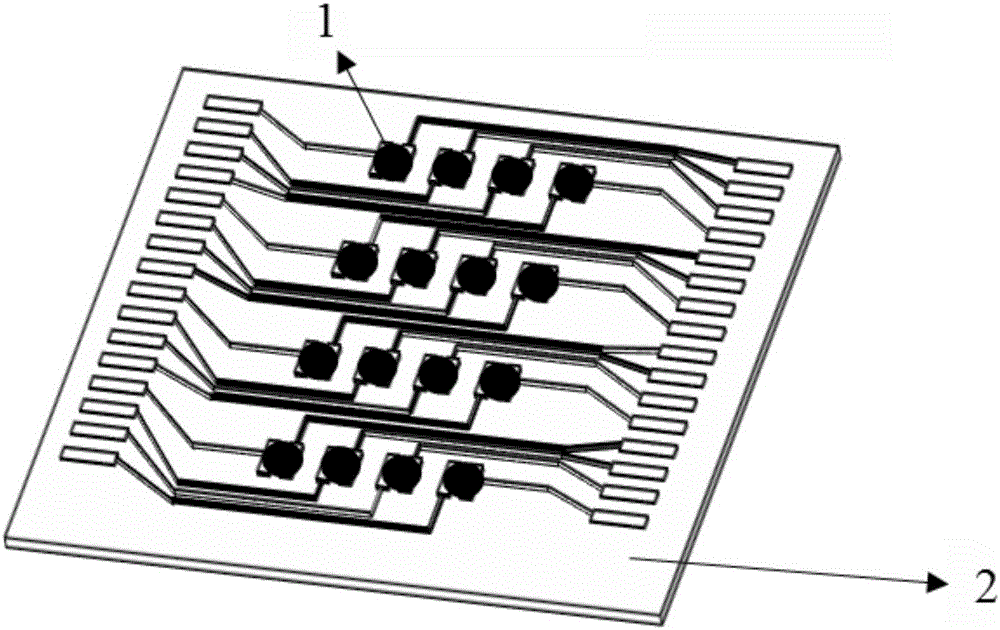

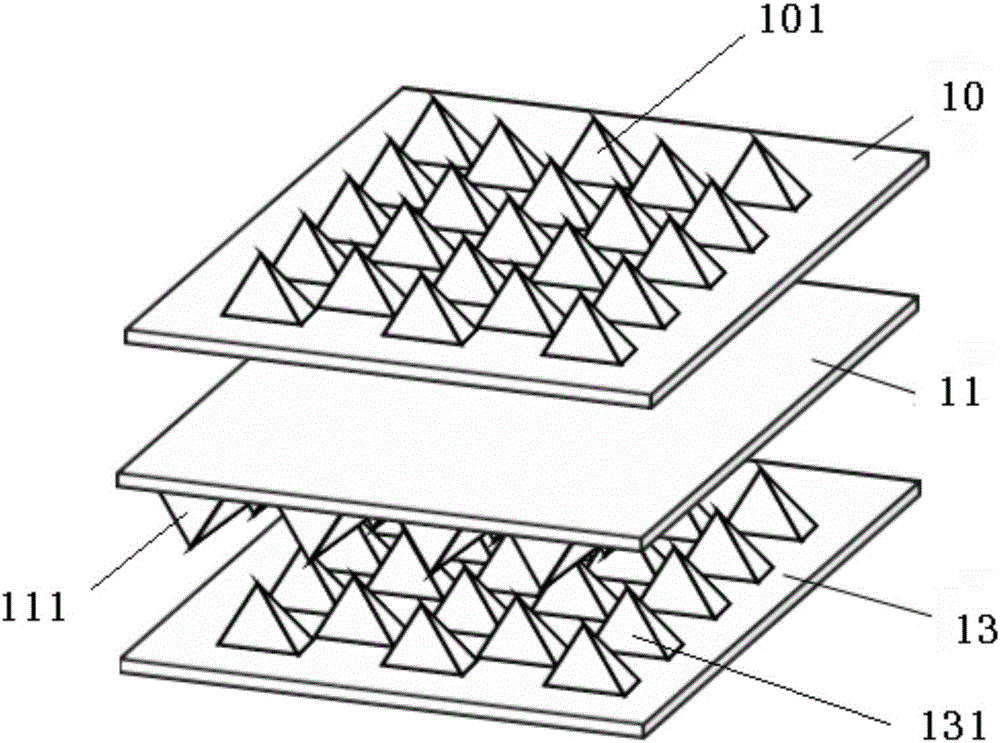

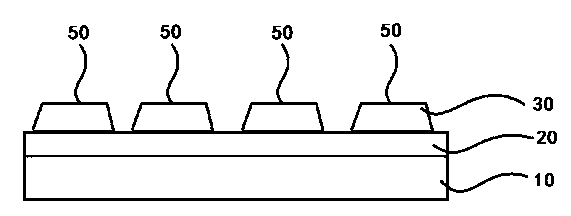

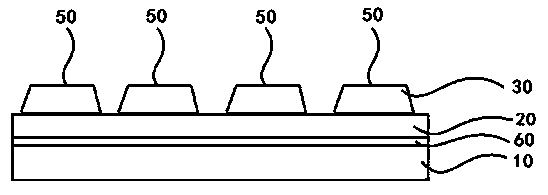

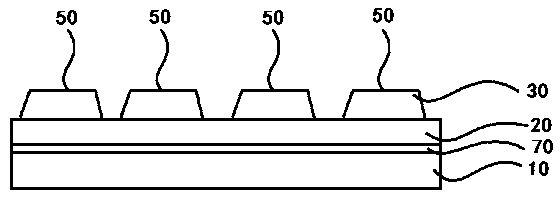

Flexible piezoresistive touch sensor array and preparation method thereof

ActiveCN106197774AIncreased pressure sensitivityImprove electrical isolationForce measurement using piezo-resistive materialsSensor arrayLow voltage

The invention provides a flexible piezoresistive touch sensor array and a preparation method thereof. The sensor array comprises N*N separated piezoresistive layers and a coplanar electrode layer. The piezoresistive layers are arranged on the coplanar electrode layer. Each piezoresistive layer comprises an upper finger pressing layer, a middle sensitive layer and a bottom sensitive layer, wherein the three layers are each provided with a micro pyramid; the coplanar electrode layer comprises a polymer electrode substrate and N*N gold electrode pairs located on the polymer electrode substrate. The piezoresistive layers adopt polymer films with the micro pyramid, and due to the three-layer structure, the sensitivity of the sensor at the low-voltage region can be greatly improved. In addition, in order to overcome the defect that a traditional touch sensor is large in crosstalk due to a sandwiched structure, the coplanar electrode layer is adopted, all electrodes are located on the same plane, each piezoresistive layer is attached to the corresponding electrode pair, the piezoresistive units are completely separated, and the sensitivity and anti-interference capacity of the sensor are effectively improved.

Owner:SHANGHAI JIAO TONG UNIV

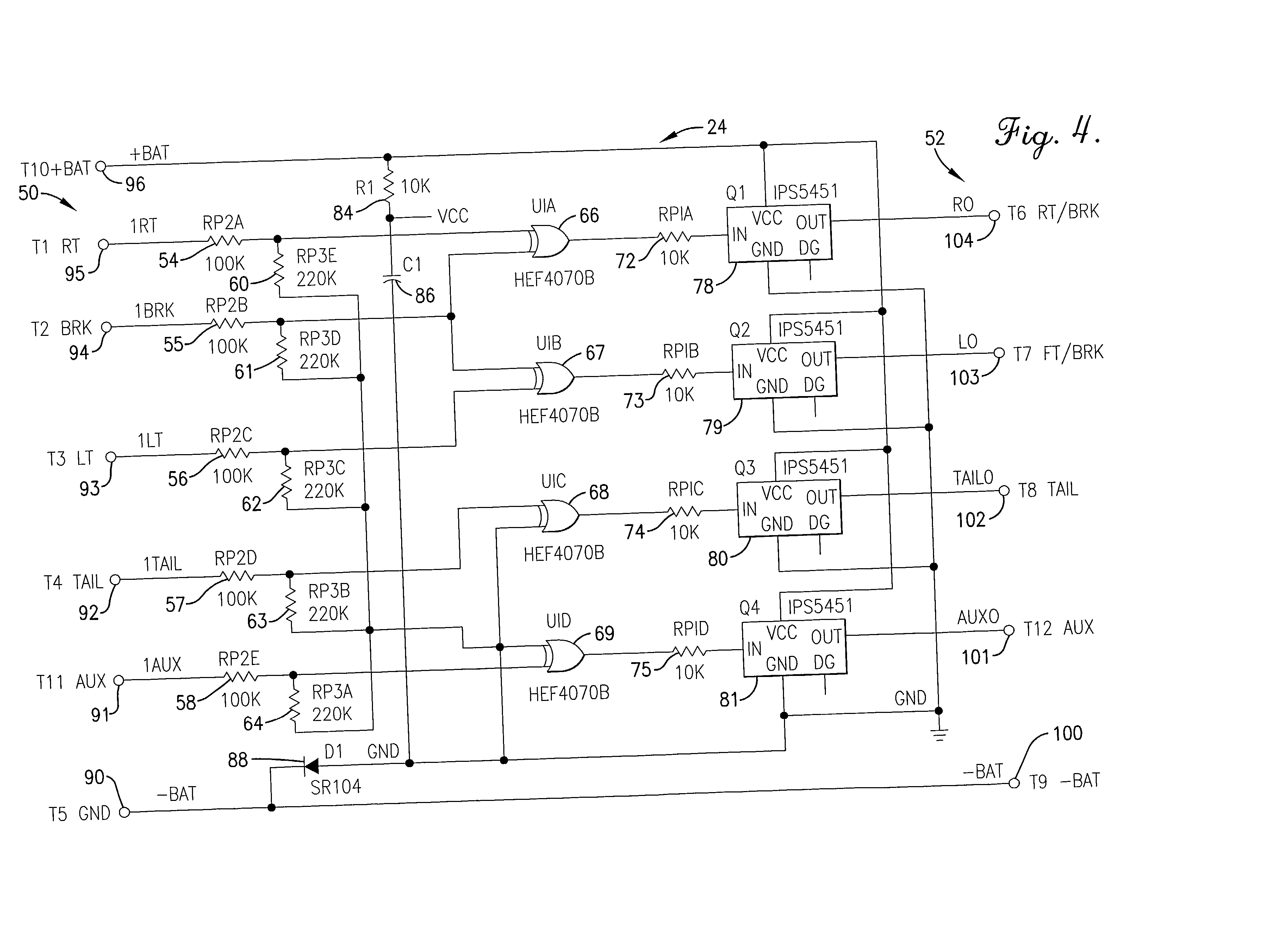

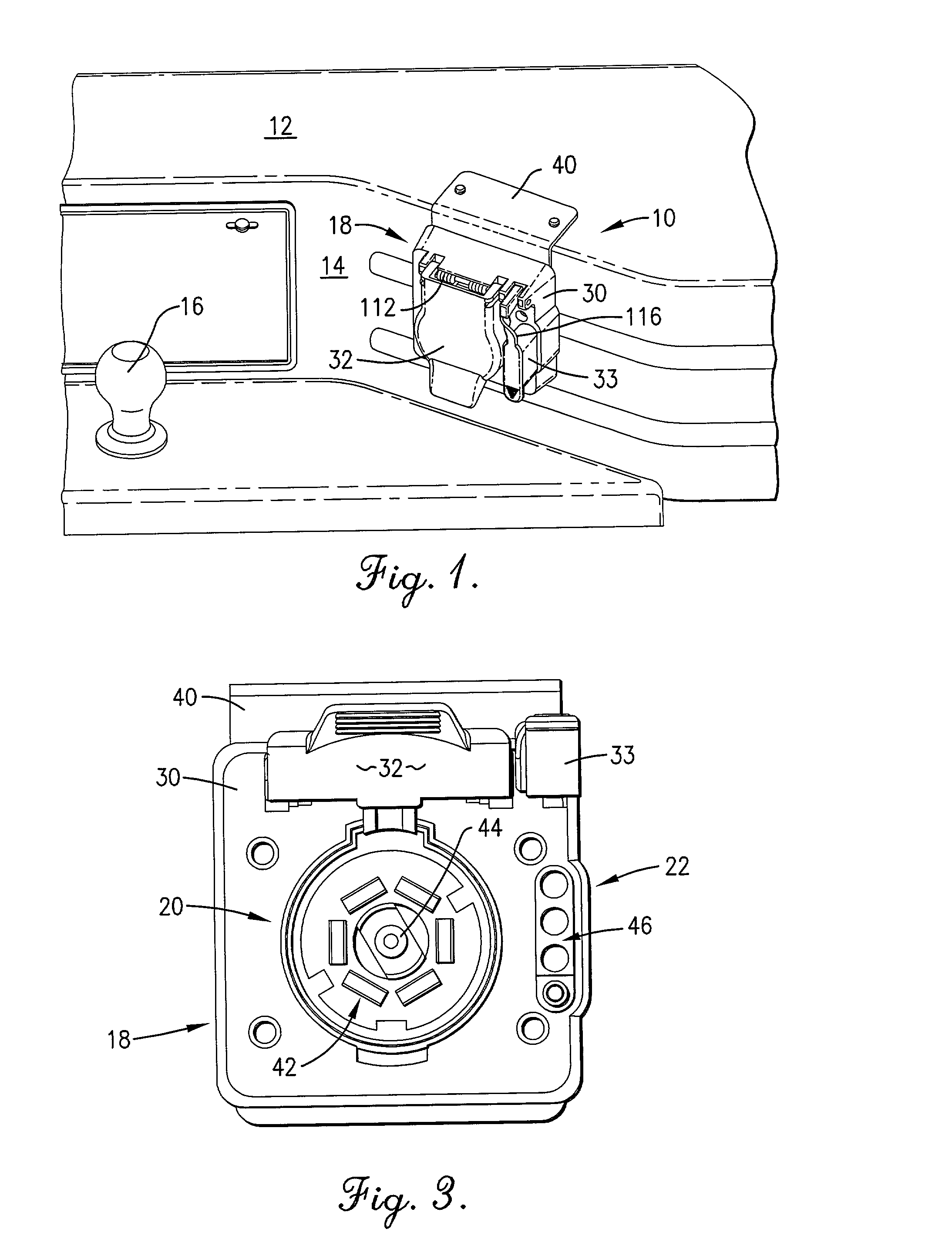

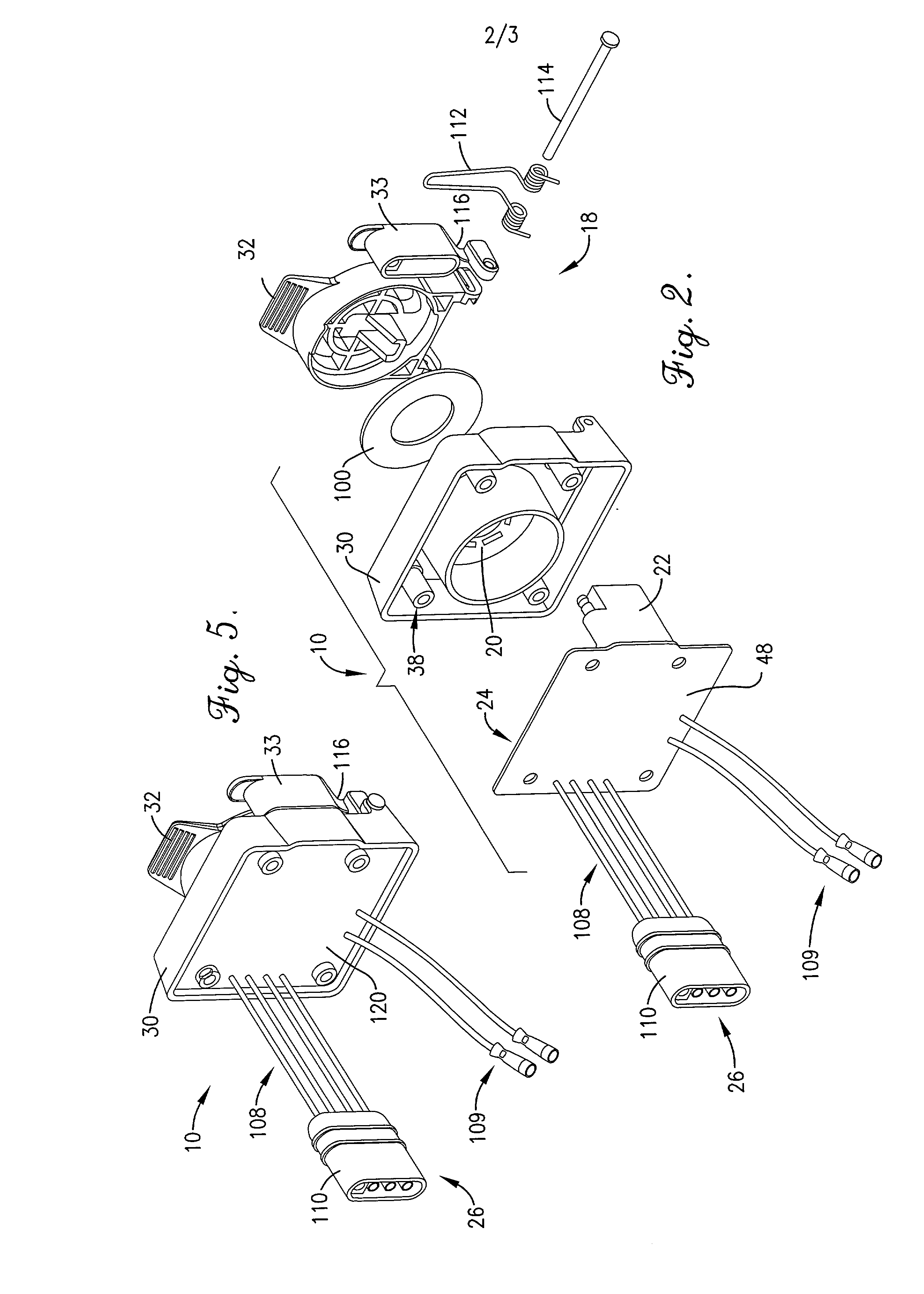

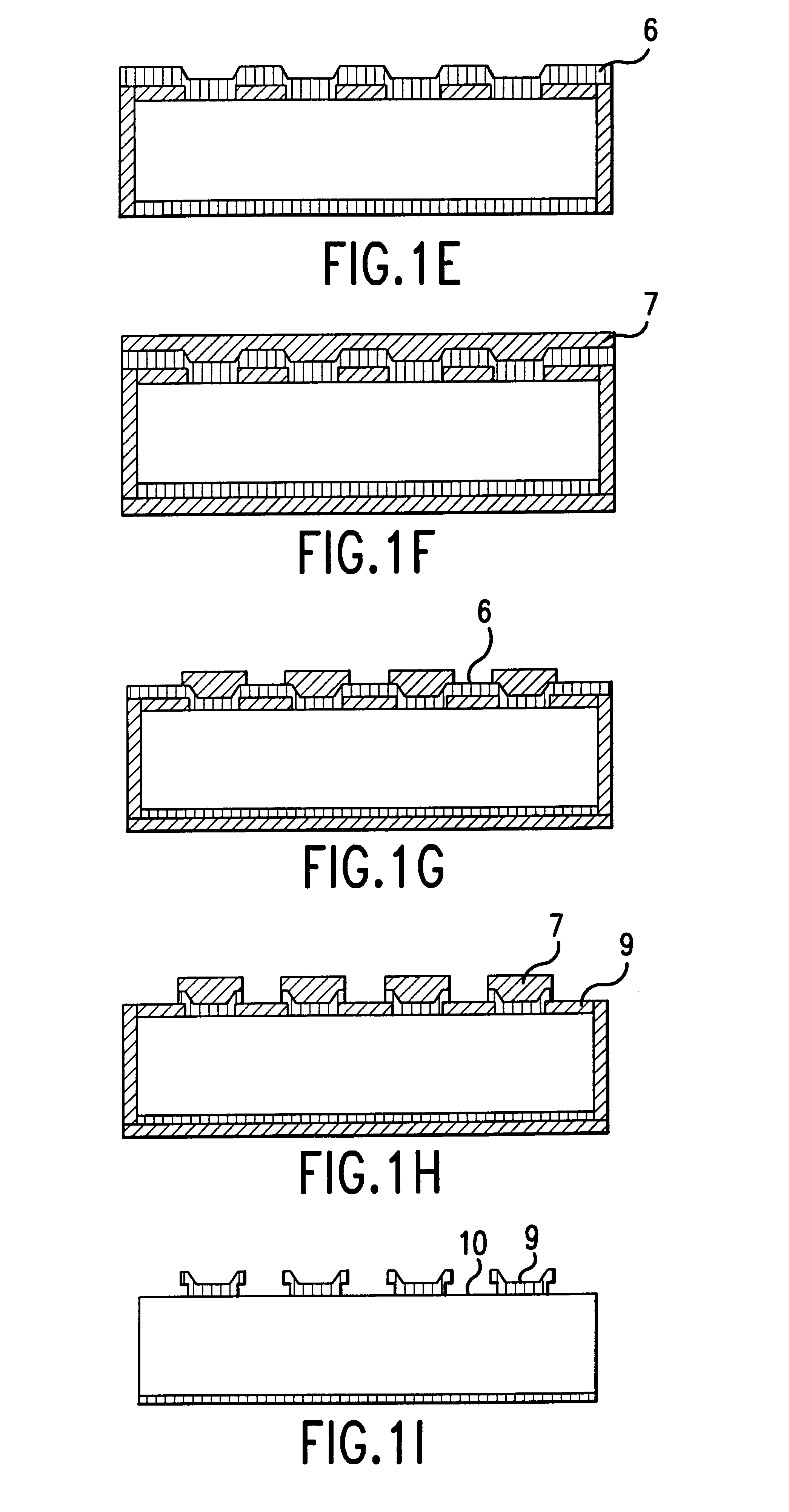

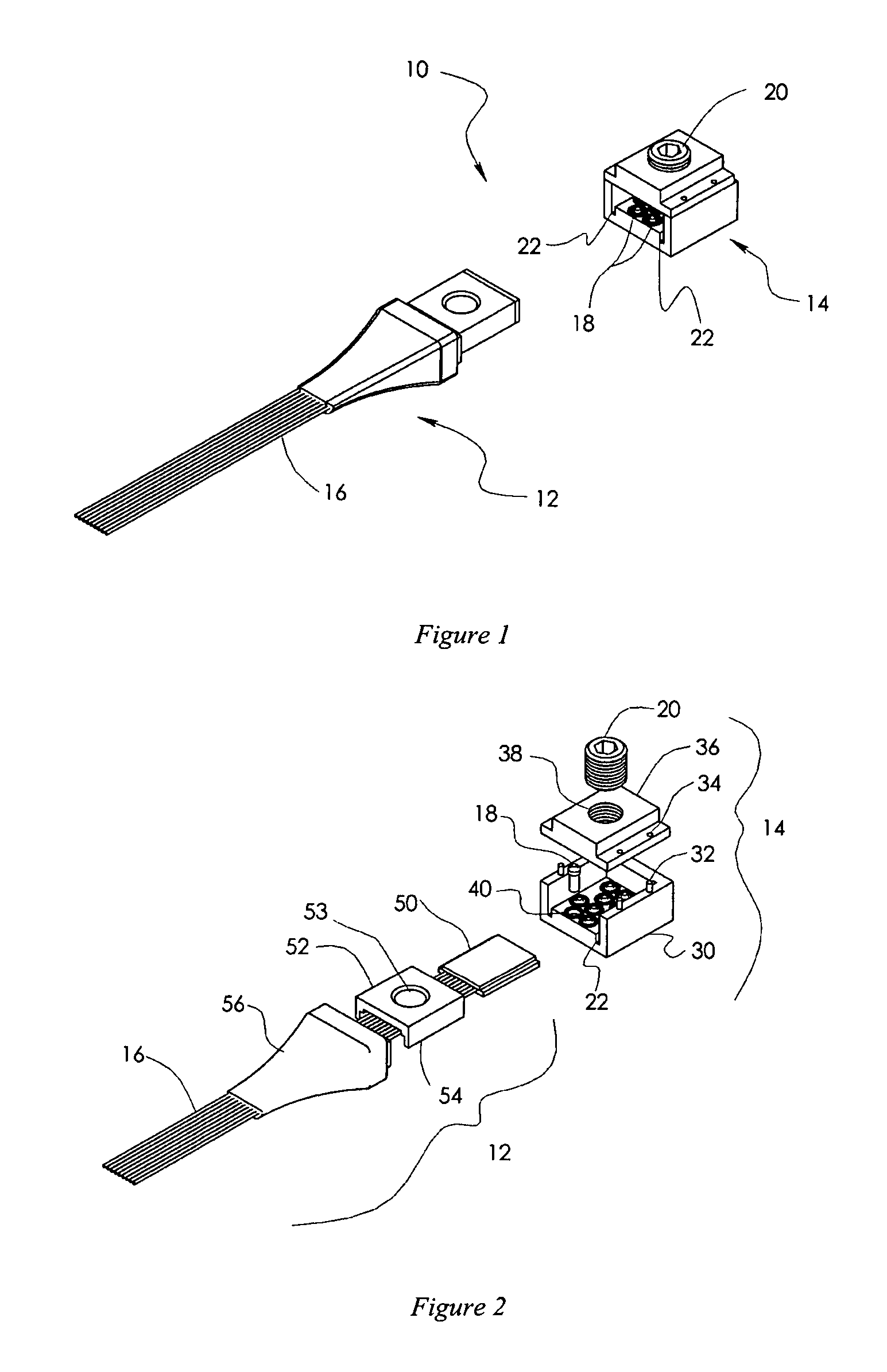

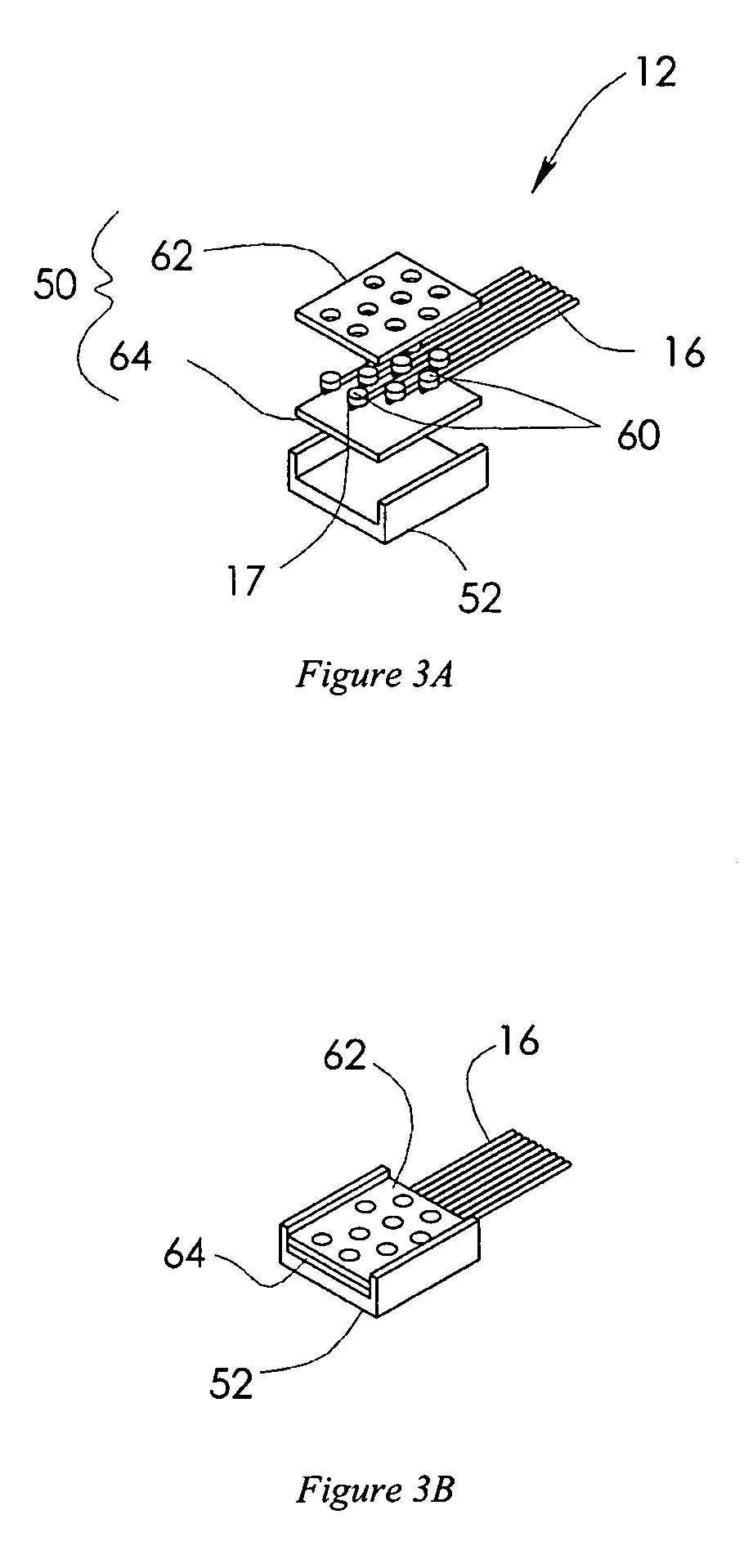

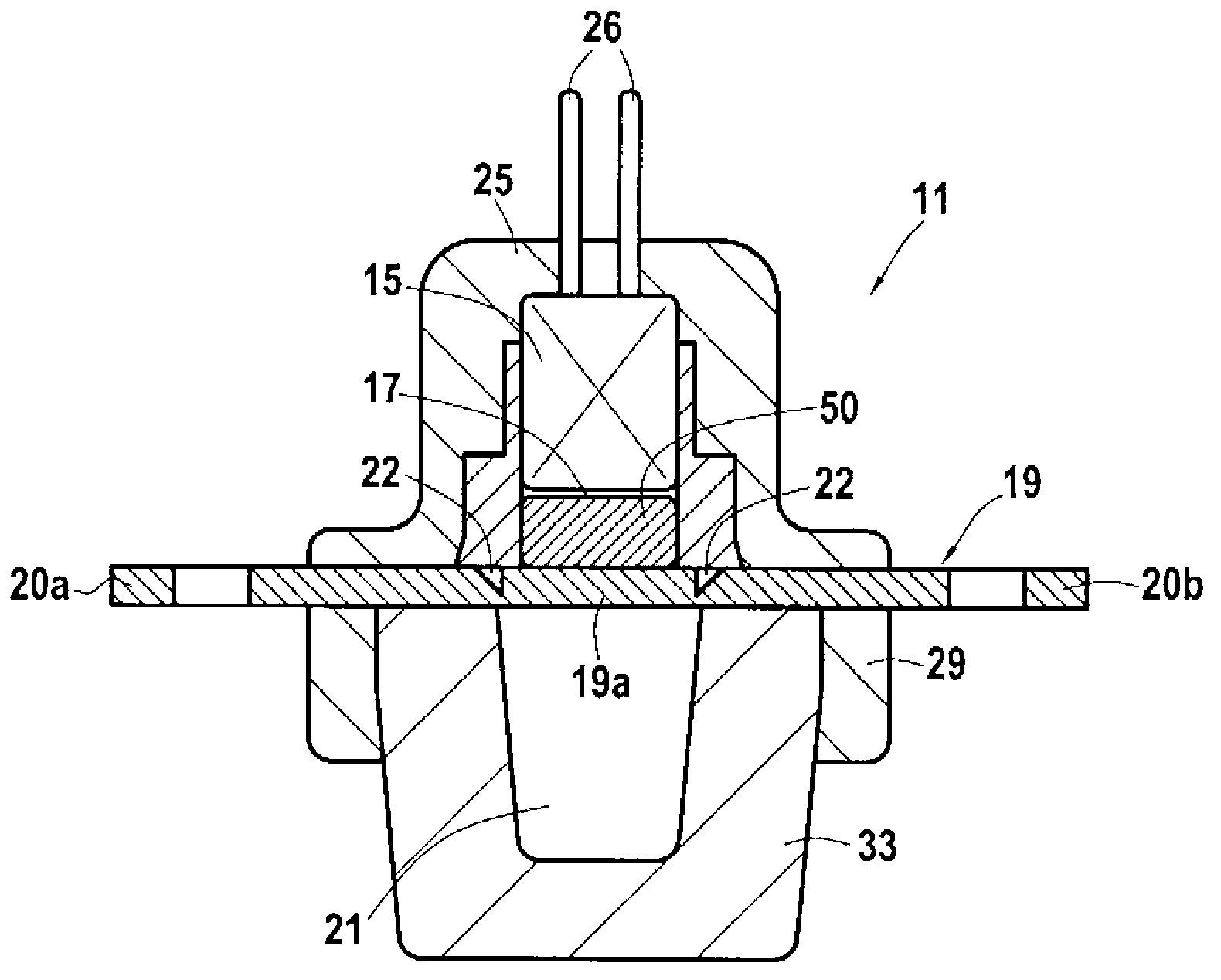

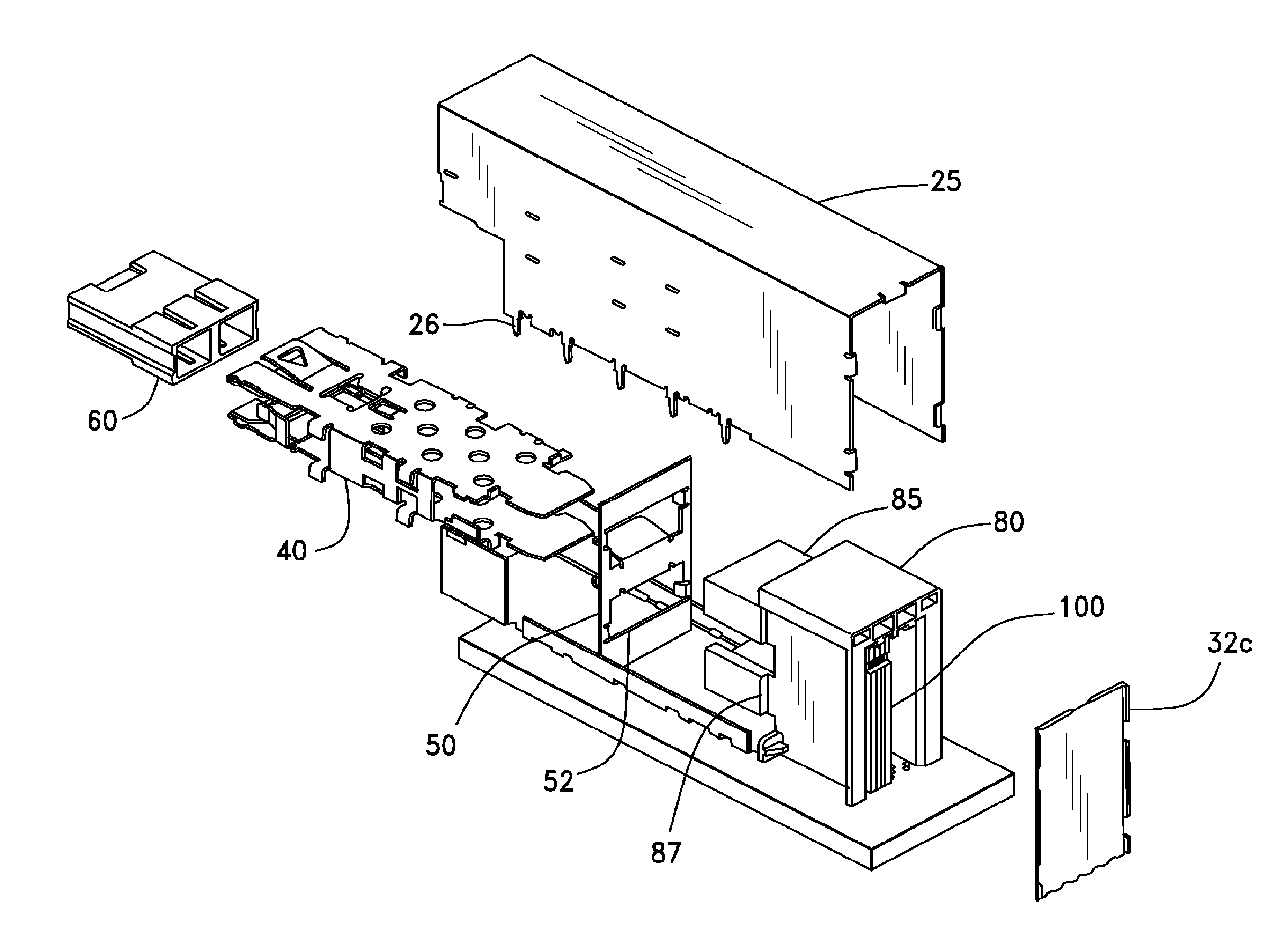

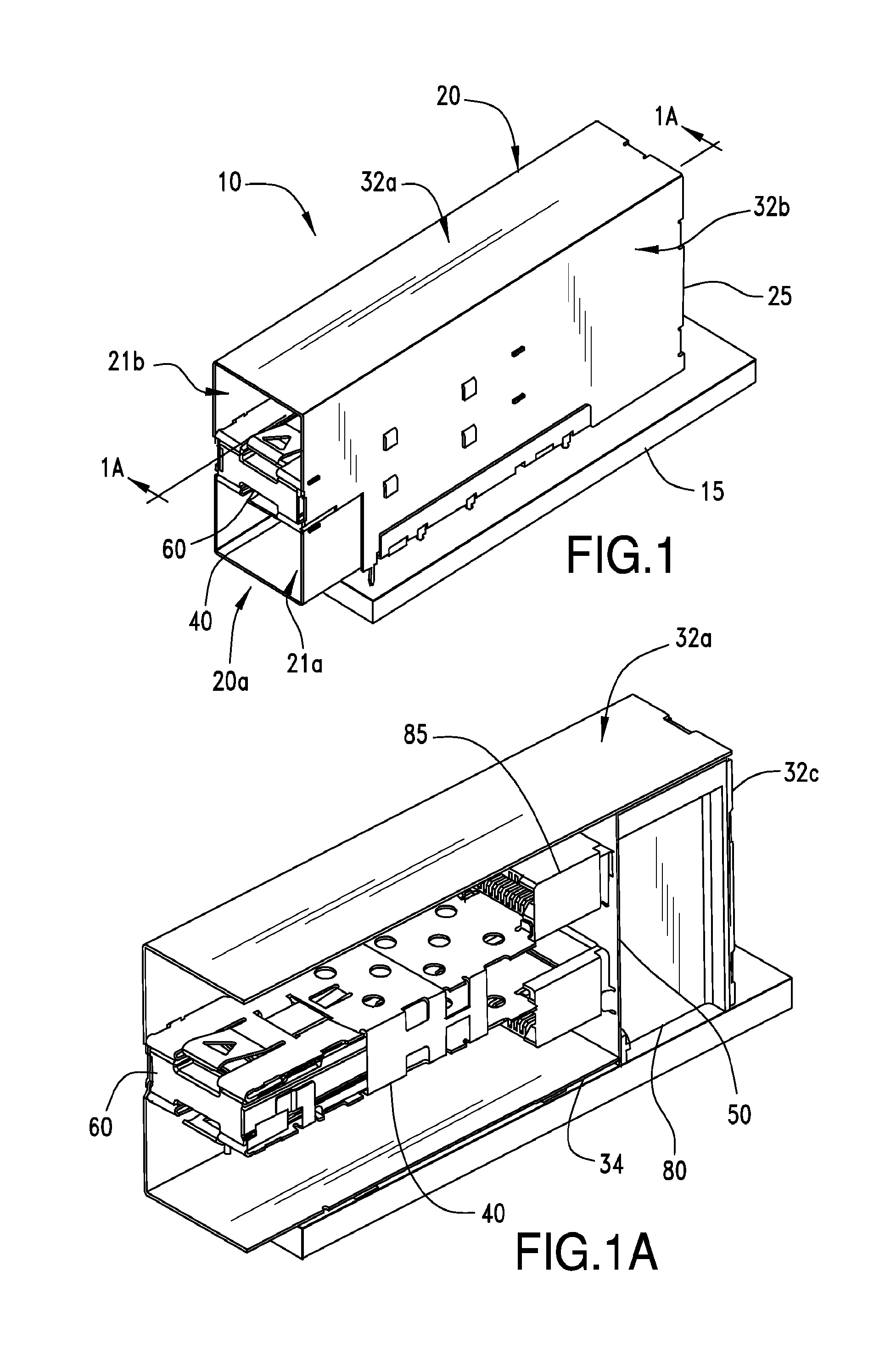

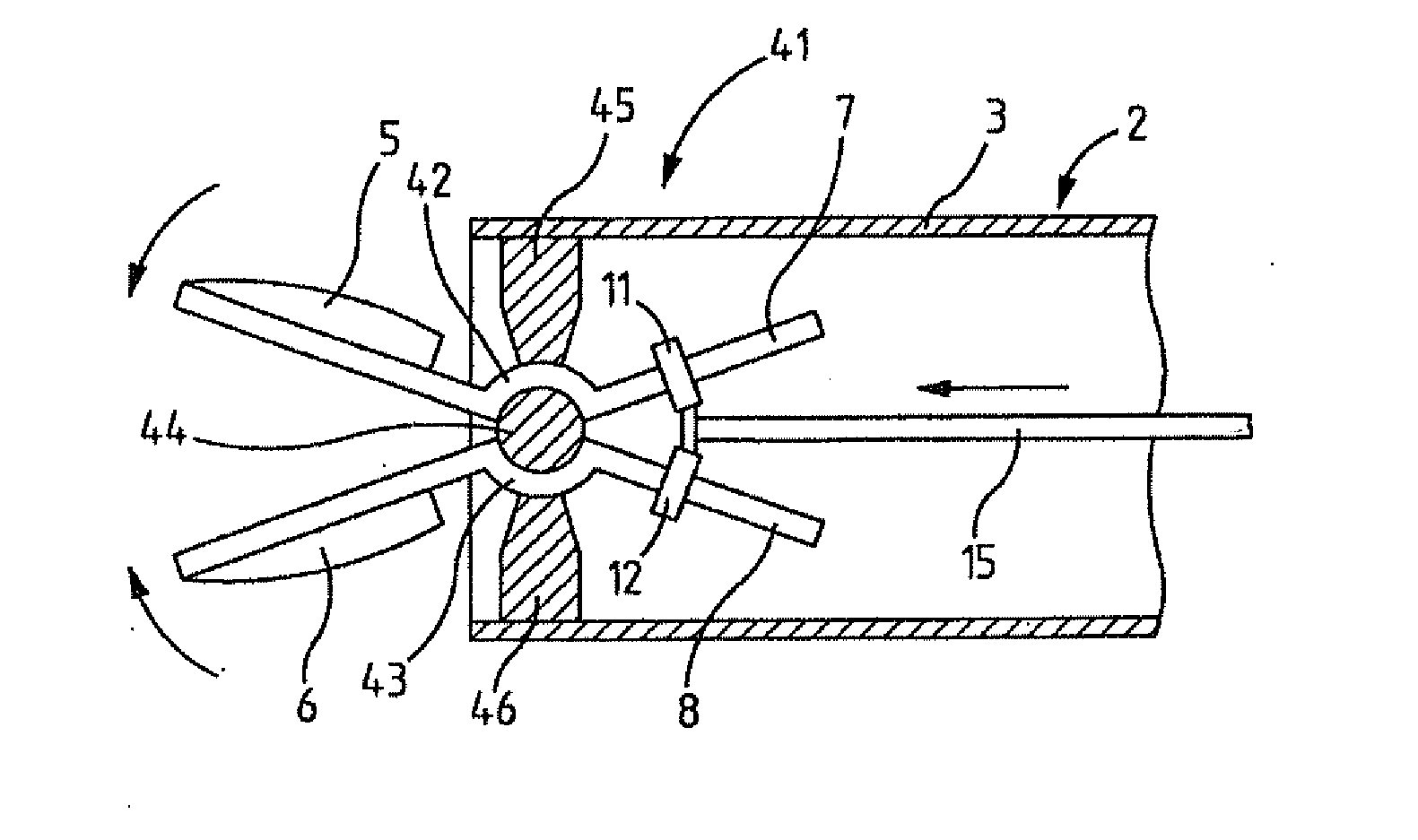

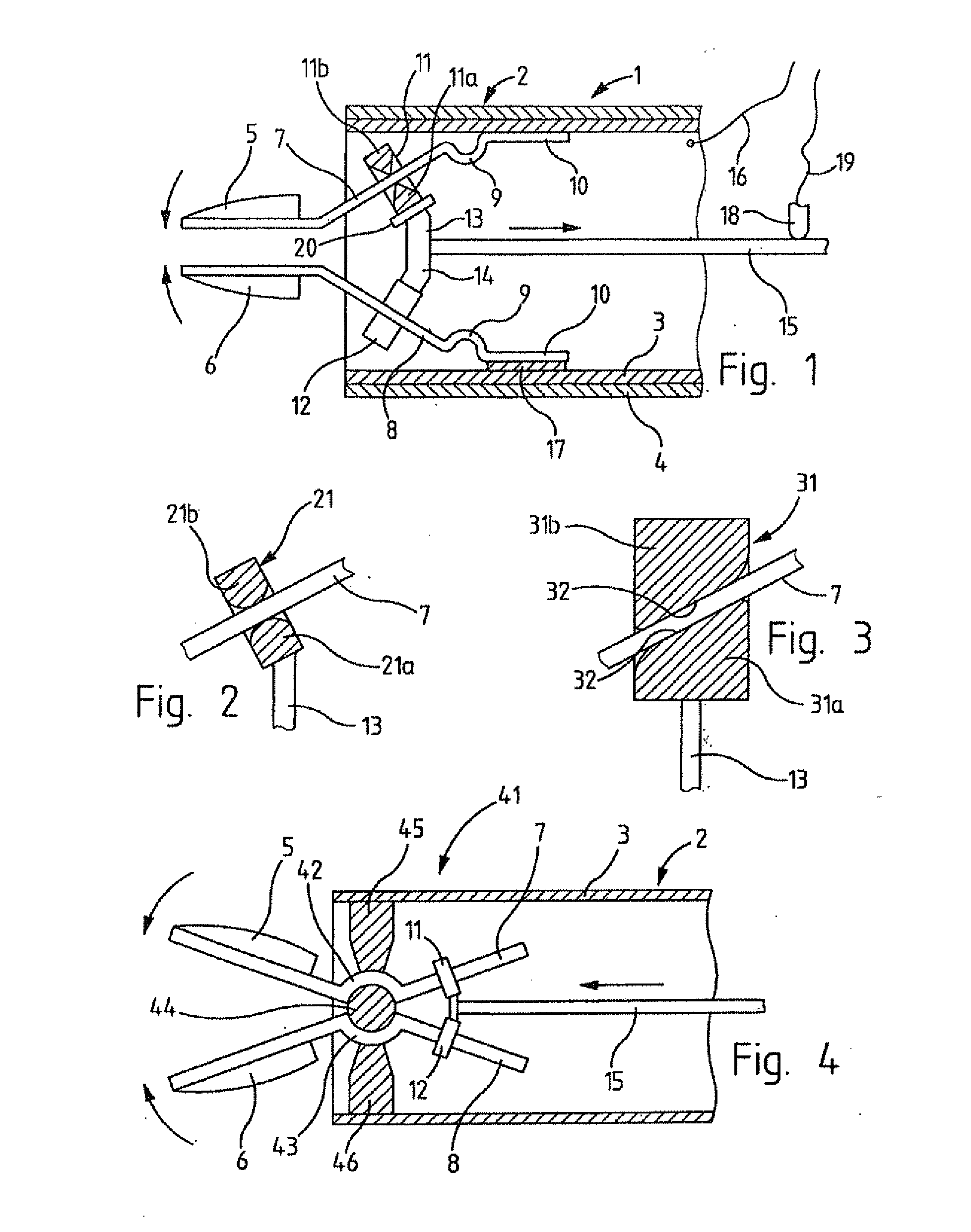

Electrical interface device for towing

InactiveUS20020125771A1Restricts feedback damageImprove electrical isolationVehicle connectorsElectric devicesElectricityElectronic systems

An electrical interface device (10) for towing, operable to facilitate releasably coupling one or more electrical subsystems of a towing vehicle (12) and a towed vehicle, and including associated modular, removable circuitry (24). The circuitry (24) may provide overload, short-circuit, and reverse connection protection and power signal filtering. Alternative or additional circuitry may be added to support other functionality, including interfacing a brake control subsystem. Circular receptacle and flat plug connectors (20,22) are provided to accommodate without modification a variety of electrical connectors. Covers (32,33) are also provided to protect unused connectors from adverse environmental conditions.

Owner:HOPKINS MFG

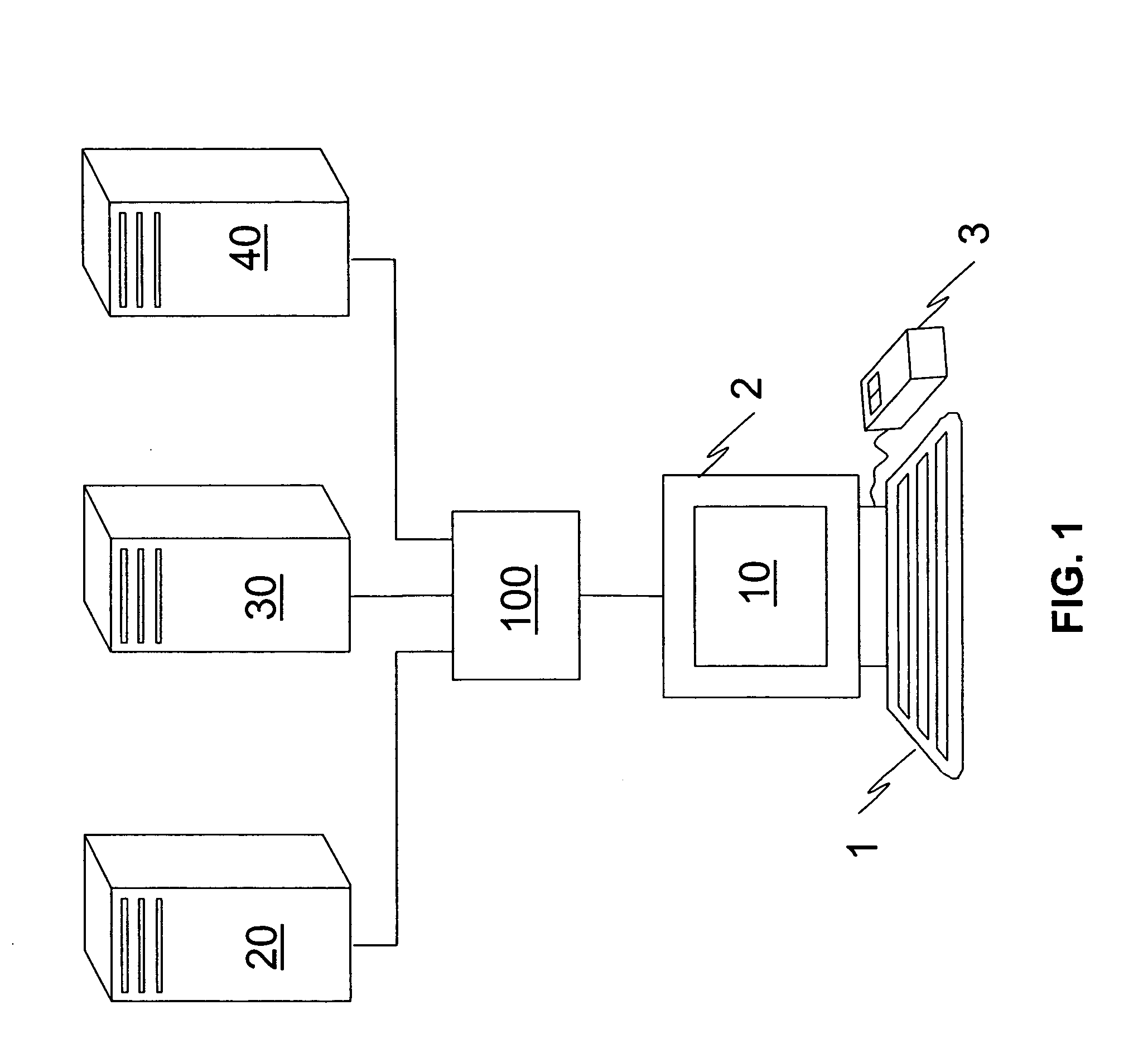

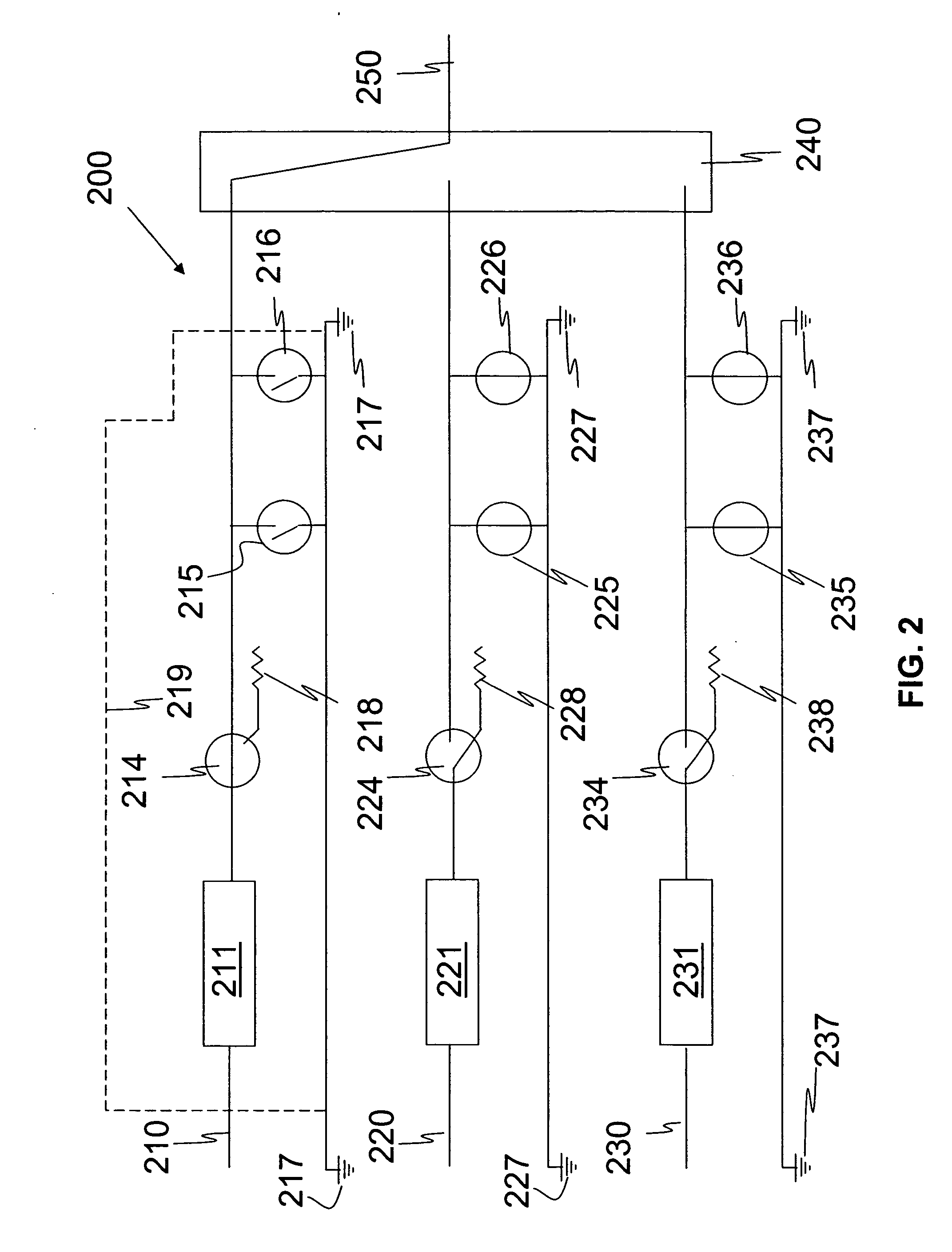

High isolation KVM switch

InactiveUS20050044266A1Good electrical isolationHigh level of electrical isolationMultiplex system selection arrangementsDigital computer detailsDisplay deviceEngineering

A switching system between channels from connected computers, the system comprising a signal path for each channel extending from each connected computer to a user's input and display devices, each signal path being substantially shielded and comprising a filter, a series switch connected to a resistor, and at least one shunt switch connected to a ground; and a channel selector switch receiving all of the signal paths; wherein the user selects a channel and a corresponding signal from the selected channel travels in the corresponding signal path through the filter, the series switch, and the channel selector, and wherein the signals of an unselected channel pass through the filter in the corresponding signal path to the resistor of the series switch, the signal passes through the at least one shunt switch to the ground, and the signal path of the unselected channel terminates at the channel selector.

Owner:DIGITALNET GOVERNMENT SOLUTIONS

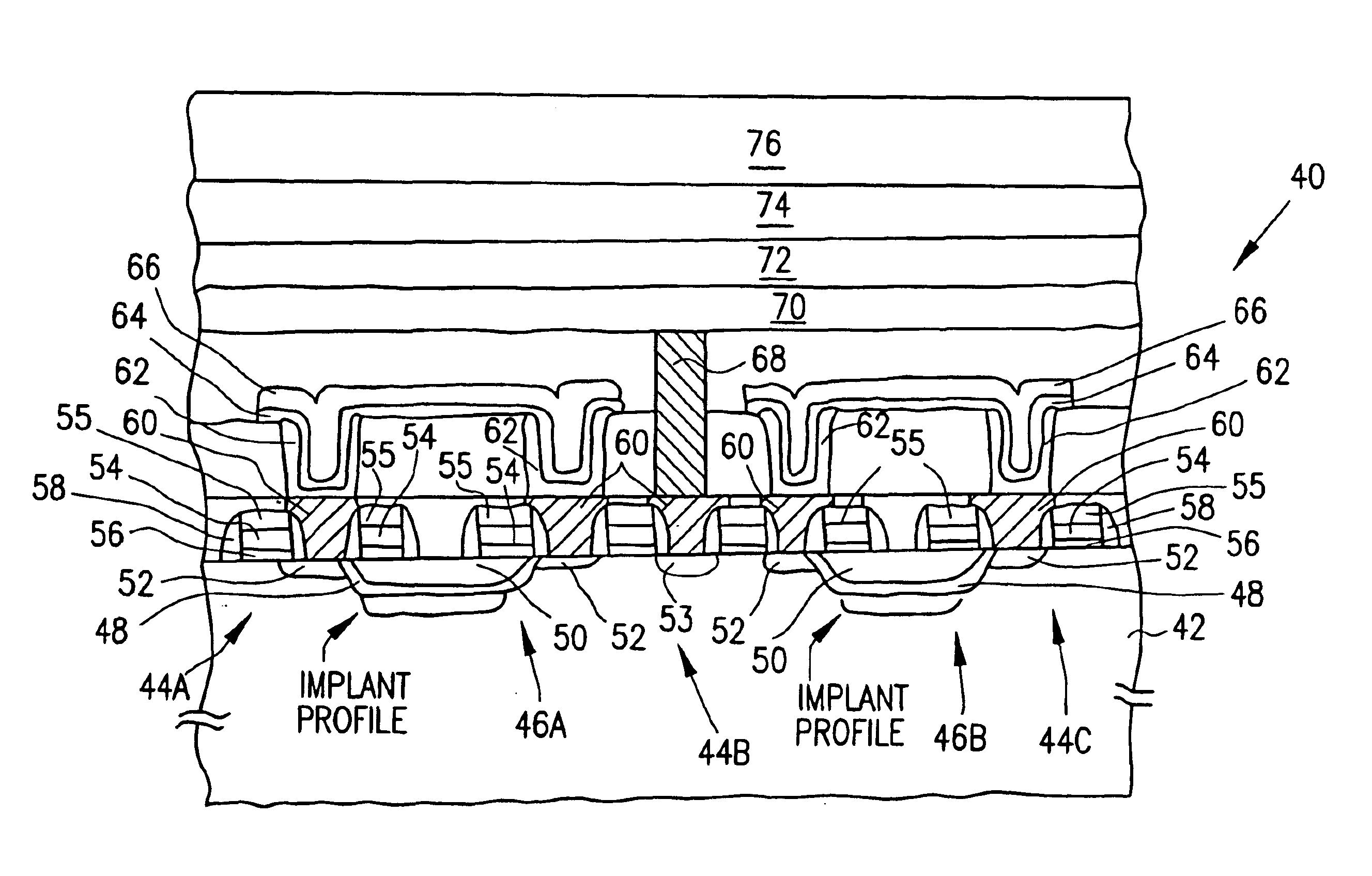

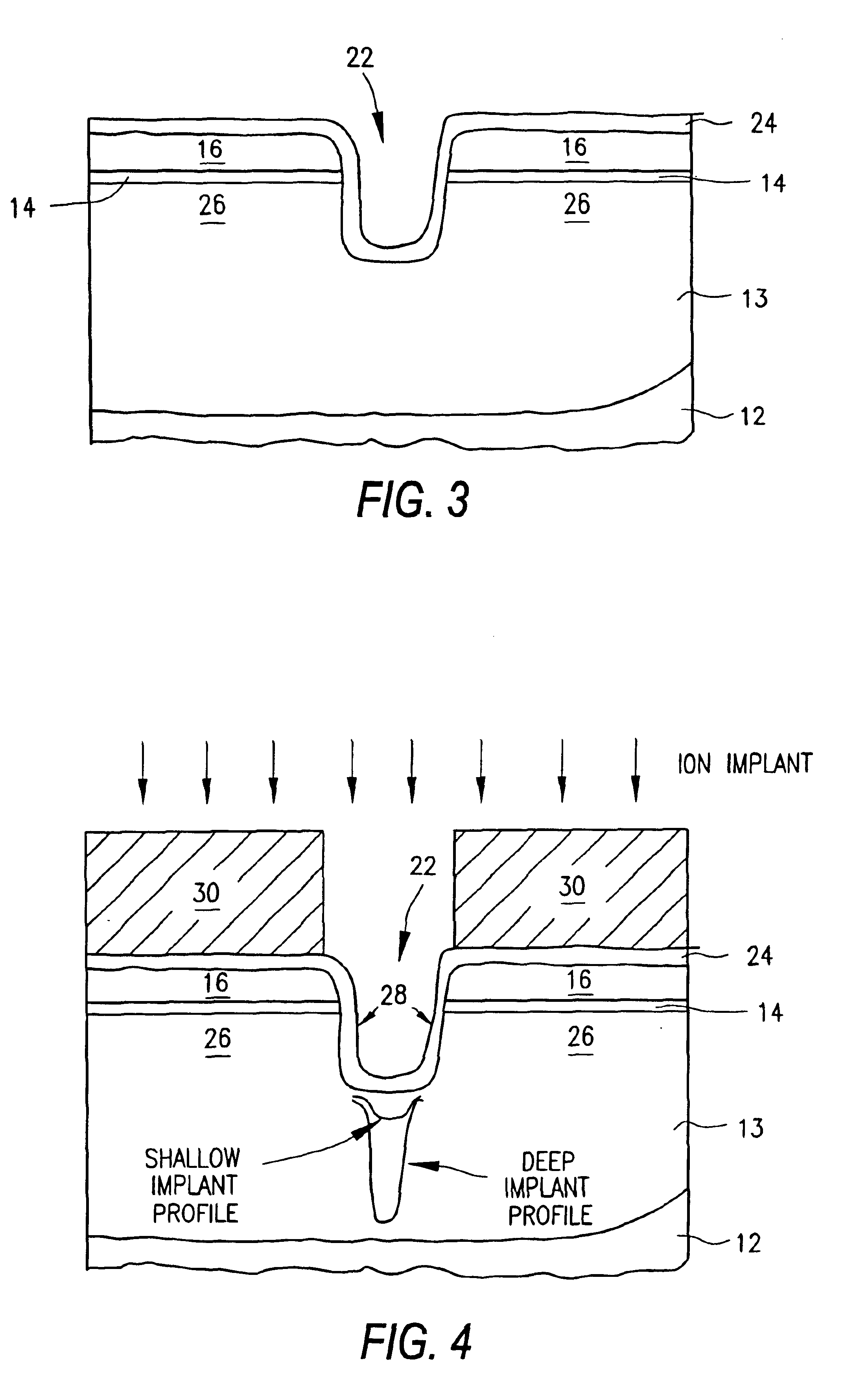

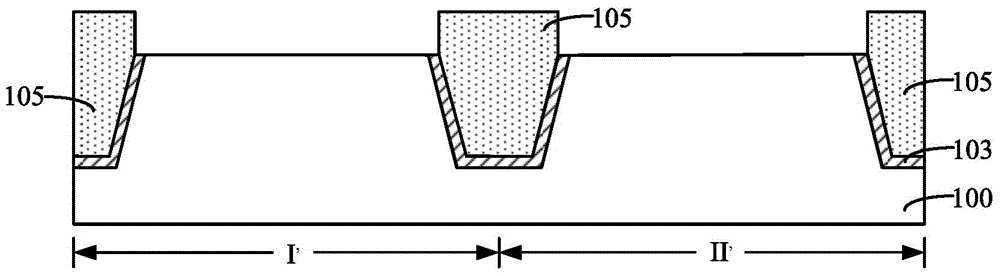

Trench isolation for semiconductor devices

InactiveUS6856001B2Improve electrical isolationReduce optical cross-talkTransistorSolid-state devicesDielectricIsolation techniques

A method of fabricating an integrated circuit includes forming an isolation trench in a semiconductor substrate and partially filling the trench with a dielectric material so that at least the sidewalls of the trench are coated with the dielectric material. Ions are implanted into the substrate in regions directly below the isolation trench after partially filling the trench with the dielectric material. The dielectric along the sidewalls of the trenches can serve as a mask so that substantially all of the ions implanted below the isolation trenches are displaced from the active regions. The dielectric along the sidewalls of the trenches serves as a mask so that substantially all of the ions implanted below the isolation trenches are displaced from the active regions. After the ions are implanted in the substrate below the trenches, the remainder of the trench can be filled with the same or another dielectric material. The trench isolation technique can be used to fabricate memory, logic and imager devices which can exhibit reduced current leakage and / or reduced optical cross-talk.

Owner:MICRON TECH INC

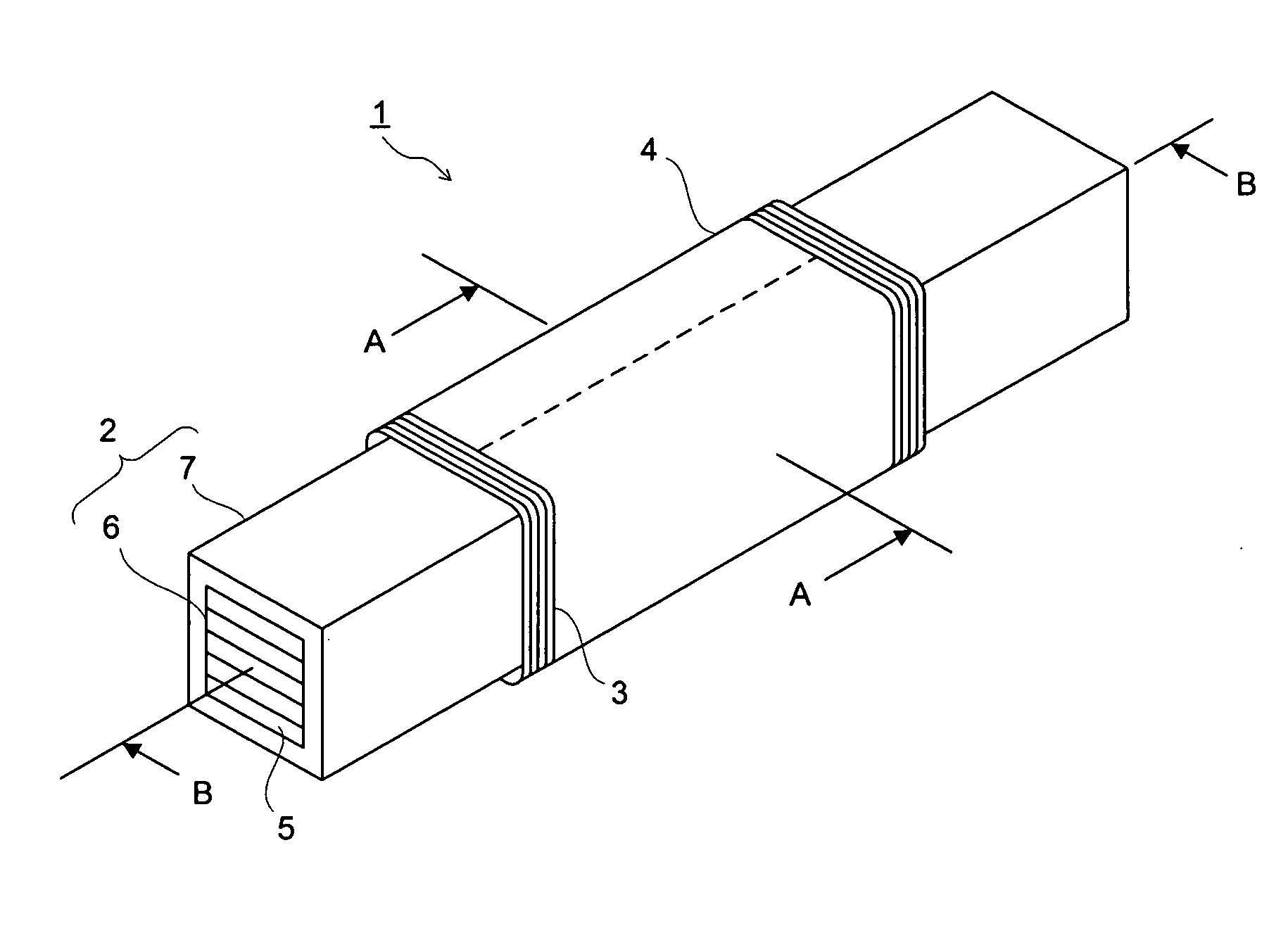

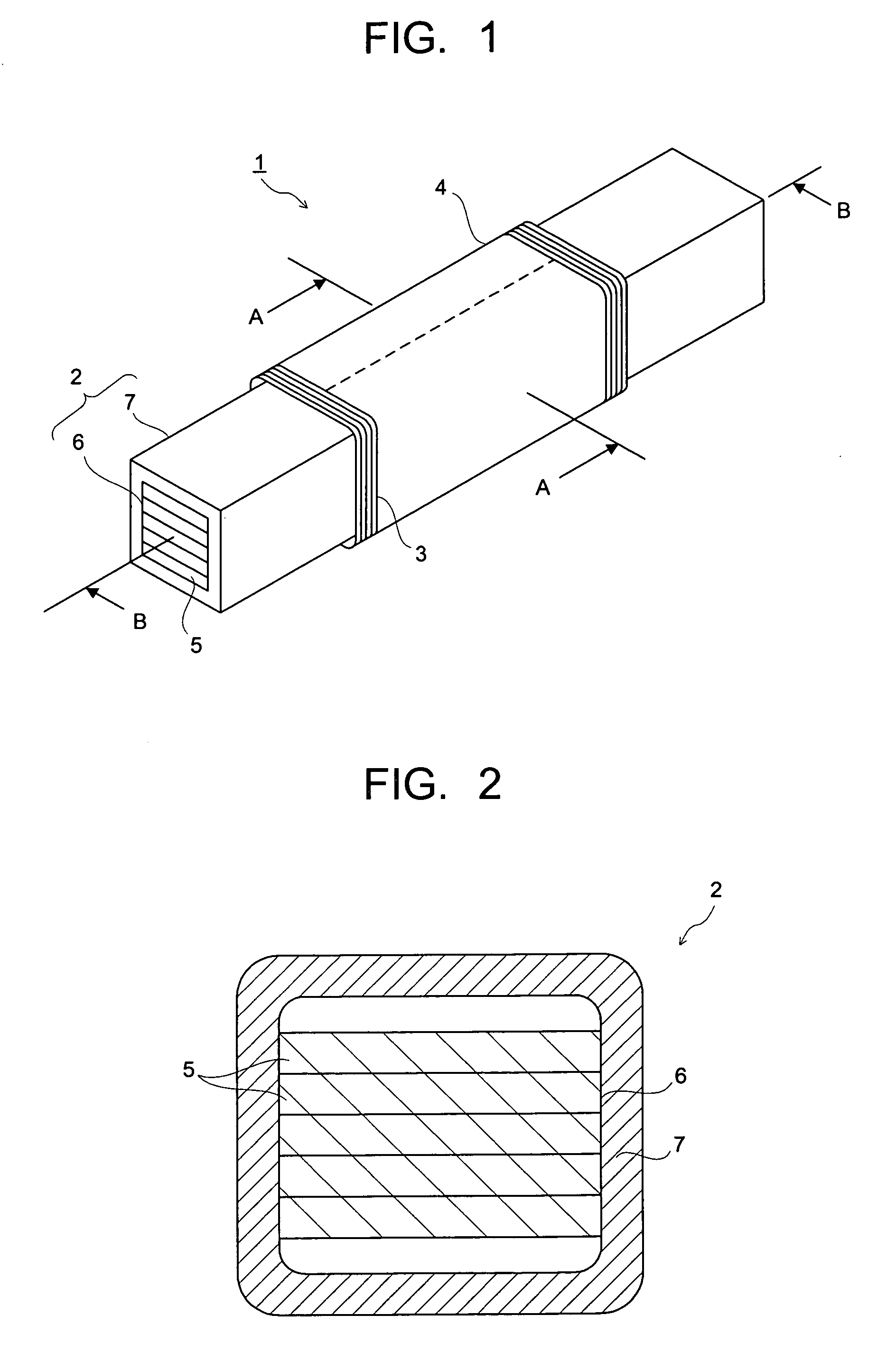

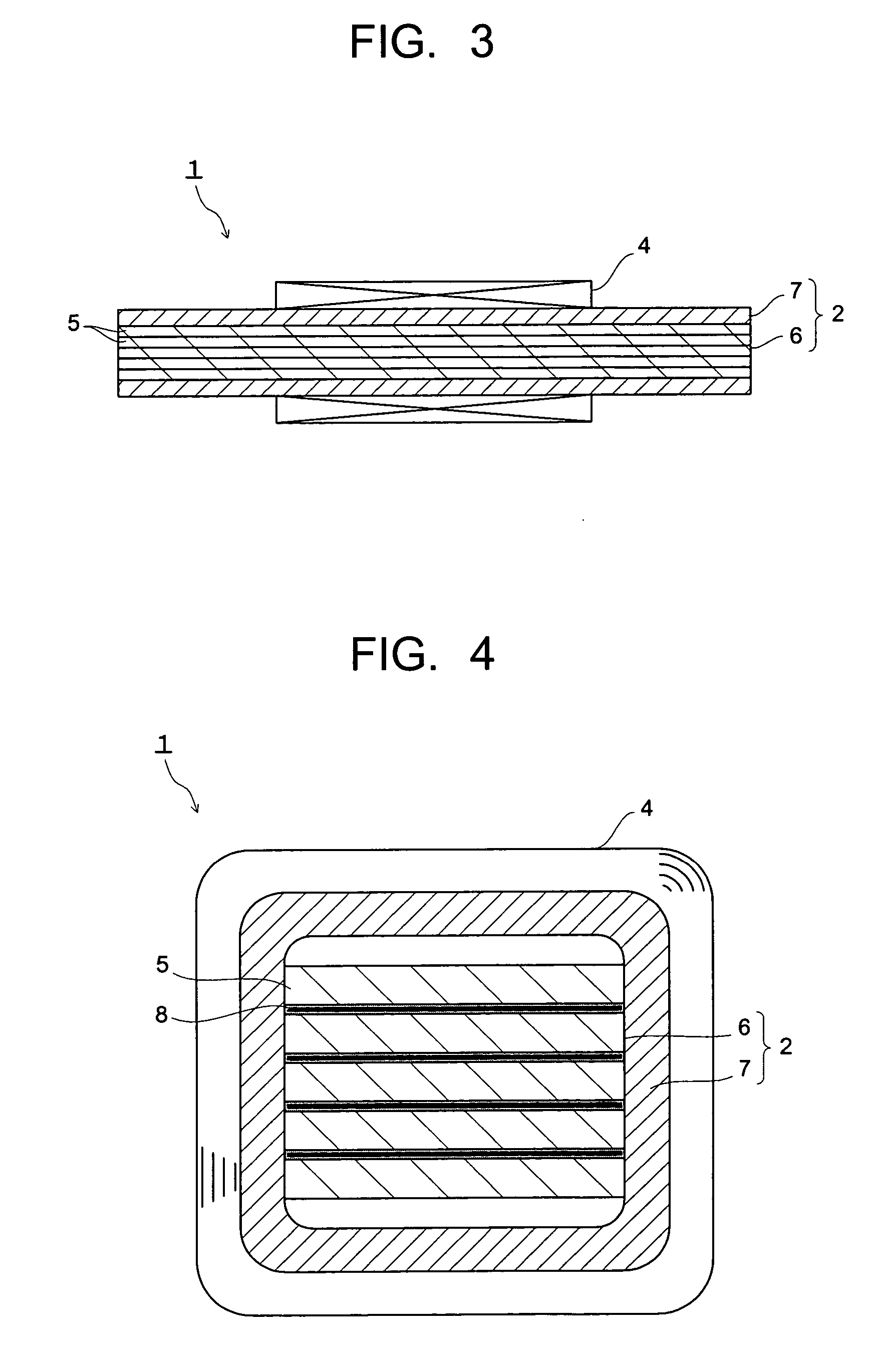

Liquid crystal display device and manufacturing method thereof

ActiveUS20070040643A1Improve featuresReduce bendabilityLoop antennas with ferromagnetic coreTransformers/inductances coils/windings/connectionsLiquid-crystal displayInductance

An inductance element (1) comprises a core (2) having a multilayer body (6) composed of magnetic alloy thin ribbons (5) and an insulating coating layer (7) which covers the peripheral surface of the multilayer body without being bonded thereto, and a coil (4) wound around the core (2). The magnetic alloy thin ribbons (5) are stacked in a non-adhered state or with a flexible insulating adhesive layer therebetween. Having such a structure, the inductance element can stably attain good characteristics even when it is small-sized or made short.

Owner:KK TOSHIBA +1

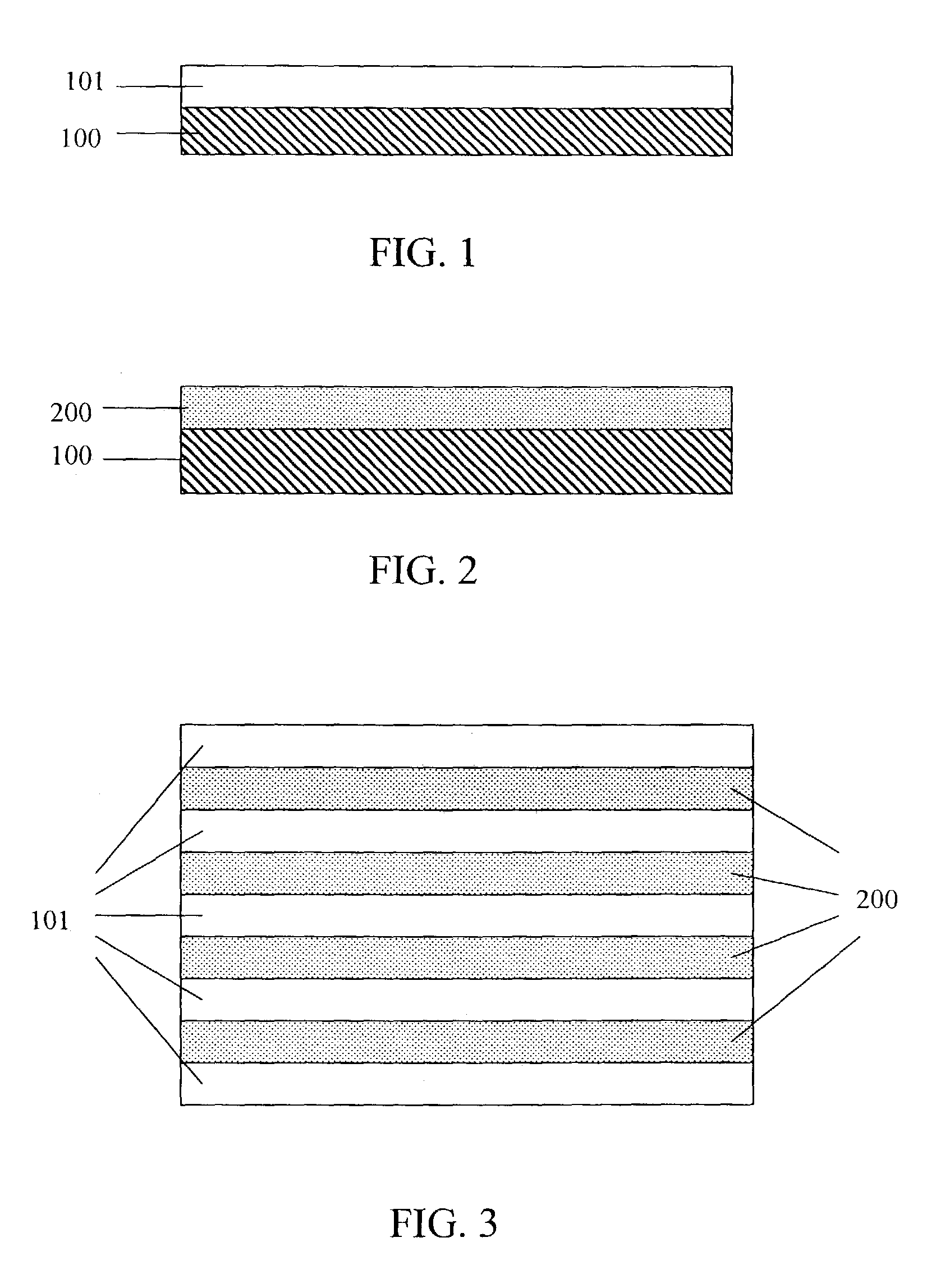

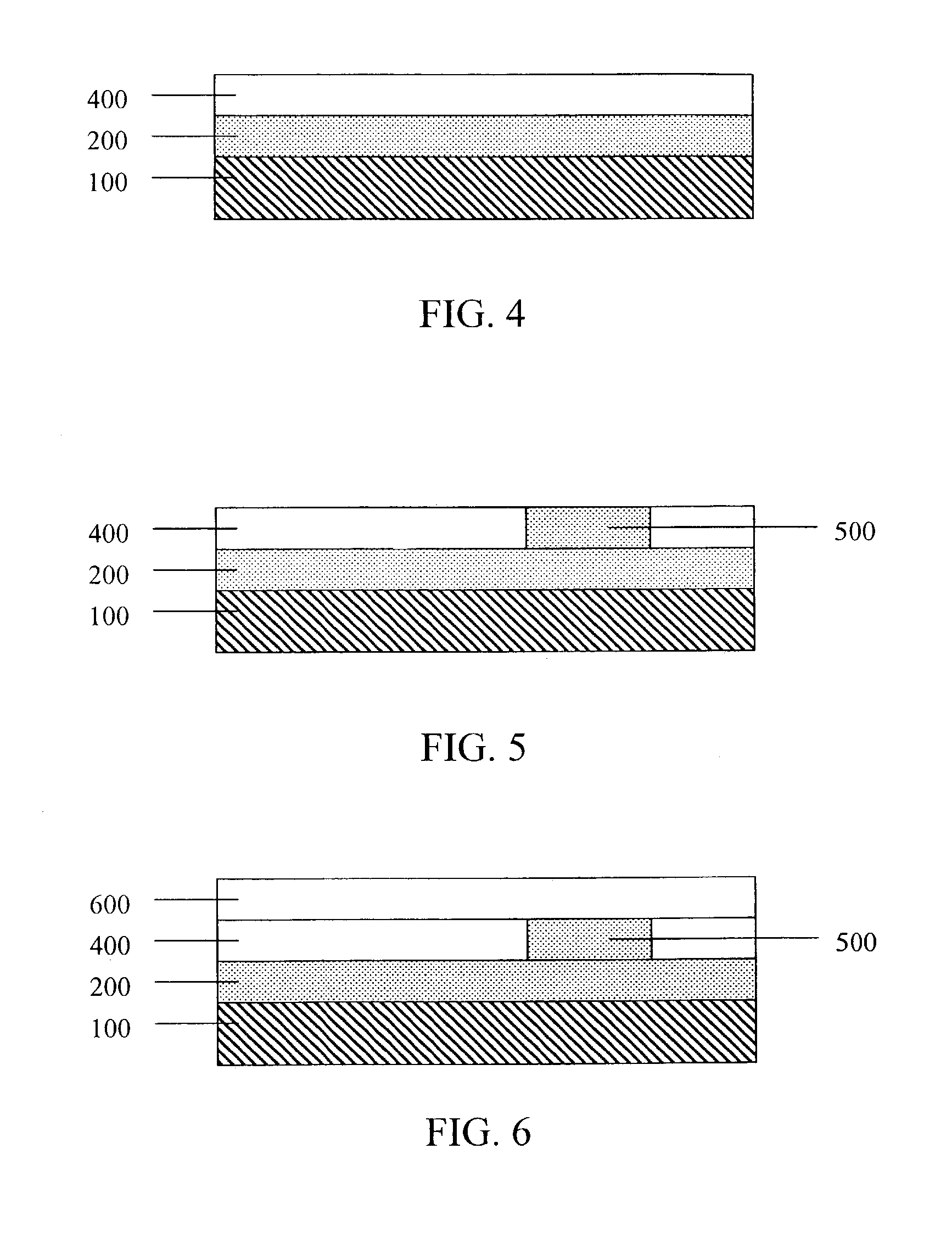

Forming contacts on semiconductor substrates, radiation detectors and imaging devices

InactiveUS6215123B1Avoid damageImprove electrical isolationSolid-state devicesMaterial analysis by optical meansContact positionSemiconductor

A method, suitable for forming metal contacts on a semiconductor substrate at positions for defining radiation detector cells, includes the steps of forming one or more layers of material on a surface of the substrate with openings to the substrate surface at the contact positions; forming a layer of metal over the layer(s) of material and the openings; and removing metal overlying the layer(s) of material to separate individual contacts. Optionally, a passivation layer to be left between individual contacts on the substrate surface may be applied. Etchants used for removing unwanted gold (or other contact matter) are preferably prevented from coming into contact with the surface of the substrate, thereby avoiding degradation of the resistive properties of the substrate.

Owner:SIEMENS HEALTHCARE GMBH

Implantable modular, multi-channel connector system for nerve signal sensing and electrical stimulation applications

InactiveUS7303422B2Improve electrical isolationEasy to mergeEngagement/disengagement of coupling partsElectrotherapyElectrical conductorLocking mechanism

Owner:4491343 CANADA

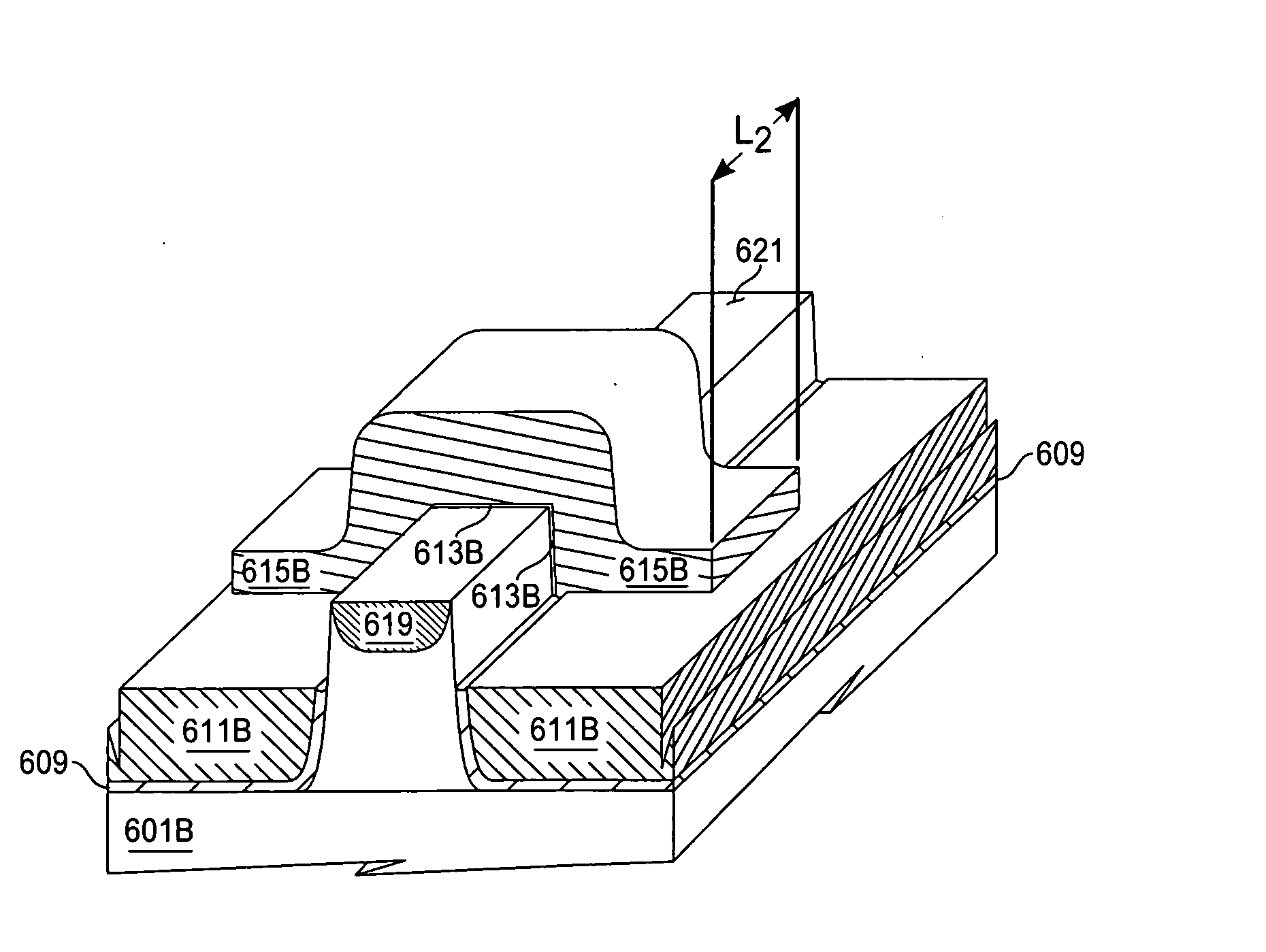

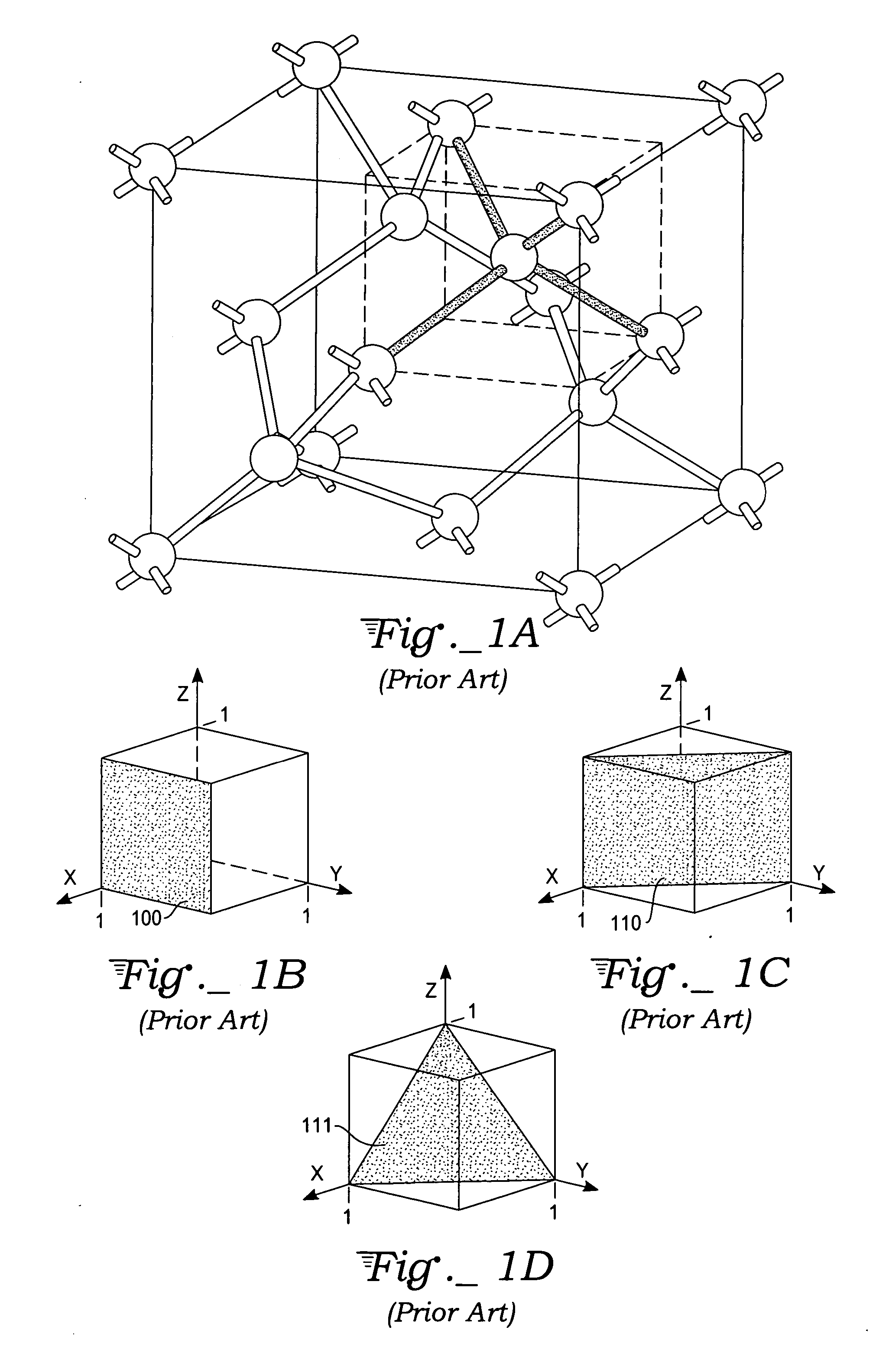

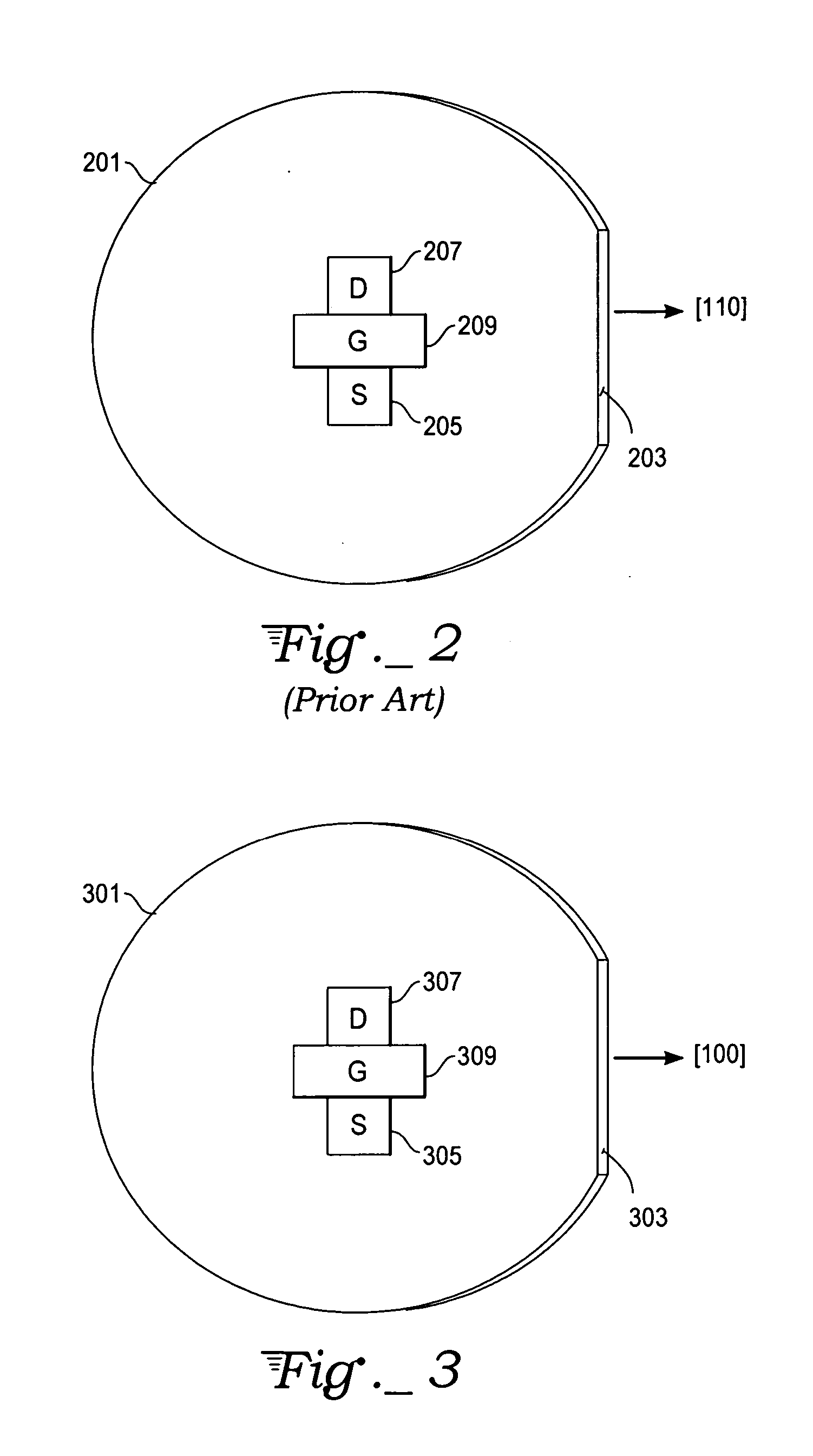

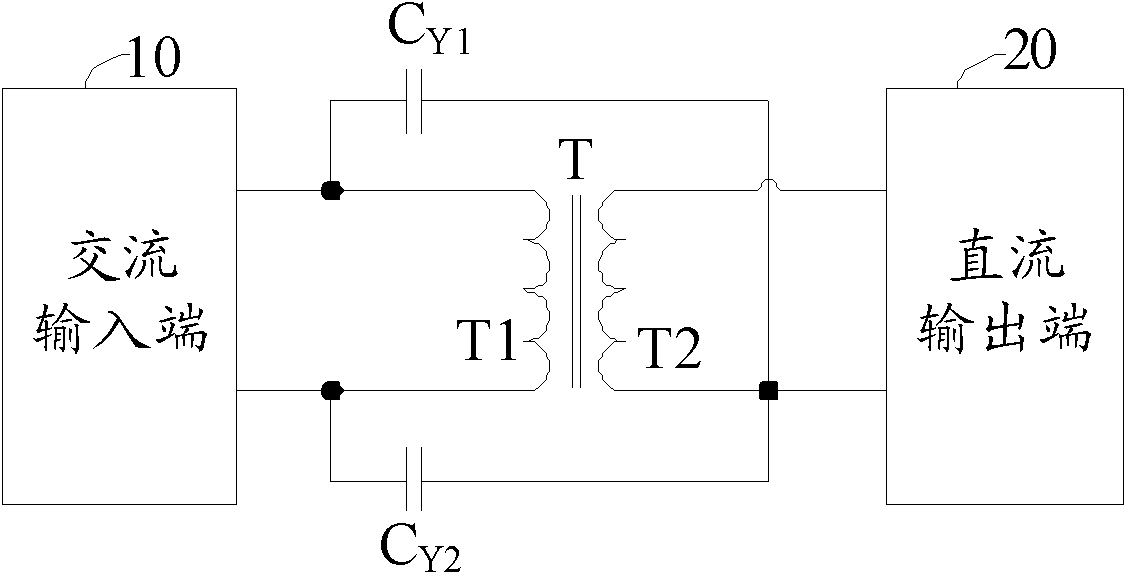

Method and manufacturing low leakage MOSFETs and FinFETs

InactiveUS20070228425A1Relieve pressureReduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCMOS

By aligning the primary flat of a wafer with a (100) plane rather than a (110) plane, devices can be formed with primary currents flowing along the (100) plane. In this case, the device will intersect the (111) plane at approximately 54.7 degrees. This intersect angle significantly reduces stress propagation / relief along the (111) direction and consequently reduces defects as well as leakage and parasitic currents. The leakage current reduction is a direct consequence of the change in the dislocation length required to short the source-drain junction. By using this technique the leakage current is reduced by up to two orders of magnitude for an N-channel CMOS device.

Owner:ATMEL CORP

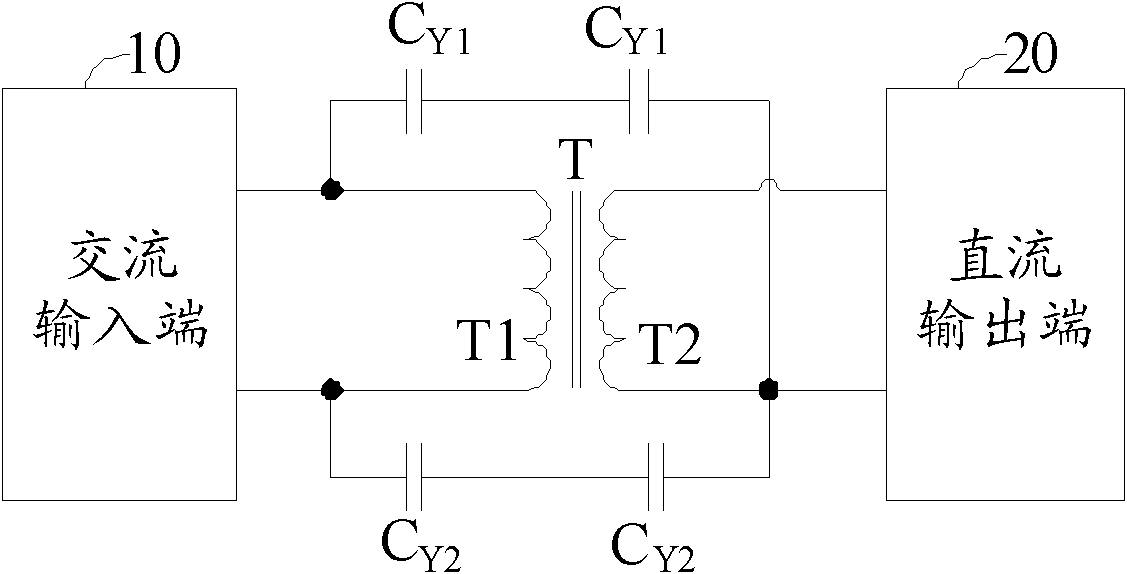

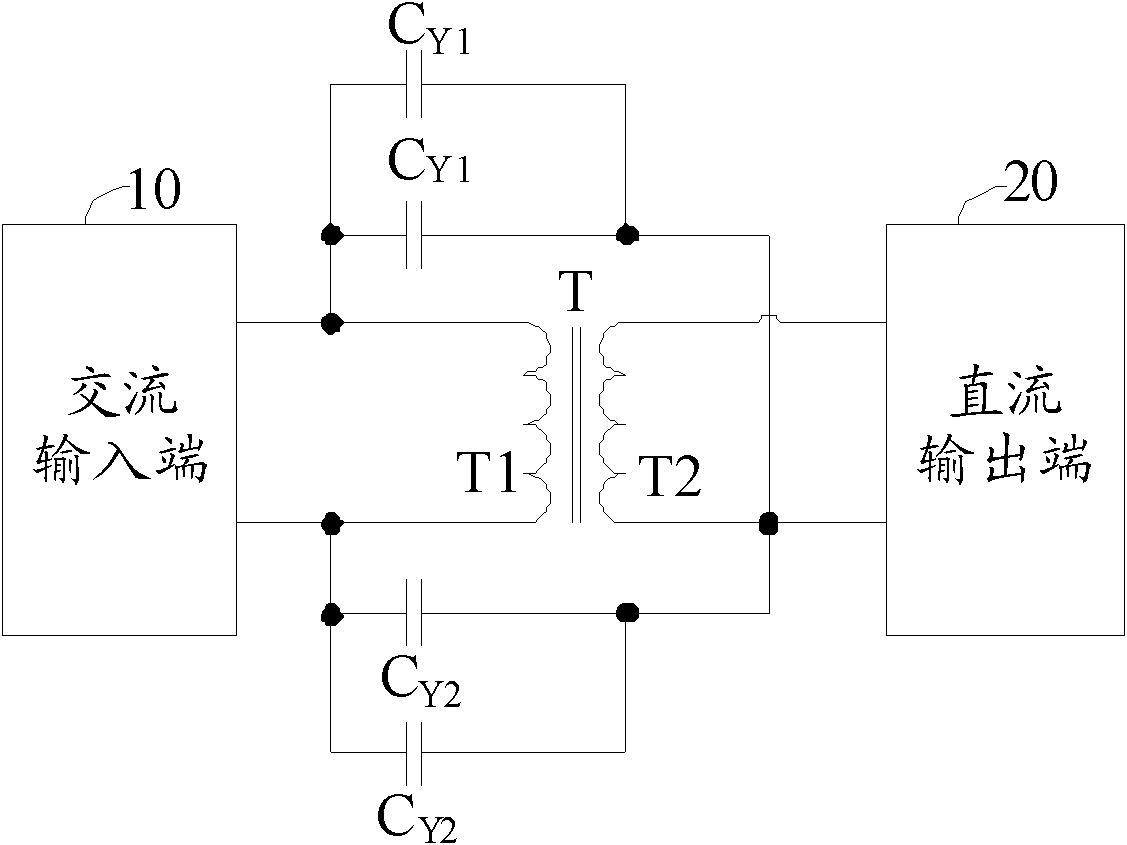

Circuit for eliminating noise of switching power supply

InactiveCN102044961ACancel noiseImprove efficiencyPower conversion systemsConnection typeCapacitance

Owner:SHENZHEN HUNTKEY ELECTRIC

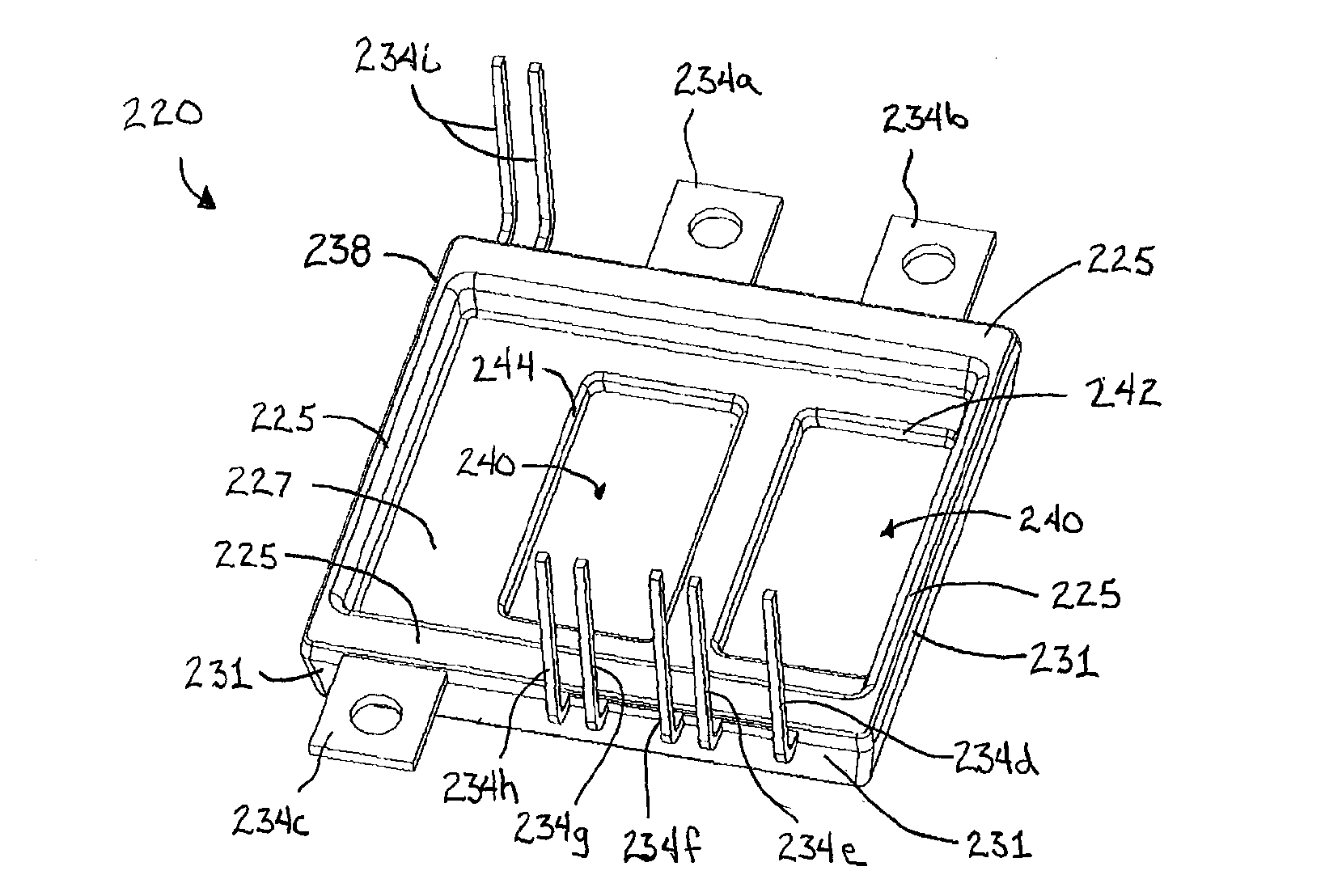

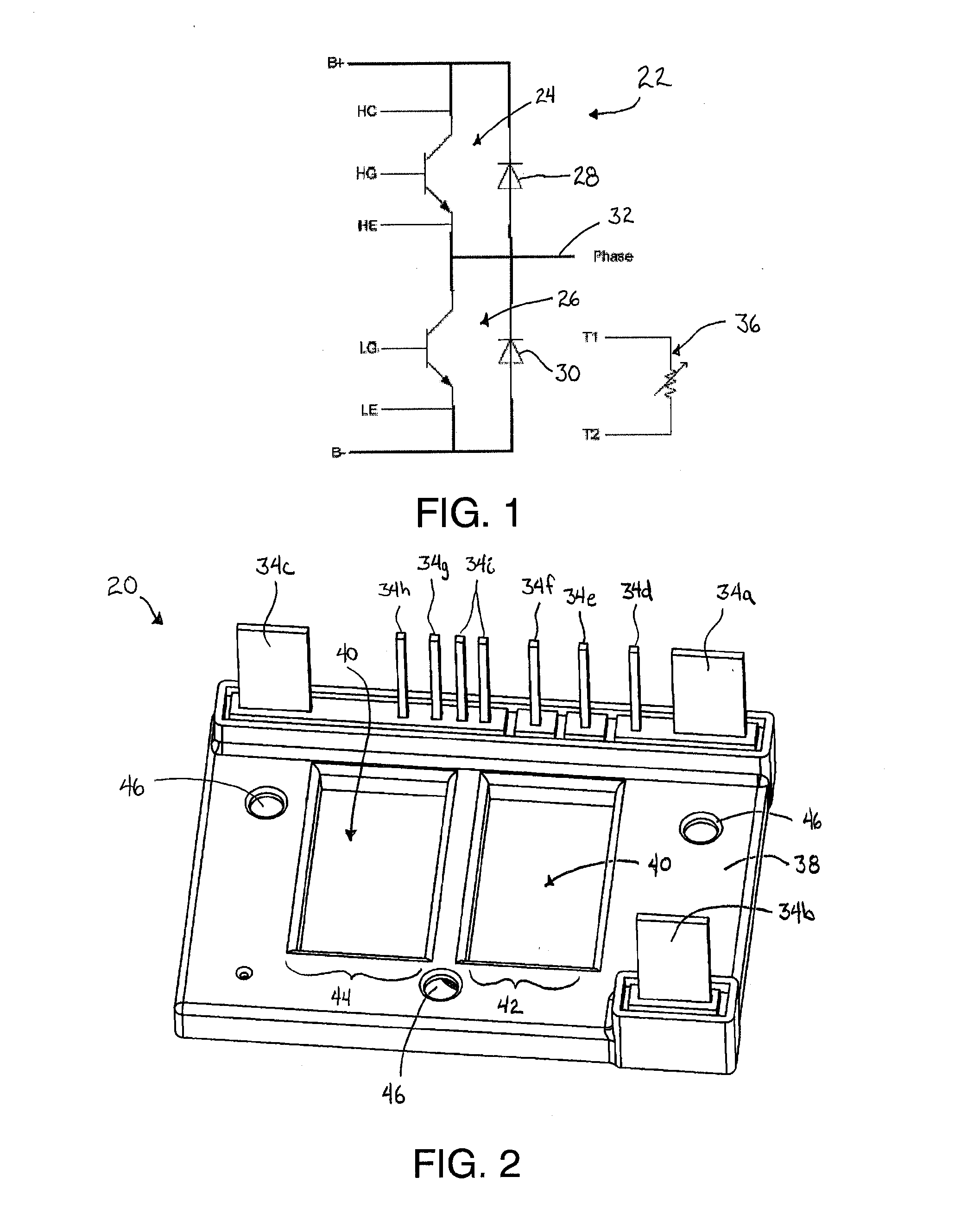

Power module for converting DC to ac

InactiveUS20130201741A1Improve electrical isolationEliminates wirebond connectionConversion constructional detailsSolid-state devicesEngineeringAlternating current

A power module for converting direct current to alternating current comprising a semiconductor switching circuit device, a substrate onto which the switching circuit device is physically and electrically coupled without wirebonds, a plurality of leadframe terminals physically and electrically coupled to the substrate, and a cover including an opening exposing a bottom side of the substrate and including a wall portion oriented generally orthogonally relative to the substrate with at least some of the leadframe terminals projecting outwardly from the wall portion. The leadframe terminals projecting outwardly from the wall portion may include an affixed portion coupled to the substrate and an extending segment lying in a plane above the affixed portion with the extending segment projecting outwardly from the wall portion and the cover encapsulating the affixed portion whereby the extending segment is spaced from a plane defined by the bottom side of the substrate.

Owner:ELECTRONICS MOTION SYST HLDG

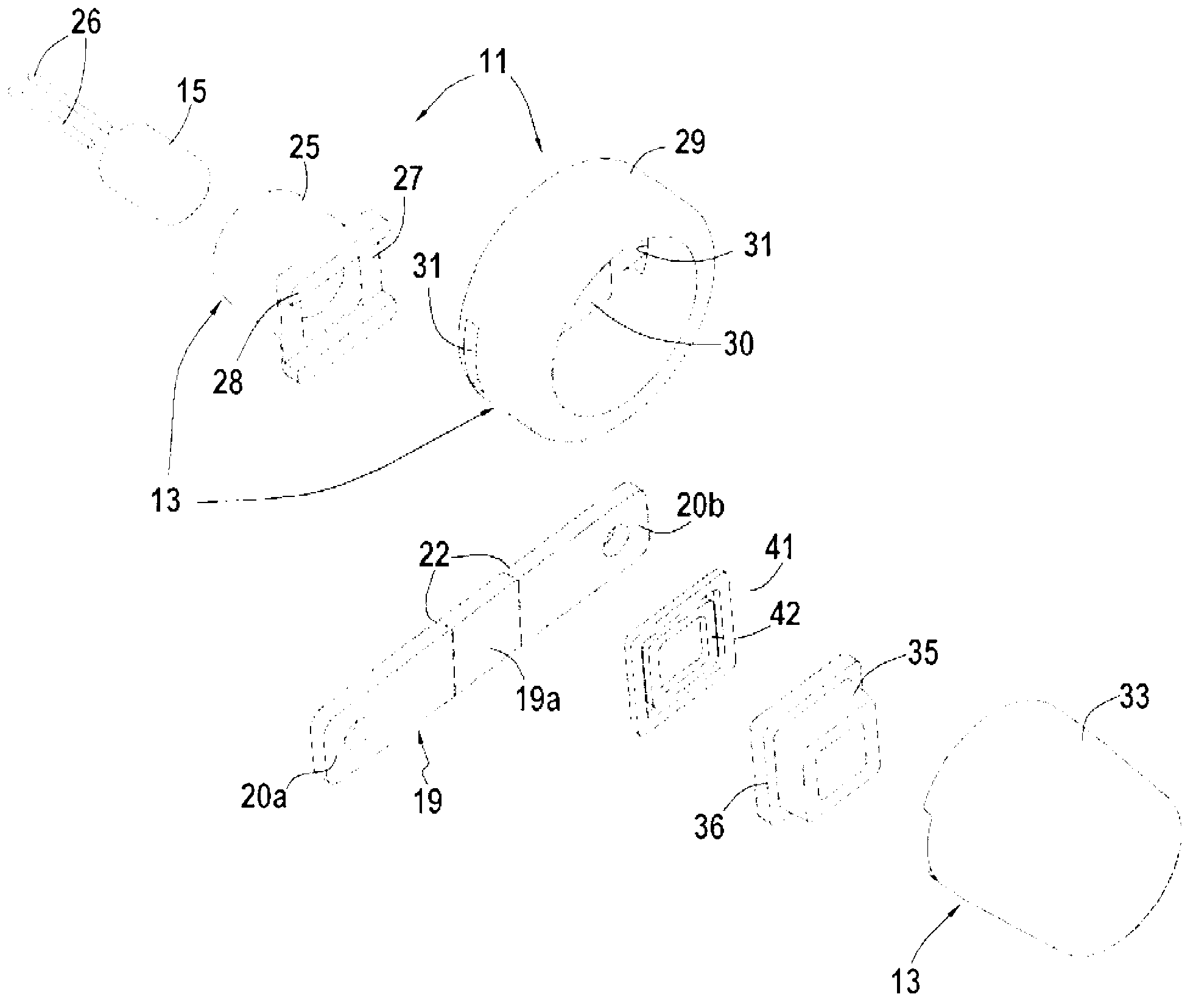

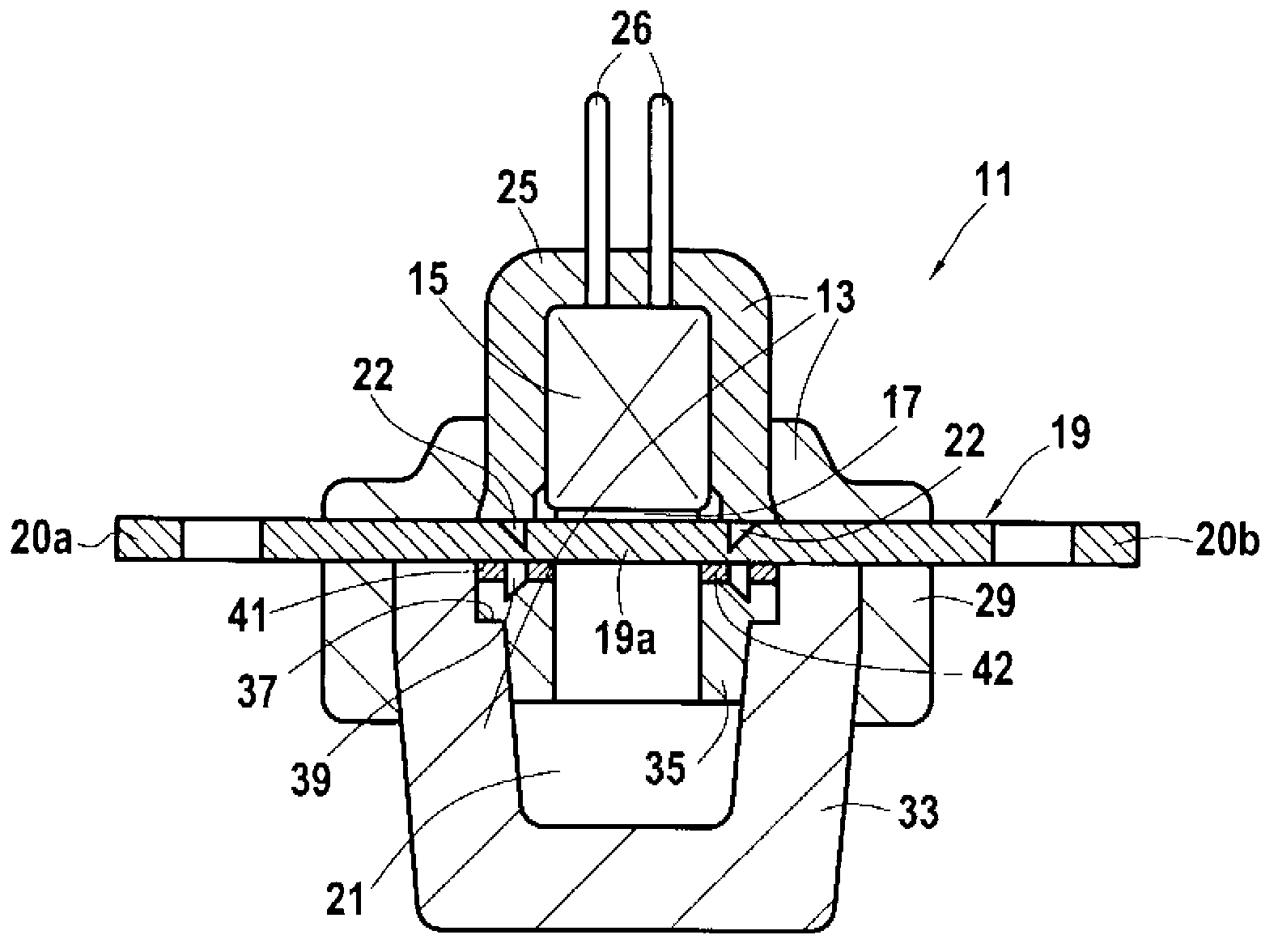

Electric circuit breaker with pyrotechnic actuation

InactiveCN103003907AGuaranteed boostGuaranteed air tightnessBattery cutoff switchesEmergency protective devicesCombustionEngineering

Electric circuit breaker forming a breaker switch in particular, in which a conducting blade is broken by the tripping of a pyrotechnic activation gas generator. According to the invention, a gas generator (15) with pyrotechnic actuation is designed so as to emit gases resulting from the combustion of a charge, and the generator is associated with a variable-configuration chamber (17) and a breakable conducting blade (19) constitutes a back wall of this chamber, the breaking of the blade under the actuation of the gases causing the interruption of the electric circuit of which the blade forms part.

Owner:海瑞克里兹

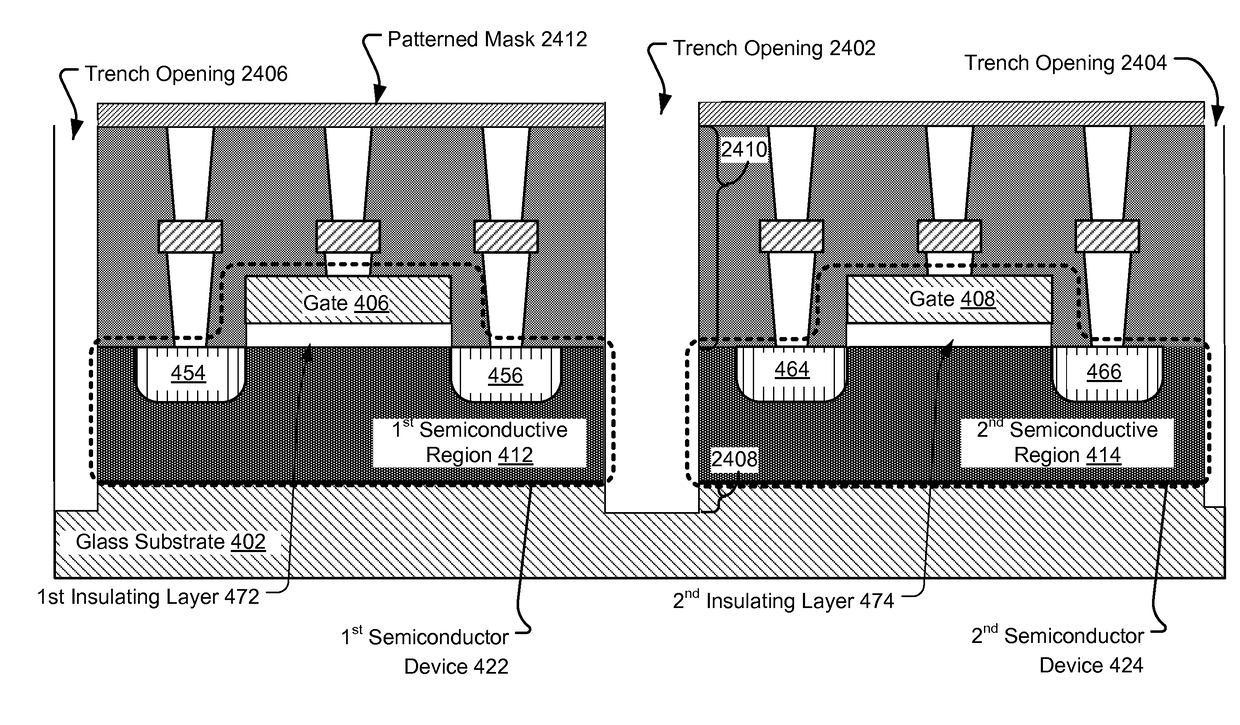

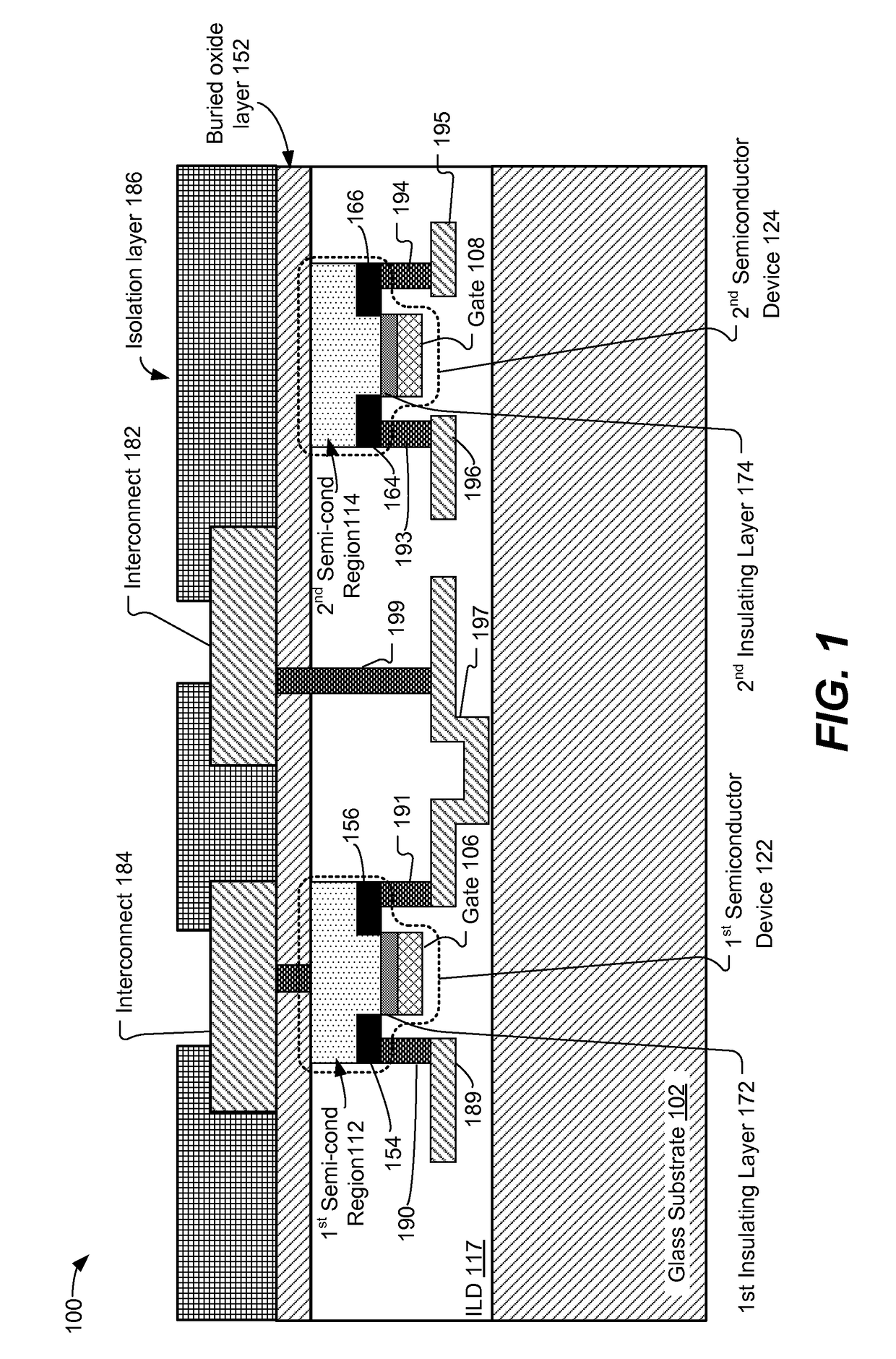

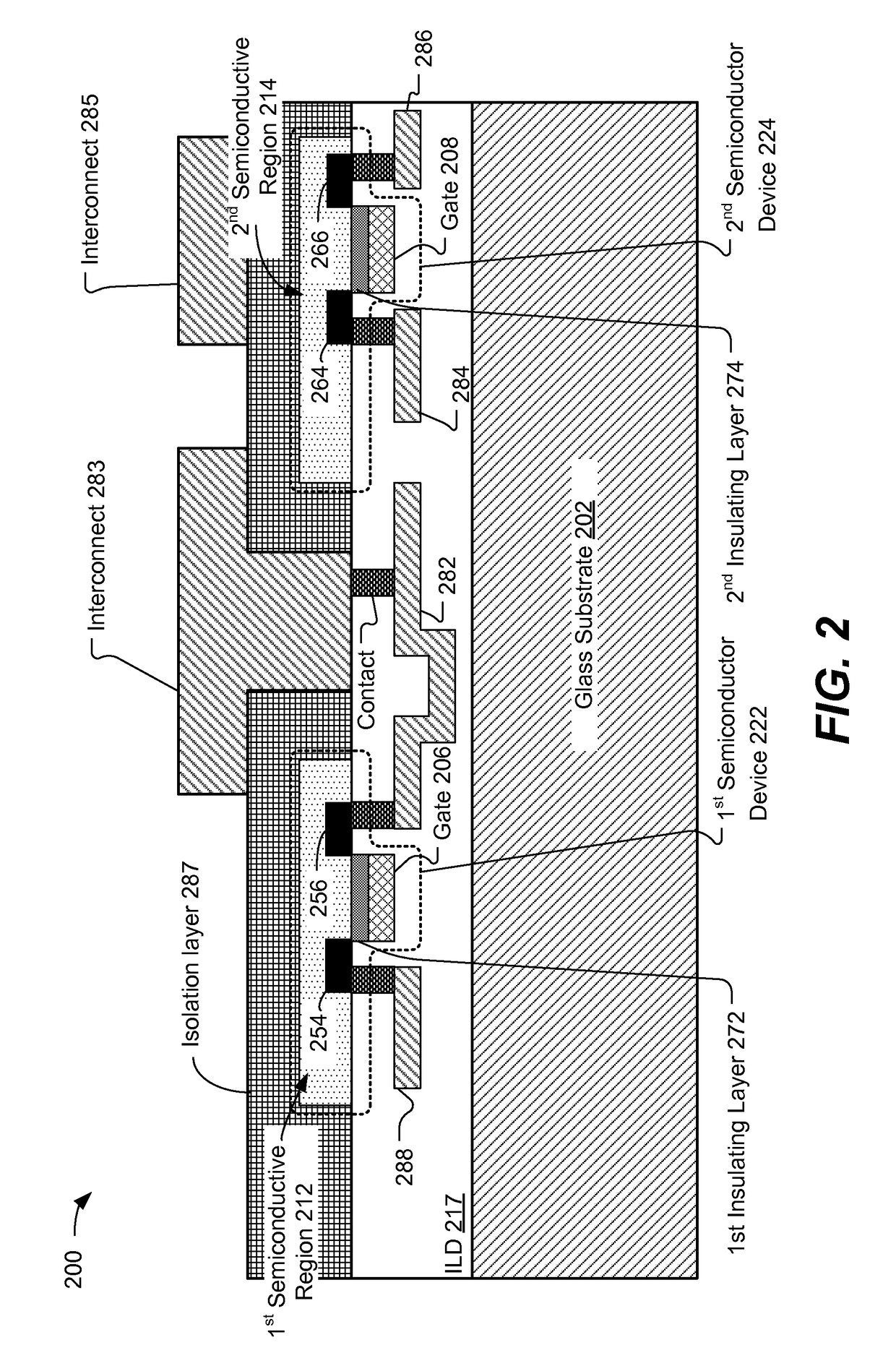

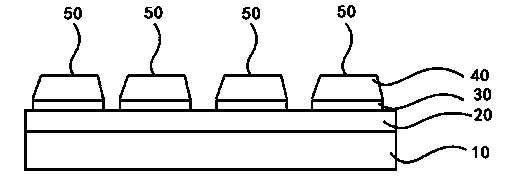

Integrated circuits (ICS) on a glass substrate

ActiveUS20170084531A1Improve electrical isolationPreventing and reducing loadTransistorSemiconductor/solid-state device detailsElectrical conductorSemiconductor

An integrated circuit (IC) includes a first semiconductor device on a glass substrate. The first semiconductor device includes a first semiconductive region of a bulk silicon wafer. The IC includes a second semiconductor device on the glass substrate. The second semiconductor device includes a second semiconductive region of the bulk silicon wafer. The IC includes a through substrate trench between the first semiconductive region and the second semiconductive region. The through substrate trench includes a portion disposed beyond a surface of the bulk silicon wafer.

Owner:QUALCOMM INC

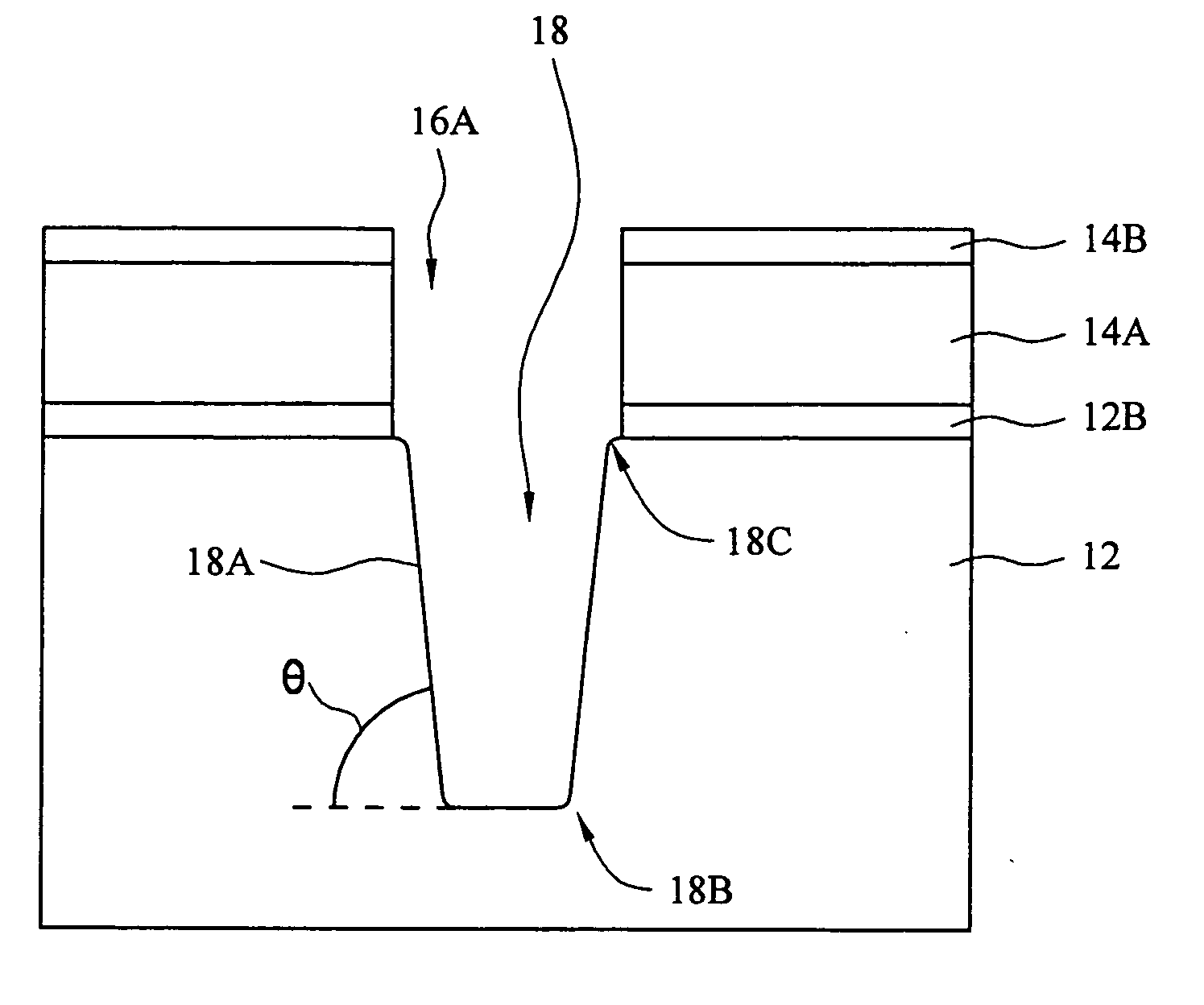

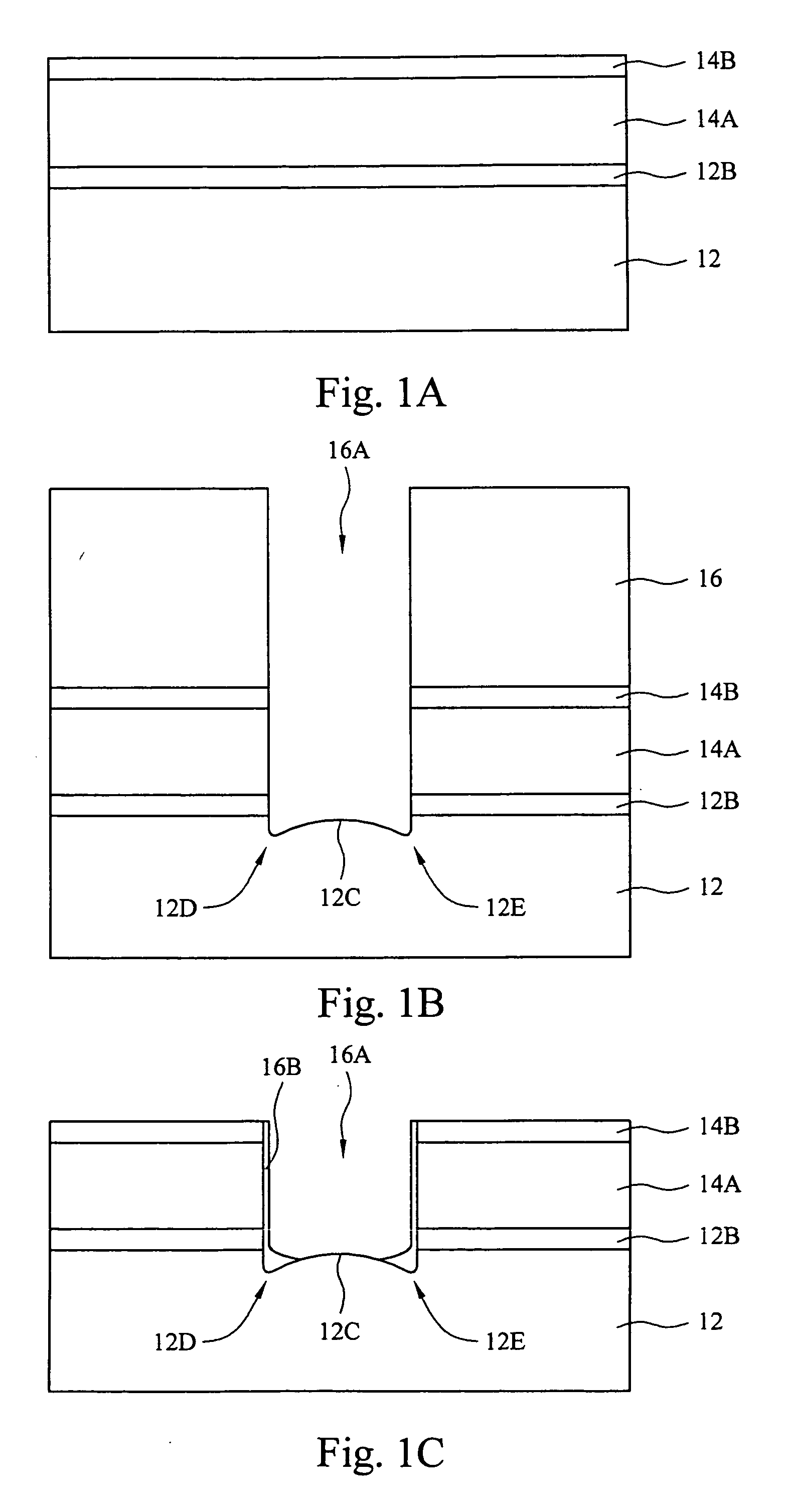

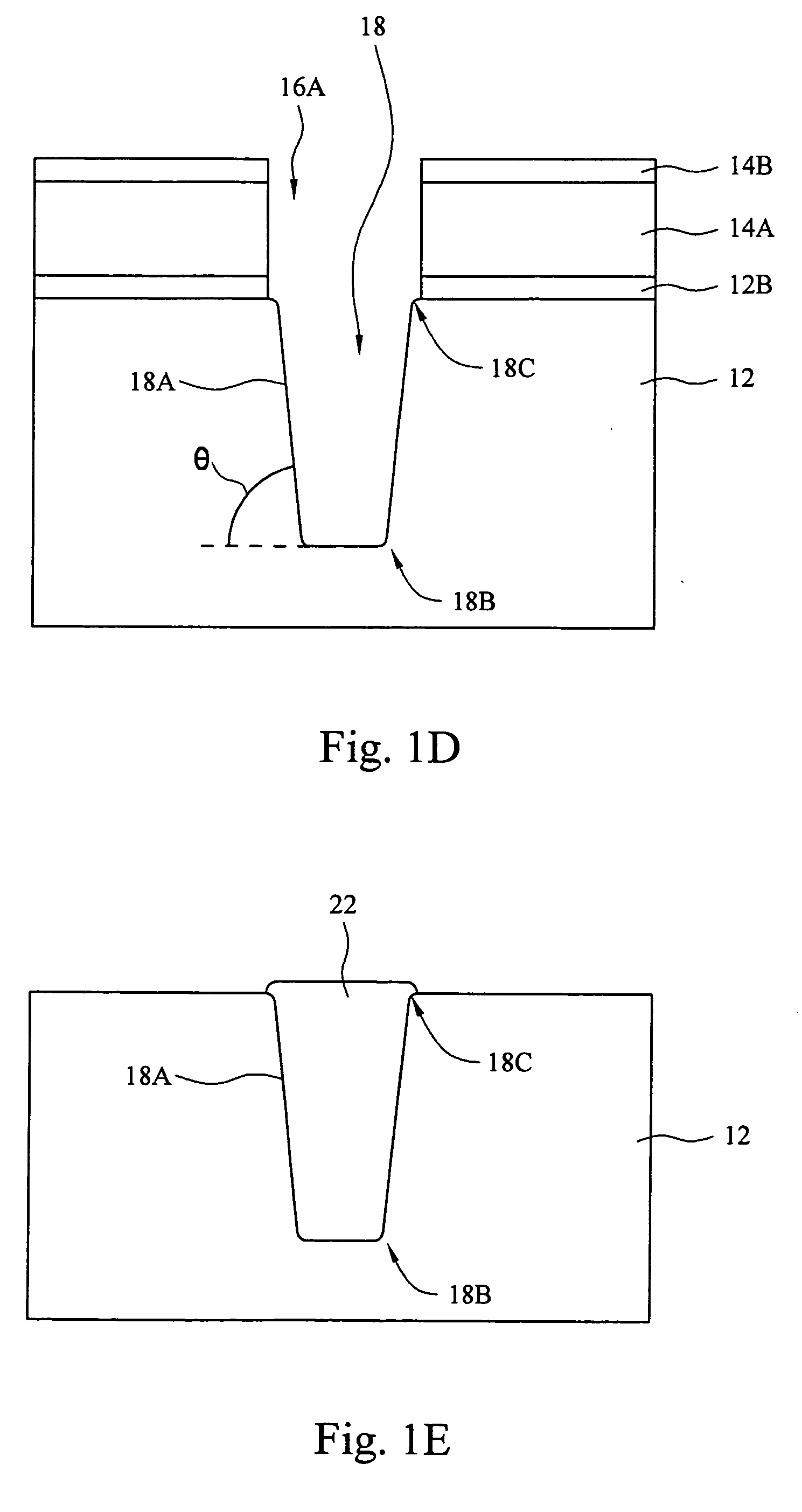

Method of forming improved rounded corners in STI features

InactiveUS20060063348A1Improve electrical isolationSemiconductor/solid-state device manufacturingEngineeringSilicon oxide

A method for forming a shallow trench isolation (STI) structure with improved electrical isolation performance including providing a semiconductor substrate including an overlying silicon oxide layer on the semiconductor substrate and a hardmask layer on the silicon oxide layer; dry etching in a first etching process to form a patterned hardmask opening for etching an STI opening; dry etching in a second etching process the semiconductor substrate to form an upper portion of an STI opening to form a polymer layer along sidewall portions of the STI opening; and, dry etching in a third etching process the STI opening to form rounded bottom corners and rounded top corners.

Owner:TAIWAN SEMICON MFG CO LTD

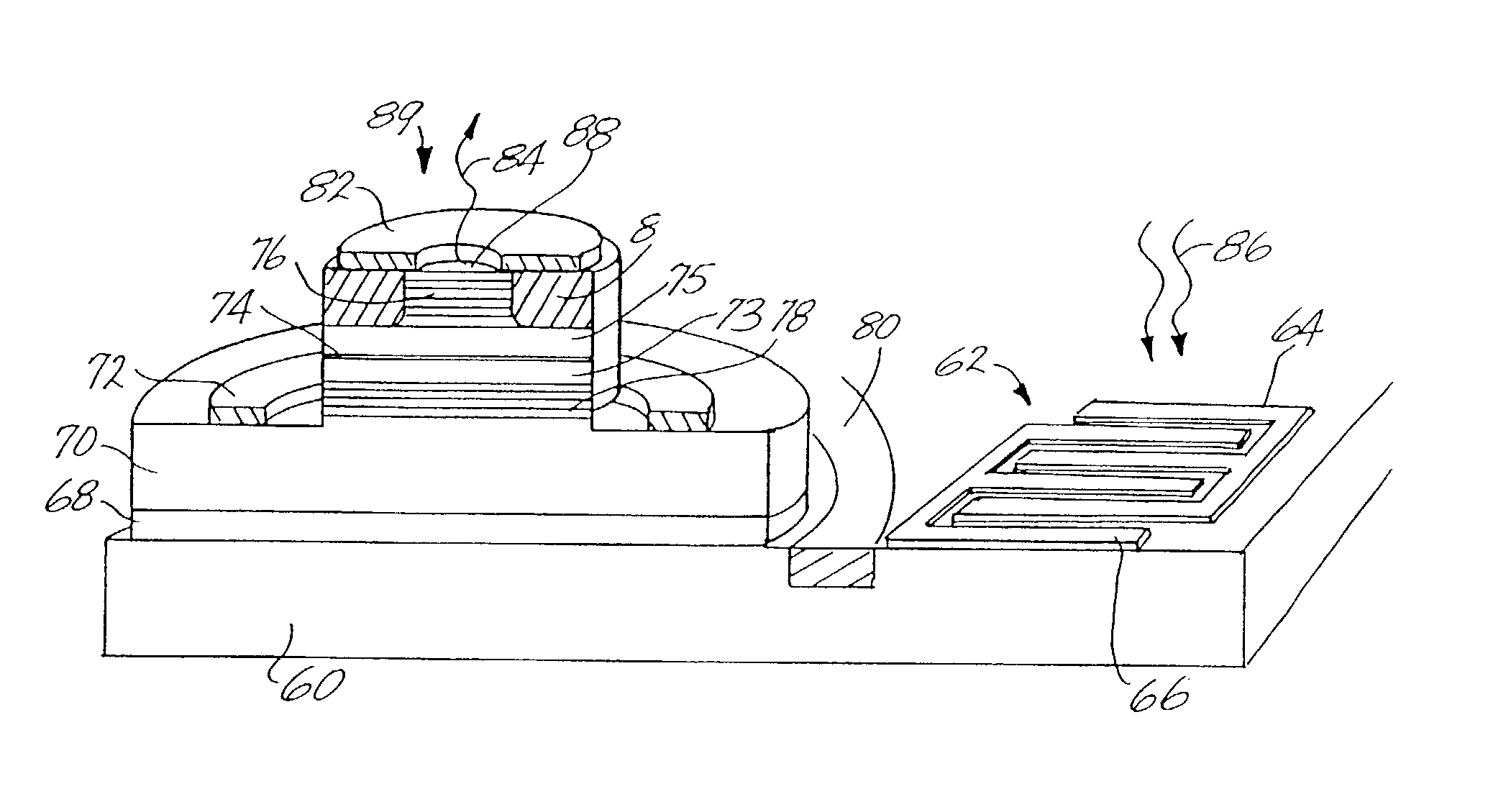

A multilayered composite ceramic layer patterned structure substrate for optical and electronic devices

ActiveCN103354222ASmall sizeImprove electrical isolationSemiconductor/solid-state device detailsSolid-state devicesThermal isolationEtching

The invention relates to a multilayered composite ceramic layer patterned structure substrate for optical and electronic devices. The multilayered composite ceramic layer patterned structure substrate comprises a metal substrate, wherein a voltage-withstanding ceramic layer and a high heat-conducting ceramic layer are sequentially formed on the metal substrate; an active brazing layer is arranged between the voltage-withstanding ceramic layer and the high heat-conducting ceramic layer; multiple isolation bases are formed by selective etching performed on the high heat-conducting ceramic layer and the active brazing layer through a mask; and a metal circuit layer is formed on every isolation base. The multilayered composite ceramic layer patterned structure substrate for optical and electronic devices has a metal substrate in a relatively large size, can accommodate multiple optical and / or electronic devices, and is provided with good electrical isolation and thermal isolation between the multiple optical and / or electronic devices.

Owner:浙江云隐科技有限公司

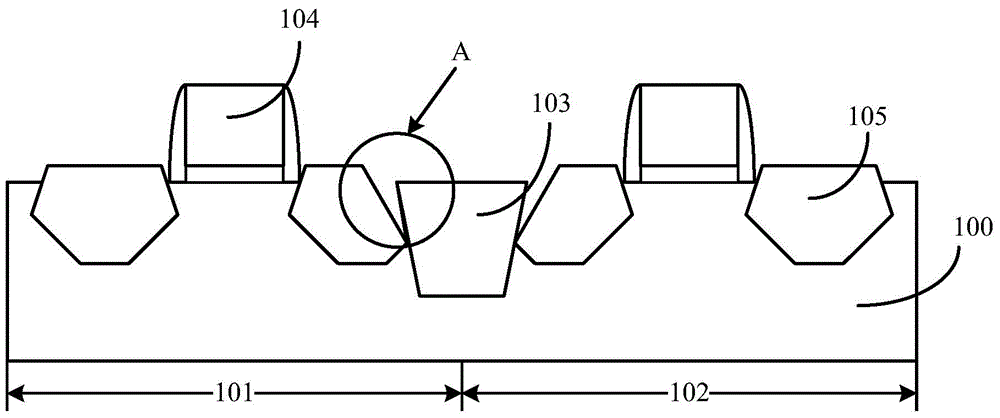

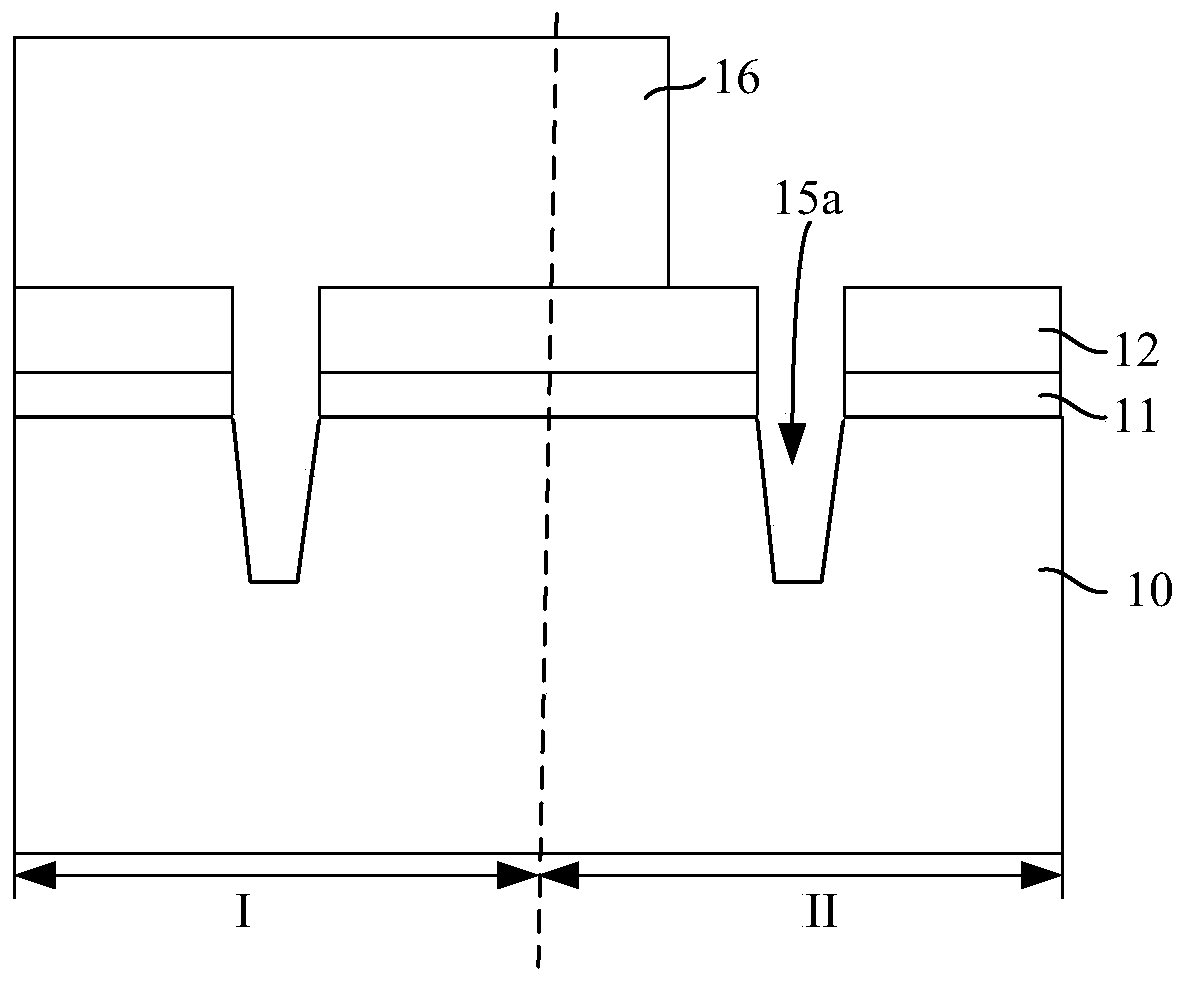

Formation method of semiconductor device

ActiveCN105097521AImprove electrical isolationAvoid problems with residues on the surface of isolation structuresTransistorSemiconductor/solid-state device manufacturingDielectric layerCondensed matter physics

Semiconductor devices and fabrication methods are provided. A semiconductor substrate is provided having dummy gate structures formed thereon. A stress layer is formed in the semiconductor substrate between adjacent dummy gate structures. A first dielectric layer is formed on the semiconductor substrate, the stress layers, and the sidewall spacers of the dummy gate structures, exposing dummy gate electrode layers. Gate structures are formed in the dielectric layer to replace the dummy gate structures. The gate structures include functional gate structures and at least one non-functional gate structure. The at least one non-functional gate structure is removed to form at least one second opening in the first dielectric layer. At least one third opening is formed in the semiconductor substrate at a bottom of the at least one second opening. A second dielectric layer is formed in the at least one second opening and the at least one third opening.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A patterned ceramic layer printed circuit substrate for optical and electronic devices

ActiveCN103354698ASmall sizeImprove electrical isolationPrinted circuit detailsPrinted circuit non-printed electric components associationThermal isolationHemt circuits

The invention relates to a patterned ceramic layer printed circuit substrate for optical and electronic devices. The patterned ceramic layer printed circuit substrate comprises a metal substrate, wherein a voltage-withstanding ceramic layer is formed on the metal substrate; on the voltage-withstanding ceramic layer, by using a PVD (physical vapor deposition) method, a patterned high heat-conducting ceramic layer is deposited through a baffle plate, and multiple heat-conducting isolation bases are formed; and a metal circuit layer is formed on every heat-conducting isolation base. The patterned ceramic layer printed circuit substrate for optical and electronic devices has a metal substrate in a relatively large size, can accommodate multiple optical and / or electronic devices, and is provided with good electrical isolation and thermal isolation between the multiple optical and / or electronic devices.

Owner:浙江云隐科技有限公司

Shielded connector

ActiveUS20120264330A1Improve electrical isolationImprove isolationCoupling device detailsEngineeringMulti port

Owner:MOLEX INC

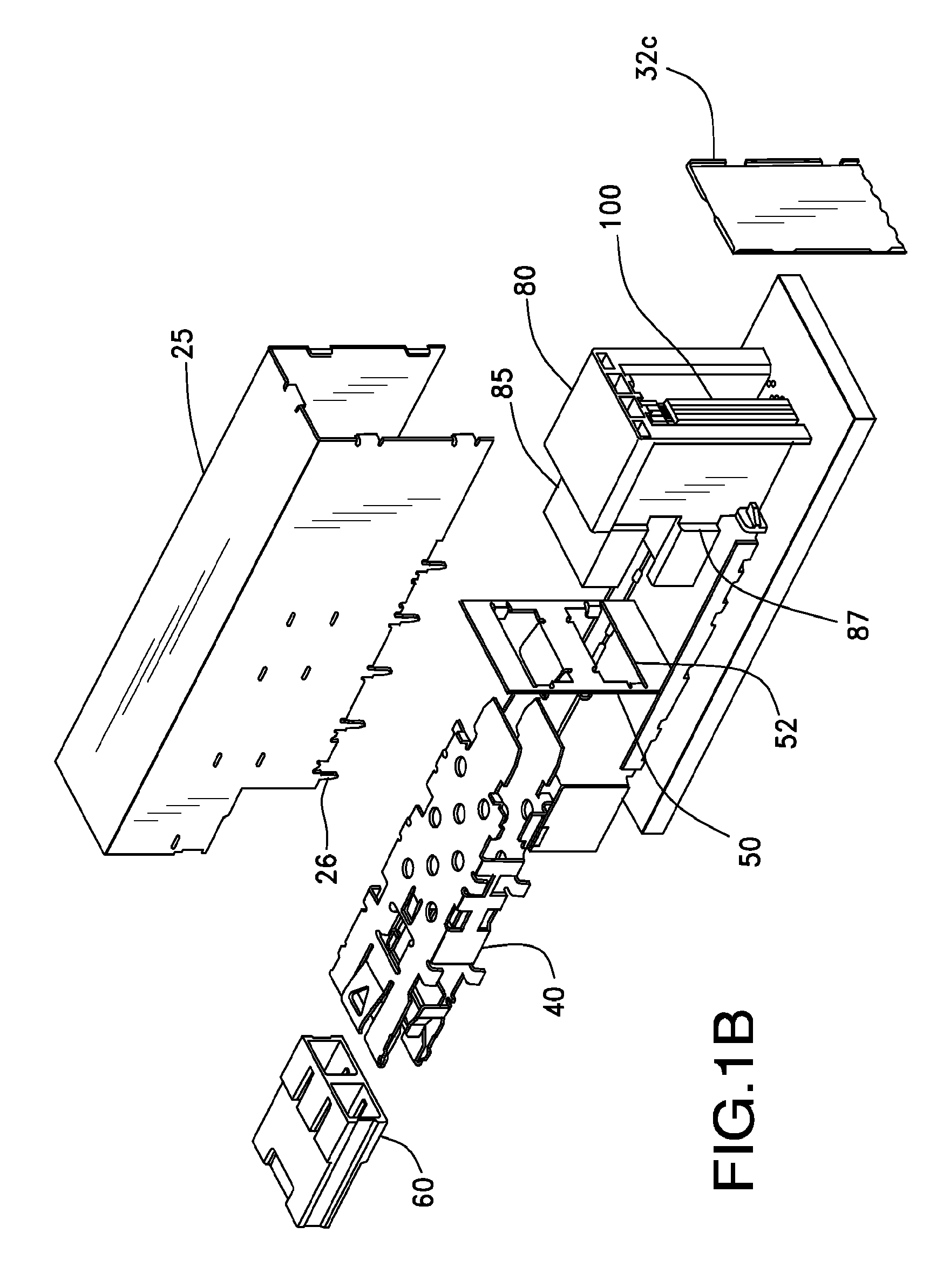

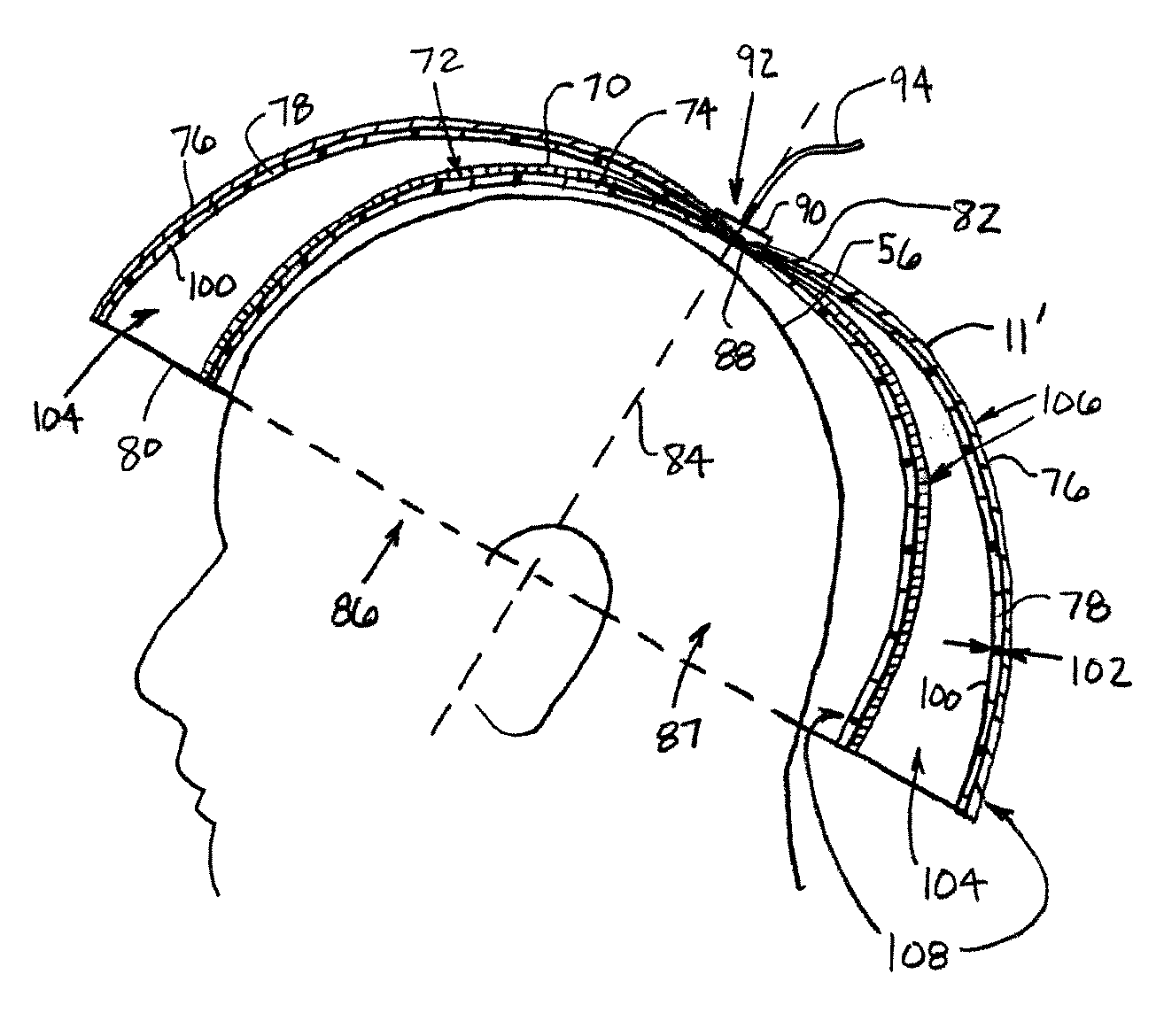

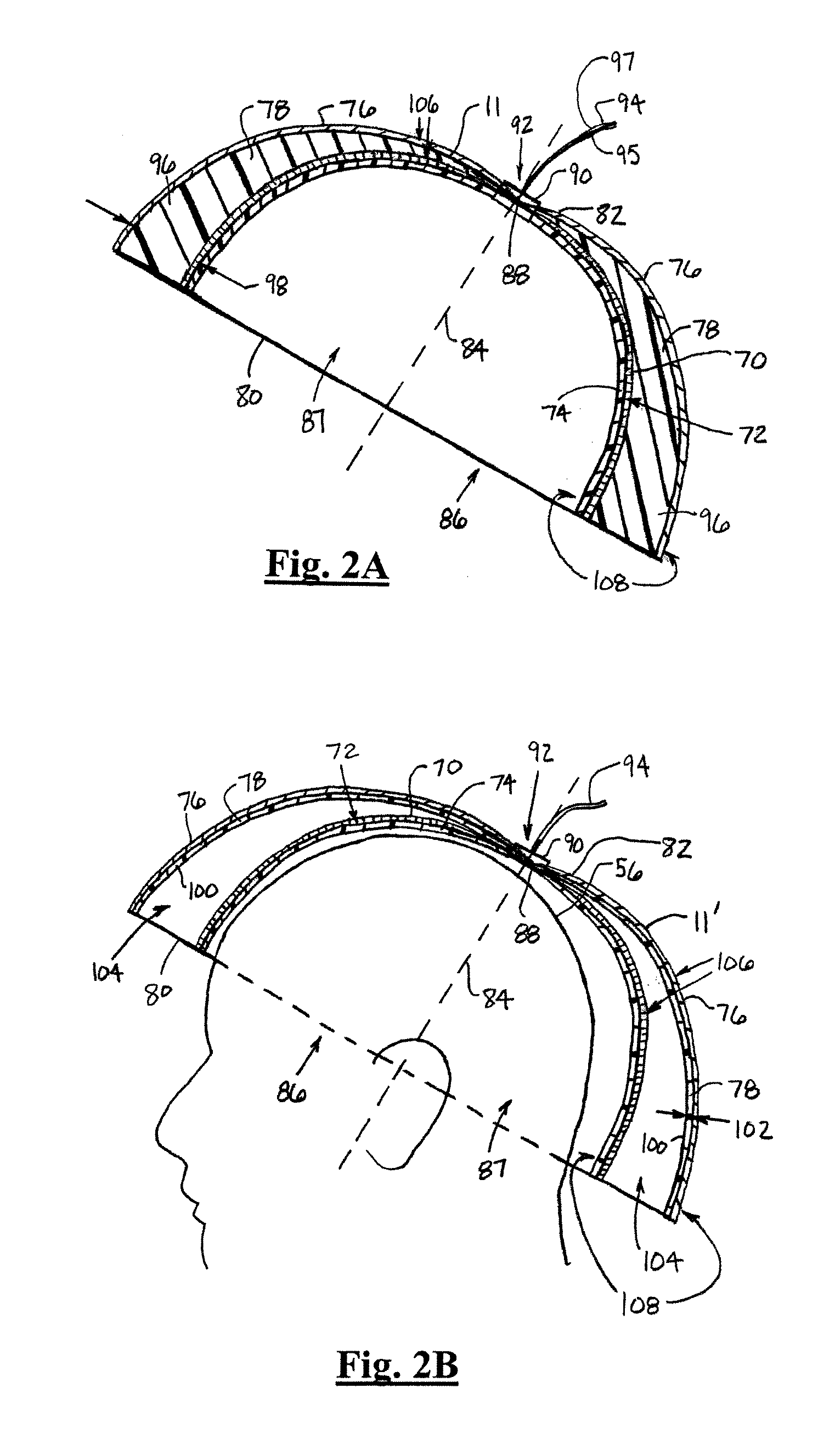

Shielded dome resonator for mr scanning of a cerebrum

ActiveUS20050059882A1High sensitivityImprove electrical isolationMagnetic measurementsSensorsRadio frequencyCondensed matter physics

A dome resonator (11) includes a resonator circuit (70) that excites and / or receives radio frequency magnetic resonance signals that emanate from a region of interest (14). The resonator circuit (70) includes multiple longitudinal conductive elements (110) that are coupled at a first end (80) and a second end (82) and tapered from the first end (80) to the second end (82). A resonator circuit support (74) is coupled to and supports the resonator circuit (70). A shield (76) is coupled to the resonator circuit support (74) and electrically isolates the resonator circuit (70) from a surrounding environment.

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

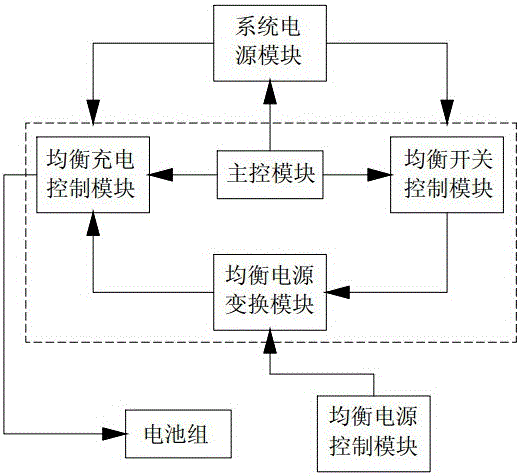

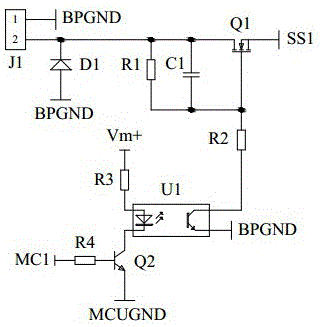

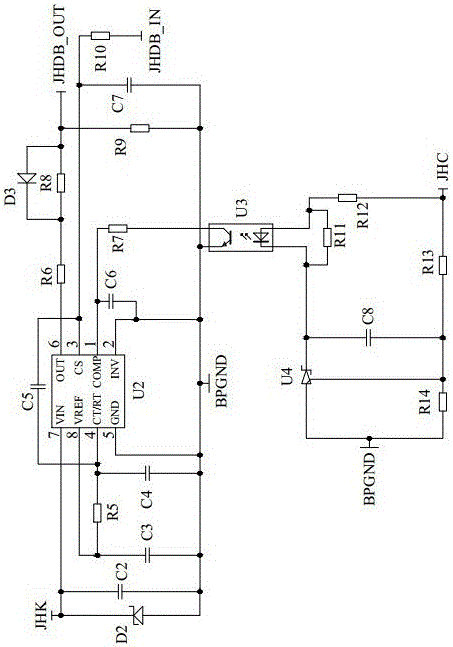

Lossless equalization controller and control method

ActiveCN106100078ALow costImprove securityCharge equalisation circuitElectric powerCharge controlComputer module

A lossless equalization controller and a control method belong to the technical field of battery equalization control. The controller comprises a battery pack formed by a plurality of cells, an equalization switch control module, an equalization power control module, an equalization power transformation module, an equalization charging control module, a system power supply module and a master control module, wherein the system power supply module supplies power to the equalization switch control module, the equalization charging control module and the master control module. The controller has the advantages of rapid equalization speed, safe and reliable equalization process, low cost and easy promotion and application. The control method includes detecting battery equalization degree, equalizing laggard cells in the battery pack when the battery equalization degree is equal to or greater than 0.3%, detecting system fault, clearing system fault and other detection steps. The equalization precision is high, and the equalization process is safe and reliable.

Owner:SHANDONG DEPUDA ELECTRIC MOTOR CO LTD

Wireless power supply system used for printed circuit boards

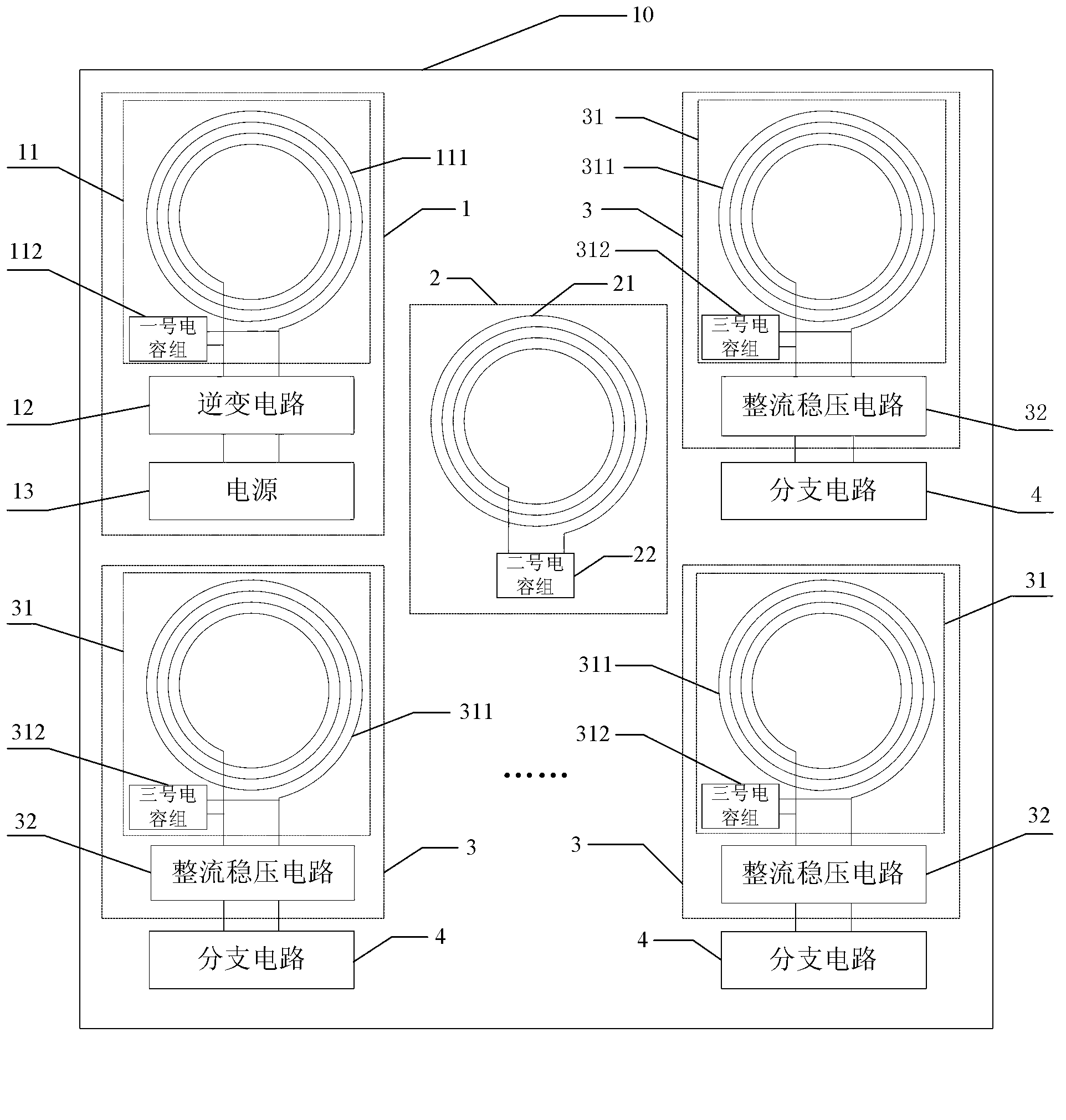

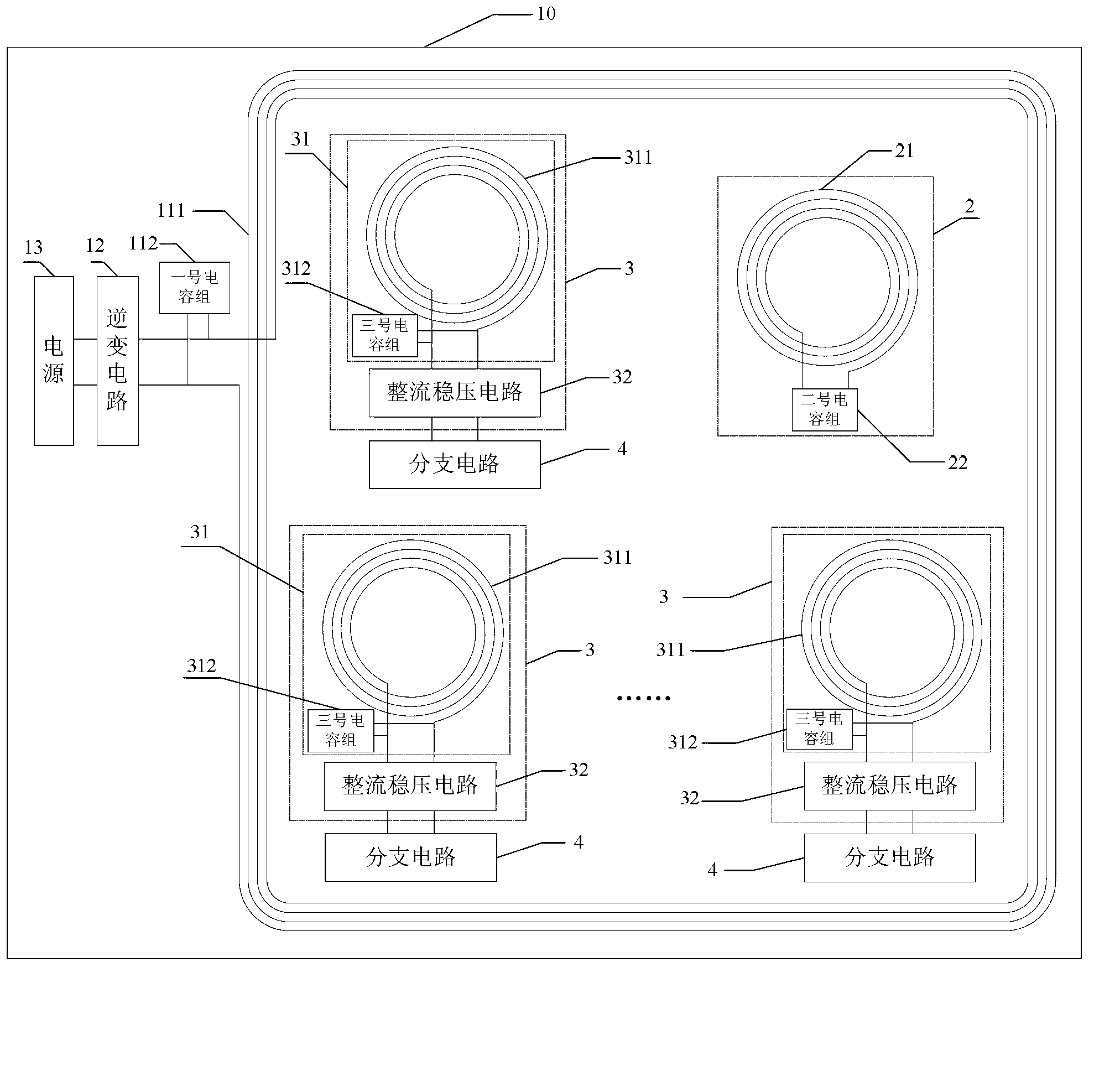

InactiveCN103023160ARealize wireless power supplyEasy wiringElectromagnetic wave systemPrinted circuit detailsAnti jammingAlternating current

The invention discloses a wireless power supply system used for printed circuit boards, relates to the field of wireless electric energy transmission, and solves the problems of complicated routing and poor power supply quality which are caused by existing power supply modes adopting externally connected power lines, and poor anti-jamming capability of the printed circuit boards. A transmitter circuit of the wireless power supply system used for printed circuit boards is used for inverting direct current into alternating current with an f frequency and sending out an alternating magnetic field with the f frequency; each receiving circuit is used for sensing the alternating magnetic field generated by the transmitter circuit and generating alternating current with the f frequency; and the alternating current is performed with rectification and voltage stabilization and then supplies power for a branch circuit. The wireless power supply system used for printed circuit boards is suitable for wireless power supply of printed circuit boards.

Owner:HARBIN INST OF TECH

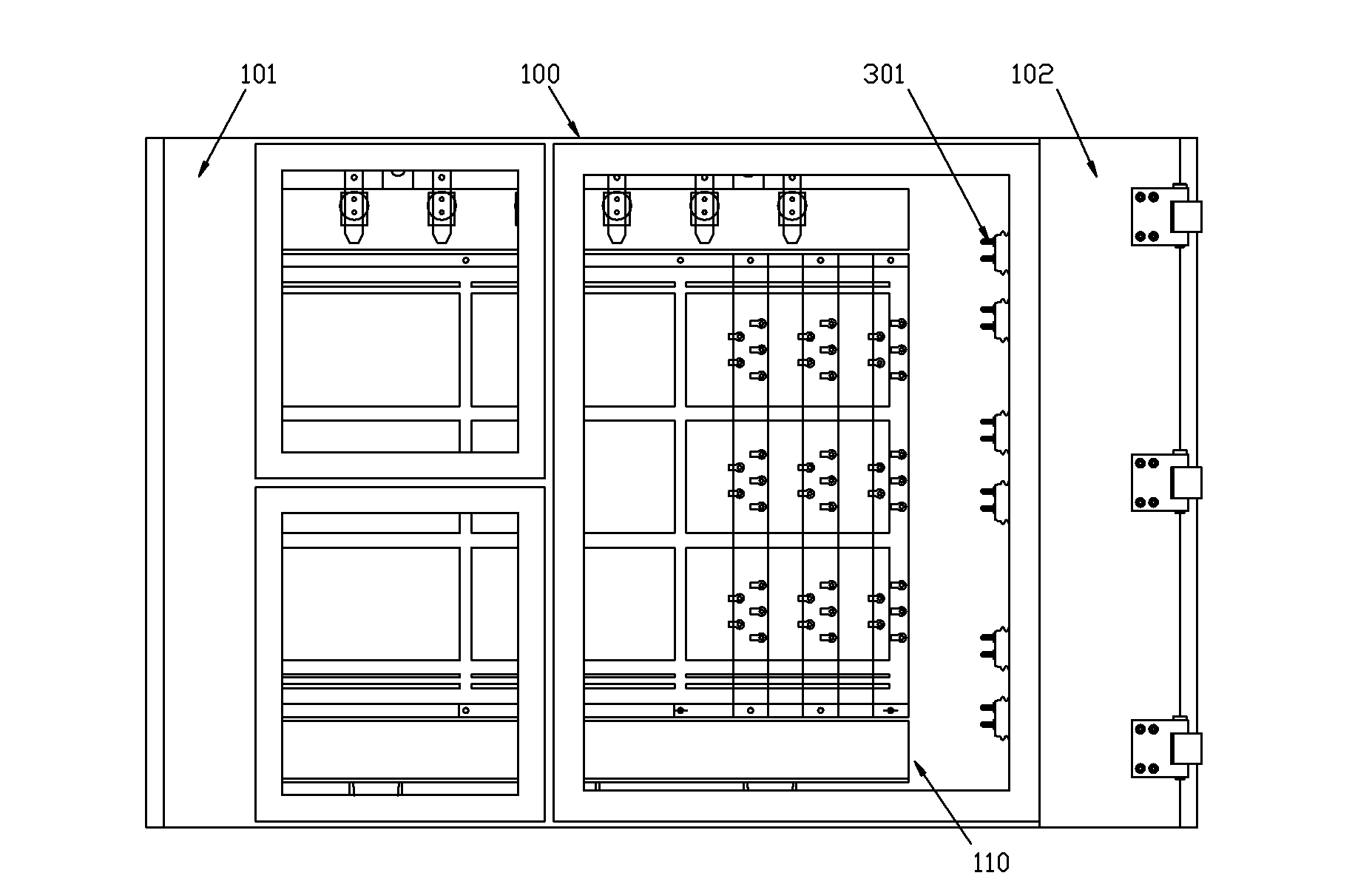

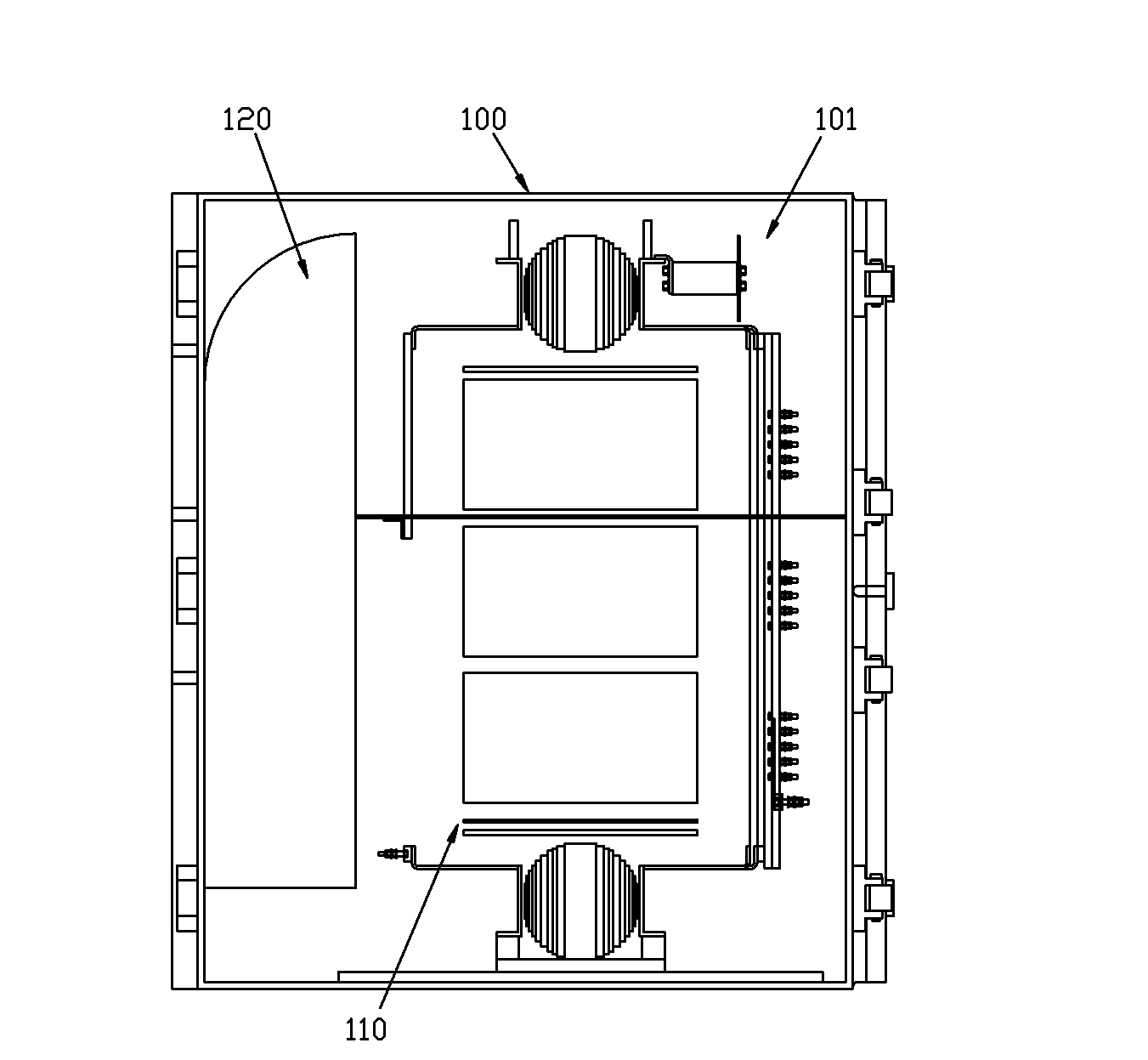

Mining high-voltage frequency converter with explosion-proof type

InactiveCN102307000APrevent Chain ExplosionsImprove explosion-proof performanceCooling/ventilation/heating modificationsPower conversion systemsControl signalEngineering

The invention discloses a mining high-voltage frequency converter with an explosion-proof type. The frequency converter comprises a phase-shifting transformer unit explosion-proof box and a power unit explosion-proof box; a phase-shifting isolation transformer and a heat radiation system are arranged in the phase-shifting transformer unit explosion-proof box; and a plurality of sets of power units, a control unit and a heat radiation system are arranged in the power unit explosion-proof box, wherein the plurality of sets of power units are in series connection. A high-tension side of the phase-shifting isolation transformer is in series connection with a three phase high voltage power network; the plurality of sets of power units are respectively connected with a low tension side of the phase-shifting isolation transformer; and the power units and the control unit are connected by a fiber. According to the invention, all assembling combination surfaces of the phase-shifting transformer unit explosion-proof box and the power unit explosion-proof box are constructed into sealing structures, so that an external environment is isolated from the phase-shifting transformer unit explosion-proof box and the power unit explosion-proof box; therefore, it can be avoided that corresponding chain explosions happen at high-risk occasions including a coal mine and the like and an explosion-proof effect is good. Besides, a control signal is transmitted by a fiber, so that an electrical isolation capability and an anti-electromagnetic interference performance are good.

Owner:江苏聚友电气有限公司

Remote control of lighting

InactiveUS7405523B2Reduce the amount requiredLittle power lossPoint-like light sourceElectrical apparatusEffect lightEngineering

An electronic ballast system controls one or more ballasts of HID or fluorescent lamps, which are controlled in an “on / off” manner by a ultra low power controller that is isolated for a primary power circuit or derives its very low switch power from the ballast itself. The on / off control provides a near lossless control system. This system may be applied to electronic ballast for operates at fractional power levels corresponding to different lighting intensities and with conventional occupancy sensors. The system may also be applied to other electronically compatible end-use devices and applications.

Owner:WILHELM WILLIAM GEORGE +1

Surgical jaw instrument having a slide system

ActiveUS20120101484A1Improve electrical isolationHigh strengthSurgical instrument detailsSurgical forcepsEngineering

Owner:OLYMPUS WINTER & IBE

Semiconductor device and formation method therefor

ActiveCN105336660AInhibited DiffusionPrevent proliferationSemiconductor/solid-state device manufacturingSemiconductor devicesVacancy defectDielectric layer

A semiconductor device and a formation method therefor are disclosed. The formation method for the semiconductor device comprises the steps of providing a substrate including a first region and a second region; forming a groove including a first part and a second part in the substrate; forming a first barrier layer at the bottom of the first part and the surface of the side wall of the groove, wherein the first barrier layer captures lattice vacancy defects or interstitial atom defects in the substrate; forming a second barrier layer at the bottom of the second part and the surface of the side wall of the groove, wherein the second barrier layer captures lattice vacancy defects or interstitial atom defects in the substrate, and defect types captured by the first barrier layer and the second barrier layer are different; forming dielectric layers for filling the grooves; forming a first well region in the first region substrate; forming a second well region in the second region substrate, wherein the doping types of the second well region and the first well region are opposite. According to the semiconductor device and the formation method therefor, the diffusion of the doping ions in the first well region and the second well region can be effectively prevented to endow the semiconductor device with a good electrical isolation performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

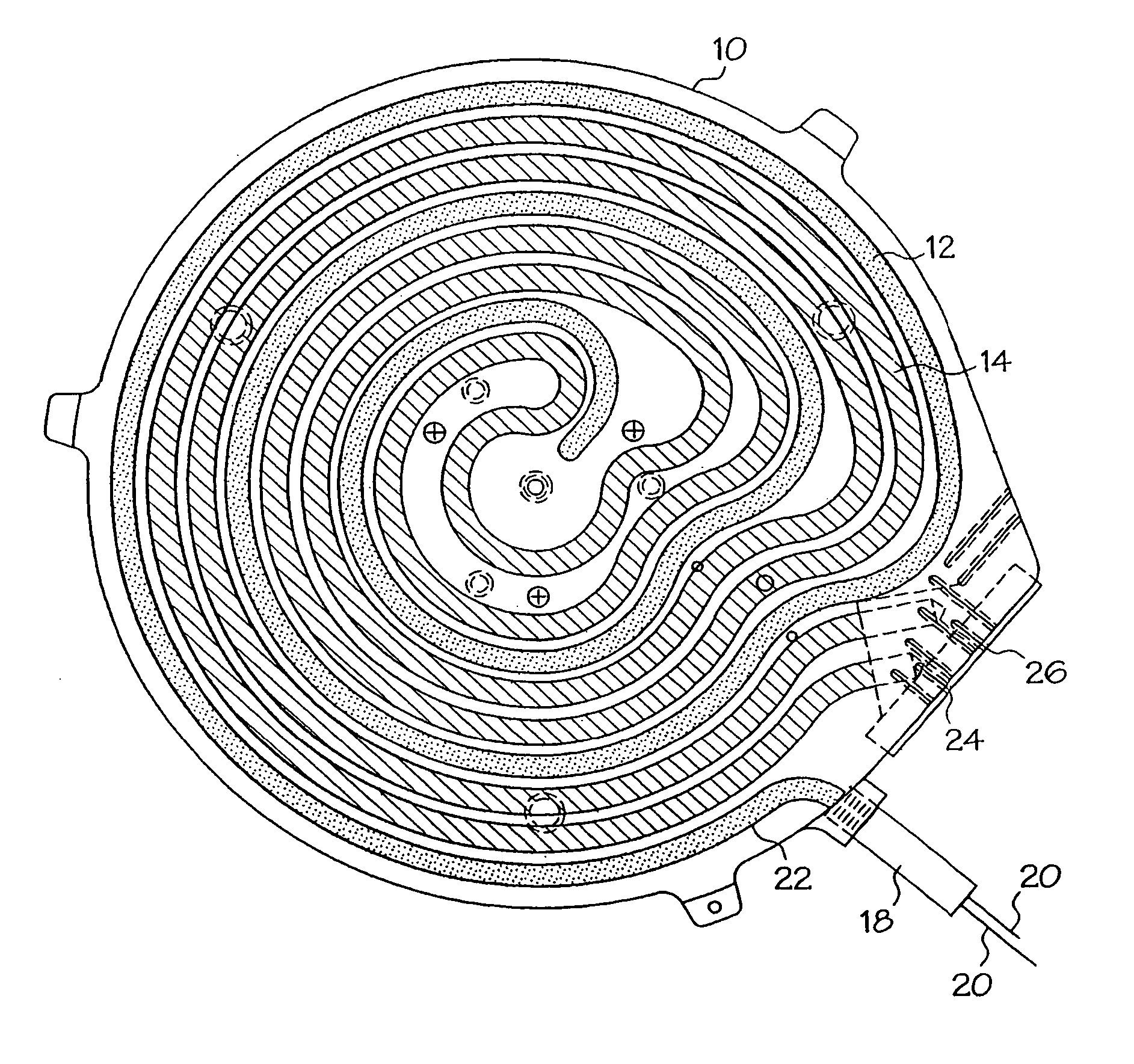

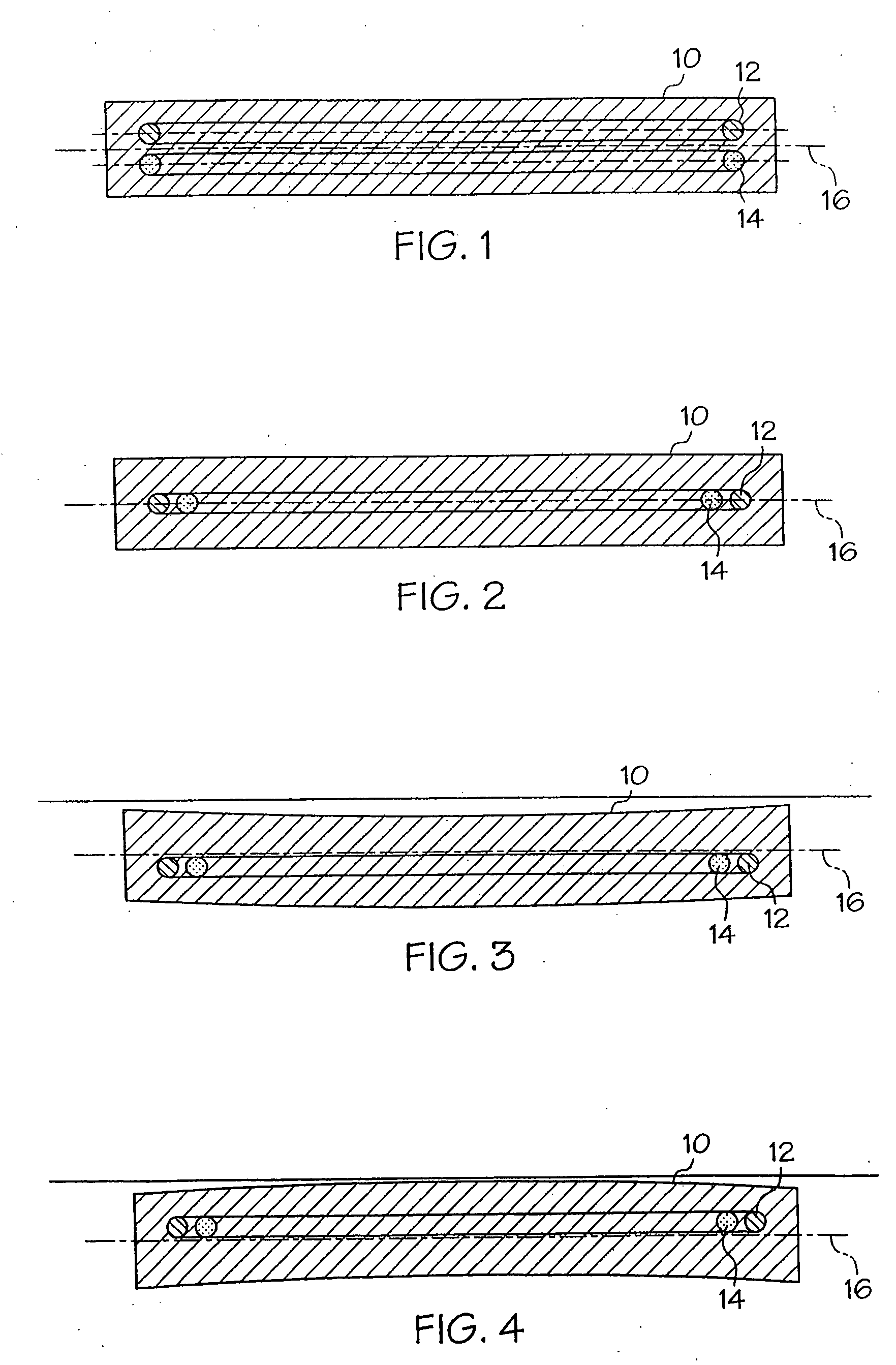

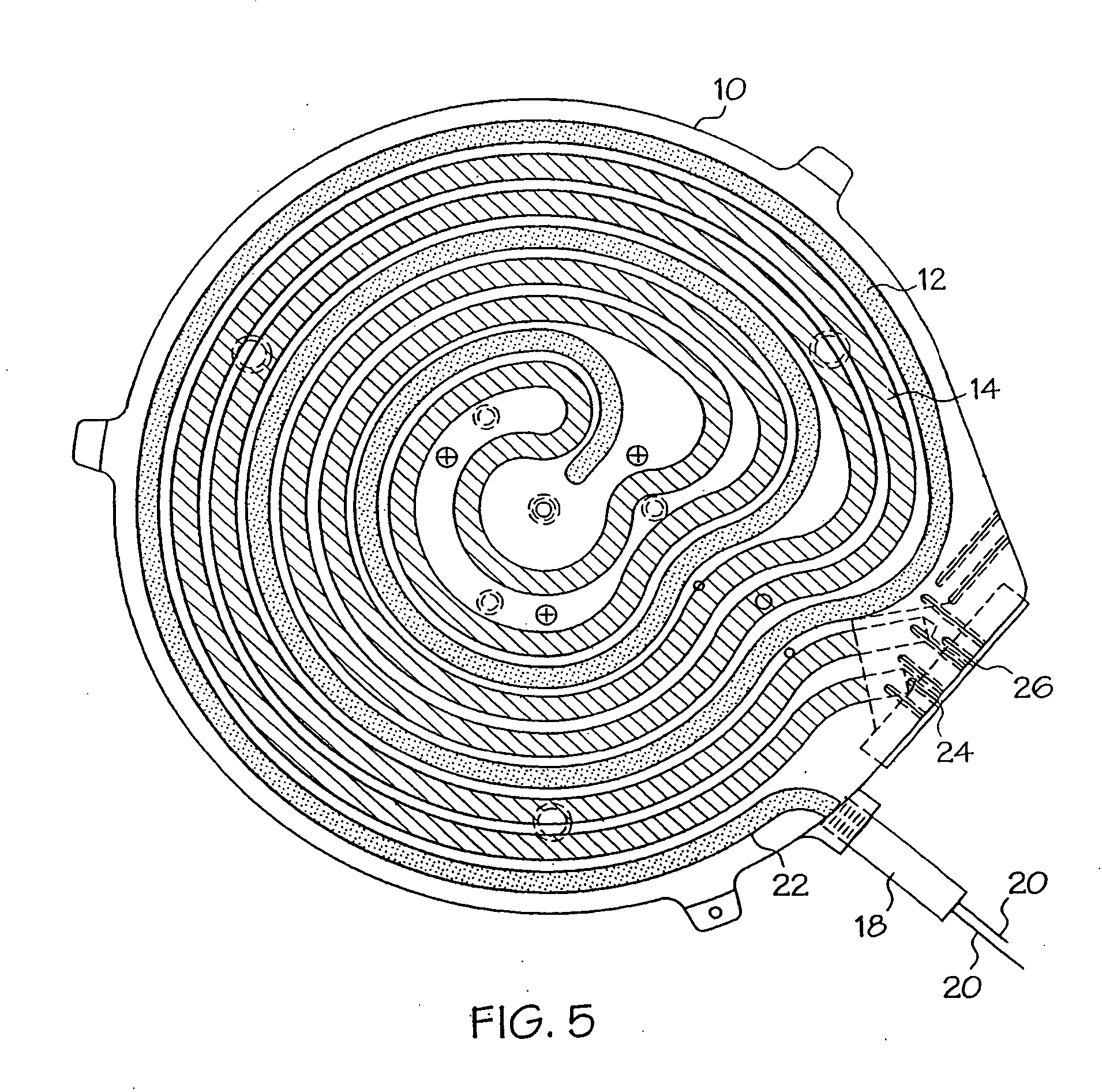

Wafer chuck having thermal plate with interleaved heating and cooling elements

InactiveUS20050217583A1Conserve costImprove electrical isolationSemiconductor/solid-state device testing/measurementElectronic circuit testingEngineeringCooling fluid

A workpiece chuck includes a thermal plate assembly which includes both heating and cooling capability. The heating element can be a resistive heater in a coiled configuration disposed in a plane. The cooling can be performed via a cooling fluid circulated through cooling tubes which are also disposed in a coiled configuration in a plane. The plane of the heating element and the cooling tubes can be the same plane, and that plane can be a center plane of the thermal plate assembly. By locating the heating and cooling in the same plane, uniform heating and cooling are achieved. Also, by locating the heating element and cooling tubes in the center of the thermal plate, distortions such as doming and dishing in the thermal plate are eliminated such that the wafer can be held extremely flat on the chuck. The heating element and cooling tubes are coiled in an interleaved fashion to provide uniform heating and cooling while allowing them to simultaneously occupy the same plane.

Owner:TEMPTRONIC

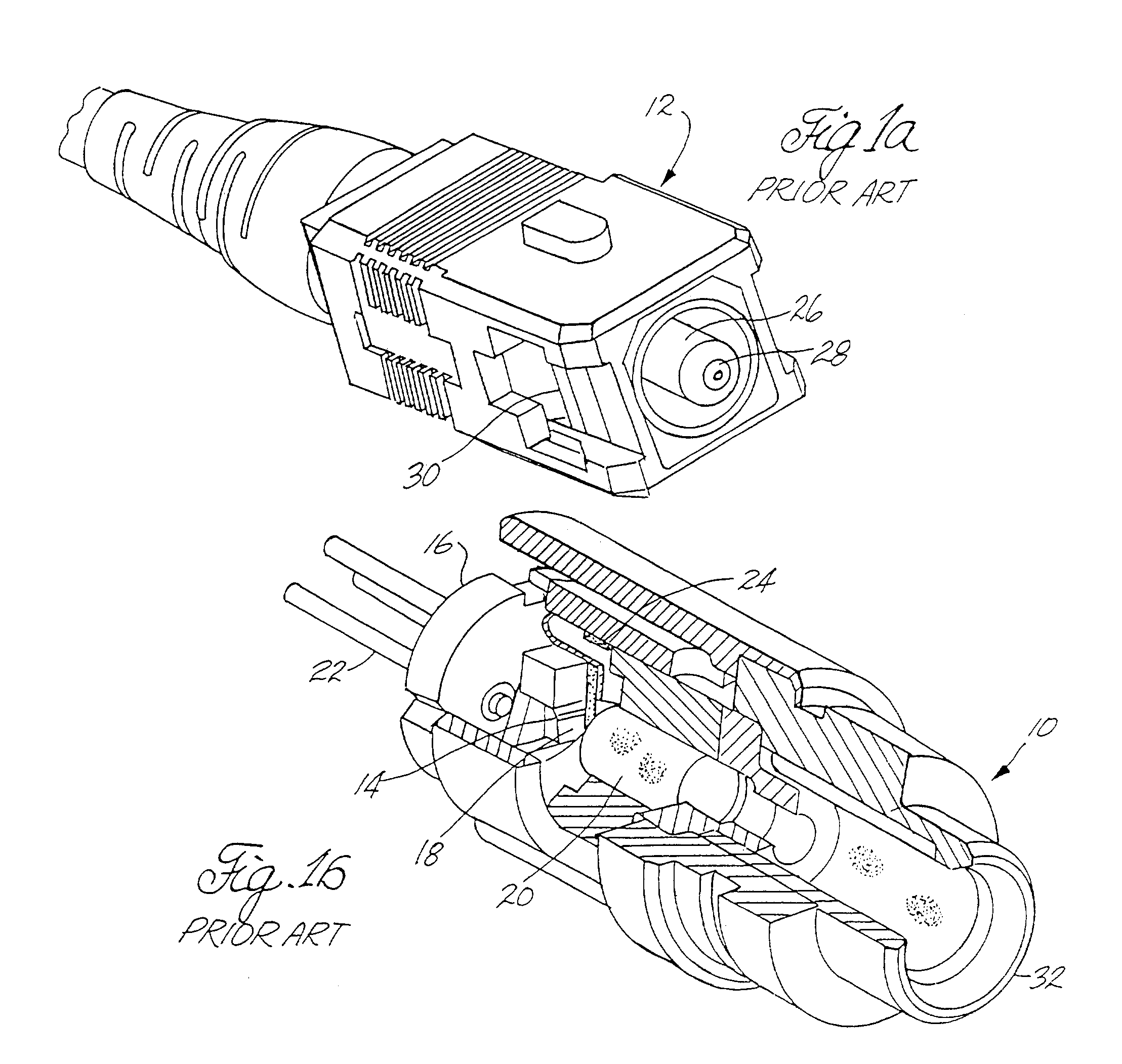

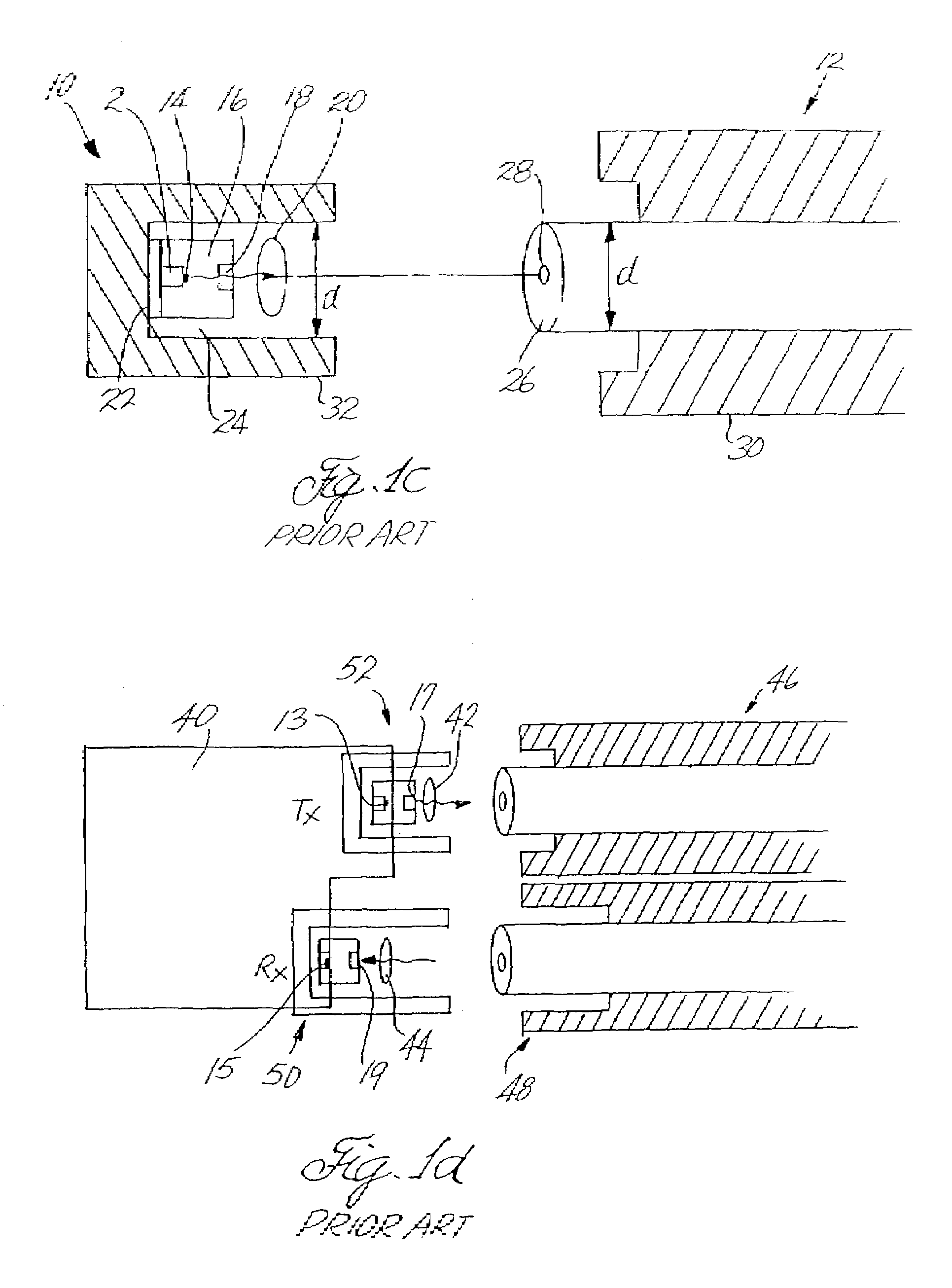

Closely-spaced VCSEL and photodetector for application requiring their independent operation

InactiveUS7053415B2Avoid parasitic effectsImprove efficiencyLaser detailsSolid-state devicesPhotovoltaic detectorsAudio power amplifier

A monolithically integrated VCSEL and photodetector, and a method of manufacturing the same, are disclosed for applications where the VCSEL and photodetector require separate operation such as duplex serial data communications applications. A first embodiment integrates a VCSEL with an MSM photodetector on a semi-insulating substrate. A second embodiment builds layers of a p-i-n photodiode on top of layers forming a VCSEL using a standard VCSEL process. The p-i-n layers are etched away in areas where VCSELs are to be formed and left where photodetectors are to be formed. The VCSELs underlying the photodetectors are inoperable, and serve to recirculate photons which are not initially absorbed back into the photodetector. The transmit and receive pairs are packaged into a single package for interface to multifiber ferrules. The distance between the devices is precisely defined photolithographically, thereby making alignment easier. In a further alternate embodiment, a FET is coupled to the p-i-n photodiode to form an integrated detector preamplifier along with the VCSEL transmitter all on the same optical reference plane.

Owner:OPTICAL COMM PRODS

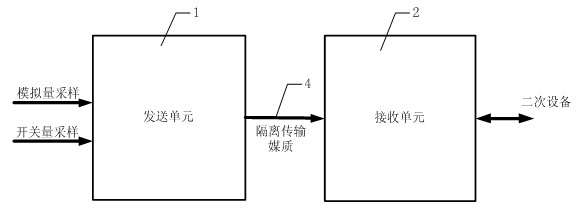

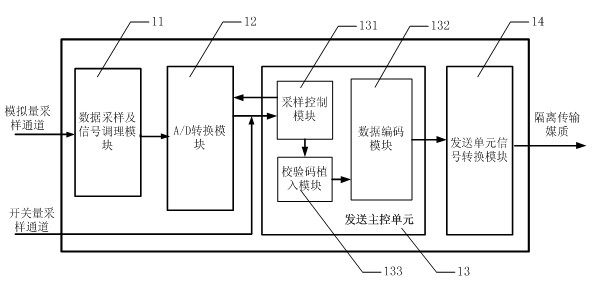

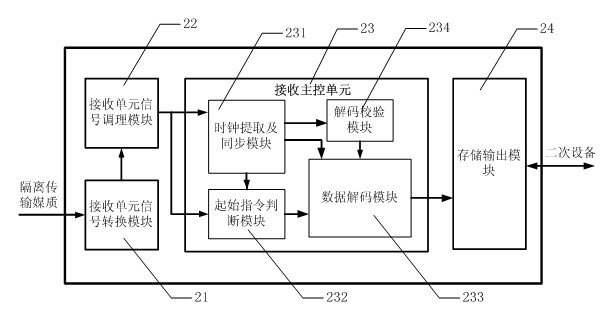

Multi-channel isolated high-speed intelligent transmitting-receiving device and method for power electronic system

InactiveCN102158336ASolve the problem that wiring is susceptible to electromagnetic interferenceImprove accuracyError preventionSynchronising arrangementElectronic systemsSignal conditioning

The invention discloses a multi-channel isolated high-speed intelligent transmitting-receiving device and method for a power electronic system. The device comprises transmitting units, receiving units and isolated transmission mediums. Each transmitting unit comprises a data sampling and signal conditioning module, an A / D (Analog / Digital) conversion module, a transmitting main control unit and a transmitting unit signal conversion module; each receiving unit comprises a receiving unit signal conversion module, a receiving unit signal conditioning module, a receiving main control unit and a memory output module. The device can perform digital coding on multi-channel analog sampling and switch sampling, and transmits through the isolated transmission mediums; each receiving unit can be connected with a plurality of the transmitting units for simultaneously decoding. The multi-channel isolated high-speed intelligent transmitting-receiving device has the advantages of prominent high-reliable electrical isolation performance, instantaneity and intelligent performance.

Owner:ZHEJIANG UNIV

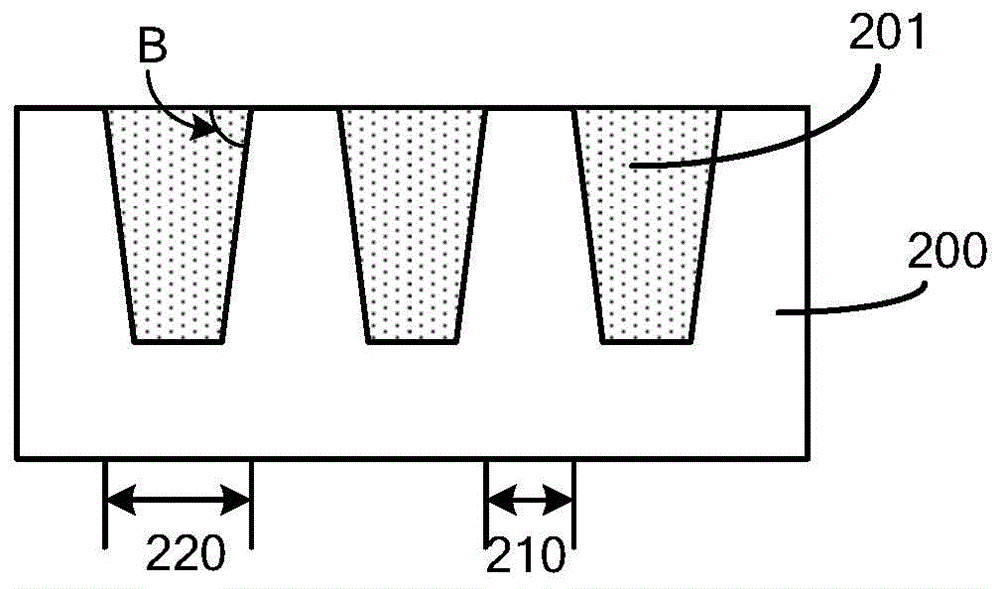

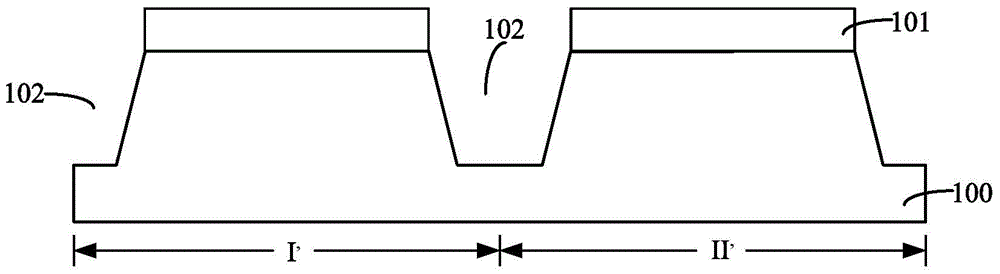

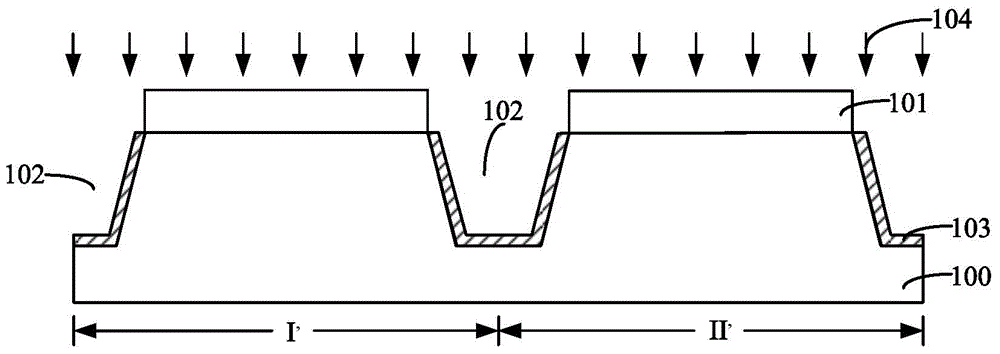

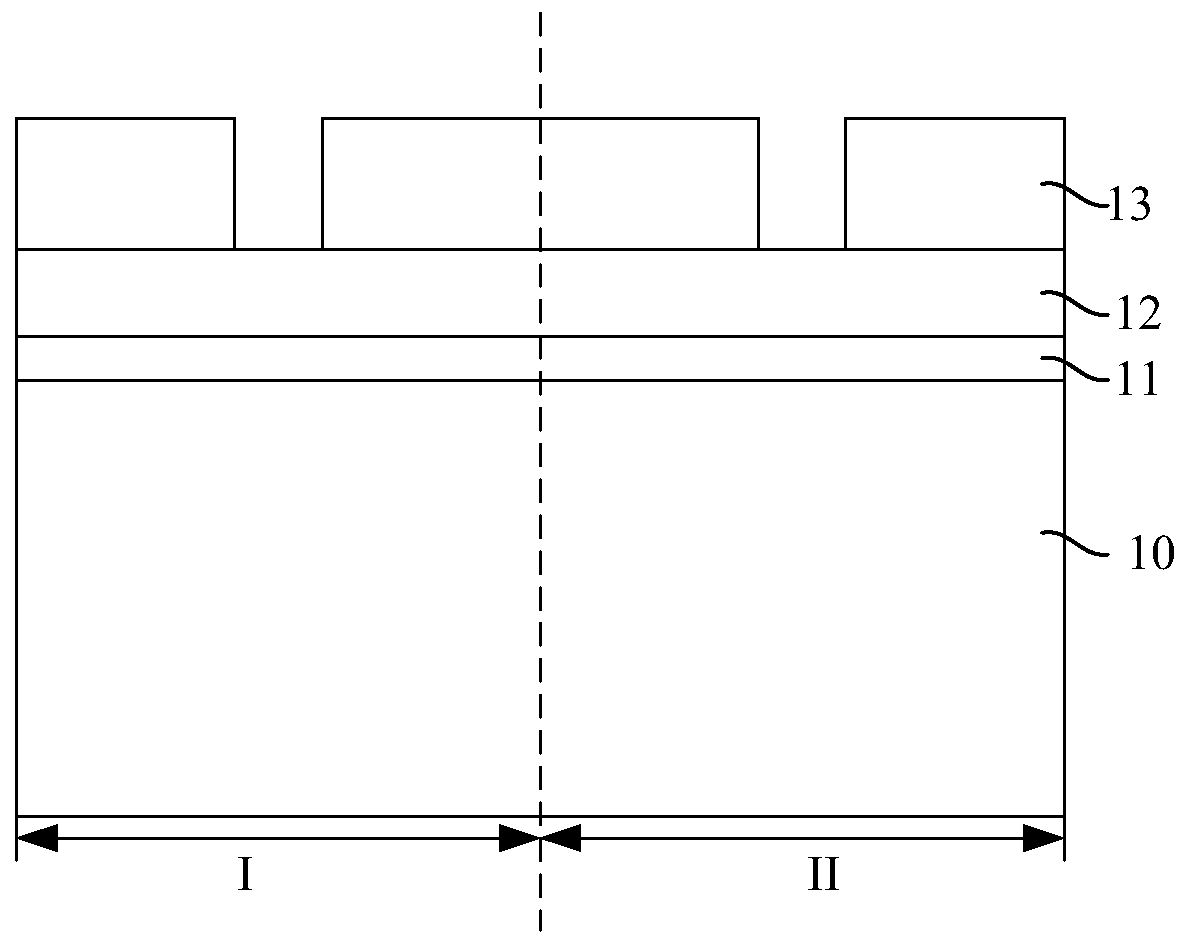

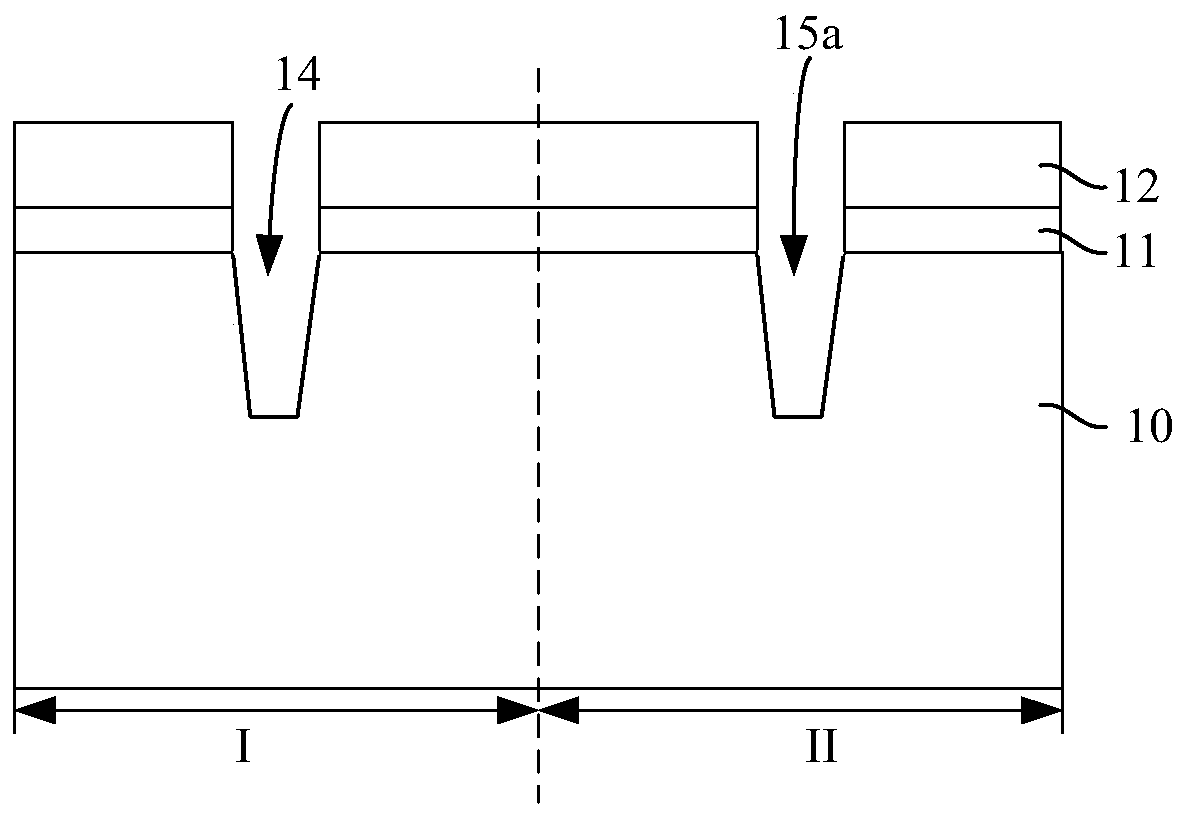

Double-depth shallow channel isolation groove and preparation method thereof

ActiveCN110148580AAvoid contamination riskAvoid Double Slope TopographySolid-state devicesSemiconductor/solid-state device manufacturingElectrical performanceProcess window

The invention provides a double-depth shallow channel isolation groove and a preparation method thereof. The preparation method of the double-depth shallow channel isolation groove comprises the following steps: providing a substrate, and sequentially forming a hard mask layer and a graphical first photoresist layer on the substrate; taking the graphical first photoresist layer as a mask, etchingto form a first opening and a second opening, and then removing the first photoresist layer; forming a graphical second photoresist layer on the hard mask layer; taking the graphical second photoresist layer and hard mask layer as masks, etching to form a first part of a second isolation groove, and then removing the second photoresist layer; taking the hard mask layer as a mask, and etching to form the second part and the first isolation groove of the second isolation groove so that the first isolation groove of a photosensitive region and the second isolation groove of a logic region are formed at the same time. Thus, the electrical performance of the photosensitive device is improved, the STI electrical isolation performance is also improved, the process difficulty is reduced, and the process window is expanded.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1