Double-depth shallow channel isolation groove and preparation method thereof

A technology of shallow trench isolation and isolation grooves, which is applied in radiation control devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of poor electrical performance of photosensitive devices and low electrical isolation performance of STI, and achieve improved performance , avoid double-slope morphology, and expand the effect of the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0038] A traditional method for preparing a double-depth shallow trench isolation trench includes the following steps:

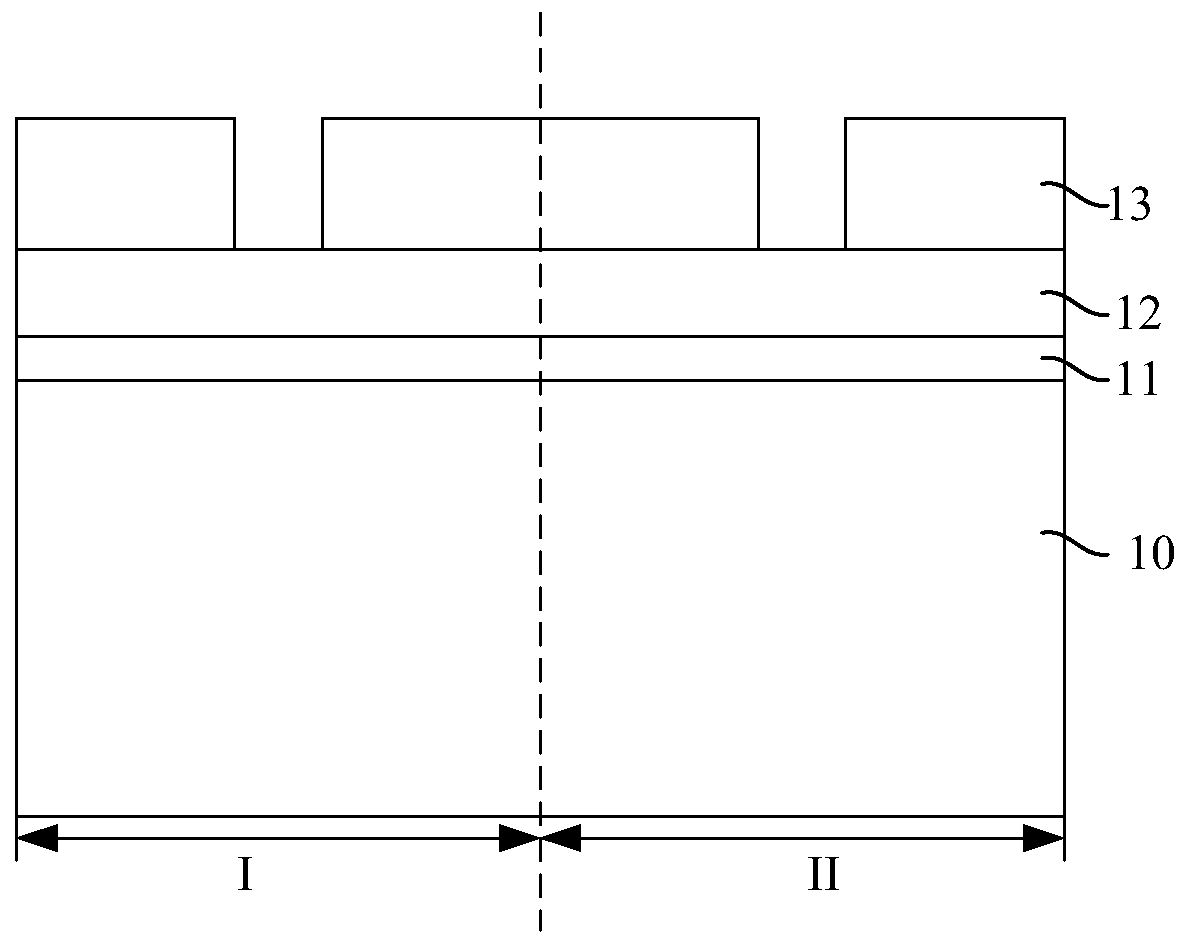

[0039] Step S11: See Figure 1a , providing a substrate 10 including a photosensitive region I and a logic region II, and sequentially depositing silicon oxide 11, a silicon nitride hard mask layer 12, and a patterned first photoresist 13 on the substrate 10;

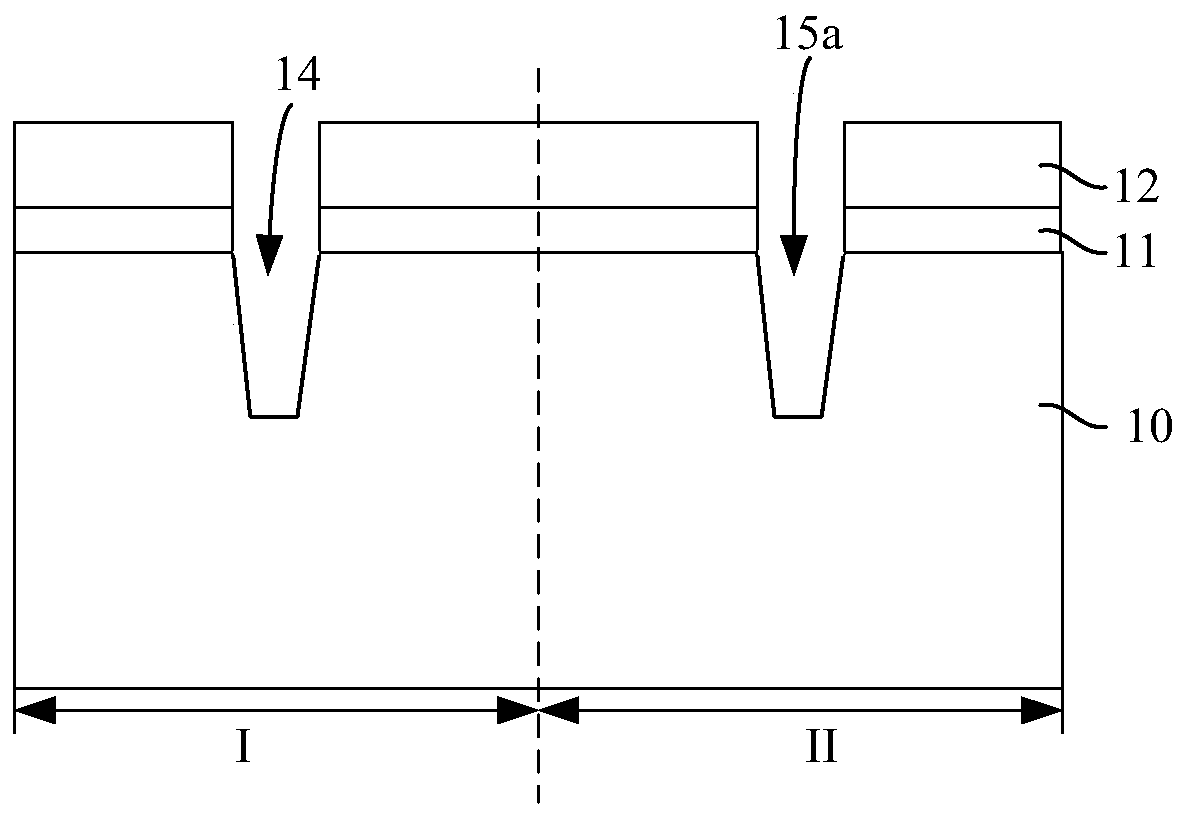

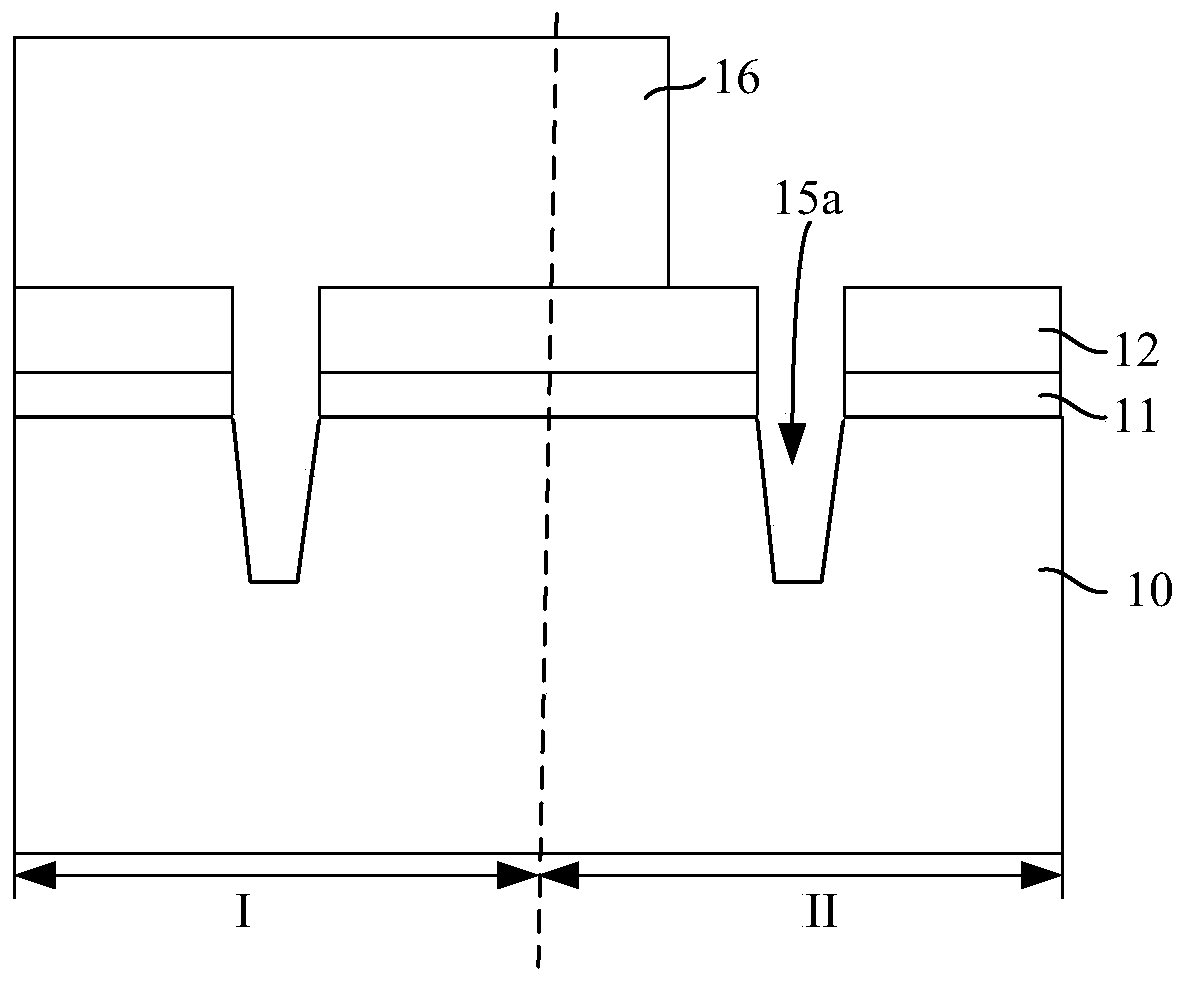

[0040] Step S12: See Figure 1b , the silicon nitride hard mask layer 12 and the silicon oxide 11 are sequentially etched by the first dry etching process, and the etching stops in the substrate 10 at a partial depth, so as to form the first isolation trench 14 and the second isolation trench 14. The first part 15a of the two isolation grooves, the first isolation groove 14 is located in the photosensitive area I, and the first part 15a is located in the logic area II, and the remaining first part 15a is cleaned and removed by an oxygen ashing method and a wet etching process. a photoresist 13;

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More