Patents

Literature

312 results about "Channel isolation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Bidirectional photothyristor chip, optical lighting coupler, and solid state relay

ActiveUS7423298B2Improving luminous sensitivityCoupling device detailsSemiconductor/solid-state device manufacturingOxygenSolid-state relay

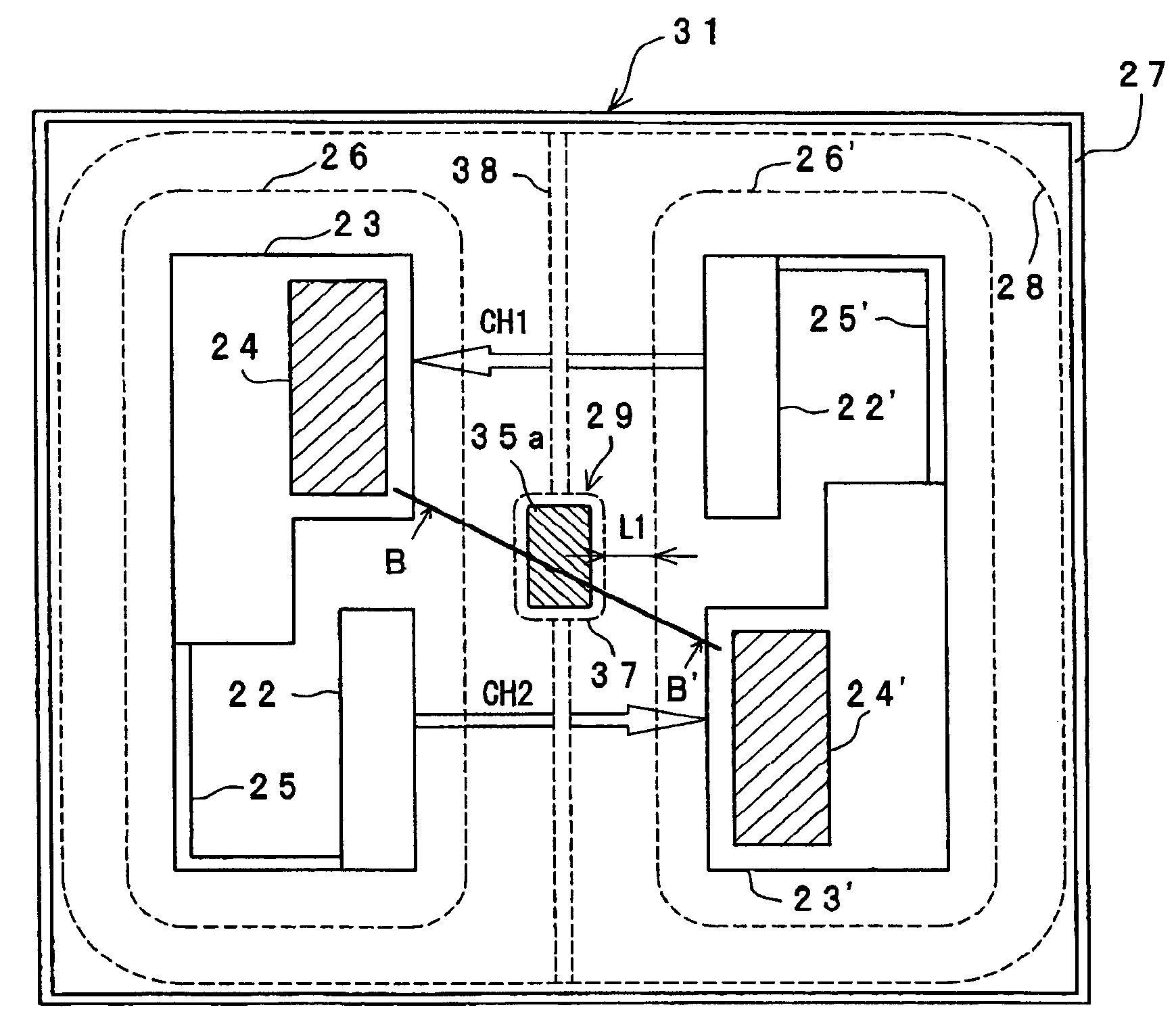

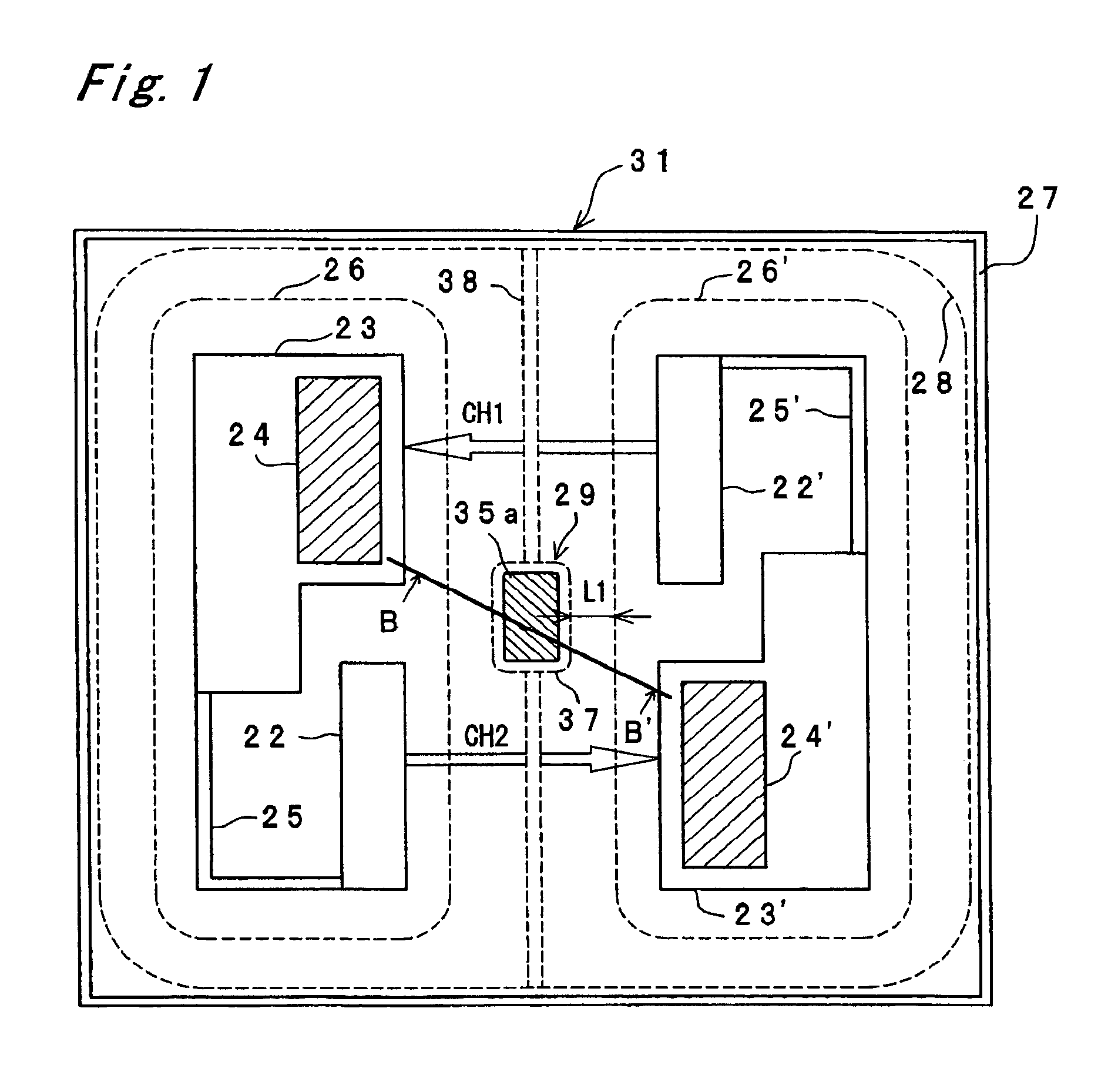

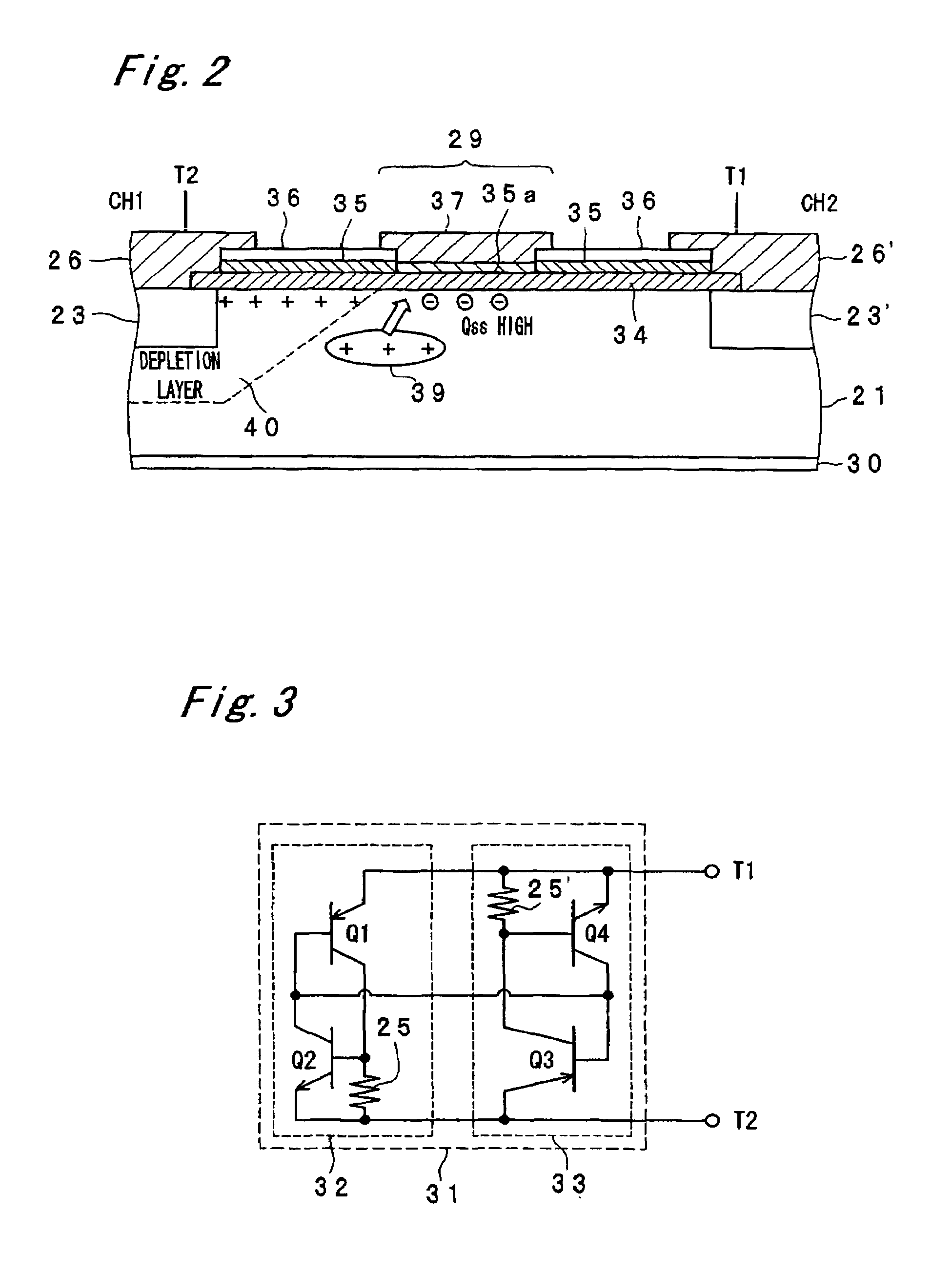

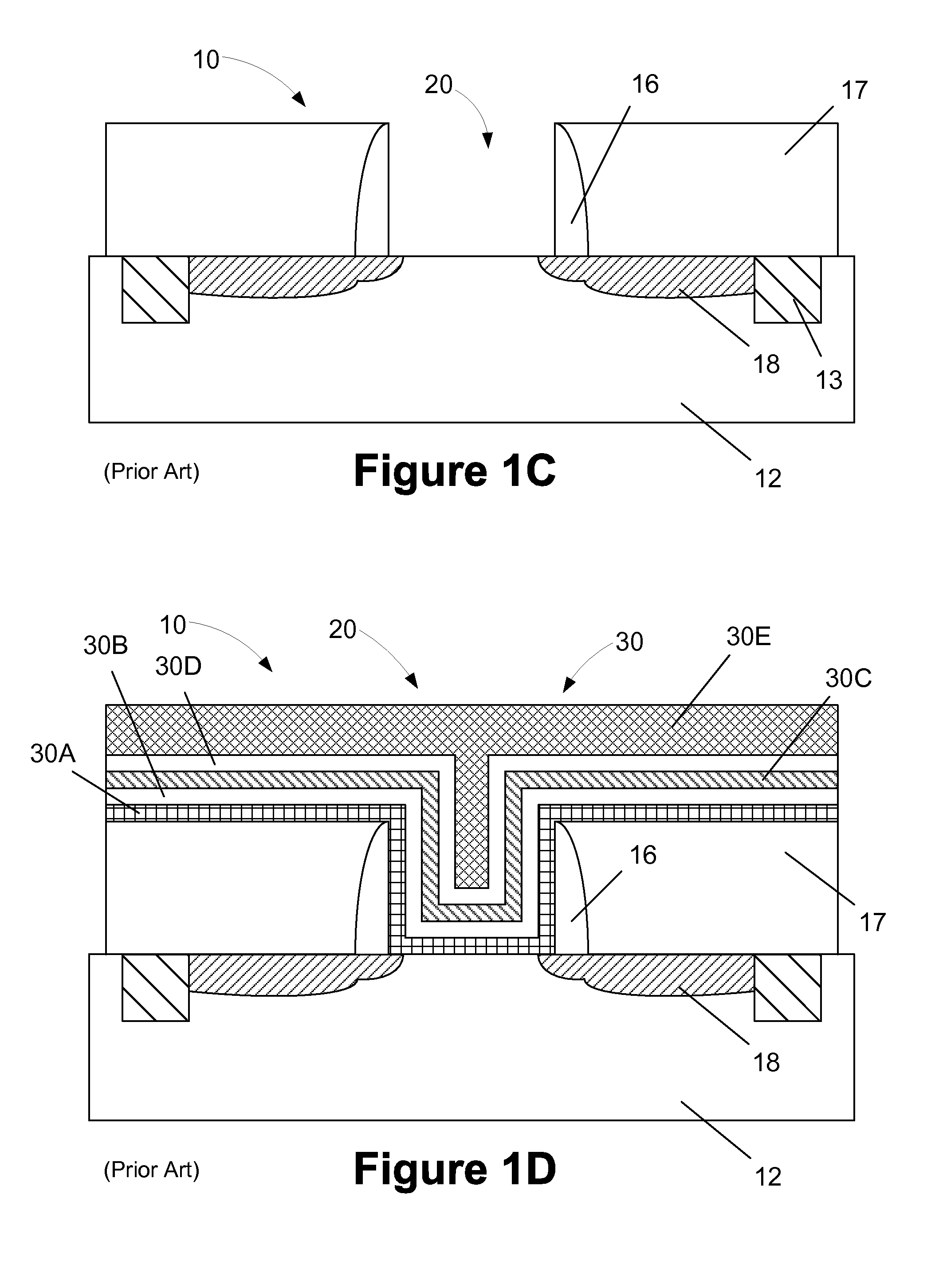

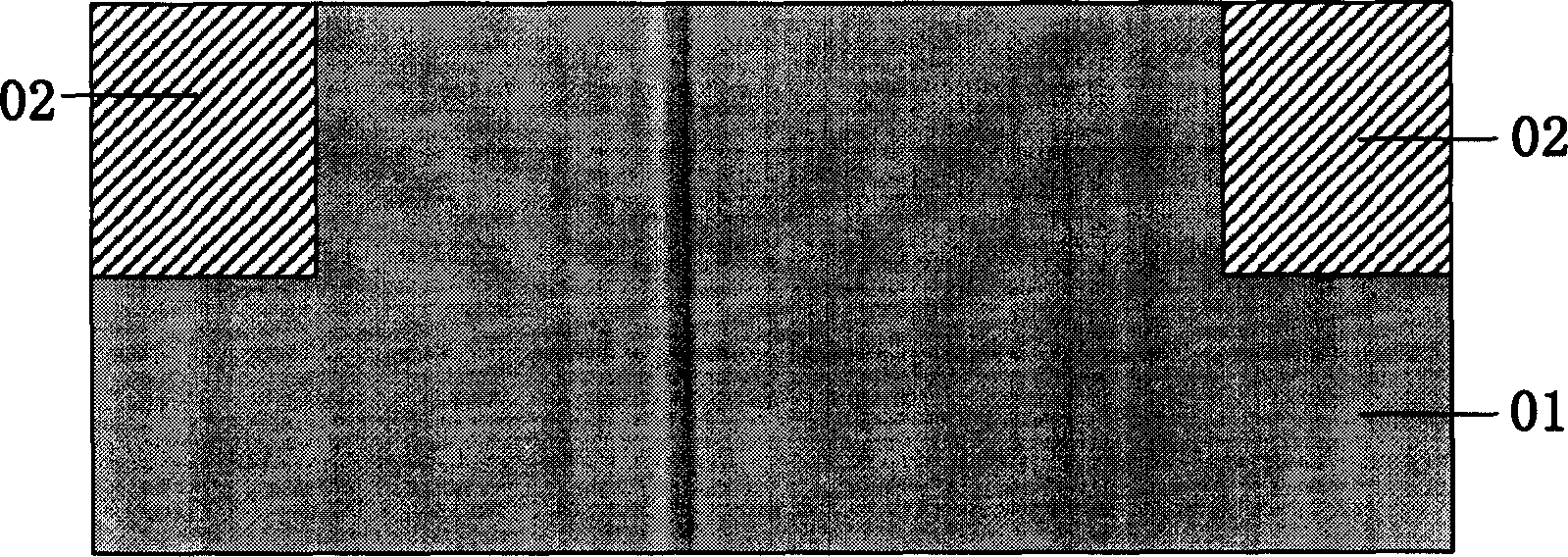

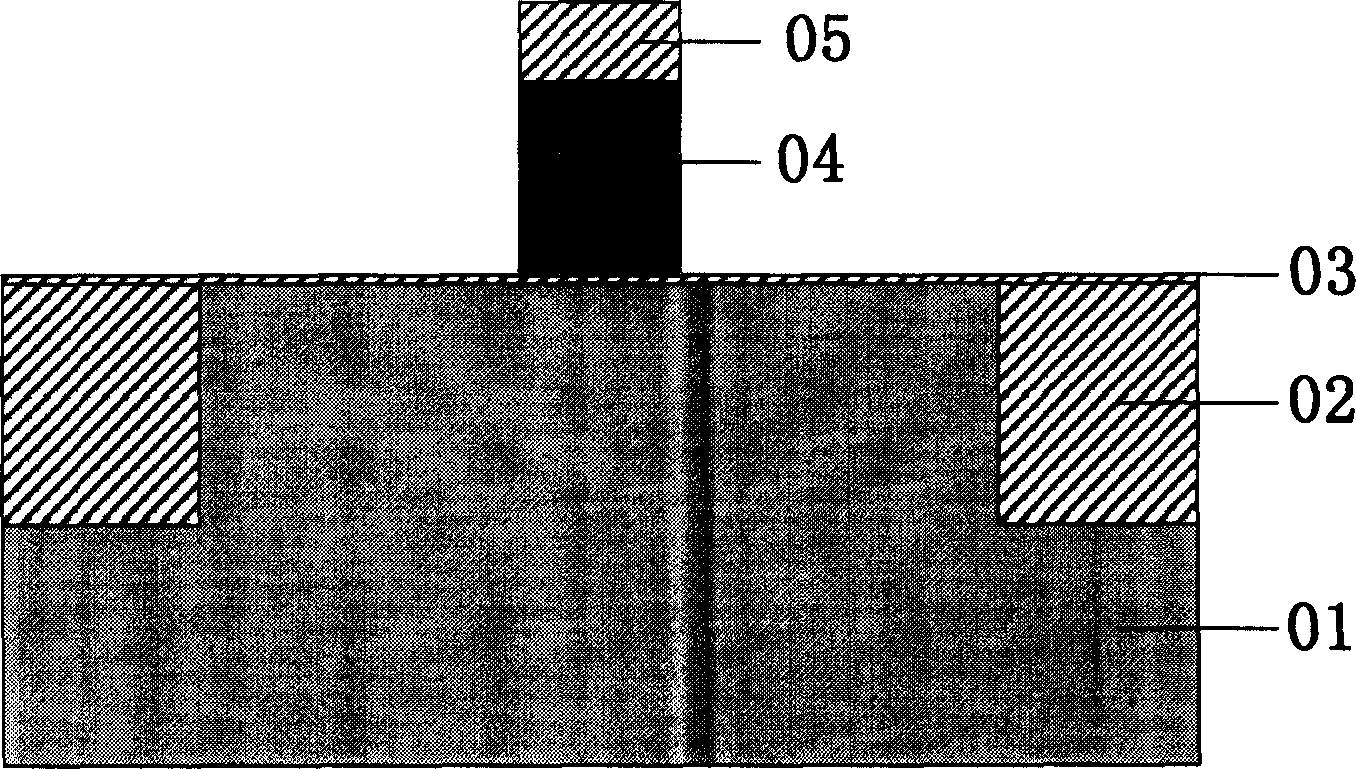

Two operation channels CH1 and CH2 of a bidirectional photothyristor chip 31 are disposed away from each other so as not to intersect with each other. In between a P-gate diffusion region 23 on the left-hand side and a P-gate diffusion region 23′ on the right-hand side on an N-type silicon substrate, and in between the CH1 and the CH2, a channel isolation region 29 comprised of an oxygen doped semi-insulating polycrystalline silicon film 35a doped with phosphorus is formed. Consequently, a silicon interface state (Qss) in the vicinity of the channel isolation region 29 on the surface of the N-type silicon substrate increases, so that holes or minority carriers in the N-type silicon substrate are made to disappear in the region. This makes it possible to prevent such commutation failure that when a voltage of the inverted phase is applied to the CH2 side at the point of time when the CH1 is turned off, the CH2 is turned on without incidence of light, and this allows a commutation characteristic to be enhanced.

Owner:SHARP KK

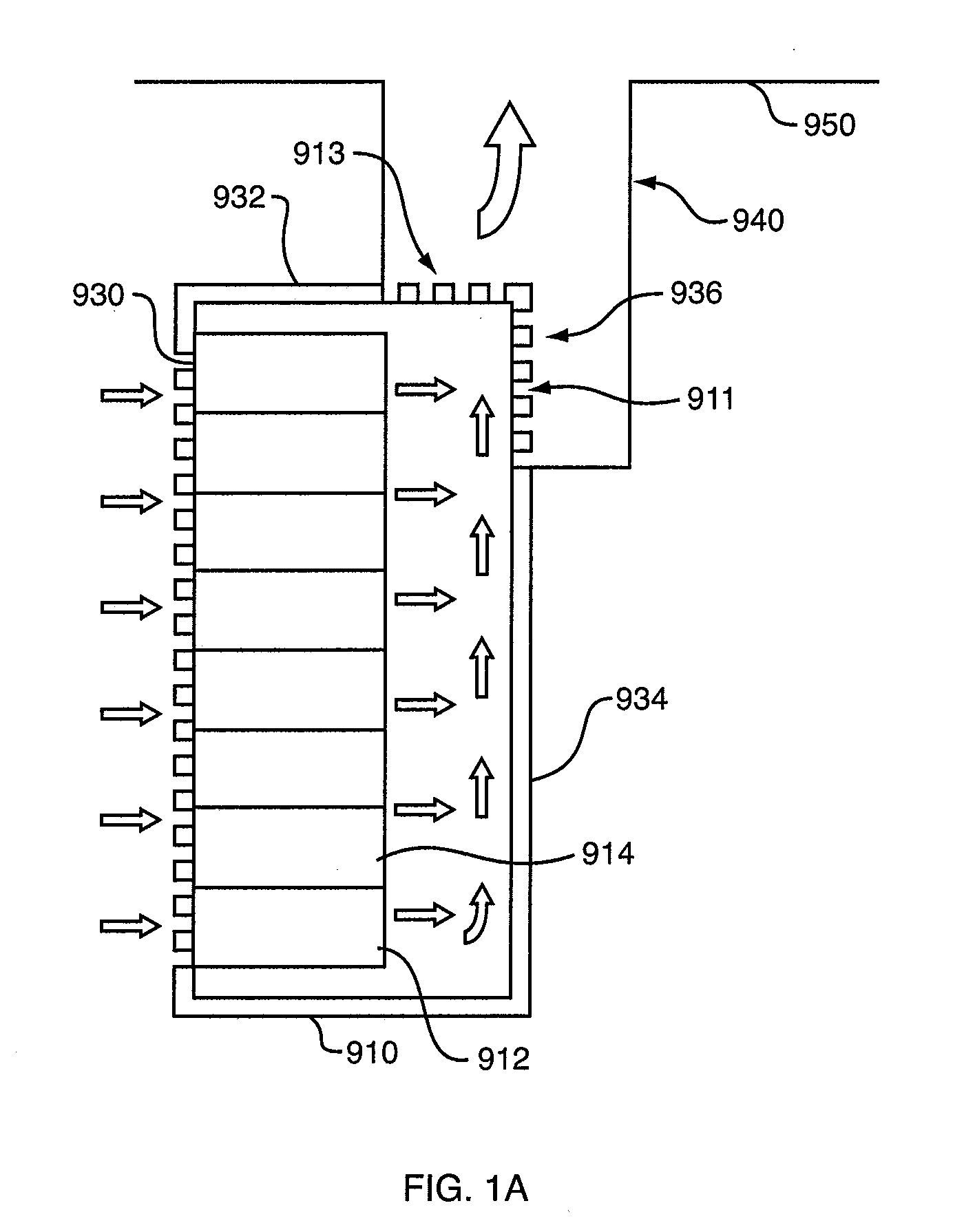

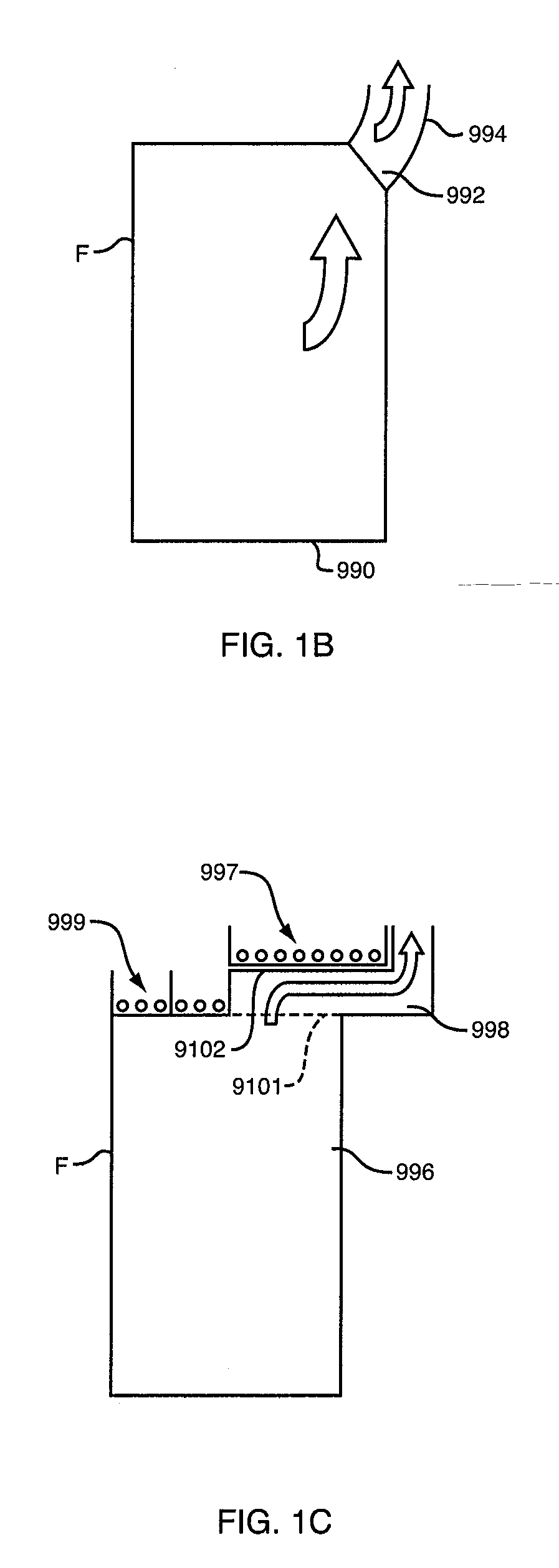

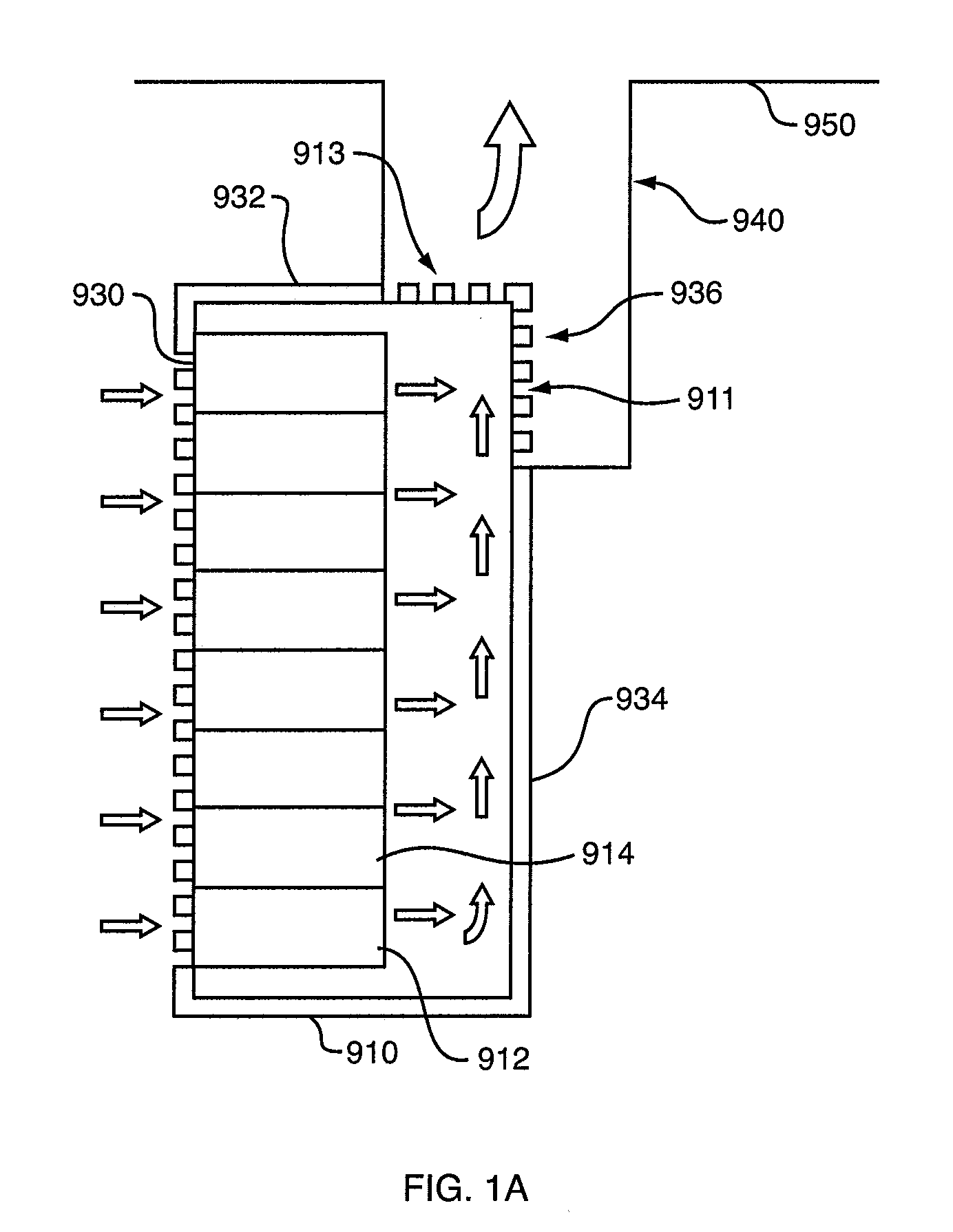

Systems and Methods for Closed Loop Heat Containment with Cold Aisle Isolation for Data Center Cooling

ActiveUS20100216388A1Maximize capacityMaintain depthCasings/cabinets/drawers detailsIndirect heat exchangersCold airData center

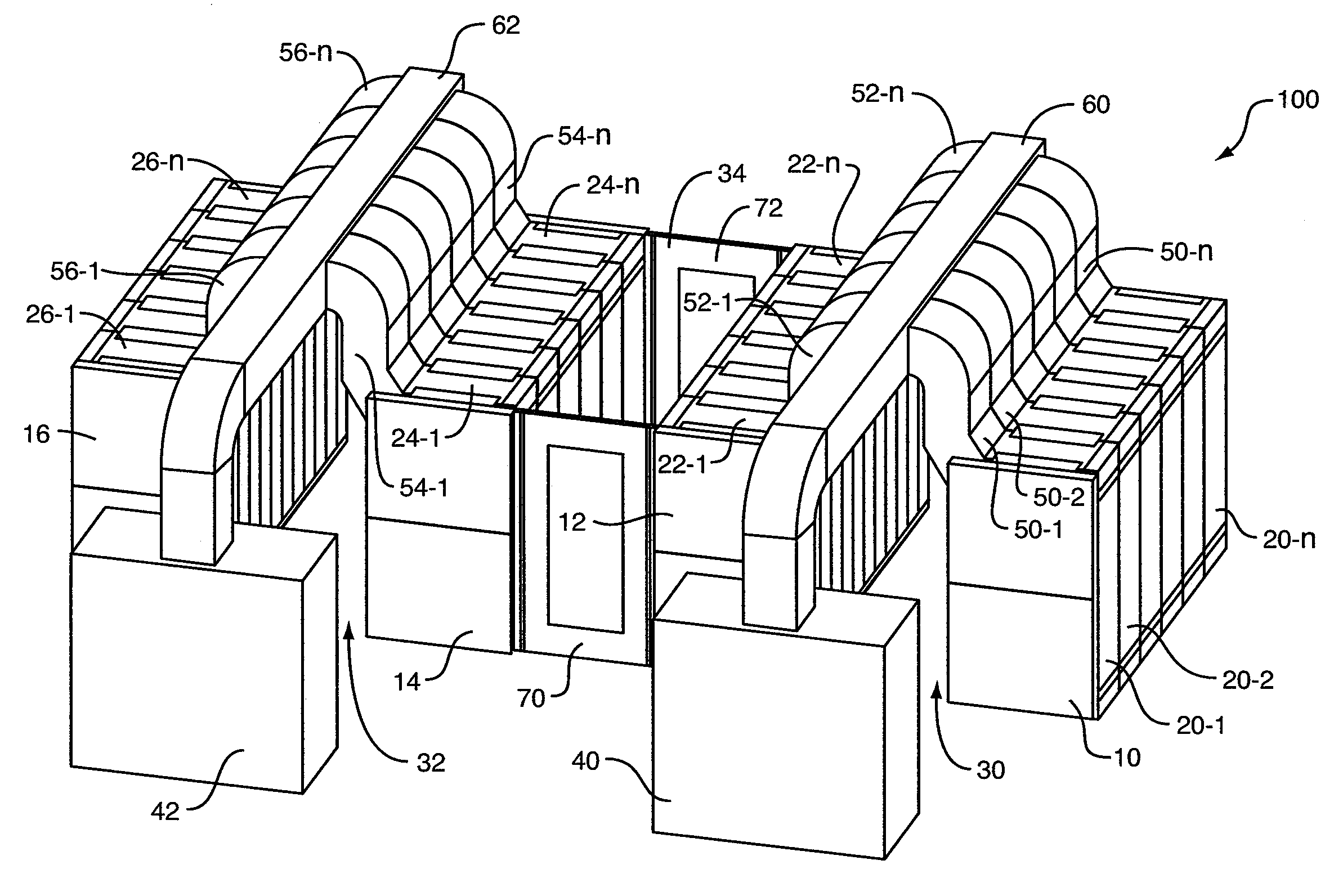

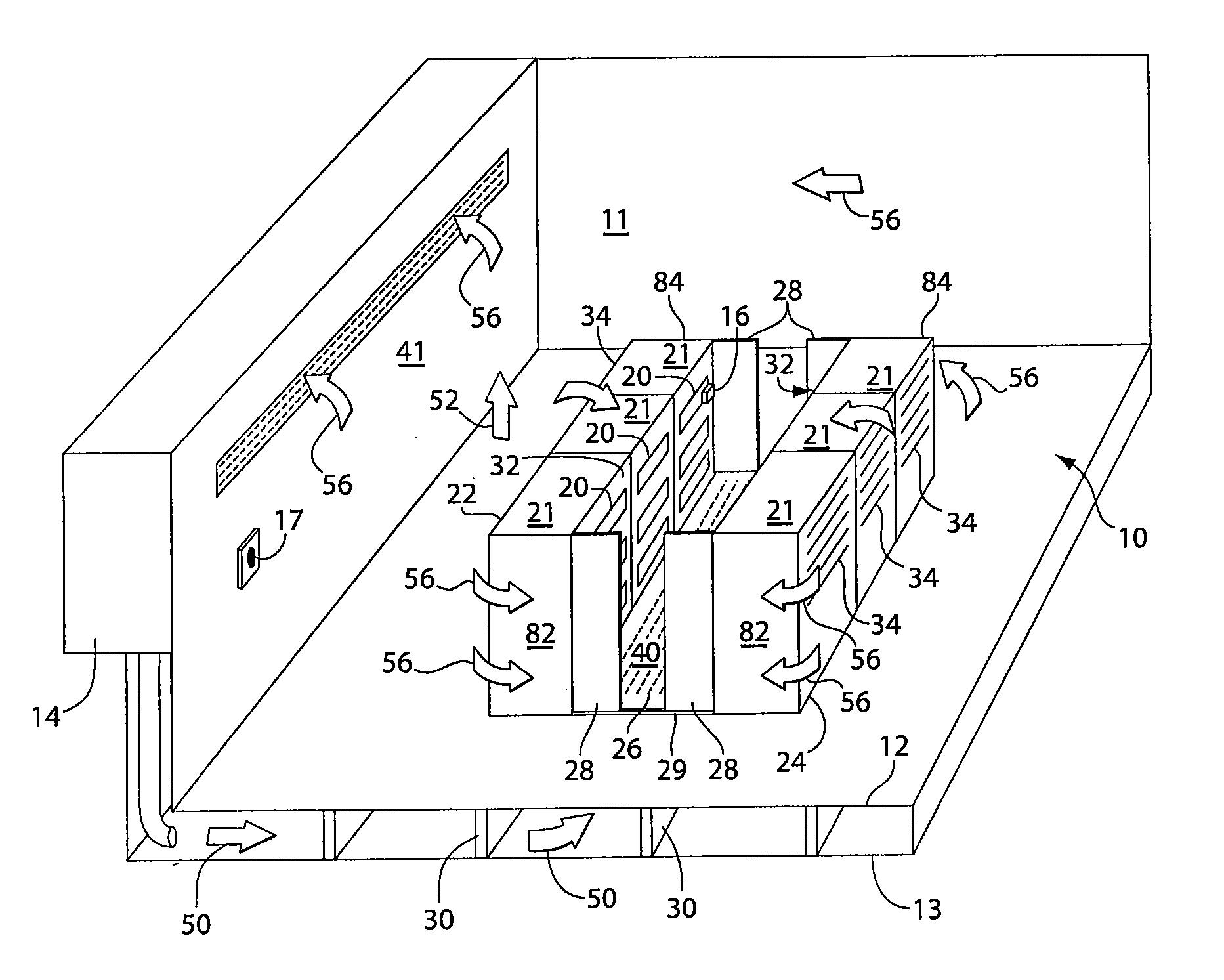

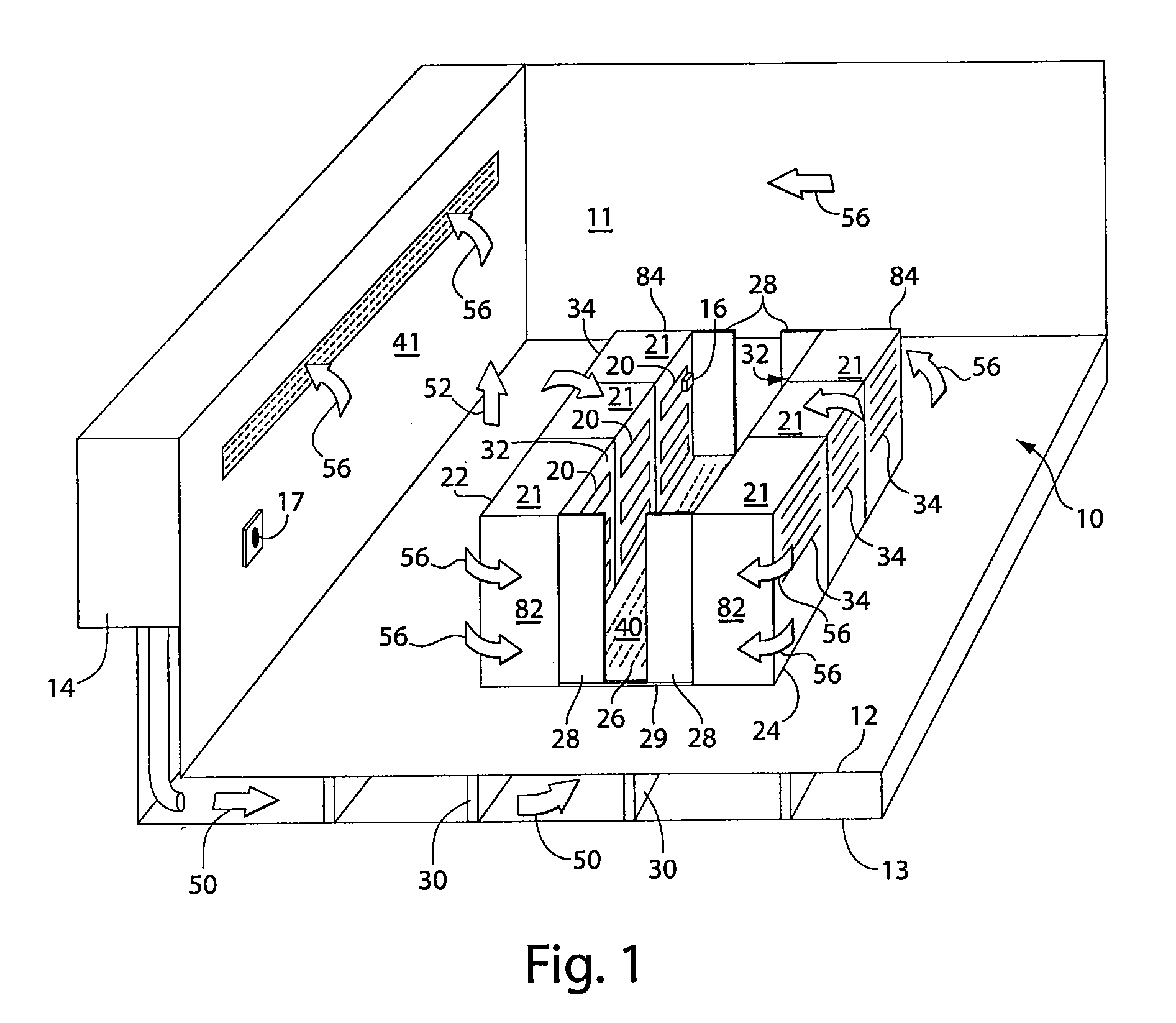

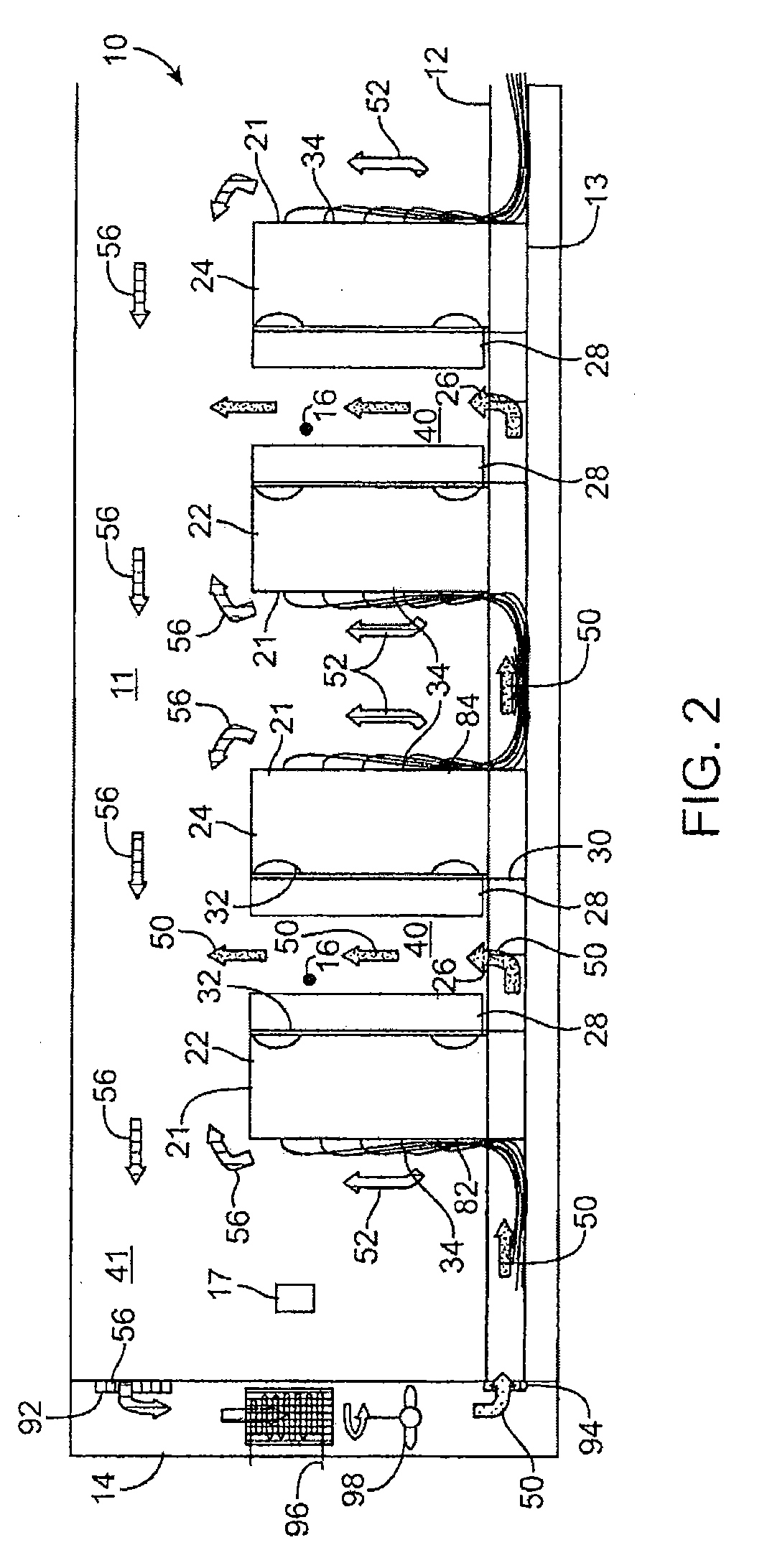

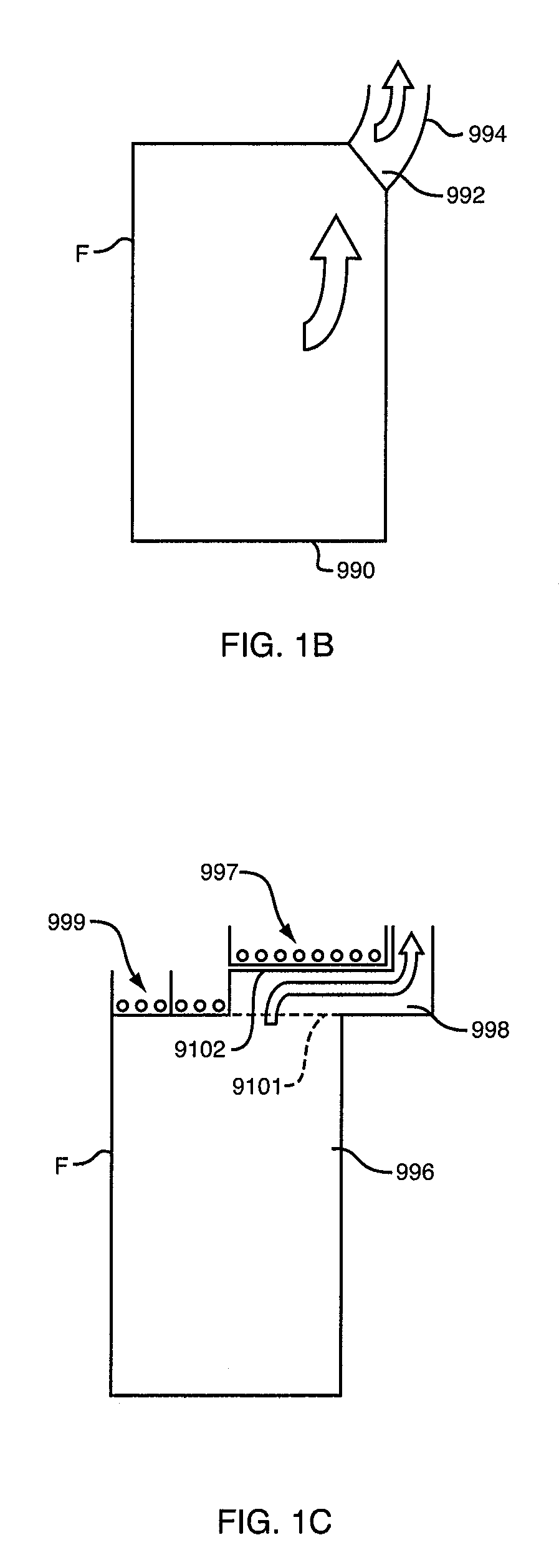

The invention combines systems and methods for heat containment and cold air isolation for managing airflow and temperature in data centers. The data center contains at least two rows of cabinets containing heat-generating equipment and arranged to form a cold aisle and a hot aisle. The data center system includes panels or doors at both ends of the cold aisle and an optional cover over the cold aisle to inhibit cooled air supplied by an air conditioning system from exiting the cold aisle and inhibit air warmed by the heat-generating components from entering the cold aisle,. A chimney coupled to the top, rear, or top and rear of the cabinets is configured to exhaust the warmed air into a region above the rows of cabinets. The chimneys may be ducted to a plenum or suspended ceiling or to the intake of the air conditioning system. Baffles and / or fans may be included in the chimneys, ducts, and / or plenums to control the air pressure. The invention may also include one or more data center air conditioning units, and each air conditioning unit may be configured to service one or more rows of cabinets. Alternatively, or in addition, cool air may be supplied by the building's air conditioning system.

Owner:EATON INTELLIGENT POWER LTD

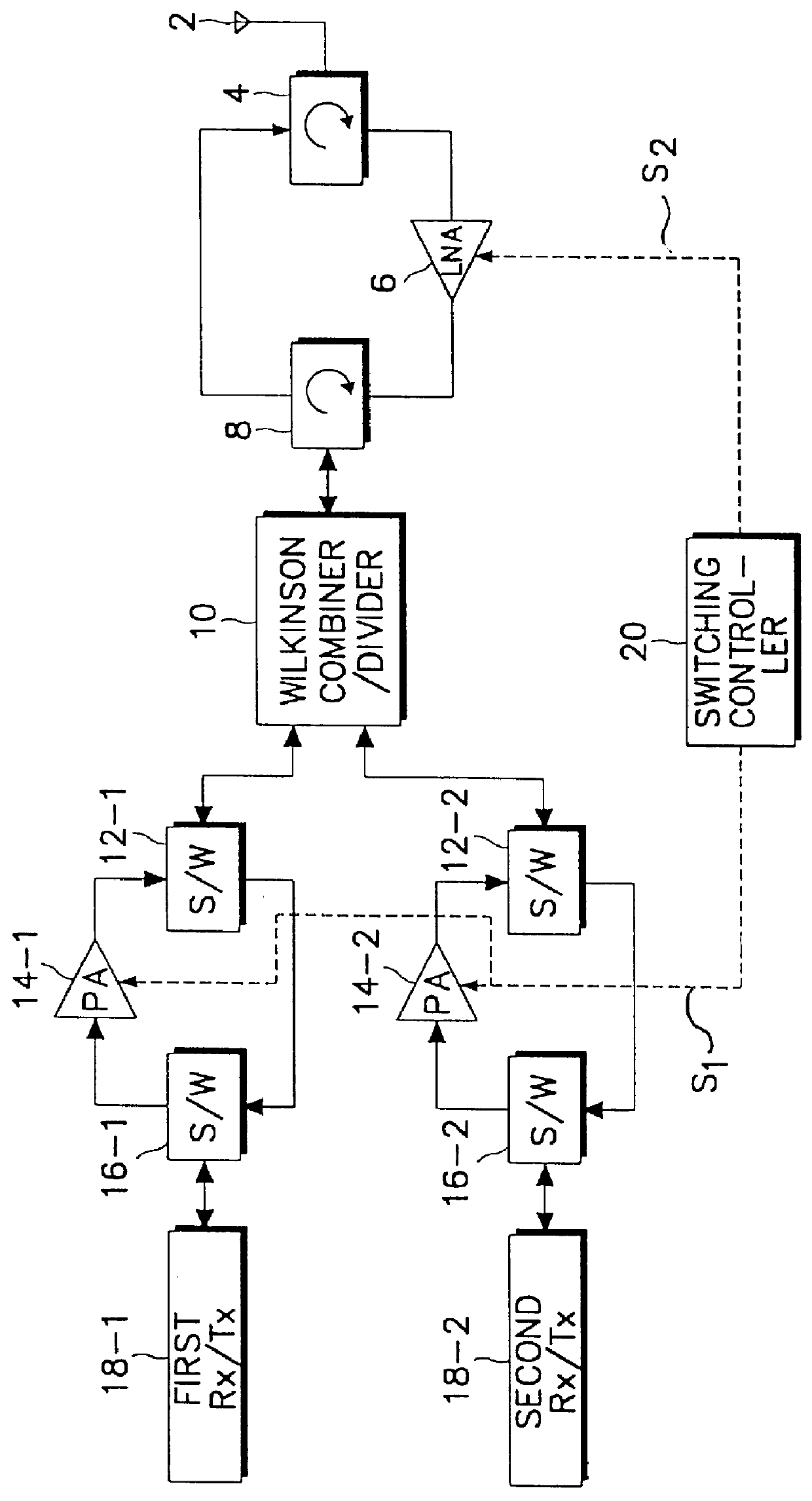

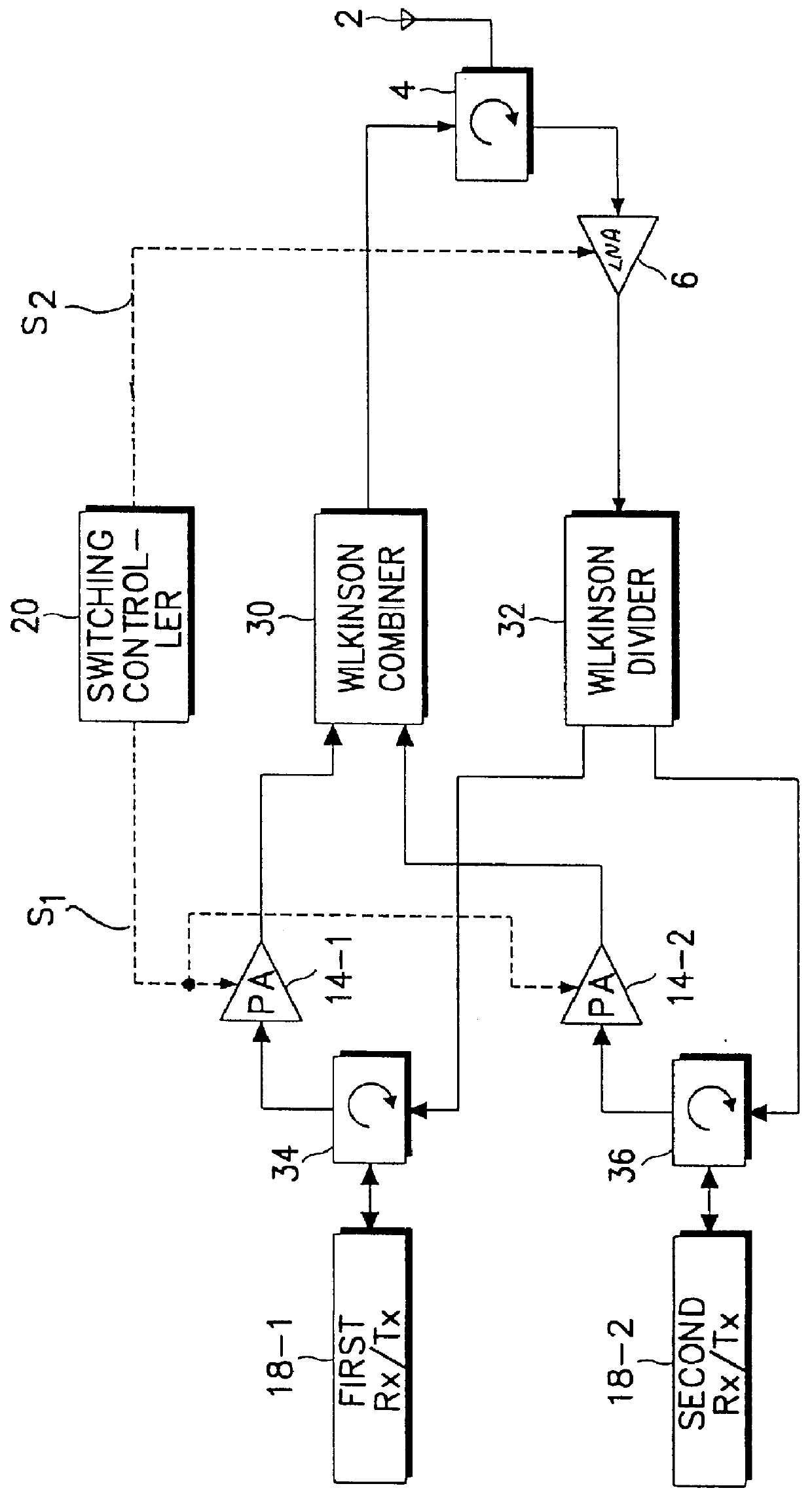

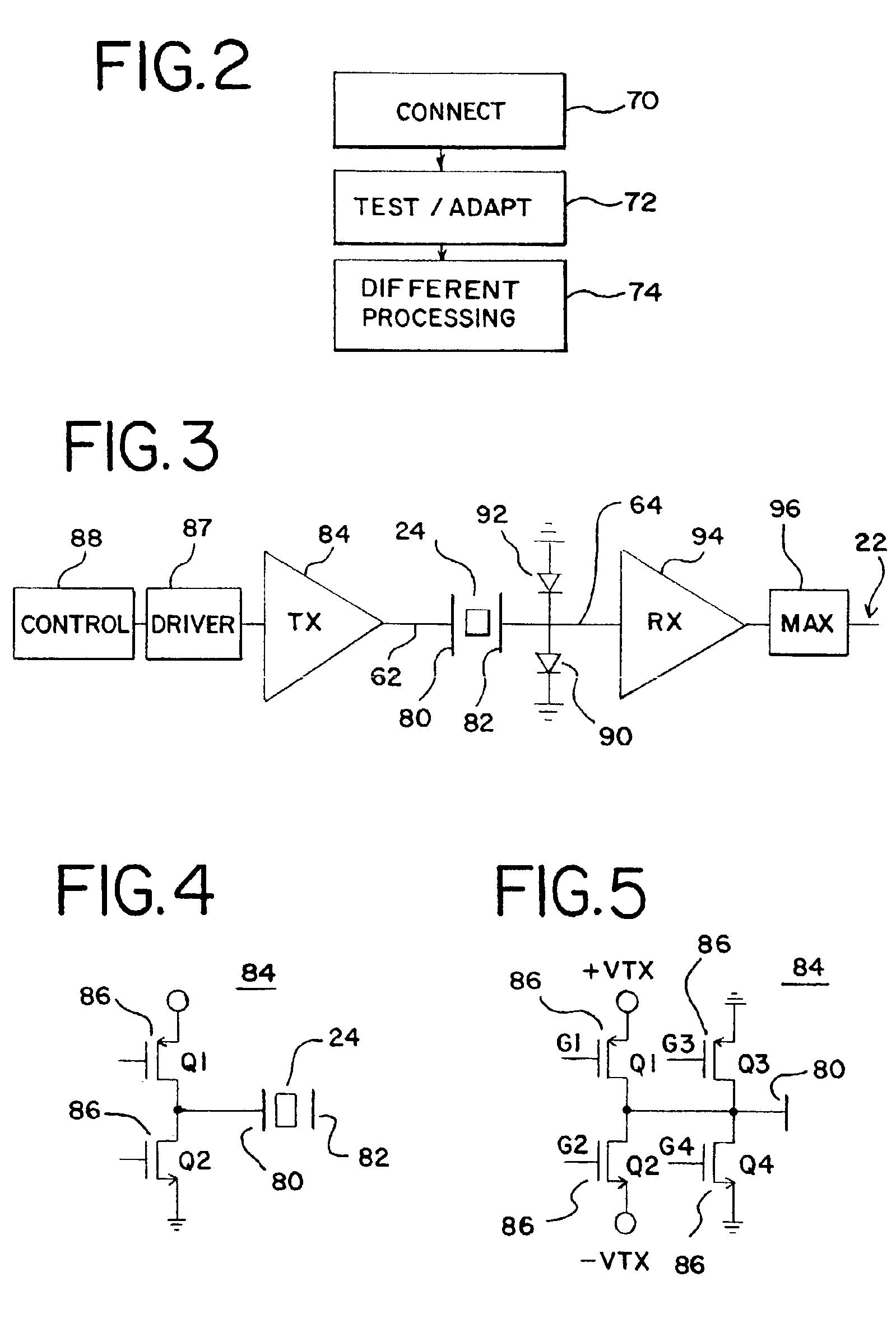

Transmitter/receiver for use in multichannel time division duplexing system providing isolation between transmission channels and reception channels

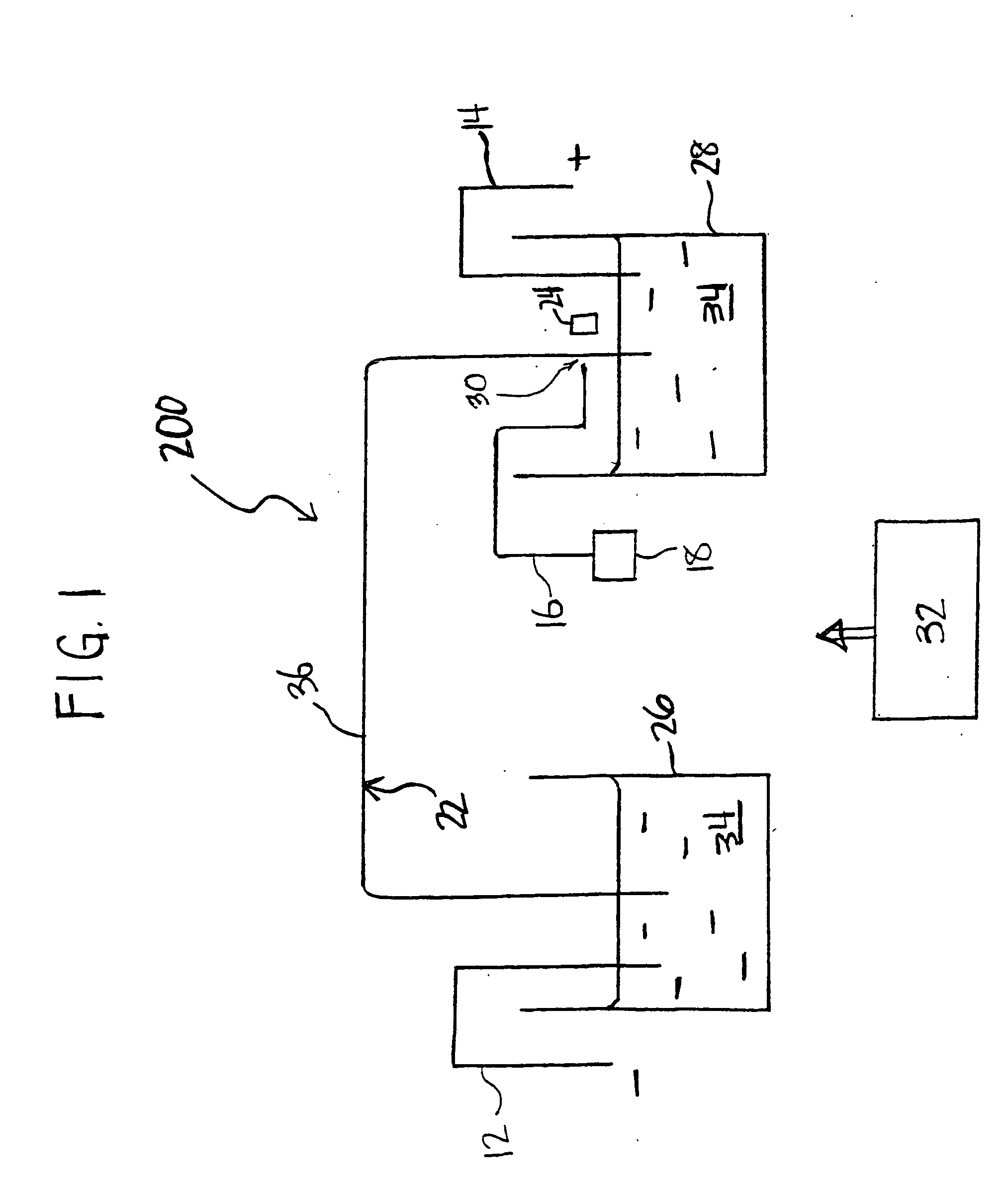

A transmitter / receiver for use in a multichannel time division duplexing system having an independent combiner and divider to isolate a transmission channel from a reception channel. The transmitter / receiver includes a first and second circulator connected, respectively, to a first and second transceiver. A transmission channel, formed between the first and second circulators and an antenna, transfers transmission signals from the first and second transceivers to the antenna in response to a transmission enable signal. A reception channel, formed between the first and second circulators and the antenna, transfers a reception signal from the antenna to the first and second transceiver in response to a reception enable signal. A switching control circuit is provided for generating the transmission enable signal during a transmission mode of operation and for generating the reception enable signal during a reception mode of operation.

Owner:SAMSUNG ELECTRONICS CO LTD

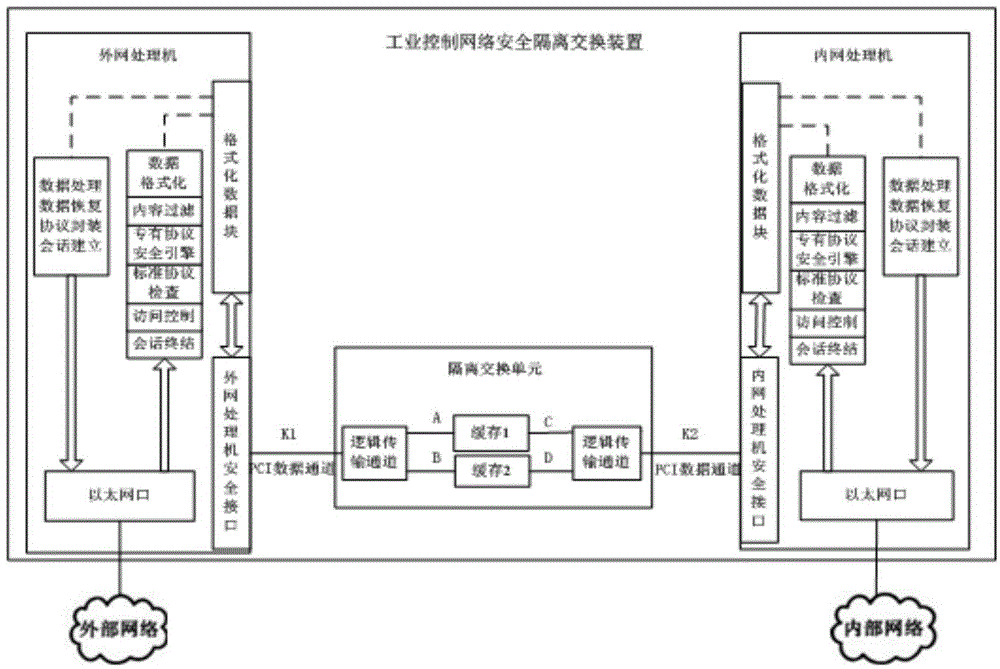

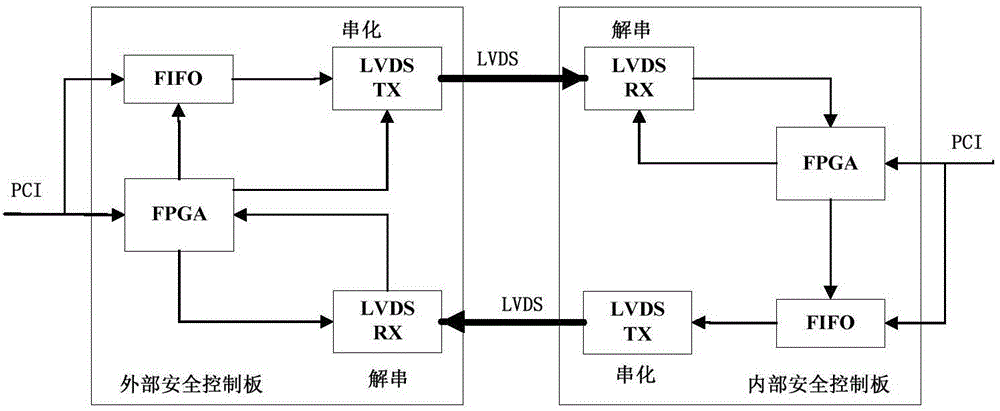

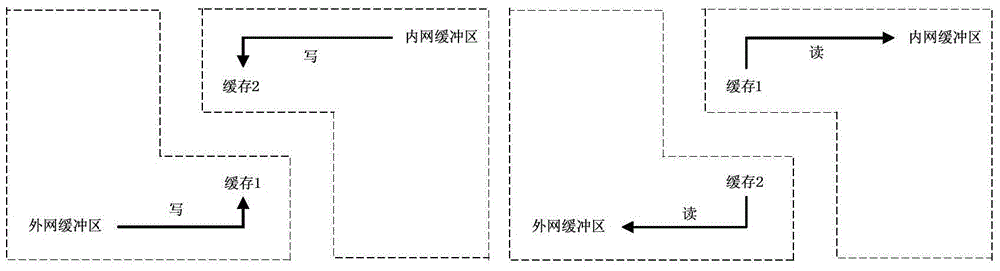

Device for safely isolating and exchanging industrial control networks

InactiveCN104486336ALow costReduce complexityTransmissionStructure of Management InformationBidirectional transmission

The invention discloses a device for safely isolating and exchanging industrial control networks and belongs to the technical field of security of the industrial control networks. A '2+1' structure system is adopted; the device comprises an external network processor, an internal network processor and an isolating and exchanging unit, wherein the isolating and exchanging unit is of a two-channel structure based on a bus and is connected with the external network processor and the internal network processor by virtue of an PCI bus. According to the device, the bus-based two-channel isolation control technology is used for opening and closing two channels in real time; bidirectional data transmission of the internal network and the external network is converted to two unidirectional data transmissions; the safe isolation of the internal network and the external network is ensured from hardware and software; many security problems in the bidirectional transmission of the same system in the conventional security technology are solved; meanwhile, the hardware cost and the complexity are reduced; the system reliability and the data exchange rate can be increased; the switching time is shortened.

Owner:AUTOMATION RES & DESIGN INST OF METALLURGICAL IND

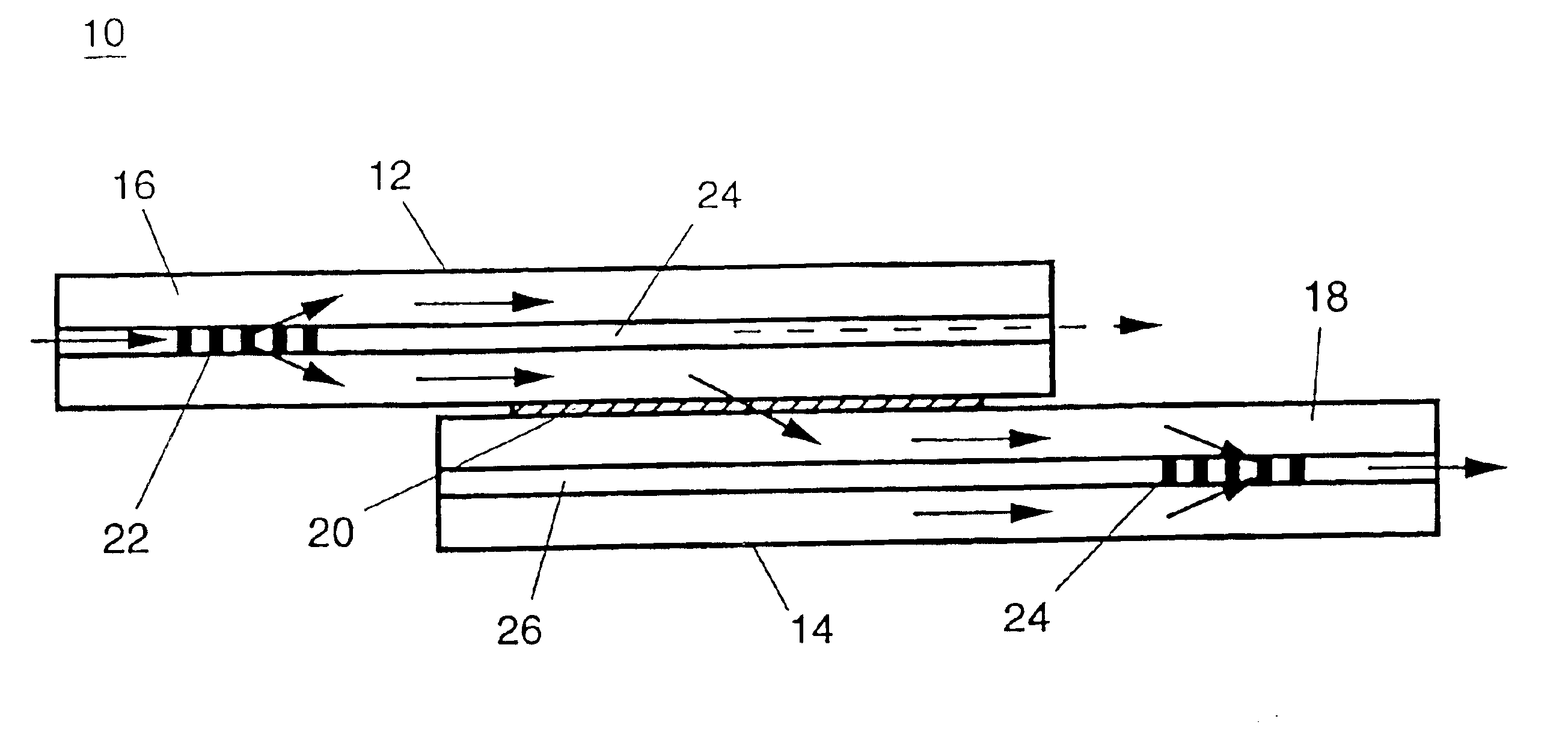

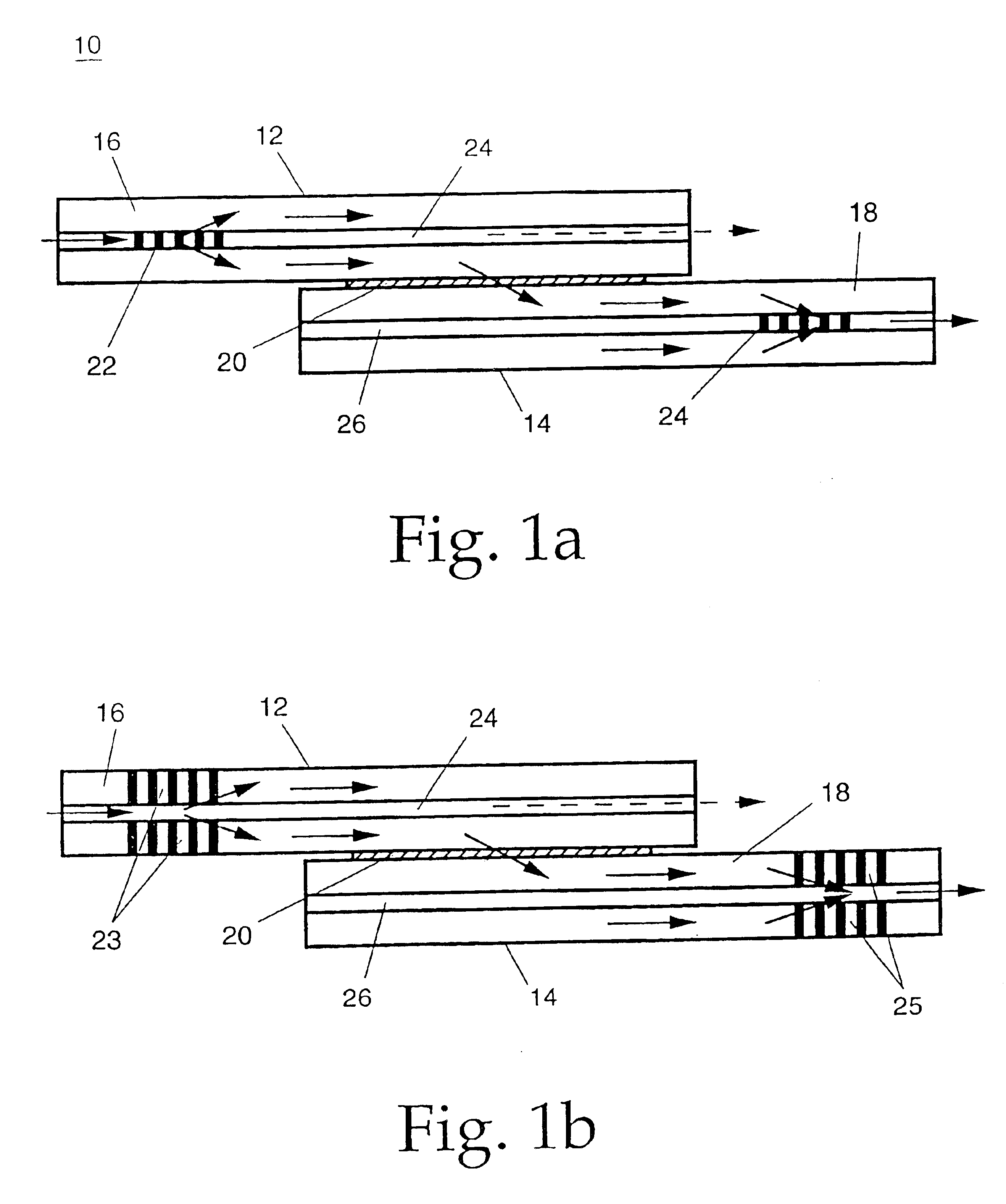

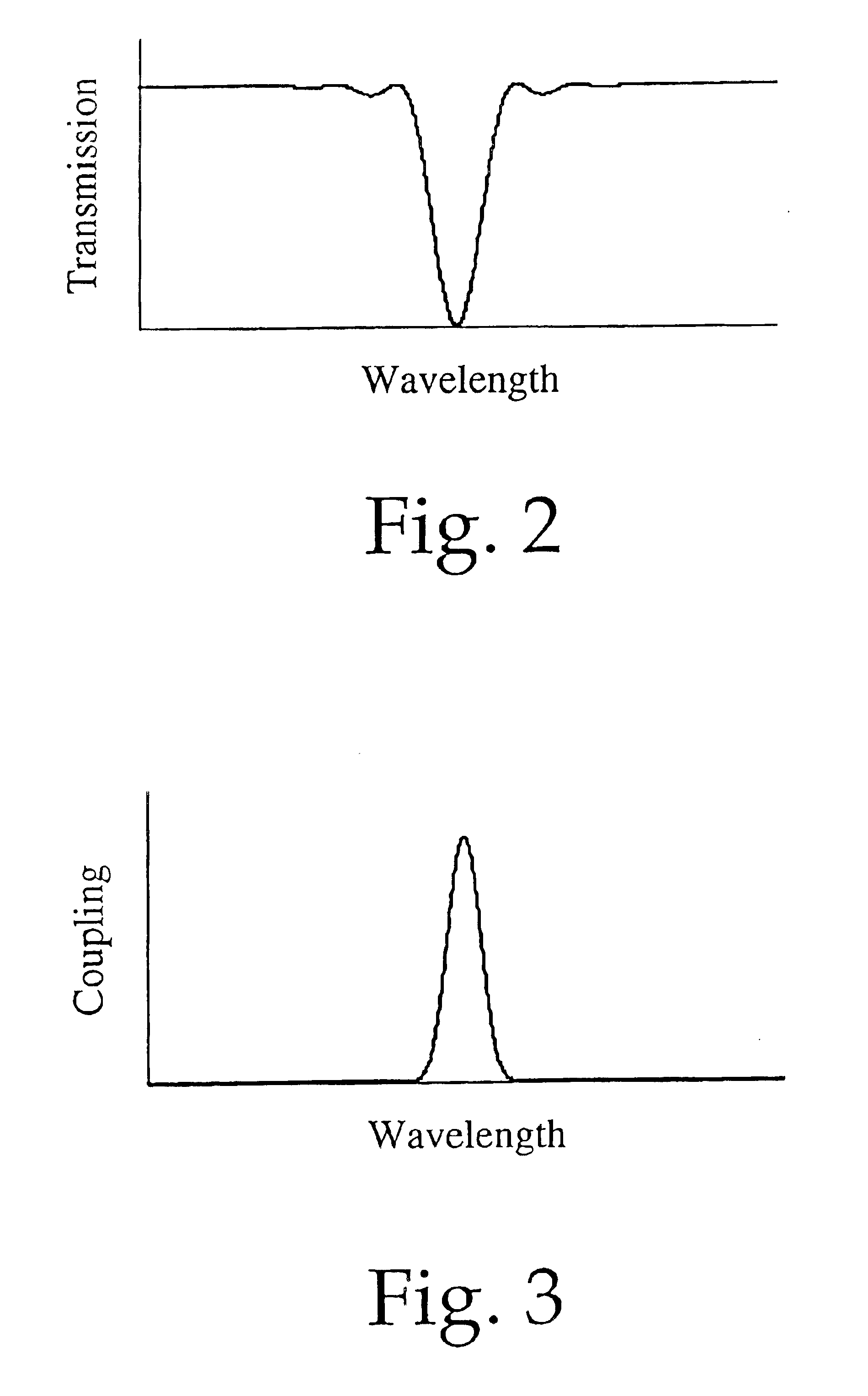

Wavelength-selective optical fiber components using cladding-mode assisted coupling

InactiveUS6850665B2High isolation between channelsIncrease light intensityWavelength-division multiplex systemsCoupling light guidesFiberGrating

A wavelength-selective optical device for coupling of light at predetermined wavelength from one optical fiber waveguide to another using at least two gratings and cladding-mode assisted coupling is disclosed. The transfer of light is performed using intermediate coupling to one or more cladding mode of the waveguides. In the case when the fibers have physically different cladding's, an arrangement for transfer of light from one cladding to another is required. The disclosed coupler has no back-reflection, small insertion loss, and very high channel isolation. The device can be used in wavelength-division multiplexing networks.

Owner:MURATA MFG CO LTD +1

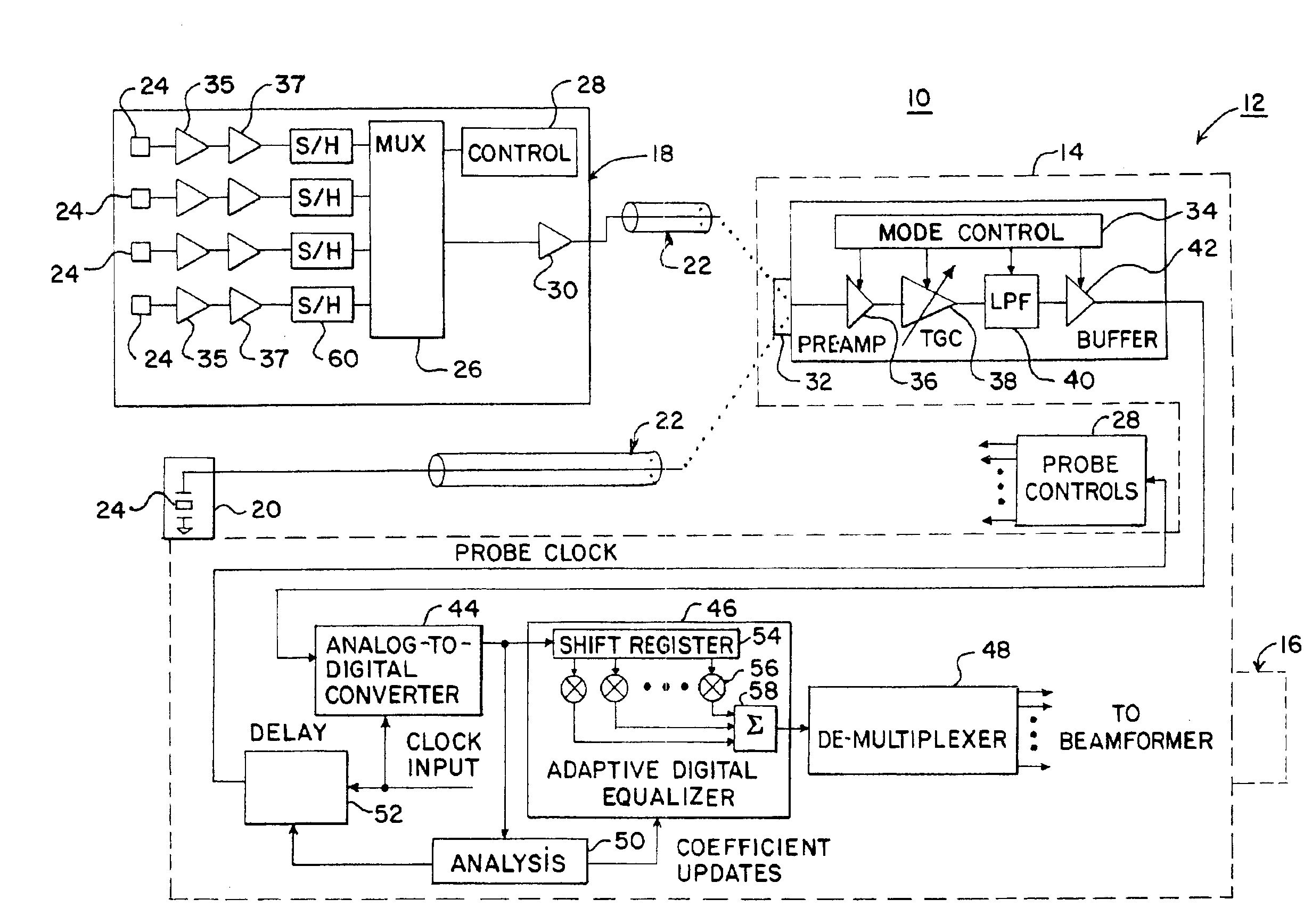

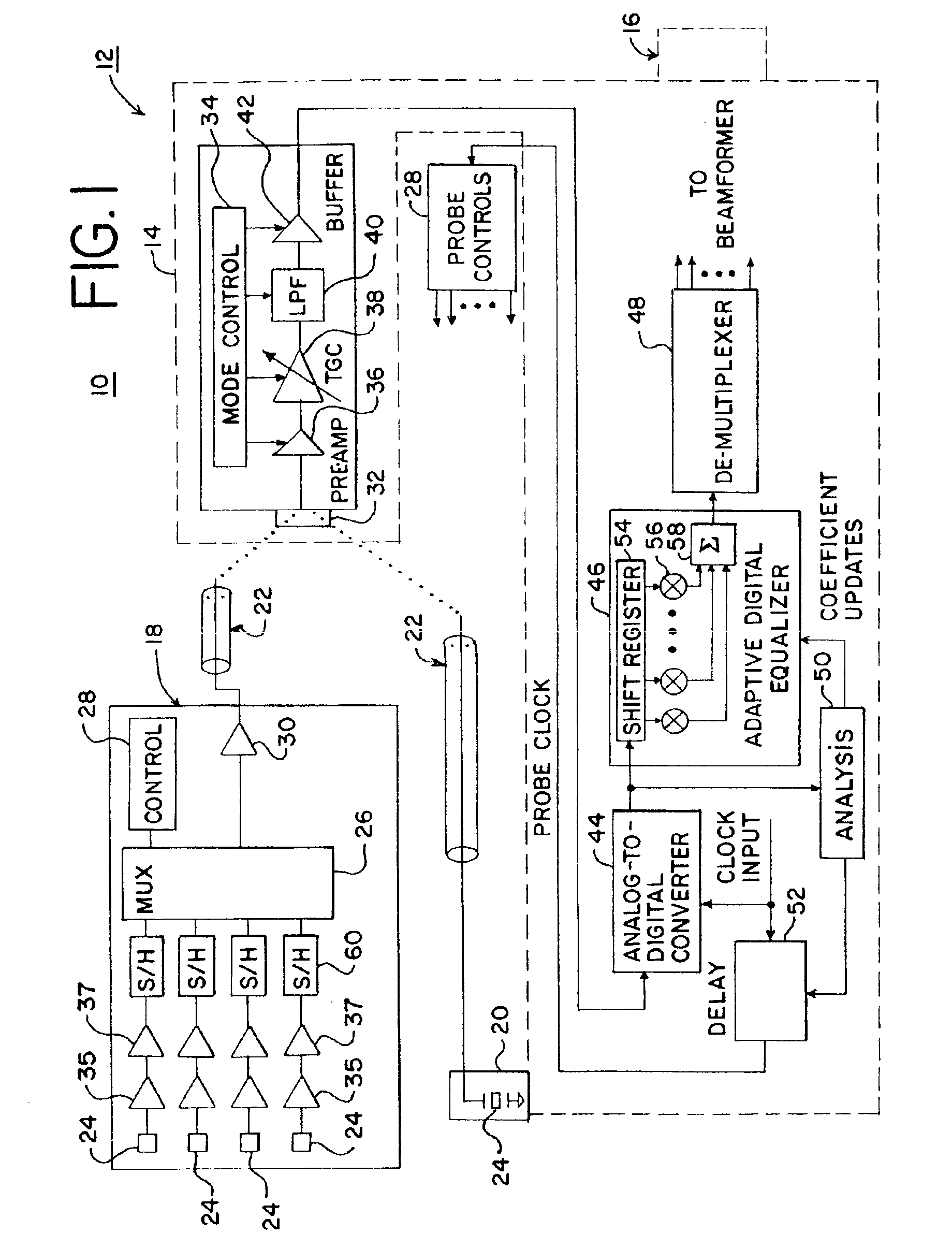

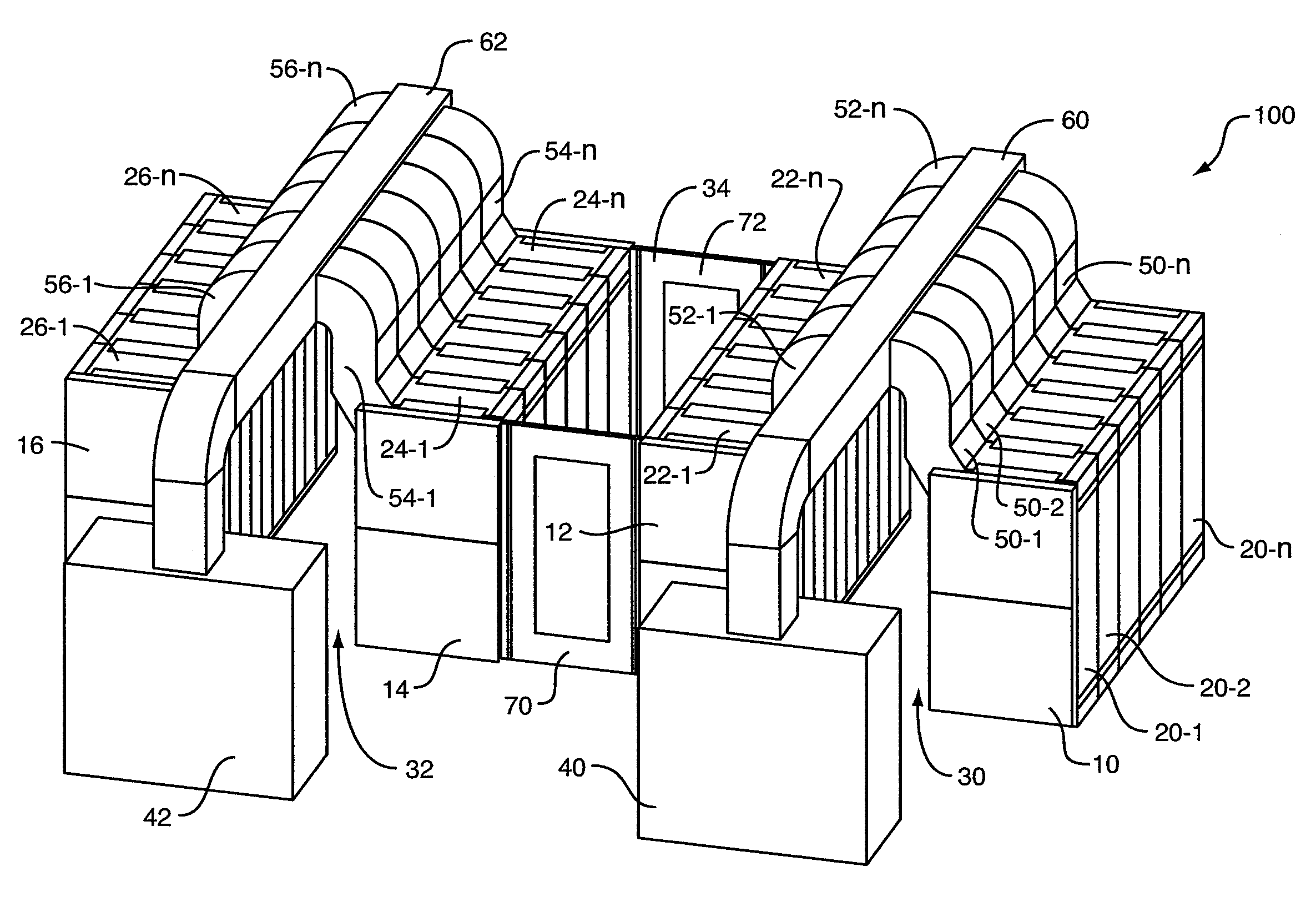

Multi-dimensional transducer arrays and method of manufacture

A multi-dimensional transducer array has pitch along one dimension less than the pitch along a second dimension. The multi-dimensional transducer array with the same or different pitch is manufactured from a plurality of modules. Each of the modules are separately diced and then aligned and combined. Elements of a transducer array are used for isolating a transmit channel from a receive channel. Separate signal lines or traces are provided individually for each element on opposite sides of each element. A transmit channel may connect to one electrode on an element, and the receive channel may connect to an opposite electrode on the element. A multi-dimensional array is provided for time division multiplex processing. A probe houses the multi-dimensional array and a multiplexer.

Owner:SIEMENS MEDICAL SOLUTIONS USA INC

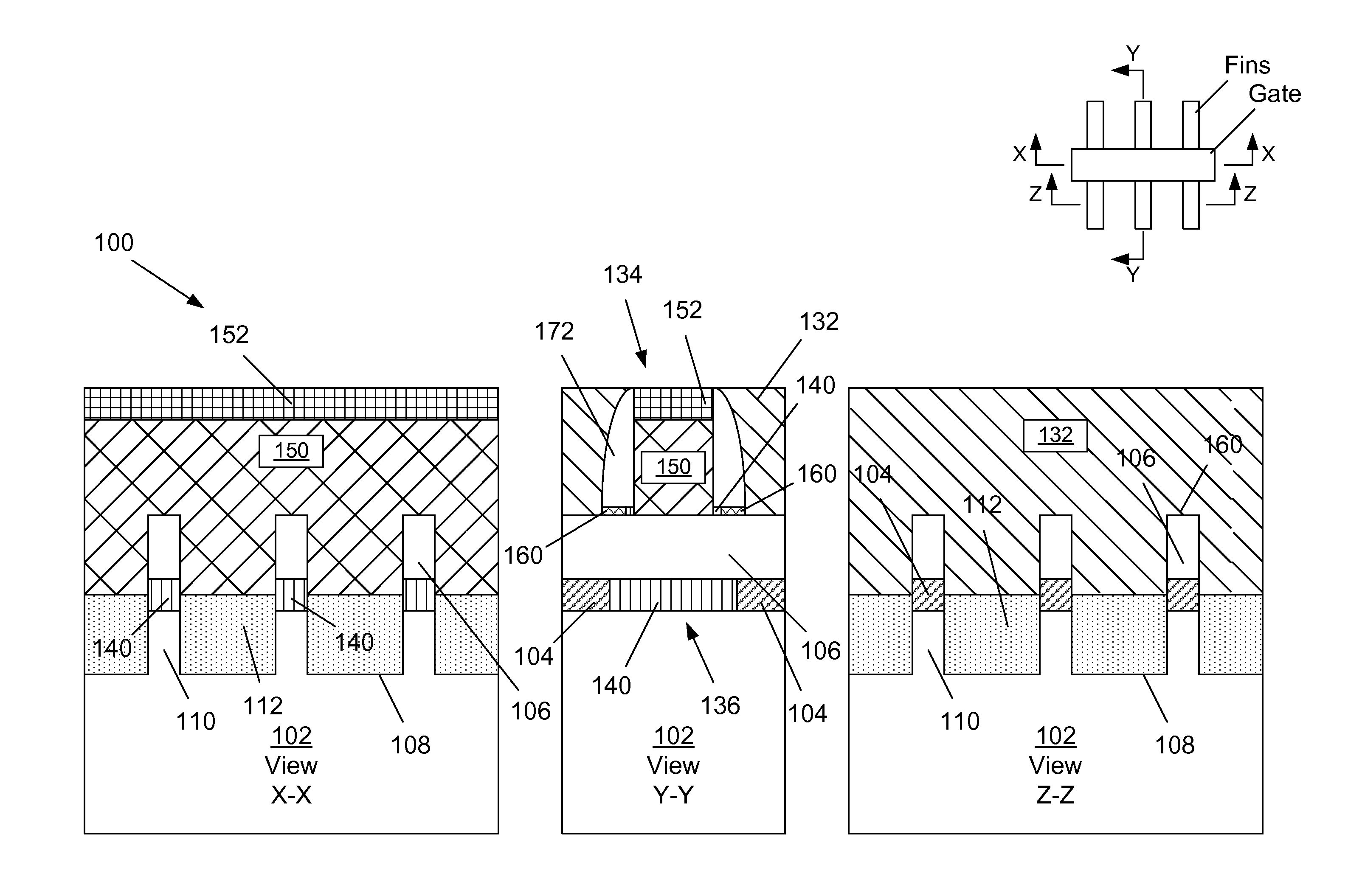

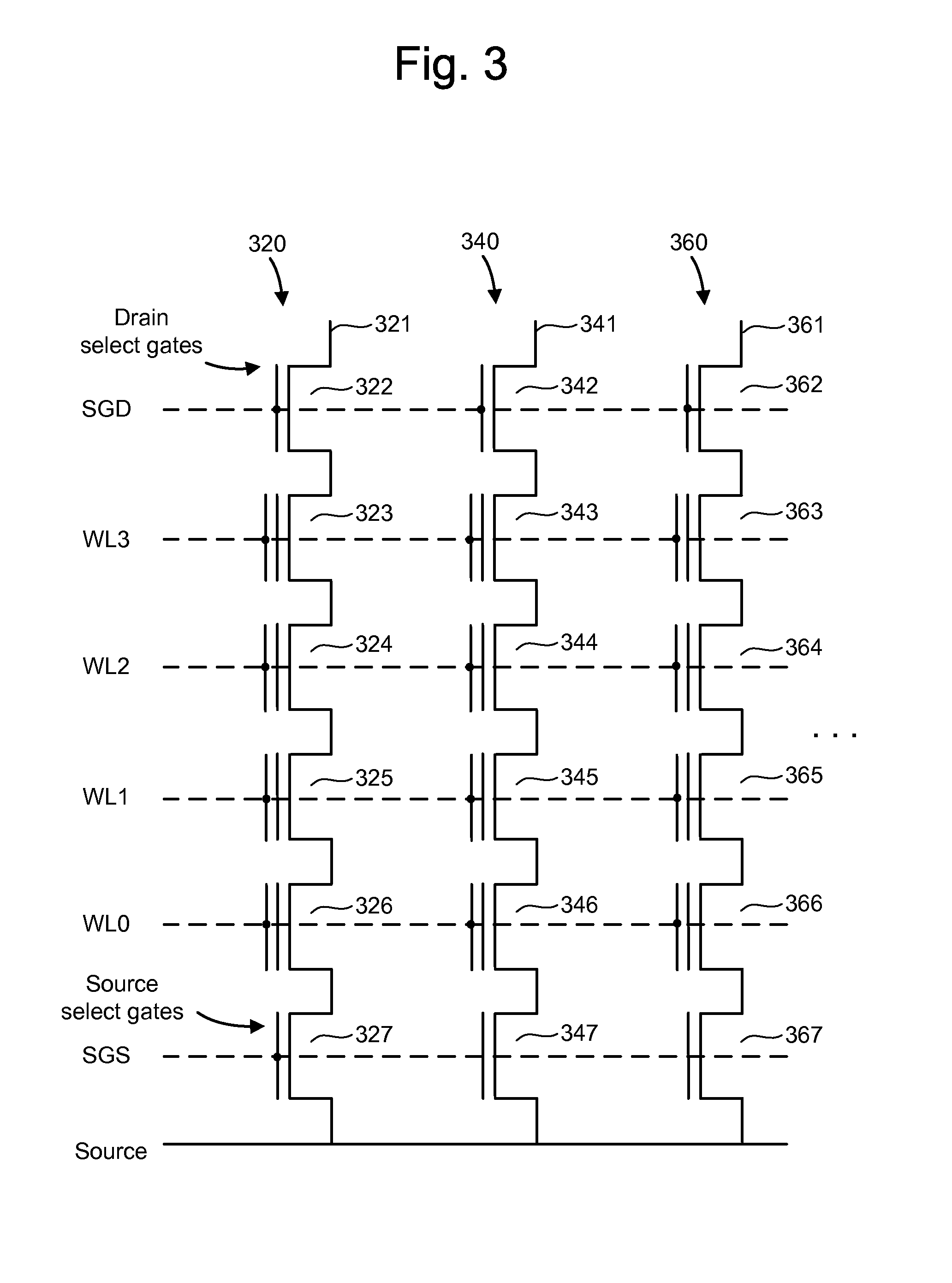

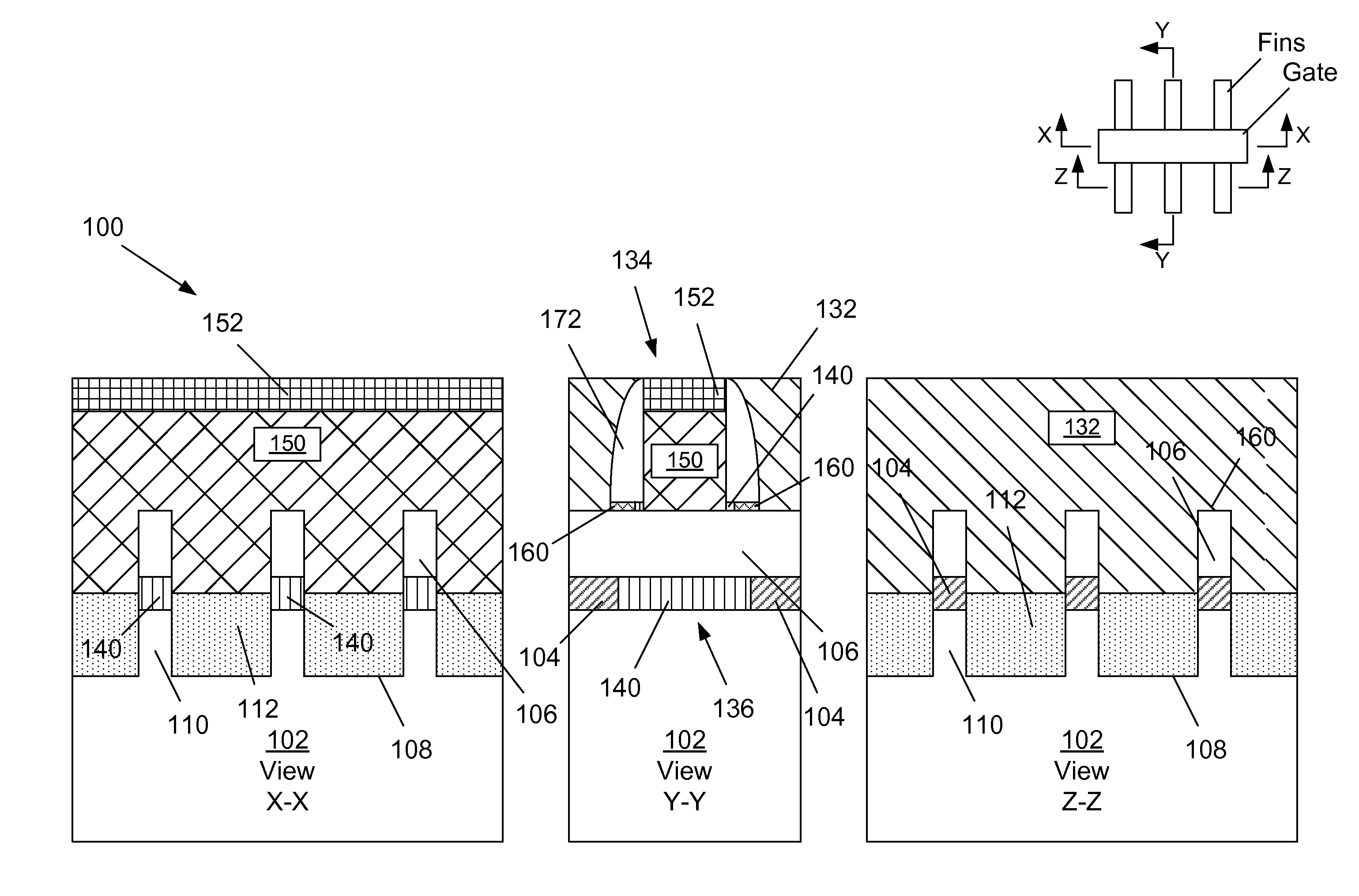

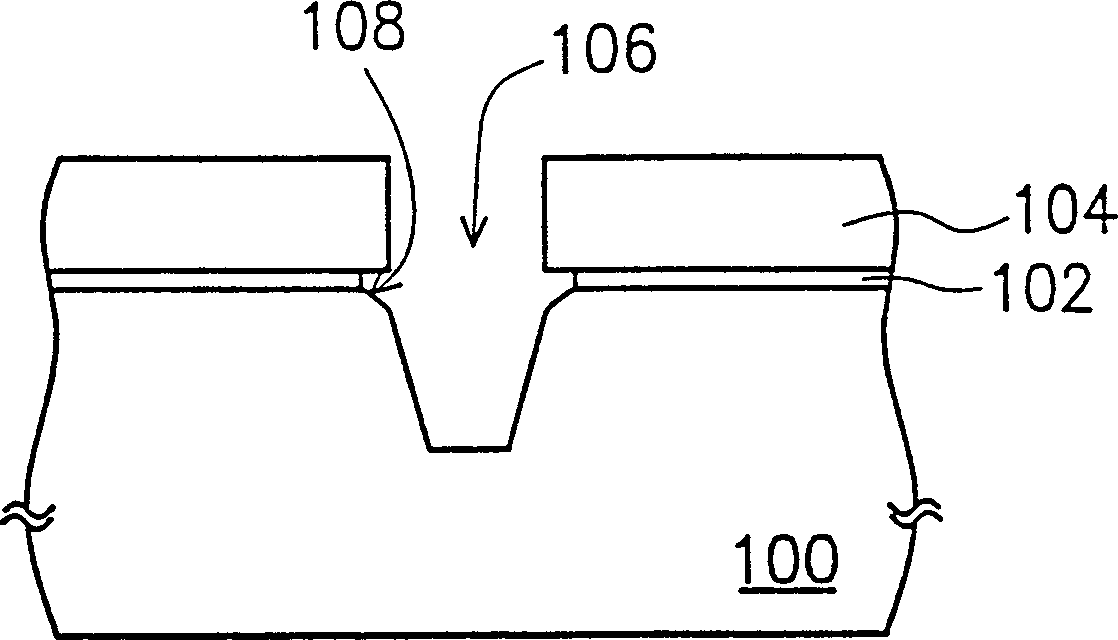

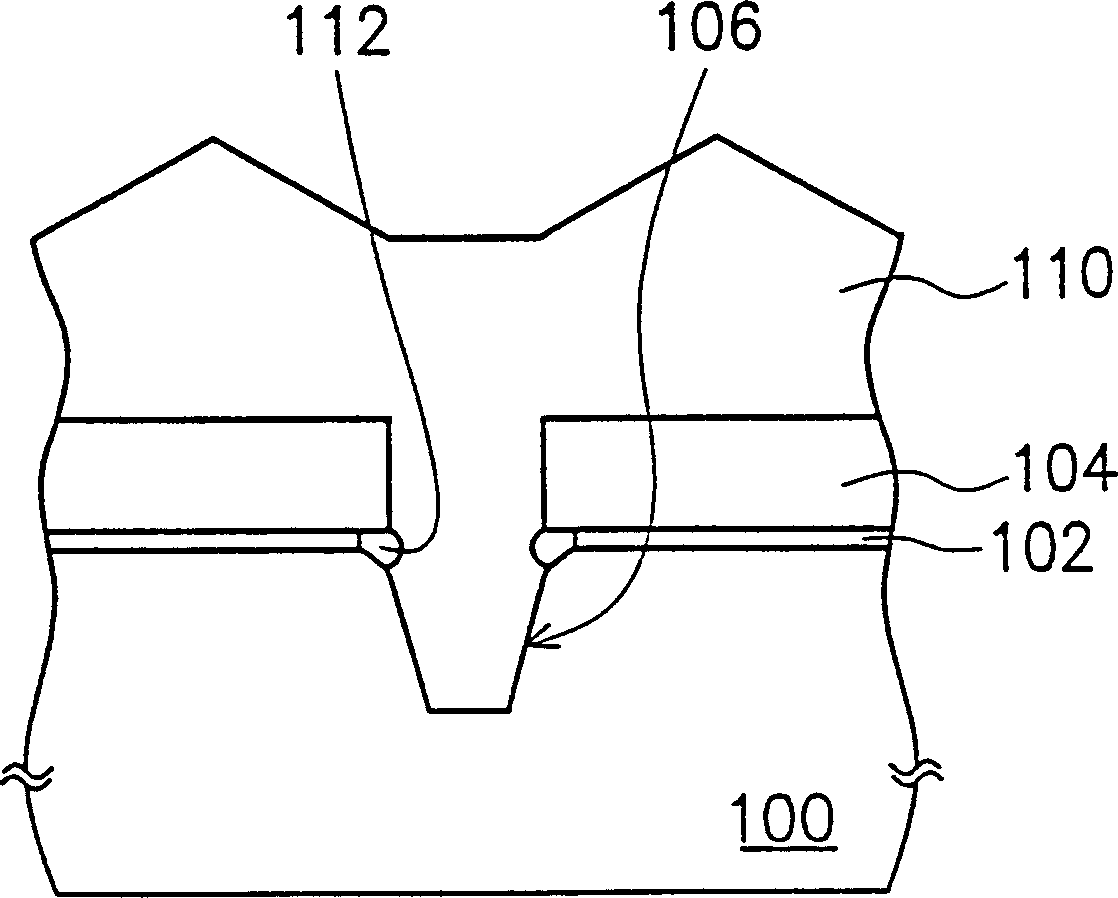

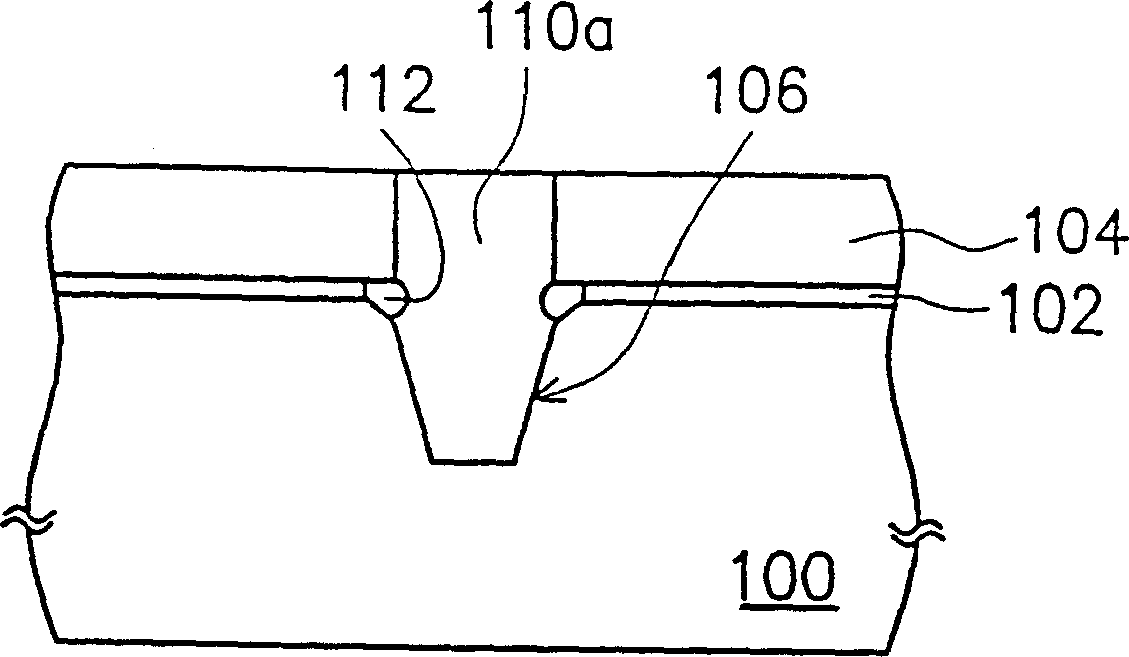

Methods of forming substantially self-aligned isolation regions on finfet semiconductor devices and the resulting devices

One method disclosed includes performing a selective etching process through a gate cavity to selectively remove a portion of a first semiconductor material relative to a second layer of a second semiconductor material and a substrate so as to thereby define a space between the second semiconducting material and the substrate, filling substantially all of the space with an insulating material so as to thereby define a substantially self-aligned channel isolation region positioned under at least what will become the channel region of the FinFET device.

Owner:GLOBALFOUNDRIES INC

Cold aisle isolation

ActiveUS20090107652A1Easy to modifyLarge capacityDigital data processing detailsElectrical apparatus contructional detailsAir cooling systemEngineering

A data center cooling solution providing techniques for using baffles, doors and roof sections to prevent warm air from being entrained into a cold aisle in a data center, wherein the data center generally contains an air cooling system and a raised floor structure. The raised floor structure is configured to deliver cool air into the data center through a plurality of grates and perforated tiles in the floor. Electronic equipment racks are disposed around the grates and perforated tiles, such that the front faces of the equipment racks face the grates and perforated tiles. A collection of baffles, doors or roof sections inhibit the mixing of the cool air delivered by the air cooling system and the warm air exhausted by the electronic equipment.

Owner:SCHNEIDER ELECTRIC IT CORP

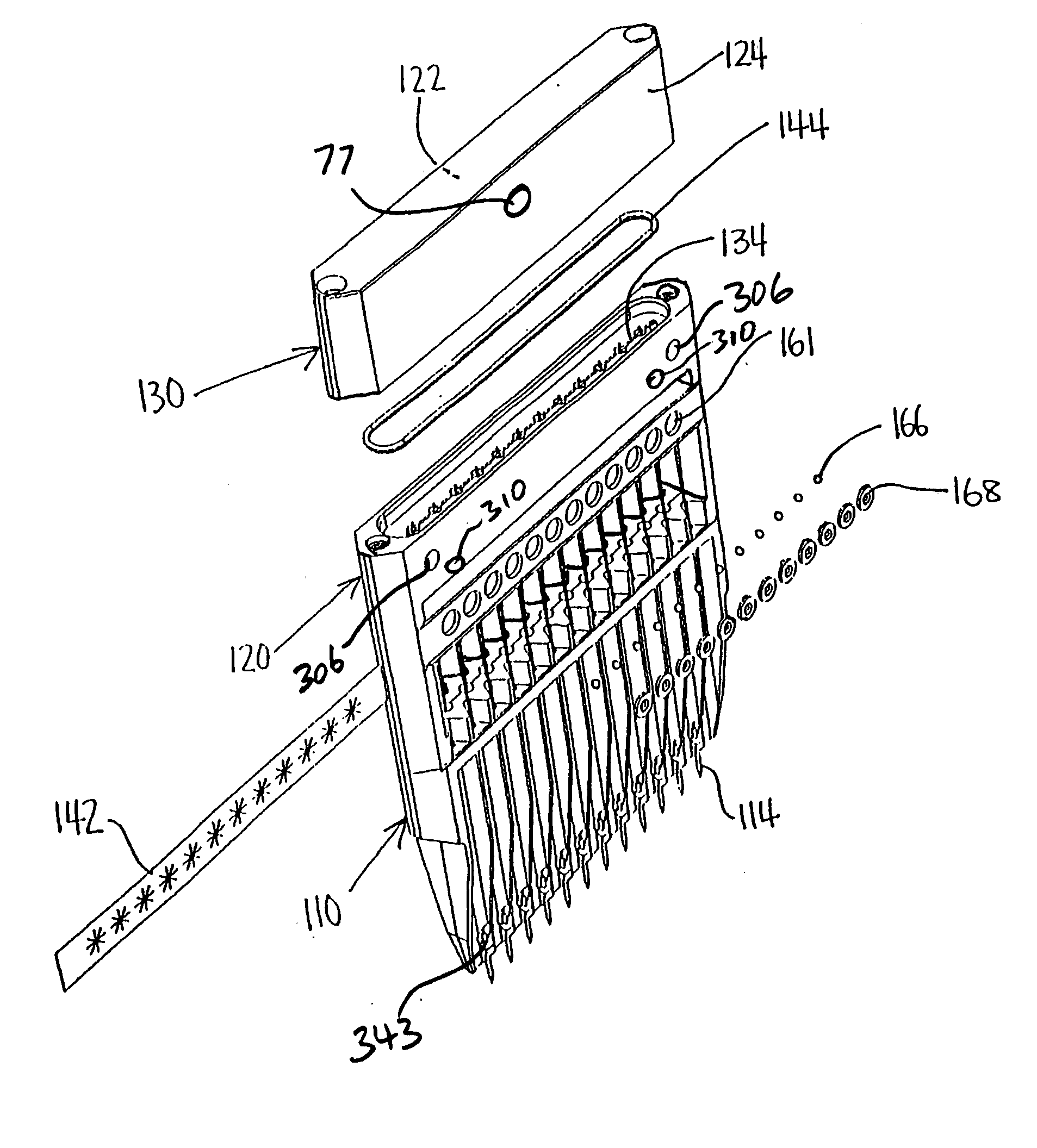

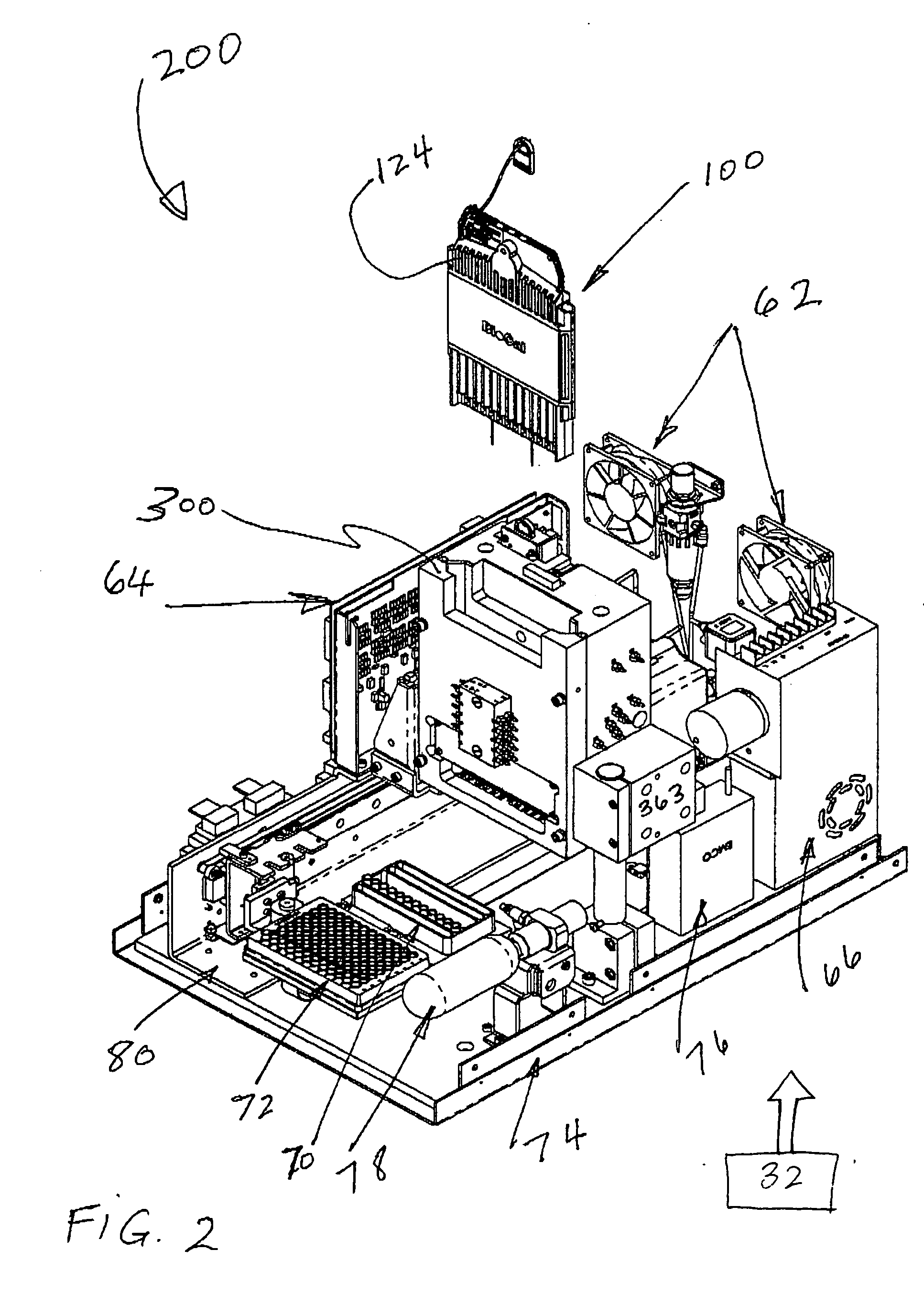

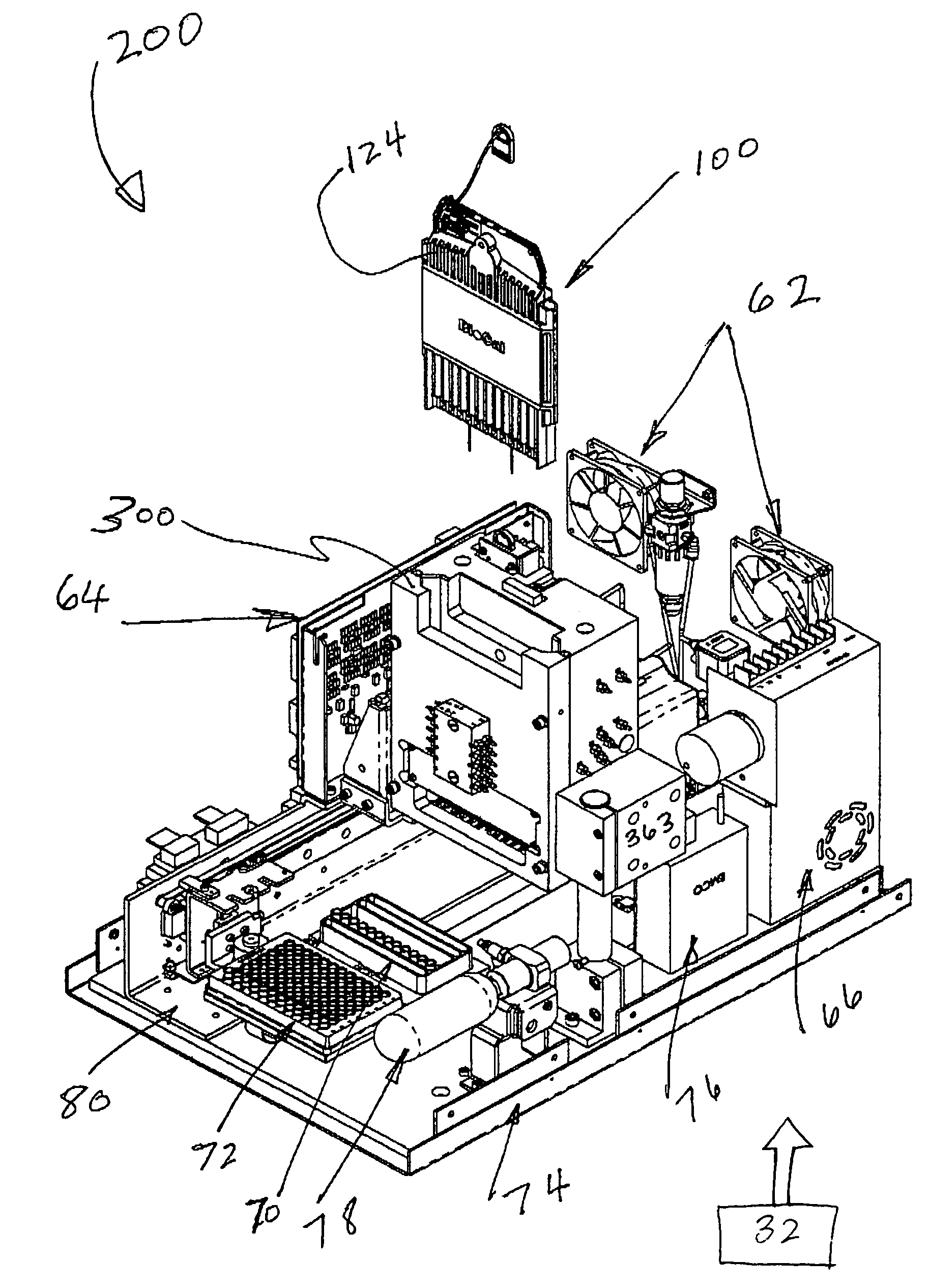

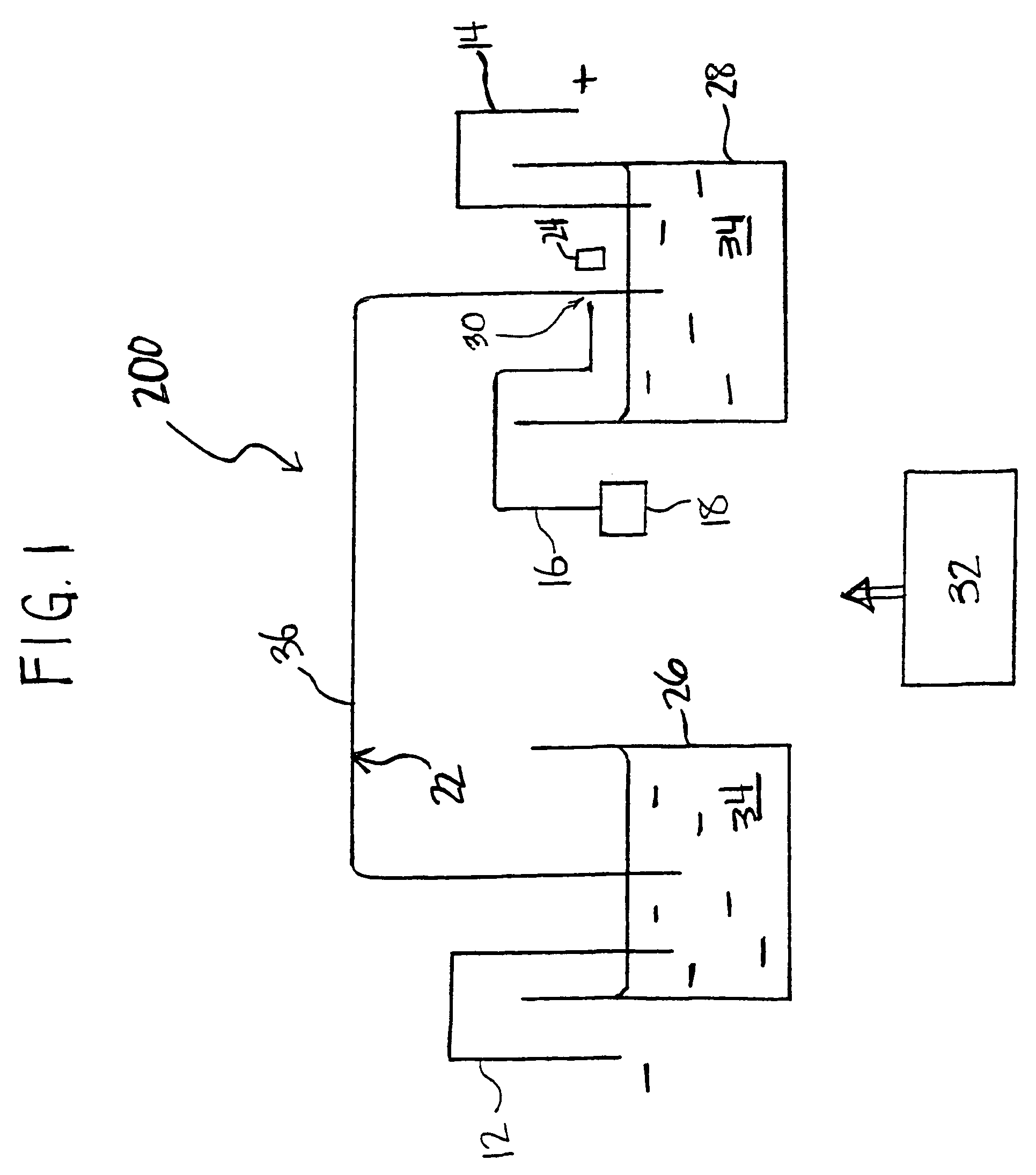

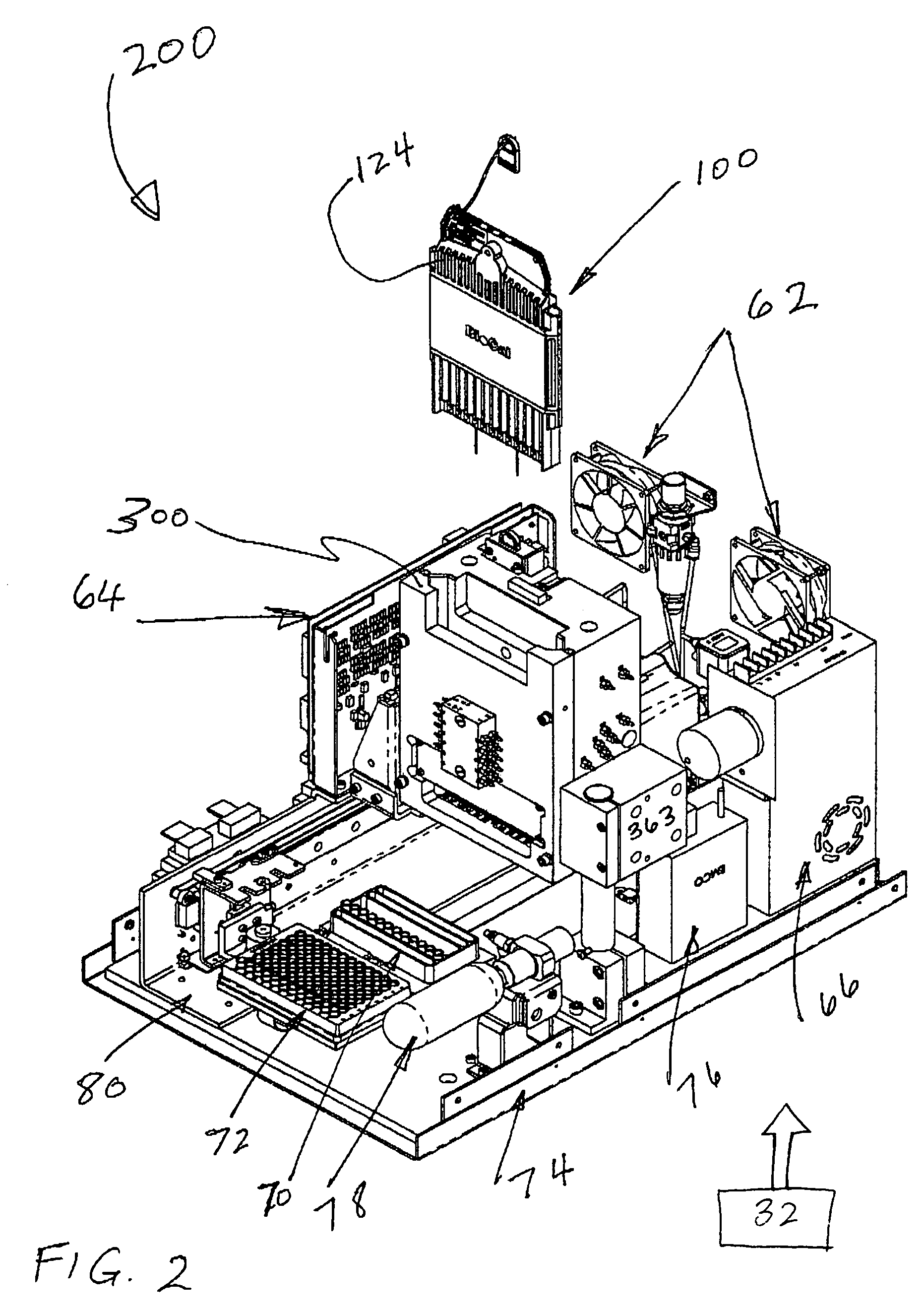

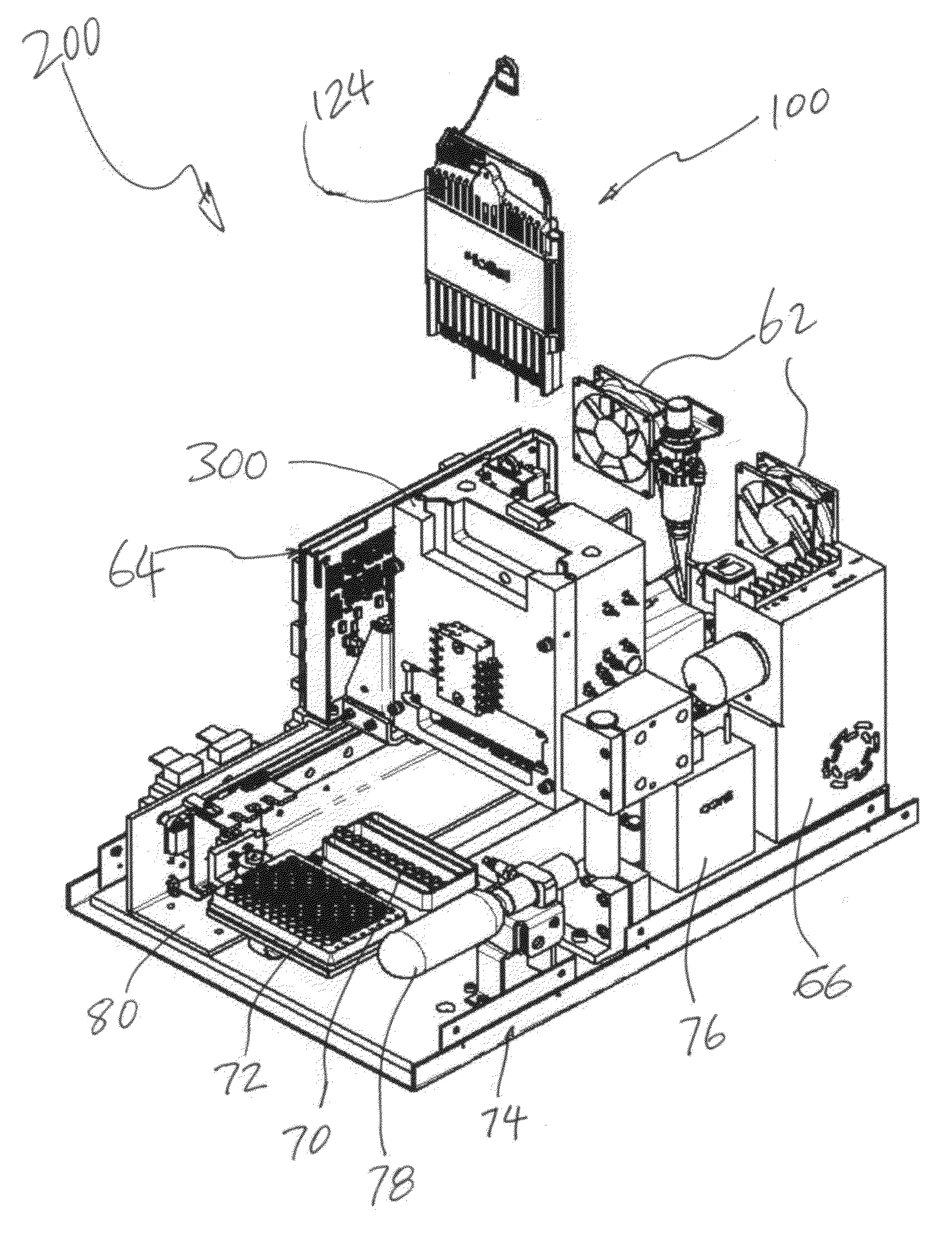

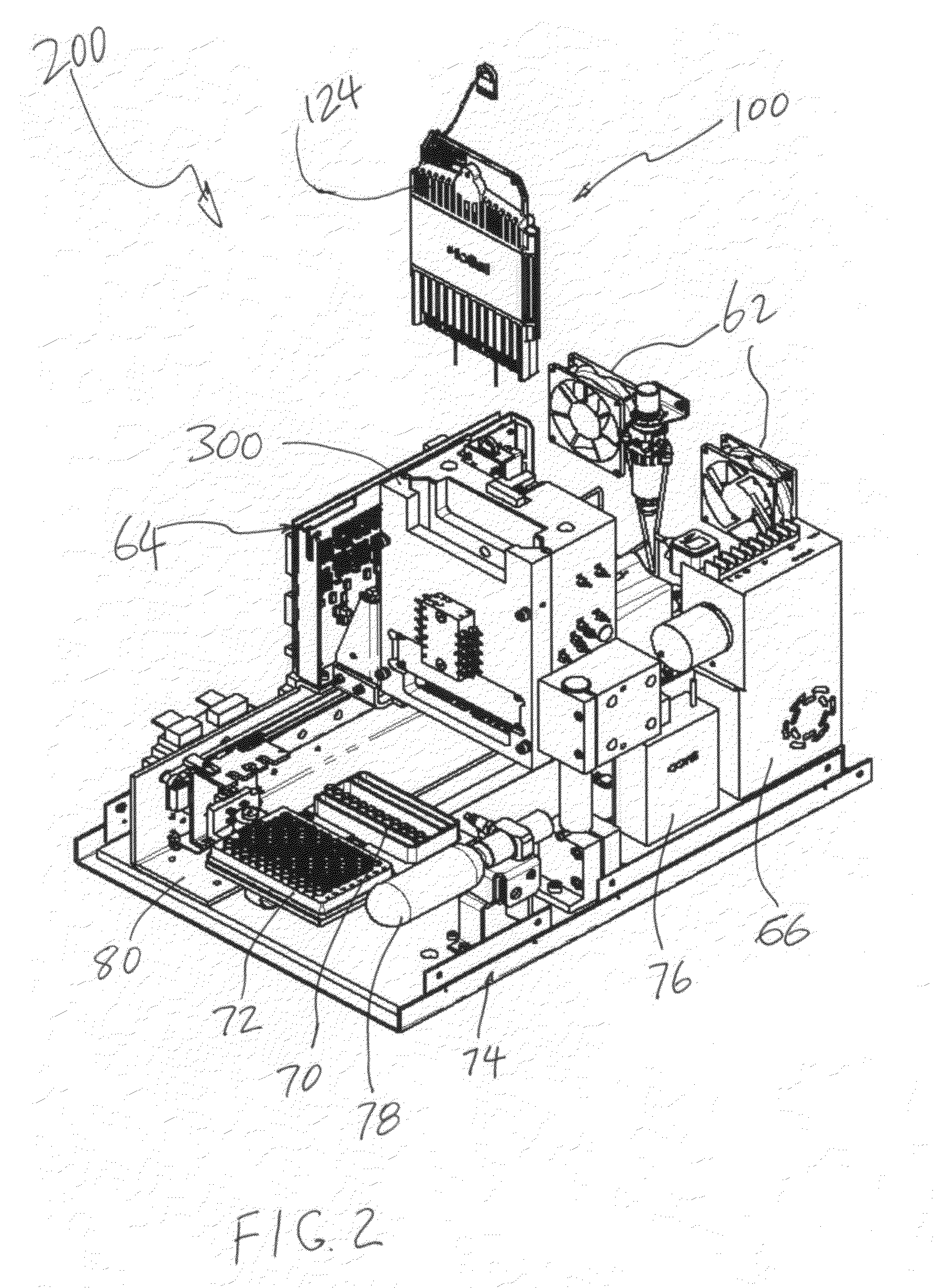

Multi-capillary electrophoresis cartridge interface mechanism

ActiveUS20050016852A1Precise positioningReliable implementationImmobilised enzymesBioreactor/fermenter combinationsCapillary electrophoresisMagnetic tape

The present invention provides for an interface mechanism in a bio-separation instrument that makes interface connections to a multi-channel cartridge. The interface mechanism precisely positions the cartridge in relation to the support elements in the instrument (e.g., high-voltage, gas pressure, incident radiation and detector), and makes automated, reliable and secured alignments and connections between various components in the cartridge and the support elements in the supporting instrument. The interface mechanism comprises pneumatically or electromechanically driven actuators for engaging support elements in the instrument to components on the cartridge. After the cartridge has been securely received by the interface mechanism, the connection sequence is initiated. The interface provides separate high voltage and optical connections for each separation channel in the cartridge, thus providing channel-to-channel isolation from cross talk both electrically and optically.

Owner:QIAGEN SCIENCES LLC

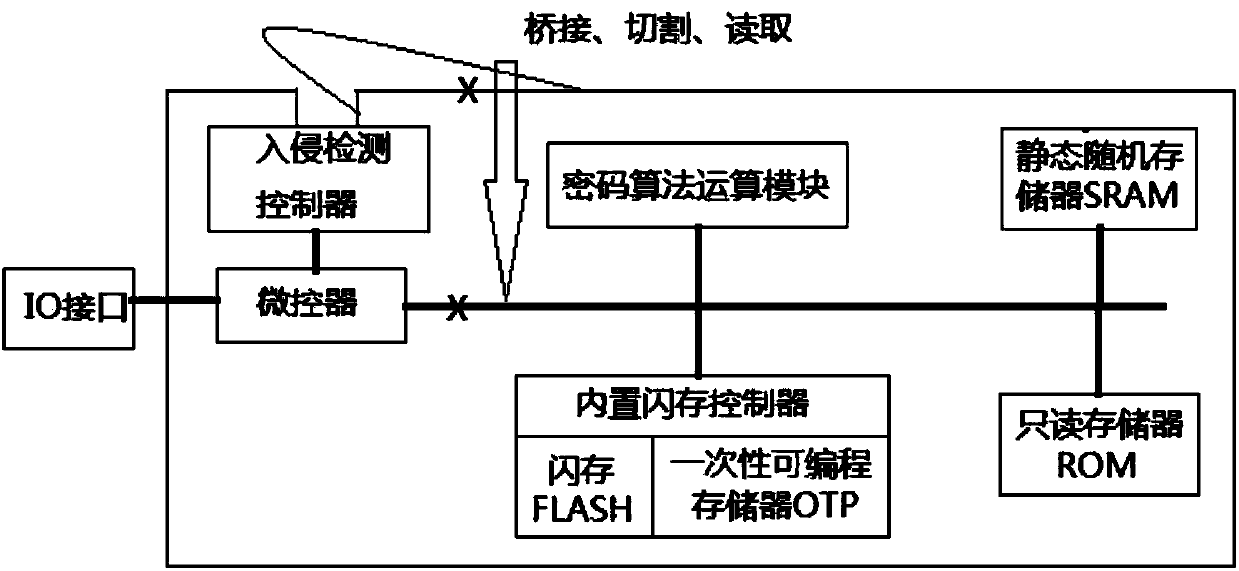

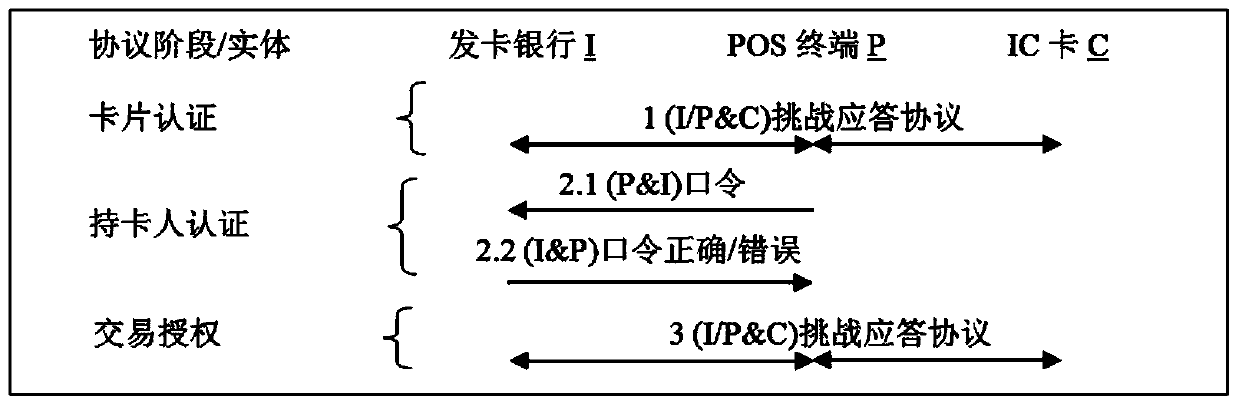

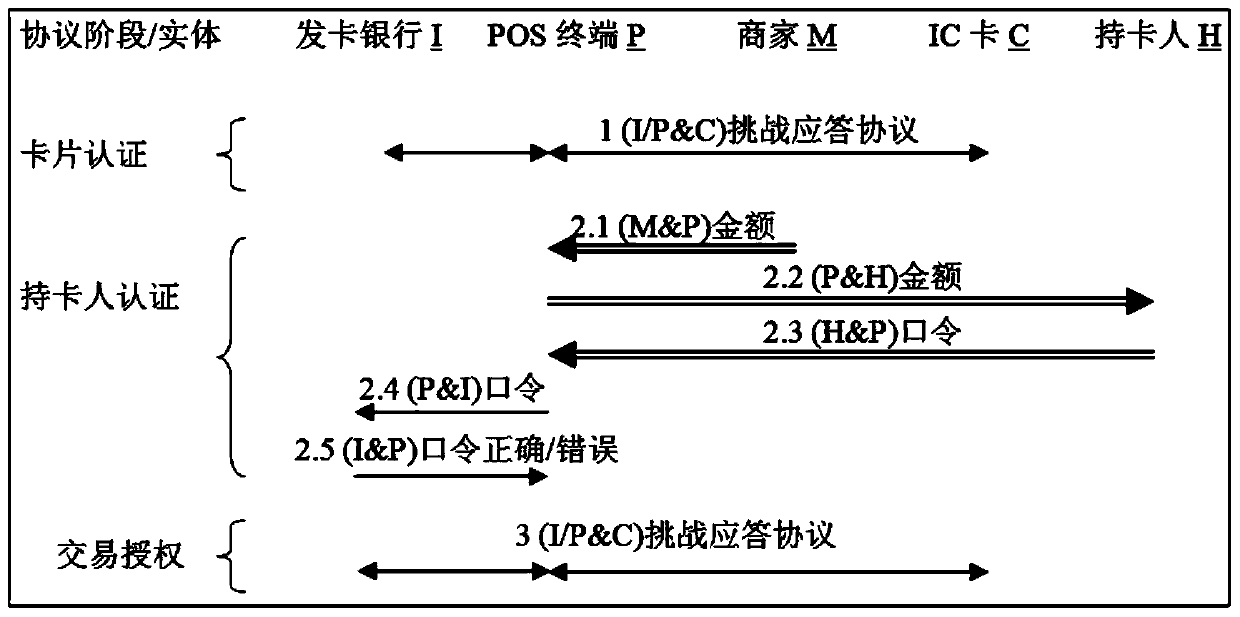

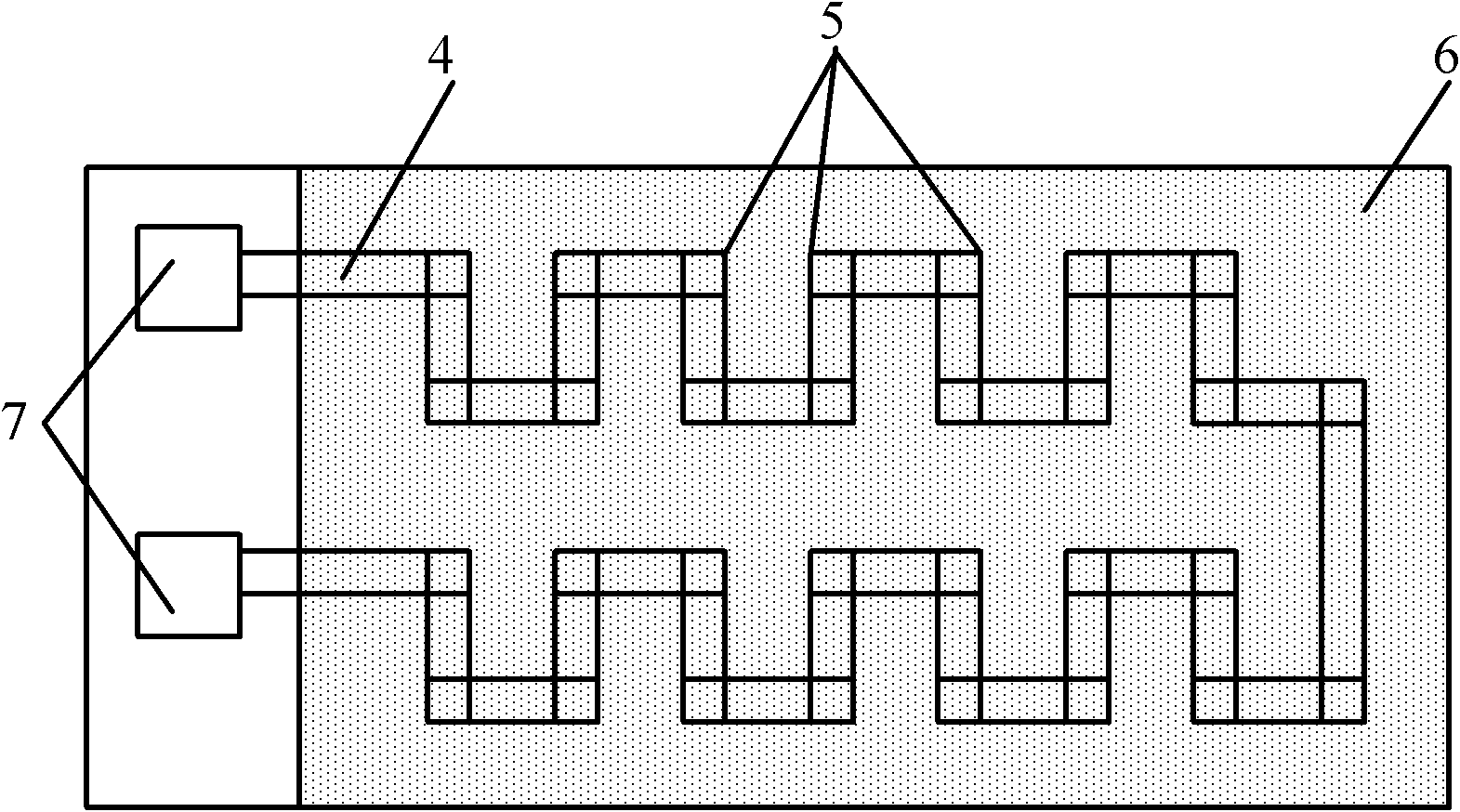

Trusted terminal, double-channel card, anti-cloning chip, chip fingerprint and channel attack resistance method

InactiveCN103778374ANon-clonableImprove securityCash registersPayment architectureCommunication interfacePayment

The invention discloses a trusted terminal, a double-channel card, an anti-cloning chip, a chip fingerprint and a channel attack resistance method. The trusted terminal comprises a main control chip, a double-channel card slot, a channel isolation part and a communication interface; the double-channel card slot comprises a first channel connector and a second channel connector; the first channel connector is connected with the main control chip; the second channel connector is connected with the channel isolation part; the double-channel card slot is used for enabling the double-channel card to be inserted in. The trusted terminal and the double-channel card which are disclosed by the invention can replace an existing IC (Integrated Circuit) card to carry out migration and have the advantages of high safety, strong universality, low cost, easiness for implementation and the like. The key points for high safety are as follows: the existing bank IC card is easy to clone so as to easily generate the undistinguishable condition, and a payment password of the existing bank IC card is easy to intercept and capture; the double-channel card cannot be cloned, can avoid the undistinguishable condition and can effectively protect safety of the payment password.

Owner:邹候文

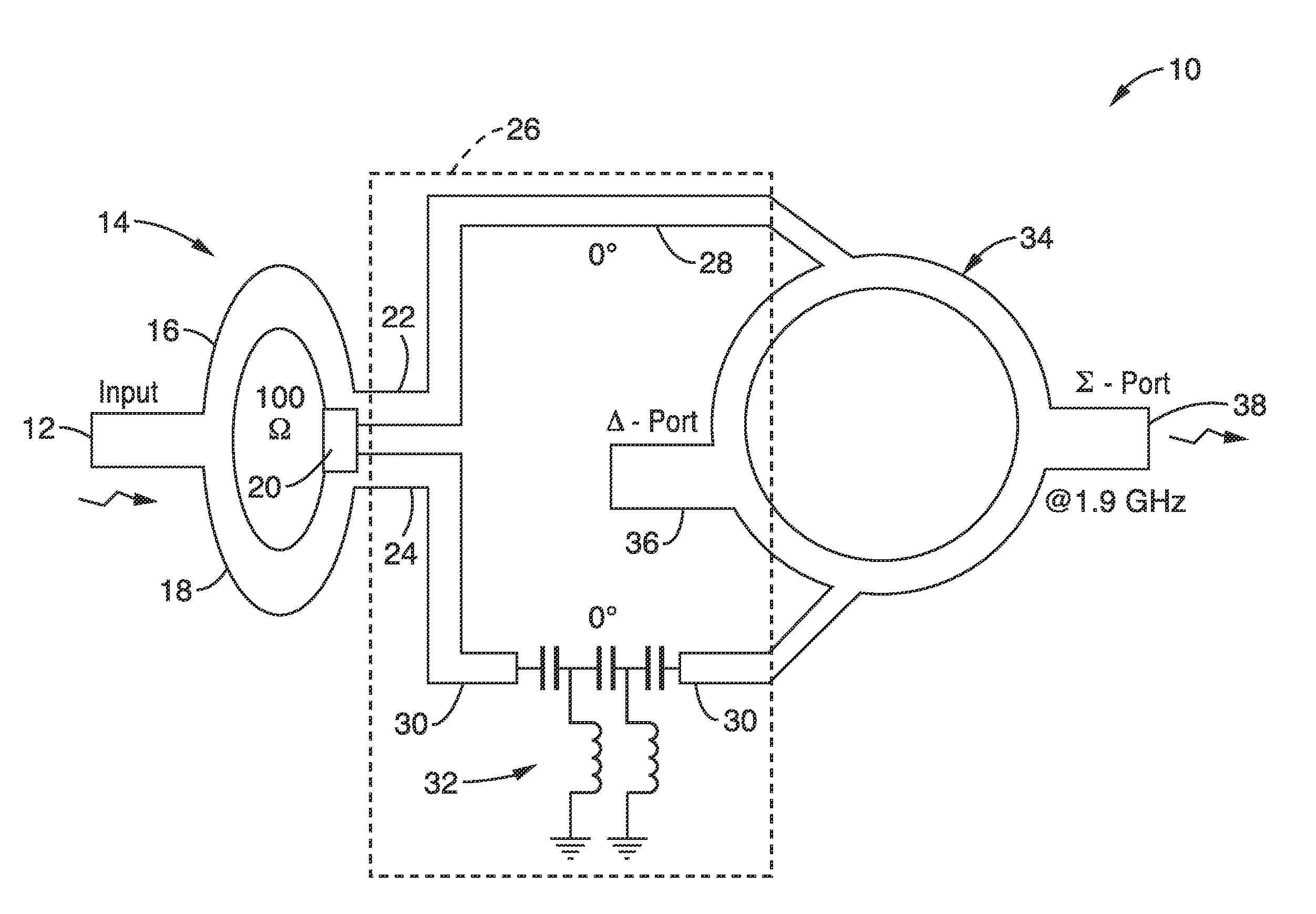

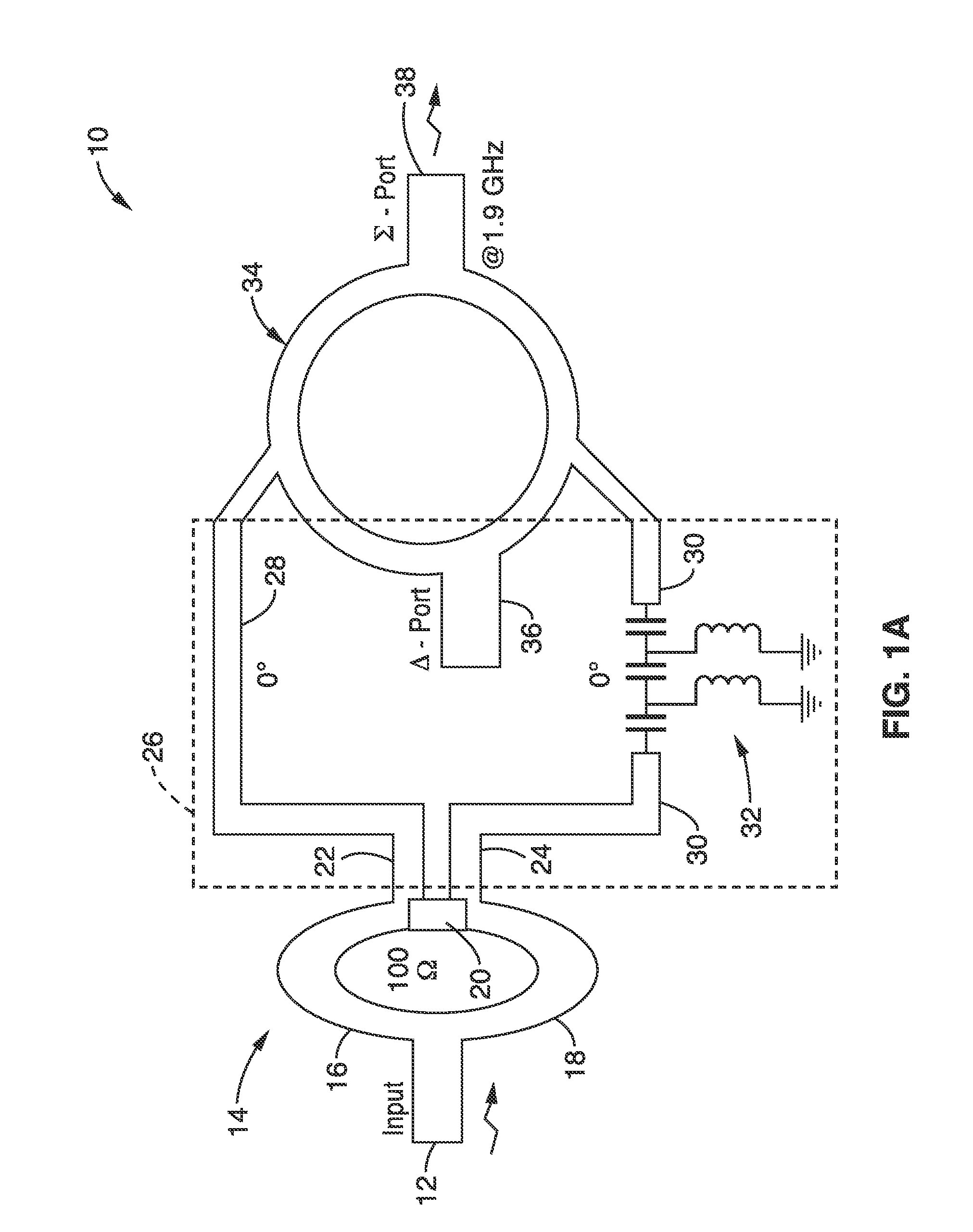

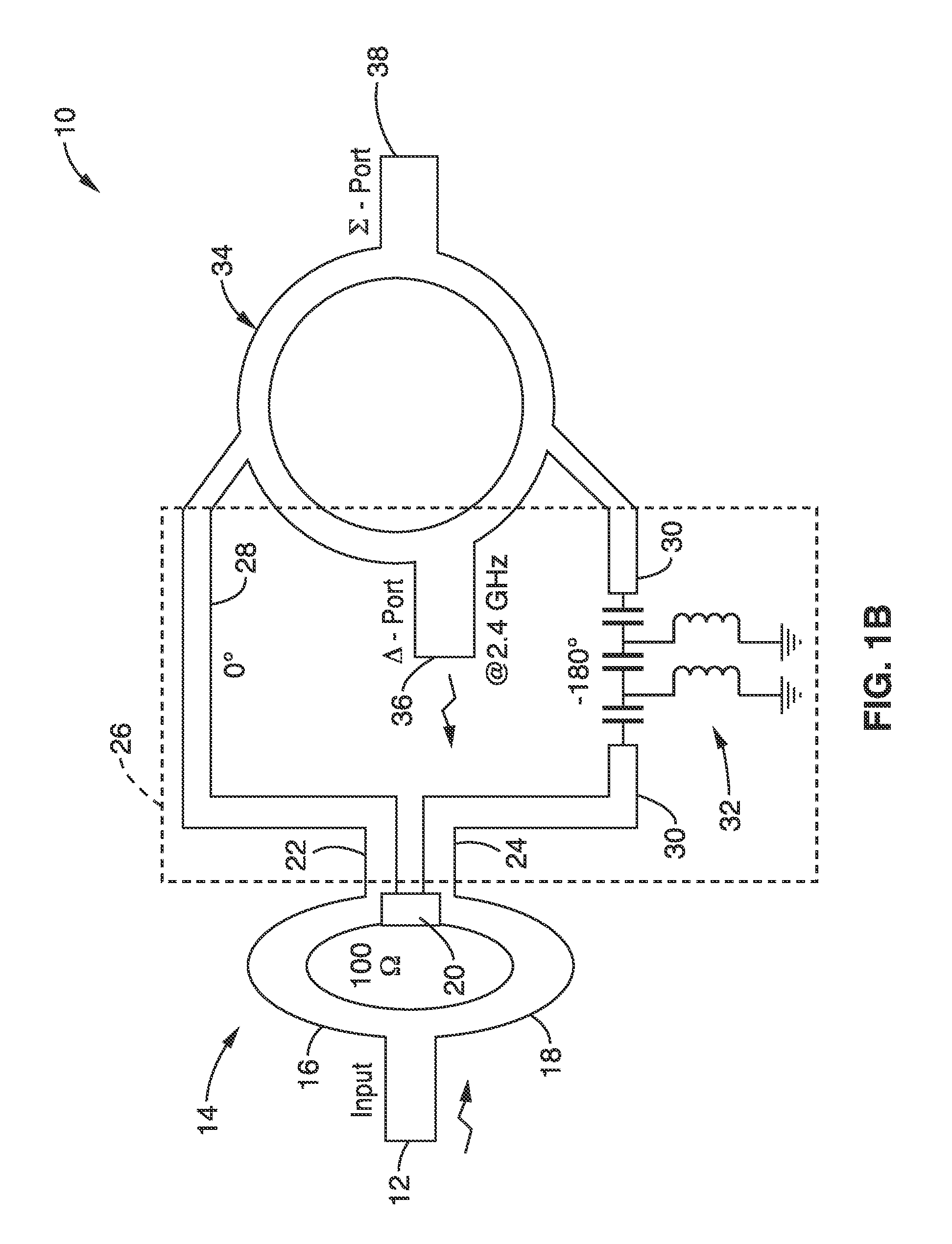

Diplexer synthesis using composite right/left-handed phase-advance/delay lines

ActiveUS20100295630A1Improve the level ofAvoid design complexityCoupling devicesHybrid couplerPhase response

A diplexing apparatus and method which utilizes composite right / left-handed (CRLH) phase-advance / delay lines combined with a coupler. By engineering CRLH-based transmission lines with desired phase responses at two arbitrary frequencies of interest, the connected CRLH delay line and / or CRLH coupler are excited in a manner such that signals at designated frequencies are separated to the corresponding output ports of the hybrid coupler. Benefits of the apparatus include elimination of design complexities such as optimization of the interconnection junctions and the harmonic spurious suppression involved in conventional filter-based diplexers. In addition, channel isolation is beneficially achieved from the isolation property of directional couplers. Measured insertion loss on the implementations was found to be less than 1 dB, with isolation greater than 20 dB in the dual bands. A high level of agreement was observed between simulated and measured results.

Owner:RGT UNIV OF CALIFORNIA

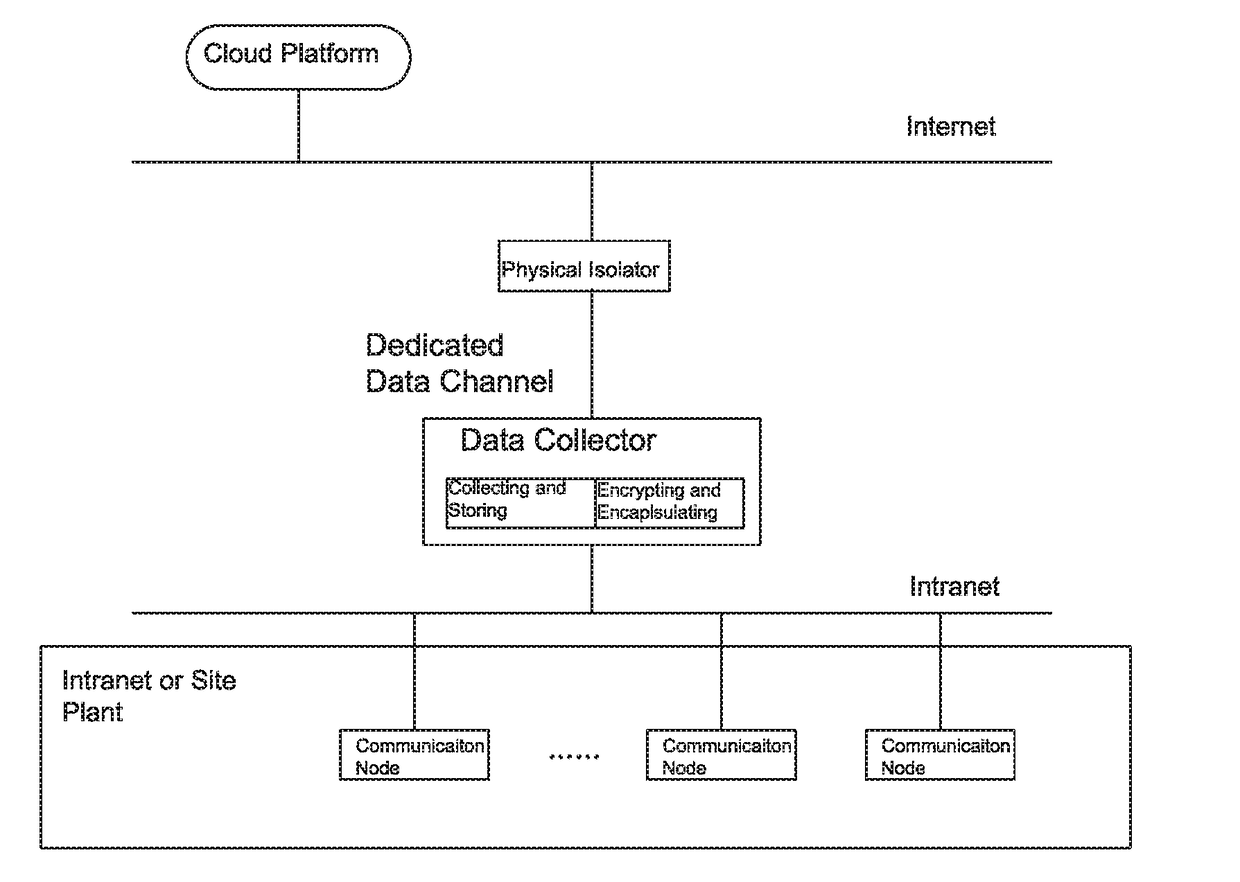

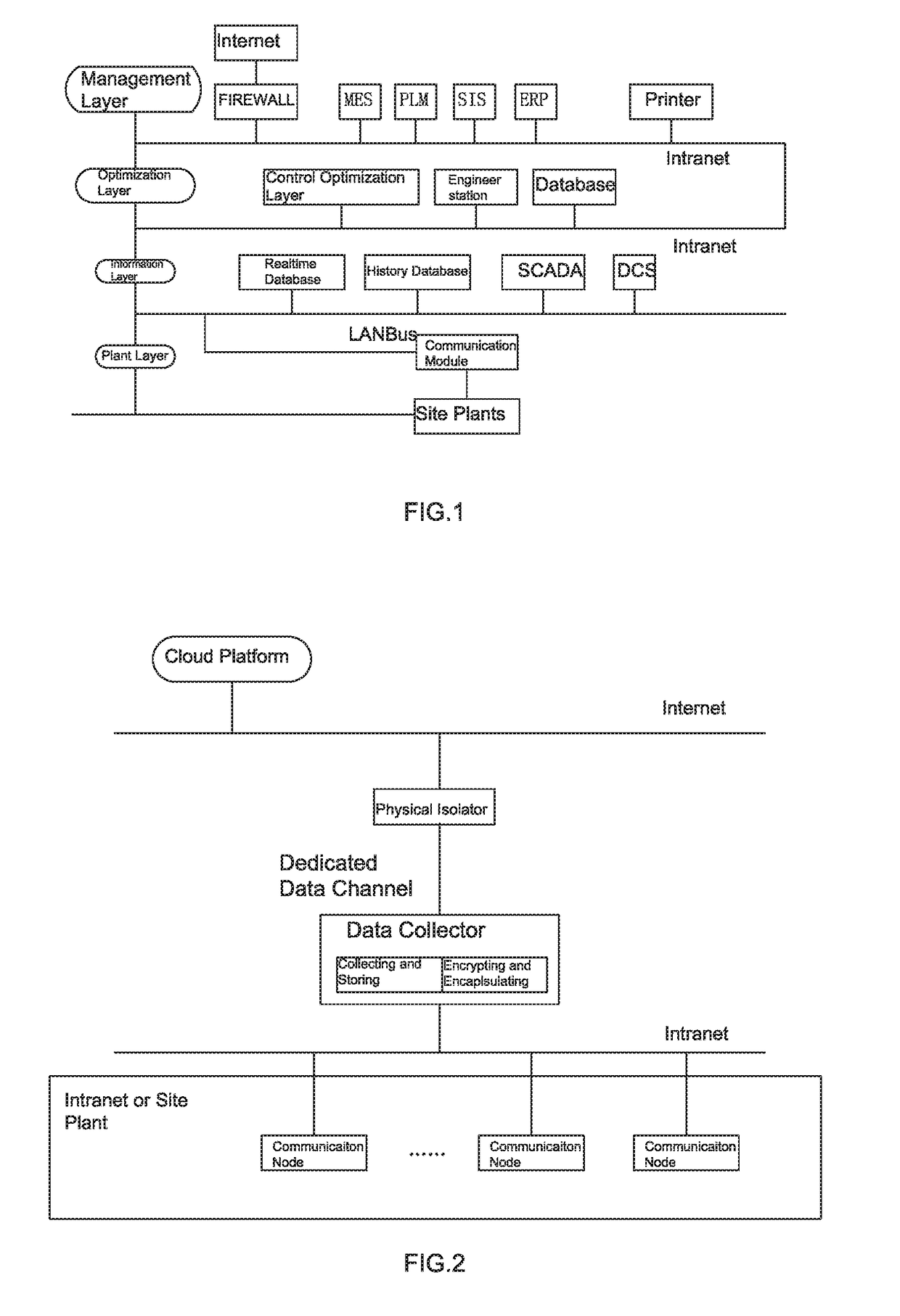

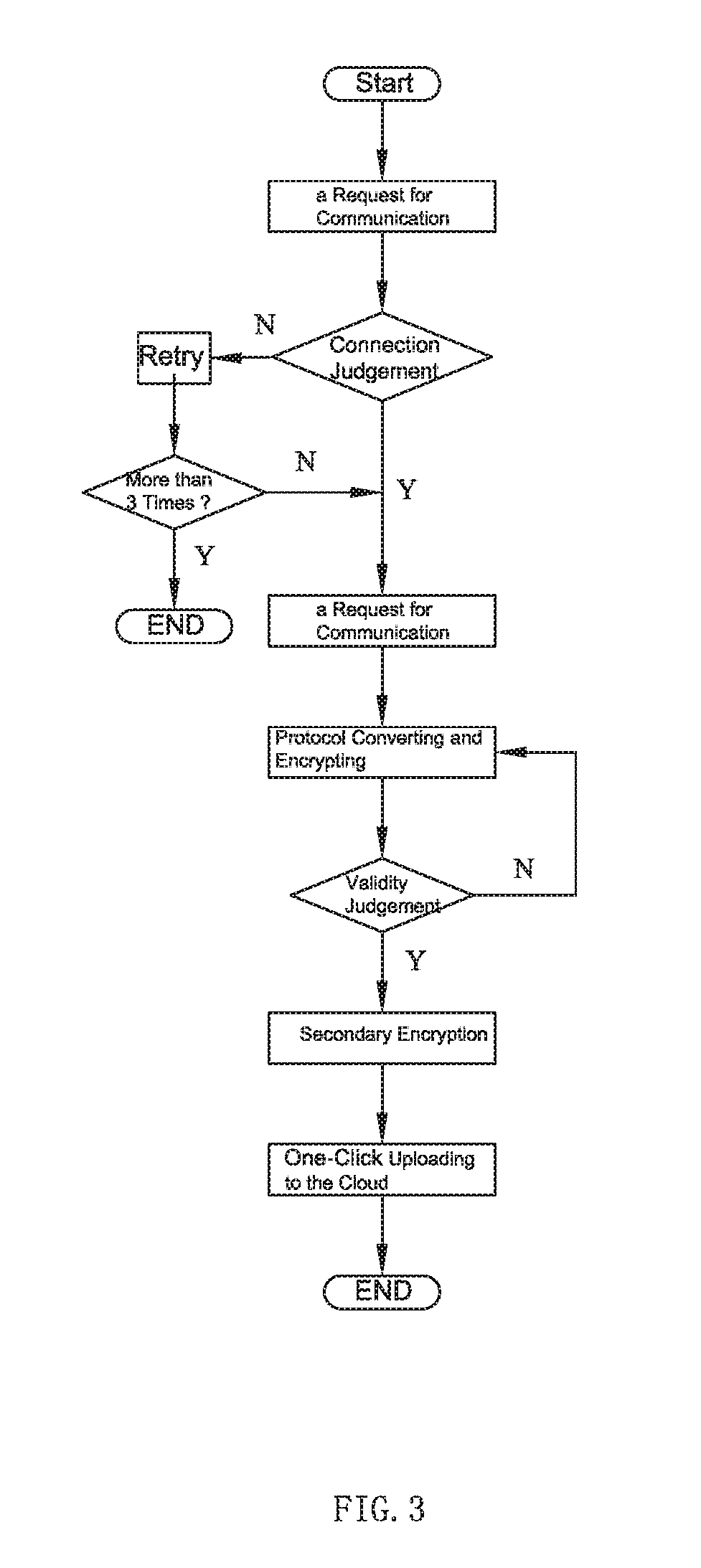

Method of industrial data communication with dedicated physical channel isolation and a system applying the method

ActiveUS20180337948A1Easy to buildLow costTransmission systemsTransmissionComputer networkData acquisition

A method and a system of industrial data communication with dedicated physical isolation are provided that, the data collector and the physical isolator cooperate with each other. The data collector collects the data of each nodes of an enterprise by the intranet or by the wired and wireless communication module. The data is converted into encrypted messages under a protocol. The physical isolator secondarily encrypts the data and uploads the standardized data to a cloud platform via the internet. The data is exchanged between the data collector and the physical isolator by a dedicated data channel. The data transmitted in the dedicated data channel is encrypted by an algorithm, and is transmitted in a form of encrypted messages. Two ports of the dedicated data channel can only transmit the data in the form of encrypted messages. The dedicated data channel uses specific communication media, and forms physical isolation directly.

Owner:XIAMEN OPTIKOM AUTOMATIC CONTROL TECH CO LTD

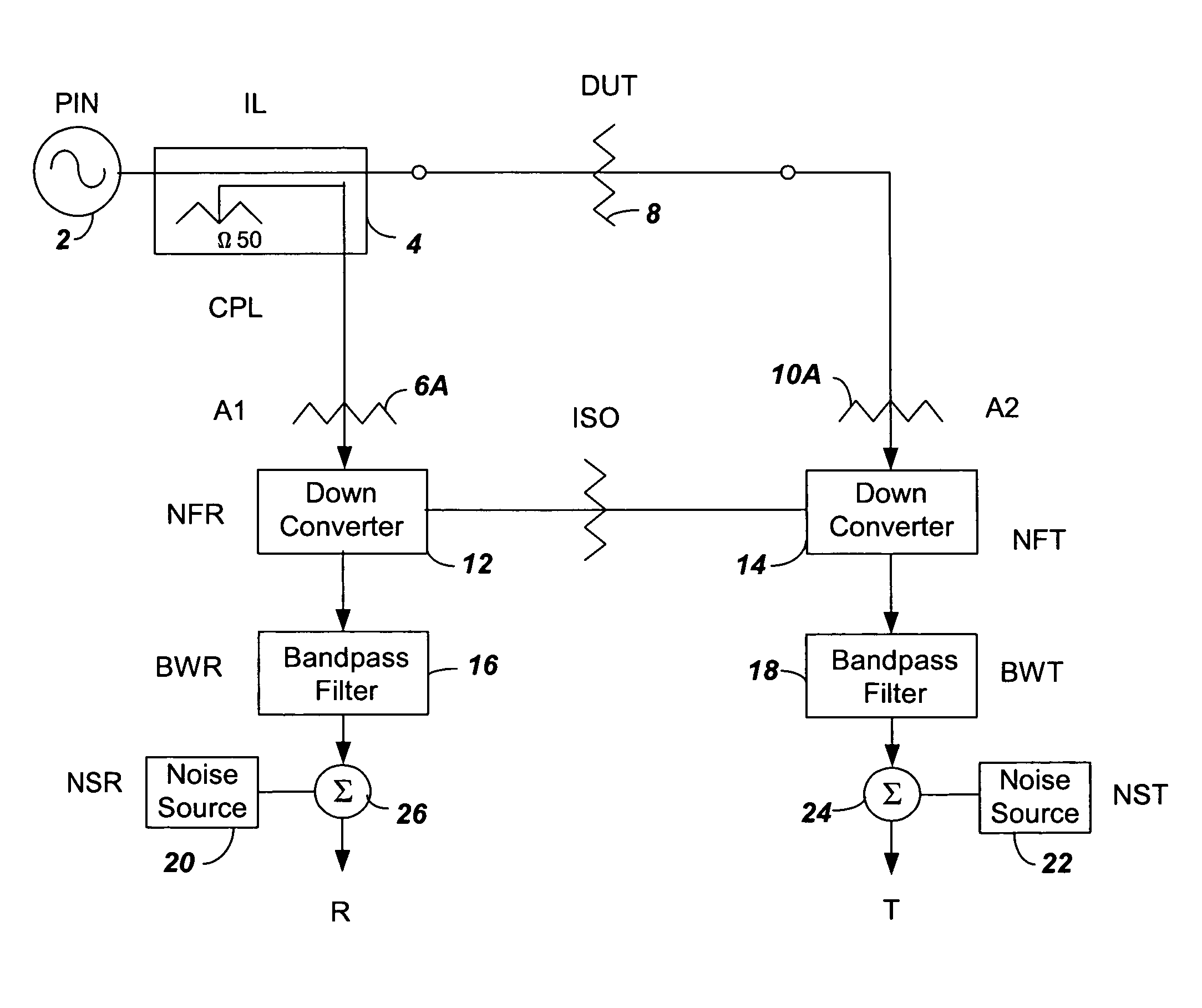

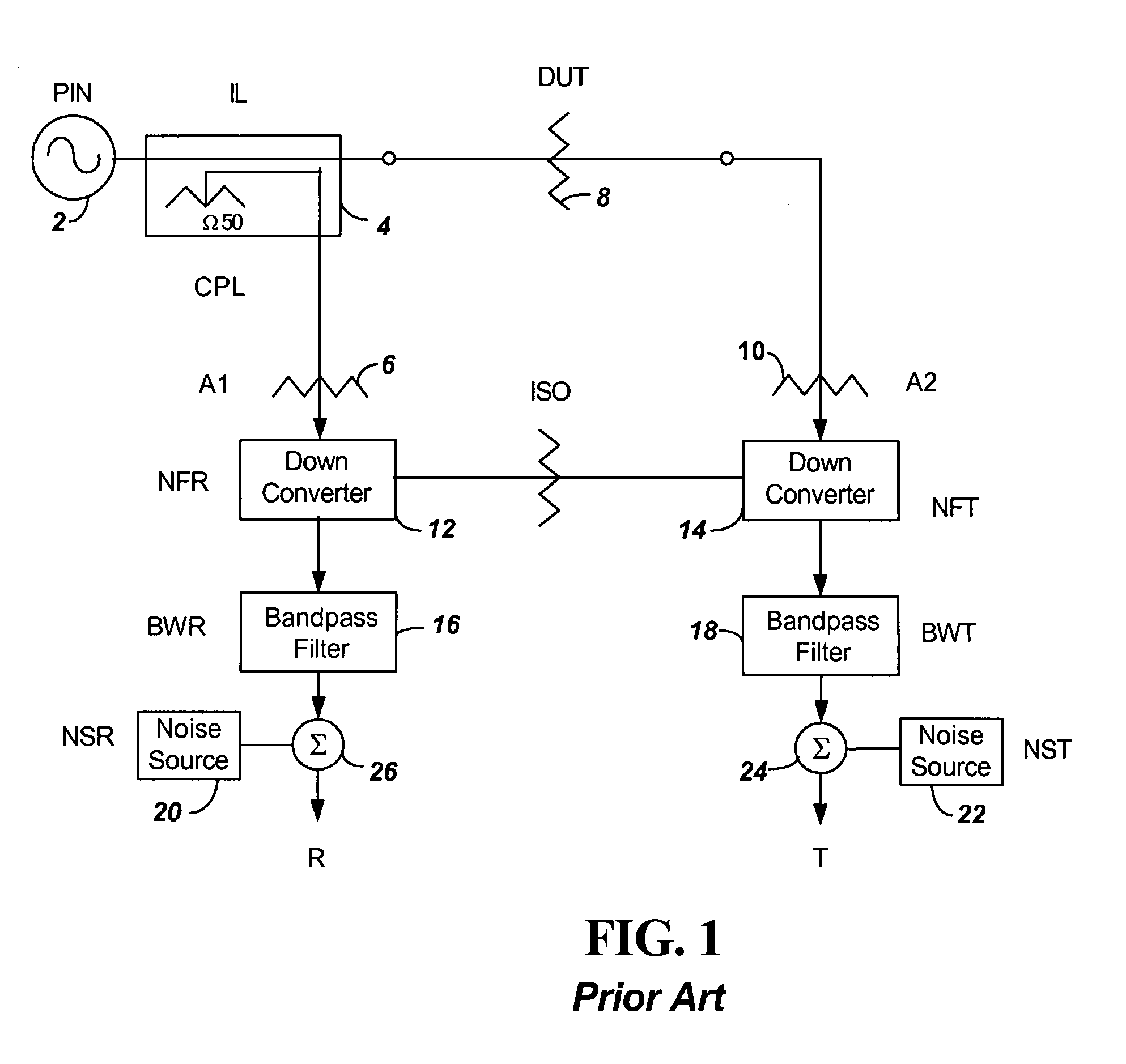

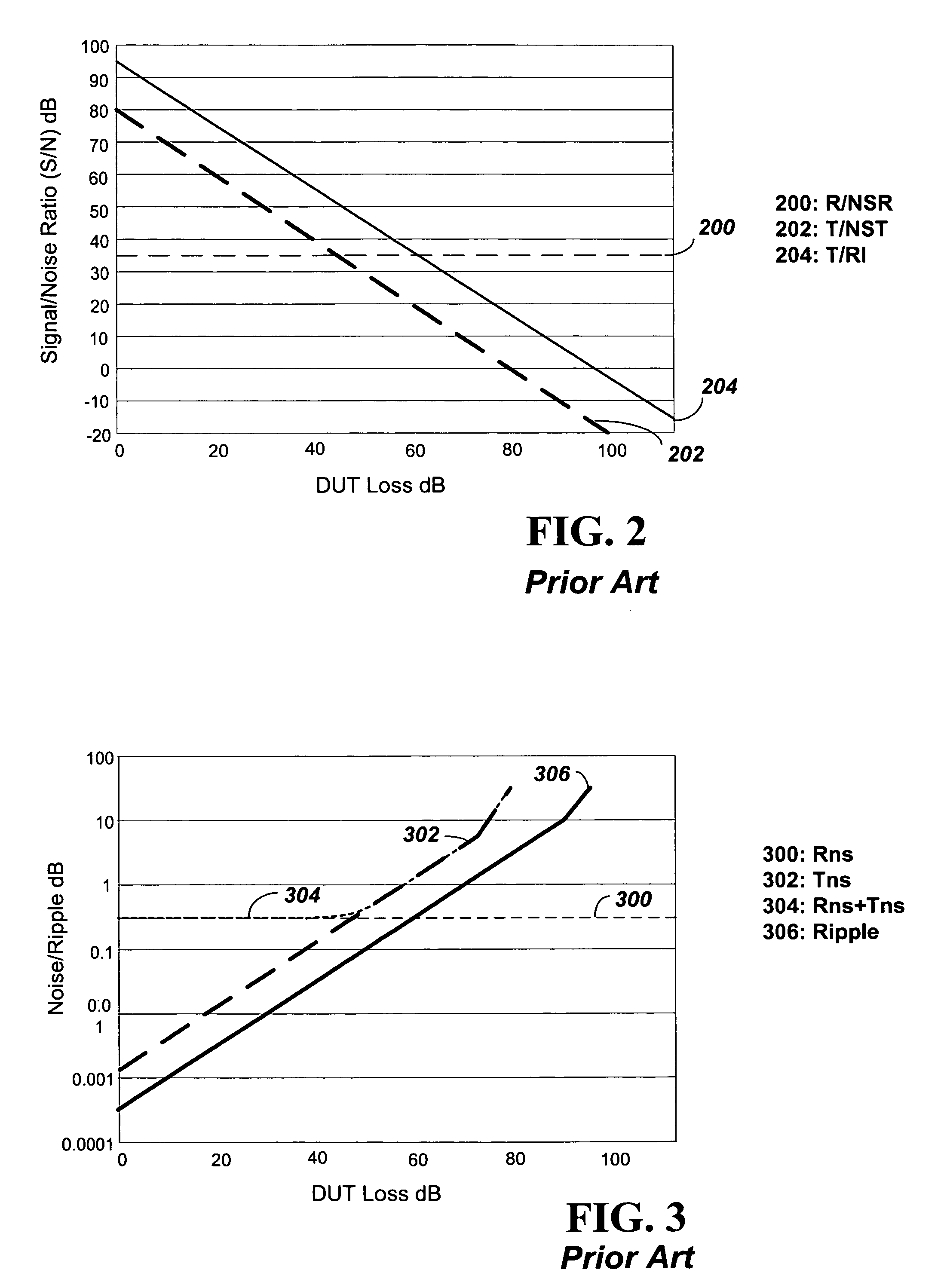

Adaptive method used to overcome channel to channel isolation

InactiveUS7304469B1Isolation requirementSpectral/fourier analysisResistance/reactance/impedenceTest channelUltrasound attenuation

Selectable attenuators are used in the reference and test paths of a VNA, with attenuation automatically inserted or deleted when the Device Under Test (DUT) attenuation reaches predetermined thresholds. Attenuation in the reference channel is removed when the signal in the test channel is sufficient to overcome the leakage of the reference channel. Additionally, attenuation is removed from the test channel when the reference channel has a high attenuation inserted to further increase the difference between the leakage reference signal and the reduced test channel signal thus allowing lower isolation requirements on the two (or more) receiving channels.

Owner:ANRITSU CO

Systems and methods for closed loop heat containment with cold aisle isolation for data center cooling

ActiveUS8764528B2Maximize capacityMaintain depthIndirect heat exchangersHeat transfer modificationCold airData center

The invention combines systems and methods for heat containment and cold air isolation for managing airflow and temperature in data centers. The data center contains at least two rows of cabinets containing heat-generating equipment and arranged to form a cold aisle and a hot aisle. The data center system includes panels or doors at both ends of the cold aisle and an optional cover over the cold aisle to inhibit cooled air supplied by an air conditioning system from exiting the cold aisle and inhibit air warmed by the heat-generating components from entering the cold aisle. A chimney coupled to the top, rear, or top and rear of the cabinets is configured to exhaust the warmed air into a region above the rows of cabinets. The chimneys may be ducted to a plenum or suspended ceiling or to the intake of the air conditioning system. Baffles and / or fans may be included in the chimneys, ducts, and / or plenums to control the air pressure. The invention may also include one or more data center air conditioning units, and each air conditioning unit may be configured to service one or more rows of cabinets. Alternatively, or in addition, cool air may be supplied by the building's air conditioning system.

Owner:EATON INTELLIGENT POWER LTD

Multi-capillary electrophoresis cartridge interface mechanism

ActiveUS7622083B2Precise positioningReliable implementationImmobilised enzymesBioreactor/fermenter combinationsCapillary TubingEngineering

The present invention provides for an interface mechanism in a bio-separation instrument that makes interface connections to a multi-channel cartridge. The interface mechanism precisely positions the cartridge in relation to the support elements in the instrument (e.g., high-voltage, gas pressure, incident radiation and detector), and makes automated, reliable and secured alignments and connections between various components in the cartridge and the support elements in the supporting instrument. The interface mechanism comprises pneumatically or electromechanically driven actuators for engaging support elements in the instrument to components on the cartridge. After the cartridge has been securely received by the interface mechanism, the connection sequence is initiated. The interface provides separate high voltage and optical connections for each separation channel in the cartridge, thus providing channel-to-channel isolation from cross talk both electrically and optically.

Owner:QIAGEN SCIENCES LLC

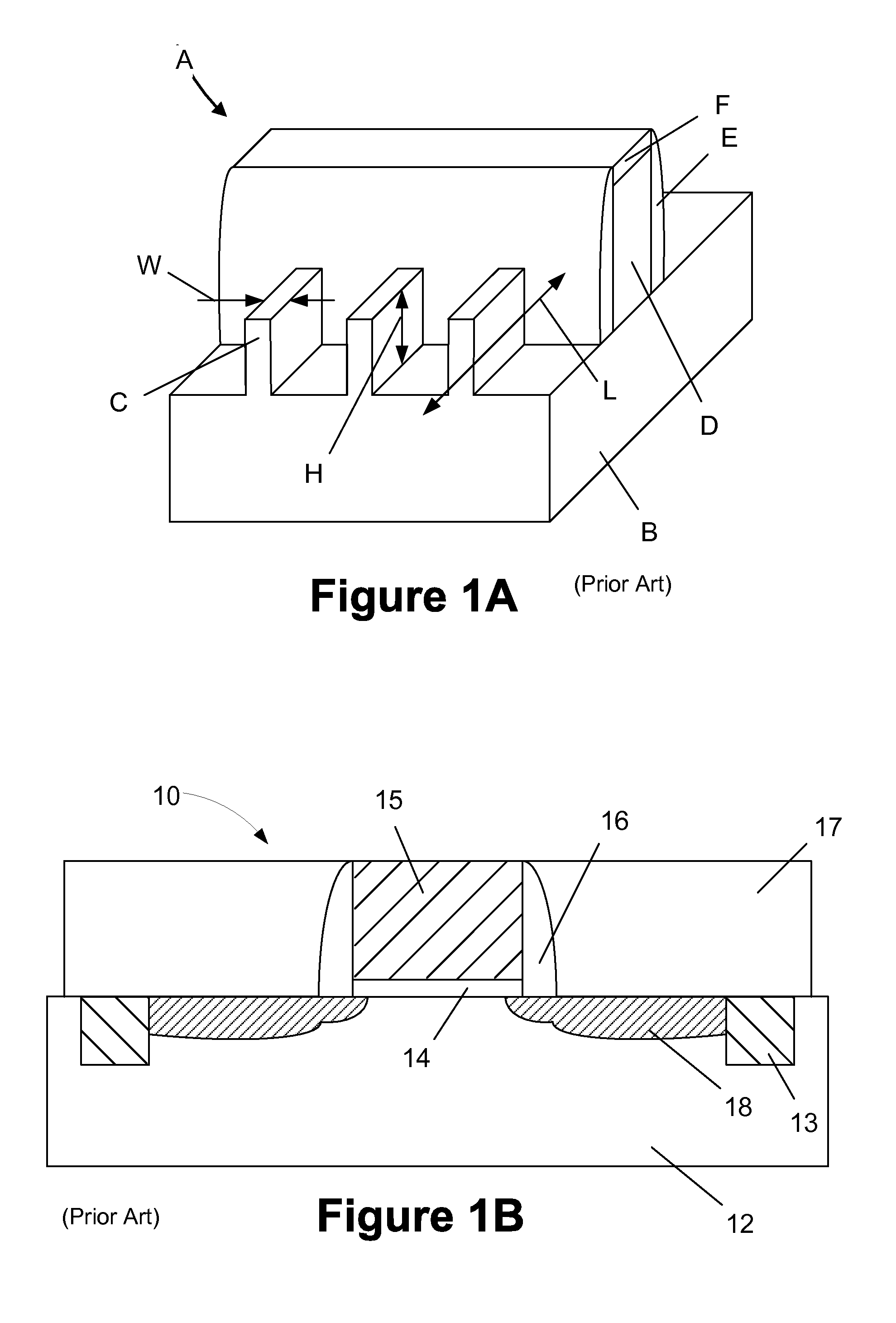

Integrated circuit integrating U-shaped channel device and fin-shaped channel device and preparation method thereof

ActiveCN103956338AImprove performanceReduced shutdown currentSemiconductor/solid-state device manufacturingDielectricGate dielectric

The invention belongs to the technical field of semiconductor device manufacturing and particularly provides an integrated circuit integrating a U-shaped channel device and a fin-shaped channel device and a preparation method of the integrated circuit. A channel isolation structure with a doping well is formed in a semiconductor substrate; a polycrystalline silicon sacrificial gate electrode is formed on the doping well, and a source electrode and a drain electrode are formed on the two sides of the polycrystalline silicon sacrificial gate electrode respectively; the formed structure is covered, interlayer dielectrics are deposited, the polycrystalline silicon sacrificial gate electrode is exposed by means of polishing and then is etched, and the U-shaped channel device is formed in the semiconductor substrate by means of photoetching; a fin-shaped channel structure is formed in the semiconductor substrate by means of photoetching again, and then a gate dielectric layer and a gate electrode are formed, so that the fin-shaped channel device is formed. According to the method, the fin-shaped channel device can be integrated on a chip and serve as a high-performance device, and the U-shaped channel device can be integrated on the same chip and sever as a low-power-consumption device; as a result, a device with a big shape difference is obtained, a small turn-off current and a large turn-on current are obtained, and the performance of the chip is improved.

Owner:FUDAN UNIV

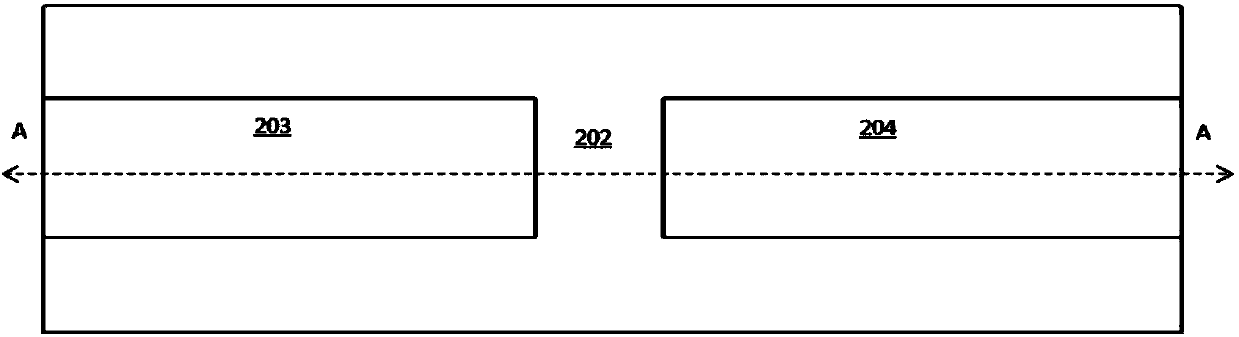

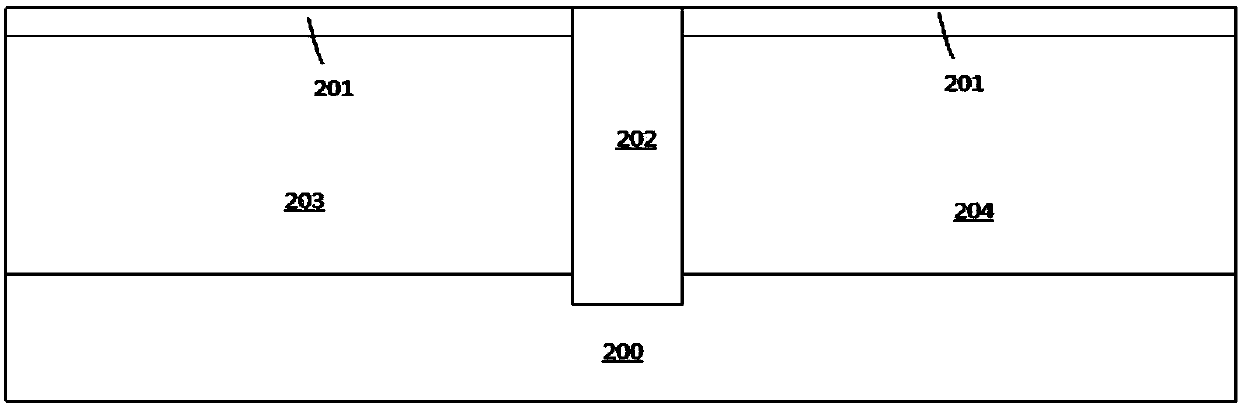

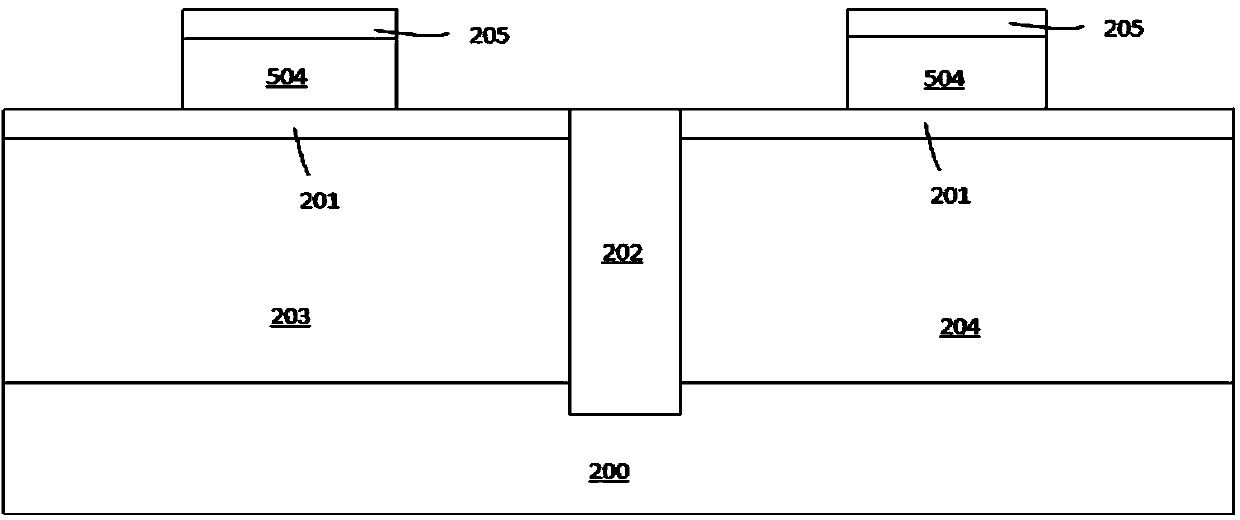

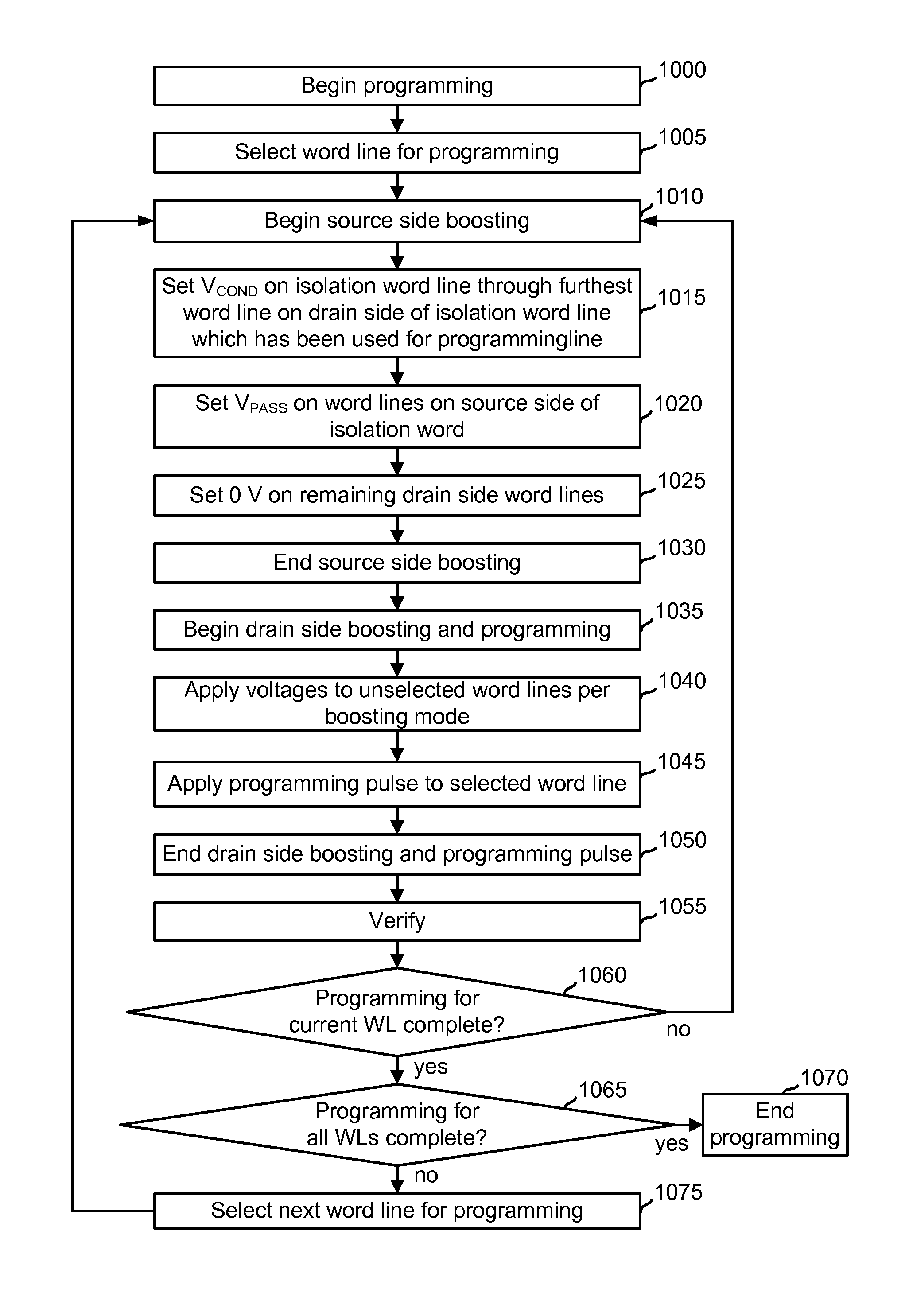

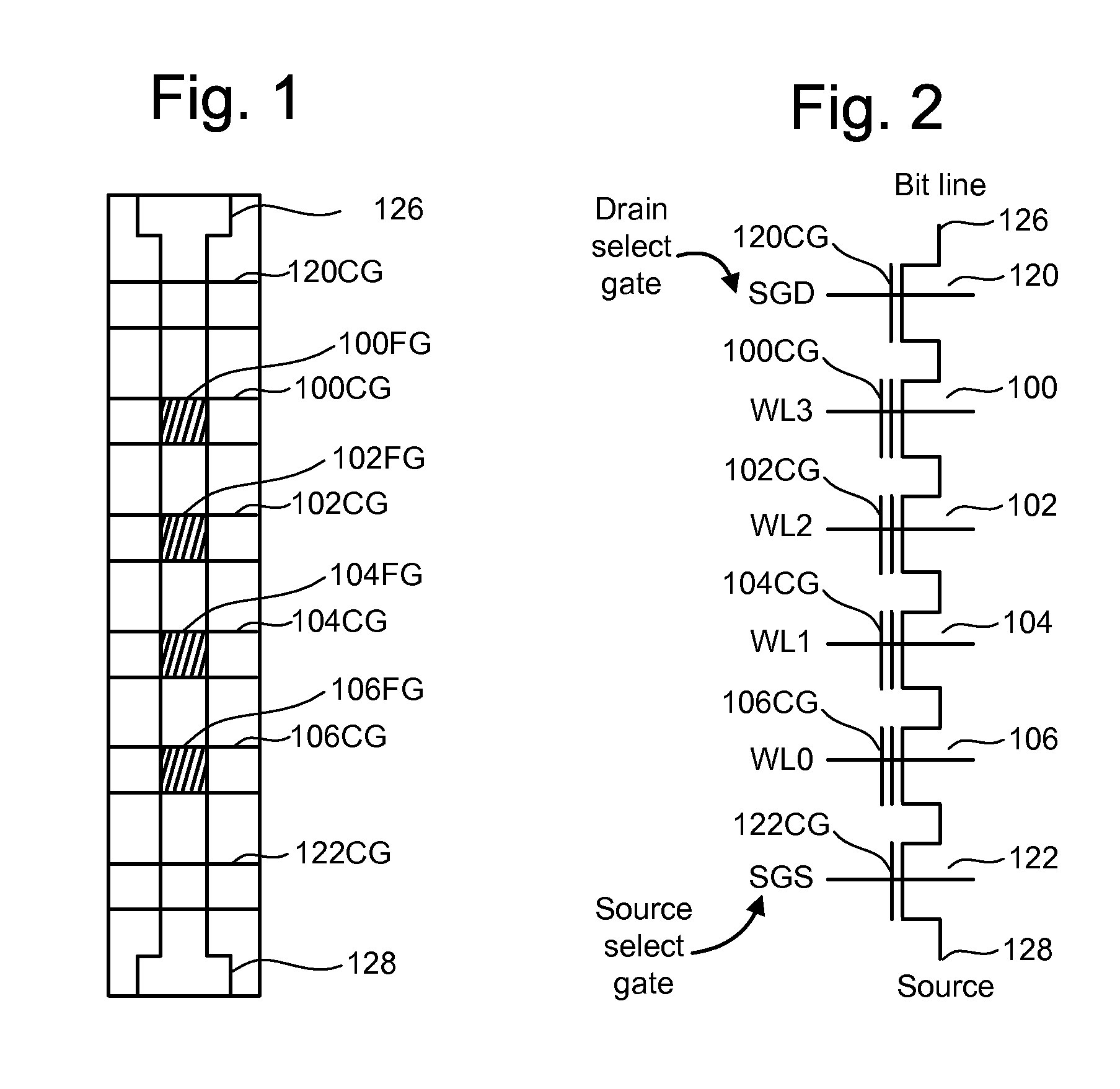

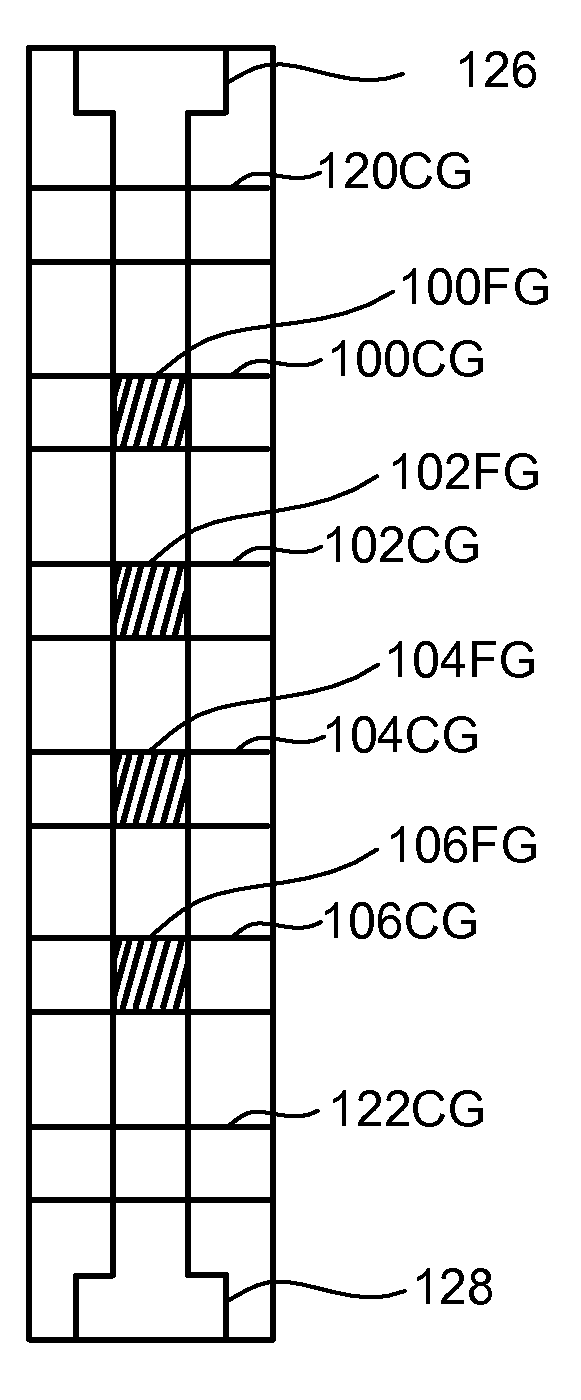

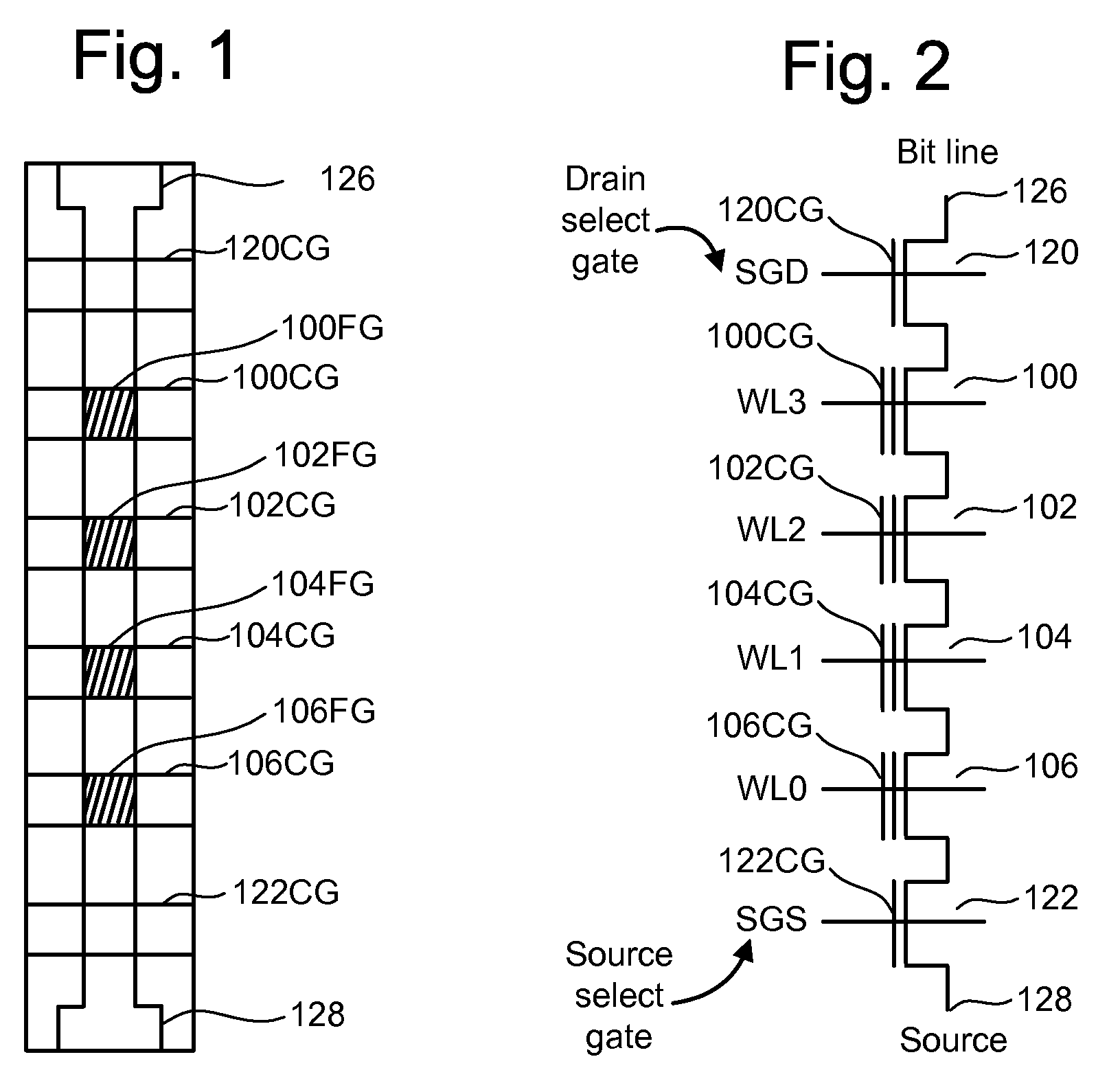

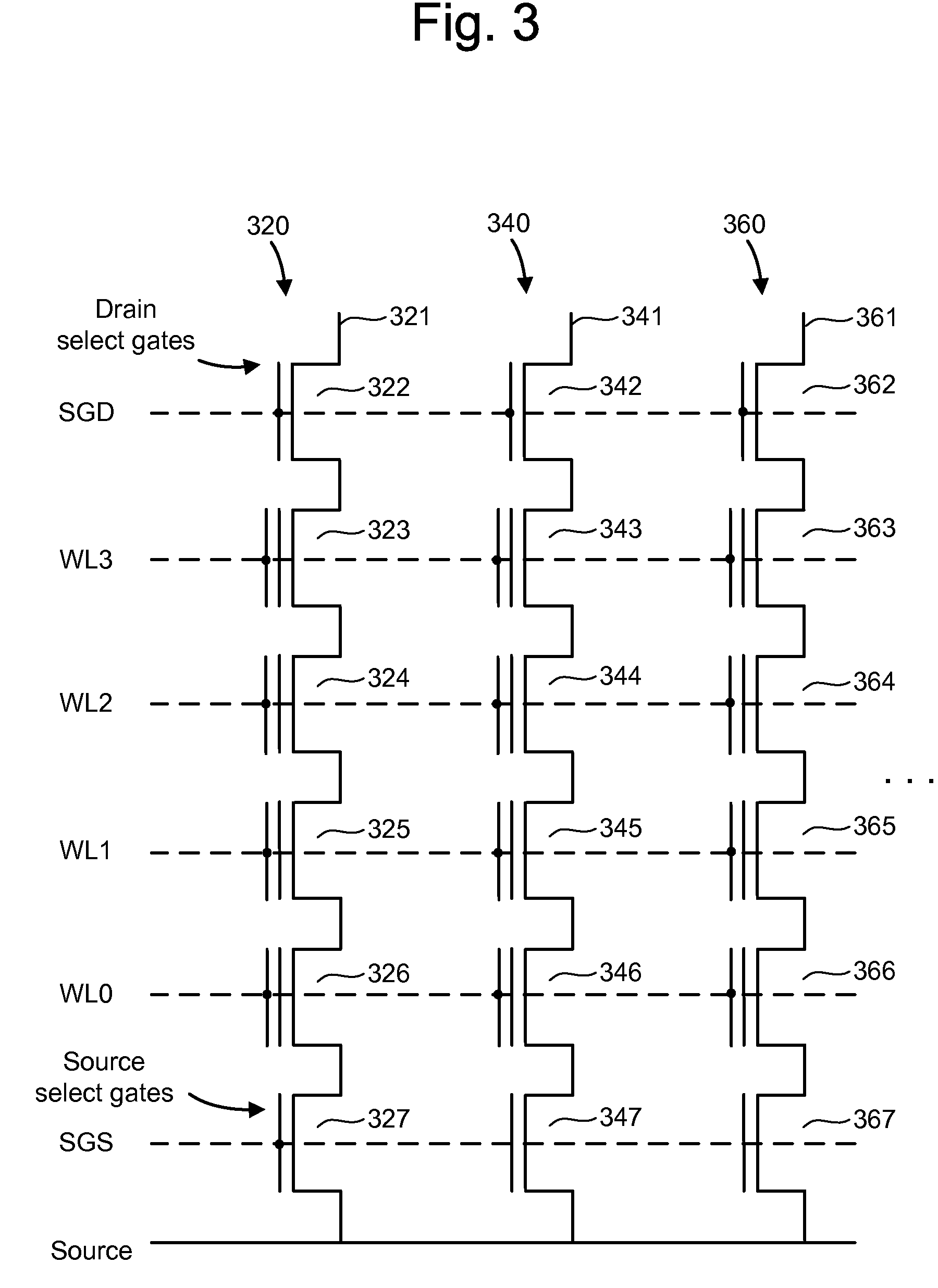

Boosting for non-volatile storage using channel isolation switching

ActiveUS7460404B1Reducing program disturbRead-only memoriesDigital storageNon-volatile memoryChannel isolation

Owner:SANDISK TECH LLC

Methods of forming substantially self-aligned isolation regions on finfet semiconductor devices and the resulting devices

InactiveUS20150294912A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsDevice material

Owner:GLOBALFOUNDRIES INC

Multi-capillary electrophoresis cartridge interface mechanism

InactiveUS20100170799A1Precise positioningReliable implementationCellsSludge treatmentCapillary electrophoresisMagnetic tape

The present invention provides for an interface mechanism in a bio-separation instrument that makes interface connections to a multi-channel cartridge. The interface mechanism precisely positions the cartridge in relation to the support elements in the instrument (e.g., high-voltage, gas pressure, incident radiation and detector), and makes automated, reliable and secured alignments and connections between various components in the cartridge and the support elements in the supporting instrument. The interface mechanism comprises pneumatically or electromechanically driven actuators for engaging support elements in the instrument to components on the cartridge. After the cartridge has been securely received by the interface mechanism, the connection sequence is initiated. The interface provides separate high voltage and optical connections for each separation channel in the cartridge, thus providing channel-to-channel isolation from cross talk both electrically and optically.

Owner:QIAGEN SCIENCES LLC

Non-volatile storage with boosting using channel isolation switching

ActiveUS20080279008A1Read-only memoriesDigital storageComputer engineeringElectrical and Electronics engineering

Owner:SANDISK TECH LLC

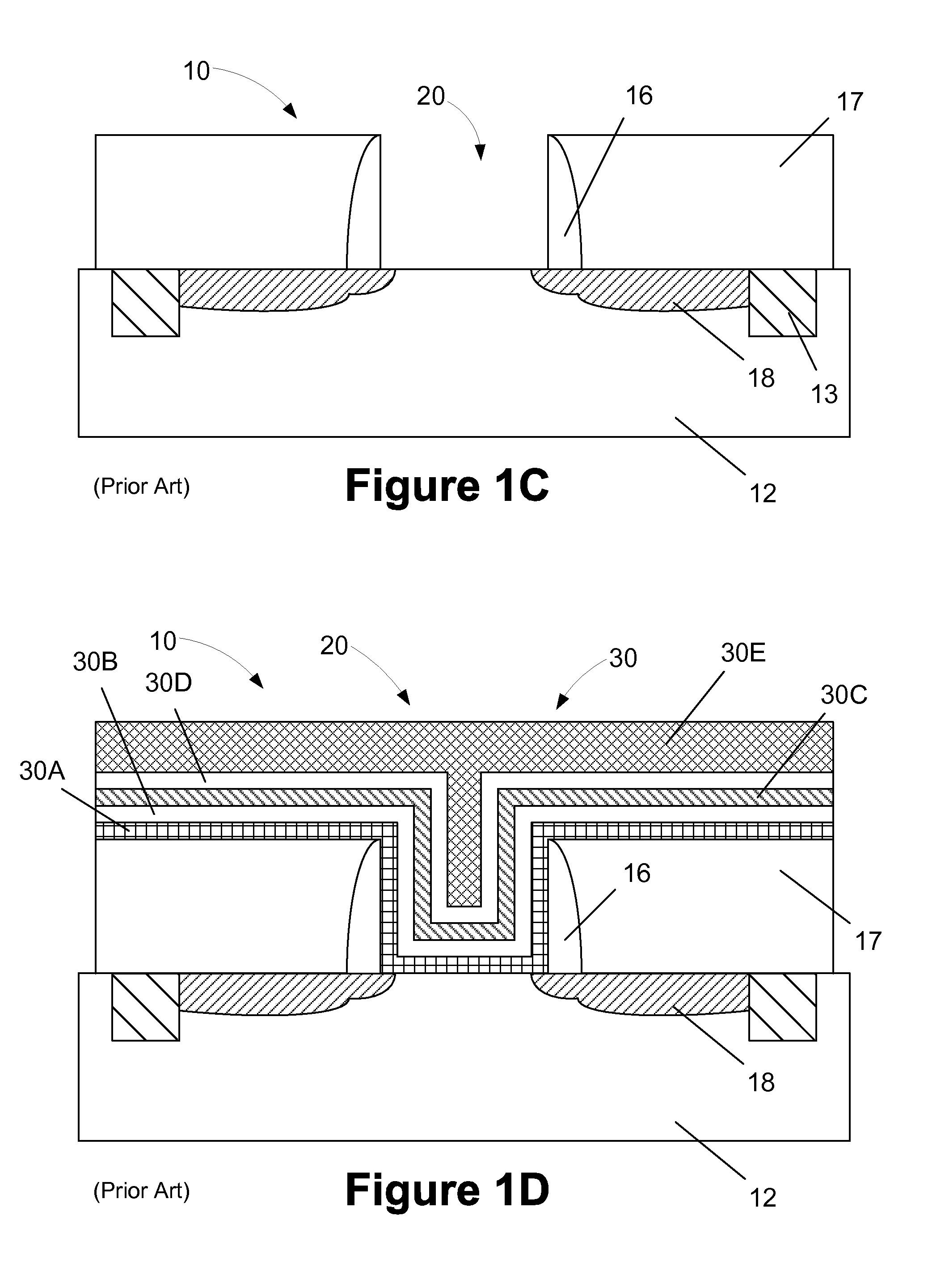

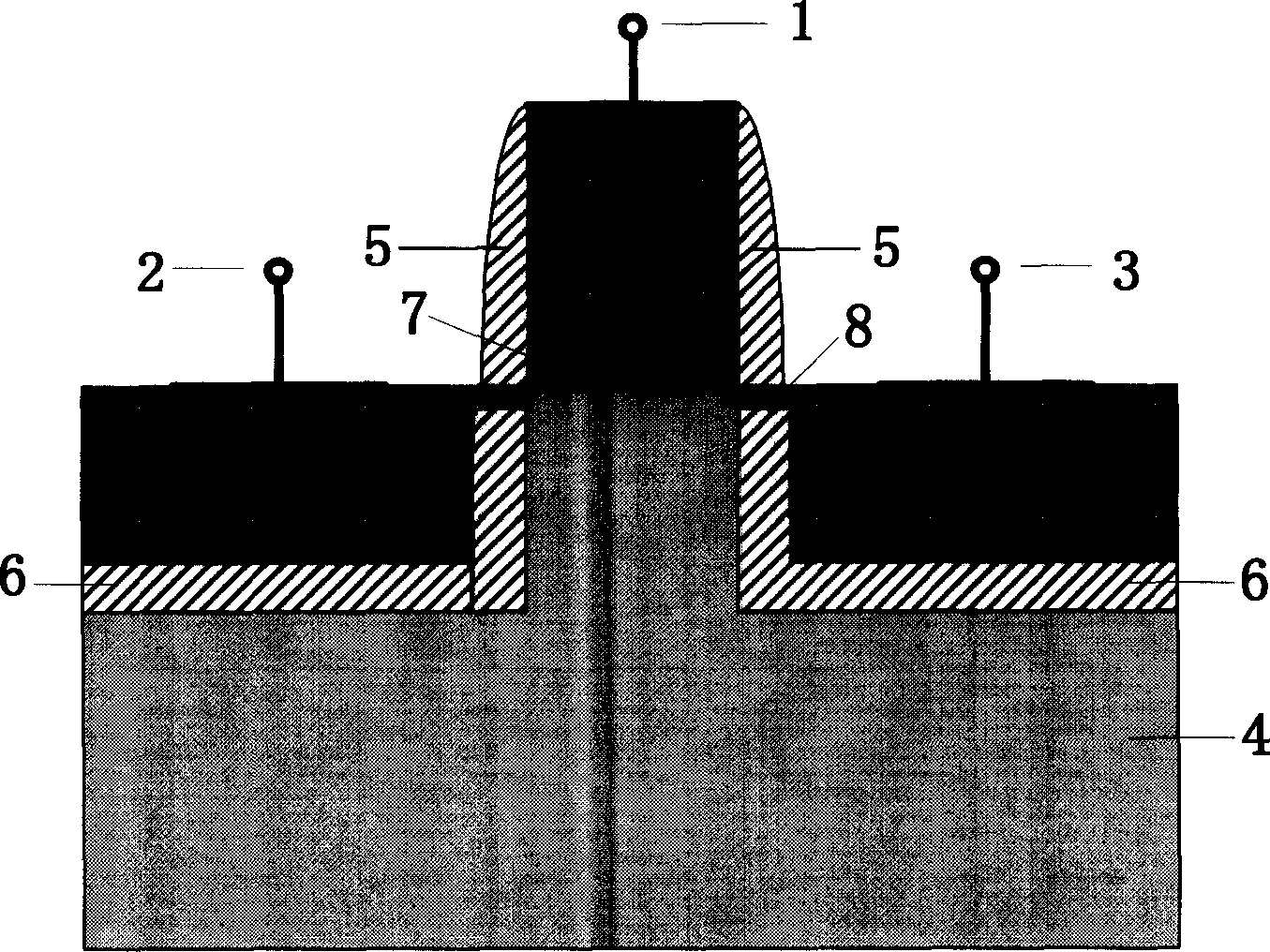

Method for preparing field effect transistor

ActiveCN1622295ARealize the structureSimple processSemiconductor/solid-state device manufacturingVery large scale integrated circuitsOxidation resistant

The present invention provides the preparation process of quasi-SOI FET, and belongs to the field of ULSI technology. The preparation process includes the first conventional technological step of shallow channel isolation, depositing and etching grid material and covered hard mask material to form grid area, and forming grid side wall to protect grid area; the second step of etching silicon in source and drain areas to certain depth h1, depositing and etching antioxidant material to form side wall, etching silicon in source and drain areas to the second depth h2 to form deeper silicon channel, and hot oxidizing the exposed silicon to form L-shaped silica layer inside the channels in source and drain areas; and the third step of eliminating side wall of antioxidant material, depositing source and drain material and forming source arean and drain arean in flat course, so as to form the quasi-SOI structure. The said process is simple, low in cost and easy in integration.

Owner:PEKING UNIV +1

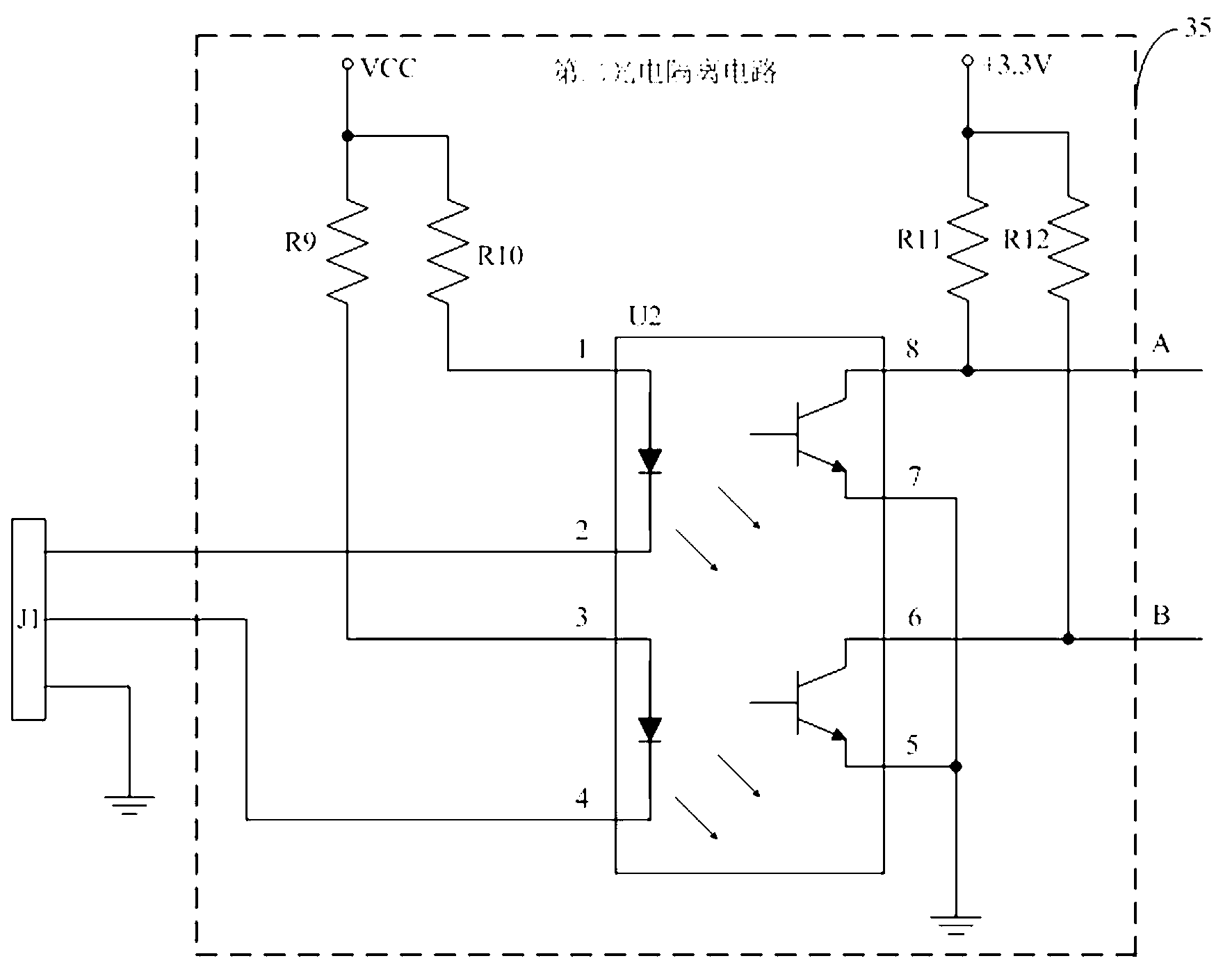

Automatic switching circuit for RS232 interface and RS485 interface and serial port liquid crystal display module

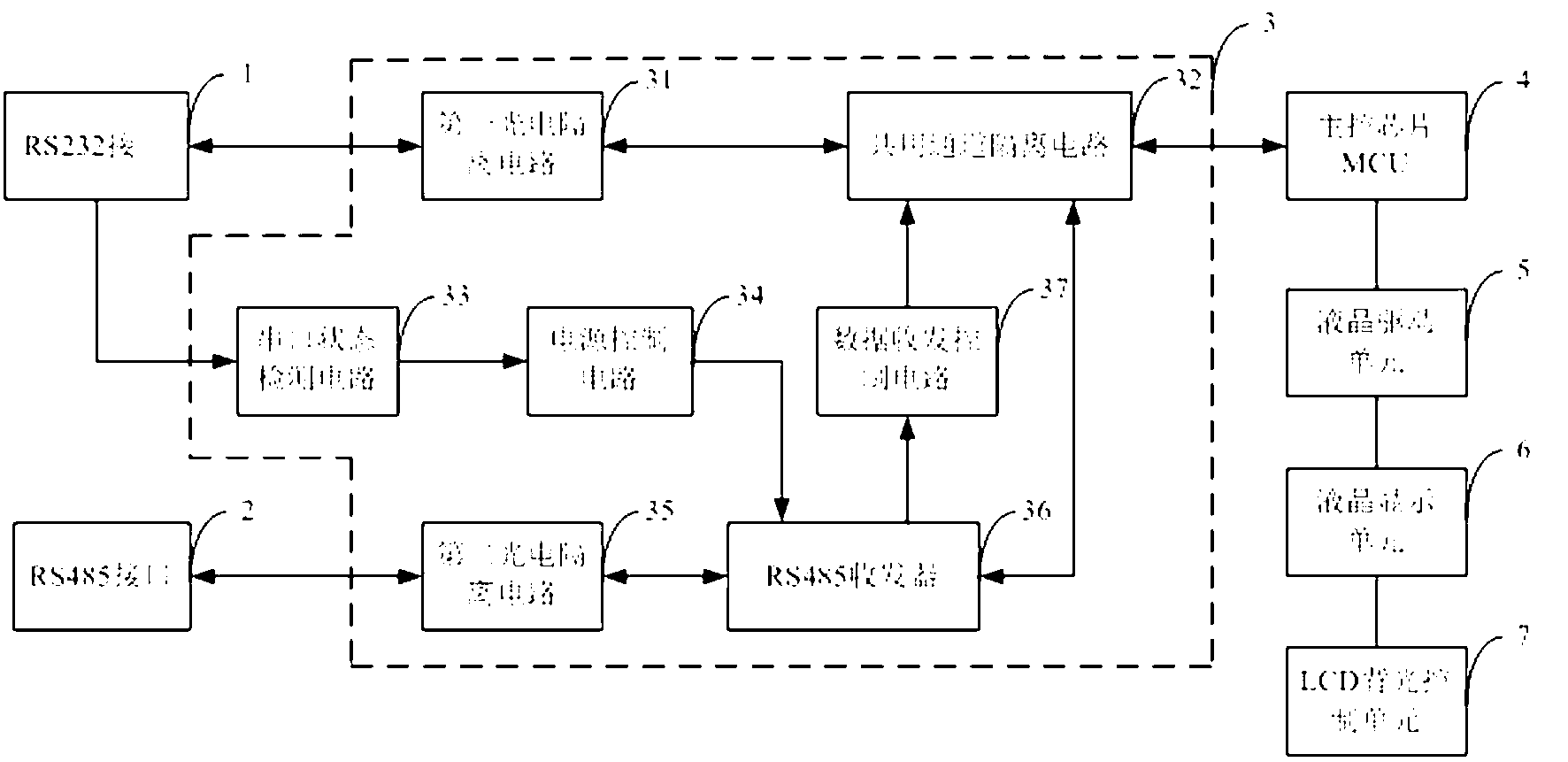

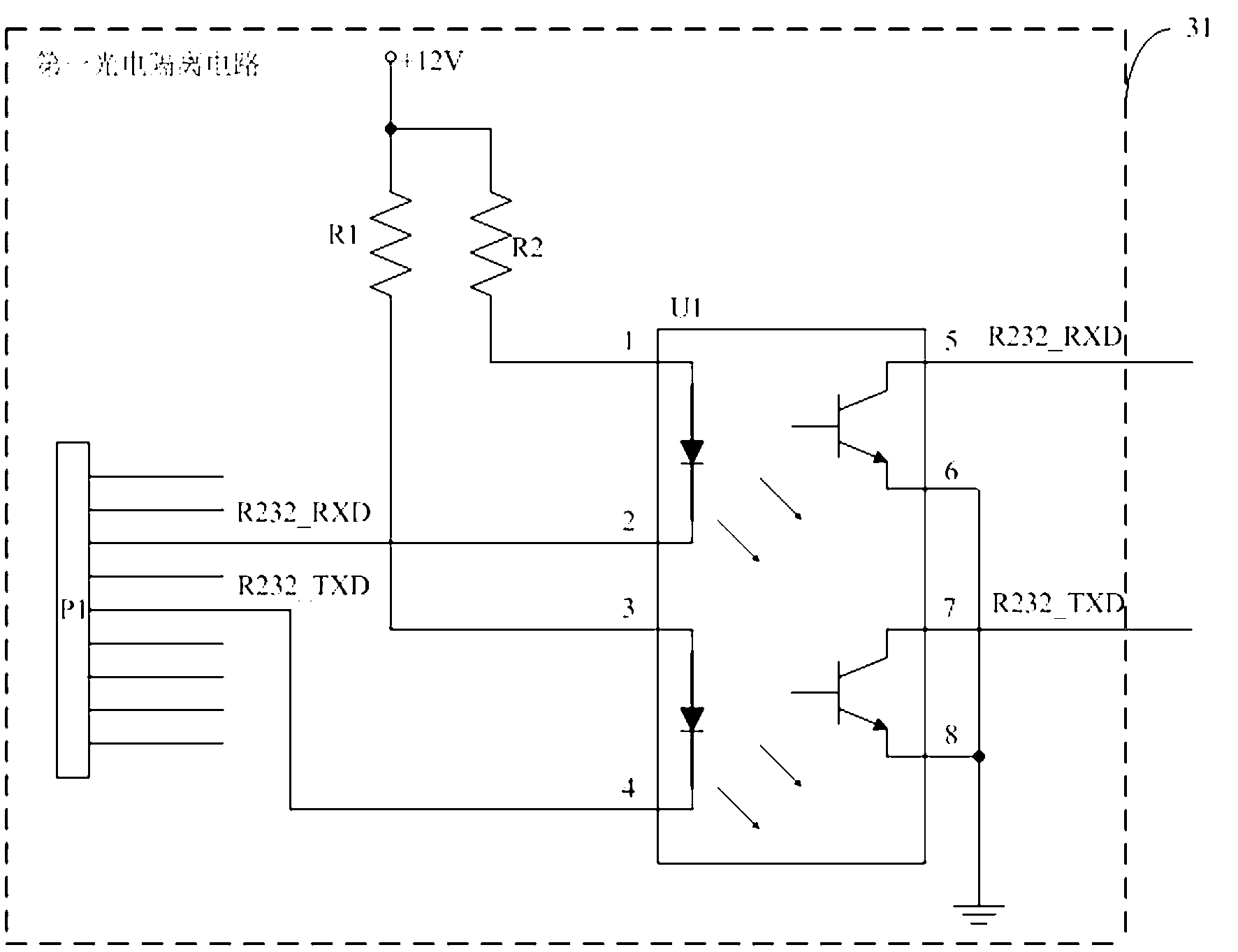

ActiveCN102708823AResolve mutual interferenceResolve interferenceStatic indicating devicesData displayTransceiver

The invention is applied to the field of serial port communication, and provides an automatic switching circuit for an RS232 interface and an RS485 interface and a serial port liquid crystal display module. The automatic switching circuit comprises a first photoelectric isolation circuit, a second photoelectric isolation circuit, a serial port state detection circuit, a power control circuit, a data transmission and reception control circuit, an RS485 transceiver and a common channel isolation circuit. In the embodiment of the invention, when the automatic switching circuit adopts a common data display channel for the RS232 interface and the RS485 interface to communicate with a master control micro control unit (MCU), and the common channel is completely isolated, so that the problem of mutual interference of the common channel is solved; the serial port state detection circuit judges the current working conditions of the RS232 interface and the RS485 interface, and is matched with the power control circuit to timely cut off power supplied to the RS485 interface, so that the problem of possible interference when the RS232 interface and the RS485 interface are simultaneously connected can be solved; and in addition, a photoelectric isolation method is adopted to prevent surge and lightning, so that the automatic switching circuit can be well applied to industrial application places.

Owner:芜湖天马汽车电子有限公司

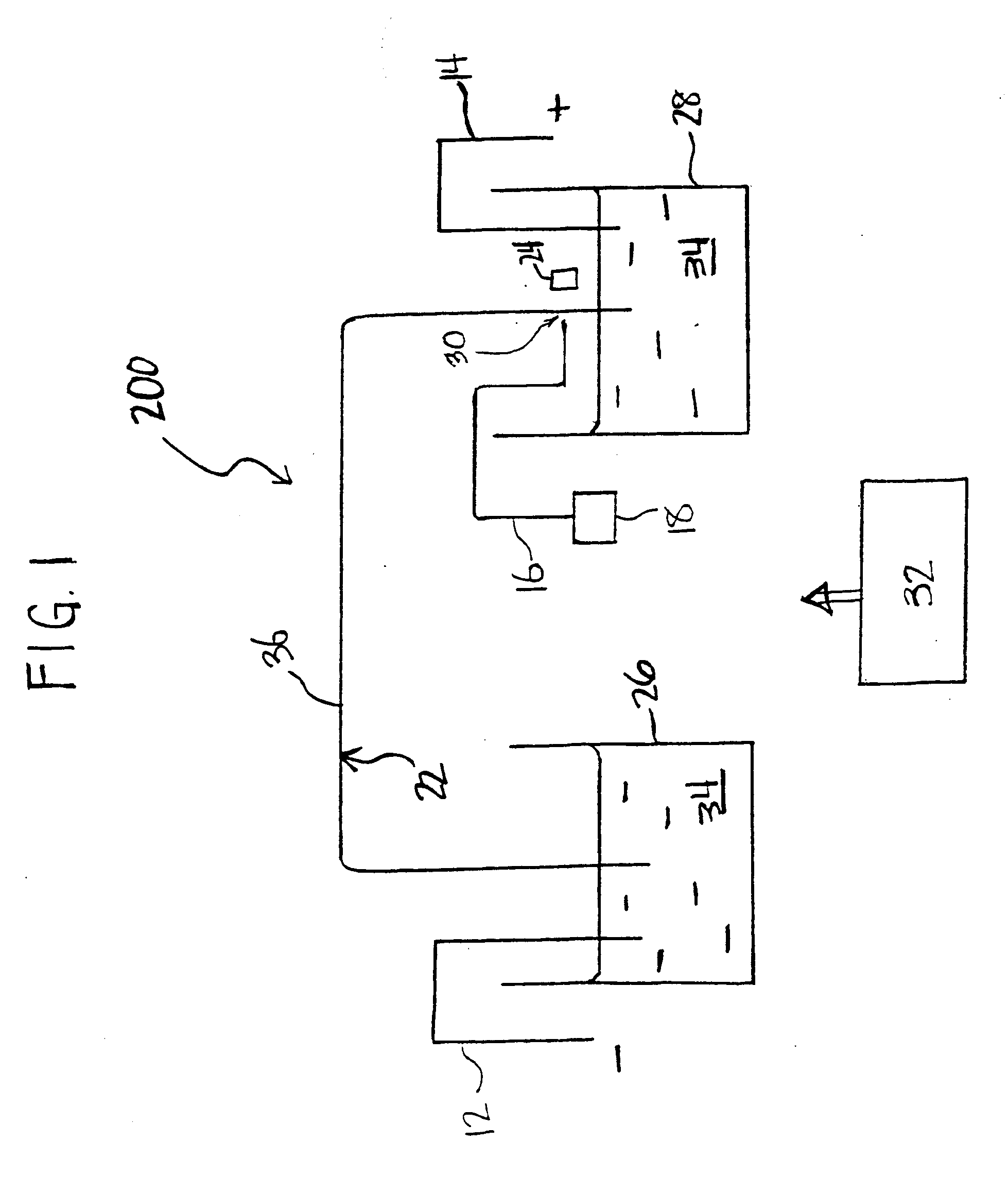

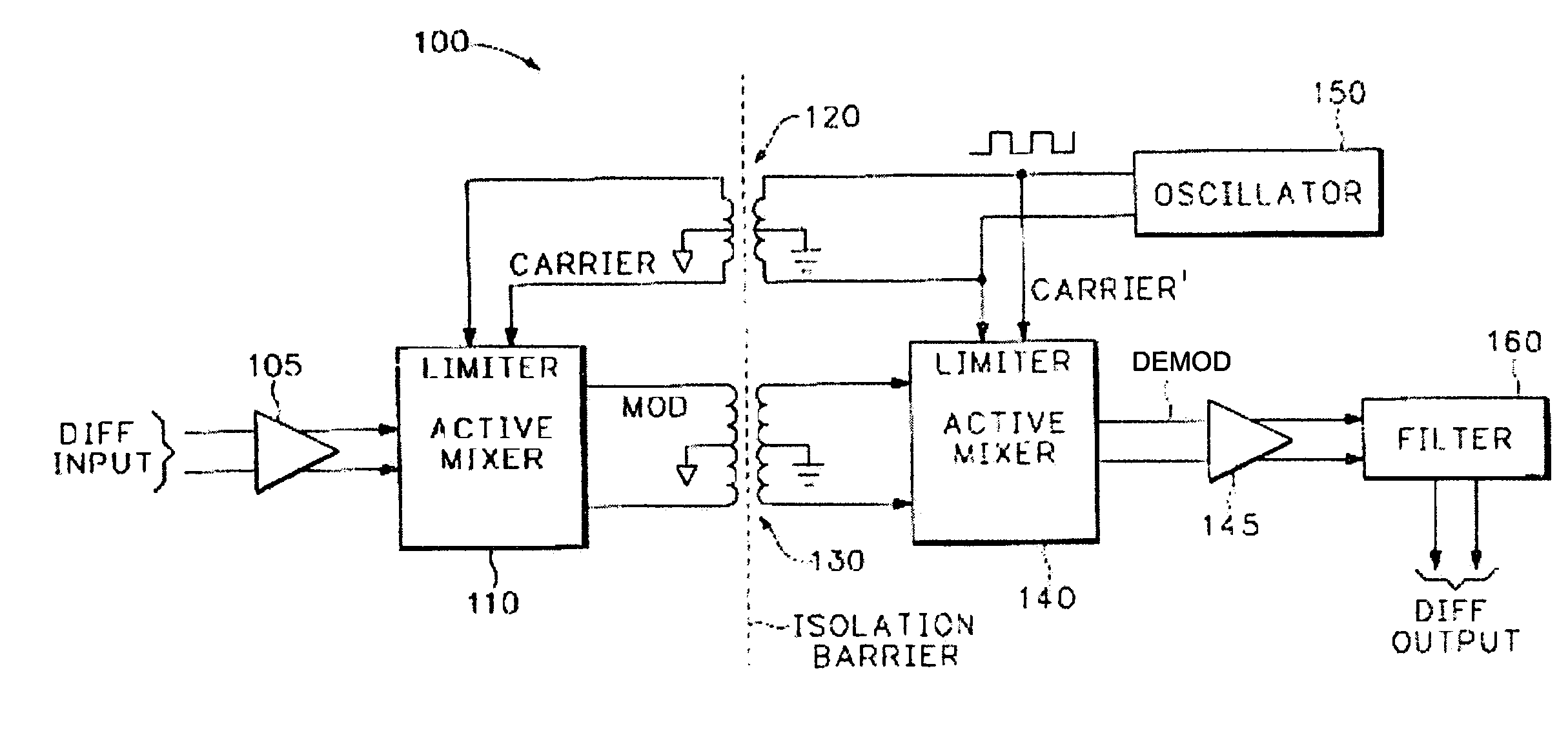

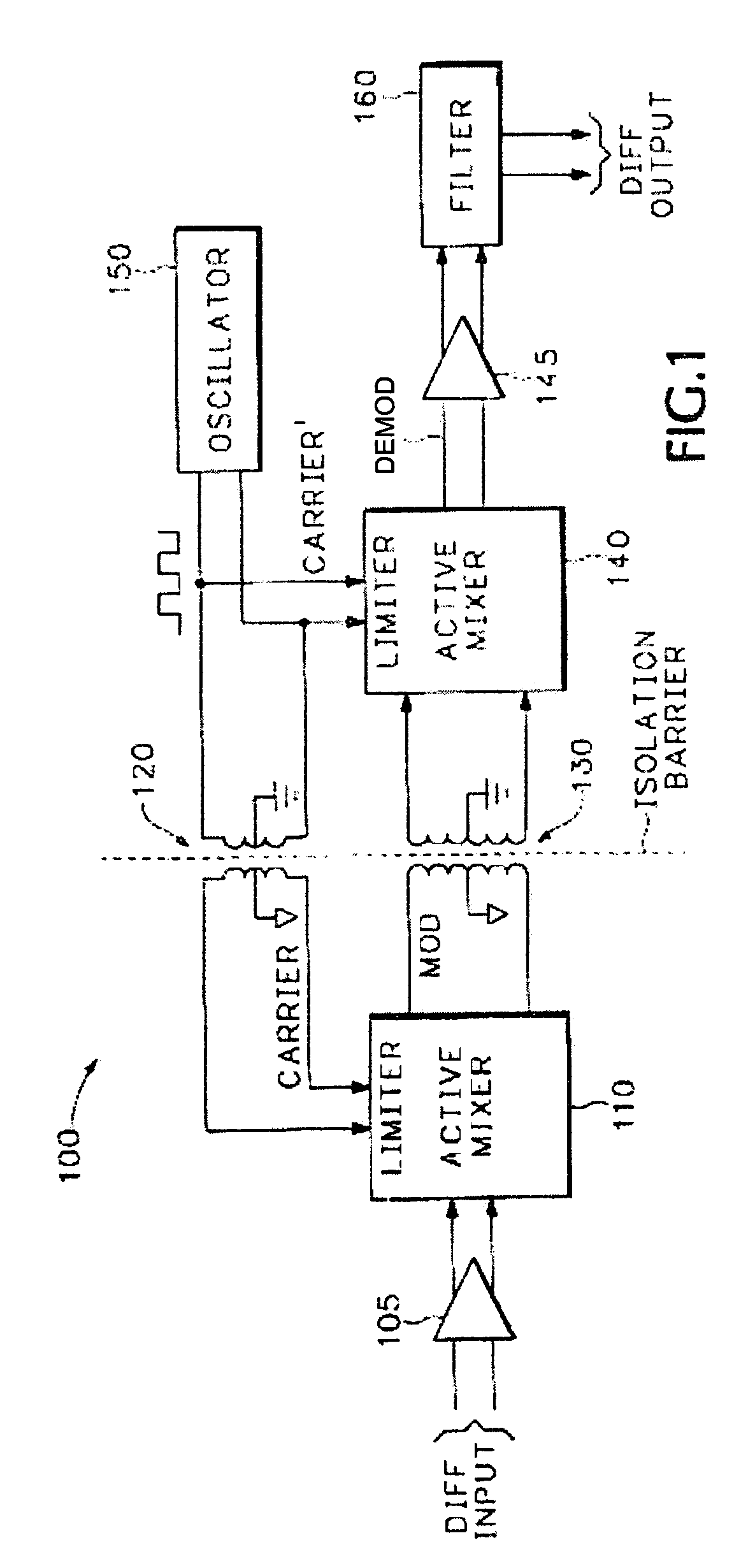

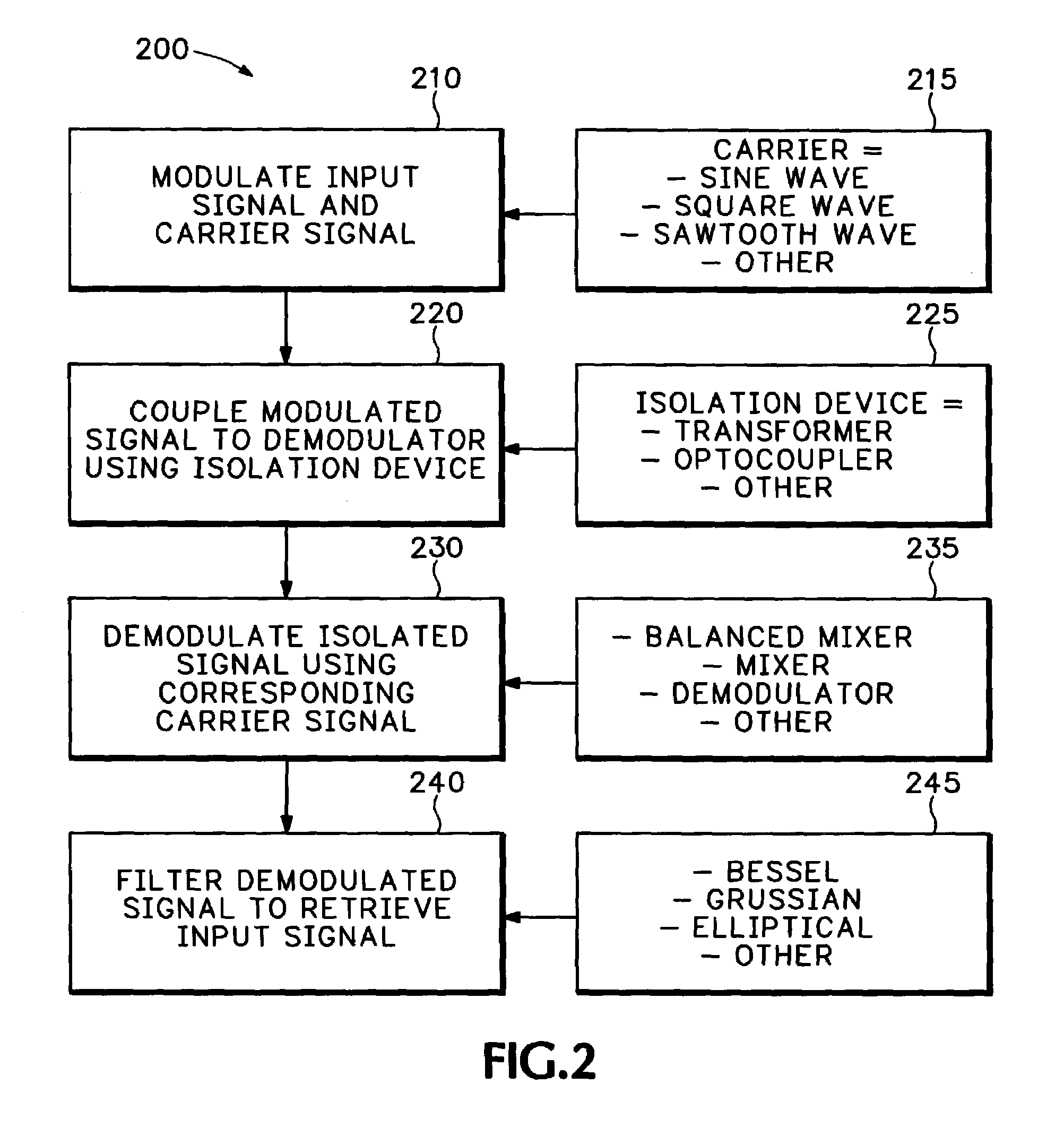

Apparatus and method for input channel isolation within an electronic test instrument

An electrical isolation device wherein a signal to be electrically isolated is mixed with a carrier signal by a multiplier to produce a modulated carrier signal which is passed through an isolation barrier and demodulated and filtered to extract thereby the initial input signal.

Owner:TEKTRONIX INC

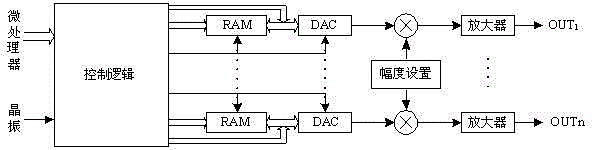

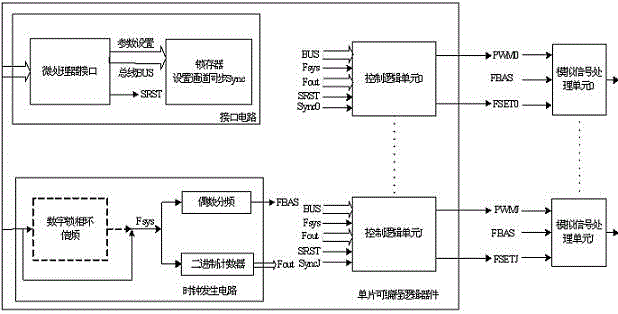

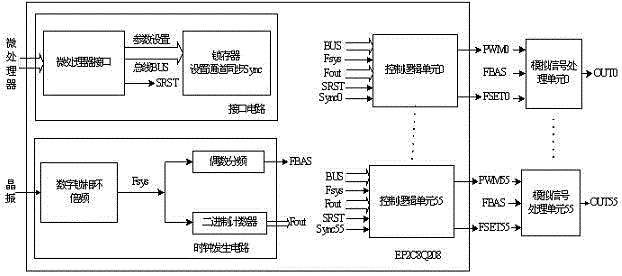

Multi-channel sinusoidal signal generator and method for generating multi-channel sinusoidal signals

InactiveCN103607174AImprove scalabilityPromote expansionElectrical apparatusControl signalPhase difference

The invention discloses a multi-channel sinusoidal signal generator and a method for generating multi-channel sinusoidal signals. By the adoption of the multi-channel sinusoidal signal generator and the method for generating the multi-channel sinusoidal signals, the sinusoidal signals of tens of or hundreds of channels can be directly generated, and the amplitude, the frequency, and the initial phase of each signal can be digitally set; synchronization of the signals of all channels or signals of a plurality of channels can be achieved, and phase difference can be set between every two same-frequency signals. A waveform generation circuit is composed of a single programmable logic device and multiple analog units. Each analog unit is controlled by an amplitude control signal, a phase frequency control signal and a public fundamental frequency square signal. At least 2N+1 control lines, for driving the N channel analog units, of the programmable logic device are arranged. According to the multi-channel sinusoidal signal generator, a storage, a DAC and an analog multiplier are not applied to the waveform generation circuit, and only one programmable logic device, N analog multi-channel switches, N four-operational-amplifiers and N dual-operation-amplifiers are adopted, so that the hardware cost is low, and an analog circuit is simple. The multi-channel sinusoidal signal generator and the method for generating the multi-channel sinusoidal signals are suitable for application occasions requiring one or more characteristics such as a large number of channels, channel synchronization, and channel isolation.

Owner:HARBIN UNIV OF SCI & TECH

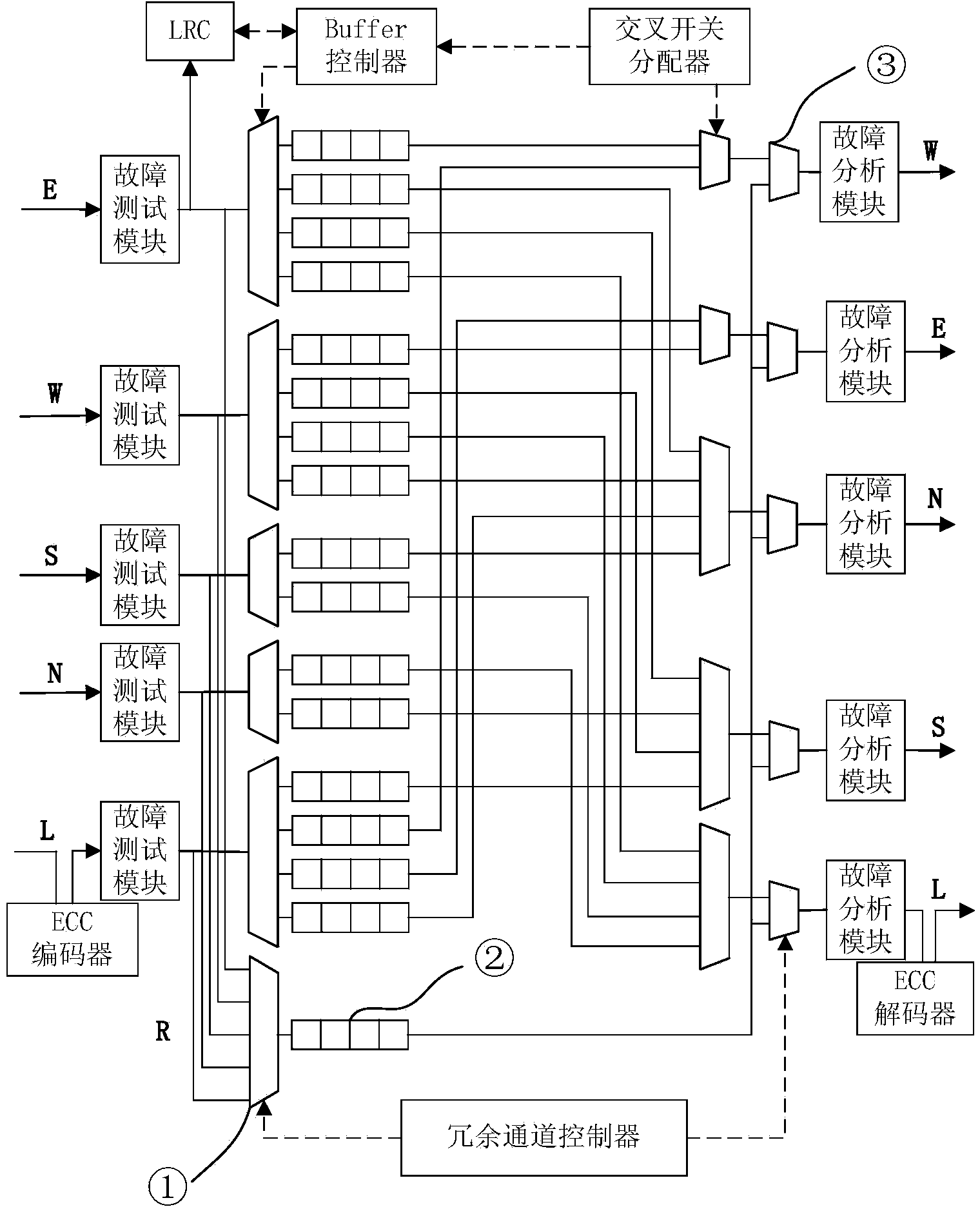

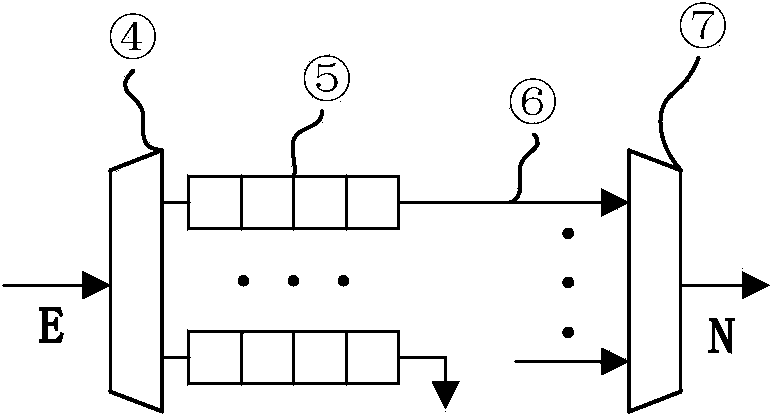

Router fault-tolerant method based on fault channel separation detection in NoC

ActiveCN104052622AReduce overheadImprove performanceError prevention/detection by using return channelData switching networksData transmissionThroughput

The invention provides a router fault-tolerant method based on fault channel separation detection in a NoC. A fault channel separation detection technology is used for detecting the channel fault in a router, so that fault detection does not influence normal data transmission; a Buffer with a recovery pointer is used for temporarily storing transmitted data and for retransmitting wrong data in a fault channel so as to reduce the fault-tolerant spending of the router; meanwhile, a redundancy channel is additionally arranged to be used for transmitting the data in a permanent fault channel. According to the router fault-tolerant method based on fault channel separation detection in the NoC, a low hardware cost is used, normal data transmission can be conducted during fault detection, so that network delay is lowered, and the network throughput is improved.

Owner:黄山市开发投资集团有限公司

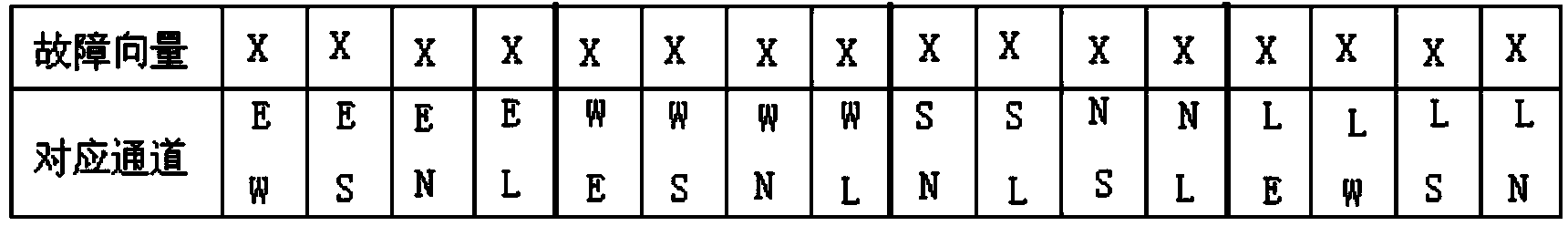

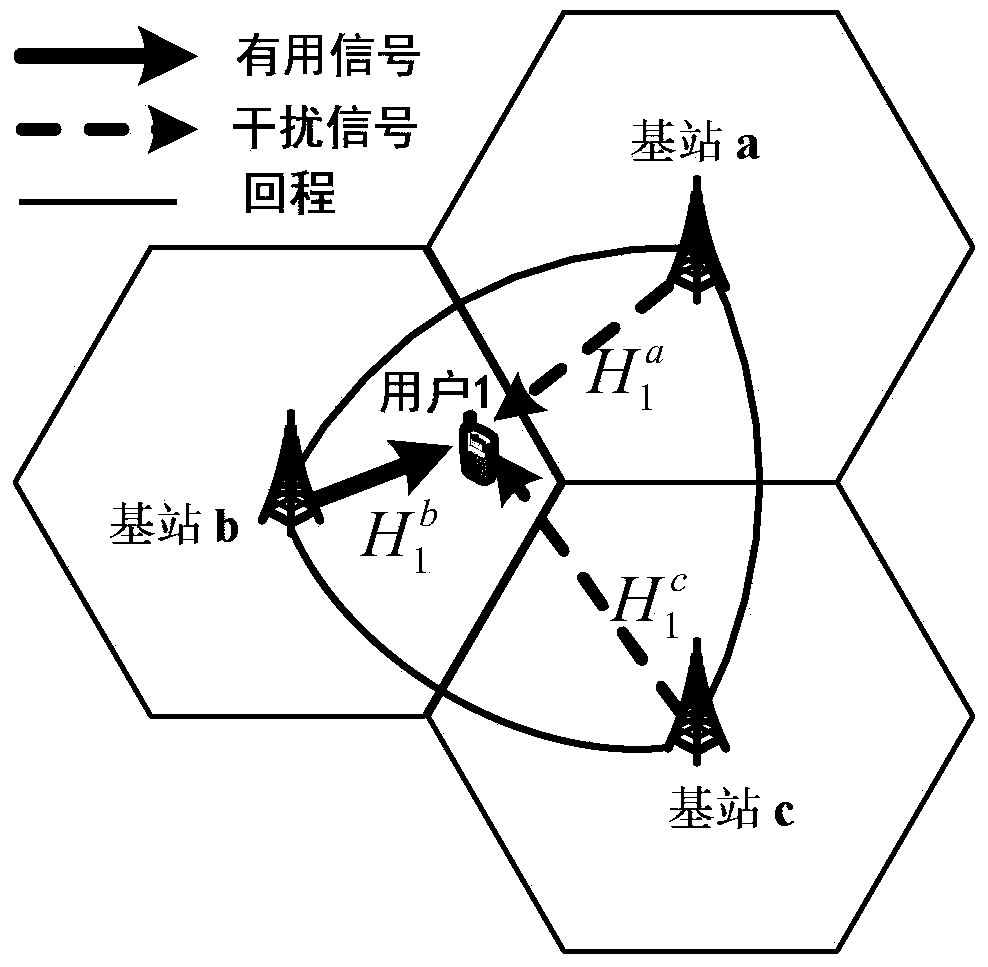

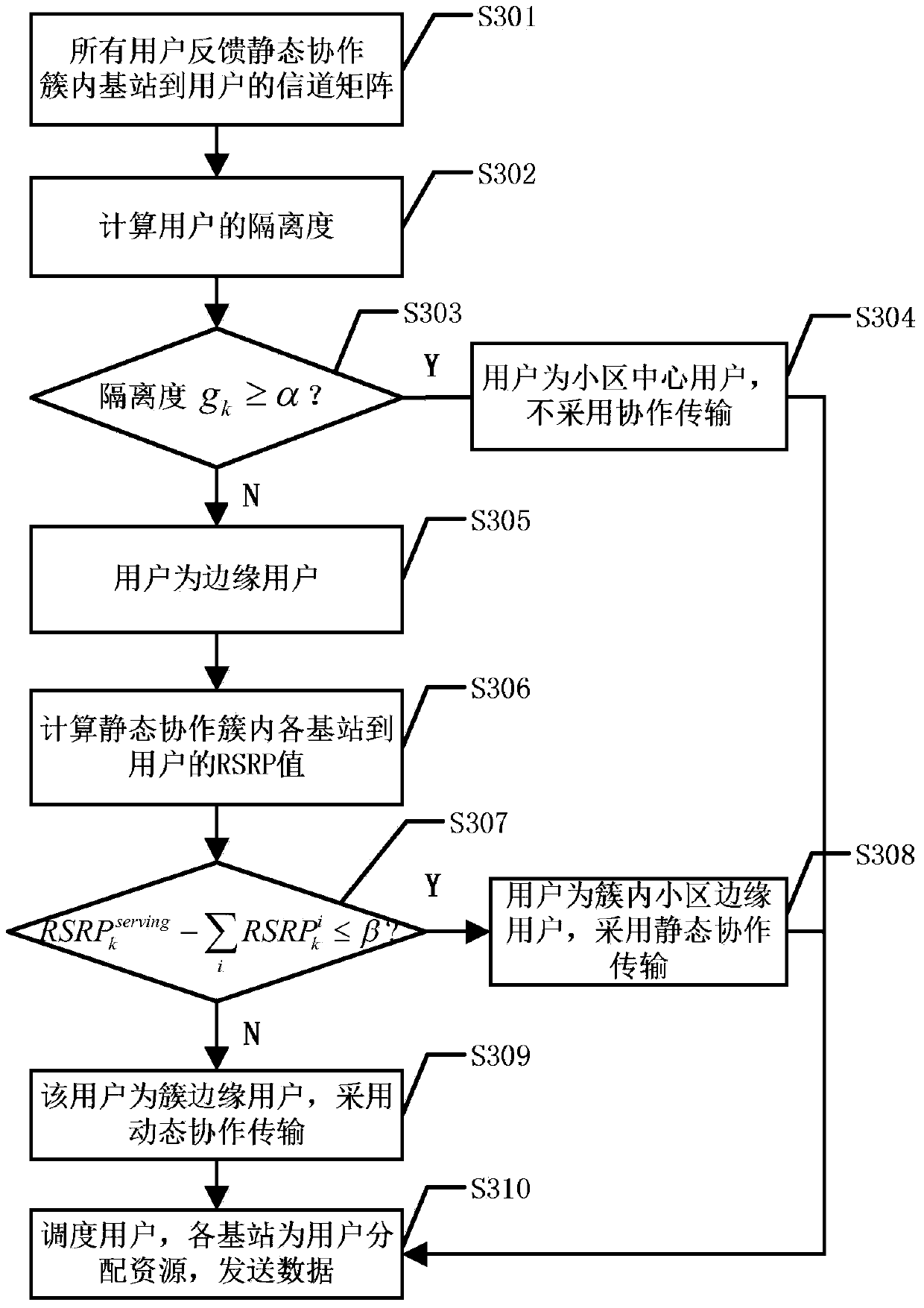

Cooperative clustering transmission method

InactiveCN103747531AReduce distractionsReduce complexityDiversity/multi-antenna systemsTransmission path multiple useRound complexityCell site

The invention discloses a cooperative clustering transmission method which comprises the following steps: users are firstly divided into cell-center users and edge users according to channel isolation; then, the edge users are further divided into intra-cluster cell-edge users and cluster edge users according to received signal power of each user; and finally, non-cooperative, static cluster cooperative and dynamic cluster cooperative schemes are respectively adopted for the three different types of users so as to reduce interference from intra-cluster other cell sites as well as interference from inter-cluster other sites. According to the invention, different cooperative transmission modes are adopted according to different types of users, and good throughput gain can be obtained by low complexity and return cost.

Owner:UNIV OF SCI & TECH BEIJING

Process for preparing shallow-channel isolating structure

InactiveCN1396643AHigh etch/deposition ratioGood trench filling abilitySemiconductor/solid-state device manufacturingHigh densityGas phase

A process for preparing shallow channel isolation (STI) structure includes such steps as providing substrate, generating pad oxide layer and mask layer on the substrate, removing part of pad oxide layer, mask layer and substrate to form a channel in the substrate, chemical gas-phase deposition by high-density plasma with high etching / deposition ratio to depositing insulating layer, depositing again with low etching / deposition ratio, removing the insulating layer except the channel, and removing mask layer and oxide layer.

Owner:MACRONIX INT CO LTD

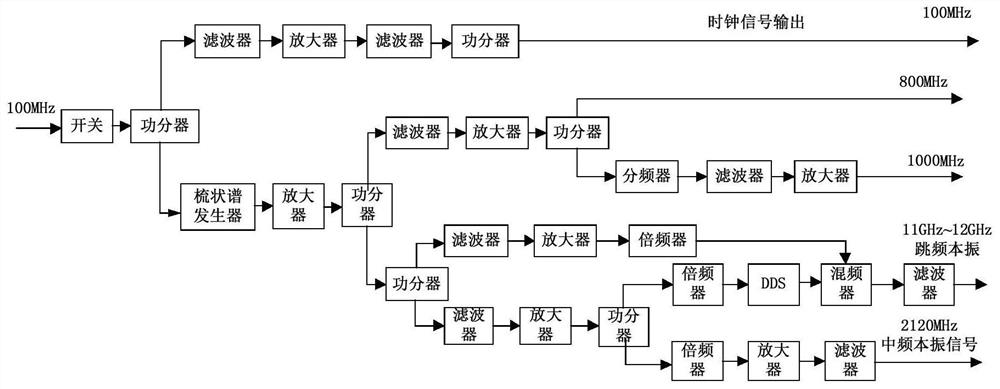

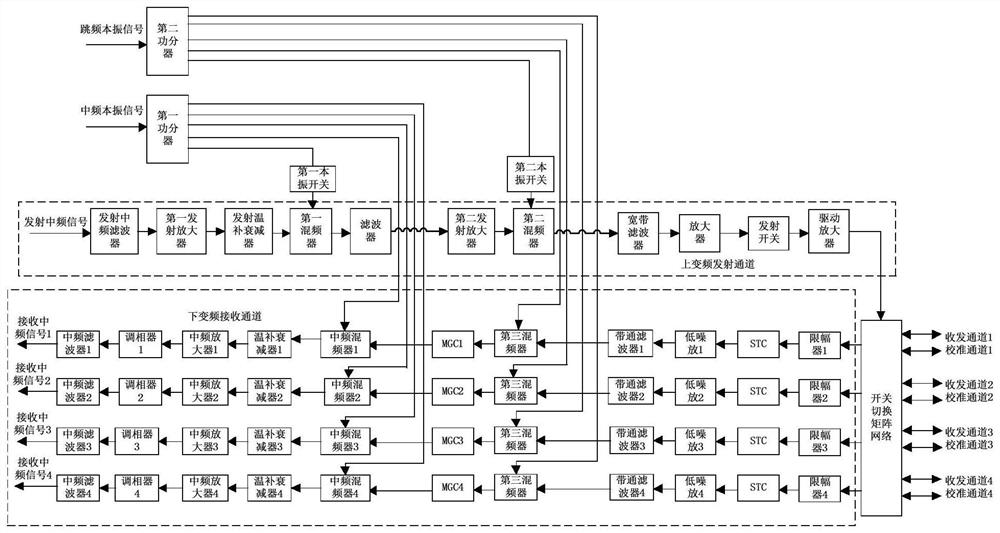

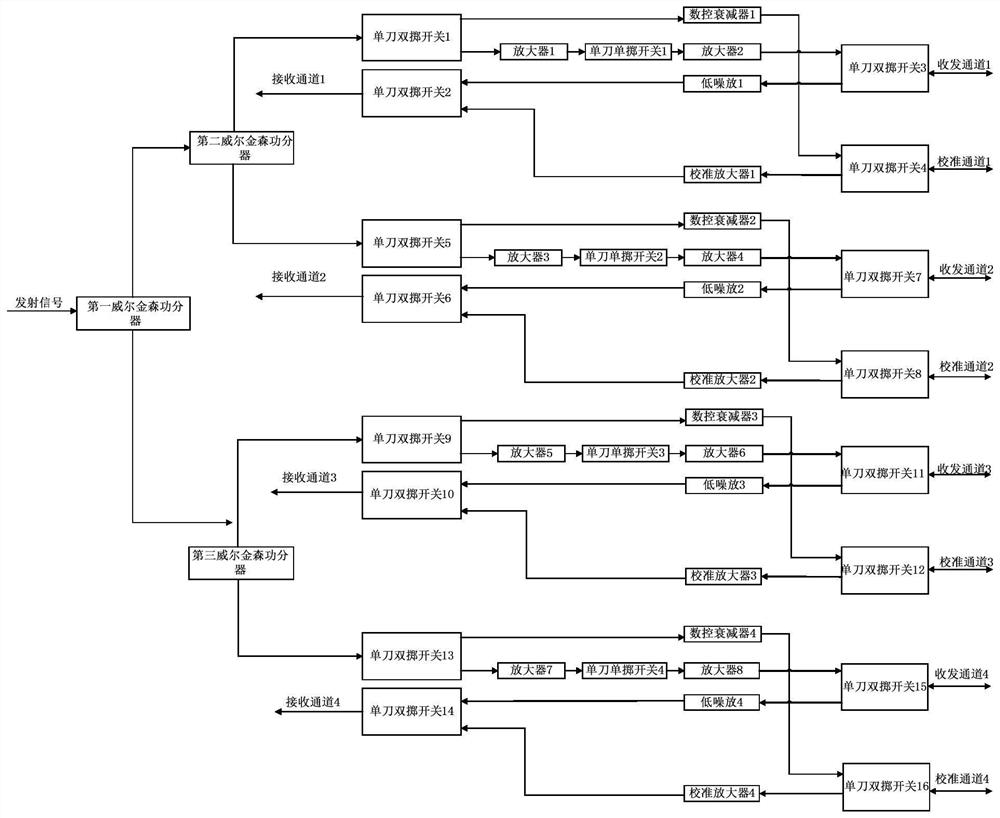

X-band high-isolation radio frequency transceiver system and channel consistency calibration method thereof

PendingCN113630194ASuppress spursHarmonic suppressionTransmitters monitoringReceivers monitoringLow noiseTransceiver

The invention relates to an X-band high-isolation radio frequency transceiver system and a channel consistency calibration method thereof, and relates to the technical field of radars, and the method comprises the steps: a calibration mode is set, and a calibration antenna receives an echo signal; the received echo signal is injected into a first-stage single-pole double-throw switch in the switch switching array network, then is subjected to low-noise amplification and then is input into a second-stage single-pole double-throw switch, and the signal is input into a down-conversion receiving channel; the down-conversion receiving channel outputs an intermediate frequency calibration signal after carrying out signal amplitude limiting processing, signal dynamic adjustment, spurious signal suppression, full temperature range gain compensation and phase consistency compensation. According to the invention, high channel isolation and switching of a plurality of working modes including a transceiving working mode, a calibration mode and the like are realized by adopting a switch assembly network. And meanwhile, the system also has the functions of sensitivity time control and manual gain control, and can realize large-dynamic-range echo signal processing and receiving under the condition of ensuring high isolation and multi-mode working conditions.

Owner:成都雷通科技有限公司

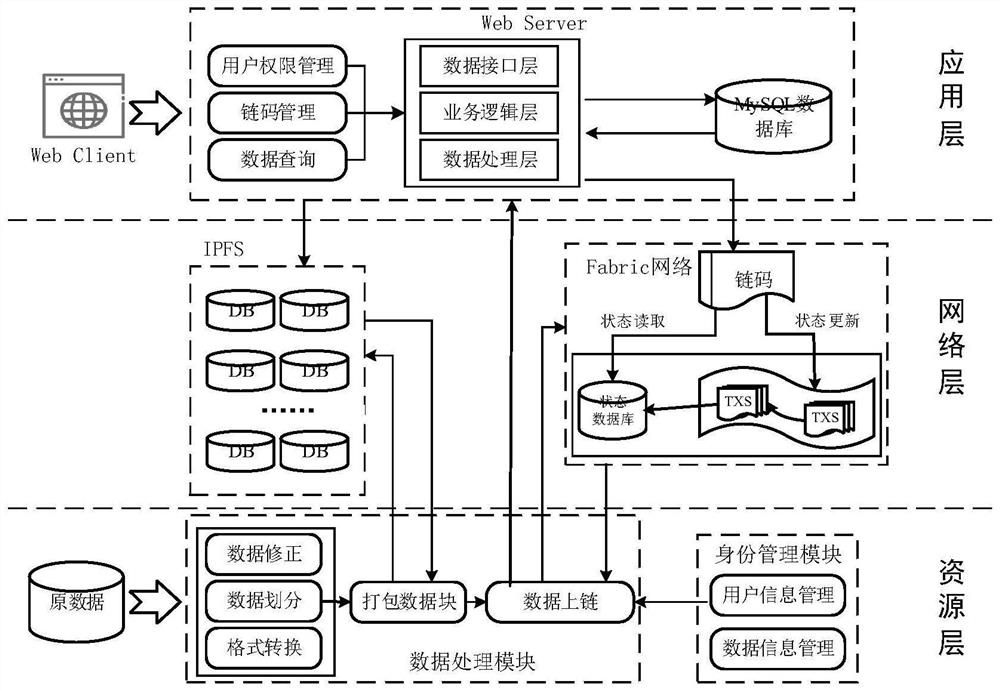

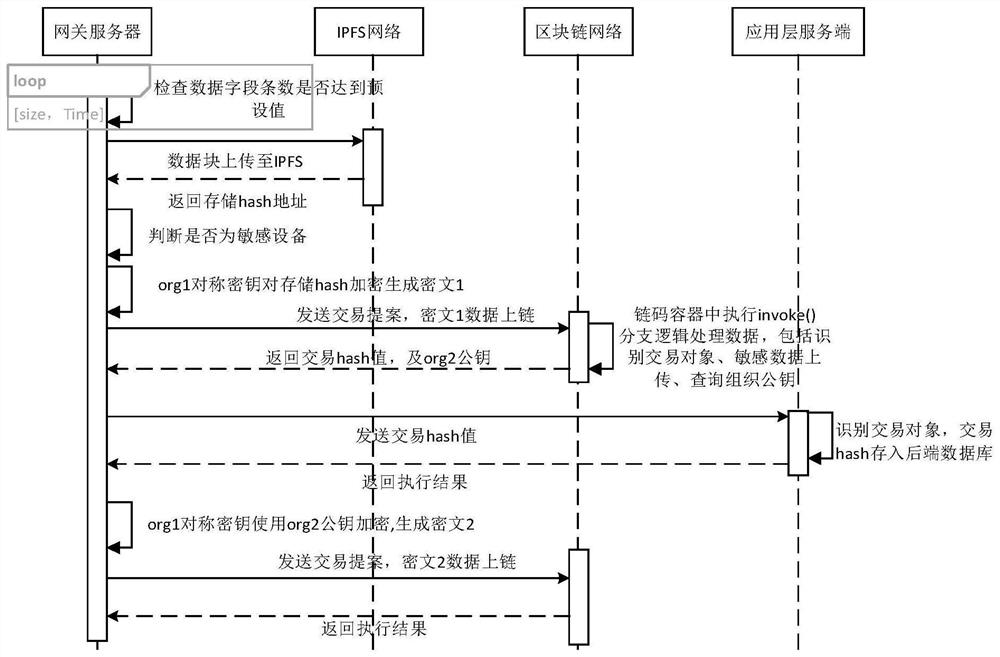

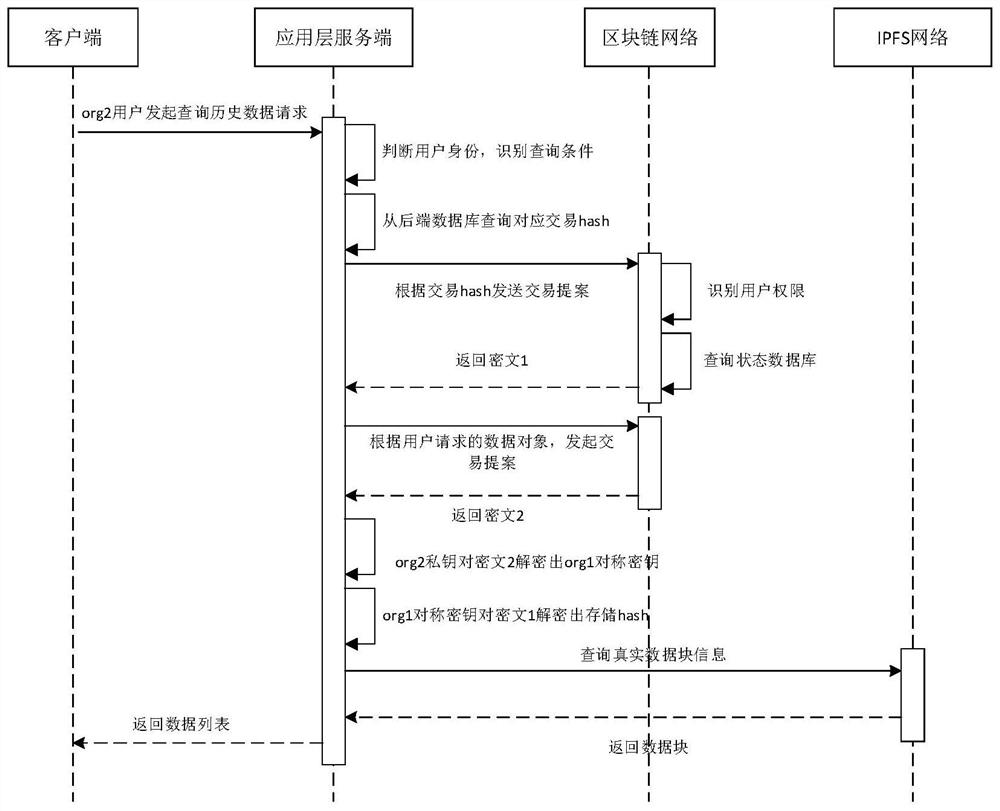

QAR data management method based on block chain technology

PendingCN112671580ARelieve pressureSolve data integrationData switching networksIdentity managementReliability engineering

The invention discloses a QAR data management method based on a block chain technology, and relates to the block chain technology and aviation information management. The architecture comprises a resource layer, a network layer and an application layer from bottom to top, in the network layer design, different organizations undertake different tasks, even if an identity authentication private key of a certain organization is leaked, only a certificate issued by an intermediate CA of the organization is influenced, and meanwhile, a more flexible and fine-grained sensitive data protection mechanism is adopted, so that the network performance is prevented from being influenced by coarse-grained modes such as channel isolation and the like; the resource layer corrects, divides and packages the data through a data processing module, an identity authentication mechanism of an identity management module ensures security of the data, and an IPFS is introduced to further reduce the network pressure of the blockchain; and the application layer directly faces users with different authorities under each organization to realize data sharing among the organizations. The problems of data fusion, equipment safety, information protection, multi-agent cooperation and the like in the construction process of the QAR data management system are effectively solved.

Owner:XIAMEN UNIV +1

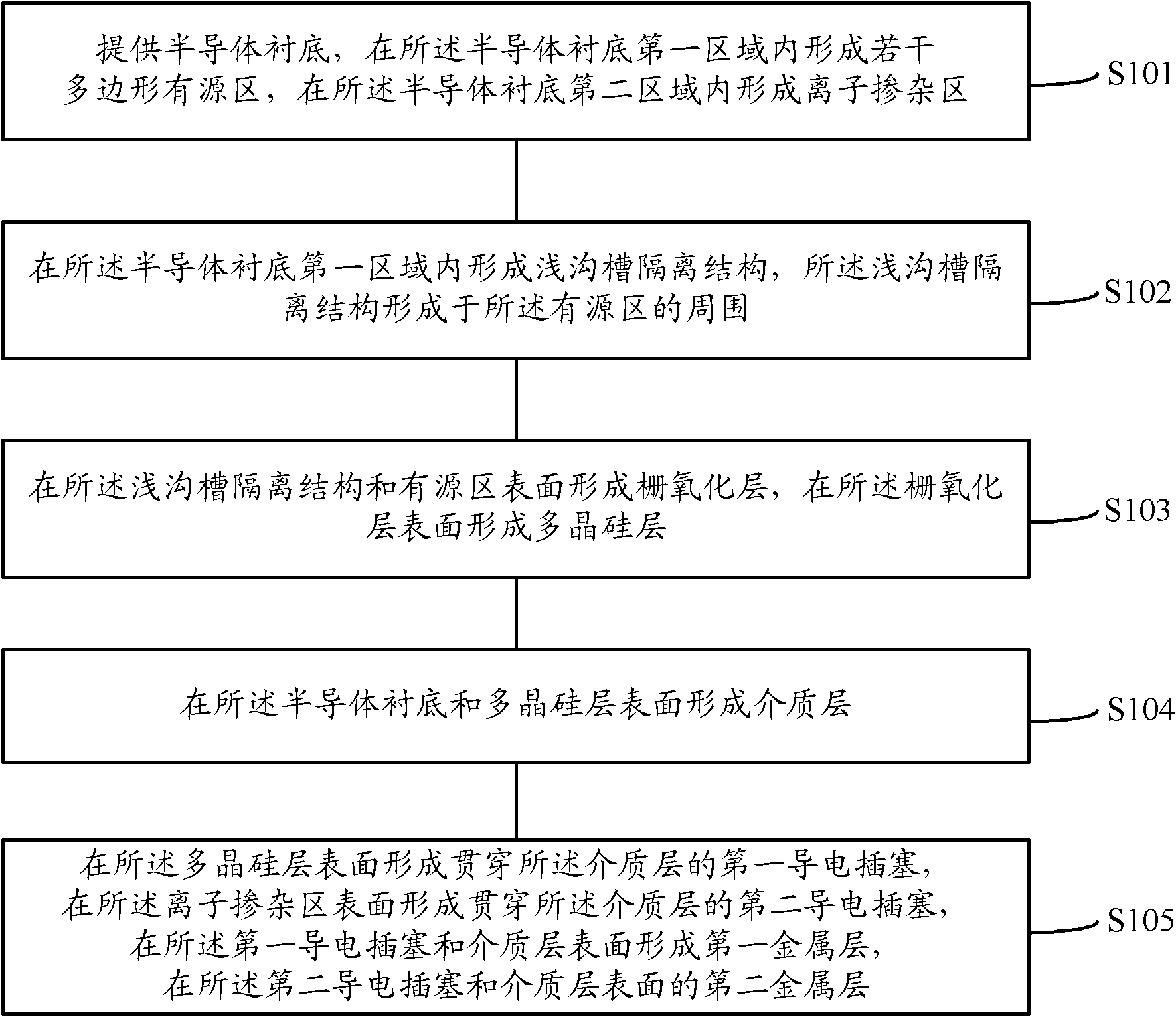

Detecting structure, forming method and detecting method

ActiveCN102931170AJudge eligibilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsIon mixingGate oxide

The invention discloses a detecting structure, a forming method and a detecting method. The detecting structure comprises a plurality of polygon active areas, a shallow channel isolation structure, an ion mixing area, a gate oxide layer, a polycrystalline silicon layer, a dielectric layer, a first conducting plug, a second conducting plug, a first metal layer and a second metal layer, wherein the polygon active areas are positioned in a first area of a semiconductor substrate; the shallow channel isolation structure is positioned in the first area of the semiconductor substrate and is formed surrounding the active areas; the ion mixing area is positioned in a second area of the semiconductor substrate; the gate oxide layer covers the active area and the shallow channel isolation structure; the polycrystalline silicon layer is positioned on the surface of the gate oxide layer; the dielectric layer covers the semiconductor substrate and the polycrystalline silicon layer; the first conducting plug is positioned on the surface of the polycrystalline silicon layer; the second conducting plug is positioned on the surface of the ion mixing layer, and the first metal layer and the second metal layer are positioned on the surface of the dielectric layer. According to the detecting structure disclosed by the invention, whether a corner of the active area of the detecting structure is damaged or not can be detected by measuring the puncture voltage of the gate oxide layer for one time, and thus whether a corner of an active area of a to-be-detected semiconductor device is damaged or not can be judged.

Owner:SEMICON MFG INT (SHANGHAI) CORP