Method for preparing field effect transistor

A field effect transistor and process method technology are applied in the field of preparation of quasi-SOI field effect transistors, and can solve the problems of complex preparation process, high preparation cost, limitation of quasi-SOI application, and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

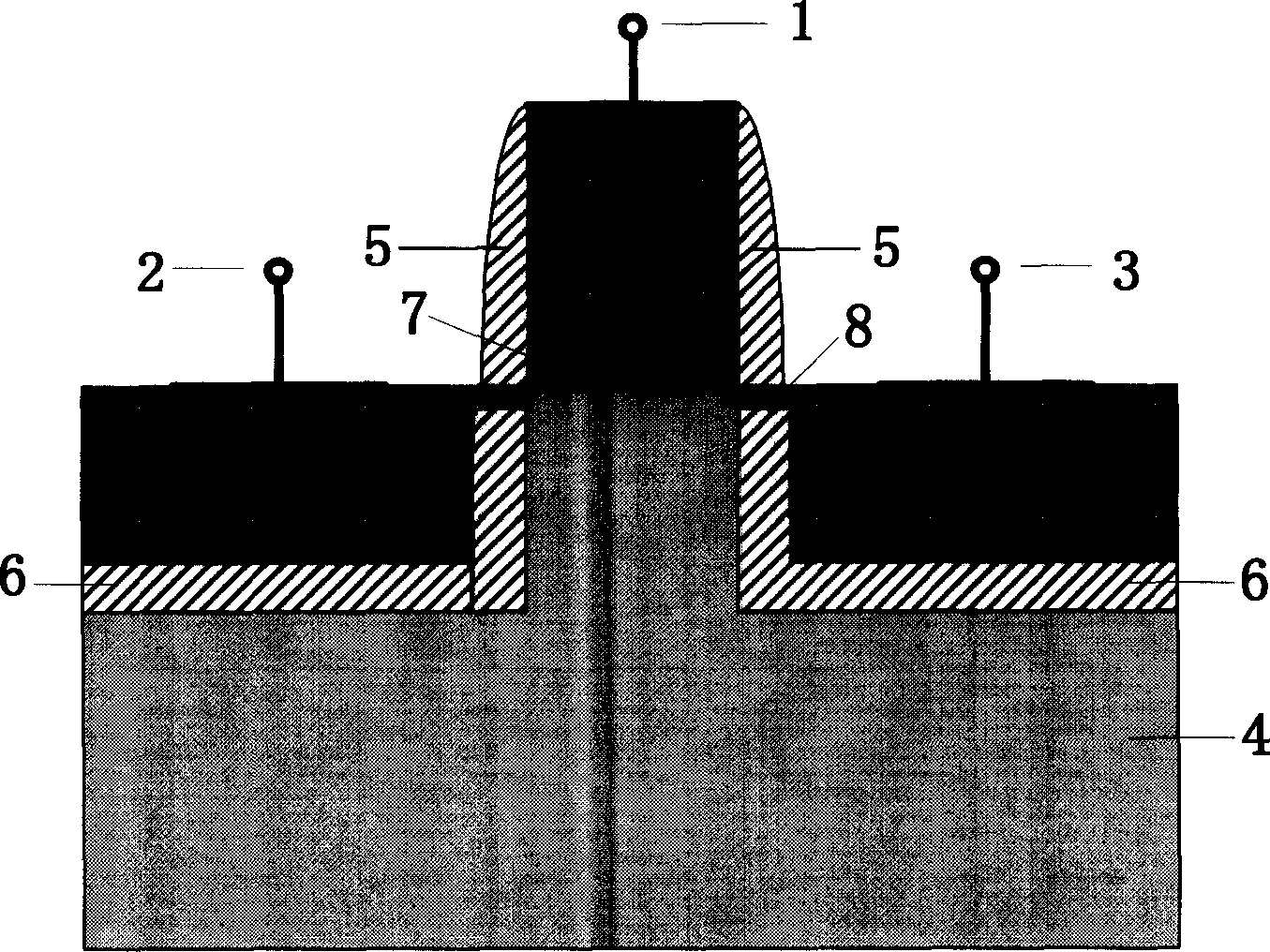

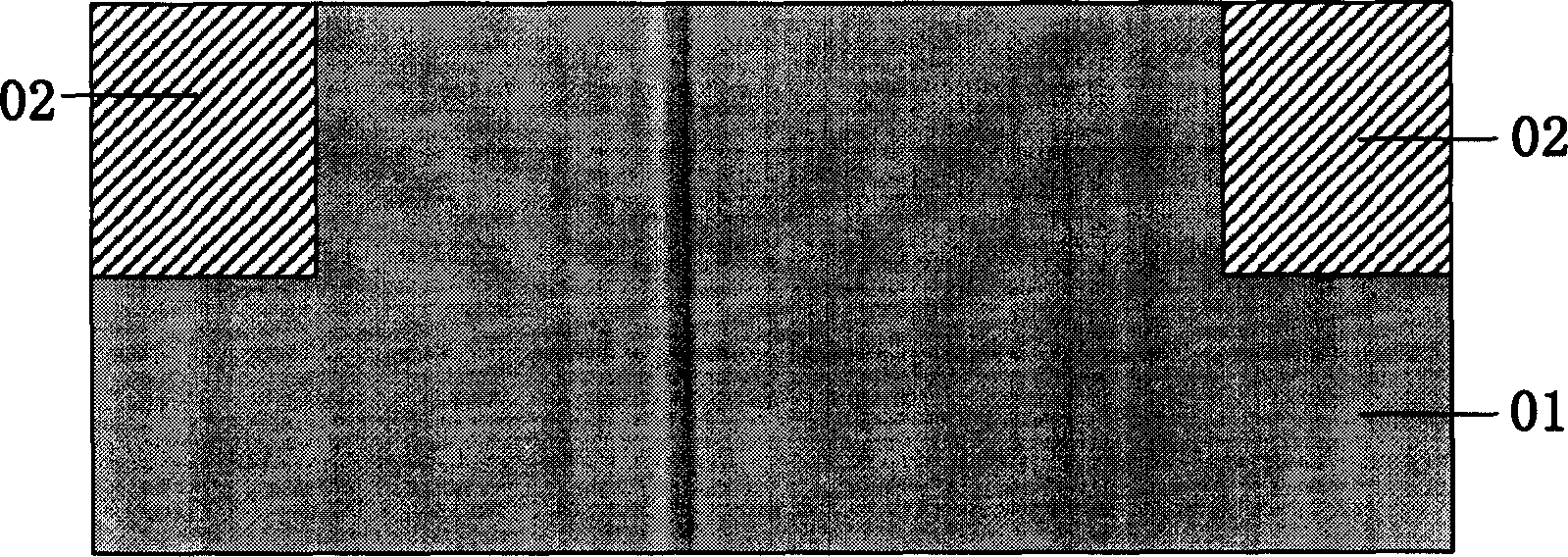

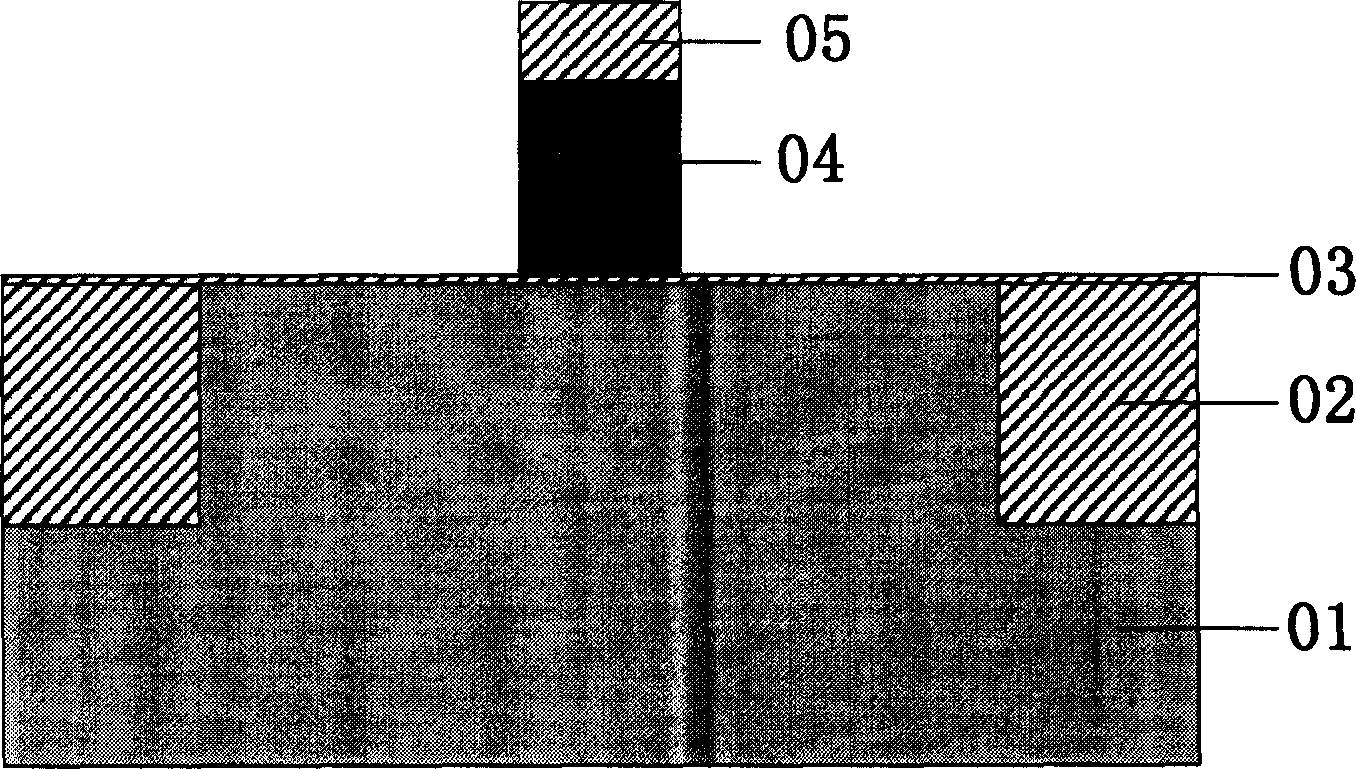

[0023] In the invention, the gate region and the channel region below it are firstly defined, and then the source and drain regions are formed. The specific method is as follows: the first step is to use a conventional process method to realize shallow trench isolation, deposit and etch the gate material and the hard mask material covering it to form the gate region, and then prepare the gate sidewall to protect the gate region. The wall thickness is L1. The second step is to form an oxide layer. First, etch the silicon in the source and drain regions to a certain depth h1, then deposit and etch anti-oxidation materials to form side walls with a width of L2, and then further etch the silicon material in the source and drain regions To the second depth h2, a deeper silicon groove is formed, and finally the exposed silicon is thermally oxidized to obtain an "L"-shaped silicon oxide with a thickness of L3. In order to ensure that the channel region is directly connected to the su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More