Patents

Literature

52results about How to "Avoid parasitic effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

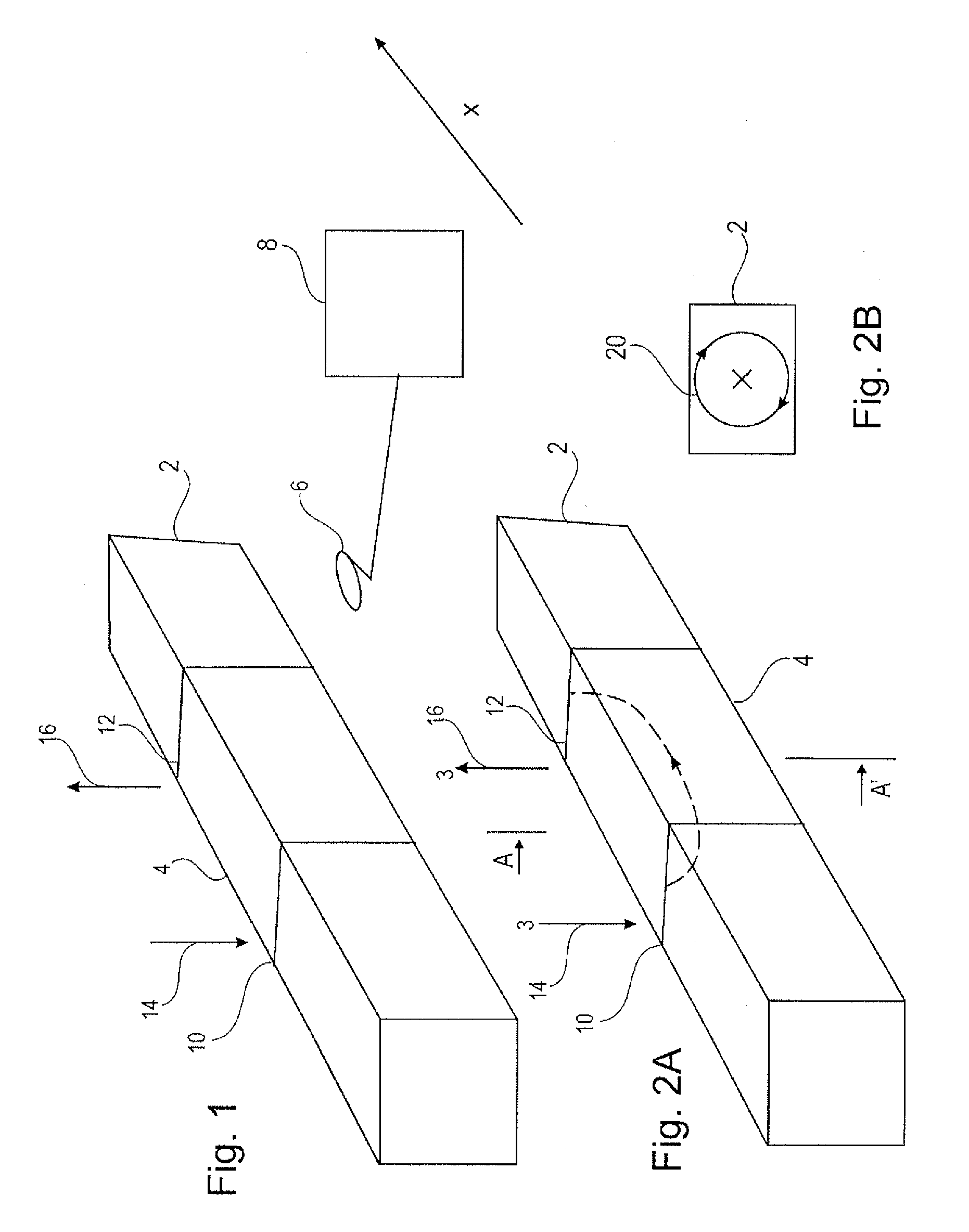

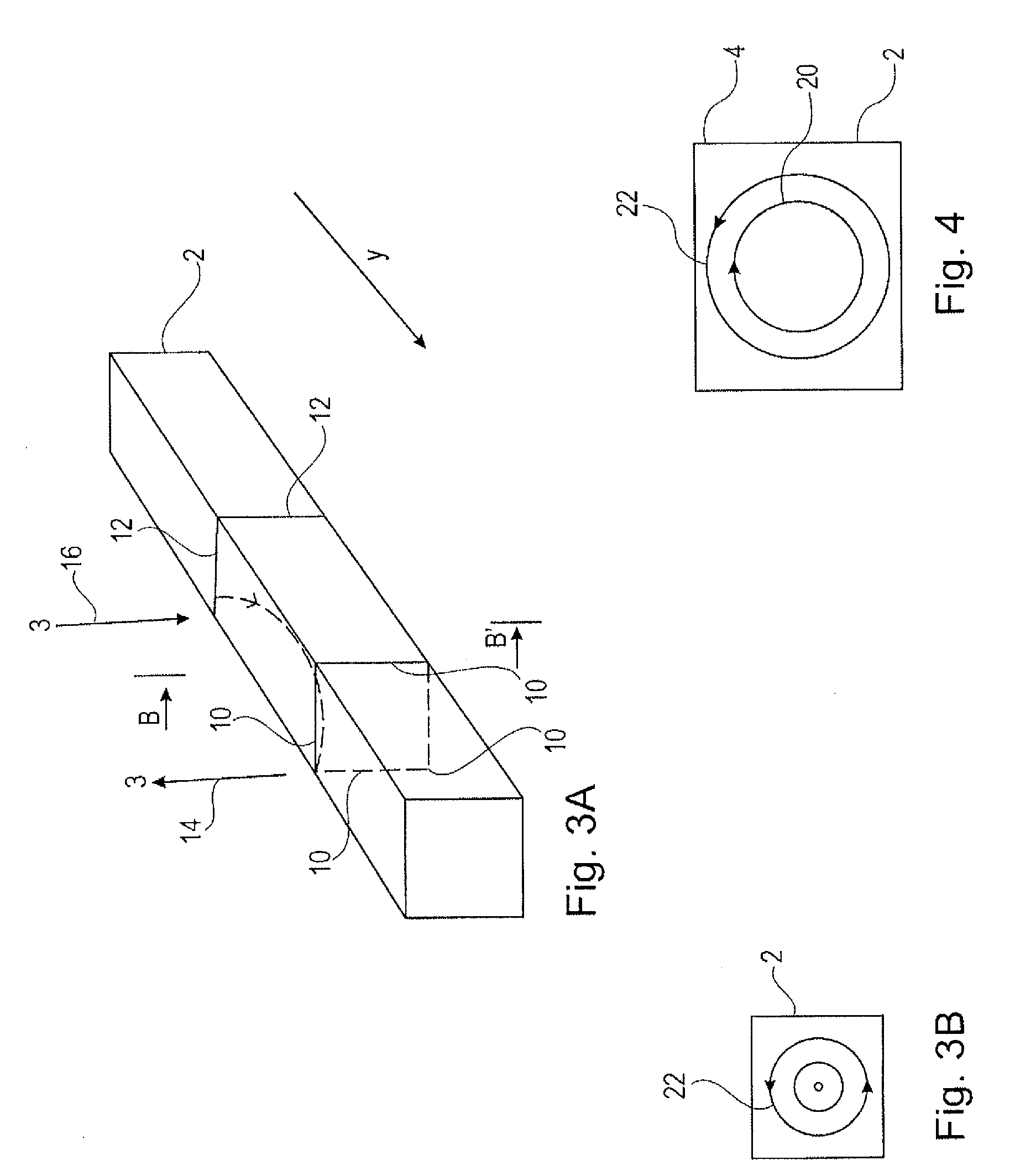

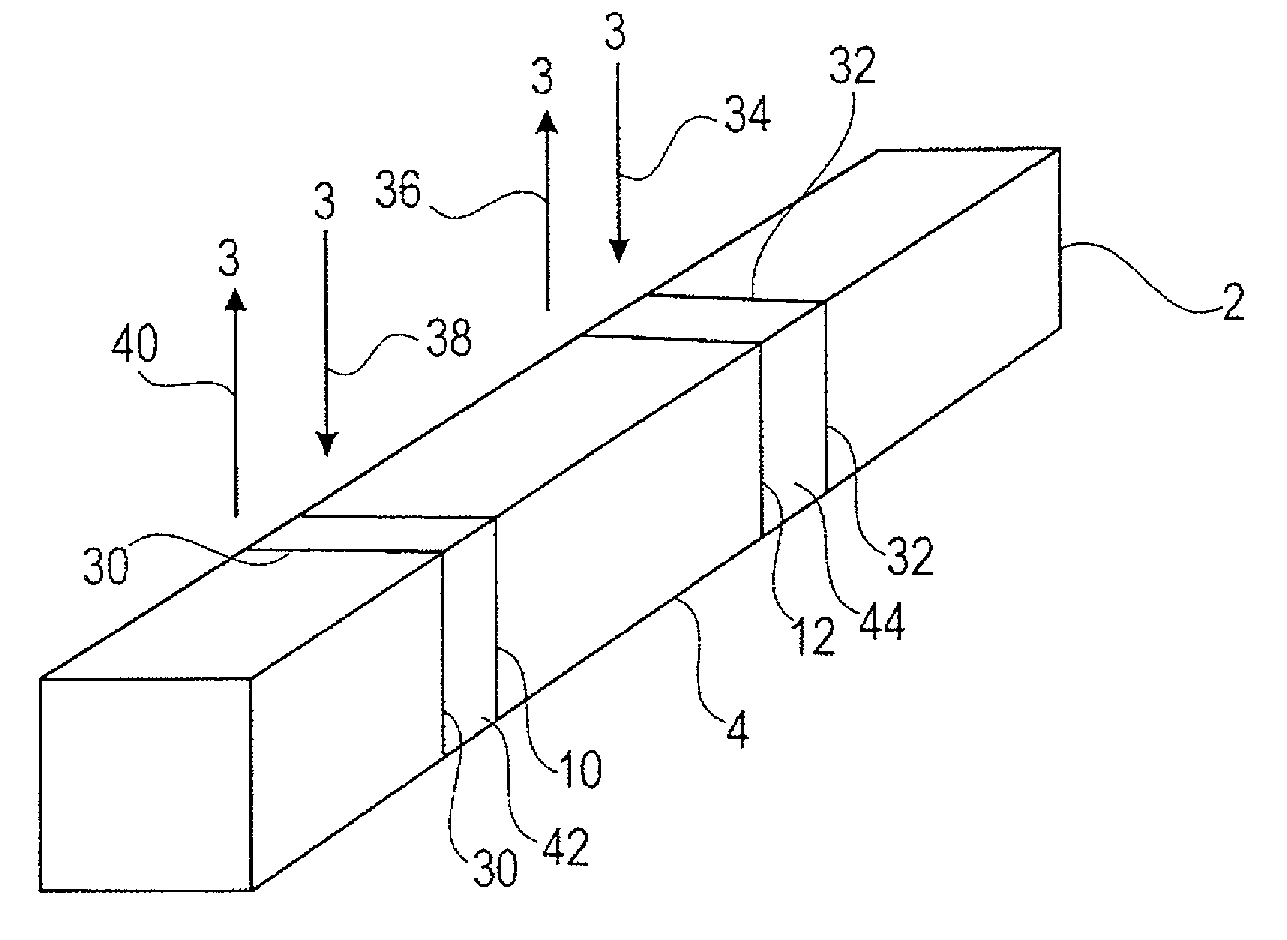

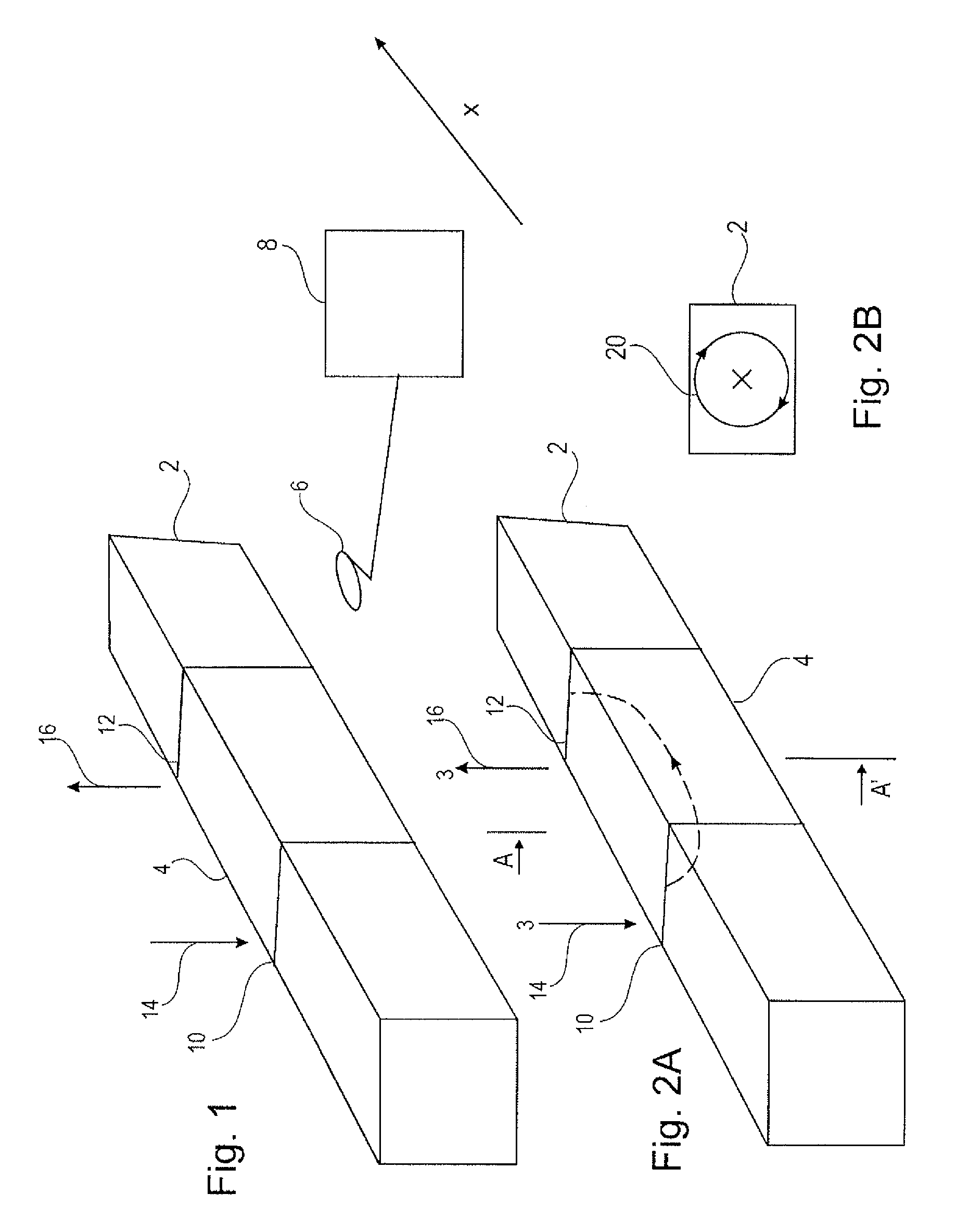

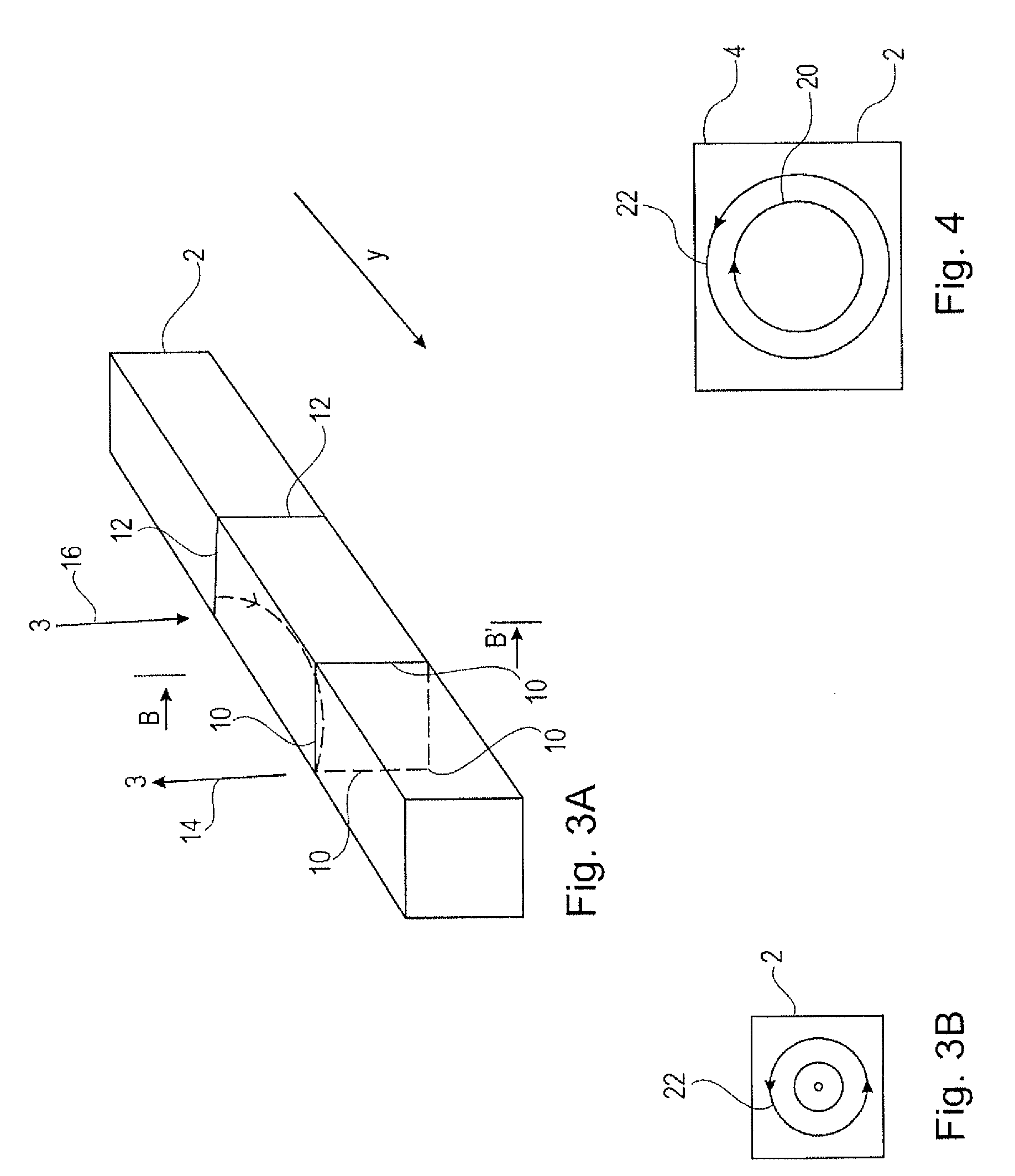

Method and an Array for Magnetizing a Magnetizable Object

ActiveUS20080316669A1Accurately define magnetizationLow effortMagnetic bodiesRelaysDegaussingComputer science

Described is a method and array for magnetizing a magnetizable object. The method includes the steps of (a) applying a first degaussing signal to the magnetizable object to degauss the magnetizable object and the first degaussing signal is an alternating electrical signal having a first frequency and a first amplitude; (b) applying a magnetizing signal to the degaussed magnetizable object to magnetize the magnetizable object; and (c) applying a second degaussing signal to the magnetized magnetizable object to partially degauss the magnetized magnetizable object and the second degaussing signal is an alternating electrical signal having a second frequency and a second amplitude.

Owner:NCTE

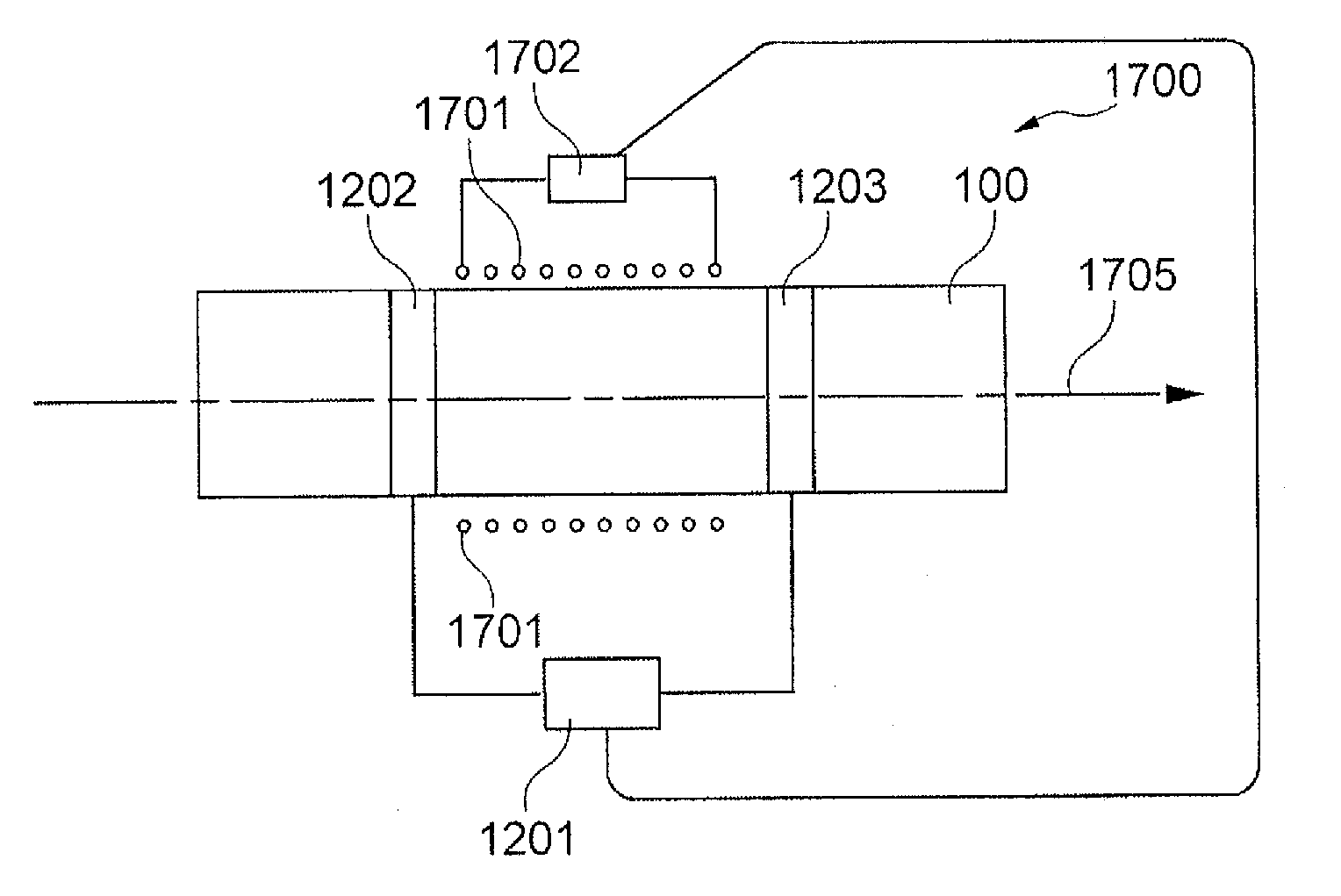

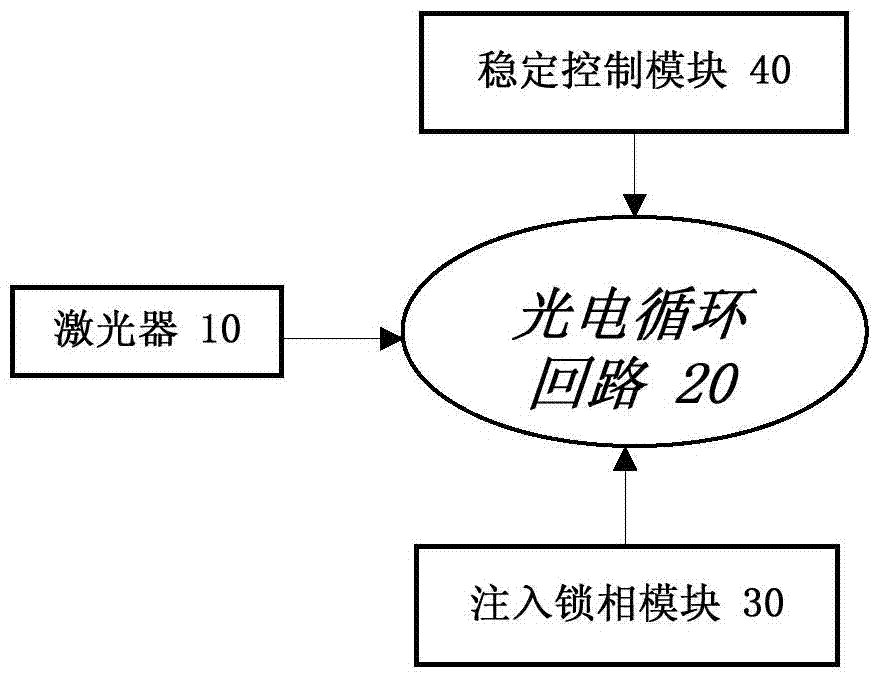

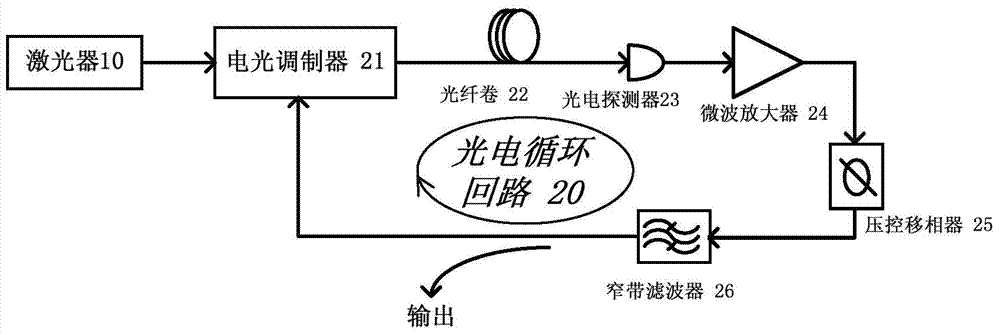

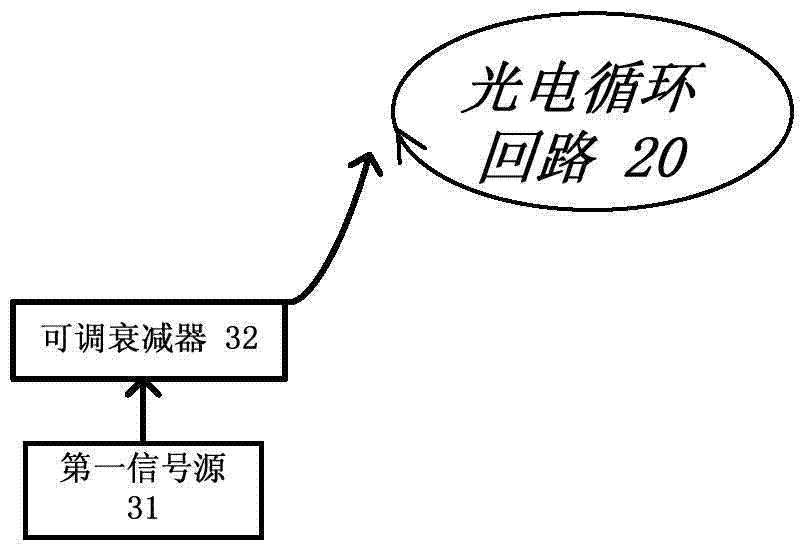

Optoelectronic oscillator

ActiveCN104767102AImplement Stability ControlAchieve low phase noise performanceSolid masersResonant cavityOptoelectronics

The invention discloses an optoelectronic oscillator which comprises a laser device used for outputting optical carriers. The laser device is connected with an optoelectronic circulation circuit for forming an optoelectronic mixing resonant cavity. The optoelectronic oscillator further comprises an injection phase-locking module and a stable control module, the injection phase-locking module is used for injecting a locking signal to the optoelectronic circulation circuit to achieve side-mode suppression, and the stable control module is used for pilot control so as to compensate delay fluctuation of the optoelectronic circulation circuit. The injection phase-locking module is arranged to inject the locking signal to the optoelectronic circulation circuit to achieve side-mode suppression, the stable control module is arranged to extract delay fluctuation of all devices of the optoelectronic circulation circuit and carry out corresponding delay fluctuation compensation, so that the aim of stabilizing oscillation frequency is achieved, and therefore low-phase-noise single-mode stable output of the optoelectronic oscillator is achieved. Due to the fact that pilot control and circulating oscillation locked by injecting the locking signal are carried out in different frequency bands, mutual interference is avoided, and the parasitic effect of control circuit noise on an oscillation signal is effectively avoided.

Owner:台晶(重庆)电子有限公司

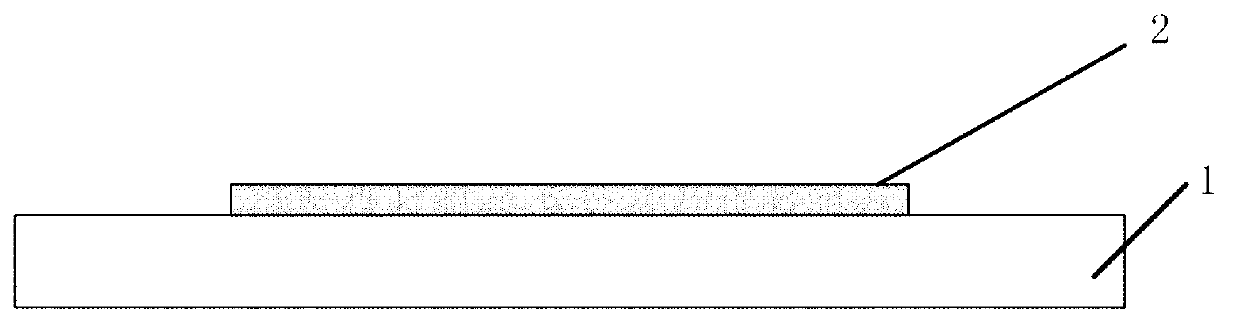

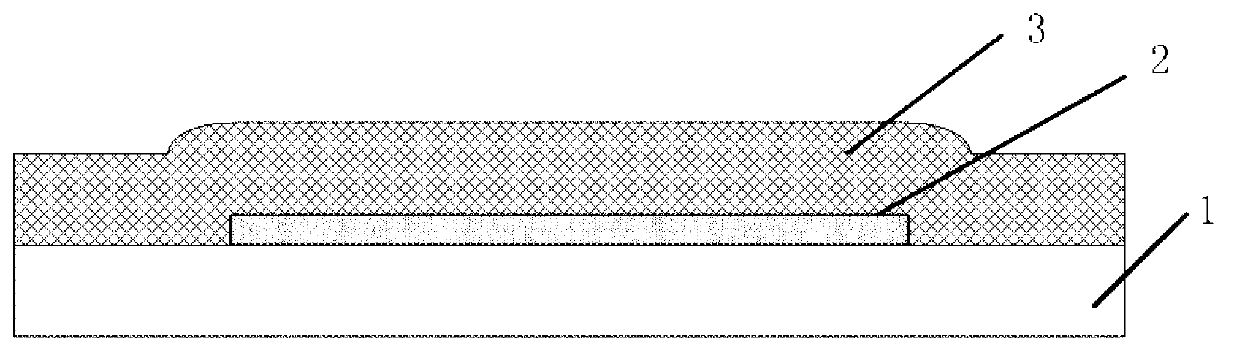

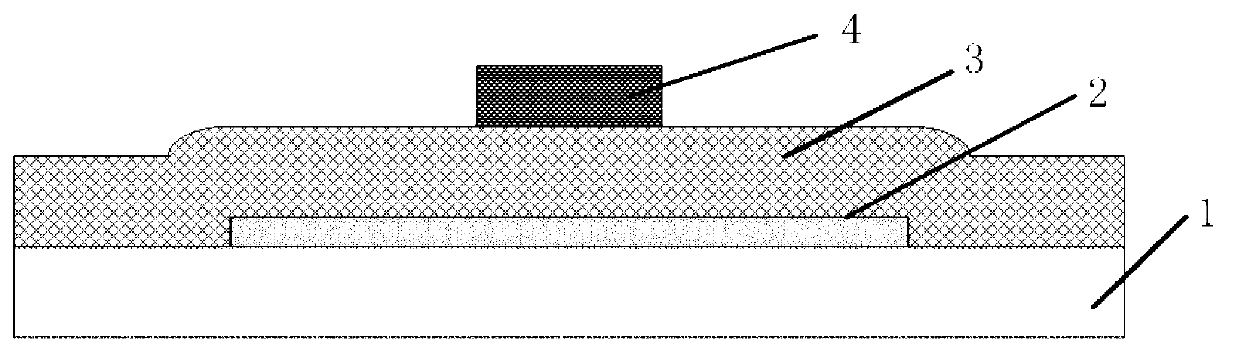

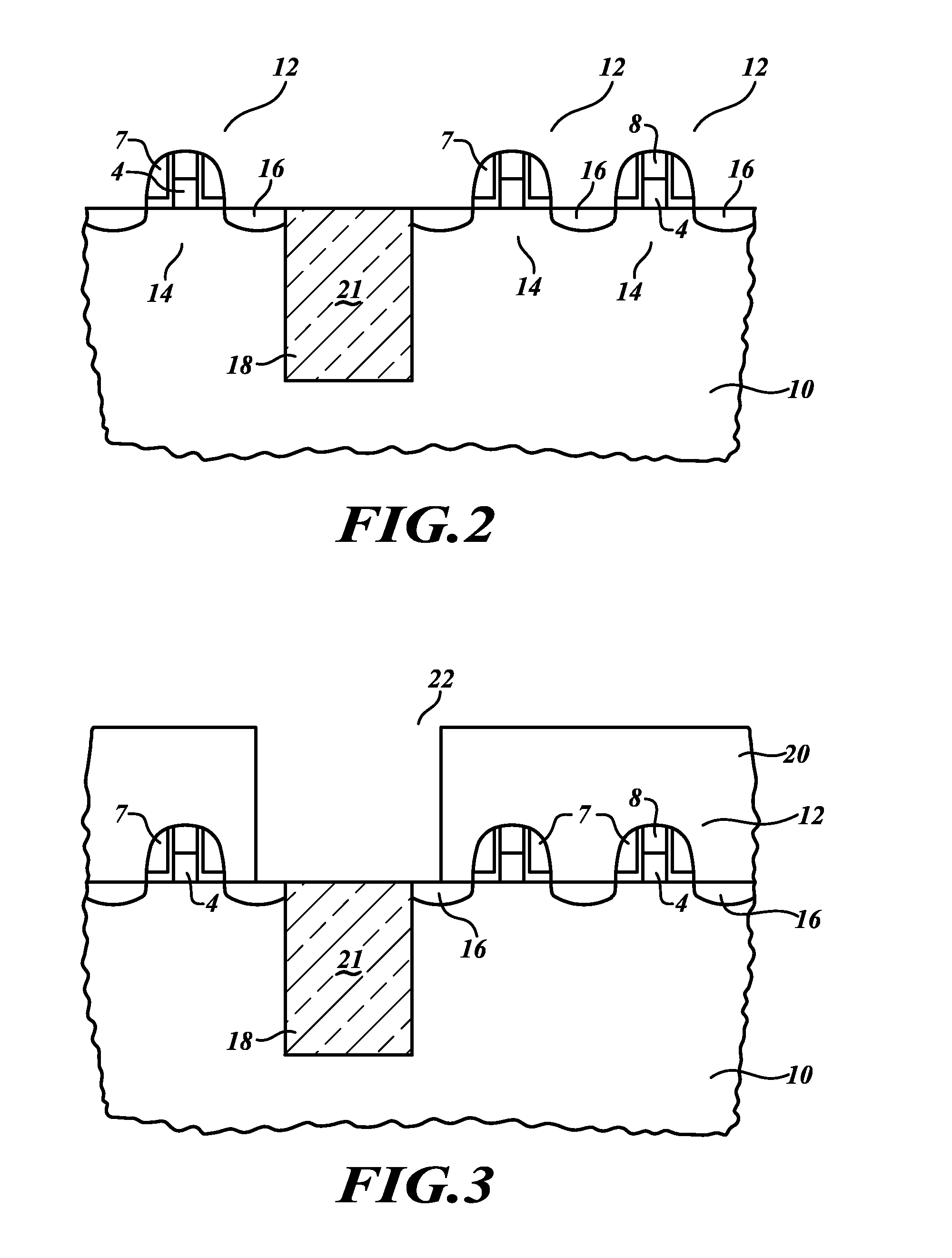

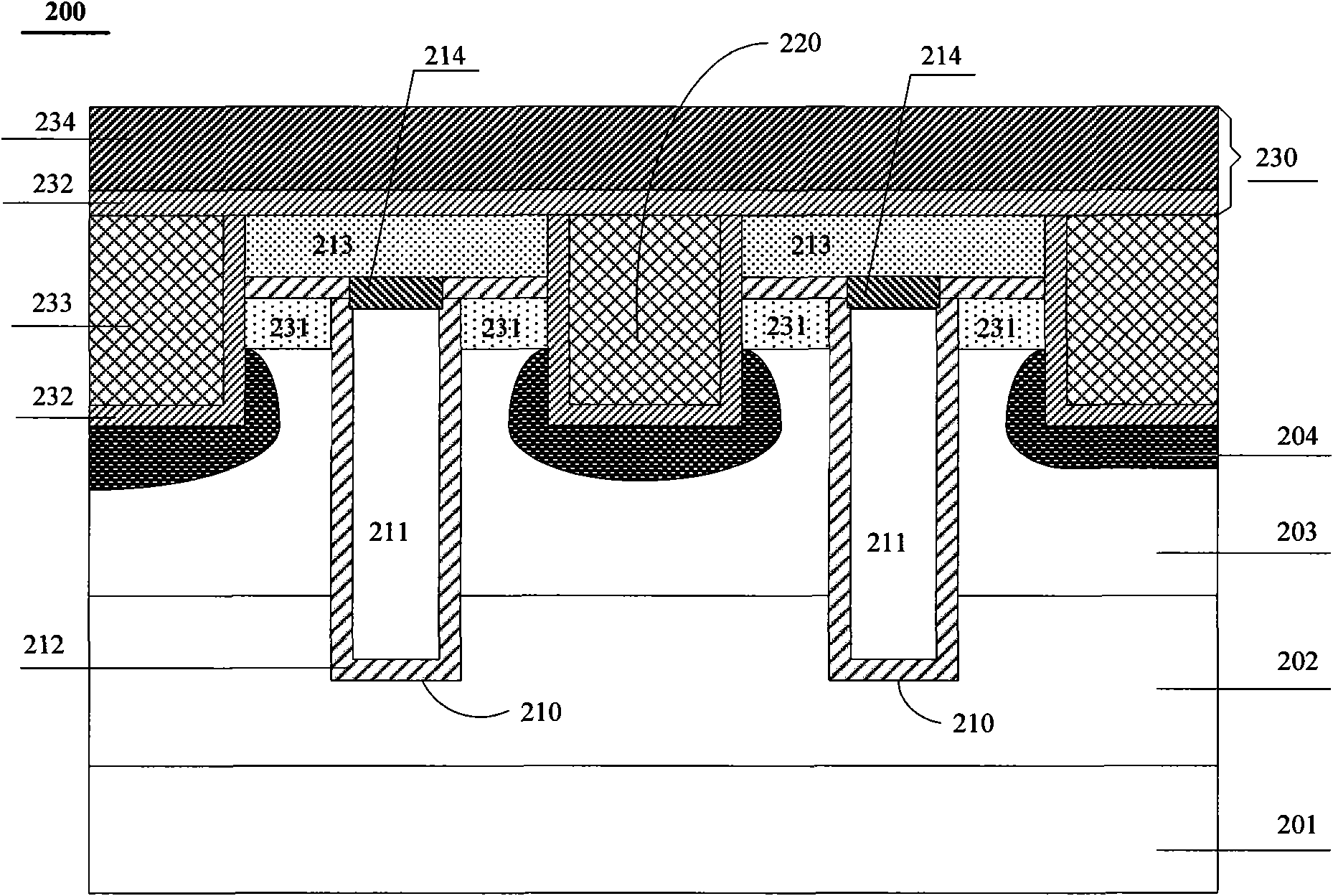

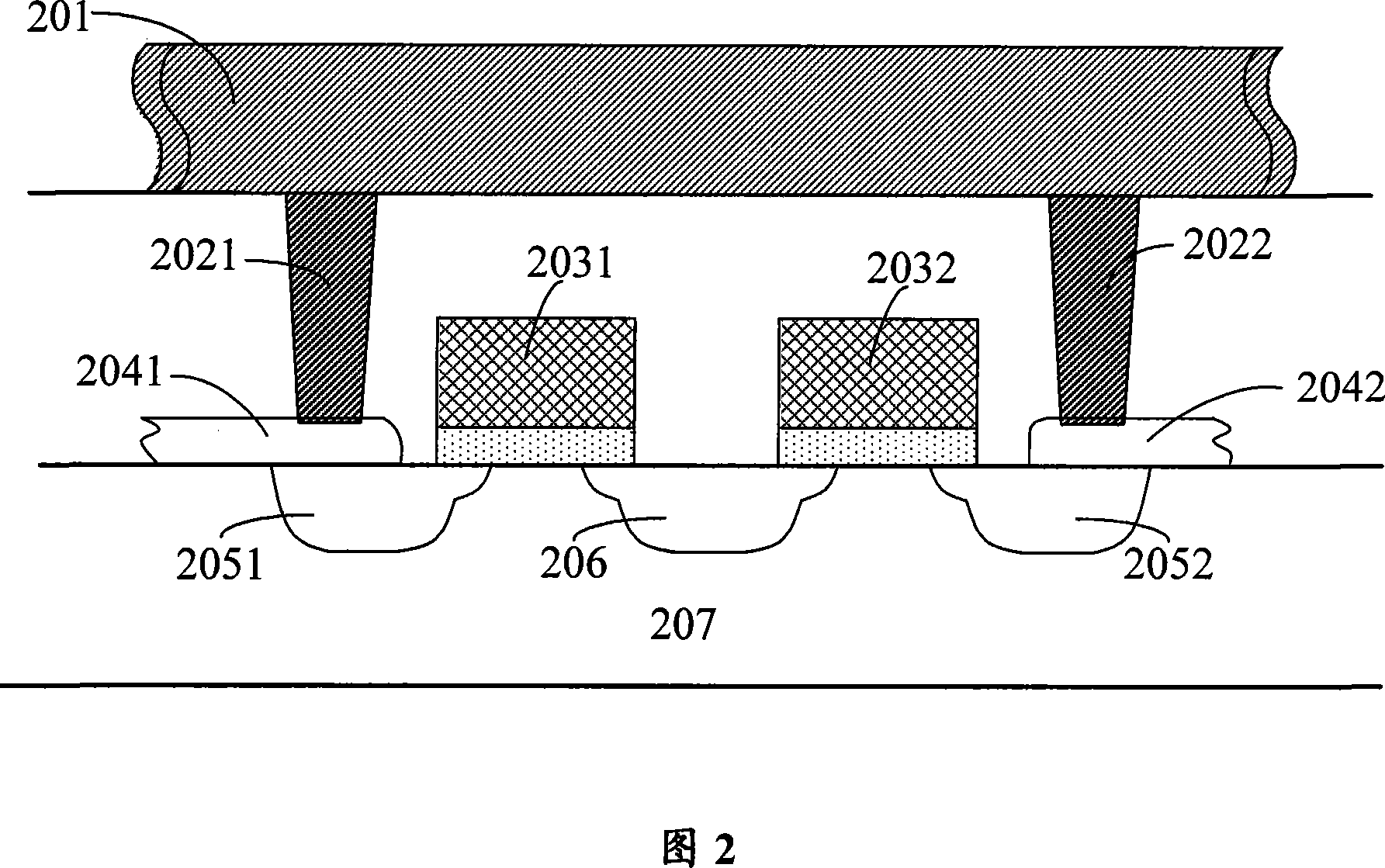

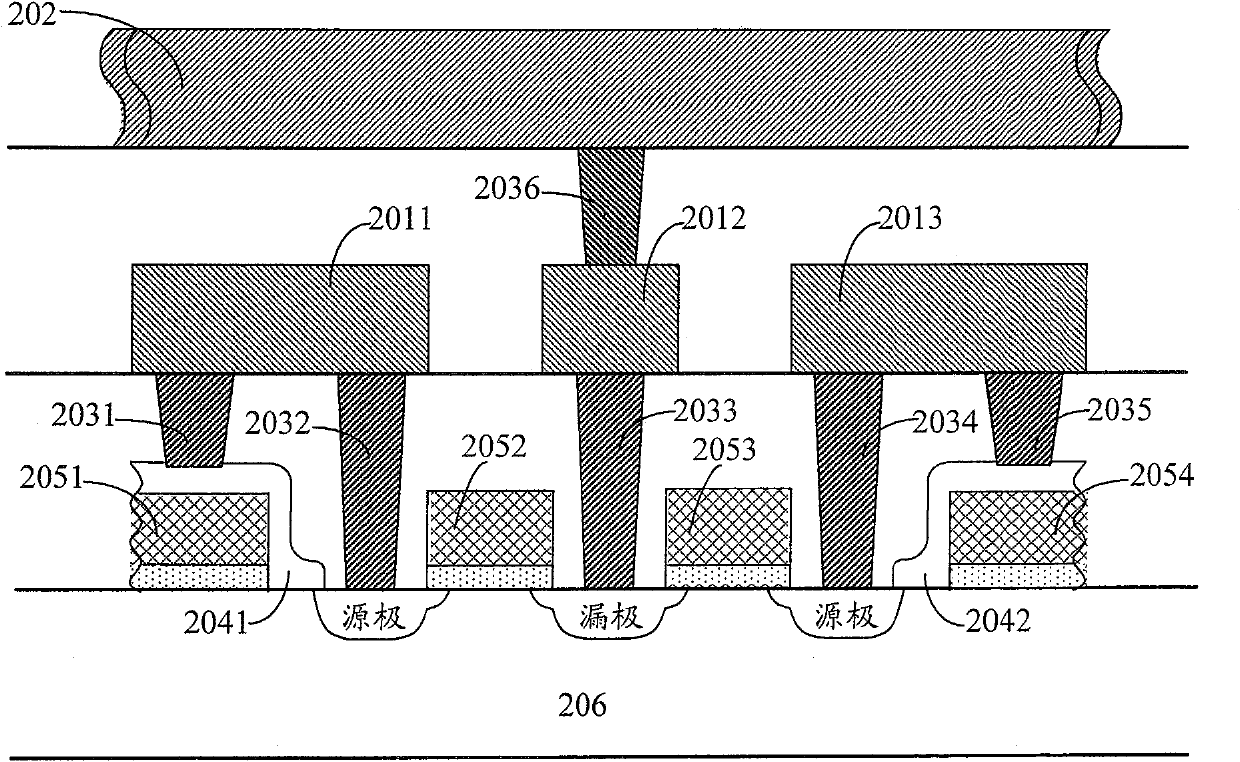

Top grid self-alignment thin-film transistor with source/drain areas raised and manufacturing method thereof

ActiveCN103346093ALower resistanceAvoid parasitic effectsTransistorSemiconductor/solid-state device manufacturingOxide semiconductorCorrosion

The invention provides a top grid self-alignment thin-film transistor with source / drain areas raised and a manufacturing method of the top grid self-alignment thin-film transistor with the source / drain areas raised. The manufacturing method includes the steps that an oxide semiconductor active layer, a grid dielectric layer and a grid electrode are sequentially formed on glass or a flexible substrate, and the thickness of the oxide semiconductor active layer is 5-20 nanometers in order to reduce influences of short-wavelength light on off-state characteristics of the thin-film transistor; then grid dielectric is corroded with the grid electrode as a stopping layer, the active layer corresponding to the grid dielectric is made to serve as a channel region, the active layers on the two sides are a source area and a drain area respectively, and self-alignment is achieved; next, low-resistivity conductive thin films are deposited, and the raised source area and the raised drain area are formed after photoetching, stripping or corrosion. The thin channels are adopted and the source area and the drain area are raised, not only are the influences of the light on the channels reduced, but also the resistance of the source area and the resistance of the drain area are reduced, and performance of the thin-film transistor is improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

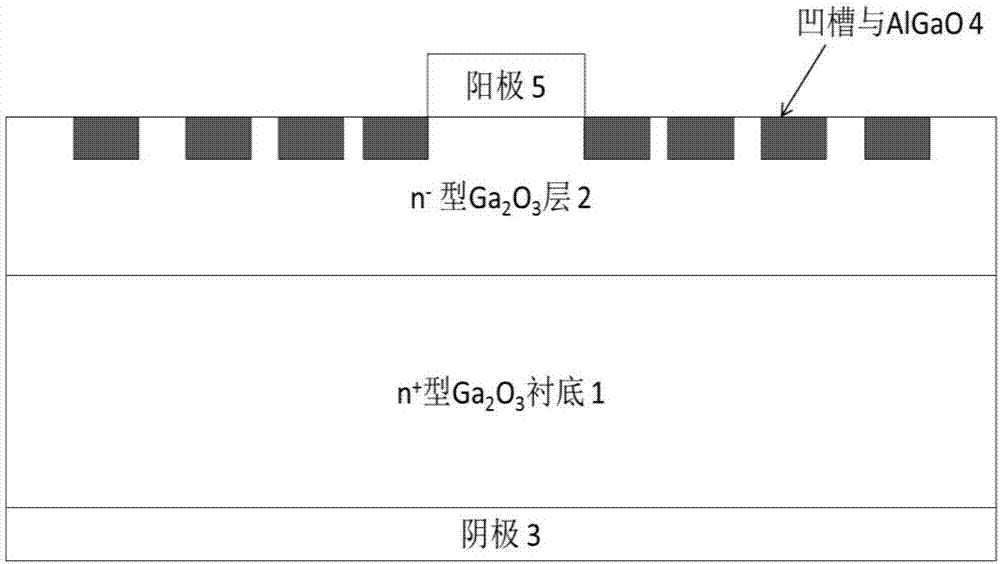

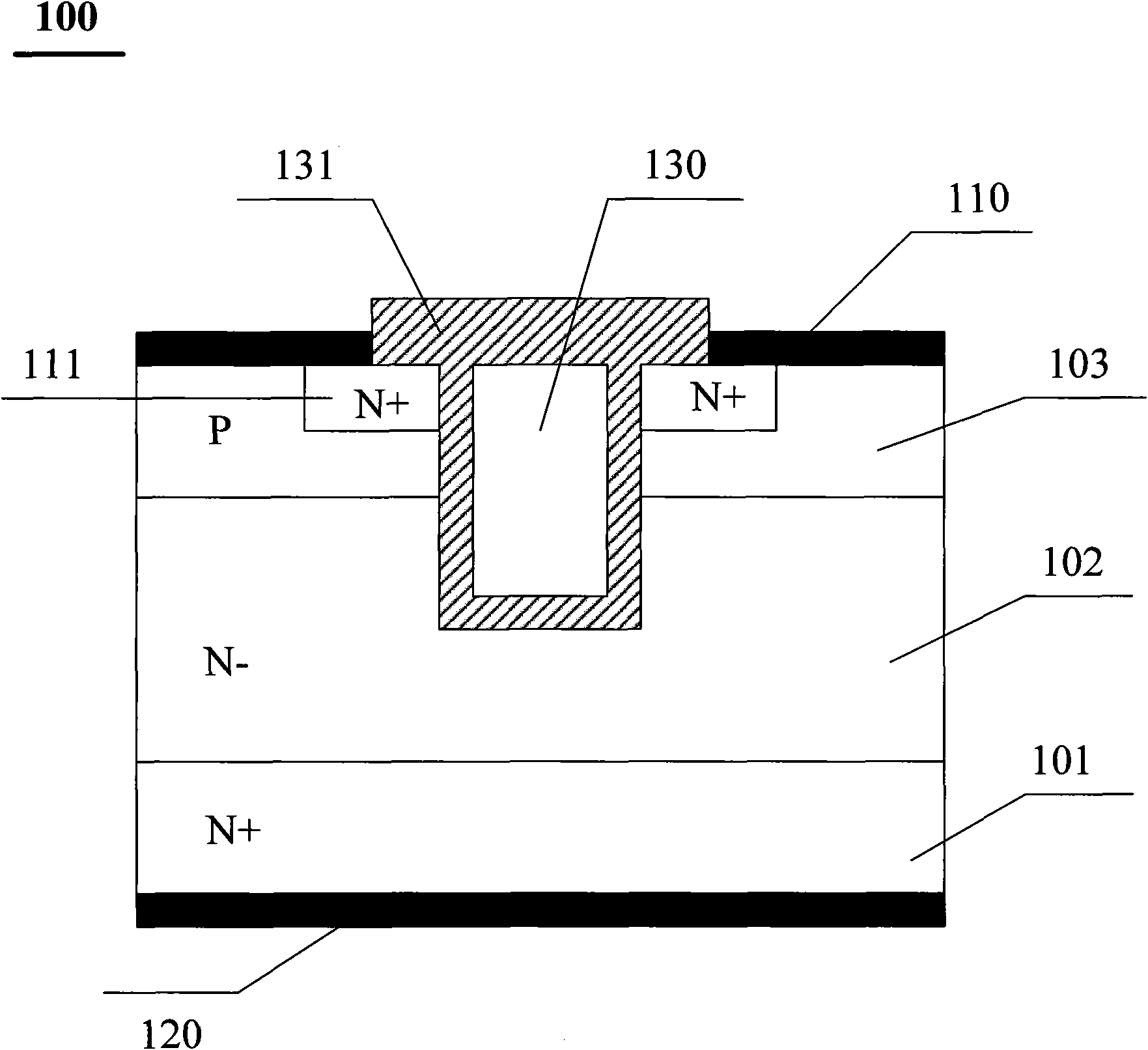

Ga2O3 Schottky diode device structure and manufacturing method thereof

ActiveCN106887470AMaintain positive characteristicsImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactParasitic capacitance

The invention discloses a Ga2O3 Schottky diode device structure and a manufacturing method thereof, and mainly aims at solving the problems that a present Schottky diode device is low in reverse breakdown voltage and the parasitic capacitance in a field plate structure is high. The Ga2O3 Schottky diode device structure comprises a cathode electrode, a heavily-doped n type Ga2O3 substrate, a low-doped n type Ga2O3 epitaxial layer and an anode electrode from bottom to top; Schottky contact is formed in the part where the anode makes contact with the epitaxial layer, the cathode and the substrate make ohmic contact, grooves are distributed separately in the low-doped n type Ga2O3 epitaxial layer, intervals of grooves are increased progressively within the range of 0.3 to 0.5 micron, the first groove is positioned below the edge of the anode, the distance between the last groove and the first groove ranges from 10 to 15 micron, and AlGaO layers in which the Al component is greater than 20% are grown in an epitaxial manner in the grooves respectively. Thus, the reverse breakdown voltage is improved, the parasitic capacitance is reduced, positive characteristic is kept unchanged, and the structure and manufacturing method thereof can be used for high-speed integration circuits and microwave technologies.

Owner:XIDIAN UNIV

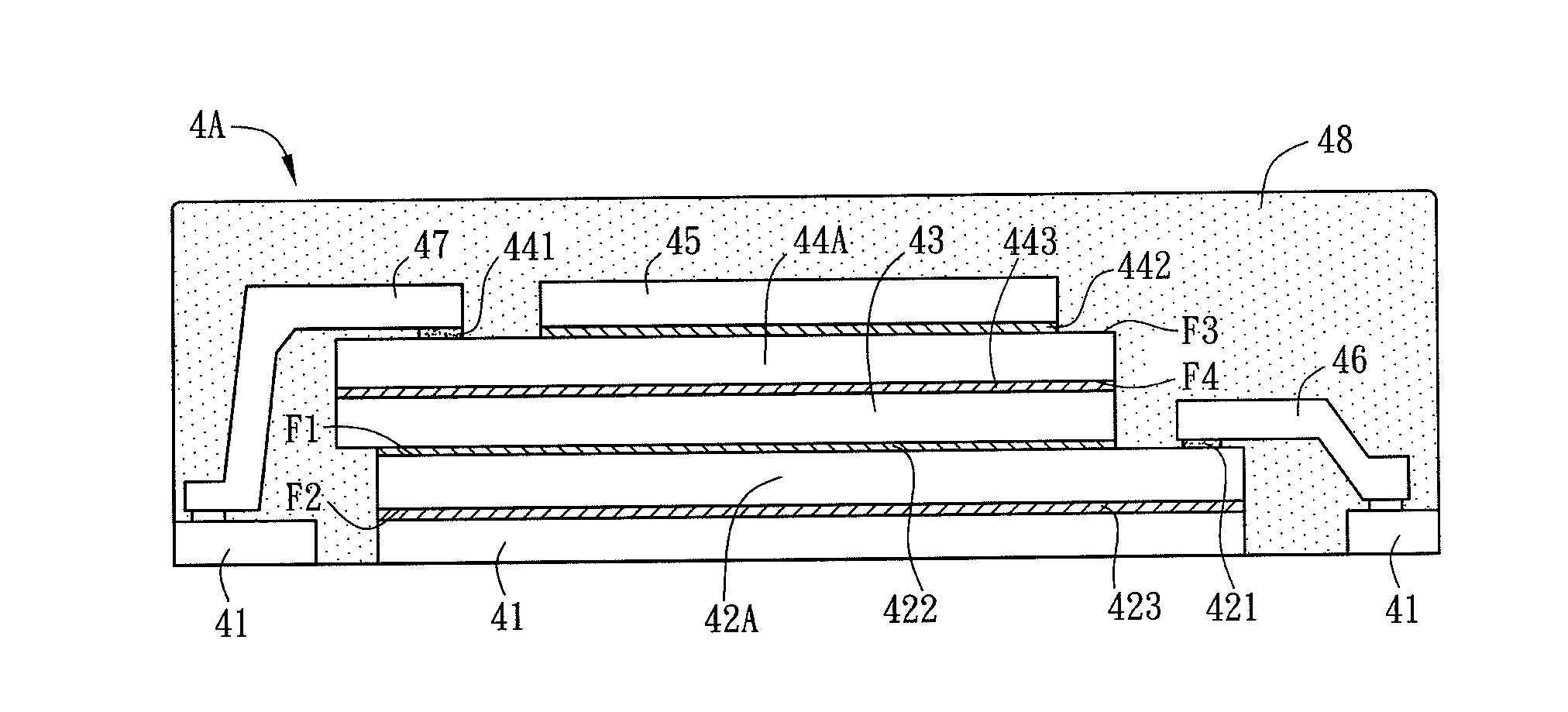

Power semiconductor package structure and manufacturing method thereof

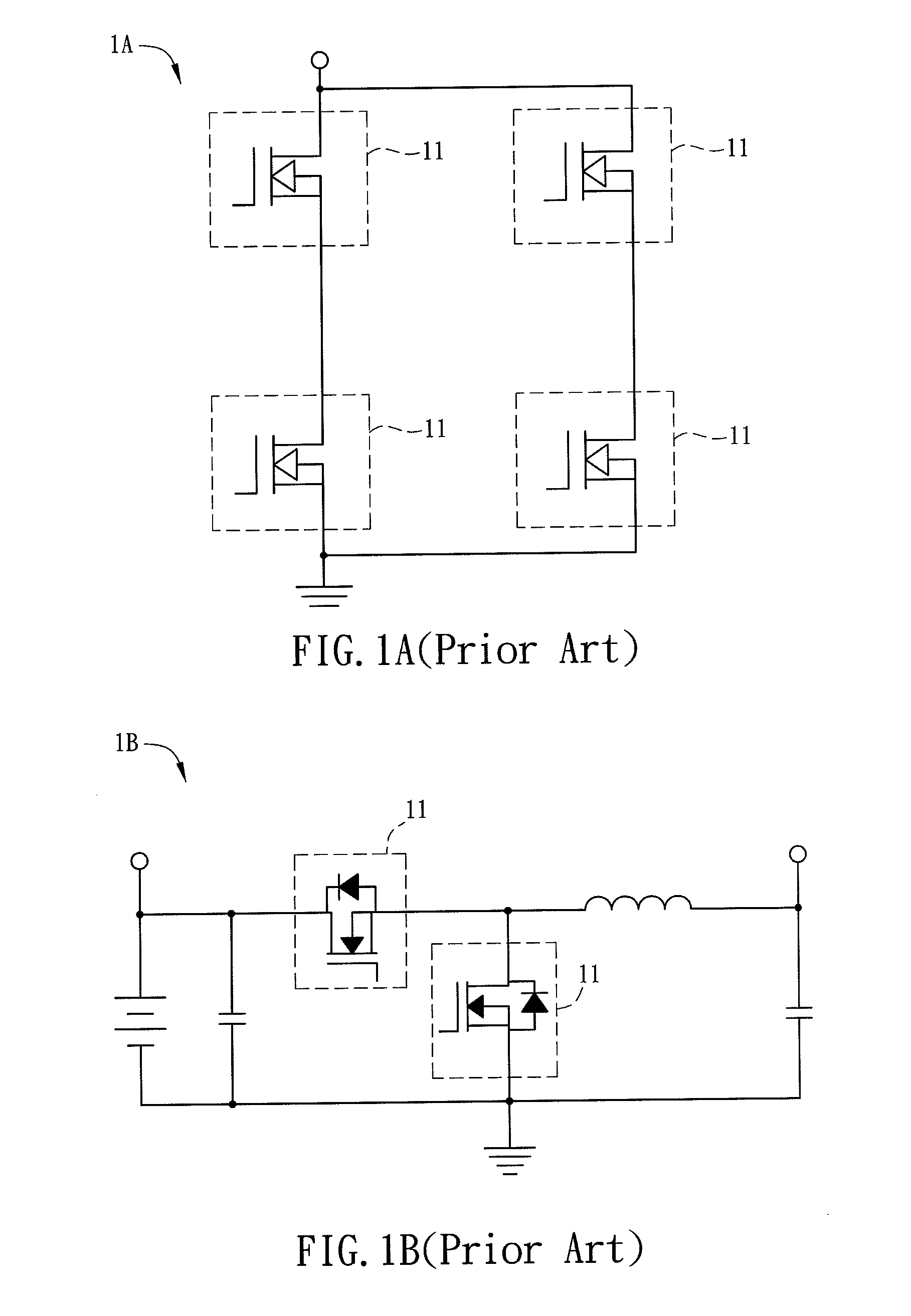

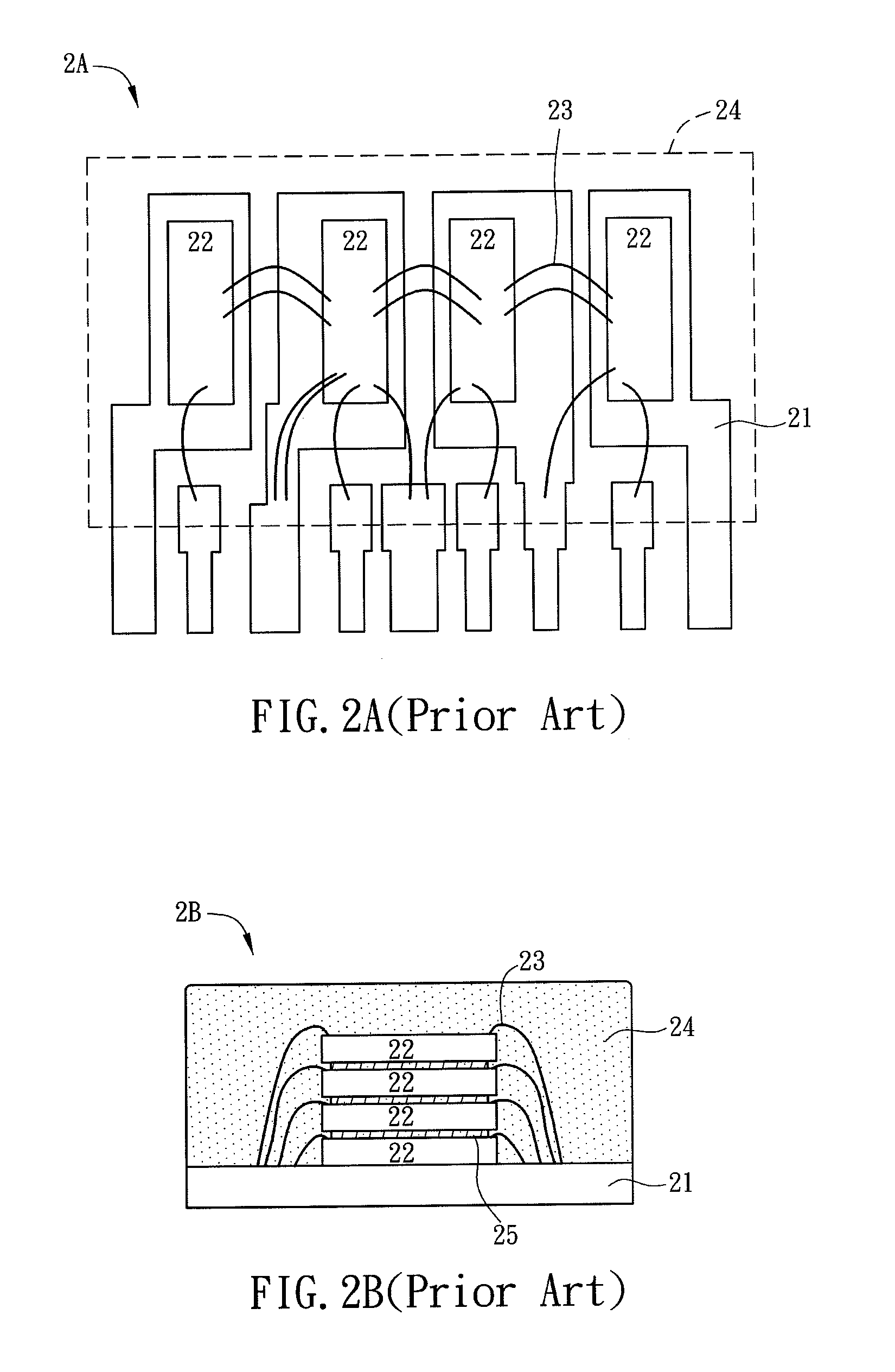

ActiveUS20120181706A1Improve reliabilityReduce parasitic effectsSemiconductor/solid-state device detailsSolid-state devicesElectricitySemiconductor package

A power semiconductor package structure includes a carrier, a first power chip, a second power chip, a first conductive sheet, a second conductive sheet and a third conductive sheet. The first power chip has a first surface and a second surface opposing to the first surface. A first control electrode and a first main power electrode are disposed on the first surface, and a second main power electrode is disposed on the second surface. The second surface is disposed on the carrier, and electrically connected to the carrier through the second main power electrode. The second power chip has a third surface and a fourth surface opposing to the third surface. A third main power electrode is disposed on the third surface, and a fourth main power electrode is disposed on the fourth surface. The fourth surface is disposed on the first power chip. The first conductive sheet is electrically connected to the first main power electrode and the fourth main power electrode. The second conductive sheet is electrically connected to the third main power electrode. The third conductive sheet is electrically connected to the first control electrode. At least a part of the first control electrode is non-covered by the second power chip along a projection direction, which is perpendicular to the carrier.

Owner:DELTA ELECTRONICS INC

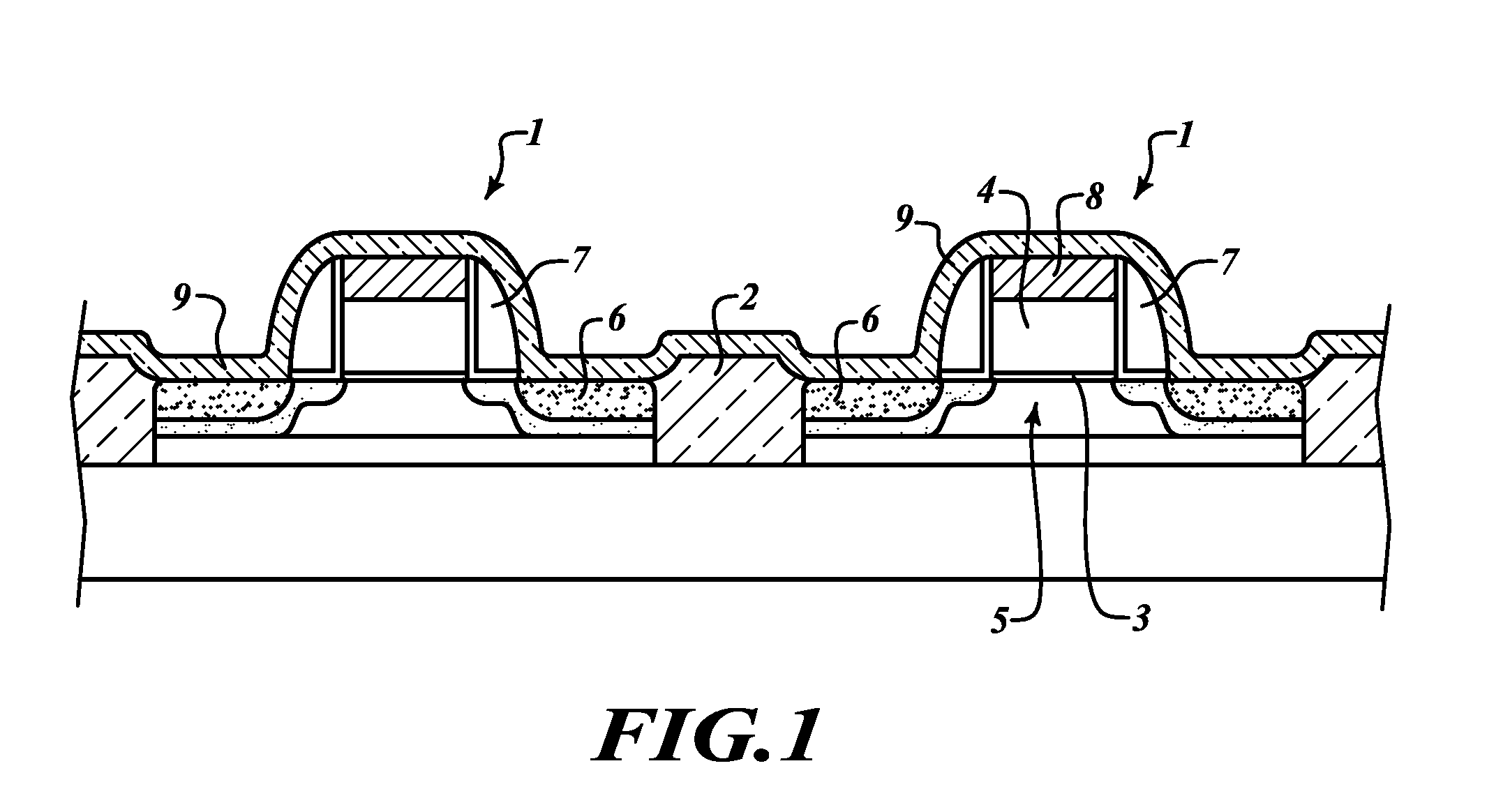

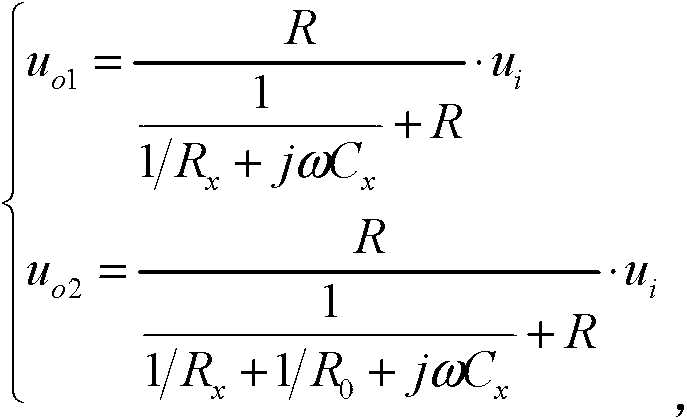

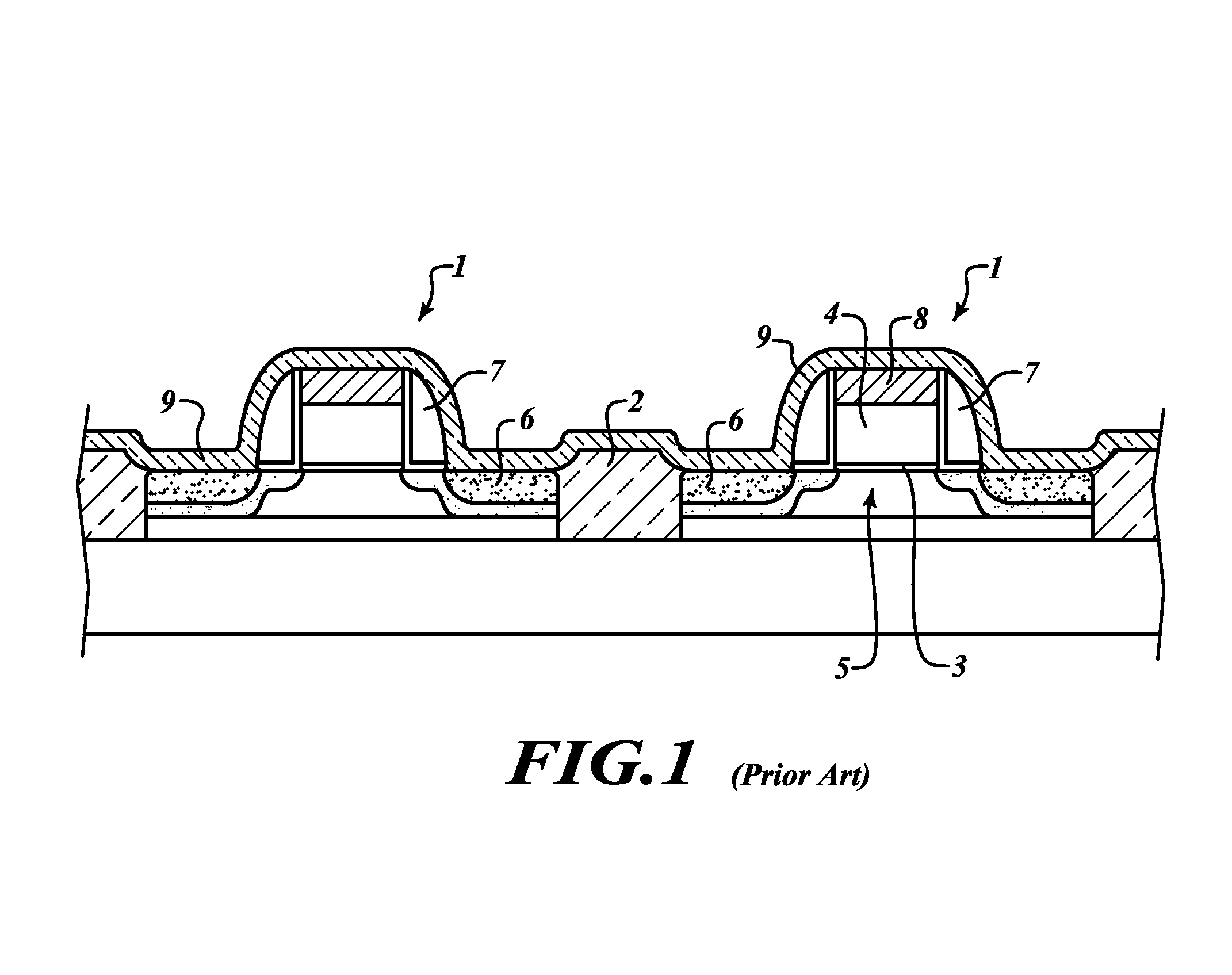

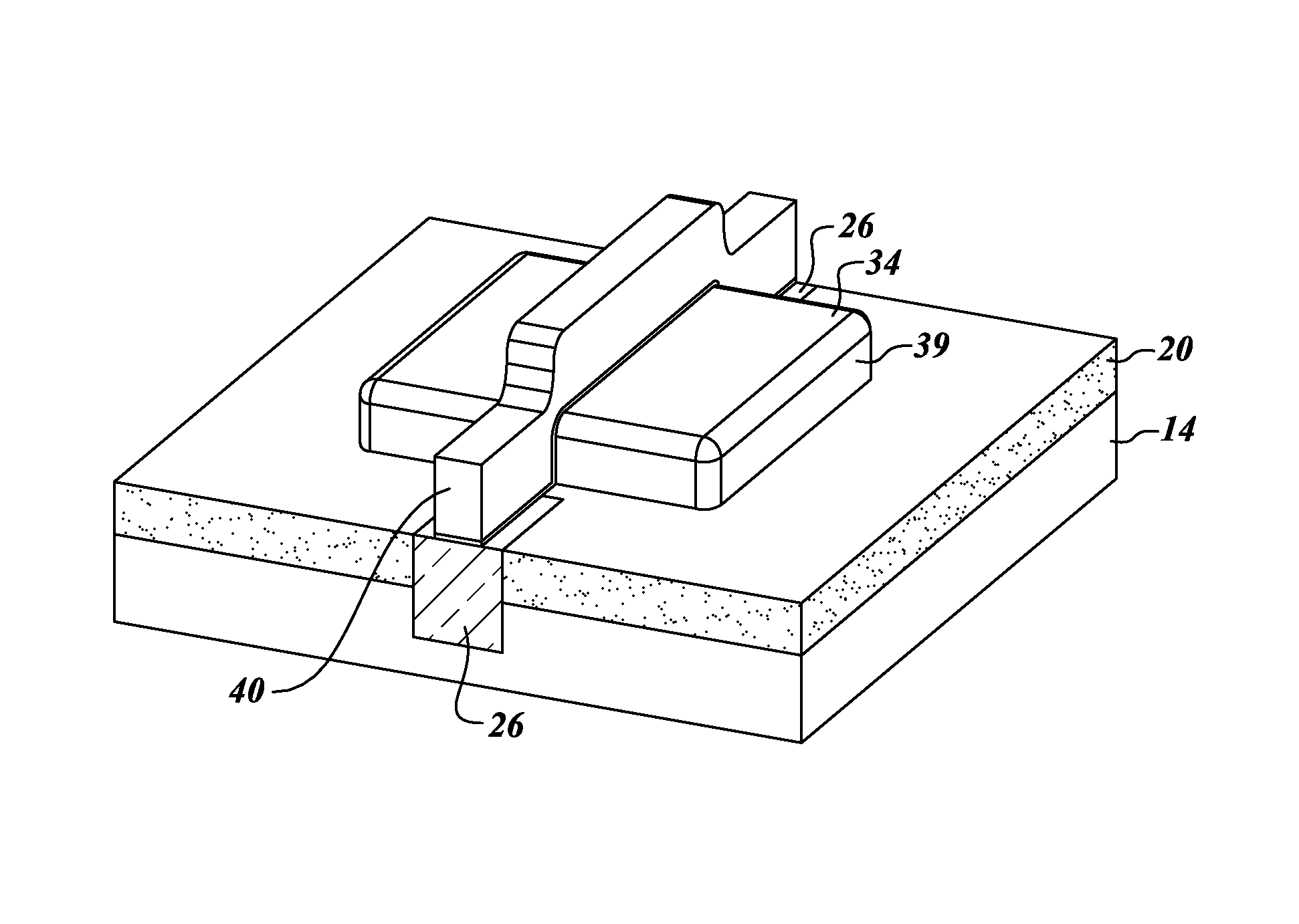

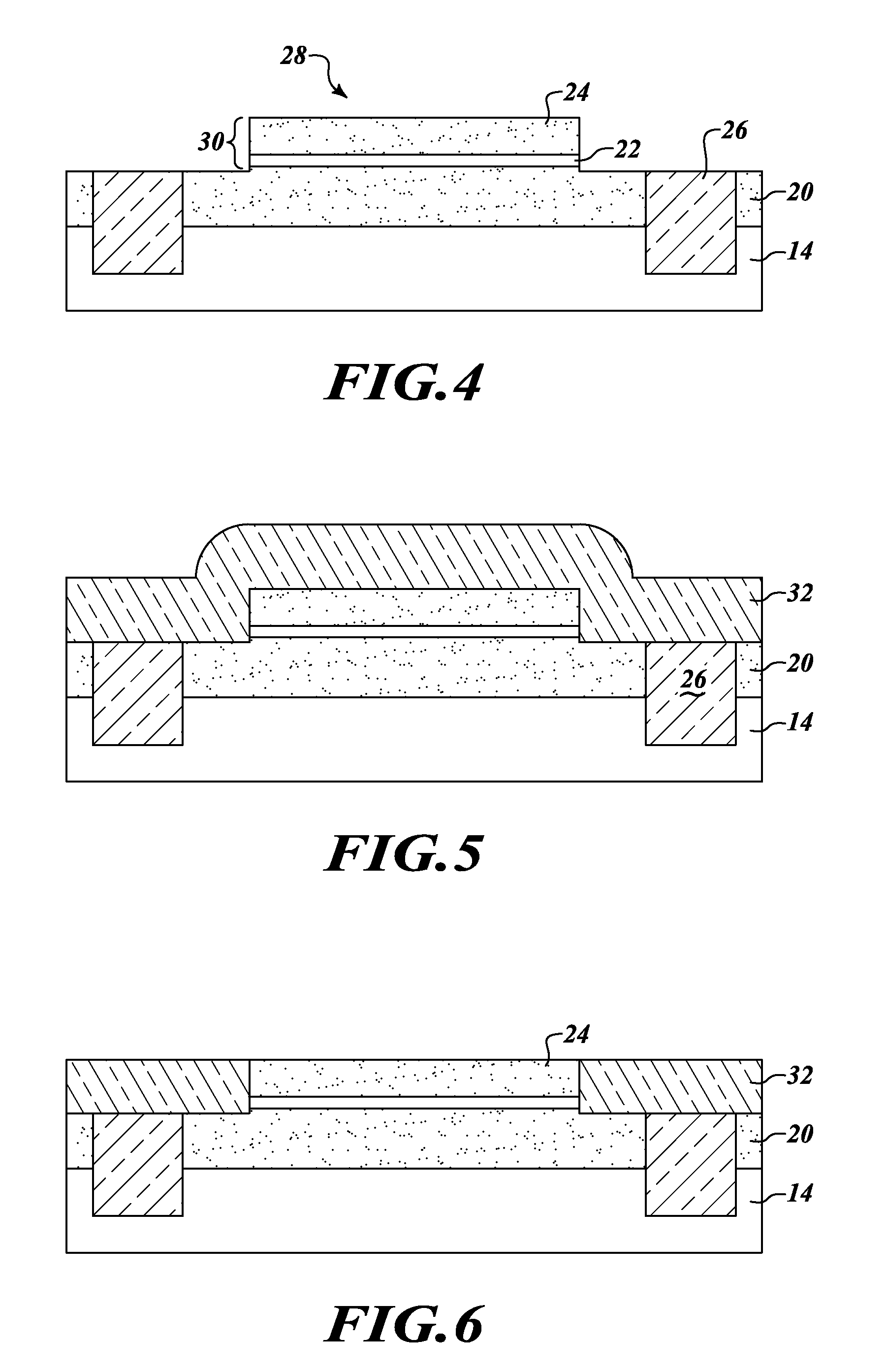

Strained transistor and method for forming the same

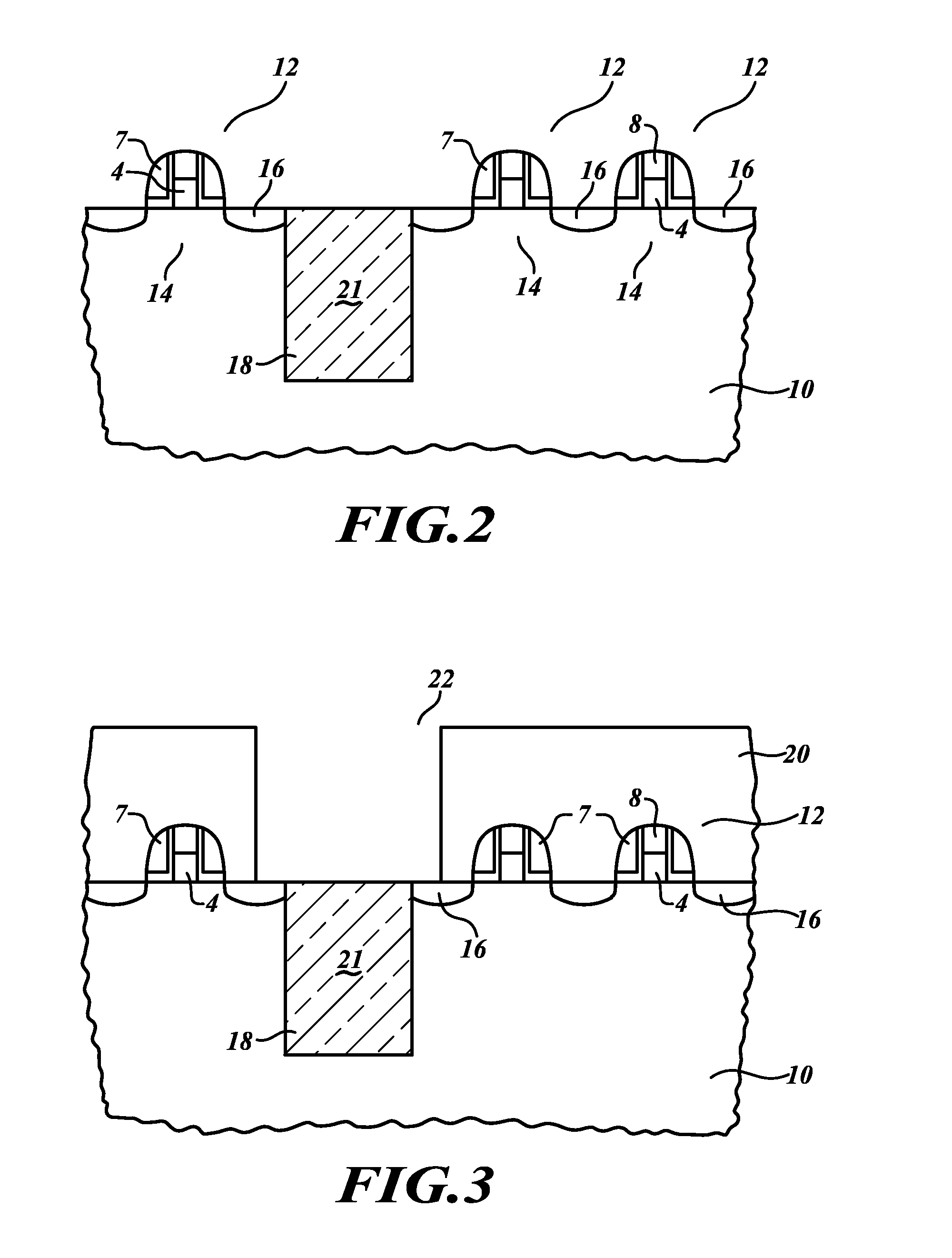

ActiveUS20100164000A1Avoid parasitic effectsMinimizes stress riserTransistorSolid-state devicesGate dielectricHigh stress

According to one embodiment, a semiconductor substrate is provided having at least two transistor regions formed therein. Overlying the channel regions is a gate dielectric and transistor gate electrodes overly the gate dielectric and are positioned overlying the channel regions. Source and drain regions are formed on either side of the channel regions to create a transistor structure. In order to provide isolation between transistors in the semiconductor substrate, a trench is formed in the substrate. A strain-inducting layer is then deposited over the transistor structures and into the trench in the semiconductor substrate. A high-stress nitride layer is one type of material which is suitable for forming the strain-inducing layer.

Owner:STMICROELECTRONICS SRL

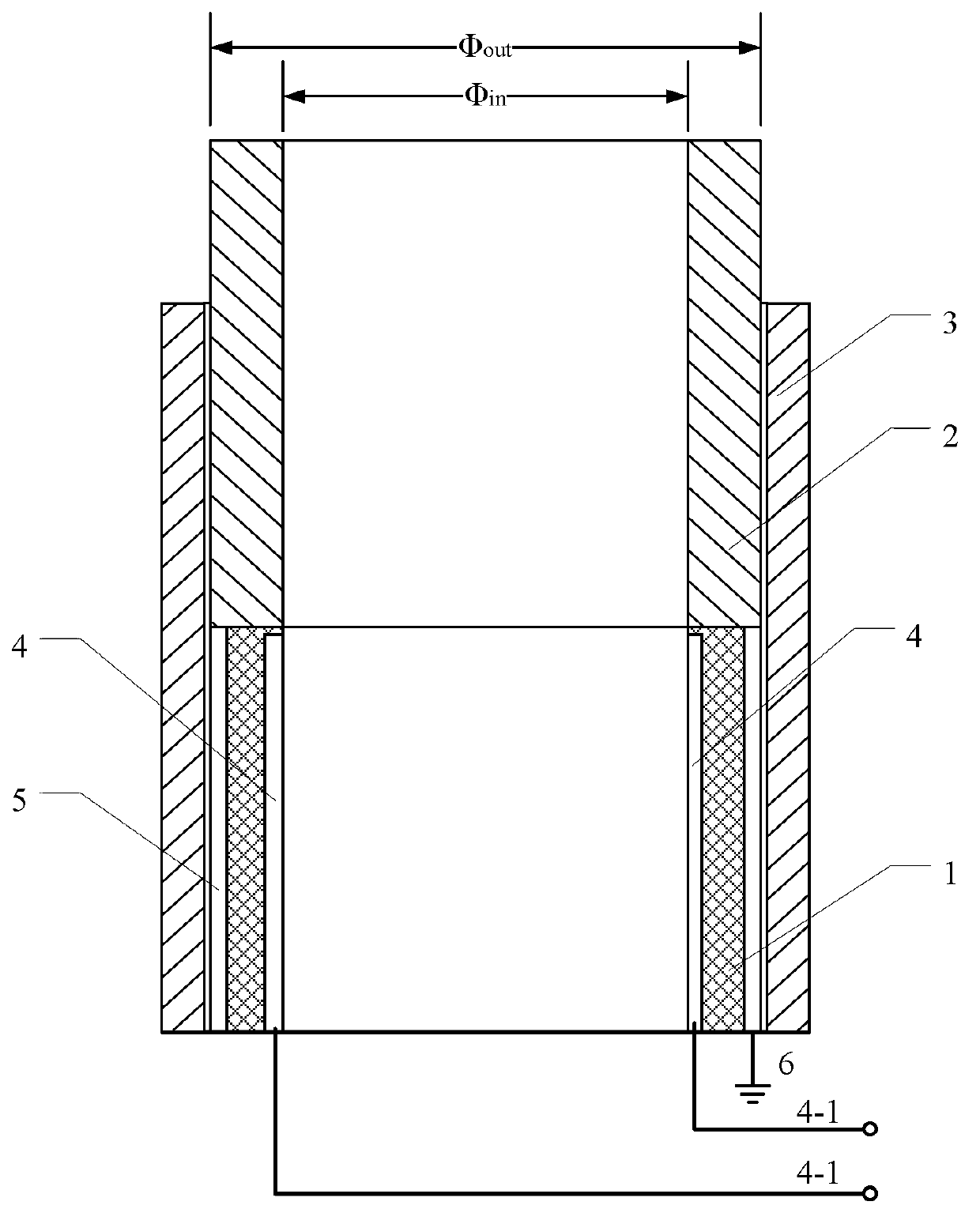

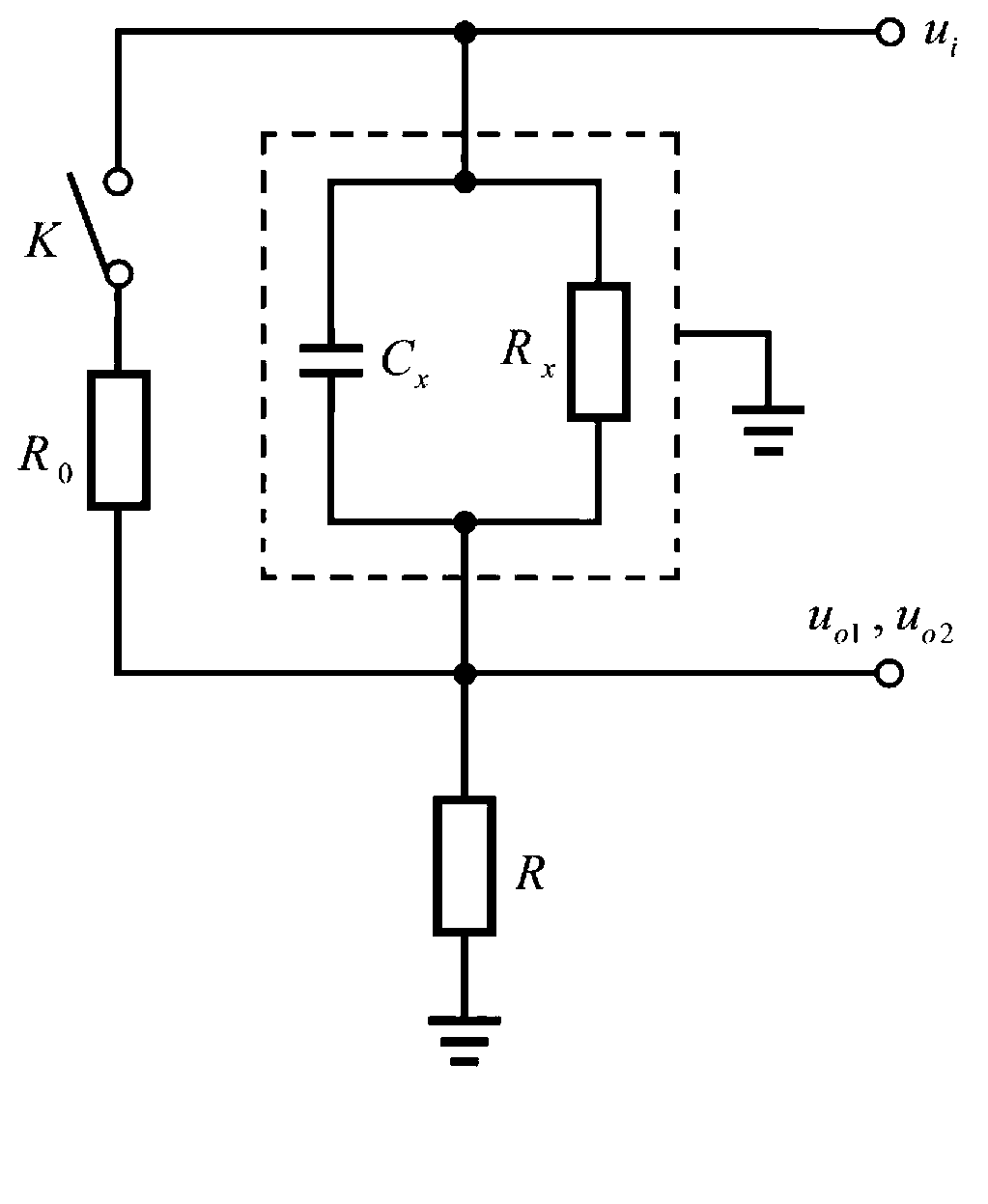

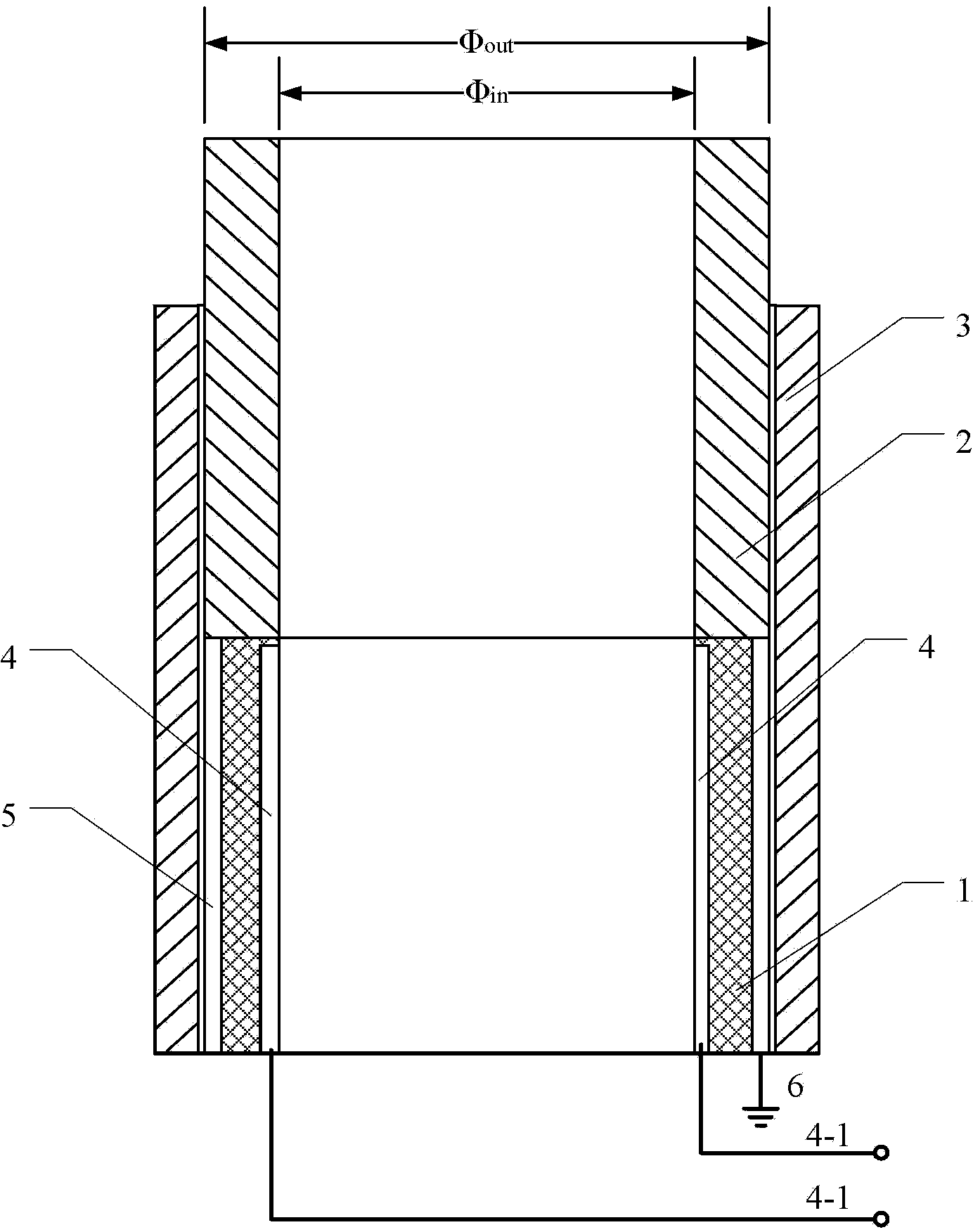

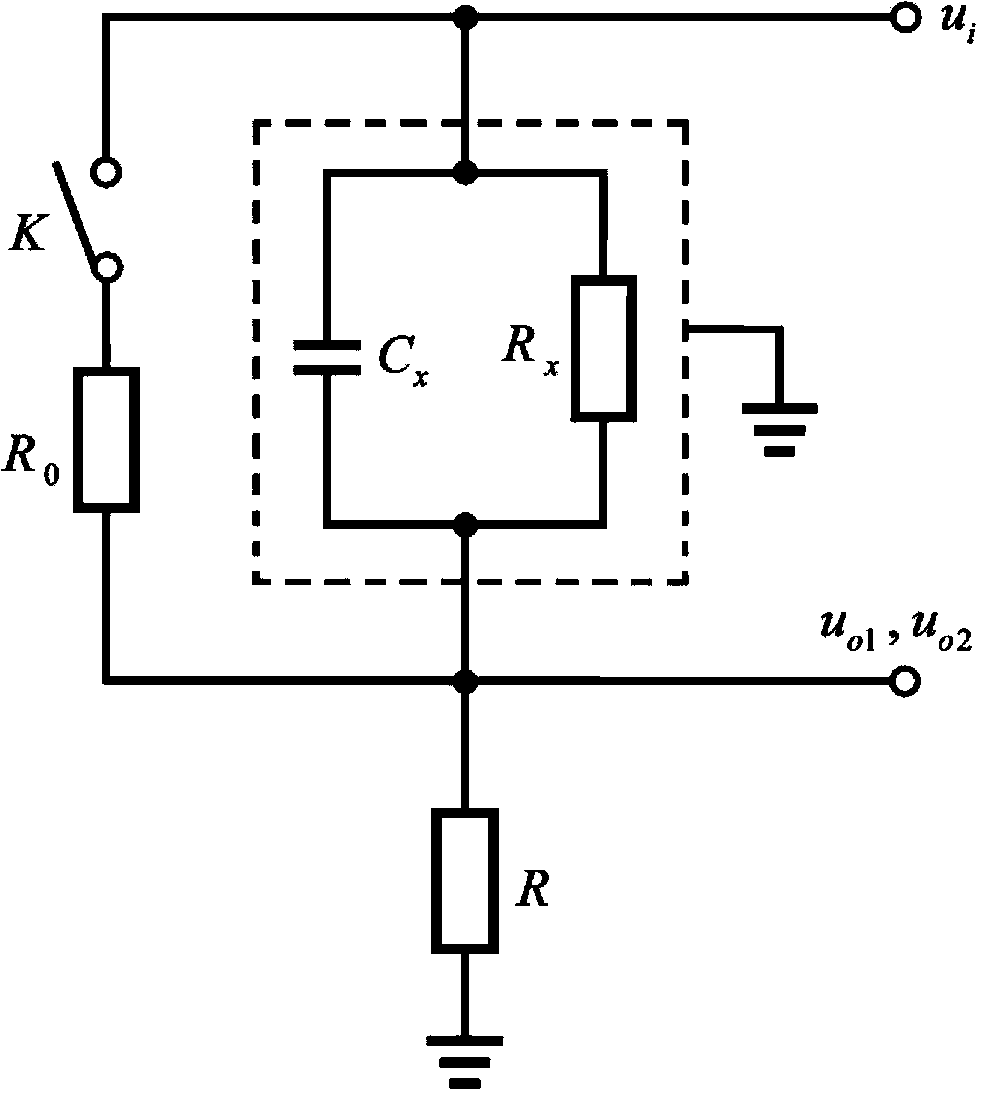

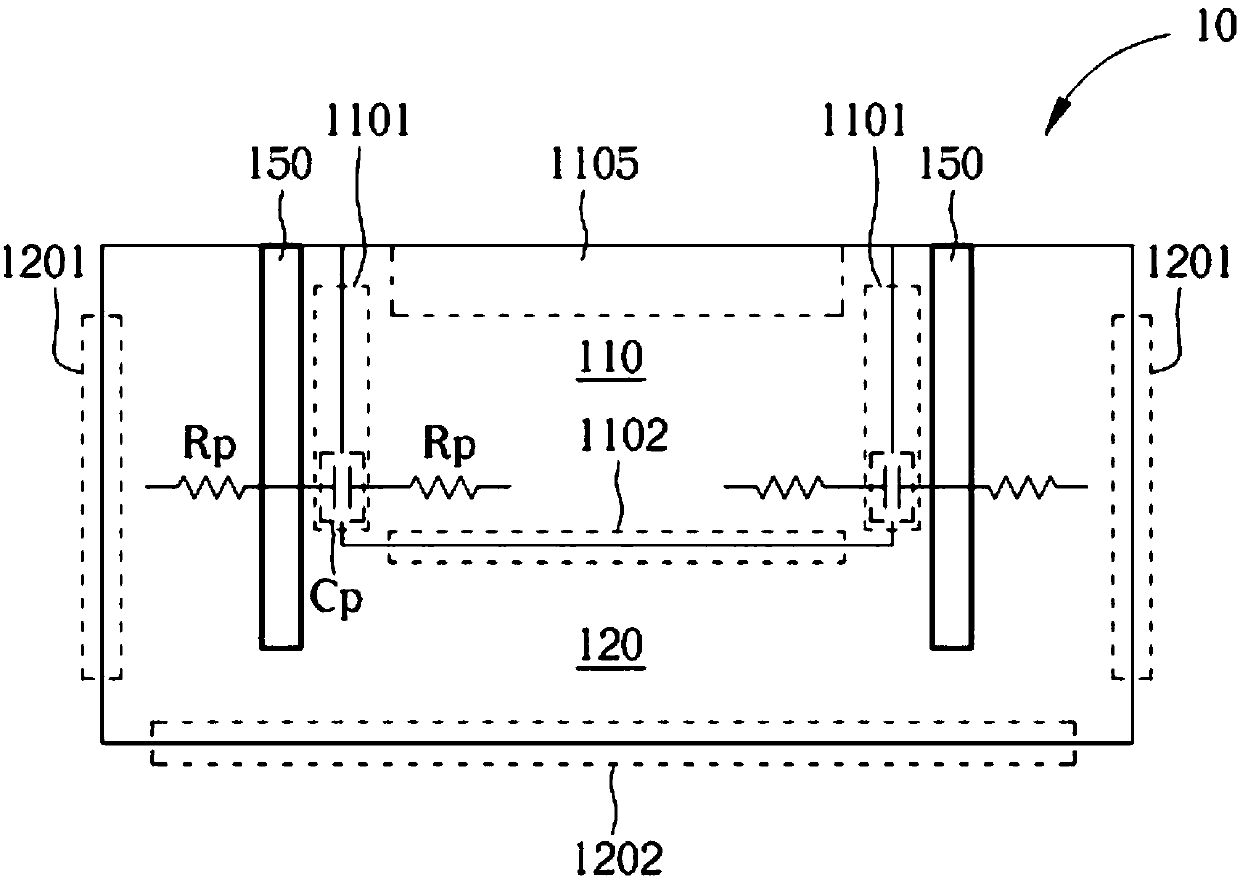

Cylindrical sample preparation device for measuring moisture content of green sand through capacitance method and method for measuring moisture content of green sand

InactiveCN102998160ASame sizeIncrease the areaPreparing sample for investigationMaterial capacitanceCapacitanceElectrical resistance and conductance

The invention discloses a cylindrical sample preparation device for measuring moisture content of green sand through a capacitance method and a method for measuring the moisture content of the green sand, belongs to the field of moisture measurement of cast green sand, and solves the problem that the measuring accuracy of the moisture content of the green sand through capacitance methods is low in the past. The method includes producing a sand sample with the height equal to a main sample drum through the sample preparation device; connecting two exciting electrode shielded wires with a parallel resistance model circuit respectively, exerting alternating current excitation voltage on two exciting electrodes through the two exciting electrode shielded wires, turning off a switch K, serially connecting a sand sample equivalent resistor Rx with a capacitor Cx, and turning on the switch K, parallelly connecting the sand sample equivalent resistor, the capacitor Cx and a first resistor R0; and measuring the voltage drop uo1 and uo2 of a second resistor R under the two states to obtain the Cx, and obtaining the moisture content of the green sand through the existing relation between capacitor Cx and the moisture content.

Owner:HARBIN UNIV OF SCI & TECH

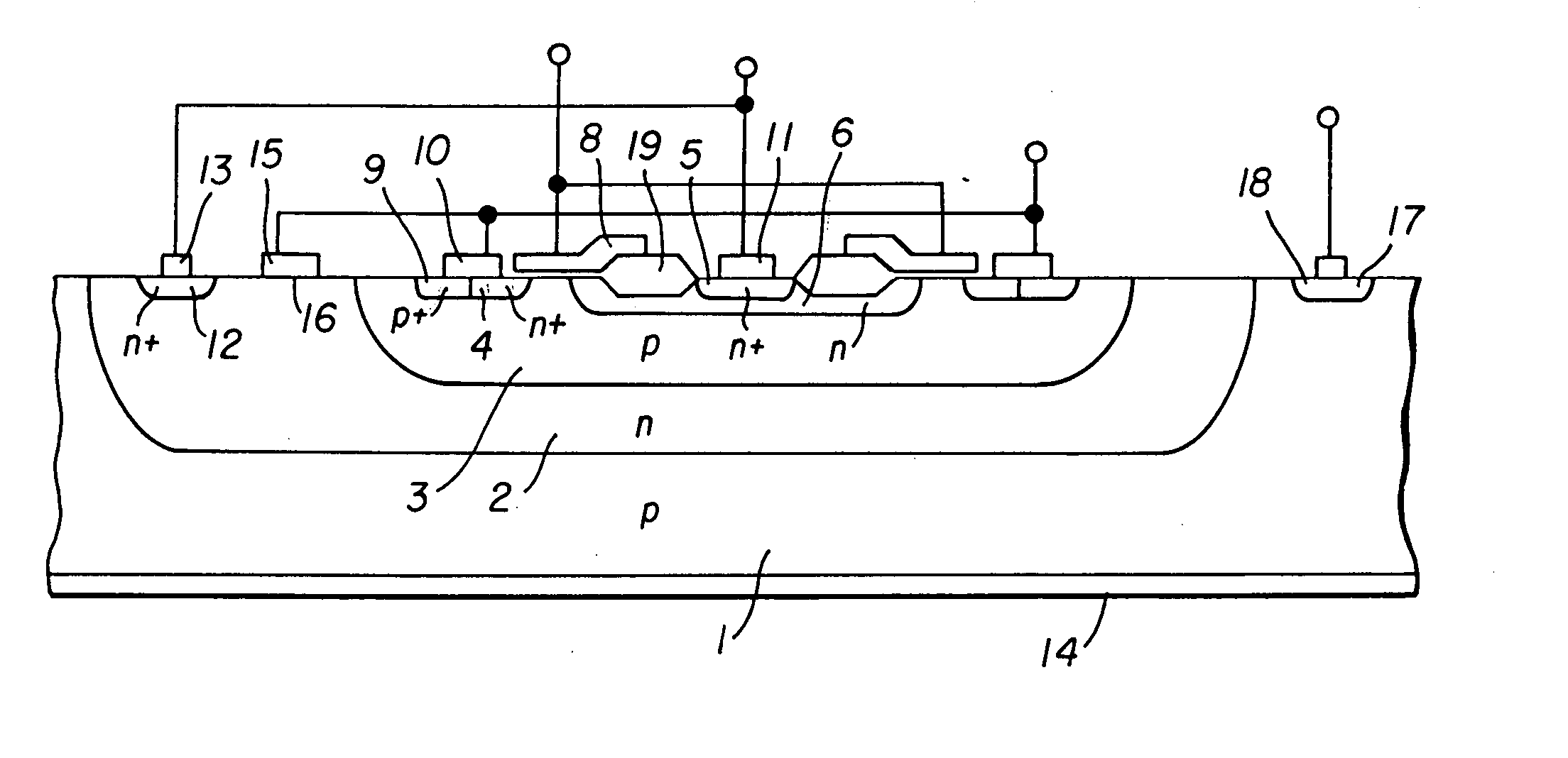

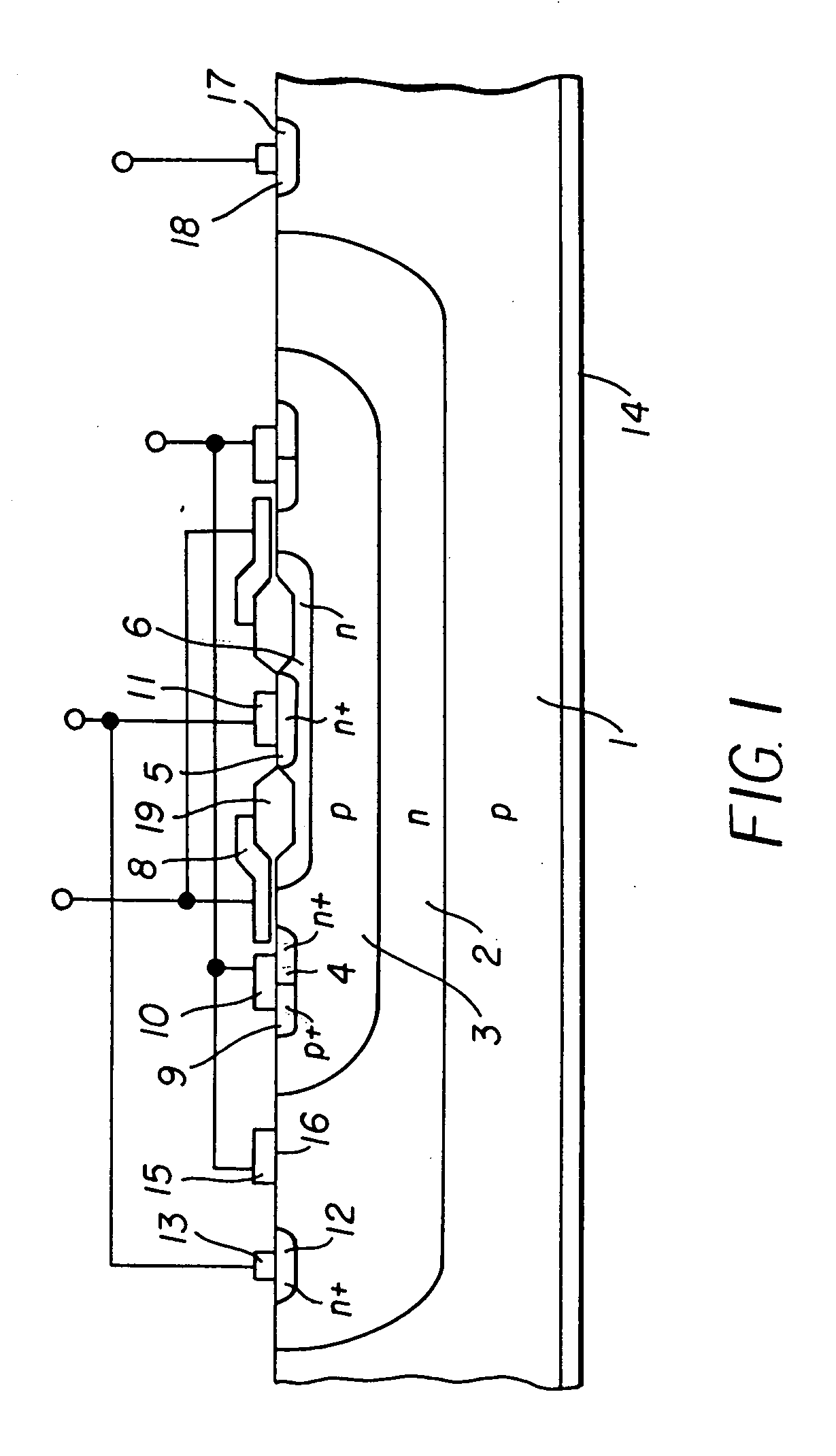

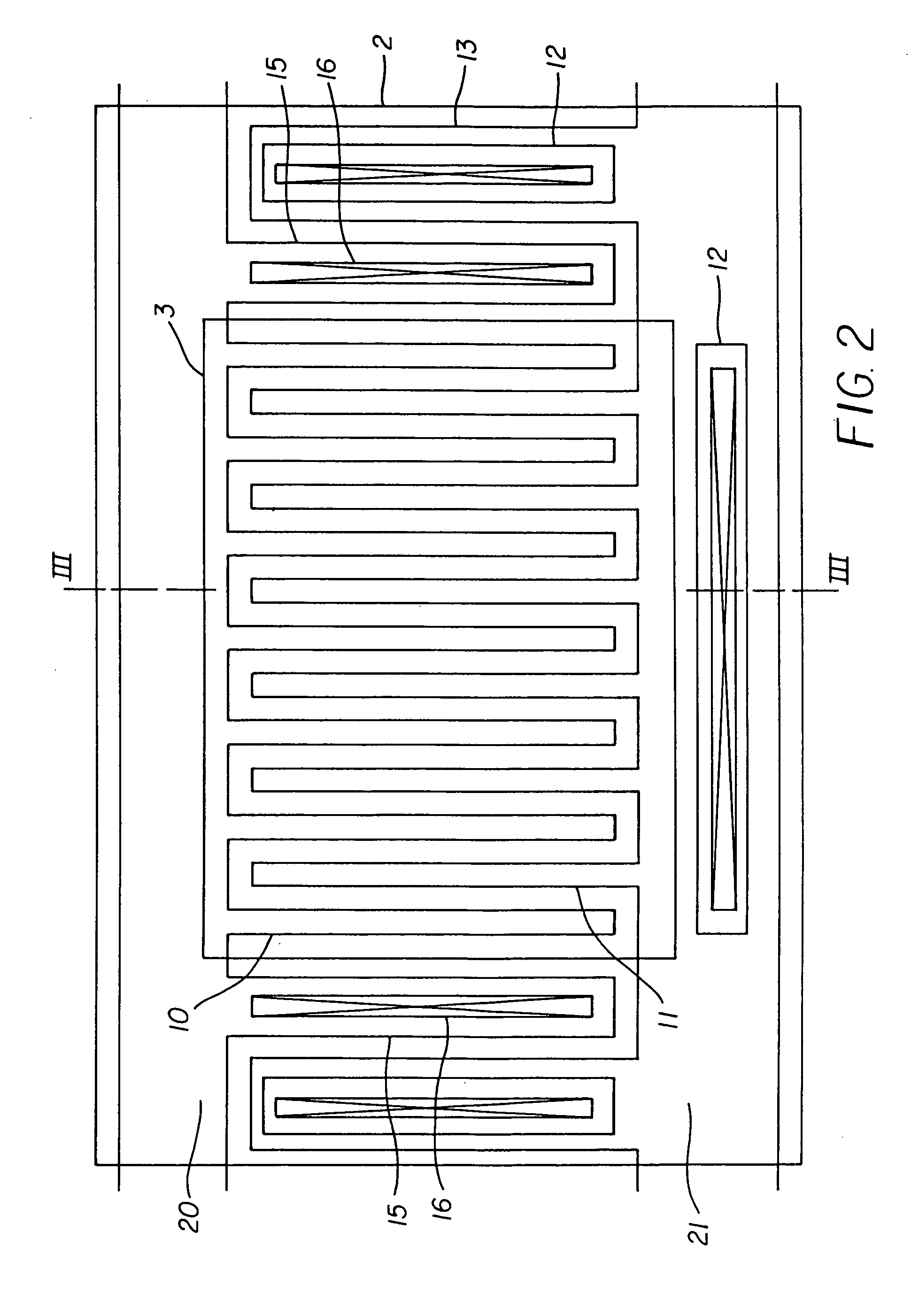

High power semiconductor device having a schottky barrier diode

InactiveUS20050145975A1Reduce parasitic effectsAvoid parasitic effectsTransistorSolid-state devicesMOSFETPower semiconductor device

A semiconductor device is configured to prevent destruction of elements and / or miss-operation of the circuit by parasitic effects produced by parasitic transistors when a MOSFET of a bridge circuit is formed on a single chip. A Schottky junction is formed by providing an anode electrode in an n well region where a source region, a drain region, and a p well region of a lateral MOSFET. A Schottky barrier diode constituting a majority carrier device is connected in parallel with a PN junction capable of being forward-biased so that the PN junction is not forward-biased so that minority carriers are not generated, and thereby suppressing parasitic effects.

Owner:FUJI ELECTRIC CO LTD

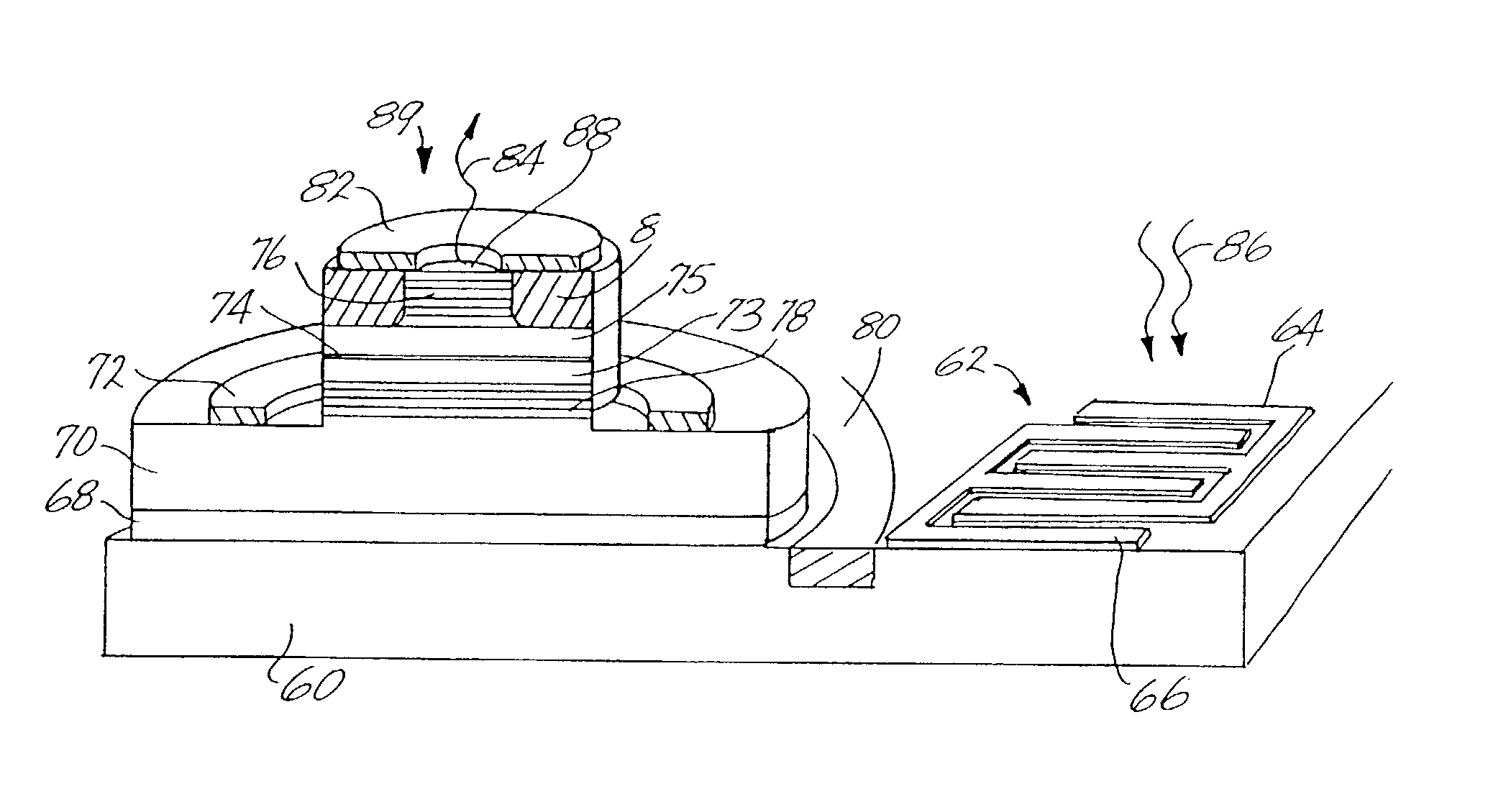

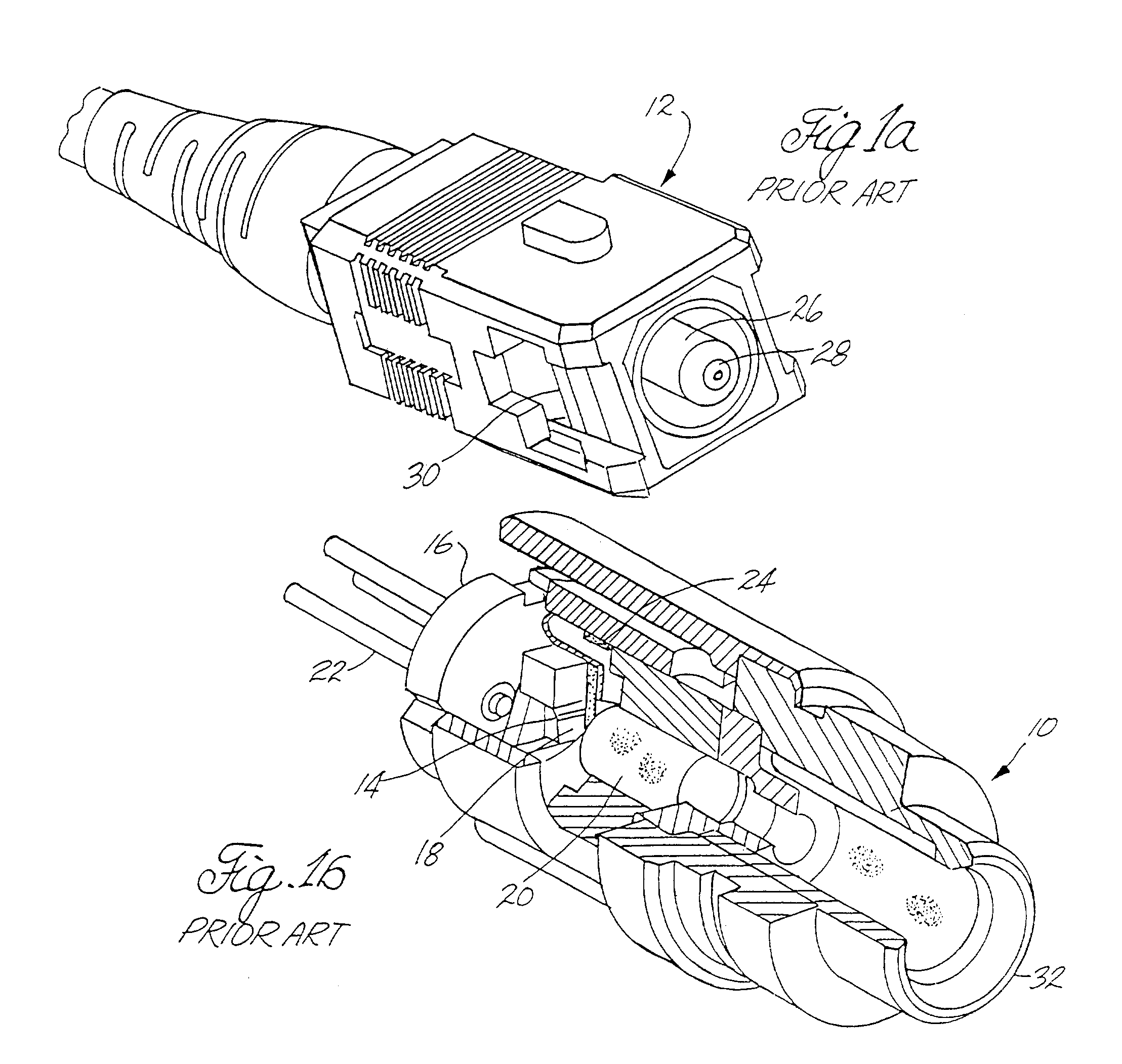

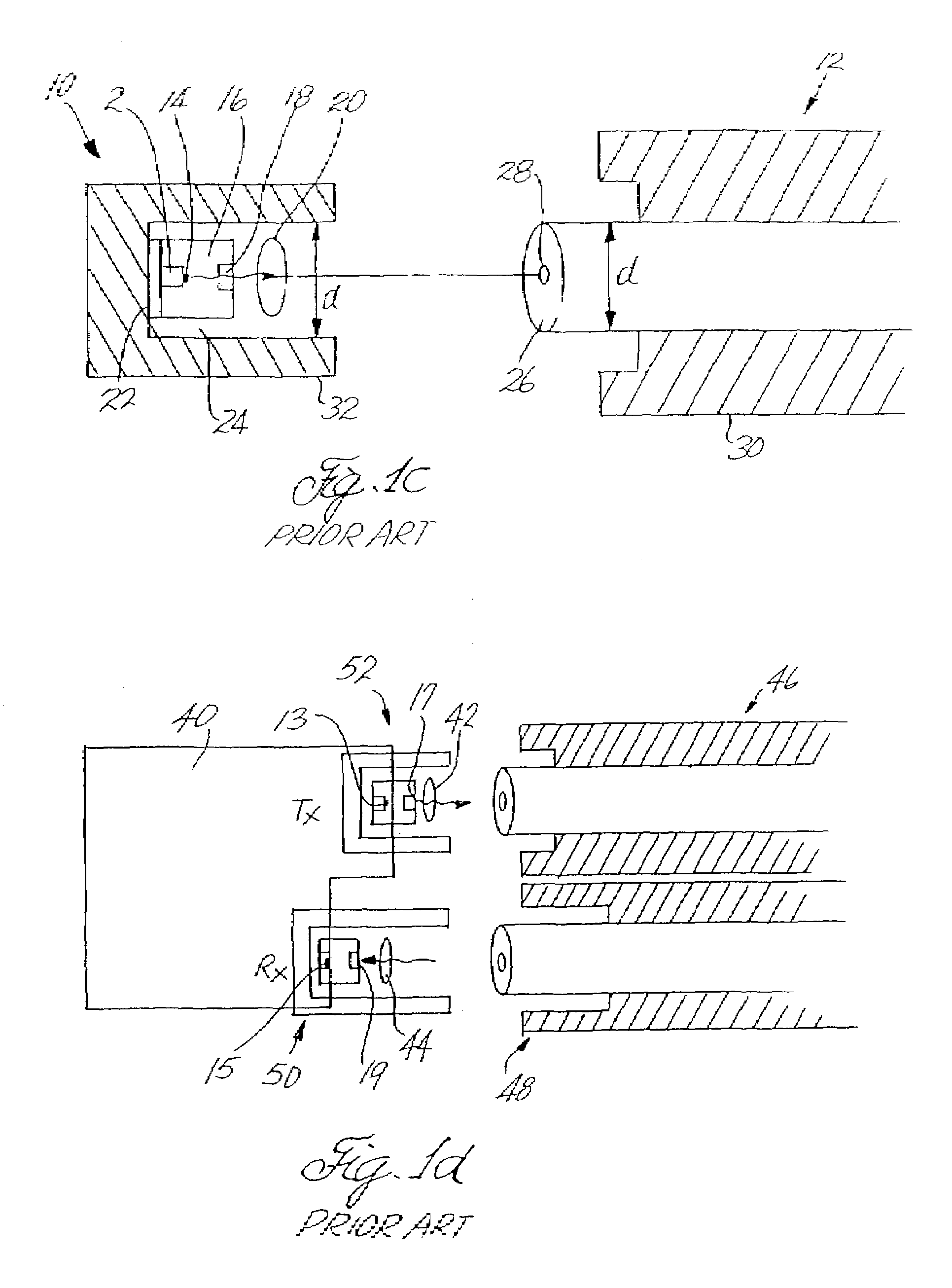

Closely-spaced VCSEL and photodetector for application requiring their independent operation

InactiveUS7053415B2Avoid parasitic effectsImprove efficiencyLaser detailsSolid-state devicesPhotovoltaic detectorsAudio power amplifier

A monolithically integrated VCSEL and photodetector, and a method of manufacturing the same, are disclosed for applications where the VCSEL and photodetector require separate operation such as duplex serial data communications applications. A first embodiment integrates a VCSEL with an MSM photodetector on a semi-insulating substrate. A second embodiment builds layers of a p-i-n photodiode on top of layers forming a VCSEL using a standard VCSEL process. The p-i-n layers are etched away in areas where VCSELs are to be formed and left where photodetectors are to be formed. The VCSELs underlying the photodetectors are inoperable, and serve to recirculate photons which are not initially absorbed back into the photodetector. The transmit and receive pairs are packaged into a single package for interface to multifiber ferrules. The distance between the devices is precisely defined photolithographically, thereby making alignment easier. In a further alternate embodiment, a FET is coupled to the p-i-n photodiode to form an integrated detector preamplifier along with the VCSEL transmitter all on the same optical reference plane.

Owner:OPTICAL COMM PRODS

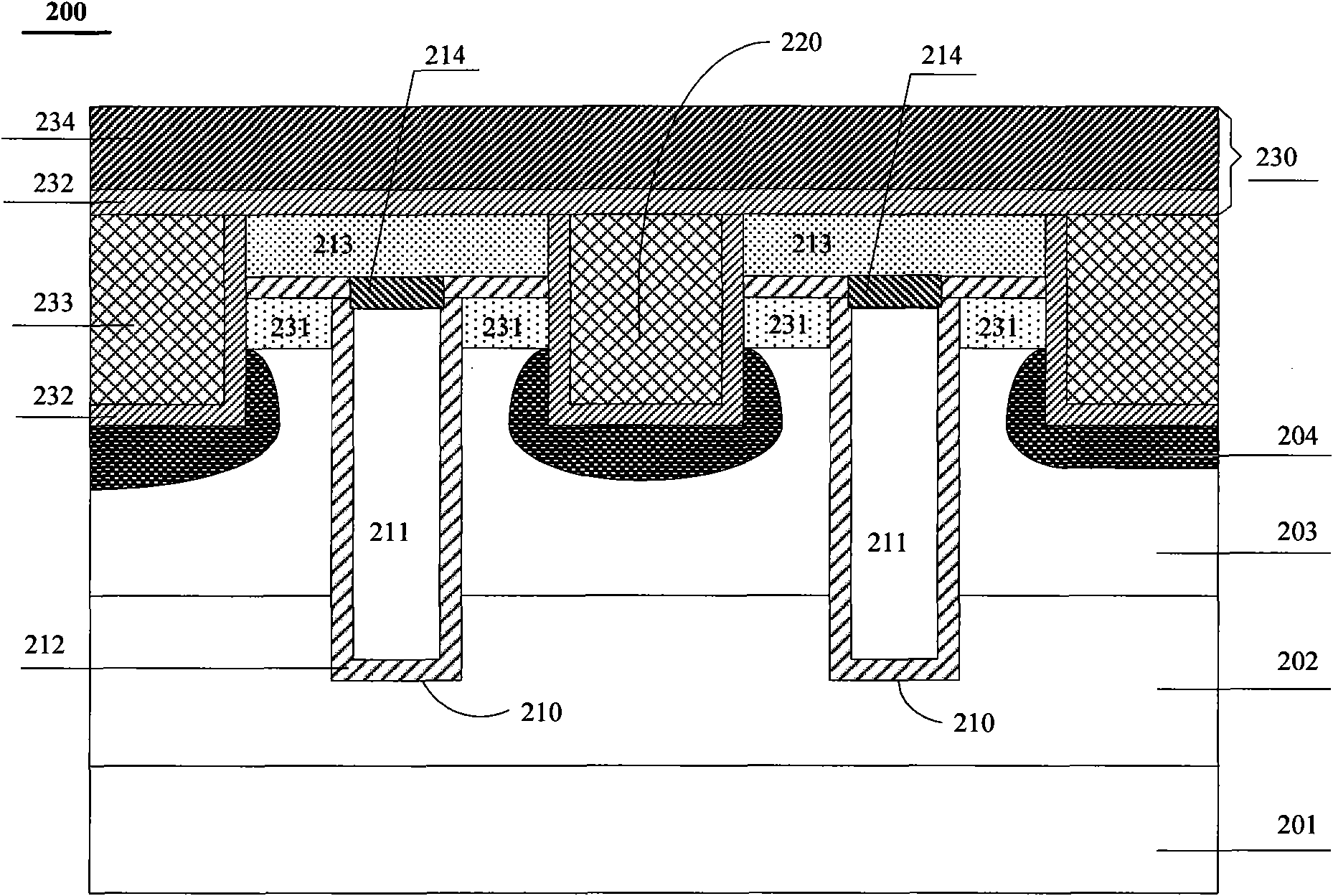

MOS (metal oxide semiconductor) transistor

InactiveCN102403352ASmall apertureImprove performanceSemiconductor devicesElectrical conductorDouble diffusion

The invention provides an MOS (metal oxide semiconductor) transistor, which is a trench vertical double-diffusion transistor. A metallic layer for leading a source electrode out is filled in a contact hole positioned between two adjacent source regions by means of a metallic plug, and a body contact area in heavy doping is formed below the contact hole. All metals in an MOS transistor structure pass through the metal plug filled in the contact hole to contact with a silicon body, the silicon body contacted by the side walls of the contact hole is a first semiconductor type doped source region, the silicon body contacted by the bottom of the contact hole is the second semiconductor type doped body contact area, and both the areas are heavy doped areas, so that various parasitic effects generated caused by contact of the metals with a light doped silicon body are prevented effectively, and the performance of the MOS transistor is improved. Simultaneously, by the aid of the metallic plug, the bore diameter of the contact hole is greatly reduced, the dimensions of devices are further decreased, and the integration level of the devices is improved.

Owner:CSMC TECH FAB1

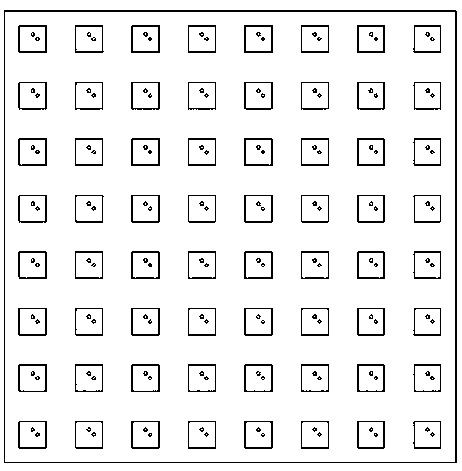

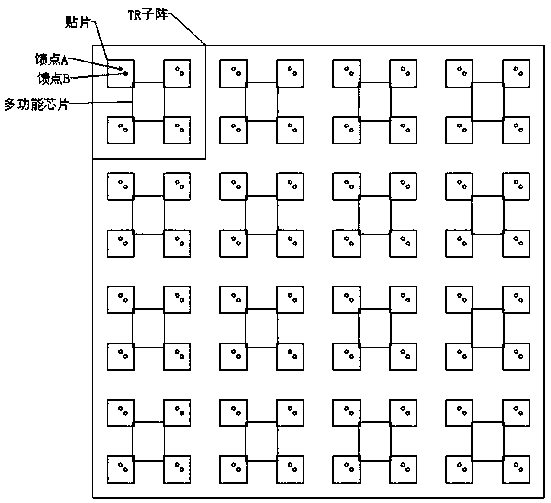

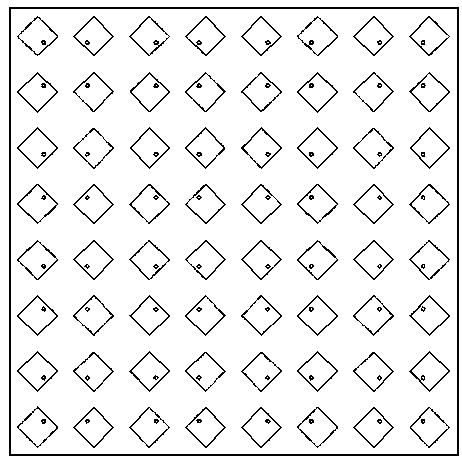

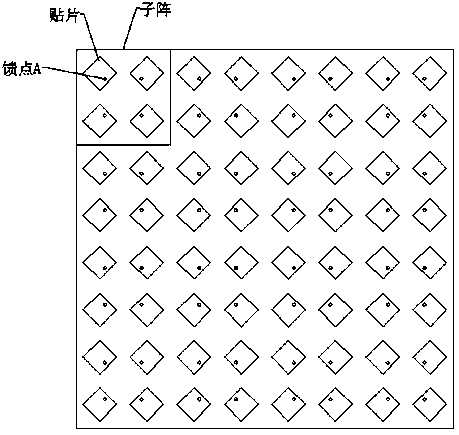

Phased-array antenna capable of realizing arbitrary polarization switching

InactiveCN111048911ALow costSmall structure sizeIndividually energised antenna arraysAntenna earthingsSoftware engineeringMechanical engineering

The invention relates to the field of phased-array antennas and especially relates to a phased-array antenna capable of realizing arbitrary polarization switching. The phased-array antenna comprises phased-array radiation units and a TR channel module. The TR channel module comprises N 2*2 TR sub-arrays, each TR sub-array comprises four radiation units, and the number of TR channels of each TR sub-array is 2*4; each phased array radiation unit comprises a patch, a feed point A and a feed point B, wherein the feed point A and the feed point B are located on the patch; and each phased array radiation unit carries out double-feed-point feeding. In the invention, one set of phased-array antenna equipment is used to realize functions of linear polarization, left-hand circular polarization, right-hand circular polarization and the like which are possessed by three sets of phased-array antenna equipment in the past so that cost and a structural size are greatly reduced, and a parasitic effectgenerated by using active devices is avoided.

Owner:CHENGDU RDW TECH CO LTD

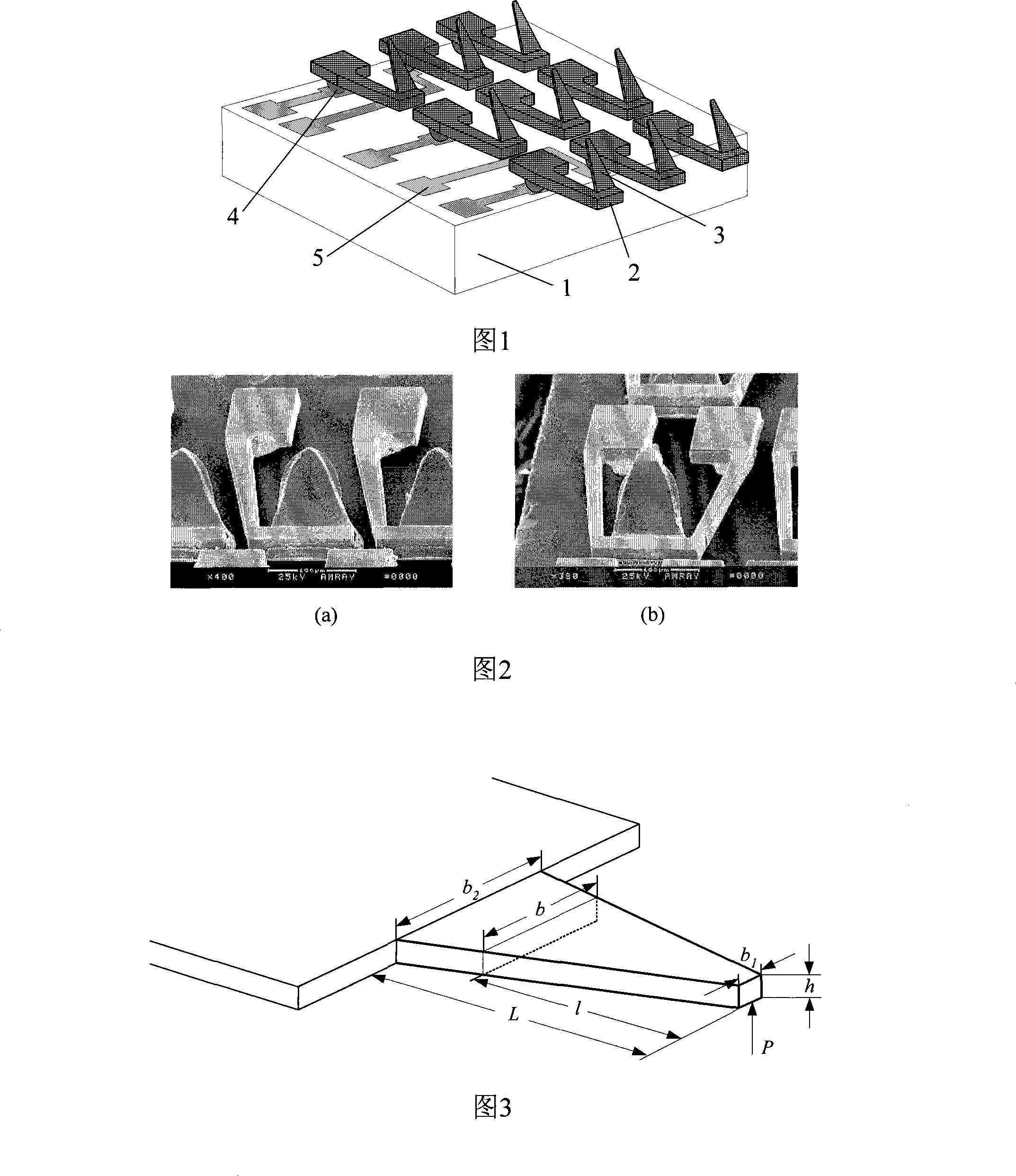

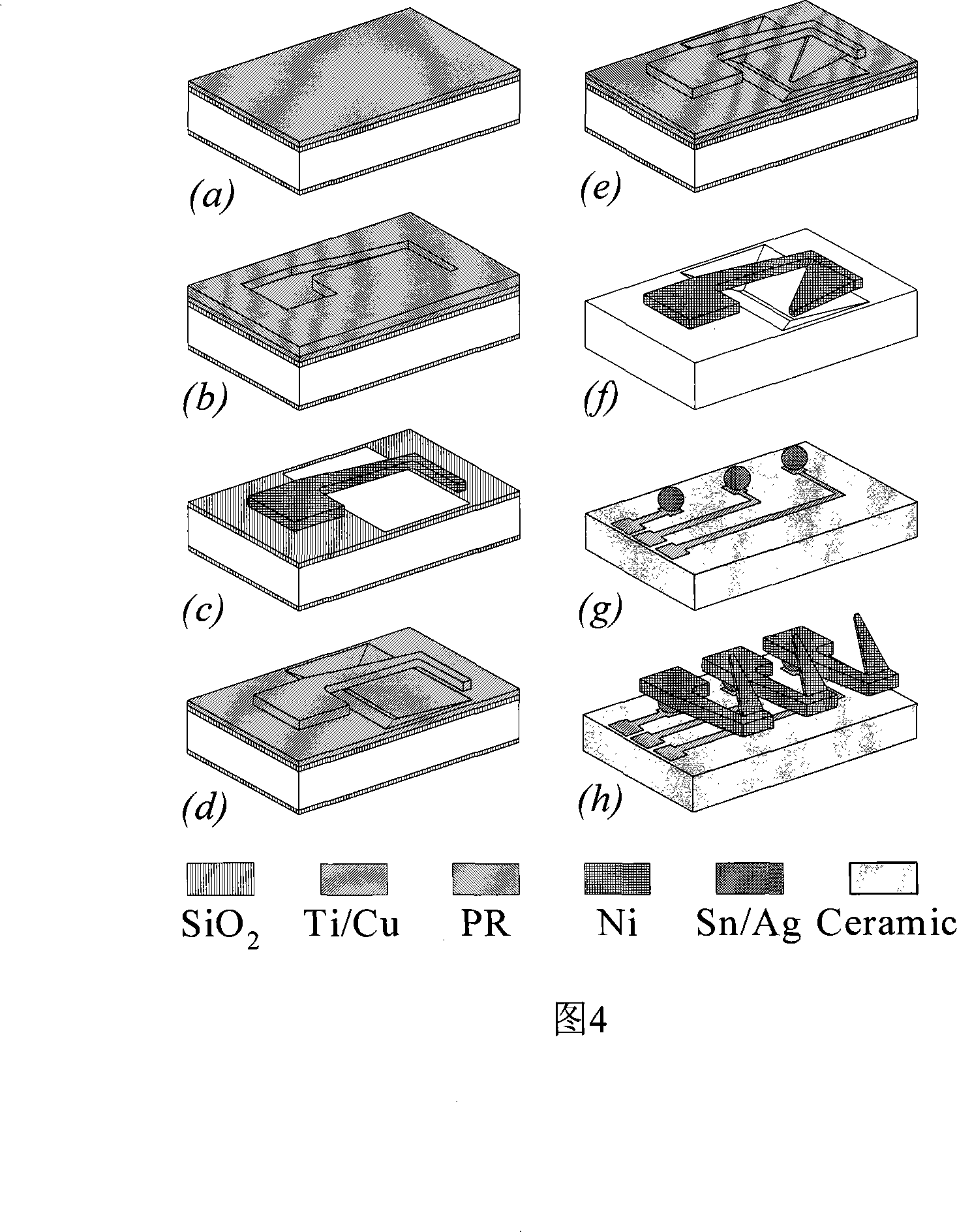

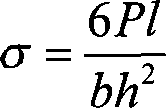

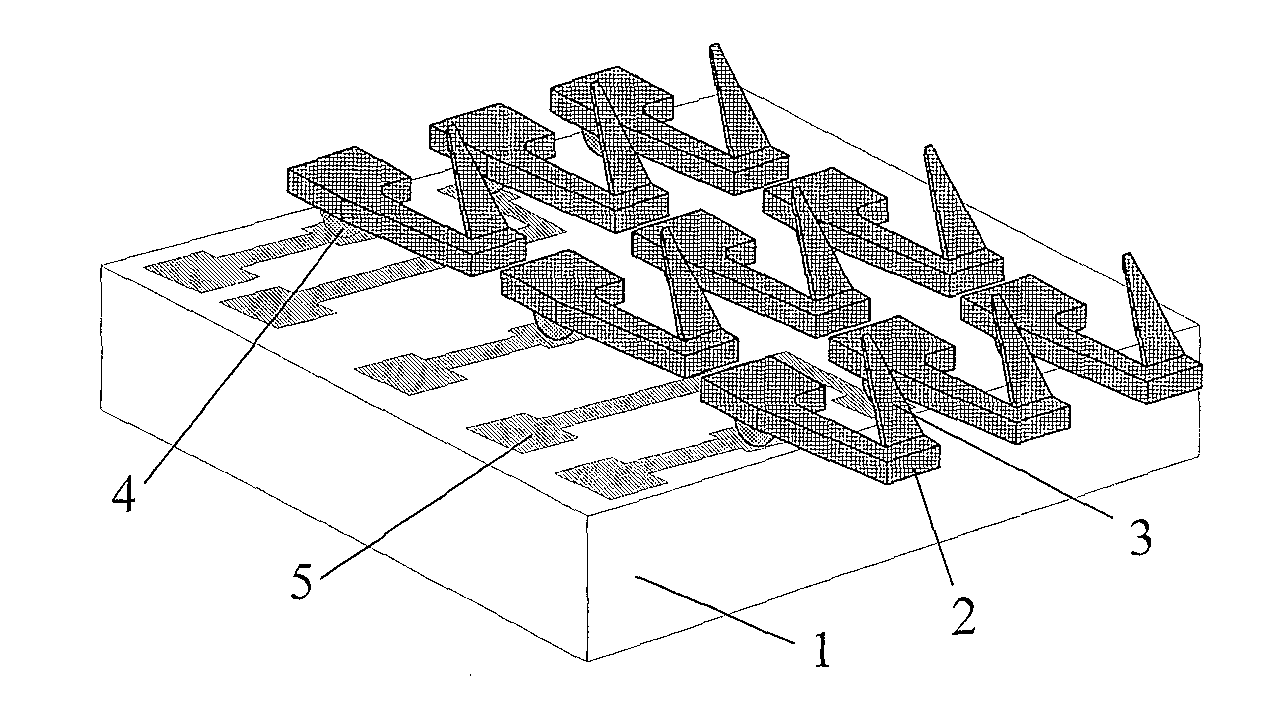

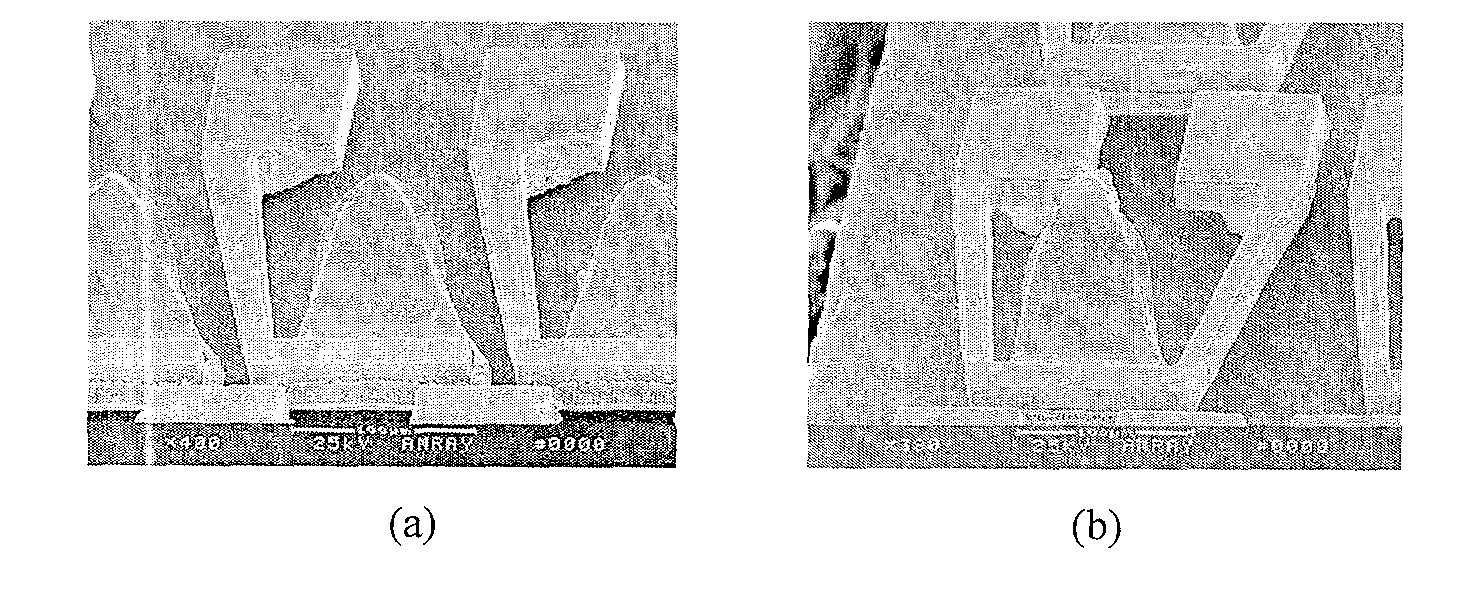

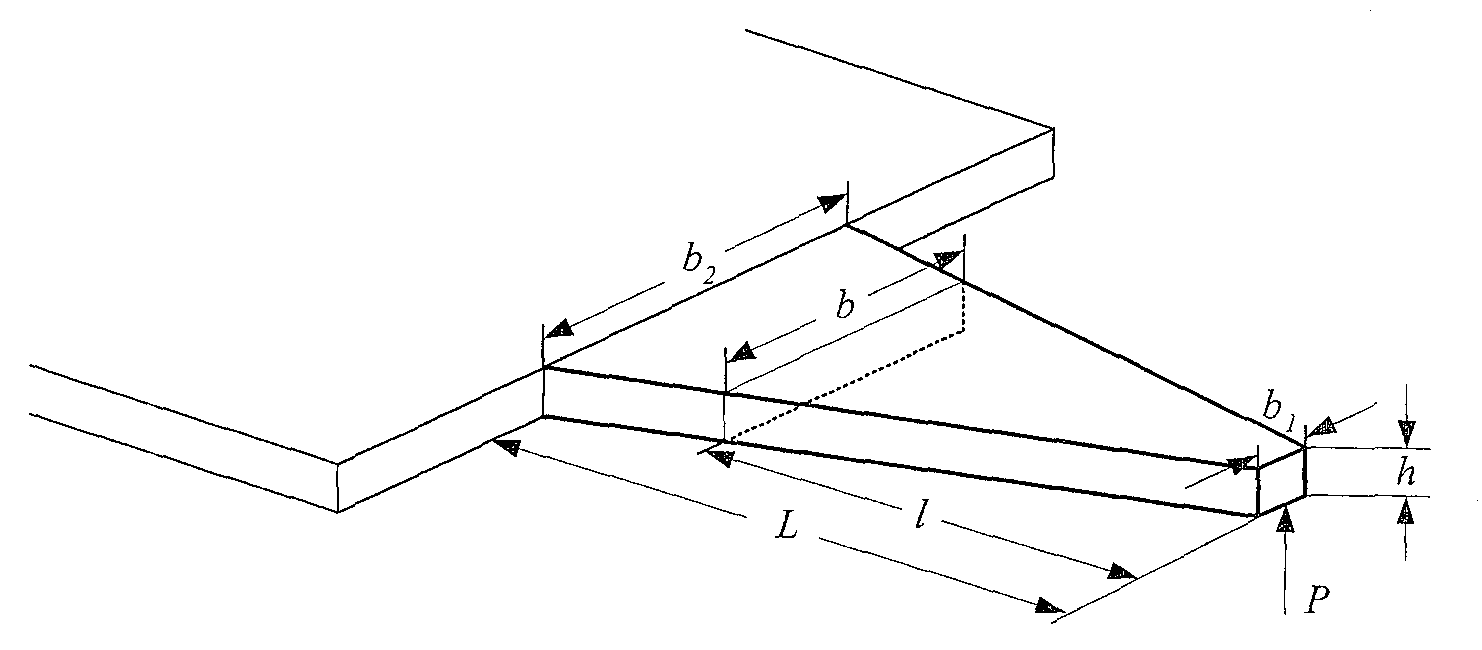

Micro-mechanism testing probe card based on electroplating technique and manufacturing method thereof

ActiveCN101214916AIncreased needle tip displacementIncrease displacementElectronic circuit testingElectrical measurement instrument detailsMicro mechanismAnisotropic etching

The invention relates to a micro mechanical testing probe card based on electroplating process and a manufacturing method thereof, and is characterized in that, cantilevers and probe tips are manufactured and formed on a silicon wafer with electroplated metal nickel; the probe tips are manufactured on an (111) inclined surface of the silicon wafer, and each probe tip is connected with a ceramic substrate with one or two probe cantilevers; the probe cantilevers and the probe tips adopt an isostress beam structure; probes on an flip chip substrate are intensively arranged in two directions. The manufacturing is characterized in that: firstly, the upper surface of the (100) silicon wafer is taken as the electroplated working face, and the probe cantilevers of a low stress nickel layer is formed by electroplating; and then a deep groove (111) inclined surface produced by anisotropic etching is taken as the working face, and the probe tips of the low stress nickel layer is formed by electroplating, and then the probes are connected with a package substrate by a flip chip process, and finally the probe structure is released through a method of removing the corrosion of the silicon wafer.

Owner:深圳市道格特科技有限公司

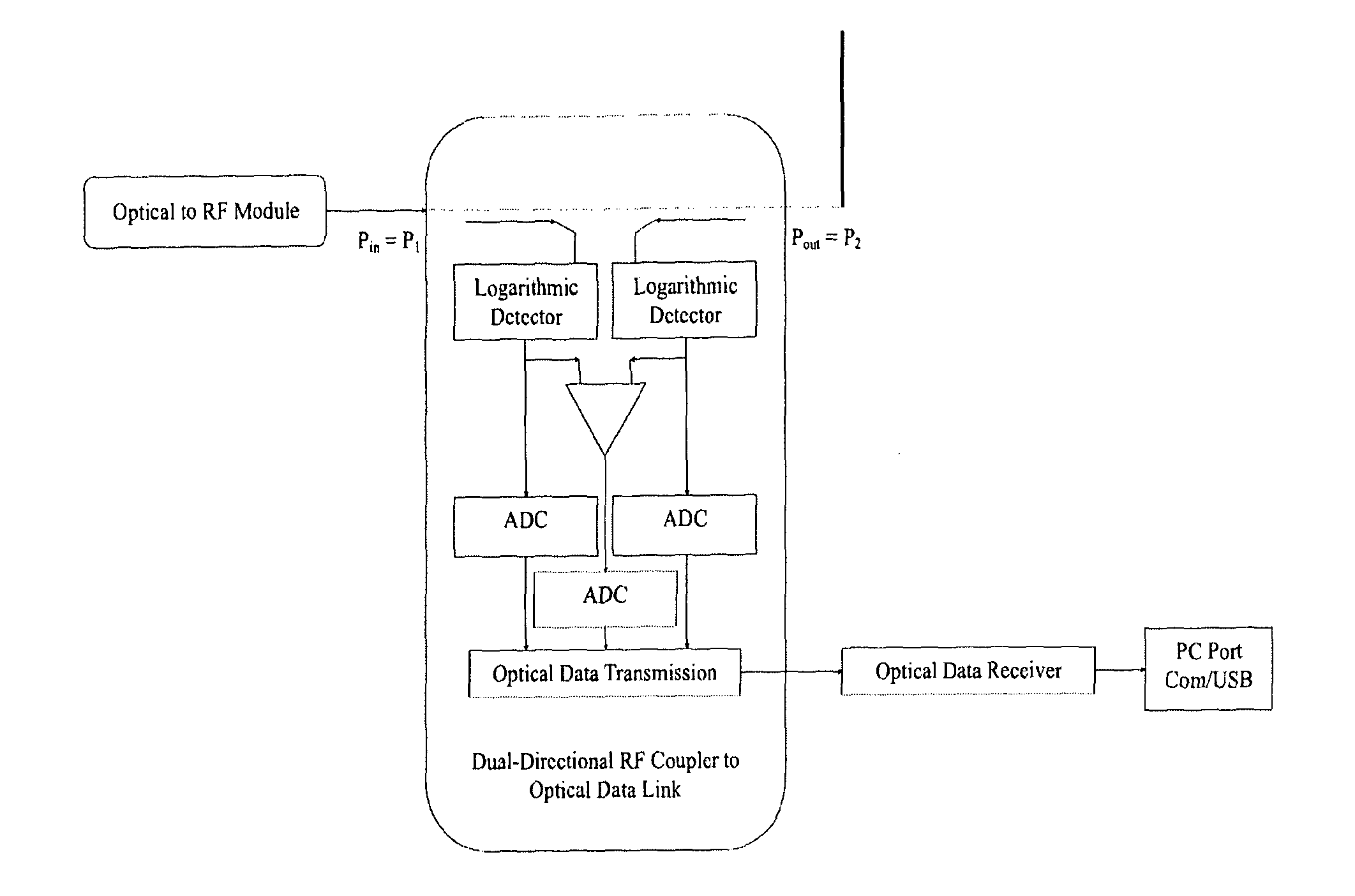

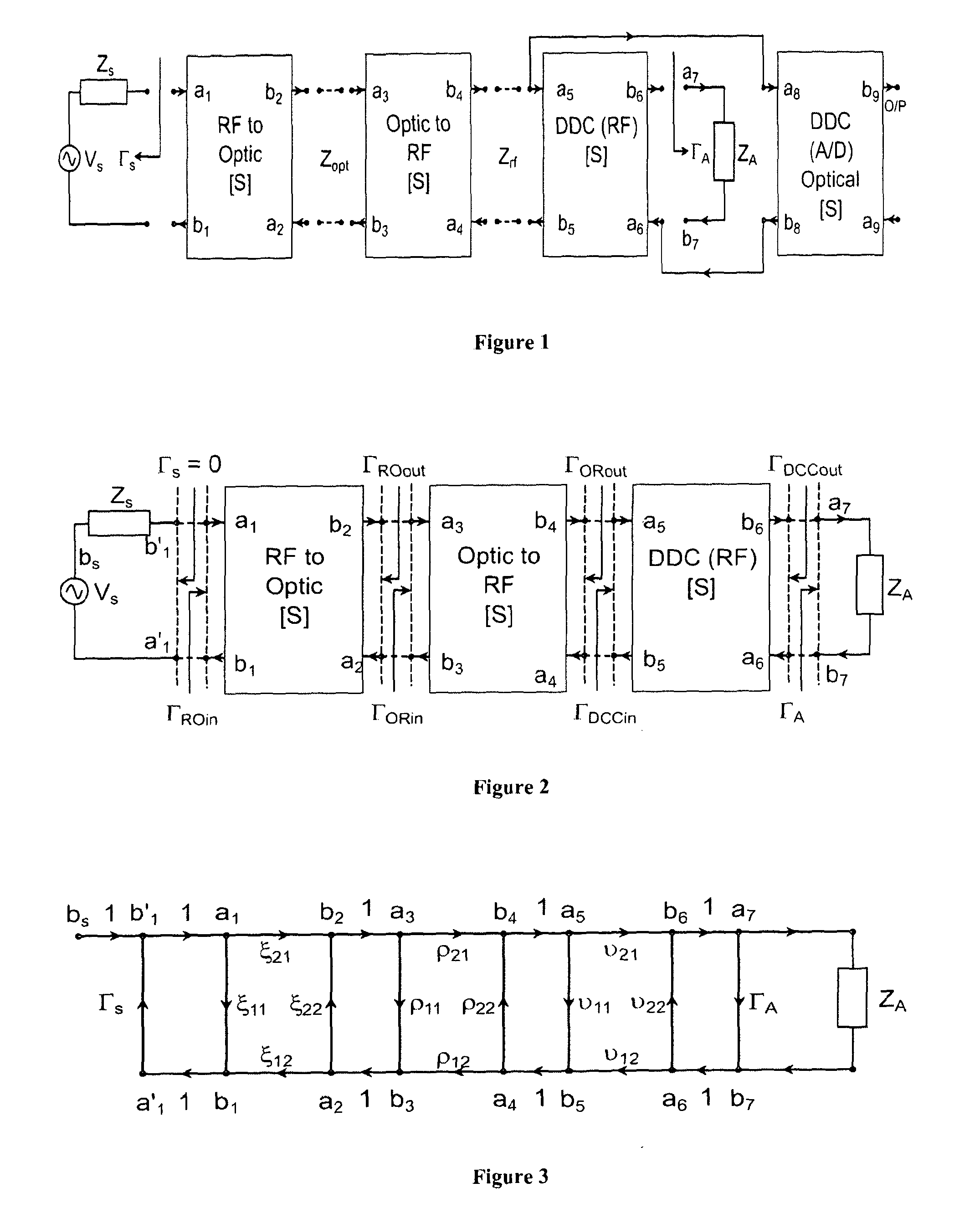

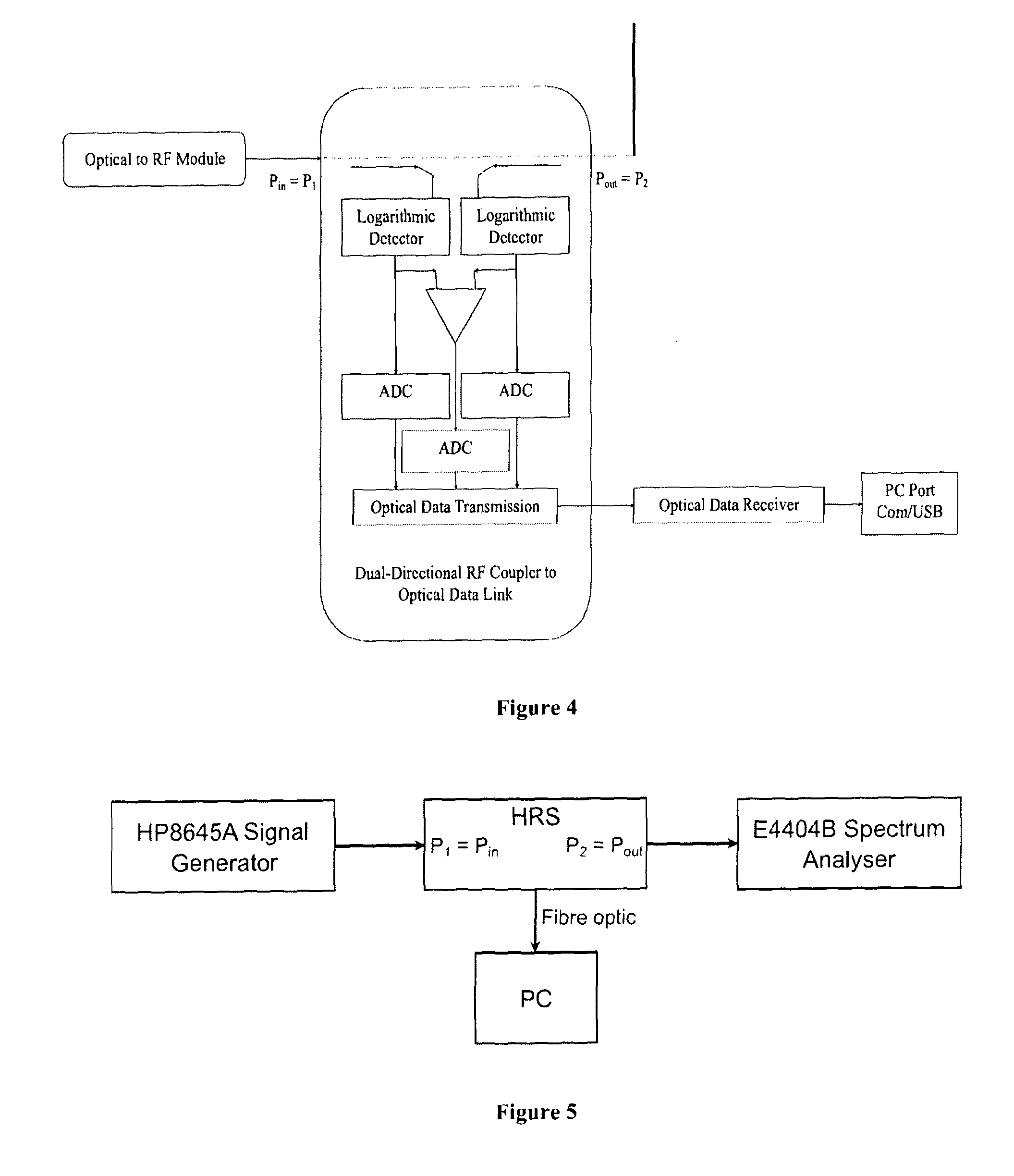

Hybrid reflectometer system (HRS)

InactiveUS20120206304A1Avoid radio frequency interferenceImprove accuracyTransmitters monitoringReceivers monitoringCommunications systemRf components

A RF signal test and measurement system capable of measuring forward and reverse signal parameters of RF components including Electrically Small Antennas (ESA) and capable of being integrated within a communications system to aid the automatic retuning of antennas.

Owner:THE SEC OF STATE FOR DEFENCE IN HER BRITANNIC MAJESTYS GOVERNMENT OF THE UK OF GREAT BRITAIN & NORTHERN IRELAND

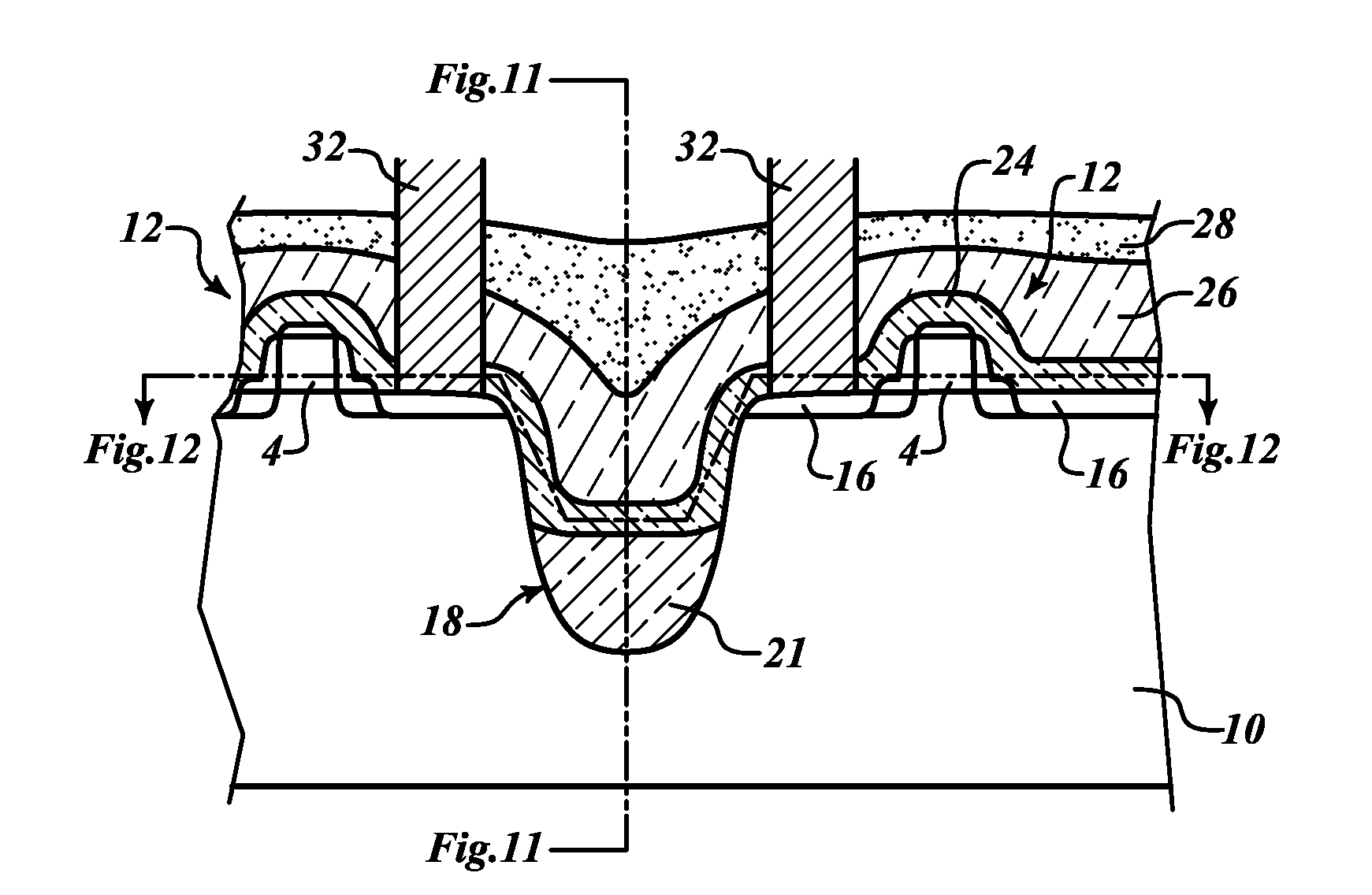

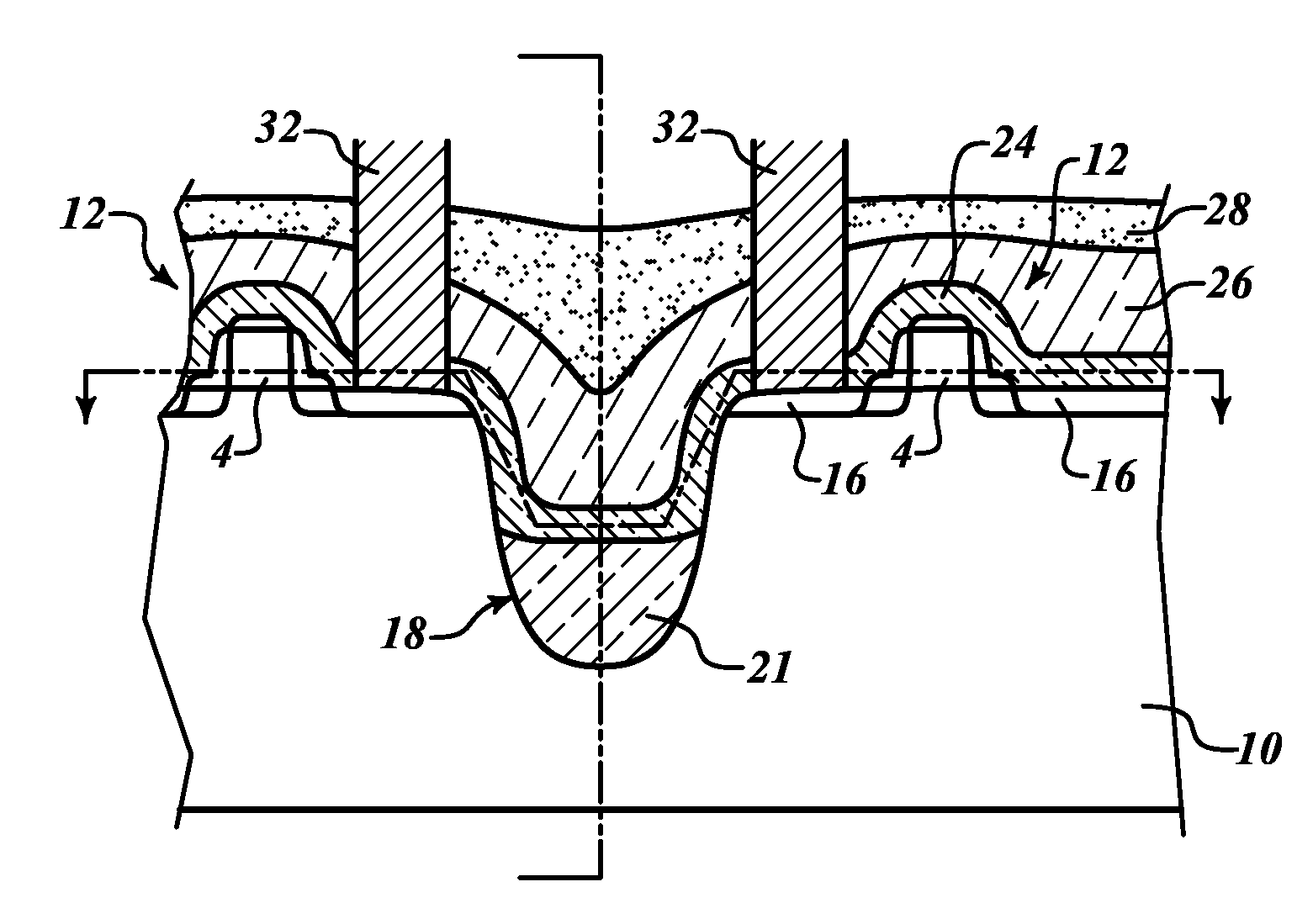

Strained transistor and method for forming the same

ActiveUS8216904B2Avoid parasitic effectsMinimizes stress riserTransistorSemiconductor/solid-state device manufacturingGate dielectricHigh stress

According to one embodiment, a semiconductor substrate is provided having at least two transistor regions formed therein. Overlying the channel regions is a gate dielectric and transistor gate electrodes overly the gate dielectric and are positioned overlying the channel regions. Source and drain regions are formed on either side of the channel regions to create a transistor structure. In order to provide isolation between transistors in the semiconductor substrate, a trench is formed in the substrate. A strain-inducting layer is then deposited over the transistor structures and into the trench in the semiconductor substrate. A high-stress nitride layer is one type of material which is suitable for forming the strain-inducing layer.

Owner:STMICROELECTRONICS SRL

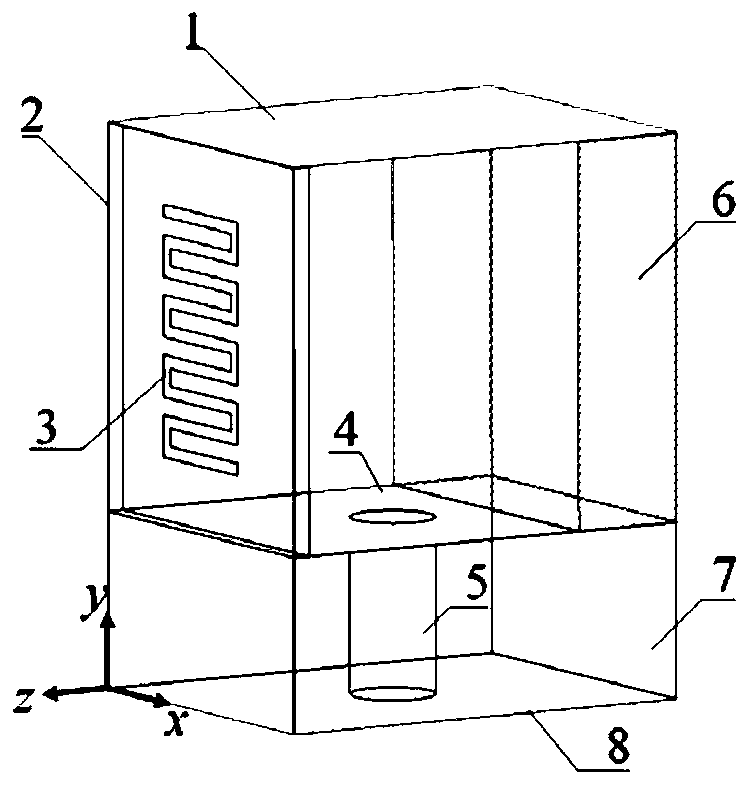

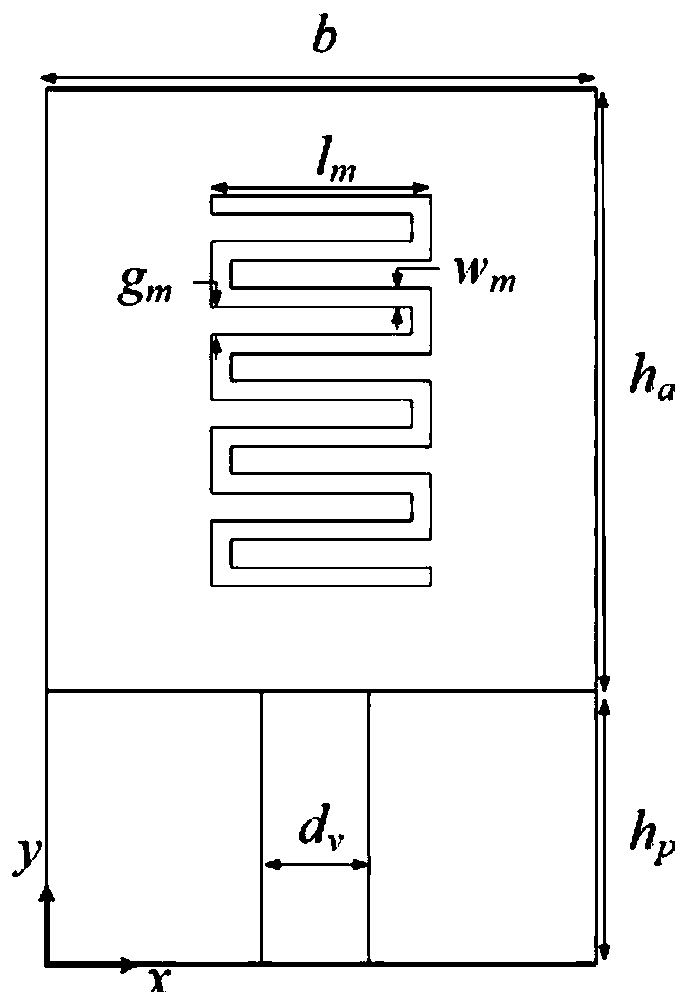

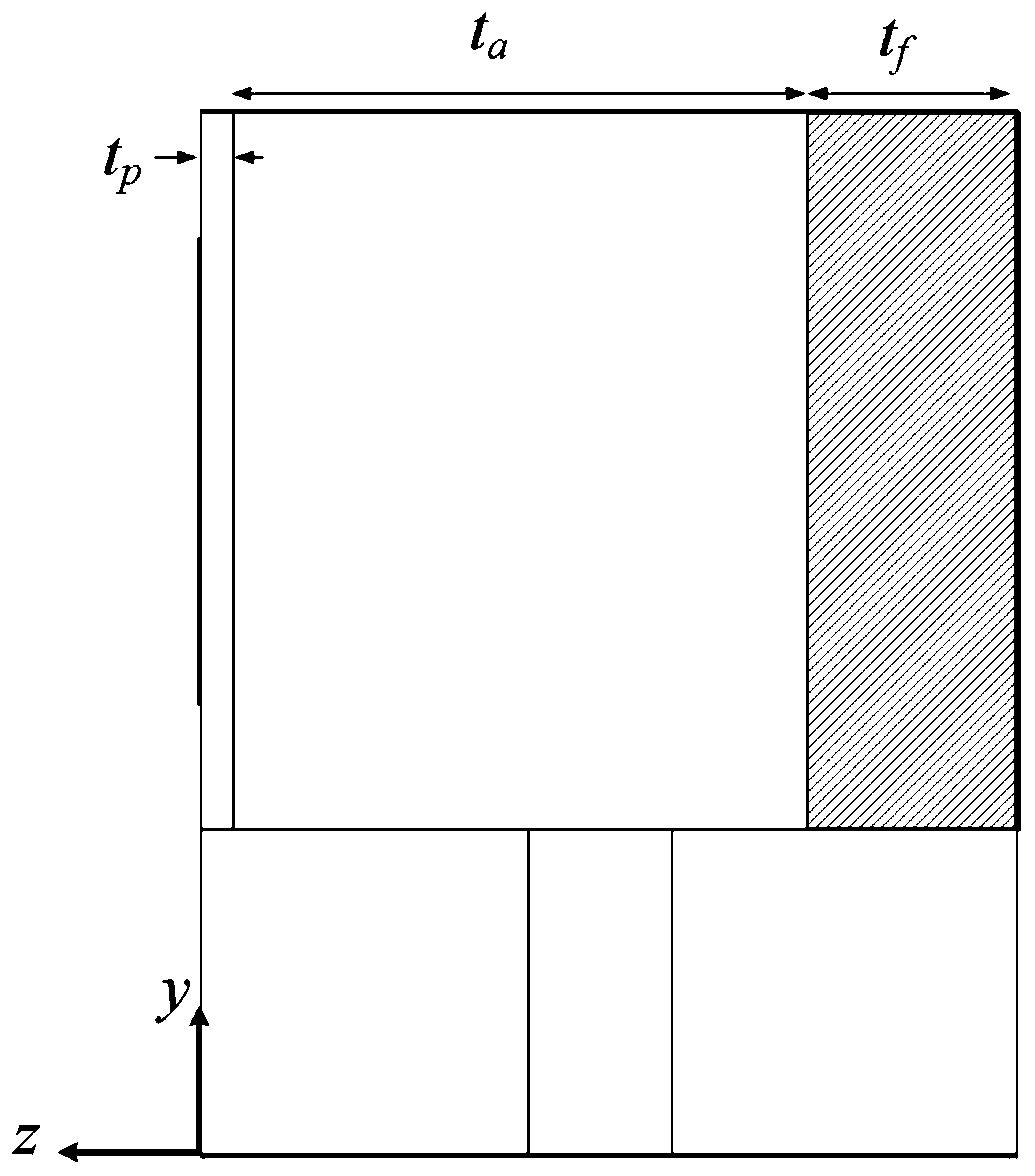

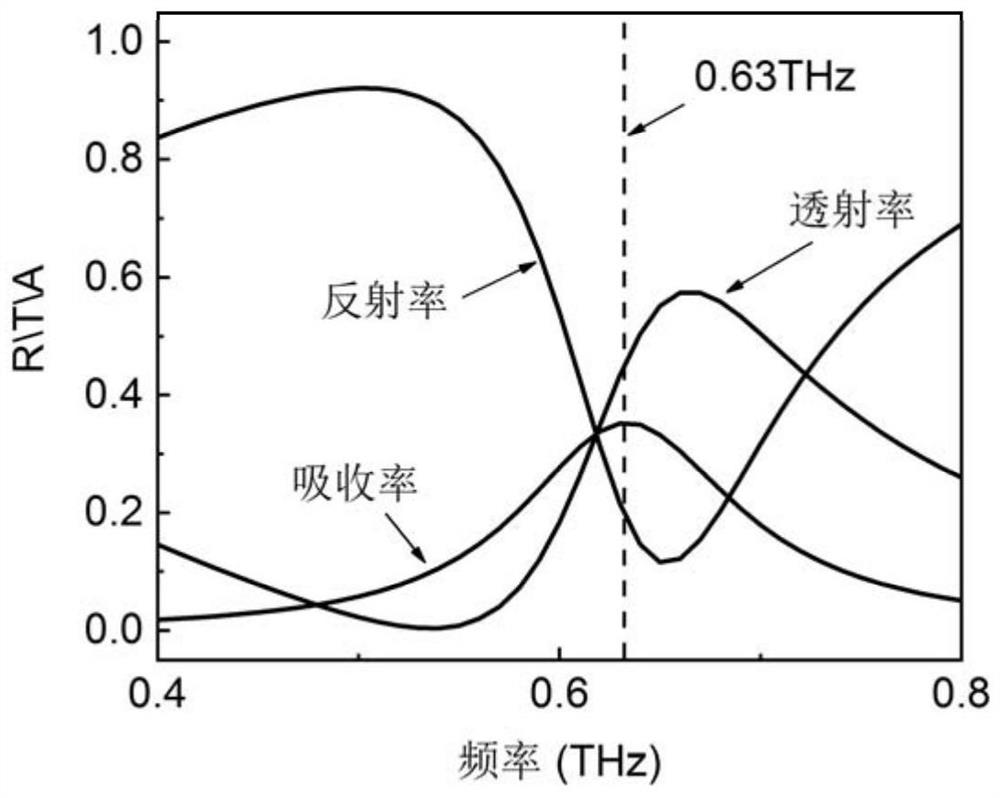

Three-dimensional broadband absorption-type frequency selection structure based on ferrite wave-absorbing material

InactiveCN110380225AReduce complexityEasy to realize broadband absorbingAntenna adaptation in movable bodiesRadiating element housingsScattering cross-sectionParallel plate

The invention relates to a three-dimensional broadband absorption-type frequency selection structure based on a ferrite wave-absorbing material. According to the invention, a periodic distribution structure is adopted, a structural unit adopts a structure mode of combining a band-pass channel with a wave-absorbing channel, and a wide pass band can be realized and two wave-absorbing bands can be realized at two sides of the pass band in combination with a metal bending line and a specific wave-absorbing material. An upper-layer parallel plate waveguide of the structural unit is composed of a metal bending line, an air cavity and the ferrite wave-absorbing material. A lower-layer parallel plate waveguide is composed of a metallized via hole and a dielectric substrate. According to the invention, a low-insertion-loss passband and two wide wave-absorbing bands can be realized, and good stability is achieved for obliquely incident electromagnetic waves. The structure not only can be appliedto the reduction of a single-station radar cross section (RCS), but also can be applied to the reduction of RCSs of double stations and even multiple stations.

Owner:HANGZHOU DIANZI UNIV

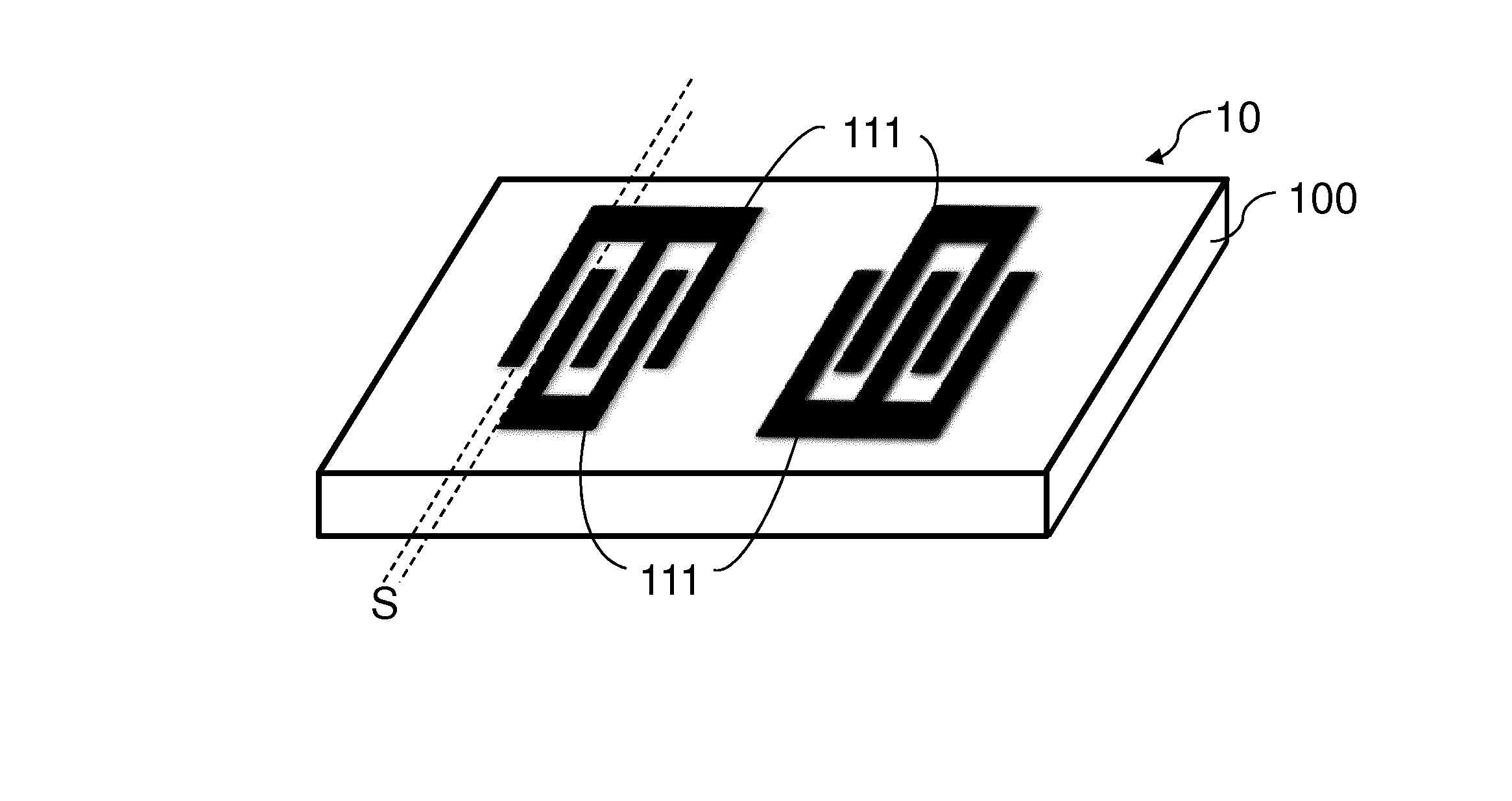

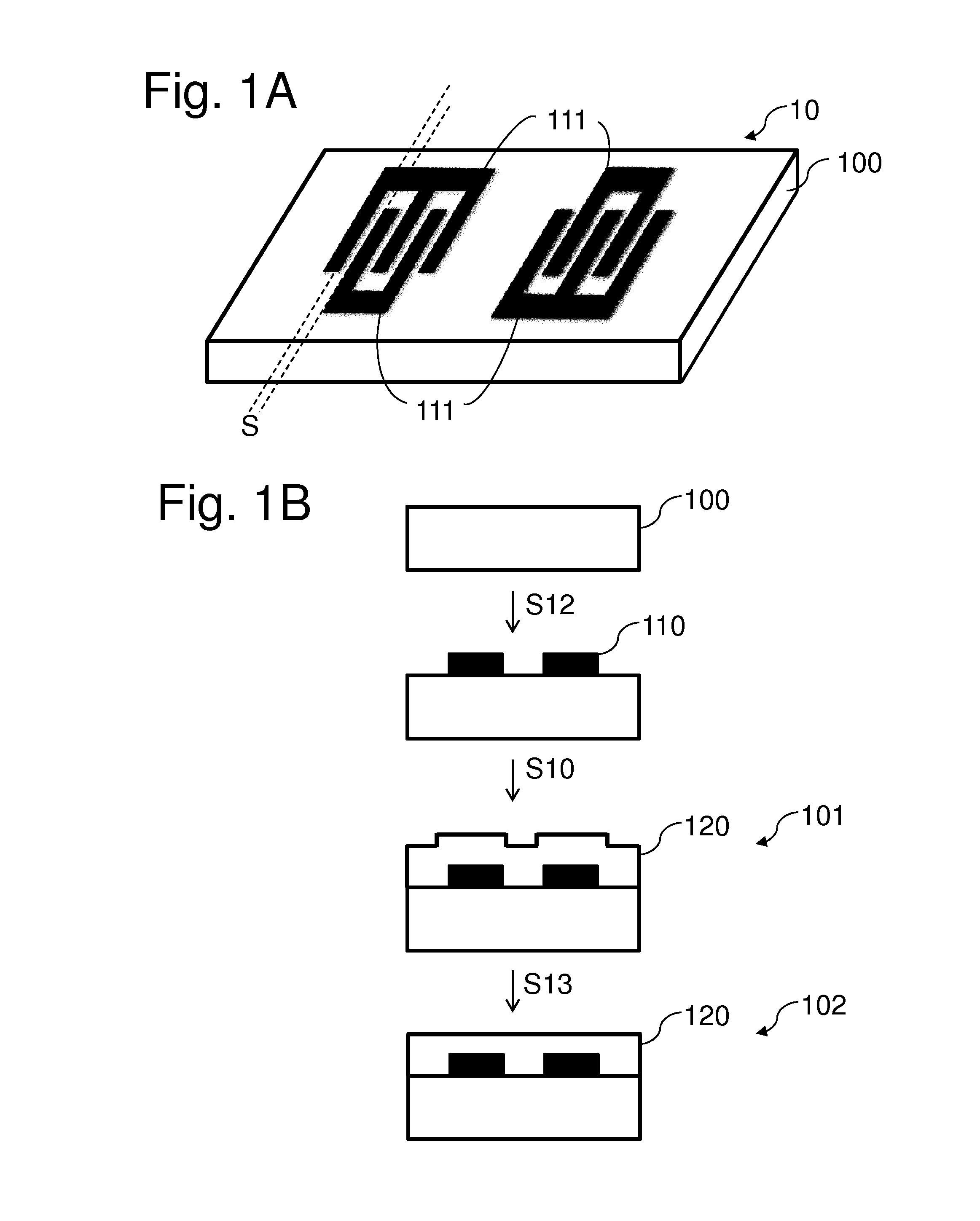

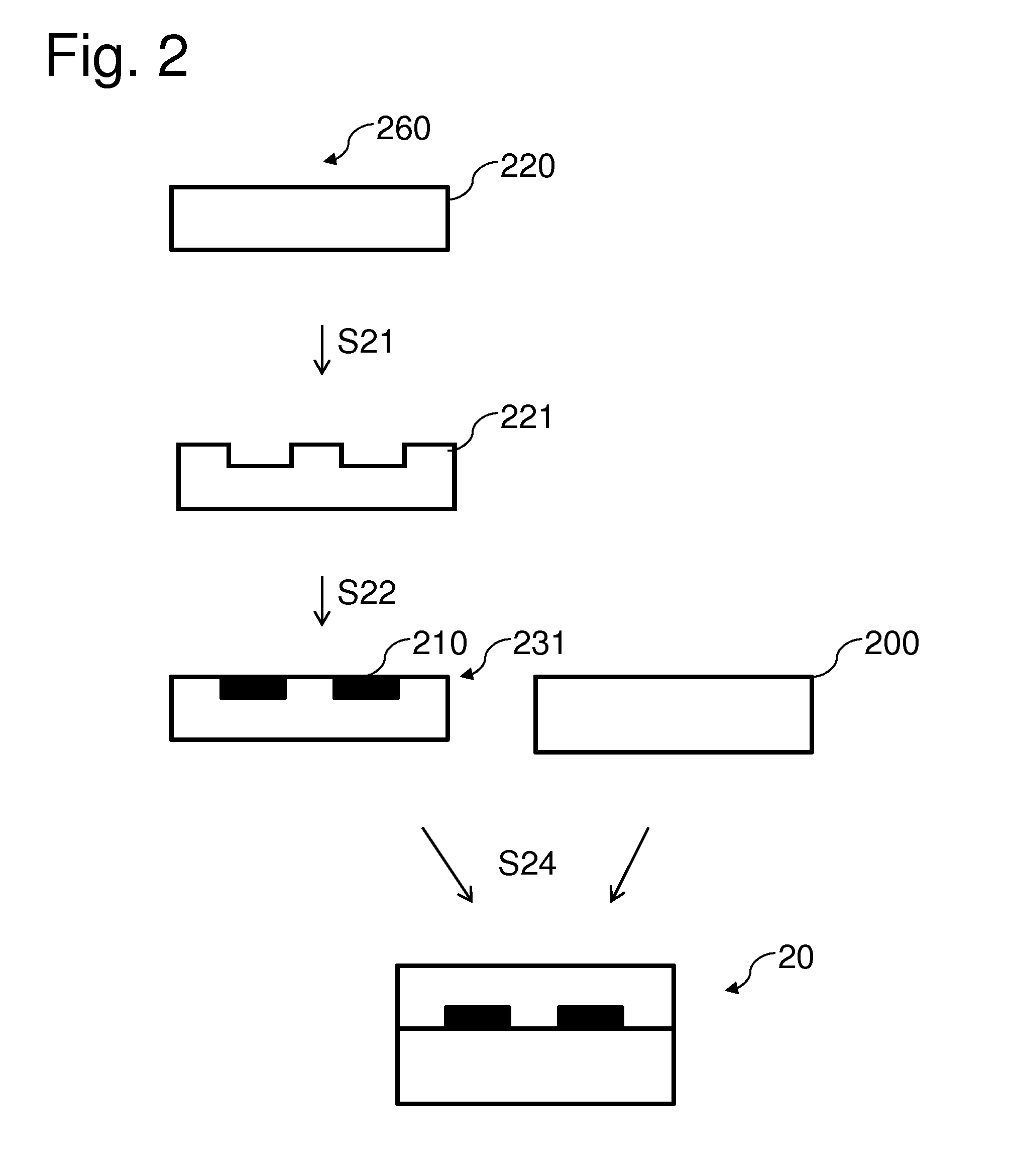

Advanced thermally compensated surface acoustic wave device and fabrication

ActiveUS20160065162A1Low insertion lossHigh power applicationPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesSurface acoustic wave sensorDielectric structure

This disclosure relates to a method of fabrication of a surface acoustic wave device comprising the step (a) of providing a piezoelectric structure, the step (b) of providing a dielectric structure, wherein the step (b) comprises a step (b1) of metalizing the dielectric structure, and the method further comprising the step (c) of bonding the metalized dielectric structure to the piezoelectric structure.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

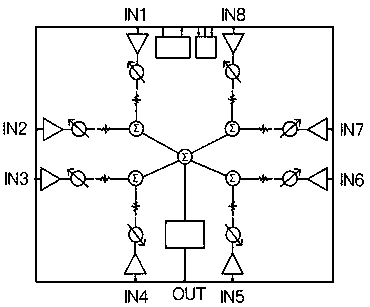

Phased-array antenna capable of realizing left-handed and right-handed circular polarization switching

ActiveCN110911834ALow costAvoid parasitic effectsParticular array feeding systemsRadiating elements structural formsAntenna radiationActive devices

The invention relates to the field of phased-array antennas, in particular to a phased-array antenna capable of realizing left-handed and right-handed circular polarization switching. The antenna comprises N 2 * 2 TR sub-arrays. Each TR sub-array comprises four phased-array antenna radiation units, and the number of TR channels of each TR sub-array is 1 * 4. Each phased-array antenna radiation unit comprises a patch and a feed point A located on the patch, and each phased-array antenna radiation unit is a single feed point. Only one set of phased-array antenna equipment in the scheme is used,the functions, such as left-handed and right-handed polarization switching, of two sets of phased-array antenna equipment in the past can be achieved, the cost and the structural size are greatly reduced, and the parasitic effect generated by using an active device is avoided. The antenna is mainly realized through an n-in-one multifunctional chip in combination with phased-array antenna layout.

Owner:CHENGDU RDW TECH CO LTD

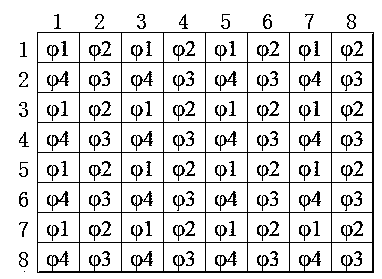

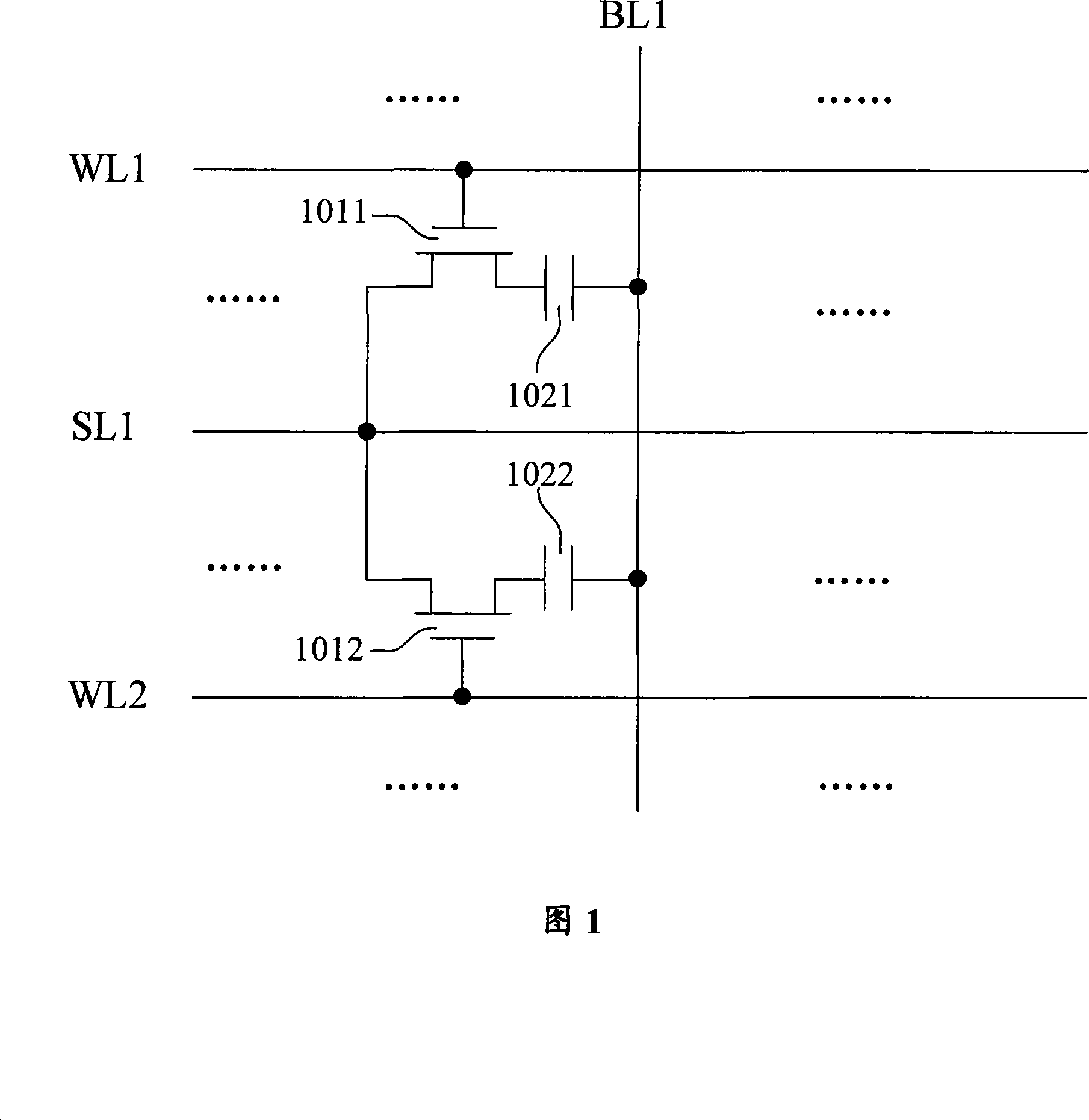

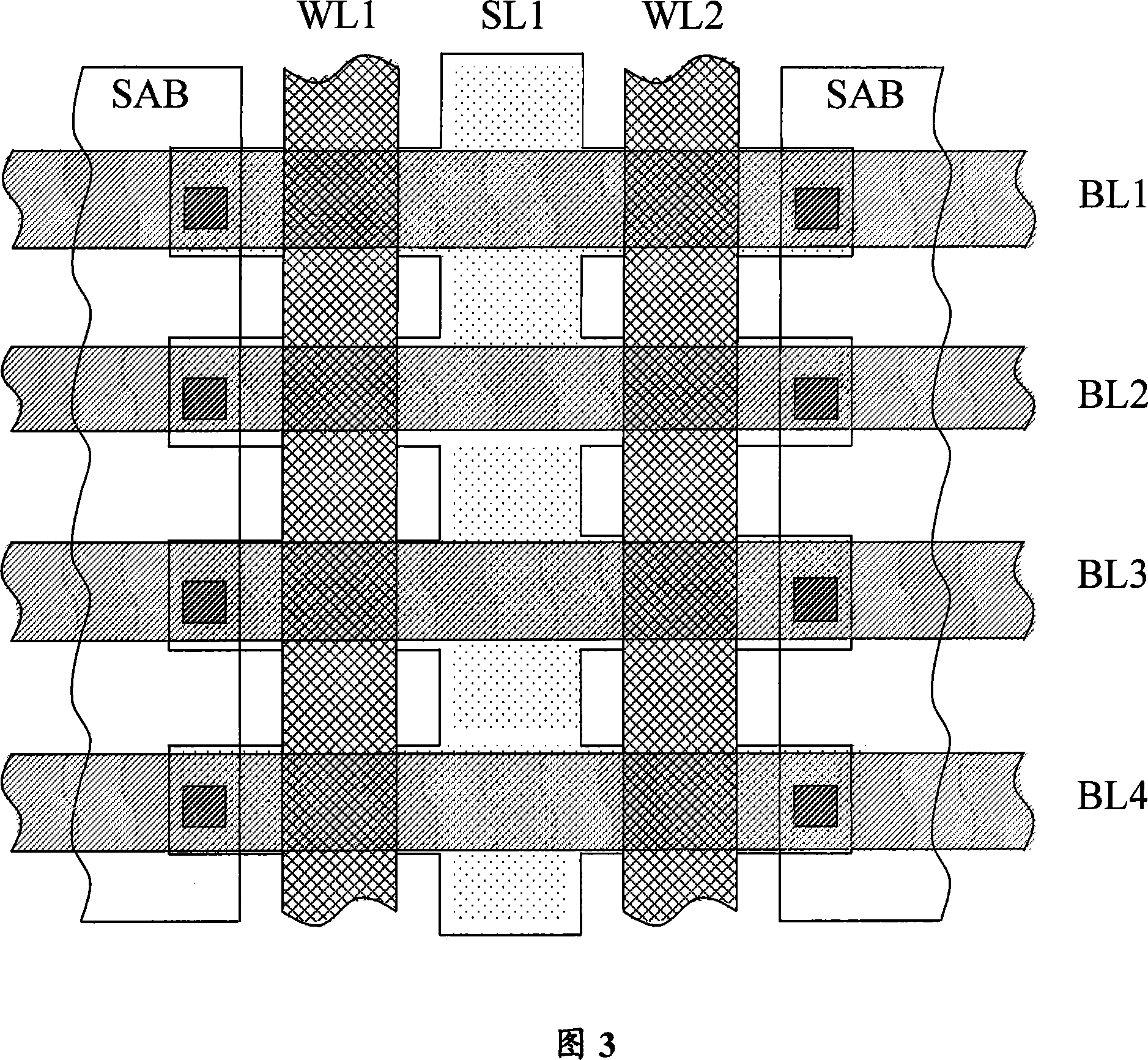

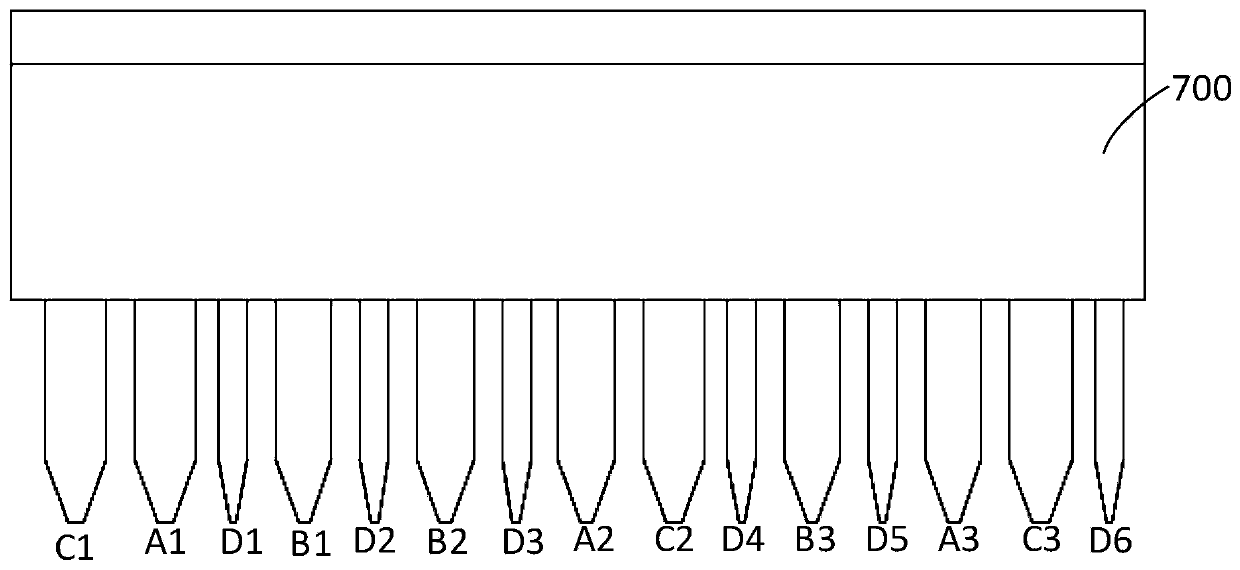

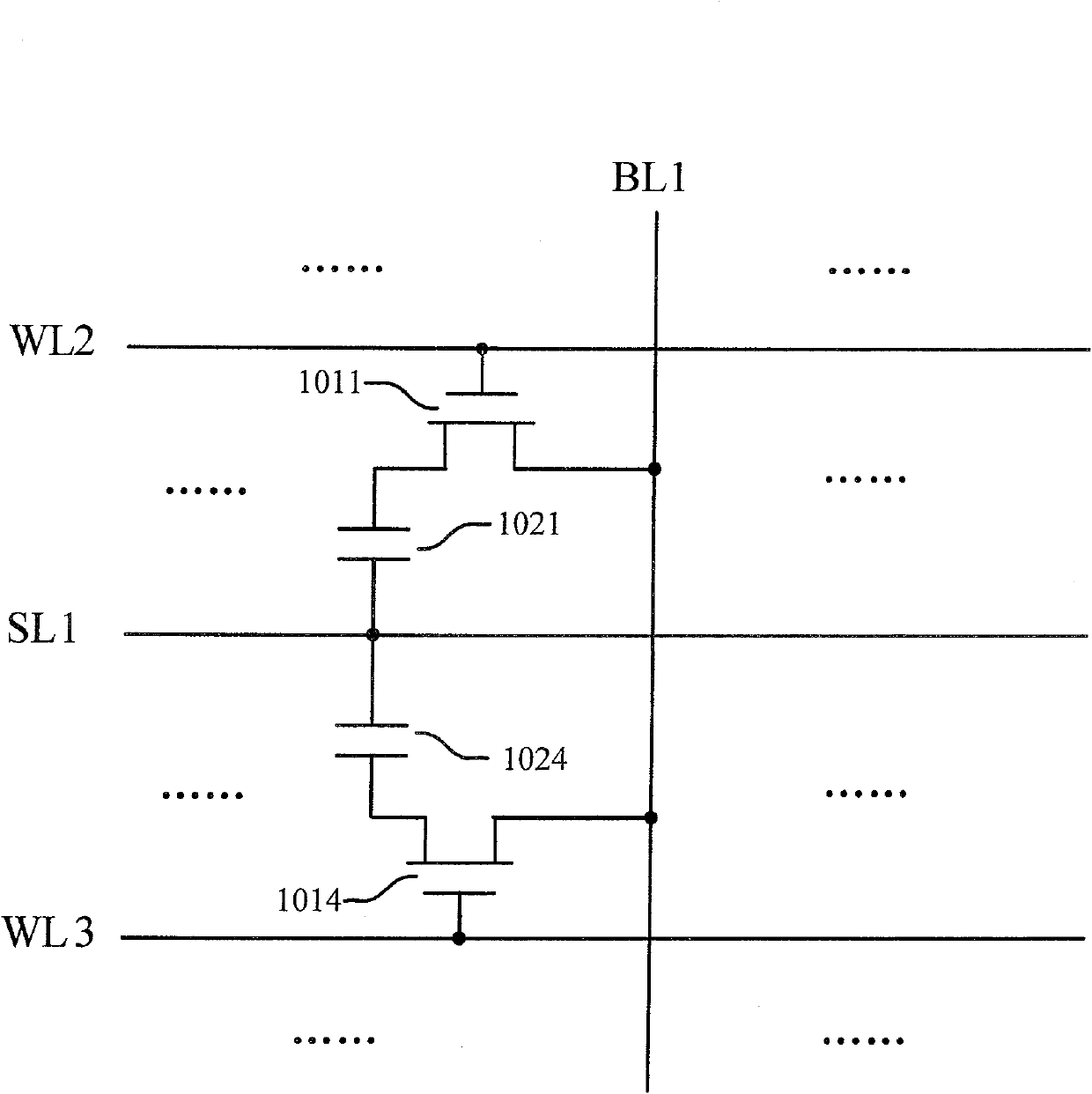

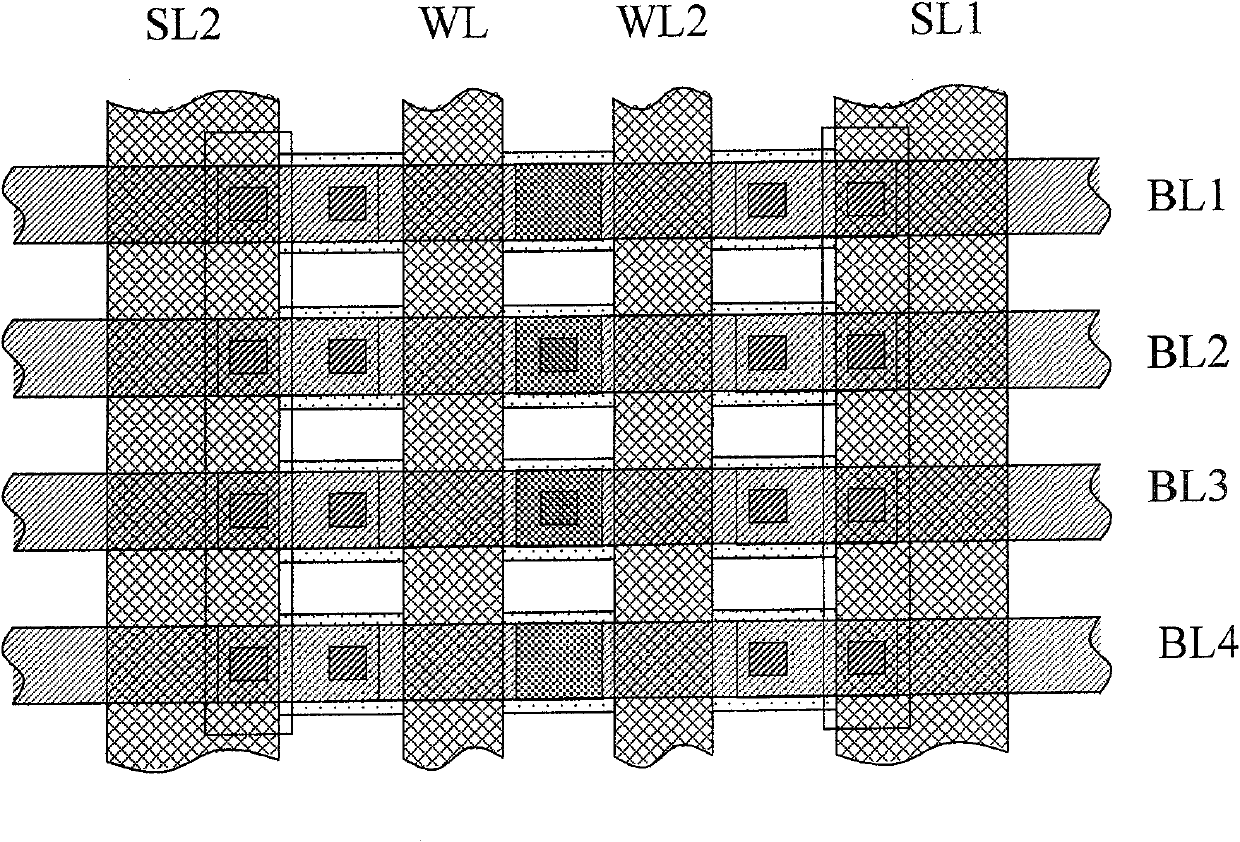

A programmable non volatile memory unit, array and its making method

InactiveCN101170116AReduce areaImprove integration densitySemiconductor/solid-state device detailsSolid-state devicesBit lineMedia layer

The invention discloses a programmable nonvolatile memory unit, an array and a manufacture method thereof. The invention provides a metal layer, a contact hole, a barrier layer, a plurality of polysilicons and an underlay with an active area. The polysilicons and the underlay with the active area form a plurality of transistors including a grid, a drain and a source. The source of the transistors forms a plurality of source lines. The polysilicons form a plurality of word lines. The metal lines in the metal layer form a plurality of bit lines. The metal layer, the contact hole, the barrier layer and the active area are connected in turn to form a capacitor, wherein, the barrier layer is used as the medium layer of the capacitor; the transistors and the capacitor are correspondingly connected to form a memory unit and arranged in corresponding wordlines, bit lines and source lines. The invention greatly improves the storage stability of the memory, further reduces the memory area and is good for the application of large scale integrated circuit.

Owner:GIGADEVICE SEMICON (BEIJING) INC

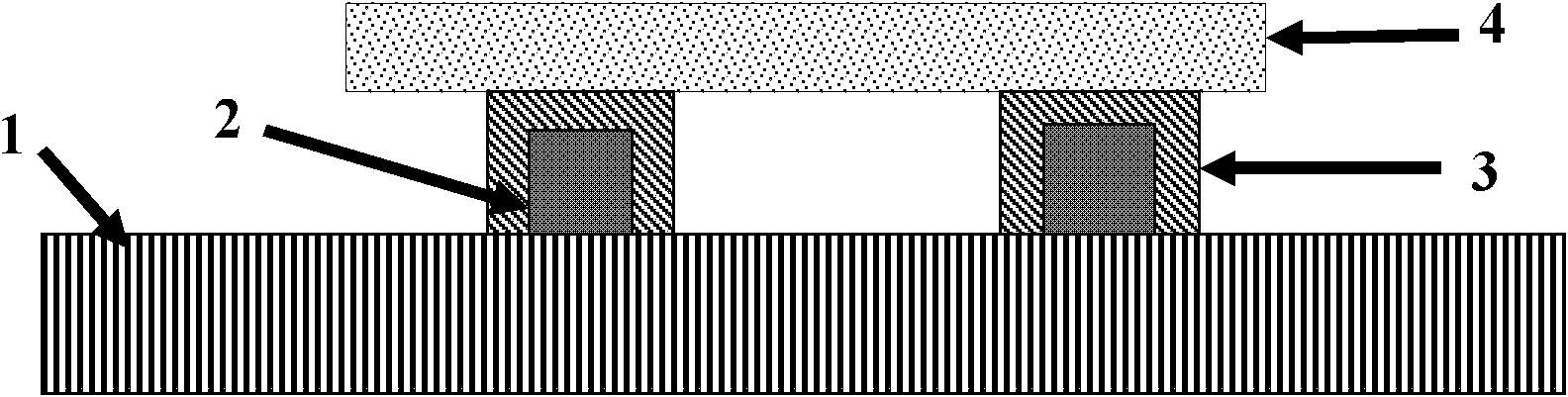

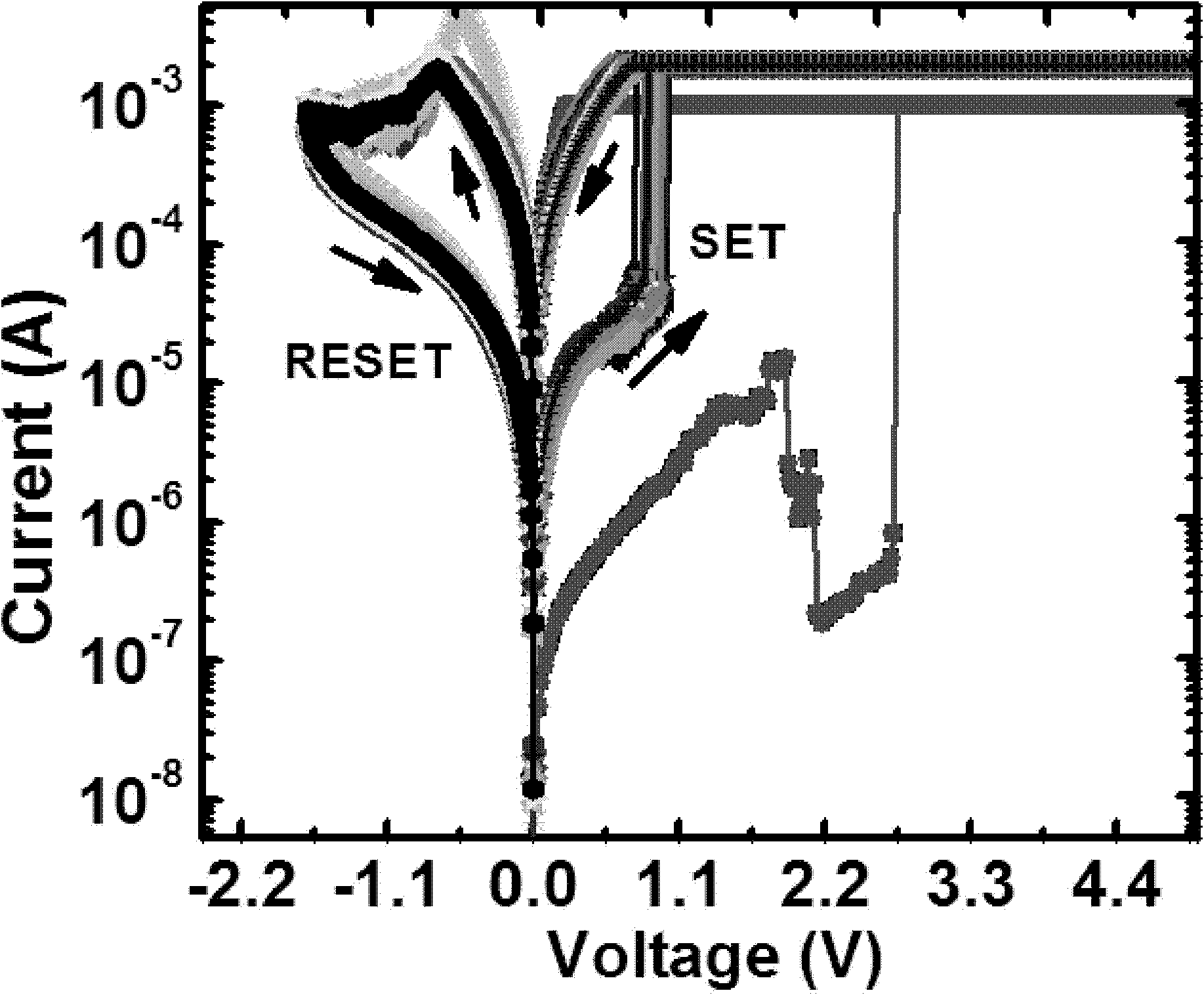

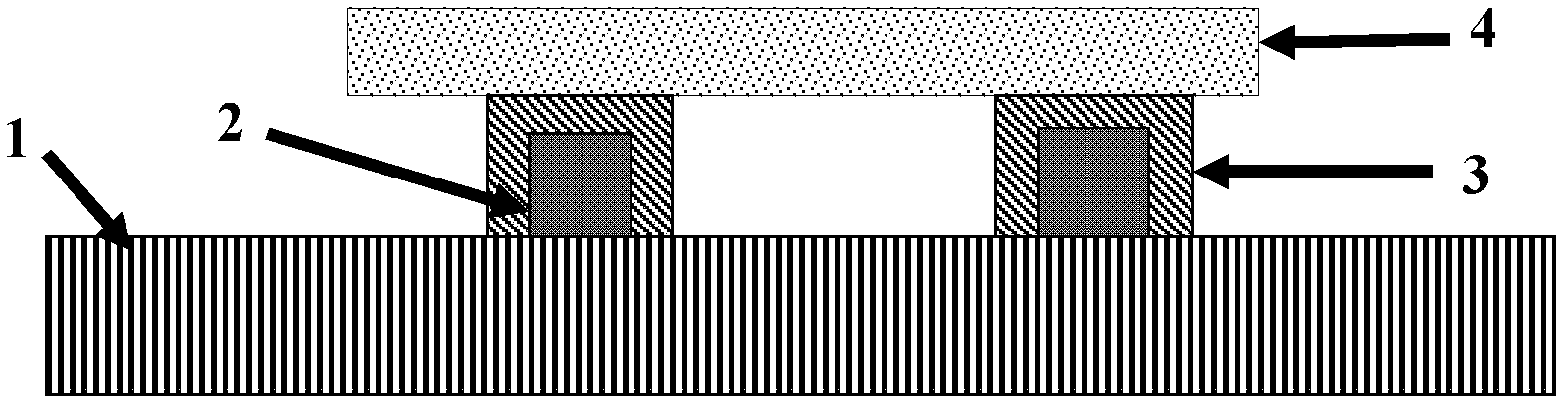

Method for preparing resistive random access memory

InactiveCN102593352AAchieve self-alignmentGuaranteed isolationElectrical apparatusDigital storagePartial oxidationStatic random-access memory

The invention discloses a method for preparing a resistive random access memory. The method comprises the following steps: preparing a bottom electrode on a substrate; then, carrying out partial oxidation on the metal of the bottom electrode so as to form a metal oxide with a thickness of 3-50 nm, and taking the metal oxide as a resistive random material layer; and finally, preparing a top electrode on the resistive random material layer. By using the method disclosed by the invention, a step of depositing a resistive random material layer in the traditional method is avoided, thereby greatly reducing the process complexity; meanwhile, the self-alignment between the resistive random material layer and the bottom electrode can be realized; the complete isolation between devices is ensured; various parasitic effects generated by the traditional process methods are avoided; and the consistency of the actual area and design area of each device is ensured.

Owner:PEKING UNIV

Method and an array for magnetizing a magnetizable object

Described is a method and array for magnetizing a magnetizable object. The method includes the steps of (a) applying a first degaussing signal to the magnetizable object to degauss the magnetizable object and the first degaussing signal is an alternating electrical signal having a first frequency and a first amplitude; (b) applying a magnetizing signal to the degaussed magnetizable object to magnetize the magnetizable object; and (c) applying a second degaussing signal to the magnetized magnetizable object to partially degauss the magnetized magnetizable object and the second degaussing signal is an alternating electrical signal having a second frequency and a second amplitude.

Owner:NCTE

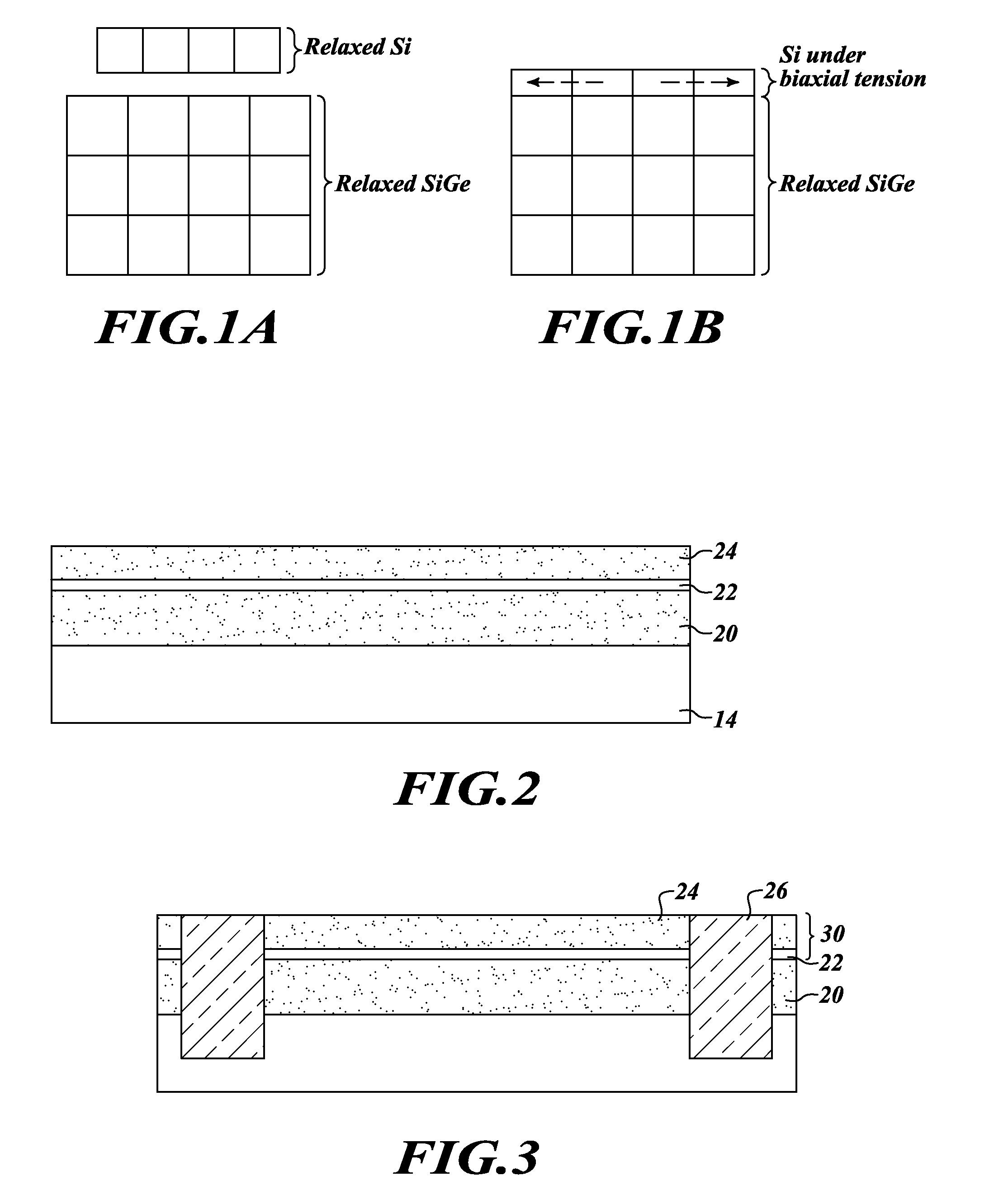

Structure and method for making a strained silicon transistor

InactiveUS8716752B2Eliminate generationPrevent lockoutSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureSingle crystal

Owner:STMICROELECTRONICS SRL

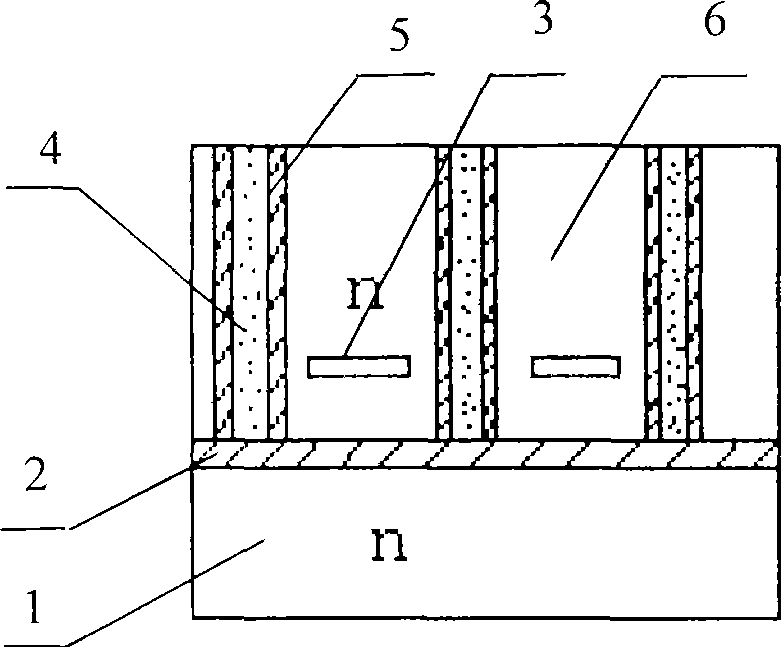

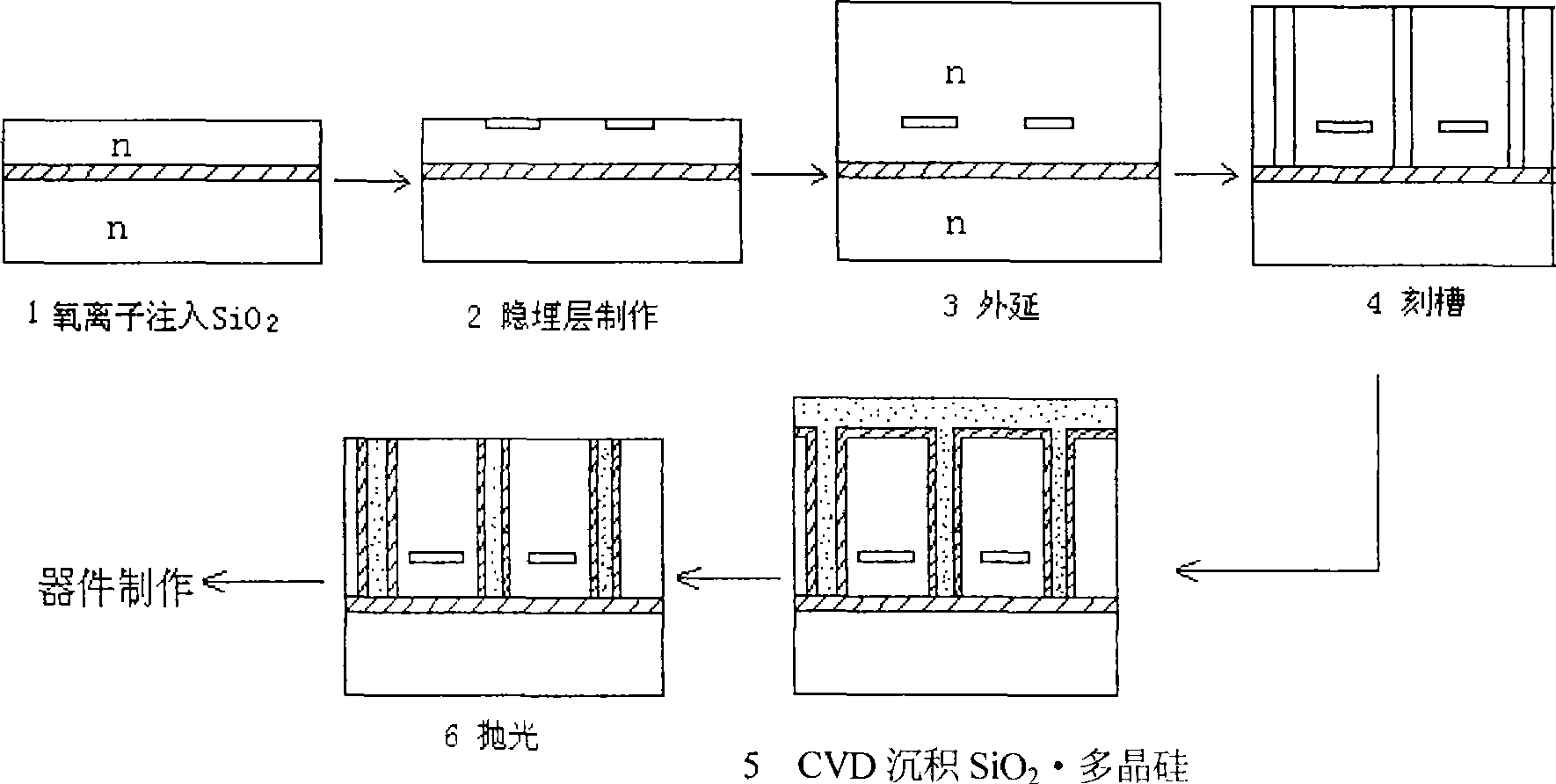

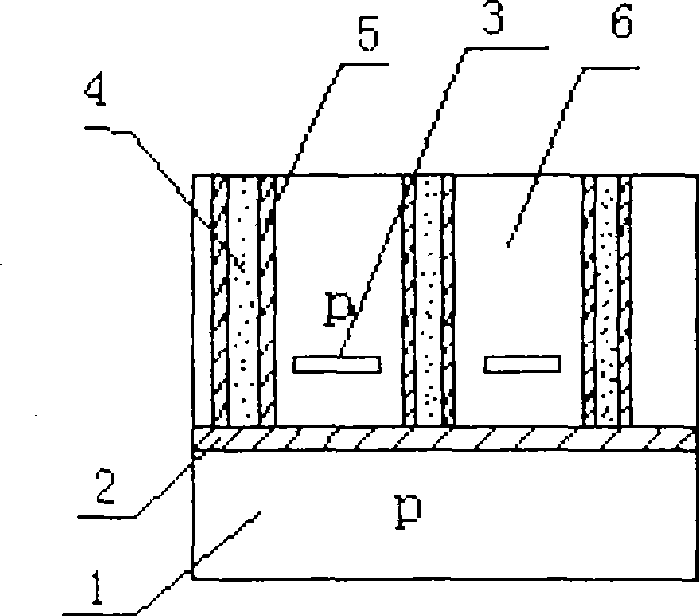

Dielectrically isolated integrated circuit extending wafer and preparation method thereof

InactiveCN101425522AImprove performanceImprove high temperature resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCrystal structureSilicon dioxide

The invention mainly relates to a dielectric isolation epitaxial wafer and a preparation method thereof. The N-shaped / P-shaped dielectric isolation integrated circuit epitaxial wafer comprises N-shaped / P-shaped monocrystalline silicon (1) with backing material. A sandwich oxide layer (2) is arranged on the monocrystalline silicon (1). The invention is mainly characterized in that the dielectric isolation epitaxial wafer further comprises an N-shaped / P-shaped silicon epitaxial layer (6); a buried layer (3) is arranged in the silicon epitaxial layer (6); the silicon epitaxial layer (6) is divided into mutually-insulating isolation blocks by silicon dioxide (5), polysilicon (4) and the sandwich oxide layer (2). The invention also discloses a preparation method of the N-shaped / P-shaped dielectric isolation integrated circuit epitaxial wafer. The preparation method comprises the following steps: preparing a silicon chip on an insulating body, preparing the buried layer with low resistance, extending outwardly, notching, growing the silicon dioxide and the polysilicon, and polishing. Because the high temperature time is shortened greatly during the preparation, the invention has the advantages of more complete crystal structure and more accurate process control, and can be used for manufacturing circuits with high performance and special requirements.

Owner:TIANSHUI HUATIAN MICROELECTRONICS

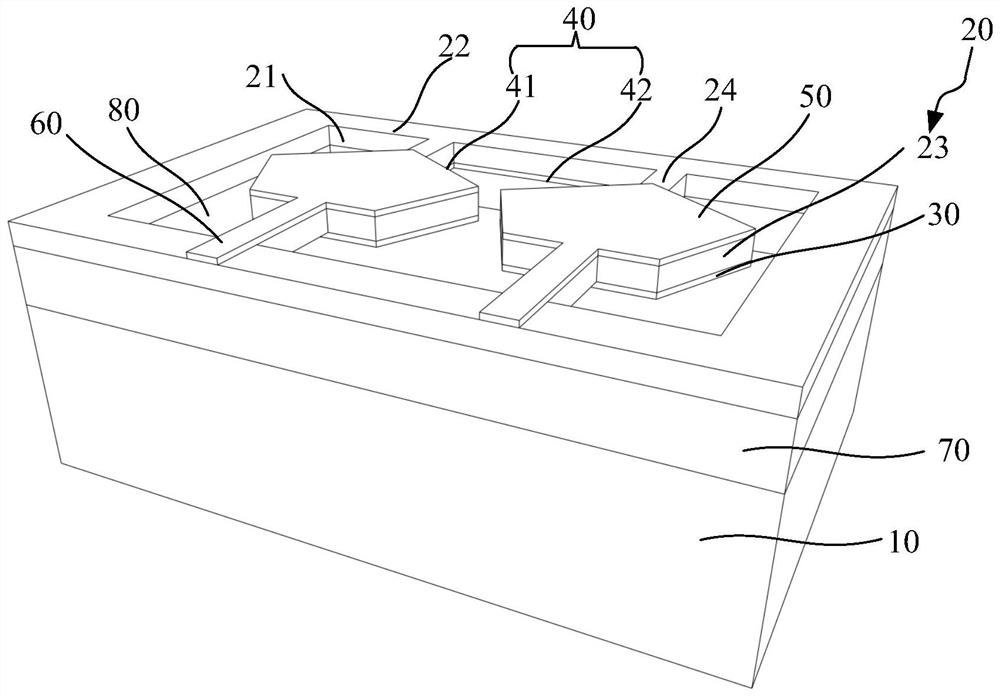

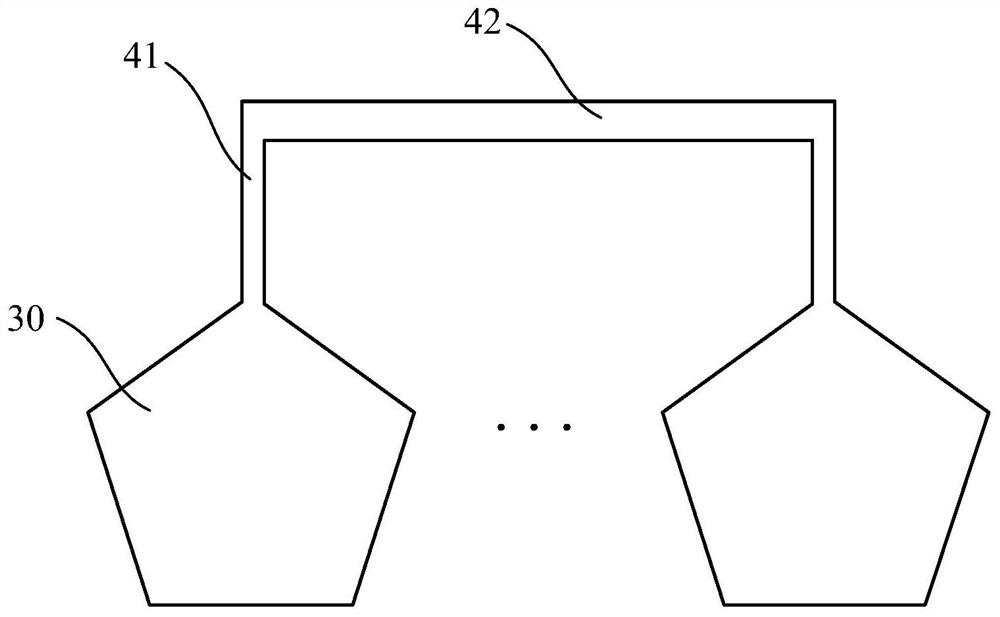

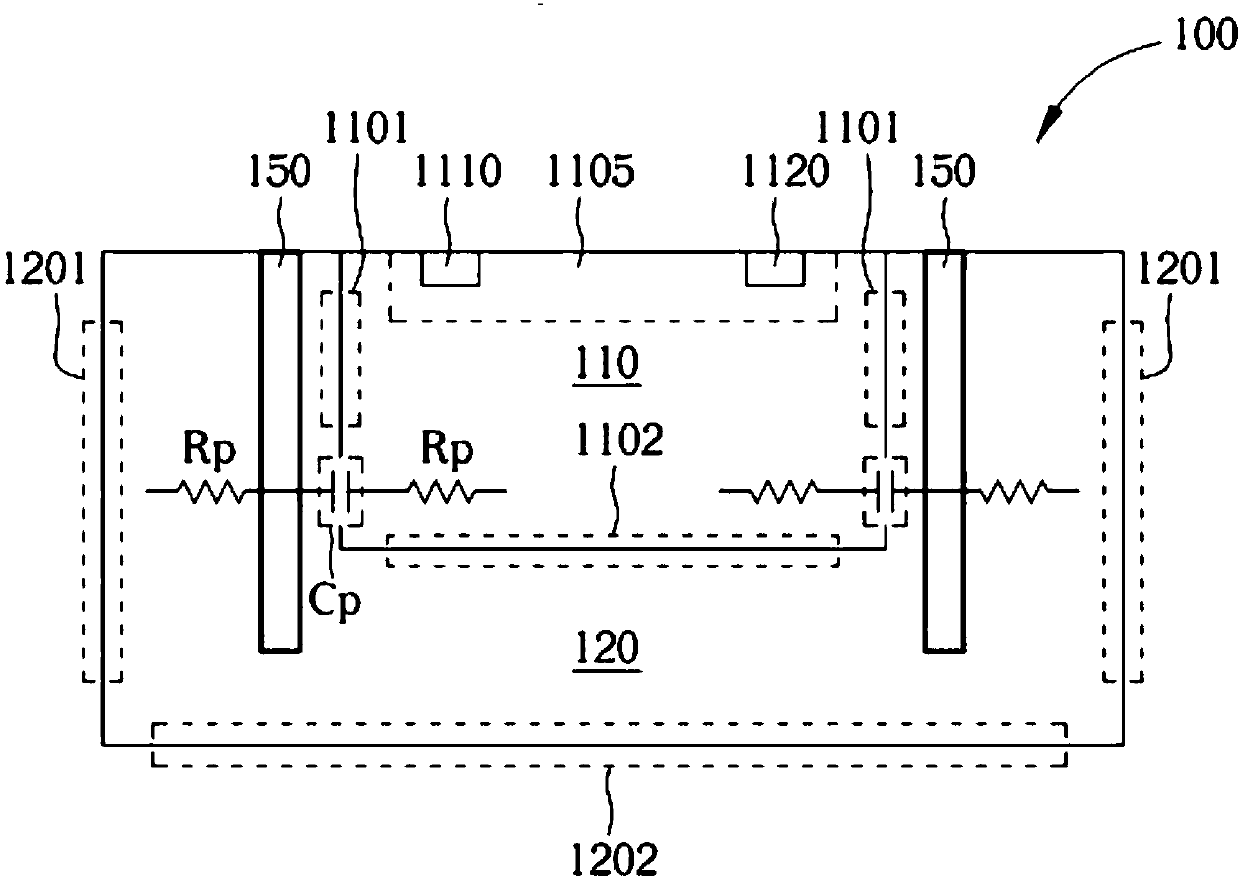

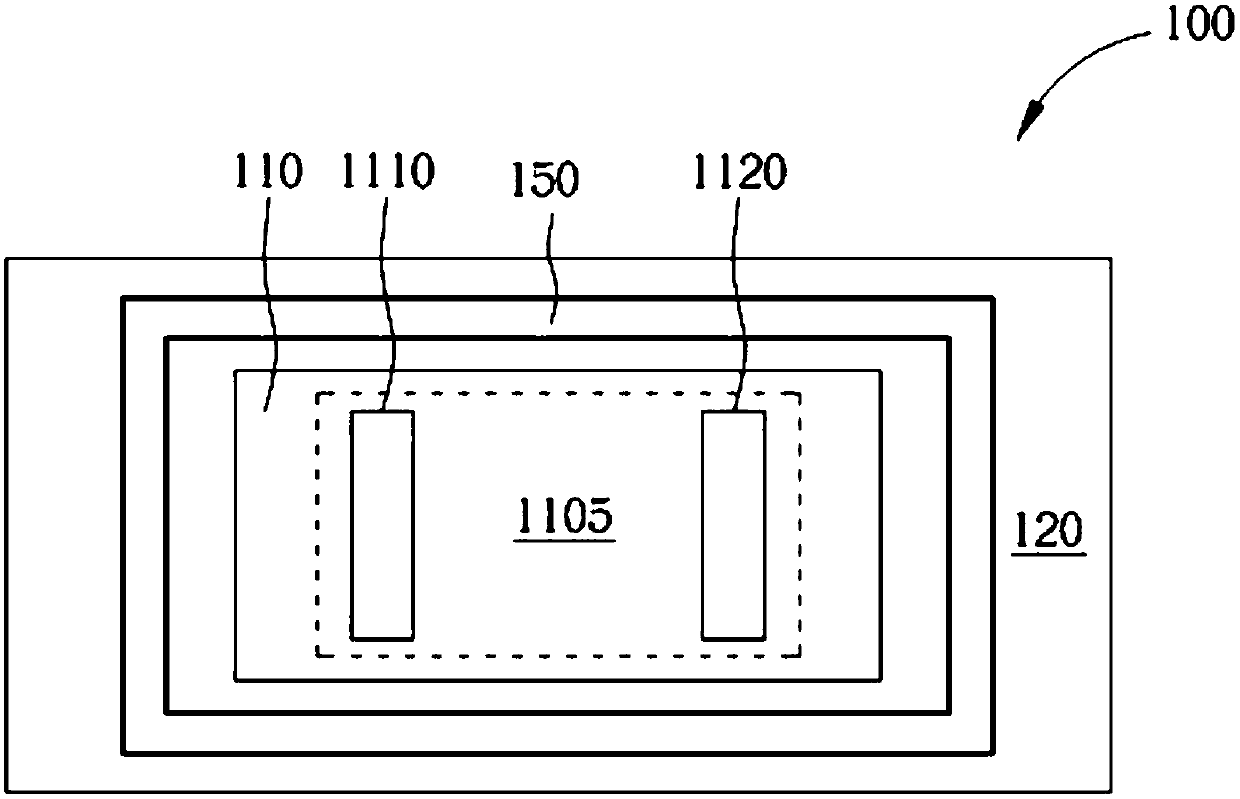

Acoustic resonator and preparation method thereof

The invention provides an acoustic resonator and a preparation method thereof. The acoustic resonator comprises a supporting substrate; a piezoelectric layer is formed on the upper surface of the supporting substrate, and the piezoelectric layer comprises a through groove, an edge supporting structure, a joint arm and N effective piezoelectric structures; N bottom electrodes are formed between the N effective piezoelectric structures and the supporting substrate and are communicated with one another through bottom electrode communication structures; N top electrodes are formed on the upper surfaces of the N effective piezoelectric structures and are led out one by one through the N top electrode leading-out structures. N is a positive integer greater than or equal to 2. According to the acoustic resonator and the preparation method thereof provided by the invention, the problem that clutters are generated by excitation of transverse and longitudinal electric fields and the problem of frequency adjustment of the acoustic resonator in the prior art are solved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

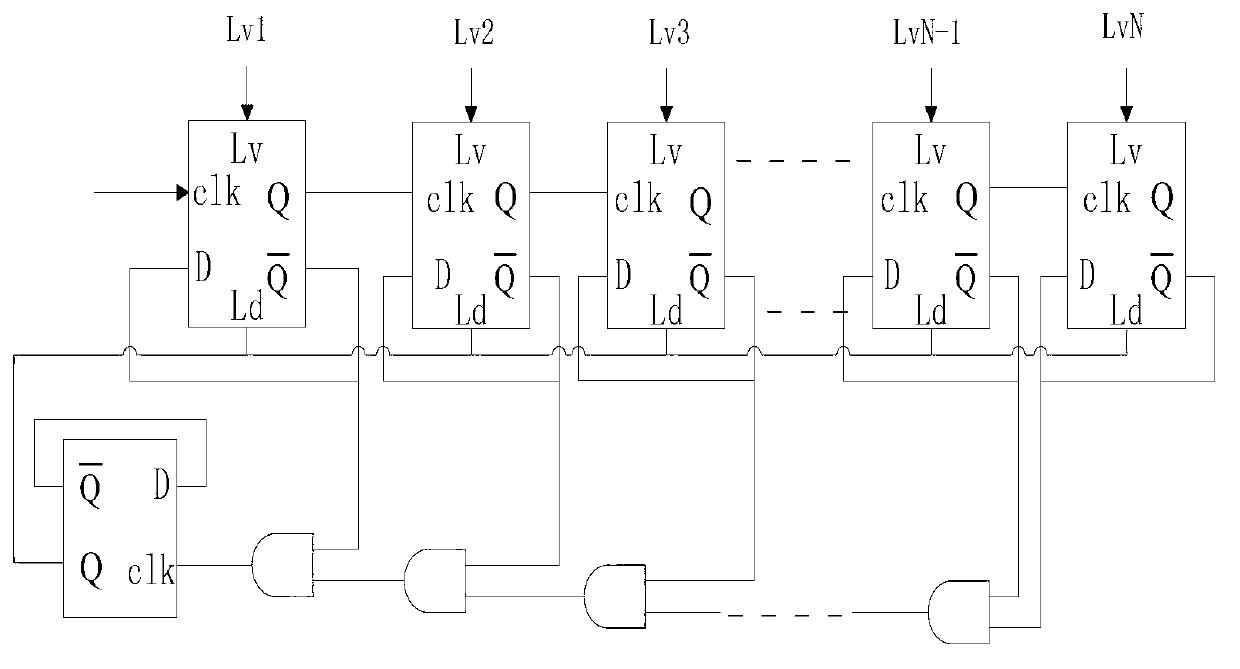

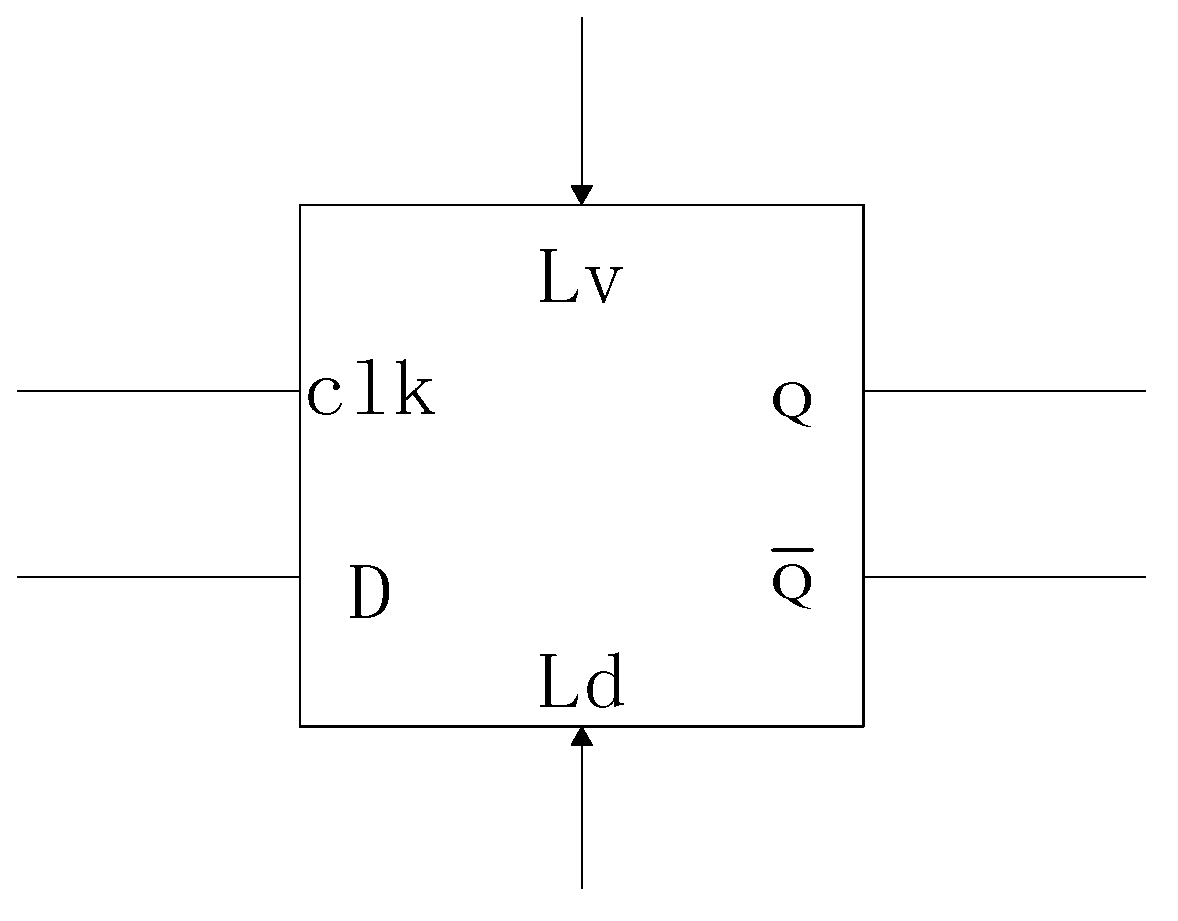

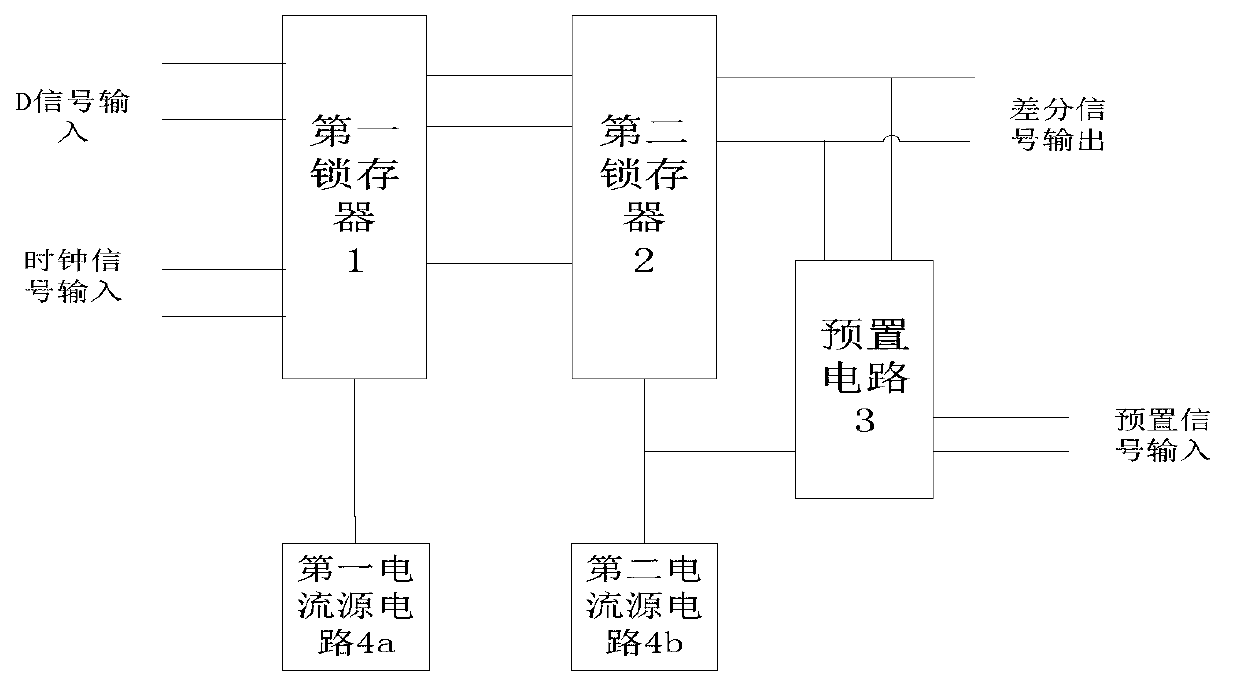

High speed D trigger based on transistor

InactiveCN103138715AHigh speedEasy to implementElectric pulse generator circuitsPower flowPhase noise

The invention discloses a high speed D trigger based on a transistor, and mainly solves the problems that an existing D trigger is high in phase noise and low in working frequency. The high speed D trigger based on the transistor mainly comprises a first latch (1), a second latch (2), a preset circuit (3), a first current source circuit (4a) and a second current source circuit (4b). The preset circuit (3) composed of a difference channel is connected with an output end of the second latch (2) and a current input end of the second latch (2). The preset circuit (3) is controlled by external signals to achieve a preset function. The first current source circuit (4a) is connected with a current input end of the first latch (1), and provides stable current for the first latch (1). The second current source circuit (4b) is connected with the current input end of the second latch (2), and provides stable current for the second latch (2). The high speed D trigger based on the transistor has the advantages of being simple in circuit, low in phase noise, high in working frequency, and the like. Accordingly, the high speed D trigger based on the transistor can be applied to a high speed program divider.

Owner:XIDIAN UNIV

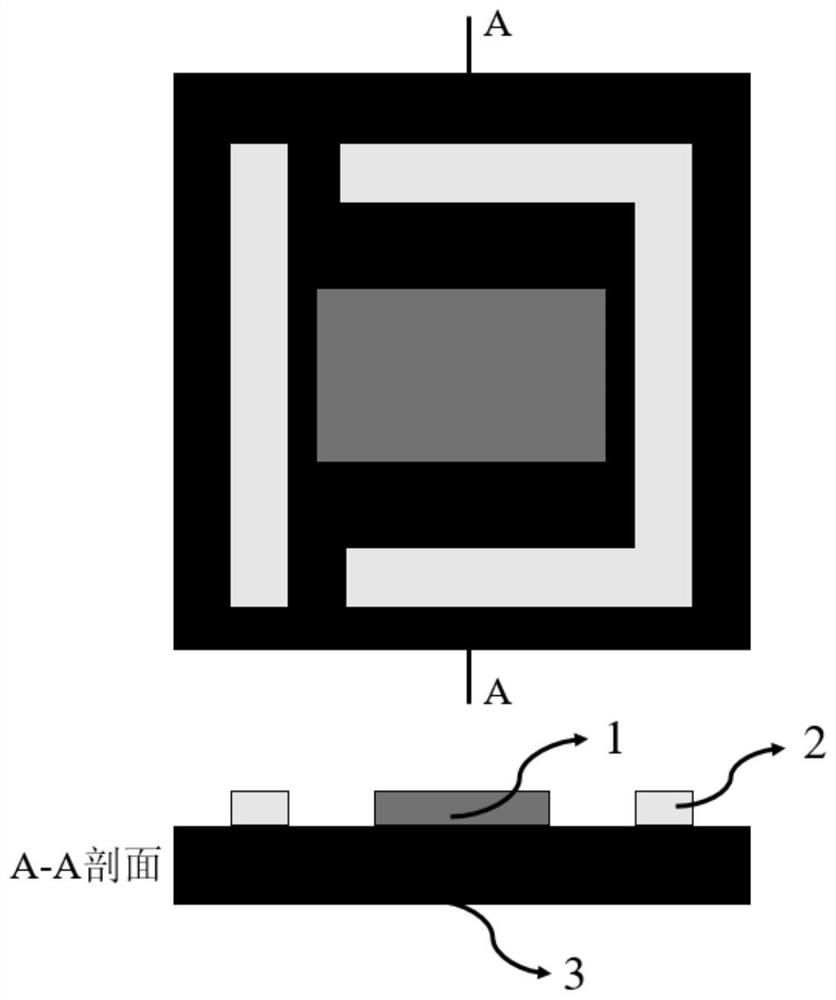

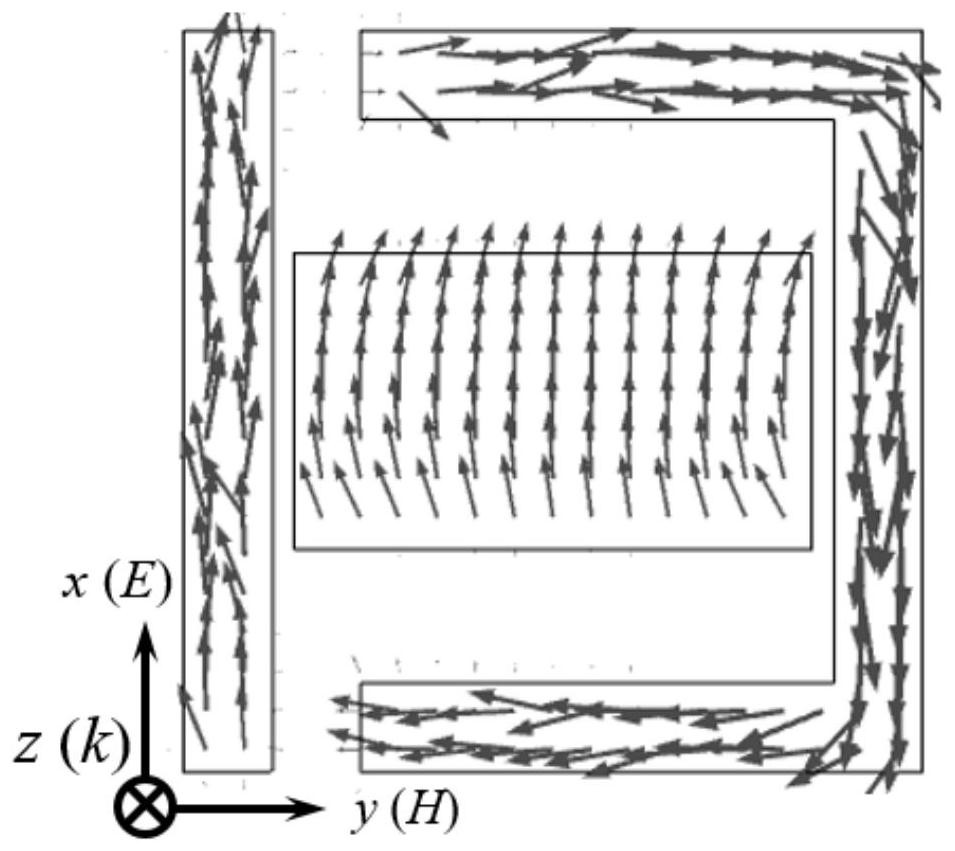

Photoelectric detector based on asymmetric metamaterial structure

PendingCN114512556AAvoid parasitic effectsAdjust the response wavelengthSemiconductor devicesEngineeringMechanical engineering

The invention discloses a photoelectric detector based on an asymmetric metamaterial structure. The photoelectric detector based on the asymmetric metamaterial structure can be composed of a metamaterial sensitive unit, and can also be composed of a plurality of metamaterial sensitive units in an array form. The metamaterial sensitive unit is composed of an asymmetric electromagnetic resonance structure and a conversion structure. During working, electromagnetic waves and the asymmetric electromagnetic resonance structure are coupled to generate a local high-intensity magnetic field, the conversion structure is arranged in the local high-intensity magnetic field, free carriers of the conversion structure deflect under the action of generated Lorentz force and have directional moving components, and then the free carriers are accumulated at the physical boundary of the conversion structure to form a direct-current potential difference; therefore, the conversion from the high-frequency electromagnetic wave (light) signal to the direct current is realized. The photoelectric detector provided by the invention has the outstanding advantages of simple structure, high detection speed, large response wave band range, low processing difficulty, low manufacturing cost and the like.

Owner:北京索通新动能科技有限公司 +1

Cylindrical sample preparation device for measuring moisture content of green sand through capacitance method and method for measuring moisture content of green sand

InactiveCN102998160BSame sizeIncrease the areaPreparing sample for investigationMaterial capacitanceCapacitanceElectrical resistance and conductance

The invention discloses an application method for measuring the moisture content of the green sand through a capacitance method, belongs to the field of moisture measurement of cast green sand, and solves the problem that the measuring accuracy of the moisture content of the green sand through capacitance methods is low in the past. The method includes producing a sand sample with the height equal to a main sample drum through the sample preparation device; connecting two exciting electrode shielded wires with a parallel resistance model circuit respectively, exerting alternating current excitation voltage on two exciting electrodes through the two exciting electrode shielded wires, turning off a switch K, serially connecting a sand sample equivalent resistor Rx with a capacitor Cx, and turning on the switch K, parallelly connecting the sand sample equivalent resistor, the capacitor Cx and a first resistor R0; and measuring the voltage drop uo1 and uo2 of a second resistor R under the two states to obtain the Cx, and obtaining the moisture content of the green sand through the existing relation between capacitor Cx and the moisture content.

Owner:HARBIN UNIV OF SCI & TECH

Micro-mechanism testing probe card based on electroplating technique and manufacturing method thereof

ActiveCN100581984CIncreased needle tip displacementIncrease displacementElectronic circuit testingDecorative surface effectsProbe cardMicro mechanism

The invention relates to a micro mechanical testing probe card based on electroplating process and a manufacturing method thereof, and is characterized in that, cantilevers and probe tips are manufactured and formed on a silicon wafer with electroplated metal nickel; the probe tips are manufactured on an (111) inclined surface of the silicon wafer, and each probe tip is connected with a ceramic substrate with one or two probe cantilevers; the probe cantilevers and the probe tips adopt an isostress beam structure; probes on an flip chip substrate are intensively arranged in two directions. The manufacturing is characterized in that: firstly, the upper surface of the (100) silicon wafer is taken as the electroplated working face, and the probe cantilevers of a low stress nickel layer is formed by electroplating; and then a deep groove (111) inclined surface produced by anisotropic etching is taken as the working face, and the probe tips of the low stress nickel layer is formed by electroplating, and then the probes are connected with a package substrate by a flip chip process, and finally the probe structure is released through a method of removing the corrosion of the silicon wafer.

Owner:深圳市道格特科技有限公司

Semiconductor structure

ActiveCN107644898AImprove performanceIncrease the equivalent parasitic resistanceSemiconductor devicesElectrical conductorSemiconductor structure

The invention discloses a semiconductor structure. The structure comprises a first well area, a semiconductor component, a second well area and a first separating layer, wherein the semiconductor component forms on or is contacted with the first well area; the first well area forms on the second well area; and the first separating layer is used for reducing a parasitic effect of the first well area and the second well area. A depth of a bottom of the first separating layer at least reaches a depth of a bottom of the first well area. The first separating layer is an annular structure which is formed along a lateral boundary of the first well area. A mixed type of the second well area is different from a mixed type of the first well area.

Owner:RICHWAVE TECH CORP

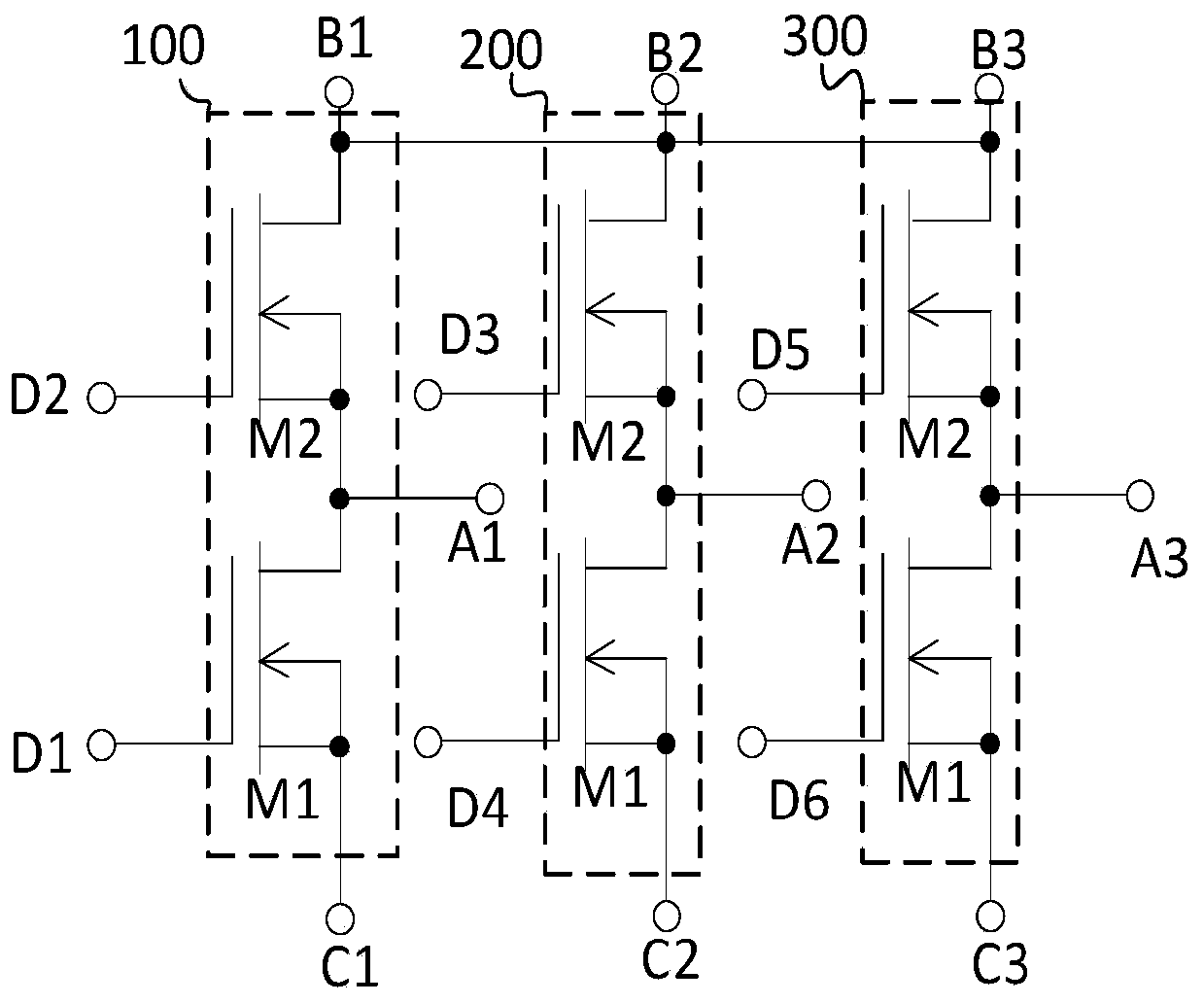

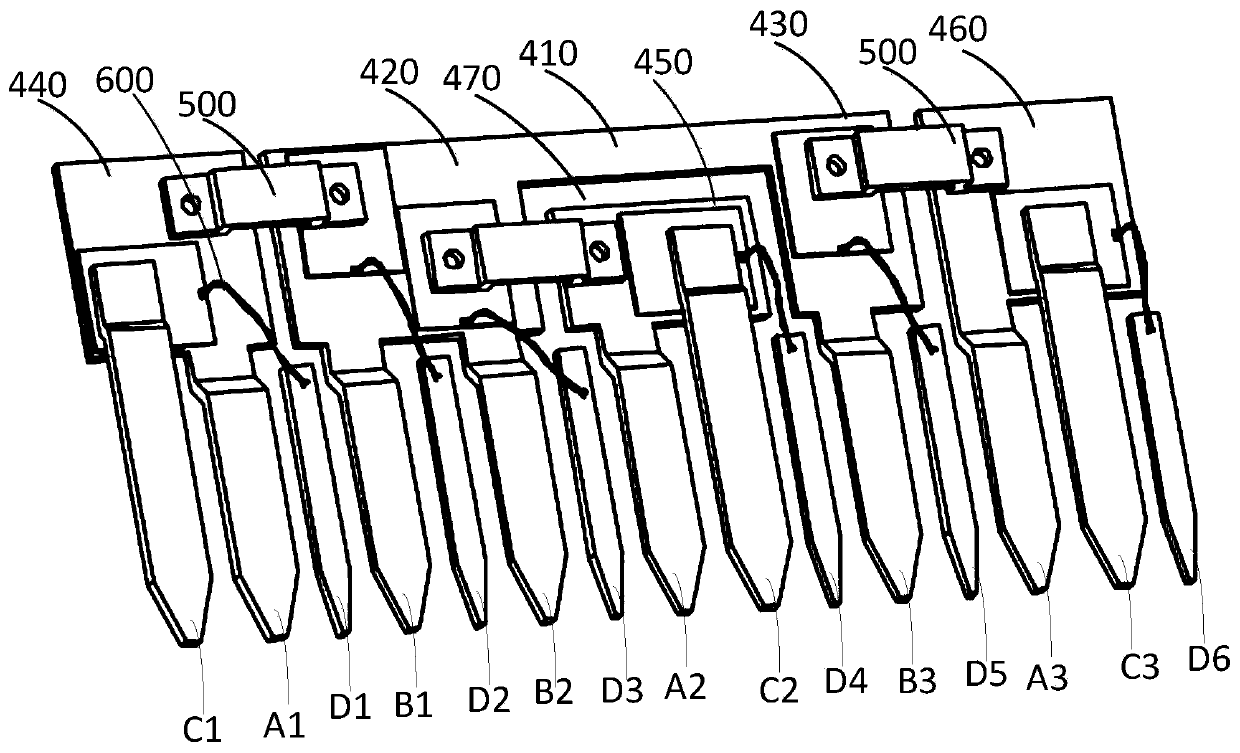

Three-phase full-bridge module and manufacturing method thereof

PendingCN110752208AReduce parasitic resistanceFirmly connectedSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceMetal framework

The invention relates to a power device electronic module, and specifically relates to a three-phase full-bridge module and a manufacturing method thereof. The three-phase full-bridge module comprisesa first-phase bridge arm, a second-phase bridge arm, a third-phase bridge arm and a metal frame, wherein the first-phase bridge arm, the second phase-bridge arm and the third-phase bridge arm respectively comprise a first power device M1 and a second power device M2; in each phase bridge arm, the drain electrode of the first power device M1 is connected with the source electrode of the second power device M2 to form a connecting pin; the connecting pins of the first-phase bridge arm, the second-phase bridge arm and the third-phase bridge arm are respectively a connecting pin A1, a connectingpin A2 and a connecting pin A3; and the metal frame comprises a metal arm, and the metal arm connects the drain electrode of the second power device M2 of the first-phase bridge arm, the drain electrode of the second power device M2 of the second-phase bridge arm and the drain electrode of the second power device M2 of the third-phase bridge arm. The parasitic resistance and the parasitic capacitance can be suppressed according to the invention.

Owner:无锡电基集成科技有限公司

A programmable non volatile memory unit, array and its making method

ActiveCN100589248CReduce areaImprove integration densitySemiconductor/solid-state device detailsSolid-state devicesBit lineEngineering

The invention discloses a programmable nonvolatile storage unit and an array, and the manufacturing method thereof. The device comprises a metal layer, a contact hole, a barrier layer, a plurality ofpolysilicons in the passive area, a plurality of polysilicons in the active area, and a substrate in the active area. A plurality of transistors are formed by the polysilicons in the active area and asubstrate in the active area; a plurality of source lines are formed by the polysilicons in the passive area; A plurality of word lines are formed by the polysilicons in the passive area. A pluralityof bit lines are formed by the metal lines in the metal layer. A capacitor is formed by connecting the metal layer, the connecting hole, the barrier layer, and the polisilicons in the passive area one by one. The storage unit is formed by means of corresponding series connection between the transistors and the capacitor and arrayed among the word-lines, the bit-lines and the source lines, which correspond to the storage unit. The invention improves the storage stability, decreases the area of the storage, and popularizes the application of VLSI.

Owner:GIGADEVICE SEMICON (BEIJING) INC