Patents

Literature

95results about How to "Achieve self-alignment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for manufacturing semiconductor device and method for manufacturing SiGe HBT (Heterojunction Bipolar Transistor)

ActiveCN102184898ASimplify the production processReduce manufacturing costSemiconductor/solid-state device manufacturingOxide semiconductorCMOS

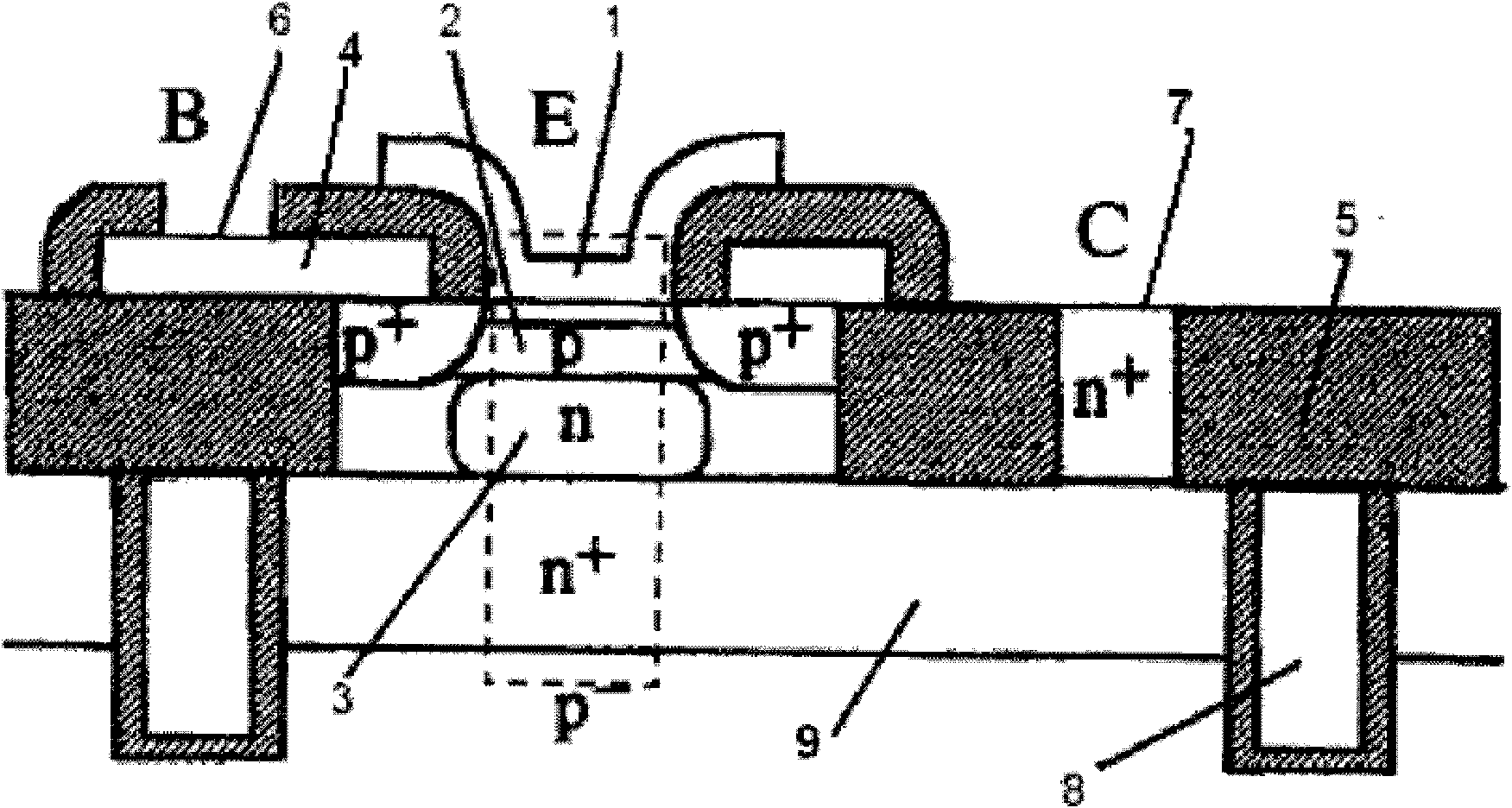

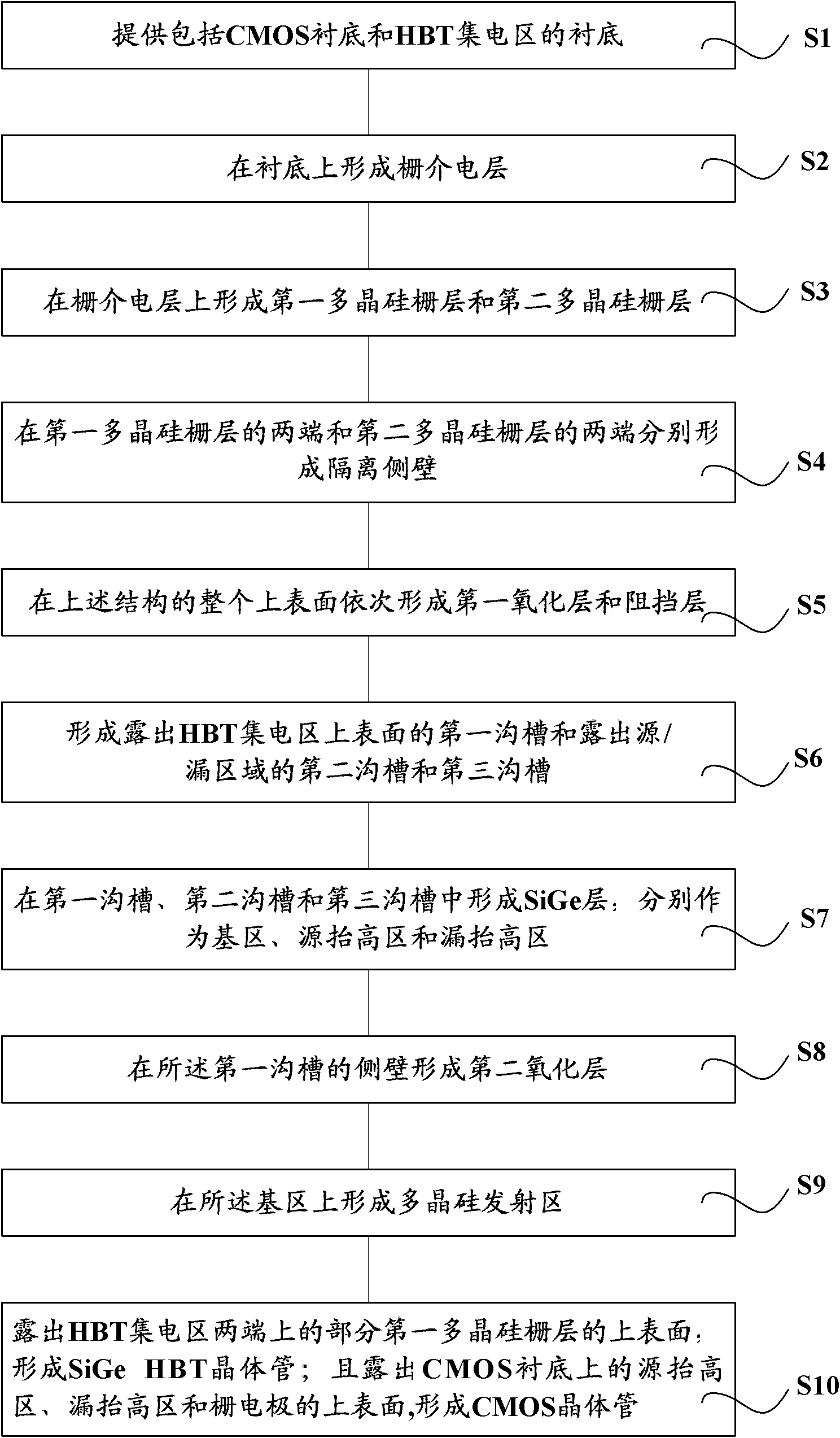

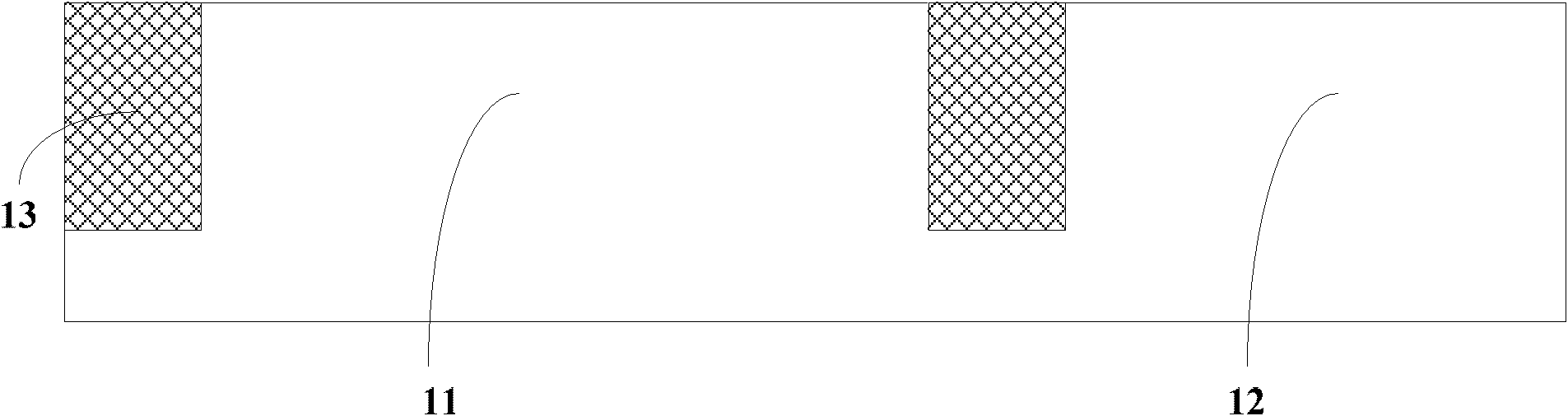

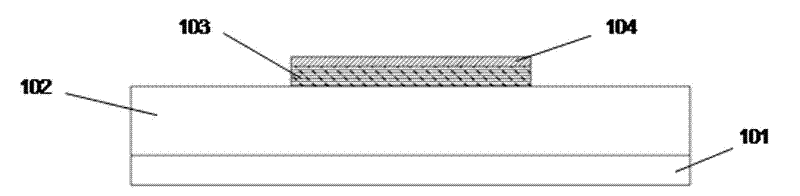

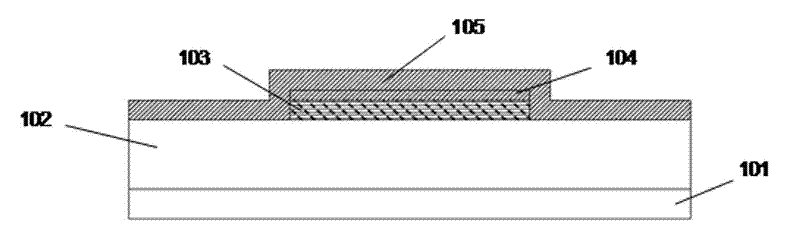

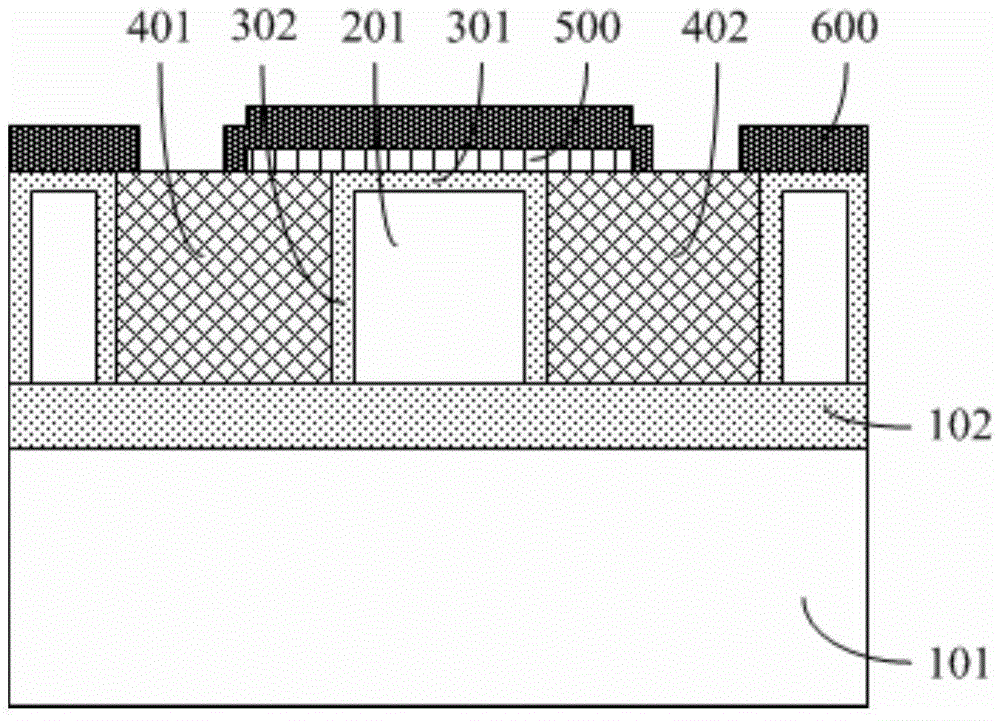

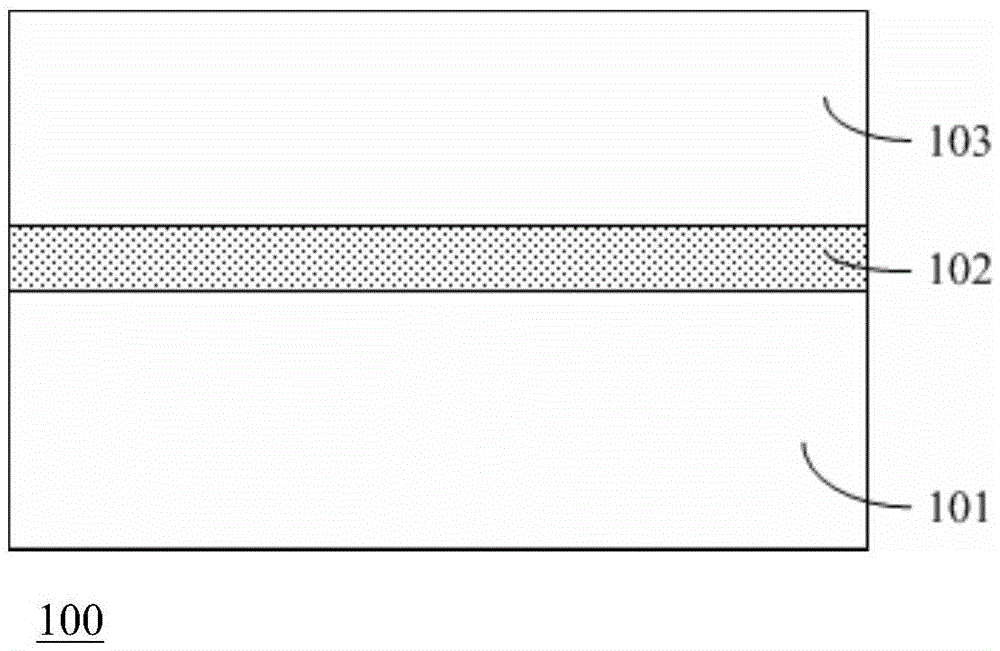

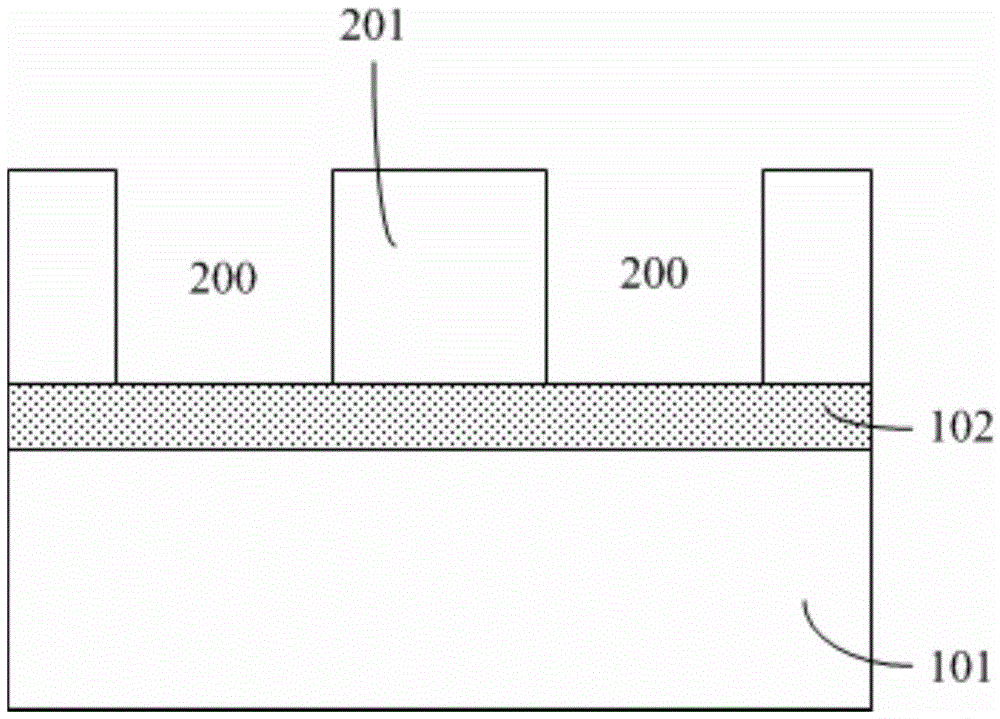

The invention relates to a method for manufacturing a semiconductor device and a method for manufacturing an SiGe HBT (Heterojunction Bipolar Transistor), wherein the method for manufacturing the SiGe HBT comprises the steps of: offering a substrate comprising an HBT collector region; sequentially forming a gate dielectric layer, a polysilicon gate layer, an oxide layer and a barrier layer on the HBT collector region; removing partial barrier layer as well as the oxide layer, the polysilicon gate layer and the gate dielectric layer under the partial barrier layer on the HBT collector region so as to form a groove where the upper surface of the HBT collector region is exposed; forming an SiGe layer in the groove to serve as a base region; forming a polysilicon emitter region on the base region; and removing the partial barrier layer and the oxide layer under the partial barrier layer on two ends of the HBT collector region till the upper surface of partial polysilicon gate layer on the two ends of the HBT collector region is exposed and preserving the barrier layer surrounding the polysilicon emitter region and the oxide layer under the barrier layer. In the invention, the manufacturing processes of the two kinds of transistors are compatible and the cost is saved; the source / drain region of a CMOS (Complementary Metal Oxide Semiconductors) transistor is raised; and therefore, the self alignment of the base region and the emitter region of the SiGe HBT is realized.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

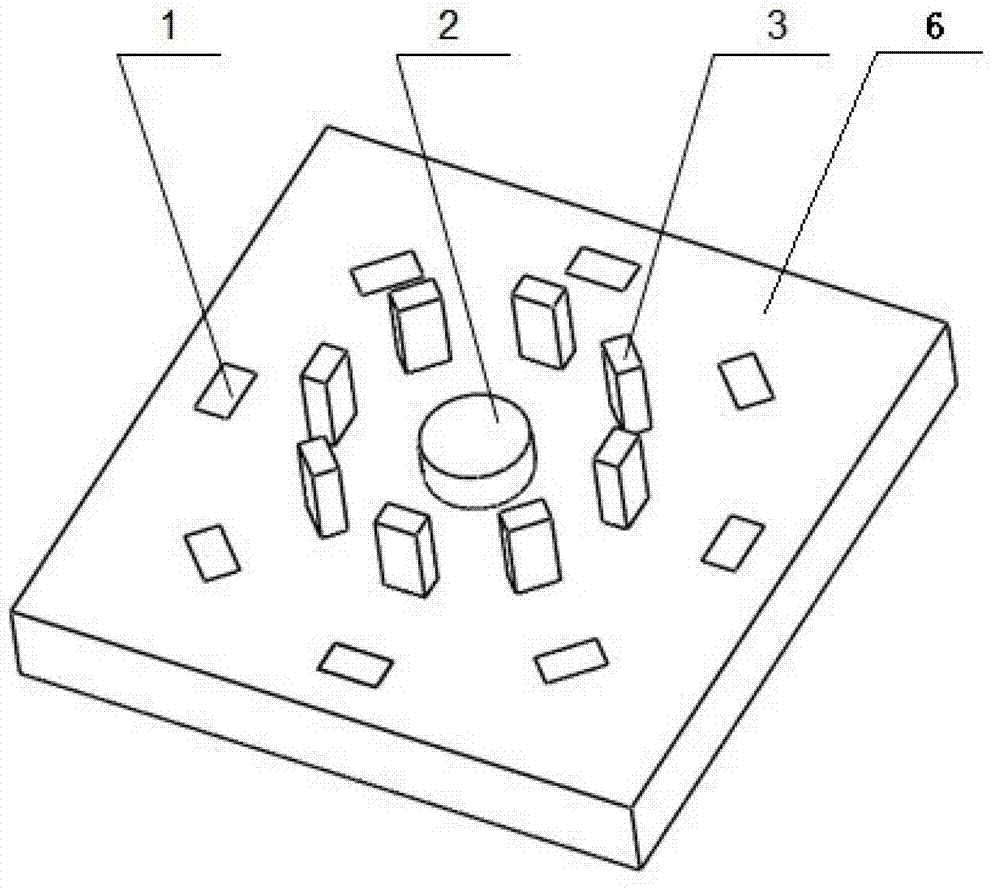

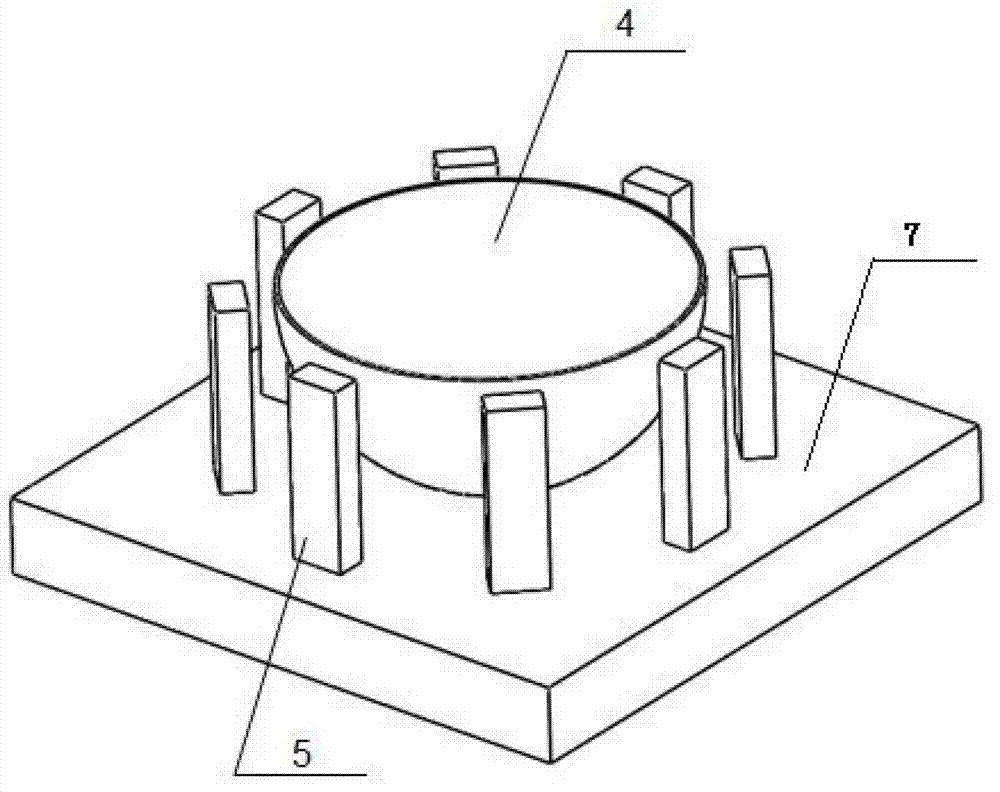

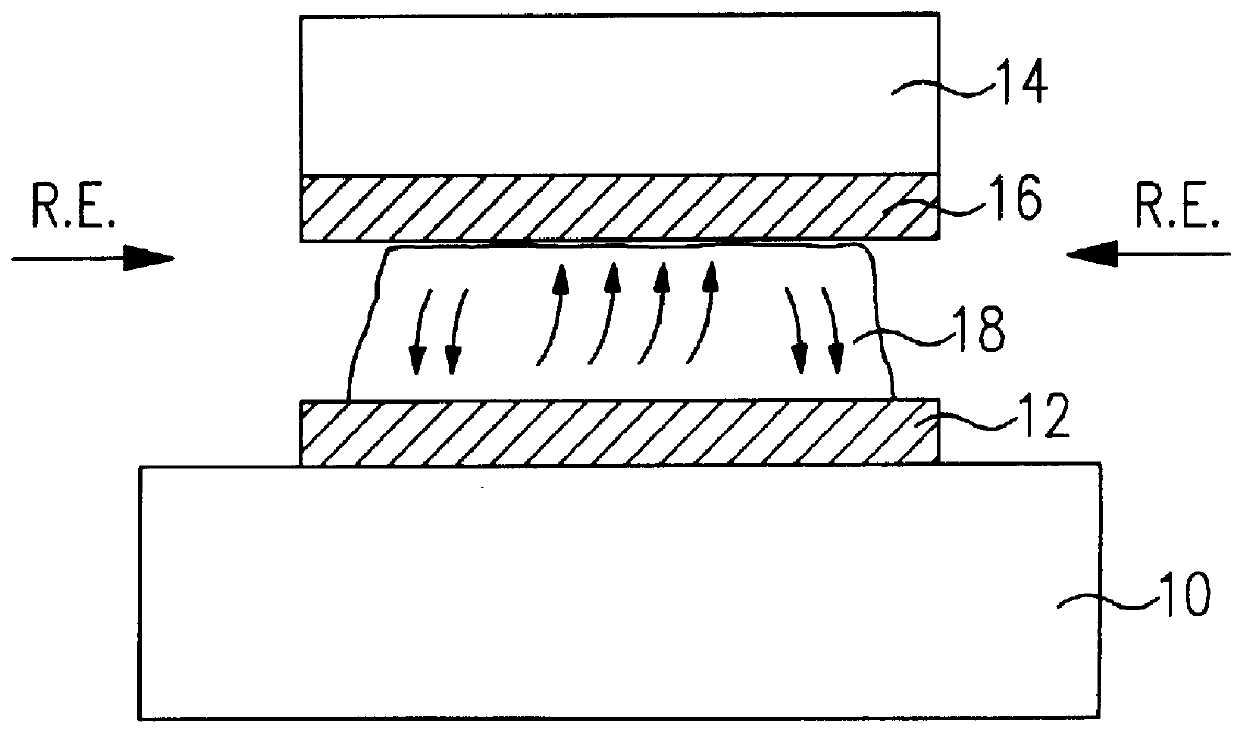

Double-wafer integrated silicon-based super-thin micro-hemispherical resonator gyroscope and preparation method thereof

InactiveCN103322994AAchieve electrical performanceAchieve mechanical propertiesDecorative surface effectsSolid-state devicesHemispherical resonator gyroscopeElectron

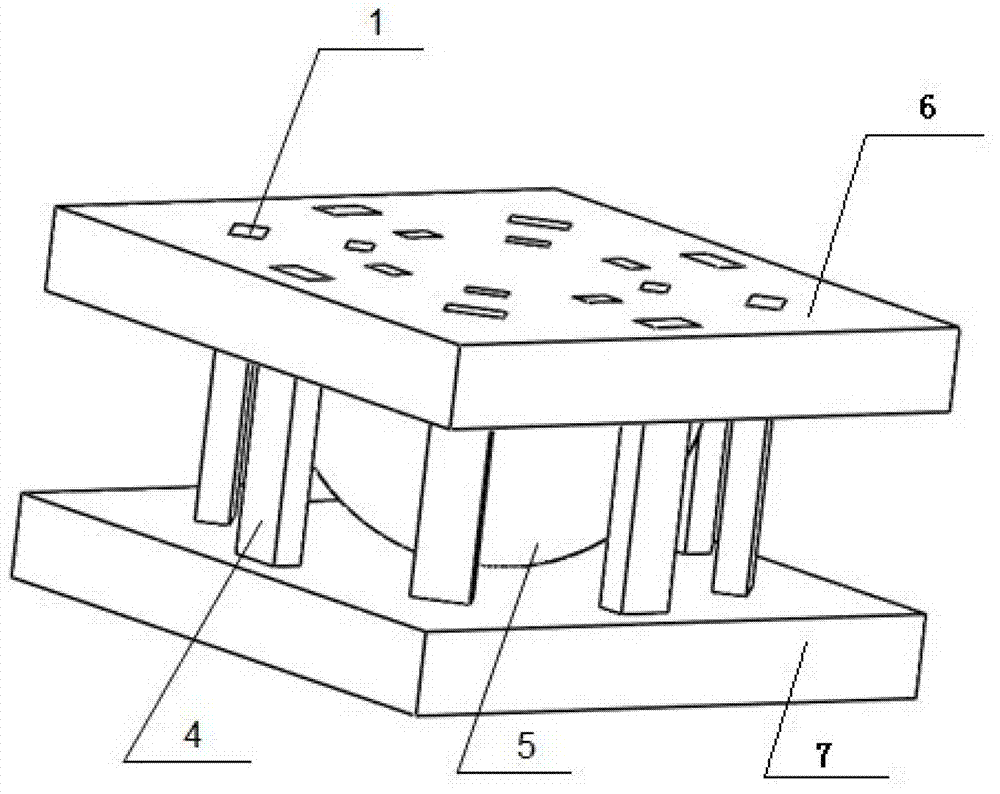

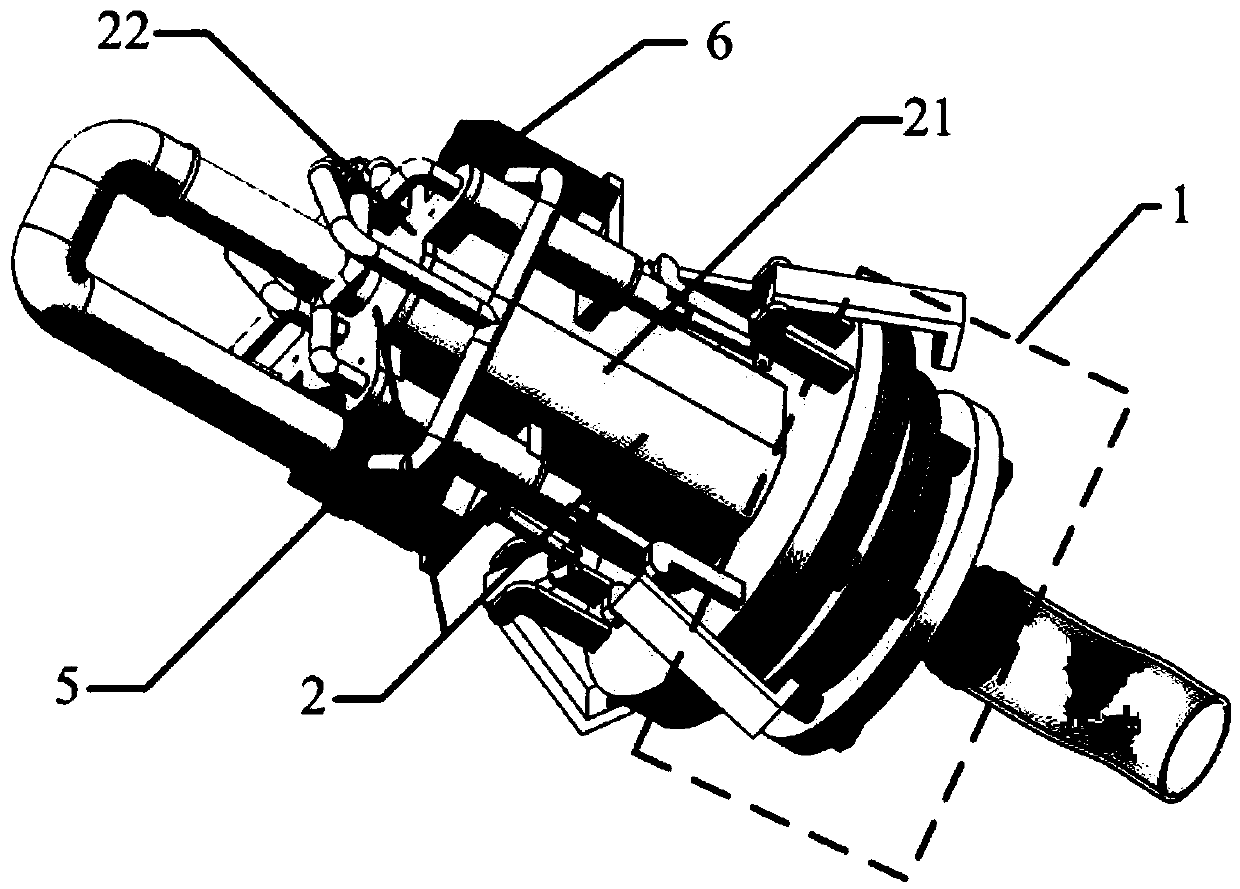

The invention discloses a double-wafer integrated-form silicon-based ultrathin micro-hemispherical resonator gyroscope. The double-wafer integrated-form silicon-based ultrathin micro-hemispherical resonator gyroscope comprises a first silicon wafer, a second silicon wafer, a micro-hemisphere casing, driving electrodes and detecting electrodes. The micro-hemispherical casing is arranged between the first silicon wafer and the second silicon wafer. The casing bottom of the micro-hemispherical casing is fixedly connected with the second silicon wafer, and the upper edge of the micro-hemispherical casing is in contacted with the lower surface of the first silicon wafer. The driving electrodes are arranged on the periphery of the micro-hemispherical casing and between the first silicon wafer and the second silicon wafer. One ends of the driving electrodes are fixedly connected with the second silicon wafer, and the other ends of the driving electrodes are movably connected with the first silicon wafer. One ends of the detecting electrodes are fixedly connected with the first silicon wafer, and the other ends of the detecting electrodes are movably connected with the inner wall of the micro-hemispherical casing. The double-wafer integrated-form silicon-based ultrathin micro-hemispherical resonator gyroscope has the advantages of small volume, light weight, low cost, high reliability, low power consumption, mass production and the like, is expected to be widely used in the fields of aerospace, automobile, medical treatment, photography, electronics consumption and the like, and has very broad application prospects.

Owner:SOUTHEAST UNIV

Method for electrochemical depositing solar cell metallic electrode

ActiveCN101257059AAvoid unevennessAvoid damagePhotovoltaic energy generationSemiconductor devicesElectrochemical responseMetallic electrode

Owner:WUXI SUNTECH POWER CO LTD

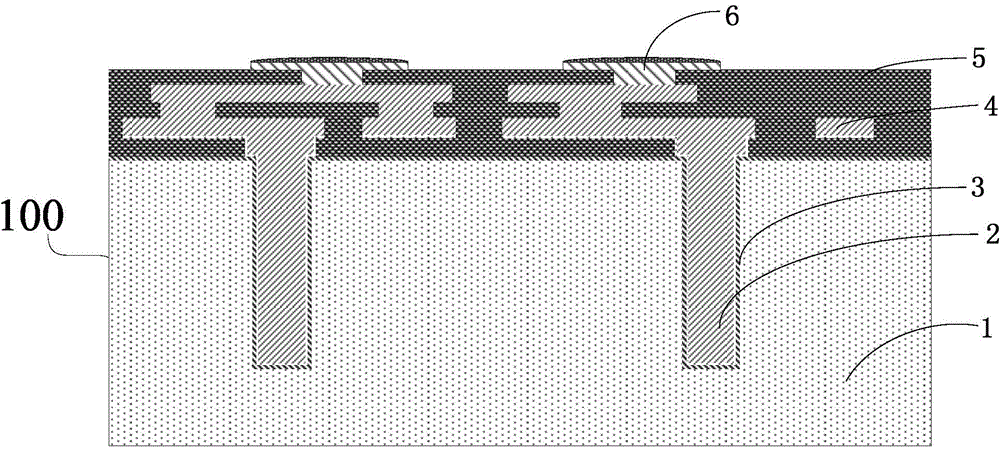

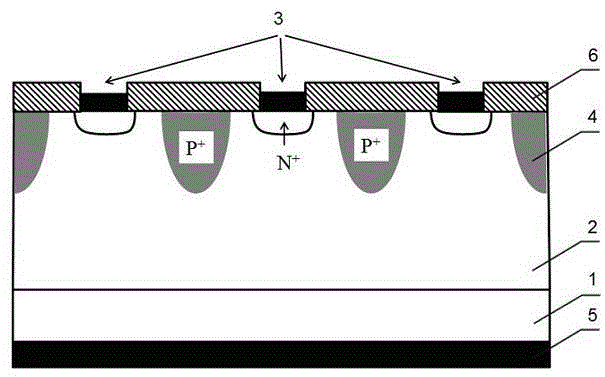

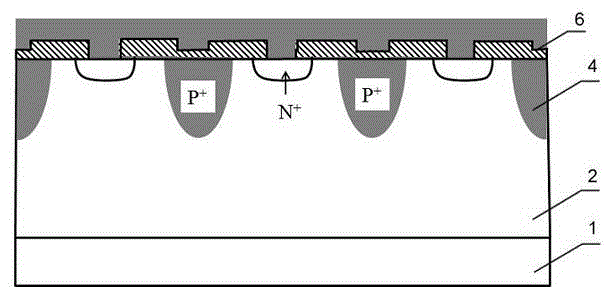

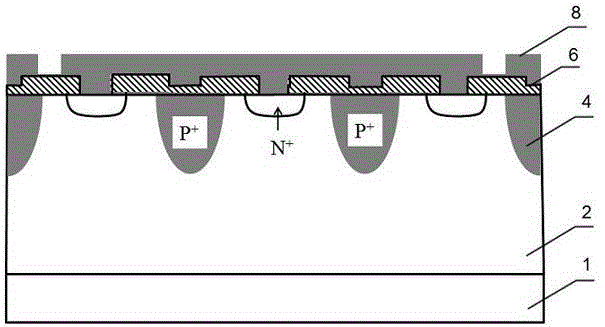

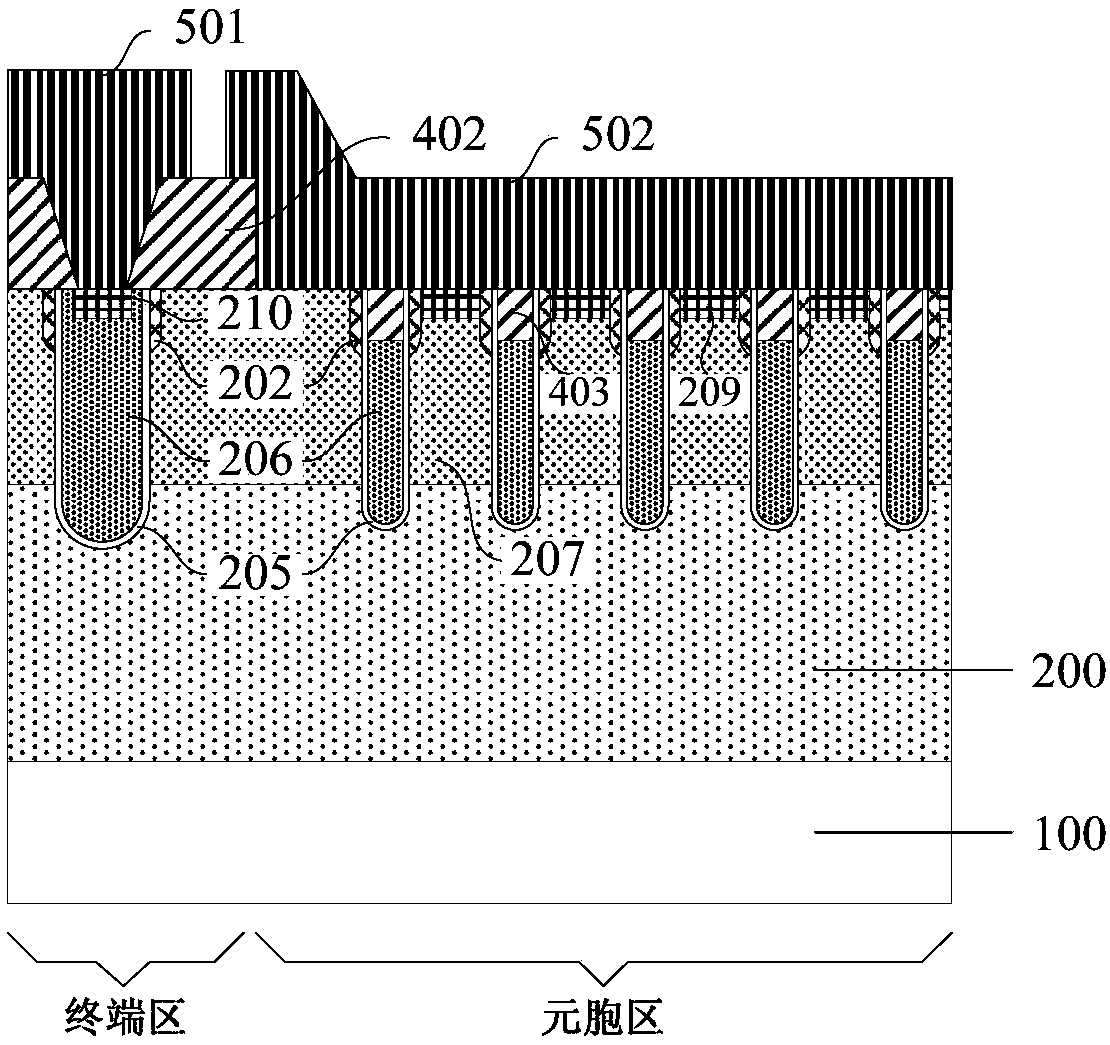

Trench MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) and manufacturing method thereof

ActiveCN102088035AReduced drain-source on-state resistanceReduce spacingSemiconductor/solid-state device detailsSolid-state devicesTrench mosfetEngineering

The invention provides a trench MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) and a manufacturing method thereof. The manufacturing method of the trench MOSFET comprises the following steps of: (1) preparing a heavily doped substrate; (2) forming a lightly doped epitaxial layer on the heavily doped substrate; (3) forming a lightly doped trap region on the lightly doped epitaxial layer; (4) forming a plurality of grid trenches penetrating through the lightly doped trap region and being in contact with the lightly doped epitaxial layer; (5) forming a heavily doped source region at the upper part of the lightly doped trap region and among the grid trenches; (6) forming a side wall on both sides of each grid trench; and (7) forming source electrode contact holes by self alignment of the side walls, wherein the top opening of each contact hole is greater than the bottom opening. The invention can further improve the density of unit cells of MOSFET, provides convenience for etching source electrode contact holes, and is favorable for metal filling of the source electrode contact holes.

Owner:WILL SEMICON (SHANGHAI) CO LTD

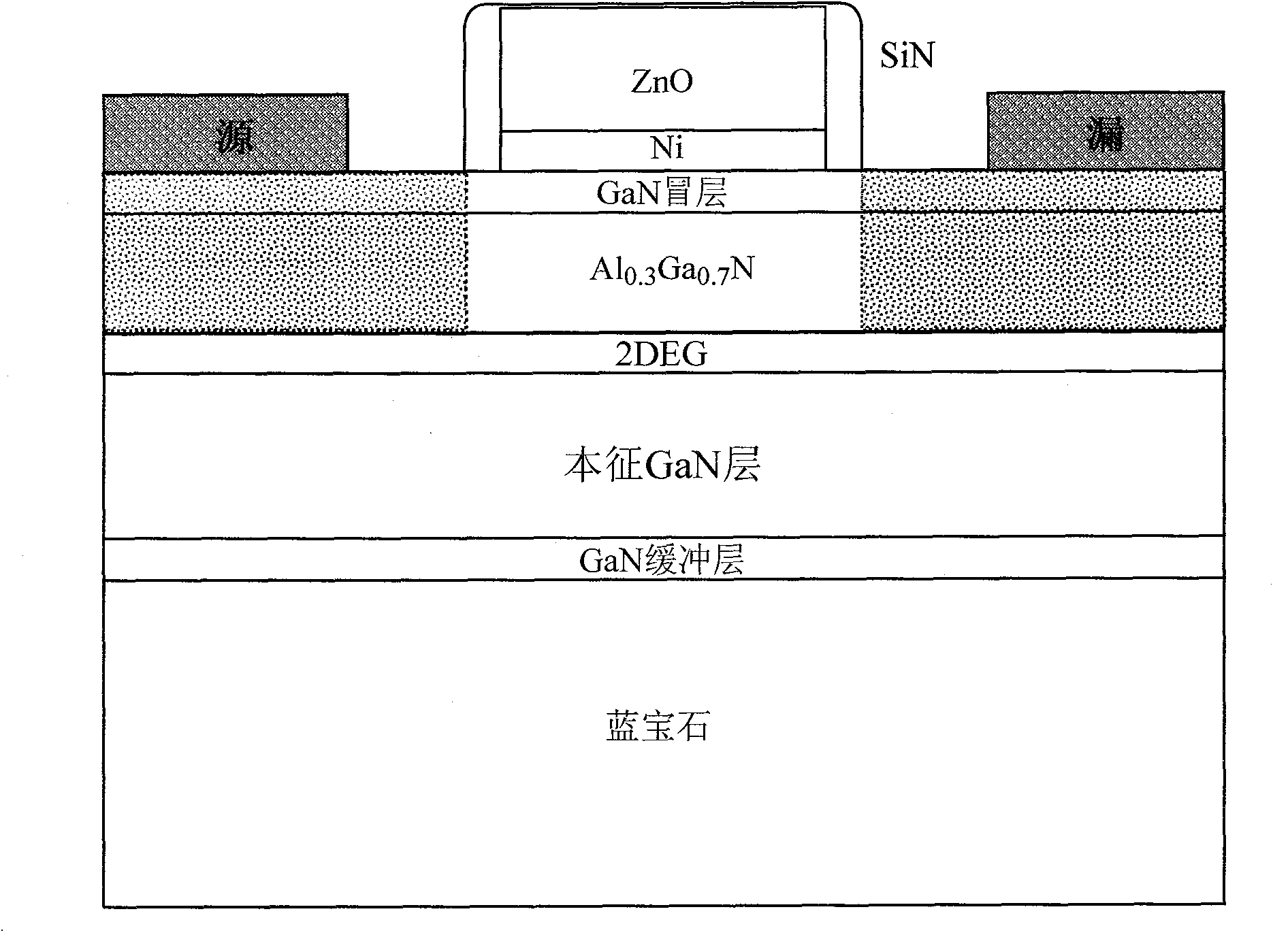

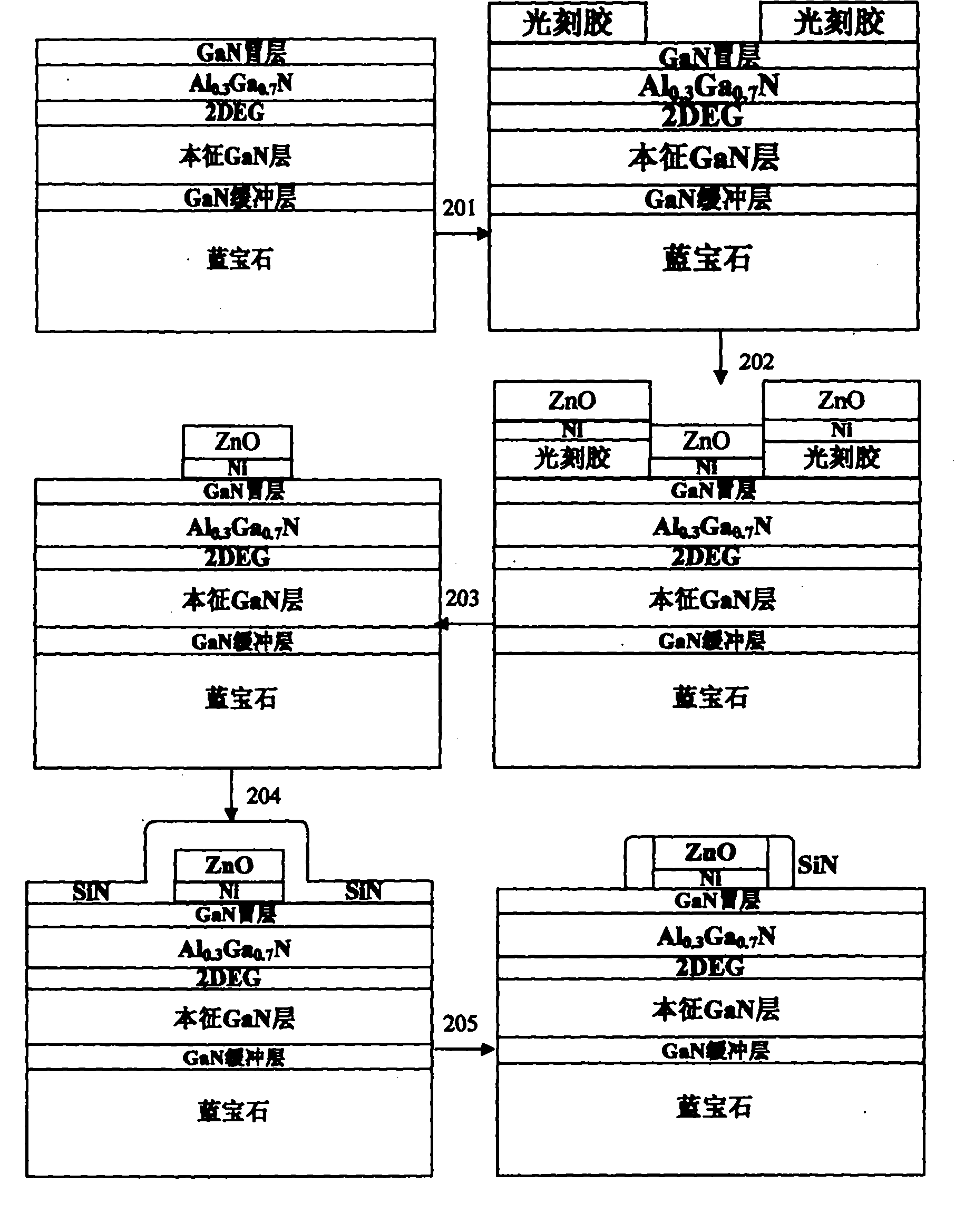

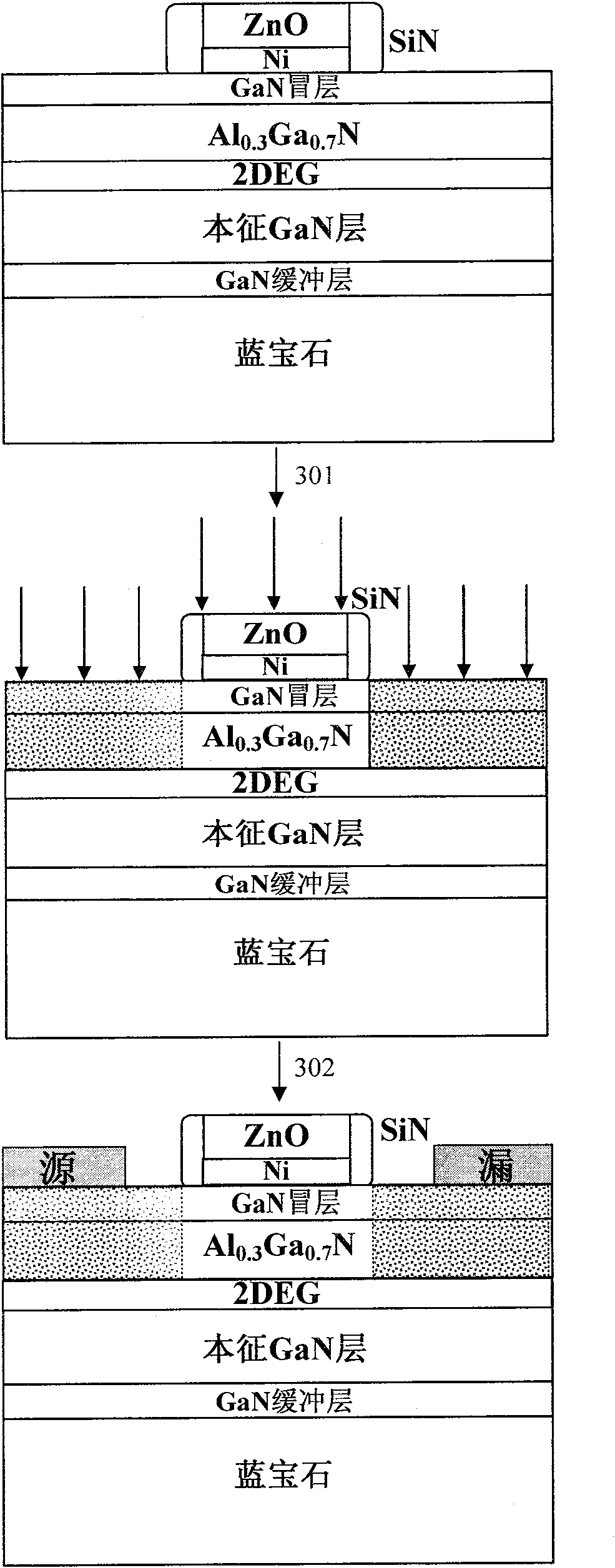

AlGaN/GaN high-electron-mobility transistor and manufacturing method thereof

ActiveCN101853880AImprove frequency characteristicsGood radiation resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEpitaxial materialEngineering

The invention discloses an AlGaN / GaN high-electron-mobility transistor and a manufacturing method thereof, which relate to the technical field of microelectronics and mainly solve the problems of low working frequency and poor anti-irradiation performance of the transistor. The transistor sequentially comprises a GaN buffer layer, an intrinsic GaN layer, an Al0.3Ga0.7N layer, a GaN capping layer, a source electrode, a drain electrode and a grid electrode according to a growth sequence, wherein transparent ZnO is adopted by the grid electrode, an Ni metal bonding layer is evaporated below the ZnO grid electrode, and SiN protection layers are arranged at both sides. Al2O3 is doped in the ZnO grid electrode, and the length of the ZnO grid electrode is equal to the distance between the source electrode and the drain electrode. The manufacturing process of the transistor sequentially comprises the following steps of: firstly, growing an epitaxial material; then manufacturing the ZnO grid electrode; and finally, manufacturing the source electrode and the drain electrode at both sides of the ZnO grid electrode by utilizing a self-aligning method. The AlGaN / GaN high-electron-mobility transistor has the advantages of high frequency characteristic and good anti-irradiation characteristic and can be used as an electronic component in high-frequency and high-speed circuits.

Owner:云南凝慧电子科技有限公司

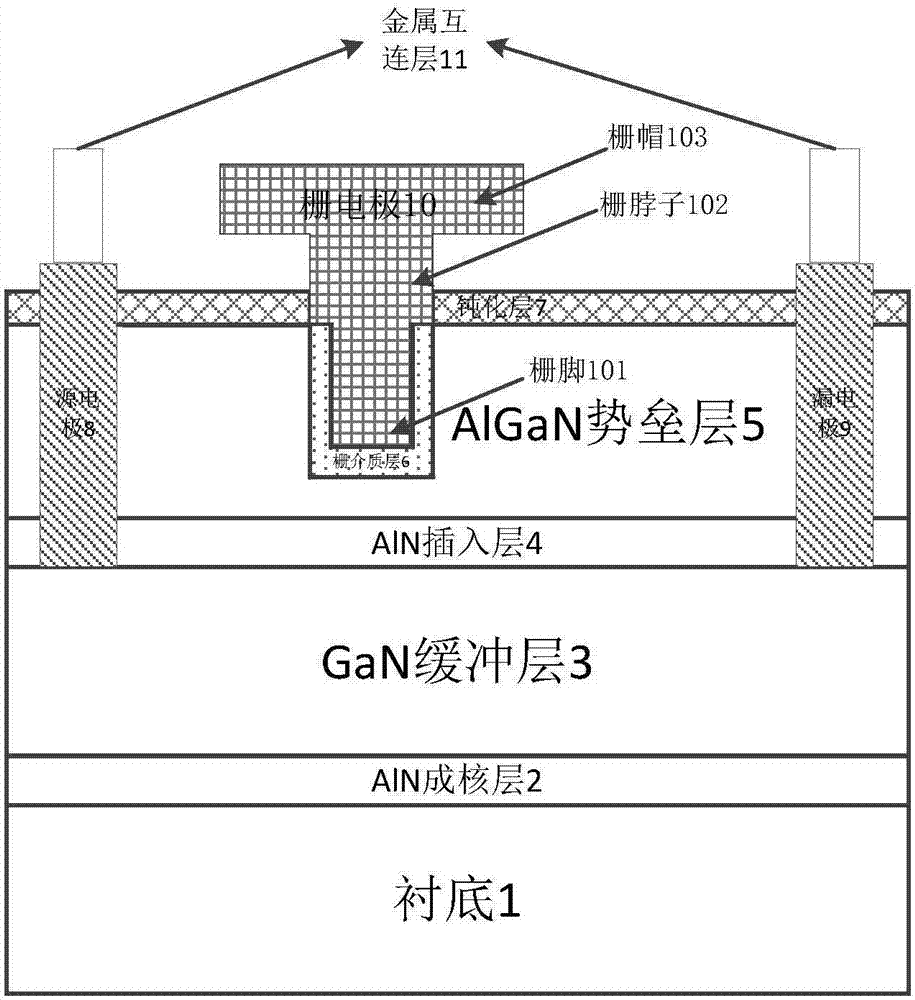

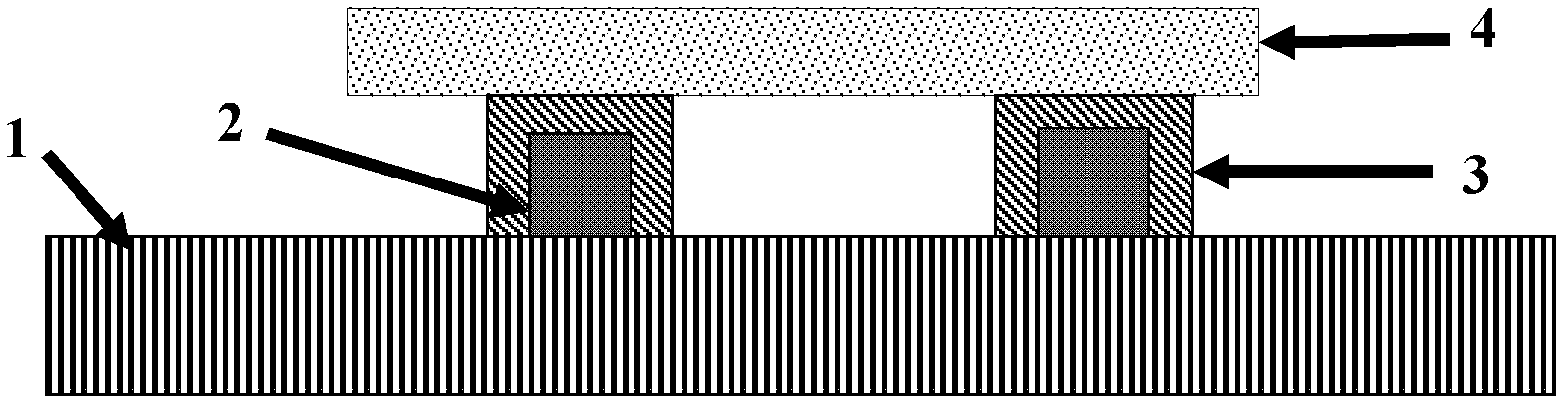

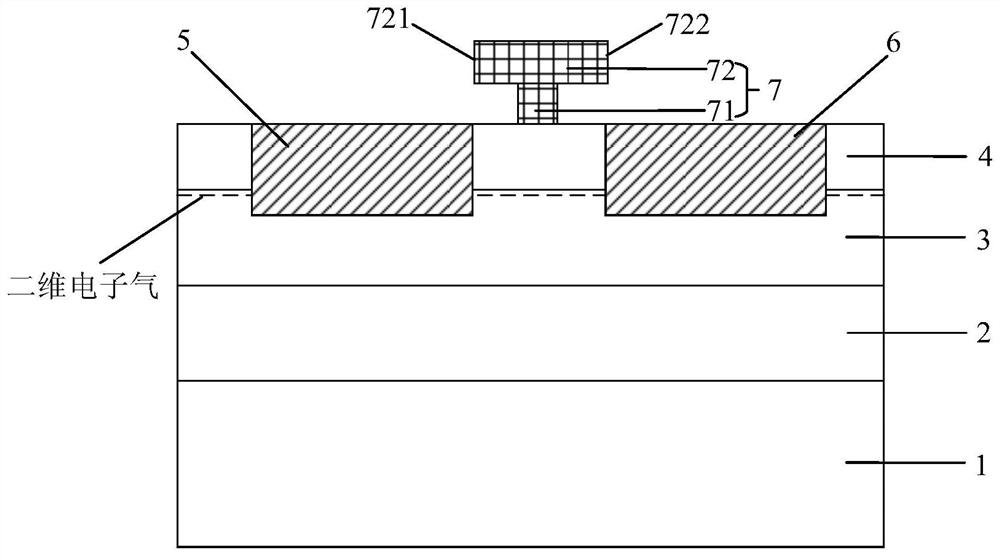

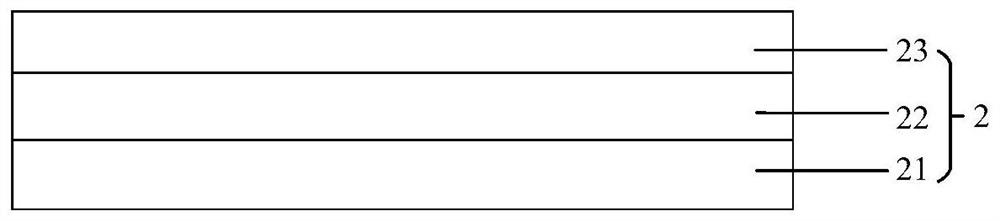

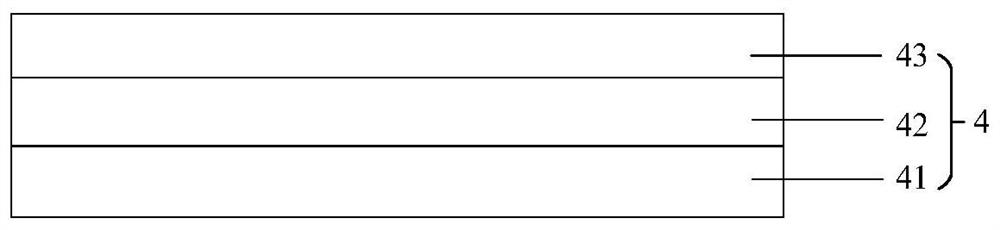

Self-alignment grid-based GaN ultrahigh-frequency device and fabrication method thereof

InactiveCN107393959AEliminate errorsImprove yieldSemiconductor/solid-state device manufacturingSemiconductor devicesUltrahigh frequencySelf-aligned gate

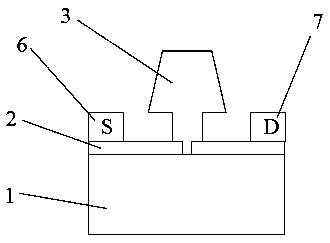

The invention discloses a high-gain and ultrahigh-frequency GaN device and a fabrication method thereof. By the high-gain and ultrahigh-frequency GaN device, the problem of low frequency, gain and power conversion efficiency of an existing similar device is mainly solved. The device comprises a substrate (1), an AlN nucleating layer (2), a GaN buffer layer (3), an AlN insertion layer (4), an AlGaN barrier layer (5) and a passivation layer (7) from bottom to top, wherein a source electrode (8) and a drain electrode (9) are arranged at two ends of the GaN buffer layer, a metal interconnection layer (11) is arranged on the source electrode and the drain electrode, a self-alignment stepped dual-T-shaped electrode (10) is arranged on the AlGaN barrier layer, a groove is formed in a grid pin (101) of the grid electrode, a grid dielectric layer (6) is arranged above the groove, and the passivation layer is arranged on a surface of the barrier layer at two sides of the grid electrode pin. By the high-gain and ultrahigh-frequency GaN device, the grid electric leakage and the parasitic capacitance are reduced, the current collapse is suppressed, the power conversion efficiency and the frequency and gain characteristic of the device are improved, and the high-gain and ultrahigh-frequency GaN device can be used as a high-gain and ultrahigh-frequency device.

Owner:XIDIAN UNIV

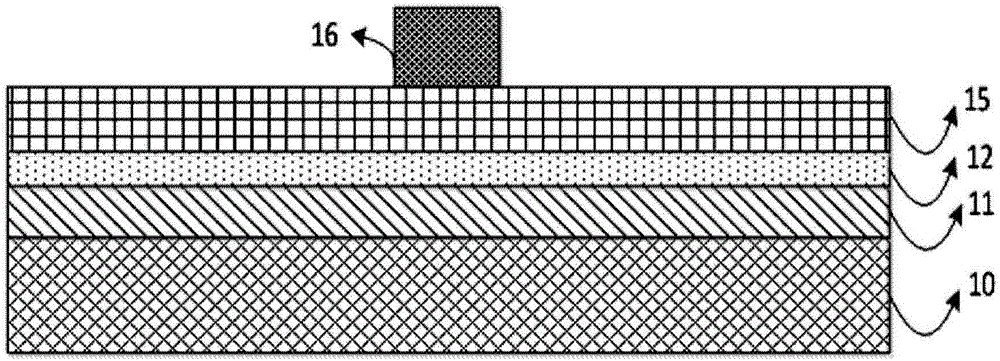

Preparation method of thermosensitive-film infrared detector

ActiveCN102315329APrevent valence changesChange heatFinal product manufactureSemiconductor devicesHeat sensitiveOptoelectronics

The invention relates to a preparation method of a thermosensitive-film infrared detector. The method comprises the following steps: depositing successively a sacrificial layer, a thermal-sensitive layer and a protective layer on a readout circuit of an infrared detector, wherein a material of the thermal-sensitive layer is vanadium oxide and the material of the protective layer is silicon nitride; simultaneously, imaging the protective layer and the thermal-sensitive layer; depositing a dielectric layer; etching a via and a contact, wherein the via etching ends at an electrode of the readoutcircuit and the contact etching ends at the thermal-sensitive layer surface; depositing a metal electrode layer and imaging the metal electrode layer; carrying out structure release of the sacrificial layer. In the method of the invention, the silicon nitride layer or SiO2 is added to be used as a protective layer of a vanadium oxide thermal-sensitive layer so that the vanadium oxide film, which is the thermal-sensitive layer, can be prevented from generating changes of a thermal property and an electrical property and influence on the detector performance can be reduced. Simultaneously, by using a high selection ratio of the silicon nitride etching to the vanadium oxide etching, the contact and the via can be used to complete the imaging of hole graphics through one lithographic plate.

Owner:YANTAI RAYTRON TECH

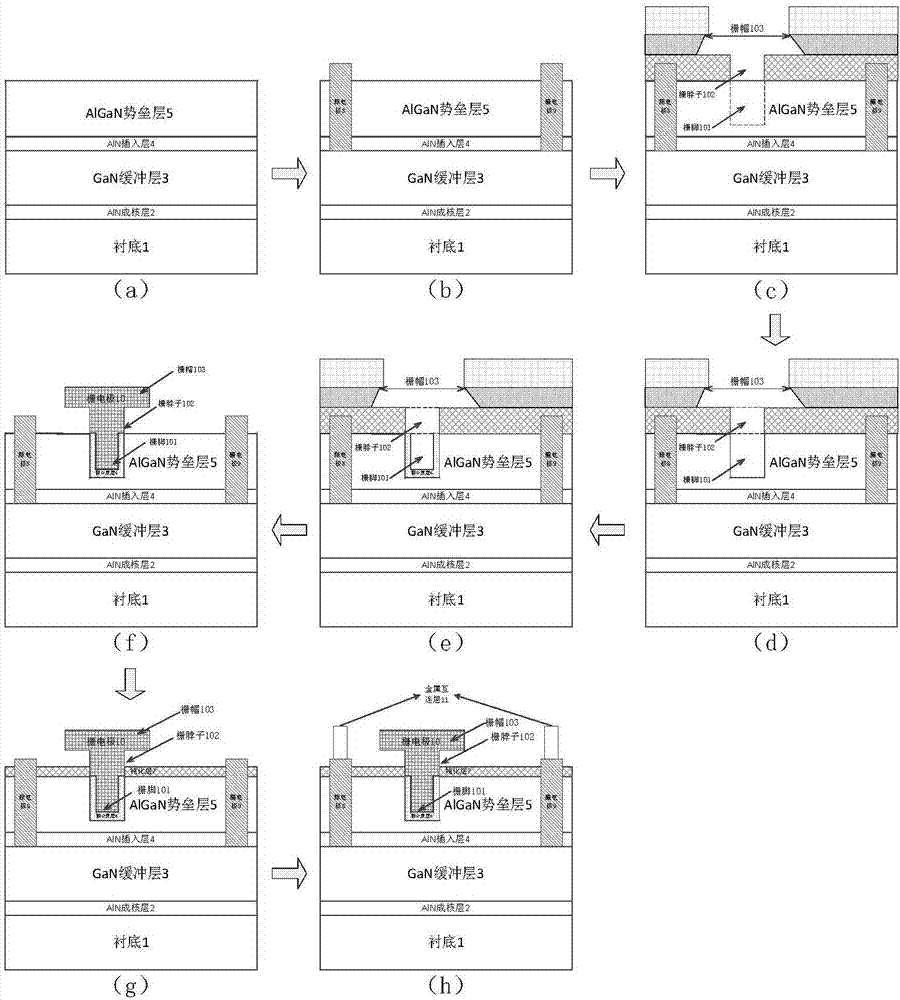

A double T-shaped gate, and a manufacturing method and an application thereof

InactiveCN109103245AImprove the problem of low exposure efficiencyIncrease production capacitySemiconductor devicesParasitic capacitanceEngineering

A double T-shaped gate, and a manufacturing method and an application thereof are provided. The double T-shaped gate comprises a gate foot, a gate root and a gate cap, wherein the gate foot and the gate root form a first level T-shaped gate, the gate root and the gate cap form a second level T-shaped gate, the gate cap is suspended, and the gate foot grows on a substrate through a dielectric passivation layer. The invention can reduce the gate resistance, and the manufacturing method thereof not only can effectively realize the small line width gate, reduce the gate parasitic capacitance, butalso can improve the efficiency of the gate fabrication.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

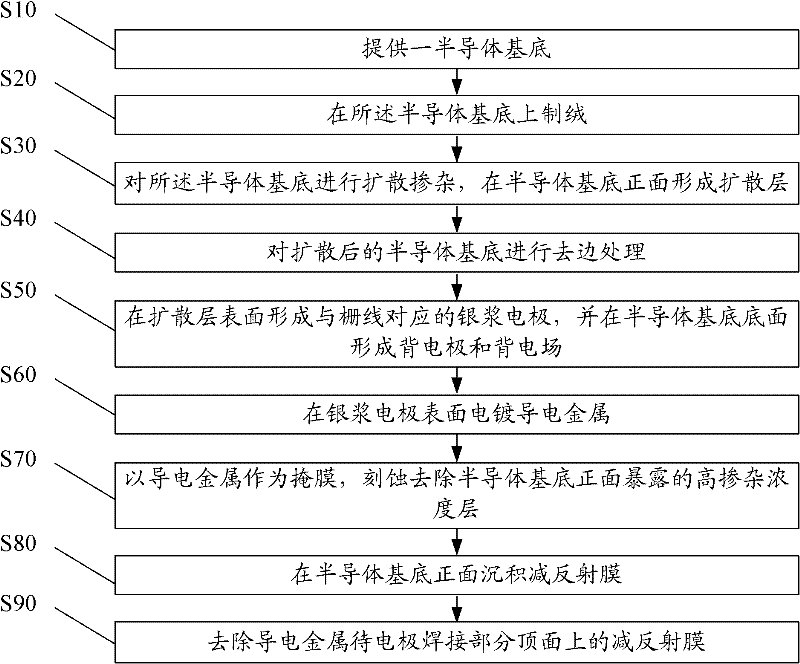

Method for manufacturing selective emitter battery

InactiveCN102185005AImprove production yieldAchieve self-alignmentFinal product manufactureSemiconductor devicesSilver pasteSurface layer

The invention discloses a method for manufacturing a selective emitter battery. The method comprises the following steps of: providing a semiconductor substrate; flocking on the semiconductor substrate; performing diffusion and doping on the semiconductor substrate and forming a diffusion layer on the front face of the semiconductor substrate, wherein the diffusion layer comprises a high-doping-concentration layer on a surface layer and a low-doping-concentration layer on an inner layer; trimming the diffused semiconductor substrate; forming a silver paste electrode which corresponds to a grid line on the surface of the diffusion layer and forming a back electrode and a back electric field at the bottom of the semiconductor substrate; plating a conductive metal on the surface of the silver paste electrode; etching and removing the high-doping-concentration layer exposed on the front face of the semiconductor substrate by taking the conductive metal as a mask; depositing an anti-reflective film on the front face of the semiconductor substrate; and removing the anti-reflective film on the top surface of a part to be subjected to electrode welding of the conductive metal. In the method, the conductive metal is plated on the silver paste electrode and is taken as the mask for removing the high-doping-concentration layer, so that the requirement for the equipment accuracy is lowered and the production yield of an SE (Spray Etching) battery is increased.

Owner:JETION SOLAR HLDG

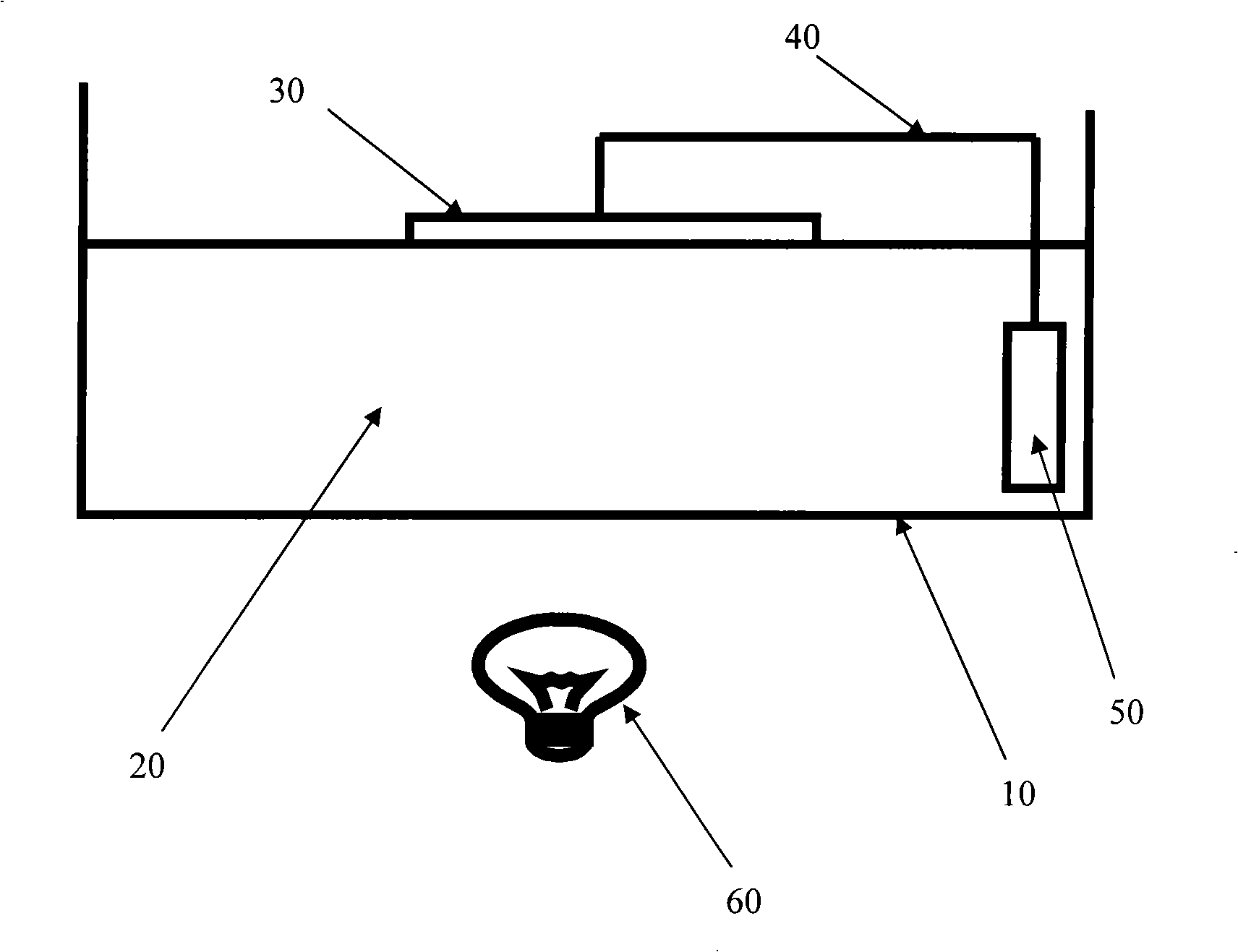

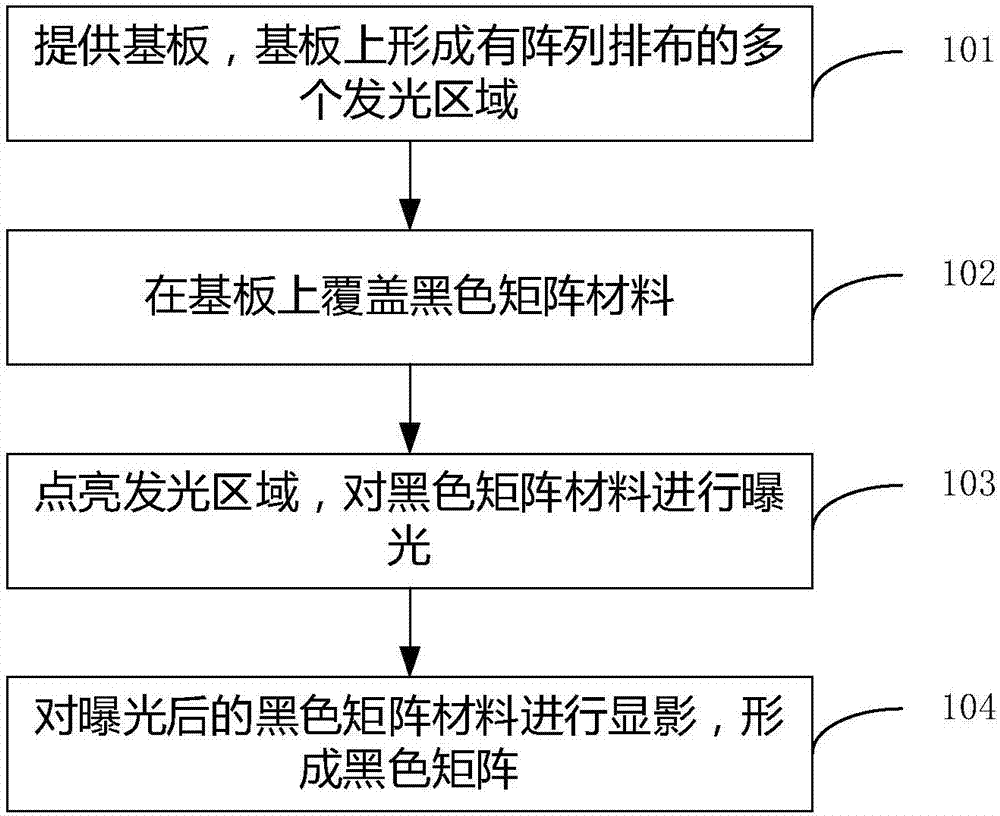

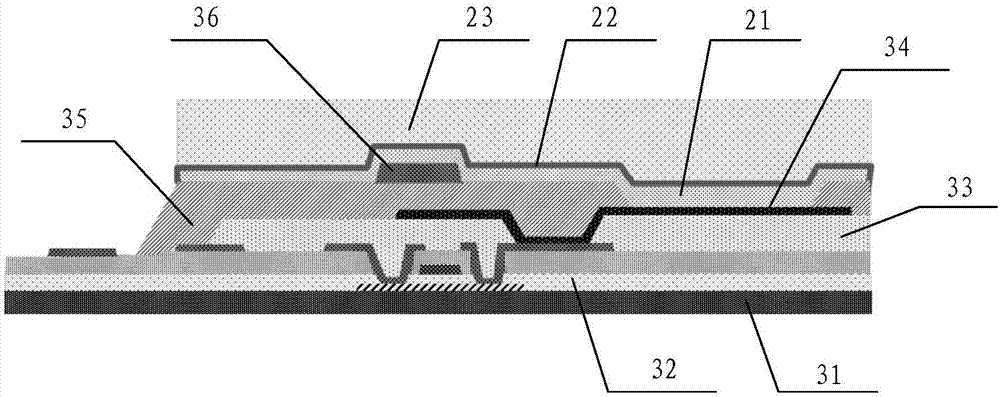

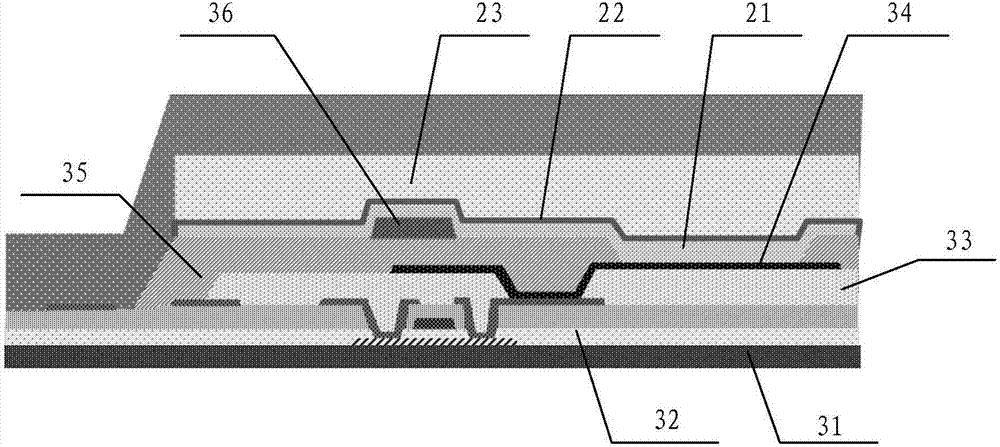

Preparation method of array substrate, array substrate and display device

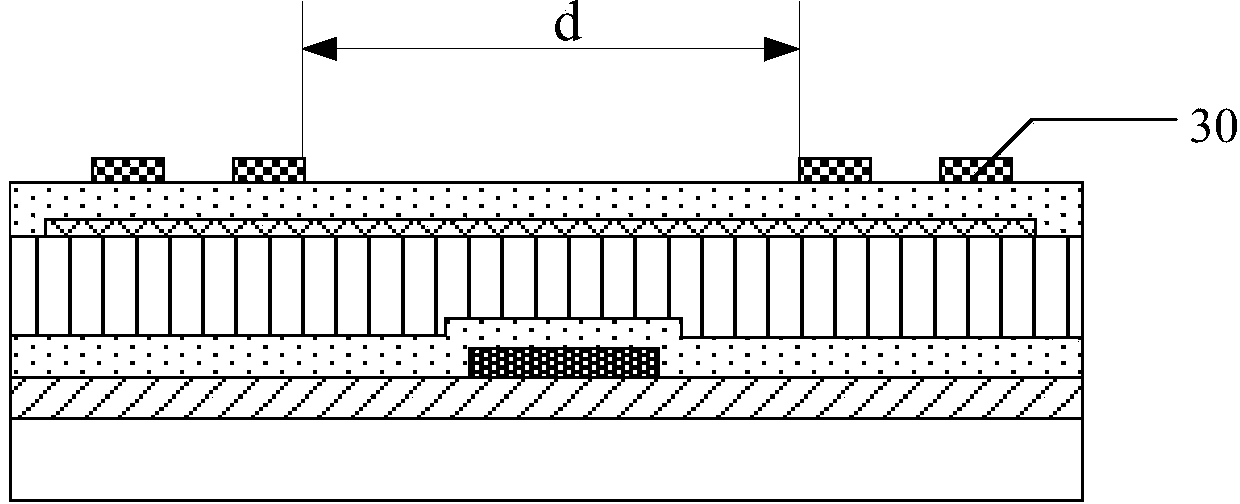

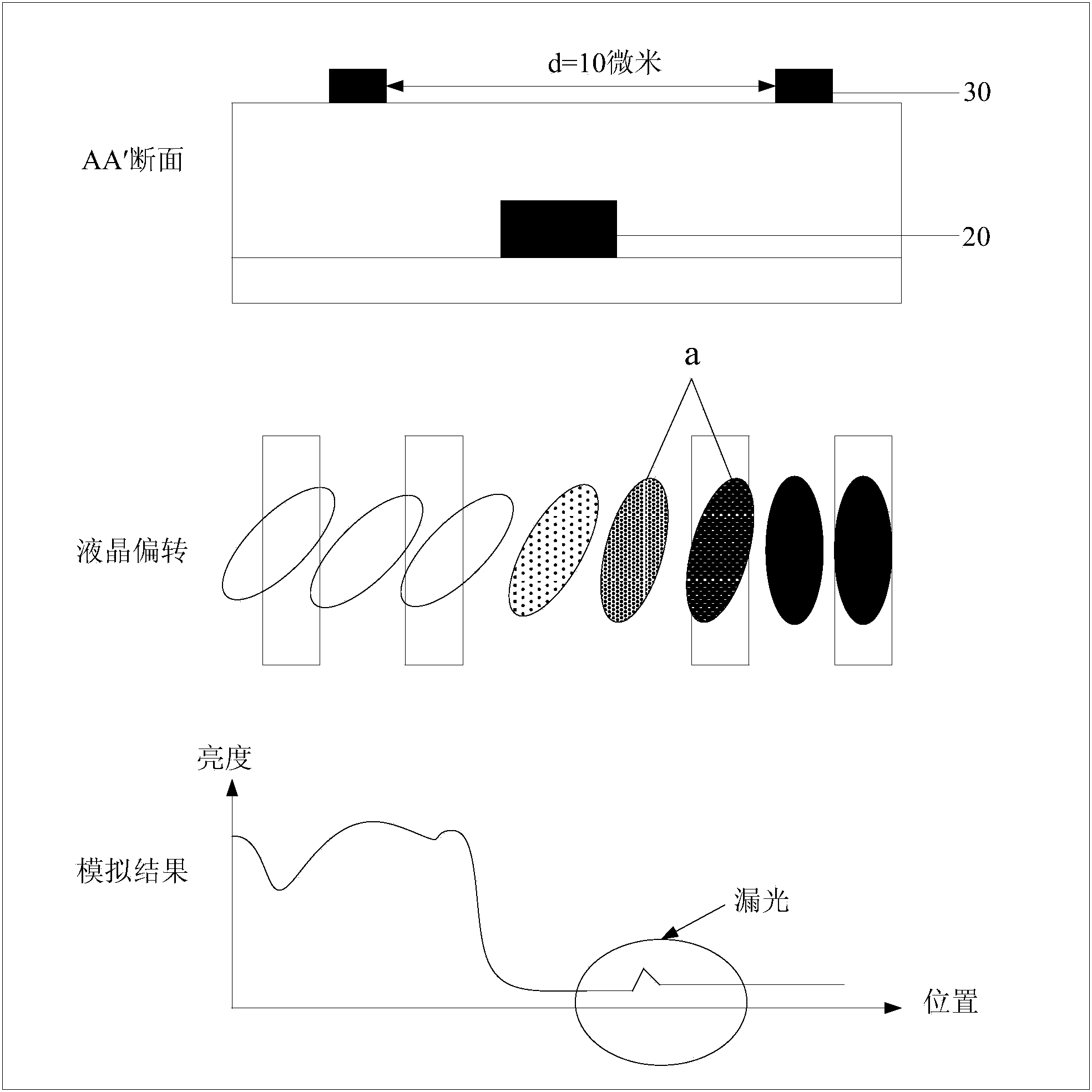

InactiveCN107516664AAvoid misalignmentReduce reflectivitySolid-state devicesSemiconductor/solid-state device manufacturingImage resolutionEvaporation

The invention provides a preparation method of an array substrate, the array substrate and a display device. According to the preparation method, exposure of a black matrix material is achieved by lightening a luminous area on the substrate, and thus the exposed black matrix material is developed to obtain a black matrix. The black matrix material at a corresponding position is exposed by adopting its luminous area, self alignment is achieved, the alignment deviation problem between the black matrix and the luminous area is avoided, and accordingly the emergent light utilization rate is improved. In addition, the made black matrix can replace a circular polarizer to reduce the reflection rate of a display panel, and accordingly the flexibility of the display panel is ensured. Furthermore, the preparation method also gets rid of the limitations of an existing process evaporation mask, and the product resolution can be thus improved.

Owner:BOE TECH GRP CO LTD

Gold-tin solder suitable for self-aligning applications

InactiveUSH1934H1Reduce growthReduce the overall heightWelding/cutting media/materialsSoldering mediaLiquid stateGold plating

A tin-rich gold-tin solder is disclosed which is particularly advantageous for self-aligning applications. When utilized with gold-plated bond locations, the out-diffusion of tin from the solder during heating functions to shift the composition of the remaining solder closer to the eutectic value, thus preserving the liquid state of the solder and improving its reflow quality with respect to conventional eutectic solders.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

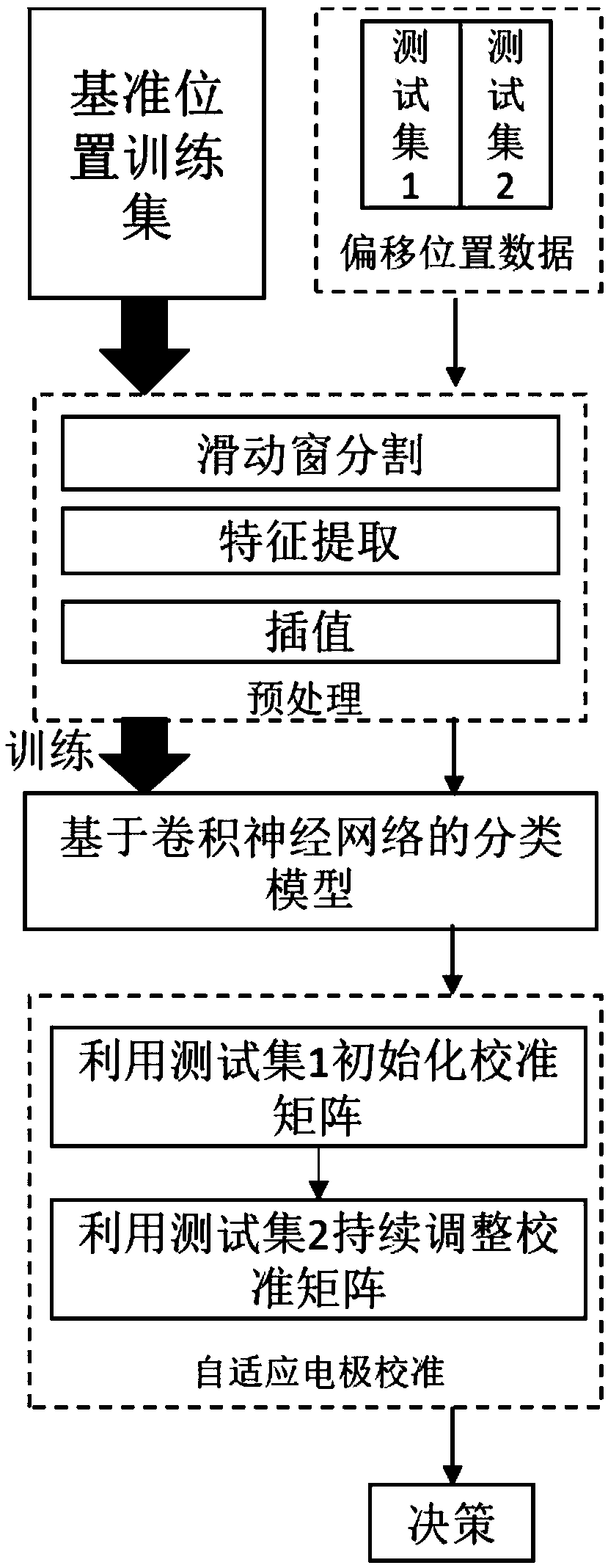

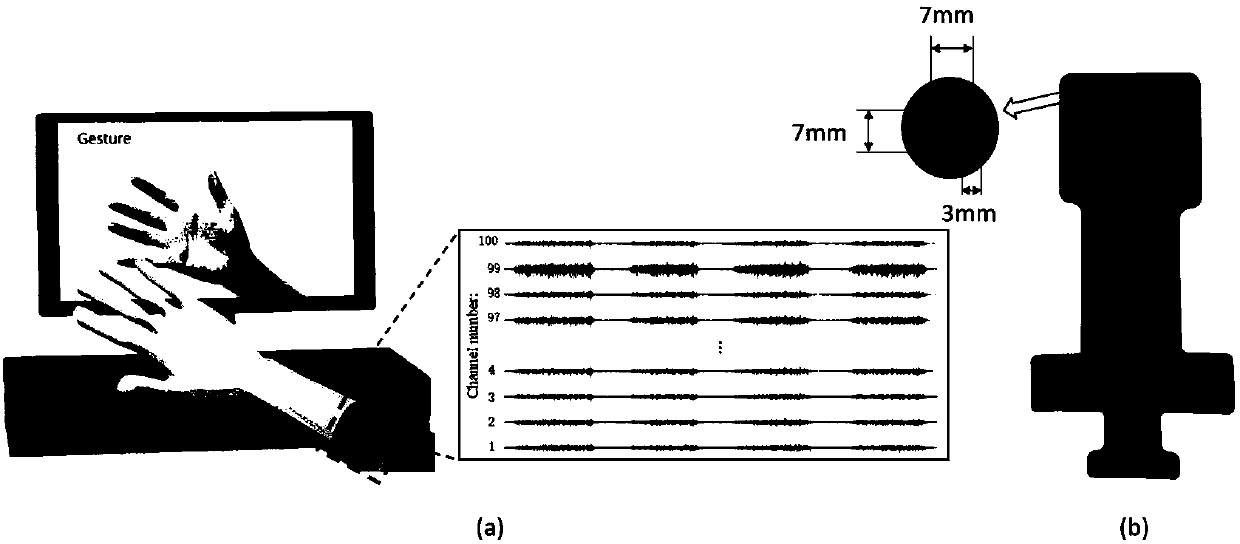

A self-adaptive electrode registration method for robust myoelectric control

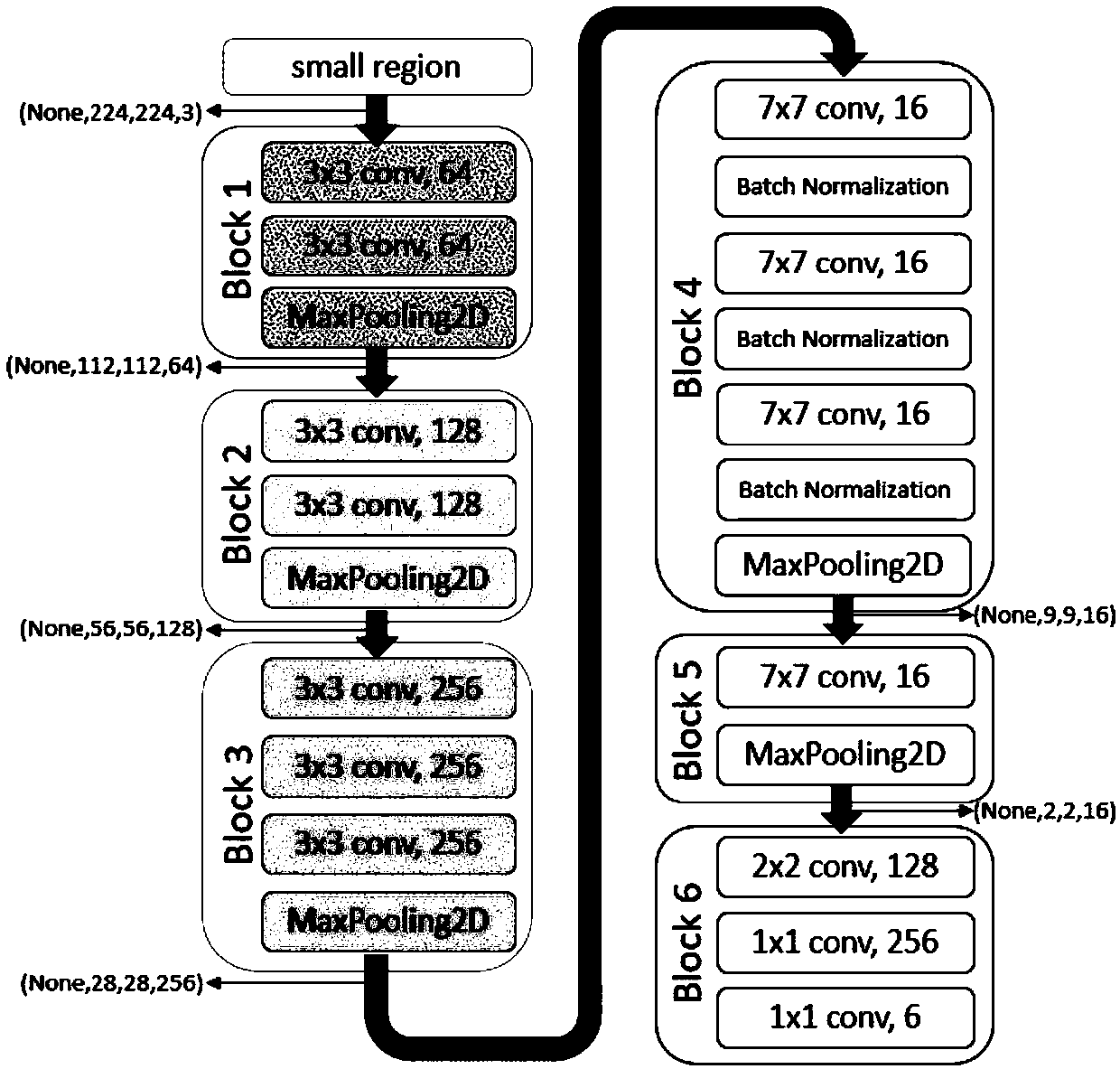

ActiveCN109598219AAchieve self-alignmentAchieving self-calibrationInput/output for user-computer interactionCharacter and pattern recognitionSupervised learningTest phase

The invention discloses a self-adaptive electrode registration method for robust myoelectric control, and the method comprises the steps: completing the matching of a local region between training data (before electrode offset) and test data (after electrode offset) based on a convolutional neural network structure, and achieving the self-alignment or self-calibration of an electrode array; A completely unsupervised learning mode is used, no extra calibration data is needed, and the electrode self-calibration process is directly completed in the test stage. On the basis, the data of the overlapped recording areas before and after the array offset is identified, so that the high accuracy of the motion pattern identification can be ensured.

Owner:UNIV OF SCI & TECH OF CHINA

Quick dynamic alignment method

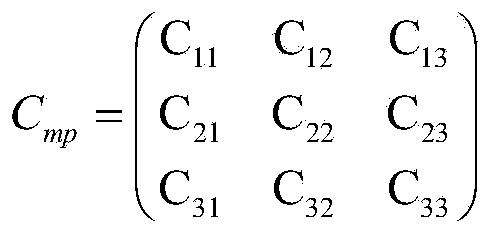

ActiveCN103557873AAchieve self-alignmentNavigation by speed/acceleration measurementsOmegaIntermediate variable

The invention belongs to alignment methods and in particular relates to a quick dynamic alignment method. The quick dynamic alignment method comprises the following steps: 1, coarsely aligning, namely 1.1, inputting information, 1.2, calculating ax, ay and az, 1.3, calculating omega x and omega z, 1.4, calculating according to a formula (1), 1.5, calculating according to a formula (2), and 1.6, calculating according to a formula (3); 2, carrying out navigation calculation; 3, calculating an intermediate variable; and 4, aligning. The quick dynamic alignment method has the beneficial effects of being capable of accurately estimating three misalignment angles of a platform system relative to a geographical system and three uncompensated platform drifts (of the platform system) under angular vibration of a carrier so as to achieve the purpose of high-precision self-alignment.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST

Self-aligning sintering clamp and method for semiconductor laser chip

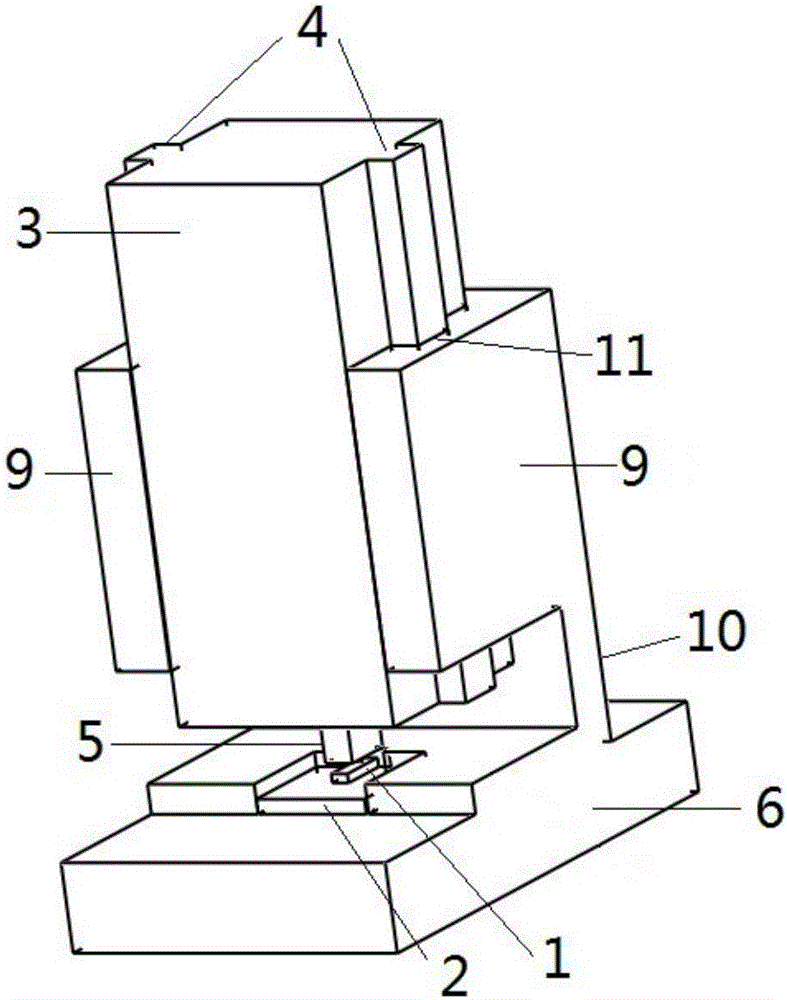

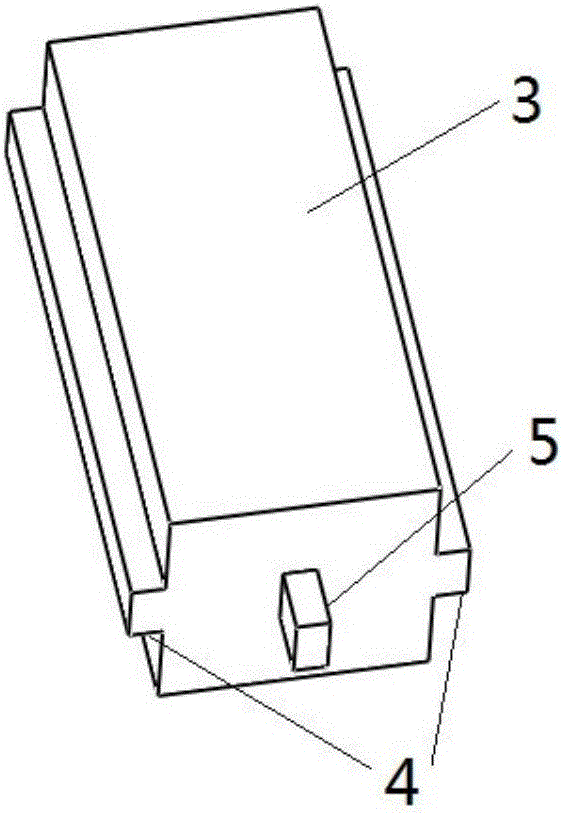

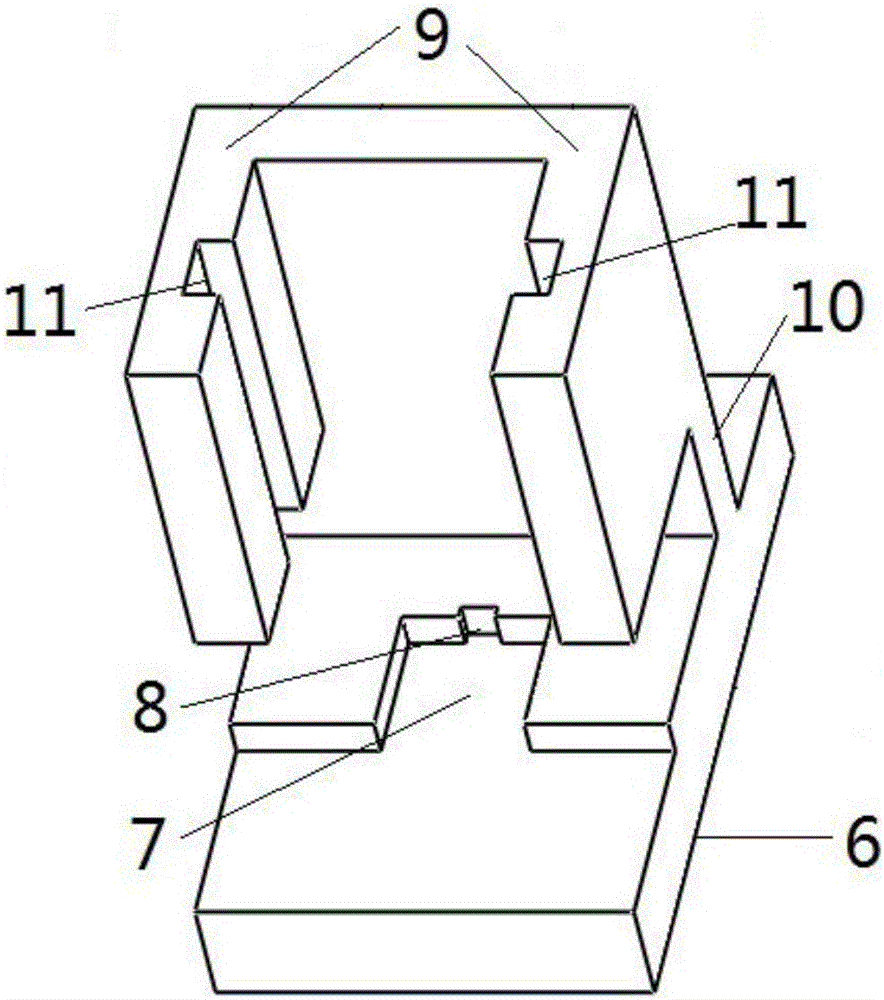

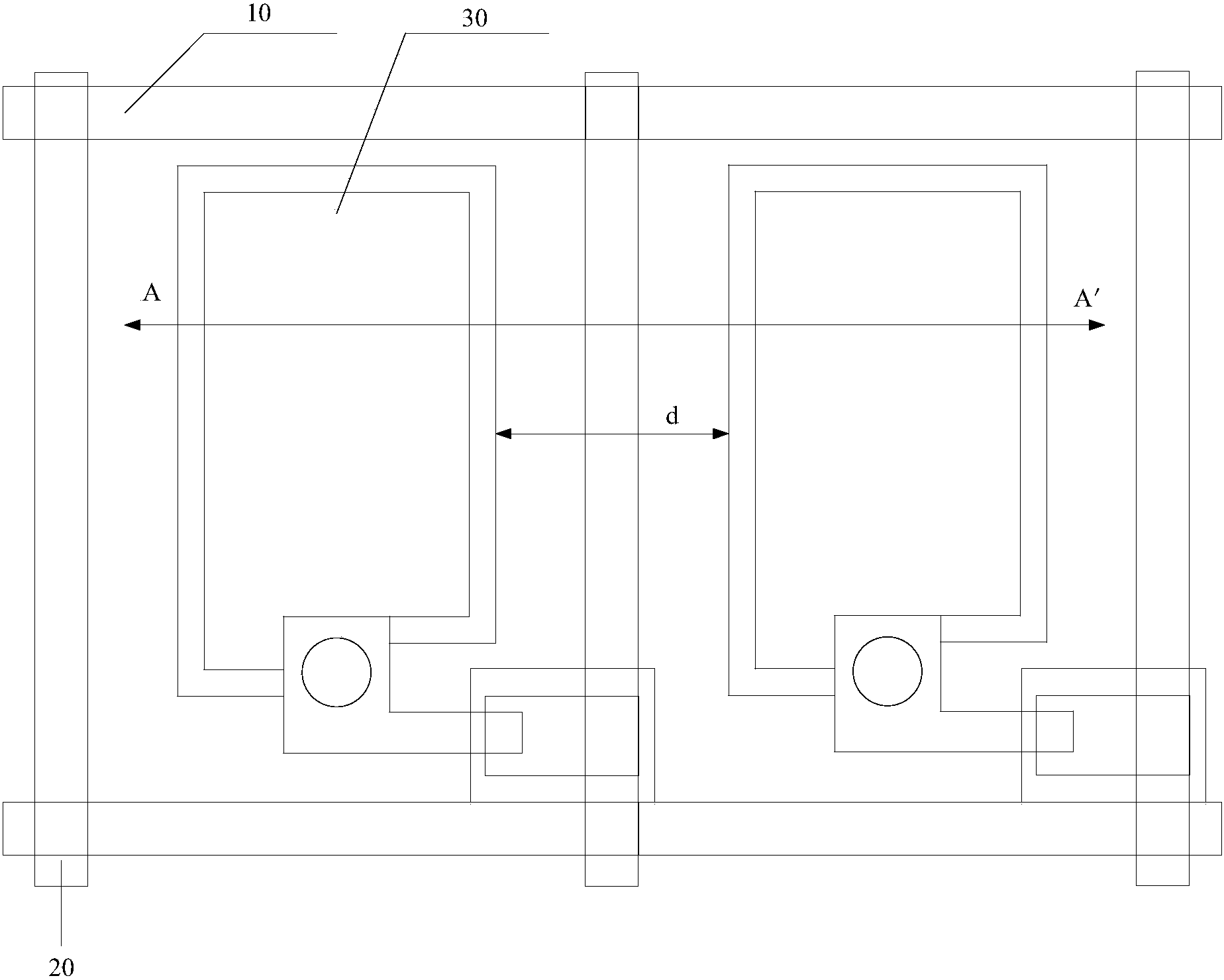

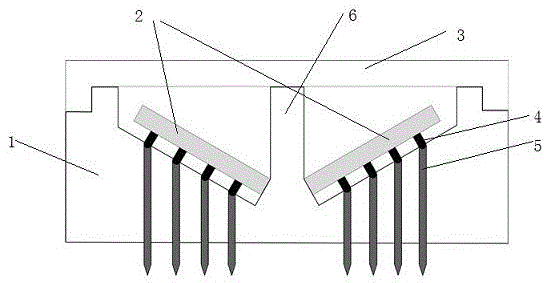

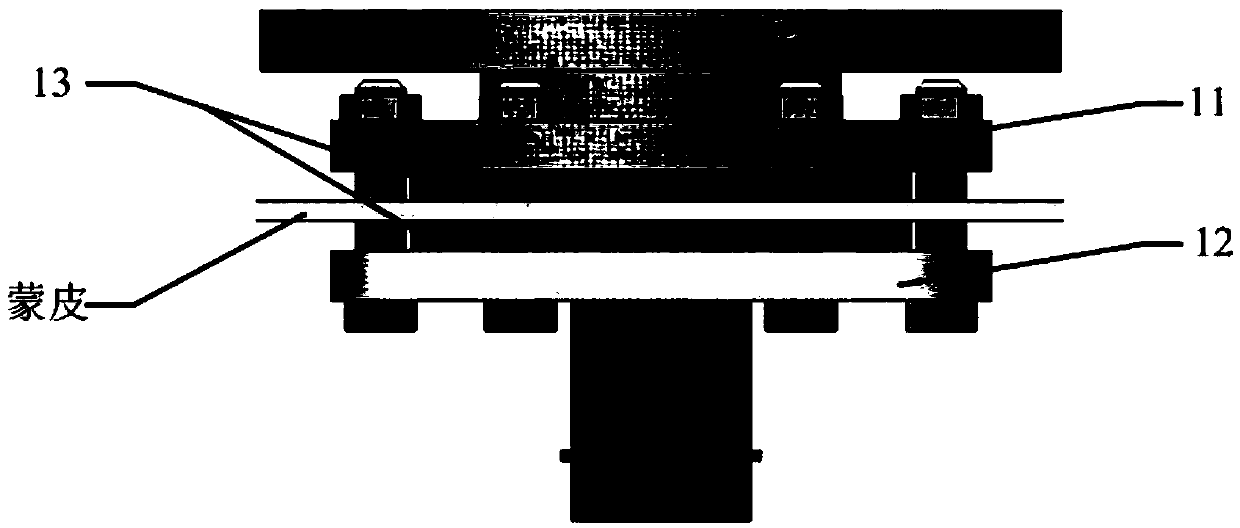

ActiveCN105896307ASimple structureLow costLaser detailsSemiconductor lasersSemiconductor chipEngineering

The invention relates to a self-aligning sintering clamp and method for a semiconductor laser chip. The clamp comprises a pedestal, a guide rail support, and a press block. The pedestal is provided with a positioning card slot matched with a heat sink. Two sides of the press block are provided with symmetric positioning racks. The guide rail support is vertically disposed on the pedestal, and is provided with symmetric suspension arms. The interior of each suspension arm is provided with a positioning guide rail. The positioning racks of the press block can be sleeved by the positioning guide rails, and move up and down in the positioning guide rails. The bottom end of the press block is provided with a press column. When the press block moves downwards, the press column compresses a chip on the heat sink. The invention also provides the method for sintering the semiconductor laser chip through the above clamp. The clamp is simple in structure, is low in cost, can achieve the self-aligning, and is convenient for operation and observation. The method can achieve the quick batch sintering of the semiconductor laser chips and heat sinks, and remarkably improves the sintering yield of the clamp.

Owner:Shandong Huaguang Optoelectronics Co. Ltd.

Array substrate as well as production method thereof and display device

InactiveCN103777395AFunction increaseReduce complexitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

The invention relates to the technical field of the display, in particular to an array substrate, a display device and a production method of the array substrate, which is used for reducing the interference of an electric field between two adjacent first transparent electrodes of the array substrate. The array substrate comprises an underlayer substrate, a plurality of grid lines, a plurality of data lines and first transparent electrodes, wherein the grid lines and the data lines are arranged on the underlayer substrate and intersected with one another to define pixel areas, each first transparent electrode is arranged in each pixel area, and the array substrate also comprises insulation parts; each insulation part is arranged between every two adjacent first transparent electrodes, the upper surface of each insulation part is higher than the upper surface of the first transparent electrode, and the lower surface of each insulation part is lower than the upper surface of the first transparent electrode. By adopting the array substrate, the interference of the electric field between two adjacent first transparent electrode can be reduced.

Owner:BOE TECH GRP CO LTD

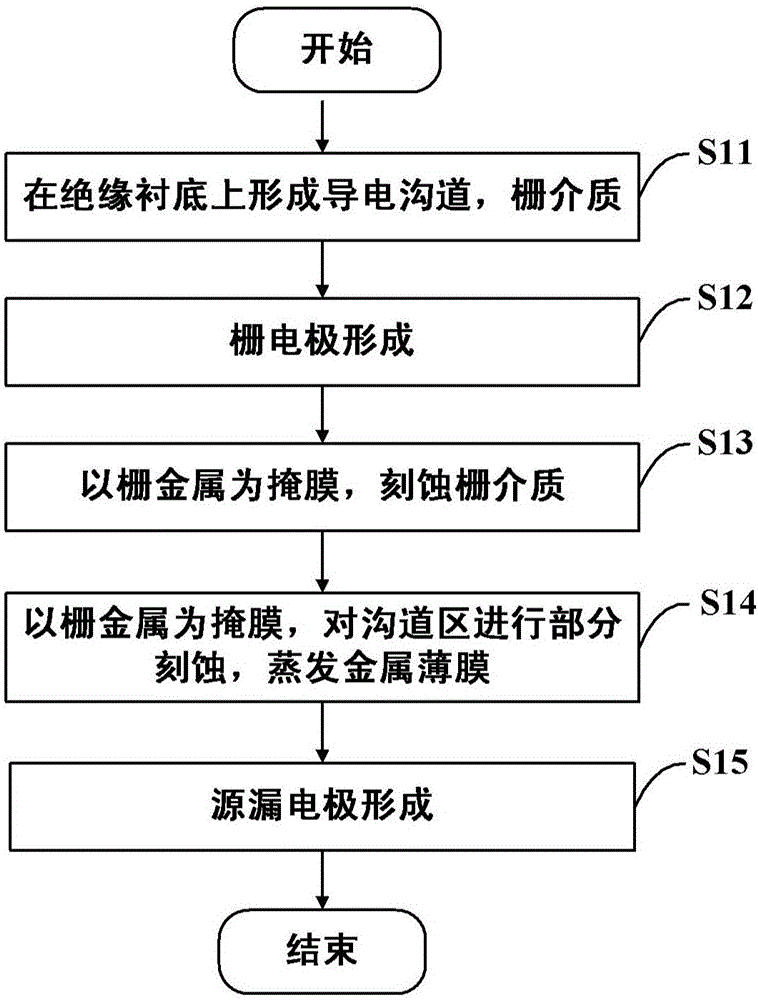

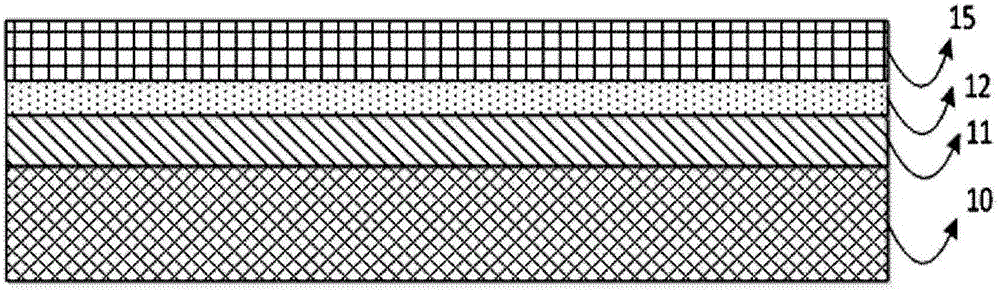

Graphene field effect transistor and manufacturing method thereof

ActiveCN105762194AAvoid pollutionAvoid direct contactSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMedia layer

Provided are a graphene field effect transistor and a manufacturing method thereof.The manufacturing method comprises the following steps that a top gate metal is used as a gate medium under a mask protecting top gate metal, and a gate medium layer is etched to remove the gate medium covering a graphene active area between a gate source and a gate drain; a top gate electrode is used as a mask to etch graphene, and a lattice structure of a graphene material is destroyed to form a defect; then, a metal film layer is formed on a formed device, and a source electrode and a drain electrode are prepared on the metal film layer; and the completed device is annealed.By the adoption of the manufacturing method, the separation distance between the gate source and the gate drain can be decreased, the graphene pollution caused by a device machining process is effectively avoided, the lower contact resistivity can be obtained by partially etching the graphene material in a contact area, and accordingly the performance of the graphene transistor can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

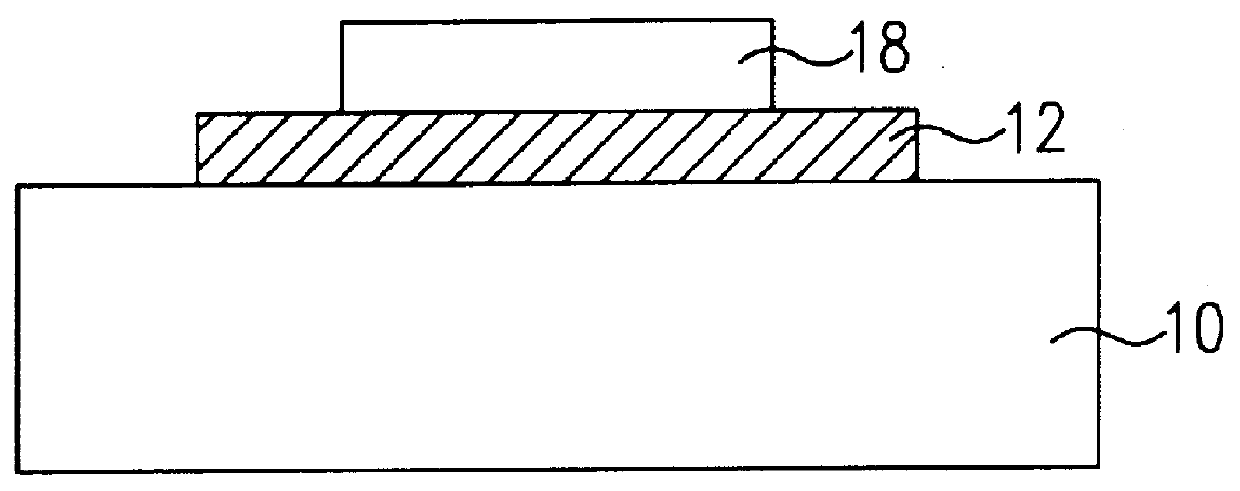

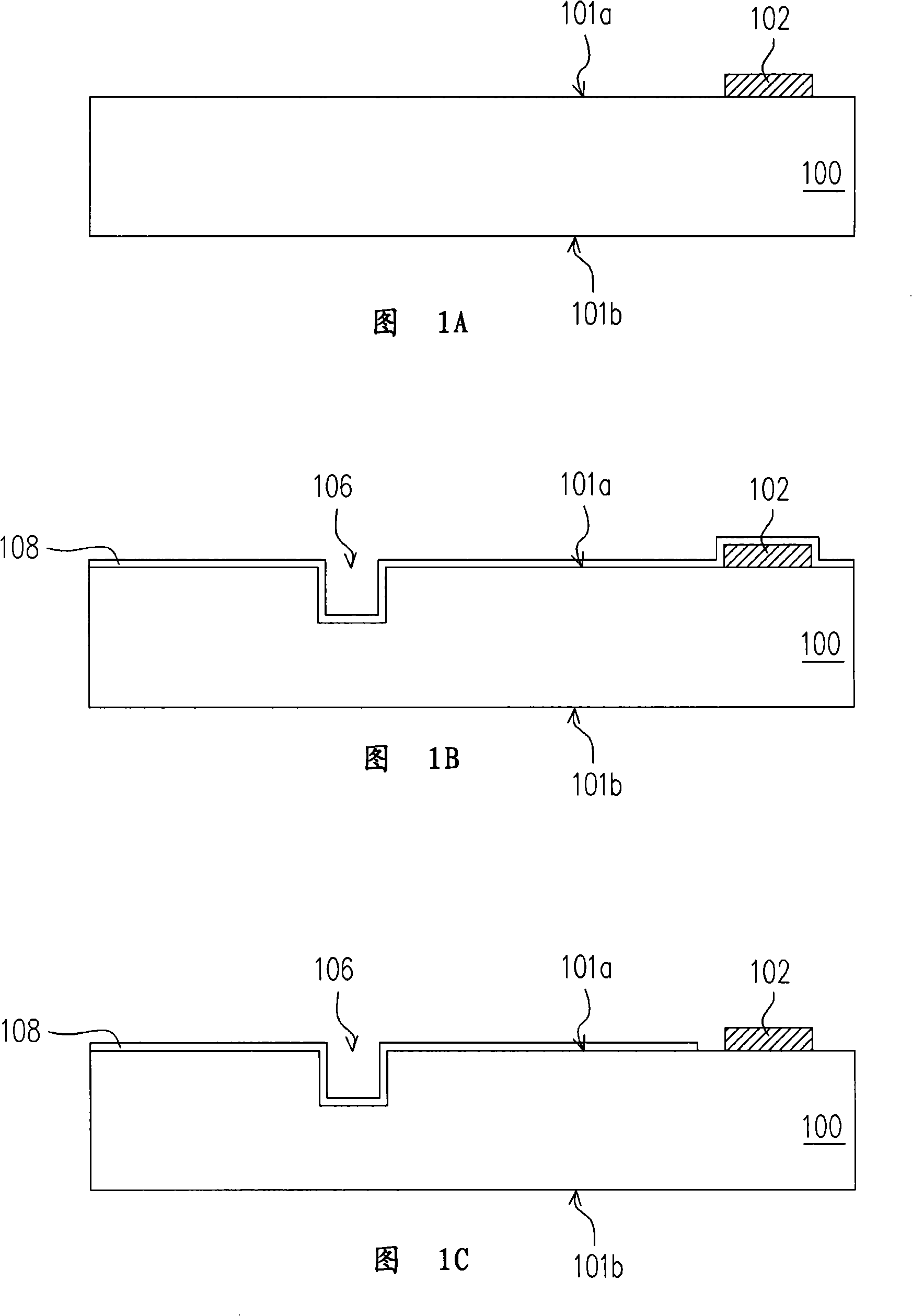

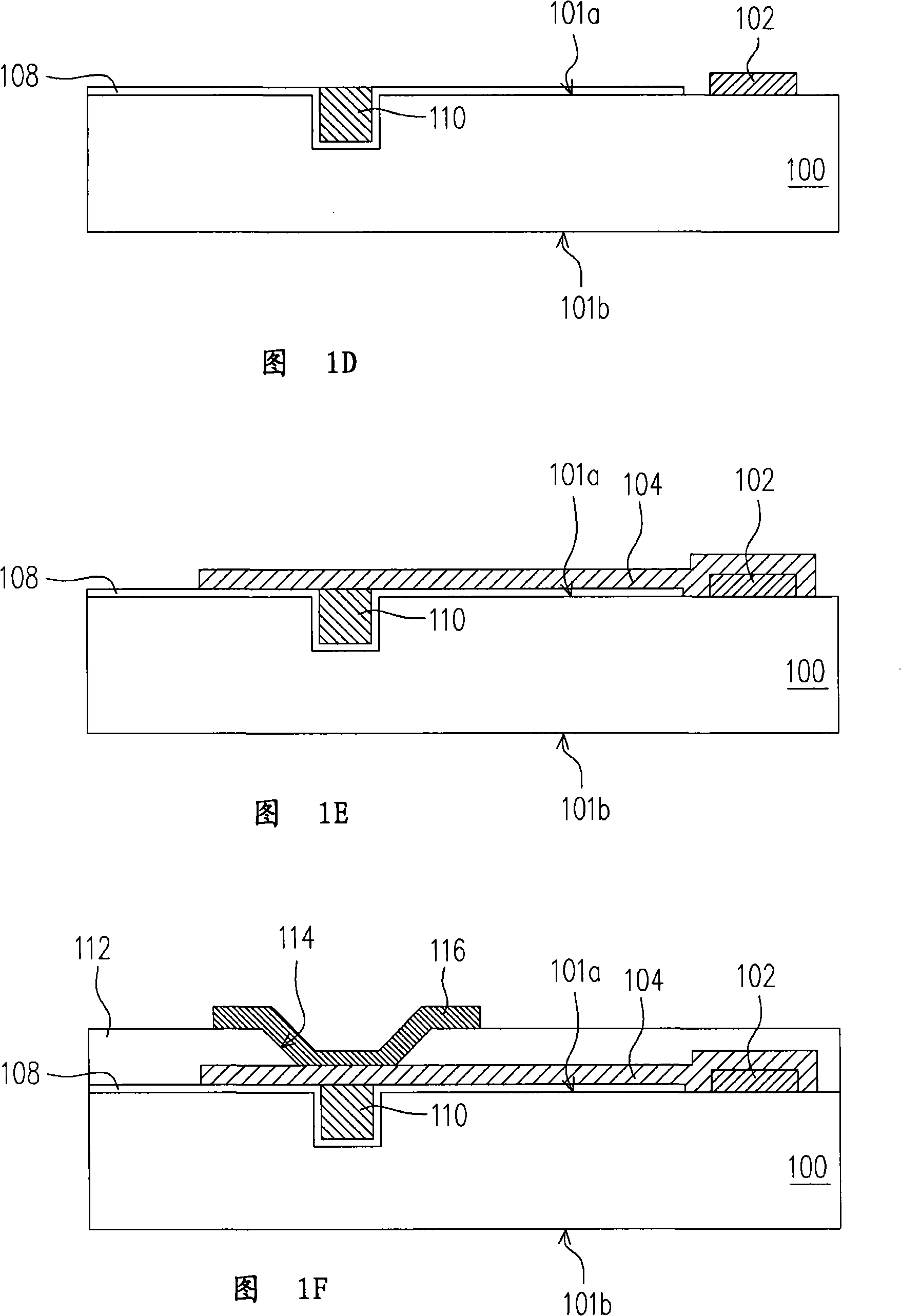

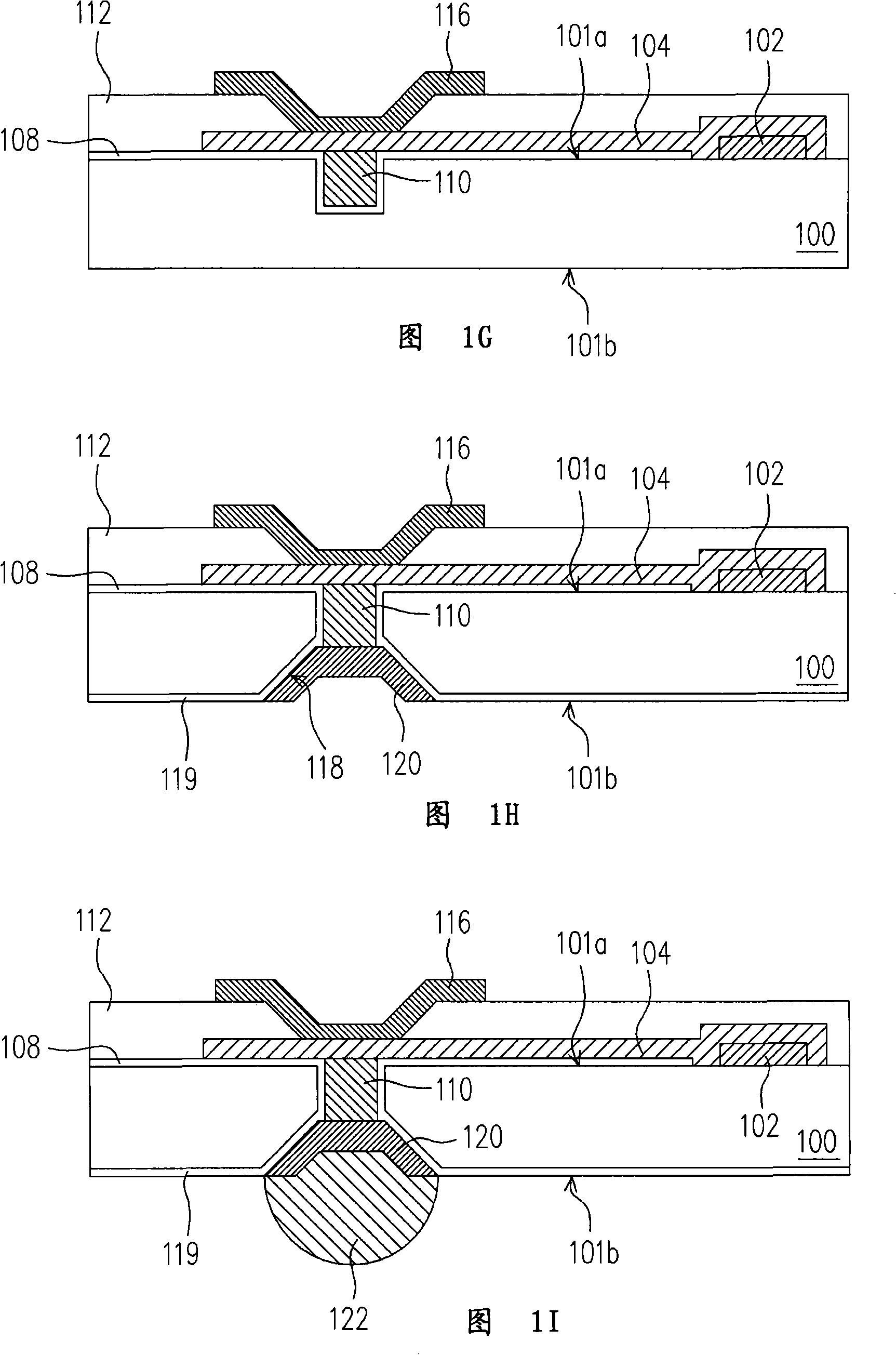

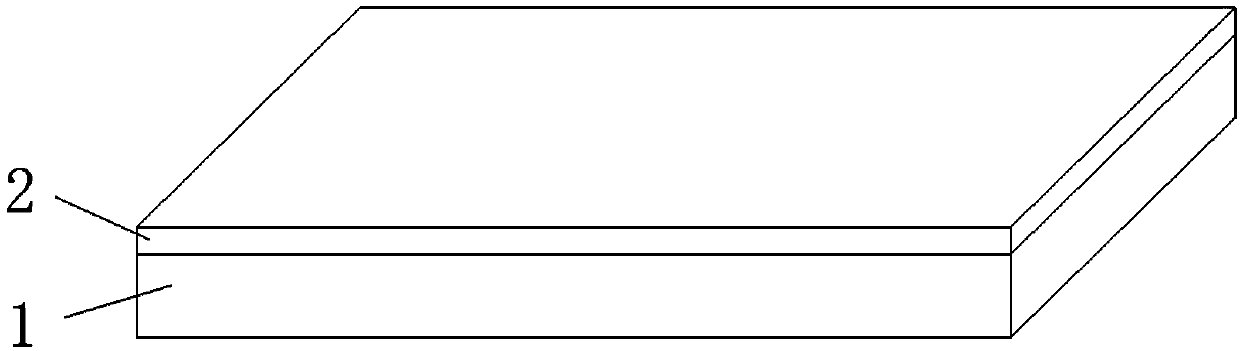

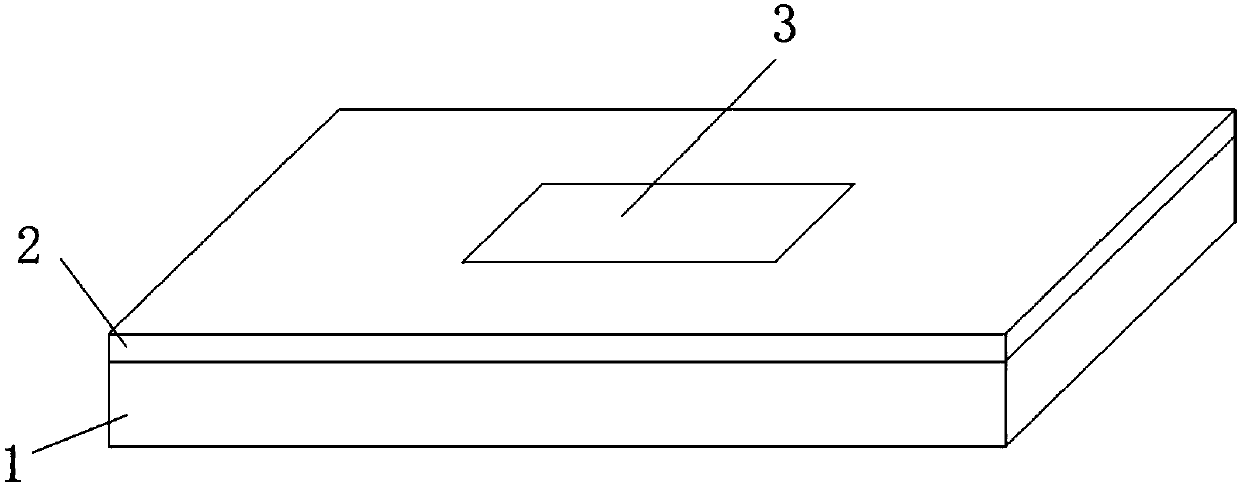

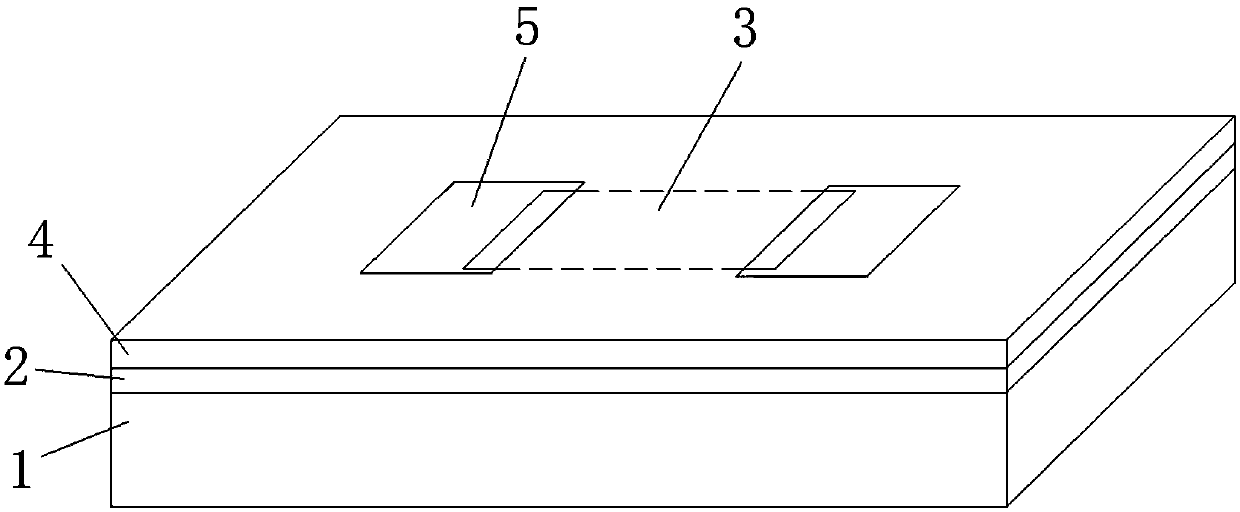

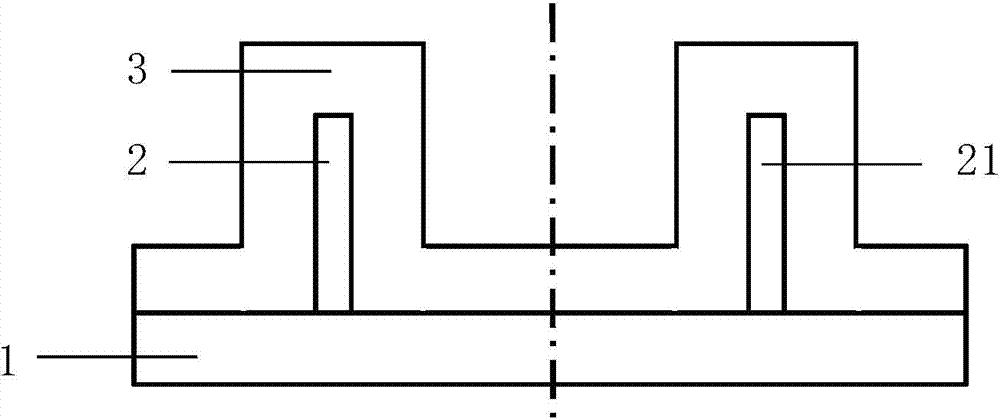

Self-aligning wafer or chip structure and self-aligning stacking structure and manufacturing method thereof

InactiveCN101330067AAchieve self-alignmentSimple methodSemiconductor/solid-state device detailsSolid-state devicesEngineeringSelf alignment

The invention relates to a self-alignment chip or a chip structure, which comprises a substrate, at least a first recess, at least a second recess, at least a connecting structure and at least a lug. The substrate comprises a first surface and a second surface, and at least a pad is formed on the first surface. The first recess is positioned on the first surface, and the first recess is electrically connected with the pad. The second recess is arranged on the second surface. The connecting structure penetrates the substrate and is positioned between the first recess and the second recess, and the connecting structure is electrically connected with the first recess and the second recess. The lug can be filled in the second recess, and extend from the second surface.

Owner:IND TECH RES INST

Double-chip flip chip structure

InactiveCN104701305APrevent chips from interacting with each otherImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesHeat sinkContact position

The invention provides a double-chip flip chip structure by taking a flip chip structure as a starting point. The double-chip flip chip structure is characterized in that a substrate with a central partition plate is provided with two chip slots in certain gradients, and a plurality of semispherical grooves are formed at contact positions of the slot slopes and chip conducting projections; each chip is provided with a plurality of cylindrical conducting projections with semispherical tops; an upper cooling fin is fastened to the top of the substrate. The double-chip flip chip structure has the advantages of realization of self-alignment chip bonding, realization of integral packaging of double chips, high integration level, reduction of chip packaging area and improvement of a heat radiation function.

Owner:SHANGHAI RES INST OF MICROELECTRONICS SHRIME PEKING UNIV

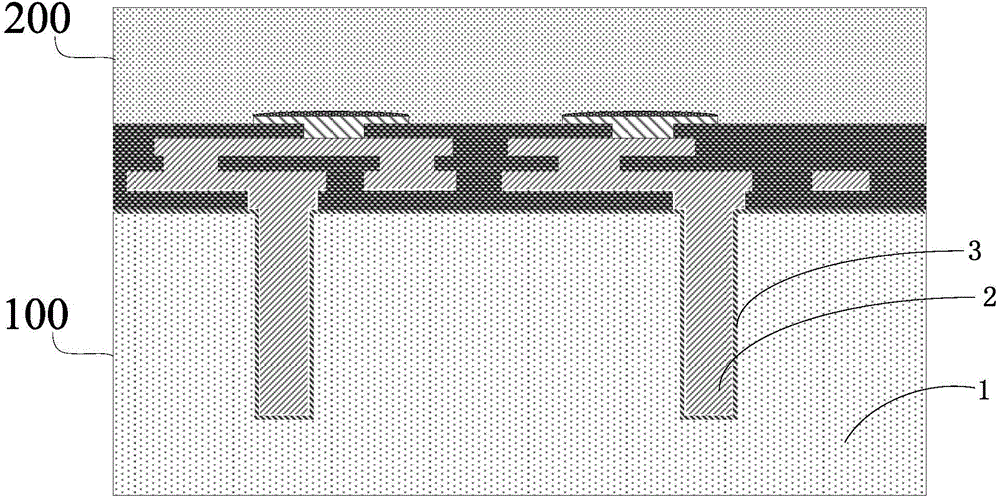

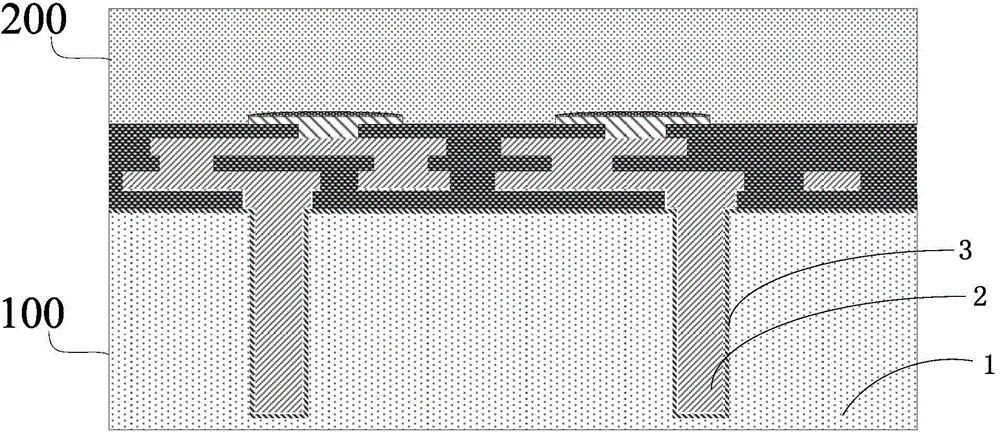

TSV (through silicon via) back side hole leaking technology without CMP (chemical mechanical grinding) technology

InactiveCN104637870ACMP process avoidReduce processing costsSemiconductor/solid-state device manufacturingCompound (substance)Engineering

The invention provides a TSV (through silicon via) back side hole leaking technology without CMP (chemical mechanical grinding) technology. The TSV back side hole leaking technology comprises the following steps of S1, providing a device wafer which completes a front side technology, wherein the device wafer comprises a substrate and a TSV (through silicon via) blind hole, and the TVS blind hole is formed in the substrate; S2, providing a carrier wafer, and bonding the front side of the device wafer and the carrier wafer by a temporary bonding technology, so as to obtain a temporary bonding body; S3, mechanically grinding the back side of the substrate of the device wafer, and thinning; S4, etching the back side of the substrate, and enabling the TSV blind hole to expose out of the back side of the substrate; S5, coating a back side medium layer at the back side of the substrate of the device wafer, and completely covering the exposing part of the TSV blind hole in the step S4; S6, utilizing a mechanical grinding technology to process the back side medium layer, and enabling the TSV blind hole to expose out of the back side medium layer. The TSV back side hole leaking technology has the advantages that the CMP process in the TSV back side end exposing process is avoided, the technological cost is greatly reduced, the output efficiency is obviously improved, and the self-aligning effect of the back side medium layer hole via is realized.

Owner:NAT CENT FOR ADVANCED PACKAGING

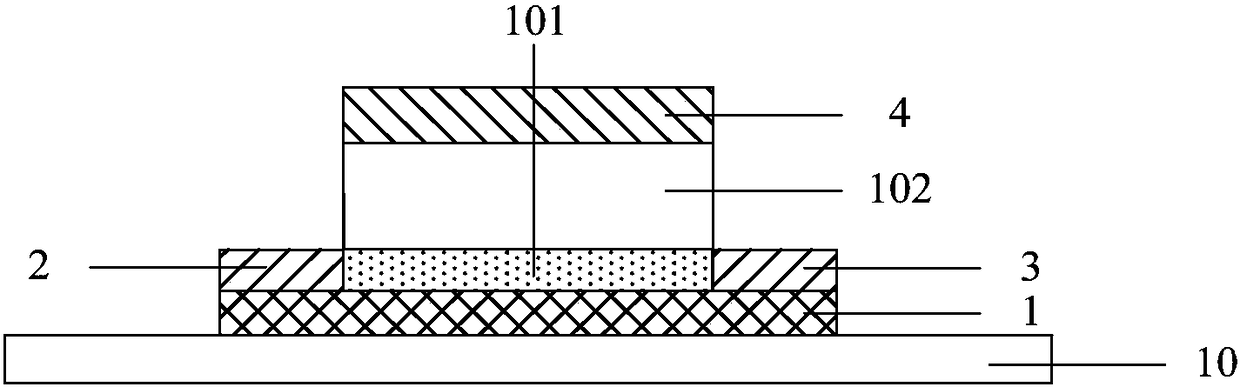

Self-aligned two-dimensional crystal material field-effect semiconductor device and preparation method thereof

InactiveCN105609539AIncrease working frequencyOverlay Capacitance DecreaseTransistorSemiconductor/solid-state device manufacturingCapacitanceGate dielectric

The invention provides a self-aligned two-dimensional crystal material field-effect semiconductor device and a preparation method thereof, and belongs to the technical field of semiconductor devices. The semiconductor device provided by the invention comprises a gate electrode region, a source electrode region, a drain electrode region and a two-dimensional crystal material layer, wherein the two-dimensional crystal material layer is connected with a source electrode and a drain electrode, and strides the local part of the gate electrode region; and a gate dielectric oxidation layer is arranged between the two-dimensional crystal material layer and the gate electrode region at the lower part of the two-dimensional crystal material layer. By a self-aligned technology provided by the invention, position alignment of the gate electrode and the source electrode and the drain electrode of the device can be automatically achieved, so that, on one hand, the coverage capacitance of the gate electrode, the source electrode and the drain electrode is greatly reduced, which has important significance for improvement of the working frequency of the device; and on the other hand, the self-aligned device structure with the gate electrode, the source electrode and the drain electrode greatly reduces channel layers, namely the parasitic resistance of the two-dimensional crystal material, between the gate electrode and the source electrode and between the gate electrode and the drain electrode, which is also beneficial to improvement of the working frequency of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Convenience quick inflator for airship balloons

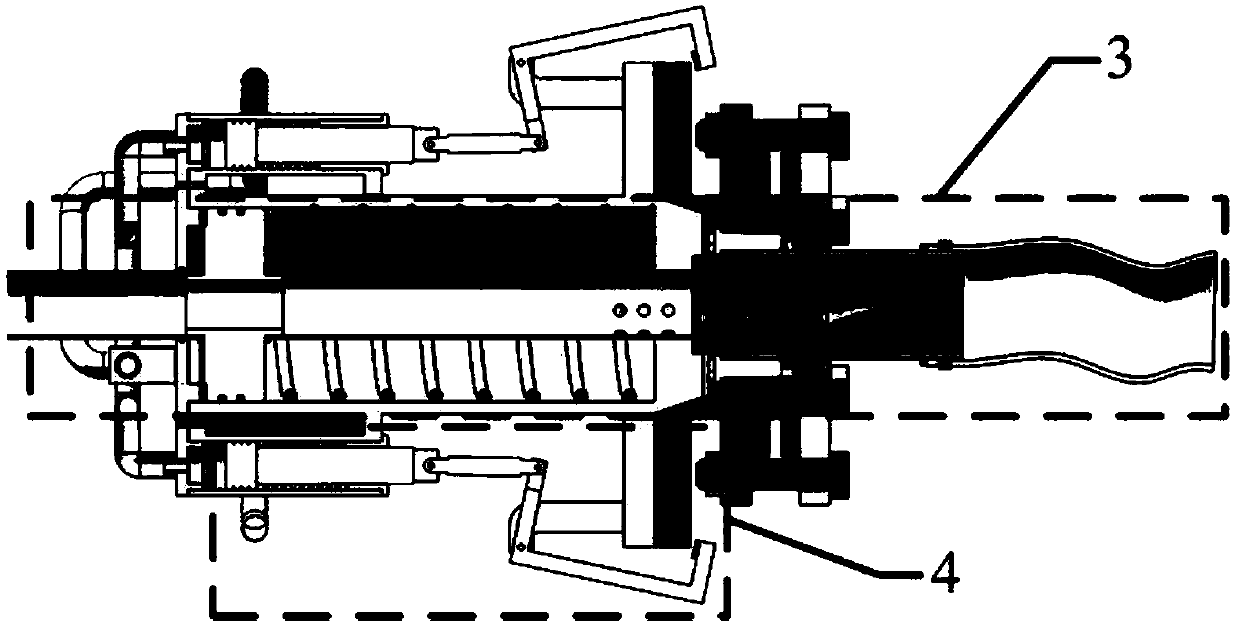

ActiveCN109649630AReasonable structureStrong reliabilityGas-bag arrangementsFour-way valveEngineering

The invention belongs to the technical field of aircrafts and particularly relates to a convenience quick inflator for airship balloons, comprising a fixing seat, a moving seat, an inflating mechanism, a buckle mechanism, an electromagnetic four-way valve and an electromagnetic relief valve. The convenience quick inflator for airship balloons can provide quick alignment and fastening, inflating, and release and separation; manpower, material and time materials of the inflating process are saved. The convenience quick inflator for airship balloons is reasonable in design, compact in structure,high in practicality and reliability, and convenient to maintain.

Owner:中国人民解放军63660部队

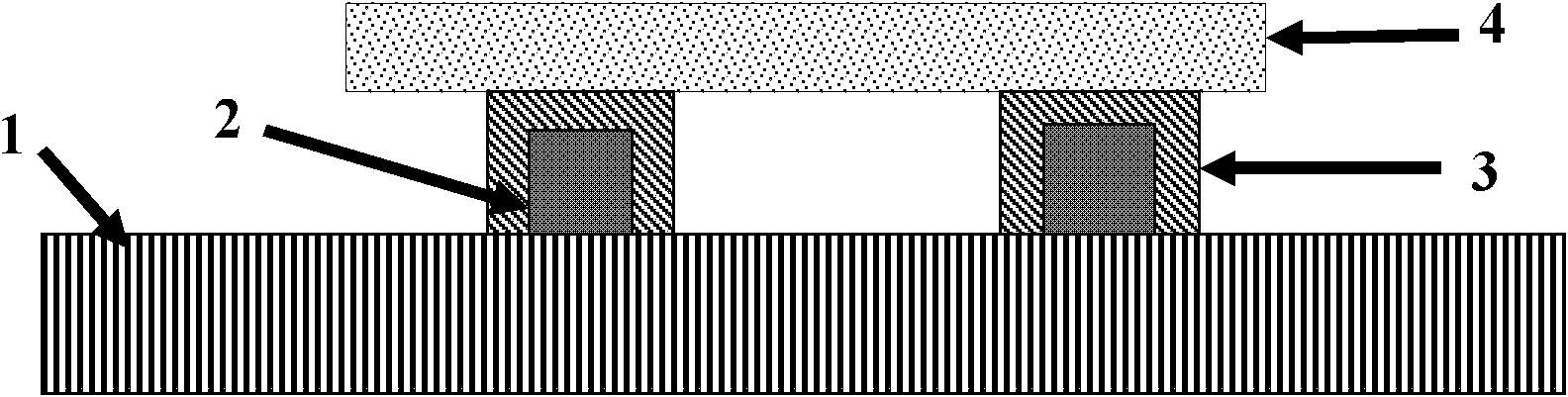

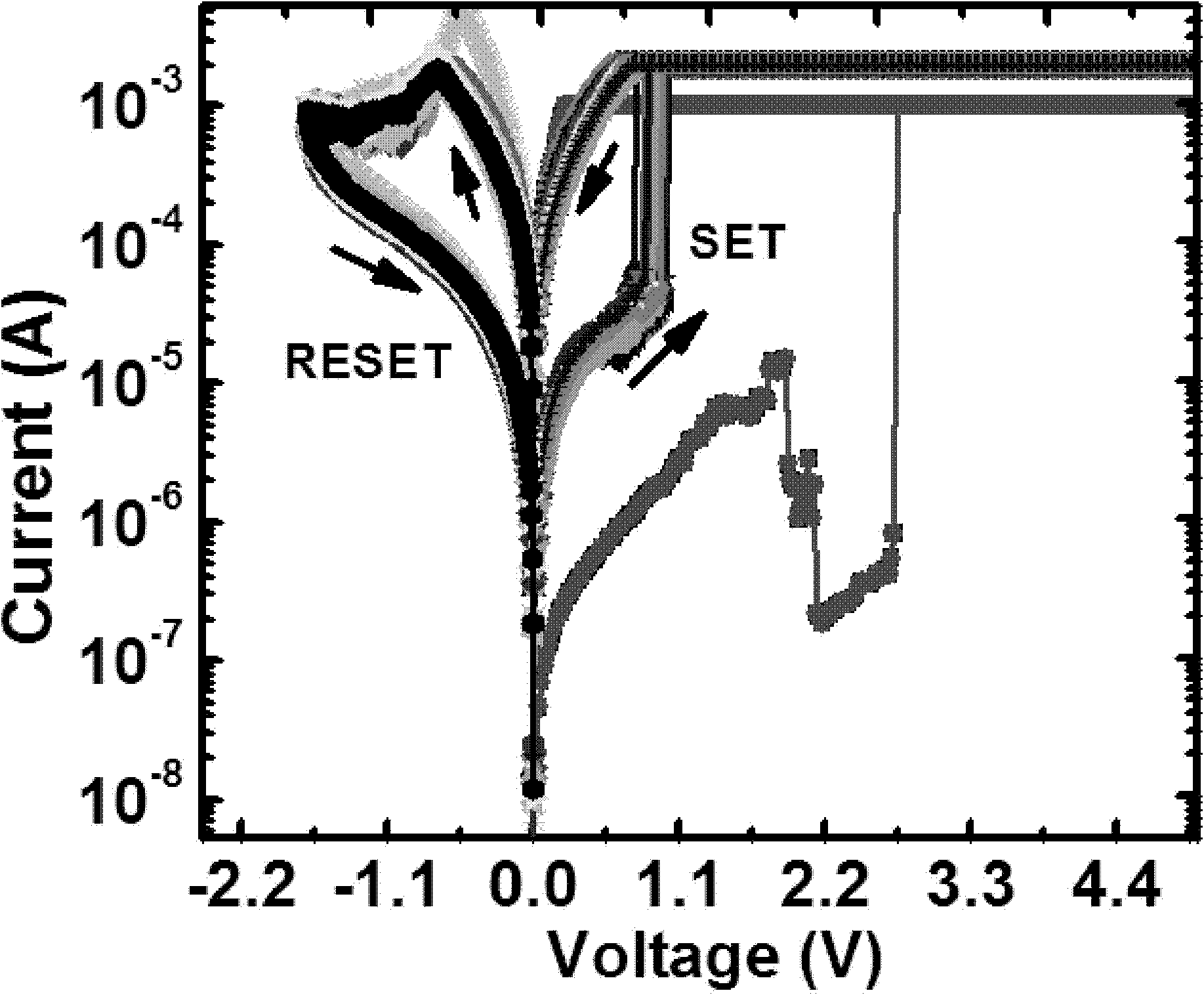

Method for preparing resistive random access memory

InactiveCN102593352AAchieve self-alignmentGuaranteed isolationElectrical apparatusDigital storagePartial oxidationStatic random-access memory

The invention discloses a method for preparing a resistive random access memory. The method comprises the following steps: preparing a bottom electrode on a substrate; then, carrying out partial oxidation on the metal of the bottom electrode so as to form a metal oxide with a thickness of 3-50 nm, and taking the metal oxide as a resistive random material layer; and finally, preparing a top electrode on the resistive random material layer. By using the method disclosed by the invention, a step of depositing a resistive random material layer in the traditional method is avoided, thereby greatly reducing the process complexity; meanwhile, the self-alignment between the resistive random material layer and the bottom electrode can be realized; the complete isolation between devices is ensured; various parasitic effects generated by the traditional process methods are avoided; and the consistency of the actual area and design area of each device is ensured.

Owner:PEKING UNIV

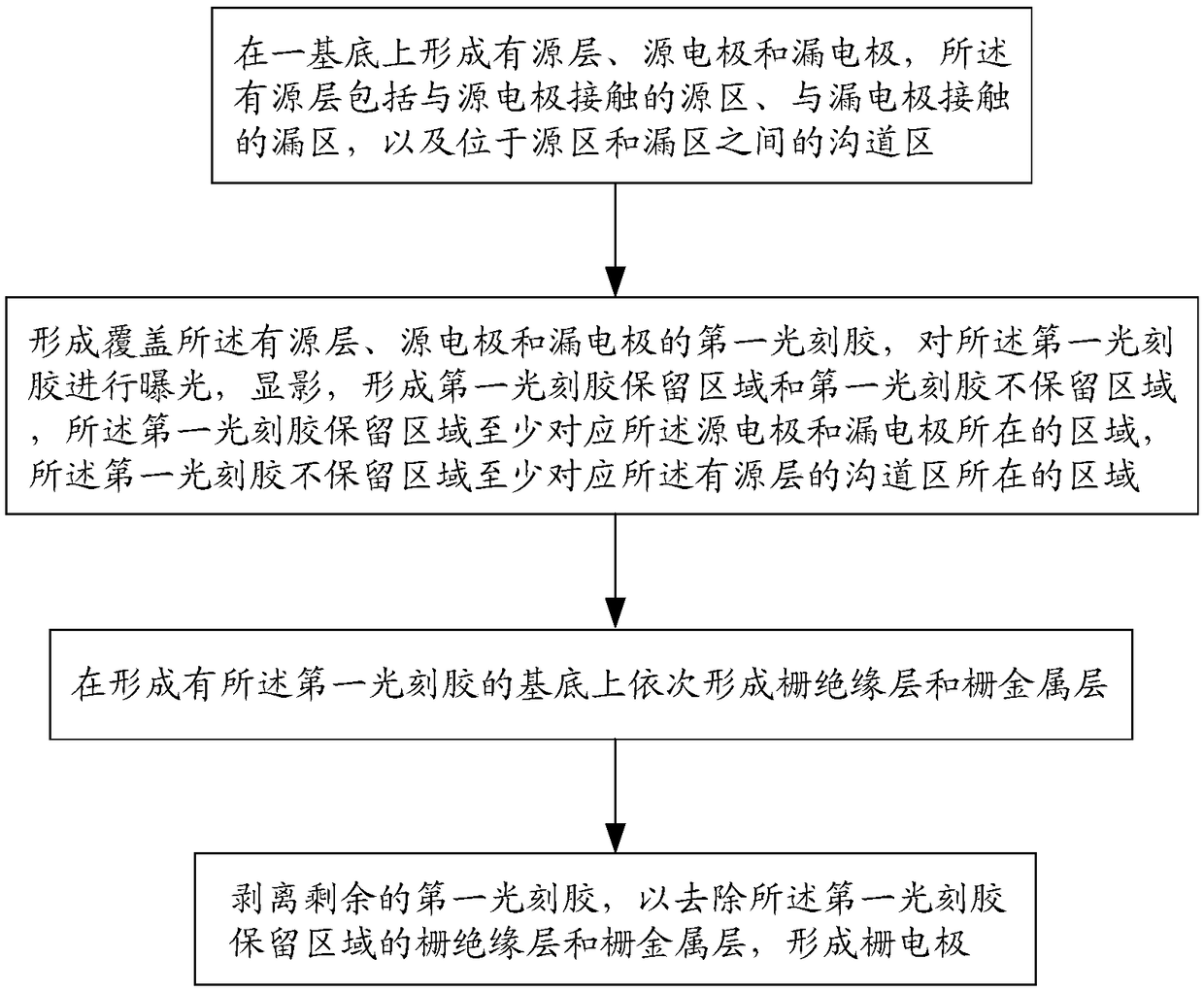

Thin film transistor and manufacturing method thereof, array substrate and display device

ActiveCN108122759AEliminates conductorization processAchieve self-alignmentTransistorSemiconductor/solid-state device manufacturingInsulation layerDisplay device

The invention relates to the technical field of display, and discloses a thin film transistor and a manufacturing method thereof, an array substrate and a display device. The manufacturing method comprises steps: firstly, an active layer, a source electrode and a drain electrode of the thin film transistor are formed; the graph of a first photoresist is then formed, wherein the first photoresist covers the area of the source electrode and the drain electrode, is in position correspondence with the source electrode and the drain electrode and has the consistent graph; and finally, a gate insulation layer and a gate metal layer are sequentially formed on the first photoresist, through a process of stripping the first photoresist, the gate insulation layer and the gate metal layer above the first photoresist are removed, a gate electrode is formed, self alignment between the gate electrode and the source electrode and the drain electrode is realized, contraposition is strict and accurate,parasitic resistance of the device and the total source-drain resistance are reduced, the device performance is improved, and the display quality of a display product is enhanced, and besides, the procedure is saved, time and energy consumption are saved, and the production cost is reduced.

Owner:BOE TECH GRP CO LTD

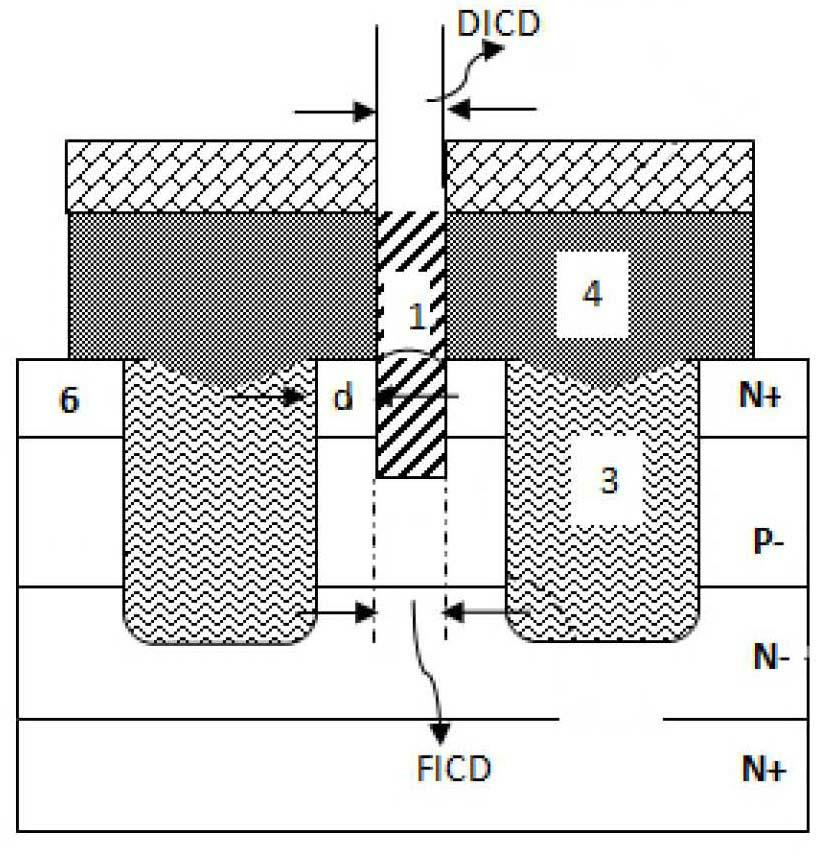

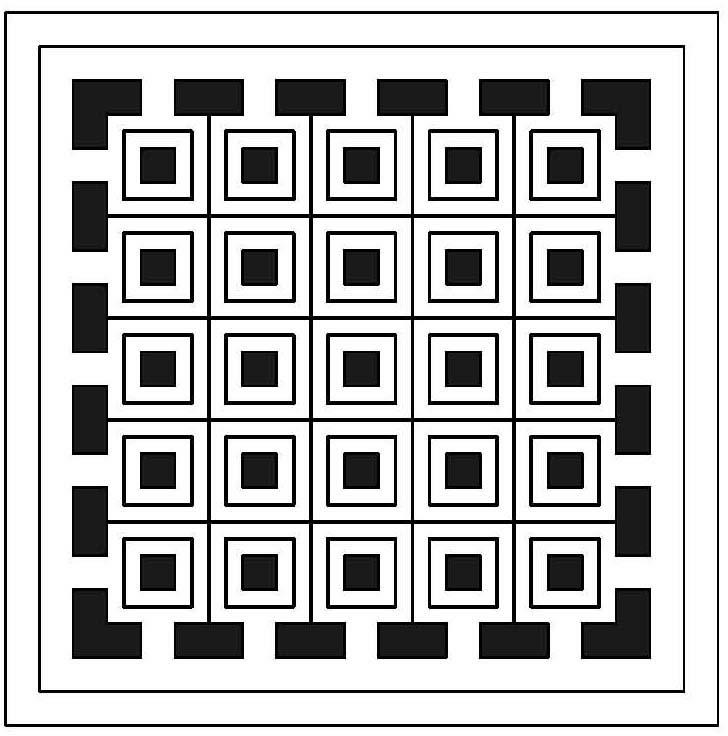

Surface grid-type static induction transistor

InactiveCN104810395AImprove transconductanceReduce parasitic capacitanceTransistorSemiconductor/solid-state device manufacturingParasitic capacitanceVoltage drop

The invention relates to a normally closed surface grid-type static induction transistor (SIT) of low power and a manufacturing method. The transistor is formed by parallelly connecting a drain electrode, a substrate of N+ low resistance monocrystal located on the drain electrode, an N- high resistance epitaxial layer located on the substrate of N+ low resistance monocrystal and multiple mutually parallelly-connected SIT units located in the N- high resistance epitaxial layer, wherein the active region uses the short channel design. The transistor is capable of enabling the impurity concentration of the device grid body to be high and enabling the impurity distribution to be more uniform under the corresponding technology support, reducing the own voltage drop of the grid body, increasing the sensitivity of the grid control, improving the device transconductance, reducing the grid source area, reducing the stray capacitance of the grid source, and increasing the SIT working frequency. Compared with the prior art, the short channel design is completely improved revolutionarily.

Owner:LANZHOU UNIVERSITY

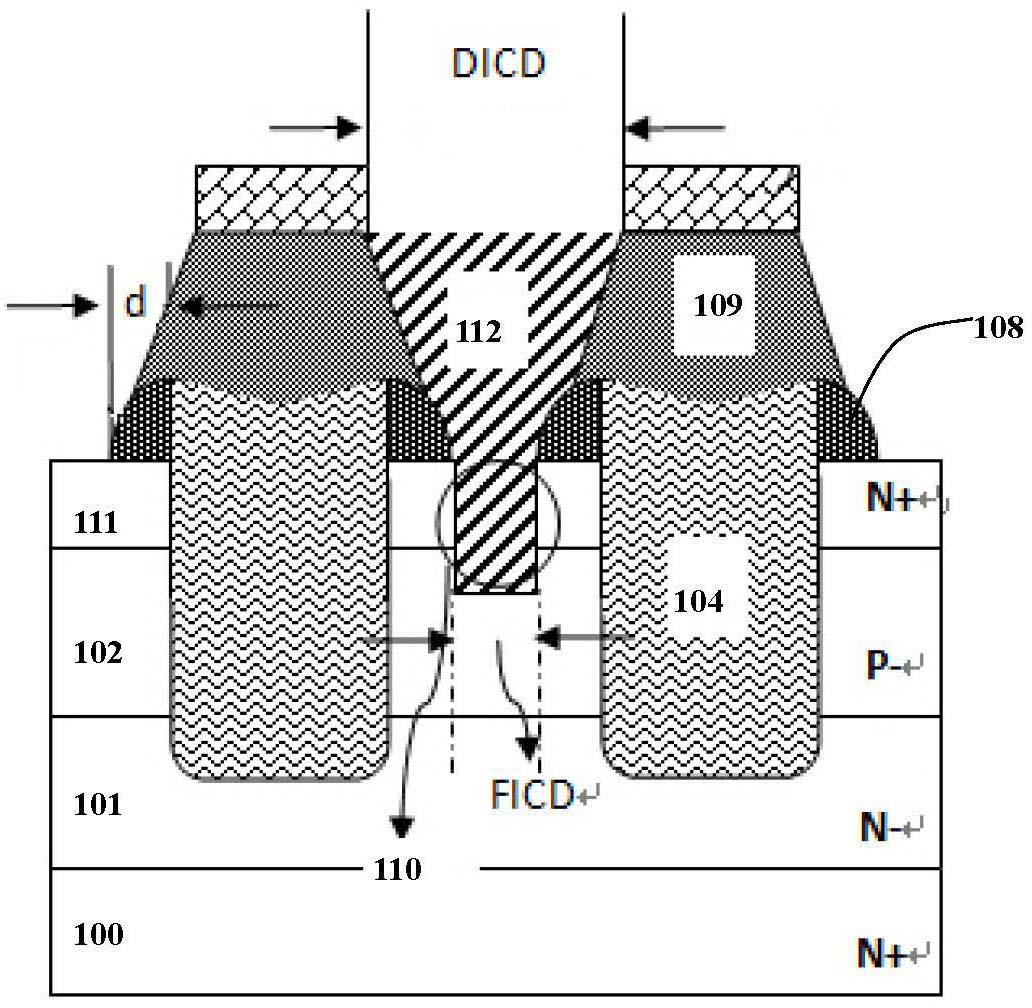

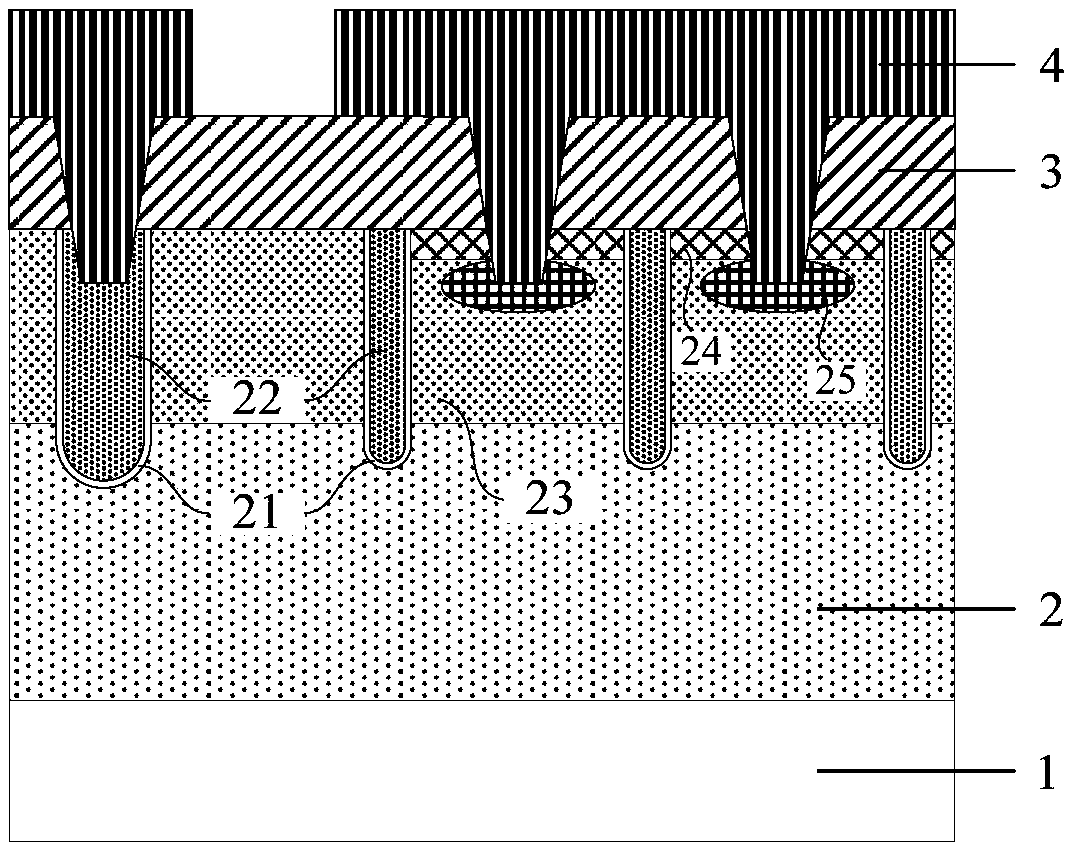

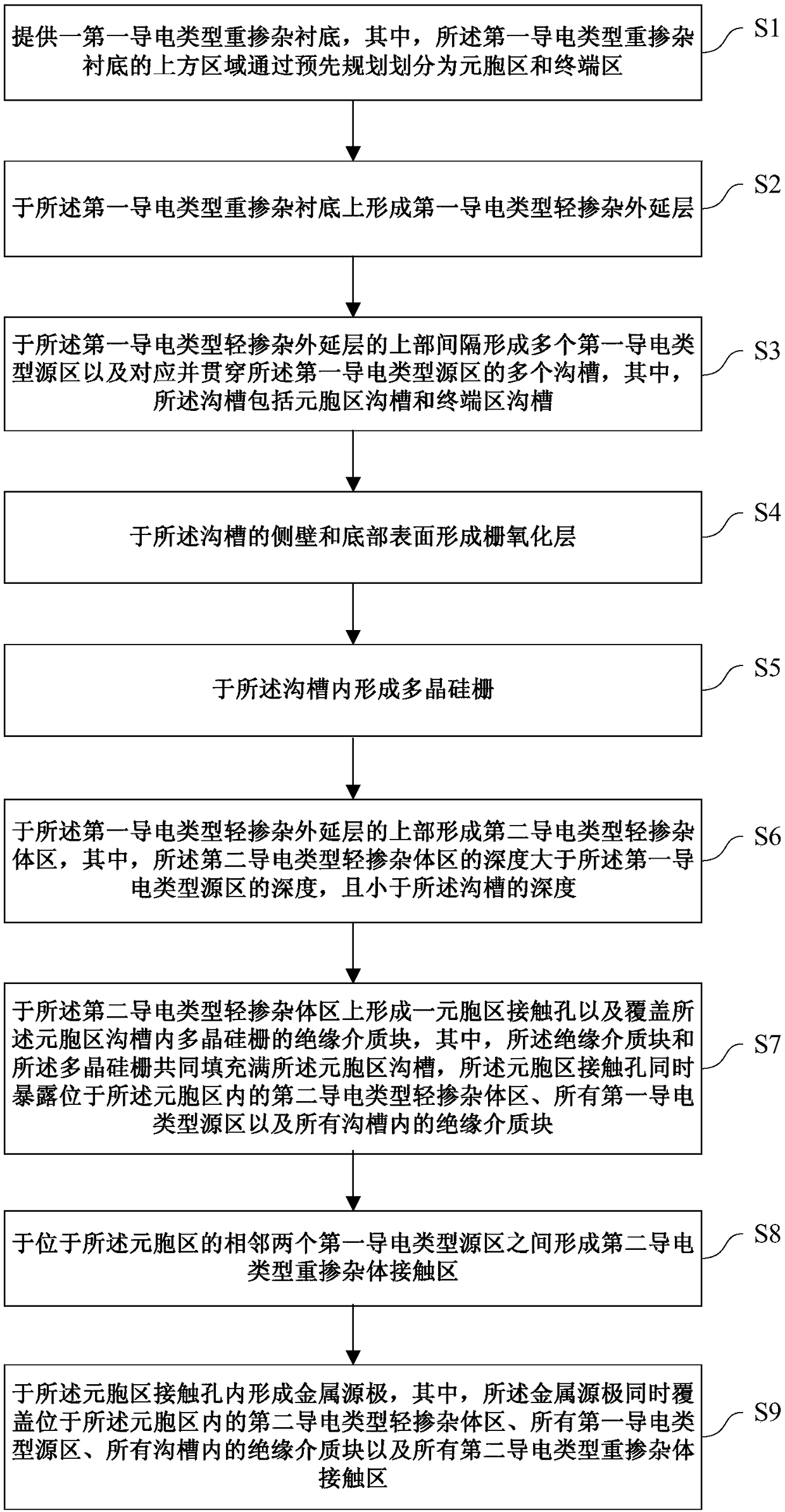

Groove-type MOS device and manufacturing method thereof

ActiveCN108962989AGuaranteed stabilityImprove device densitySemiconductor/solid-state device manufacturingSemiconductor devicesBody regionOxide semiconductor

The invention provides a groove-type MOS (Metal-Oxide-Semiconductor) device and a manufacturing method thereof. The groove-type MOS device at least includes a first conductive heavily doped substrate,a first conductive lightly doped epitaxial layer on the first conductive heavily doped substrate, a plurality of first conductive source regions, a plurality of grooves, a gate oxide layer and a polysilicon gate which are formed in the each groove, a second conductive lightly doped body region formed on the upper portion of the first conductive lightly doped epitaxial layer, a cellular region contact hole formed in the second conductive lightly doped body region, an insulating dielectric block covering the polysilicon gate in the groove of the cellular region, a second conductive heavily doped body contact region formed between two adjacent first conductive source regions of the cellular region, and a metal source electrode formed in the contact hole of the cellular region, wherein the plurality of first conductive source regions and the plurality of grooves are formed on the upper portion of the first conductive lightly doped epitaxial layer at intervals. The groove-type MOS device can guarantee stability of the device while improving the device density and reducing the conduction resistance.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

Method for manufacturing flexible-substrate-based self-encapsulation passive wireless pressure sensor

The invention discloses a method for manufacturing a flexible-substrate-based self-encapsulation passive wireless pressure sensor. The method comprises the following steps of: (10) manufacturing an upper flexible substrate: electroplating an upper metal layer on the lower surface of a flexible substrate, and photoetching the upper metal layer so as to form an upper capacitance pole plate and a planar inductance coil; (20) manufacturing a middle flexible substrate: boring a flexible substrate so as to form cavities and electrical through holes; (30) manufacturing a lower flexible substrate: electroplating a lower metal layer on the upper surface of a flexible substrate, and photoetching the lower metal layer so as to form a lower capacitance pole plate and a lower connecting wire; (40) manufacturing connecting wires: coating the electrical through holes with a conductive adhesive so as to form the connecting wires; and (50) manufacturing the pressure sensor: laminating the upper flexible substrate, the middle flexible substrate and the lower flexible substrate so as to form an oscillation circuit, thereby manufacturing the passive wireless pressure sensor. The method has the advantages that the self alignment of the substrates can be realized, the self encapsulation of the sensor can be realized, the process is simple, and the consistency and reliability are high.

Owner:SOUTHEAST UNIV

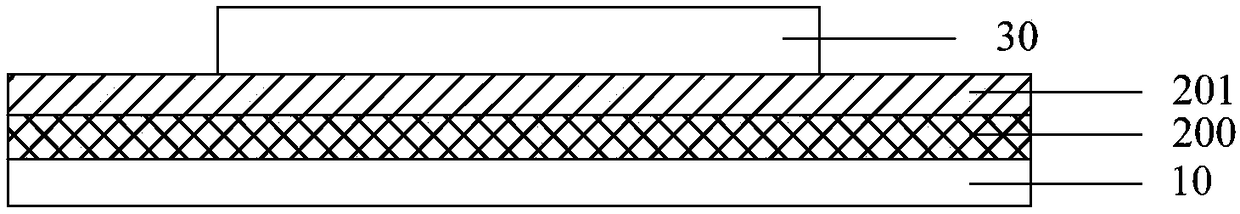

Method for lowering contact resistance of two-dimensional material field effect transistor

InactiveCN107919388AAchieve self-alignmentReduce overlap areaSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerField-effect transistor

The invention relates to a method for lowering contact resistance of a two-dimensional material field effect transistor. The method comprises the following steps of enabling at least one transitionalmetal region to be evaporated on the partial surface of a substrate to form a transitional metal layer, wherein the transitional metal region is 0.1-2nm in thickness; performing photoetching and developing to form a photoresist layer, wherein at least two holes for evaporating source and drain electrodes are formed in the photoresist layer, the downward side of each hole is just aligned to the partial transitional metal layer and the partial substrate surface, and each hole is positioned in one side of the transitional metal region separately; enabling the source and drain electrodes to be evaporated in the holes, and next, removing the photoresist layer to expose the other part of the substrate; and adopting a sulphur source to perform sulfuration on the transitional metal, or adopting aselenium source to perform selenylation of the transitional metal, and then performing cooling to form the two-dimensional material field effect transistor on the surface of the substrate. By adoptingthe source and drain electrodes as a protection isolation layer, a two-dimensional material channel is formed between the source and drain electrodes, so that the overlapped area between the channeland the source and drain electrodes is reduced, thereby lowering the contact resistance between the two parties.

Owner:SUZHOU UNIV

Gallium nitride transistor with self-aligned source and drain electrodes and preparation method of gallium nitride transistor

PendingCN111834454AReduce power lossImprove frequency characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesAccess resistanceEngineering

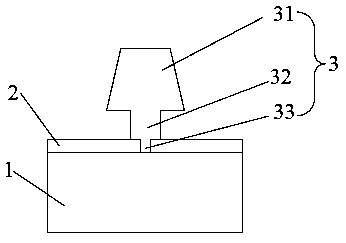

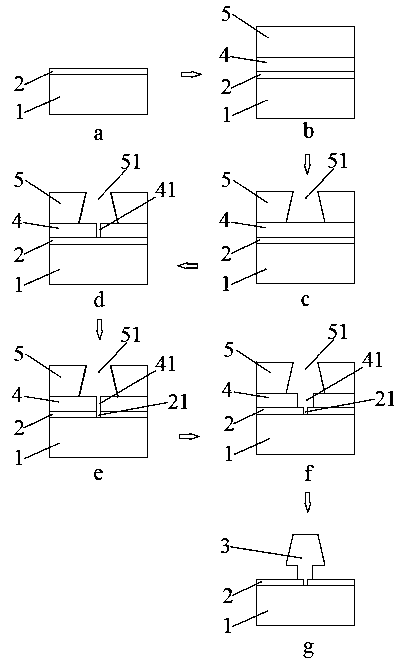

The invention relates to a gallium nitride transistor with self-aligned source and drain electrodes and a preparation method of the gallium nitride transistor. The gallium nitride transistor with theself-aligned source and drain electrodes comprises a substrate, a composite buffer region, a channel layer, a composite barrier region, a source electrode, a drain electrode and a grid electrode, wherein the grid electrode comprises a grid pin and a grid head, and the width of the grid head is greater than that of the grid pin; the side surface, which is close to the grid electrode, of the sourceelectrode and the first side surface of the grid head are in the same vertical plane; the side surface, which is close to the grid electrode, of the drain electrode and the second side surface of thegrid head are in the same vertical plane. According to the gallium nitride transistor with the self-aligned source and drain electrodes, through self-alignment of the source electrode, the drain electrode and the grid electrode, a source-drain interval similar to the width size of the grid head is realized, the source-drain interval is reduced to the greatest extent, and the source electrode access resistance and the drain electrode access resistance of the transistor are reduced, so that the power loss of the transistor is reduced, and the frequency characteristic of the transistor is improved.

Owner:XIDIAN UNIV

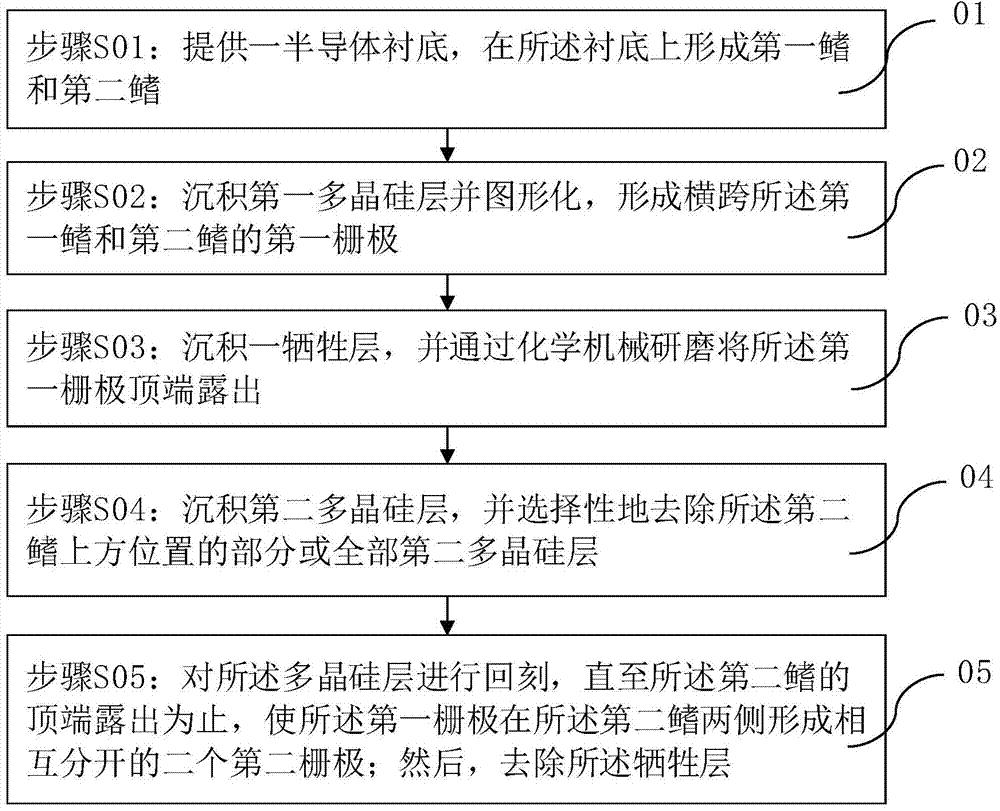

Method for manufacturing fin field effect transistor (FET)

InactiveCN104716046AAvoid damageAccurate control of etching precisionSemiconductor/solid-state device manufacturingEngineeringHeight difference

The invention discloses a method for manufacturing a fin field effect transistor (FET). Polycrystalline silicon layers are deposited on two fin structures of the FinFET twice, a height difference is correspondingly formed above the two fin structures, polycrystalline silicon is etched back by means of the height difference, a gate of one fin structure is divided to form two gates for further formation of a 4T-FinFET, the 4T-FinFET and a 3T-FinFET can be integrated to be manufactured, etching precision can be accurately controlled, damage to a device structure is avoided, and self-alignment is achieved during manufacturing.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

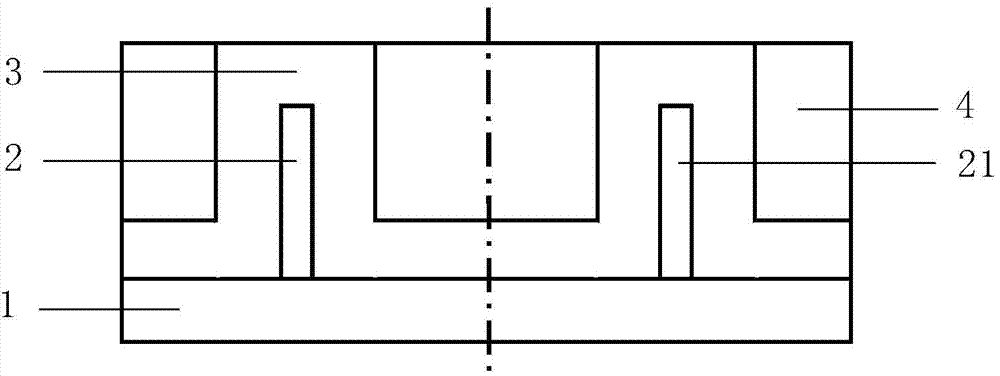

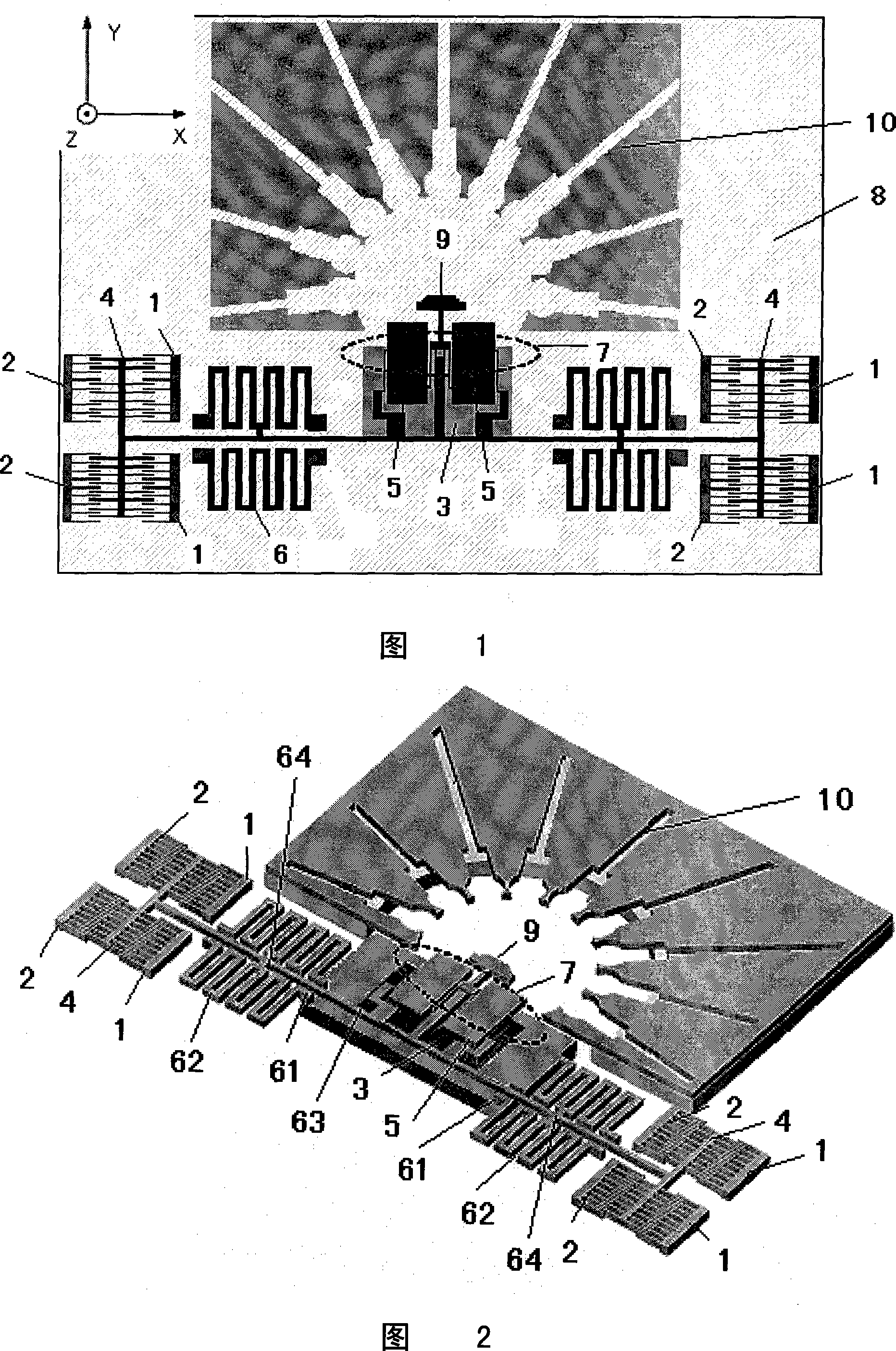

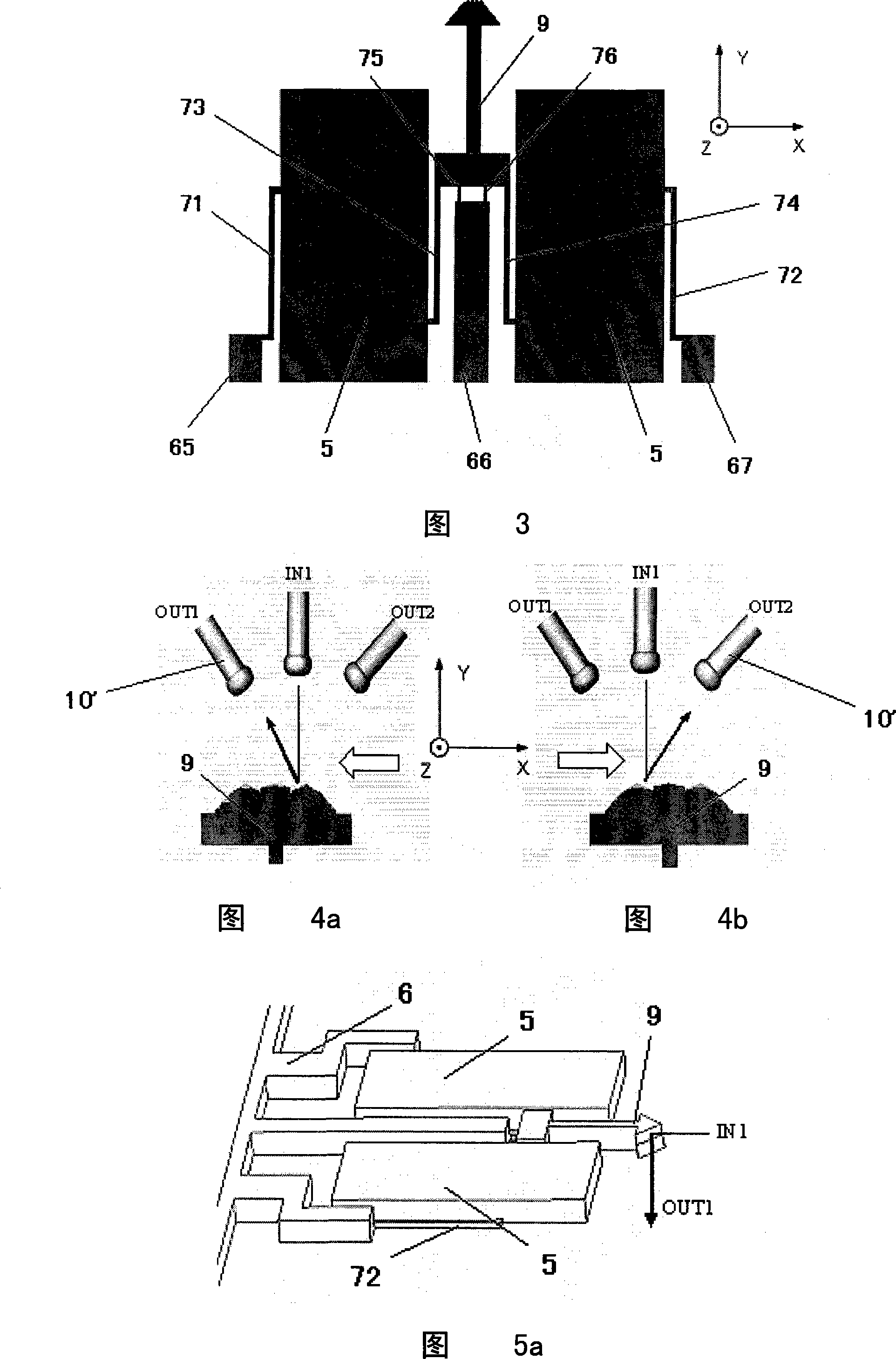

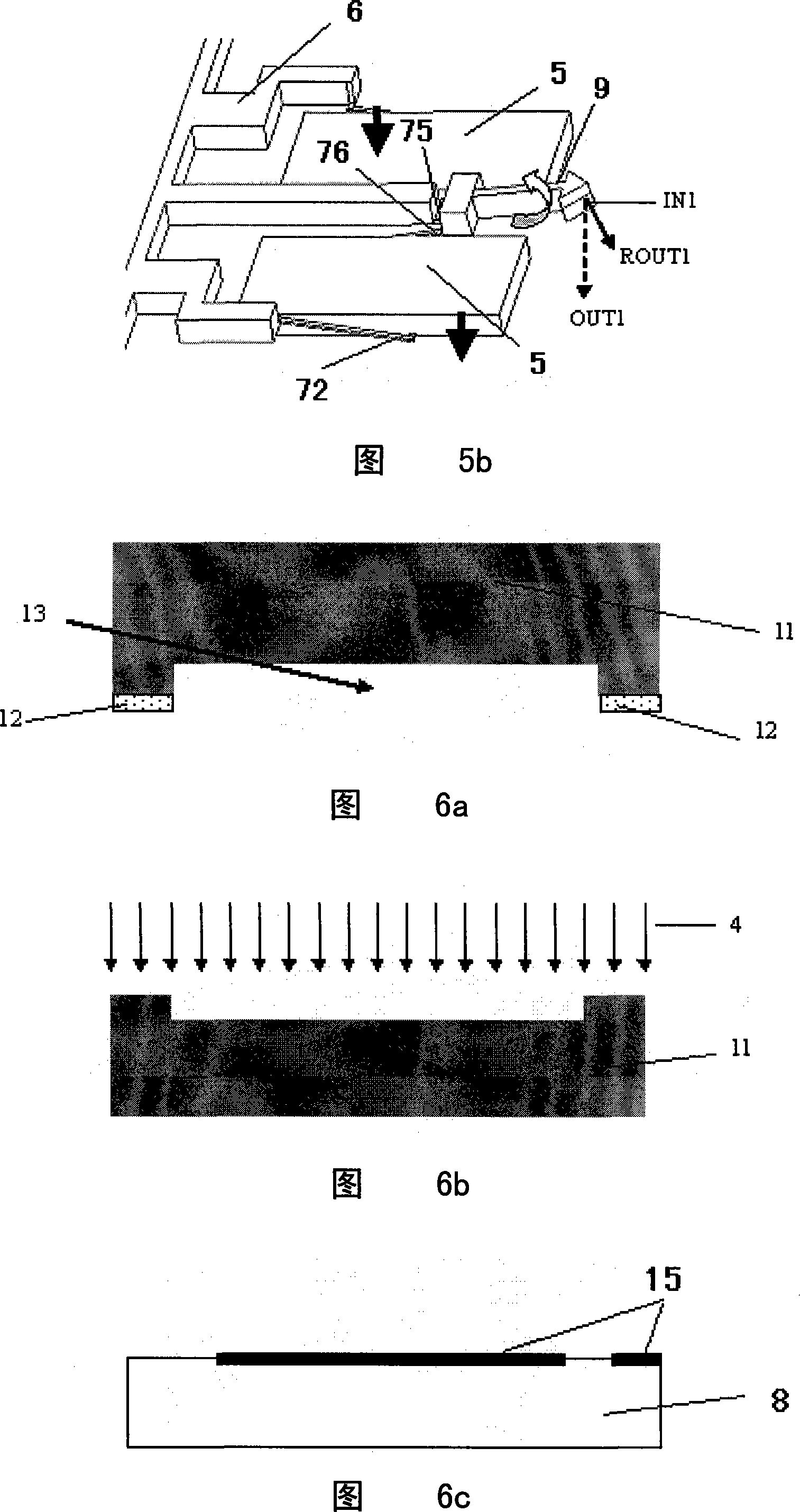

Minitype optical device and method for producing the same

ActiveCN101246259ASelf-aligningImprove controllabilityDecorative surface effectsPhotomechanical apparatusFiberComputer module

The invention relates to a micro type optics apparatus and the preparing process thereof, which is characterized in that: the apparatus includes fixed electrode, moveable electrode, supporting beam, glass substrate, light reflecting module and fiber fixed module; the fixed electrode includes the comb type fixed electrode connected to the double sides of the top surface of the glass substrate and the flat type fixed electrode fixed to the middle part of the glass substrate top surface; the moveable electrodes are two comb type moveable electrodes inserted equipped between the comb type fixed electrodes and two flat type movable electrodes equipped above the flat type fixed electrode; the supporting beam includes folding beam and combined torsion beam, the light reflecting module is the center above the fiber fixed module which is equipped with several fiber grooves in radiation type, and every fiber groove is separately focused to one of many light reflecting surfaces above the light reflecting module. The invention is easy to prepare, and is compatible with many kinds of types of MEMS components processes, which can be used for realizing more powerful micro optical integrated system.

Owner:PEKING UNIV