Gallium nitride transistor with self-aligned source and drain electrodes and preparation method of gallium nitride transistor

A source-drain electrode, gallium nitride technology, used in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as high manufacturing cost, increase, and limit device operating frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

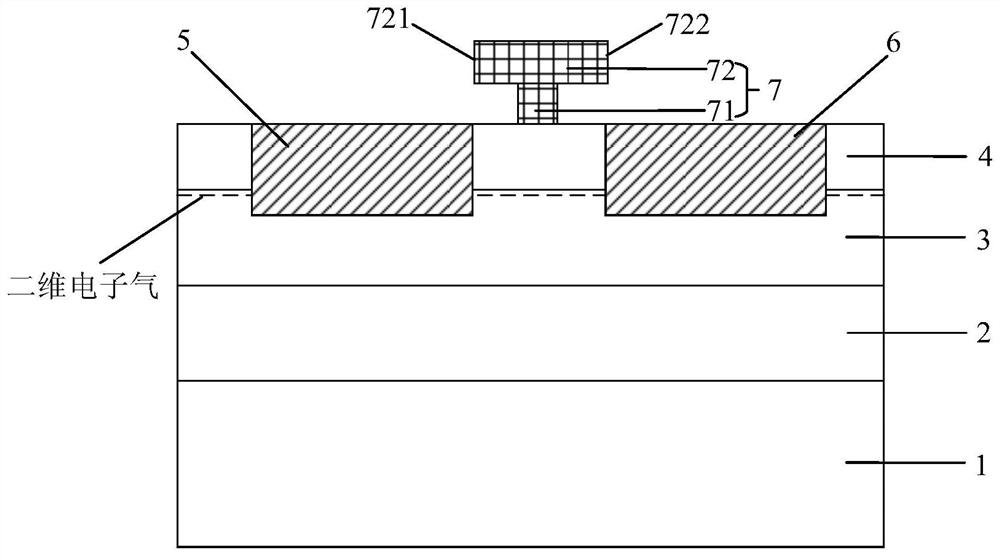

[0048] Please refer to figure 1 , figure 1 It is a structural schematic diagram of a gallium nitride transistor with self-aligned source-drain electrodes provided by an embodiment of the present invention. As shown in the figure, the gallium nitride transistor with self-aligned source-drain electrodes in this embodiment includes:

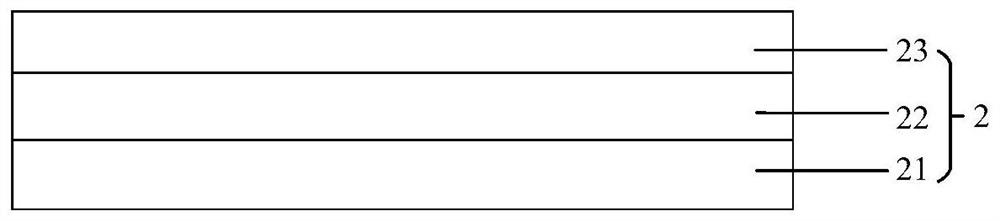

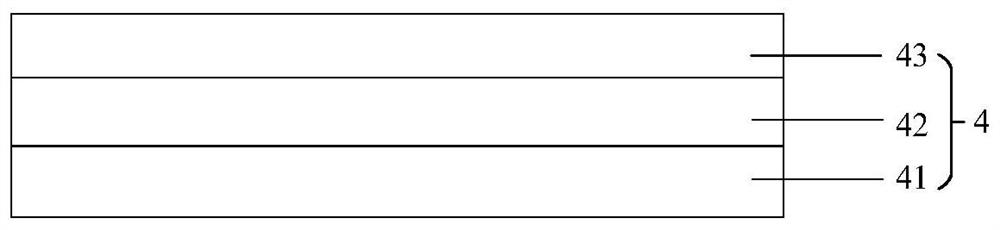

[0049] A substrate 1, a compound buffer zone 2, a channel layer 3 and a compound barrier region 4 are sequentially arranged from bottom to top, and there is a two-dimensional electron gas channel between the channel layer 3 and the compound barrier region 4;

[0050] The source electrode 5 is arranged inside the composite barrier region 4 and the channel layer 3;

[0051] The drain 6 is arranged inside the composite barrier region 4 and the channel layer 3, and is arranged at intervals from the source 5;

[0052] The gate 7 is arranged on the composite barrier region 4 and is located between the source 5 and the drain 6. The gate 7 includes a gate ...

Embodiment 2

[0077] See Figure 4 , Figure 4 It is a schematic flow chart of a method for preparing a gallium nitride transistor with self-aligned source-drain electrodes provided by an embodiment of the present invention. As shown in the figure, the method includes:

[0078] S100: continuously growing a compound buffer zone, a channel layer and a compound barrier region on the surface of the substrate;

[0079] Wherein, the composite buffer zone includes a nucleation layer, a transition layer and a buffer layer stacked in sequence, and the composite barrier region includes an isolation layer, a core barrier layer and a cap layer stacked in sequence.

[0080] S200: preparing a gate on the composite barrier region;

[0081] Wherein, the gate includes a grid foot and a grid head, the grid foot is located on the composite barrier region, the grid head is located on the grid foot, and the width of the grid head is greater than the width of the grid foot .

[0082] S300: Using the gate hea...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More