Self-aligning wafer or chip structure and self-aligning stacking structure and manufacturing method thereof

A technology of chip structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve time-consuming and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

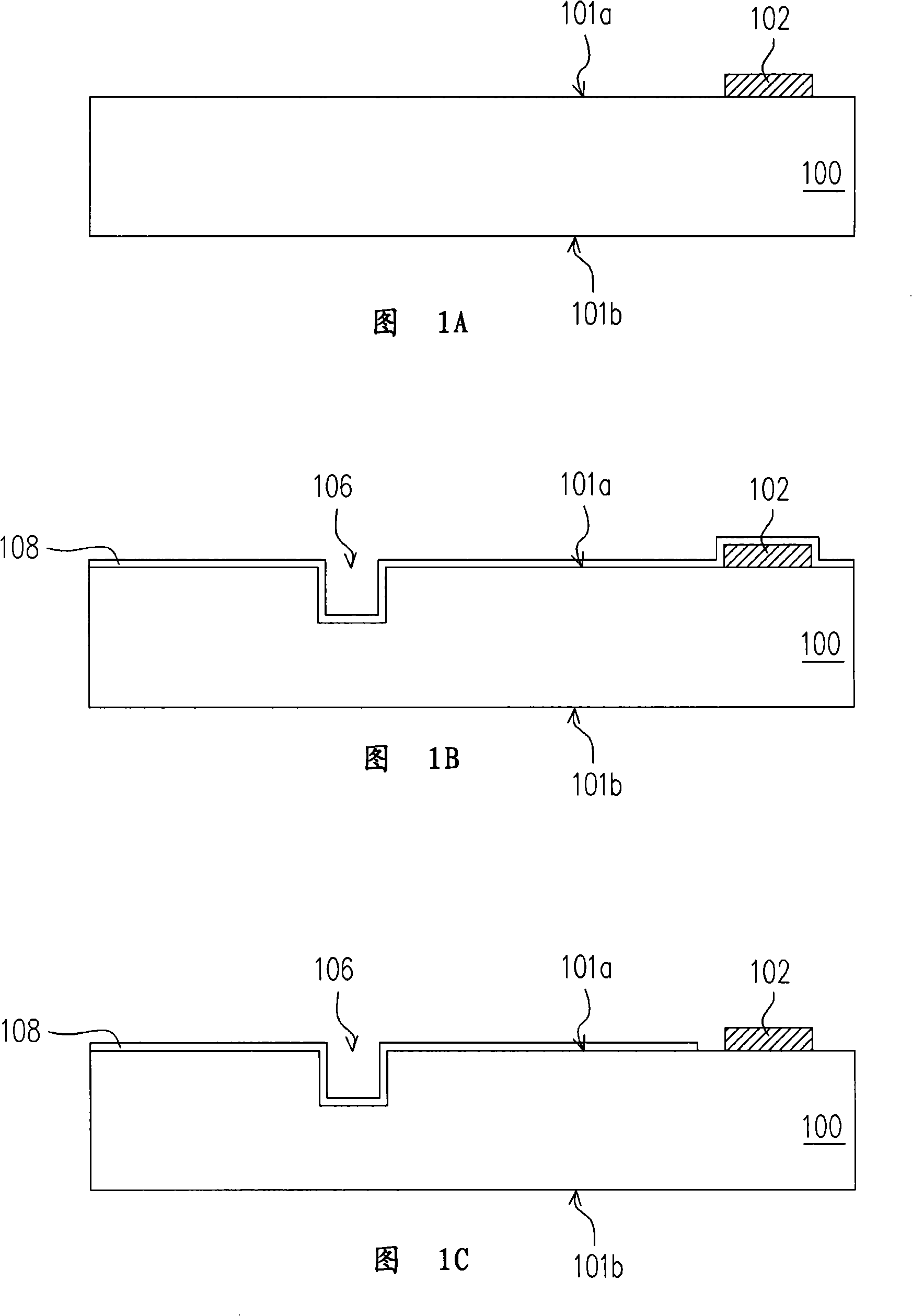

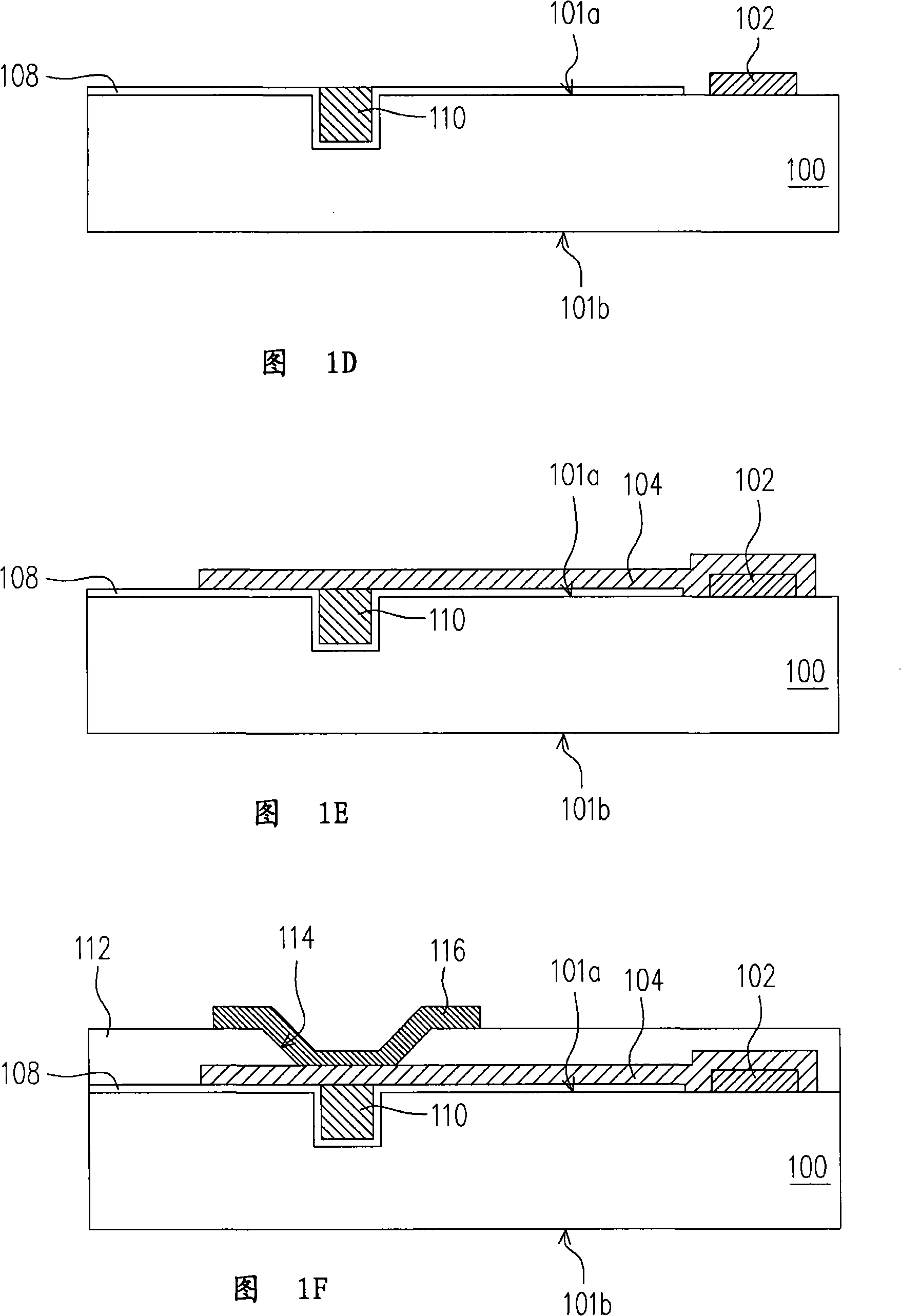

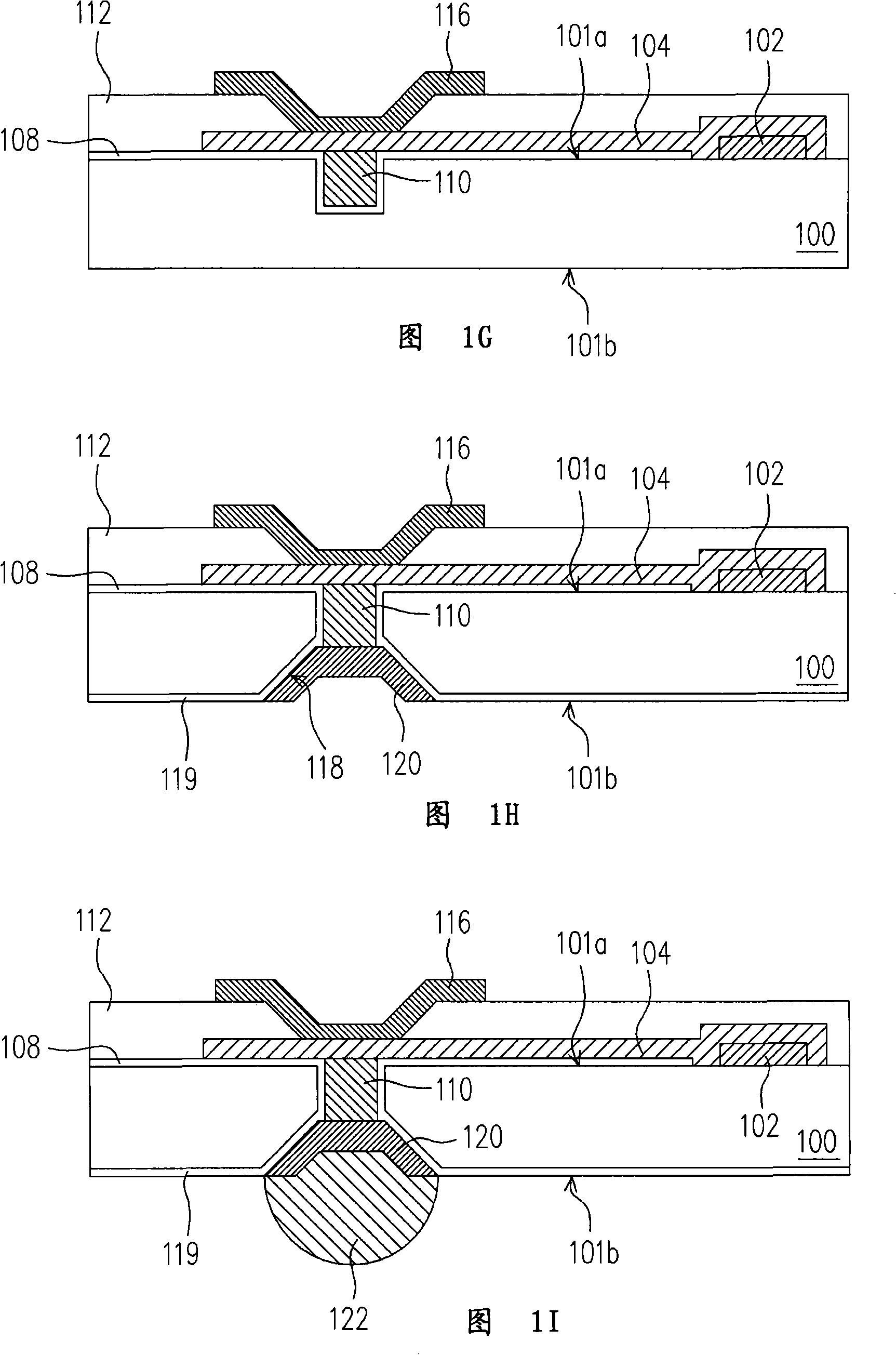

[0052] 1A to 1I are schematic cross-sectional views of a fabrication process of a self-aligned wafer or chip structure according to an embodiment of the present invention. Referring to FIG. 1A , firstly, a substrate 100 is provided, which has a first surface 101a and a second surface 101b. The substrate 100 is, for example, a wafer or a chip, and a plurality of elements and interconnection structures (not shown) have been formed in the substrate 100 . In particular, at least one solder pad 102 has been formed on the first surface 100 of the substrate 100 . The bonding pad 102 is electrically connected to the components and interconnection structures in the substrate 100 . The material of the pad 102 is, for example, metal. The bonding pad 102 is fabricated by using known deposition, photolithography and etching techniques, for example. In this embodiment, the bonding pad 102 is a bonding pad located at the center of the wafer or chip.

[0053] Next, please refer to FIG. 1B...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More