TSV (through silicon via) back side hole leaking technology without CMP (chemical mechanical grinding) technology

A technology for through silicon vias and processes, applied in the field of through-silicon via backside leakage process solutions, can solve the problems of complex process, high cost, low production capacity, etc., and achieve the effects of avoiding CMP process, improving output efficiency and reducing process cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described below in conjunction with specific drawings and embodiments.

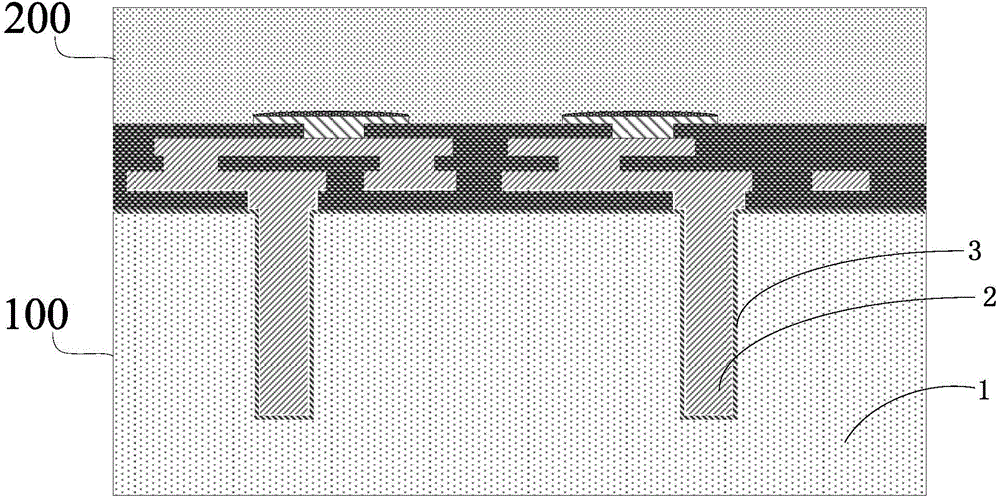

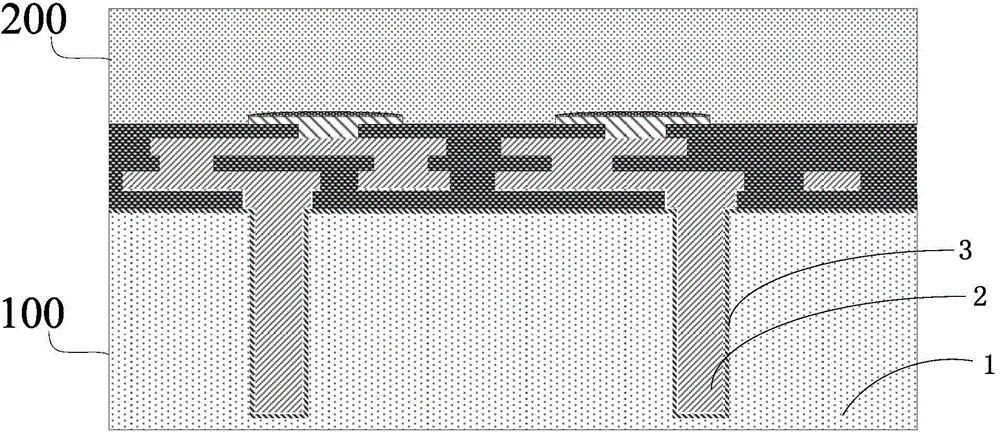

[0028] The TSV back leakage process scheme proposed in this embodiment without CMP process includes the following steps:

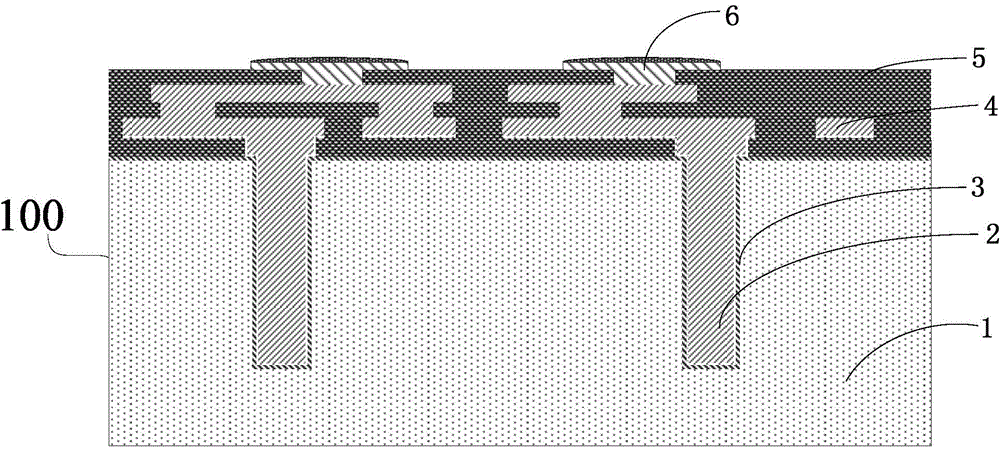

[0029] S1. Provide a device wafer 100 that has completed the front process; figure 1 As shown, the device wafer 100 has completed the fabrication of the front structure according to the existing conventional process; the device wafer 100 includes a substrate 1, a TSV blind hole 2 in the substrate 1, an insulating layer and a seed on the wall of the TSV blind hole 2 layer (the two layers are marked with a mark 3), the front RDL layer 4, the front dielectric layer 6 and the connection bump 6 connecting the front RDL layer, etc.; the TSV blind hole 2 is filled with conductive metal, such as copper.

[0030] The substrate 1 is a silicon substrate. The TSV hole is a through-silicon hole. In step S1, since the TSV hole has not realized the expo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More