Self-aligned two-dimensional crystal material field-effect semiconductor device and preparation method thereof

A two-dimensional crystal and self-alignment technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve the problems of low switching and difficult application of integrated circuits, so as to reduce covering capacitance, reduce parasitic resistance, and avoid The effect of destruction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

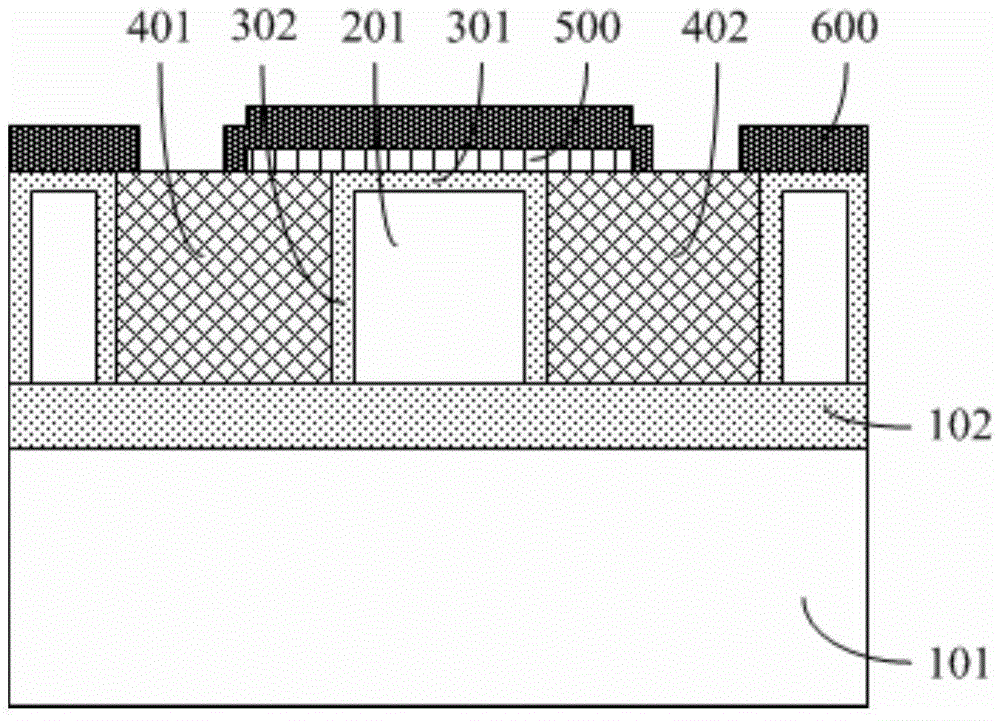

[0084] The method for preparing a self-aligned two-dimensional crystal material field-effect semiconductor device of the present invention comprises the following steps:

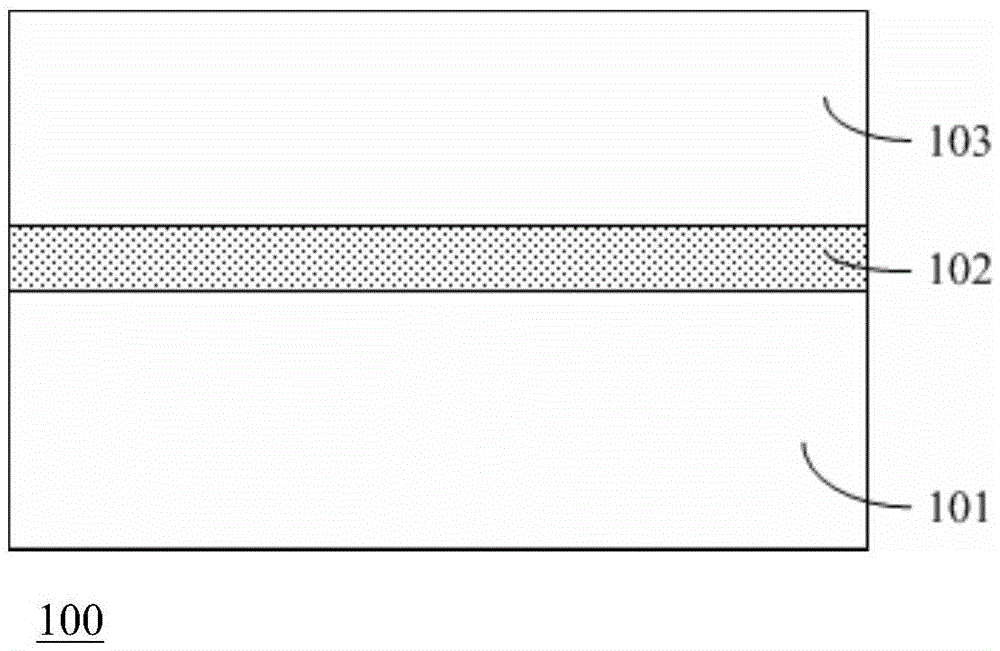

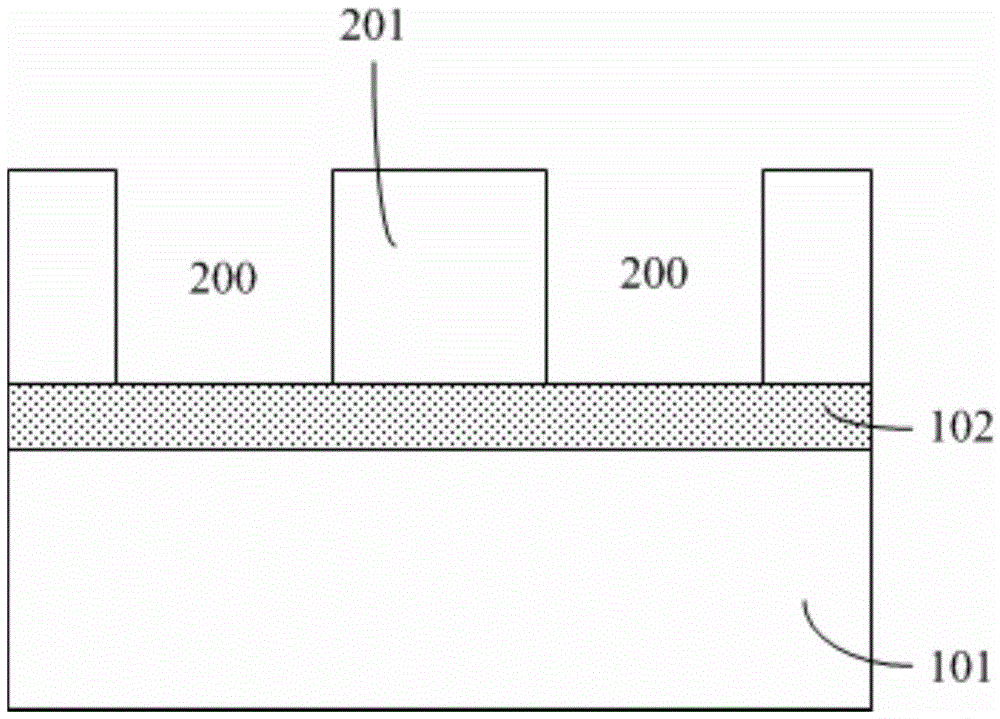

[0085] (1) Select a silicon (SOI) wafer on an insulating substrate as the base, select a suitable mask as a mask, etch the top silicon of the SOI until the buried oxide layer in the SOI is exposed, and the rest after etching The silicon on top of the SOI is the gate electrode of the device.

[0086] (2) Form a layer of good-quality silicon dioxide dielectric on the upper surface and side surfaces of the silicon gate electrode on the top layer of SOI.

[0087] (3) Depositing metal on the surface of the SOI substrate, the thickness of the metal layer is greater than the depth of the existing grooves on the surface of the SOI substrate.

[0088] (4) The metal layer is planarized by using a planarization process, and the process is controlled so that the silicon dioxide on the upper surface of the silicon gate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More