Method for forming gate structure of NAND memory, NAND memory and photomask

A gate structure and memory technology, applied in the field of NAND memory and photomask mask, can solve the problem of load effect weakening the influence of registration deviation between layers and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The technical solutions in the present invention will be clearly and completely described below in conjunction with the accompanying drawings. Apparently, the described embodiments are part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

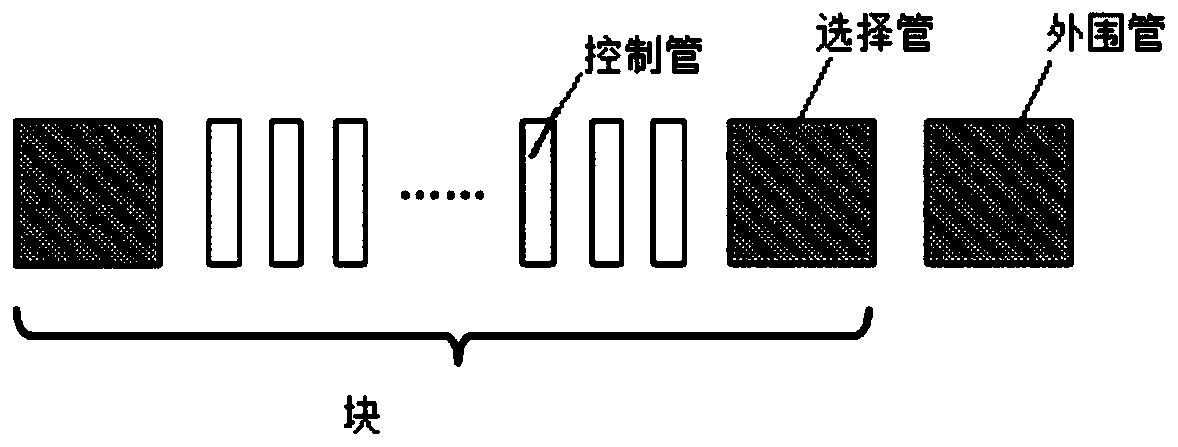

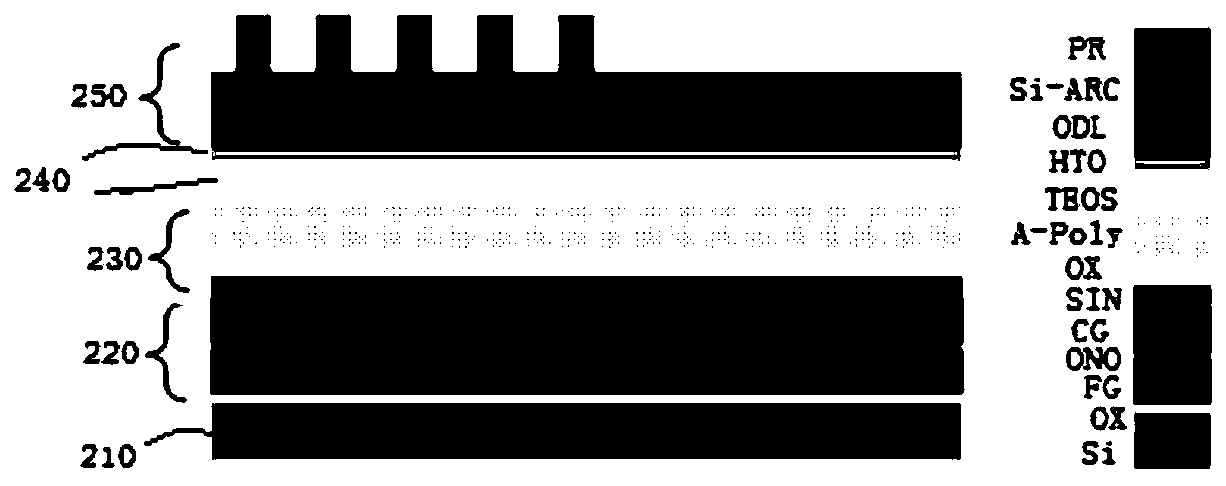

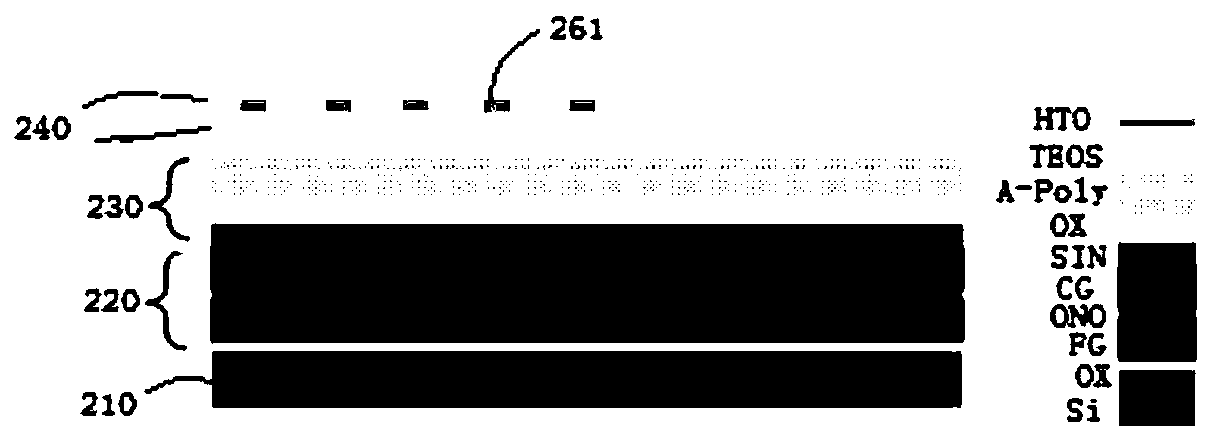

[0036] Specifically, see Figures 2a-2g , Figures 2a-2g It is a schematic diagram of the manufacturing process of the prior art NAND memory, such as Figures 2a-2g Shown, the manufacturing process of the NAND memory of prior art comprises:

[0037] S1: Provide a substrate 210, on which a gate structure layer 220, a pattern transfer layer 230, a mandrel pattern layer 240, and an organic dielectric Tri-Layer layer 250 are sequentially formed, such as Figure 2a shown;

[0038] S2: to Figure 3a The photomask s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More