Patents

Literature

188results about How to "Improve the layout density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

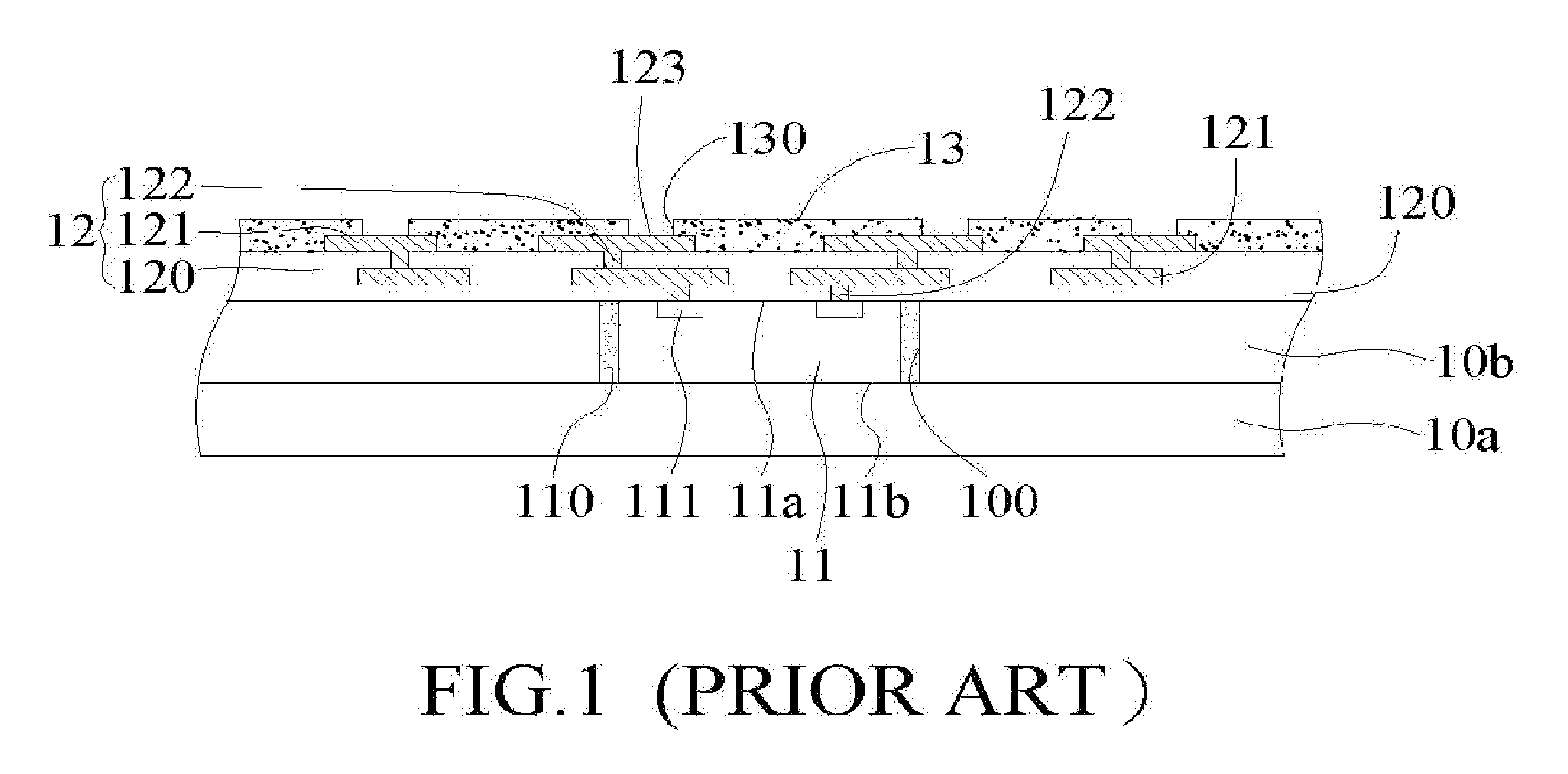

Semiconductor package substrate

ActiveUS7705456B2High bonding strengthImprove the layout densitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

Owner:PHOENIX PRECISION TECH CORP

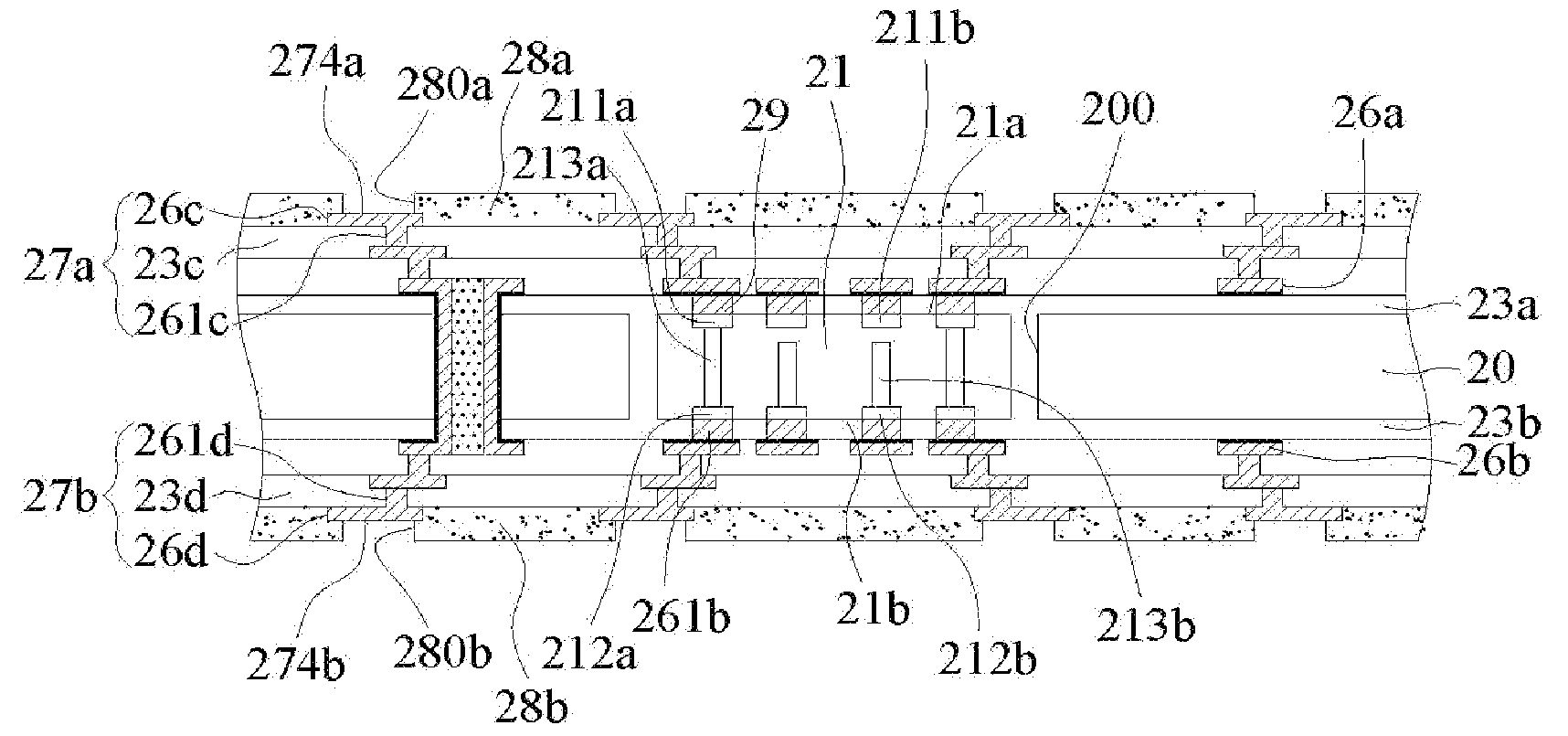

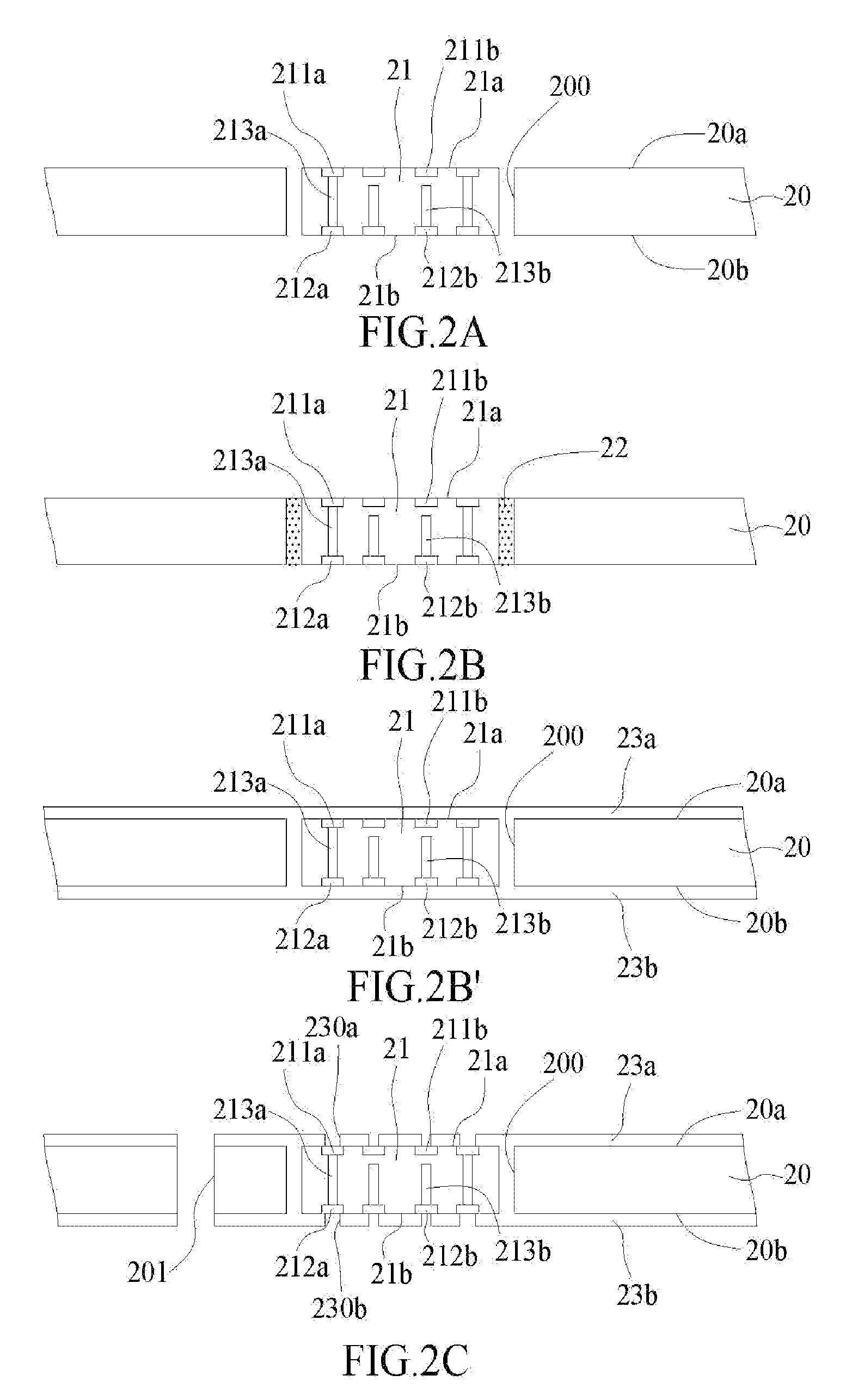

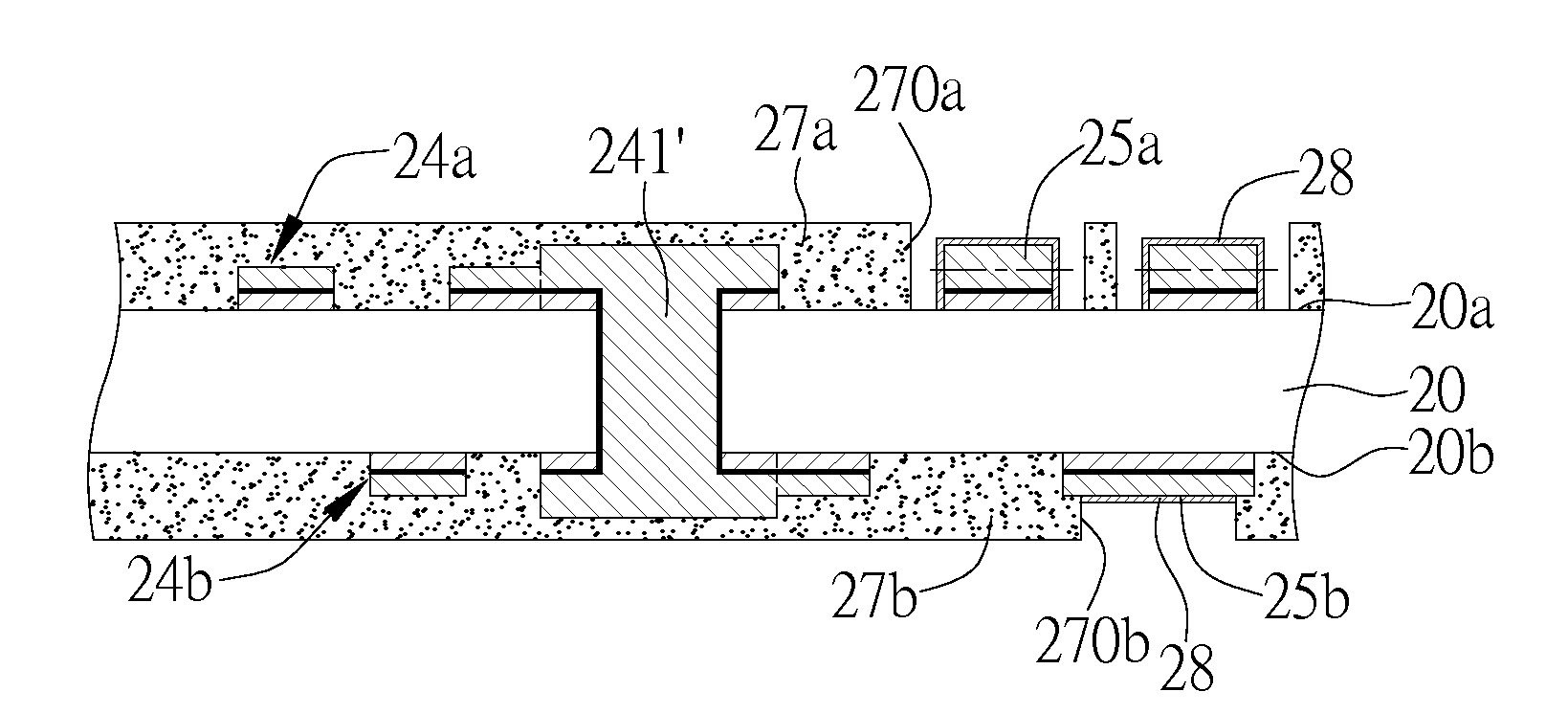

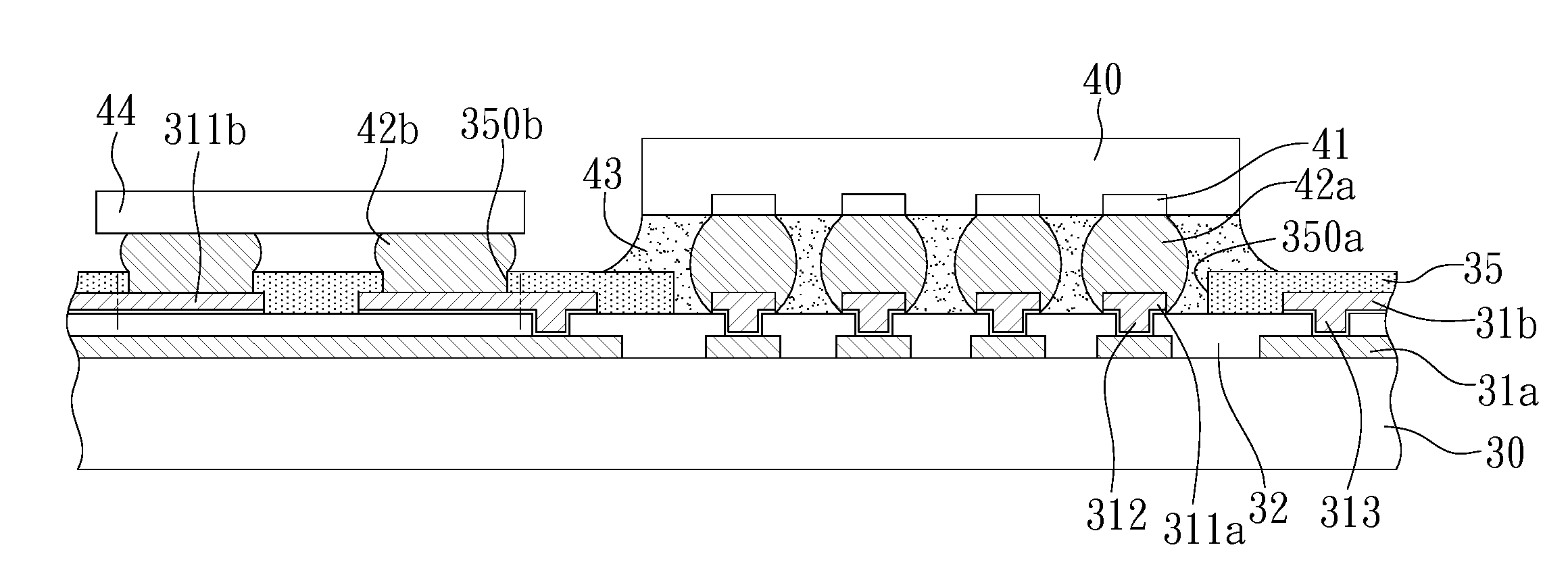

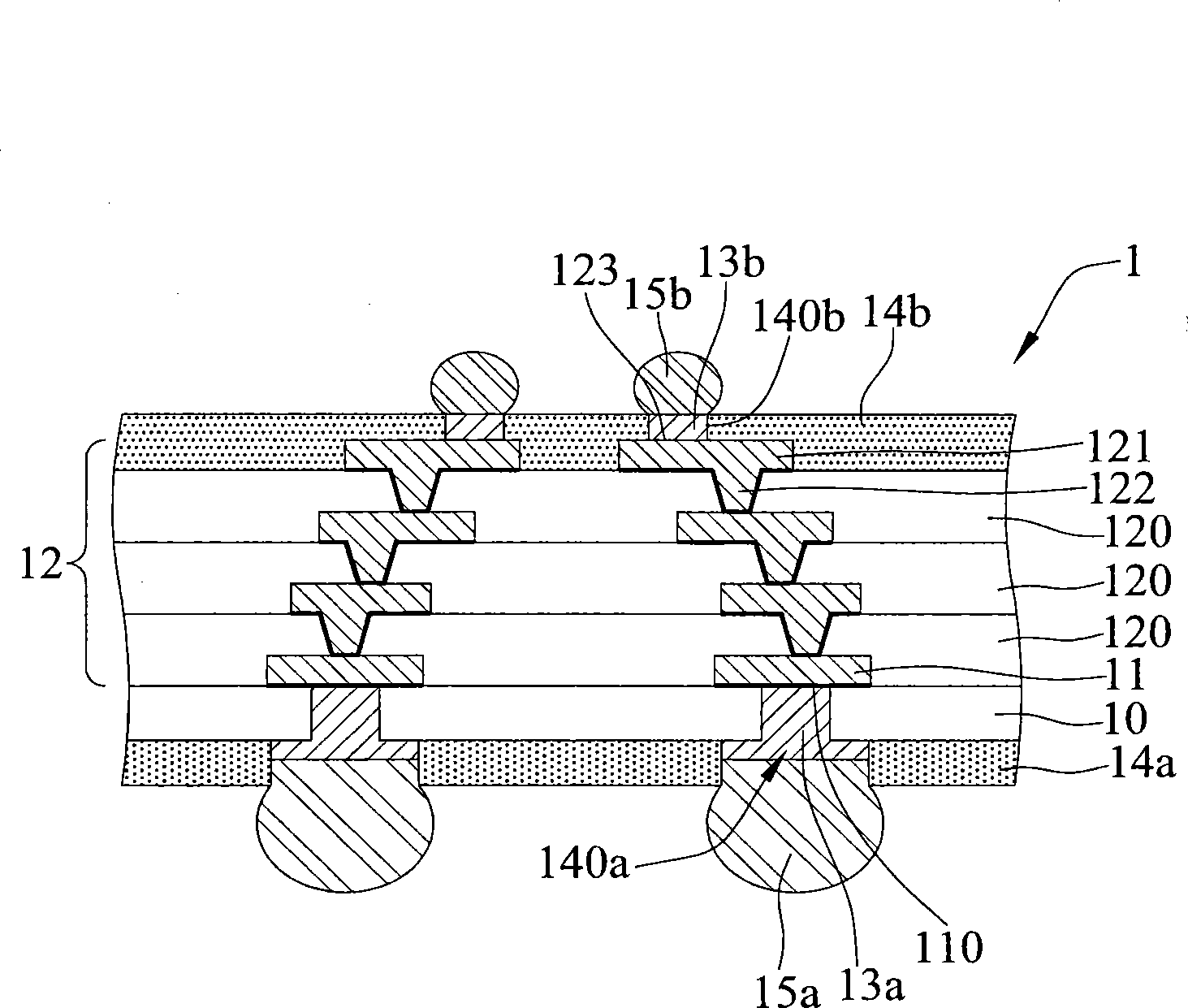

Package structure

ActiveUS20100032827A1Improve electrical performanceIncrease wiring layout densitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

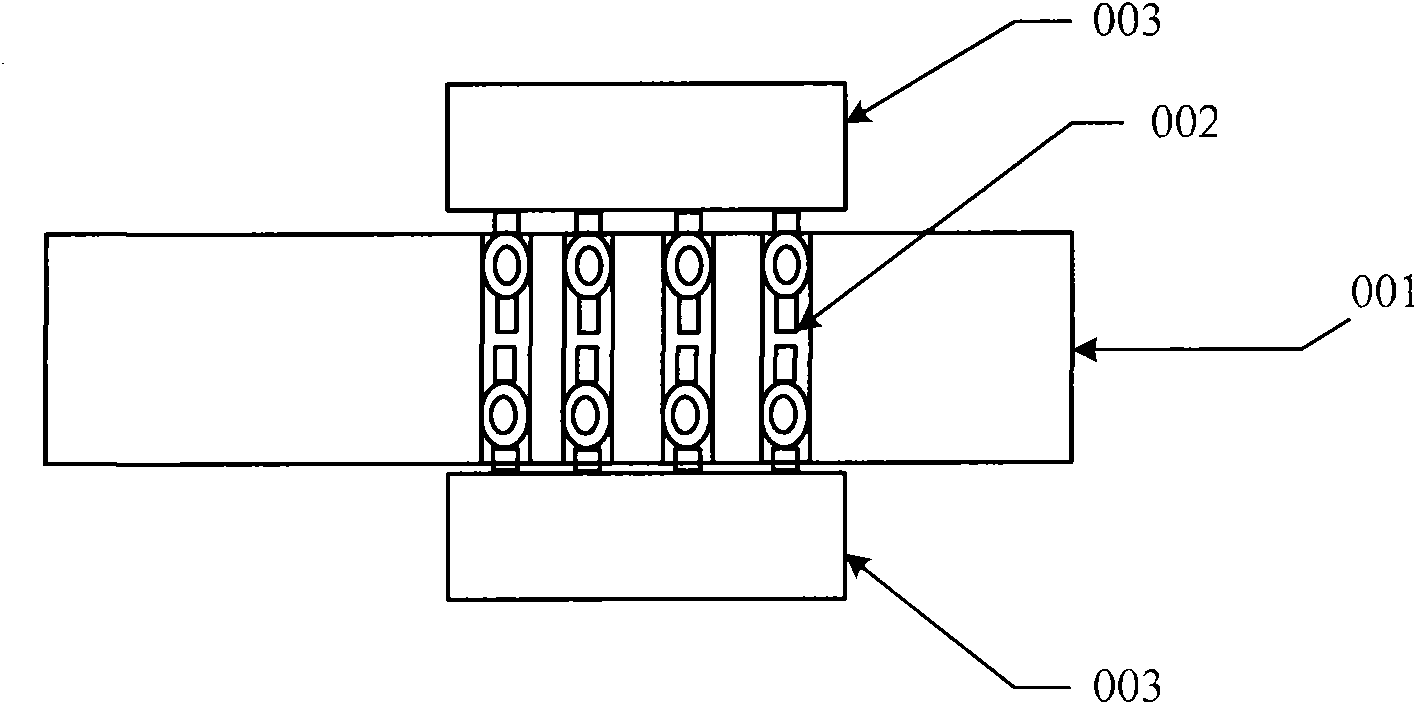

Disclosed is a package structure including a semiconductor chip disposed in a core board having a first surface and an opposite second surface. The package structure further includes a plurality of first and second electrode pads disposed on an active surface and an opposite inactive surface of the semiconductor chip respectively, the semiconductor chip having a plurality of through-silicon vias for electrically connecting the first and second electrode pads. As a result, the semiconductor chip is electrically connected to the two sides of the package structure via the through-silicon vias instead of conductive through holes, so as to enhance electrical quality and prevent the inactive surface of the semiconductor chip from occupying wiring layout space of the second surface of the core board to thereby increase wiring layout density and enhance electrical performance.

Owner:UNIMICRON TECH CORP

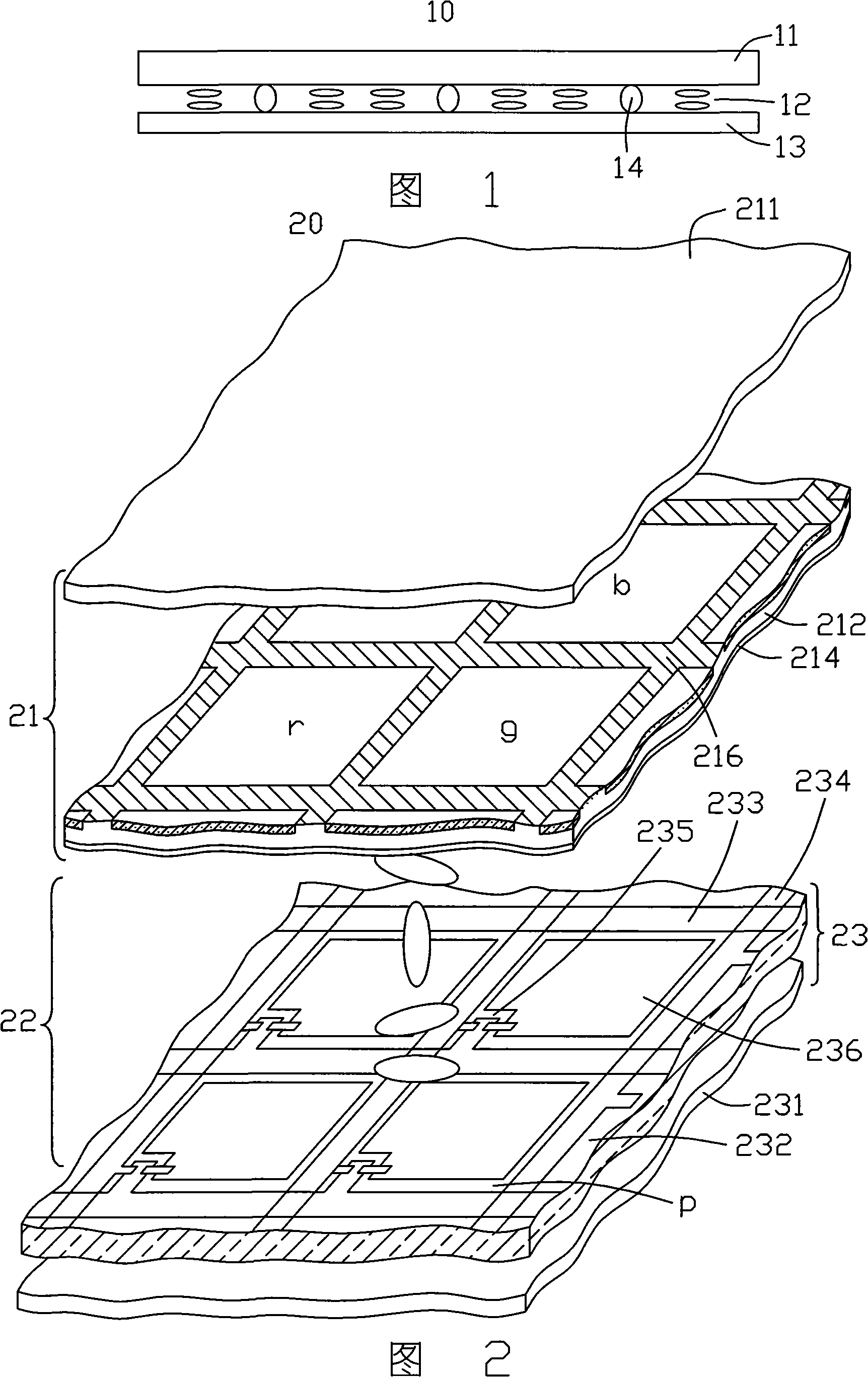

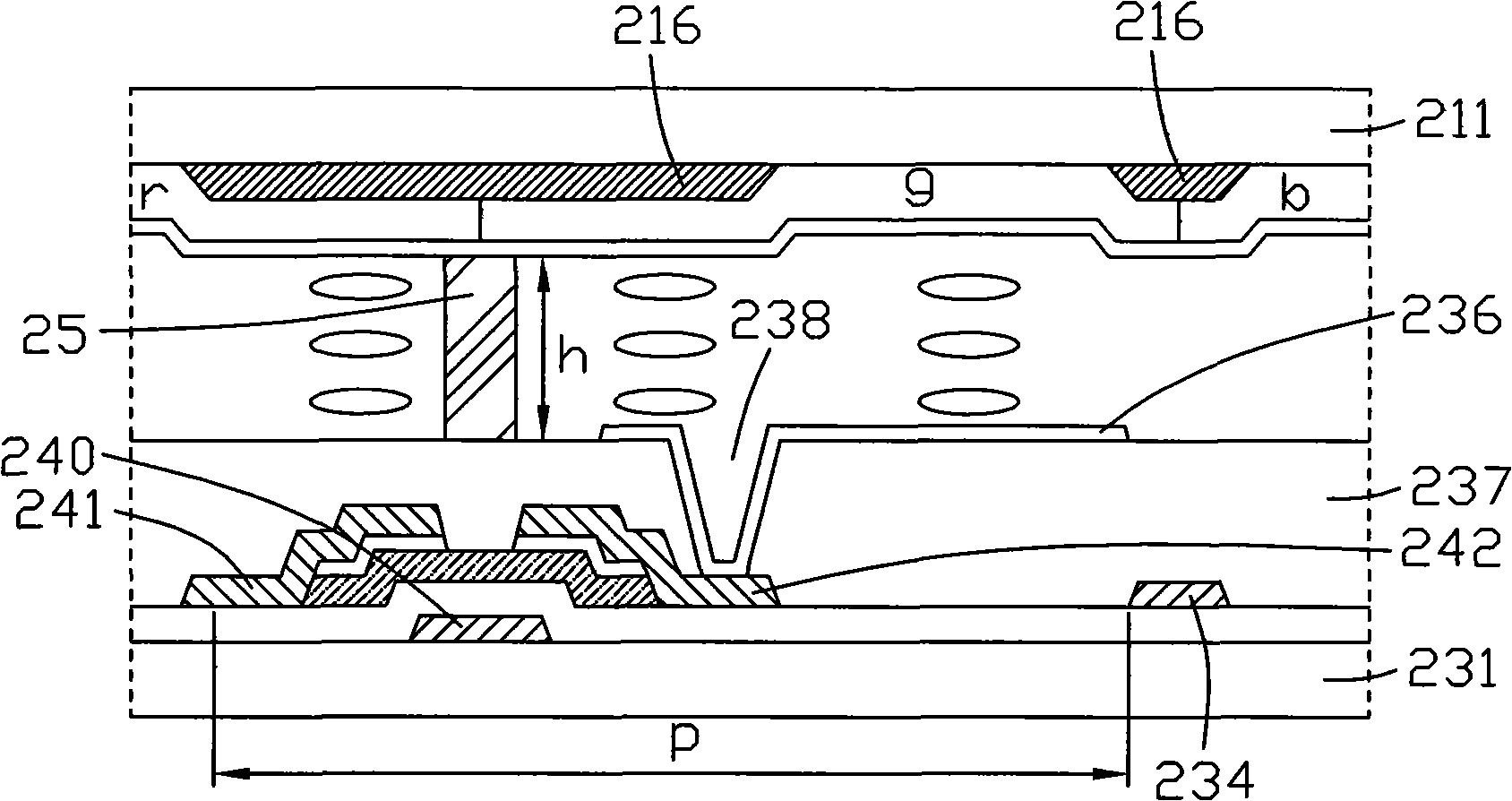

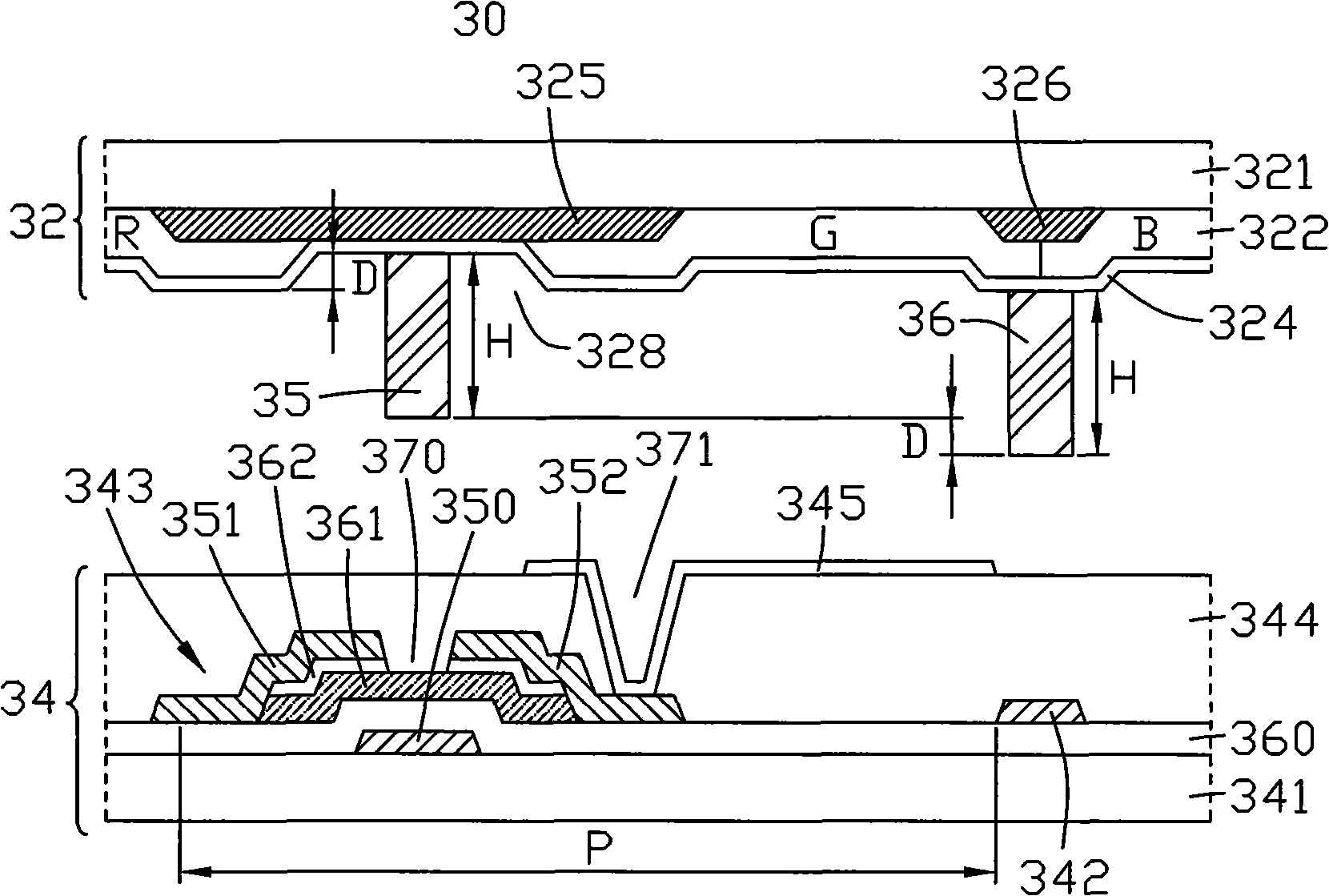

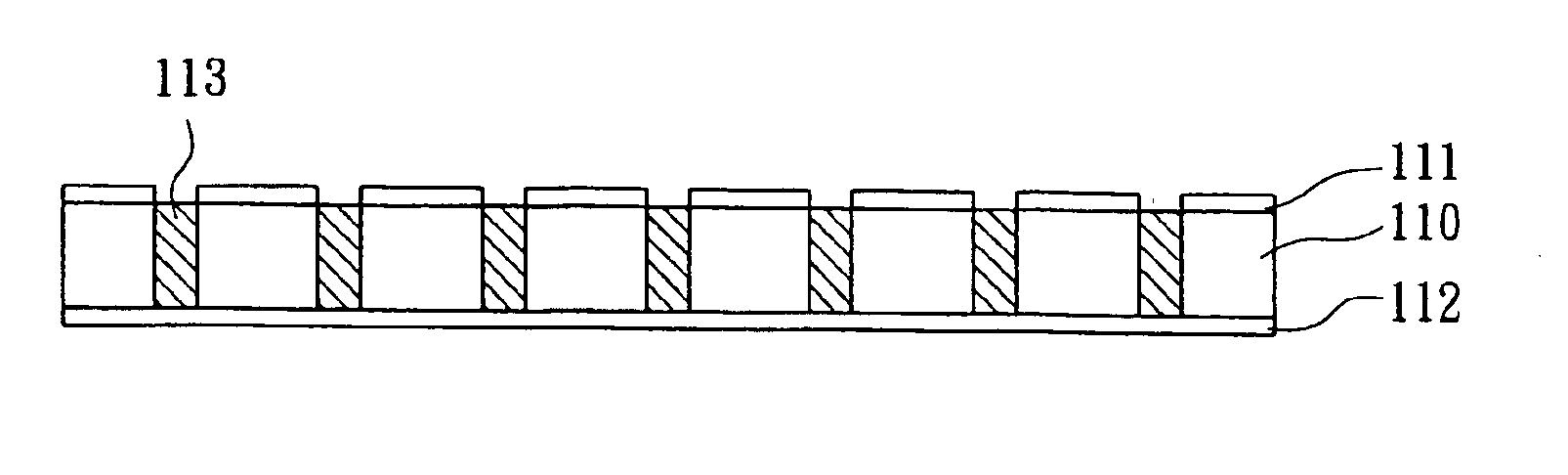

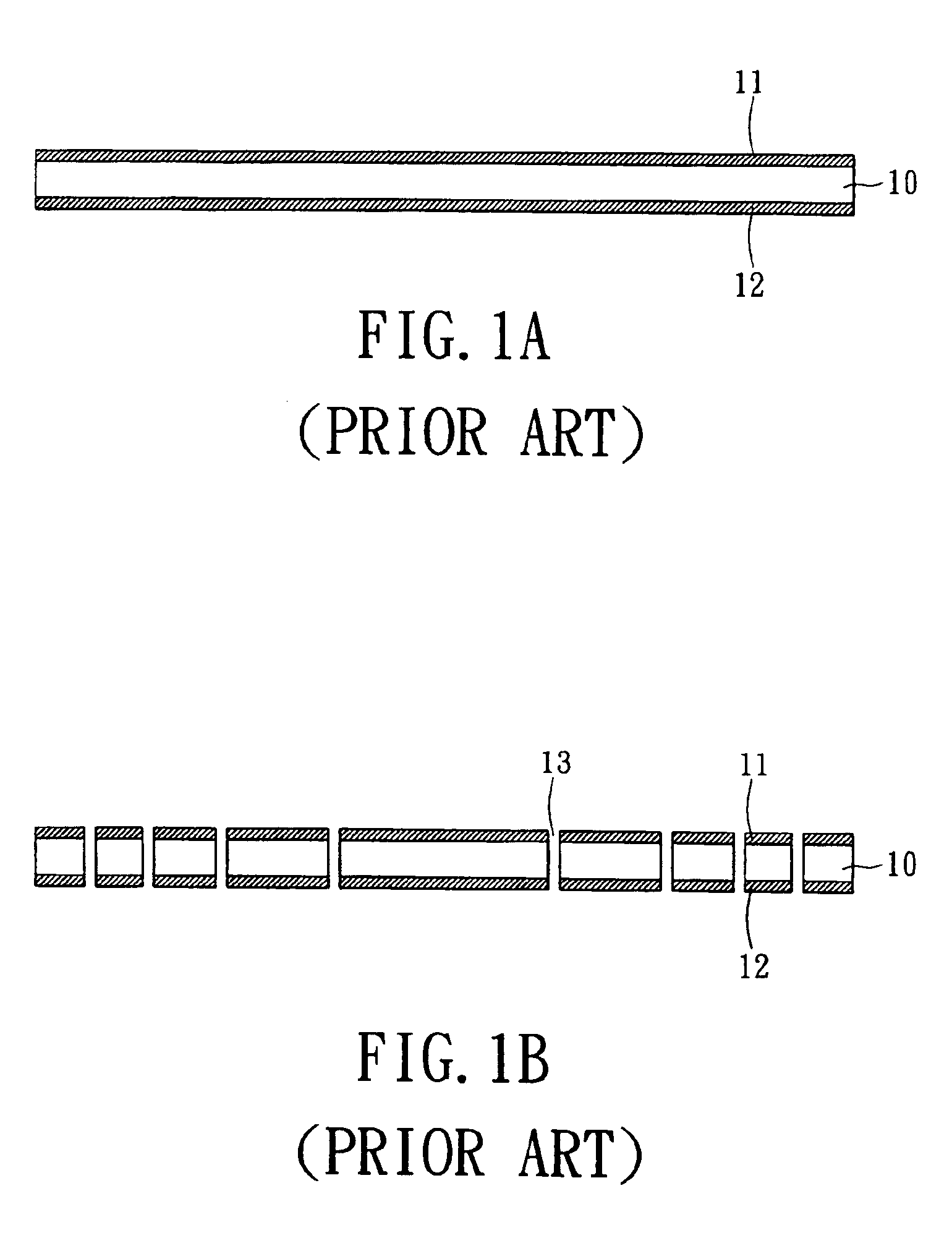

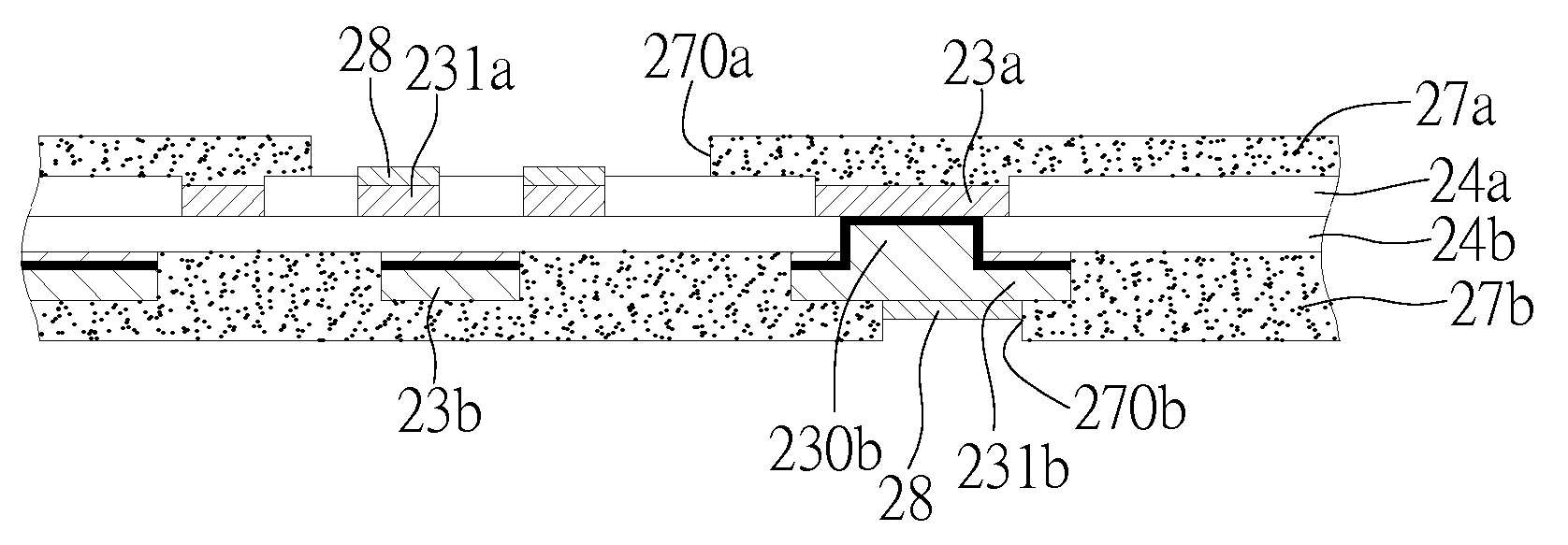

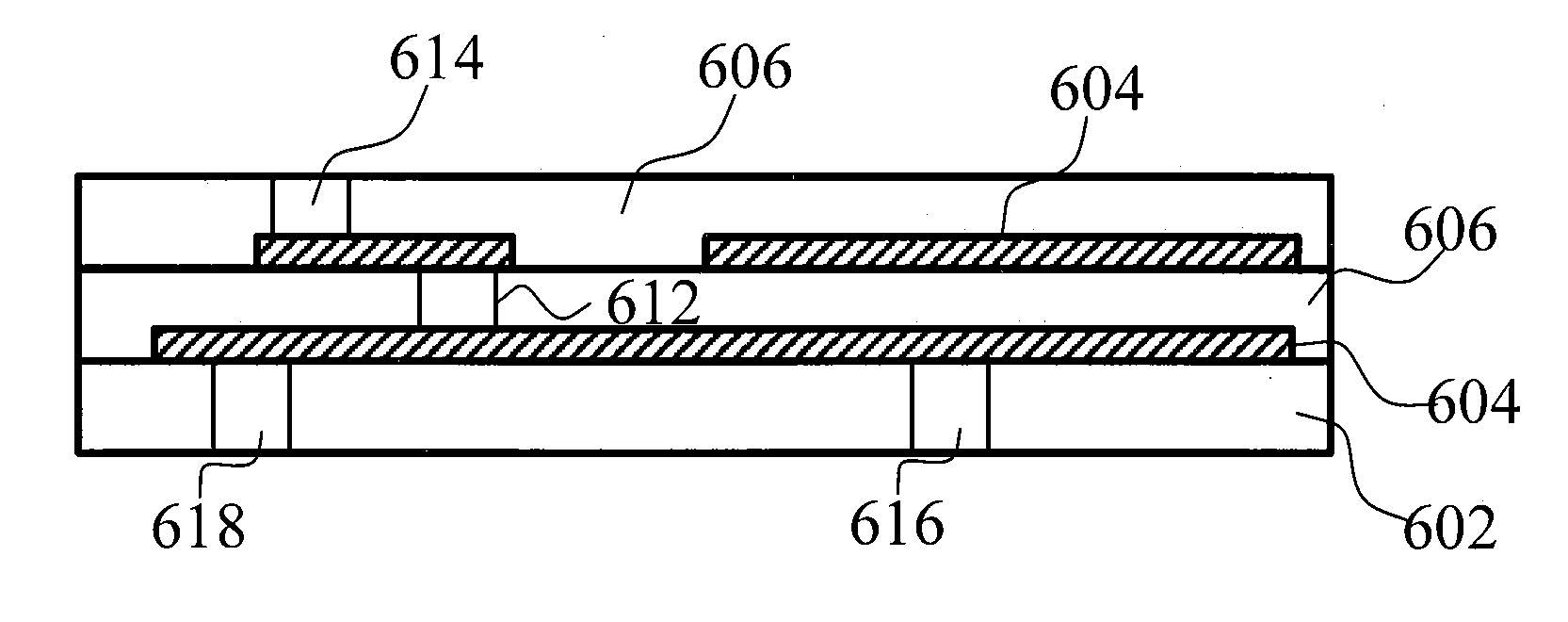

Liquid crystal display panel and liquid crystal display panel assembling method

InactiveCN101334561APrevent hollow stateImprove the layout densityNon-linear opticsGravitational forceLiquid-crystal display

The invention relates to a liquid crystal display panel and a liquid crystal display panel assembly method. The liquid crystal panel comprises a first substrate and a second substrate which is provided with a colourful filter layer. The colourful filter layer comprises a plurality of pixel units; each pixel unit comprises a first black matrix, a second black matrix which is arranged in an interval way to the first black matrix, a first cylindrical clearance article and a second cylindrical clearance article. The first cylindrical clearance article is arranged on the colourful filter layer correspondingly to the first black matrix. The second cylindrical clearance article is arranged on the colourful filter layer correspondingly to the second black matrix. The two cylindrical clearance articles, after being compressed, are respectively butted with the same horizontal surface of the first substrate and are used for supporting the two substrates; furthermore, the first cylindrical clearance article and the second cylindrical article are provided with different compression quantities. The liquid crystal display panel and the liquid crystal display panel assembly method can effectively avoid the display fleck problem caused by the non-uniform distribution of the gravity force and can obtain the gravity residues with large range.

Owner:INNOCOM TECH SHENZHEN +1

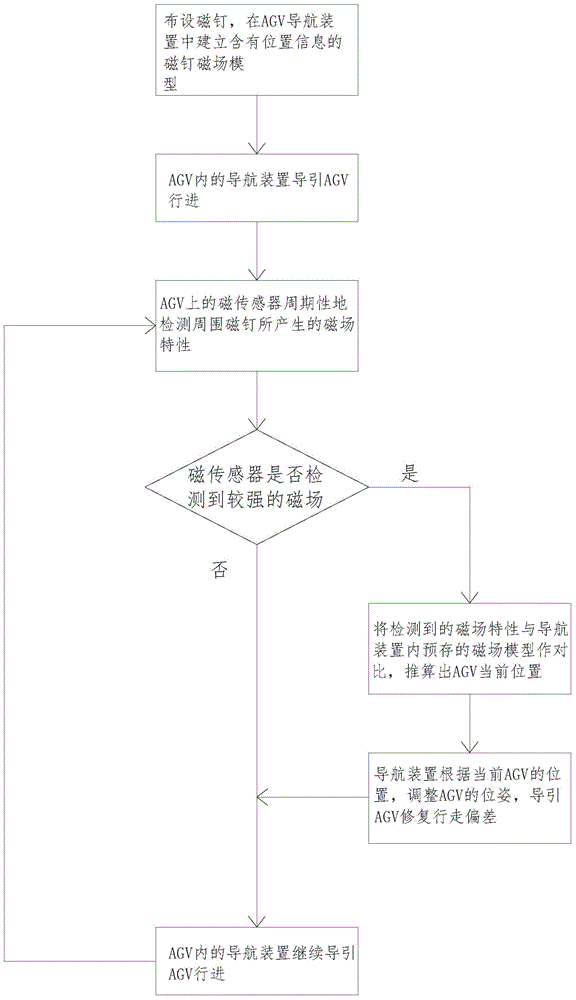

Navigation error correction method based on magnetic nail location

InactiveCN104897177ALow costAccuracy not affected by mediumMeasurement devicesVehicle position/course/altitude controlCorrection methodComputer science

Owner:GUANGDONG JATEN ROBOT & AUTOMATION

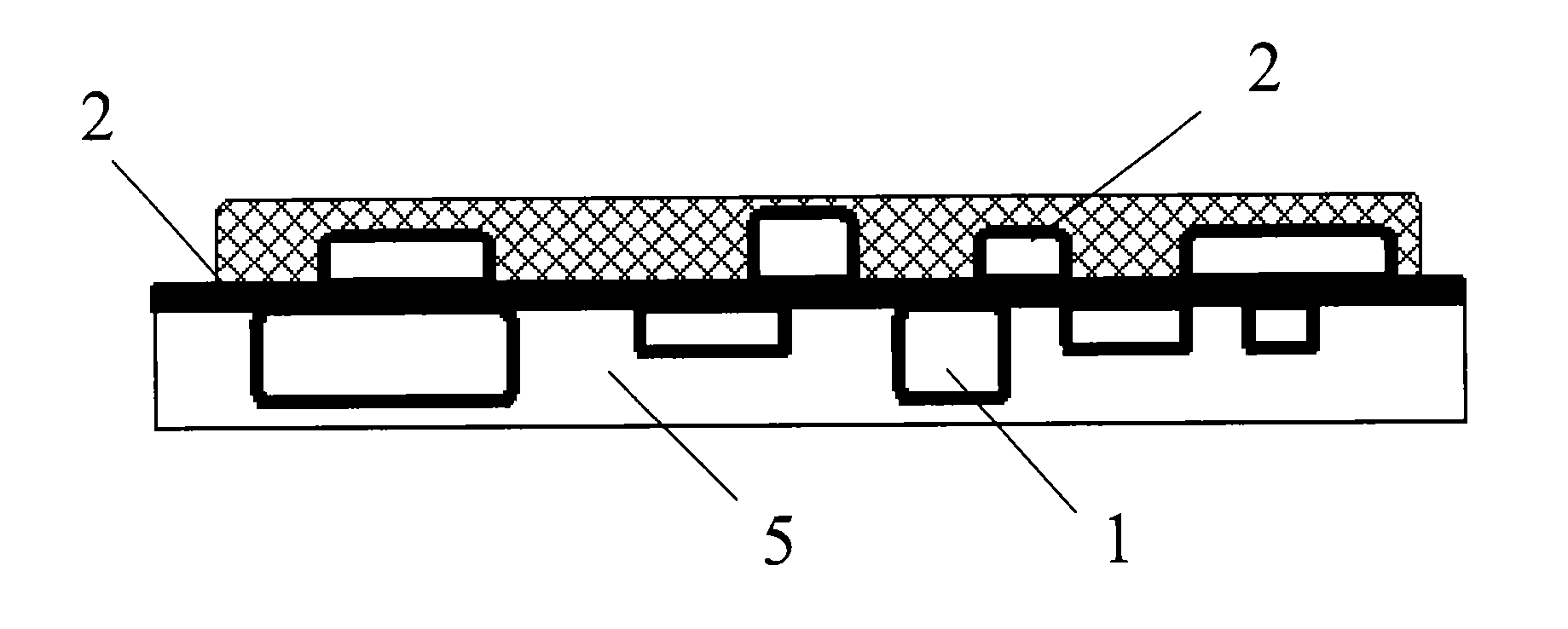

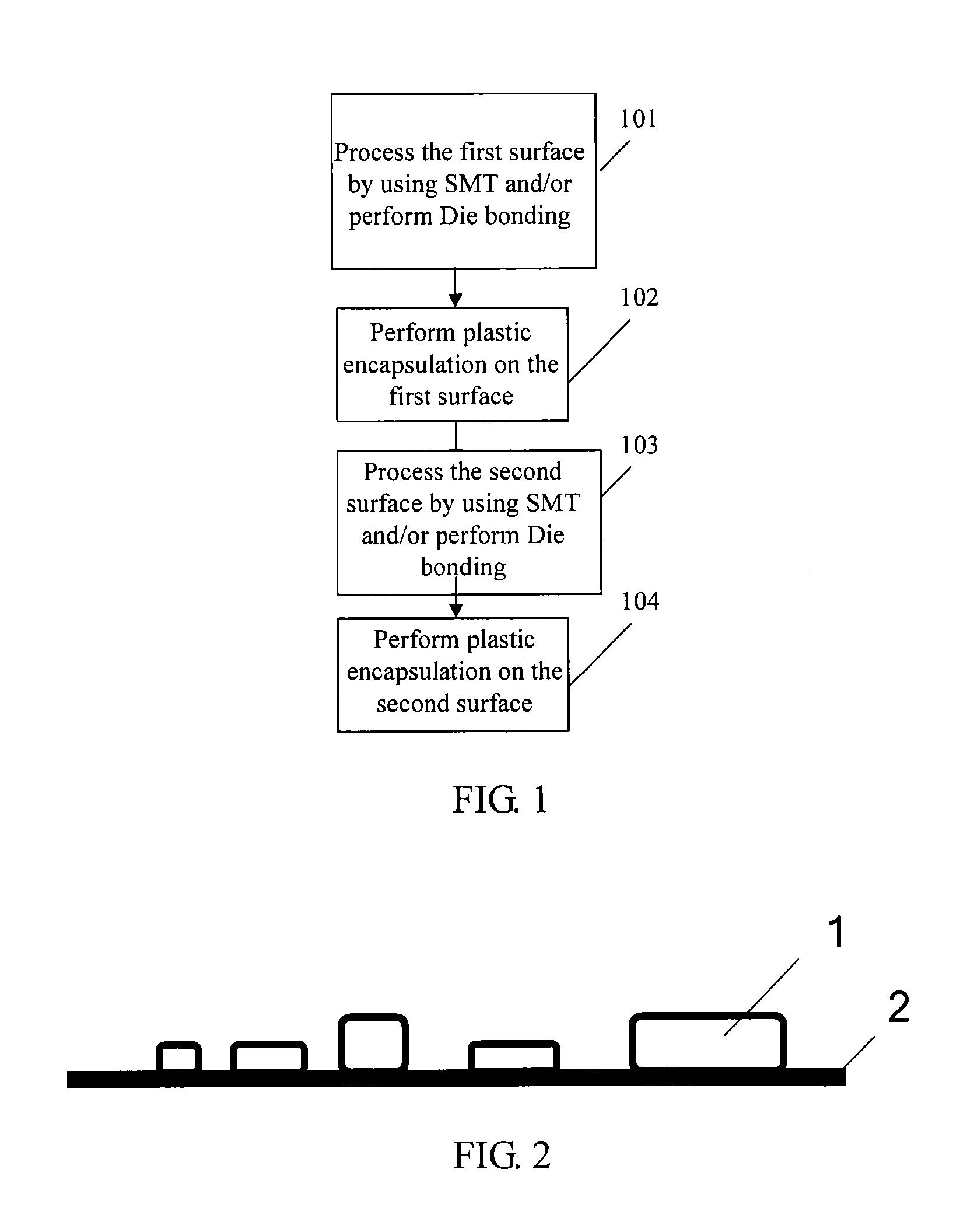

Method for encapsulating semiconductor and structure thereof

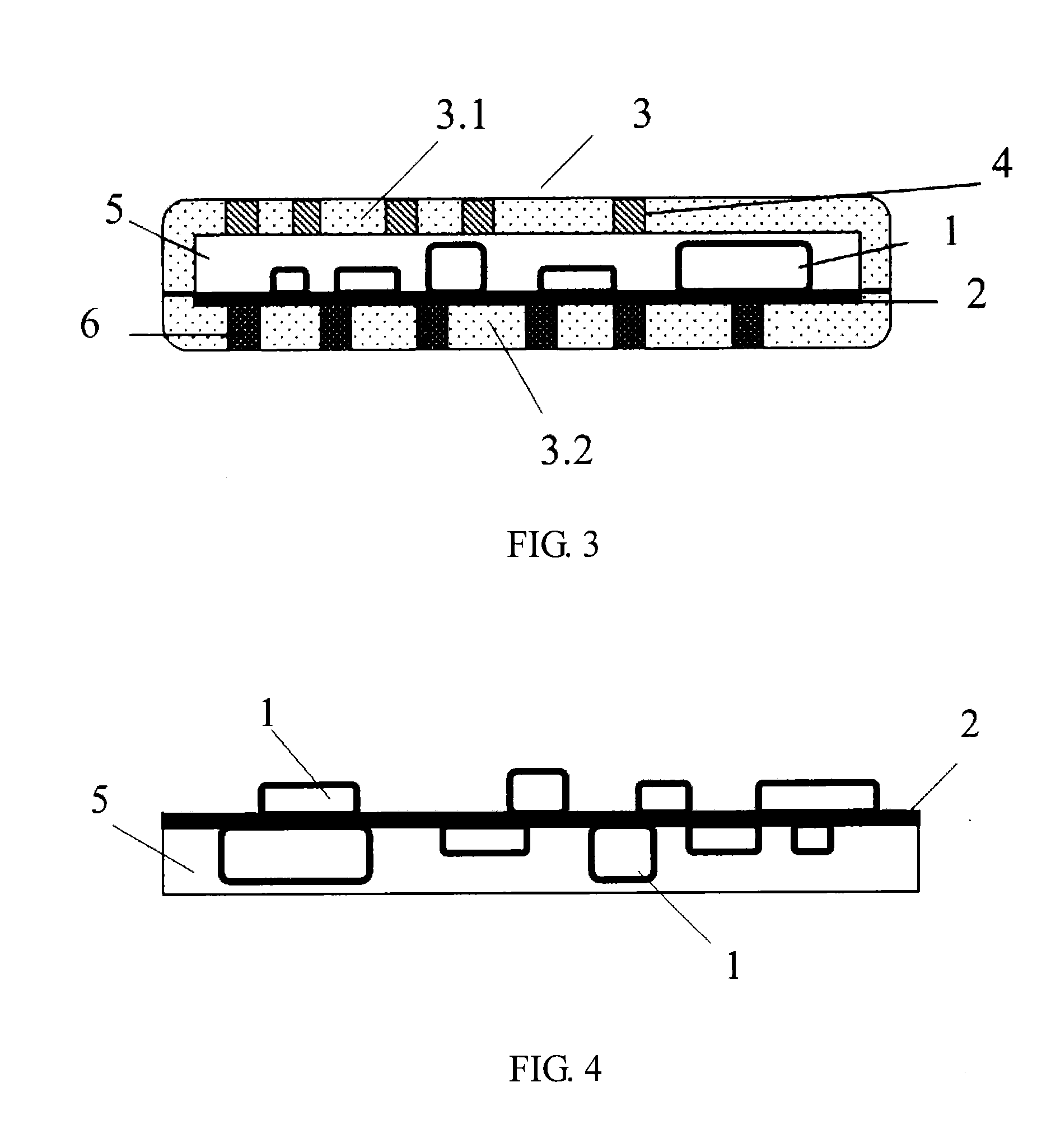

ActiveUS20130102113A1Increasing component layout densityReduce thicknessLayered productsSemiconductor/solid-state device detailsSurface mountingSurface-mount technology

Embodiments of the present invention disclose a method for encapsulating a component with plastic and its encapsulation structure, which belong to the plastic encapsulation technology field. The method includes: processing, by using the surface mounting technology, a first surface of a part to be encapsulated with plastic and / or performing die bonding on the first surface; encapsulating, with plastic, the first surface of the part to be encapsulated with plastic a second surface of the part to be encapsulated with plastic the first surface and / or performing die bonding in the second face; and encapsulating, with plastic, the second surface of the part to be encapsulated with plastic. This encapsulation structure includes a substrate, where components are fixed on an upper surface and a lower surface of the substrate, and the components on the upper surface and lower surface are all encapsulated with plastic in seal.

Owner:HUAWEI DEVICE CO LTD

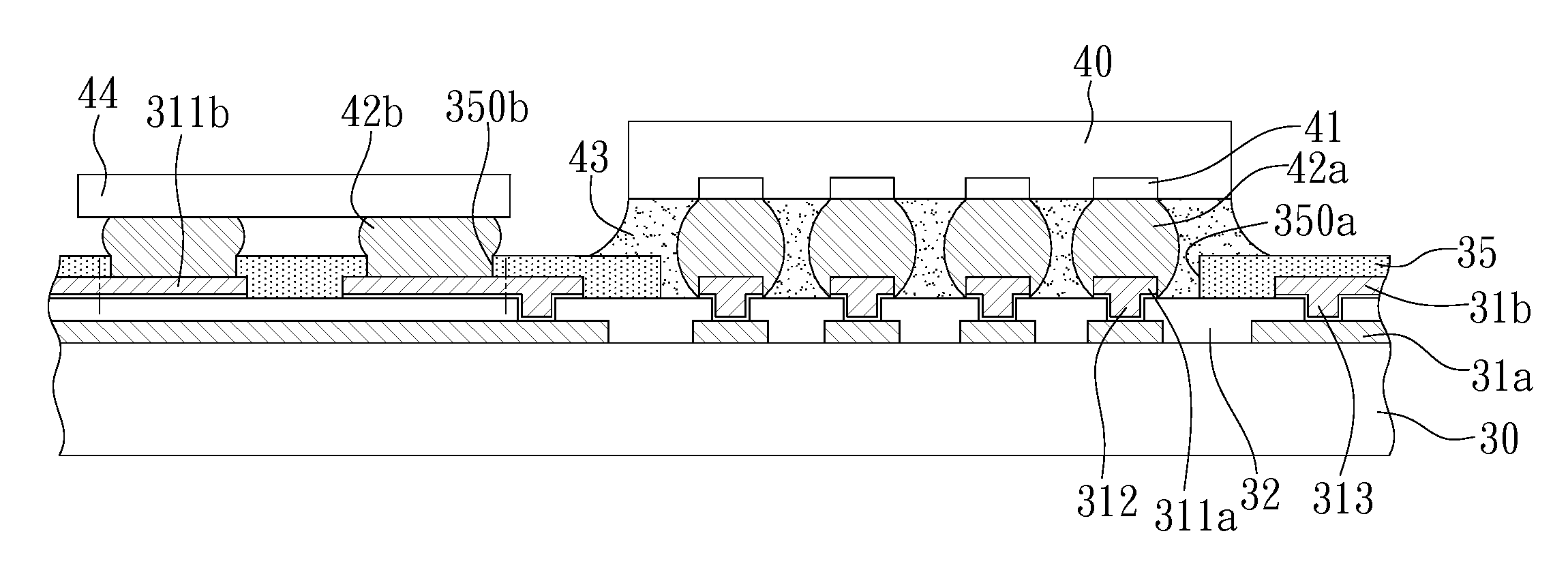

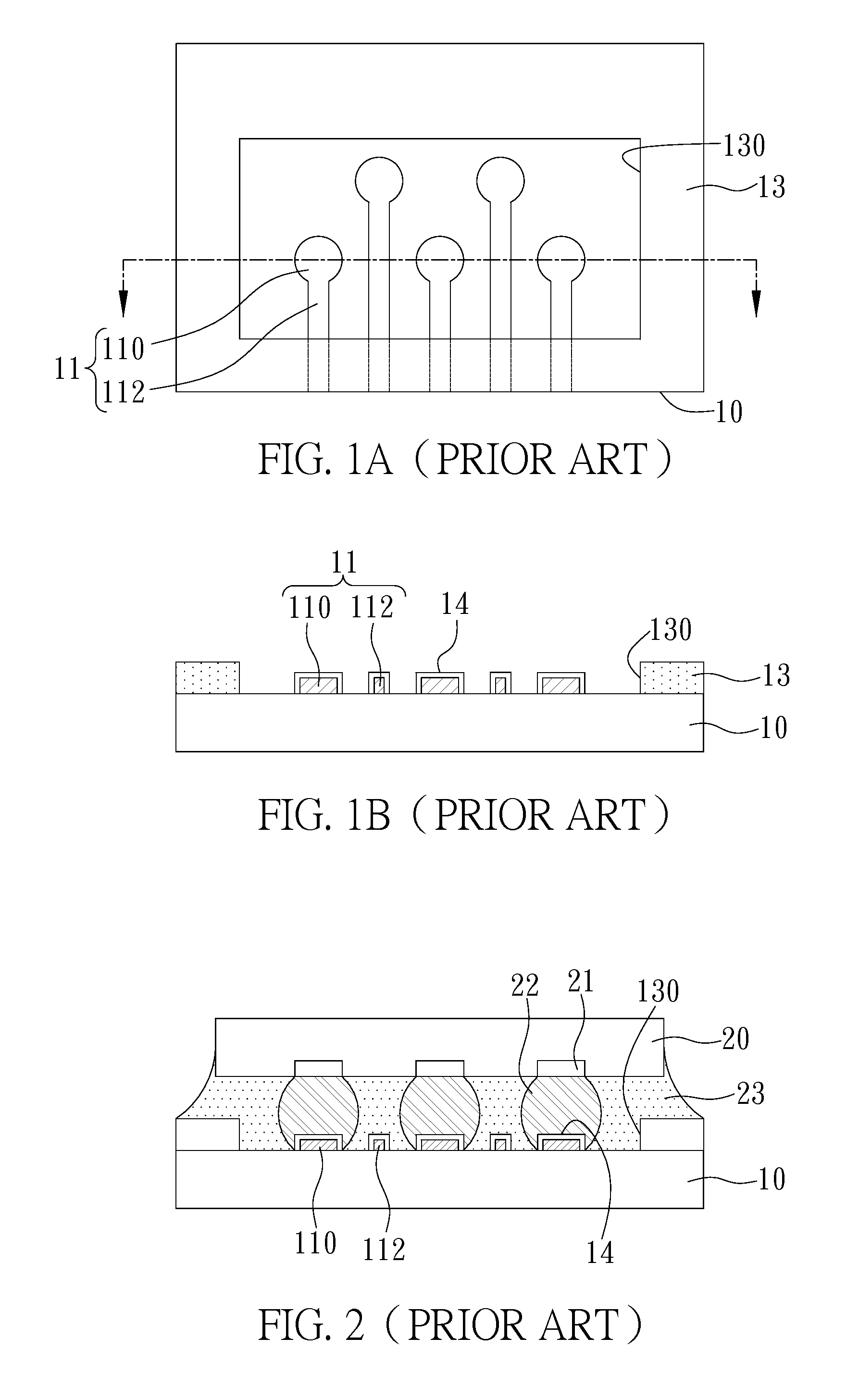

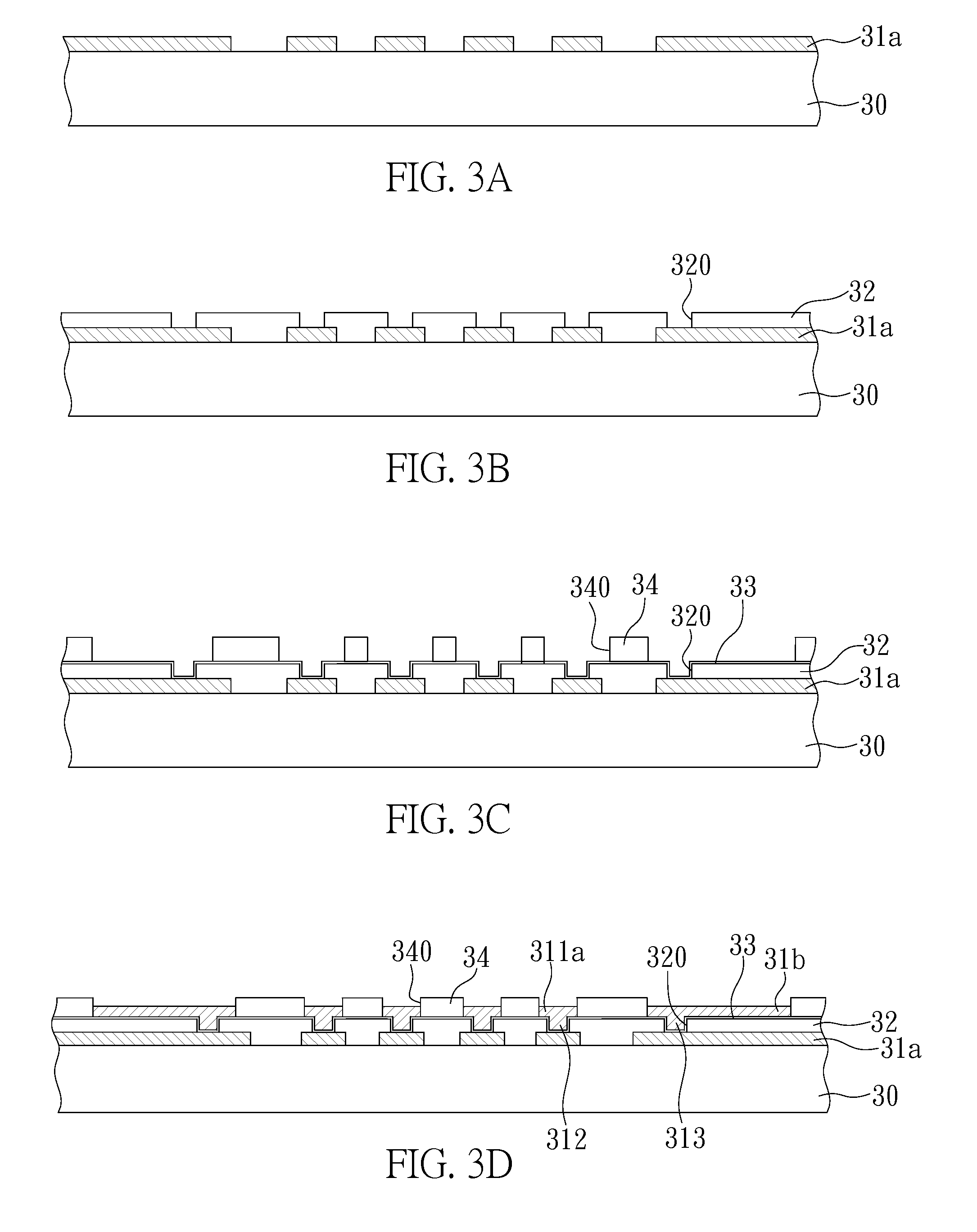

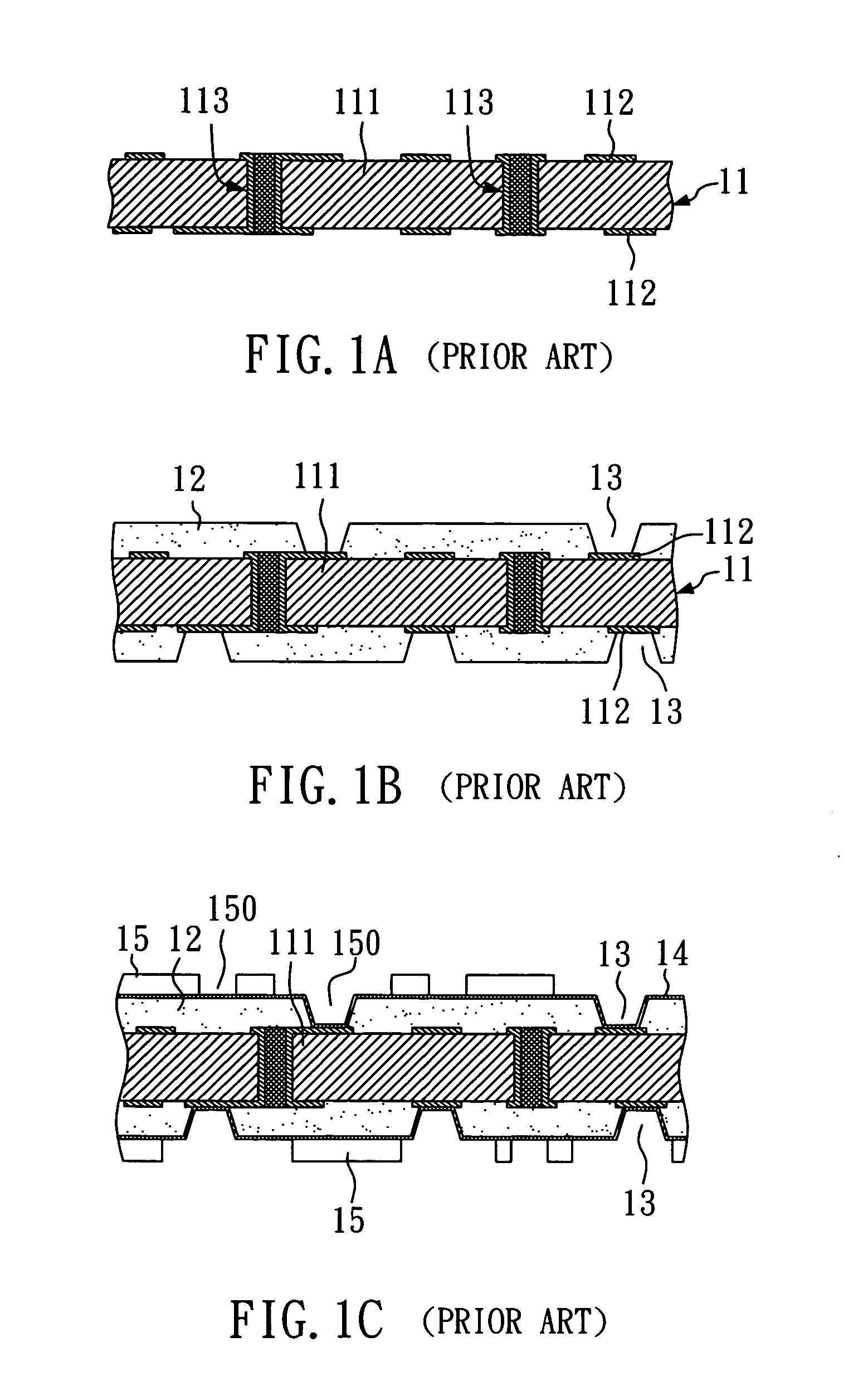

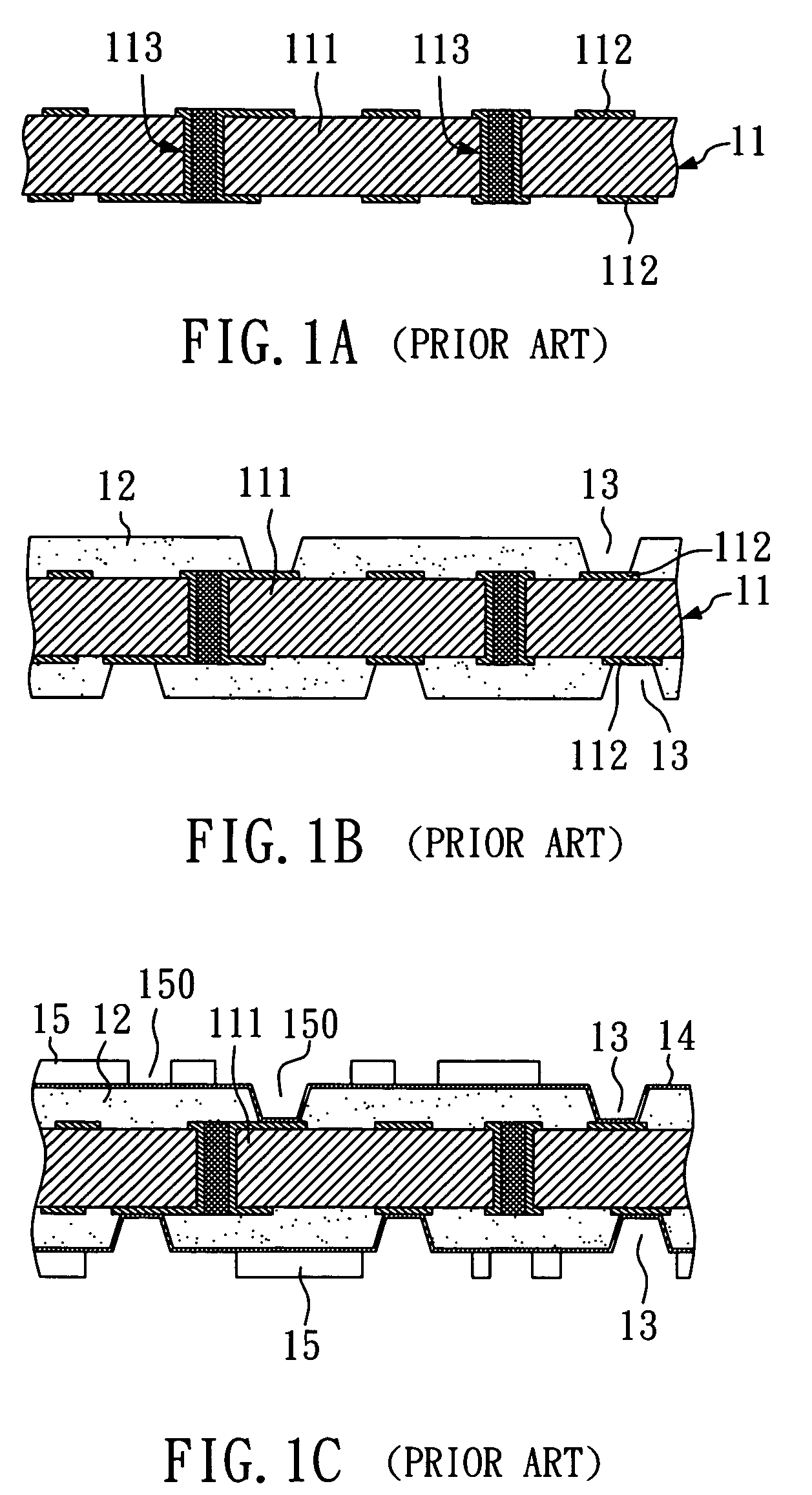

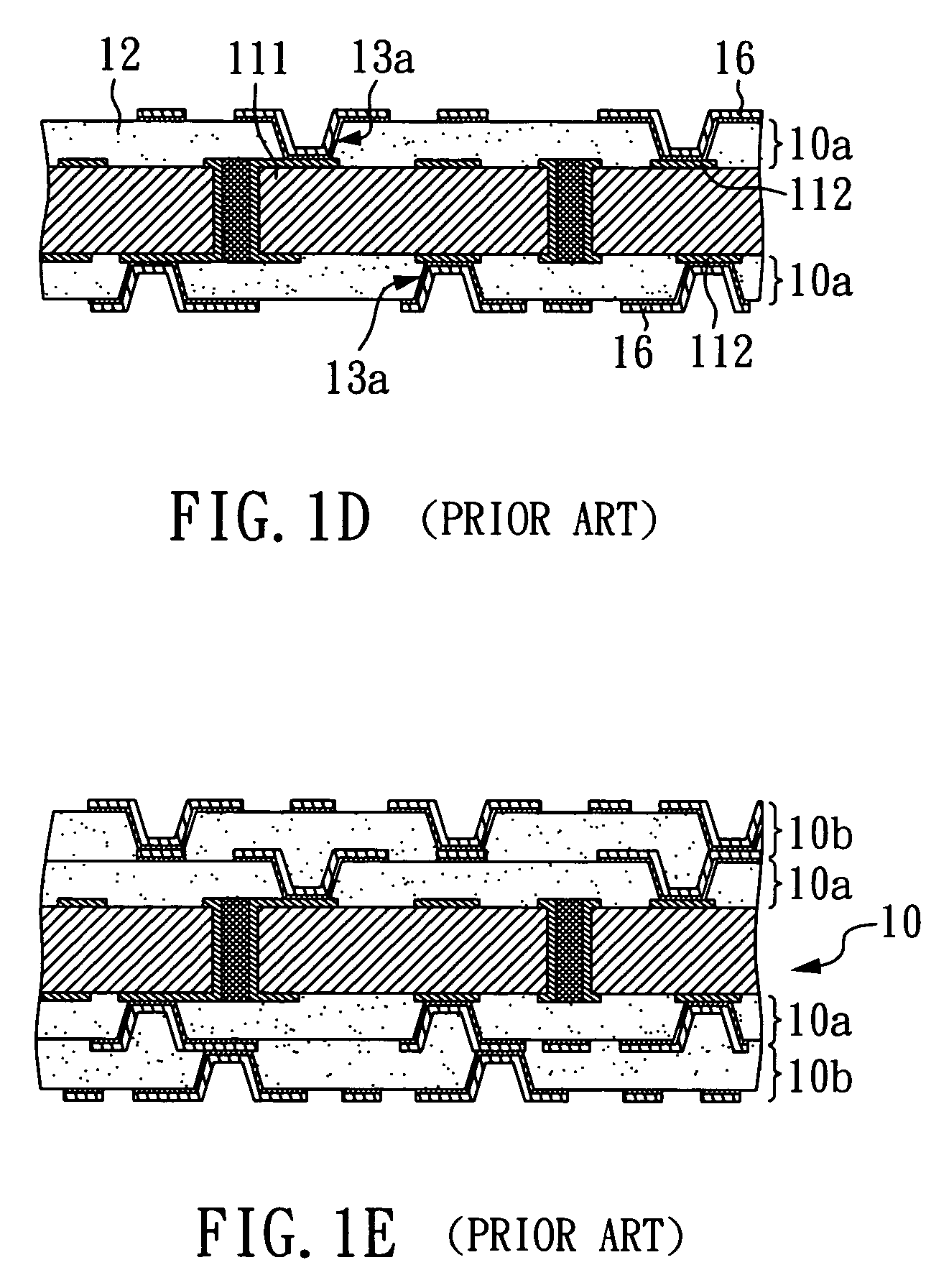

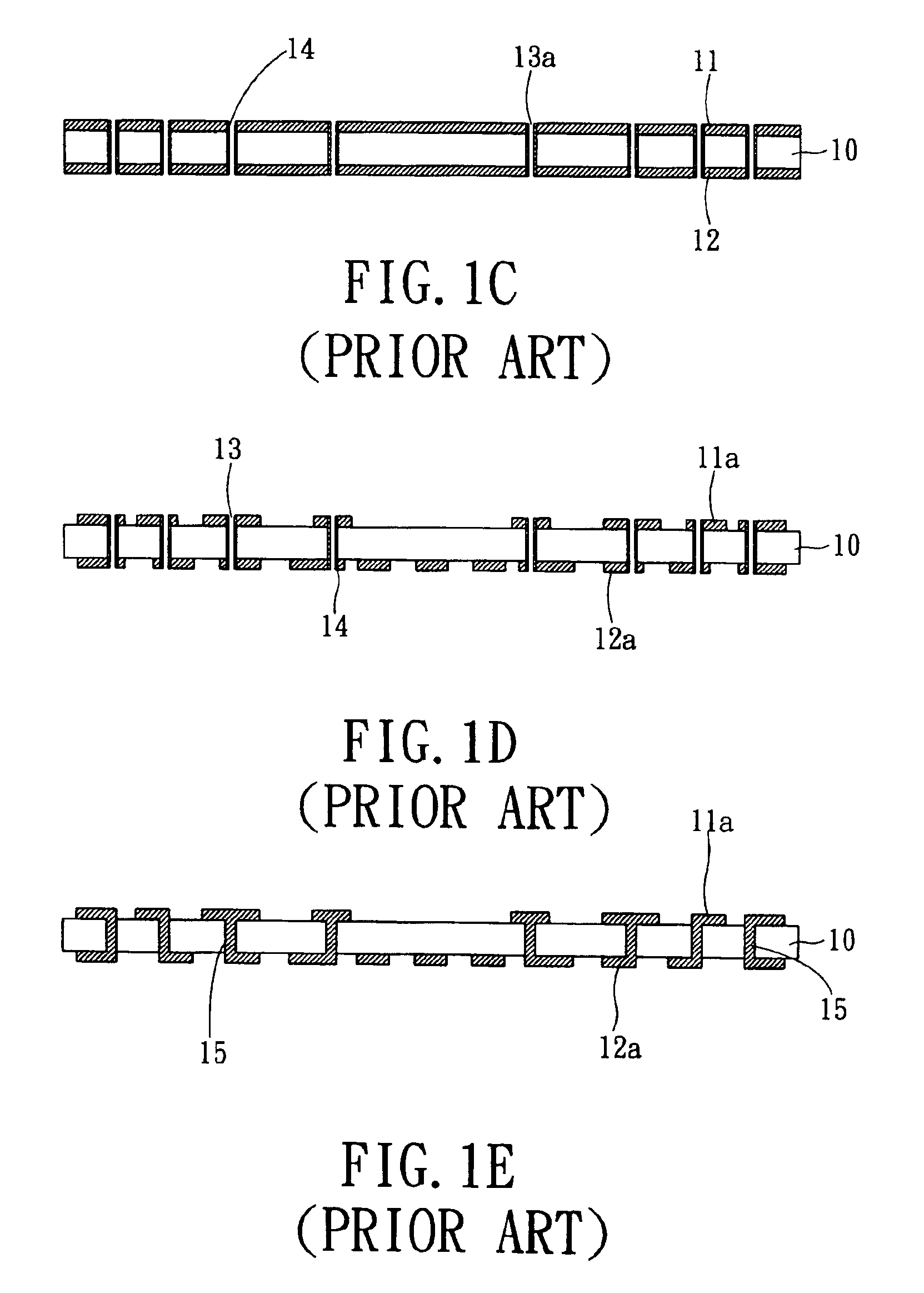

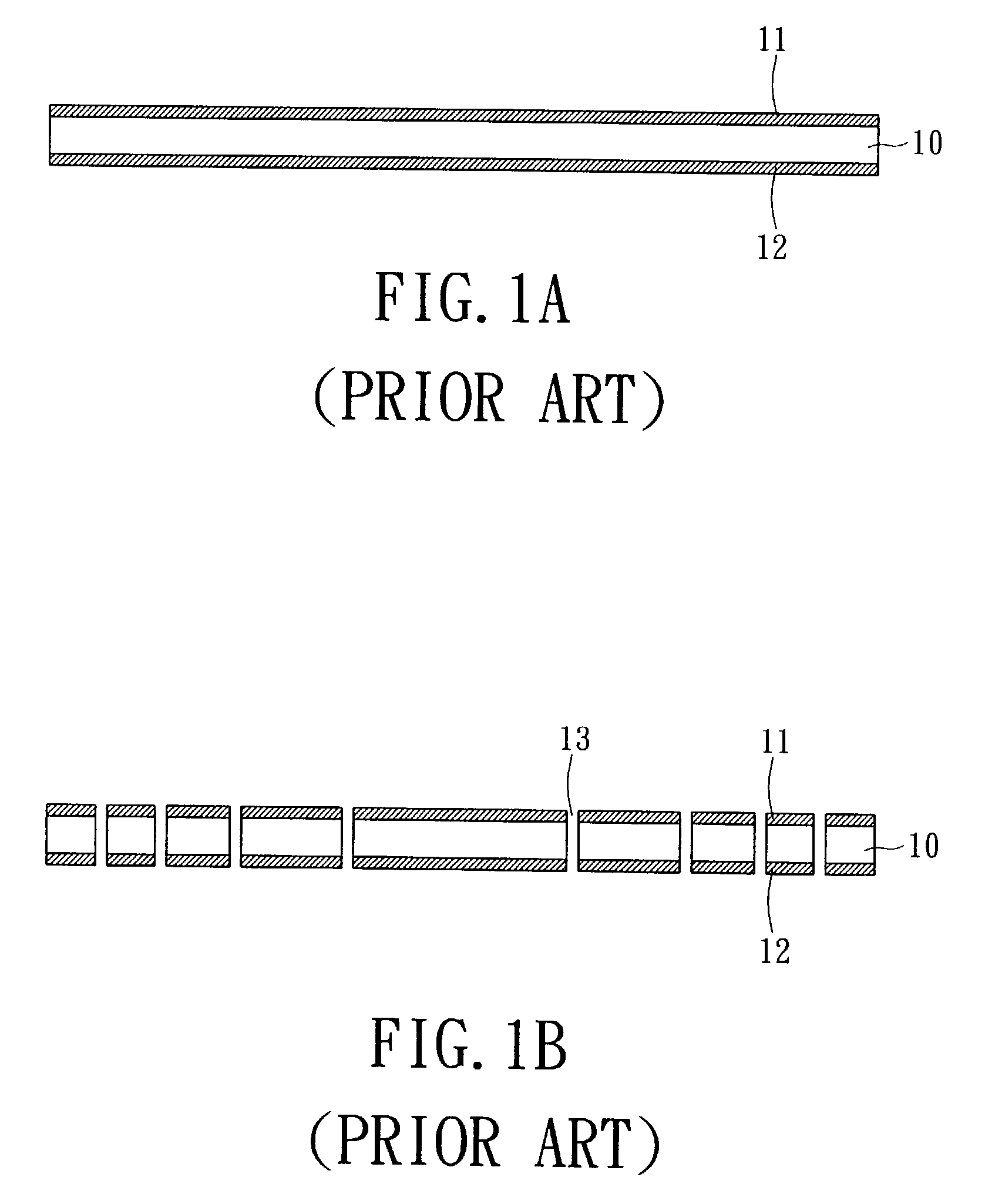

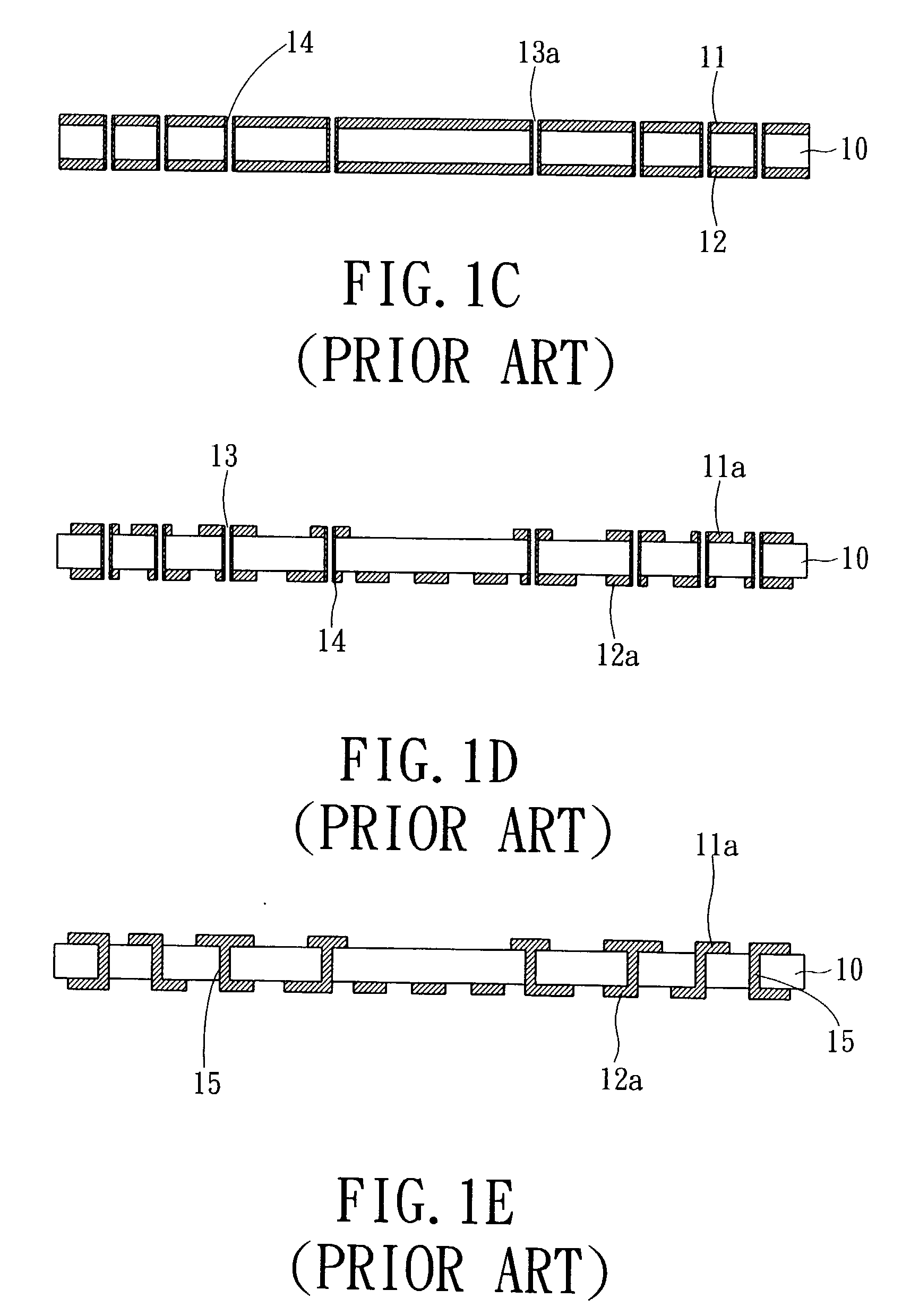

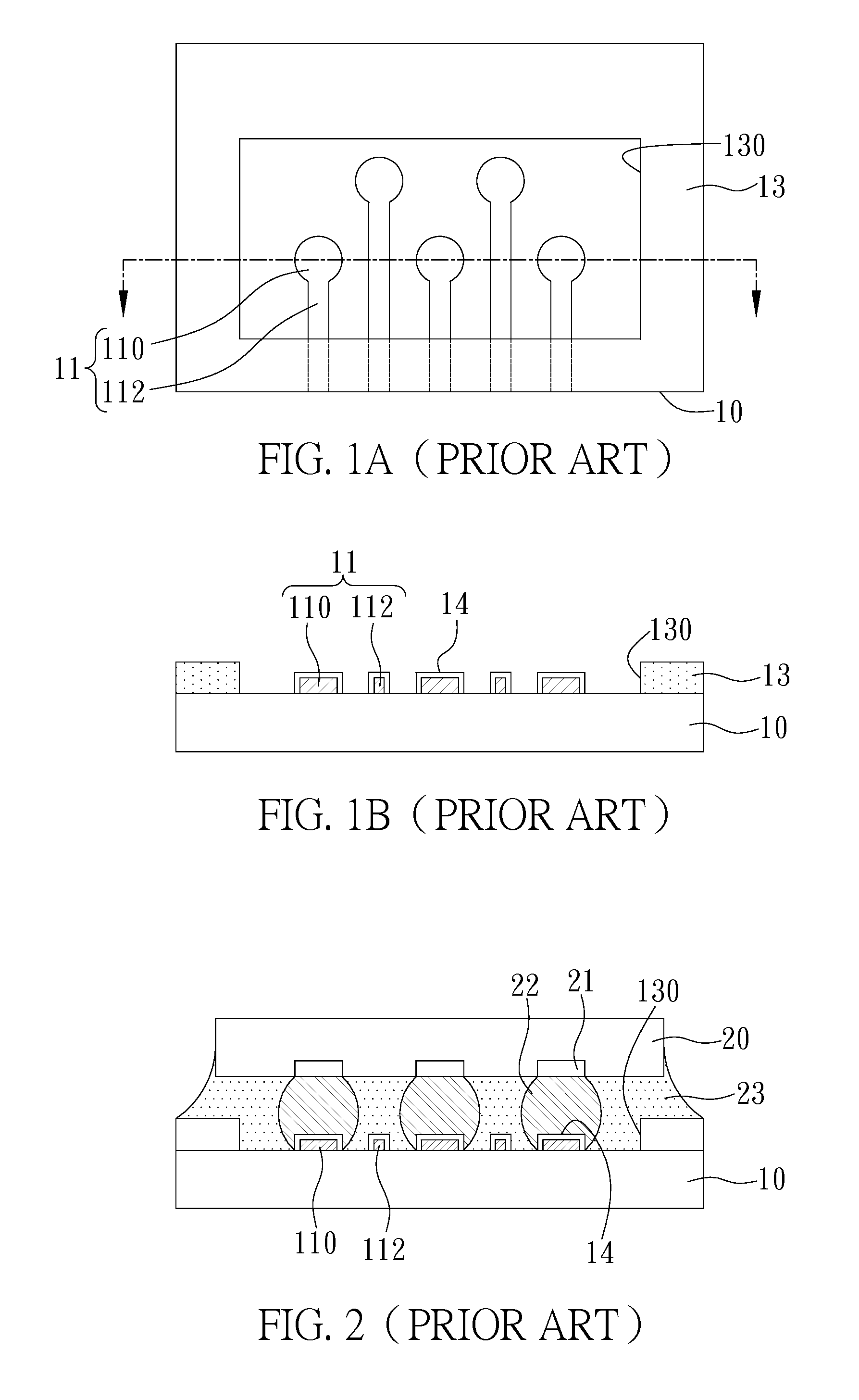

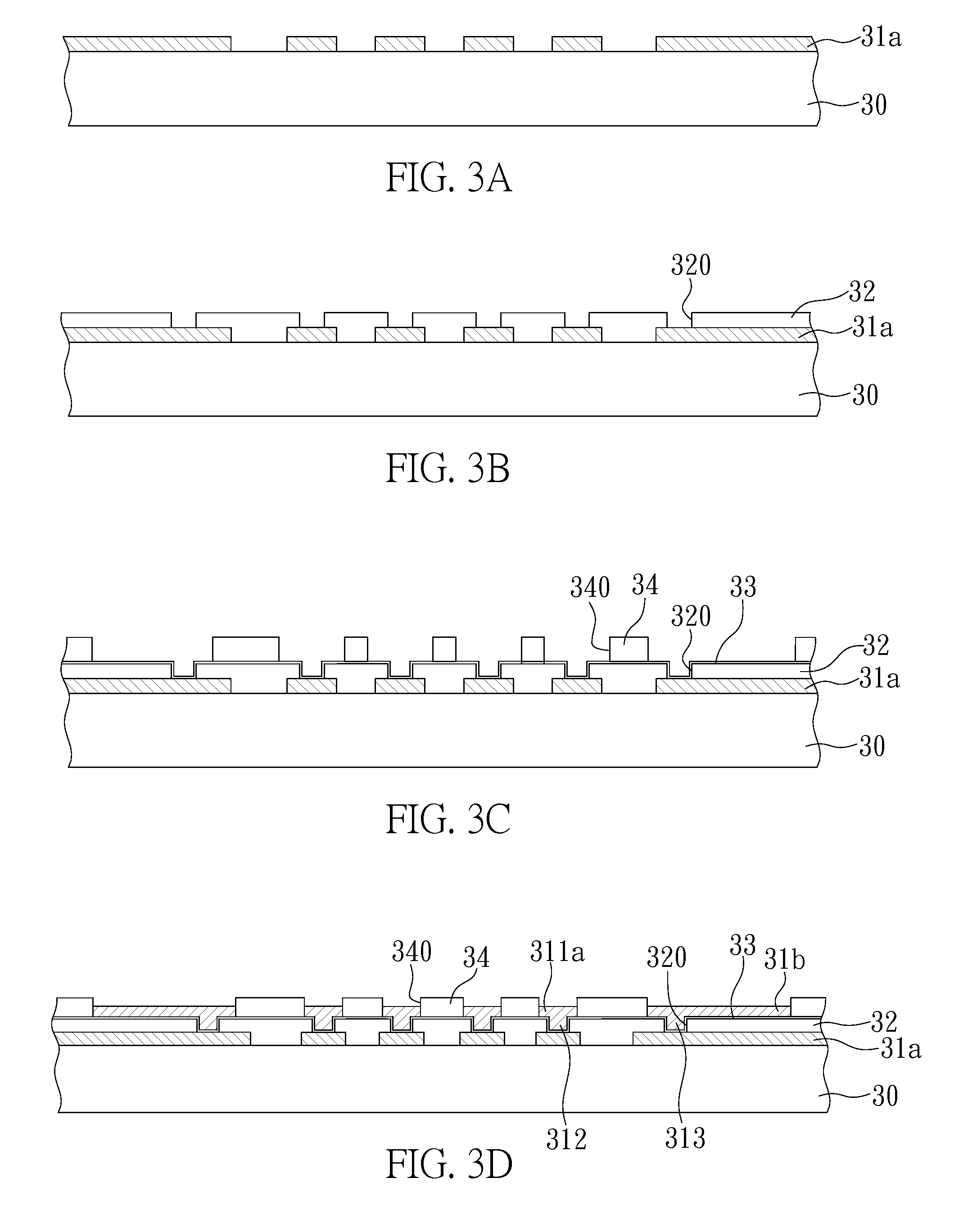

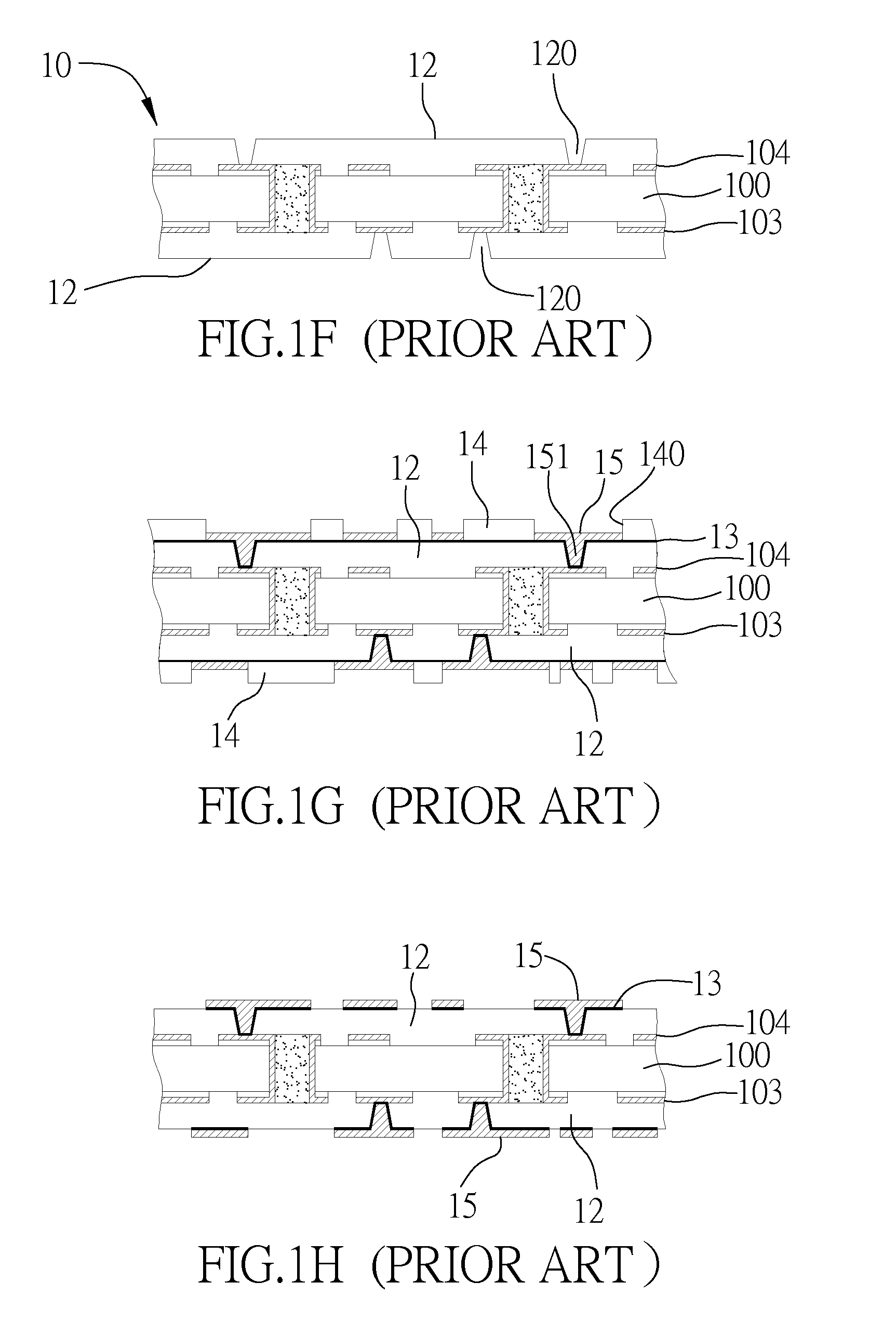

Method of manufacturing a coreless package substrate and conductive structure of the substrate

InactiveUS20070246744A1Reduce thicknessImprove routing densitySemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskHigh density

A method of manufacturing a coreless package substrate together with a conductive structure of the substrate is disclosed. The method can produce a coreless package substrate which comprises: at least a built-up structure having a first solder mask and a second solder mask, wherein a plurality of openings are formed in the first and second solder mask to expose the conductive pads of the built-up structure; and a plurality of solder bumps as well as solder layers formed on the conductive pads. Therefore, the invention can produce the coreless package substrate with high density of circuit layout, less manufacturing steps, and small size.

Owner:PHOENIX PRECISION TECH CORP

Coreless package substrate with conductive structures

InactiveUS7626270B2Reduce thicknessImprove routing densitySemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskHigh density

A method of manufacturing a coreless package substrate together with a conductive structure of the substrate is disclosed. The method can produce a coreless package substrate which comprises: at least a built-up structure having a first solder mask and a second solder mask, wherein a plurality of openings are formed in the first and second solder mask to expose the conductive pads of the built-up structure; and a plurality of solder bumps as well as solder layers formed on the conductive pads. Therefore, the invention can produce the coreless package substrate with high density of circuit layout, less manufacturing steps, and small size.

Owner:PHOENIX PRECISION TECH CORP

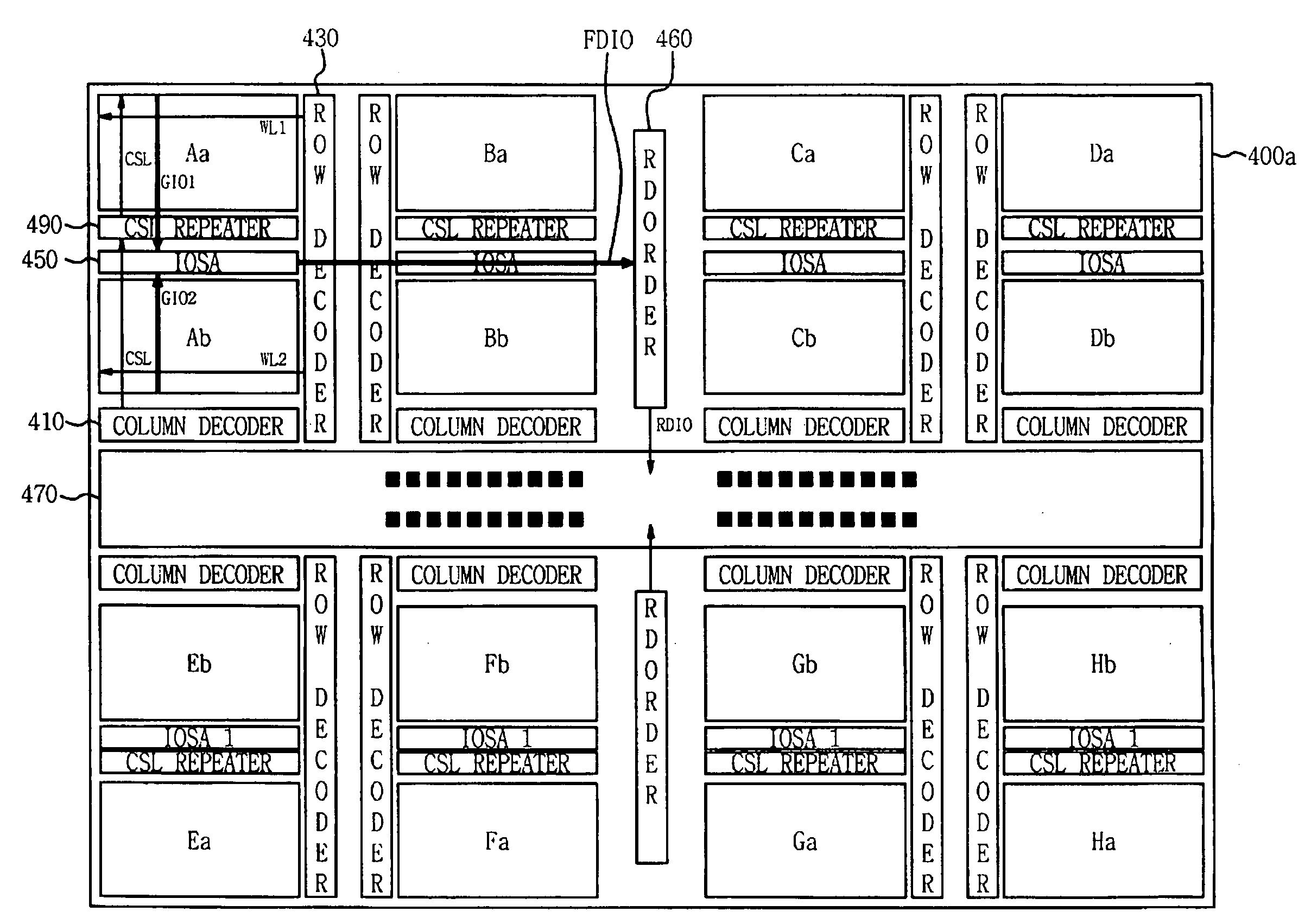

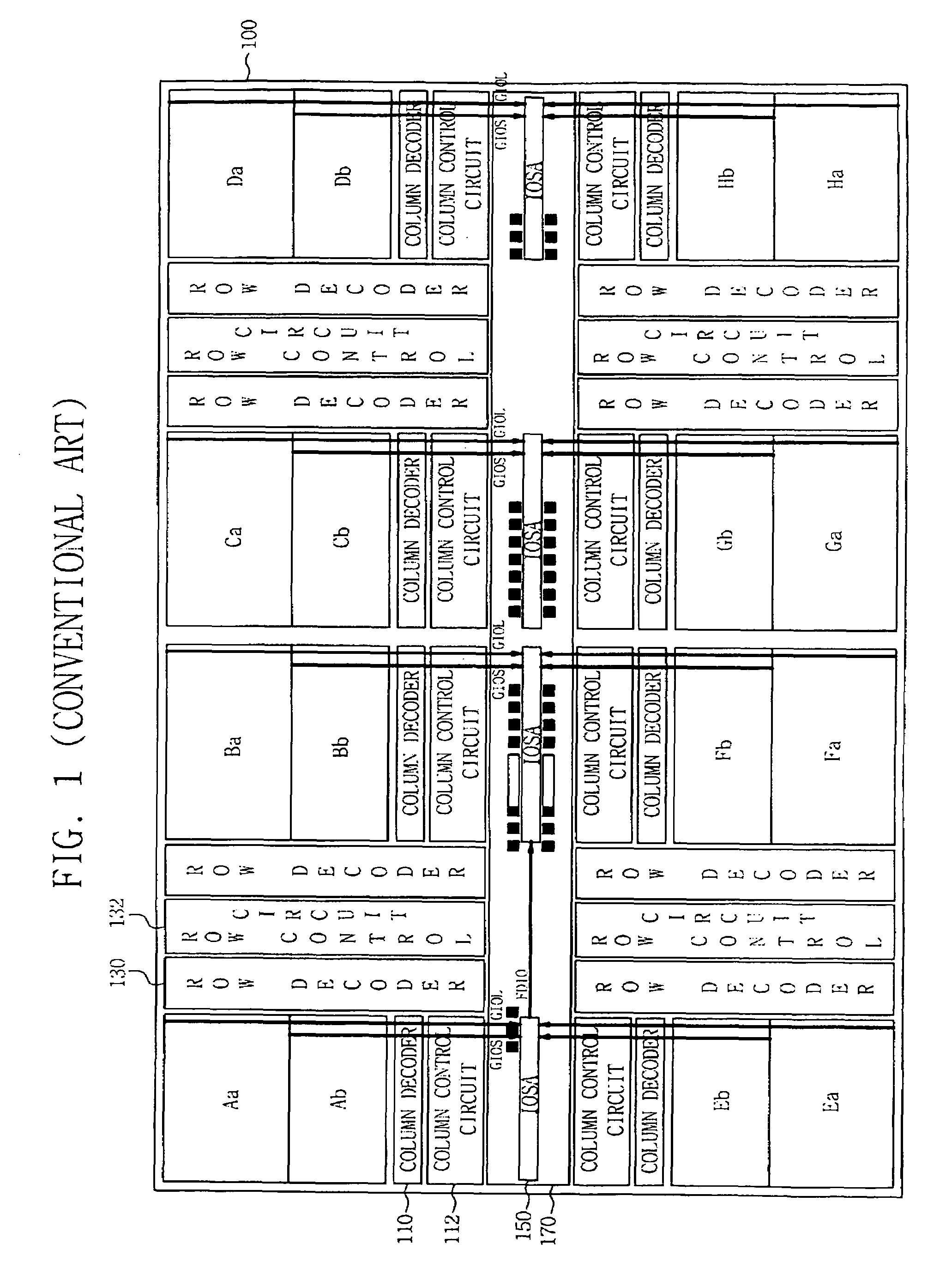

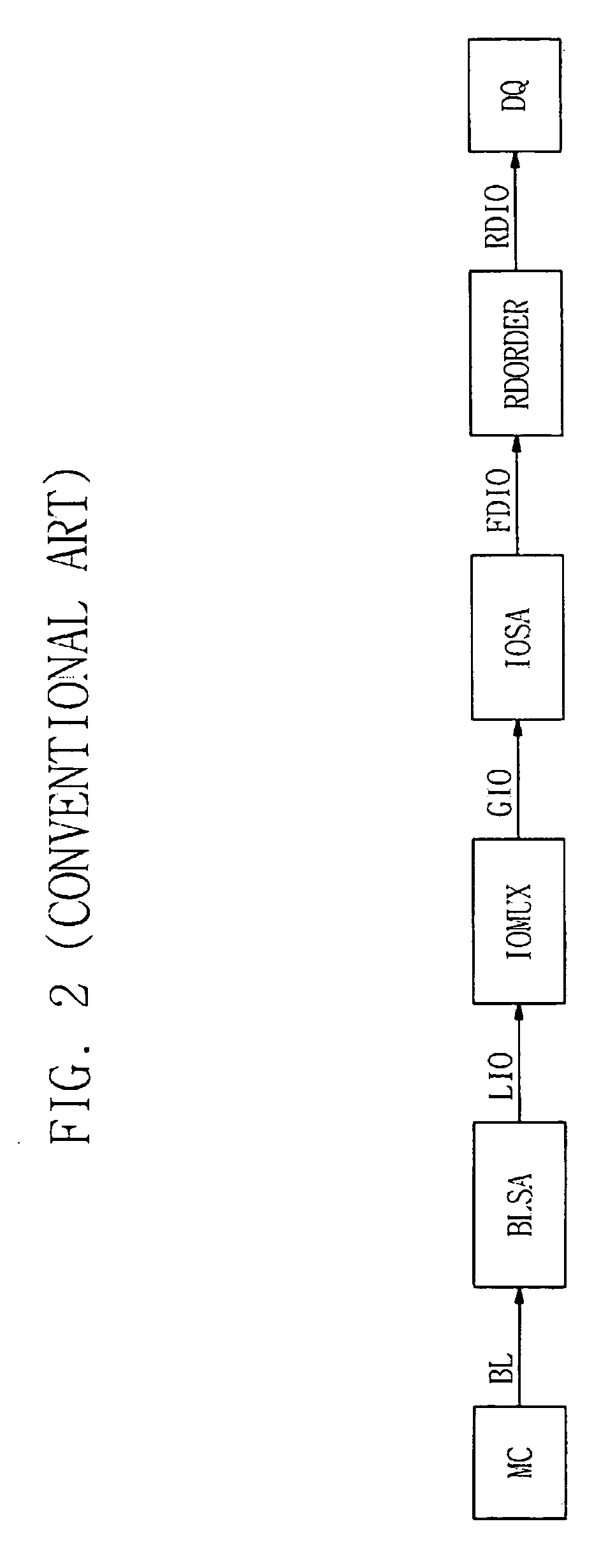

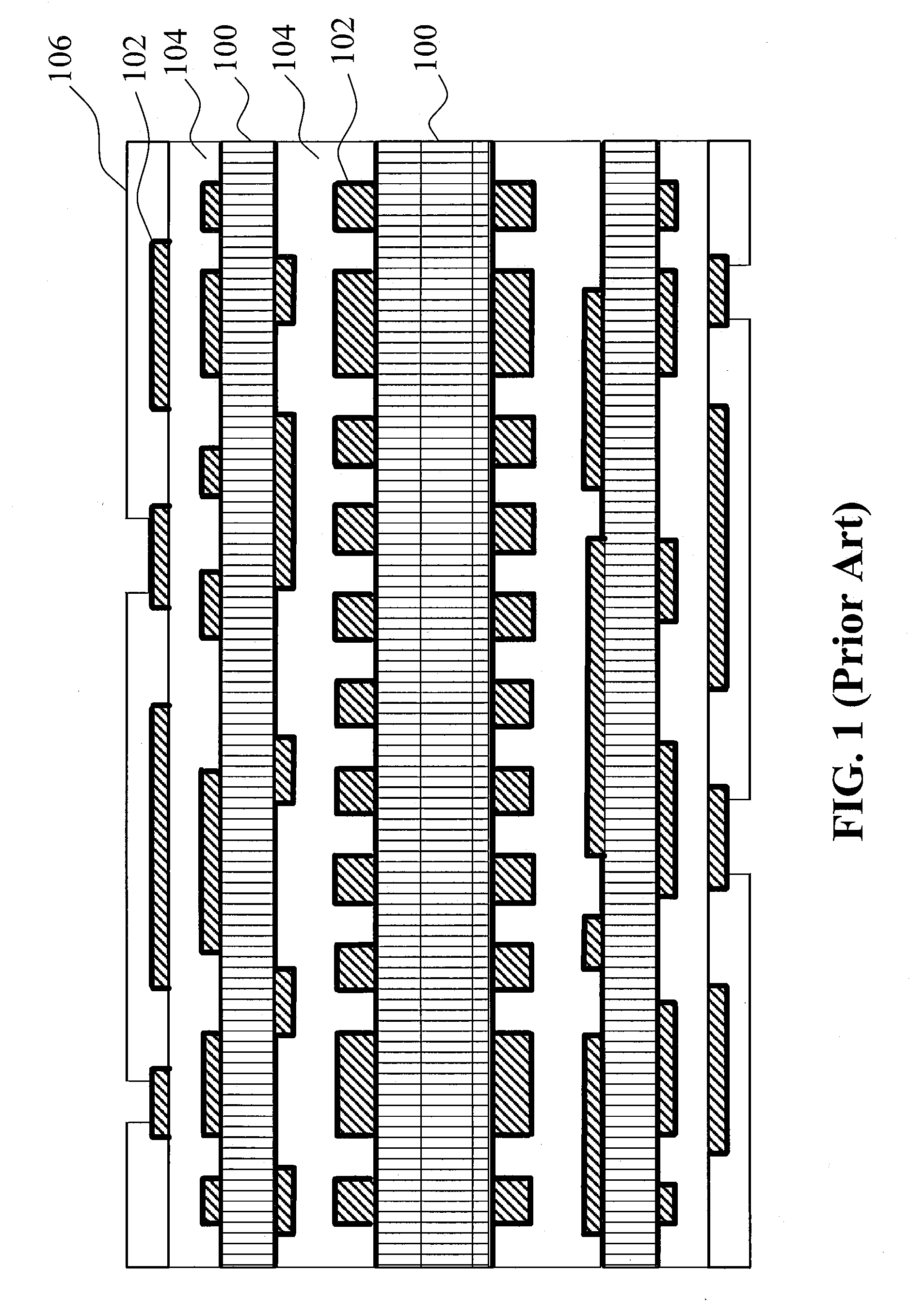

Layout structure of semiconductor memory device having iosa

ActiveUS20080205177A1Improve densityImprove the layout densityDigital storageData transmissionSense amplifier

Embodiments of the invention provide a layout for a semiconductor memory device that splits each memory bank into two blocks. Embodiments of the invention dispose input / output sense amplifiers between the two memory blocks to achieve relatively short global input / output lines to all areas of the memory bank. Shorter global input / output lines have less loading and therefore enable higher-speed data transfer rates. Some embodiments of the invention include column selection line repeaters between the two memory blocks. The column selection line repeaters reduce loading in the column selection lines, and increase column selection speed. Embodiments of the invention include both input / output sense amplifiers and column selection line repeaters disposed between the two memory blocks to increase data transfer rates on the global input / output lines and also increase column selection speed.

Owner:SAMSUNG ELECTRONICS CO LTD

Pattern formation process for an integrated circuit substrate

InactiveUS6881662B2Improve the layout densityQuality improvementMolten spray coatingPhotomechanical apparatusGas phaseEngineering

A pattern formation process for an integrated circuit substrate, which is not employing the conventional method of filling resin material directly in via filling process but adapting the metal spray method, the metal vapor deposition method or any combination thereof to form the pattern including circuits and pads and stuff the vias and the through holes.

Owner:VIA TECH INC

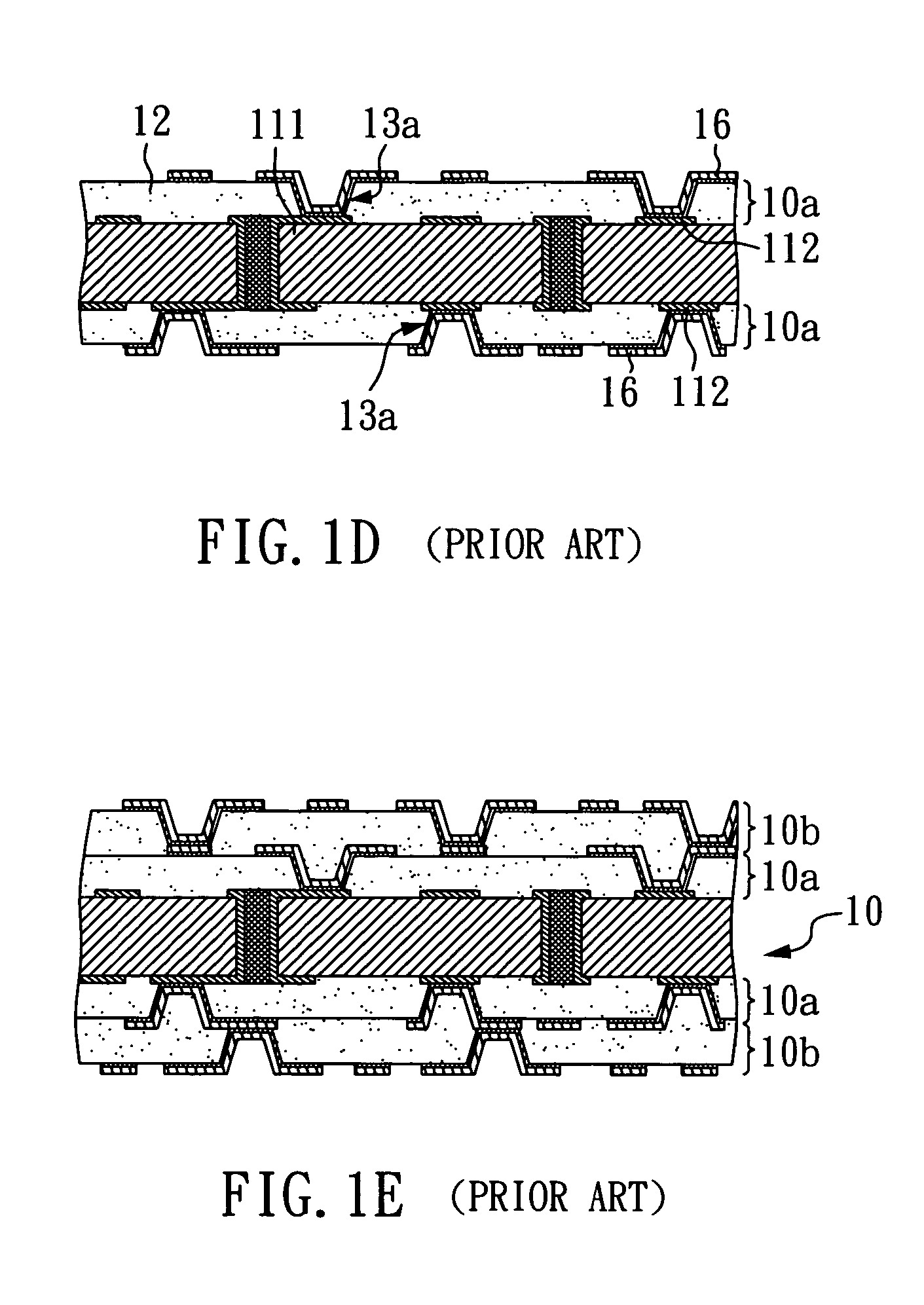

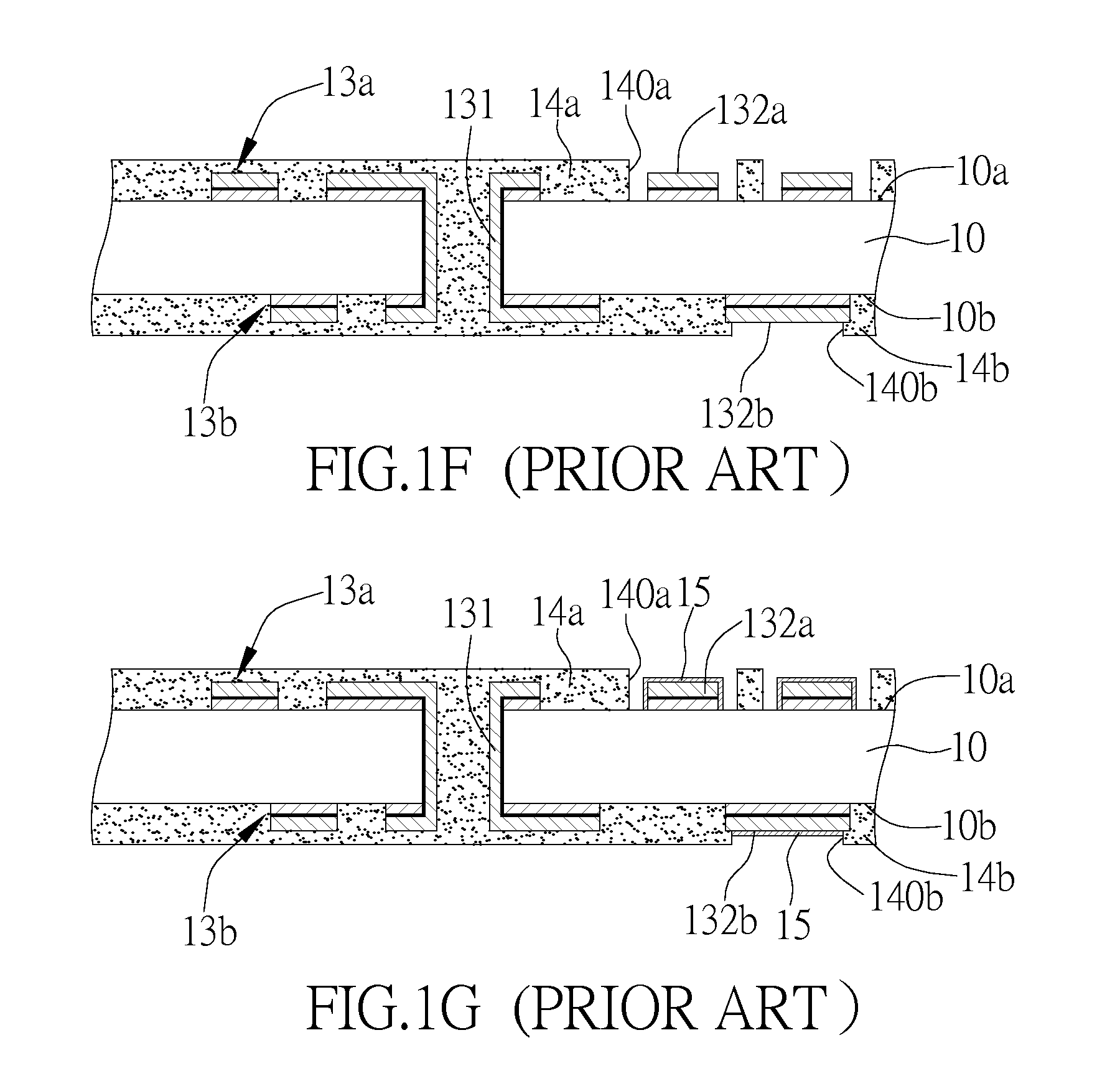

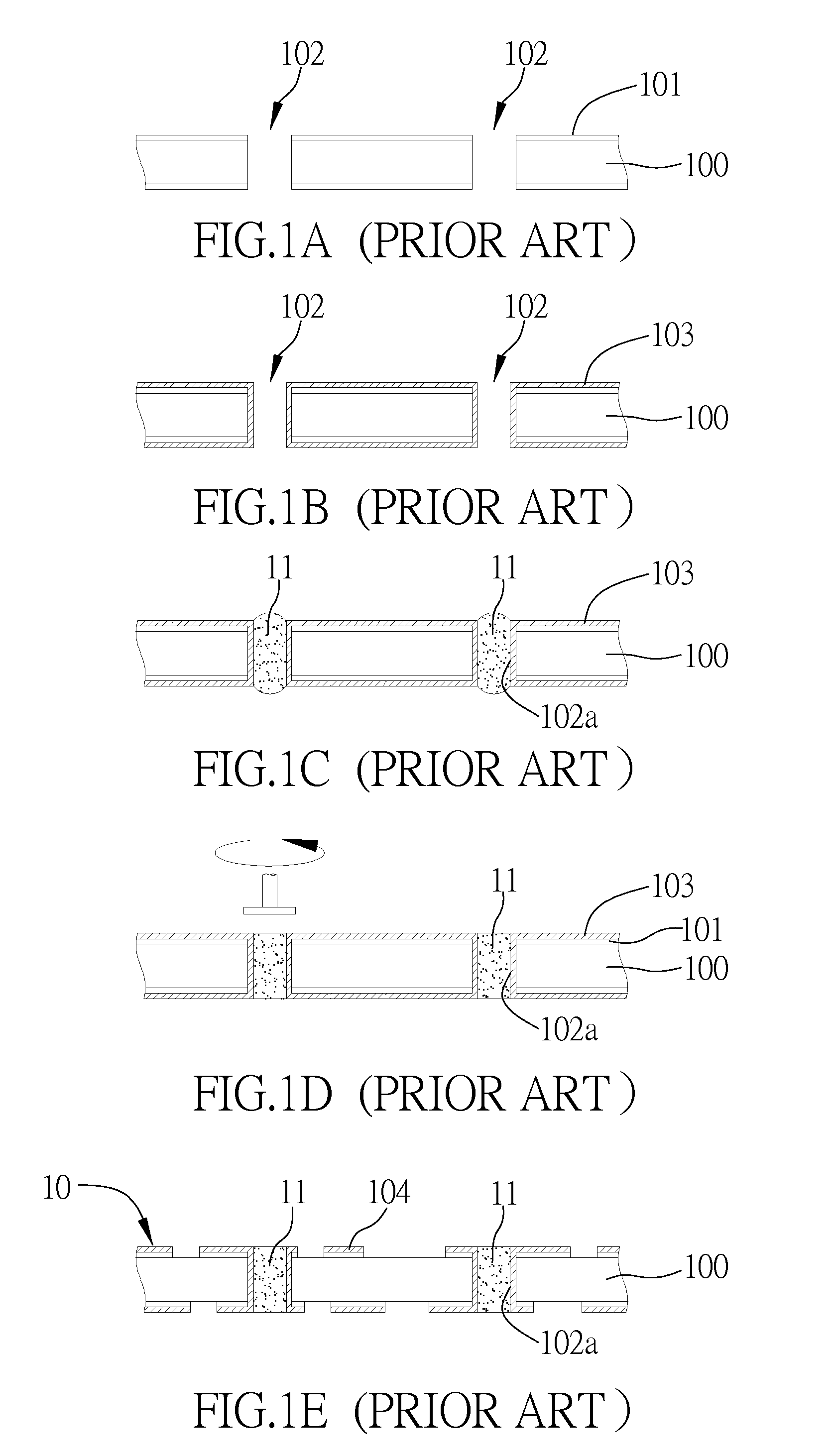

Package substrate having double-sided circuits and fabrication method thereof

InactiveUS20090308652A1Increase density of layoutEnhance electrical connection yieldStacked resist layersPrinted circuit aspectsSolder maskElectrical connection

A package substrate having double-sided circuits and a method of manufacturing the same are proposed. The package substrate includes a core board having a plated through hole, a plurality of first electrical contact pads, and a first solder mask layer formed on the core board. A first wiring layer and a second wiring layer are disposed on two opposite surfaces of the core board, respectively, and electrically connected to the plated through hole. A portion of the first wiring layer is exposed from a first opening formed in the first solder mask layer. The first electrical contact pads are disposed on the exposed portion of the first wiring layer. The top surface of the first electrical contact pads is higher than that of the first wiring layer to thereby allow a semiconductor chip to be mounted on the electrical contact pads for improving electrical connection.

Owner:PHOENIX PRECISION TECH CORP

Pattern formation process for an integrated circuit substrate

InactiveUS20030190799A1Improve the layout densityQuality improvementMolten spray coatingPhotomechanical apparatusIntegrated circuitEngineering

A pattern formation process for an integrated circuit substrate, which is not employing the conventional method of filling resin material directly in via filling process but adapting the metal spray method, the metal vapor deposition method or any combination thereof to form the pattern including circuits and pads and stuff the vias and the through holes.

Owner:VIA TECH INC

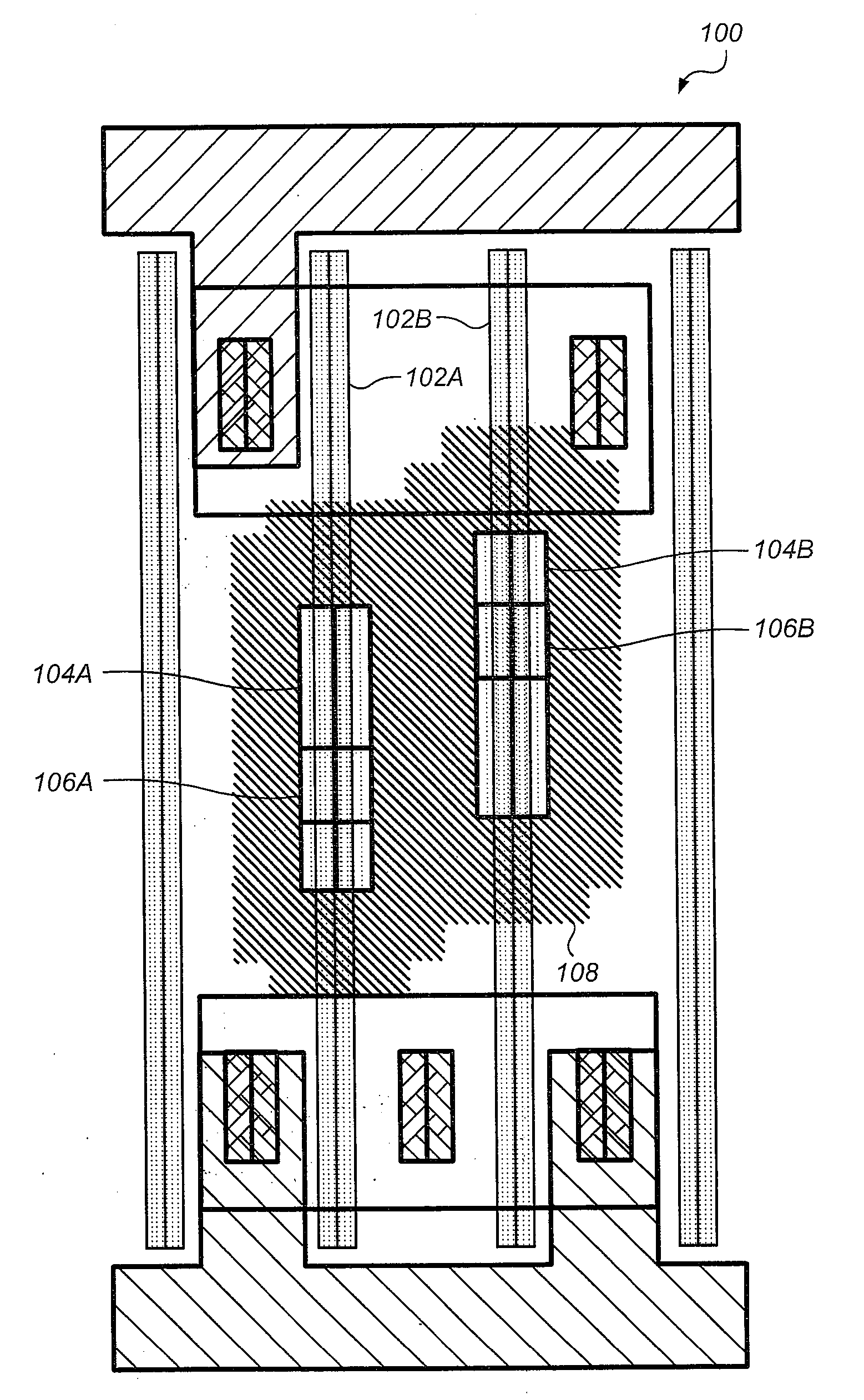

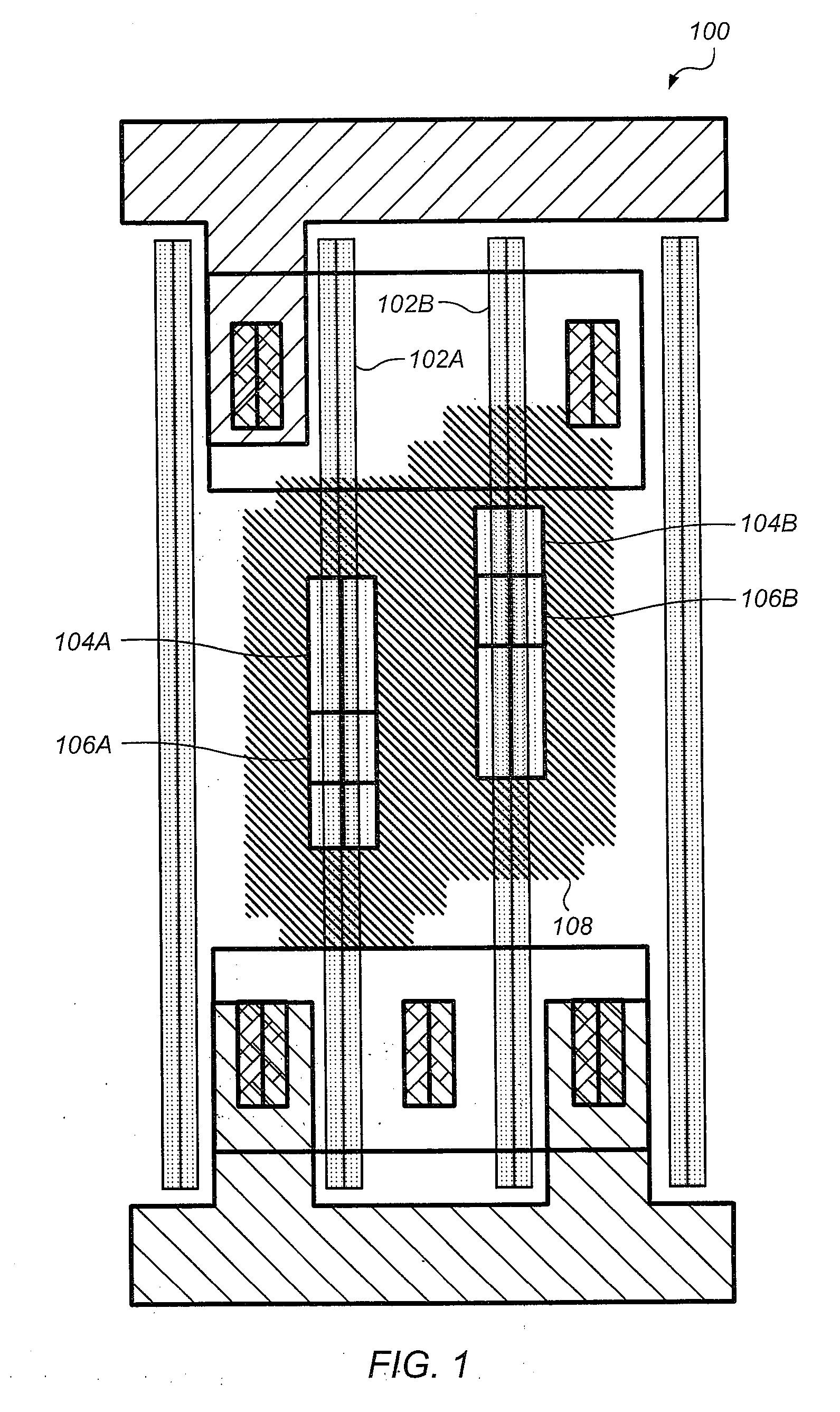

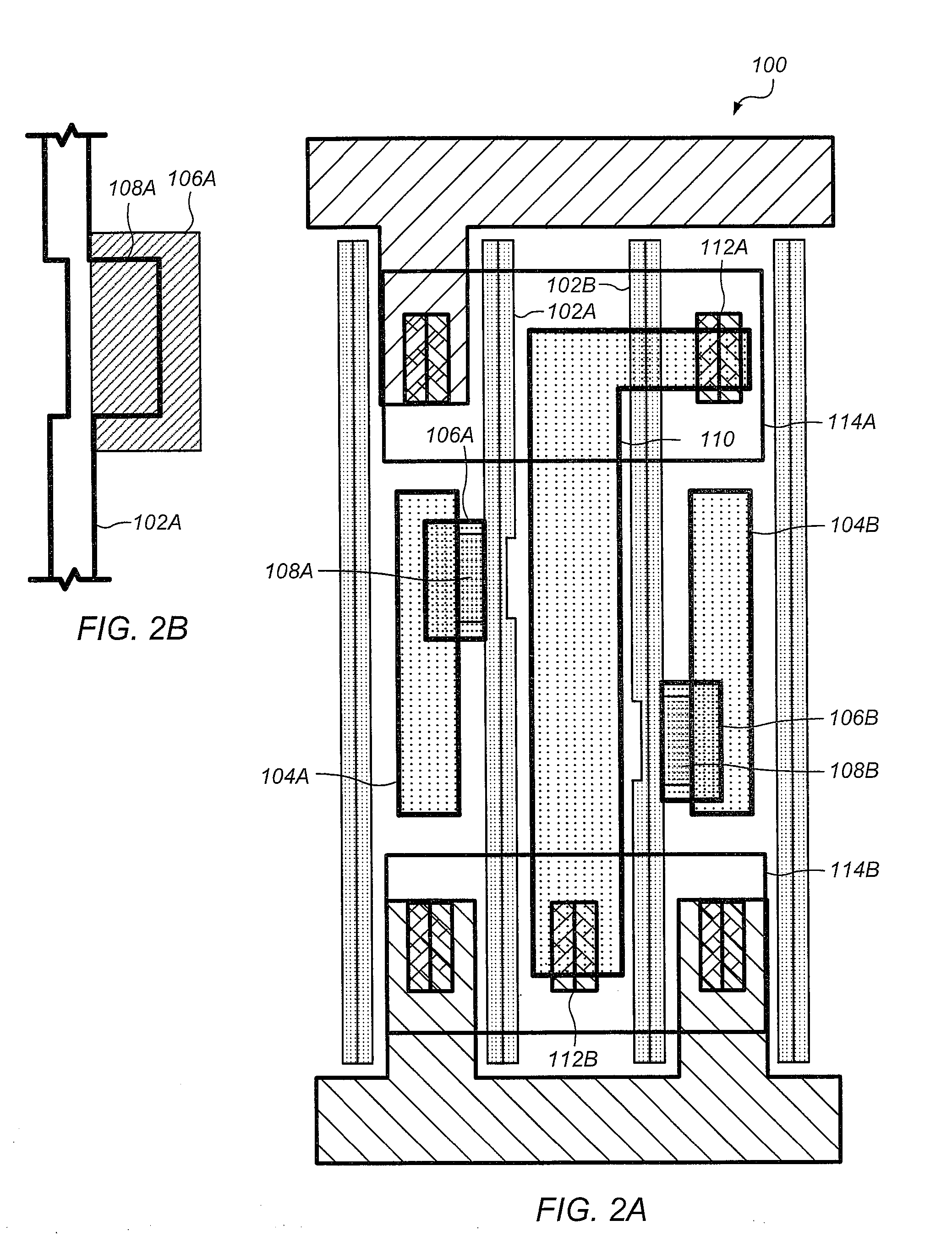

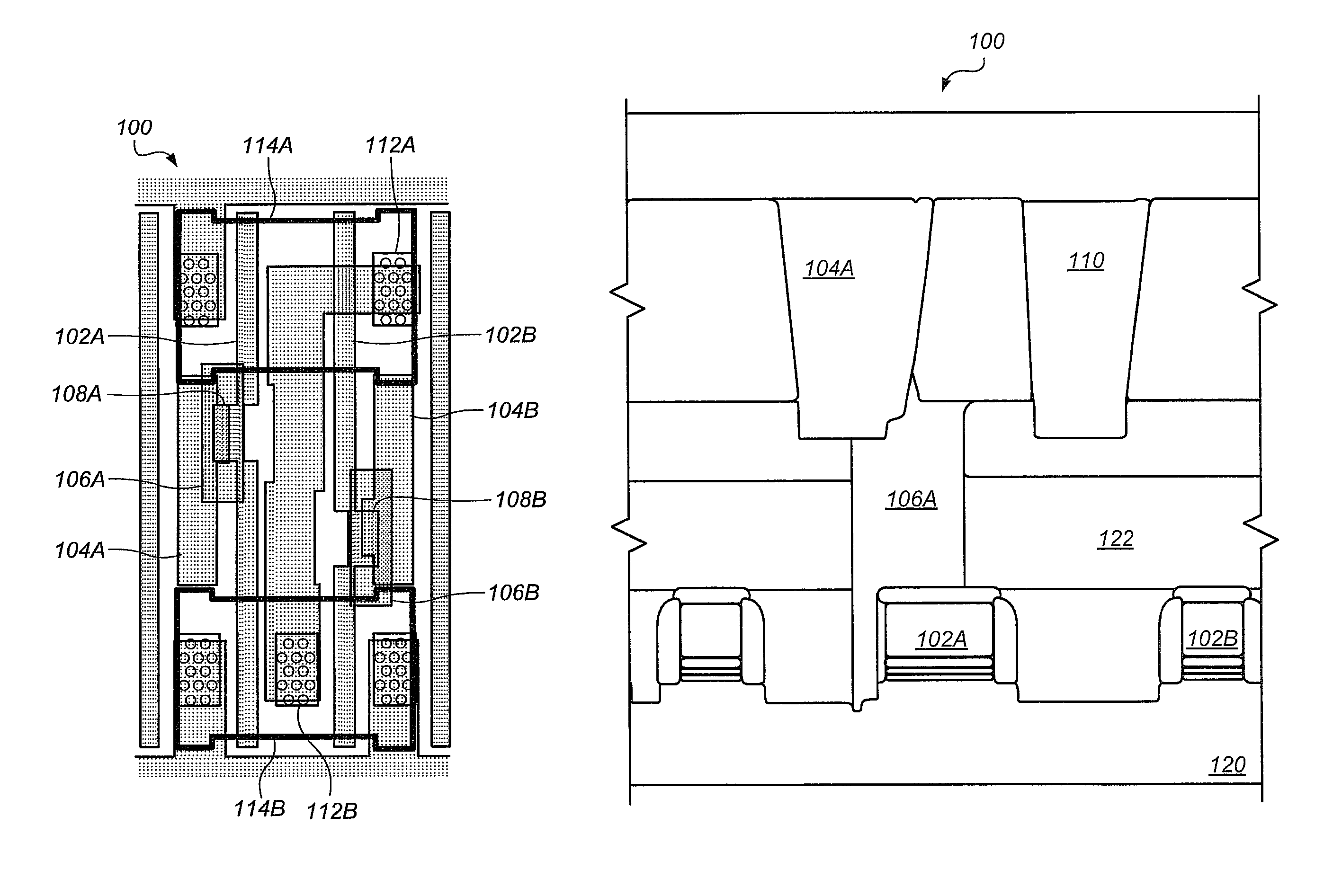

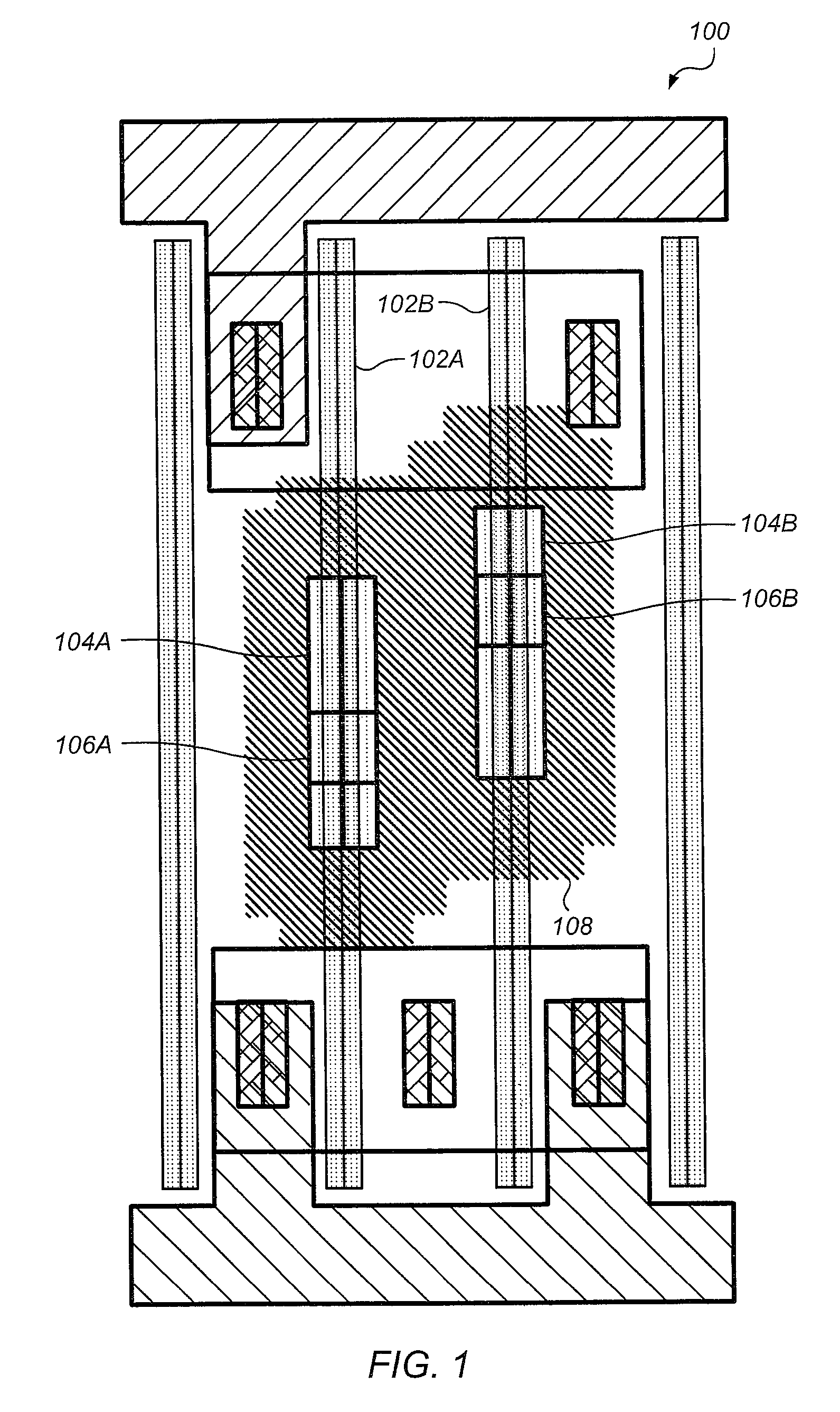

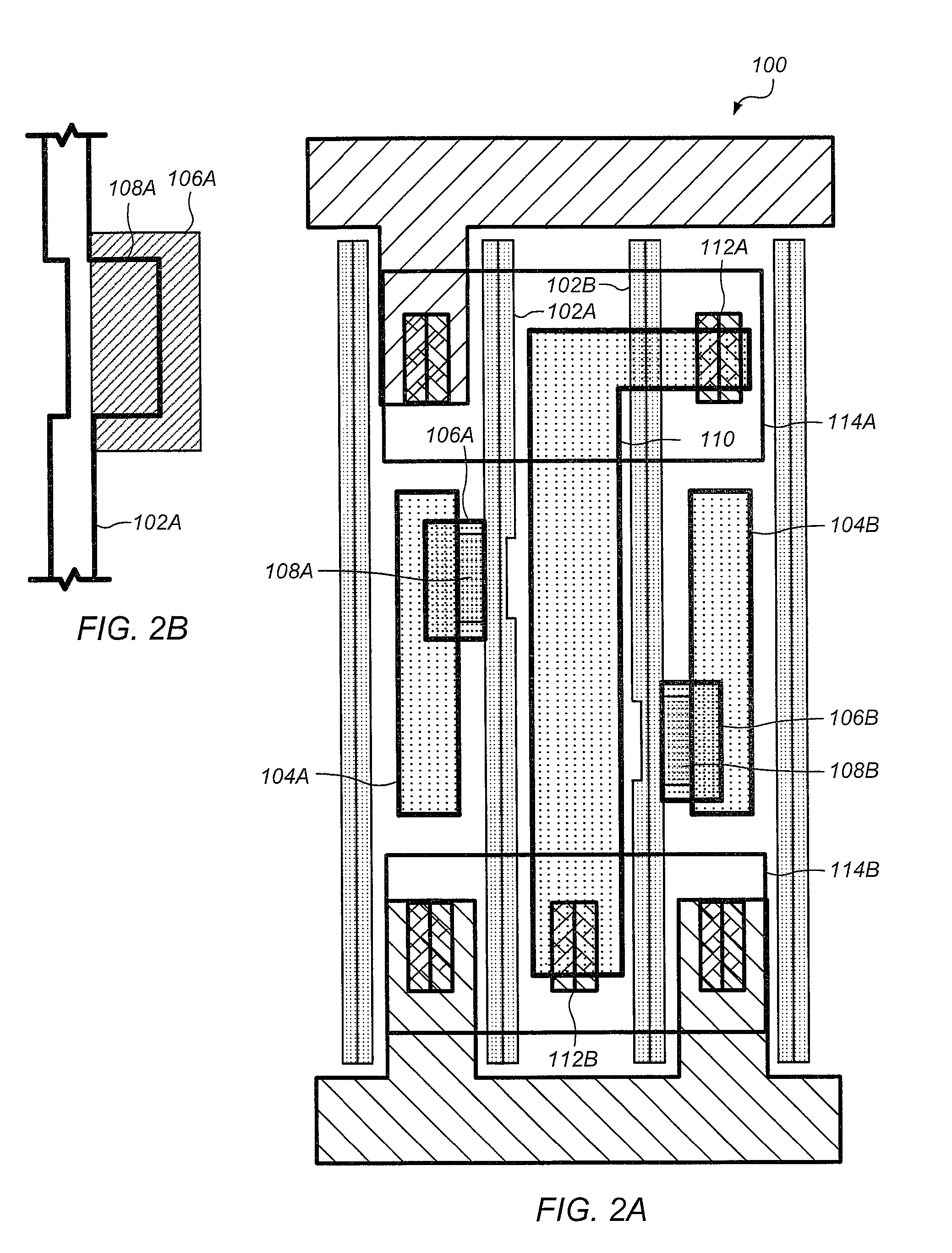

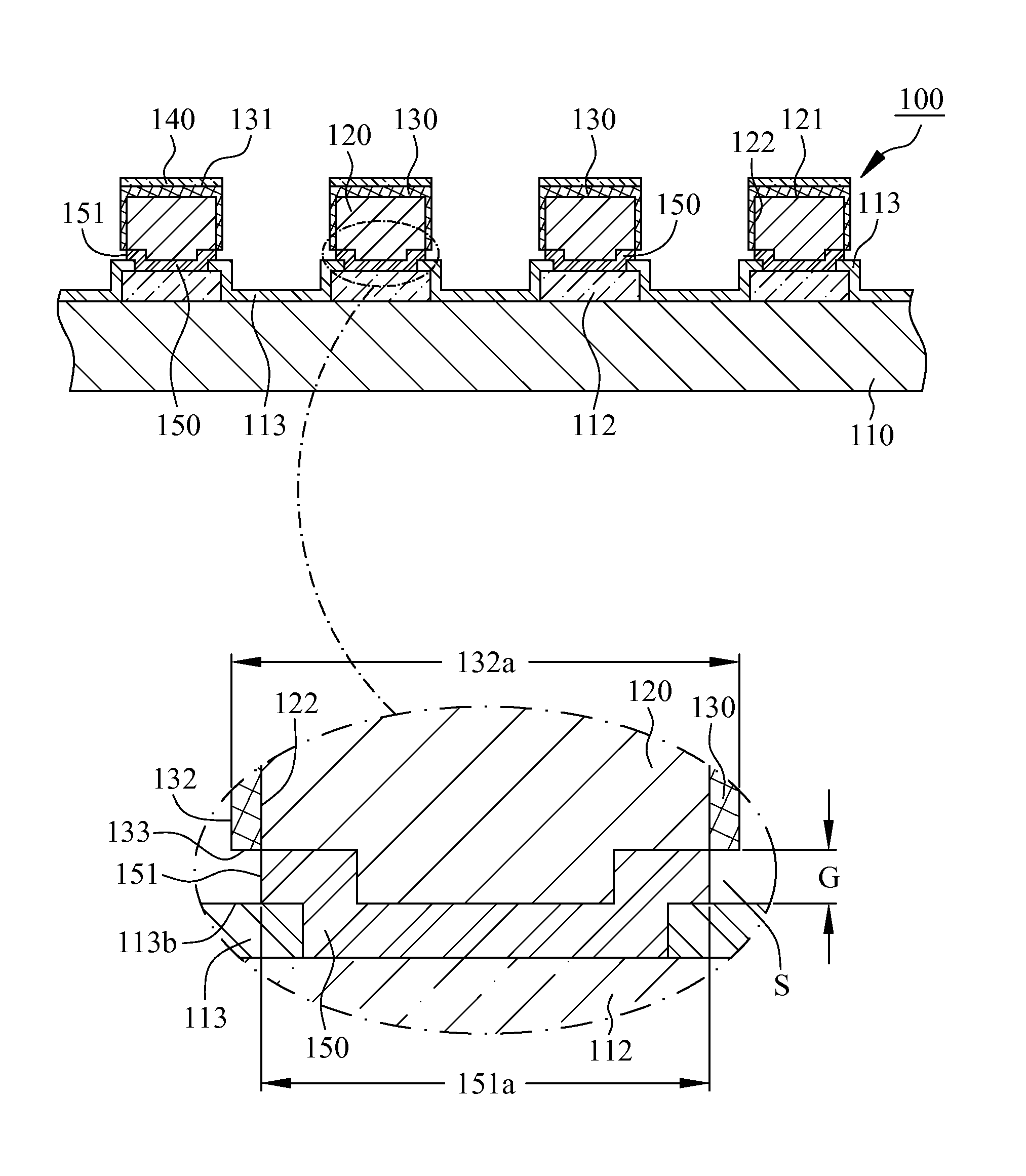

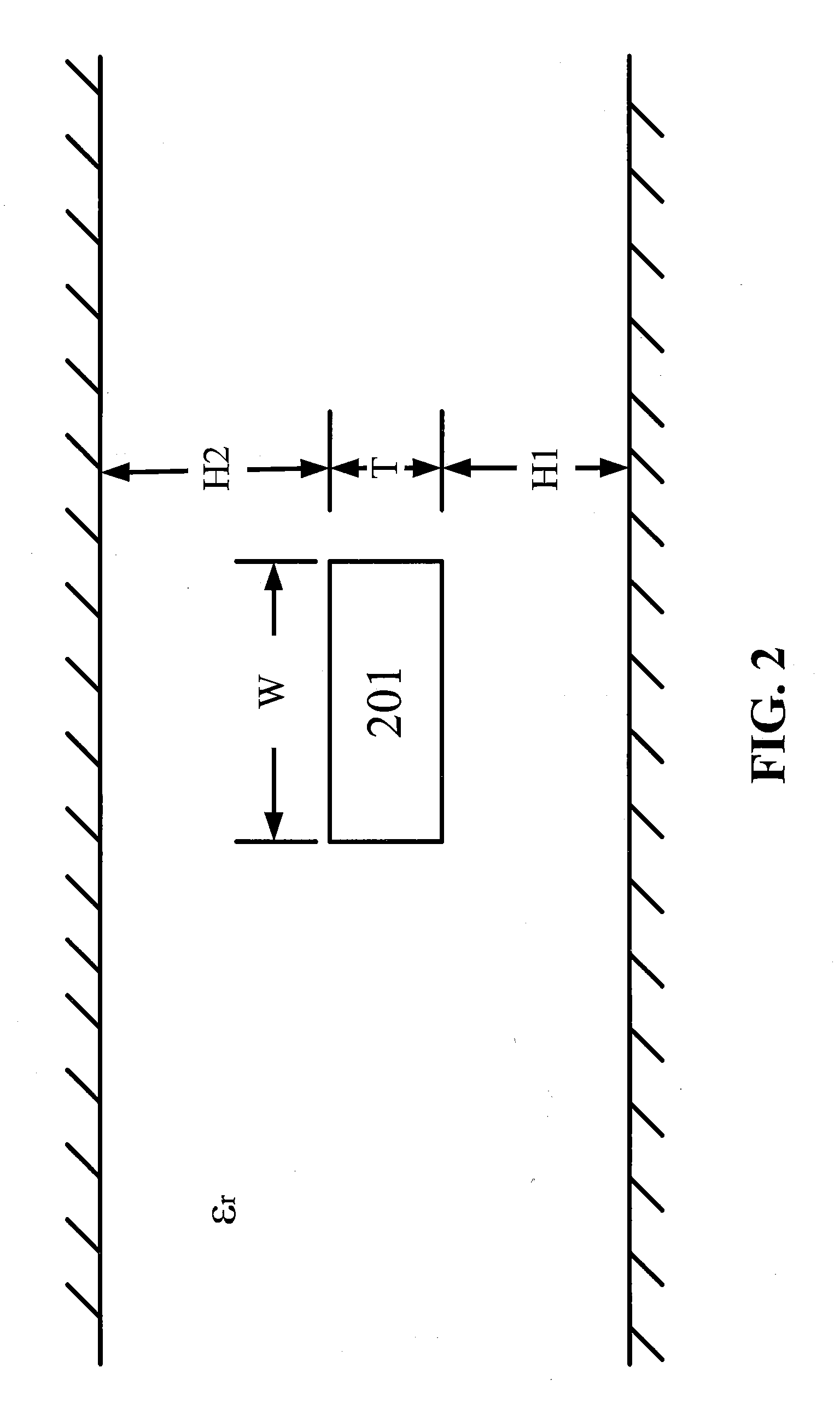

Handshake structure for improving layout density

ActiveUS20110049635A1Improve the layout densityIncrease gate widthTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

A semiconductor device includes a gate on a semiconductor substrate. One side wall of the gate may include at least one protrusion and an opposite side wall of the gate may include at least one depression. A contact is formed through an insulating layer disposed over the gate. The contact at least partially overlaps at least one of the protrusions in the gate. A metal layer is disposed on the insulating layer. The metal layer includes a first structure shifted to a first side of the gate. The first structure at least partially overlaps the contact such that the contact electrically couples the first structure to the gate through the insulating layer.

Owner:ADVANCED MICRO DEVICES INC

Handshake structure for improving layout density

ActiveUS8258578B2Improve the layout densityIncrease gate widthTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

A semiconductor device includes a gate on a semiconductor substrate. One side wall of the gate may include at least one protrusion and an opposite side wall of the gate may include at least one depression. A contact is formed through an insulating layer disposed over the gate. The contact at least partially overlaps at least one of the protrusions in the gate. A metal layer is disposed on the insulating layer. The metal layer includes a first structure shifted to a first side of the gate. The first structure at least partially overlaps the contact such that the contact electrically couples the first structure to the gate through the insulating layer.

Owner:ADVANCED MICRO DEVICES INC

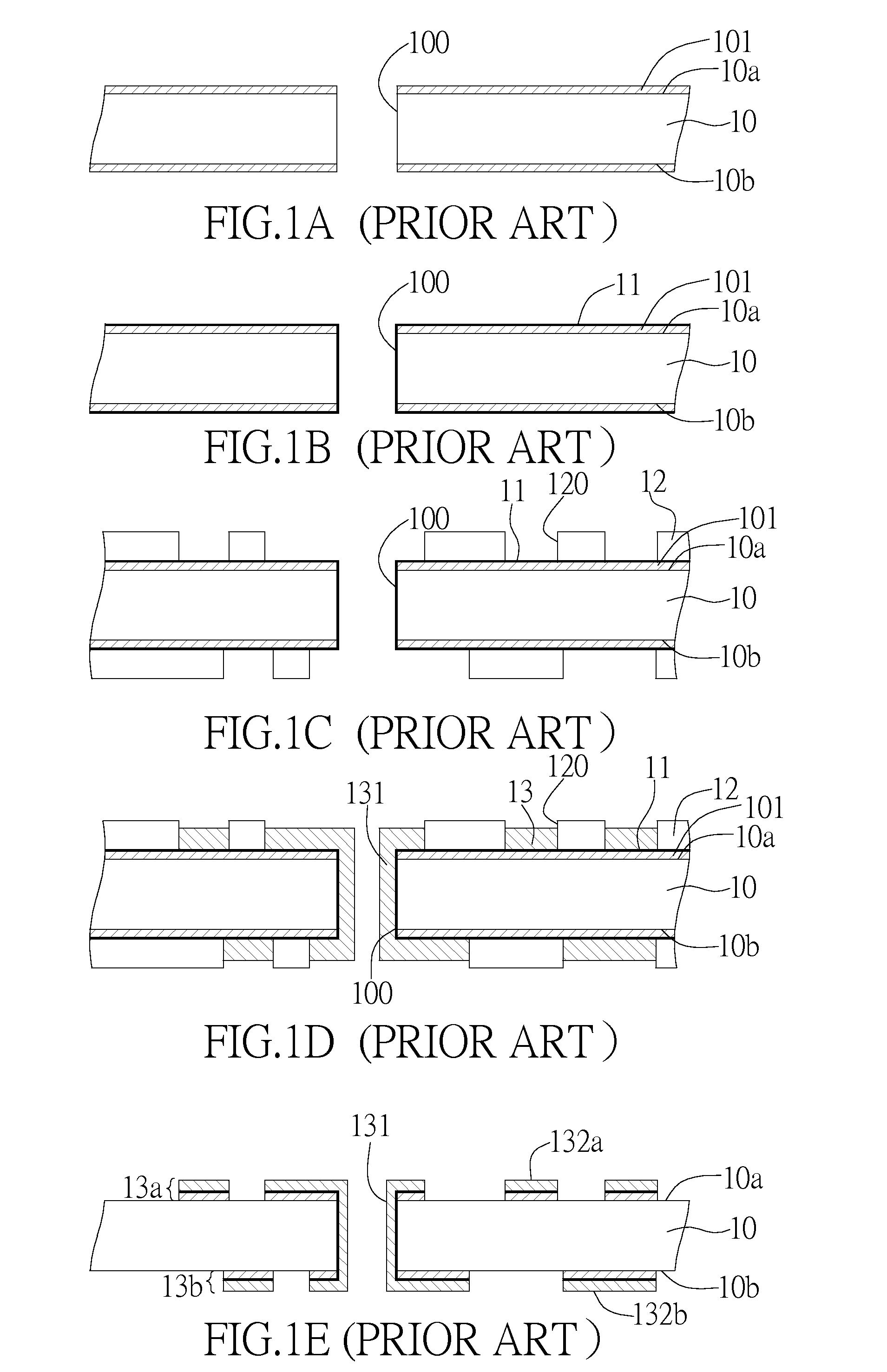

Semiconductor package substrate

ActiveUS20090134515A1High bonding strengthImprove the layout densitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package substrate includes a main body with a surface having a first circuit layer thereon and a dielectric layer covering the first circuit layer, with a plurality of vias on a portion of the first circuit layer; a plurality of first conductive vias disposed in the vias; a plurality of first electrically connecting pads on the first conductive vias and completely exposed on the dielectric layer having no extending circuits for a semiconductor chip to be mounted thereon, the first electrically connecting pad being electrically connected to the first circuit layer of the first conductive via; and an insulating protective layer disposed on the main body with an opening for completely exposing the first electrically connecting pads, whereby the circuit layout density is increased without disposing circuits between the electrically connecting pads.

Owner:PHOENIX PRECISION TECH CORP

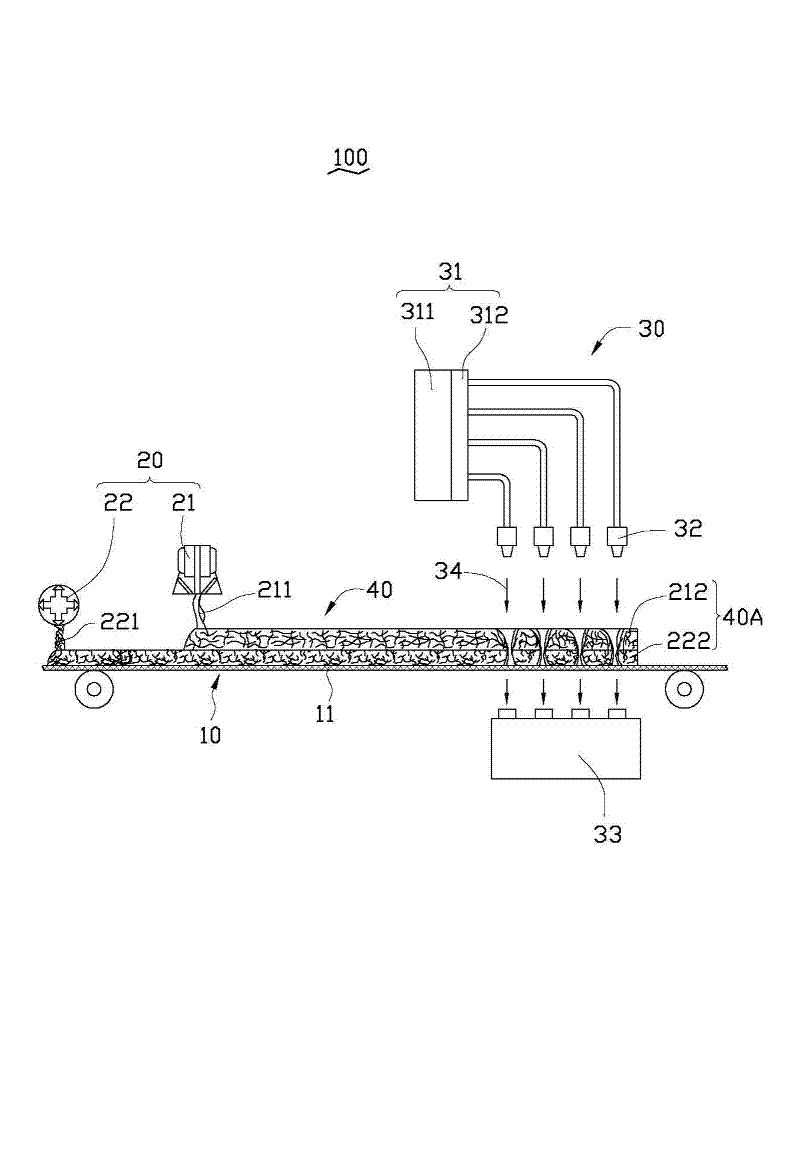

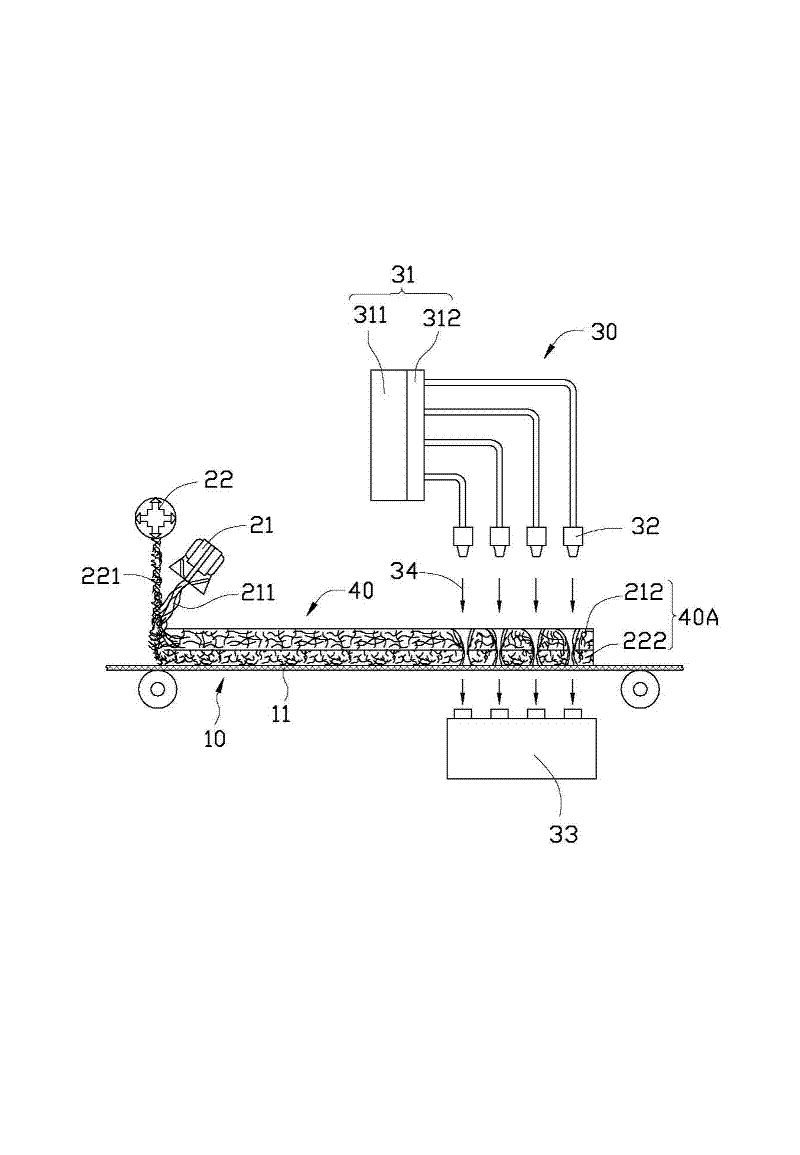

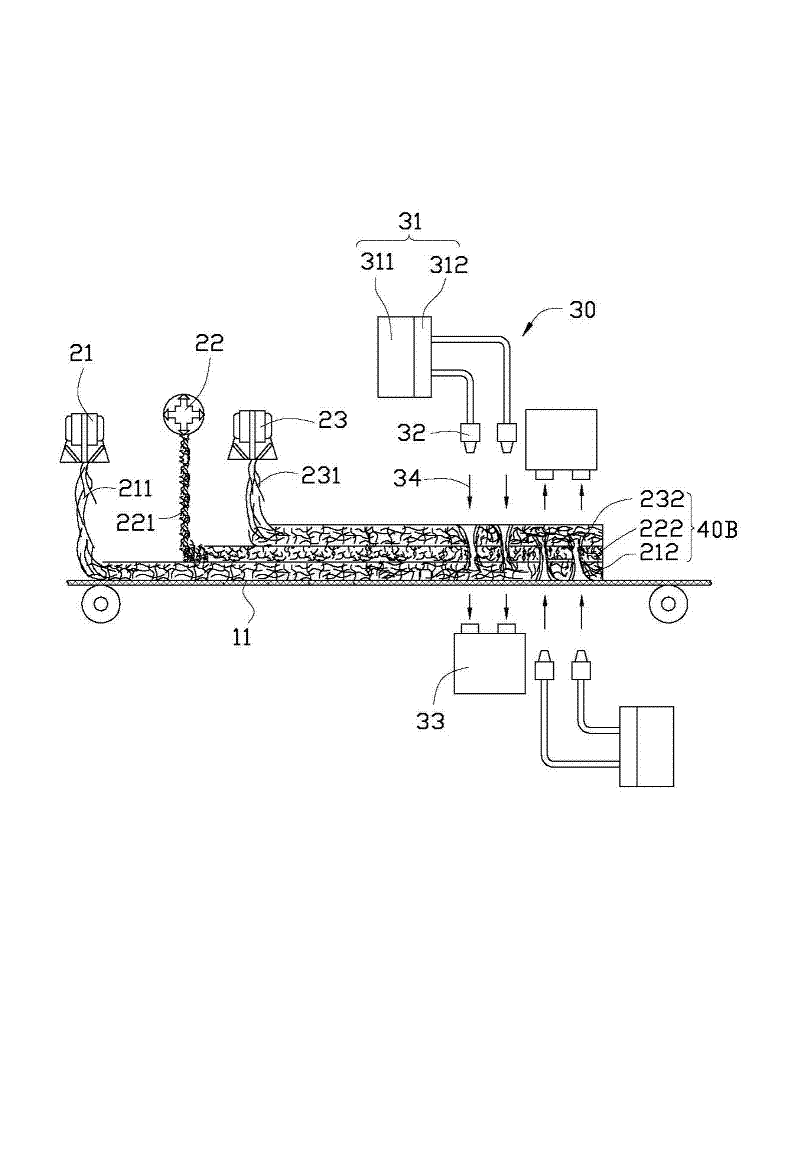

Production equipment of compound non-woven fabric absorber, process and compound non-woven fabric absorber

InactiveCN102535010AImprove the layout densityReduce the packing densityNon-woven fabricsFiber layerWoven fabric

The invention relates to production equipment of compound non-woven fabric absorber, which comprises a transmission unit, a lapping unit and a consolidating unit. The lapping unit is used to form a non-woven fabric fiber compound on the transmission unit and the non-woven fabric fiber compound is formed by at least a first thermally melting fiber layer and a hydrophilic fiber layer that are laminated. The transmission unit is used to transmit the non-woven fabric fiber compound in a predetermined transmission direction. the consolidating unit is used to provide at least a pulse hot air which is used to spray and impact the non-woven fabric fiber compound so as to soften the thermally melt fiber of the first thermally melting fiber layer and introduce the softened thermally melt fiber into the hydrophilic fiber layer so as to form consolidating points. The invention further relates to a preparation process of the compound non-woven fabric absorber and the compound non-woven fabric absorber.

Owner:GOLD HONG YE PAPER

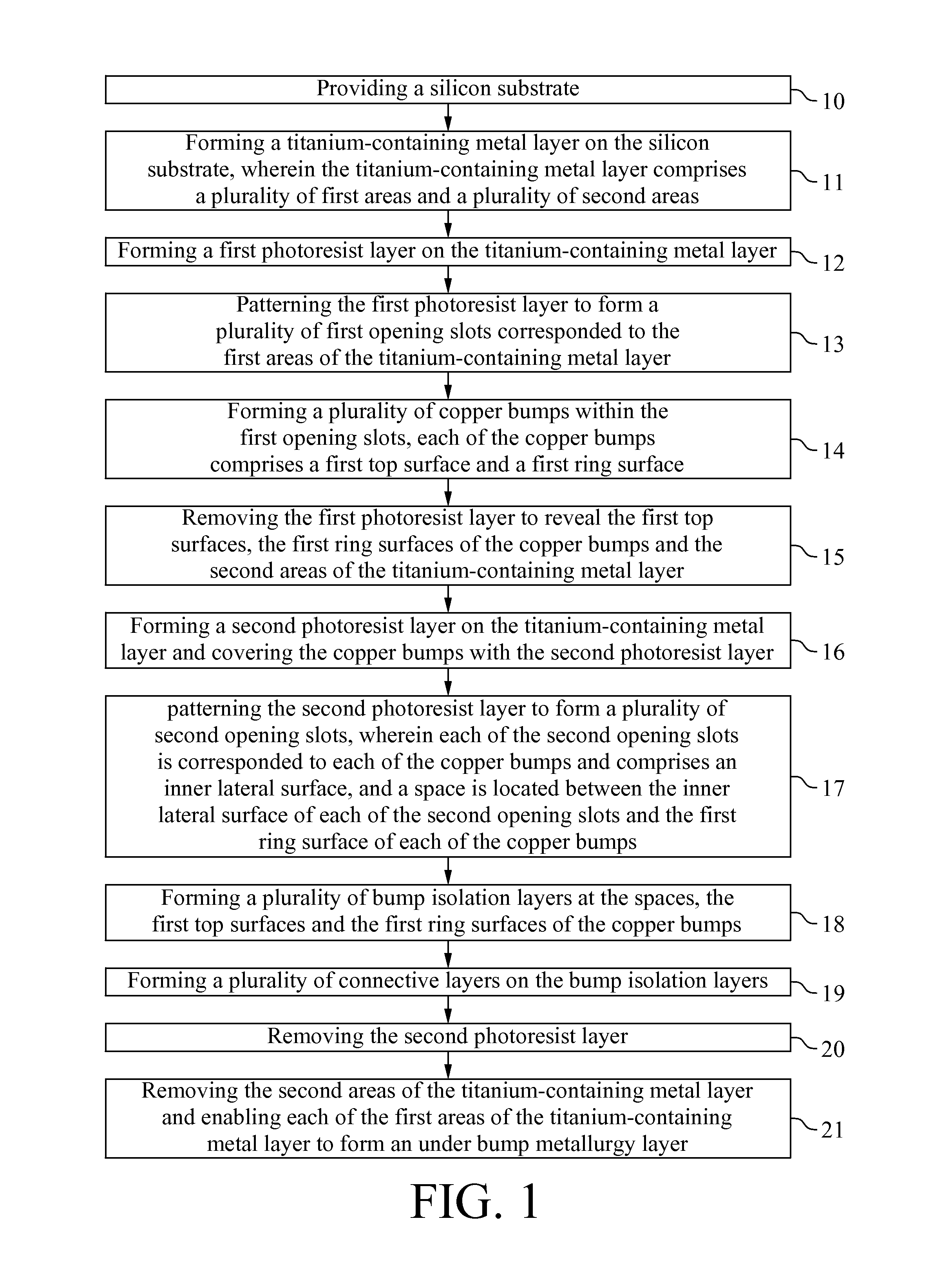

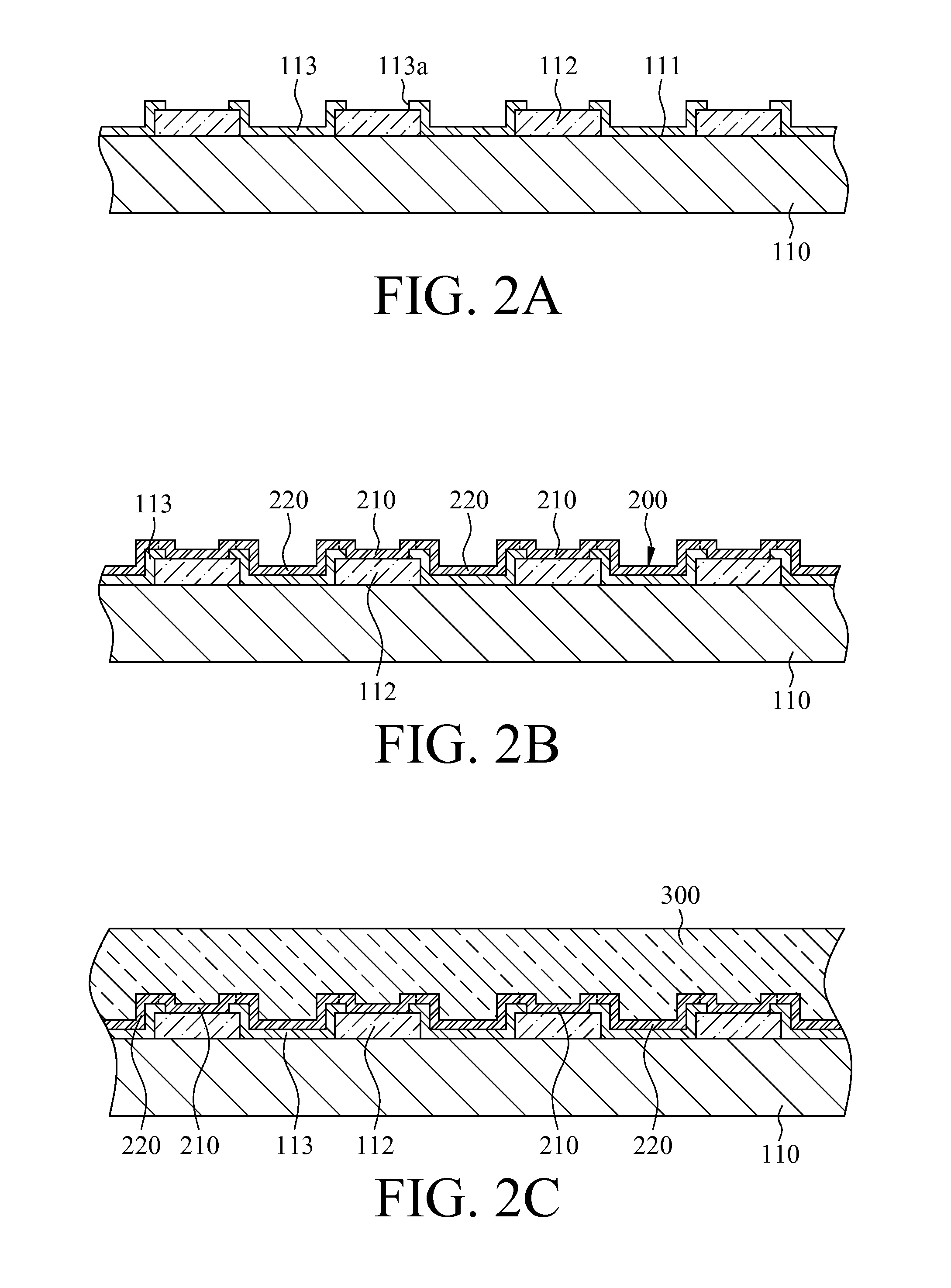

Bumping process and structure thereof

InactiveUS20130193570A1Increase circuit layout densityDistanceSemiconductor/solid-state device detailsSolid-state devicesMetallurgyIsolation layer

A bumping process includes providing a silicon substrate; forming a titanium-containing metal layer on silicon substrate, the titanium-containing metal layer comprises a plurality of first areas and a plurality of second areas; forming a first photoresist layer on titanium-containing metal layer; patterning the first photoresist layer to form a plurality of first opening slots; forming a plurality of copper bumps within first opening slots, said copper bump comprises a first top surface and a first ring surface; removing the first photoresist layer; forming a second photoresist layer on titanium-containing metal layer; patterning the second photoresist layer to form a plurality of second opening slots; forming a plurality of bump isolation layers at spaces, the first top surfaces and the first ring surfaces; forming a plurality of connective layers on bump isolation layers; removing the second photoresist layer, removing the second areas to form an under bump metallurgy layer.

Owner:CHIPBOND TECH

Coreless package substrate and fabrication method thereof

ActiveCN102867798ASolve alignment problemsSimple manufacturing methodSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

Owner:UNIMICRON TECH CORP

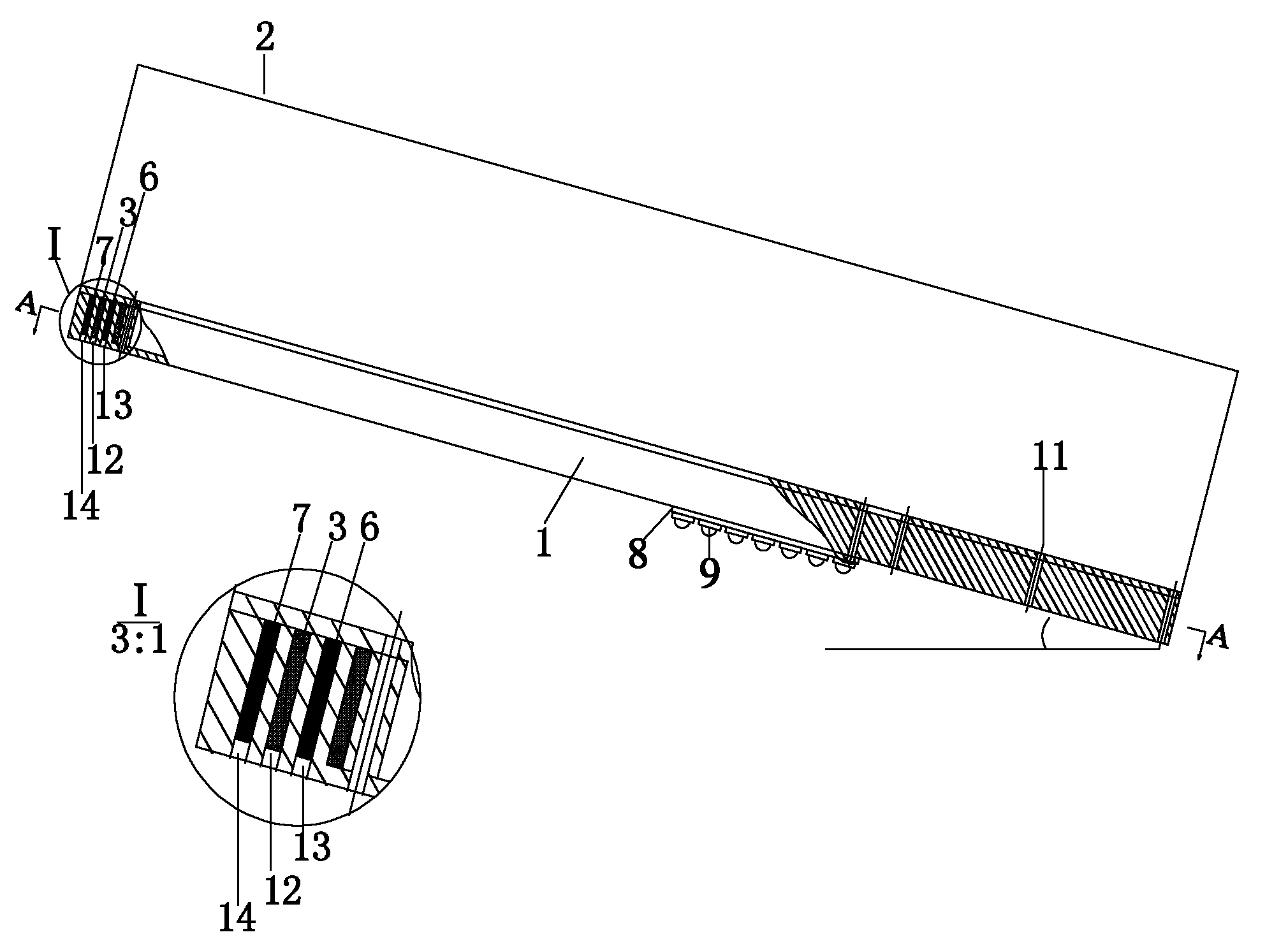

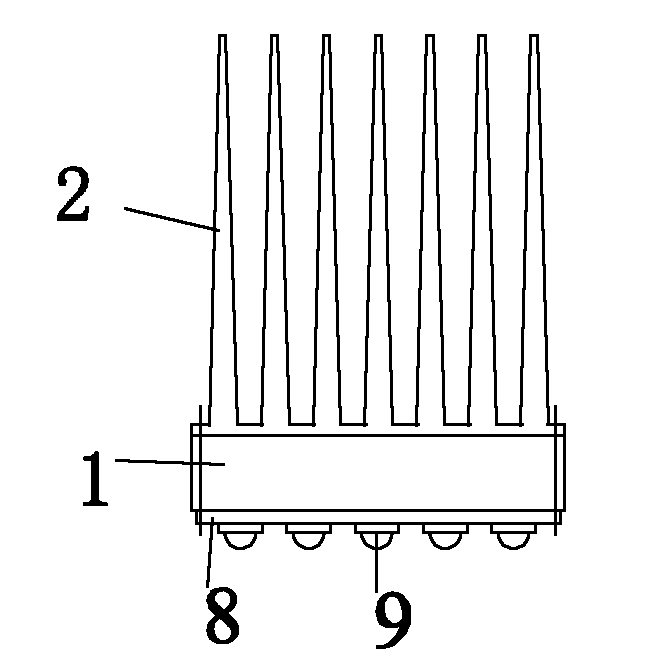

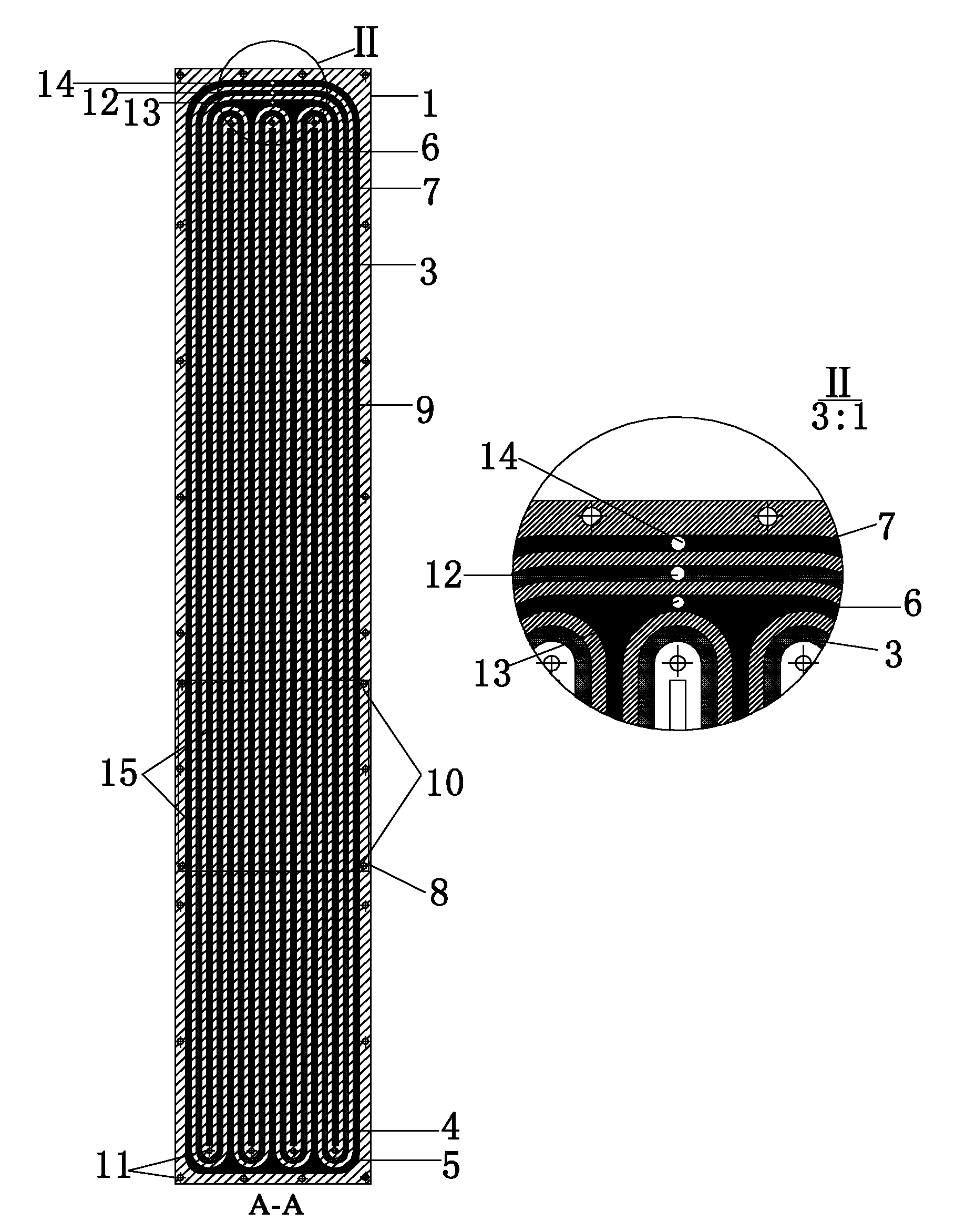

Combined planar heat pipe radiator used for cooling light emitting diode (LED)

InactiveCN101886801AImprove startup performanceImprove cooling effectPoint-like light sourceLighting heating/cooling arrangementsDie castingEngineering

The invention discloses a combined planar heat pipe radiator used for cooling a light emitting diode (LED) in the technical field of LEDs. The combined planar heat pipe radiator comprises an aluminium plate, a die-casting heat pipe set channel fin cover plate, pulse heat pipe channels and shared channels, wherein each shared channel consists of an internal mesh heat pipe set channel, an external mesh heat pipe set channel, an internal gravity heat pipe set channel and an external gravity heat pipe set channel; the pulse heat pipe channels have an independent sealed annular structure comprising a plurality of bending sections and are uniformly distributed on the inner surface of the whole aluminium plate; and the shared channels are arranged inside the pulse heat pipe channels in a staggered mode. The combined planar heat pipe radiator, as a novel large-power LED cooling method, has the advantages of large radiation area, high radiation efficiency and startup performance, light weight, high temperature uniformity, compact structure and convenient process.

Owner:SHANGHAI JIAO TONG UNIV

Method for manufacturing PCB (printed circuit board), PCB and device

ActiveCN101790277AImprove the layout densityPrinted circuit assemblingElectrical connection printed elementsEngineeringPrinted circuit board

The invention discloses a method for manufacturing a PCB (printed circuit board), a PCB and a device. Blind holes are respectively arranged on the two surfaces of the PCB provided by the embodiment of the invention, and are used for pressing in pins of connectors so as to realize opposite pressing of the connectors arranged on the two surfaces of the PCB. The blind holes are adopted to avoid the problem of mutual signal interference due to that two pins with different attributes are located in the same hole when in opposite pressing; namely, the scheme provided by the embodiment of the invention has requirements neither for the attributes of the pins of the connectors nor for the layout of the connectors on the two surfaces of the PCB, thereby not only improving the layout density of the connectors on the PCB, but also creating wide application range.

Owner:HUAWEI TECH CO LTD

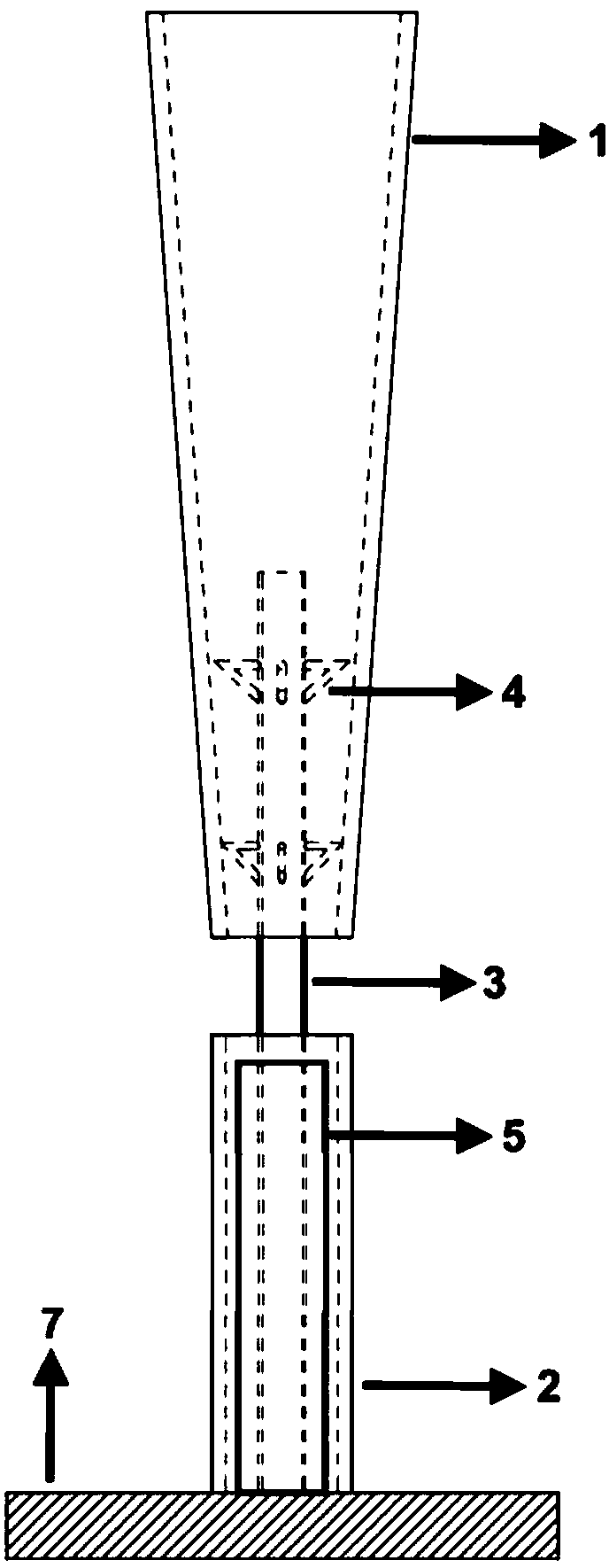

Blade-free wind power generation device based on vortex vibration theory and electromagnetic induction theory

PendingCN108278180ALarge windward sideEnhanced vortex effectWind motor combinationsMachines/enginesEngineeringFan blade

The invention discloses a blade-free wind power generation device based on a vortex vibration theory and an electromagnetic induction theory. The blade-free wind power generation device comprises a hollow thin-wall cylinder, wherein the hollow thin-wall cylinder is in an inverted circular truncated cone shape. The hollow thin-wall cylinder is installed on a connecting rod through a fixing device,the hollow thin-wall cylinder and the connecting rod are installed in an erected mode, and the bottom of the connecting rod is fixed to a foundation. A permanent magnet which synchronously swings along with the connecting rod sleeves the connecting rod located at the bottom of the hollow thin-wall cylinder. A plurality of closed electromagnetic induction coils are laid outside the permanent magnet, and when the permanent magnet synchronously swings along with the connecting rod, magnetic induction lines of the permanent magnet alternately cut the electromagnetic induction coils to generate thecurrent. By the adoption of the blade-free wind power generation device based on the vortex vibration theory and the electromagnetic induction theory, no conventional fan blades are required, a magnetic field is generated by the use of vortex vibration to conduct cutting, and then electric energy is formed; and the wind load in any wind direction can be received, and the situation that an additional device is needed to guide the wind direction so as to obtain the maximum wind energy is not required.

Owner:杭州科以才成科技有限公司

Circuit board structure and fabrication method thereof

ActiveUS20100187003A1MiniaturizationAvoid layeringPrinted circuit aspectsSolid-state devicesEngineeringBoard structure

Provided are a circuit board structure and a fabrication method thereof, including the steps of: forming a first circuit layer in a first dielectric layer and exposing the first circuit layer therefrom; forming a second dielectric layer on the first dielectric layer and the first circuit layer, and forming a second circuit layer on the second dielectric layer; forming a plurality of first conductive vias in the second dielectric layer for electrically connecting to the first circuit layer to thereby dispense with a core board and electroplated holes and thus facilitate miniaturization. Further, the first dielectric layer is liquid before being hardened and is formed on the first dielectric layer that enhances the bonding between layers of the circuit board and the structure.

Owner:UNIMICRON TECH CORP

Display panel and electronic device

InactiveCN110379832AImprove color castImprove the layout densitySolid-state devicesSemiconductor devicesUltrasound attenuationColor shift

The invention relates to a display panel and an electronic device. The display panel comprises a first display region and a second display region. The curvature of the first display region is smallerthan the curvature of the second display region. The pixel density in the first display region is less than the pixel density in the second display region. The arrangement density of the red pixels inthe second display region is increased, so that the attenuation of red light at a large viewing angle can be reduced, thereby improving the color shift degree of the display panel at the large viewing angle.

Owner:YUNGU GUAN TECH CO LTD

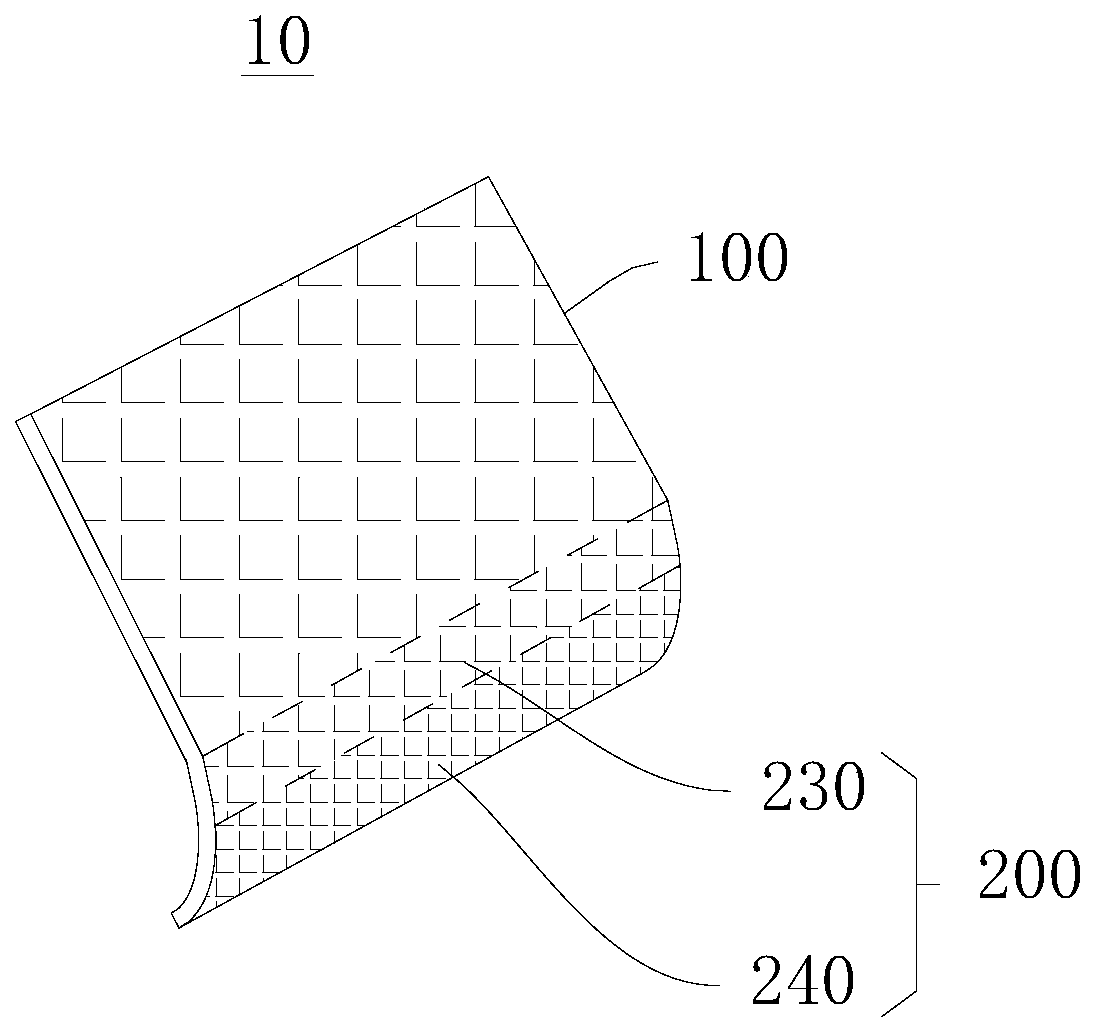

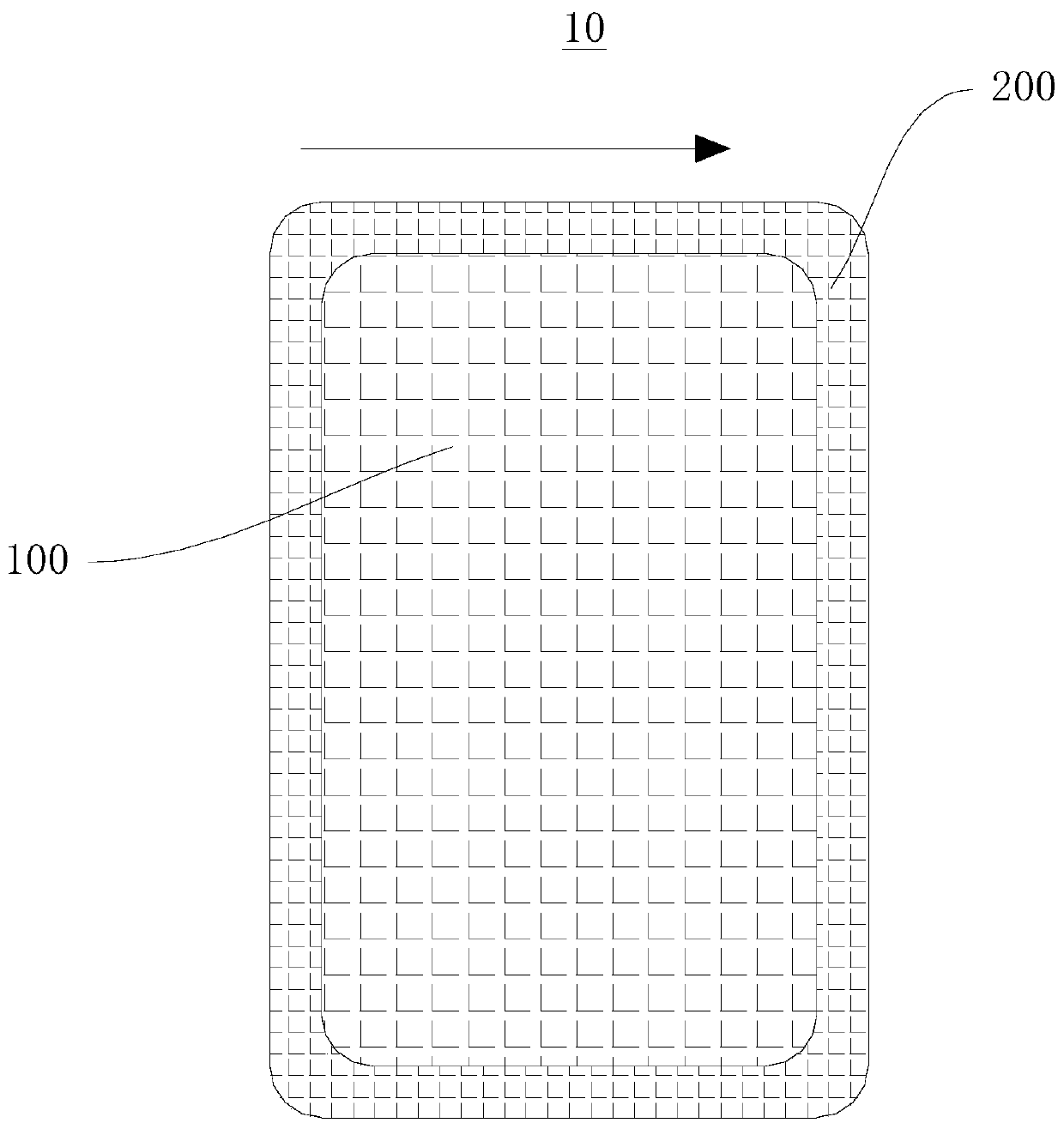

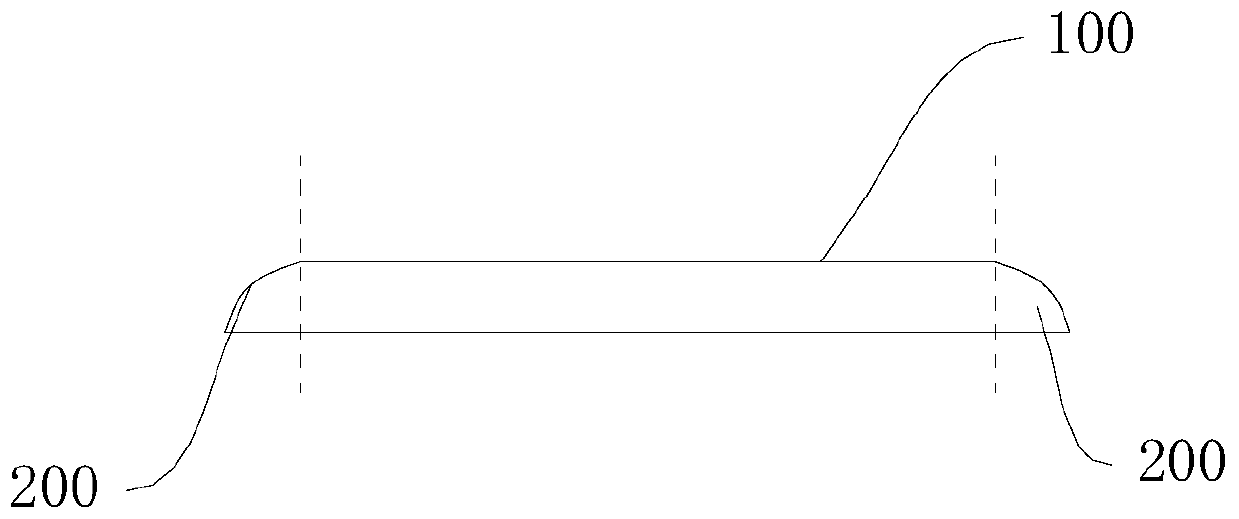

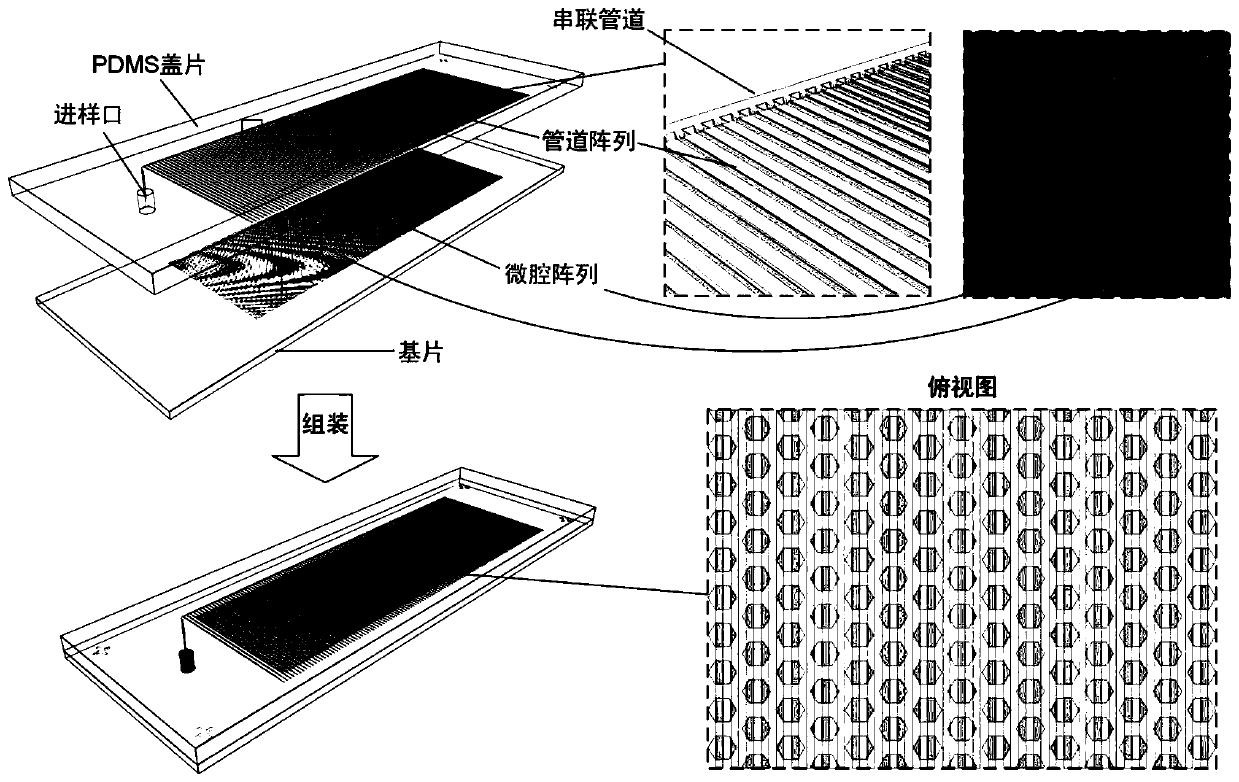

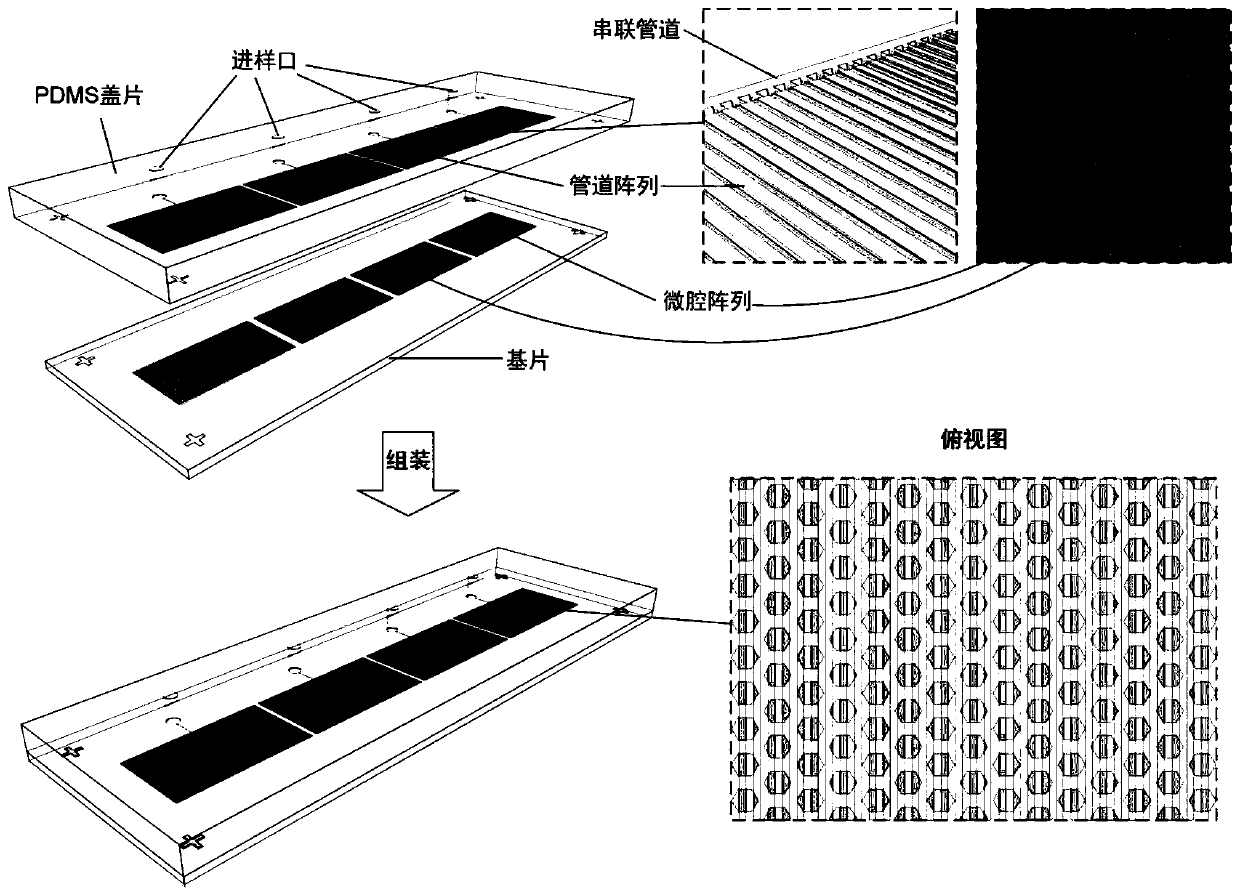

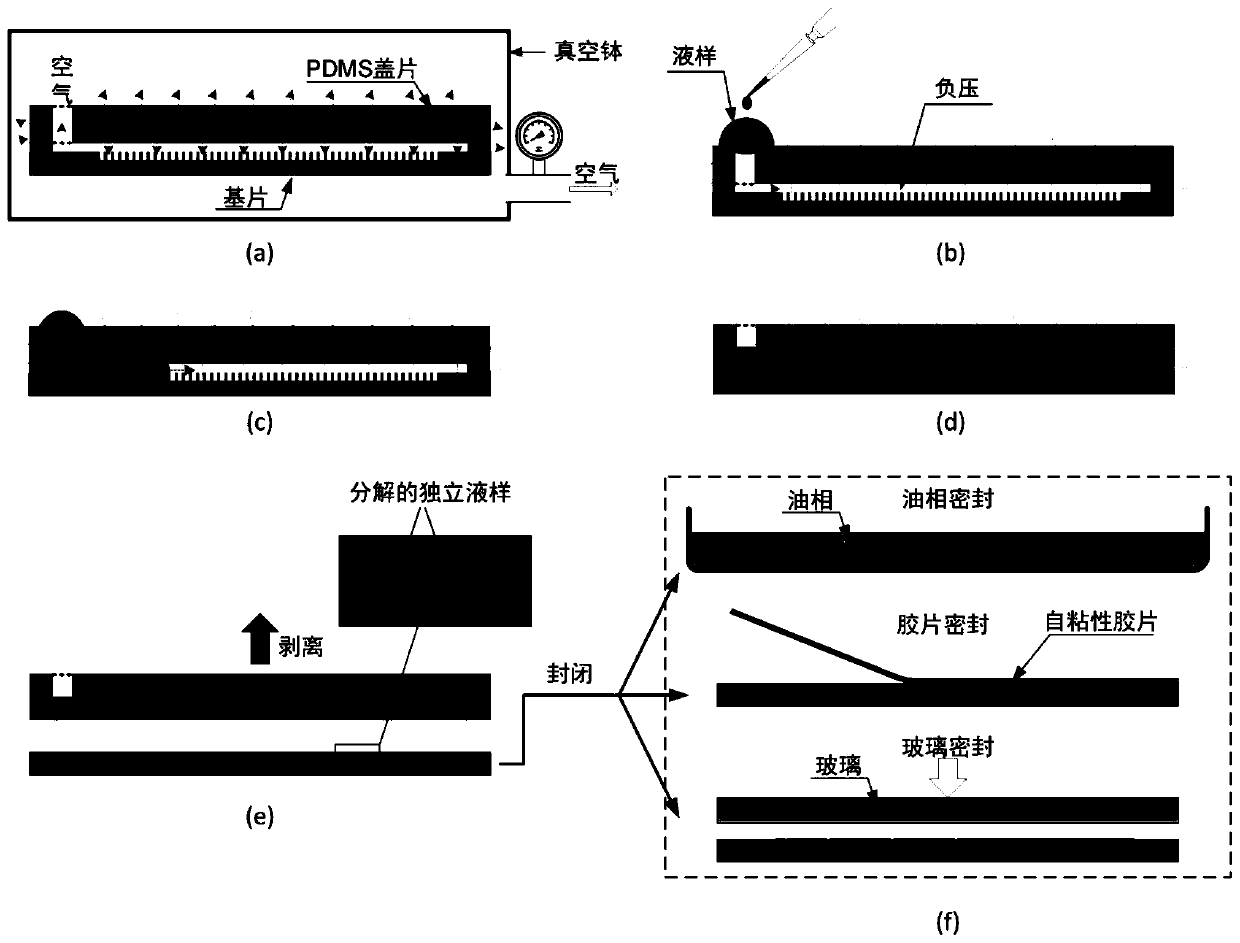

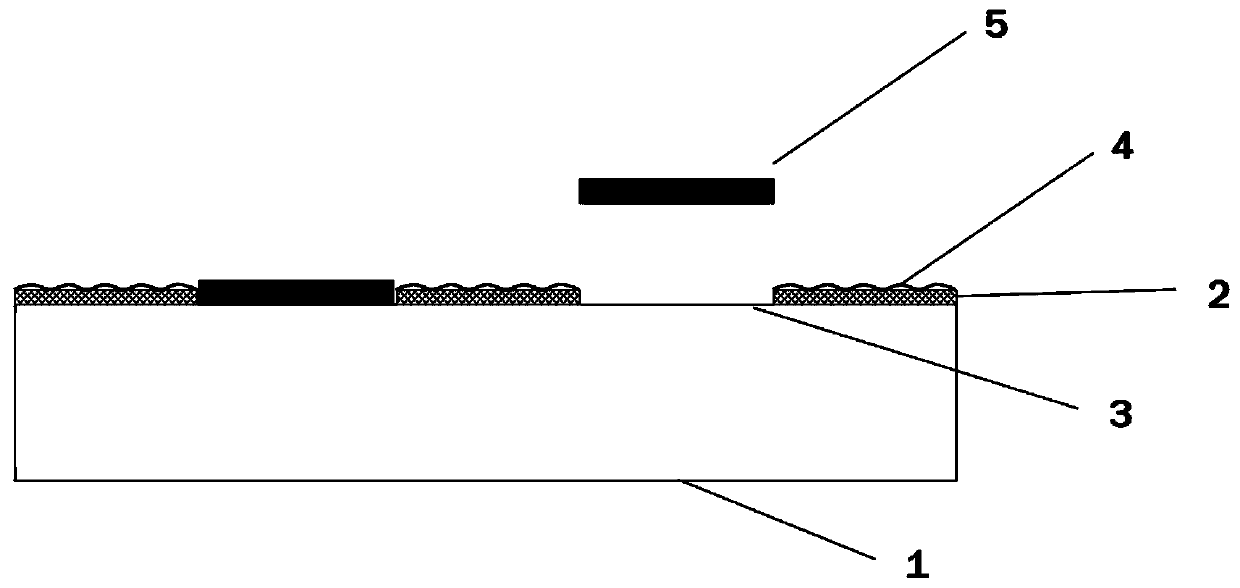

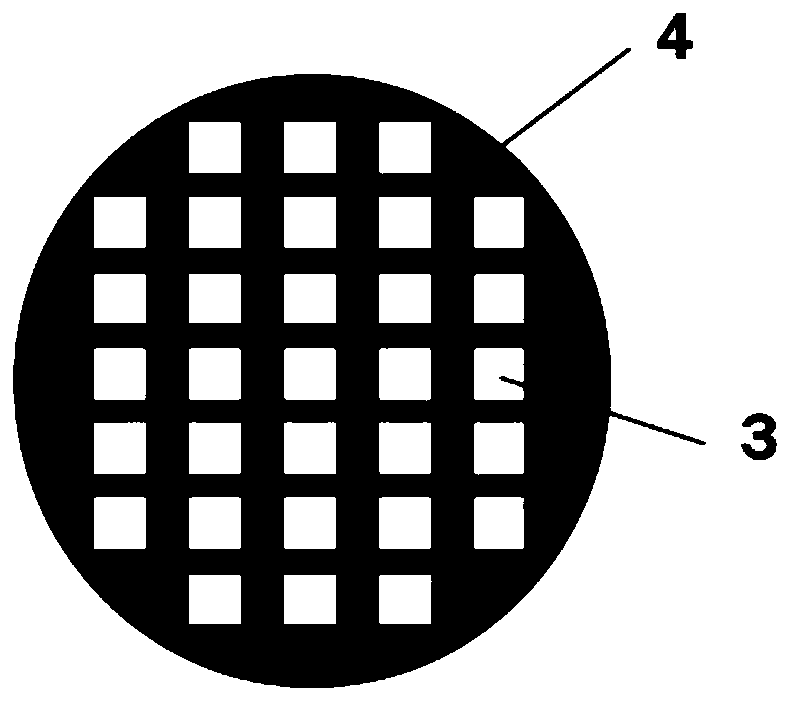

Large-scale and rapid digital decomposition chip for liquid phase samples, and use method thereof

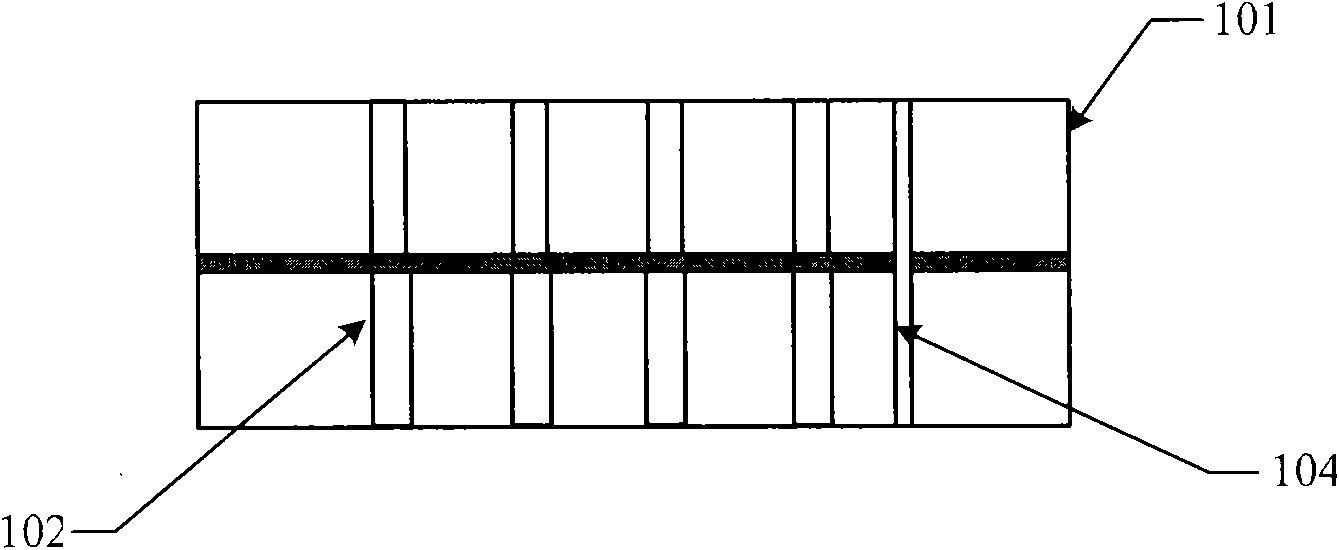

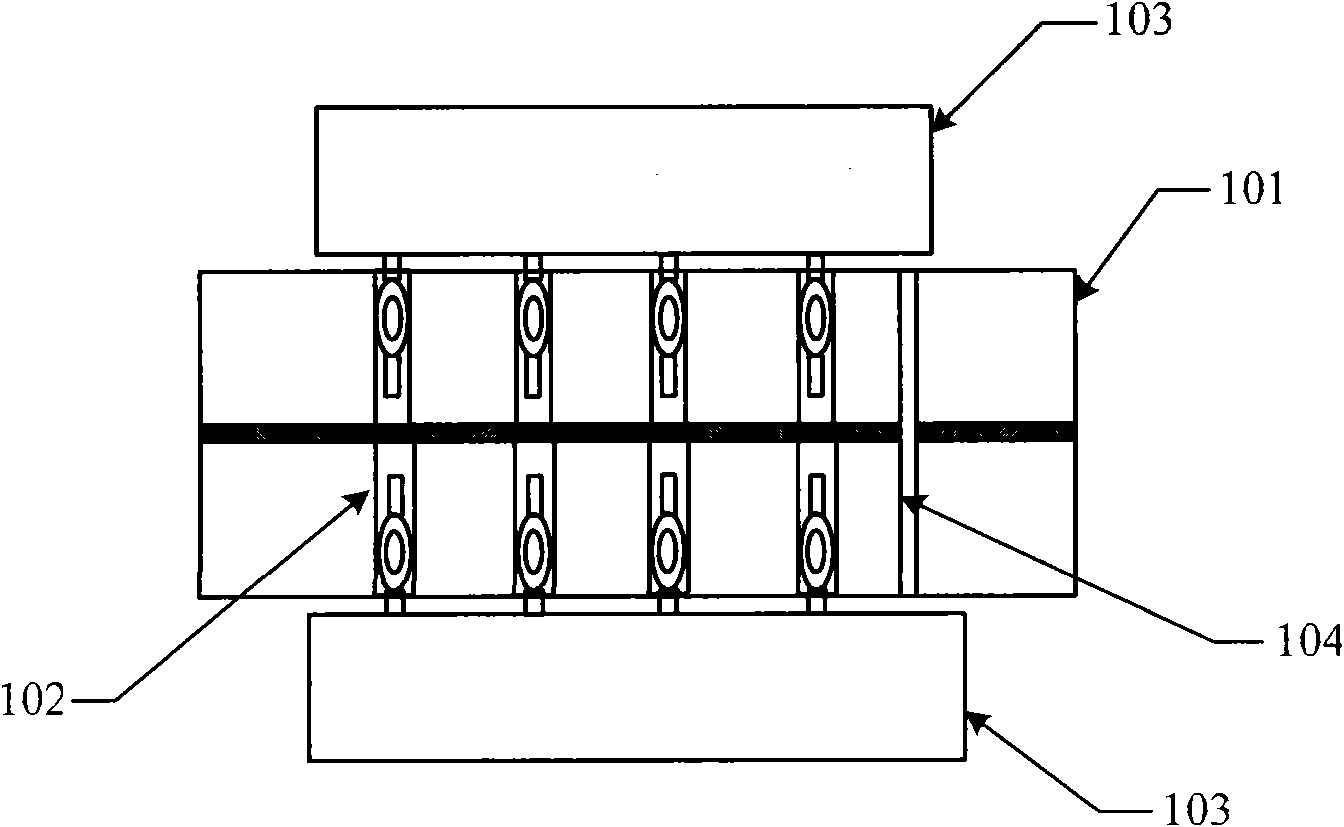

ActiveCN110437992ARapid Digital DecompositionDigital Disaggregation RealizationBioreactor/fermenter combinationsBiological substance pretreatmentsDecompositionGas phase

The present invention relates to a large-scale and rapid digital decomposition chip for liquid phase samples and a use method thereof, and belongs to the technical field of microfluidic chip analysis.The chip is composed of a polydimethylsiloxane cover sheet integrated with micro-pipe arrays and a substrate sheet integrated with microcavity arrays in a reversible bonding manner. The chip realizesseparation of the micropipe arrays and the microcavity arrays, can increase arrangement density of microcavities per unit area of the chip, increases the digital decomposition number of the liquid samples, can also avoid lengthy digital decomposition operation steps based on removal of residual sample liquid in sample injection microchannels based on a gas phase or an oil phase, and greatly shortens time for large-scale and digital decomposition of the liquid phase samples. In addition, the use of the chip does not require precise micro-pump drive and complex micro-valve control, also does not require complicated macro-micro interfaces, can realize the large-scale automatic decomposition and uniform distribution of the liquid phase samples easily, quickly and at low cost, and is expectedto promote development and widespread application of a digital analysis technology.

Owner:CHONGQING UNIV

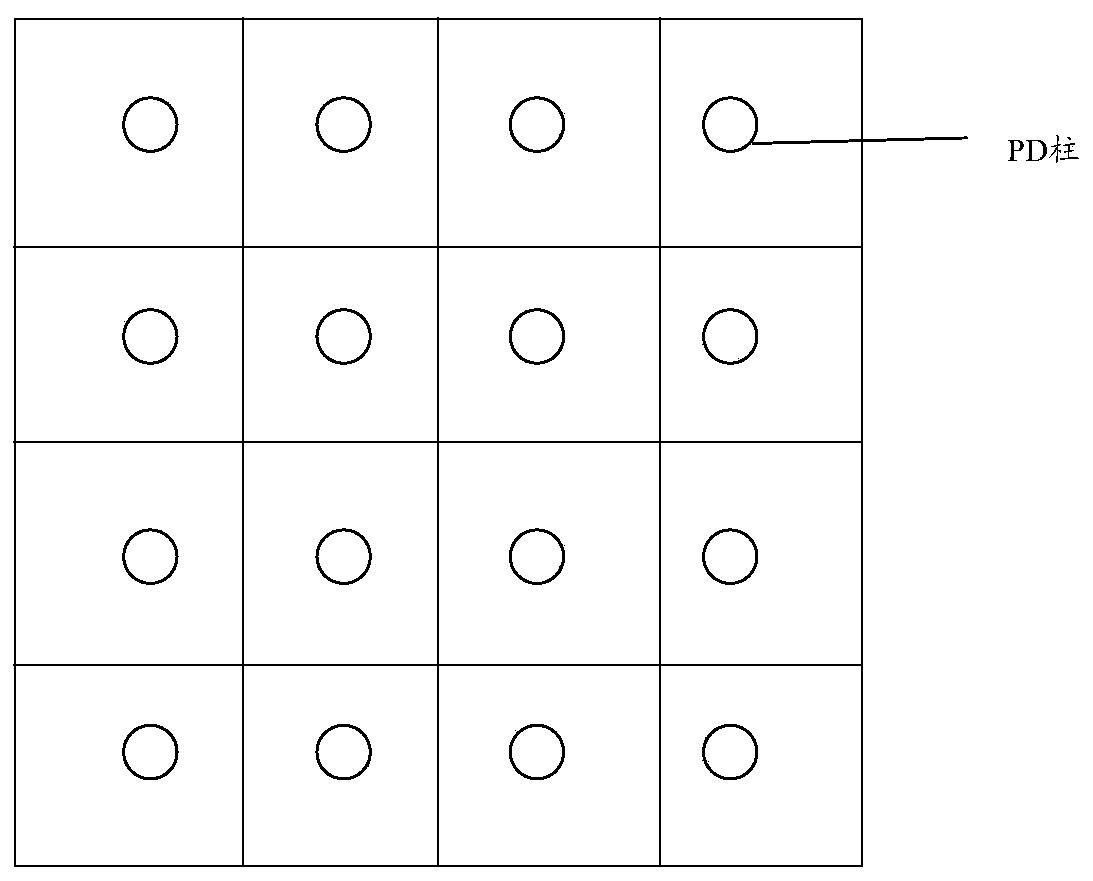

CMOS image sensor, image processing method and storage medium

PendingCN110379824AIncrease pixel densityImprove the layout densityTelevision system detailsSolid-state devicesImaging processingCmos pixels

The embodiment of the application provides a CMOS image sensor, an image processing method and a storage medium. The CMOS image sensor comprises triangular pixel units arranged in a hexagonal array and a CMOS pixel readout circuit connected with the triangular pixel units, wherein each triangular pixel unit is internally provided with a photodiode PD column and uses the photodiode PD column to absorb RGB monochromatic light and convert a corresponding optical signal into an electric signal, and the CMOS pixel readout circuit is used for amplifying and reading out the electric signals.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

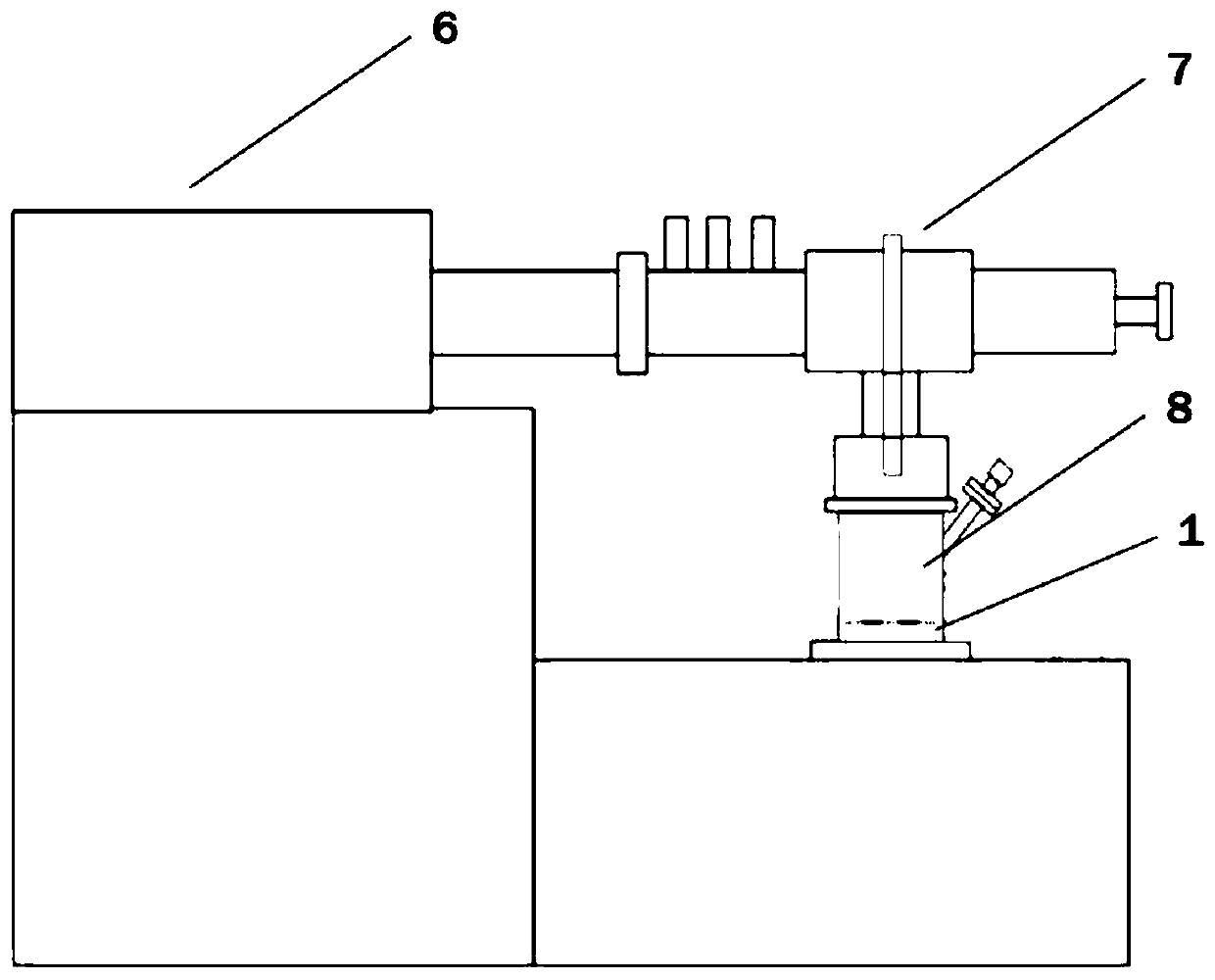

Substrate used for diamond synthesis and having coating layer as well as diamond synthesis system

InactiveCN109913947ABatch Stability AchievedImprove product qualityPolycrystalline material growthFrom chemically reactive gasesSeed crystalCoupling system

The invention provides an underlayment used for diamond synthesis and having a coating layer as well as a diamond synthesis system. The substrate is used to place seed crystals for diamond synthesis and at least comprises one sample mounting surface, a plurality of seed crystal mounting grooves are formed in each sample mounting surface, the roughness of each sample mounting surface is larger thanthat of the bottom surfaces of the seed crystal mounting grooves. aiming at the problems of diamond fixation and polycrystalline growth in diamond mass production in the prior art, a film is uniformly plated on the surface of the substrate to roughen the plating surface, so that purposes of fixation of diamond seed crystals, batch fixation and inhabitation of polycrystalline growth can be achieved. The invention also provides a diamond synthesis system which comprises a microwave source, a microwave coupling system, a reaction chamber with an air inlet system and an air outlet system, a vacuum system connected to the reaction chamber, a substrate located in the reaction chamber, wherein the substrate at least comprises one sample mounting surface, the plurality of seed crystal mounting grooves are formed in the surface of each sample mounting surface, and the roughness of each sample mounting surface is larger than that of the bottom surfaces of the seed crystal mounting grooves.

Owner:CHANGSHA ADVANCED MATERIALS IND RES INST CO LTD

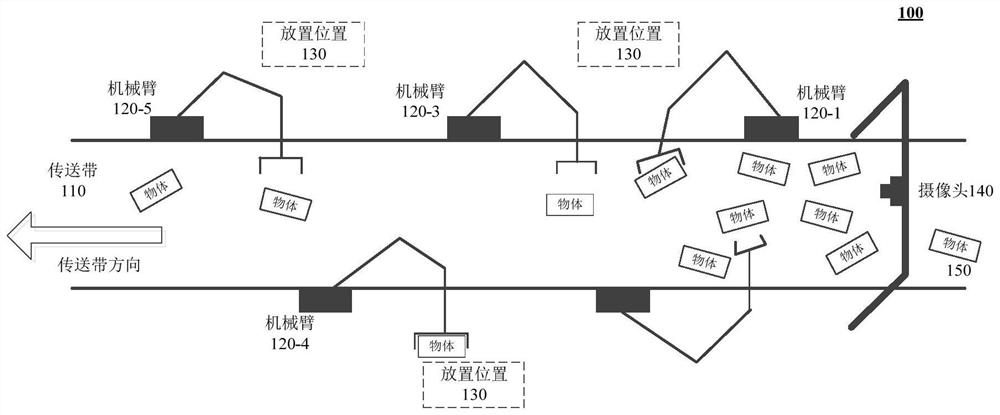

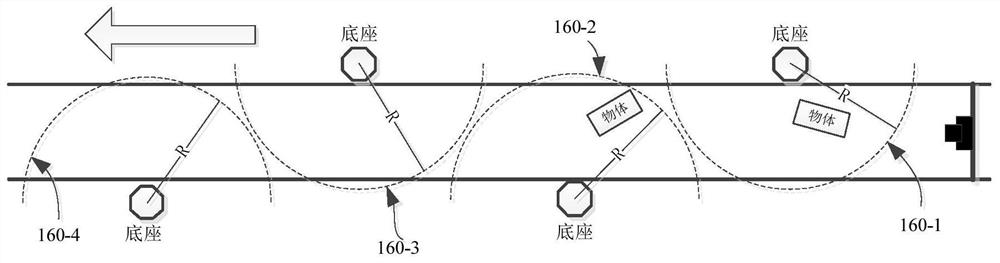

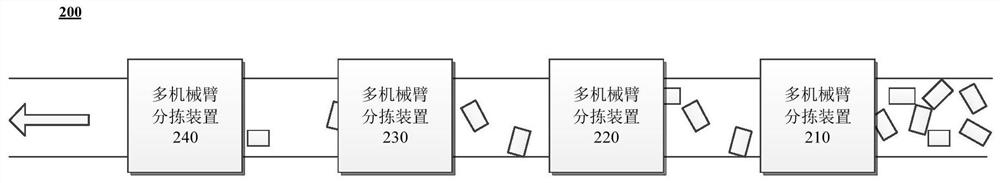

Multi-mechanical-arm device and control method thereof

ActiveCN111843996AImprove the layout densityIncrease flexibilityProgramme-controlled manipulatorSimulationConveyor belt

The invention provides a control method used for sorting a plurality of mechanical arms, and the multiple mechanical arms are used for grabbing and sorting objects moving along a conveyor belt. The method includes the steps that a task list that includes tasks to be assigned and a mechanical arm list that includes mechanical arms in an idle state are provided, and each task to be assigned includesthe grab pose of the corresponding object on the conveyor belt; the tasks to be assigned are selected from the task list; whether the tasks to be assigned are within the grab range of the first mechanical arm in the mechanical arm list or not is determined; if the tasks to be assigned are within the grab range of the first mechanical arm, whether the first mechanical arm is in collision with theother mechanical arms or not is determined; if there is no collision, the tasks to be assigned are assigned to the first mechanical arm and the first mechanical arm is deleted from the mechanical armlist, if there is a collision, the next mechanical arm in the mechanical arm list is selected, and whether the next mechanical arm is in collision with the other mechanical arms or not is determined;and a trajectory file used for execution of the mechanical arms is generated according to the grab poses of the objects.

Owner:珠海一维弦机器人有限公司

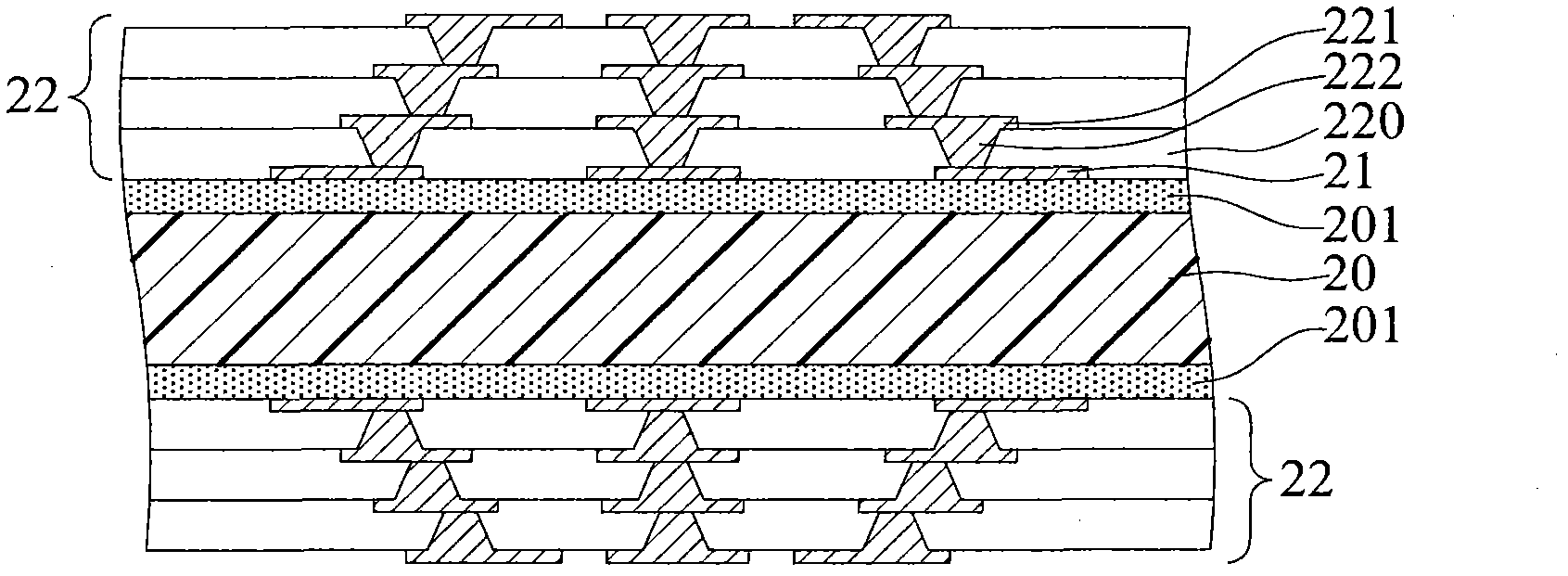

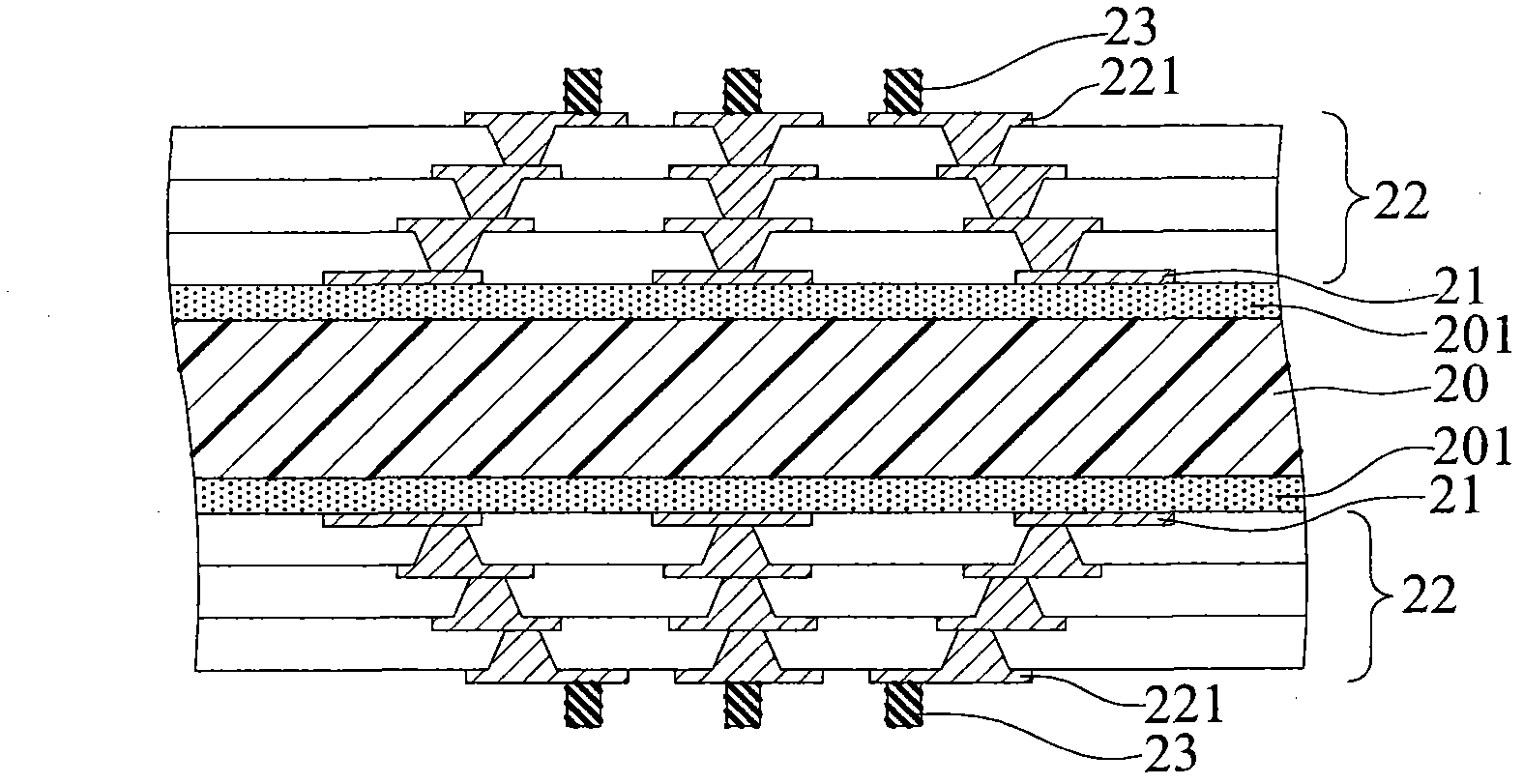

Multi-layer substrate and manufacturing method thereof

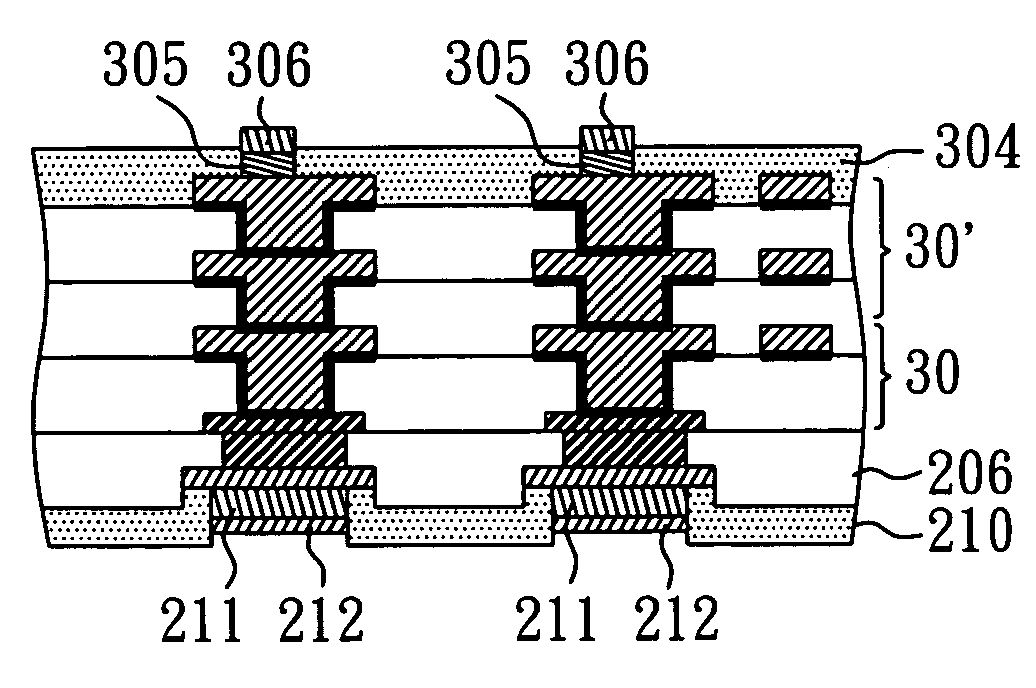

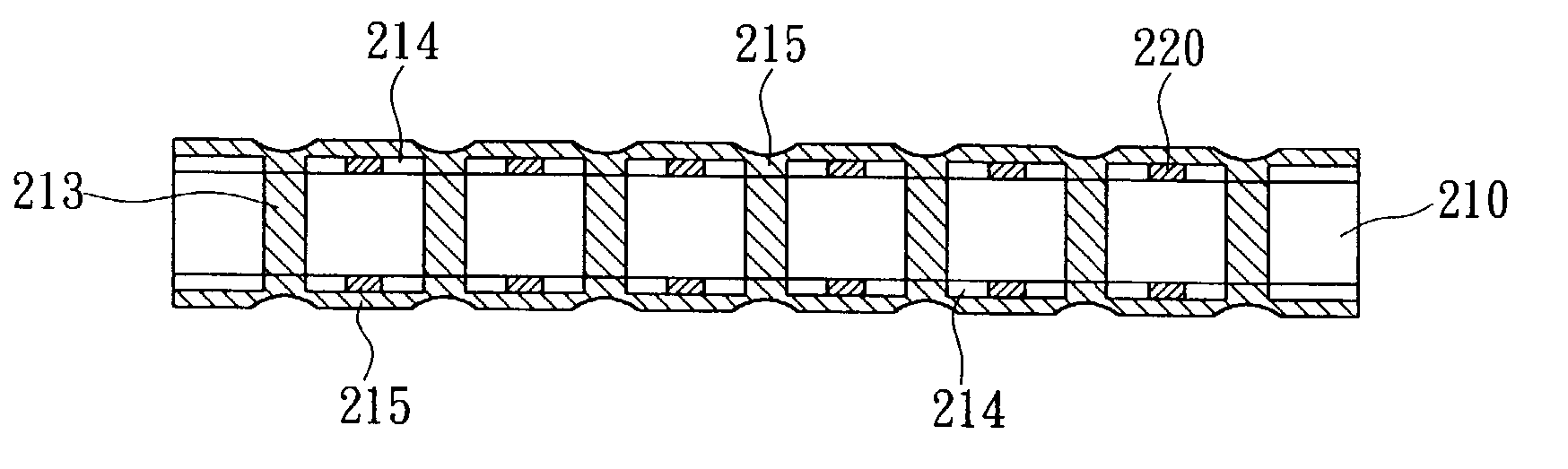

ActiveUS20080314629A1Reduce thicknessShrink in sizeInsulating substrate metal adhesion improvementPrinted circuit aspectsSignal integrityHot pressing

Disclosed are a multi-layer substrate and a manufacturing method of the multi-layer substrate. By employing a carrier to alternately form dielectric layers and metal structure layers thereon. Each dielectric layer adheres with the adjacent dielectric layer to embed the metal structure layers in the dielectric layers corresponding thereto. Comparing with prior arts, which have to use prepregs when hot pressing and adhering different layers of different materials, the present invention takes fewer processes, thus, fewer kinds of materials without using prepregs. Therefore, the present invention can promote the entire quality and yield of manufacturing the multi-layer substrate to satisfy mechanical characteristic matching of the multi-layer substrate and to reduce cost of the whole manufacturing process. Significantly, the multi-layer substrate having thin dielectric layers according to the present invention can satisfy the concern of impedance matching therefore, and can reduce crosstalk influence to keep good signal integrity therein.

Owner:PRINCO CORP

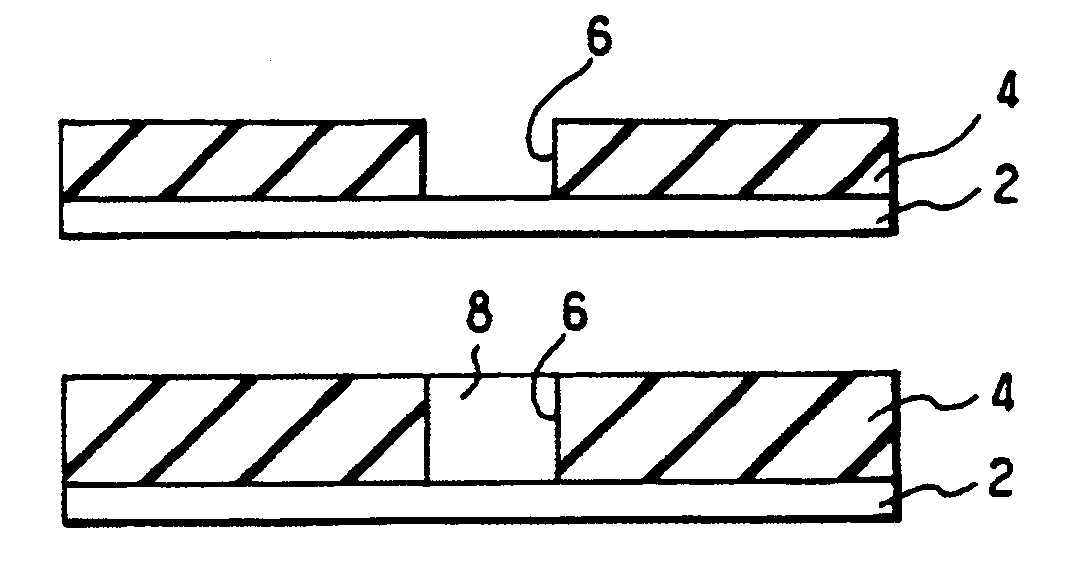

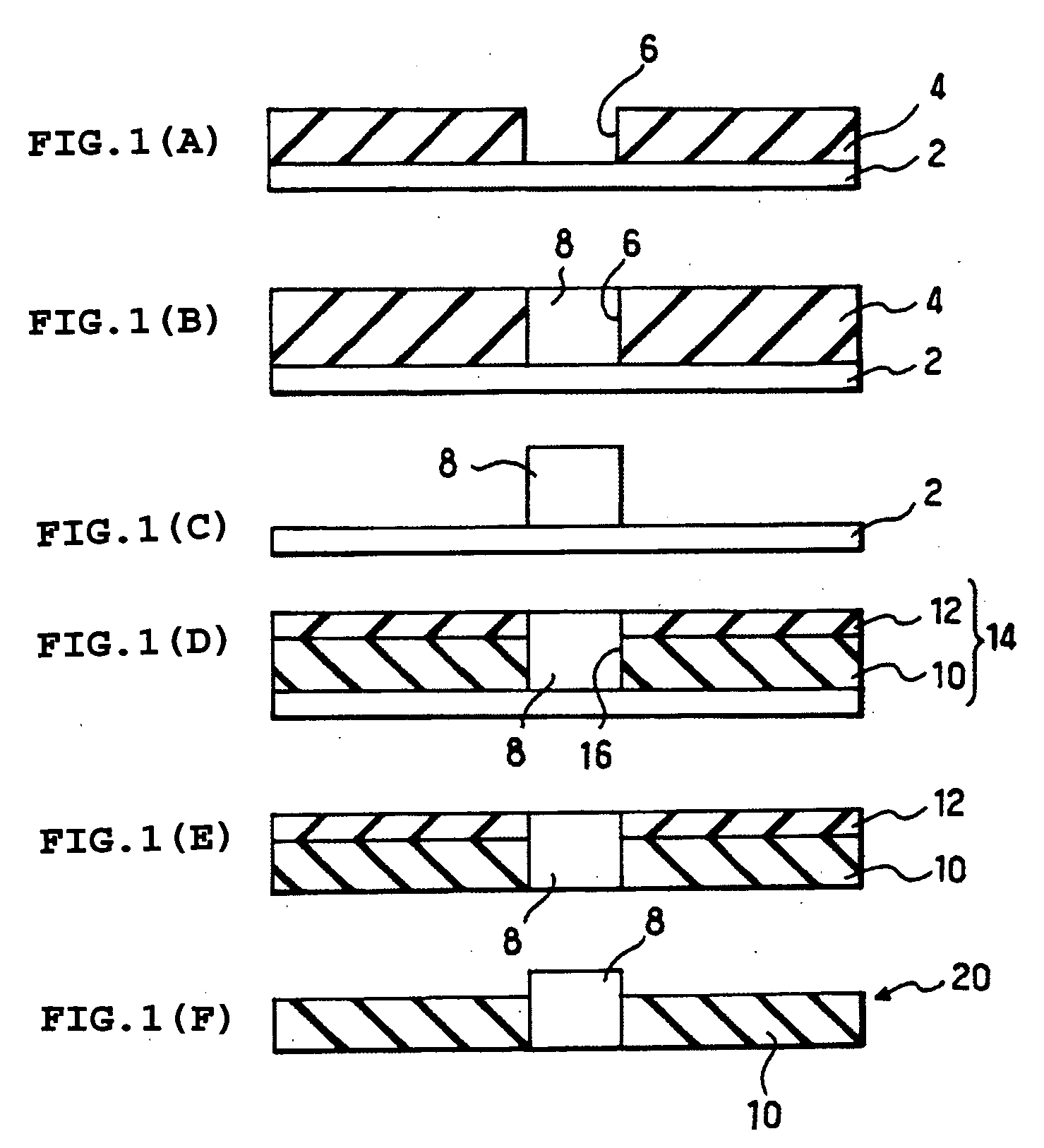

Interlayer member used for producing multilayer wiring board and method of producing the same

InactiveUS20050224256A1Reduce the amount of metalReduce the amount requiredAnti-cellulite devicesSemiconductor/solid-state device detailsCopper platingElectrical connection

To increase the dimensional accuracy of an interlayer member used for producing a multilayer wiring board which is inserted between two wiring layers to establish interlayer insulation and interlayer electrical connection between the wiring layers, to thereby increase a layout density. A mask film is formed on a main surface of a sheet-like carrier layer. A metal column for interlayer connection is formed on the main surface of the carrier layer by plating a copper using the mask film as a mask. The mask film is removed. An interlayer insulating layer and a protective sheet are laminated on the main surface of the carrier layer in such a manner that the metal column for interlayer connection penetrates them. The interlayer insulating layer and the protective sheet are polished until the upper surface of the metal column for interlayer connection is exposed. Then, the carrier layer is removed. Furthermore, the protective sheet is removed.

Owner:INVENSAS CORP

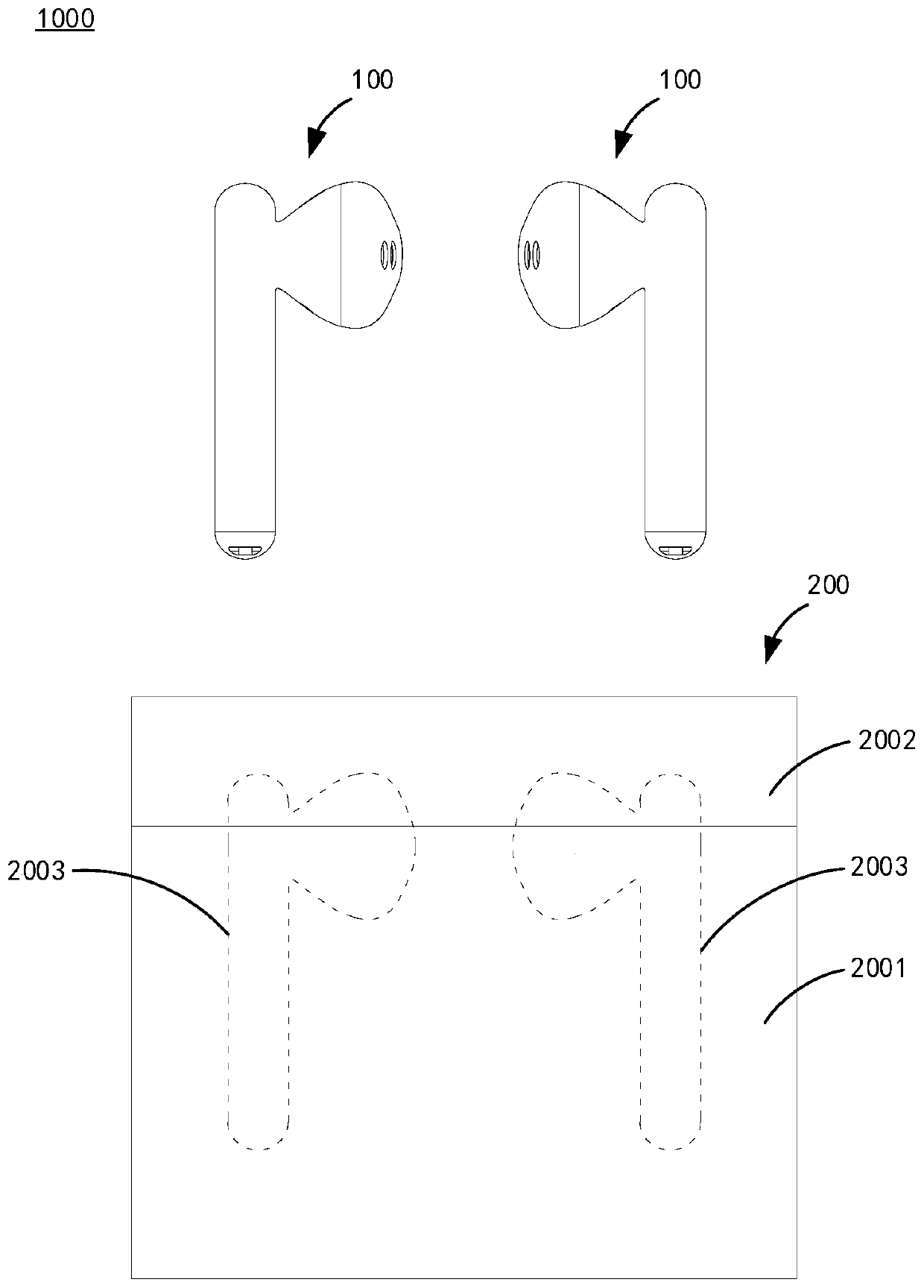

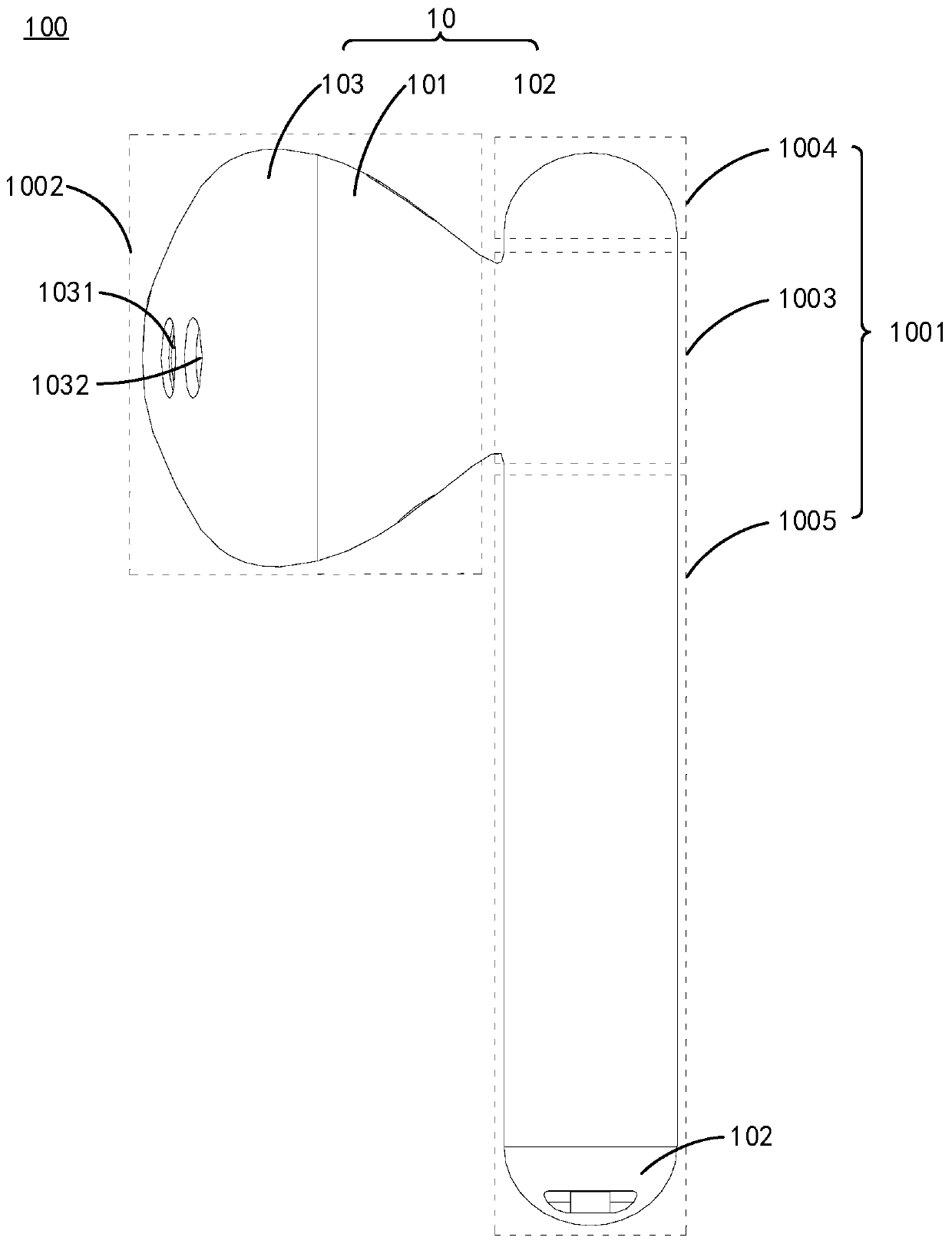

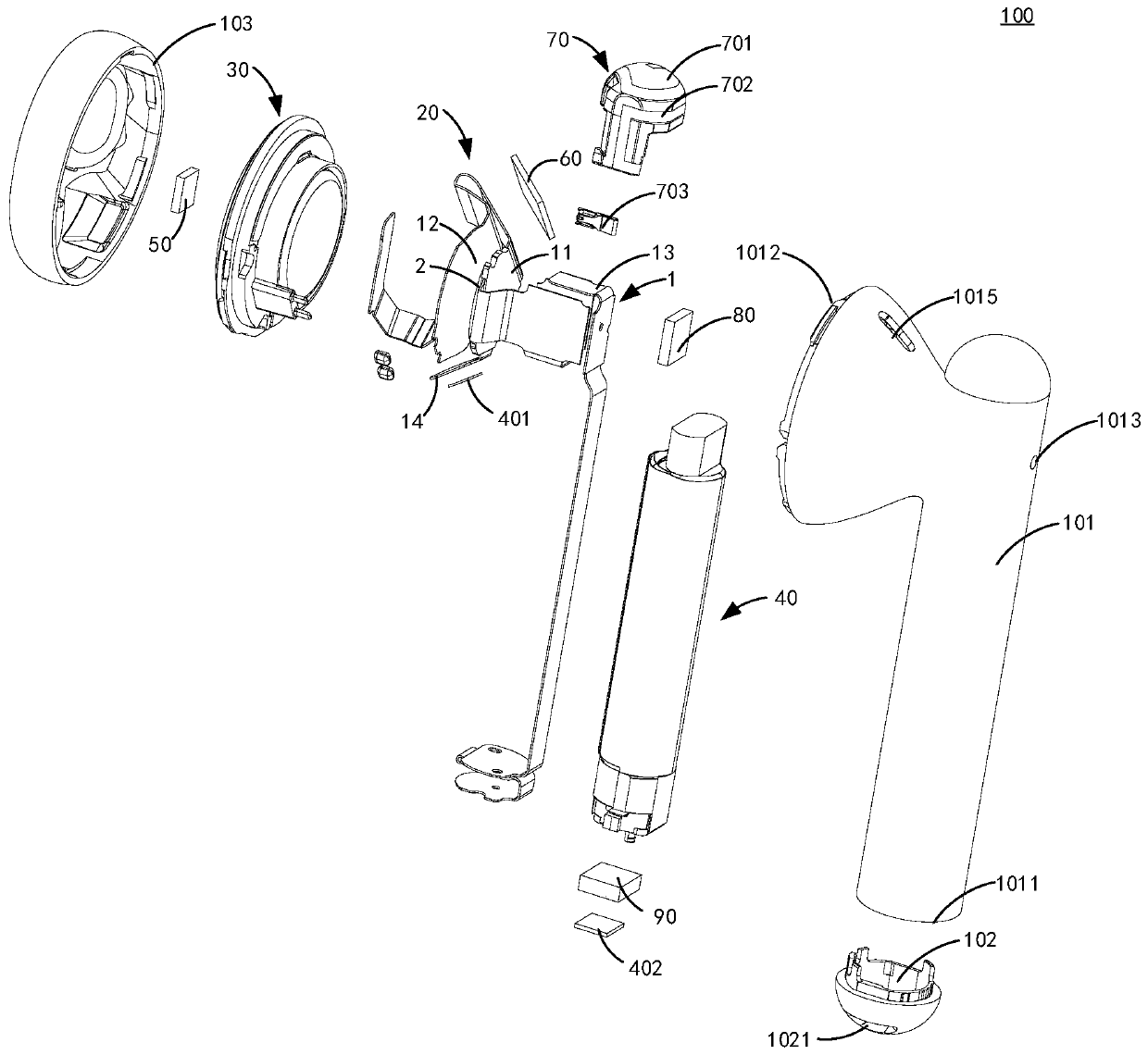

Wireless earphone

PendingCN110798768AImprove the layout densityHighly integratedMicrophonesLoudspeakersComputer hardwareEmbedded system

The embodiment of the invention discloses a wireless earphone which is provided with an ear handle part and an earplug part connected with the ear handle part, the wireless earphone comprises a main control module, and the main control module comprises a soft and hard combined circuit board, a first substrate, a first supporting piece and a plurality of chips. The rigid-flex circuit board comprises a rigid board portion, a first flexible board portion and a second flexible board portion, the first flexible board portion and the second flexible board portion are connected with the rigid board portion, the rigid board portion is located at the earplug portion, one end of the first flexible board portion is connected with the rigid board portion, and the other end of the second flexible boardportion extends to the ear handle portion. The first substrate and the hard board part are stacked at an interval; the first supporting piece is located between the first substrate and the hard boardpart and abuts against the first substrate and the hard board part, at least one chip in the multiple chips is fixed to the hard board part, at least one chip in the multiple chips is fixed to the first substrate, and the chip fixed to the first substrate is electrically connected with the hard board part through the first supporting piece. A plurality of layers of devices are stacked on the hardboard part of the wireless earphone, and the integration degree of the devices is high.

Owner:HUAWEI TECH CO LTD

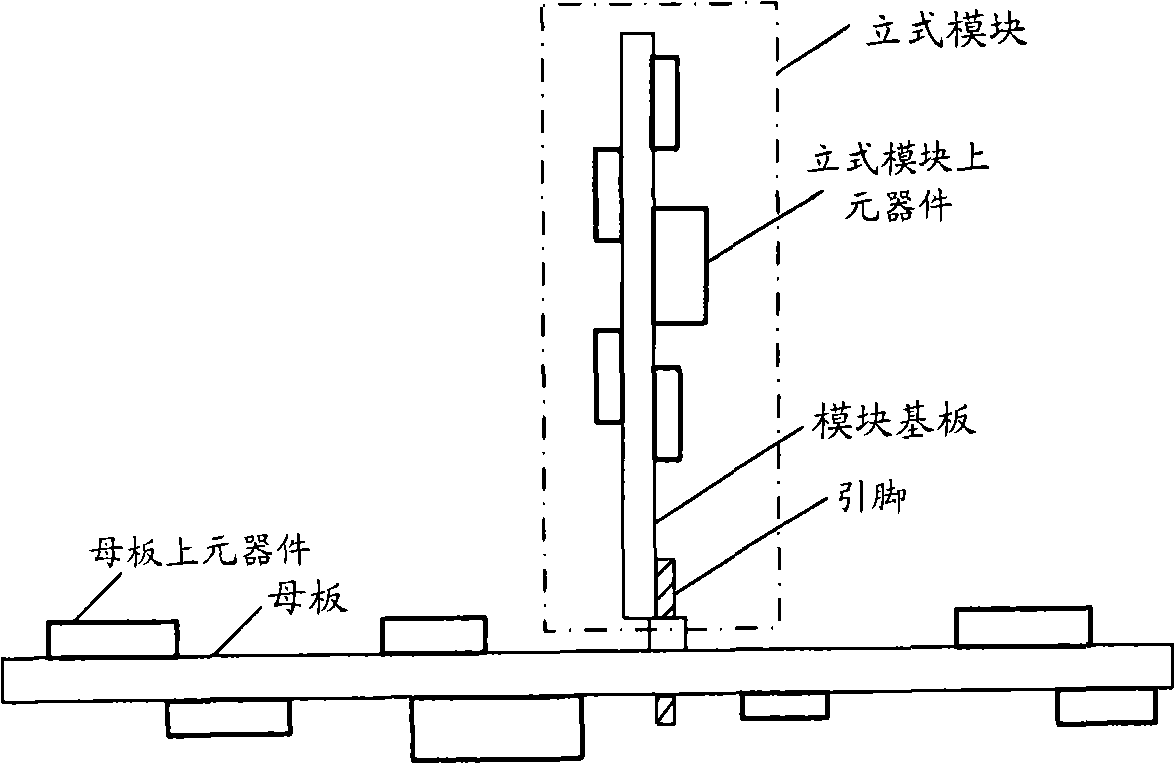

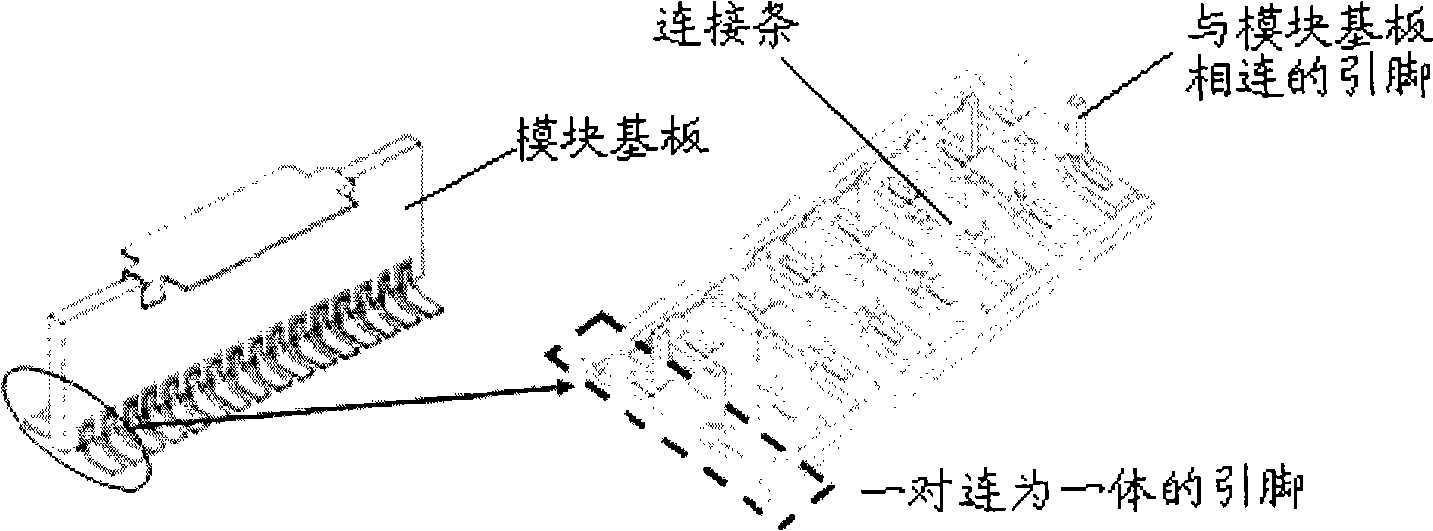

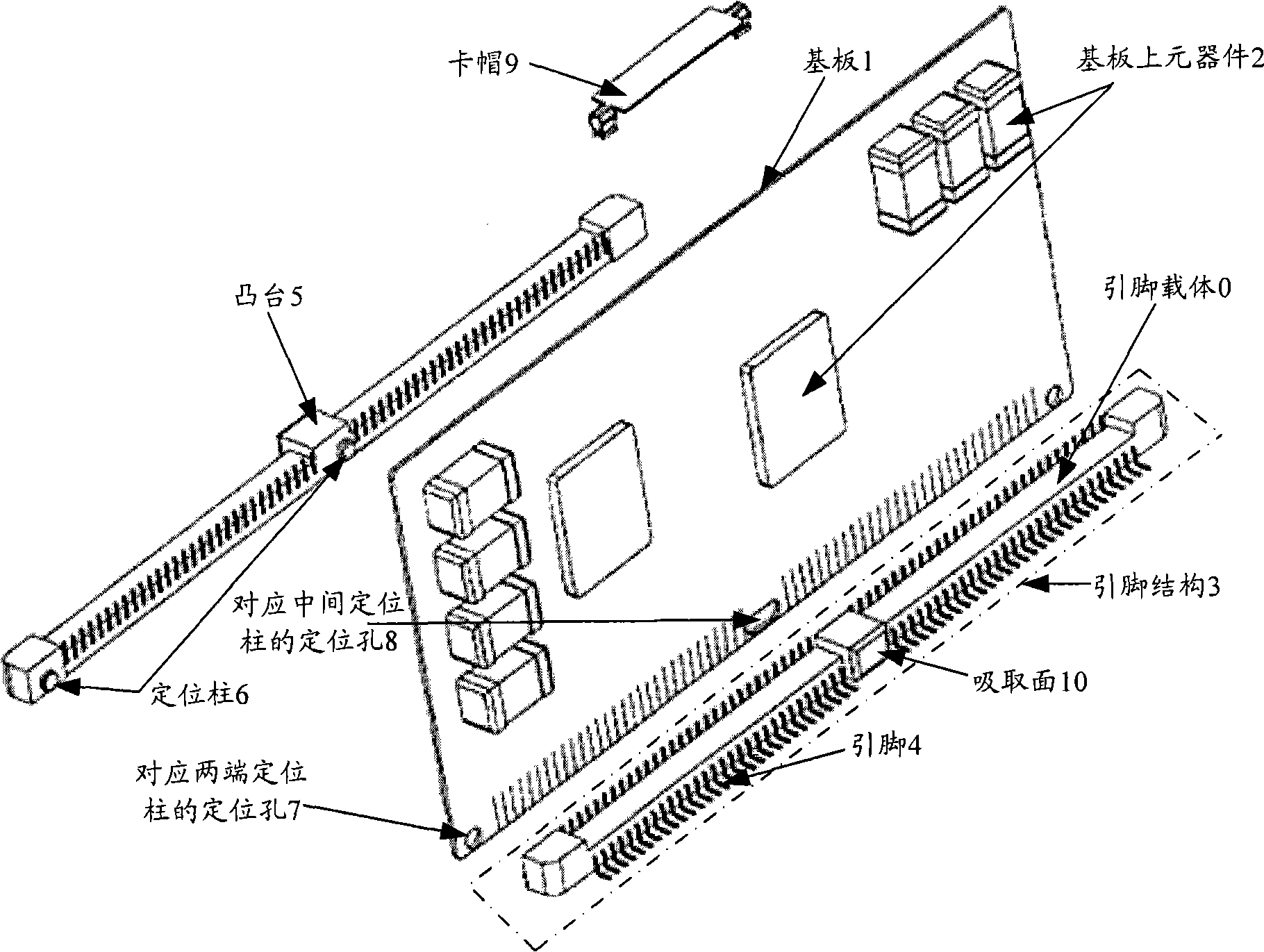

Module and electronic device

ActiveCN101299426AGood coplanaritySave layout spaceSemiconductor/solid-state device detailsSolid-state devicesBiochemical engineeringMotherboard

The invention discloses a module including a base plate and two pin structure, wherein the pin structure comprises a pin and a pin carrier; each pin is independently sticked on the pin carrier; at least two pin structures are provided respectively arranged at the two sides of the base plate for connecting the base plate and the motherboard; at least two reference columns are arranged on the pin carrier. A positioning hole corresponding to the reference column arranged on the pin structure is arranged on the base plate, wherein the positioning hole on the base plate is on the same line; the reference column on the pin carrier is assembled with the base plate. The invention also discloses an electronic equipment including a module and a motherboard. The pins at the two sides of the base plate is independant each other for connecting different I / O ports, which advances the layout density, thereby reducing the layout space of the motherboard, increasing the whole layout density, meanwhile the positioning hole on the module base plate is on the same level, which effectively ensures the coplane degree of the vertical module pin.

Owner:HUAWEI TECH CO LTD