Patents

Literature

514results about How to "Simplify manufacturing steps" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

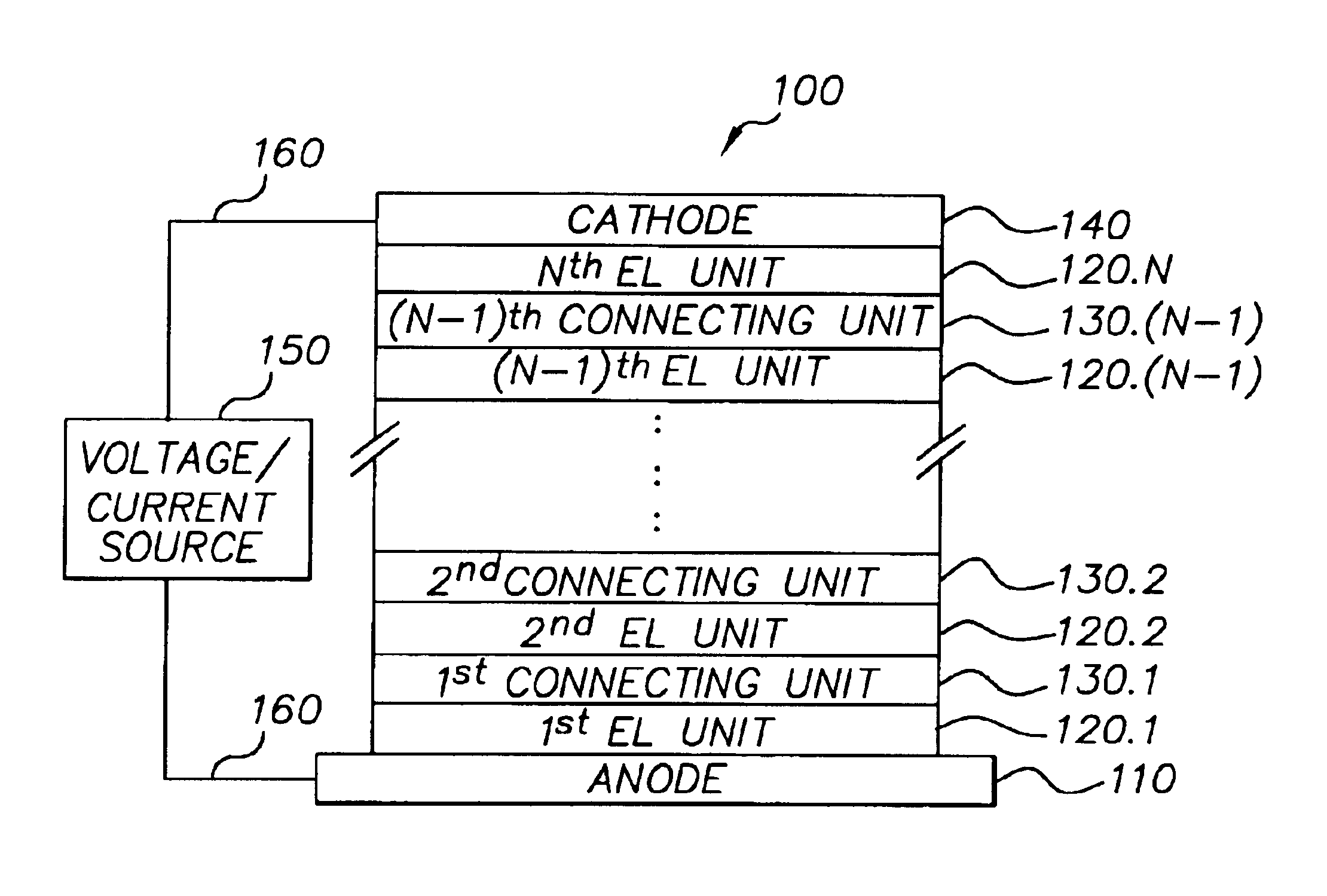

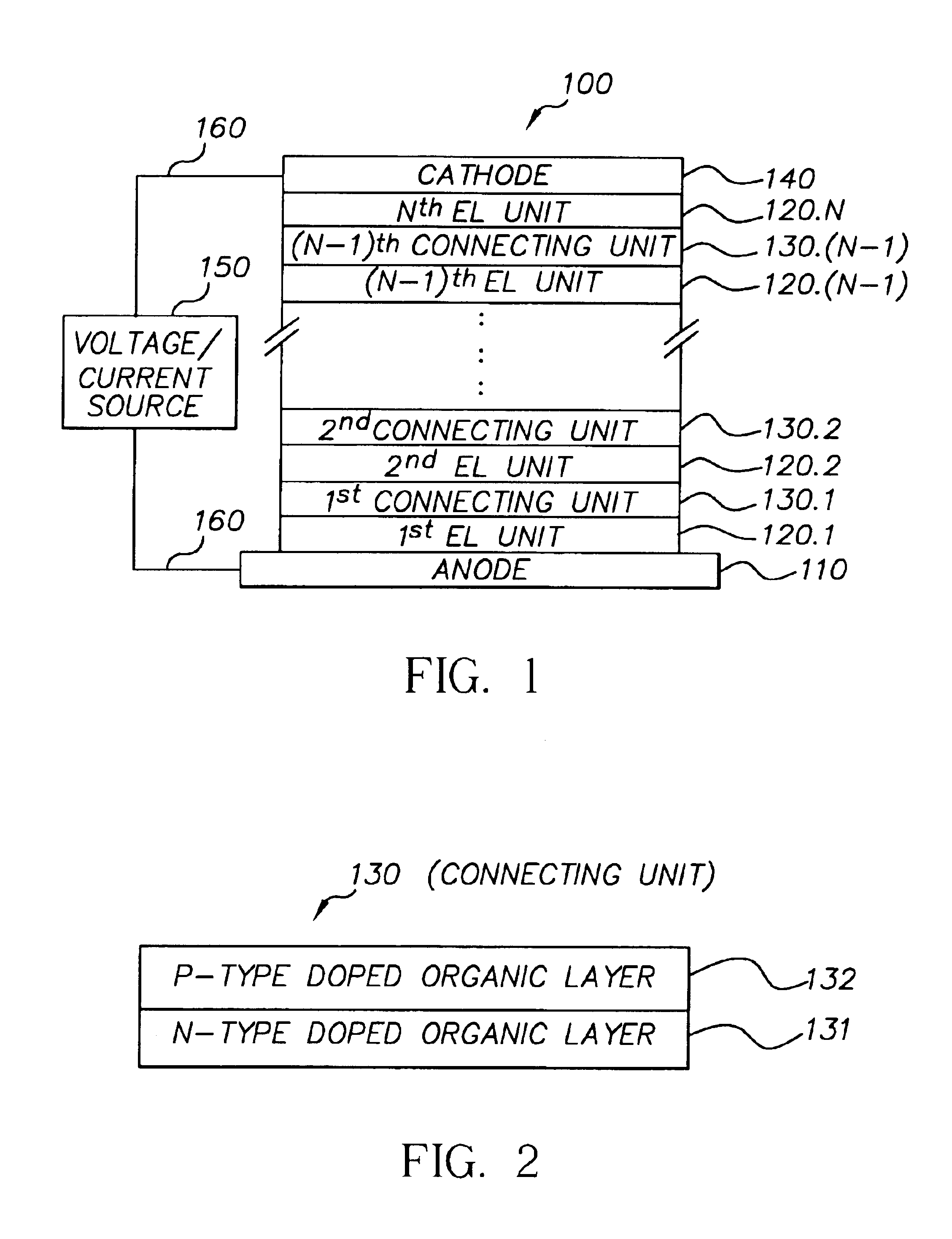

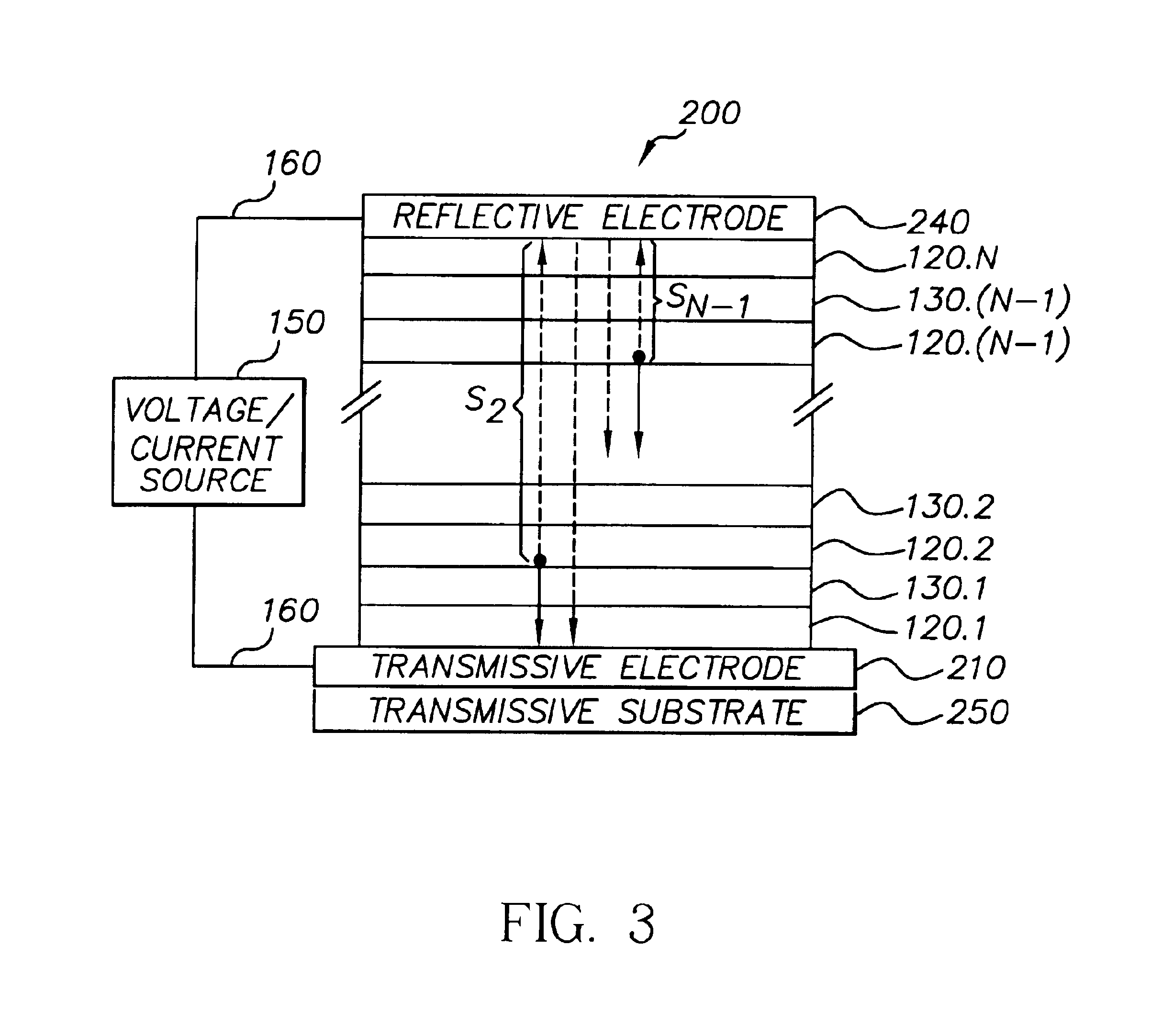

Cascaded organic electroluminescent device having connecting units with N-type and P-type organic layers

ActiveUS6936961B2Improve light extractionSimplify fabrication stepDischarge tube luminescnet screensElectroluminescent light sourcesOrganic electroluminescenceP type doping

A cascaded organic electroluminescent device includes an anode and a cathode. The device also includes a plurality of organic electroluminescent units disposed between the anode and the cathode, wherein the organic electroluminescent units comprise at least a hole-transporting layer, an electron-transporting layer, and an electroluminescent zone formed between the hole-transporting layer and the electron-transporting layer wherein the physical spacing between adjacent electroluminescent zones is more than 90 nm; and a connecting unit disposed between each adjacent organic electroluminescent unit, wherein the connecting unit comprises, in sequence, an n-type doped organic layer and a p-type doped organic layer forming a transparent p-n junction structure wherein the resistivity of each of the doped layers is higher than 10 Ω-cm.

Owner:GLOBAL OLED TECH

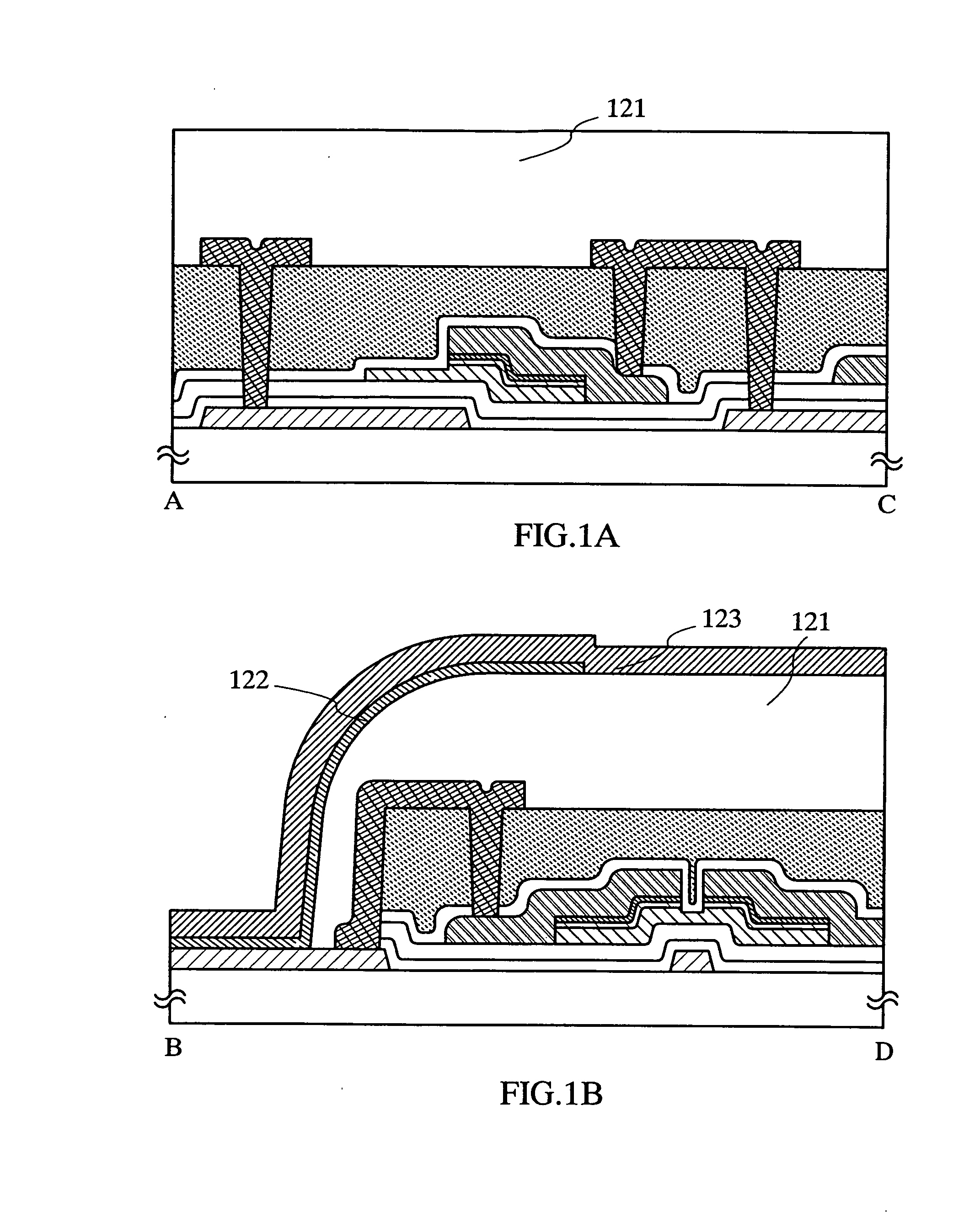

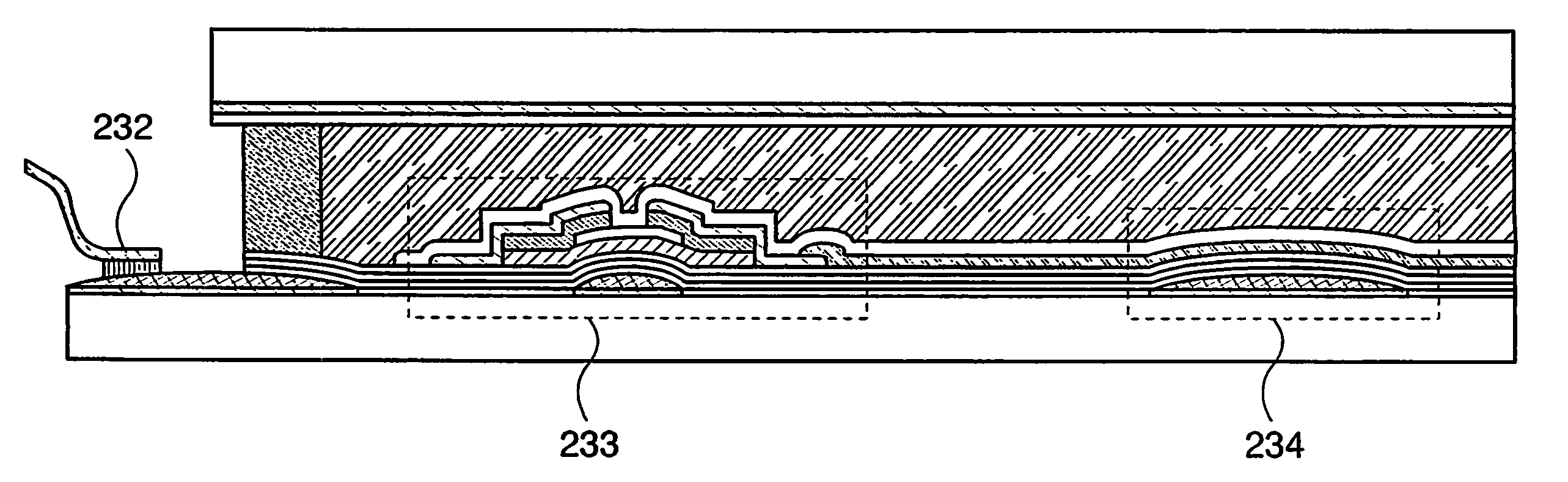

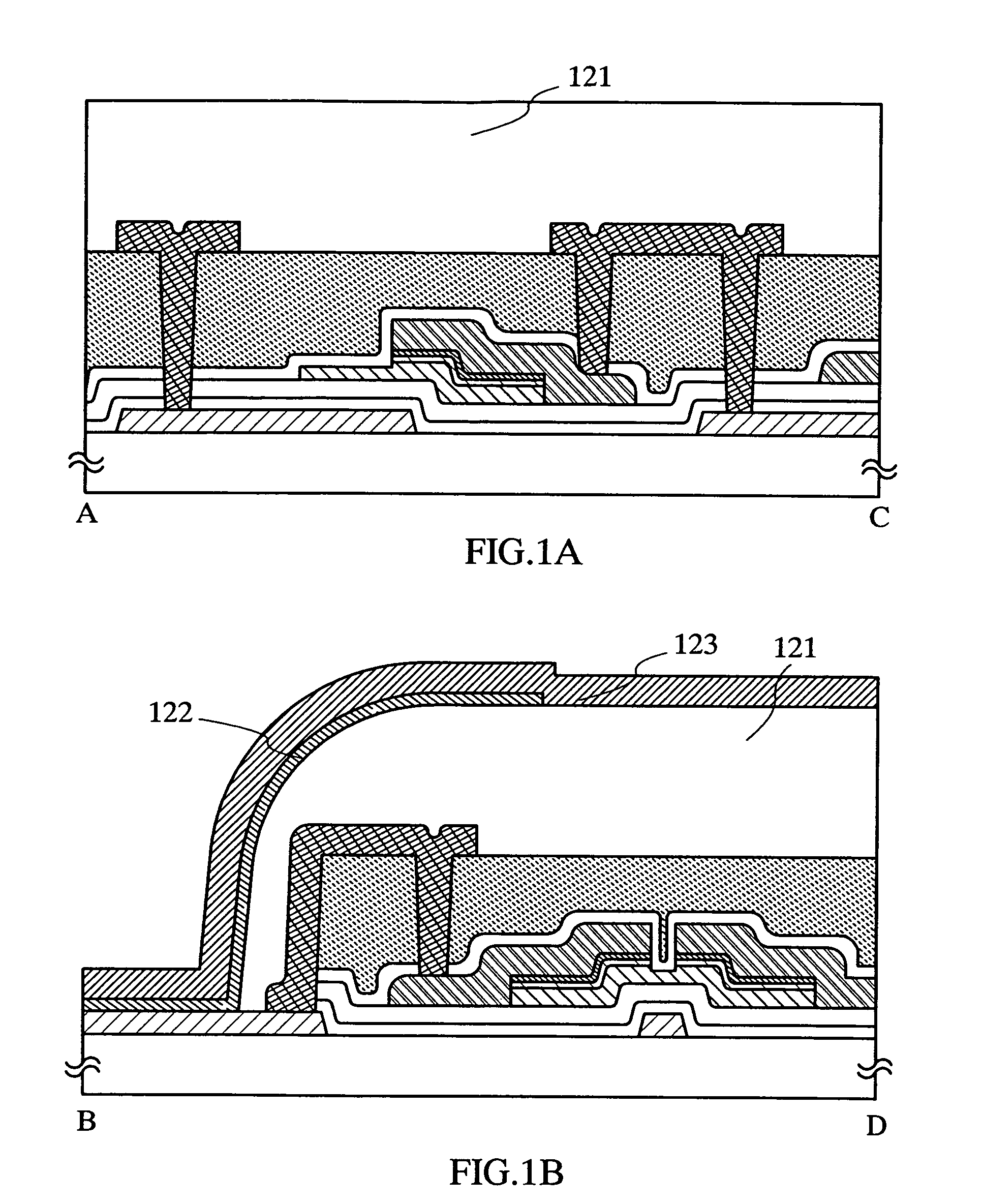

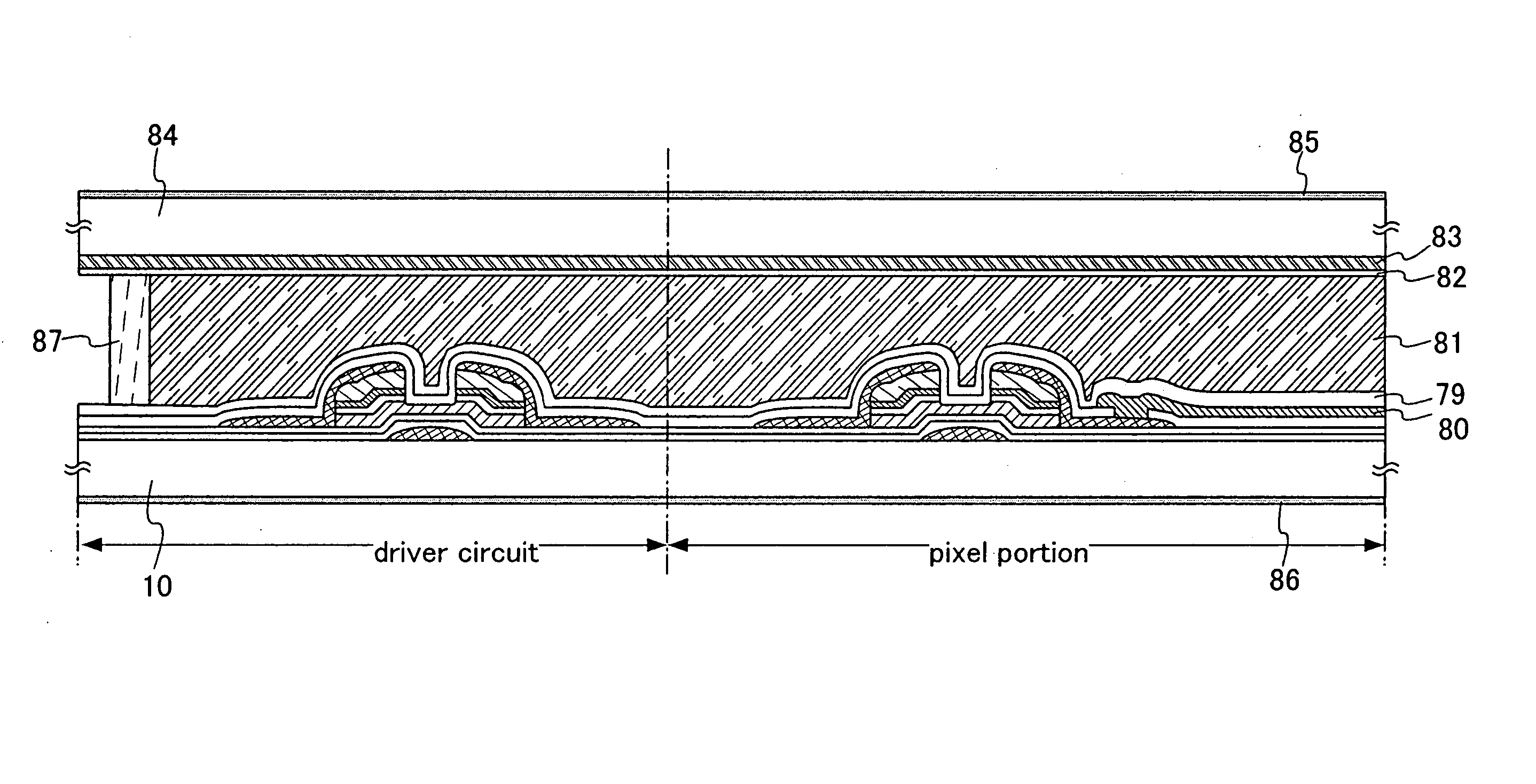

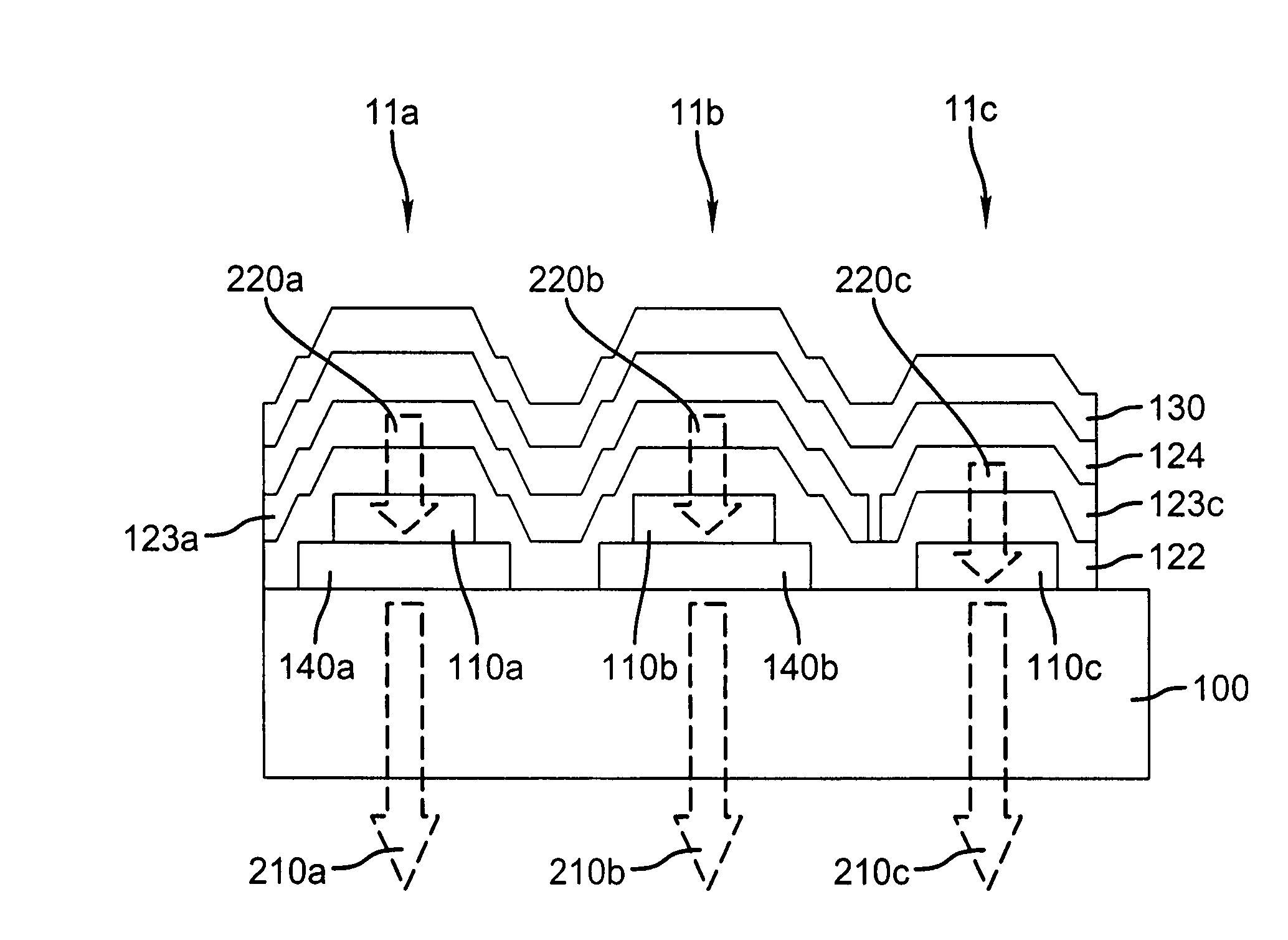

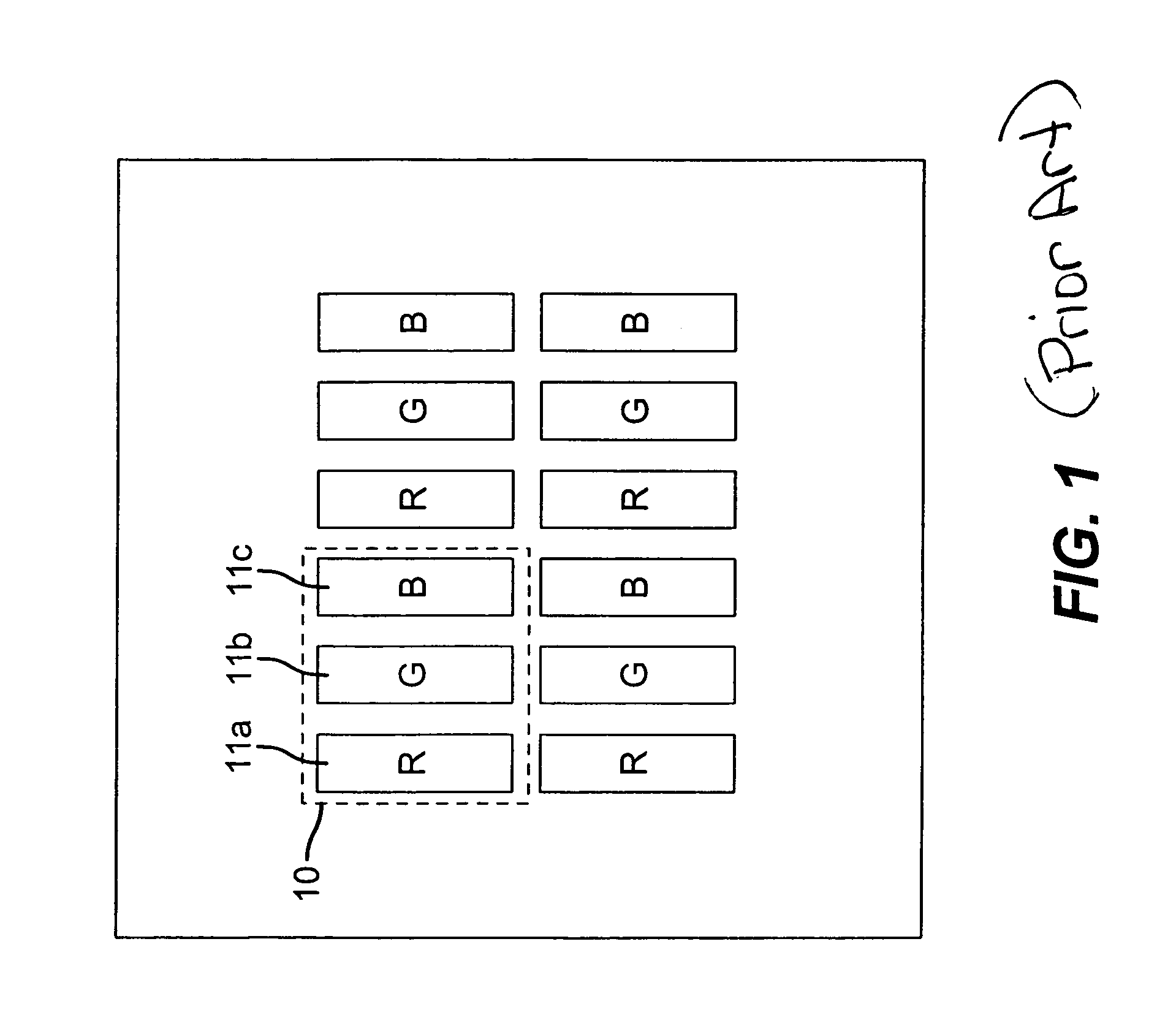

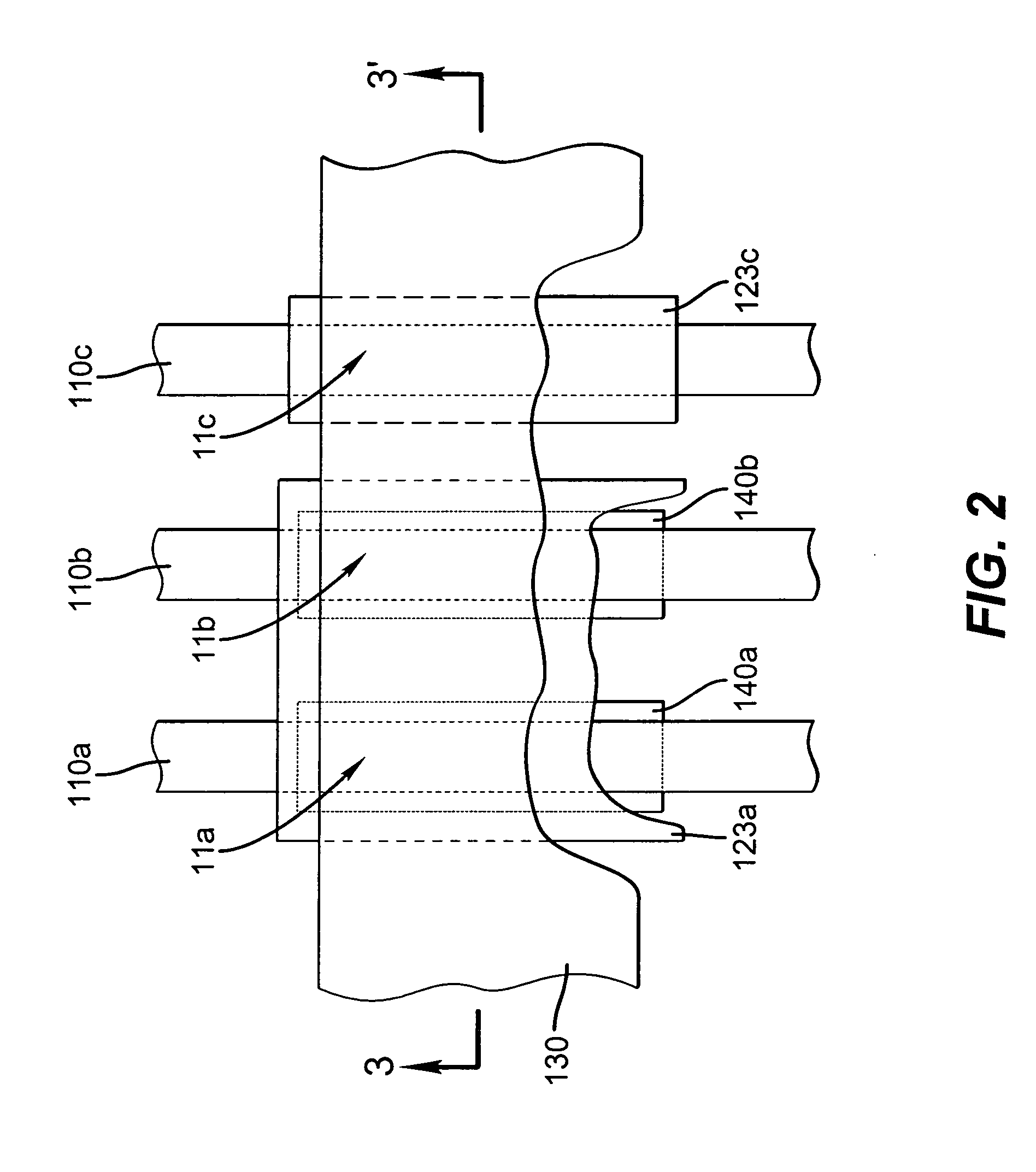

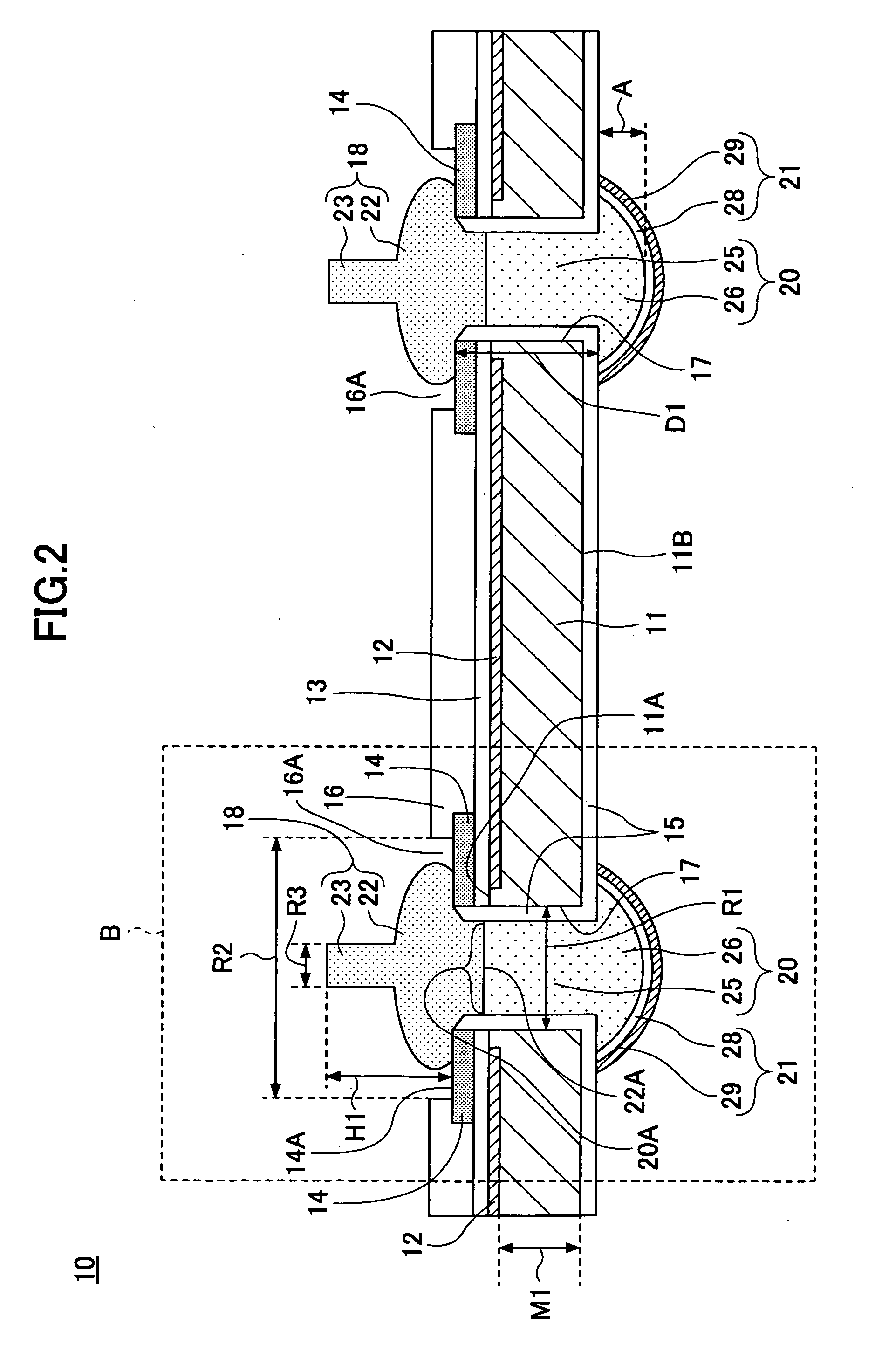

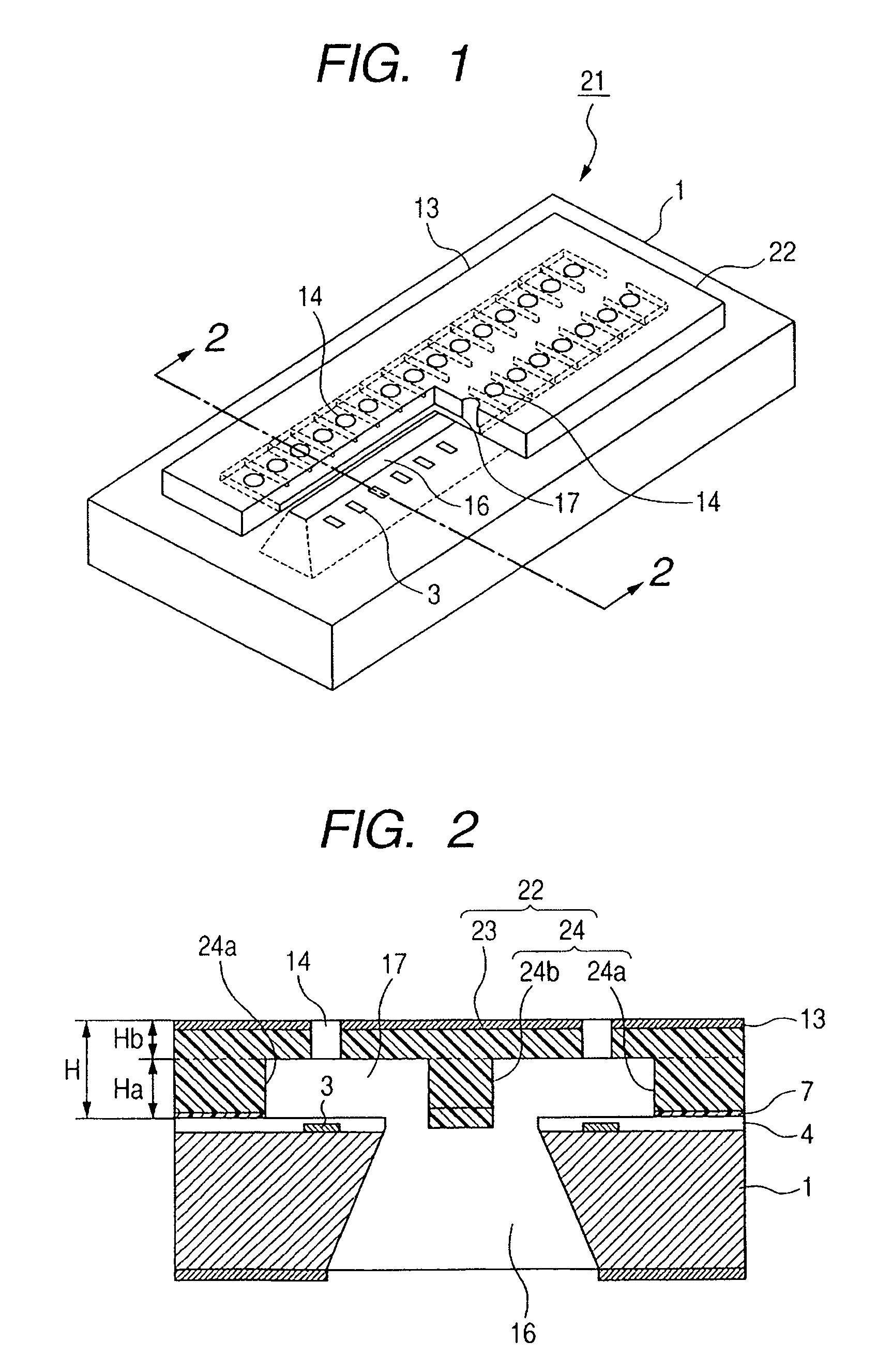

Display device, manufacturing method thereof, and television set

InactiveUS20060027804A1Improve mobilityLow resistivitySolid-state devicesSemiconductor/solid-state device manufacturingContact formationDisplay device

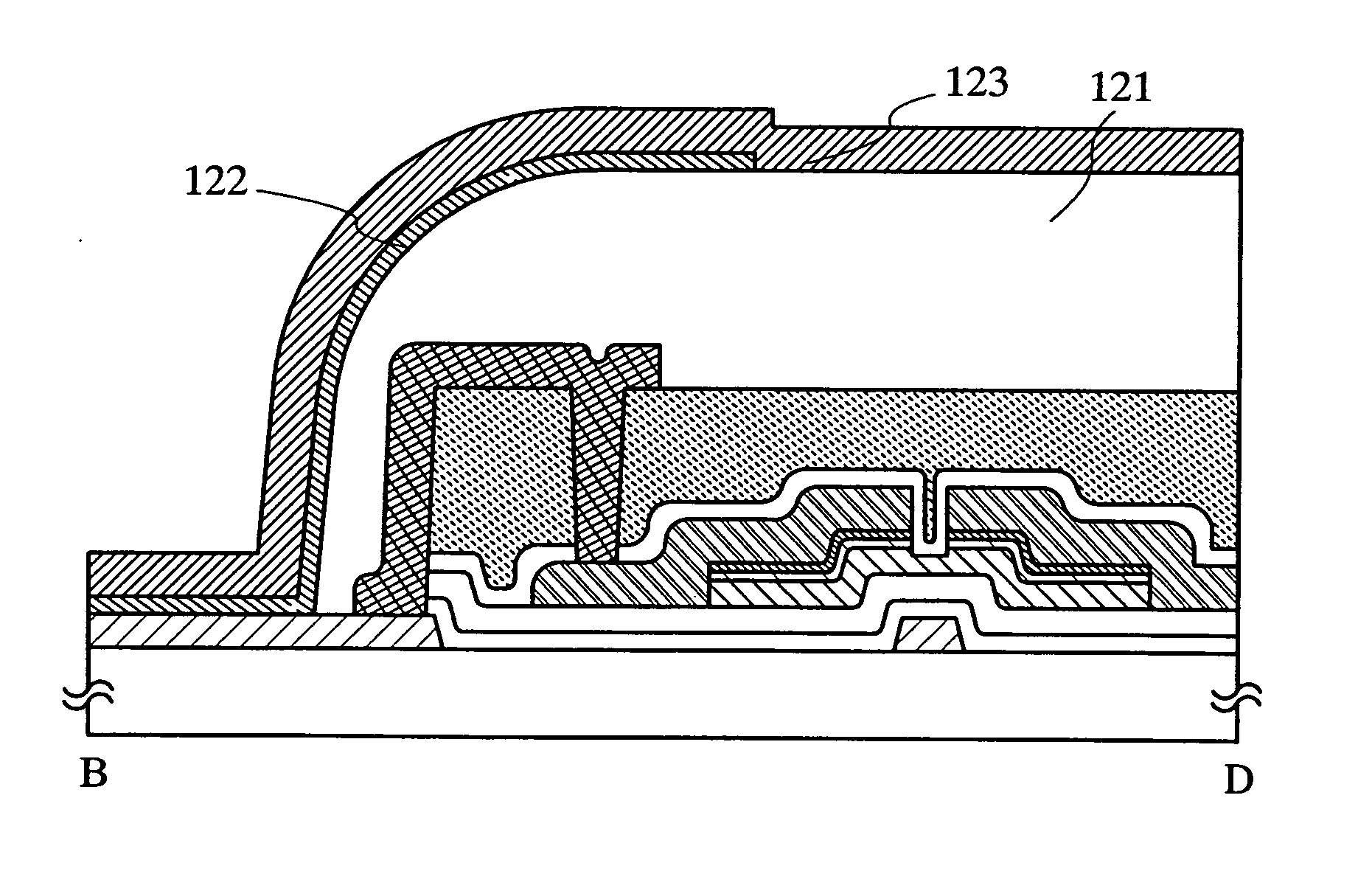

A manufacturing method of a display device having TFTs capable of high-speed operation with few variations of threshold voltage is provided, in which materials are used with high efficiency and a small number of photomasks is required. The display device of the invention comprises a gate electrode layer and a pixel electrode layer formed over an insulating surface, a gate insulating layer formed over the gate electrode layer, a crystalline semiconductor layer formed over the gate insulating layer, a semiconductor layer having one conductivity type formed in contact with the crystalline semiconductor layer, a source electrode layer and a drain electrode layer formed in contact with the semiconductor layer having one conductivity type, an insulating later formed over the source electrode layer, the drain electrode layer, and the pixel electrode layer, a first opening formed in the insulating layer to reach the source electrode layer or the drain electrode layer, a second opening formed in the gate insulating layer and the insulating layer to reach the pixel electrode layer, and a wiring layer formed in the first opening and the second opening to electrically connect the source electrode layer or the drain electrode layer to the pixel electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

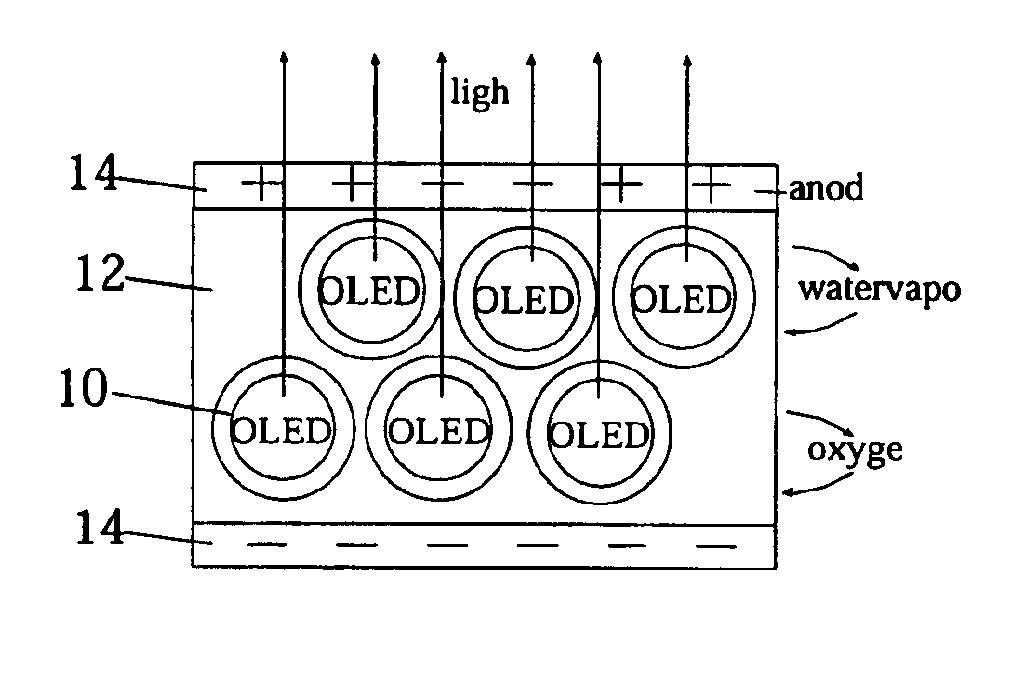

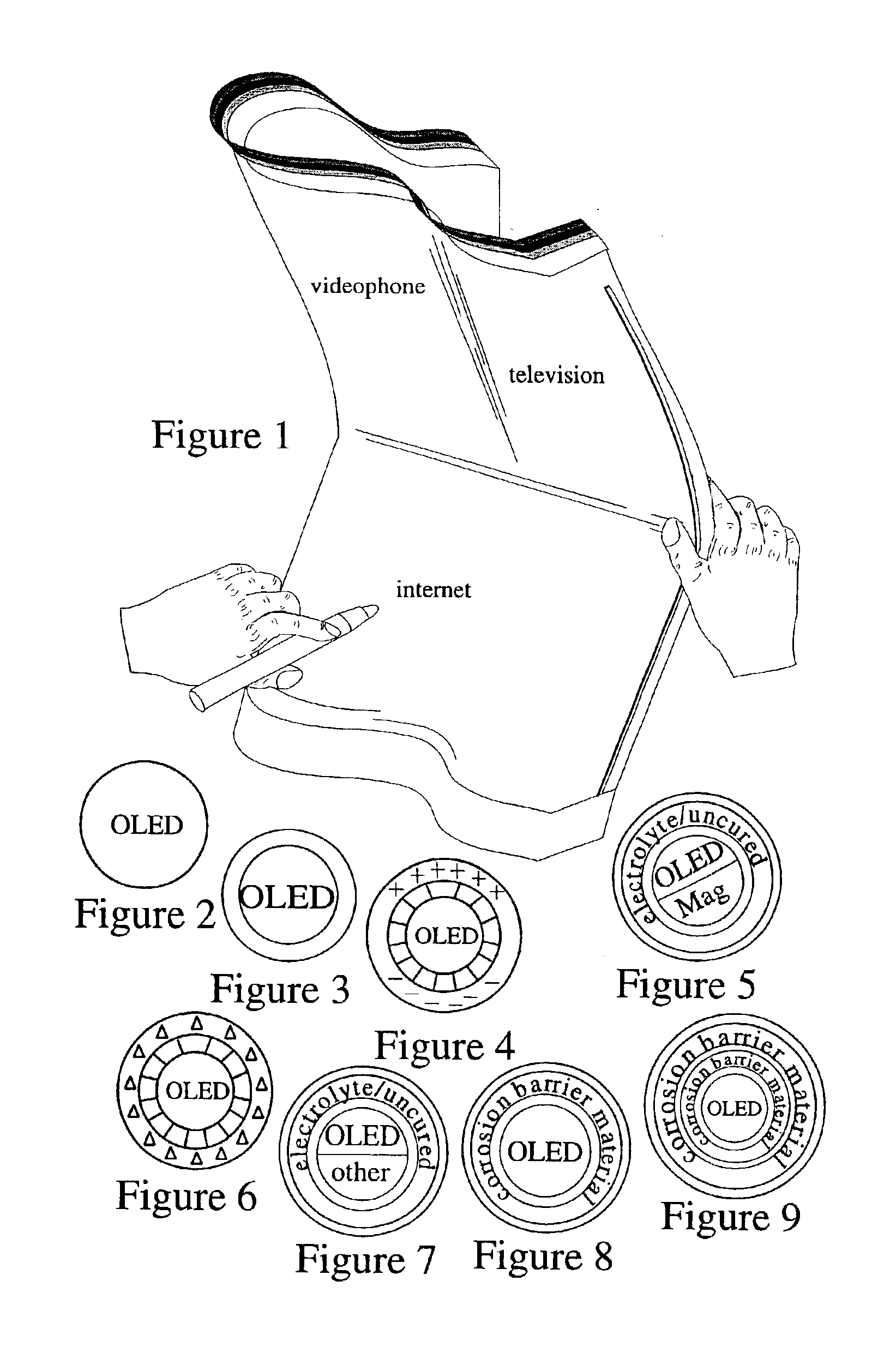

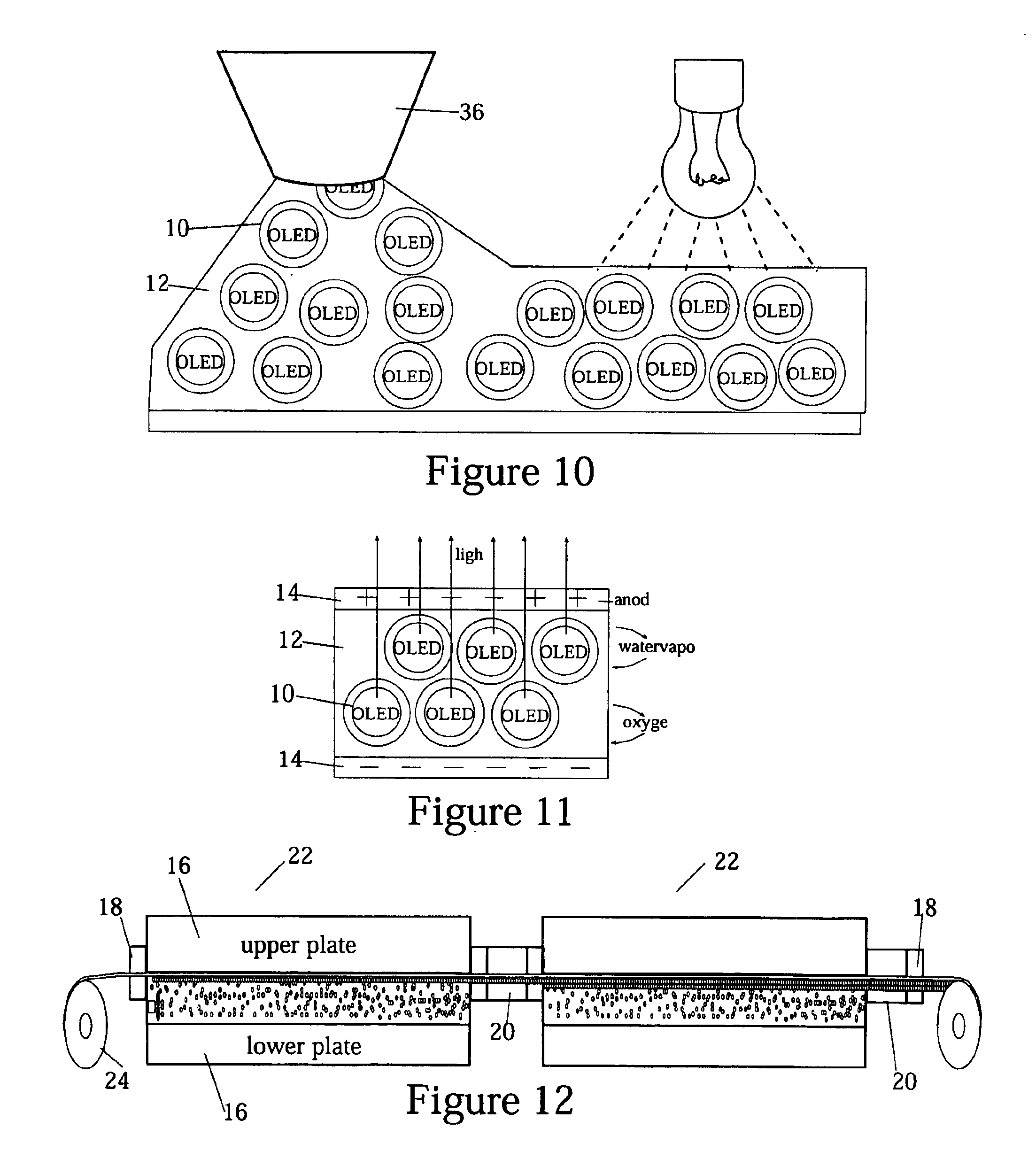

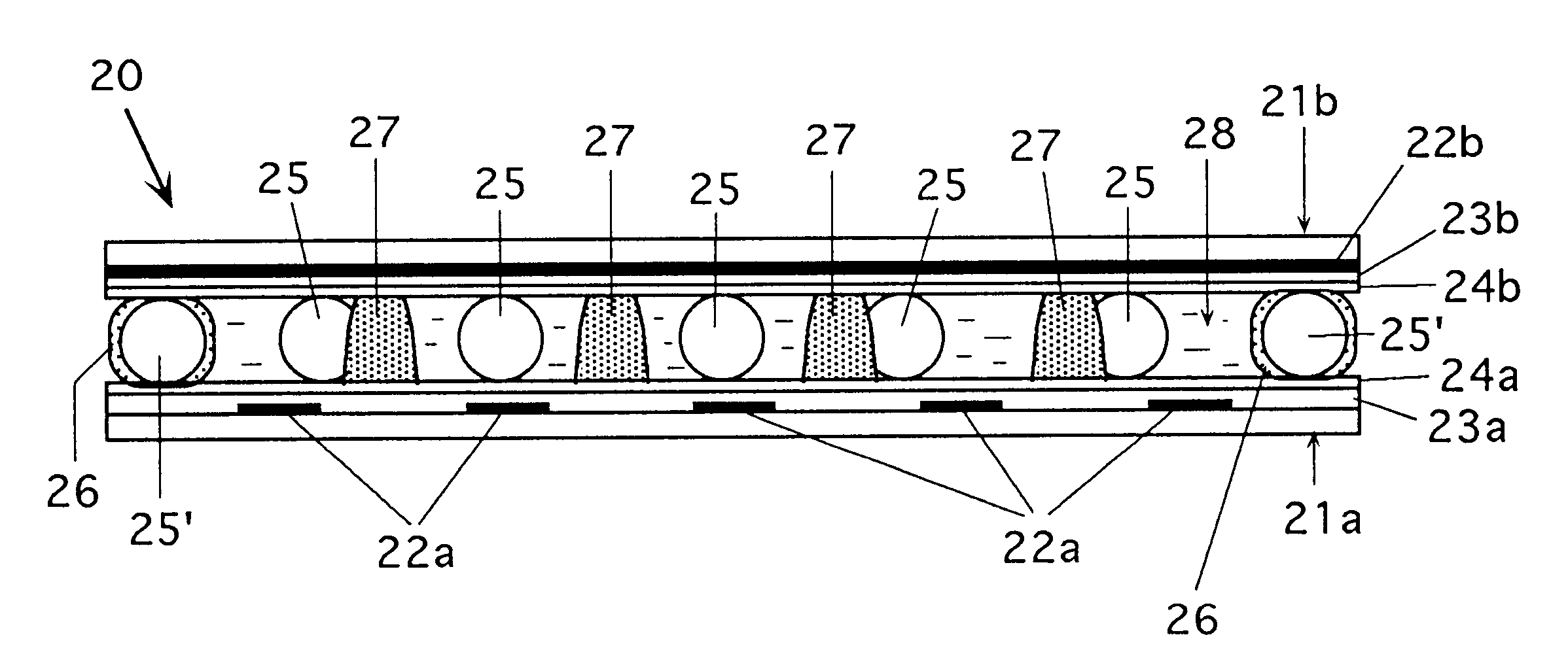

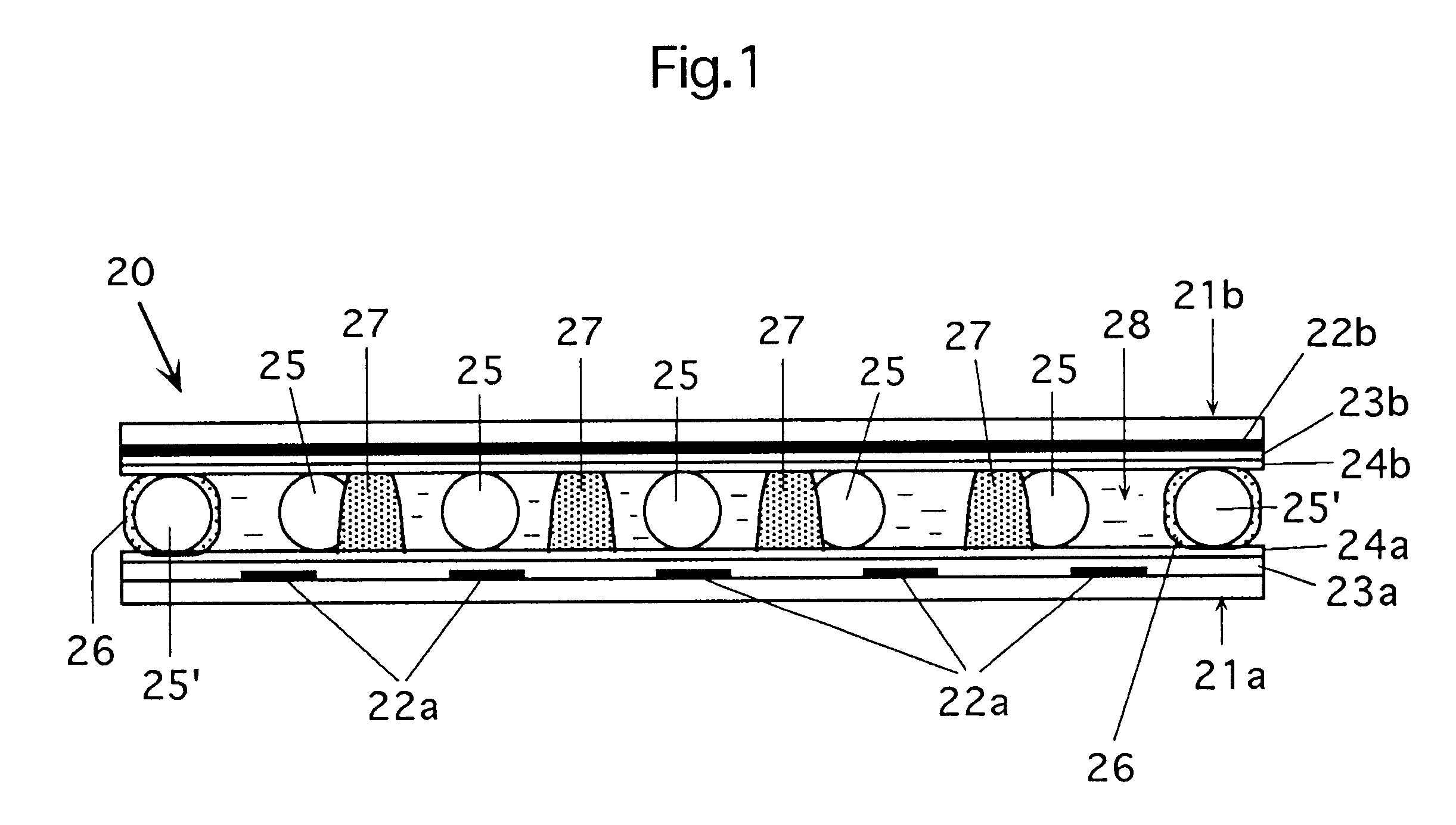

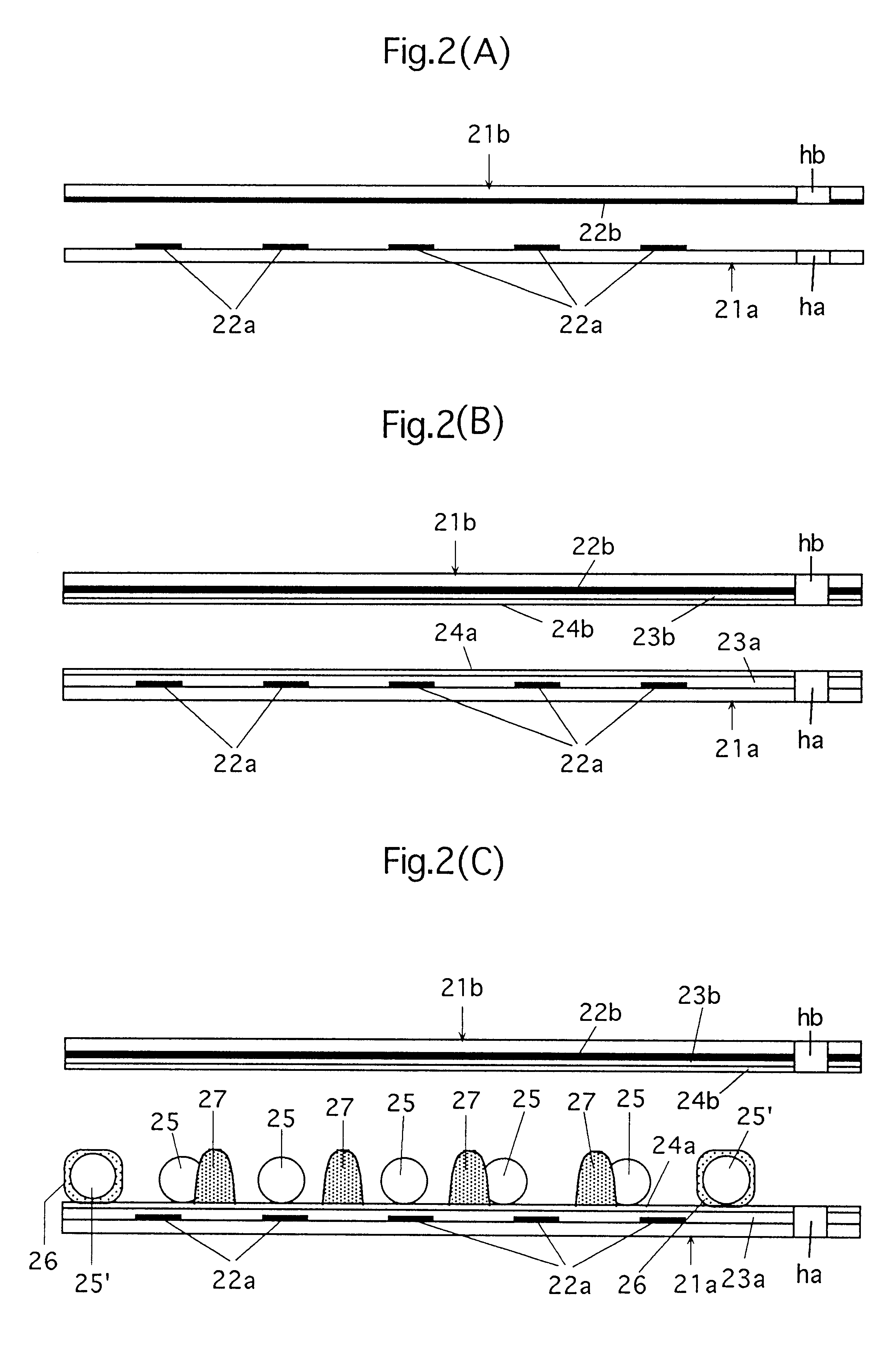

Organic light active devices and methods for fabricating the same

InactiveUS6876143B2Easy to useSimplify manufacturing stepsDischarge tube luminescnet screensFinal product manufactureDisplay deviceCarrier fluid

A method for fabricating organic light active devices using field-attractive Organic Light Active Material (“OLAM™”) microcapsules. The OLAM microcapsules are randomly dispersed within a monomer carrier fluid that is injected or otherwise disposed between two electrodes. The OLAM microcapsules may include additives that impart rheological properties, and other electrical, mechanical, optical and magnetic properties. The OLAM microcapsules form chains between the electrodes when an aligning field is applied. Holding the aligning field to keep the chains formed, the carrier fluid is cured and the OLAM microcapsule chains are locked into alignment between the electrodes. The problem of contamination of the OLAM material is the major factor limiting the display life span, and thus is a bar to commercial success. This fabrication method results in the corrosion sensitive OLAM material being protected by the microcapsule shell and the cured carrier, and the pixel alignment is automatic, since the OLAM microcapsule chains are formed only between the electrodes.

Owner:DANIELS JOHN JAMES

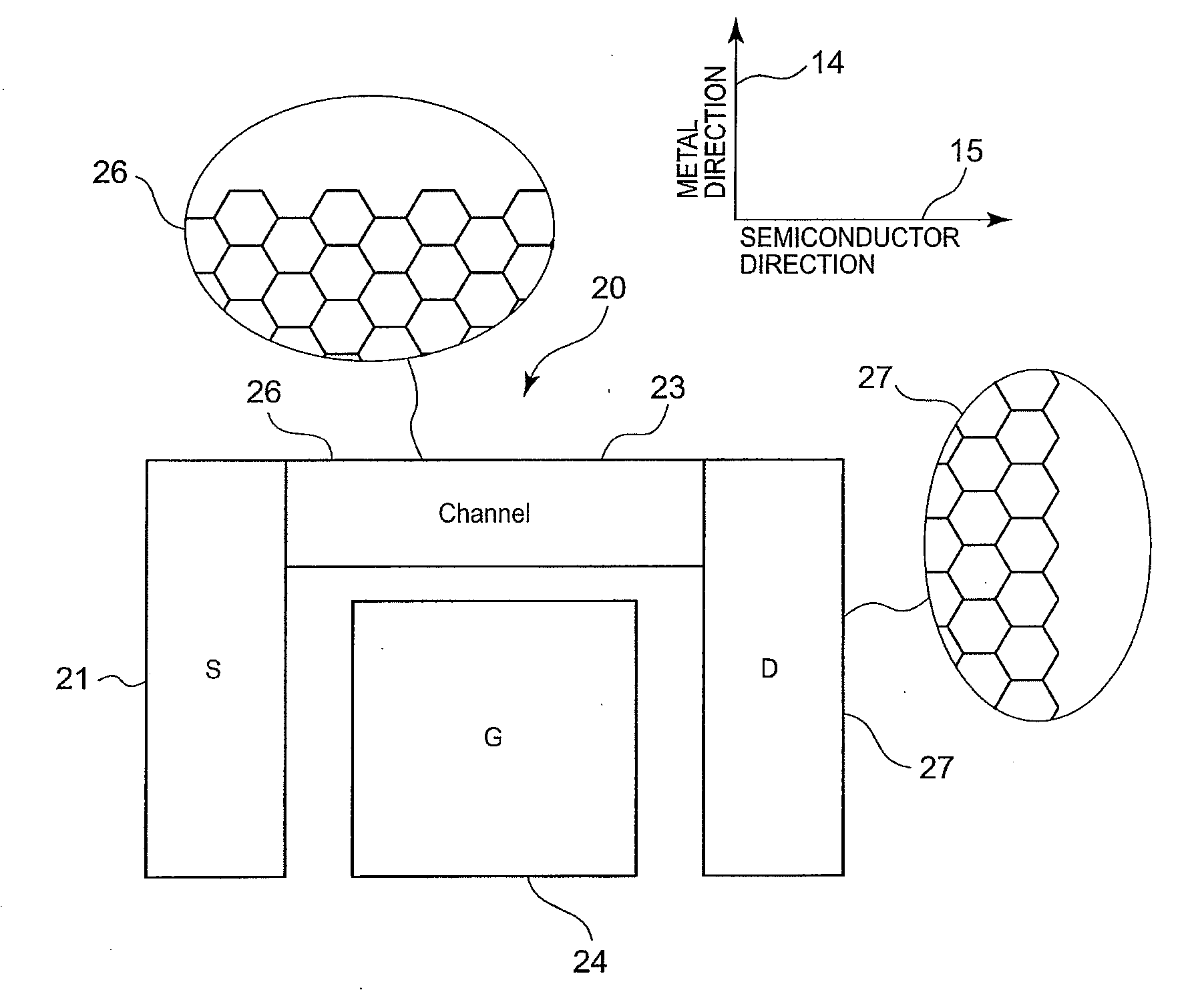

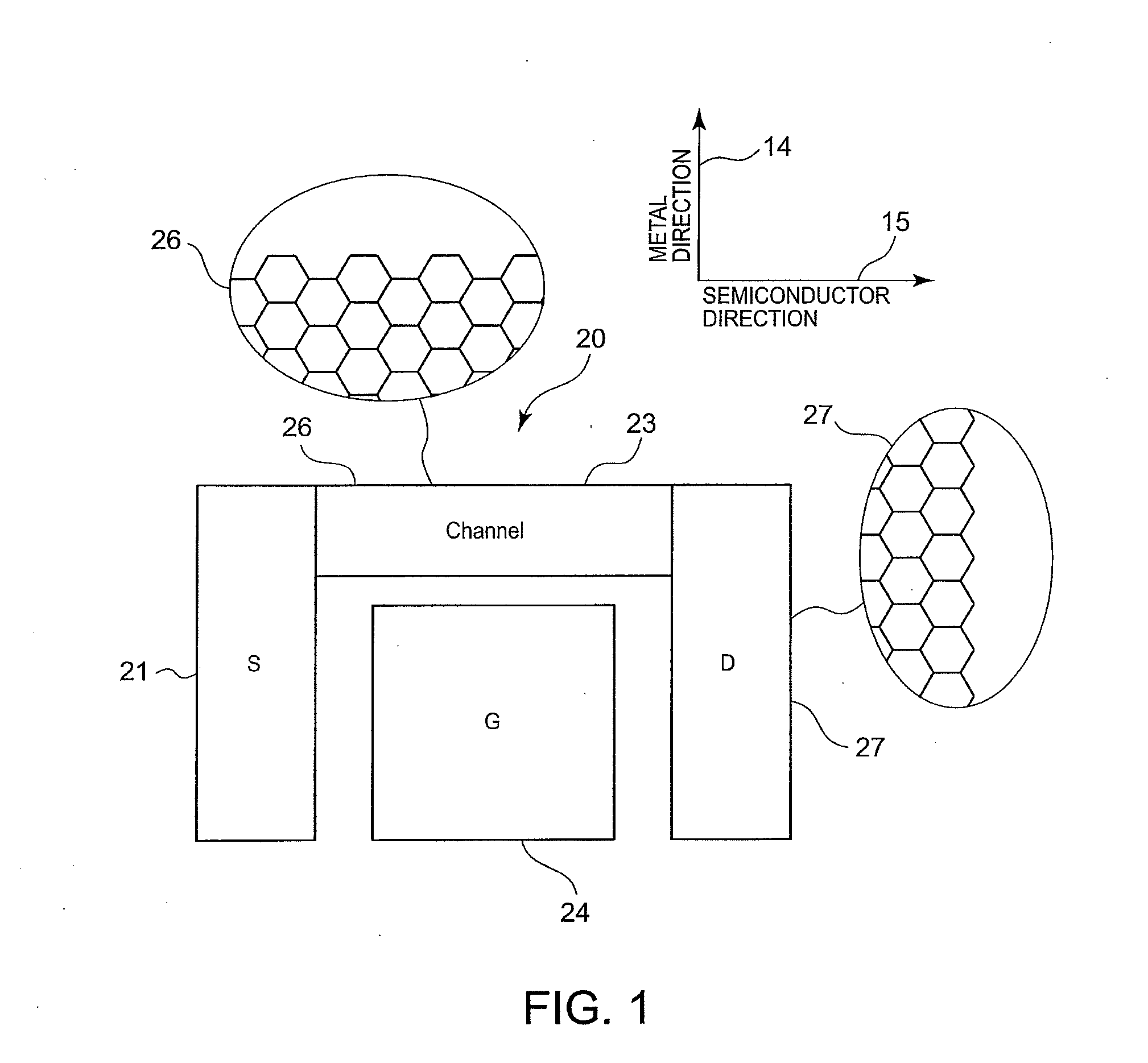

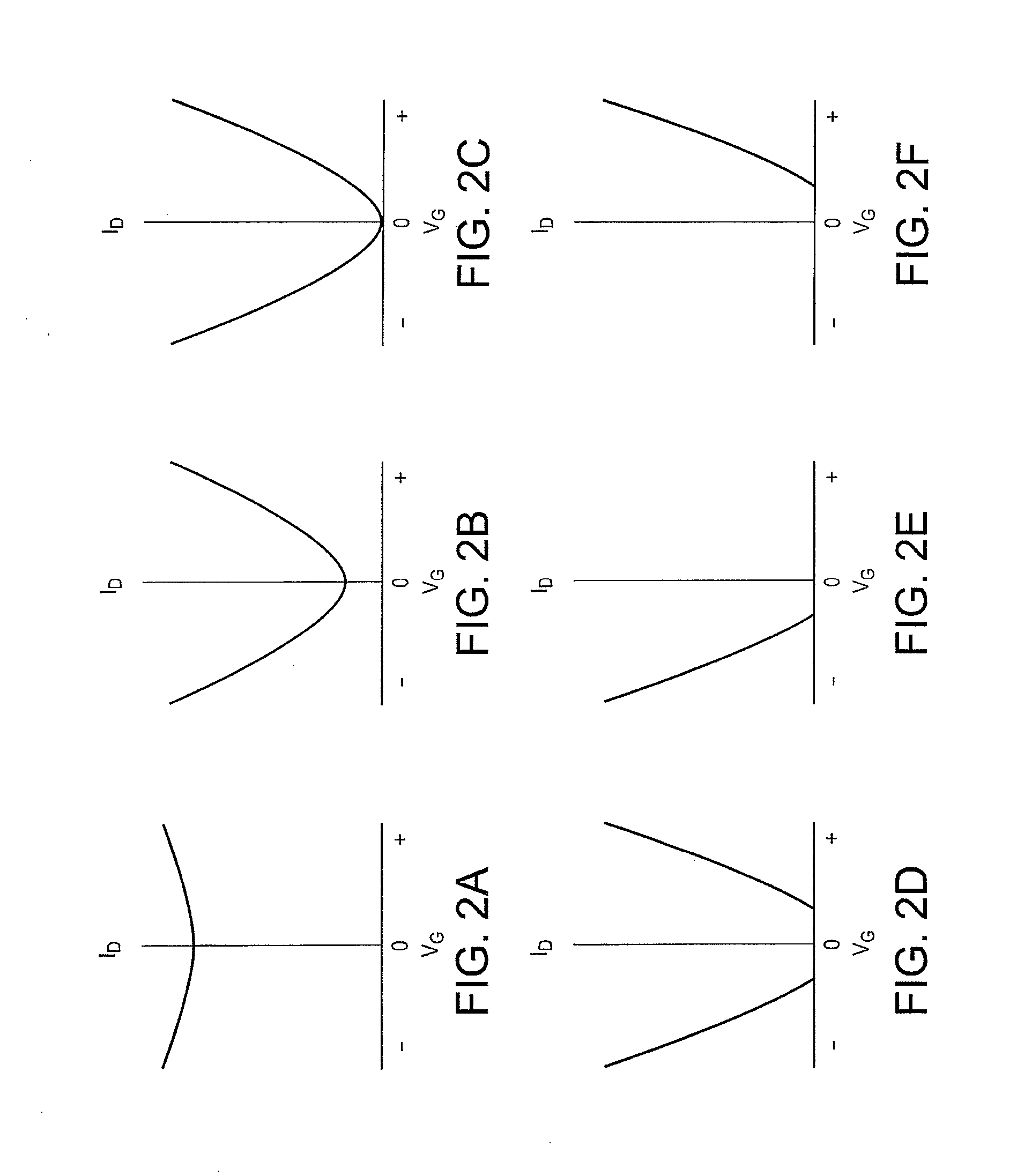

Semiconductor device using graphene and method of manufacturing the same

ActiveUS20100102292A1Guaranteed high speed operationReduce power consumptionTransistorNanoinformaticsInterconnectionGraphene

Owner:NEC CORP

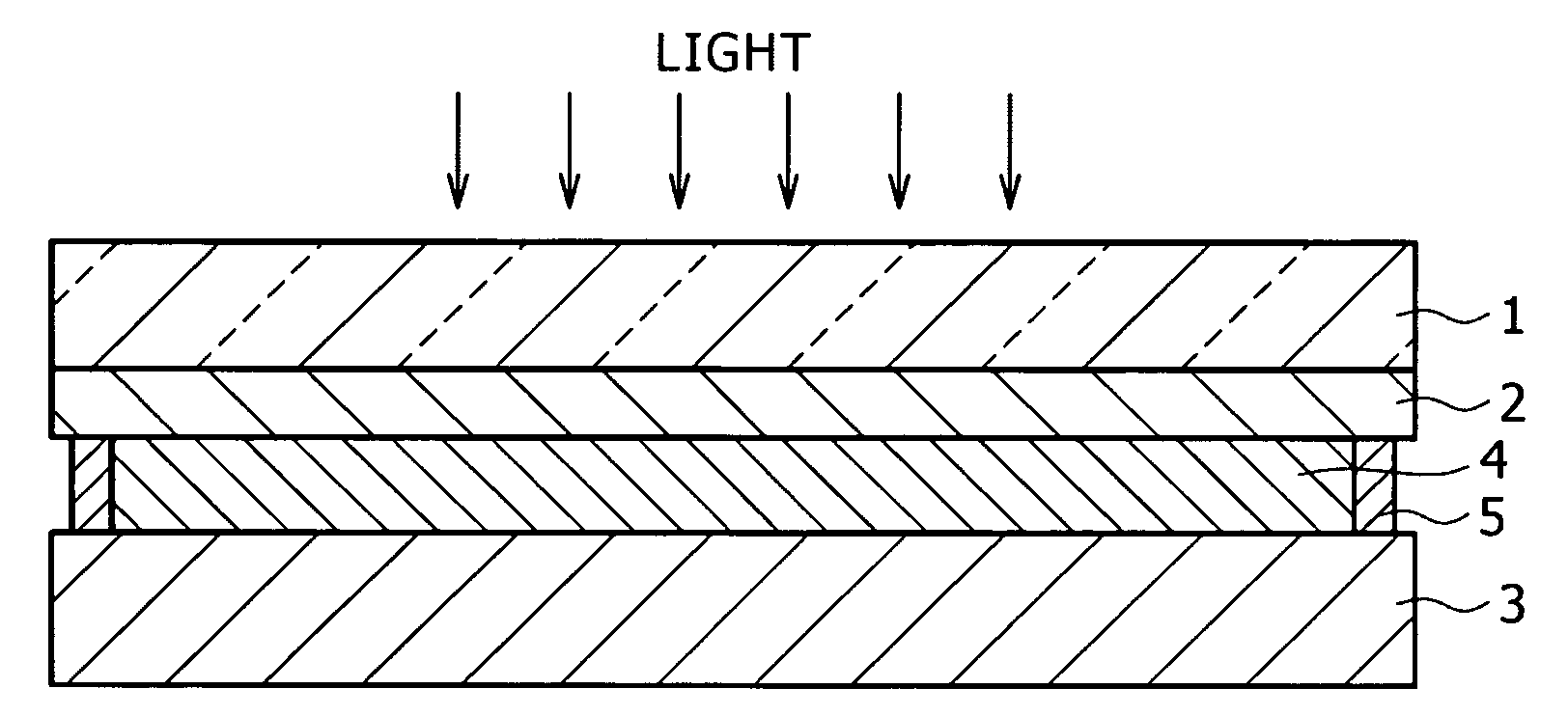

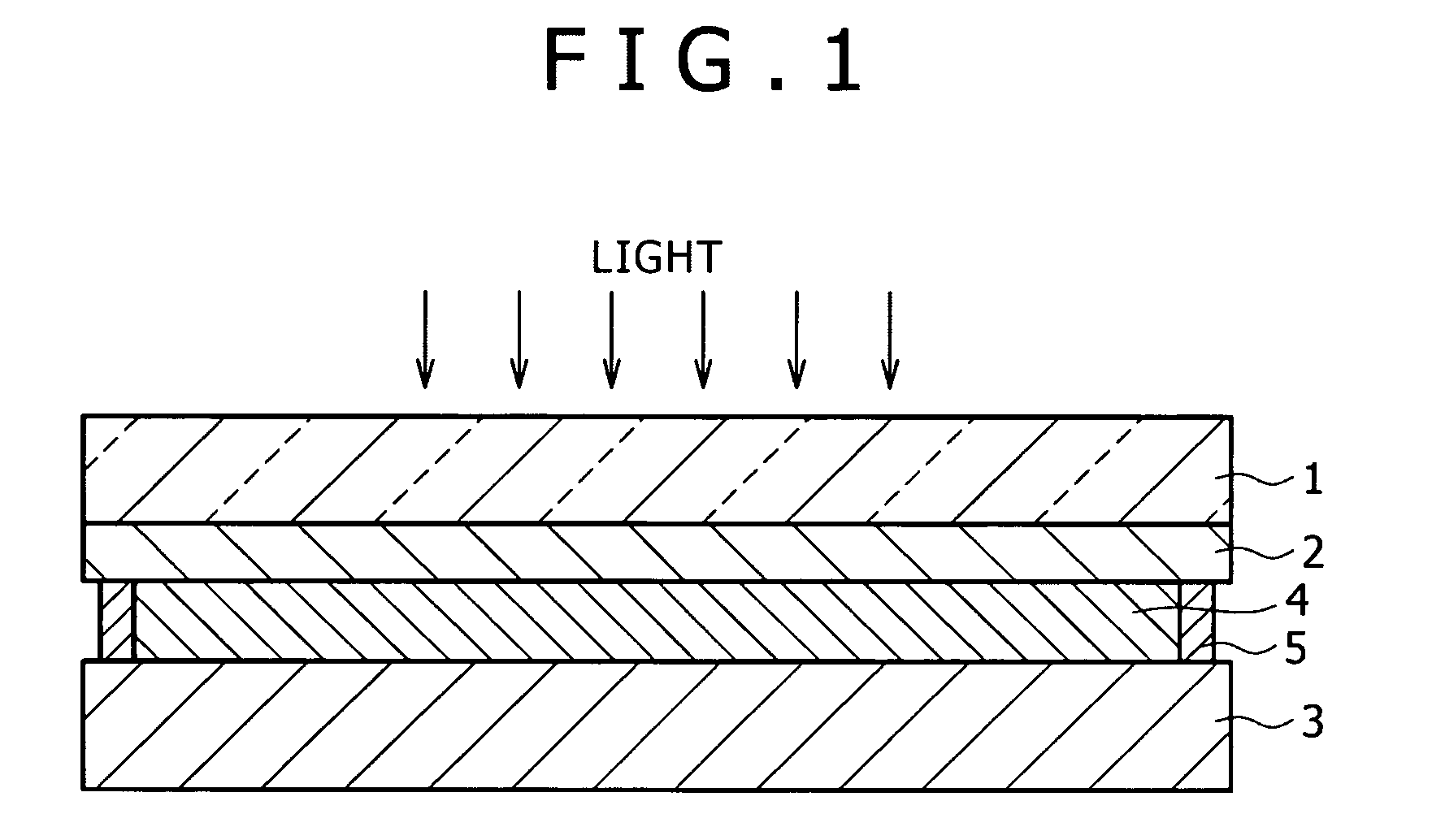

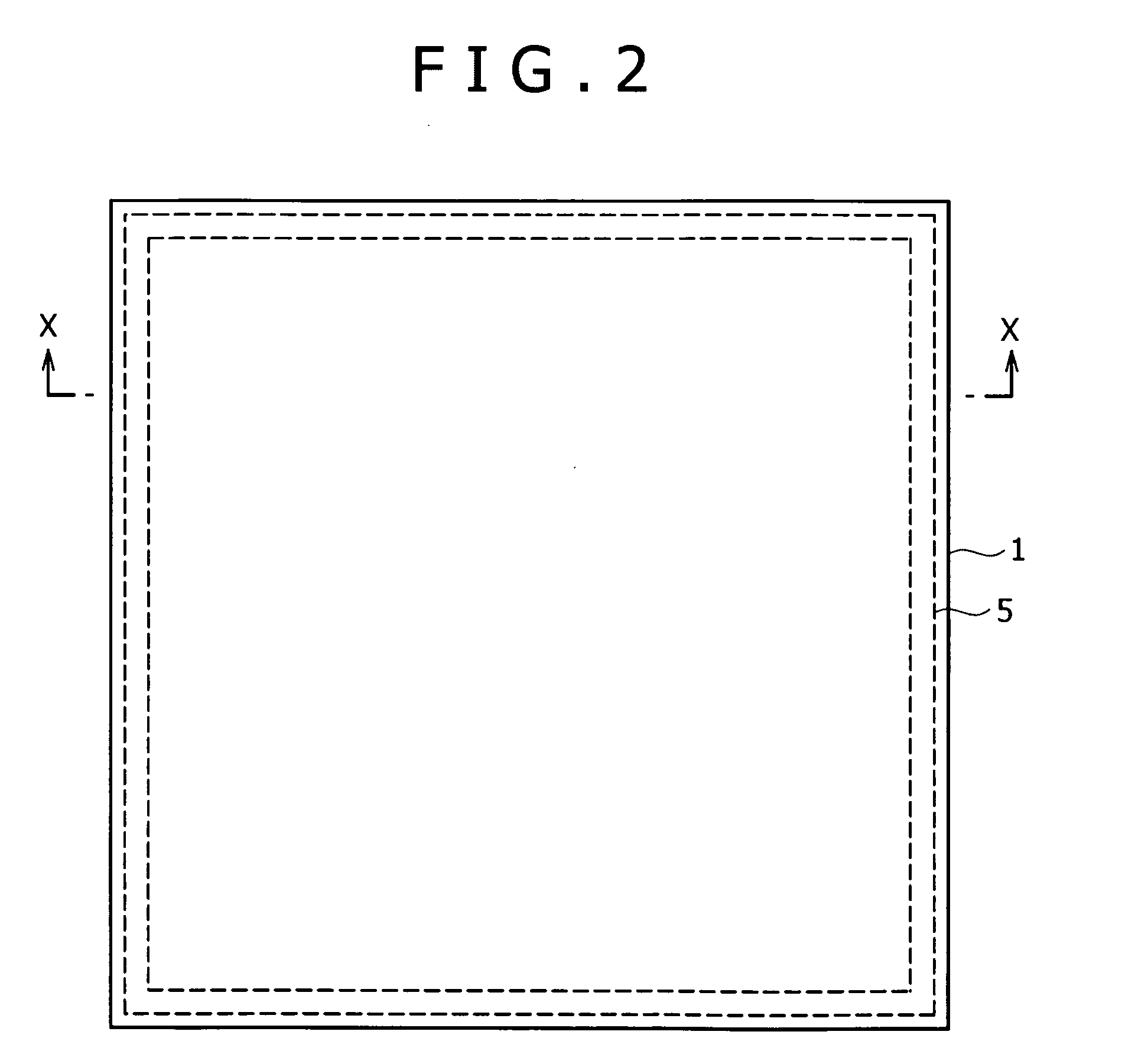

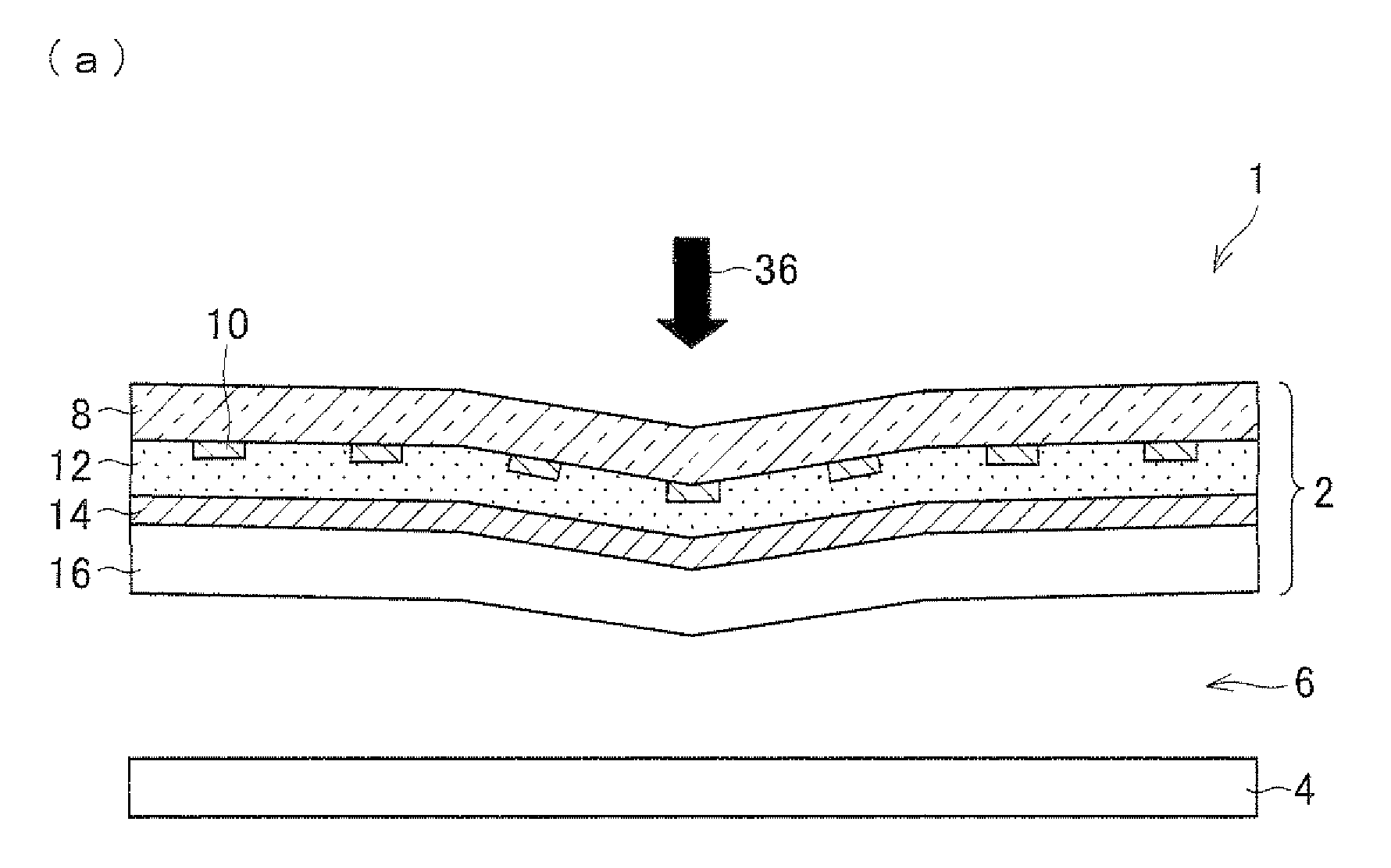

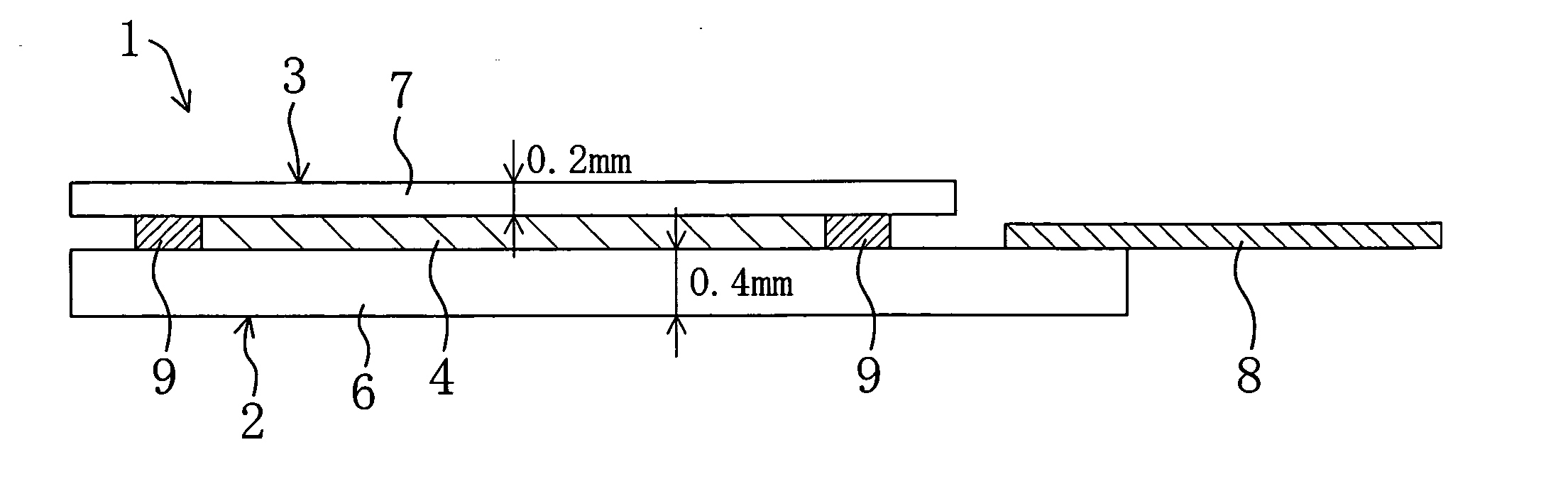

Dye-sensitized photoelectric conversion device and method of manufacturing the same

InactiveUS20100101648A1Reduced durabilityReduced strengthElectrolytic capacitorsFinal product manufactureAtmospheric airPhotoelectric conversion

A method of manufacturing a dye-sensitized photoelectric conversion device is provided by which a dye-sensitized photoelectric conversion device being excellent in strength and durability and free of any projection, as a result of the absence of need for an end seal, can be fabricated through simple manufacturing steps. In manufacturing a dye-sensitized photoelectric conversion device which has an electrolyte between a dye-sensitized semiconductor layer and a counter electrode and which also has a first armor member provided on the outside of the dye-sensitized semiconductor layer and a second armor member provided on the outside of the counter electrode, a sealing material and the electrolyte are formed at predetermined locations of one or both of the first armor member and the second armor member, thereafter the first armor member and the second armor member, with the sealing material and the electrolyte sandwiched therebetween, are adhered to each other with the sealing material under a gas pressure of not higher than the atmospheric air pressure and not lower than the vapor pressure of the electrolyte.

Owner:SONY CORP

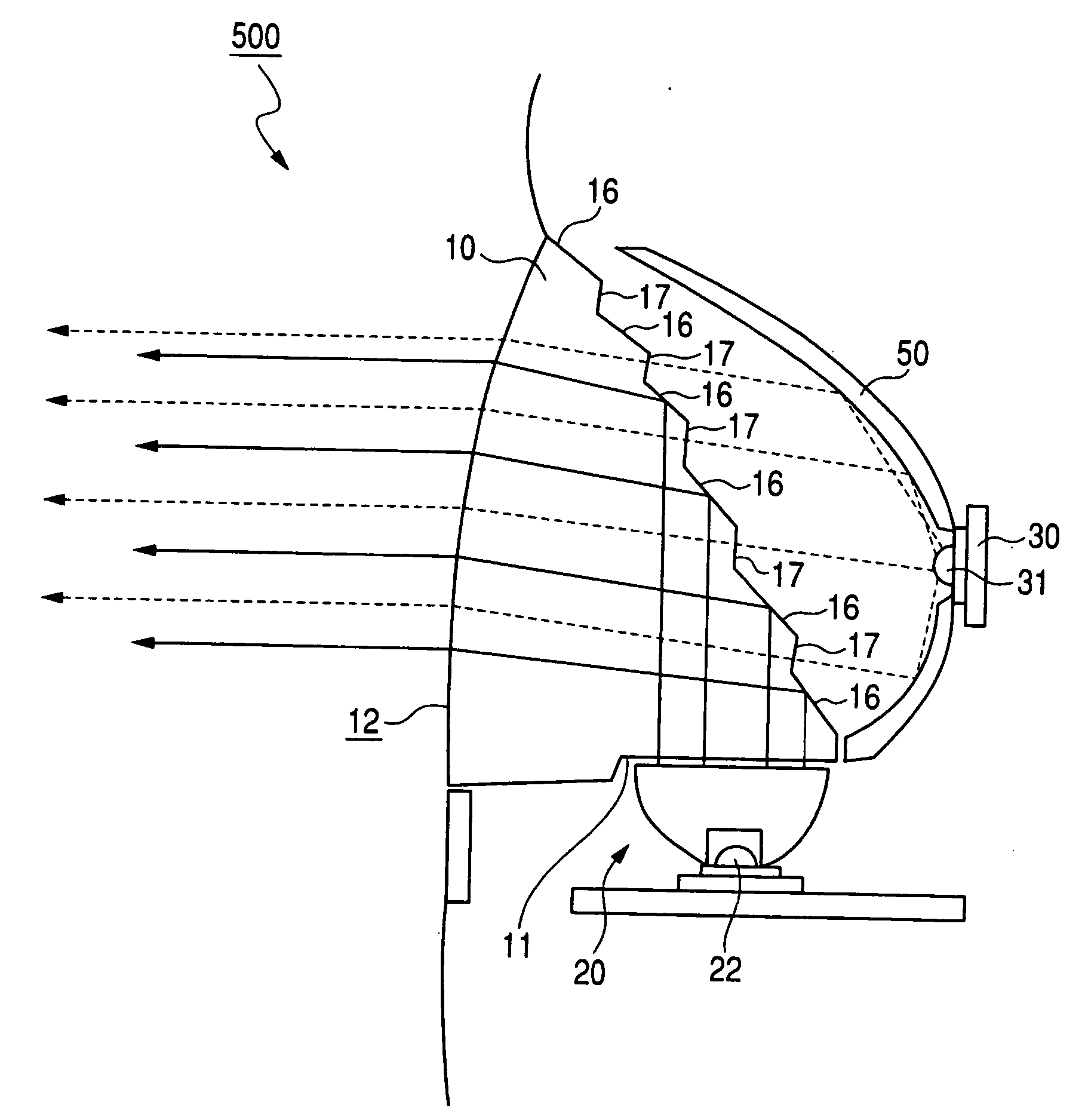

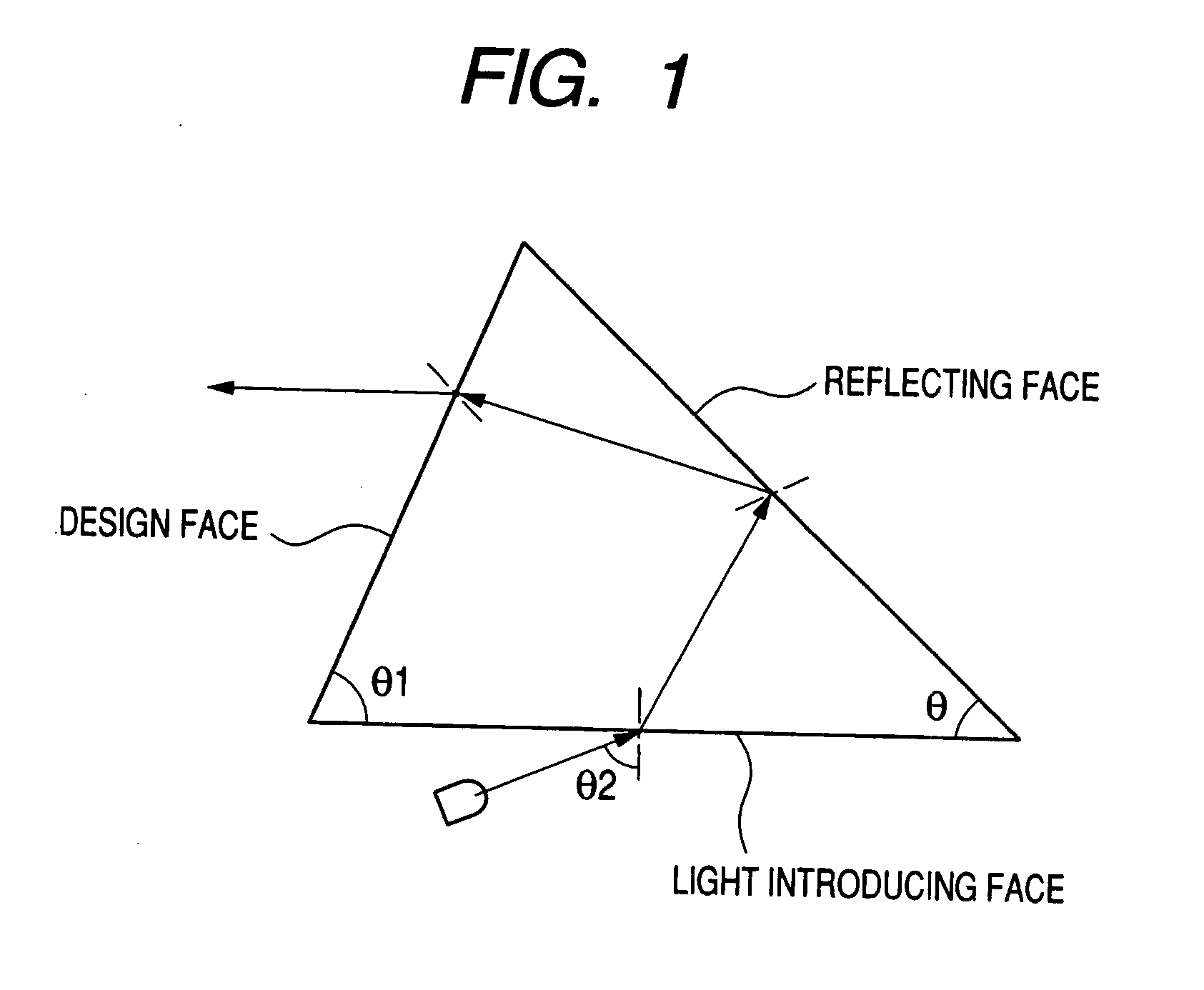

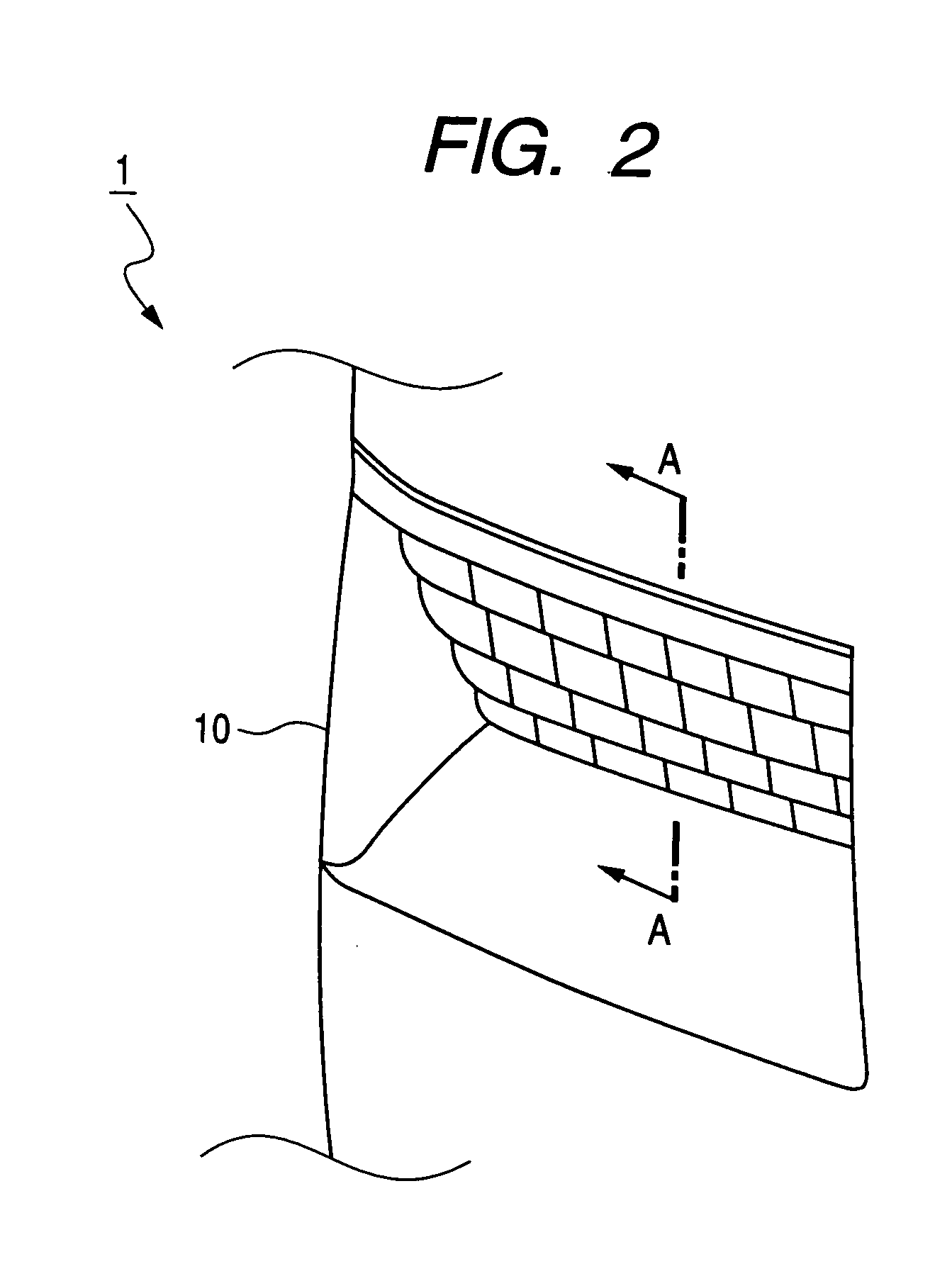

Vehicular lamp

InactiveUS20090027911A1Simplify manufacturing stepsReduce manufacturing costLighting support devicesPoint-like light sourceLight-emitting diodeLight source

The invention is constituted by a vehicular lamp characterized in a lens having a first light source, a second light source, a front light emitting face, a side end face to which the first light source is opposed, and a rear face, wherein the rear face includes a lens having pluralities of reflecting portions and transmitting portions consecutively aligned alternately in a direction of being remote from the side end face, and a reflecting face arranged on a rear side of the lens, light of the first light source is incident on the lens from the side end face of the lens, reflected by an interface of the reflecting portion, thereafter, radiated from the front light emitting face, and light of the second light source is reflected by the reflecting portion, thereafter, incident on the lens from the transmitting portion and radiated from the front light emitting face.

Owner:TOYODA GOSEI CO LTD

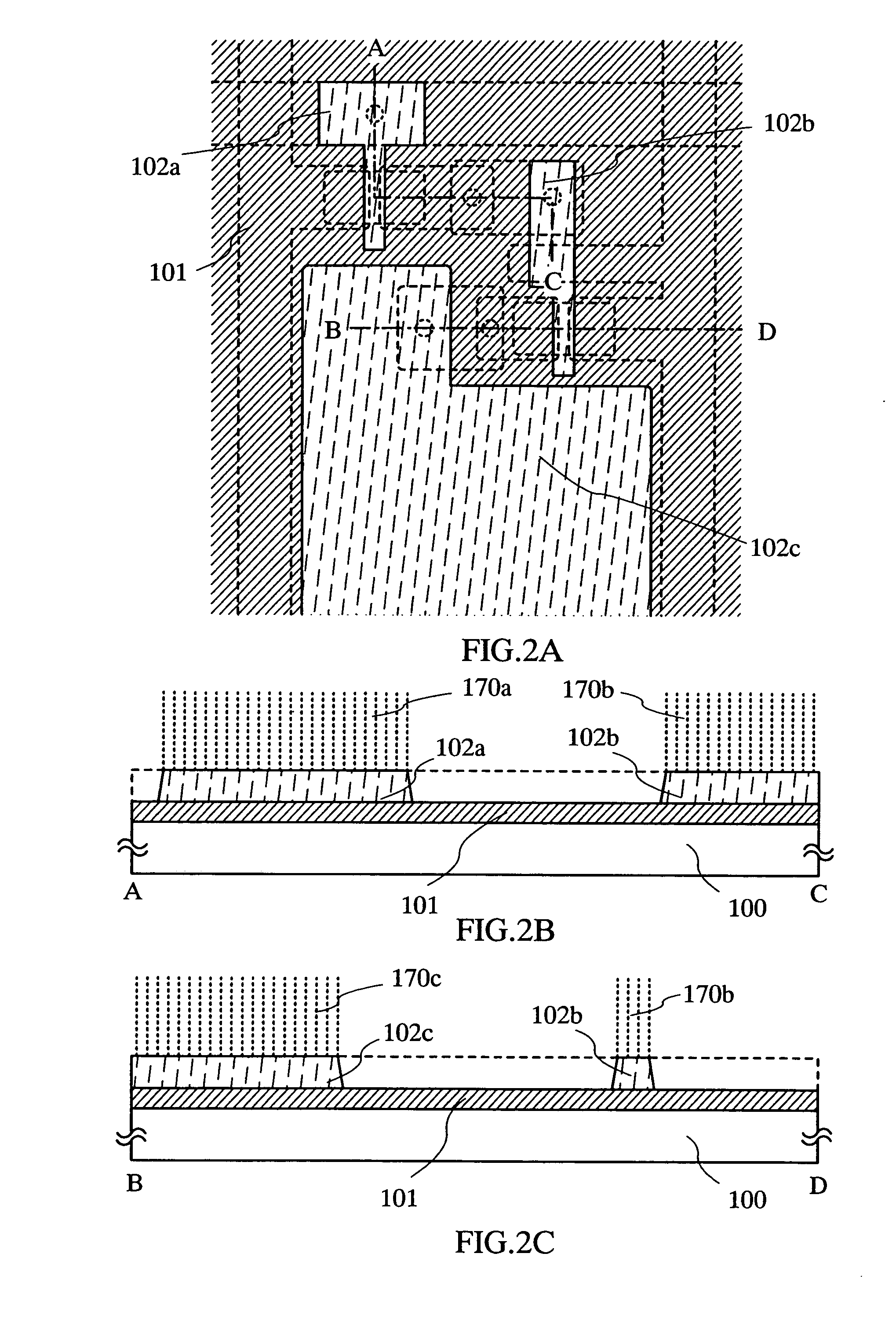

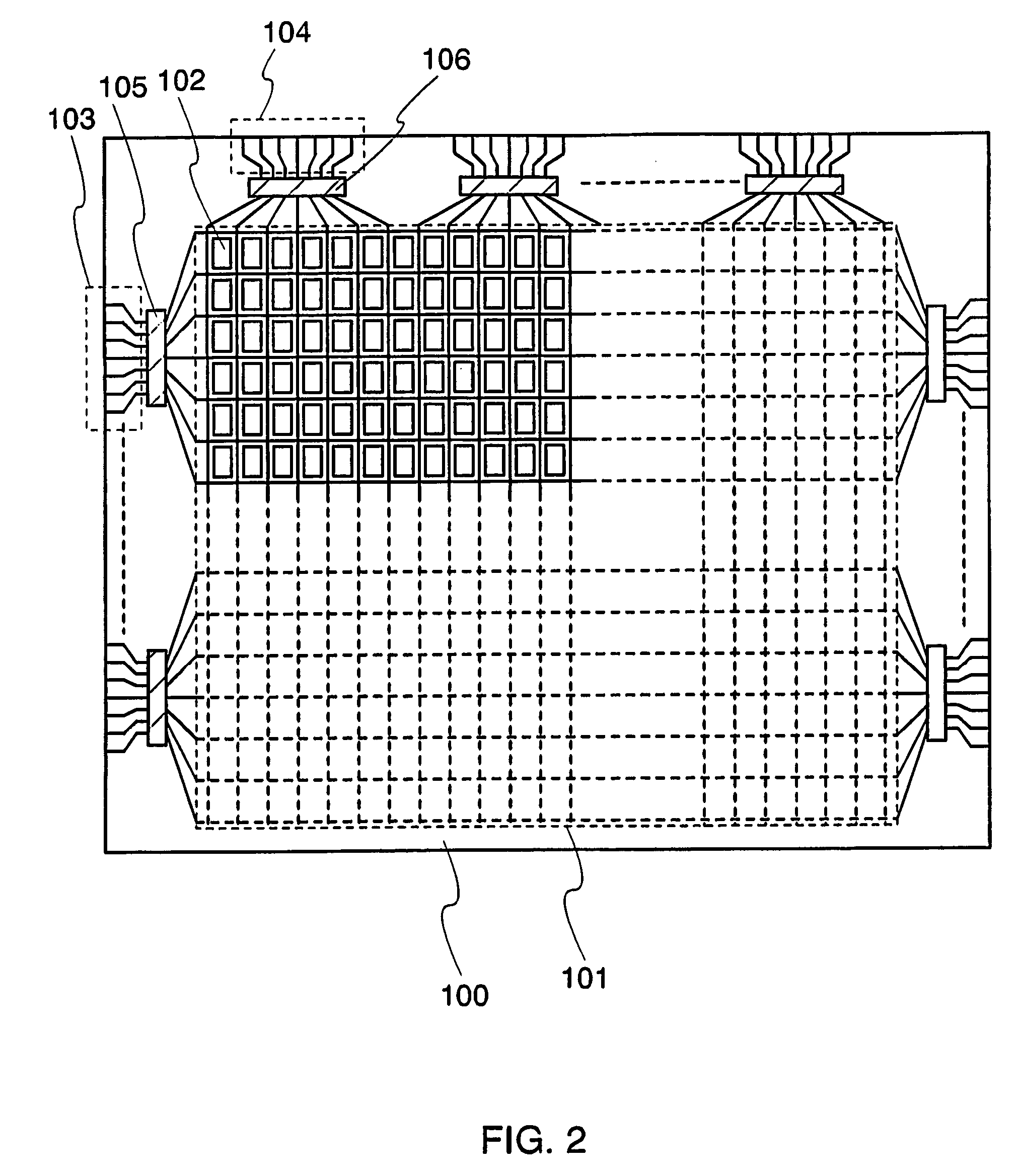

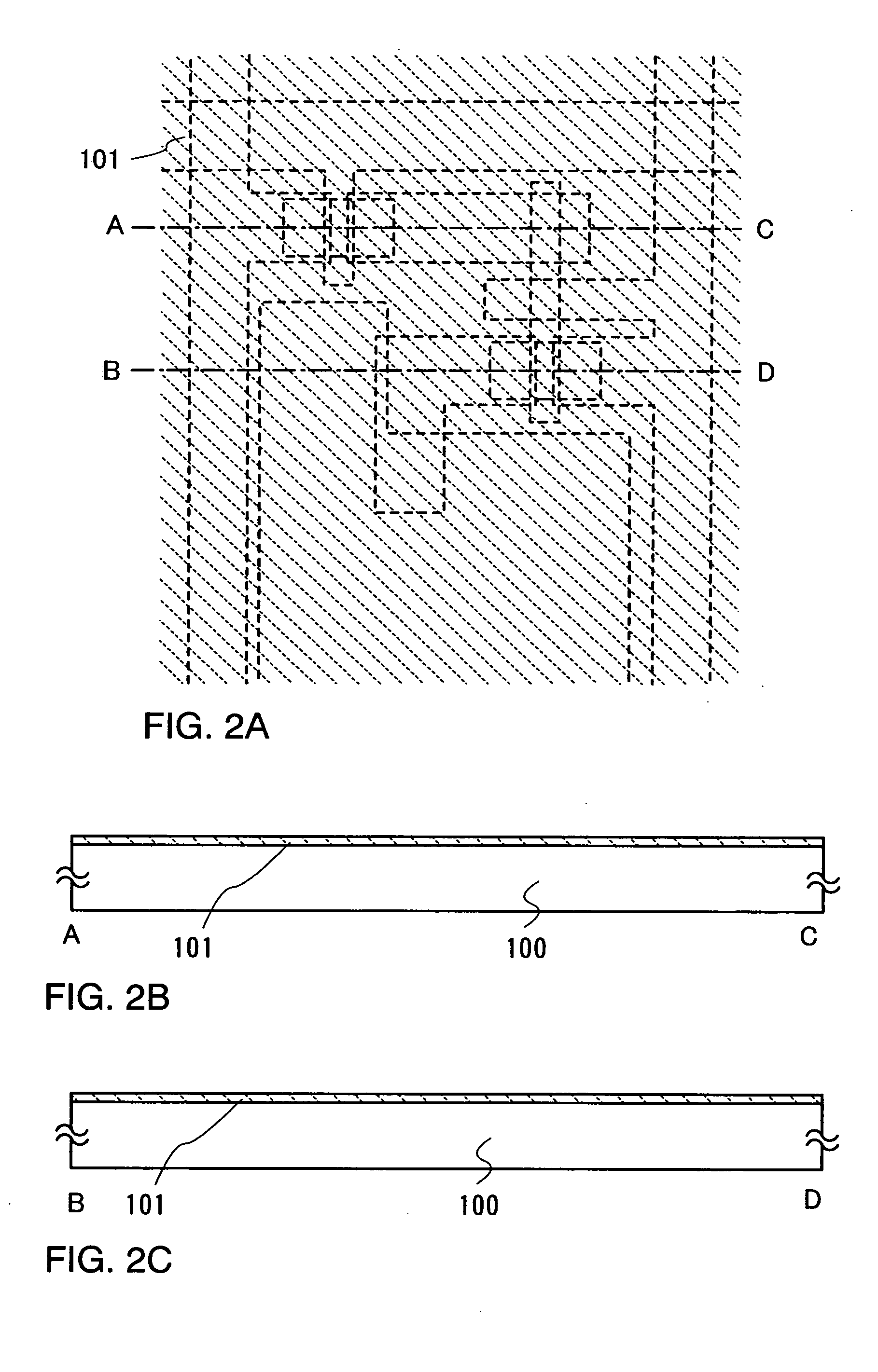

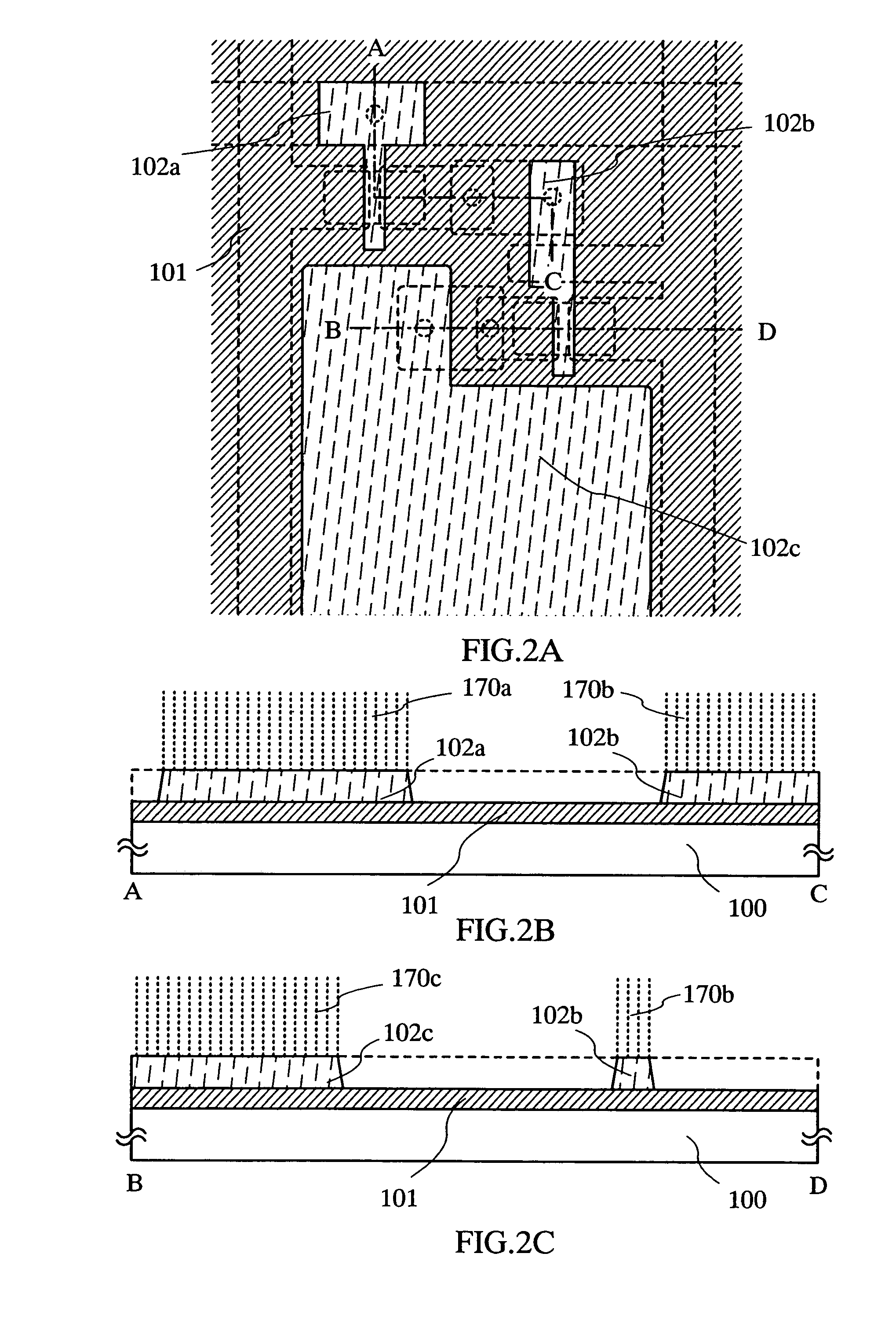

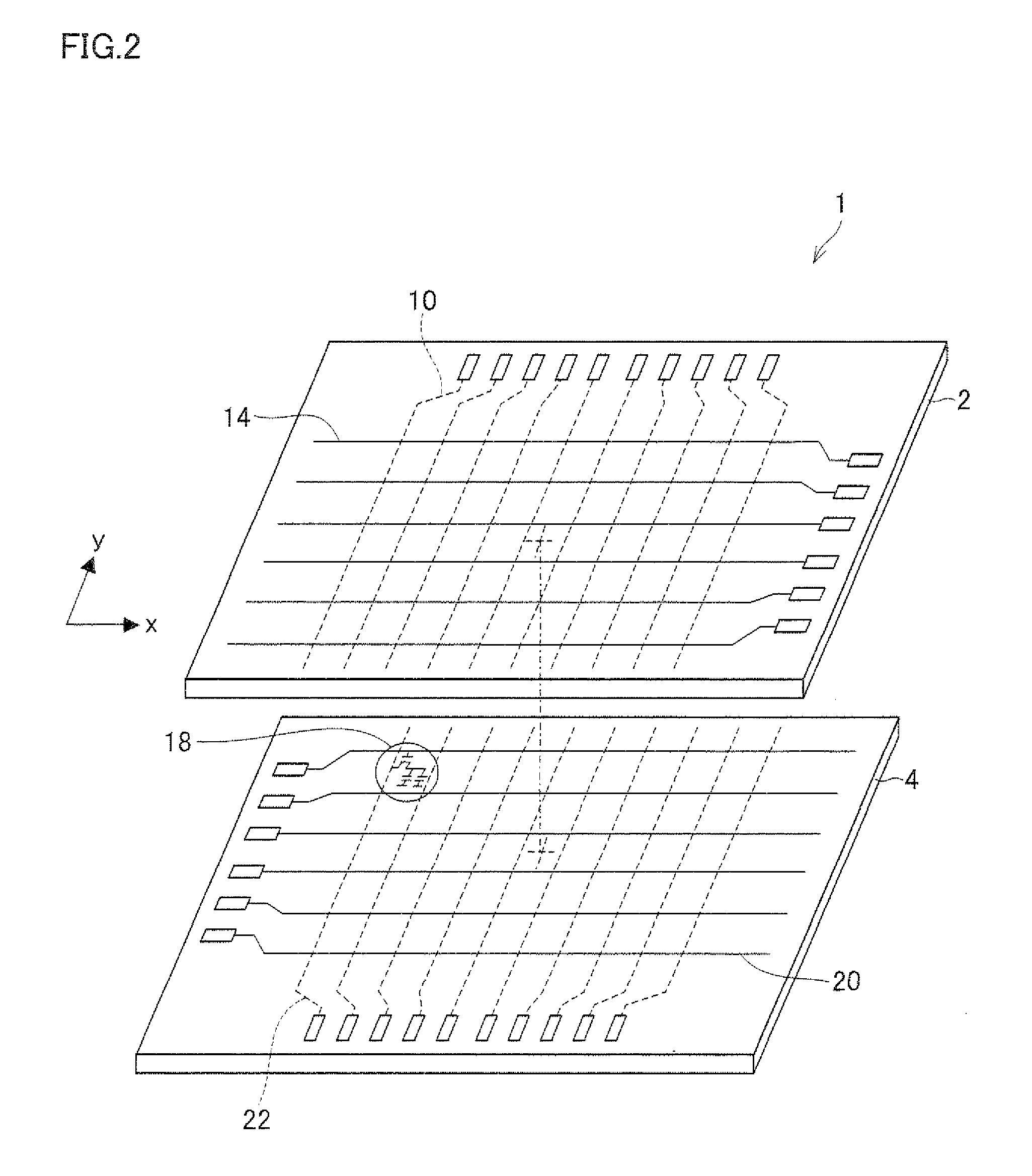

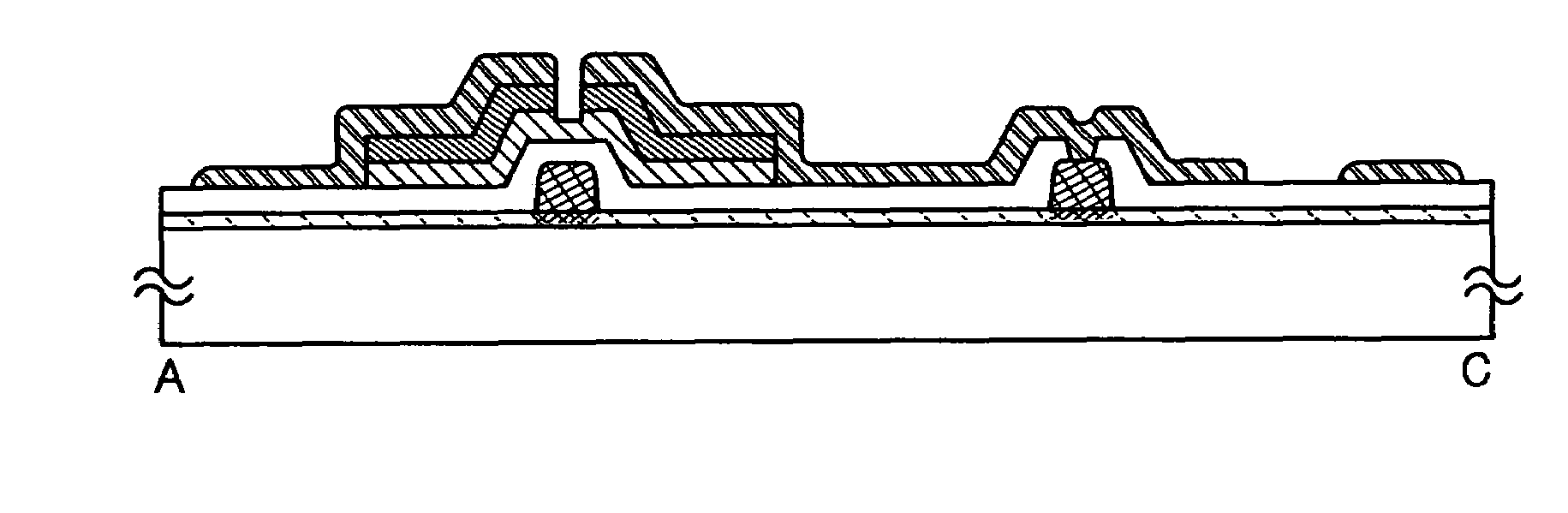

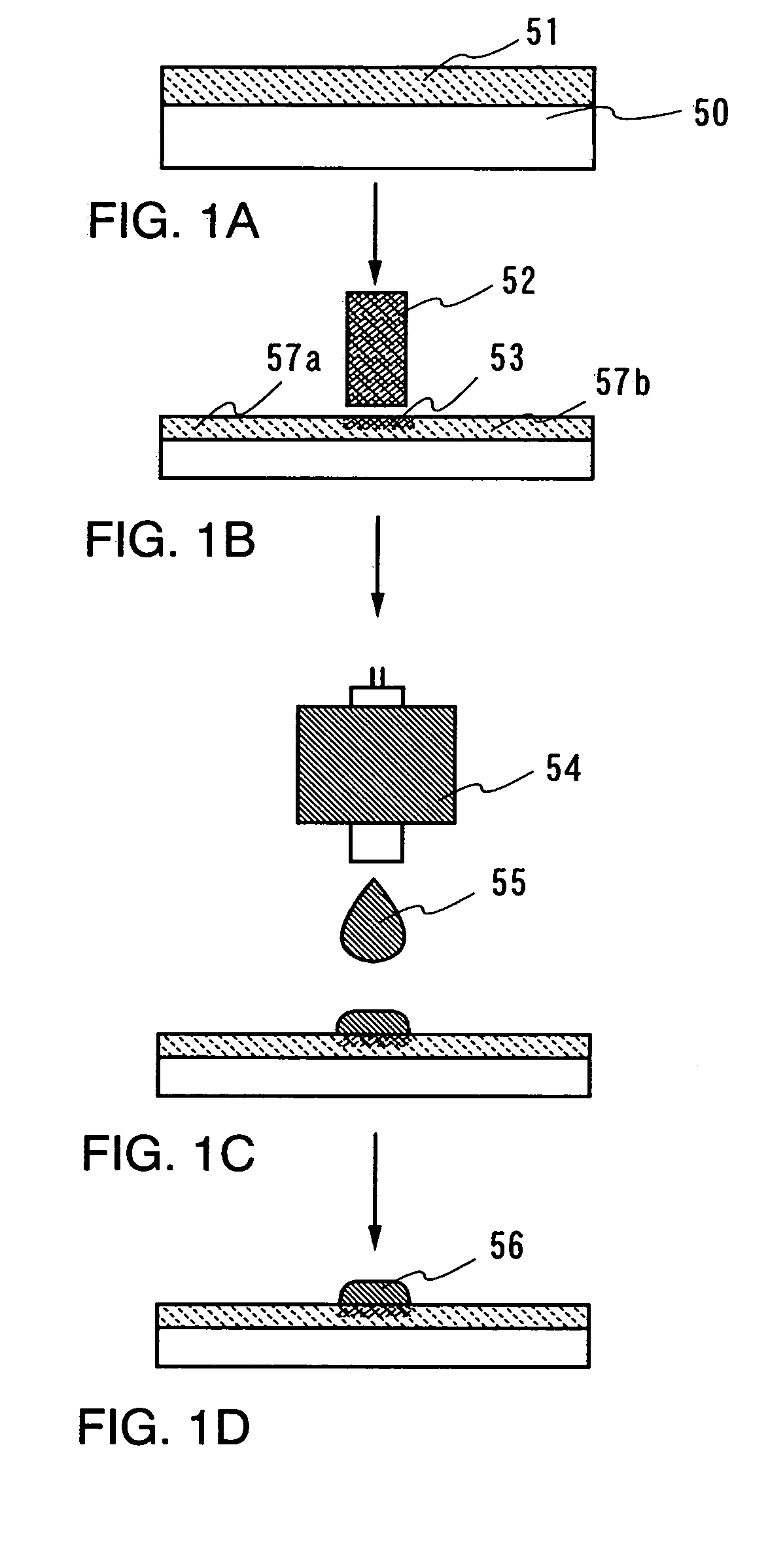

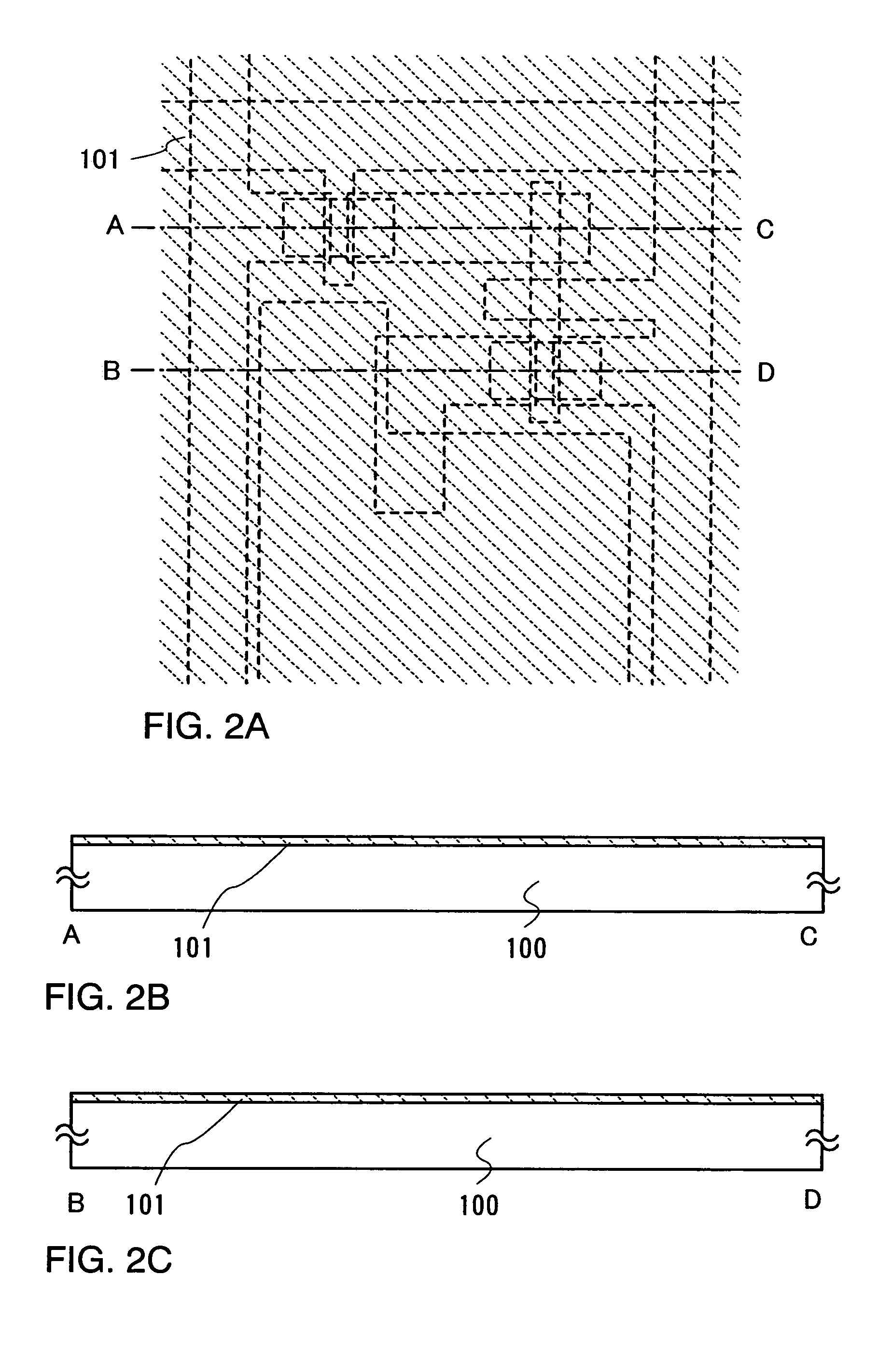

Liquid crystal display device and method for manufacturing the same, and liquid crystal television receiver

InactiveUS20070051952A1Improve material efficiencySimplify manufacturing stepsProjectorsSolid-state devicesTelevision receiversEngineering

At least one or more of a conductive layer which forms a wiring or an electrode and a pattern necessary for manufacturing a display panel such as a mask for forming a predetermined pattern is formed by a method capable of selectively forming a pattern to manufacture a liquid crystal display device. A droplet discharge method capable of forming a predetermined pattern by selectively discharging a droplet of a composition in accordance with a particular object is used as a method capable of selectively forming a pattern in forming a conductive layer, an insulating layer, or the like.

Owner:SEMICON ENERGY LAB CO LTD

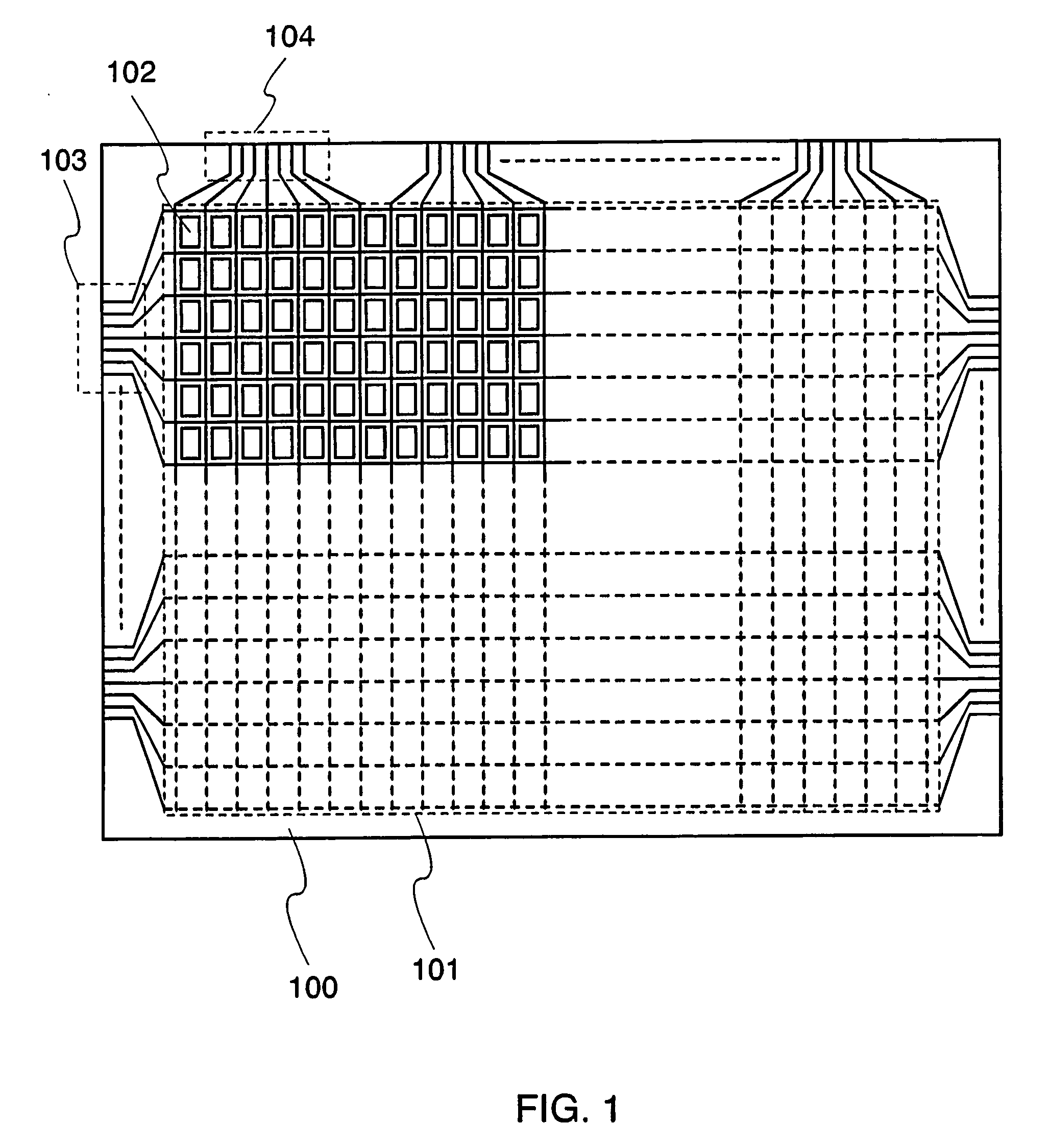

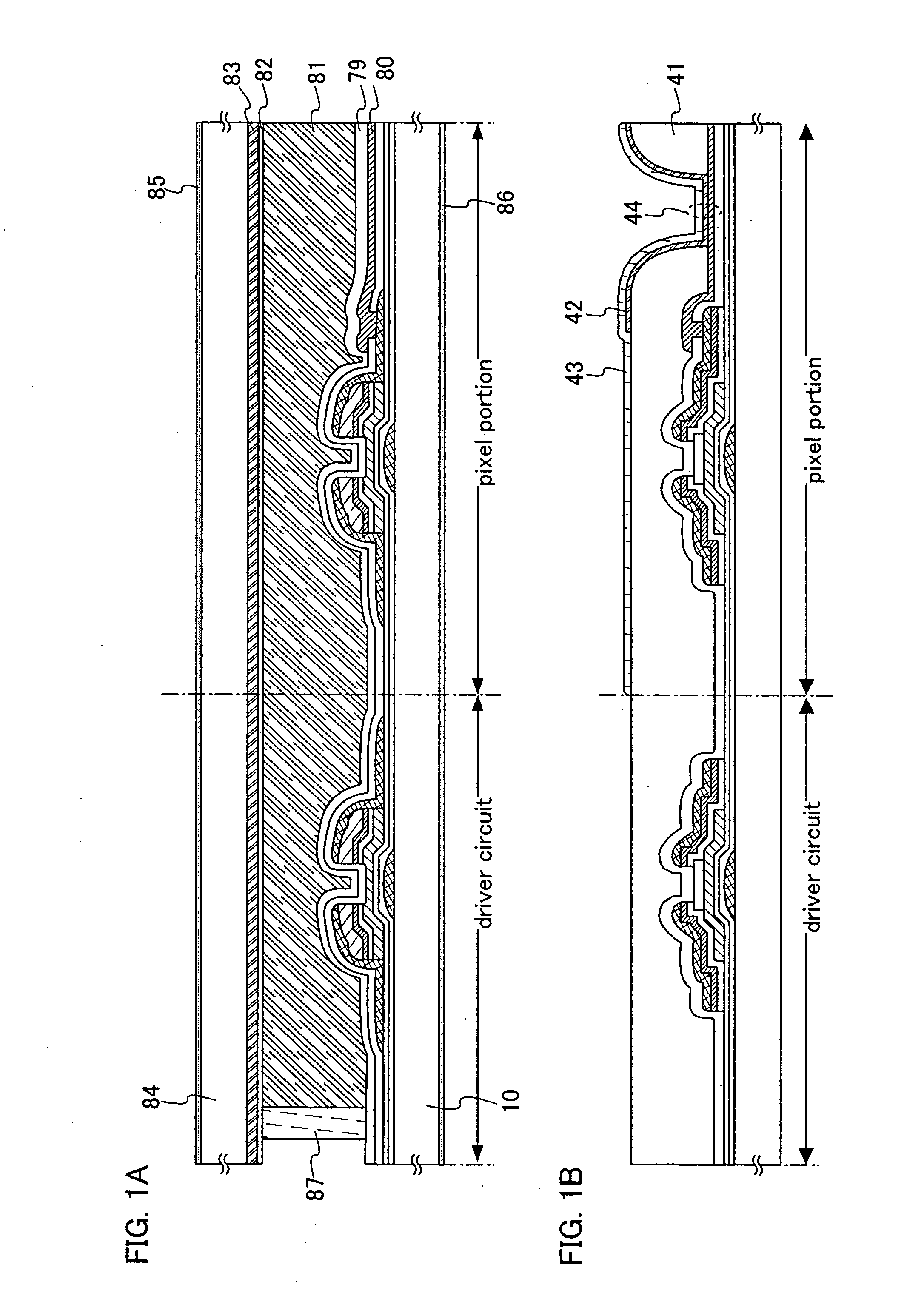

Display device, method for manufacturing thereof, and television device

InactiveUS20050163938A1Reduce in quantitySimplify manufacturing stepsStatic indicating devicesRadiation applicationsDisplay deviceConductive materials

The invention provides a display device and a method for manufacturing thereof by increasing a material efficiently as well as simplifying steps. Also, the invention provides a technique for forming a pattern such as a wiring, that is used for forming a display device, to have a predetermined shape with an excellent controllability. The method for manufacturing a display device includes the steps of: forming a lyophobic region; selectively irradiating laser beam in the lyophobic region to form a lyophilic region; selectively discharging a composition, that contains a conductive material, in the lyophilic region to form a gate electrode layer; forming a gate insulating layer and a semiconductor layer over the gate electrode layer; discharging a composition containing a conductive material over the semiconductor layer to form a source electrode layer and a drain electrode layer; and forming a pixel electrode layer on the source or drain electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

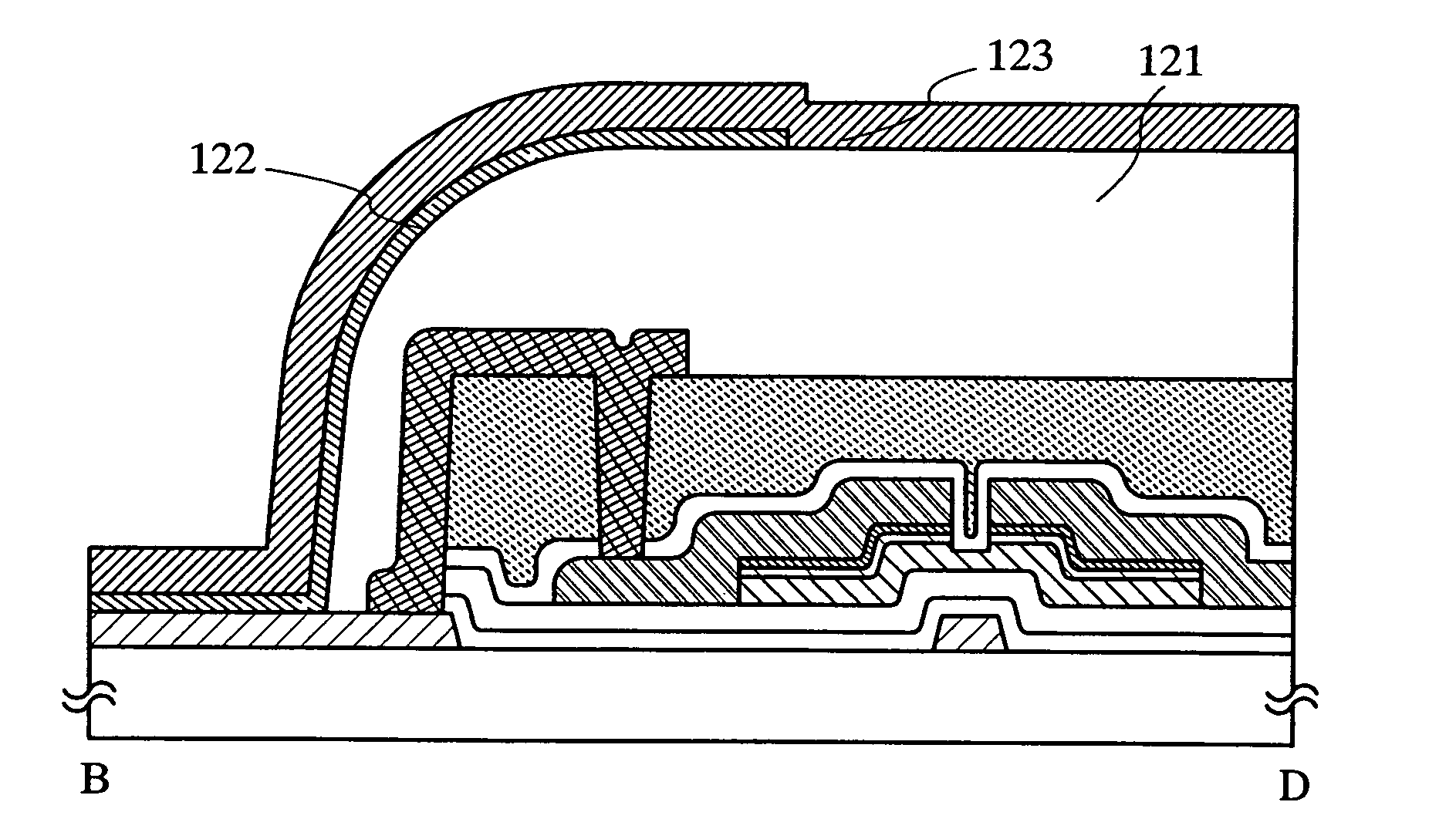

Display device, manufacturing method thereof, and television set

InactiveUS7564058B2Improve switching characteristicsImprove image contrastSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A manufacturing method of a display device having TFTs capable of high-speed operation with few variations of threshold voltage is provided, in which materials are used with high efficiency and a small number of photomasks is required. The display device of the invention comprises a gate electrode layer and a pixel electrode layer formed over an insulating surface, a gate insulating layer formed over the gate electrode layer, a crystalline semiconductor layer formed over the gate insulating layer, a semiconductor layer having one conductivity type formed in contact with the crystalline semiconductor layer, a source electrode layer and a drain electrode layer formed in contact with the semiconductor layer having one conductivity type, an insulating later formed over the source electrode layer, the drain electrode layer, and the pixel electrode layer, a first opening formed in the insulating layer to reach the source electrode layer or the drain electrode layer, a second opening formed in the gate insulating layer and the insulating layer to reach the pixel electrode layer, and a wiring layer formed in the first opening and the second opening to electrically connect the source electrode layer or the drain electrode layer to the pixel electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

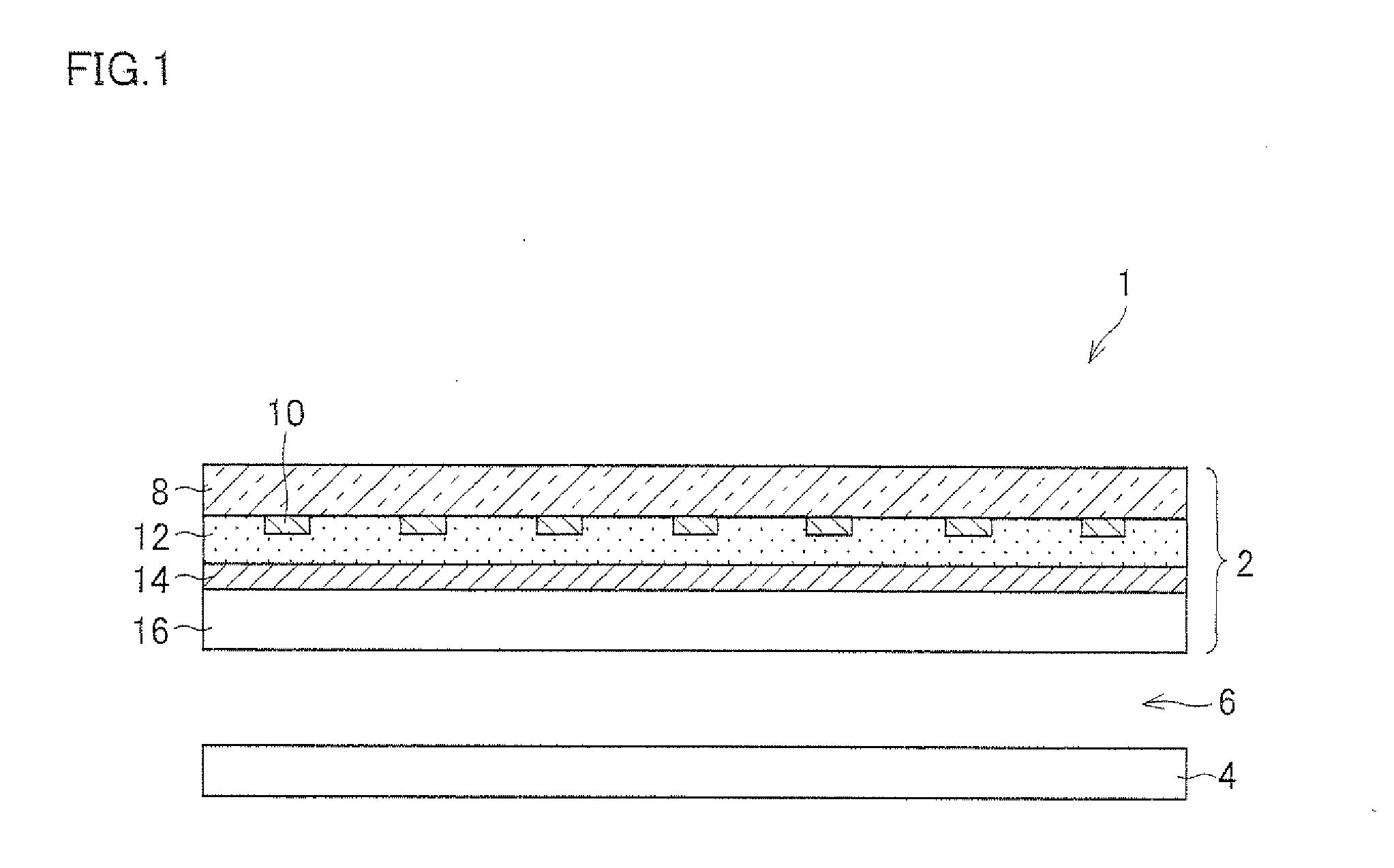

Display panel substrate, display panel, display appratus, and method for manufacturing display panel substrate

InactiveUS20100013785A1Increase the aperture ratioSimplify manufacturing stepsNon-linear opticsInput/output processes for data processingEngineeringTouch panel

A display panel substrate according to the present invention includes at least an insulating substrate, first conductive wires formed on the insulating substrate, a piezoelectric material film formed on the first conductive wires, second conductive wires intersecting with the first conductive wires, and a protecting film for protecting the first conductive wires, the second conductive wires, and the piezoelectric material film. The insulating film is formed at least in an area in an effective display area on the insulating substrate. The piezoelectric film is formed at least at an intersection of a first conductive wire and a second conductive wire. This makes it possible to provide a display panel substrate that allows integration of a touch panel function into a display panel without causing an increase in size of the display panel.

Owner:SHARP KK

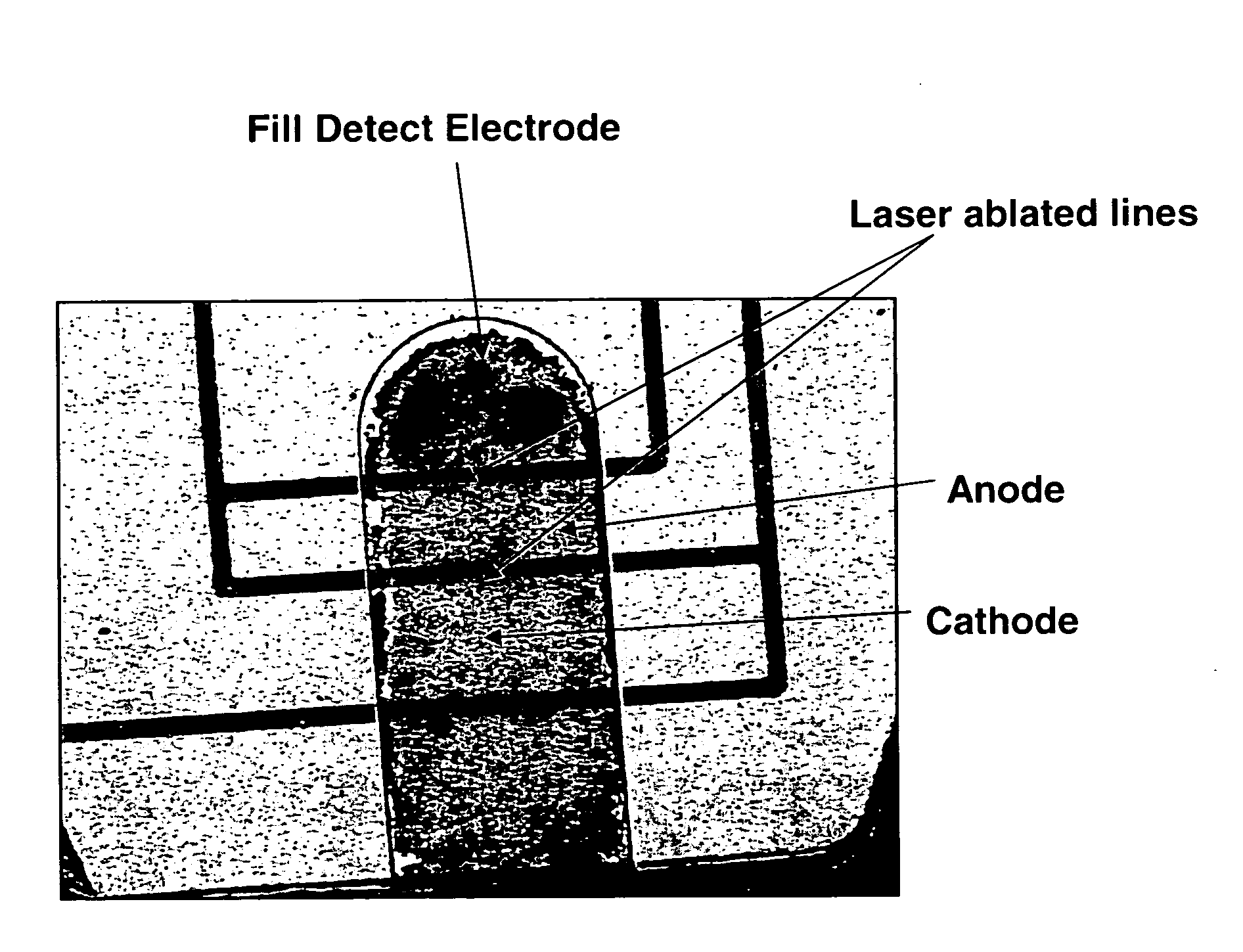

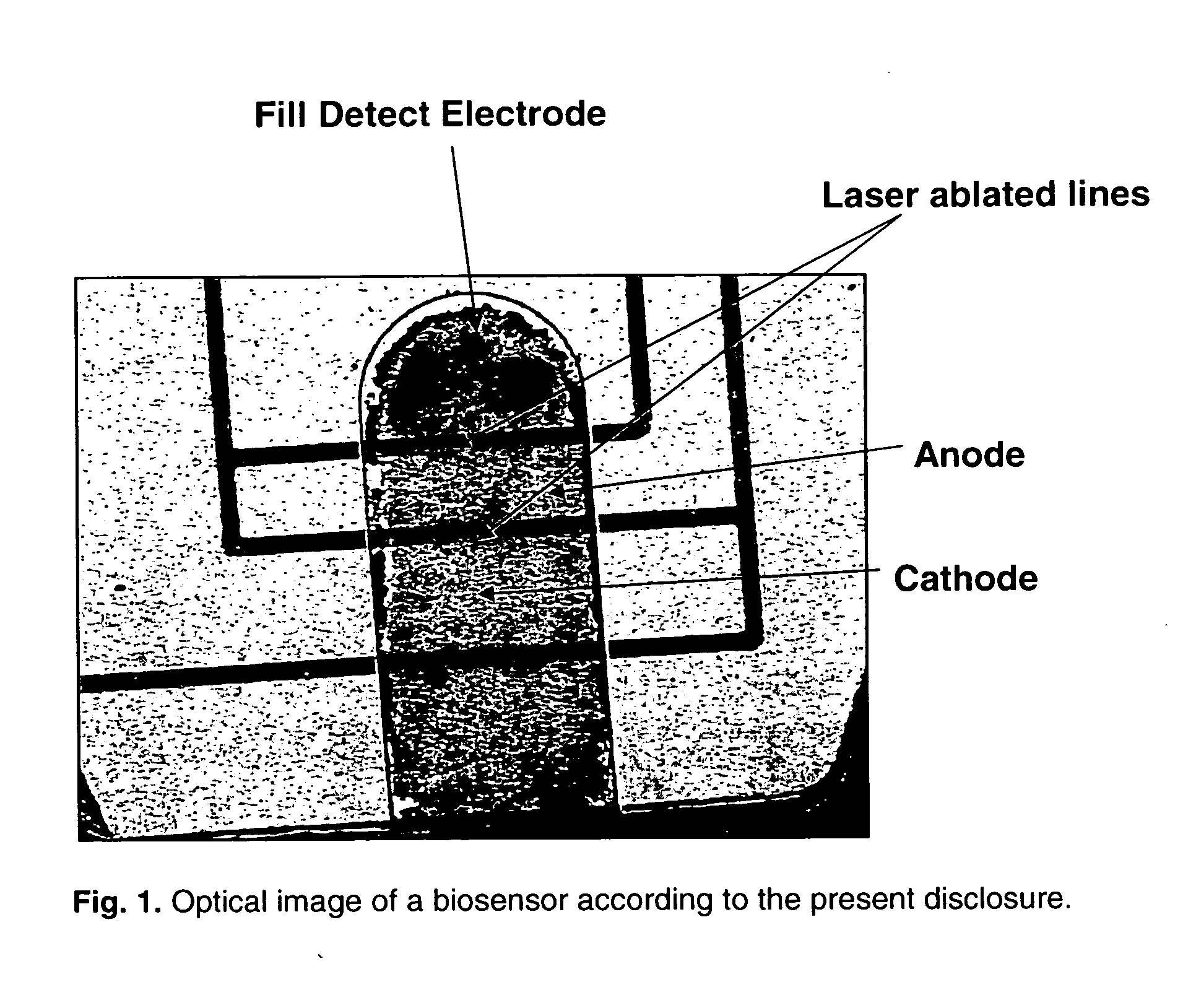

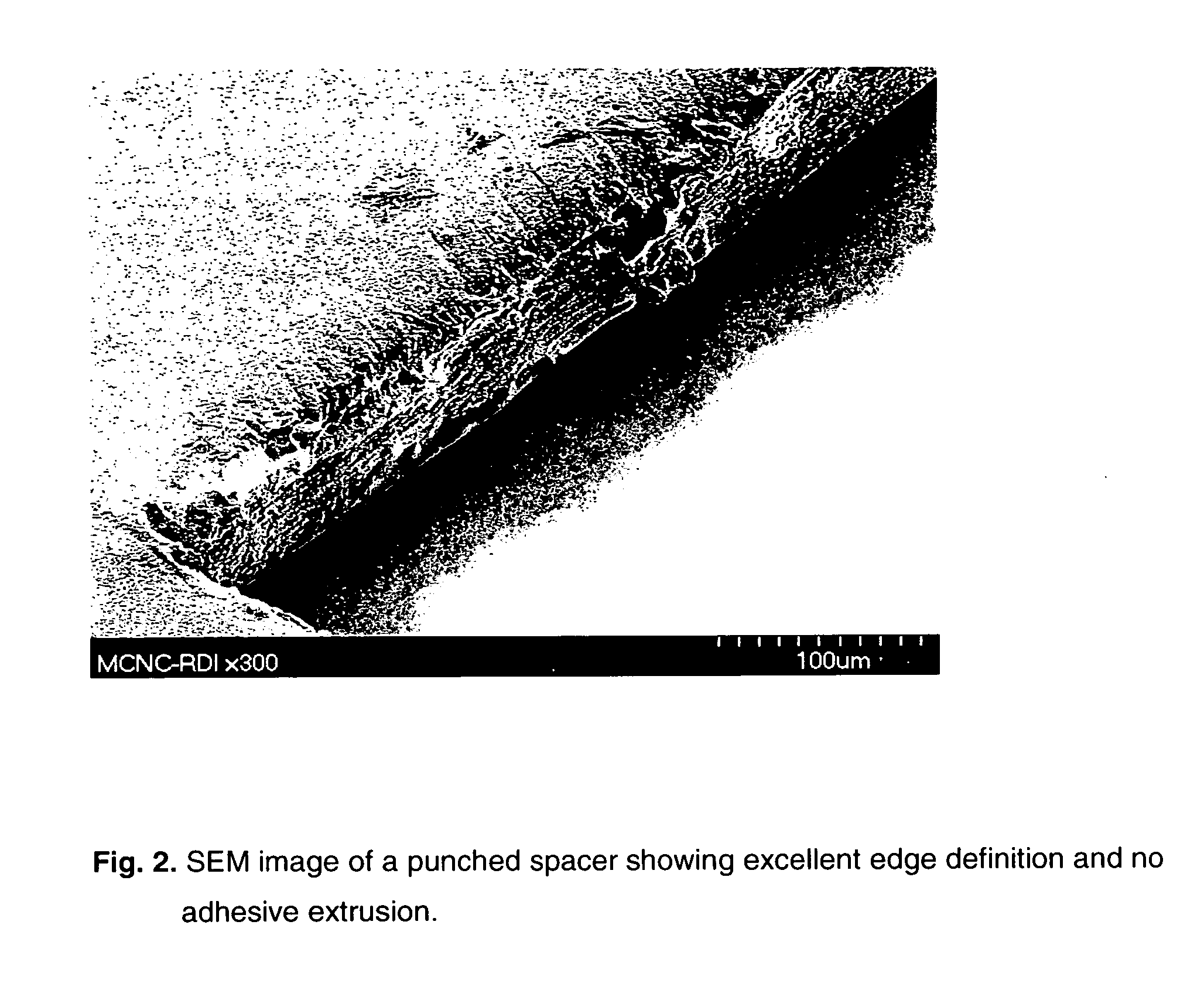

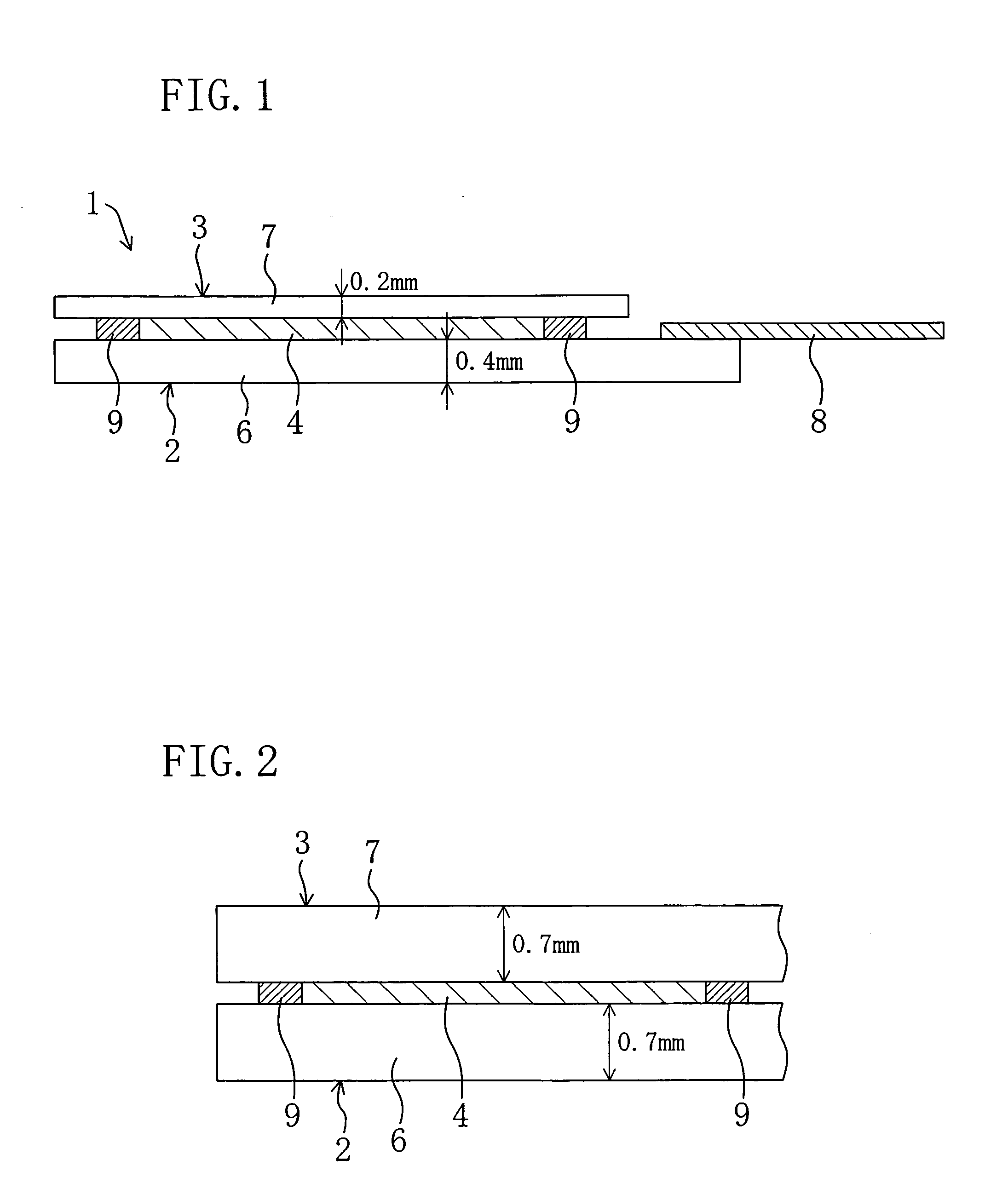

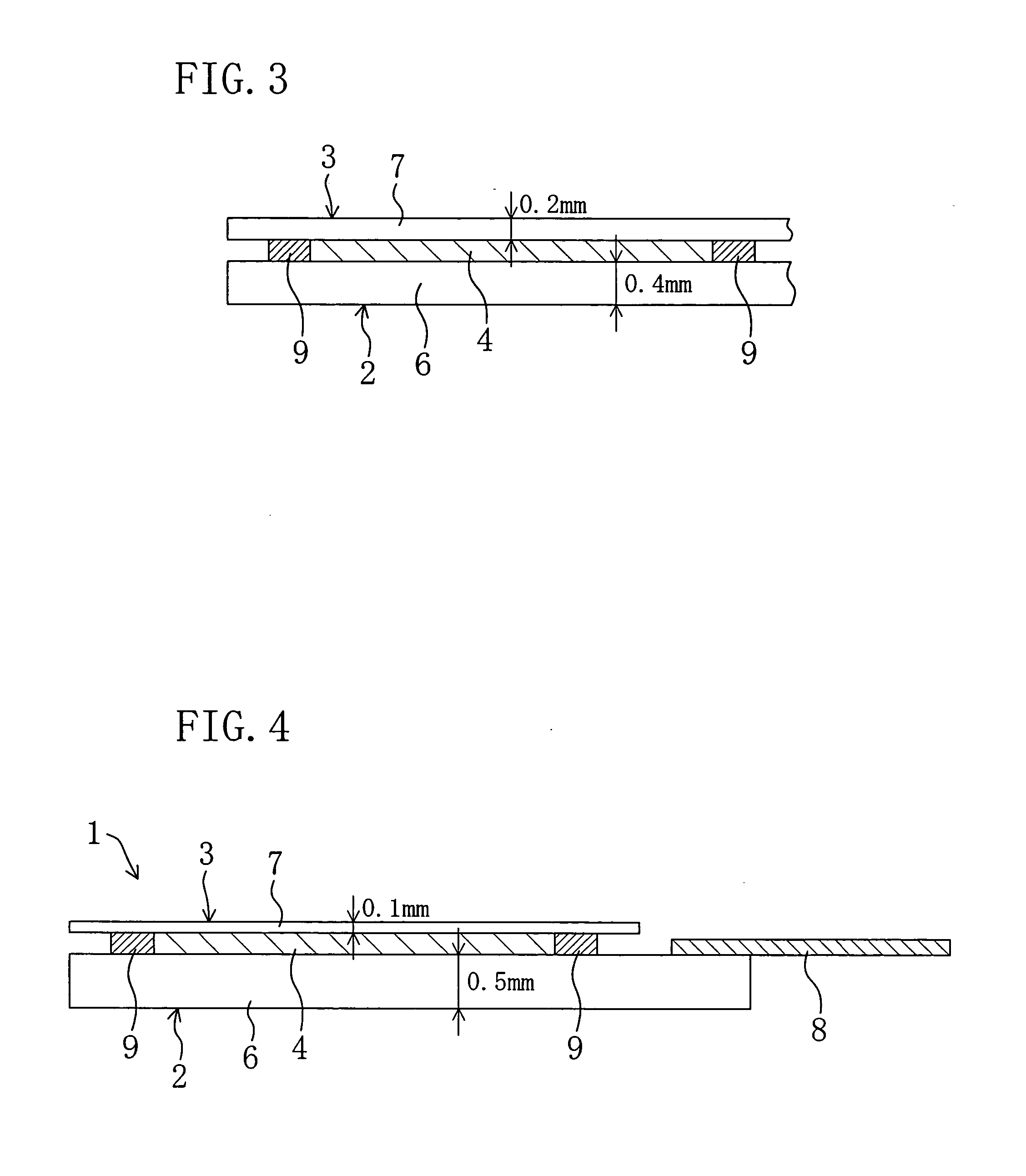

Biosensors comprising heat sealable spacer materials

InactiveUS20070240984A1Improve edge qualityLess-painful lancingImmobilised enzymesBioreactor/fermenter combinationsAnalyteOrganic layer

Disclosed herein is a biosensor for measuring analyte in a fluid that comprises a substrate layer having disposed thereon at least one each of an electrode, cathode, anode, and a novel spacer material. The spacer material according to the present disclosure comprises a heat sealable organic layer that covers at least a portion of the anode and defines at least one edge of the anode, wherein the spacer material has at least one hole punched through it and defines a cavity or well for accepting chemistry. Also disclosed is a method of making such biosensors.

Owner:NIPRO DIAGNOSTICS INC

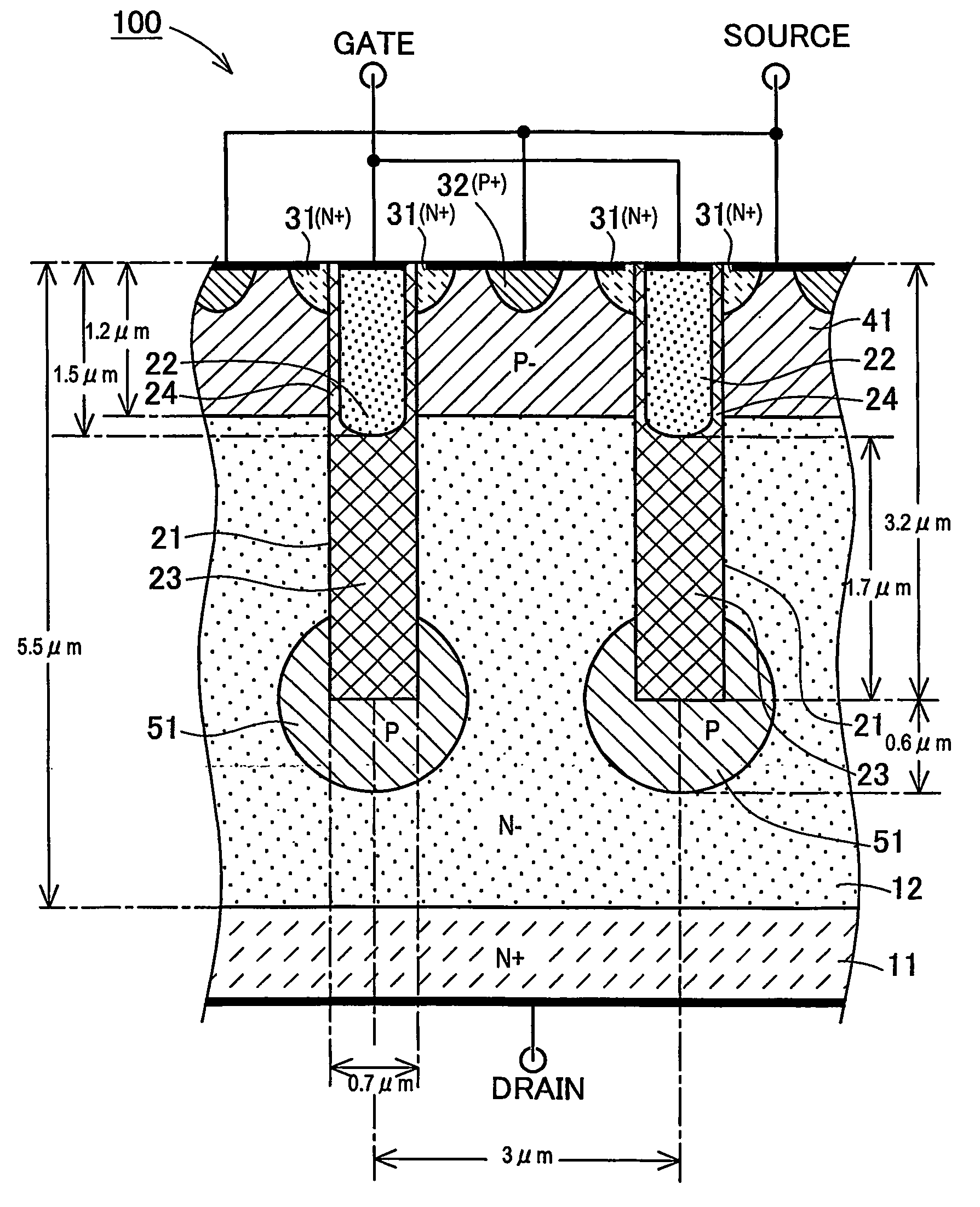

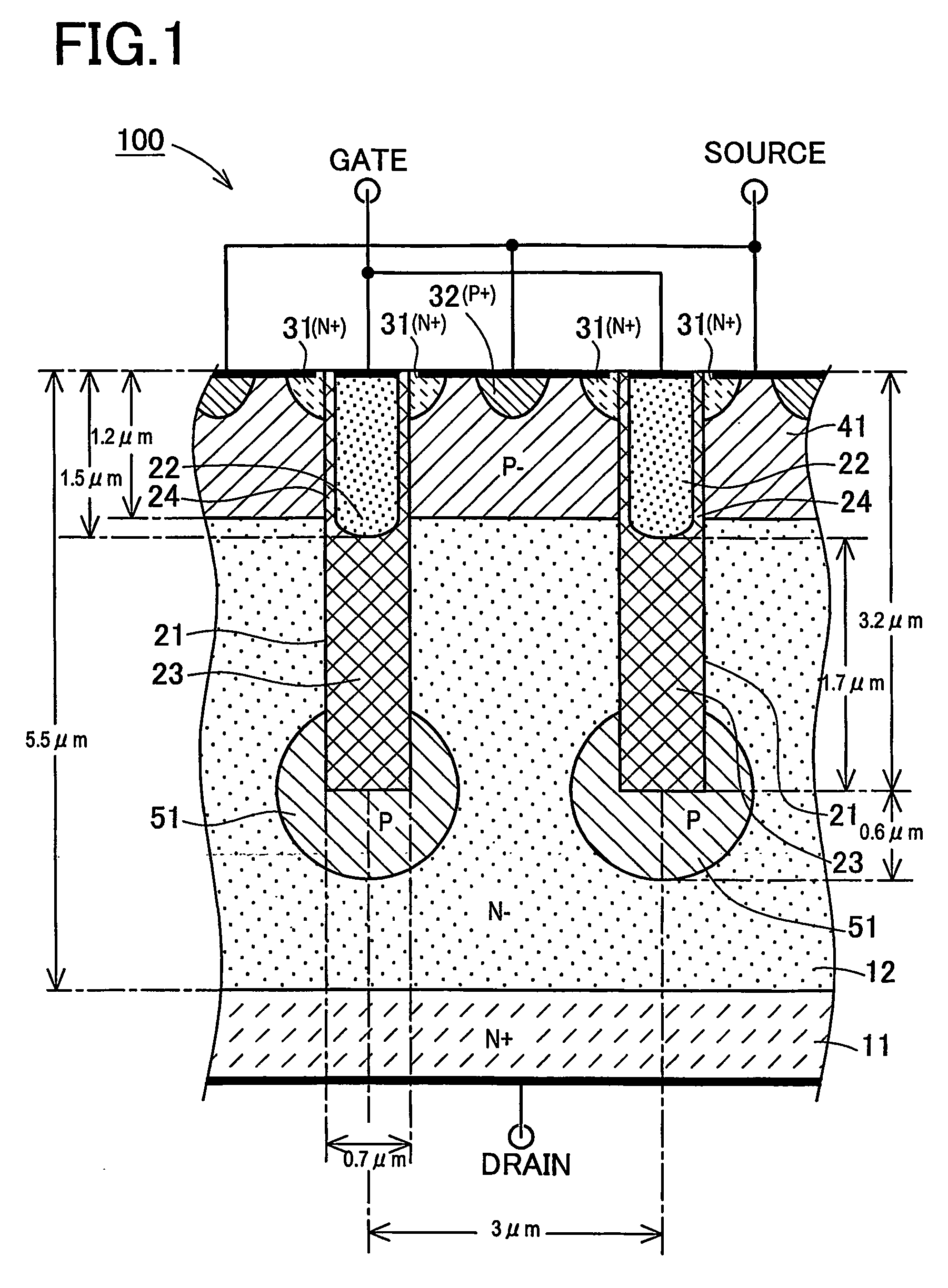

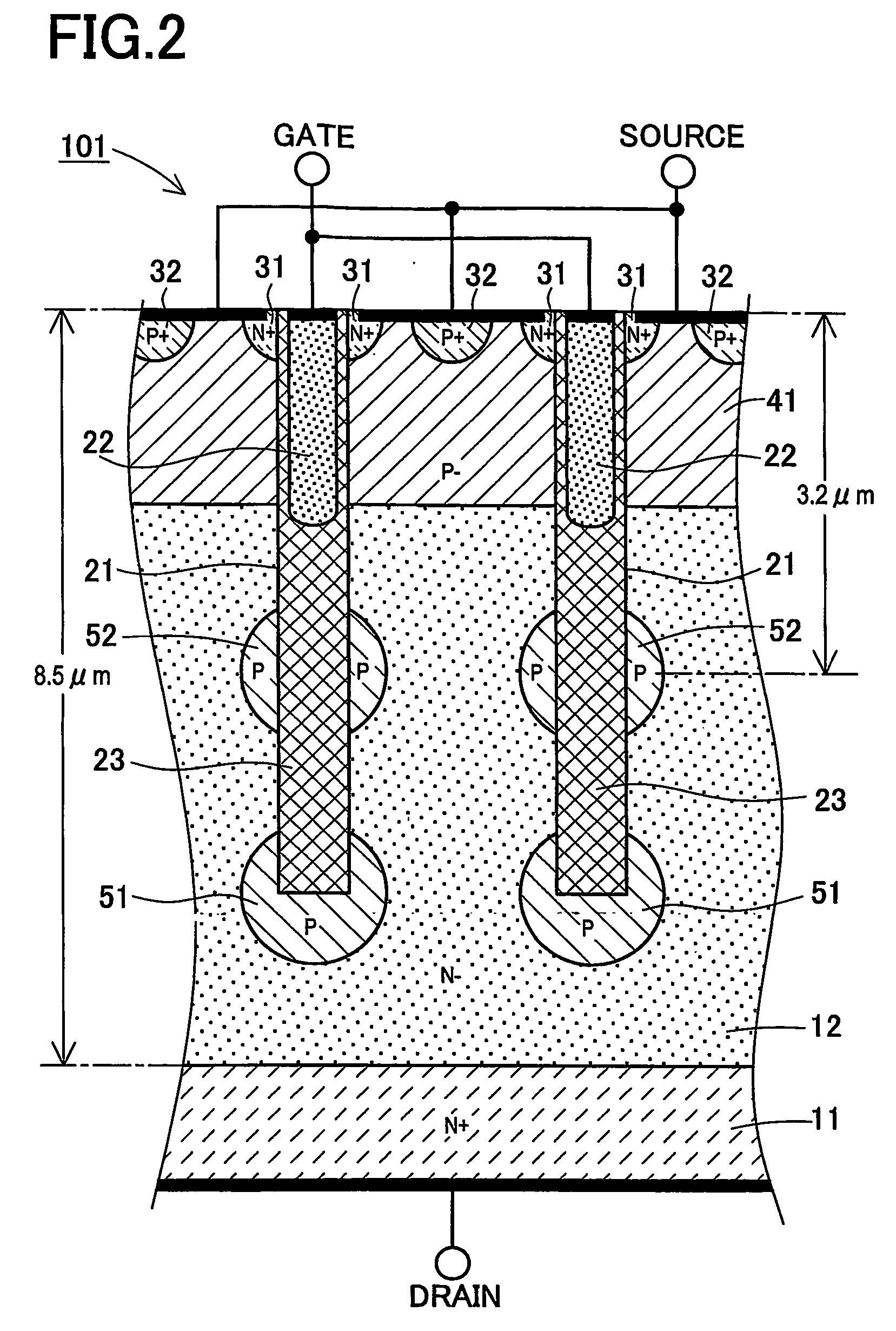

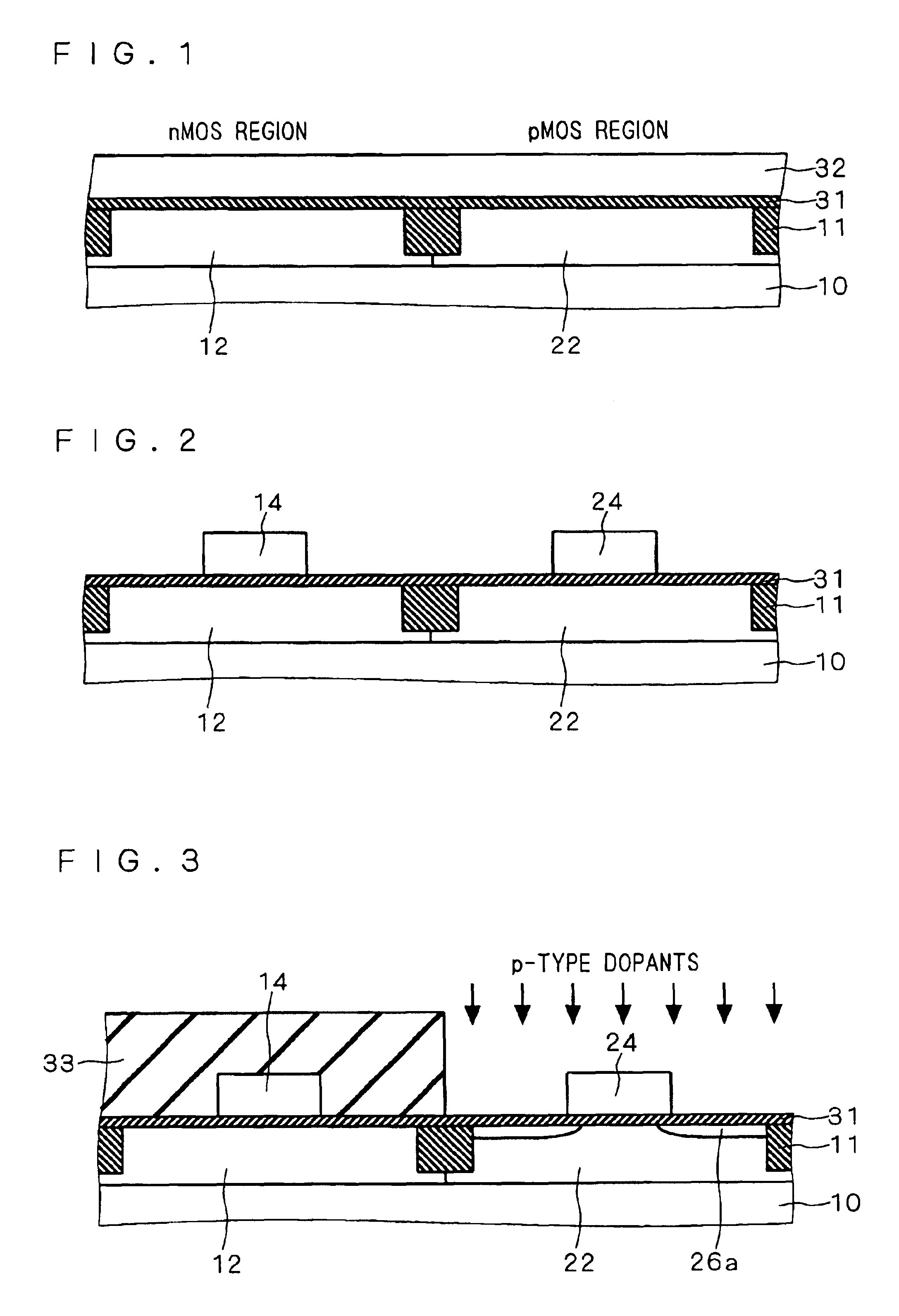

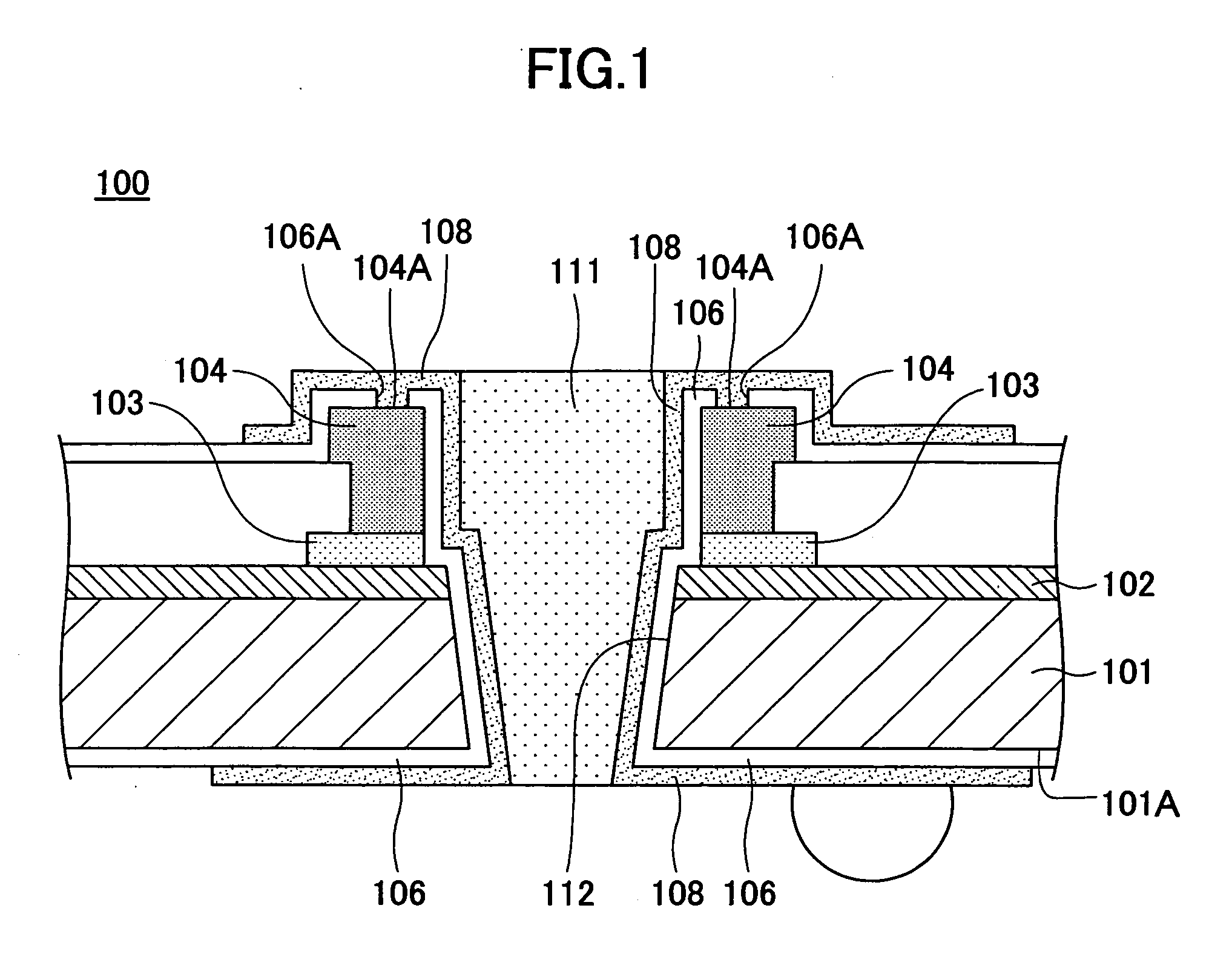

Insulated gate type semiconductor device and manufacturing method thereof

ActiveUS20060289928A1Improve design flexibilityLow reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBody region

The invention is intended to present an insulated gate type semiconductor device that can be manufactured easily and its manufacturing method while realizing both higher withstand voltage design and lower on-resistance design. The semiconductor device comprises N+ source region 31, N+ drain region 11, P− body region 41, and N− drift region 12. By excavating part of the upper side of the semiconductor device, a gate trench 21 is formed. The gate trench 21 floating region 51 is provided beneath the gate trench 21. A further trench 35 differing in depth from the gate trench 21 may be formed, a P floating region 54 being provided beneath the trench 25.

Owner:TOYOTA JIDOSHA KK +1

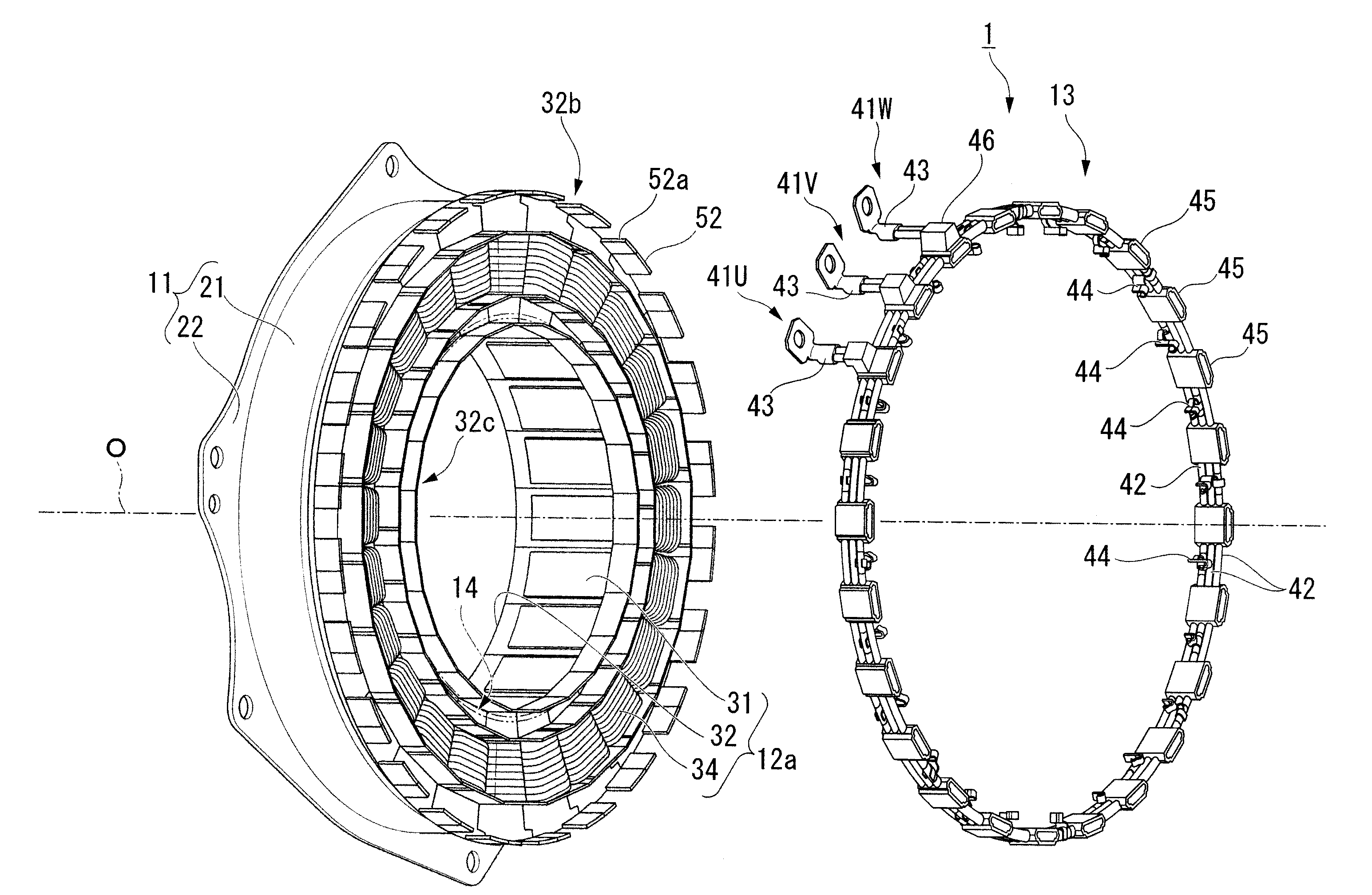

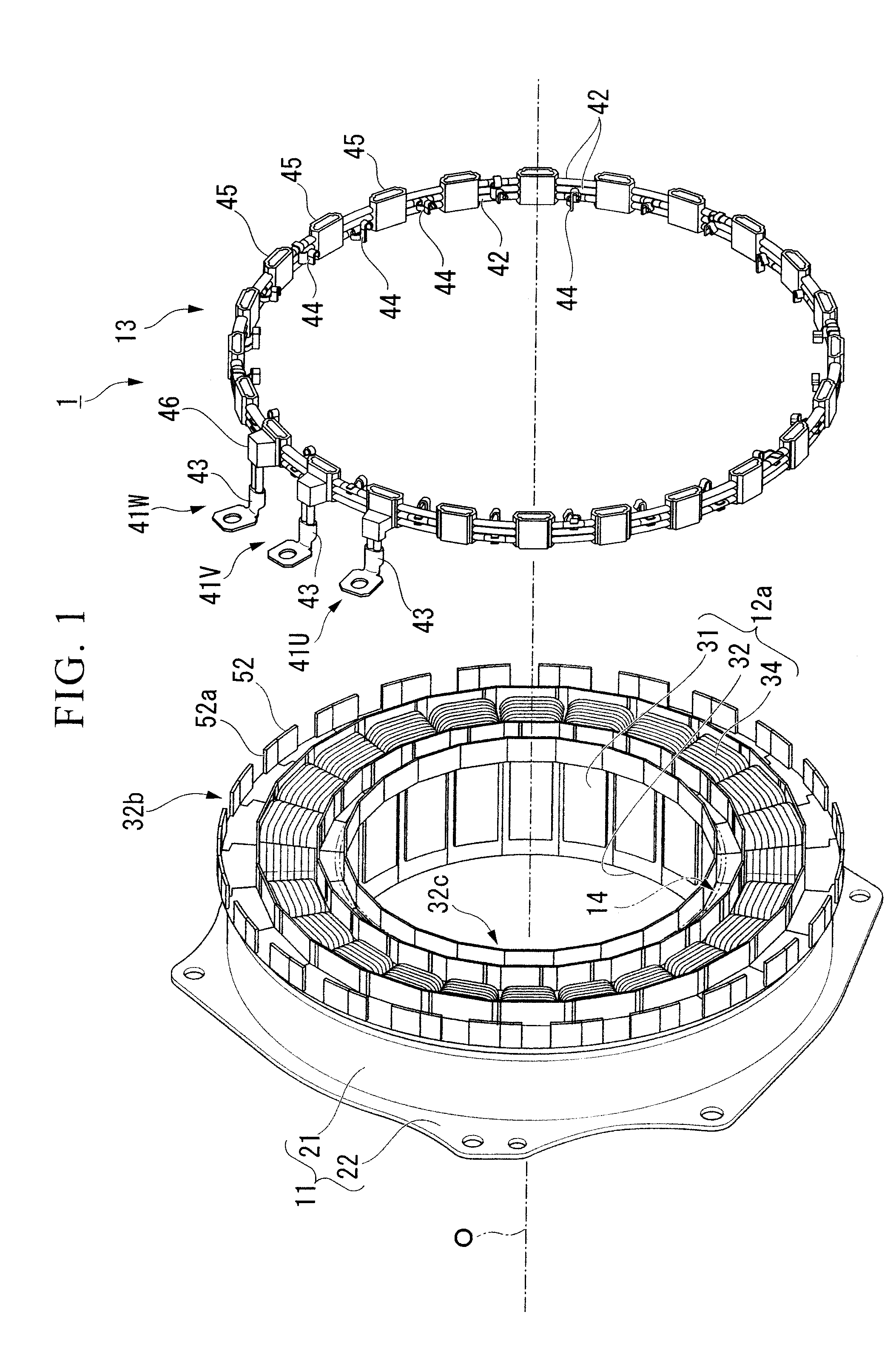

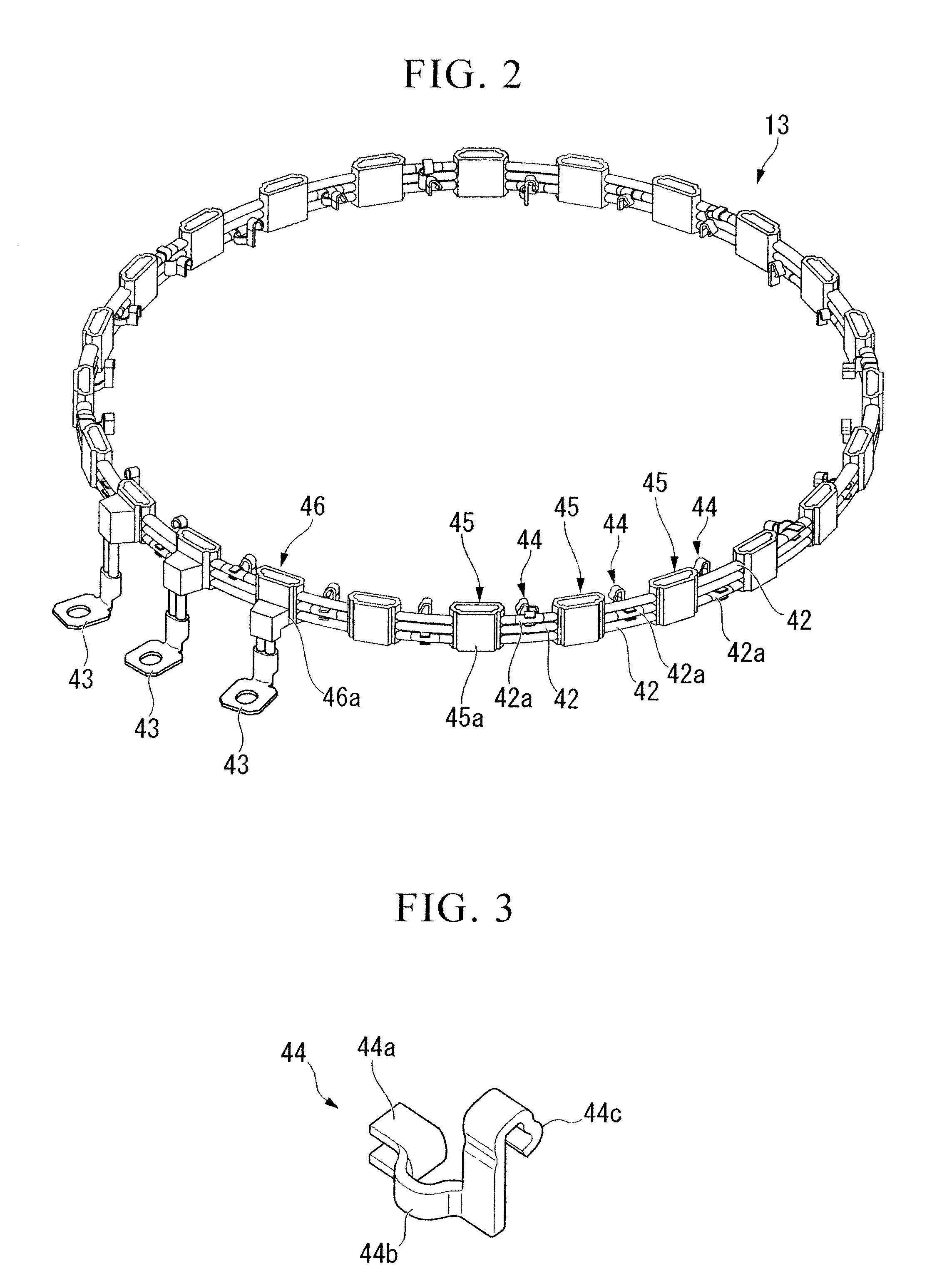

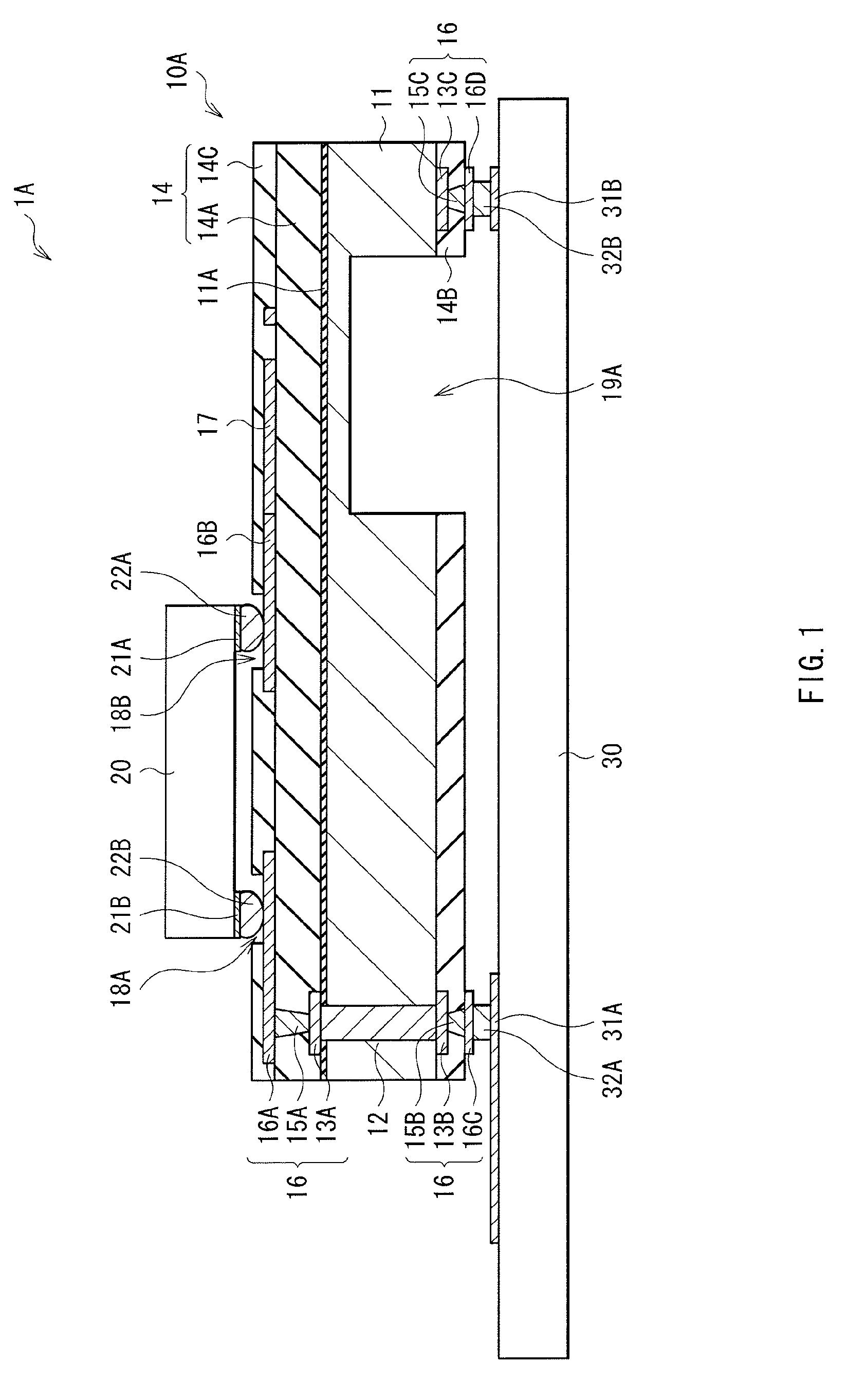

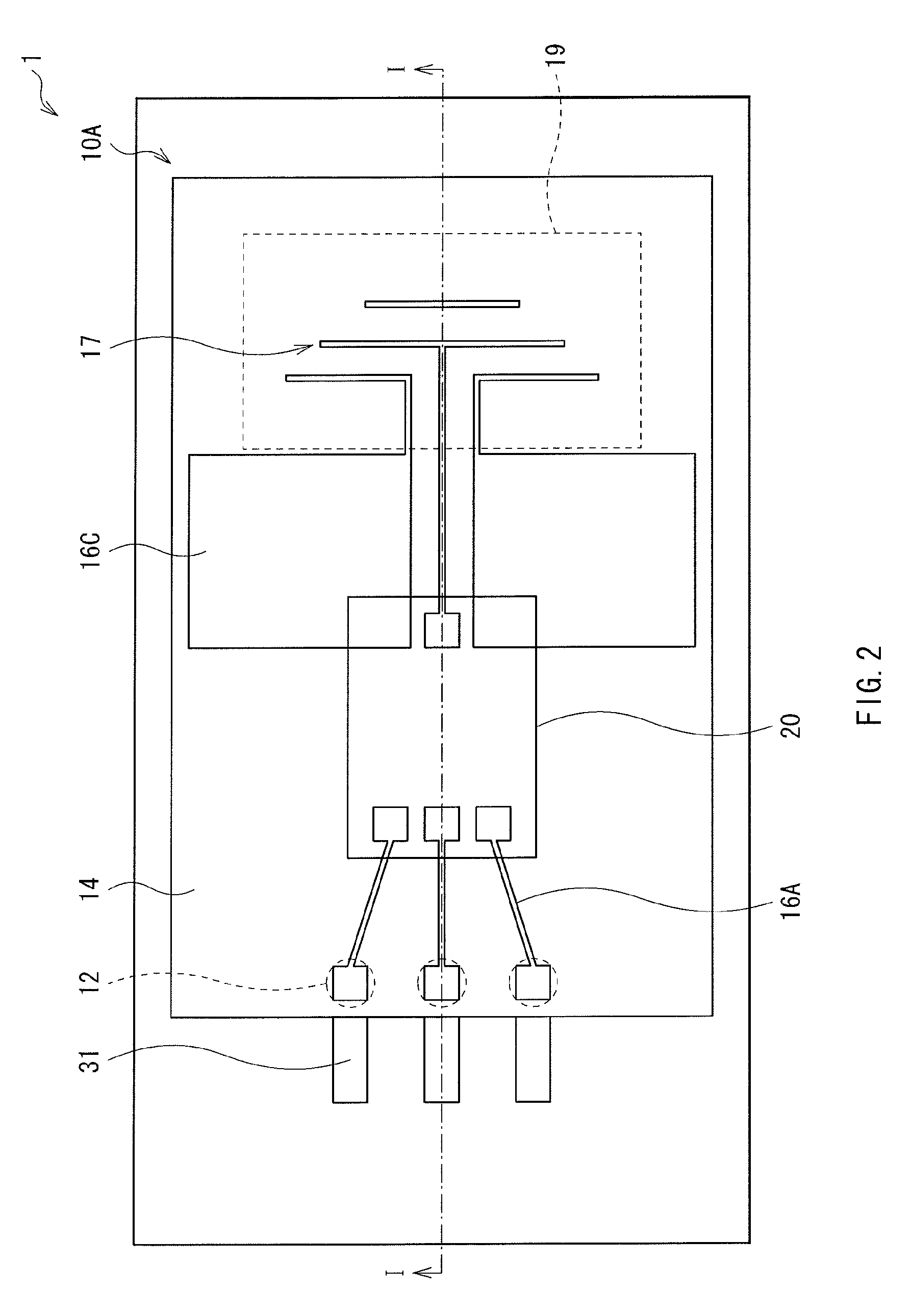

Electric power collection/distribution ring of rotary electric machine

An electric power collection / distribution ring of a rotary electric machine including: a plurality of ring shaped bus rings each of which is to be connected to one of a plurality of coils provided in the rotary electric machine, the coils each corresponding to phases of the rotary electric machine; a plurality of fixing member which are fixed to the bus rings and arranged along the circumferential direction thereof; and a plurality of connection terminals which are fixed to the bus rings and arranged along said circumferential direction, and which can be connected with one of leader line sections of the coils.

Owner:HONDA MOTOR CO LTD

Display device and method for manufacturing the same

InactiveUS20060238695A1Reduce thicknessThin display deviceNon-linear opticsLiquid-crystal displayMedia layer

A liquid crystal display device includes: an active matrix substrate including a glass substrate; a counter substrate which is arranged to face the active matrix substrate and includes a glass substrate which is thinner than the glass substrate of the active matrix substrate; and a display medium layer which is provided between the active matrix substrate and the counter substrate. The rate at which the glass substrate of the active matrix substrate is etched by an etching solution is lower than the rate at which the glass substrate of the counter substrate is etched by the etching solution.

Owner:SHARP KK

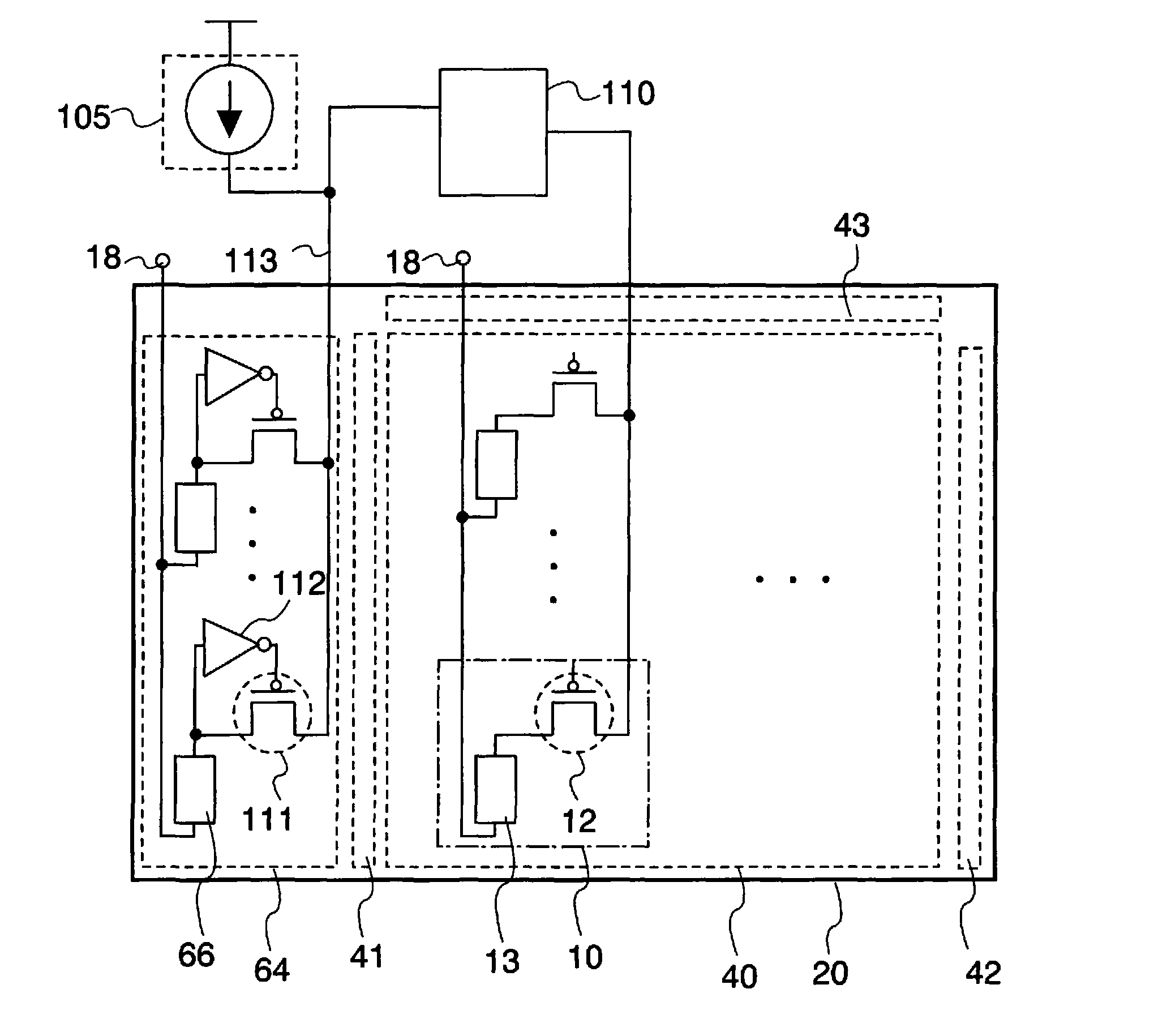

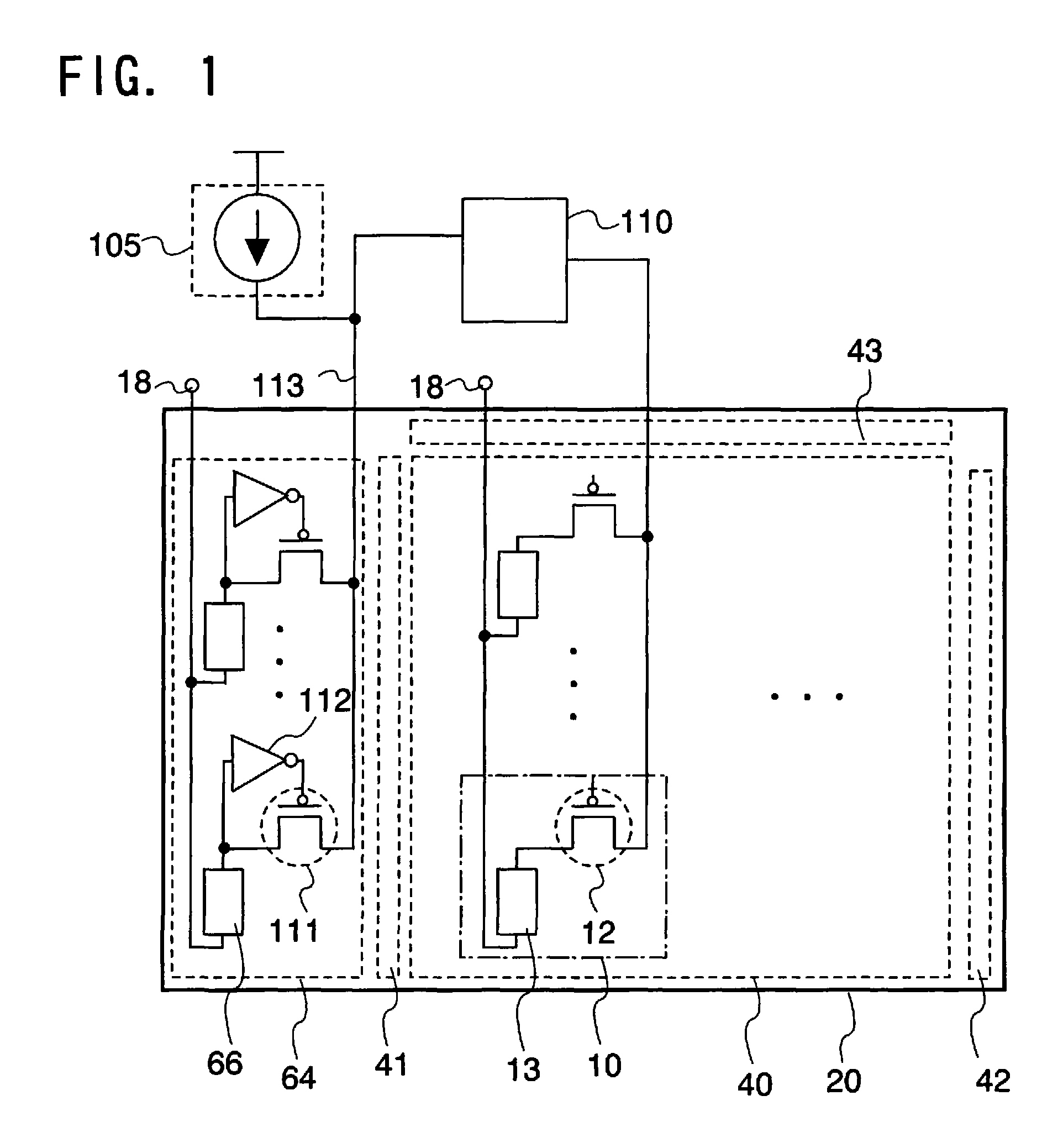

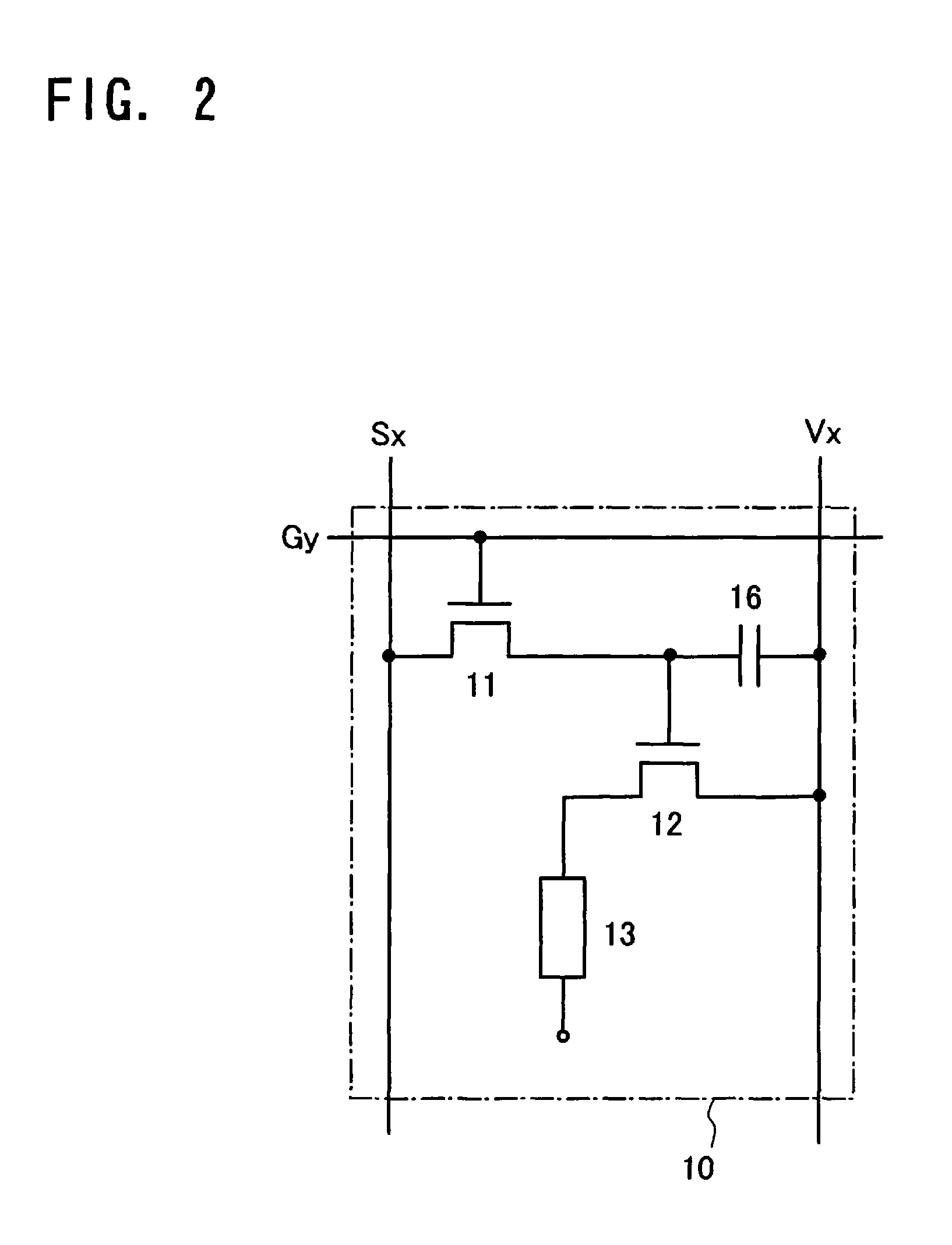

Light emitting device and electronic apparatus

InactiveUS20060244699A1Widen perspectiveEasy to useElectrical apparatusElectroluminescent light sourcesLight emitting deviceElectron

To solve degradation with time of a light emitting element by a new method. When the potential of an electrode of a monitor pixel is sampled and fed back to a light emitting pixel, degradation with time of a light emitting element can be corrected. In addition, when a writing period is divided into a plurality of periods during which a plurality of rows are selected, a gray scale can be expressed by a weighted light emitting period. That is to say, a light emitting device of the invention has a plurality of monitoring light emitting elements, a monitor line for monitoring changes in the potentials of electrodes of the plurality of light emitting elements, and a means for preventing, when any one of the plurality of monitoring light emitting elements is short-circuited, a current from flowing to the short-circuited monitoring light emitting element through the monitor line.

Owner:SEMICON ENERGY LAB CO LTD

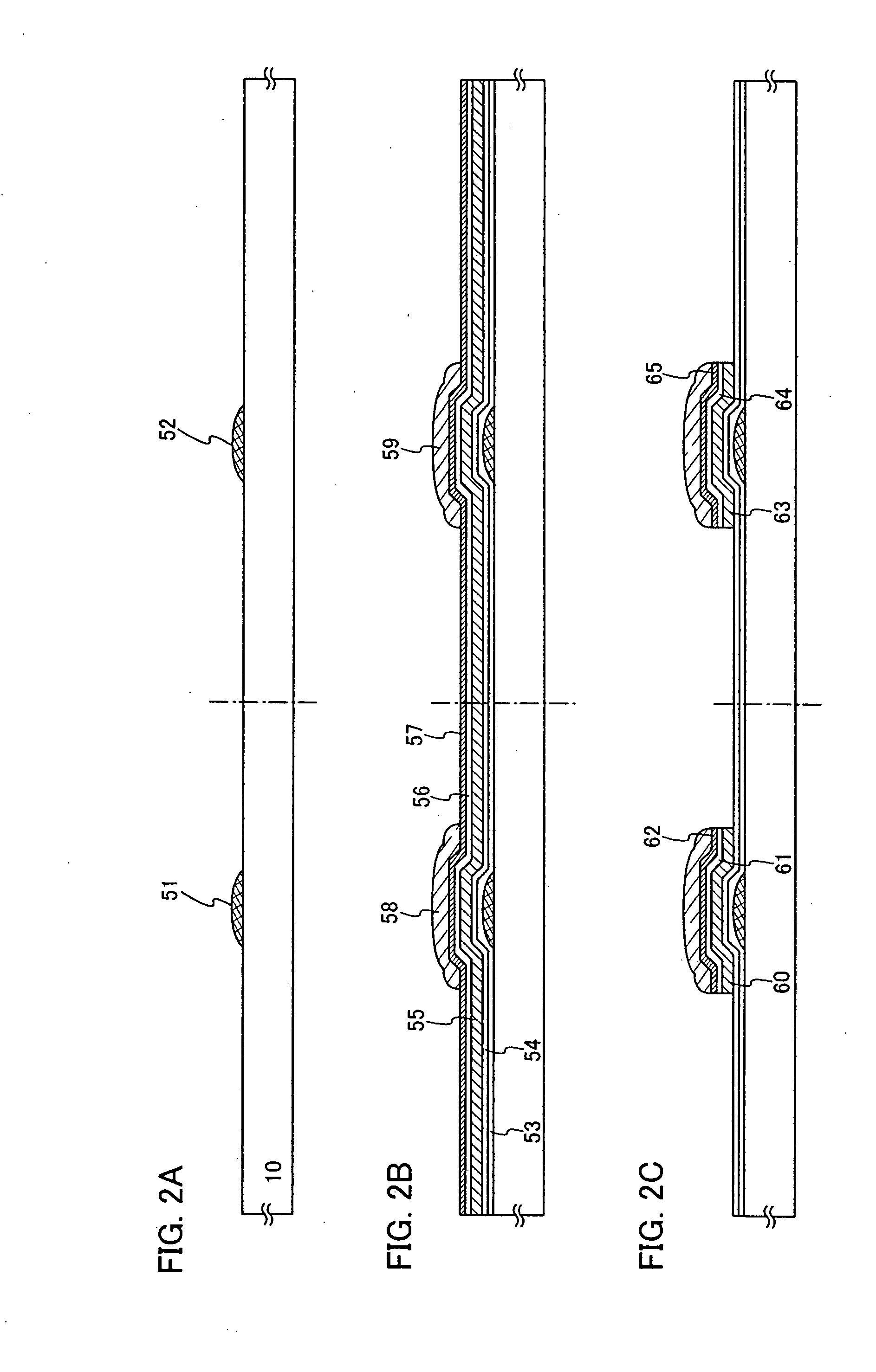

Method for manufacturing semiconductor device

An object of the present invention is to provide a method for manufacturing a semiconductor device of which manufacturing process is simplified by improving usage rate of a material. A method for manufacturing a semiconductor device of the invention comprises the steps of: forming gate electrodes with a droplet discharge method on a substrate having an insulating surface; laminating gate insulating layers, semiconductor layers, and a semiconductor layer containing one-conductivity type impurity over the gate electrodes; forming first conductive layers serving as masks with a droplet discharge method in a position overlapping the gate electrodes, etching the semiconductor layer and the semiconductor layer containing one-conductivity type impurity with the first conductive layers, forming a second conductive layer serving as a source wiring or a drain wiring with a droplet discharge method over the first conductive layers; and etching the first conductive layers and the semiconductor layer containing one-conductivity type impurity, using the second conductive layers as masks.

Owner:SEMICON ENERGY LAB CO LTD

Multicolor oled displays

ActiveUS20060238120A1Efficient preparationSimplify manufacturing stepsDischarge tube luminescnet screensElectroluminescent light sourcesDisplay deviceOptoelectronics

It is an object of the present invention to avoid the above-mentioned problems and provide a multicolor OLED display with improved power efficiency that reduces the need for precisely patterning one or more of the OLED layers. This object is achieved by an OLED display having at least red, green, and blue colored pixels, including a magenta light emitting layer provided over a substrate for red and blue pixels and a green light emitting layer provided over the substrate for producing at least a green pixel. It is also achieved by first and second color filters in operative relationship with the magenta light-emitting layer to respectively produce red and blue pixels.

Owner:GLOBAL OLED TECH

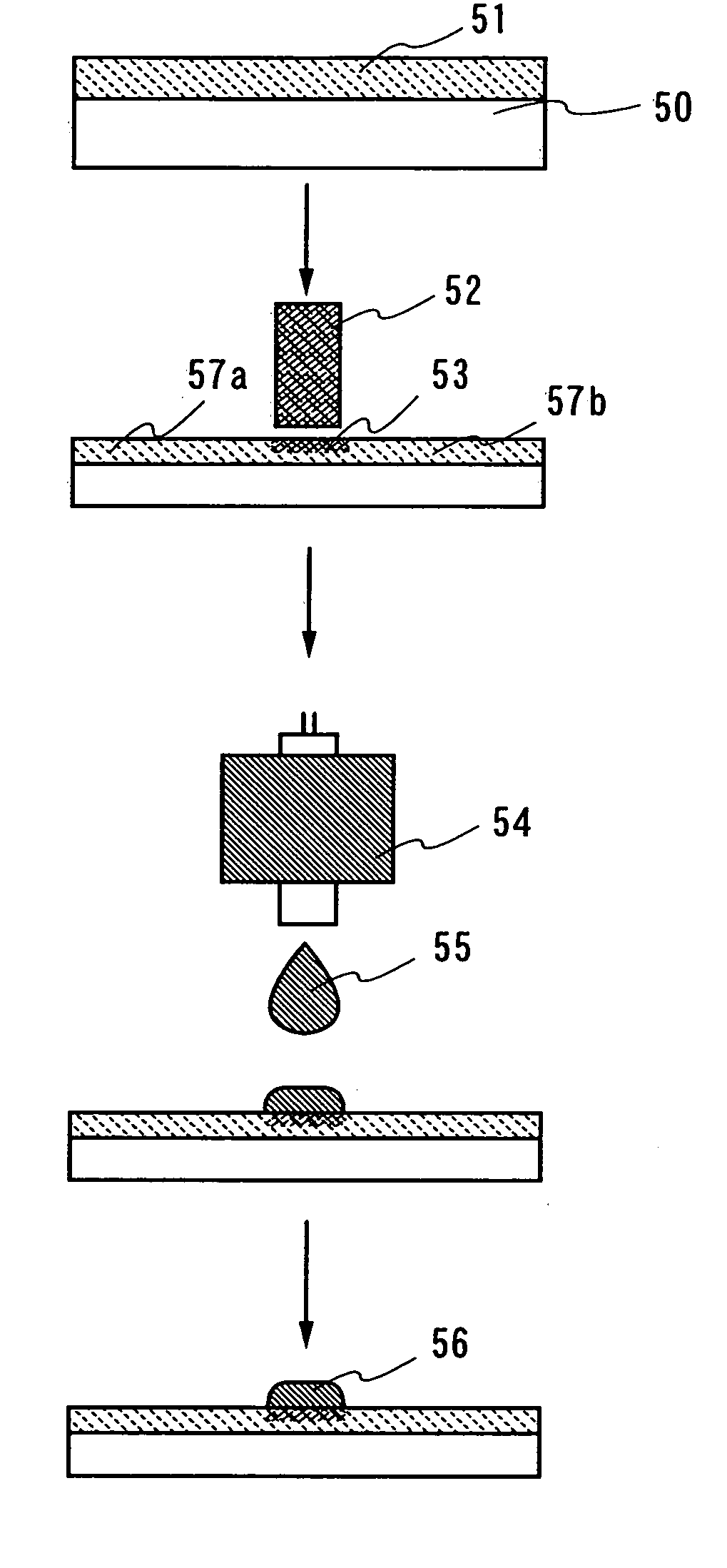

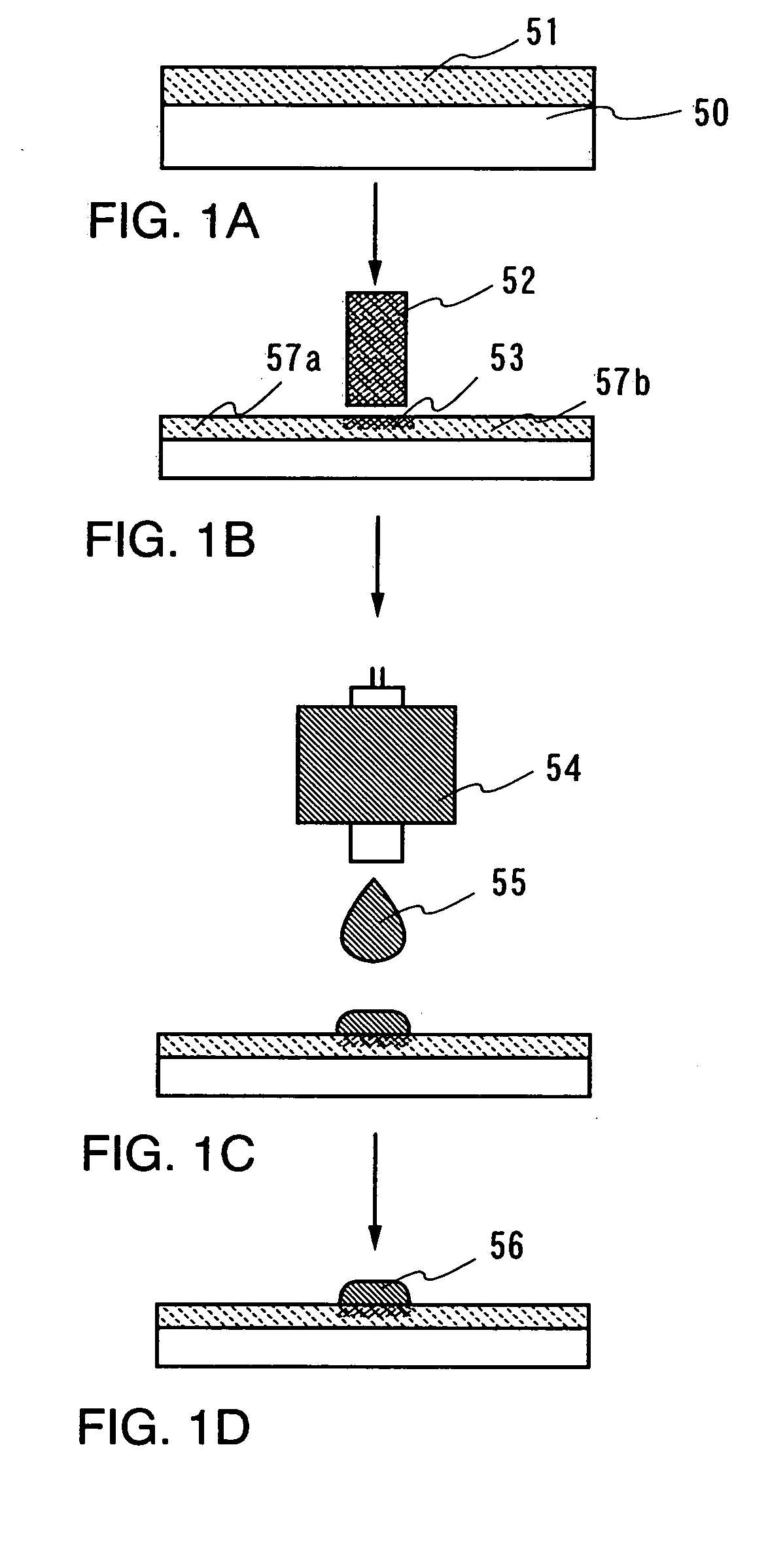

Method of manufacturing liquid crystal display element

InactiveUS6392736B1Simplify manufacturing stepsShort manufacturing timeStatic indicating devicesNon-linear opticsLiquid-crystal displayEngineering

Method of manufacturing liquid crystal display element includes disposing adhesive on at least one of first and second substrates; disposing spacer particles on at least one substrate; supplying liquid crystal material onto at least one substrate; and fixing the substrates together with adhesive spacer particles and liquid crystal material therebetween. The substrates are fixed together by applying pressure and / or heat to the substrates from an end portion toward the other end portion thereof. An impulse applied to each spacer particle can be between 0.001 gf.sec and 0.1 gf.sec in substrate fixing step. Parameter X relating to heating in fixing step can satisfy 200<=X<=3000, where X=(T-20) / (V.D), T is temperature (°C), V is fixing speed (mm / sec) of substrates, and D is diameter of spacer particles (mm). The spacer particles can occupy an area ratio of 0.003 or more to unit area of the substrate.

Owner:MINOLTA CO LTD

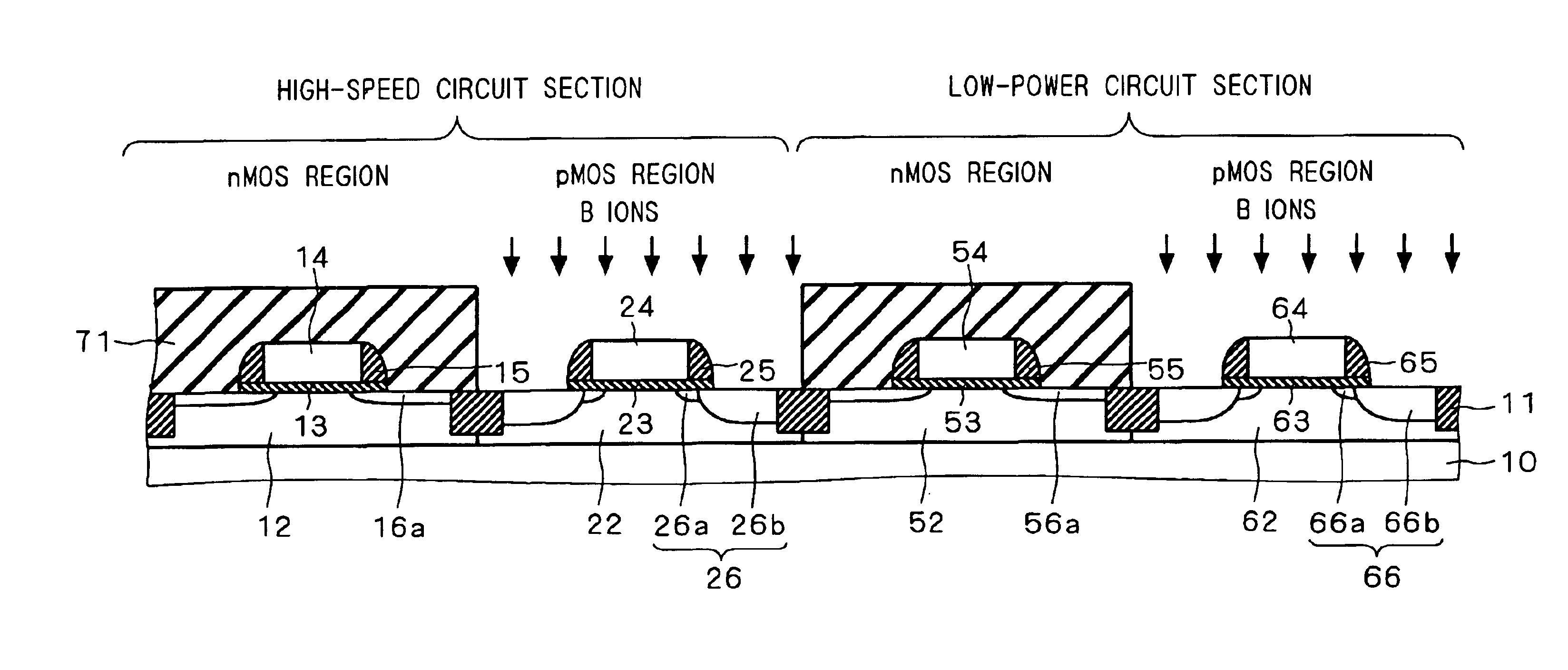

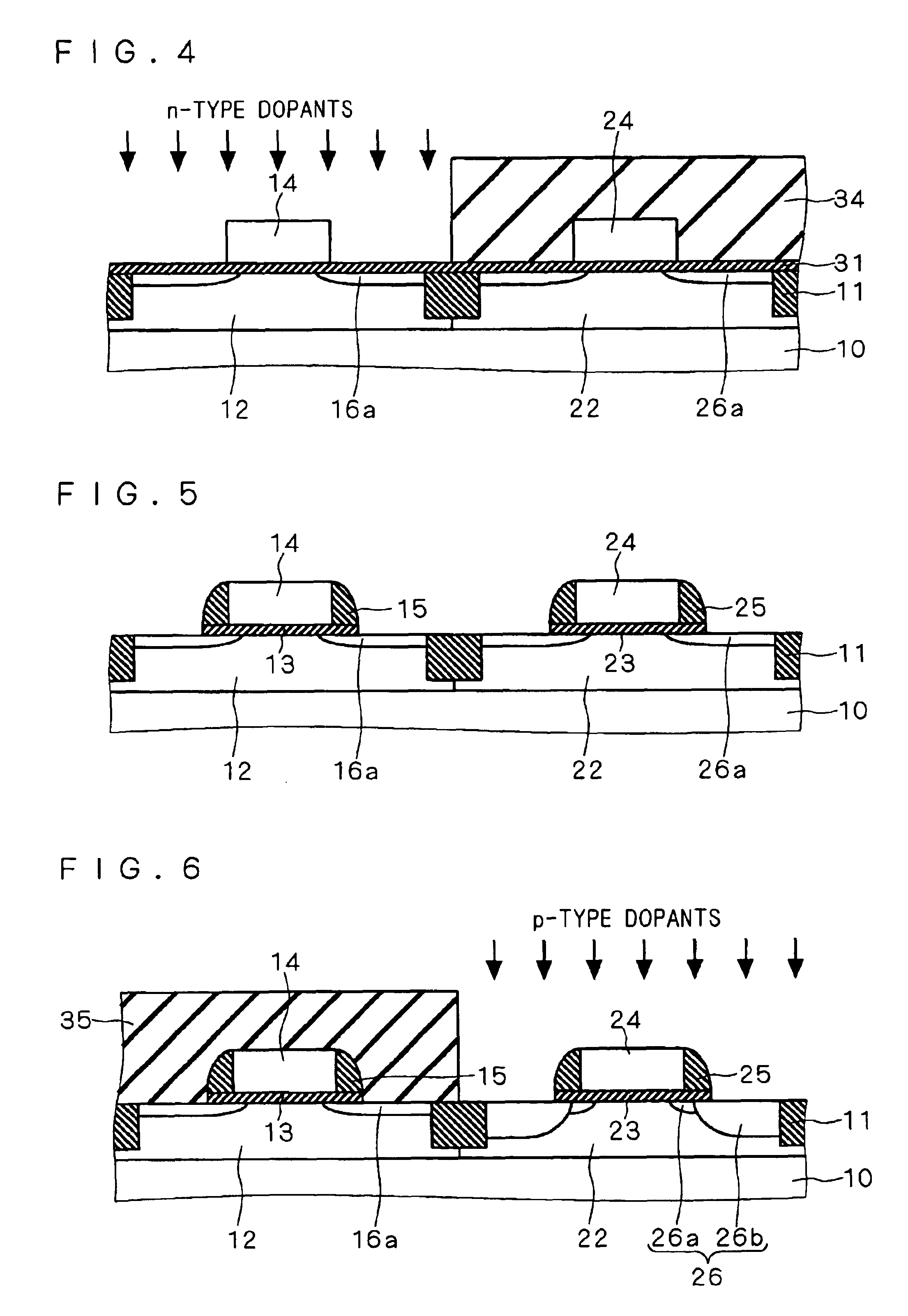

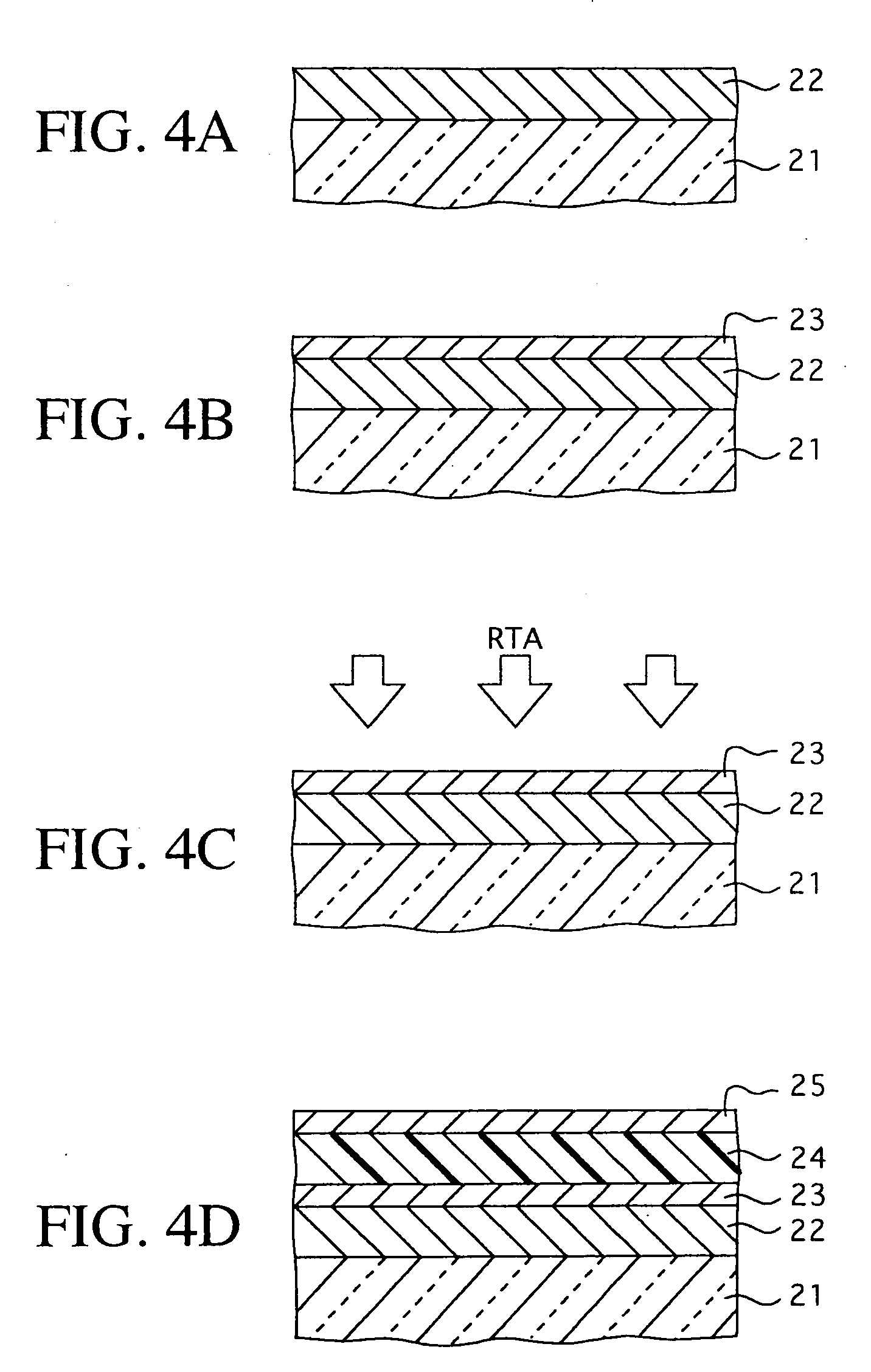

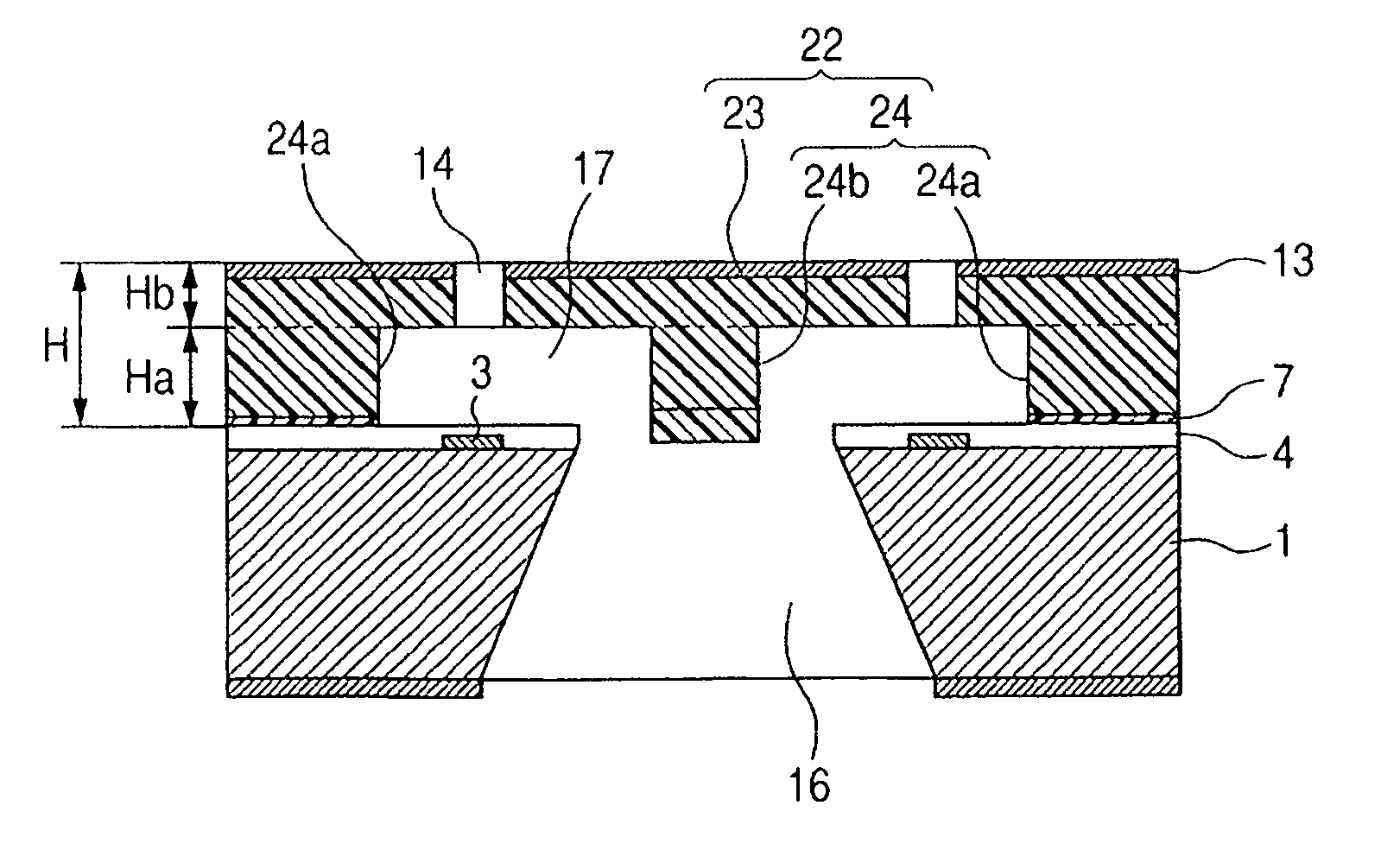

Semiconductor device including gate electrode for applying tensile stress to silicon substrate, and method of manufacturing the same

InactiveUS6906393B2High carrier mobilitySimplify manufacturing stepsTransistorSolid-state devicesMass numberCharge carrier mobility

A gate insulating film (13) and a gate electrode (14) of non-single crystalline silicon for forming an nMOS transistor are provided on a silicon substrate (10). Using the gate electrode (14) as a mask, n-type dopants having a relatively large mass number (70 or more) such as As ions or Sb ions are implanted, to form a source / drain region of the nMOS transistor, whereby the gate electrode (14) is amorphized. Subsequently, a silicon oxide film (40) is provided to cover the gate electrode (14), at a temperature which is less than the one at which recrystallization of the gate electrode (14) occurs. Thereafter, thermal processing is performed at a temperature of about 1000° C., whereby high compressive residual stress is exerted on the gate electrode (14), and high tensile stress is applied to a channel region under the gate electrode (14). As a result, carrier mobility of the nMOS transistor is enhanced.

Owner:RENESAS ELECTRONICS CORP

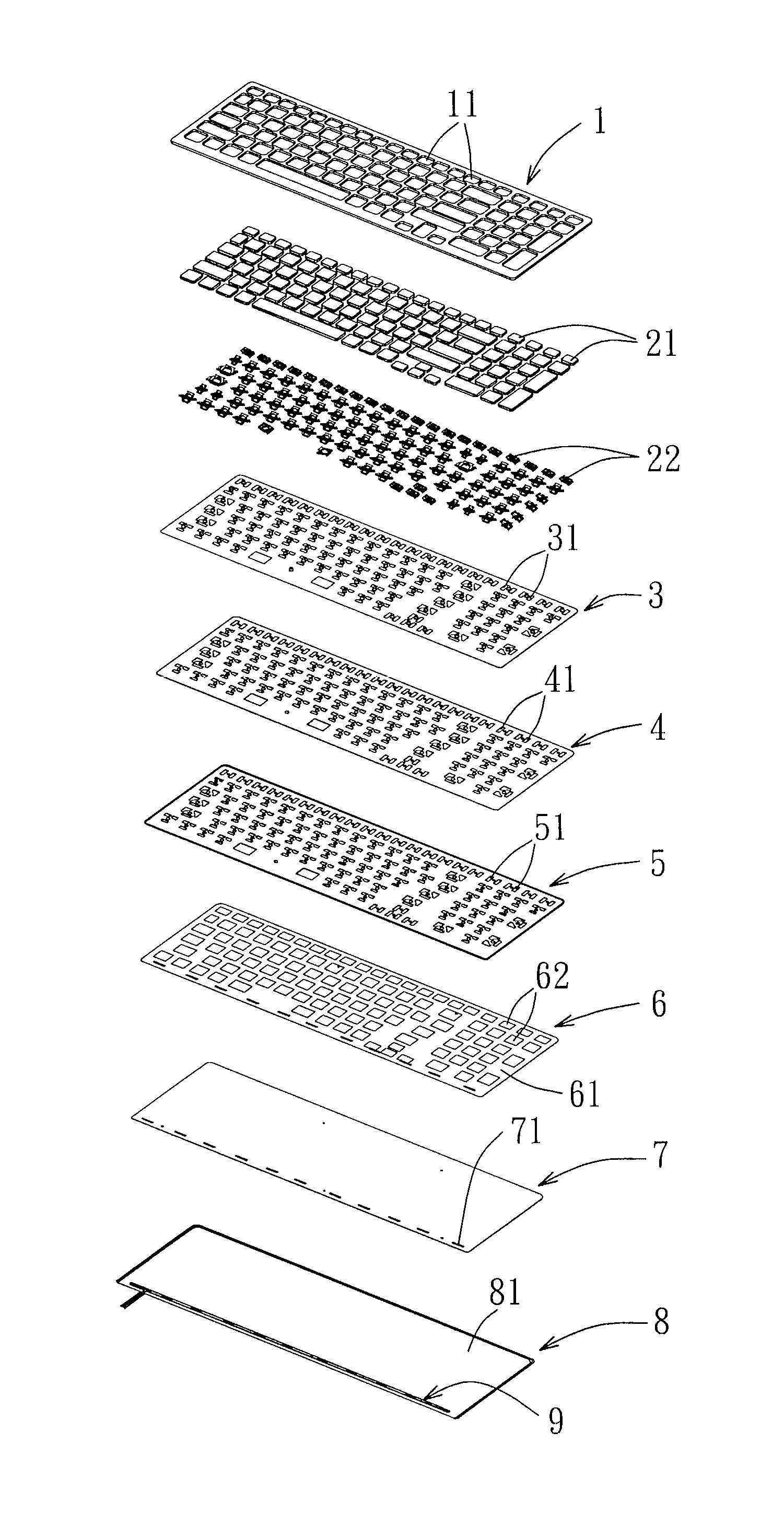

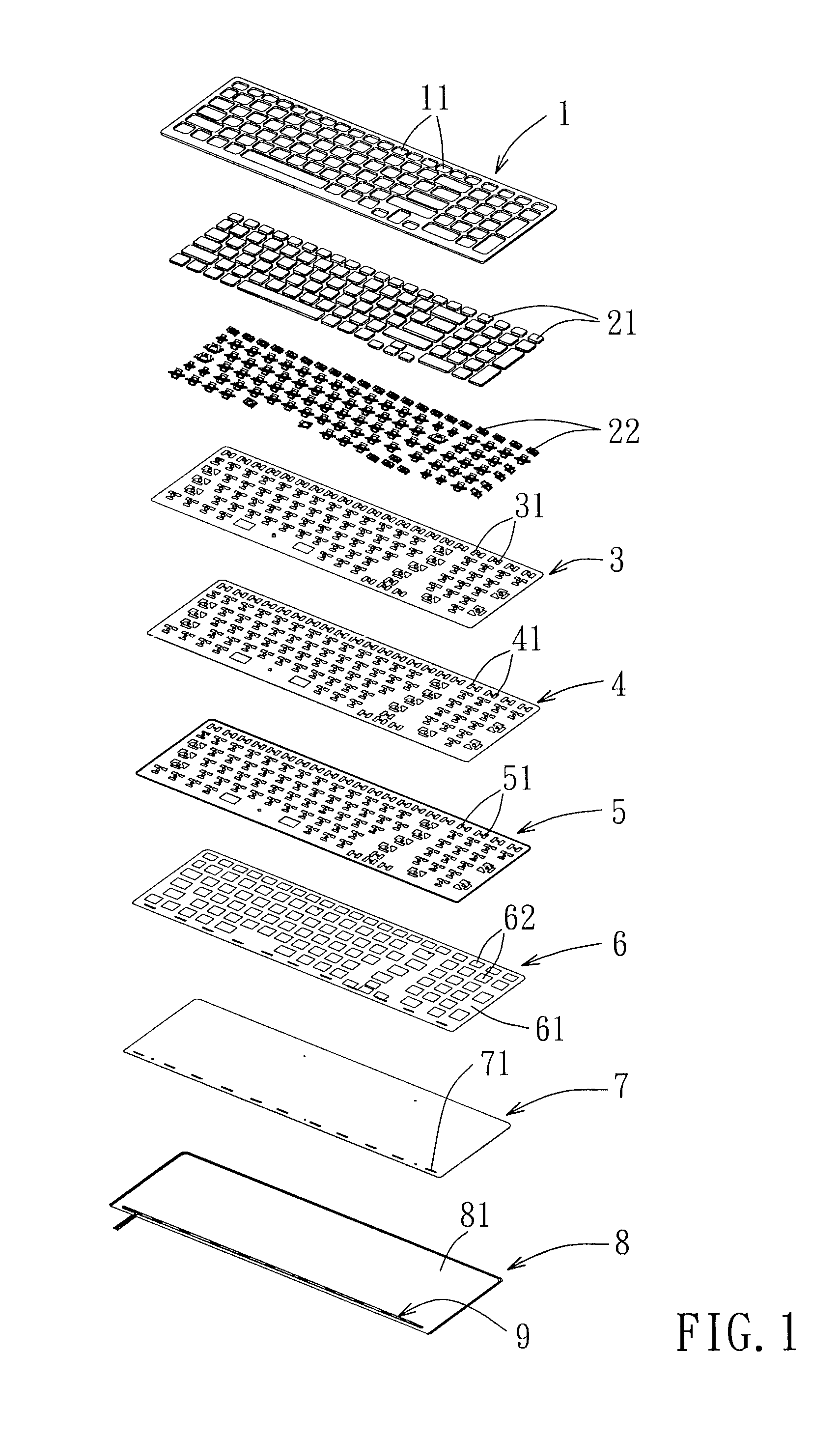

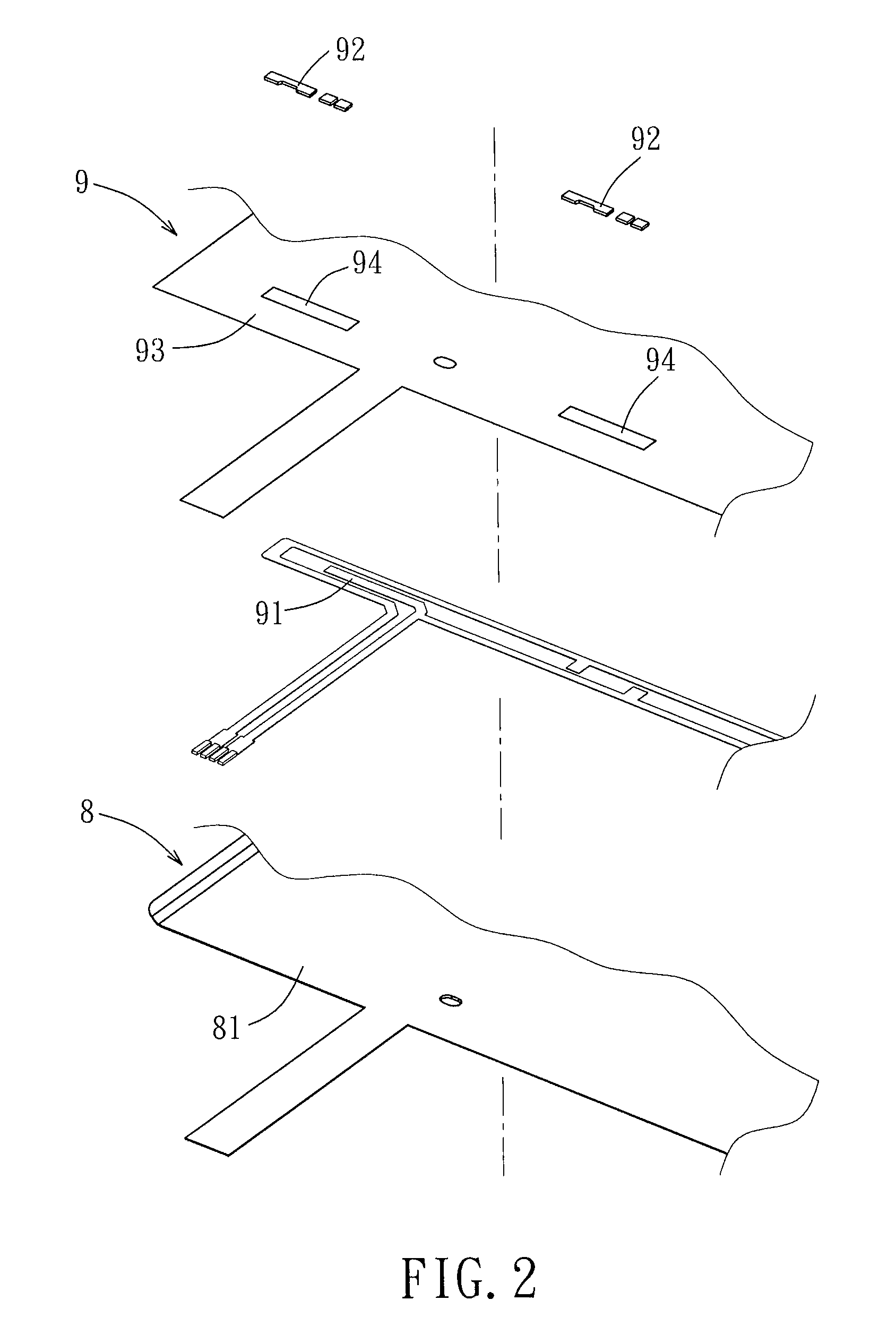

Luminous keyboard

InactiveUS20140151211A1Small sizeSimplify manufacturing stepsContact mechanismsLegendsLight guideConductive polymer

A luminous keyboard includes: a plurality of key caps; a light guiding plate disposed under the key caps; a reflector disposed under the light guiding plate; a masking layer disposed between the key caps and the light guiding plate; a membrane circuit unit disposed under the key caps and on the masking layer; and a luminous unit having a conductive lead, and an illuminant electrically connected to the conductive lead. The conductive lead is made of a material including a conductive polymer gel and a conductive powder and is formed directly on one of the reflector, the masking layer and the membrane circuit unit.

Owner:CHANGSHU SUNREX TECH

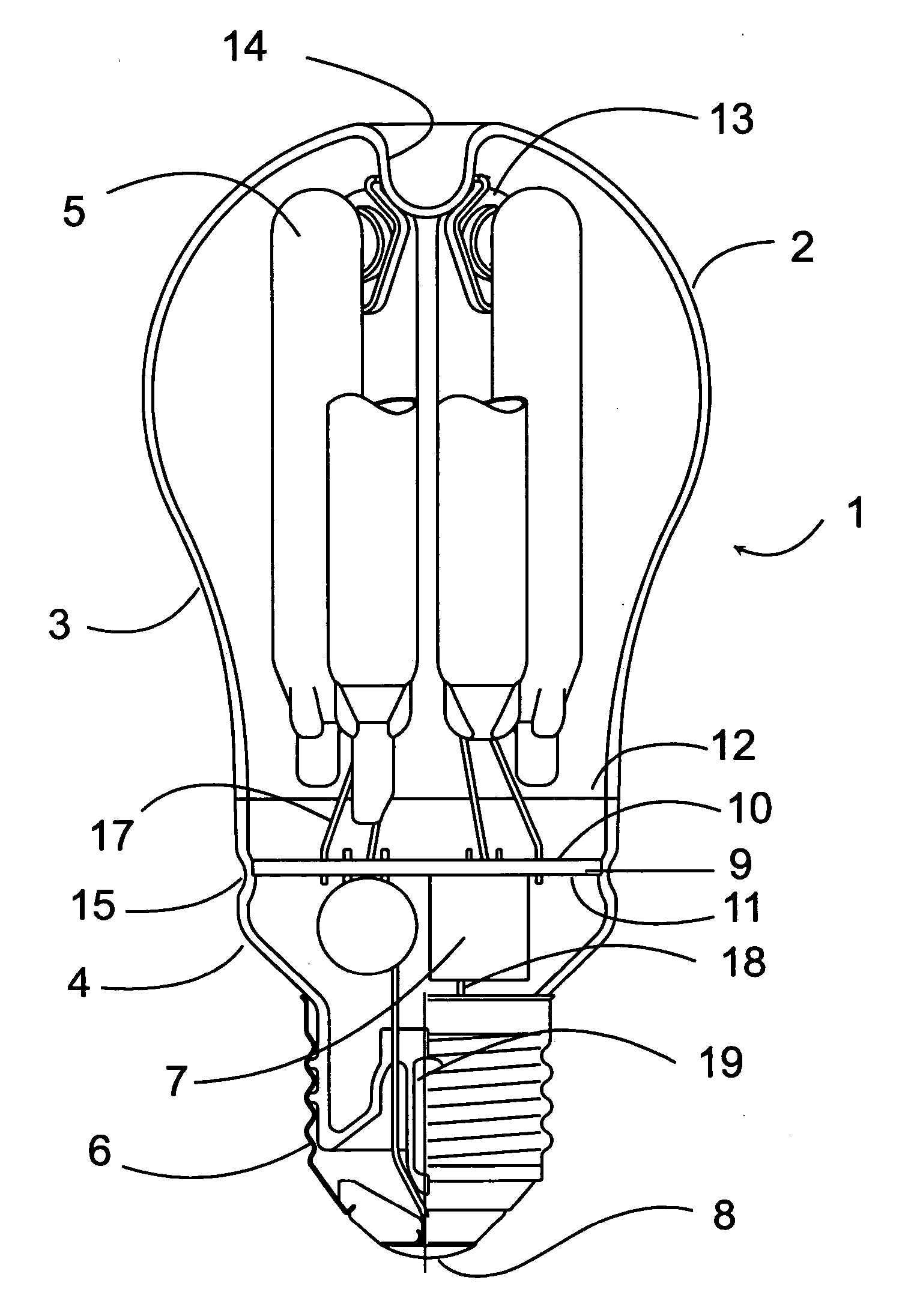

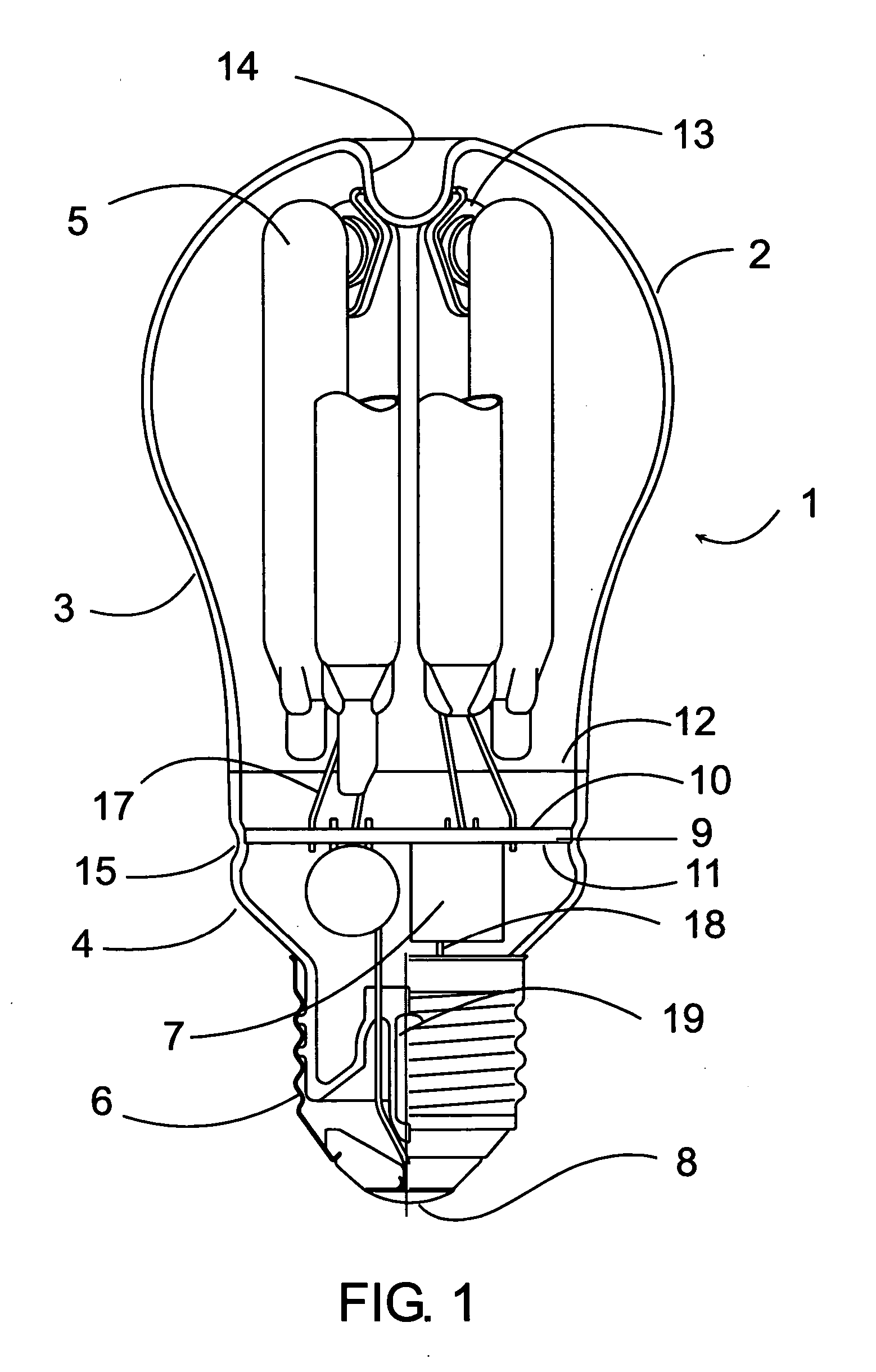

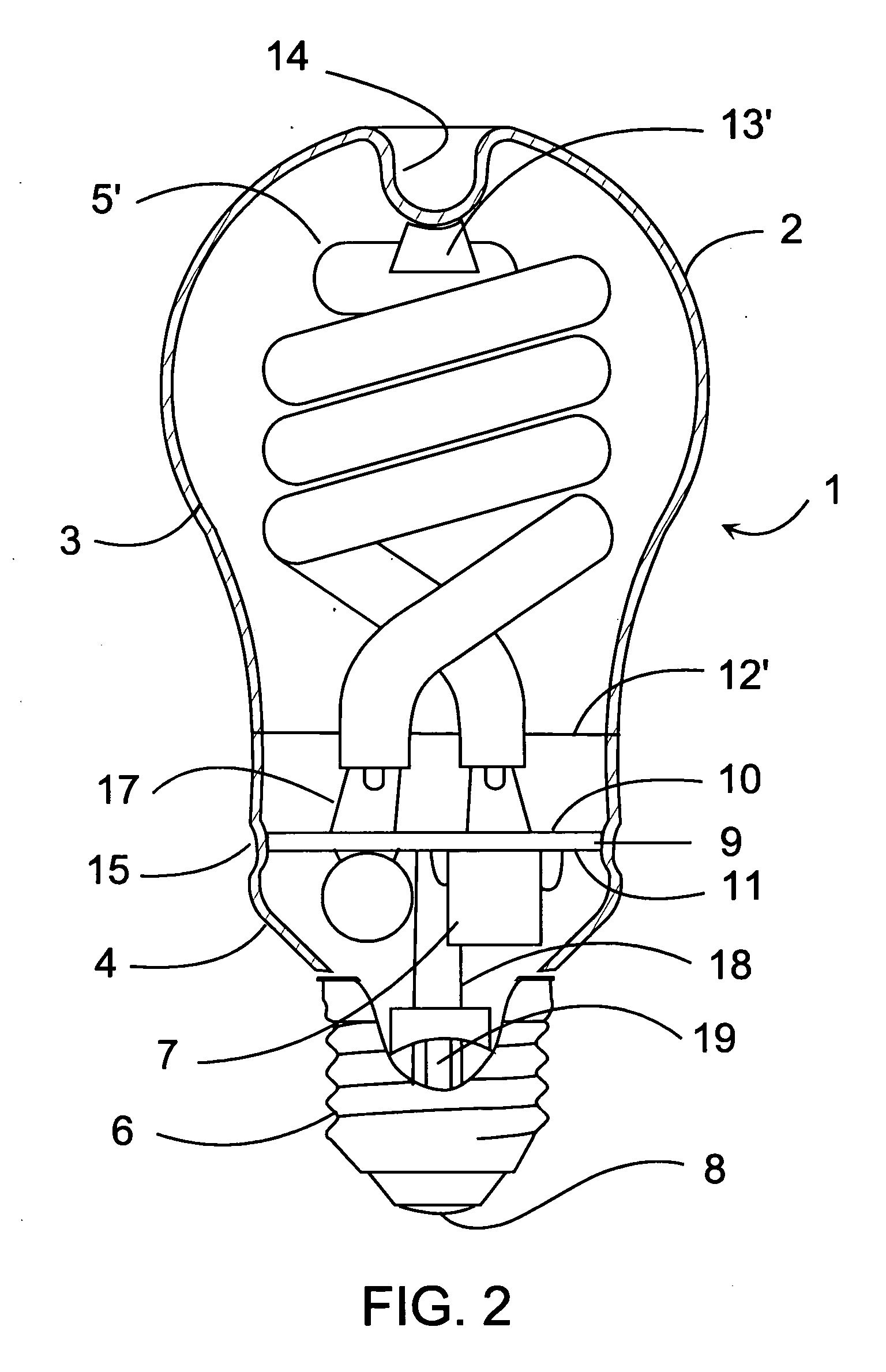

Compact fluorescent lamp and method for manufacturing

InactiveUS20070063656A1More to mechanical vibrationSimplify manufacturing stepsGas discharge lamp usageSolid cathode detailsElectrical ballastFluorescence

This compact fluorescent lamp comprises a discharge tube arrangement with at least one discharge tube. The tube is formed of glass, encloses a discharge volume filled with a discharge gas and has a fluorescent phosphor coating disposed on the inner surface of the tube. The tube forms a continuous arc path and the tube is provided with electrodes disposed at each end of the arc path. The lamp also comprises a ballast circuit connected to the electrodes for controlling the current in the tube and a lamp base for connecting said lamp to a power supply through a socket. The lamp is enclosed in an outer envelope comprising a substantially spherical portion enclosing the tube arrangement and an elongated end portion enclosing the ballast circuit. The end portion of the outer envelope is closed and sealed by a sealing means of the same material as the material of the outer envelope. The sealing means is connected to the envelope in a hermetically sealing way. A method for manufacturing a compact fluorescent lamp as described above is also disclosed. In the method, an outer envelope with an open end on the base side is provided. The open end of the envelope is closed and sealed with a sealing means to provide a hermetic seal. The envelope is separated by cutting along a circumferential line into an upper part and a lower part. The ballast circuit is introduced into the lower part and respective connection points of the ballast circuit are connected to power supply lead-out wires. The discharge tube arrangement is connected to respective connection points of the ballast circuit by lead-in wires. The lead-in wires and the lead-out wires are short and need not be insulated. The ballast circuit and the discharge tube arrangement are held and supported in the outer envelope by the connecting wires and fixing means.

Owner:GENERAL ELECTRIC CO

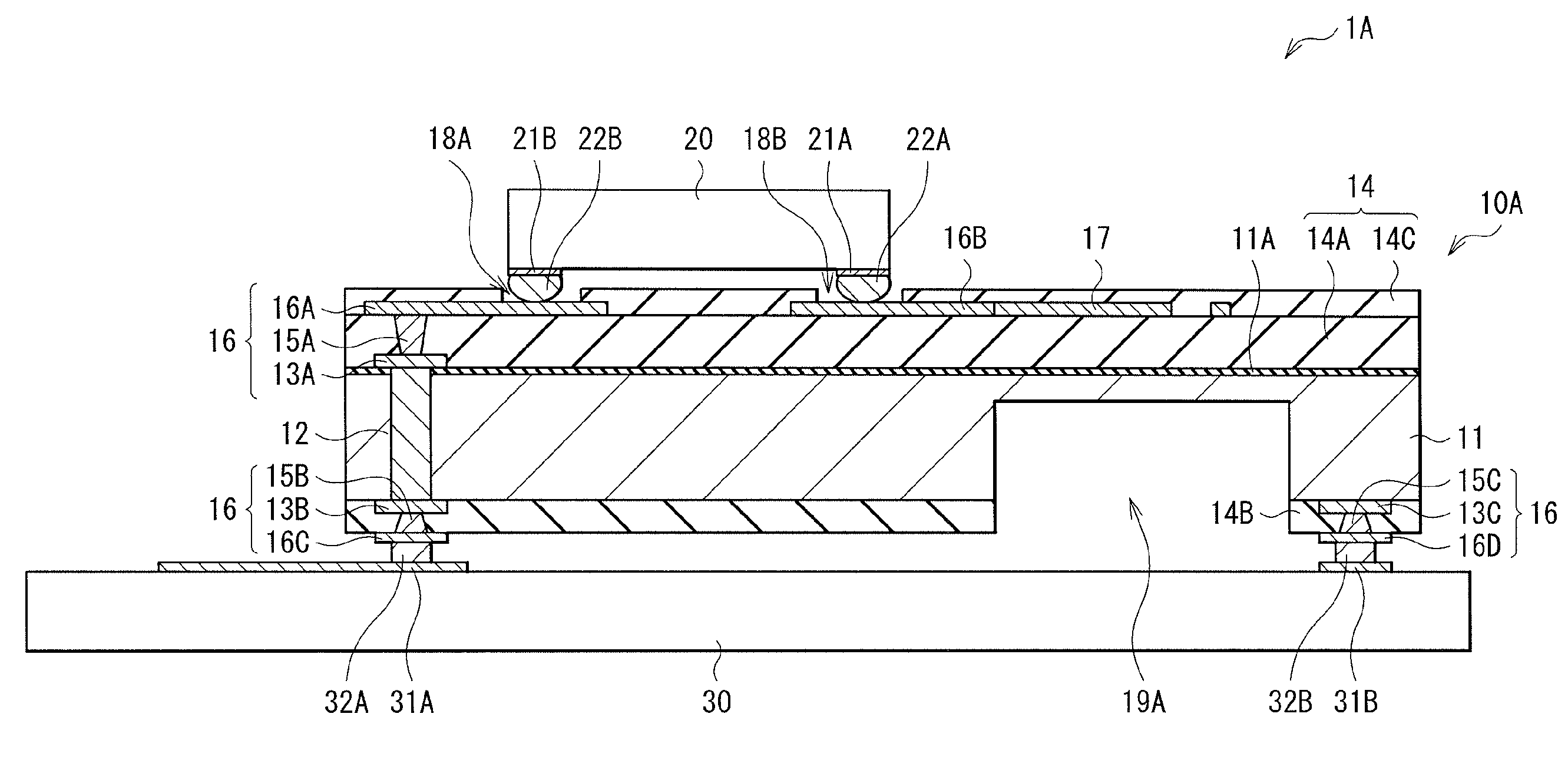

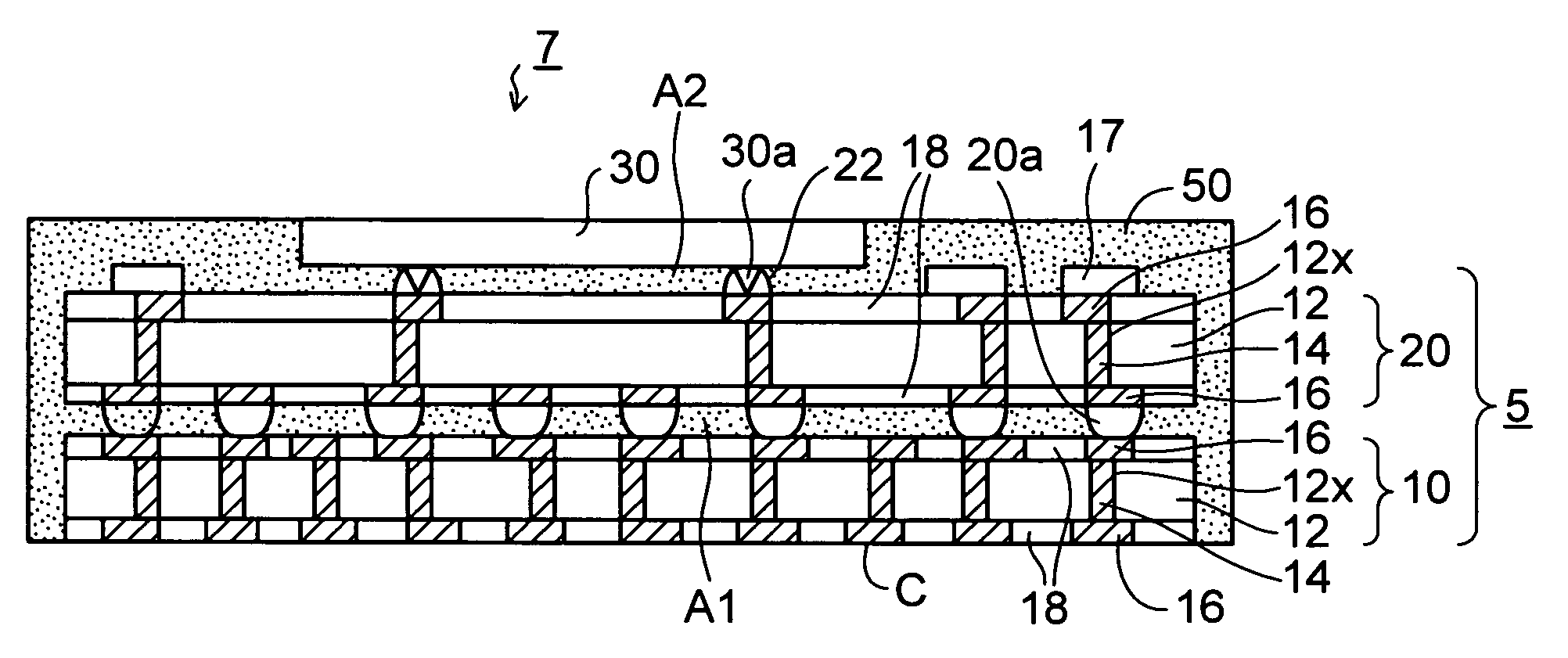

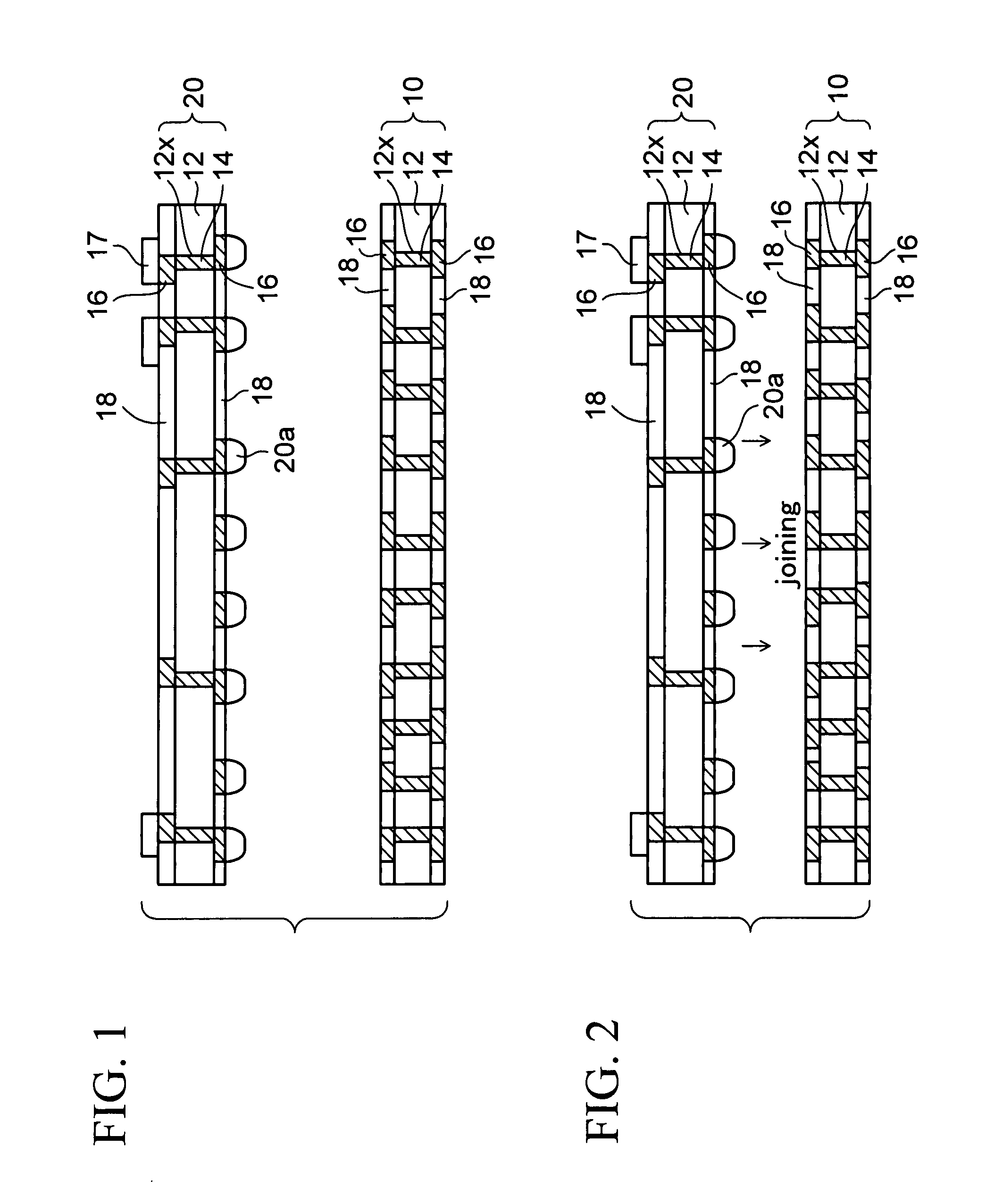

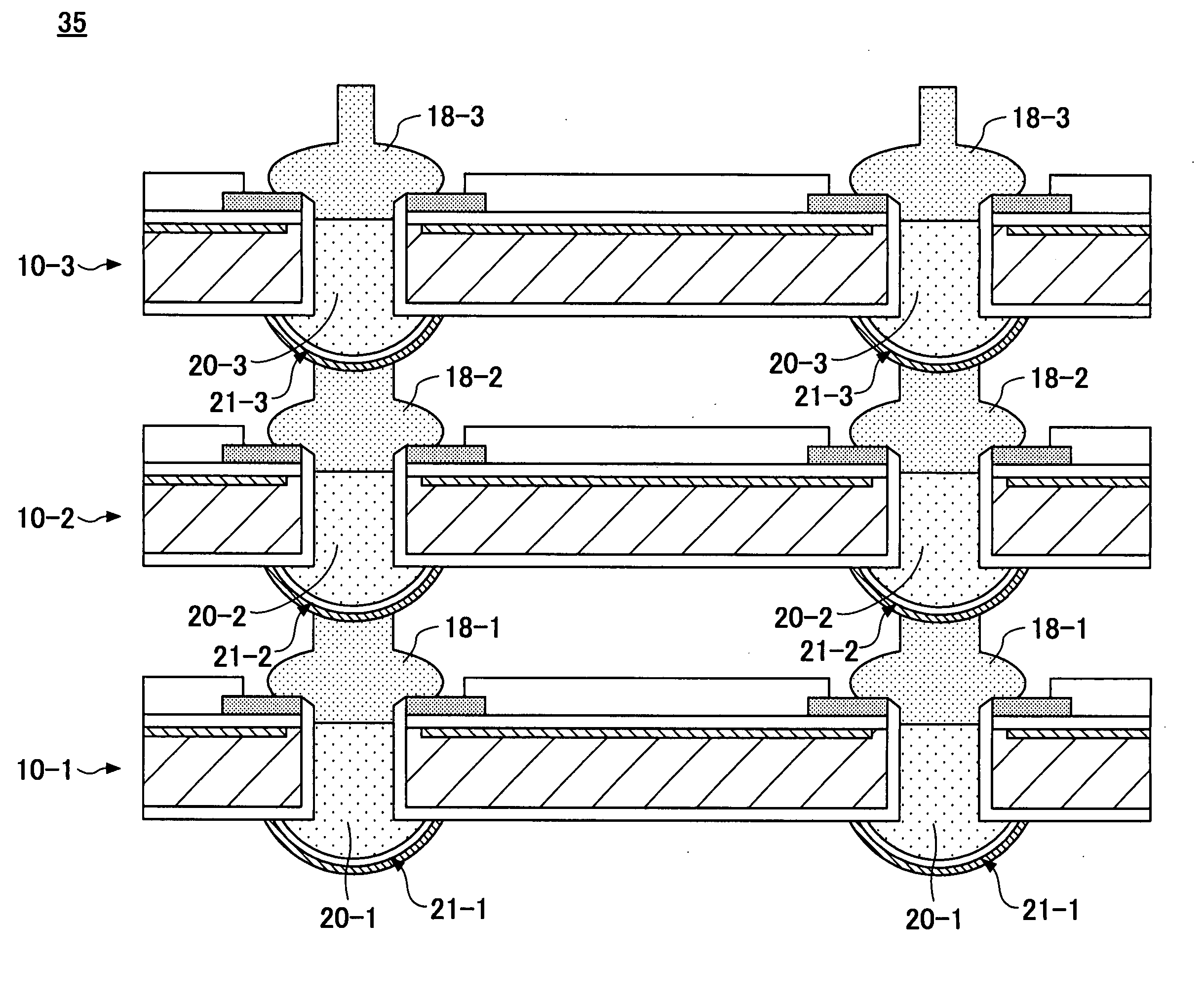

Interposer, module, and electronics device including the same

InactiveUS20110032685A1Lower Reliability RequirementsReduce yieldSemiconductor/solid-state device detailsCircuit arrangements on support structuresSemiconductor chipInterposer

An interposer with which the manufacturing steps are able to be simplified and which shows superior high frequency characteristics is provided. The interposer includes: a substrate having a front face and a rear face; a wiring that is formed on the front face side of the substrate and is electrically connected to a semiconductor chip; an electric device connected to the wiring; and a concave section that is formed from the rear face side of the substrate in a position corresponding to the electric device.

Owner:SONY CORP

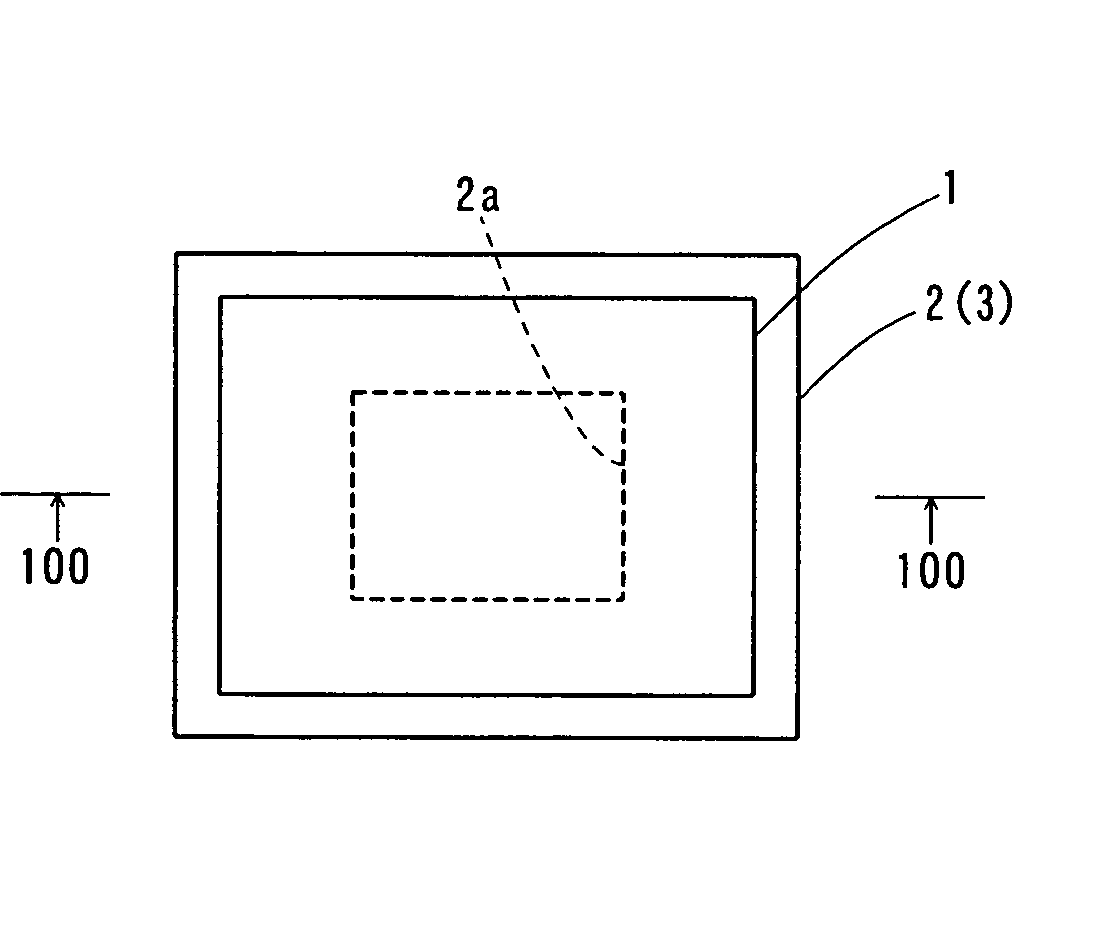

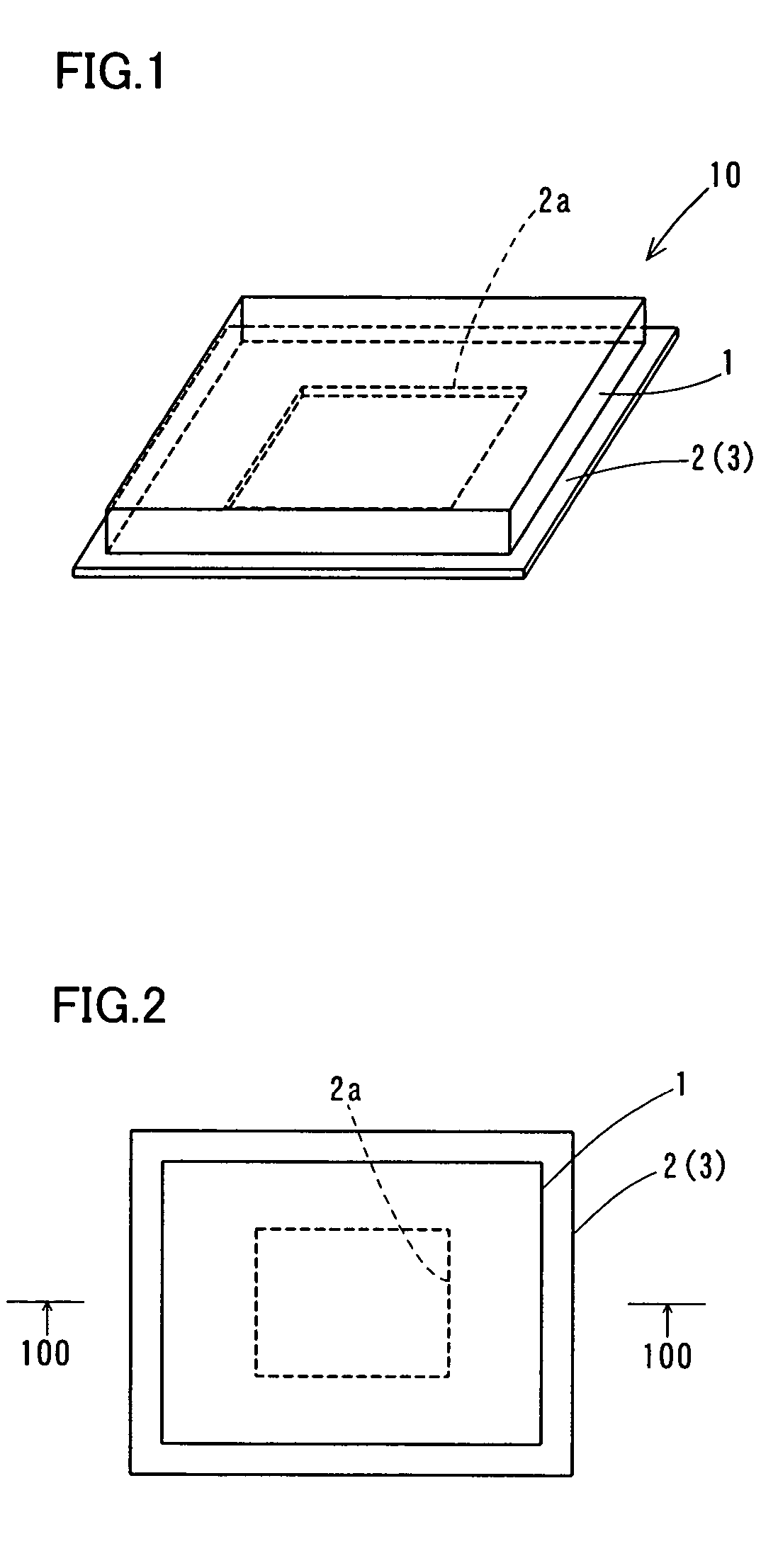

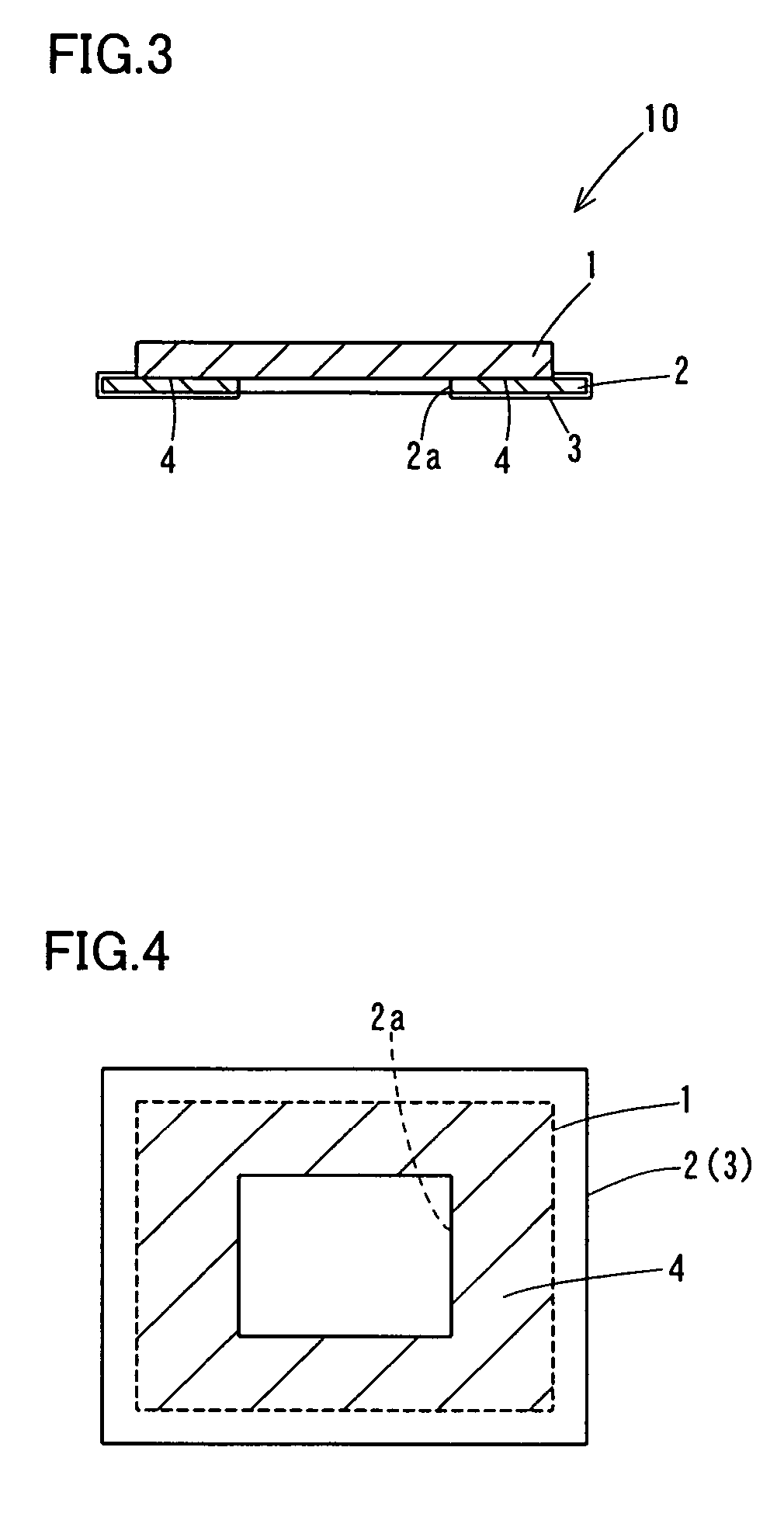

Light transmitting window member, semiconductor package provided with light transmitting window member and method for manufacturing light transmitting window member

InactiveUS20060131600A1Simple structureSimplify manufacturing stepsSemiconductor/solid-state device detailsPhotometryAdhesiveSemiconductor package

A light transmission window member capable of simplifying the structure and capable of simplifying manufacturing steps is obtained. This light transmission window member (10, 10a), which is a light transmission window member employed for a semiconductor package (30, 30a), comprises a flat metal frame (2) having an opening (2a) for defining a light passage region and a glass member (1) capable of transmitting light bonded to the upper surface of the flat frame having the opening without through an adhesive to cover the opening.

Owner:NEOMAX MATERIALS

Display device, method for manufacturing thereof, and television device

InactiveUS7273773B2Reduce in quantitySimplify manufacturing stepsStatic indicating devicesElectroluminescent light sourcesDisplay deviceConductive materials

The invention provides a display device and a method for manufacturing thereof by increasing a material efficiently as well as simplifying steps. Also, the invention provides a technique for forming a pattern such as a wiring, that is used for forming a display device, to have a predetermined shape with an excellent controllability. The method for manufacturing a display device includes the steps of: forming a lyophobic region; selectively irradiating laser beam in the lyophobic region to form a lyophilic region; selectively discharging a composition, that contains a conductive material, in the lyophilic region to form a gate electrode layer; forming a gate insulating layer and a semiconductor layer over the gate electrode layer; discharging a composition containing a conductive material over the semiconductor layer to form a source electrode layer and a drain electrode layer; and forming a pixel electrode layer on the source or drain electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

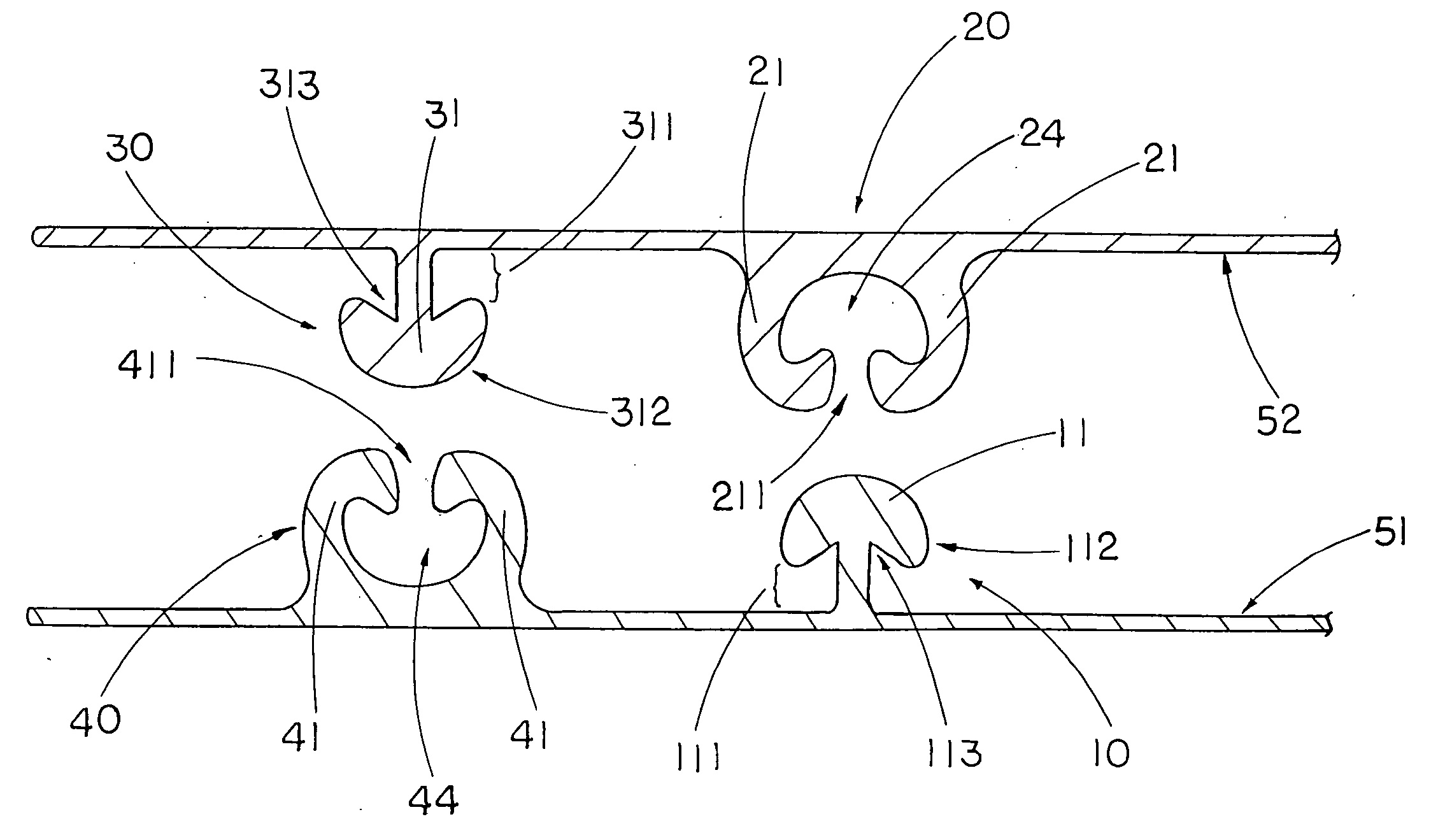

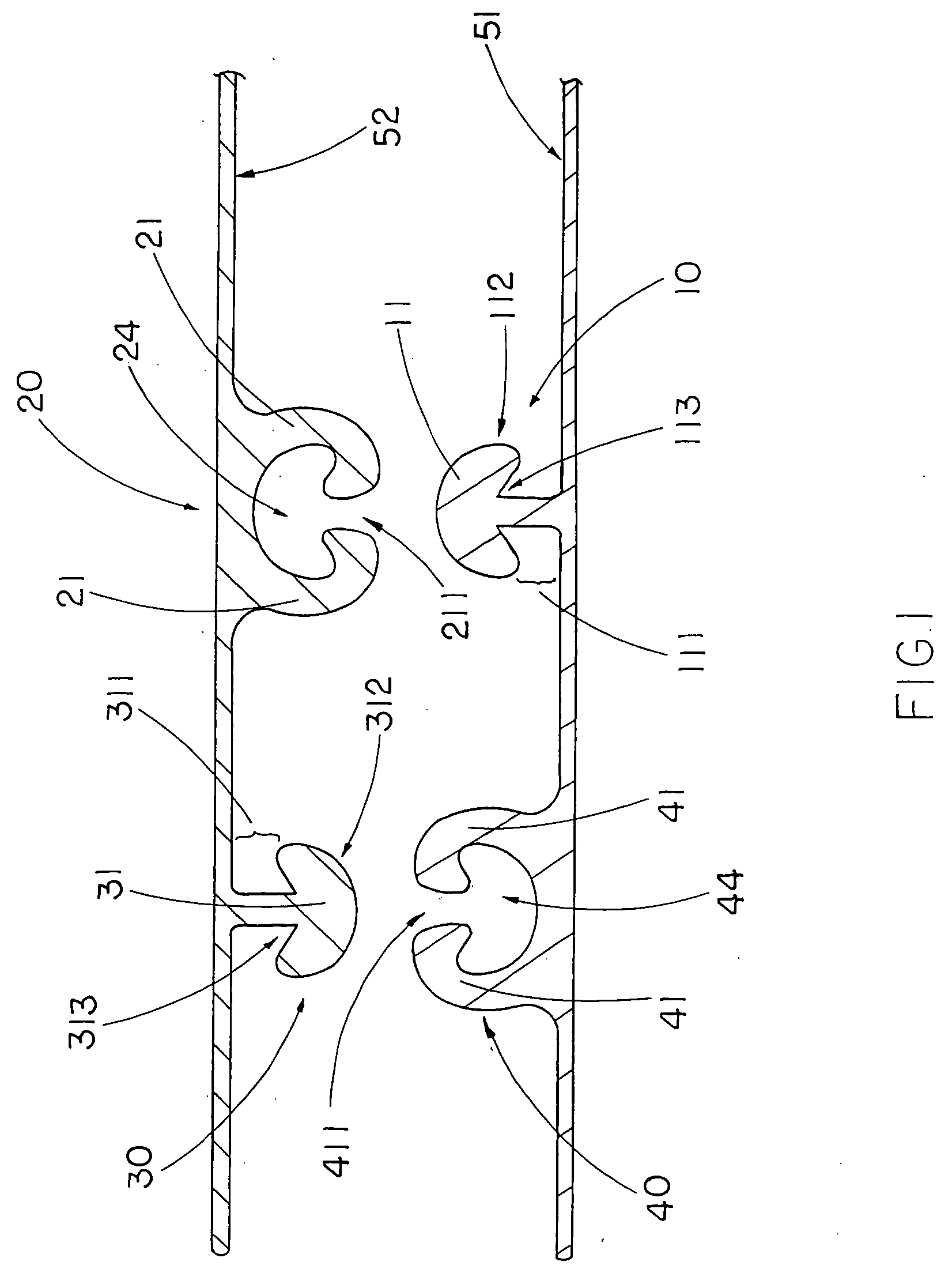

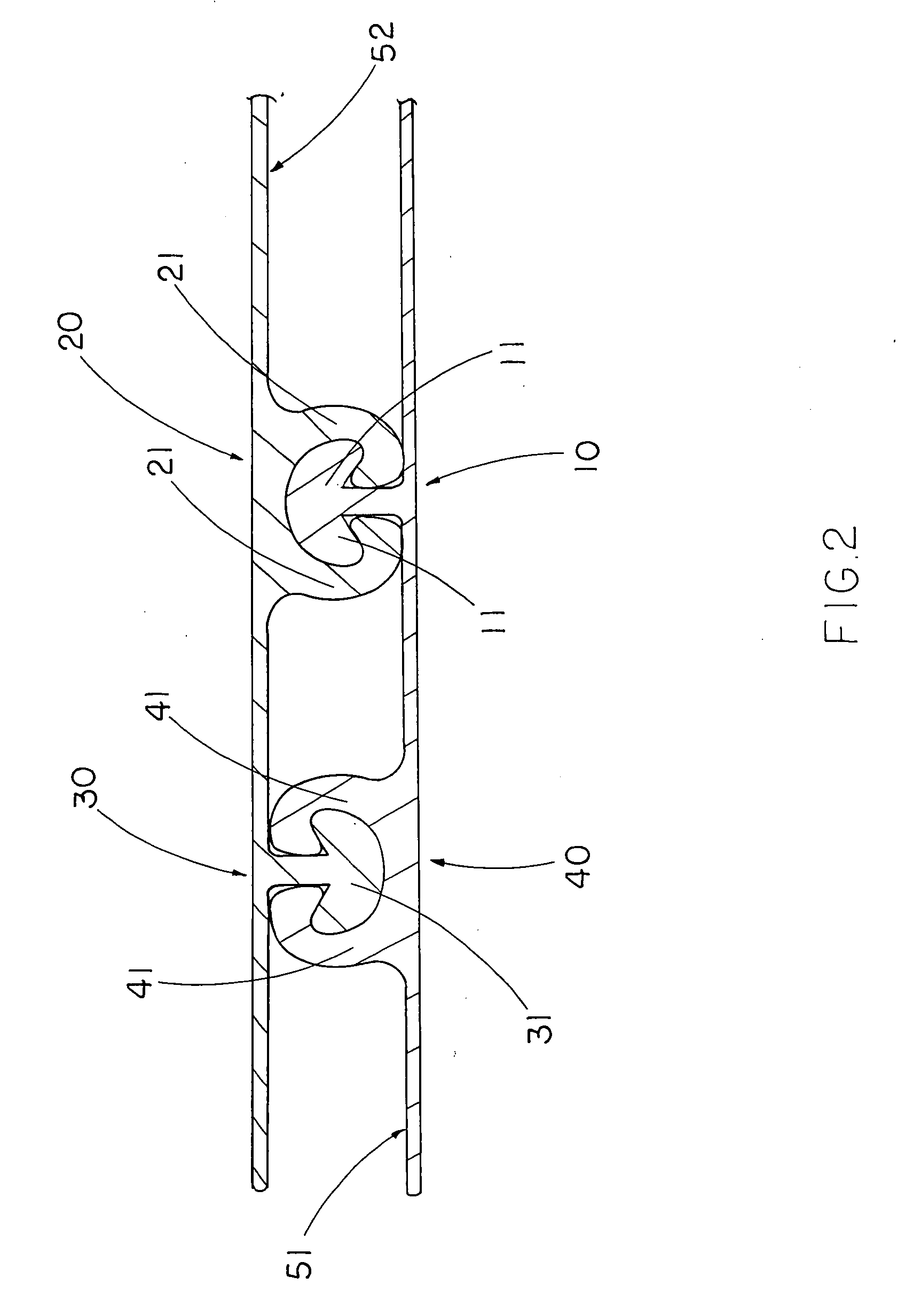

Zip lock

A zip lock for a storage bag having a first surface and a second surface, includes a zip fastener and a lock fastener integrally provided on the first and second surfaces respectively. The zip fastener has two zip bodies spacedly and integrally extended from the first surface and a coupling groove extending towards the first surface at a position between two inner walls of the zip bodies. The lock fastener has two locking arms spacedly and integrally extended from the second surface and a sealing arm integrally extended from the second surface at a position between the two locking arms to form two sealing cavities, wherein the sealing arm is sealedly inserted into the coupling groove until the round end of the sealing arm is positioned at the round end of the coupling groove.

Owner:INTELLI INNOVATIONS +1

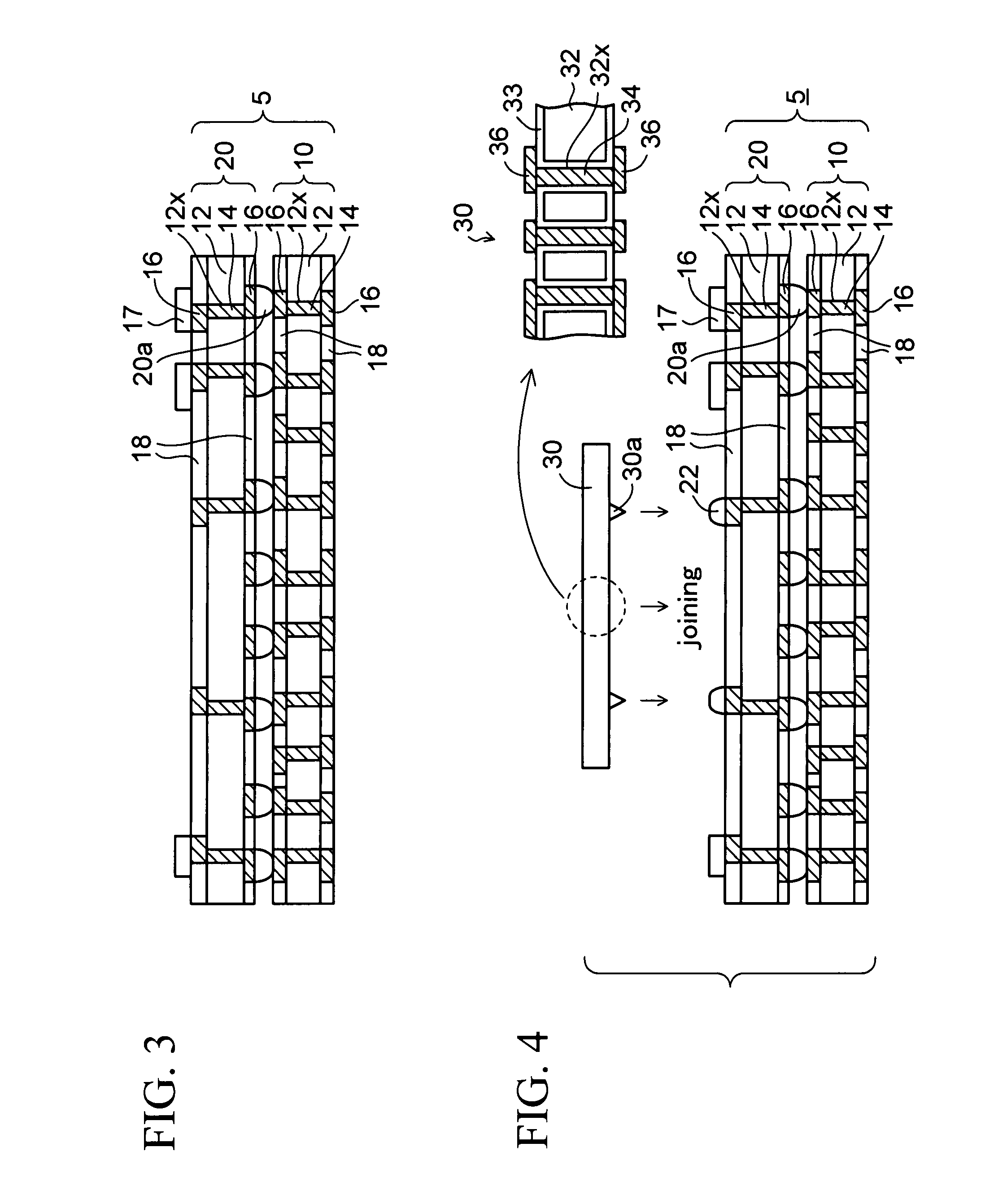

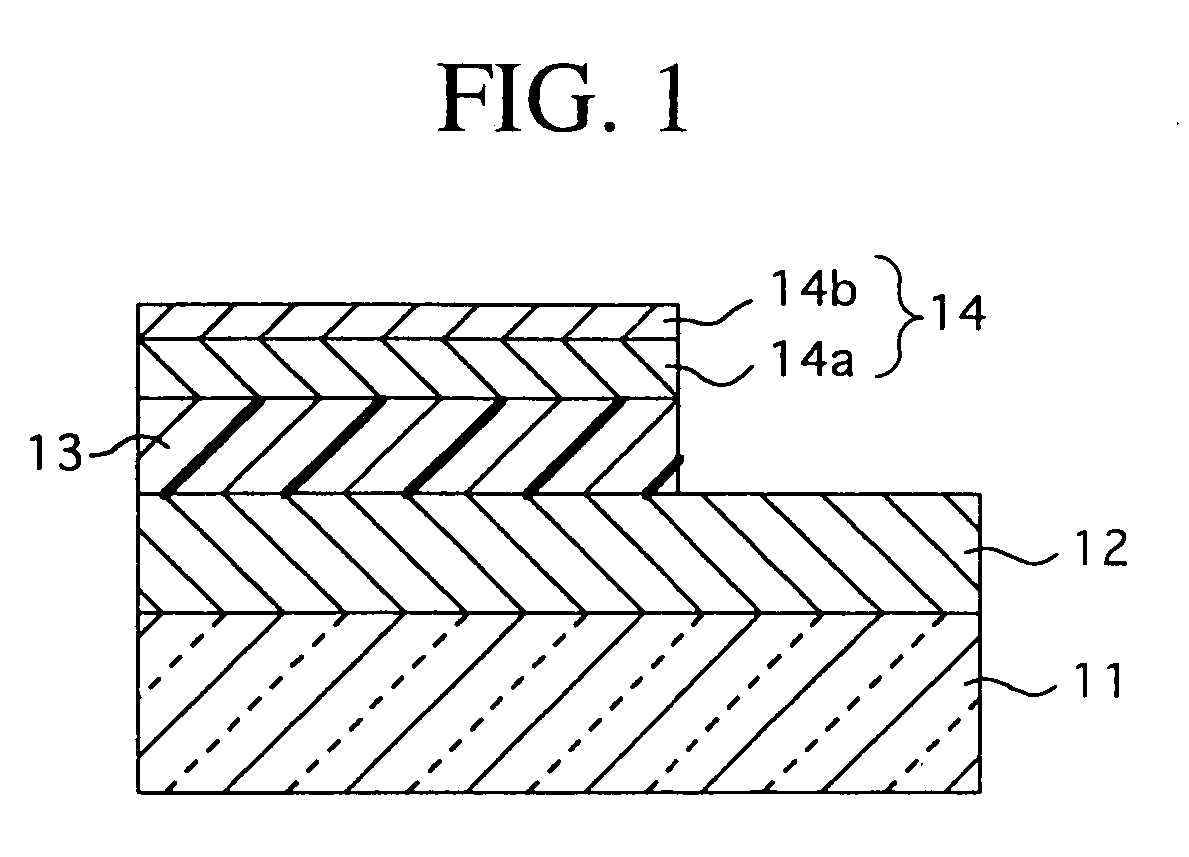

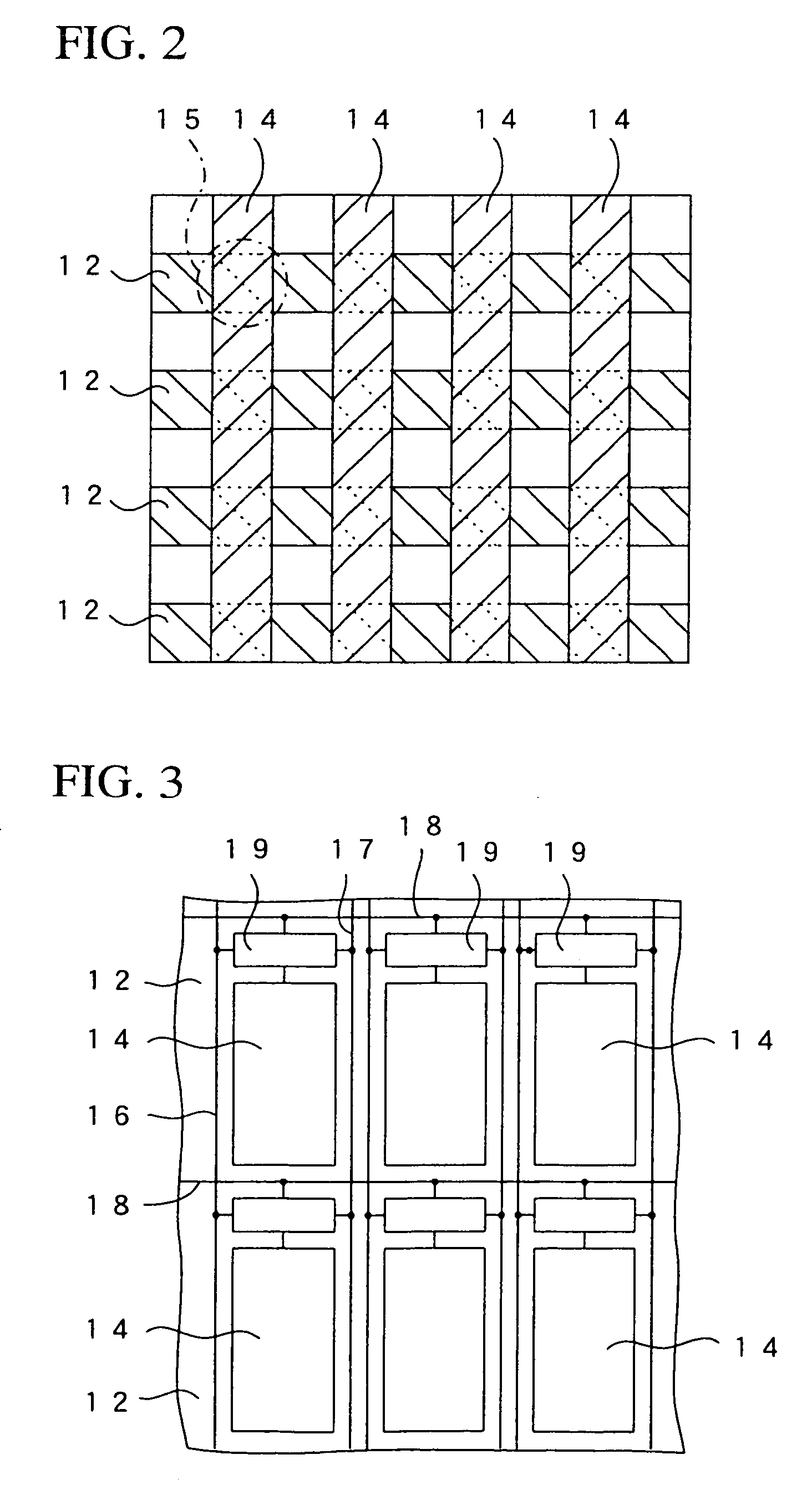

Wiring substrate, manufacturing method thereof, and semiconductor device

ActiveUS20080155820A1Easy to manufactureReliable fillingPrinted circuit assemblingSemiconductor/solid-state device detailsSilicon interposerElectrical connection

In a wiring substrate according to the present invention, a base wiring board is constructed by stacking a plurality of unit wiring boards each having wiring patterns which enable an electrical connection between upper and lower sides, in a state that the plurality of unit wiring boards are connected to each other via a connection terminal, and a silicon interposer is stacked on the base wiring board via a connection terminal, and a resin portion is filled in a gap between the plurality of unit wiring boards as well as a gap between the base wiring board and the silicon interposer, and a resin portion serves as a substrate which integrates the base wiring board and the silicon interposer.

Owner:SHINKO ELECTRIC IND CO LTD

Organic EL element and method of manufacturing the same, organic EL display device using the element, organic EL material, and surface emission device and liquid crystal display device using the material

InactiveUS20060204788A1Avoiding degradation in luminescence characteristicSimplify manufacturing stepsOrganic chemistrySolid-state devicesRheniumIridium

In an organic EL element, an organic EL layer is interposed between anodes and cathodes formed on a substrate. Each of the cathodes is made of a first conductive film that comes into contact with the organic EL layer and a second conductive film that constitutes a laminated structure together with the first conductive film. The first conductive film contains any one of an alkaline metal and an alkaline earth metal. The second conductive film contains any one of at least one type metal selected from a group consisting of Ru (ruthenium), Rh (rhodium), Ir (iridium), Os (osmium) and Re (rhenium) and its oxide.

Owner:FUJITSU LTD

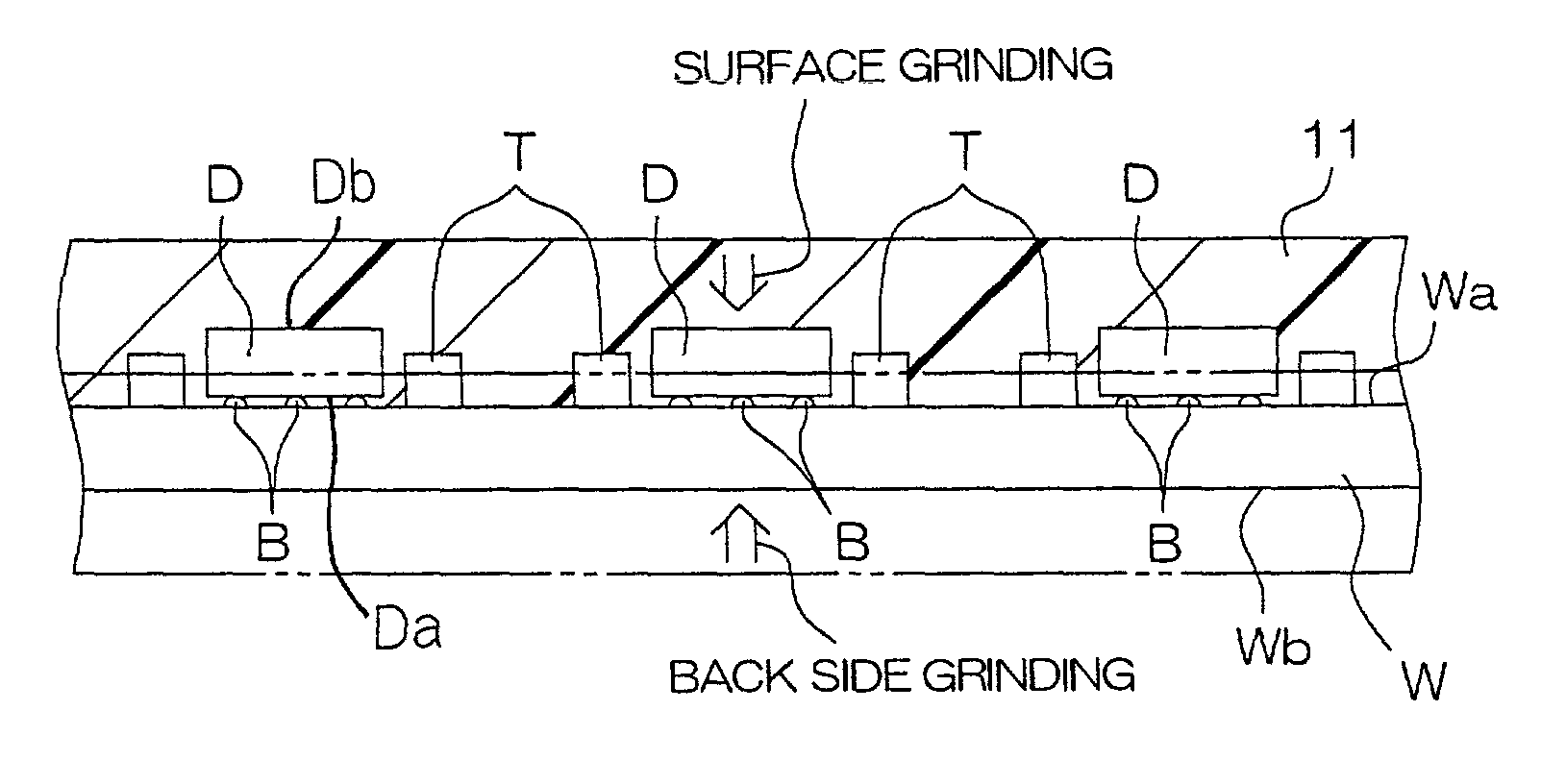

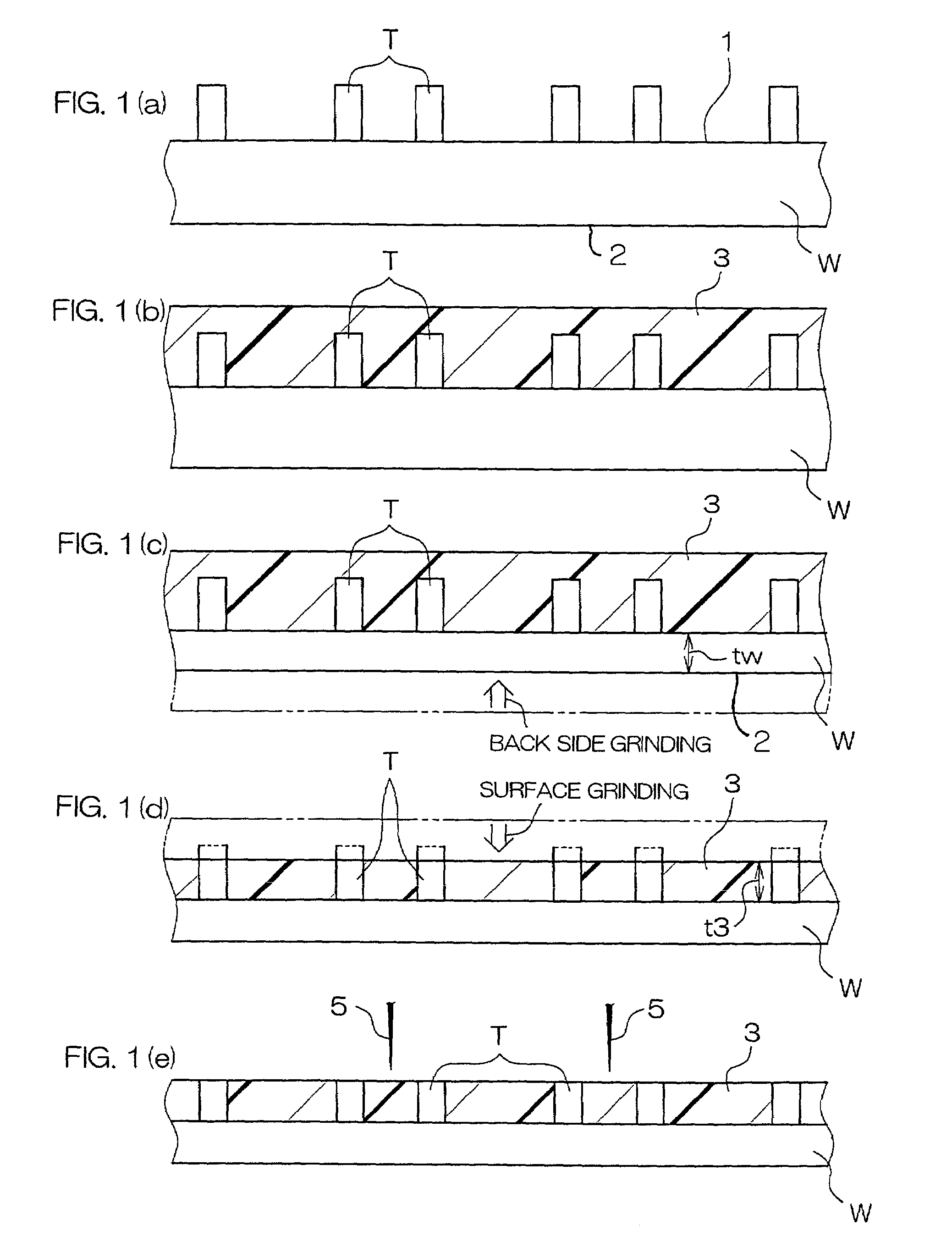

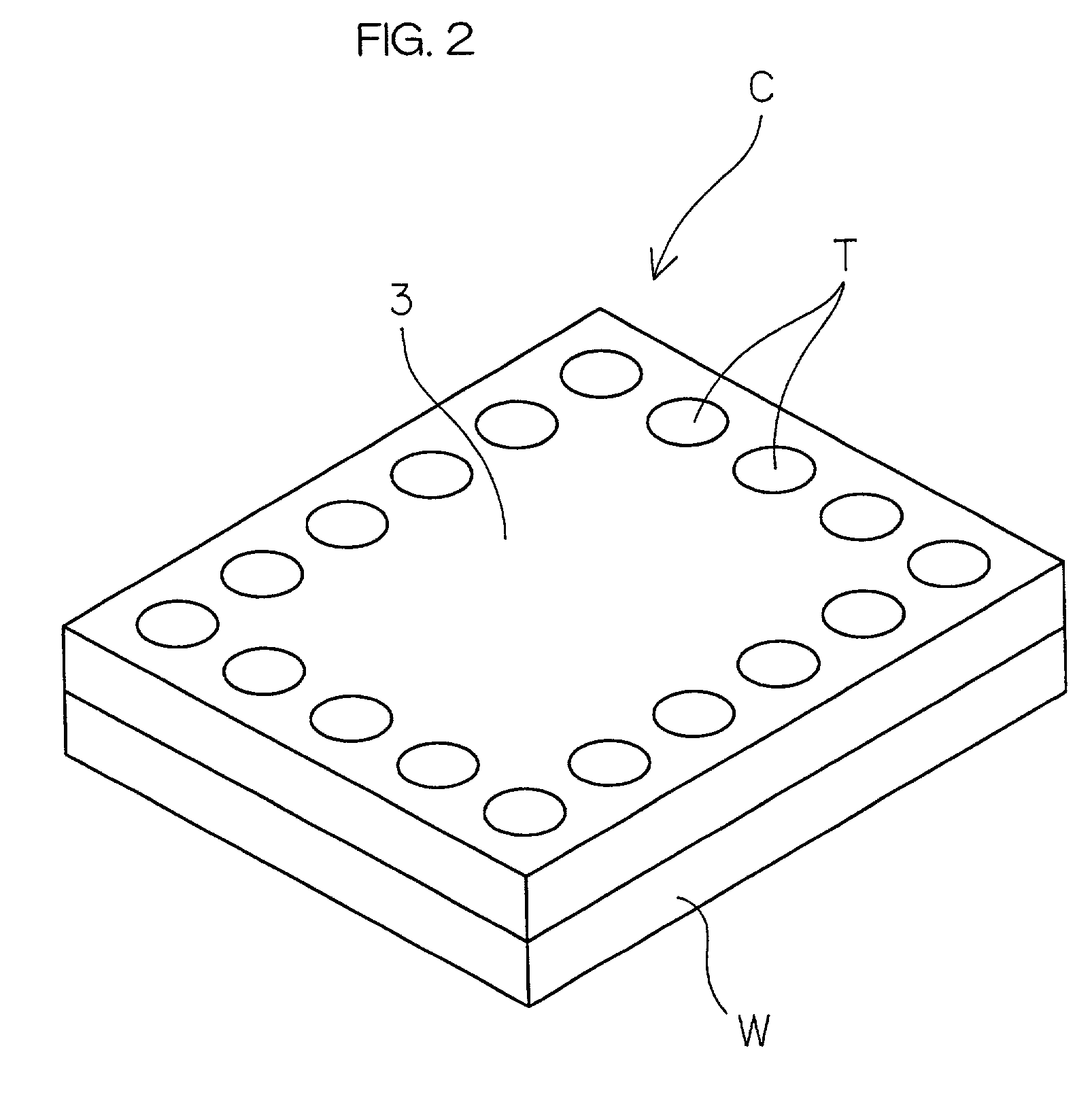

Semiconductor device and method for manufacturing the same

InactiveUS7129110B1Simplify manufacturing stepsEasy to manufactureSemiconductor/solid-state device detailsSolid-state devicesSurface grindingSemiconductor

A method for manufacturing a semiconductor device having projection electrodes on the surface of a semiconductor substrate. This method include an electrode forming step of forming the projection electrodes on the surface of the semiconductor substrate, a step of forming a protective resin layer on the whole surface of the semiconductor substrate provided with the projection electrodes, a back side grinding step of thinning the semiconductor substrate by polishing or grinding the back side of the semiconductor substrate, and a surface grinding step of exposing the projection electrodes by polishing or grinding the surface side of the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor chip and method of manufacturing semiconductor chip

ActiveUS20070085189A1Simplify manufacturing stepsReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A semiconductor chip includes a semiconductor substrate having a first principal surface, and having a device layer on the first principal surface in which a semiconductor device is formed, an electrode pad disposed on the first principal surface of the semiconductor substrate and electrically connected to the semiconductor device, a through via formed in a through hole penetrating through the semiconductor substrate and the electrode pad, and an Au bump deposited on the electrode pad and the through via such as to electrically connect between the electrode pad and the through via.

Owner:SHINKO ELECTRIC IND CO LTD

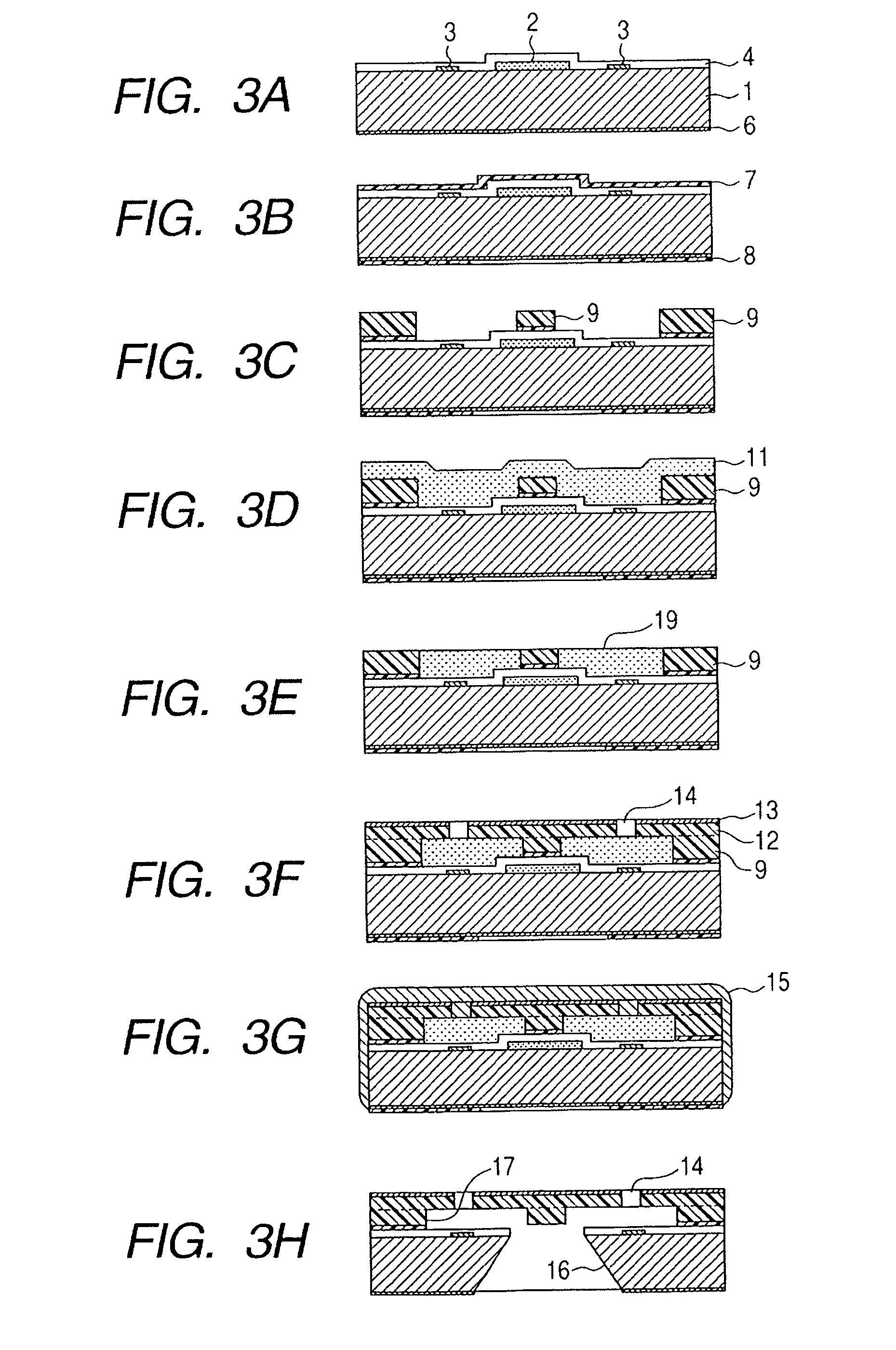

Method of manufacturing liquid discharge head

InactiveUS7300596B2Easy to manufactureImprove reliabilityRecording apparatusDecorative surface effectsVena contracta diameterEngineering

The method of manufacturing a recording head has a flow path wall forming step of forming flow path walls on a substrate having energy generating elements formed thereon, an imbedded material depositing step of depositing an imbedded material between the flow path walls and on a top of each flow path wall, a flattening step of polishing a top of the deposited imbedded material, until the top of the flow path wall is exposed, and a step of forming an orifice plate on the tops of the polished imbedded material and the exposed flow path wall. In the step of forming the flow path walls, patterning of a close contact property improvement layer is simultaneously performed to improve a close contact property between the flow path wall and the substrate.

Owner:CANON KK