Semiconductor device including gate electrode for applying tensile stress to silicon substrate, and method of manufacturing the same

a technology of tensile stress and silicon substrate, which is applied in the direction of semiconductors, semiconductor devices, electrical equipment, etc., can solve the problems of inapplicability to sti, insufficient activation annealing, and large number of problems to be solved, so as to improve carrier mobility and simplify manufacturing steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026]First Preferred Embodiment

[0027]The present inventors have found that when amorphous silicon including a large number of ions implanted therein undergoes thermal processing to form recrystallized polycrystalline silicon (polysilicon), volume expansion of silicon occurs. It has also been found that the amount of expansion of silicon is controlled largely by the mass number of ions implanted therein, and more particularly, that the amount of expansion increases as the mass number of implanted ions becomes larger (more specifically, 70 or more). It has been confirmed as well that the amount of expansion increases as the implant dose of ions increases.

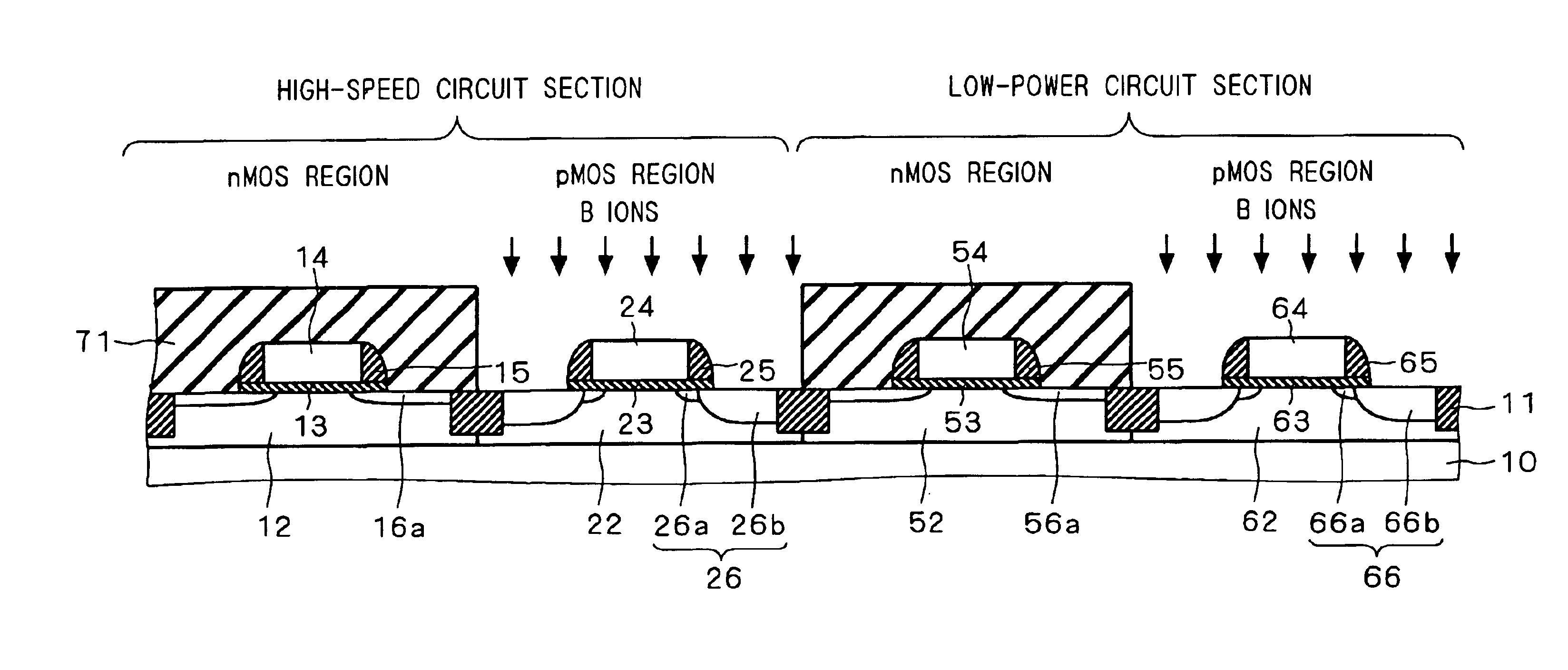

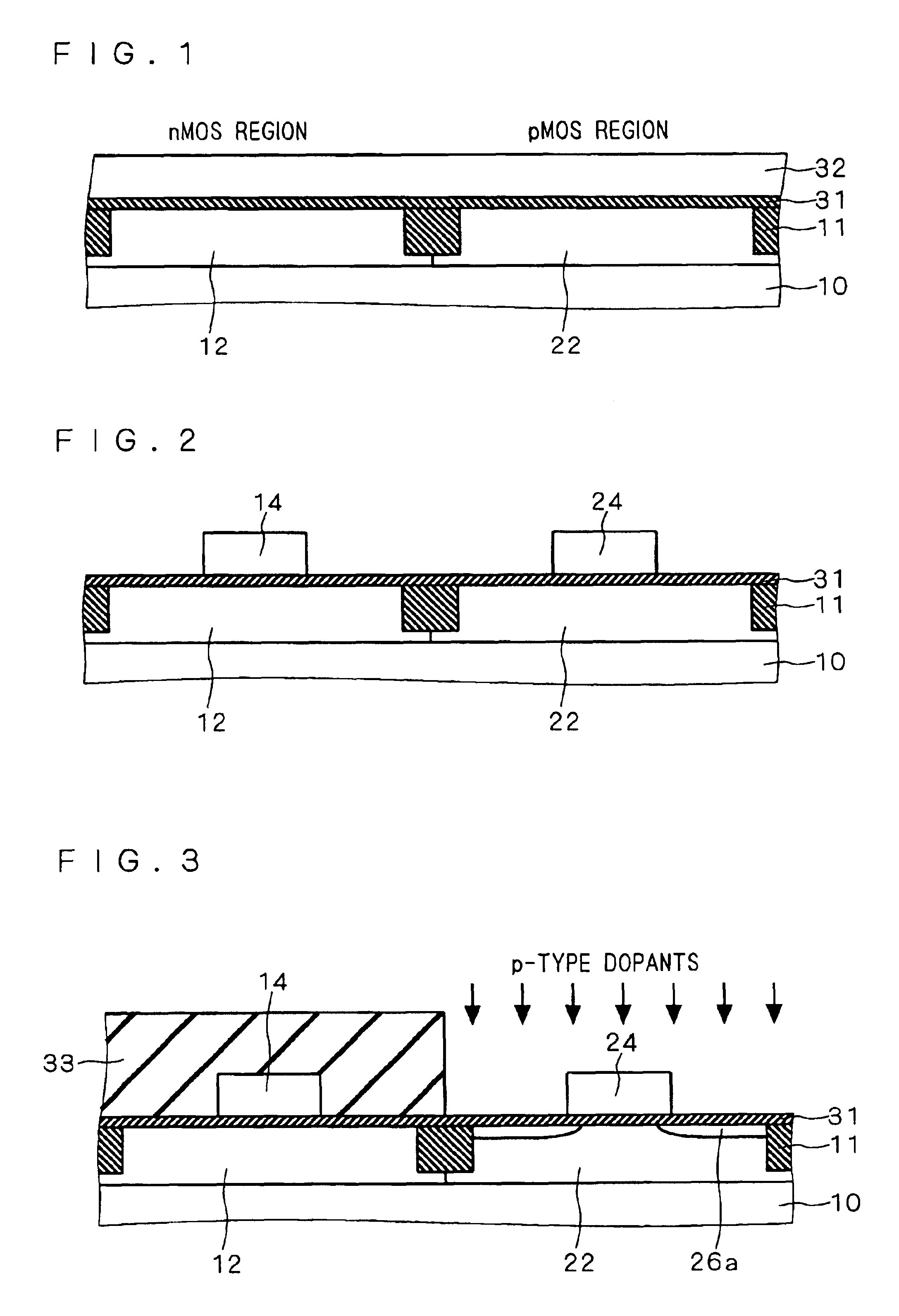

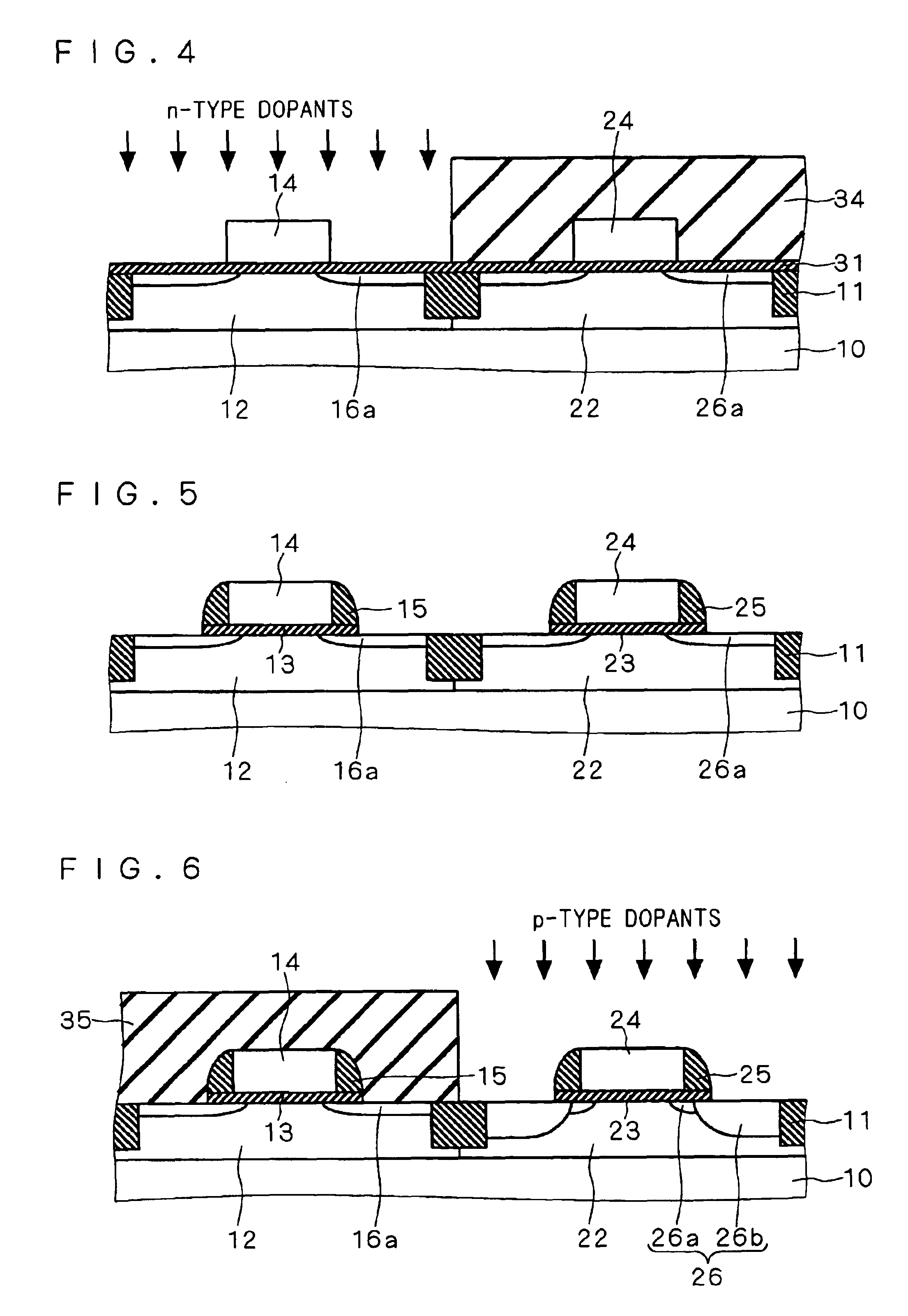

[0028]FIGS. 1 through 9 illustrate steps of manufacturing a semiconductor device according to the first preferred embodiment of the present invention. In each one of FIGS. 1 through 9, the left half shows a region for forming an nMOS transistor (hereinafter called as an “nMOS region”), and the right half shows a region for forming a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More