Bumping process and structure thereof

a technology of a copper bump and a structure, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., to achieve the effect of increasing the density of the circuit layout and reducing the distance between two adjacent copper bumps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

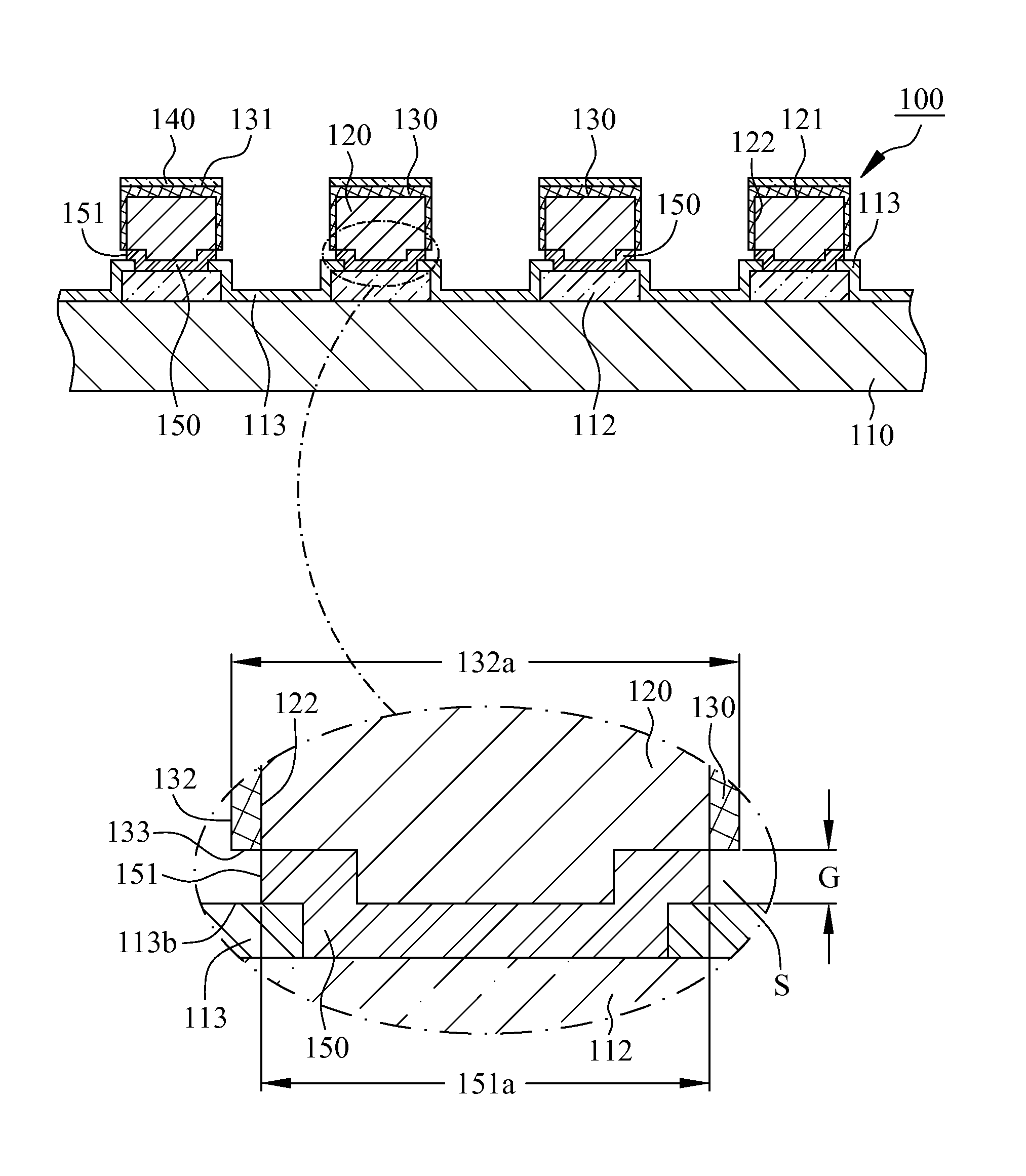

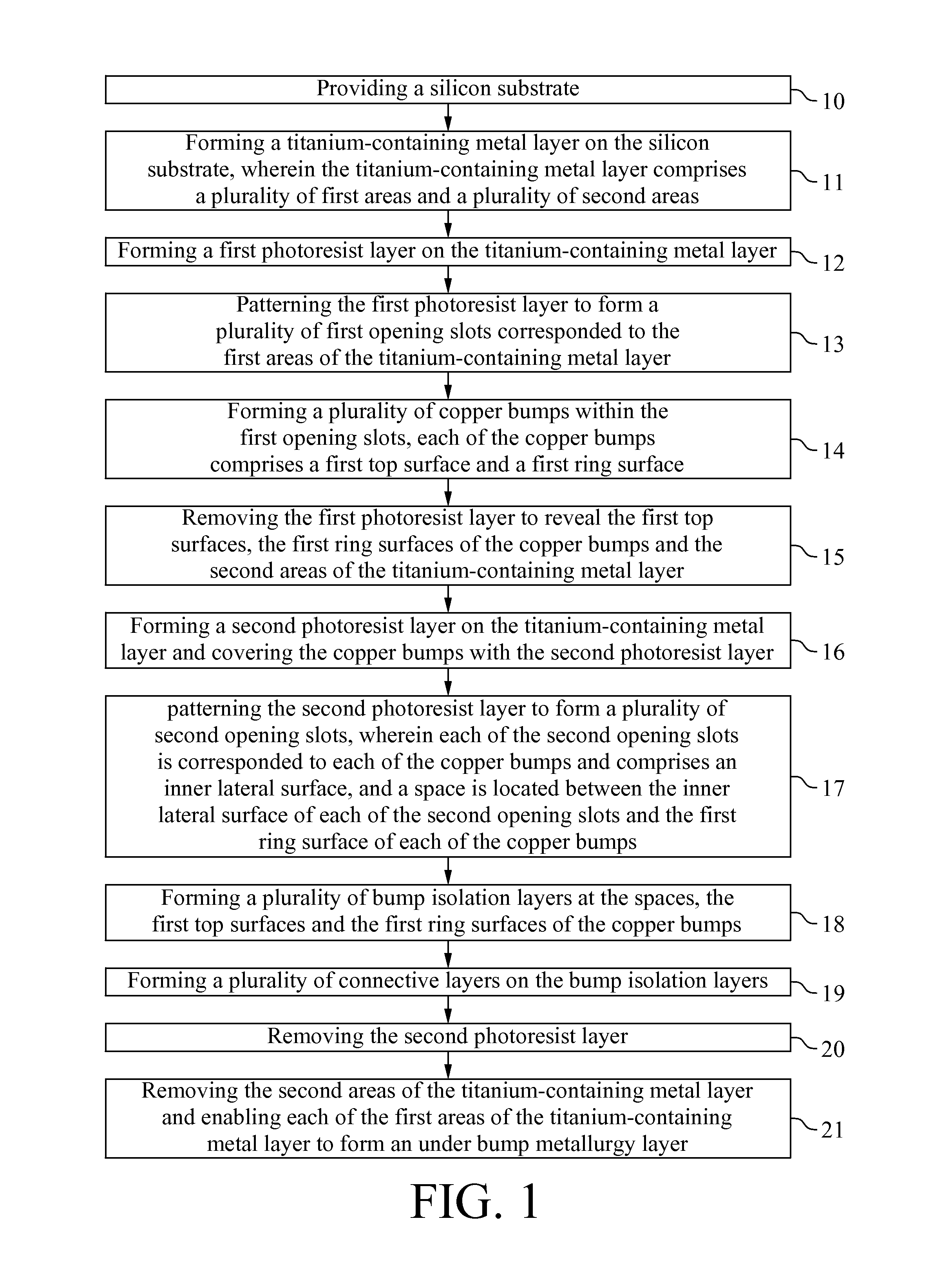

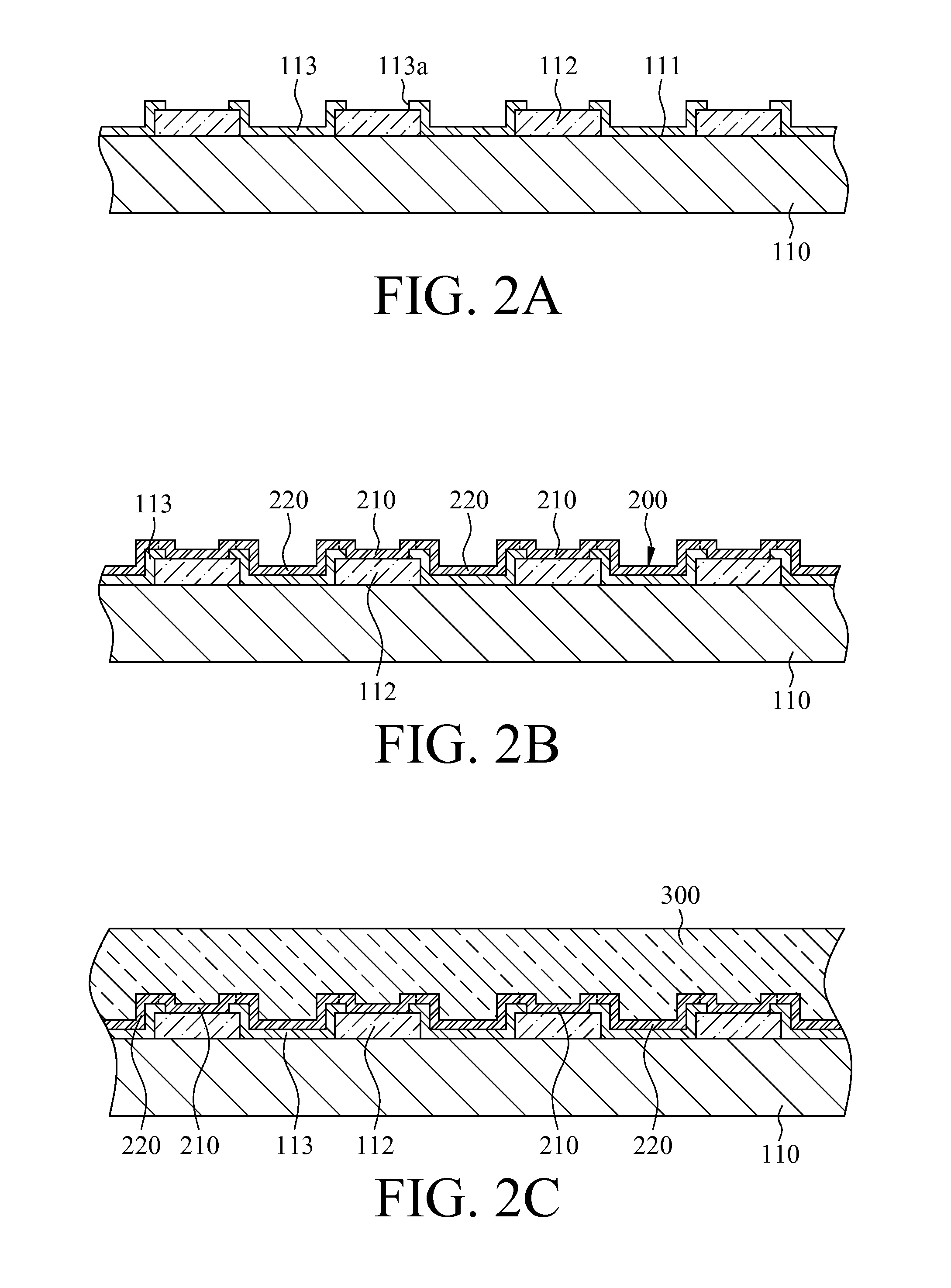

[0006]With reference to FIGS. 1 and 2A-2L, a bumping process in accordance with a preferred embodiment of the present invention comprises the steps described as followed. First, referring to step 10 of FIG. 1 and FIG. 2A, providing a silicon substrate 110 having a surface 111, a plurality of bond pads 112 disposed on said surface 111, and a protective layer 113 disposed on said surface 111, wherein the protective layer 113 comprises a plurality of openings 113a, and the bond pads 112 are revealed by the openings 113a. Next, with reference to step 11 of FIG. 1 and FIG. 2B, forming a titanium-containing metal layer 200 on the silicon substrate 110, said titanium-containing metal layer 200 covers the protective layer 113 and the bond pads 112, and said titanium-containing metal layer 200 comprises a plurality of first areas 210 and a plurality of second areas 220 located outside the first areas 210. Thereafter, referring to step 12 of FIG. 1 and FIG. 2C, forming a first photoresist lay...

PUM

| Property | Measurement | Unit |

|---|---|---|

| areas | aaaaa | aaaaa |

| circumference | aaaaa | aaaaa |

| outer circumference | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More