Patents

Literature

66 results about "Erasable programmable logic device" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An Erasable programmable logic device (EPLD) is an integrated circuit that comprises an array of programmable logic devices (PLD) that do not come pre-connected; the connections are programmed electrically by the user.

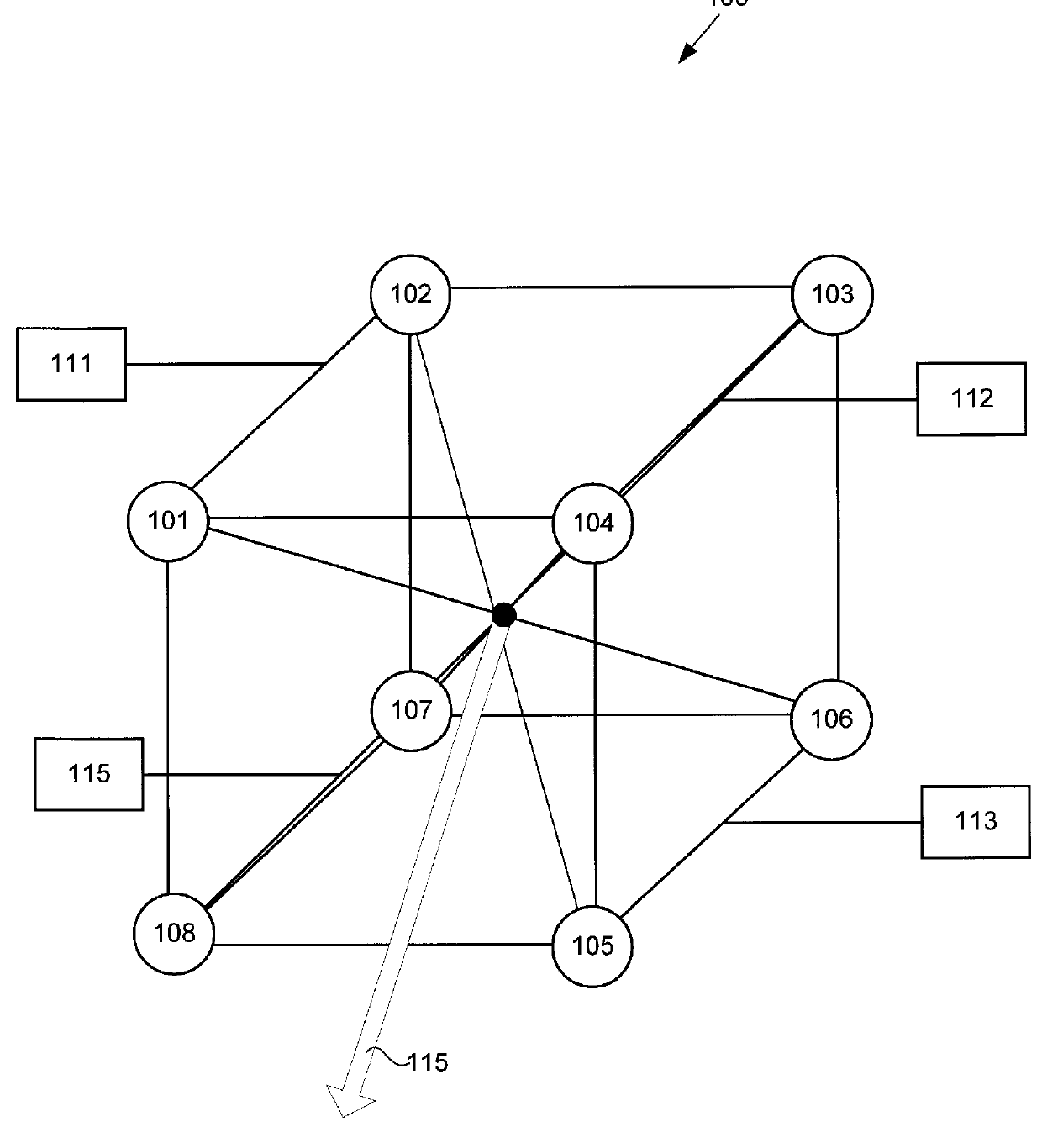

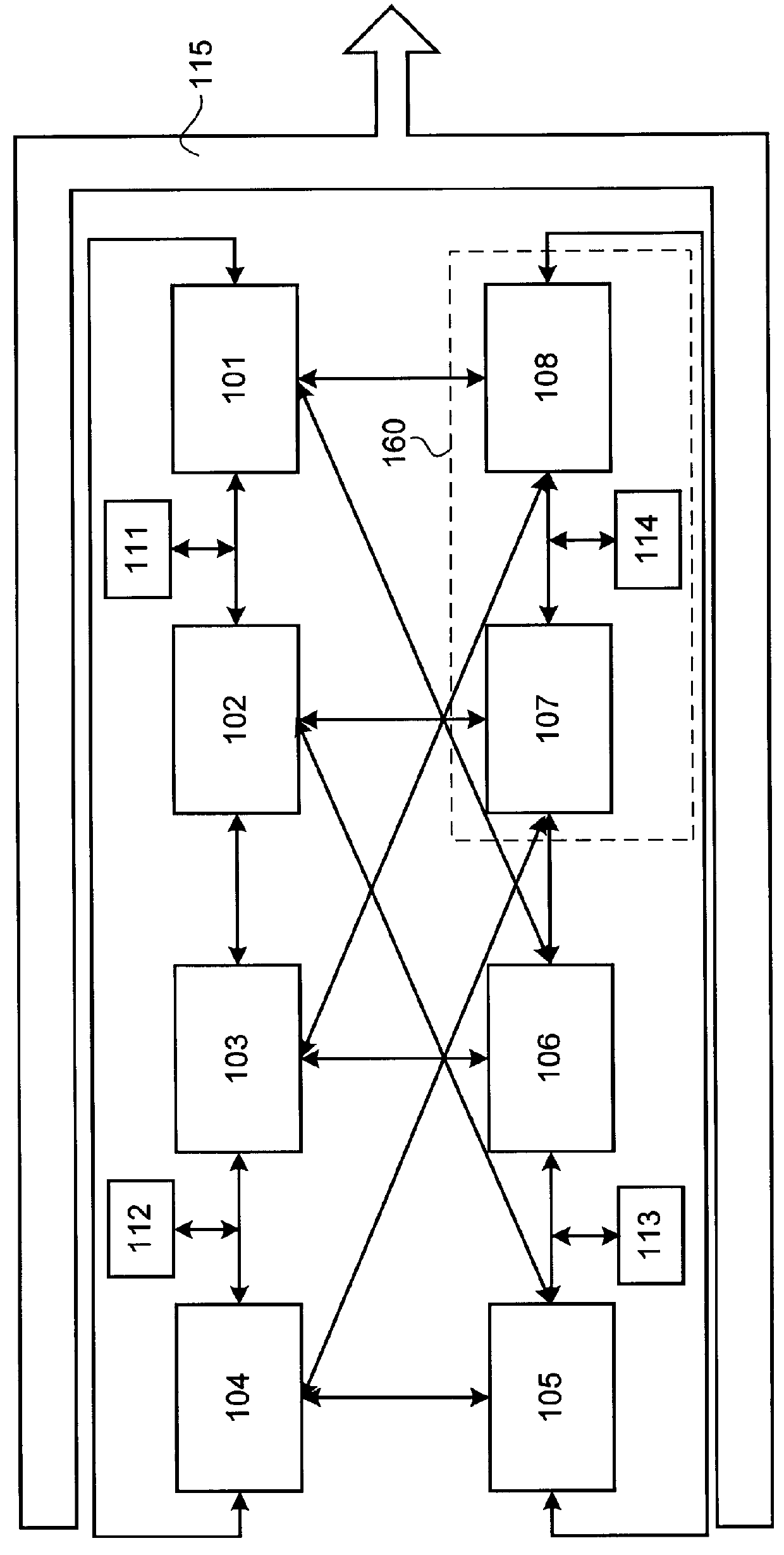

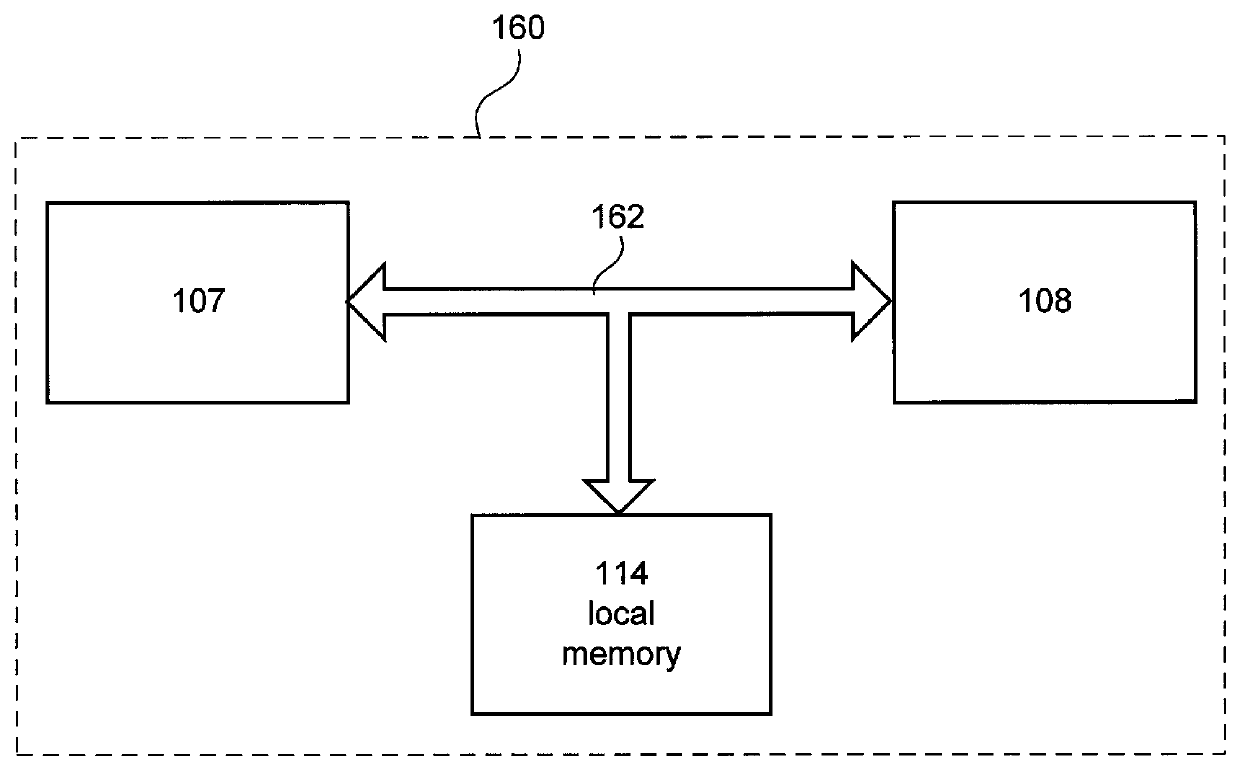

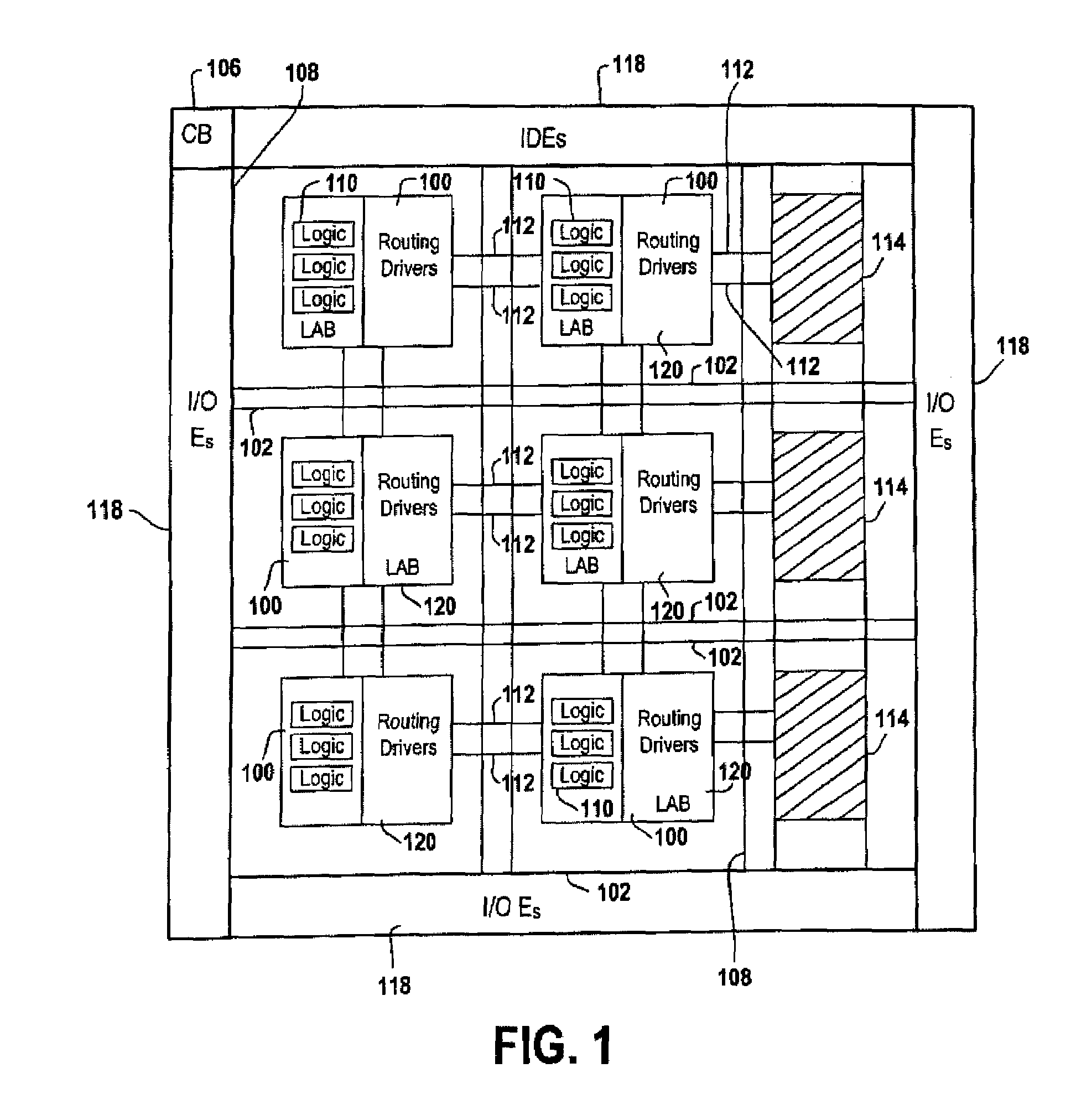

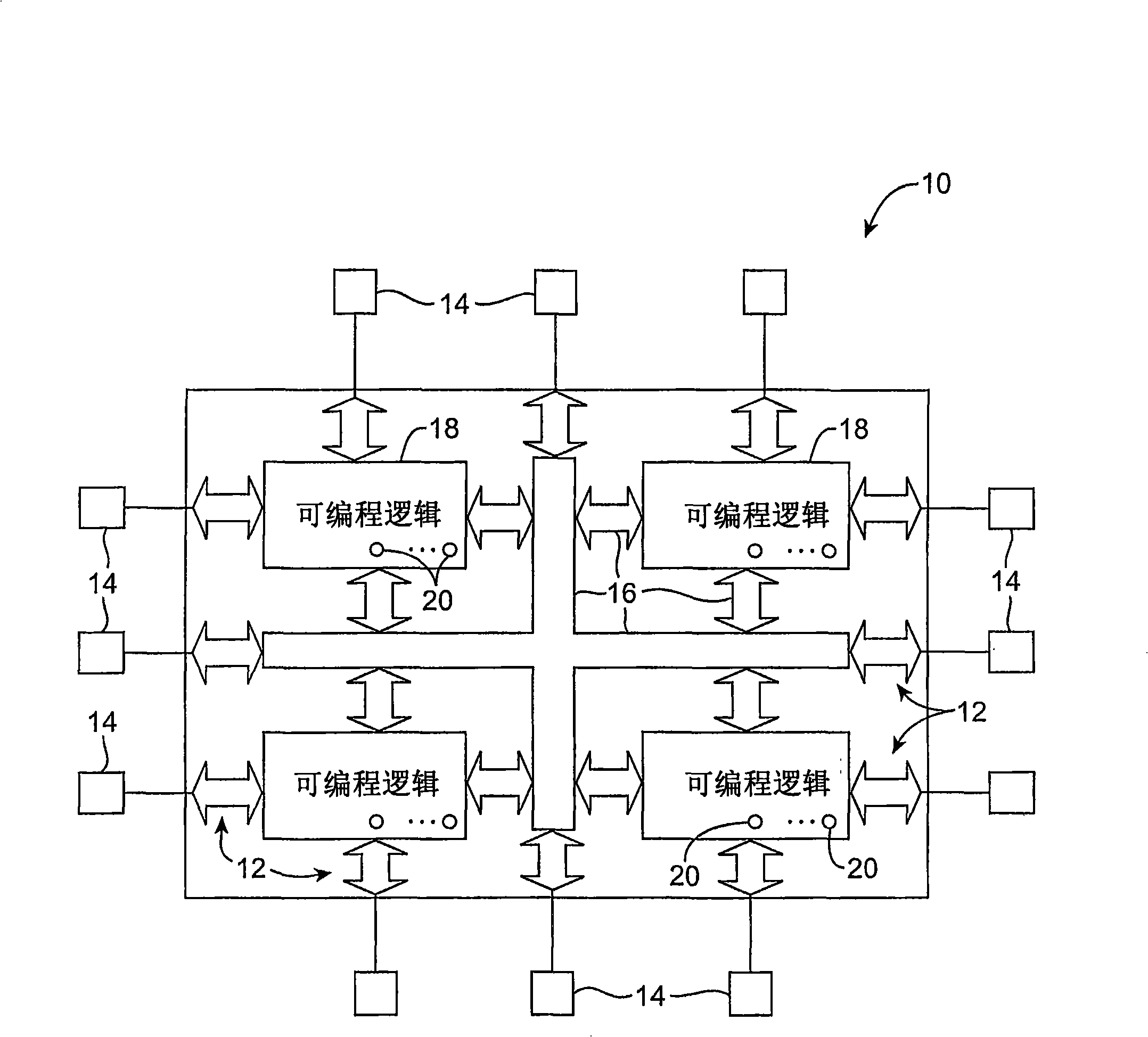

Reconfigurable computer architecture using programmable logic devices

A method and system for computing using reconfigurable computer architecture utilizing logic devices is disclosed. The computing may be accomplished by configuring a first programmable logic unit as a system controller. The system controller directs the implementation of an algorithm in a second one of the programmable logic units concurrently with reconfirguring a third one of the programmable logic units. In another aspect, the computing system may include a pair of independent, bi-directional busses each of which is arranged to electrically interconnect the system controller and the plurality of programmable logic devices. With this arrangement, a first bus may be used to reconfigure a selected one of the programmable logic devices as directed by the system controller while the second bus is used by an operational one of the programmable logic devices.

Owner:ALTERA CORP

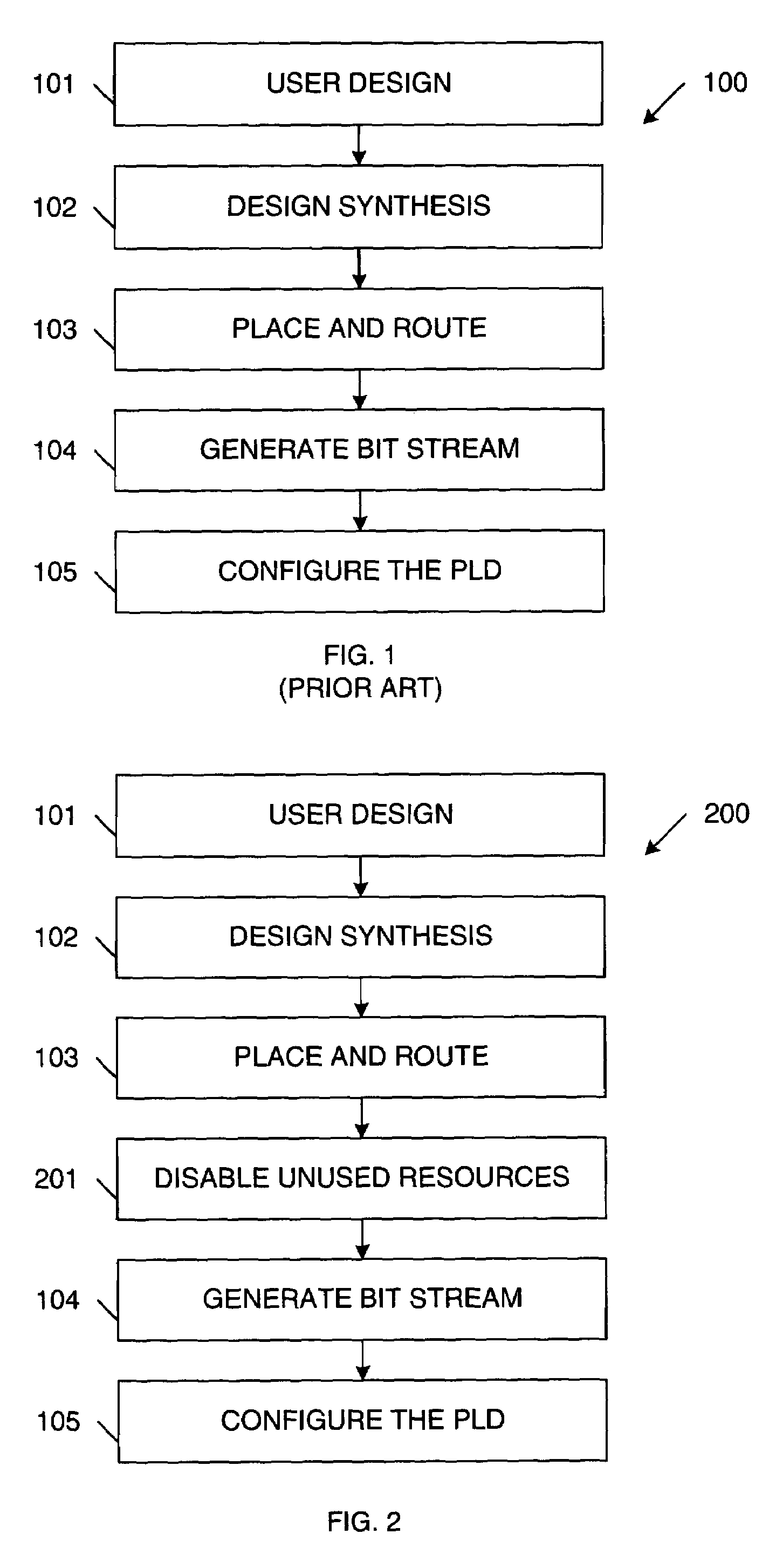

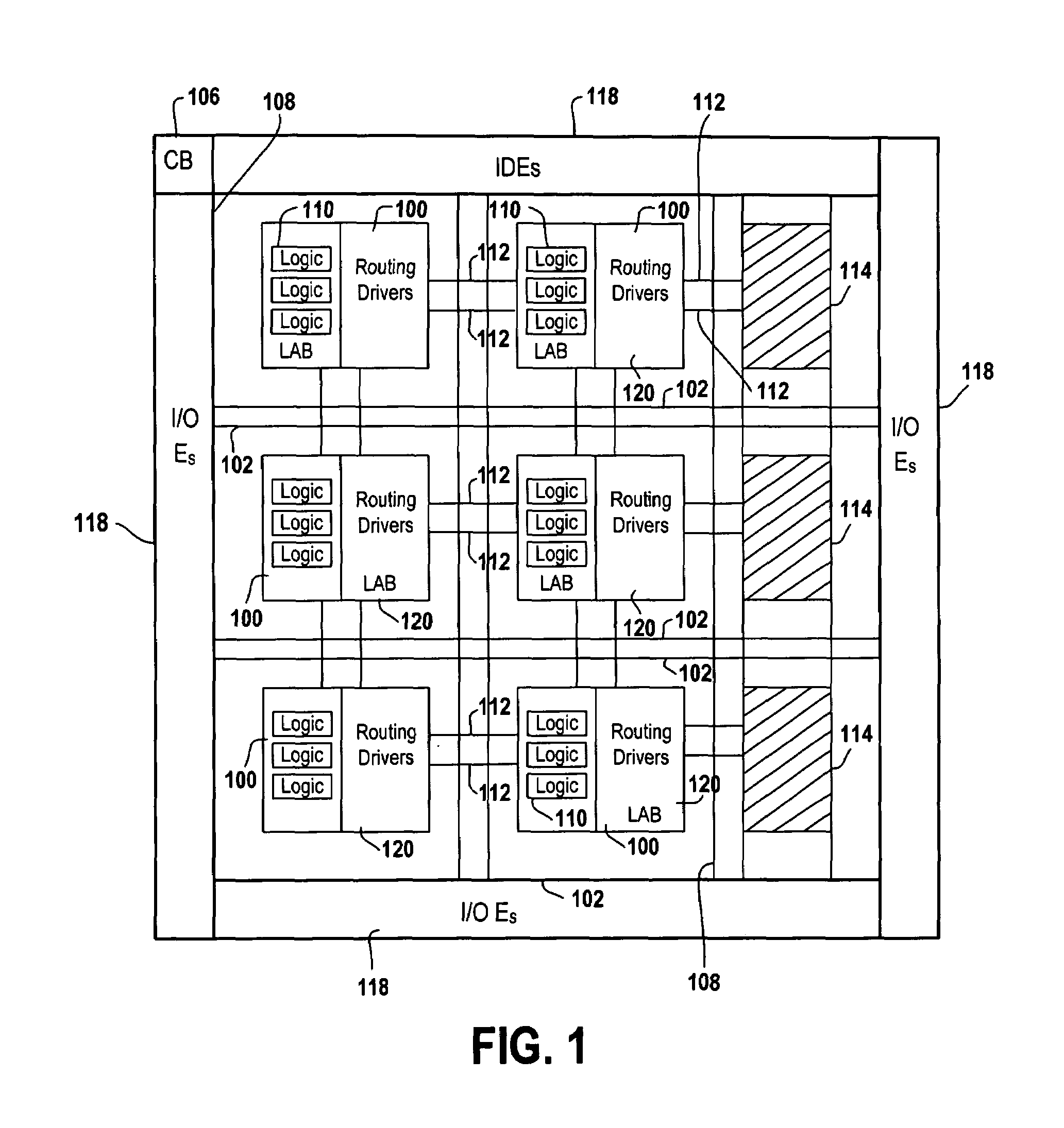

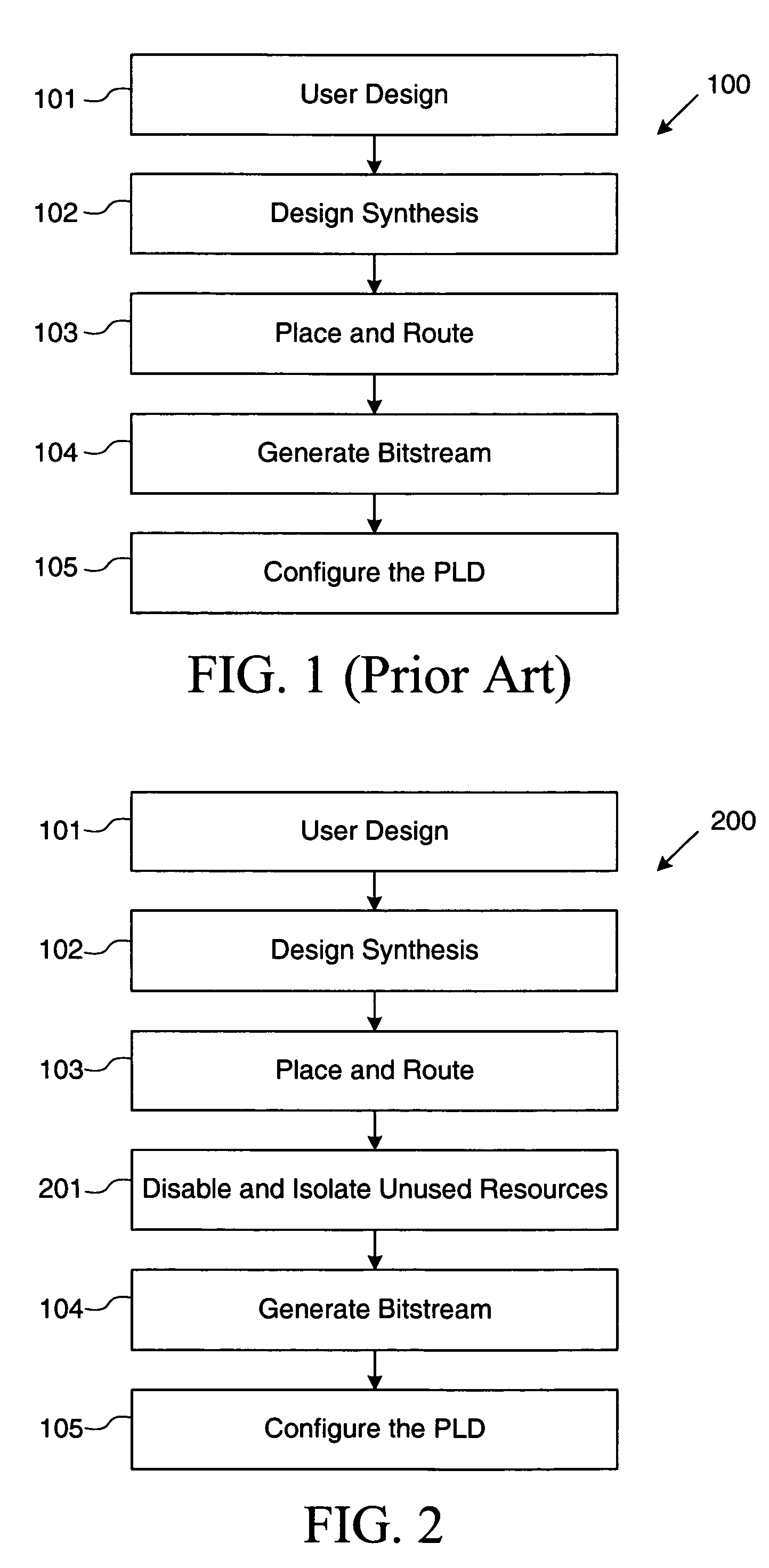

Disabling unused/inactive resources in programmable logic devices for static power reduction

ActiveUS7098689B1Reduce static power consumptionStatic storageLogic circuits using elementary logic circuit componentsProgrammable logic deviceErasable programmable logic device

A method of operating a programmable logic device, including the steps of enabling resources of the programmable logic device being used in a circuit design implemented by the programmable logic device, and disabling unused or inactive resources of the programmable logic device that are not being used in the circuit design. The step of disabling can include de-coupling the unused or inactive resources from one or more power supply terminals. Alternatively, the step of disabling can include regulating a supply voltage applied to the unused or inactive resources. The step of disabling can be performed in response to configuration data bits stored by the programmable logic device and / or in response to user controlled signals. The step of disabling can be initiated during design time and / or run time of the programmable logic device.

Owner:XILINX INC

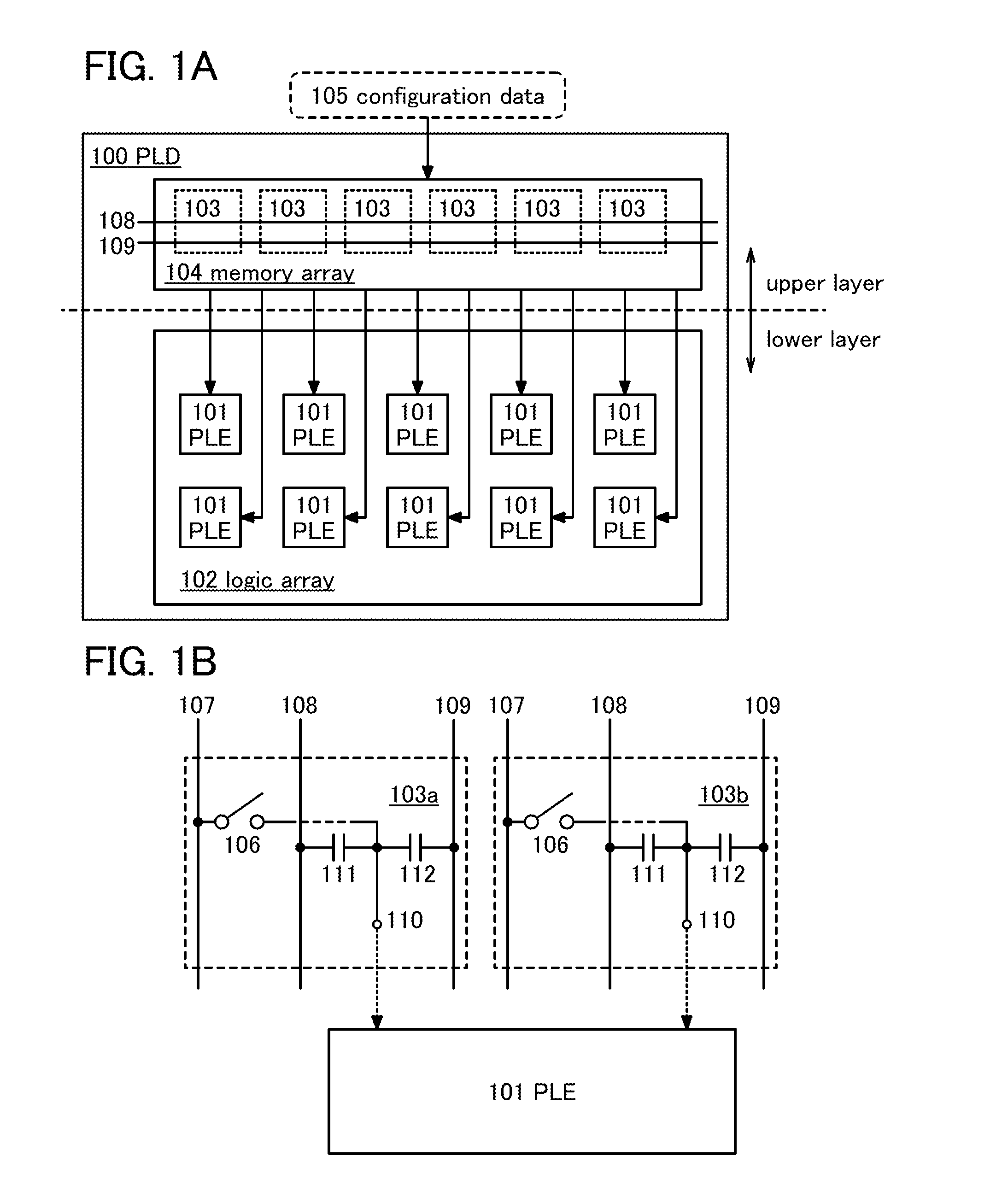

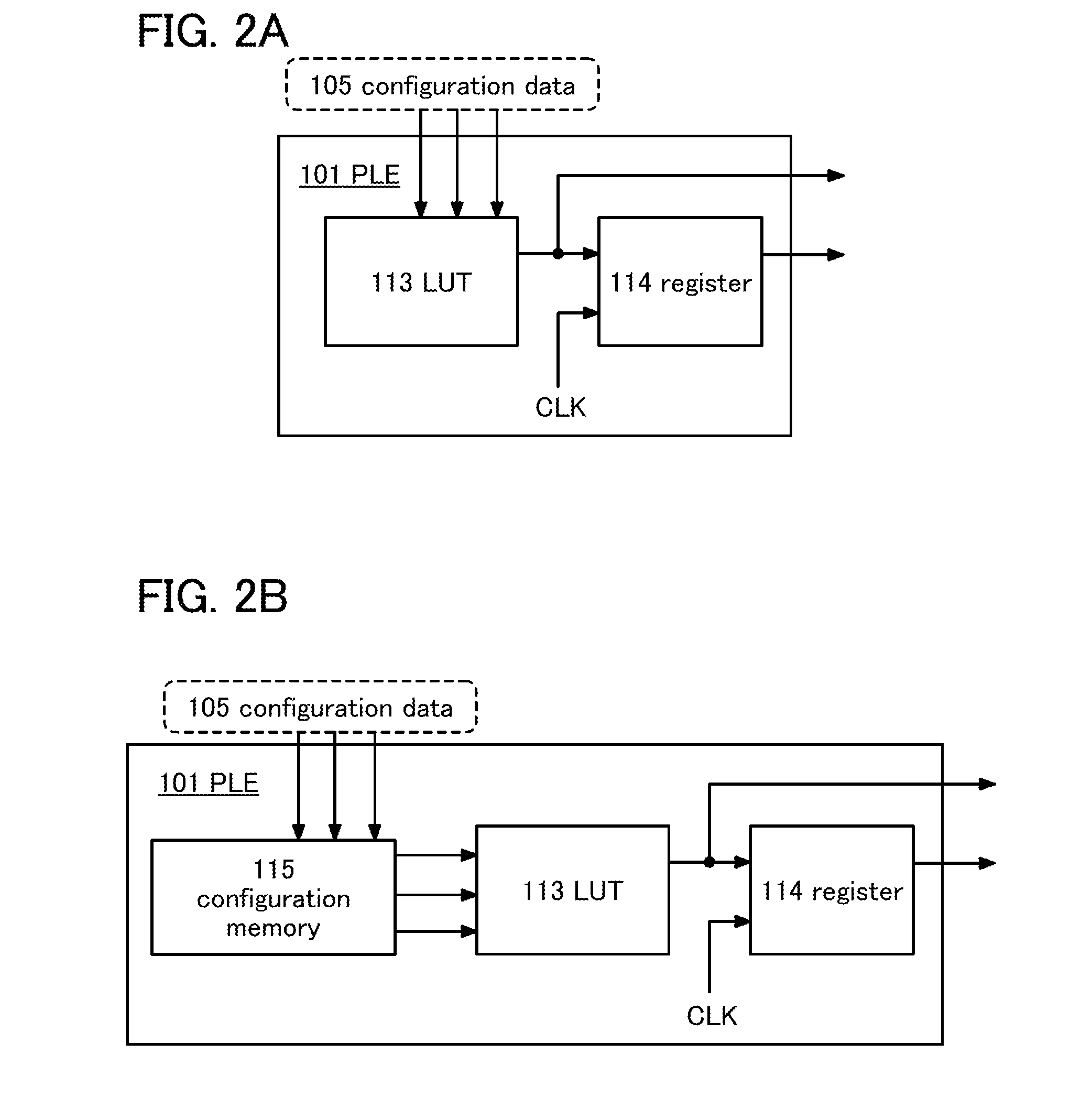

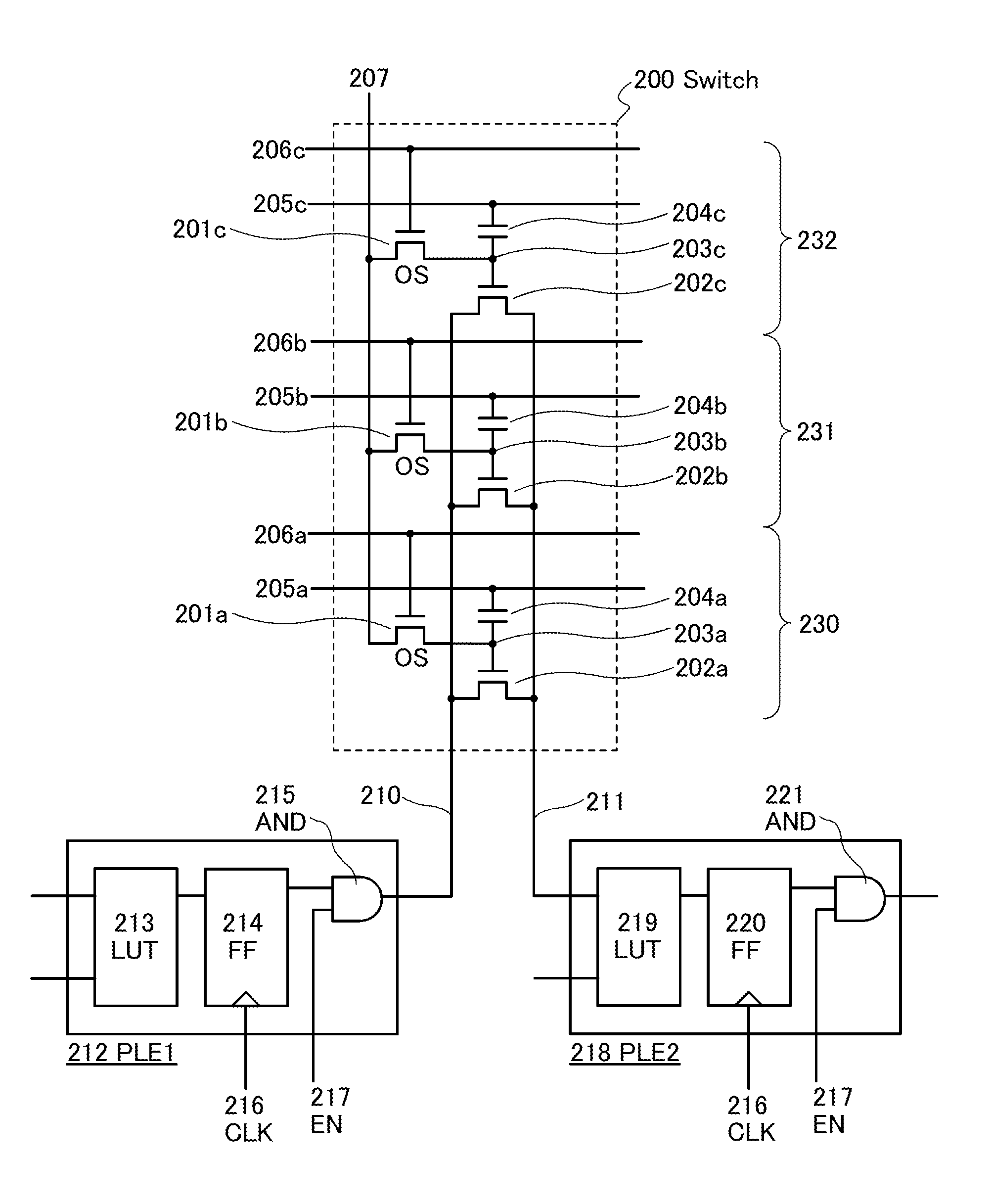

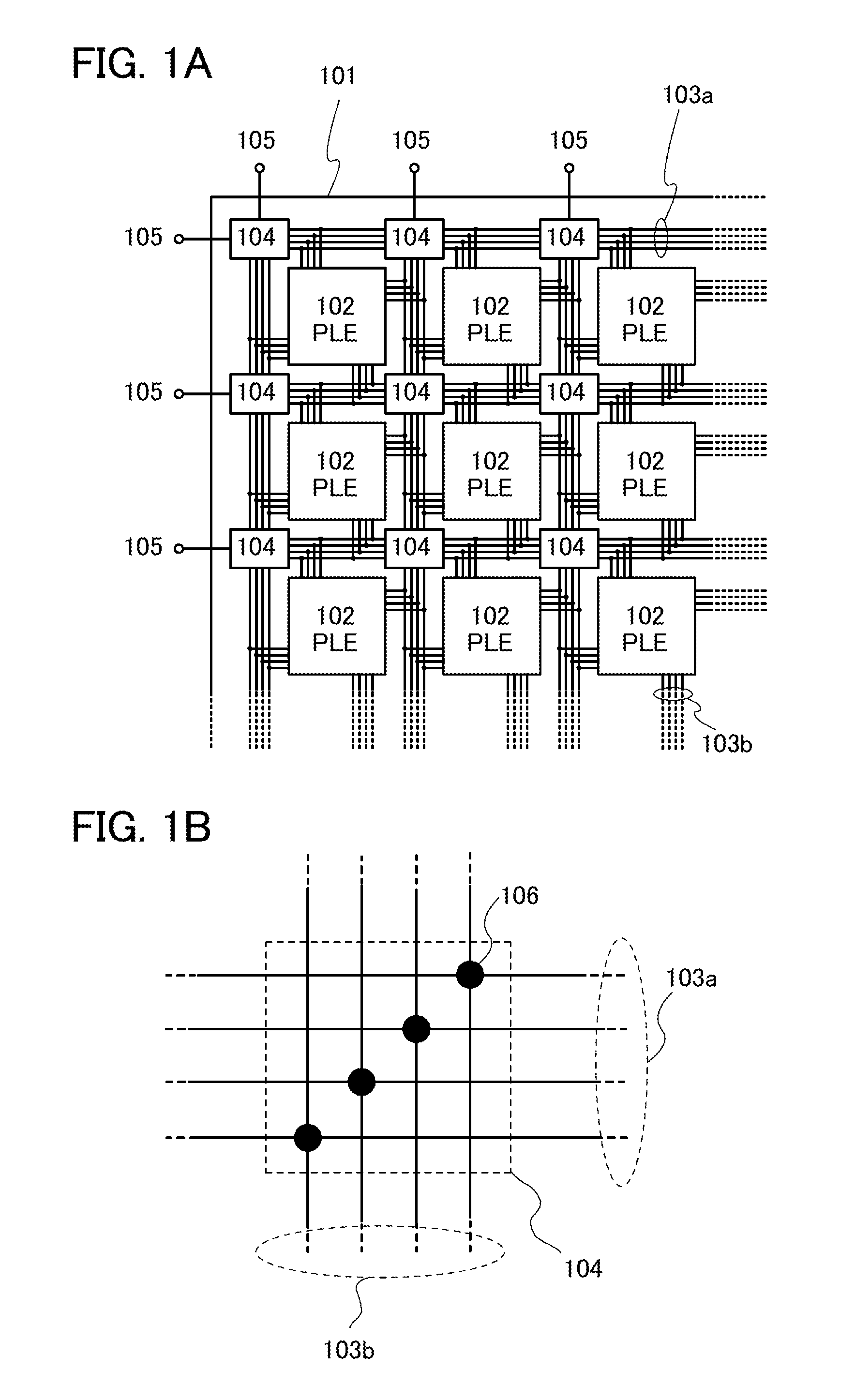

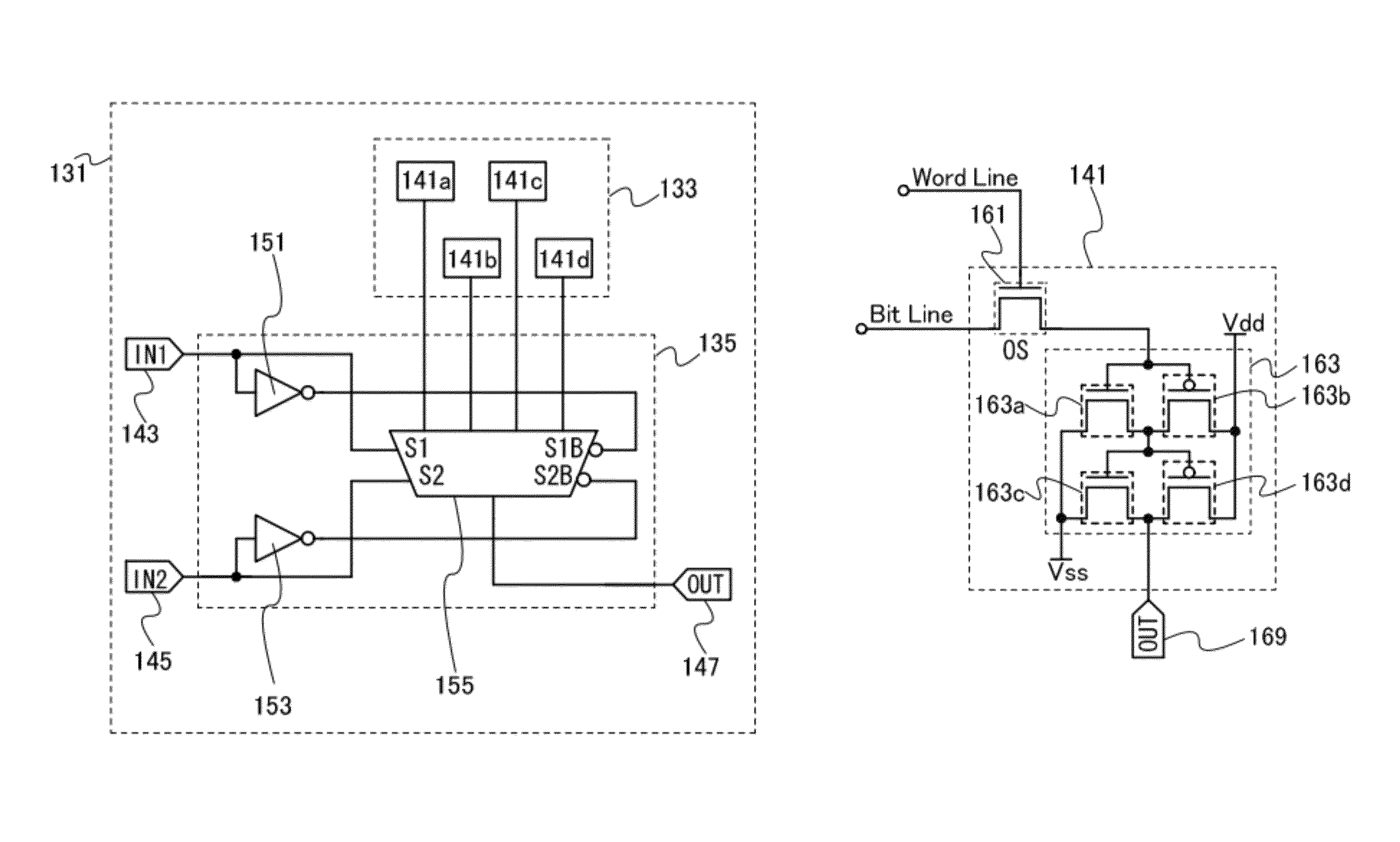

Programmable logic device and method for manufacturing semiconductor device

ActiveUS20130207170A1Reduce in quantityAccurate estimateTransistorPower consumption reductionCapacitanceProgrammable logic device

To provide a programmable logic device in which the number of elements per bit in a memory array can be reduced and with which power consumption or operation frequency can be estimated accurately at a testing stage. Provided is a programmable logic device including a plurality of programmable logic elements and a memory array which stores configuration data that determines logic operation executed in the plurality of programmable logic elements. The memory array includes a plurality of memory elements. The memory element includes a node which establishes electrical connection between the programmable logic element and the memory array, a switch for supplying charge whose amount is determined by the configuration data to the node, holding the charge in the node, or releasing the charge from the node, and a plurality of wirings. Capacitance is formed between the node and the wiring.

Owner:SEMICON ENERGY LAB CO LTD

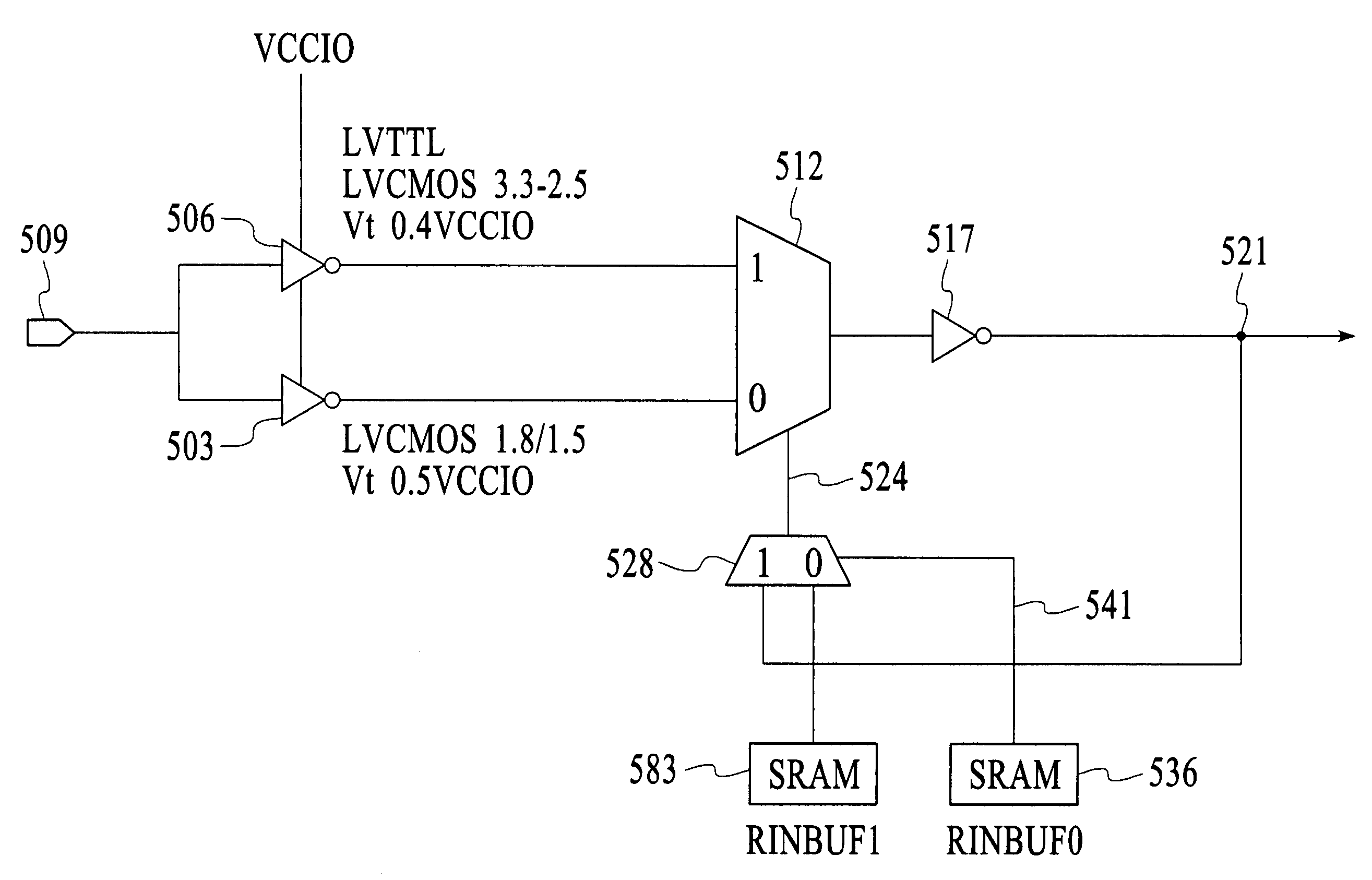

Input buffer with selectable threshold and hysteresis option

InactiveUS7023238B1Sufficient hysteresisWiden the optionsElectric pulse generatorLogic circuits using elementary logic circuit componentsHysteresisSchmitt trigger

An input buffer is configurable for use as a standard buffer with a single switching threshold, selectable to be one of at least two different switching thresholds, or used as a Schmitt trigger circuit with hysteresis, which uses at least two switching thresholds from among the at least two different switching thresholds. The integrated circuit may be a programmable logic device (PLD) or field programmable gate array (FPGA), but in other embodiments, the integrated circuit may be other types of devices such a microprocessors, ASICs, or memories.

Owner:ALTERA CORP

Data modem

InactiveUS6839792B2Maximum flexibilityMinimal costTelephonic communicationGenerating/distributing signalsMass storageModem device

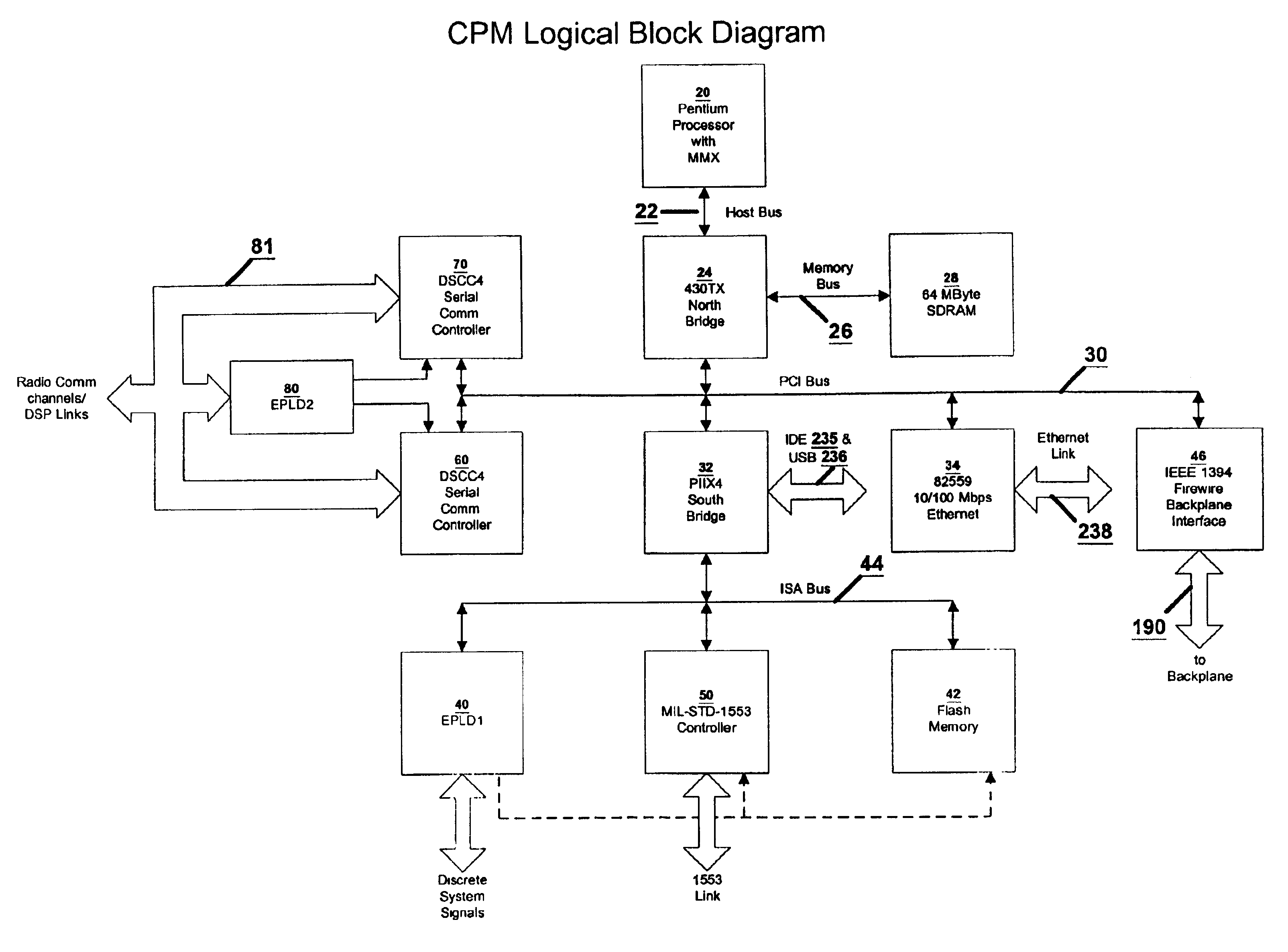

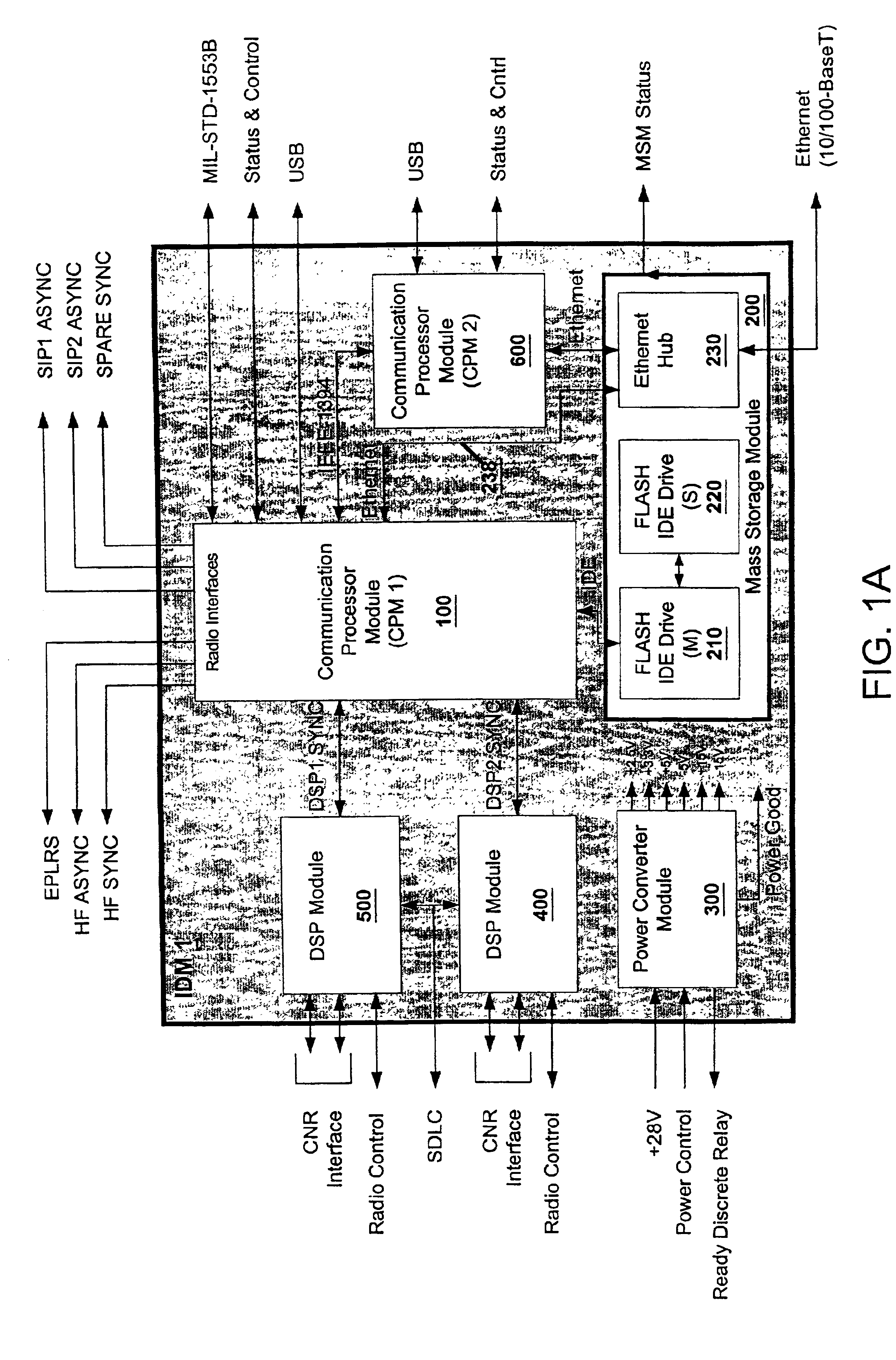

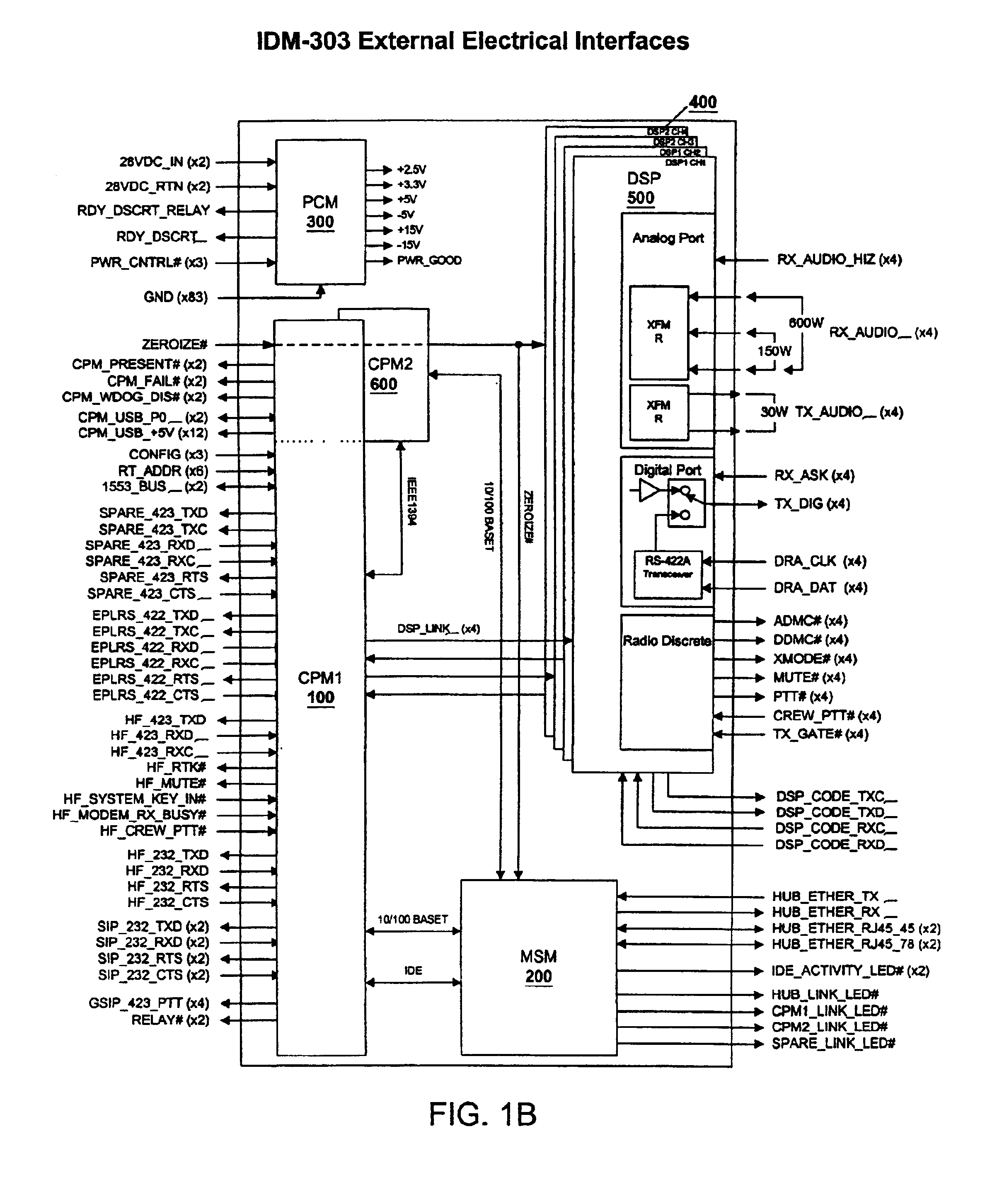

An improved data modem (IDM) and method includes a communication processor module, a mass storage module, a power converter module, and one or more DSP modules. The communication processor module utilizes commercial off-the-shelf components as well as programmable logic devices (EPLD), which are programmed to provide a watchdog timer, programmable interrupt controller, flash page addressing, ISA bus decoder and controller, and various circuits and logic.

Owner:ELBIT SYSTEMS OF AMERICA LLC

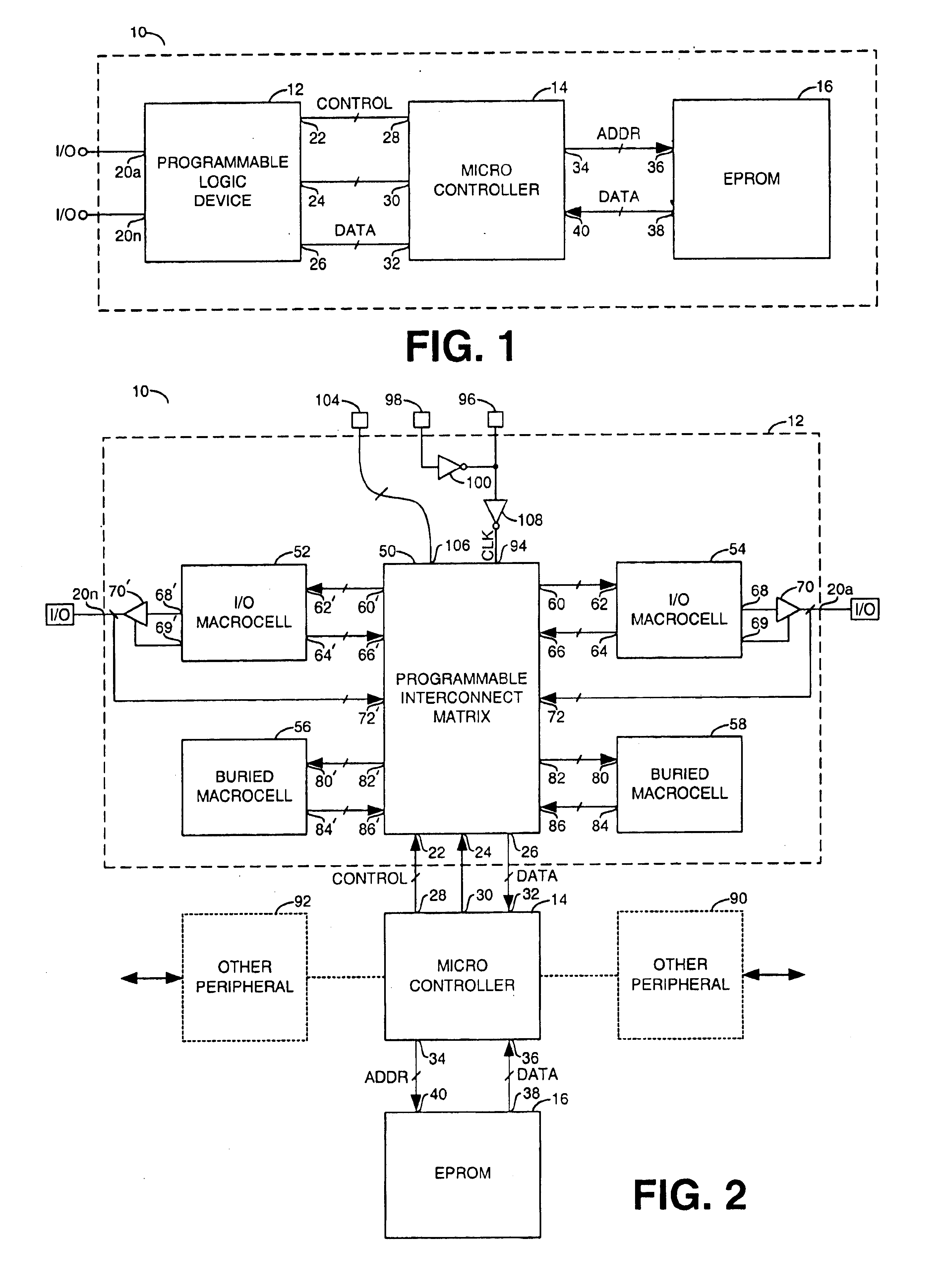

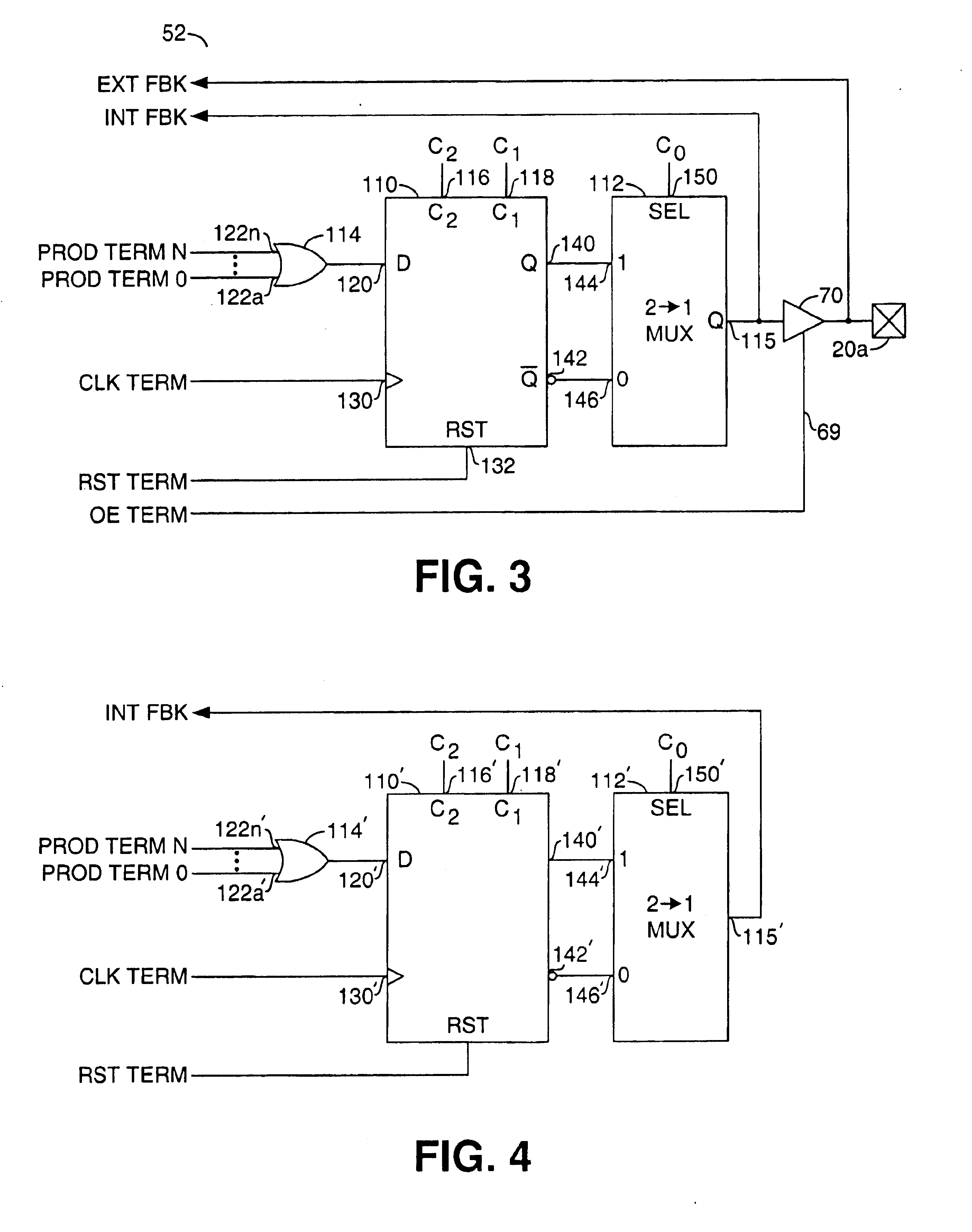

Microcontroller with programmable logic on a single chip

InactiveUS6898101B1Static storageArchitecture with single central processing unitMicrocontrollerErasable programmable logic device

A programmable logic device, a memory device and a microcontroller manufactured on a single integrated circuit chip. In one example, the programmable logic device may comprise one or more macrocells each comprising an input / output macrocell or a buried macrocell. In another example, the programmable logic device may be a complex programmable logic device (CPLD) or a programmable logic array (PLA).

Owner:MONTEREY RES LLC

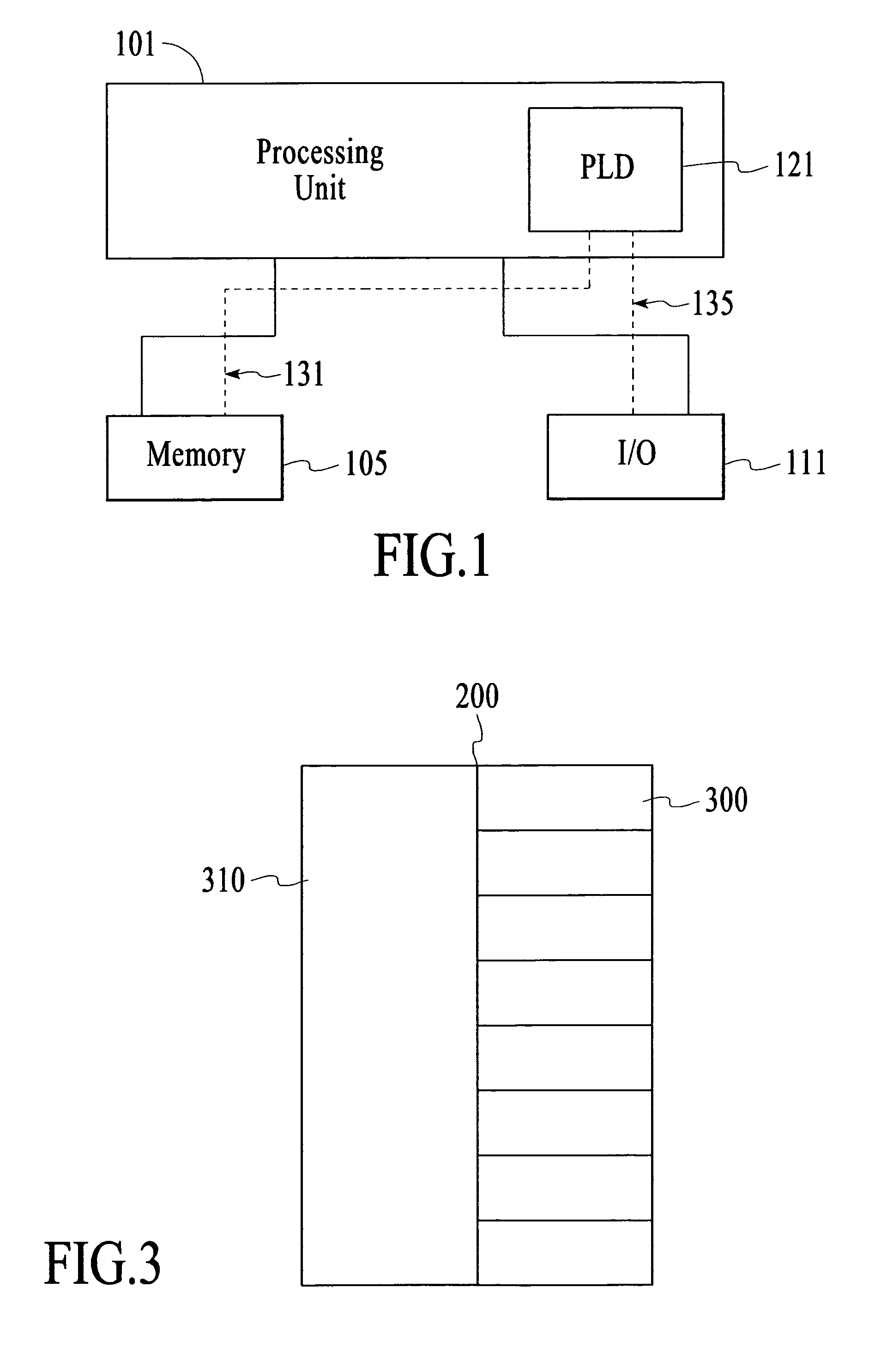

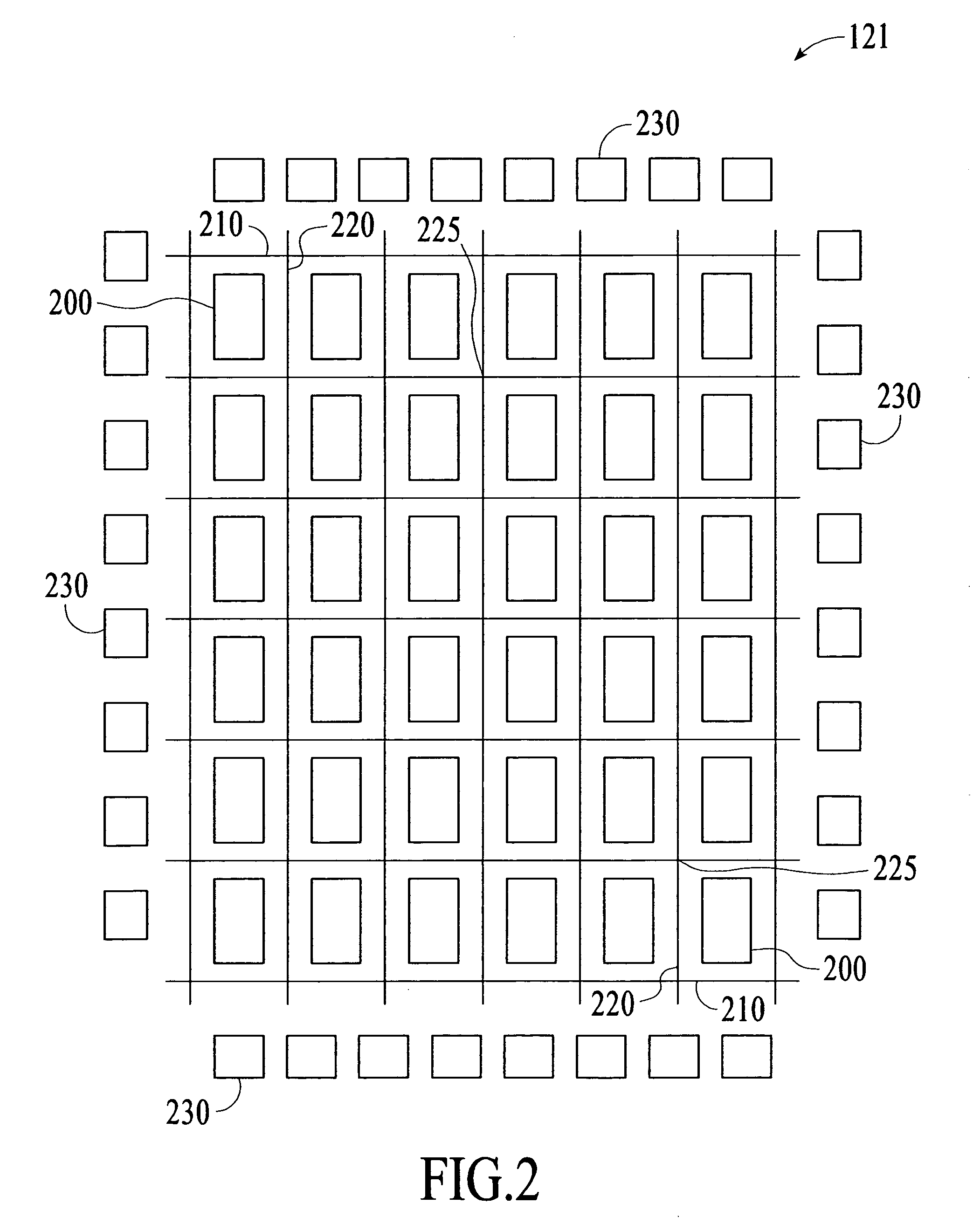

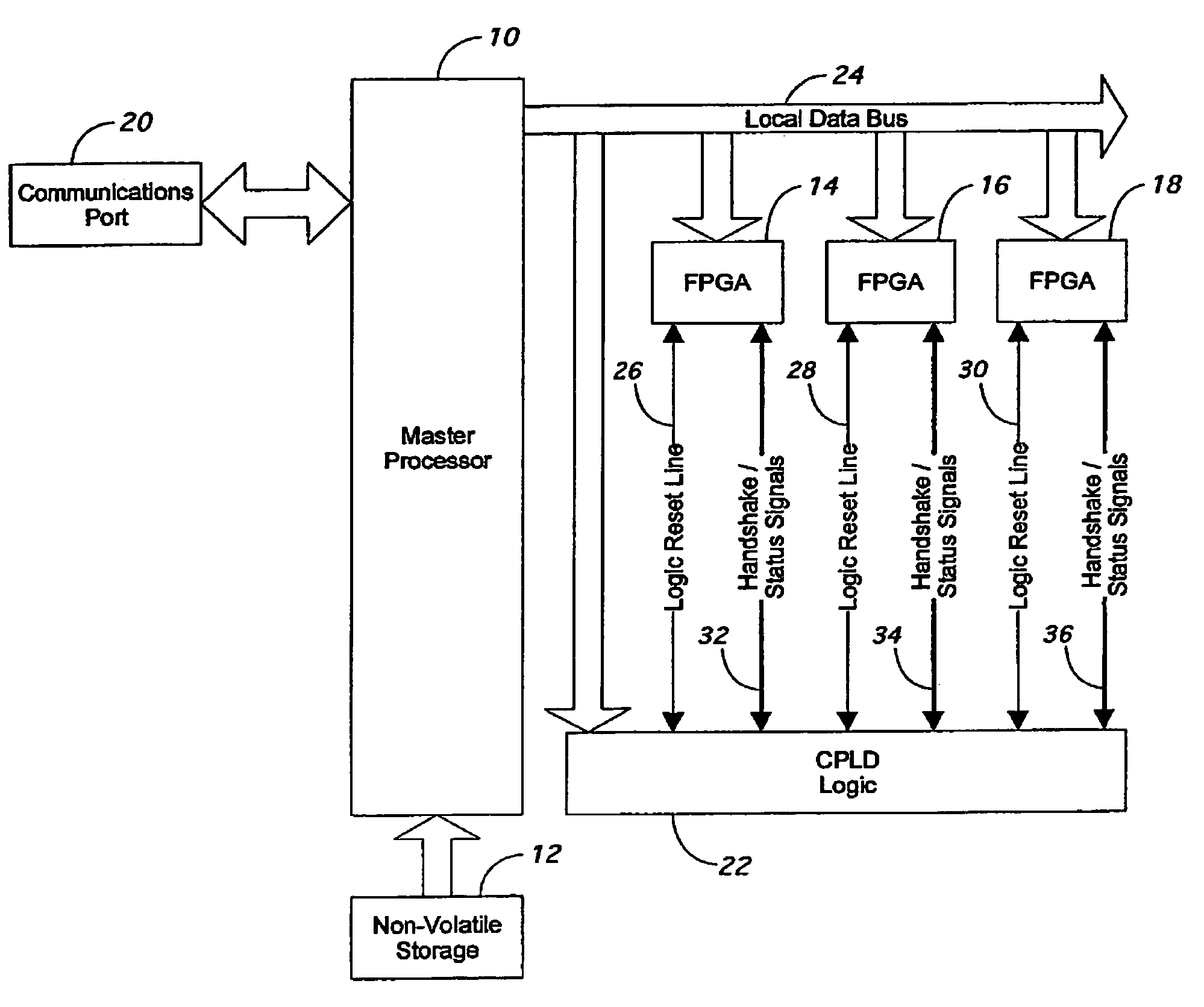

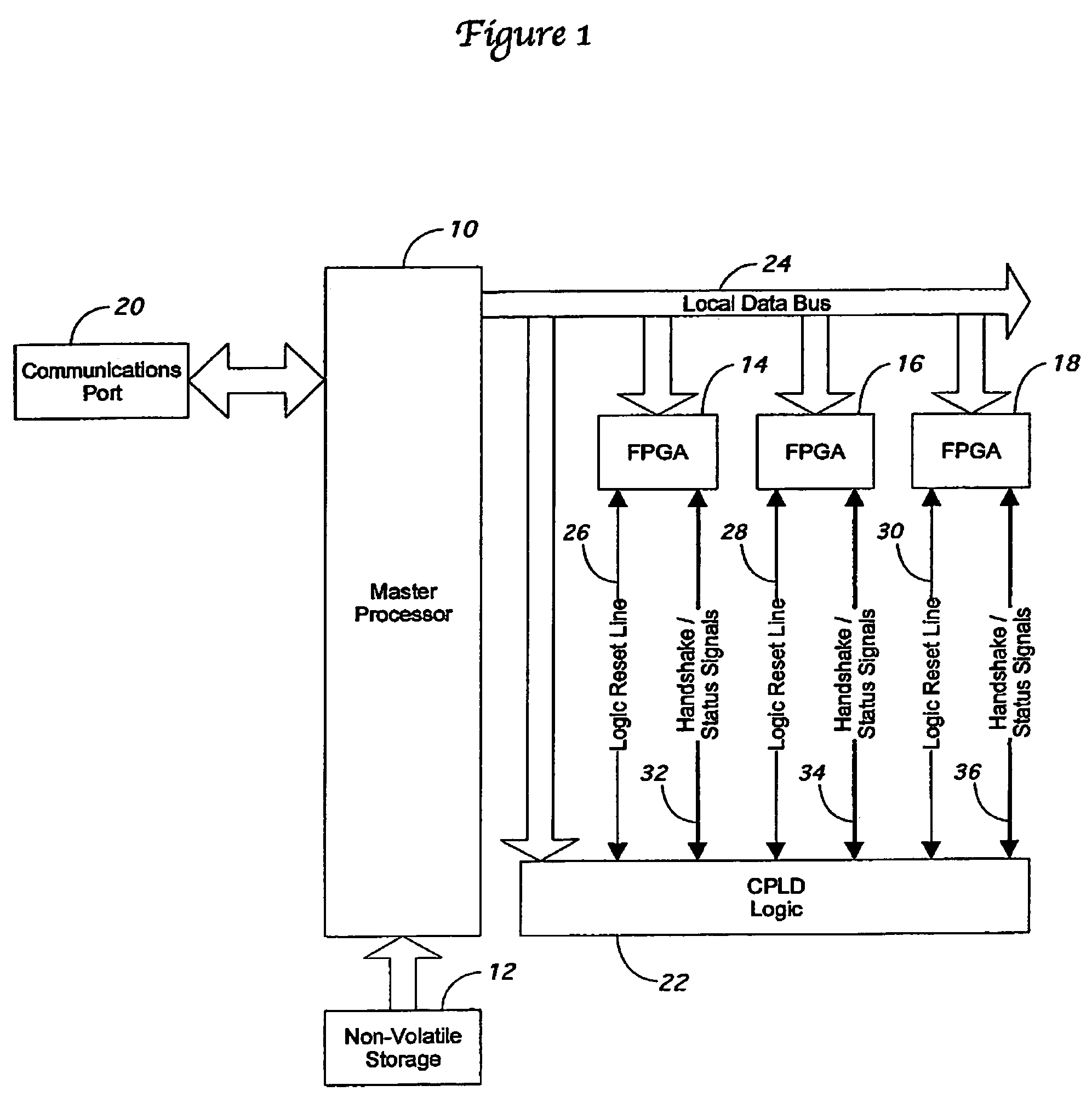

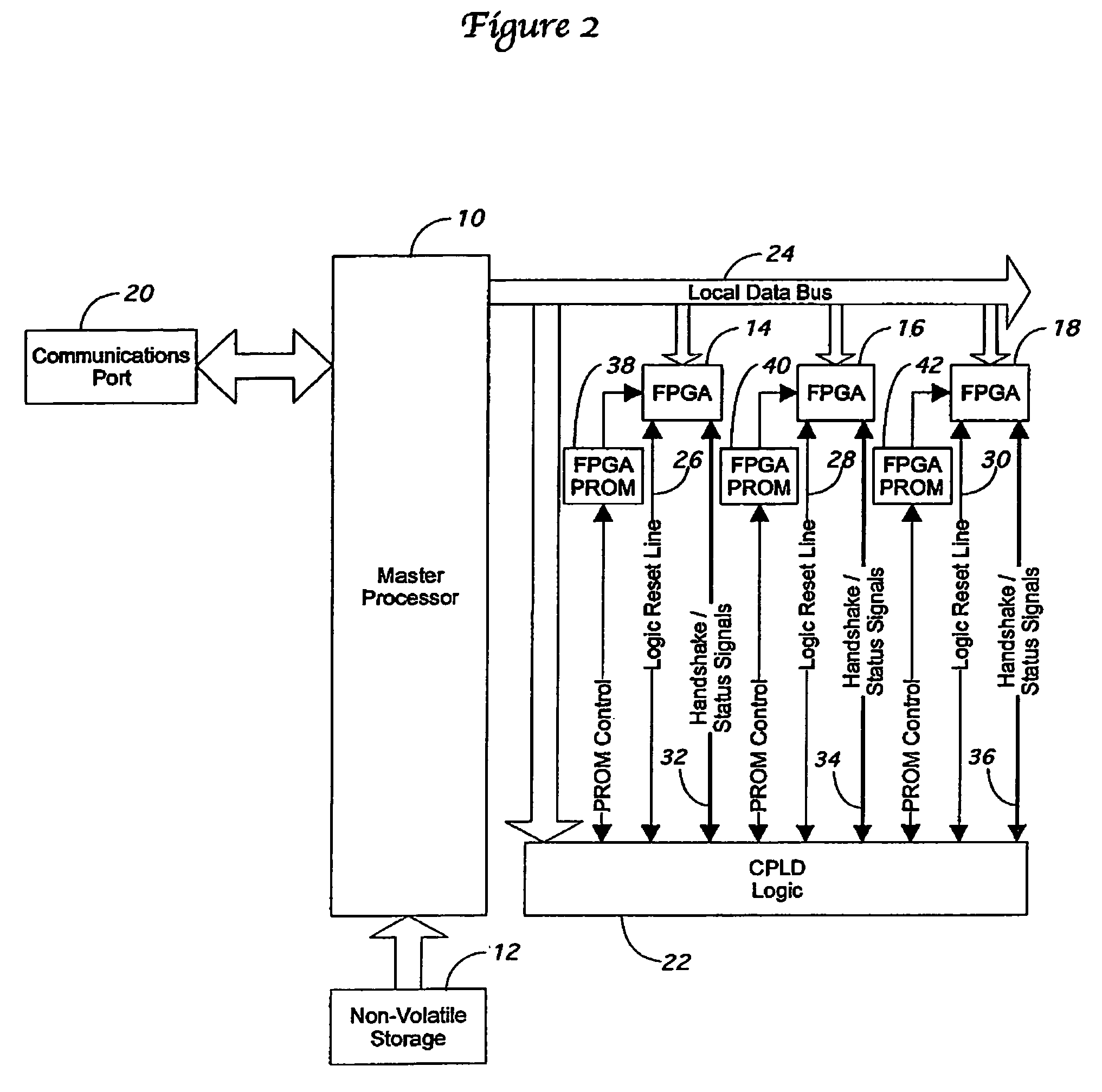

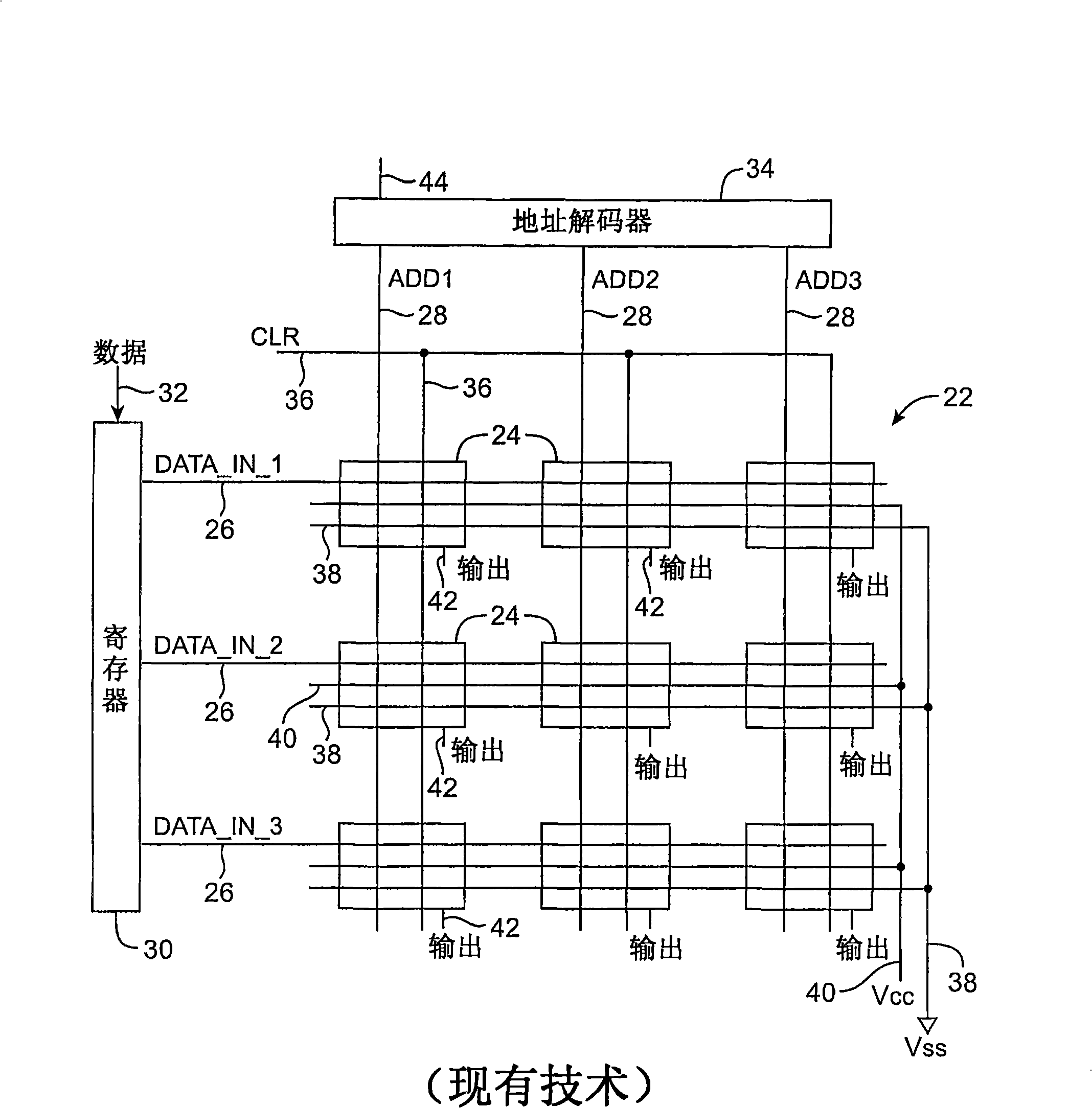

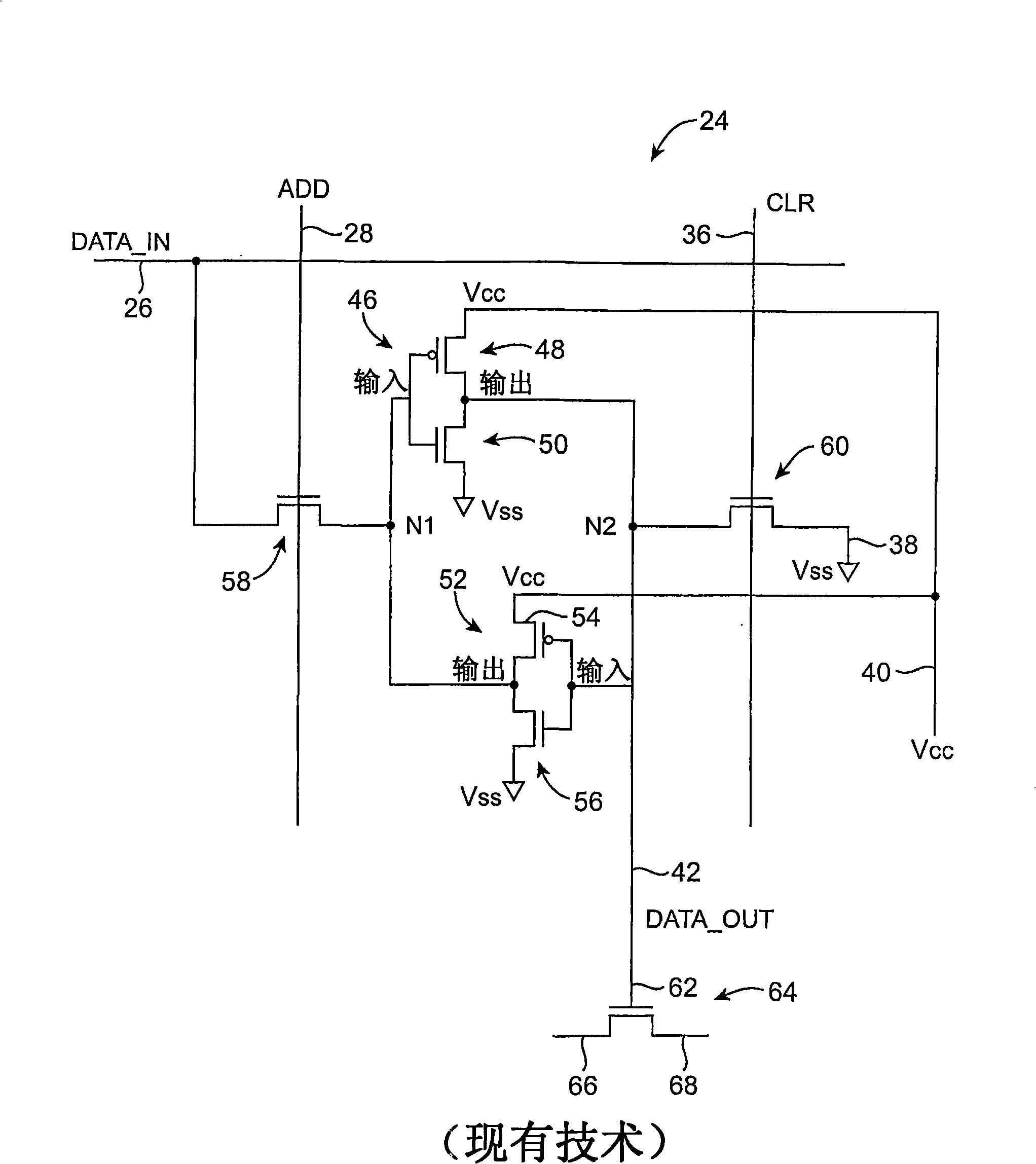

Method and apparatus for configuring a programmable logic device

InactiveUS7146598B2Minimal numberDrain can be reducedElectronic circuit testingData resettingProgrammable logic deviceErasable programmable logic device

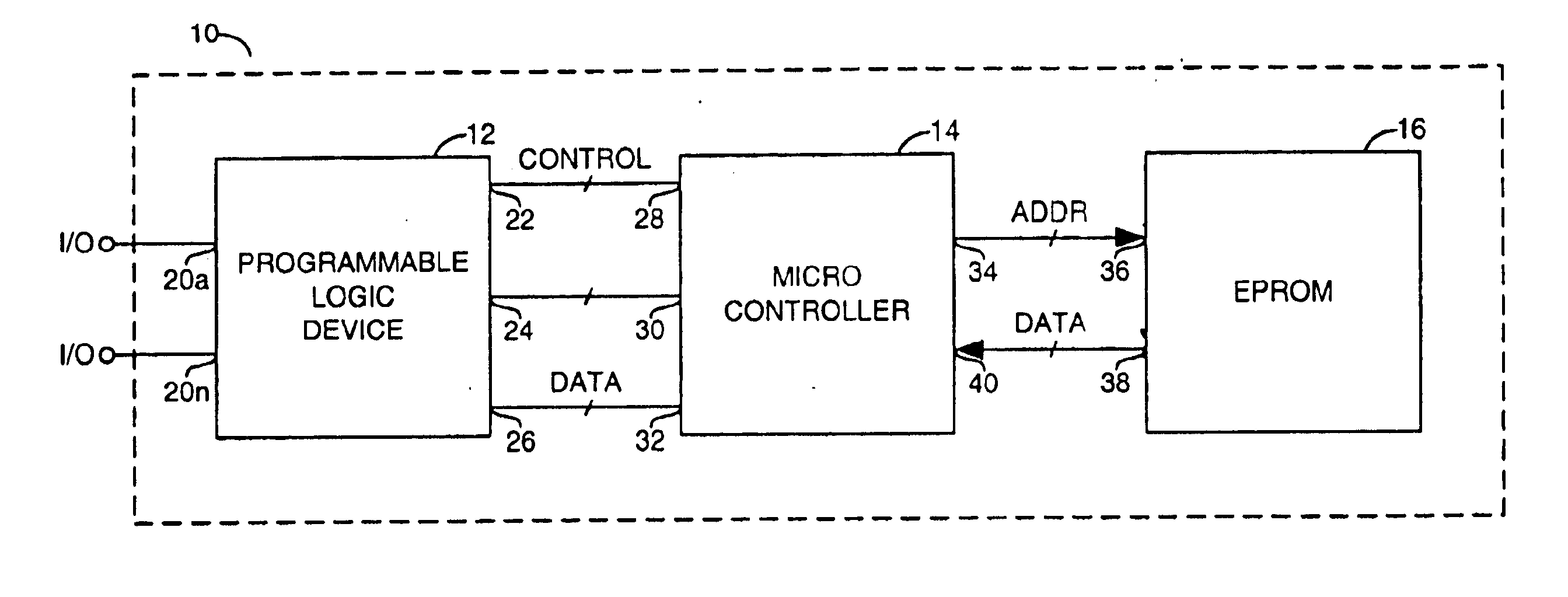

A method and apparatus for configuring multiple first programmable logic devices from a single memory includes a microprocessor, and a second programmable logic device containing the interface logic for the first programmable device and the microprocessor. The present invention allows multiple FPGAs to be programmed from a single memory structure under the control of the microprocessor thereby using fewer components than systems dedicating a separate memory to each FPGA. A communications port allows new configurations to be downloaded to the microprocessor memory. In addition, the present invention can be used in combination with standard systems with each FPGA having its own memory, with the microprocessor being able to select between the central microprocessor memory and the local memory for programming each FPGA.

Owner:MCDATA SERVICES CORP +1

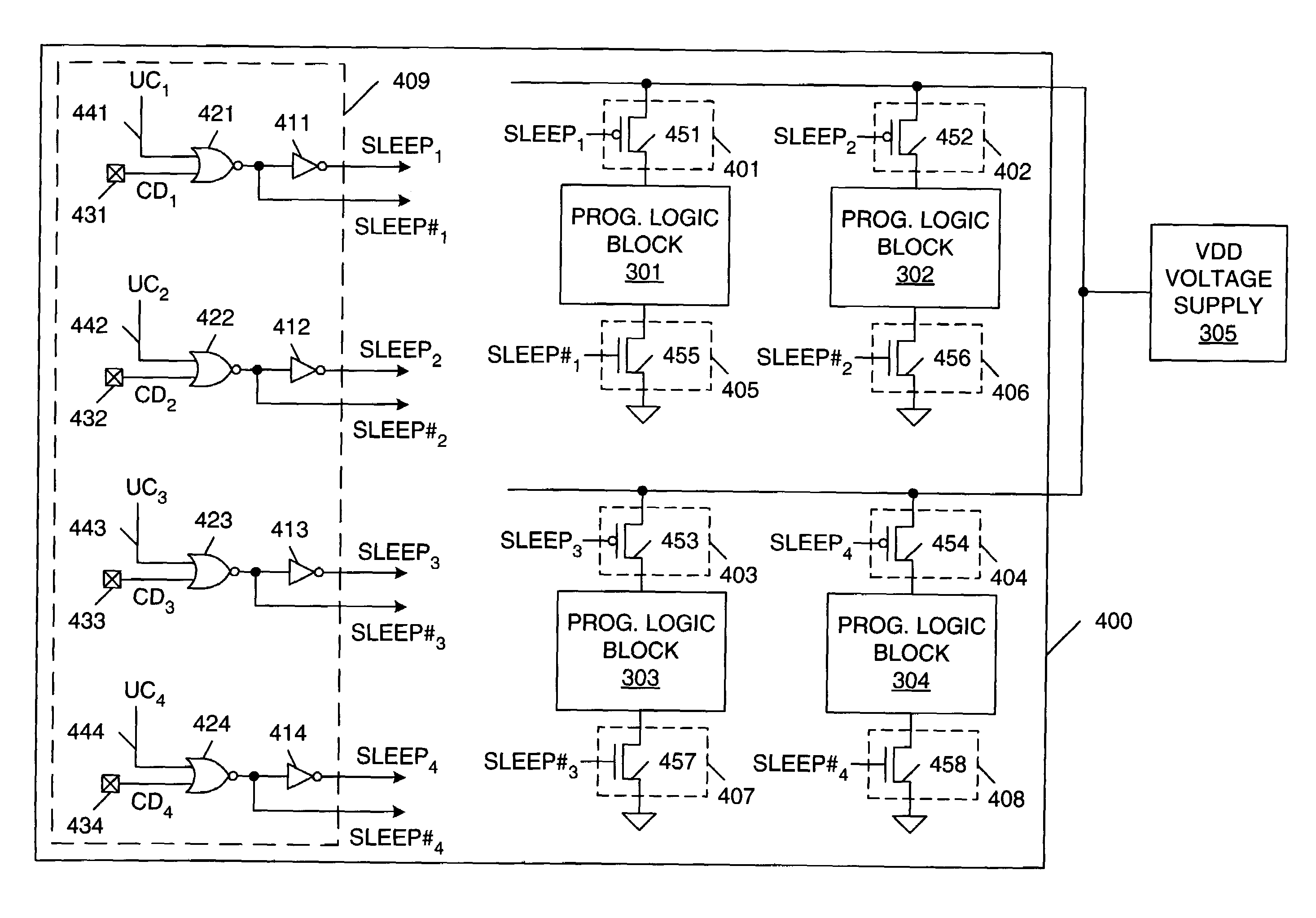

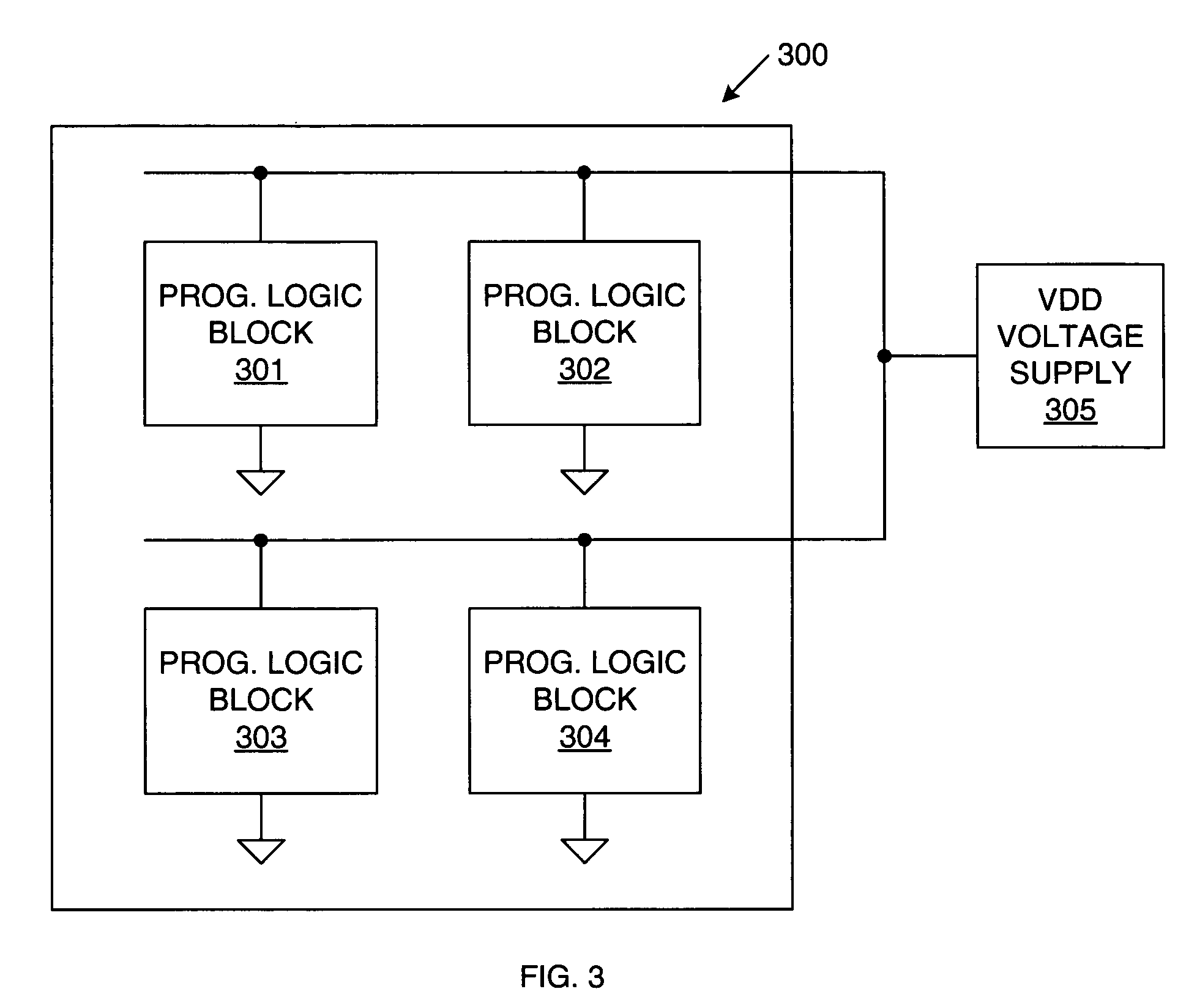

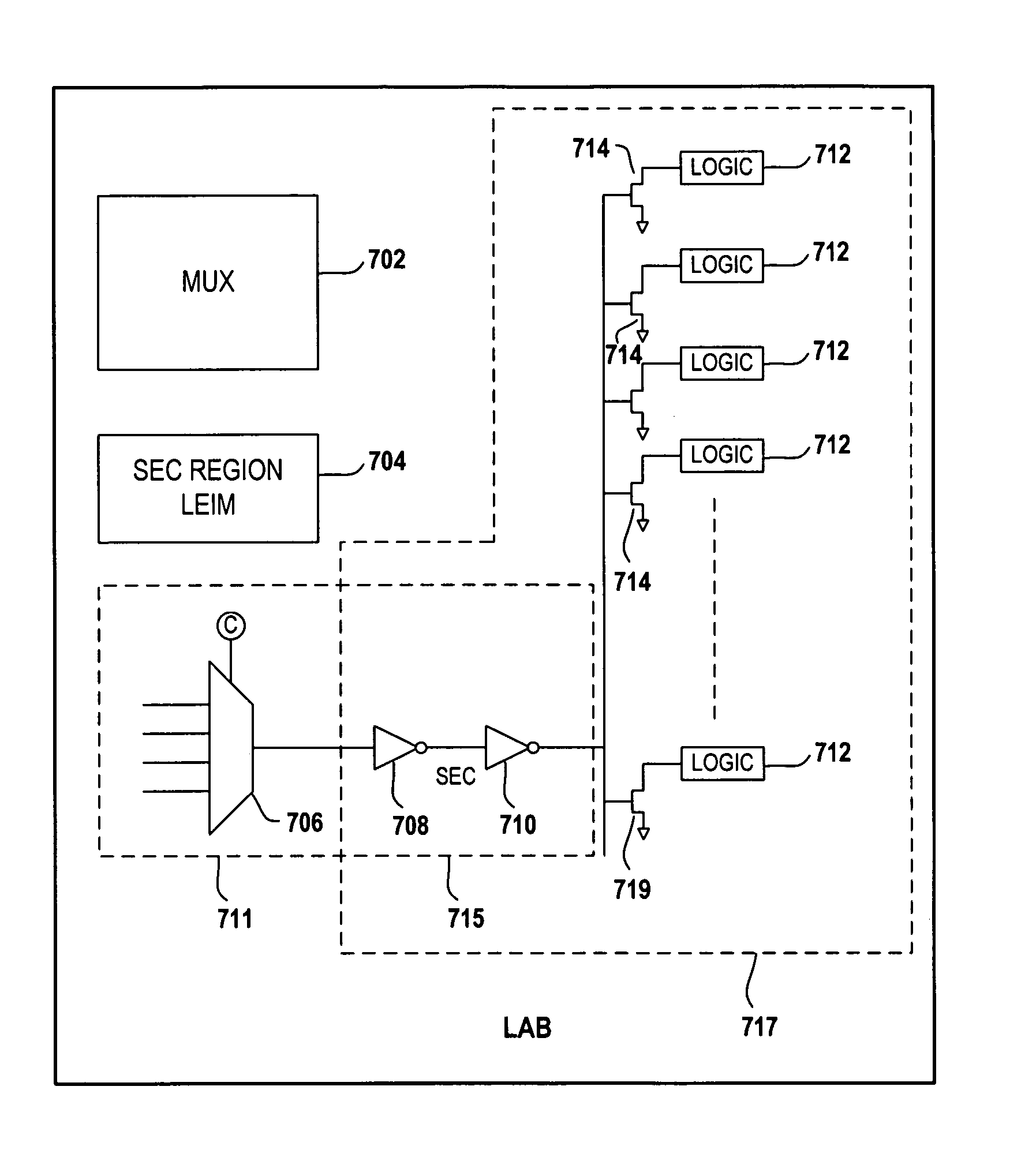

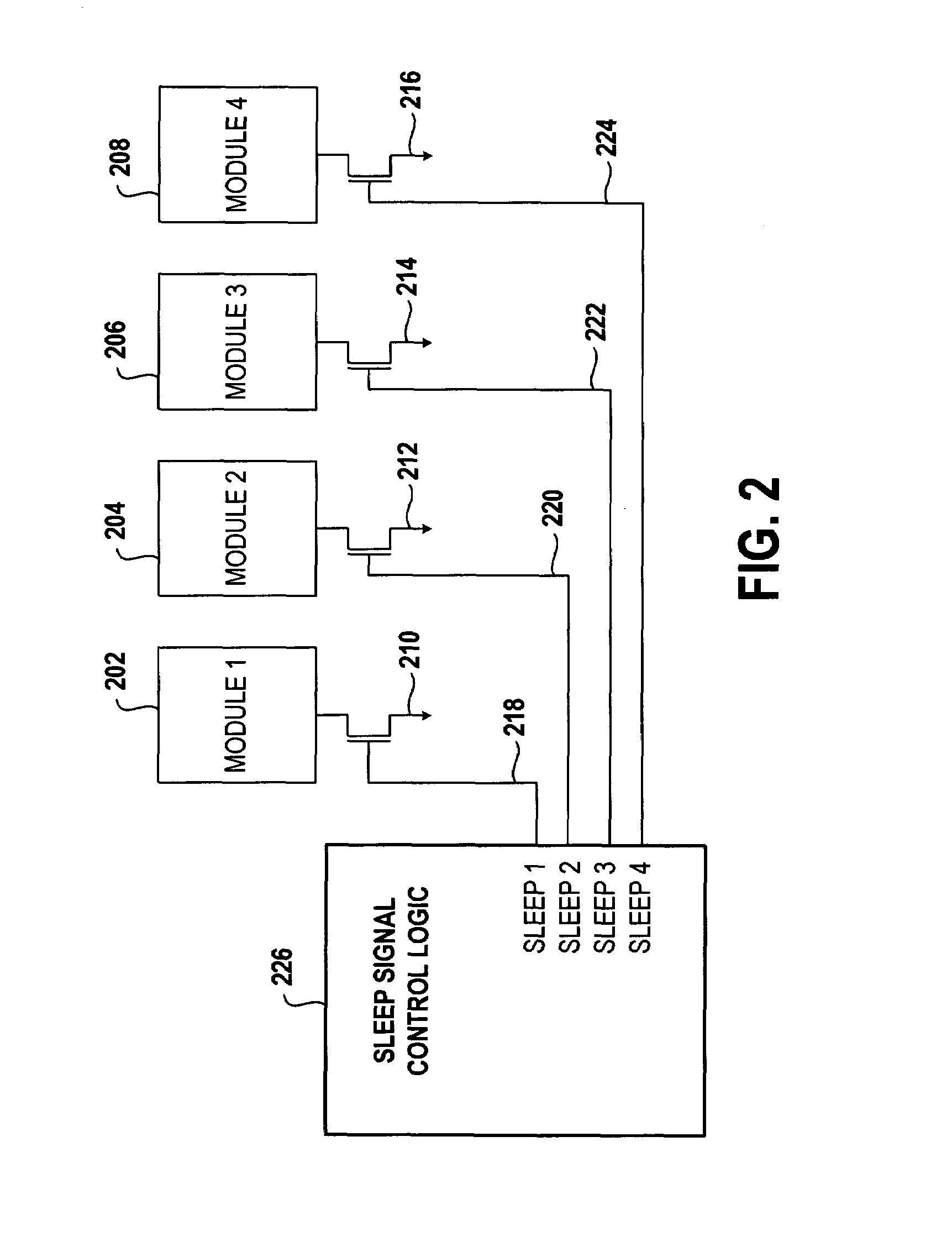

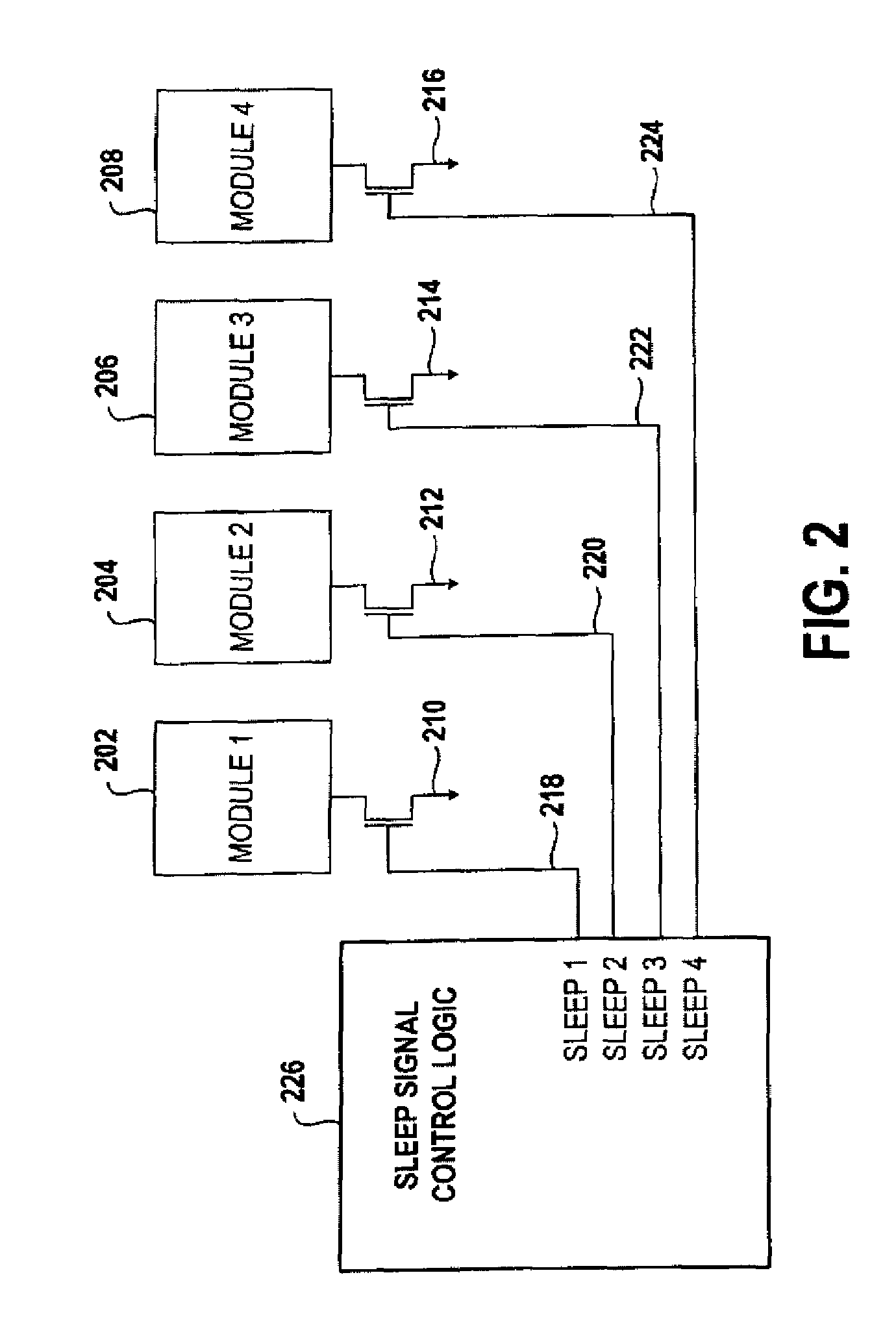

Method of reducing leakage current using sleep transistors in programmable logic device

InactiveUS7355440B1Reduce leakage currentTotal current dropPower reduction by control/clock signalSolid-state devicesProgrammable logic deviceErasable programmable logic device

A programmable logic device (PLD) having minimal leakage current for inactive logic blocks is provided. The PLD includes an array of logic blocks. Among the array of logic blocks, one of the array of logic blocks monitors the level of activity of each of the remaining logic blocks. The level of activity may be monitored by observing the input and output pin of the logic blocks. The PLD further includes a plurality of driven wires defining a routing pattern between the array of logic blocks. When one of the array of logic blocks detect inactivity in any one of the remaining logic blocks for a certain duration, the one of the array logic blocks transmits a signal invoking a sleep mode for the inactive logic blocks. A sleep transistor with a threshold voltage level that is capable minimizing the leakage current is associated with each of the remaining block. The gate of the sleep transistor receives the signal transmitted by one of the array logic blocks and the signal switches off the sleep transistor.

Owner:TAHOE RES LTD

Programmable logic device

InactiveUS8970251B2Increased power consumptionExtension of timePower reduction in field effect transistorsSolid-state devicesProgrammable logic deviceErasable programmable logic device

Owner:SEMICON ENERGY LAB CO LTD

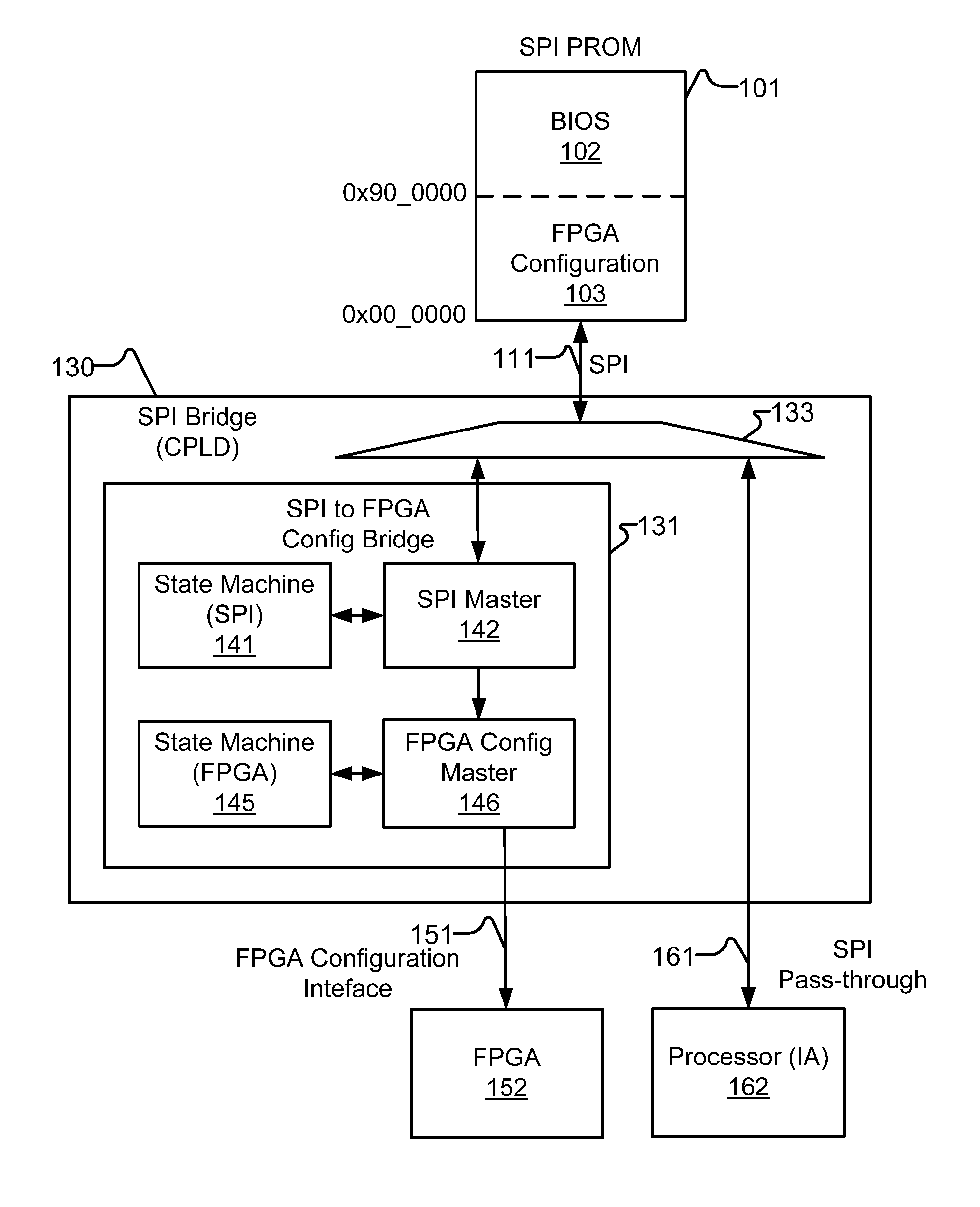

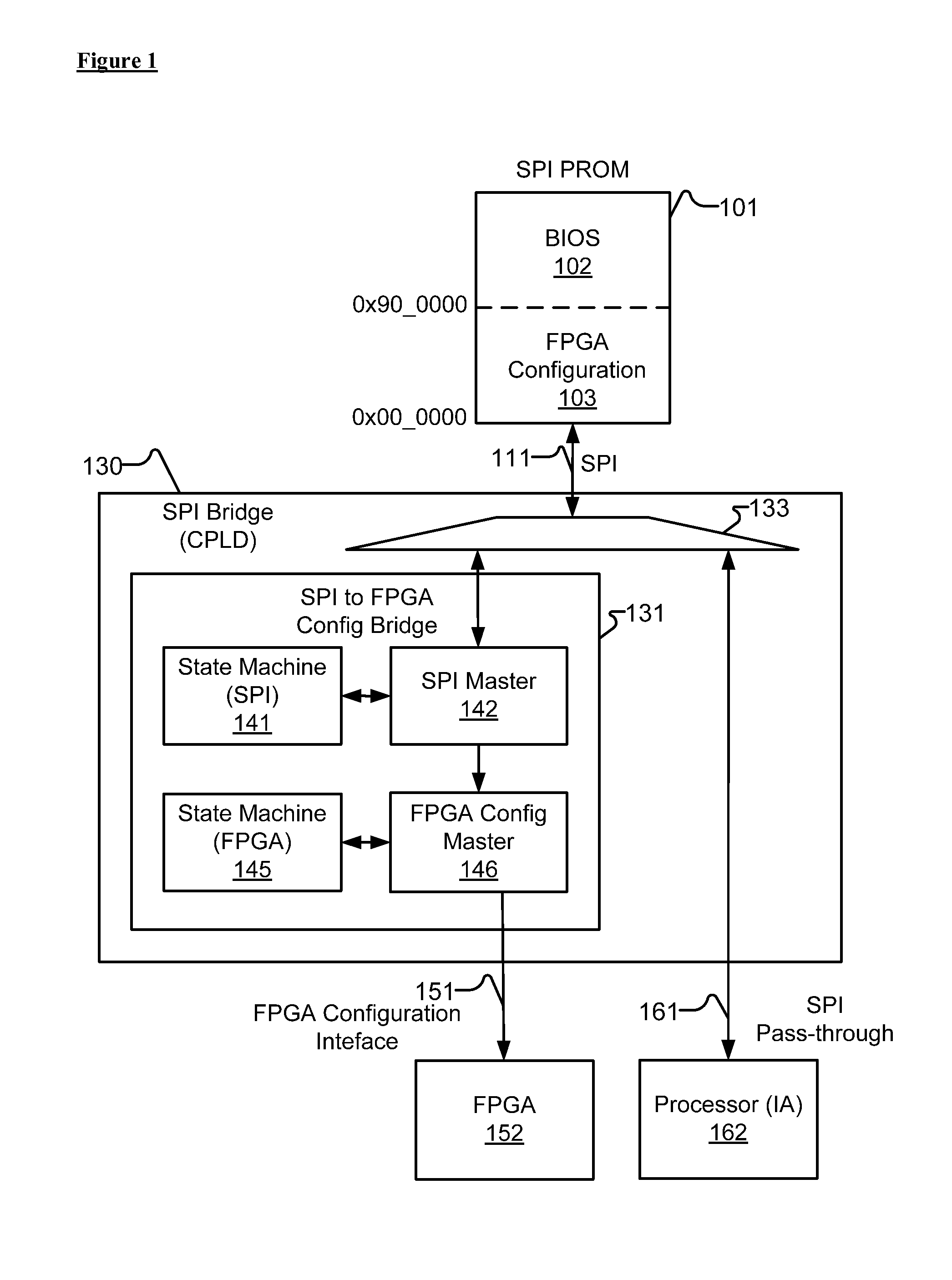

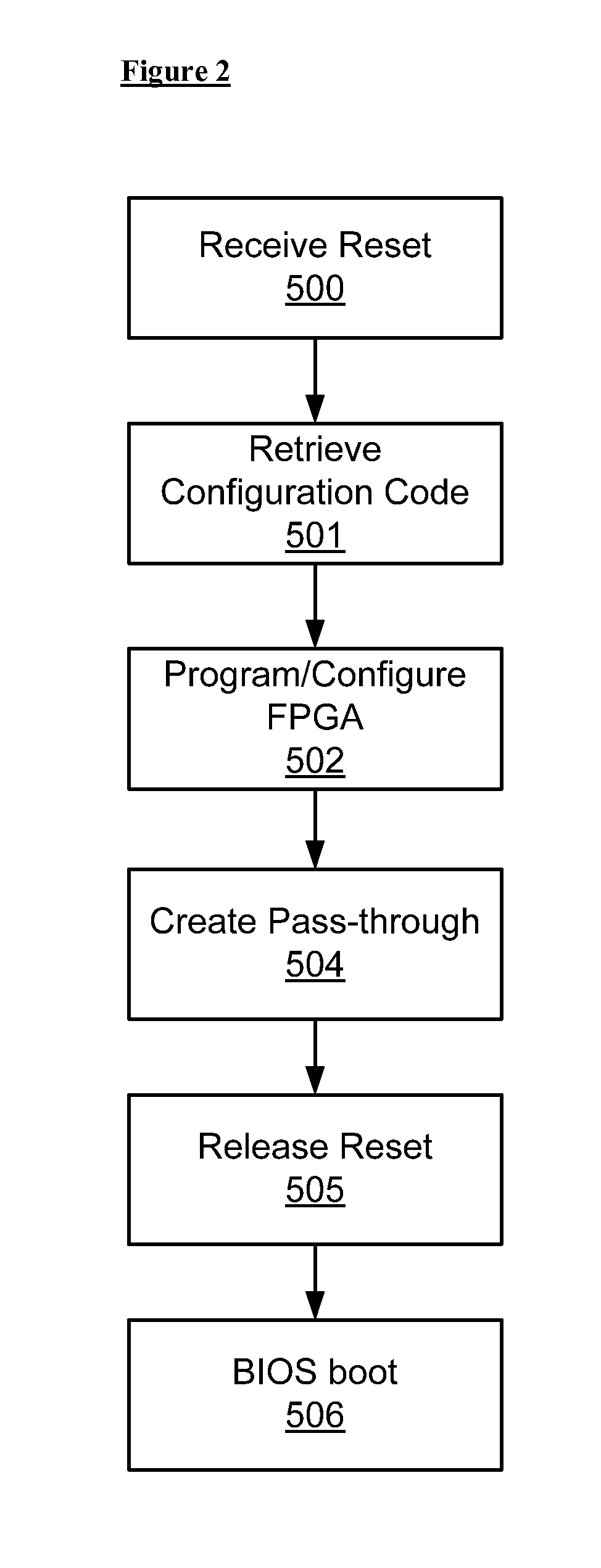

Apparatuses for configuring programmable logic devices from BIOS prom

InactiveUS20120260078A1Program control using stored programsDigital computer detailsProgrammable read-only memoryProgrammable logic device

An apparatus comprising programmable logic devices including a field programmable gate array (FPGA) is presented. In one embodiment, the apparatus also comprises a programmable read only memory (PROM) to store a firmware which includes at least a system boot code and a configuration code. The apparatus further includes a configuration agent to configure the FPGA by using the configuration code and to release the reset to the CPU after the FPGA is configured. In one embodiment, the configuration agent comprises a SPI-FPGA bridge (serial peripheral interface to FPGA configuration interface). In one embodiment, the configuration agent is operable to determine whether the FPGA is ready for configuration based at least on a status from the FPGA.

Owner:INTEL CORP

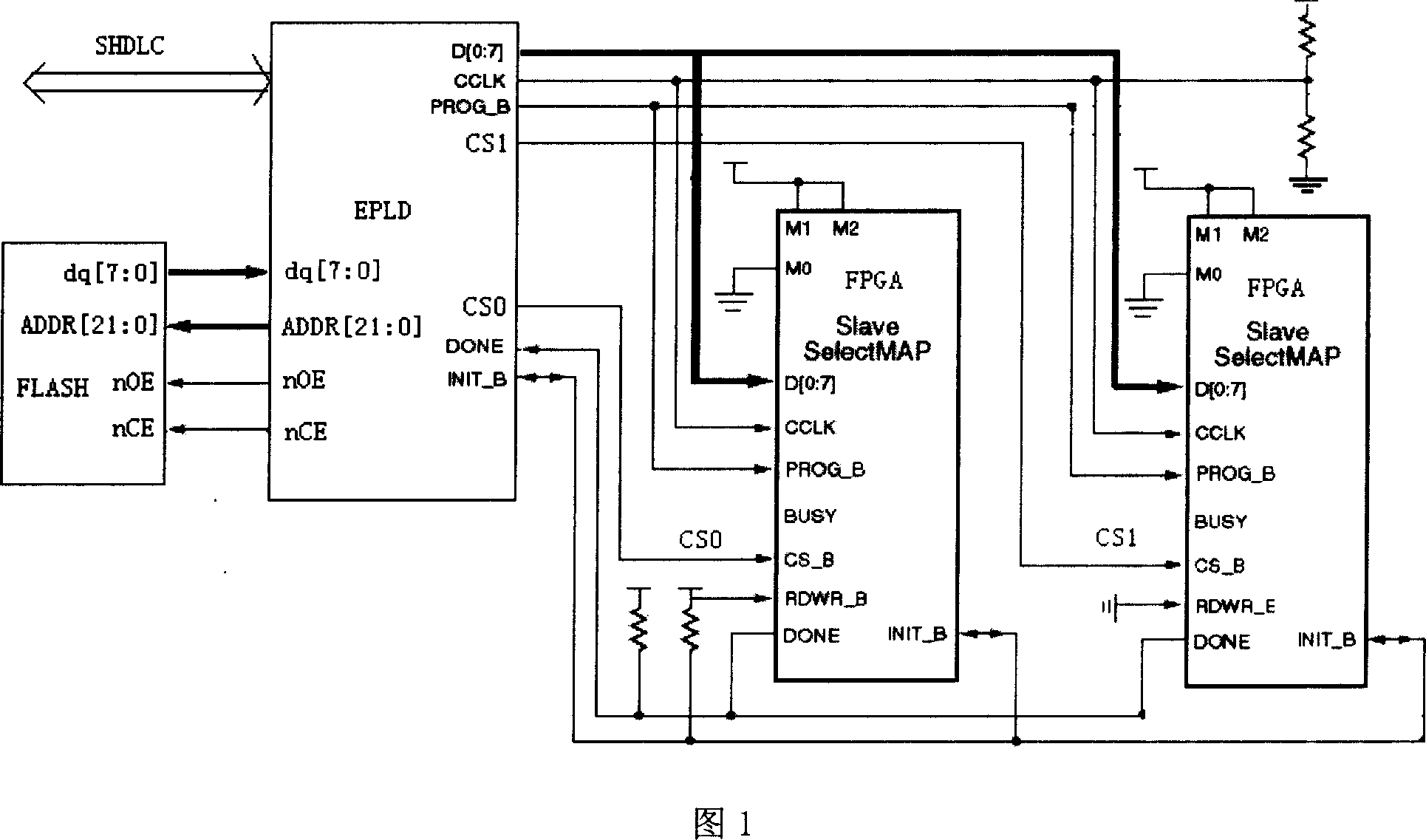

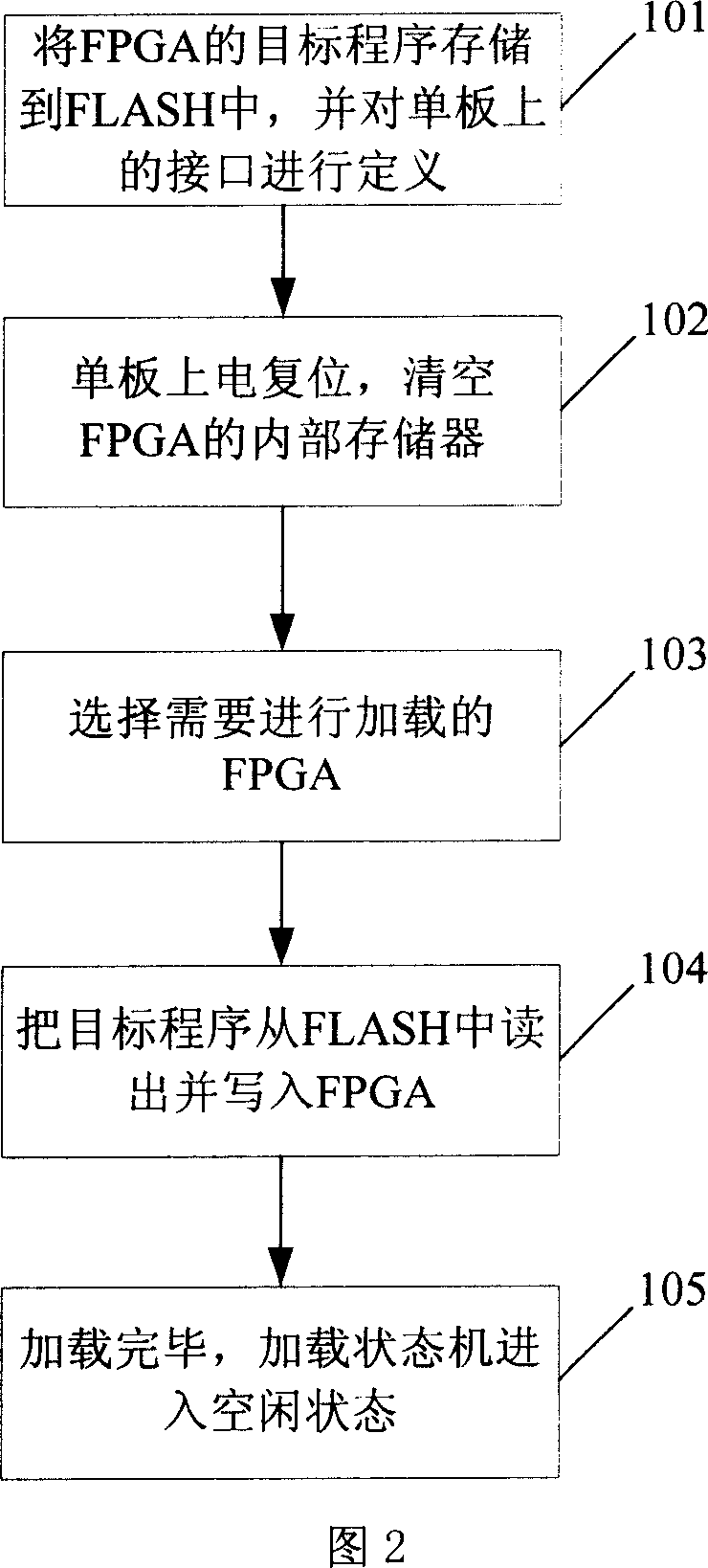

Method and system for loading FPGA target program

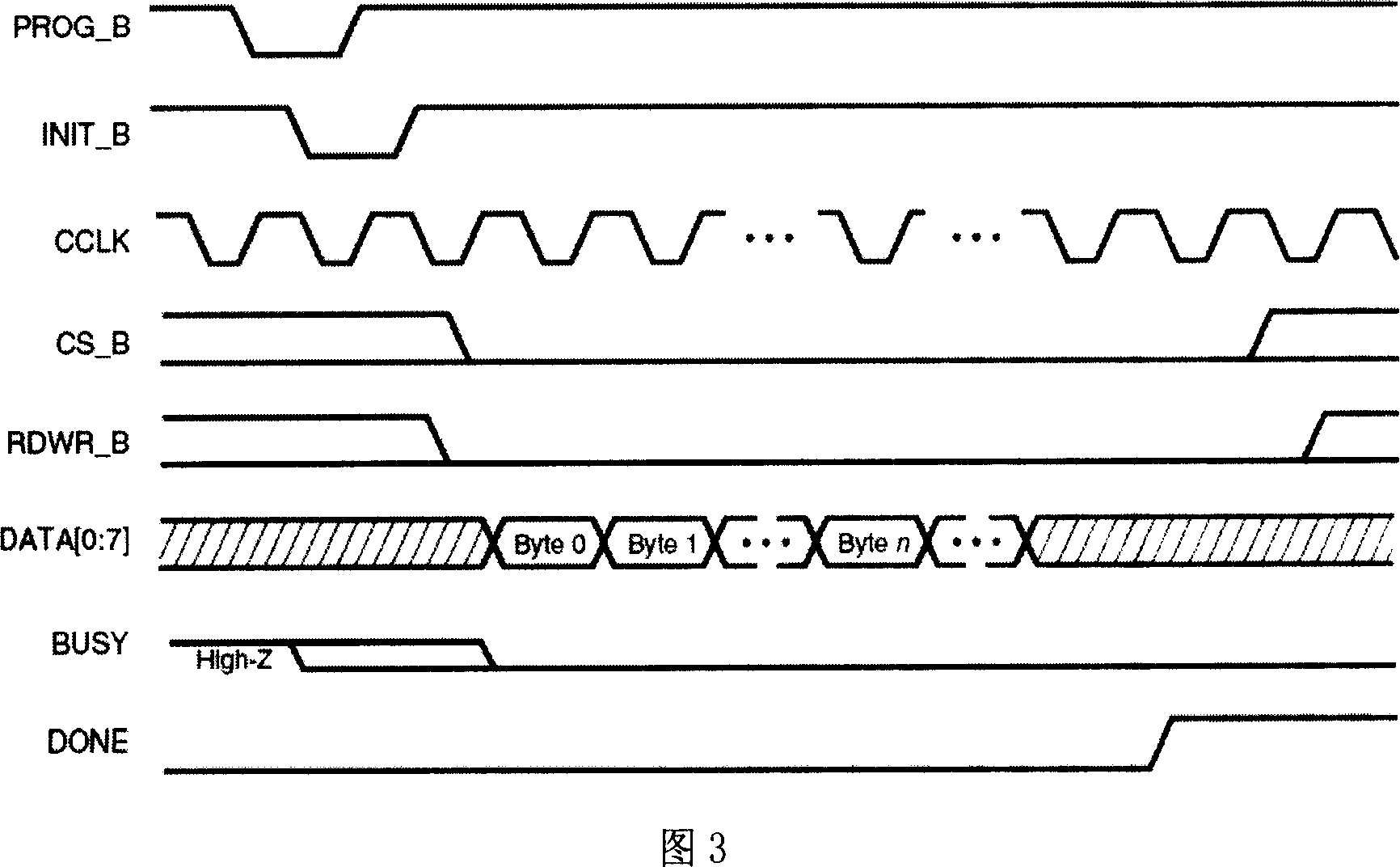

InactiveCN1928824AReduce startup timeRealize online upgradeProgram loading/initiatingLoad timeErasable programmable logic device

The provided method for loading FPGA object program comprises: externally hanging flash memory on single-board EPLC to store the FPGA object program; configuring single-board interface; electrical resetting, loading the program into FPGA. This invention implements automatic loading to save startup time, and can on-line update for maintenance.

Owner:HUAWEI TECH CO LTD

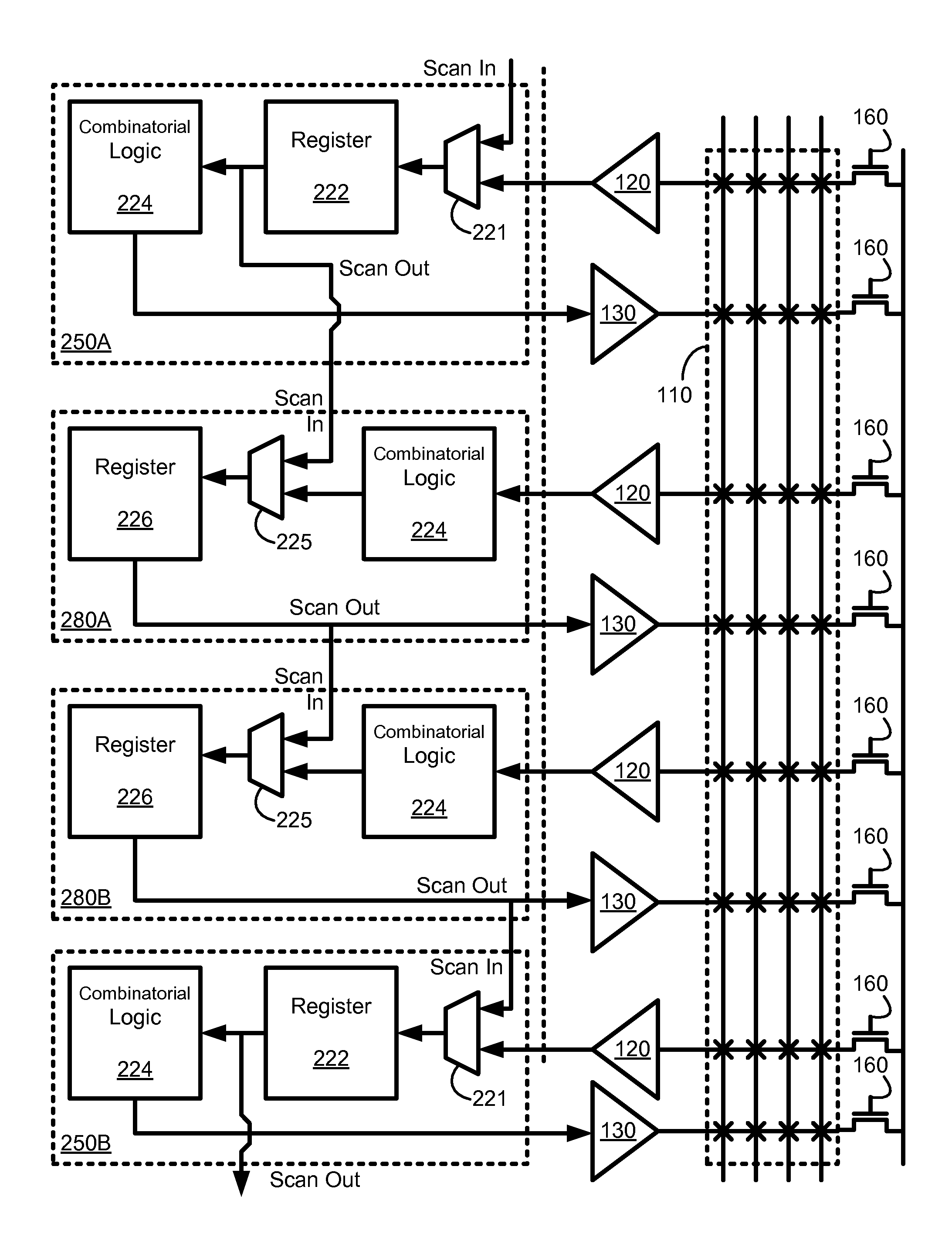

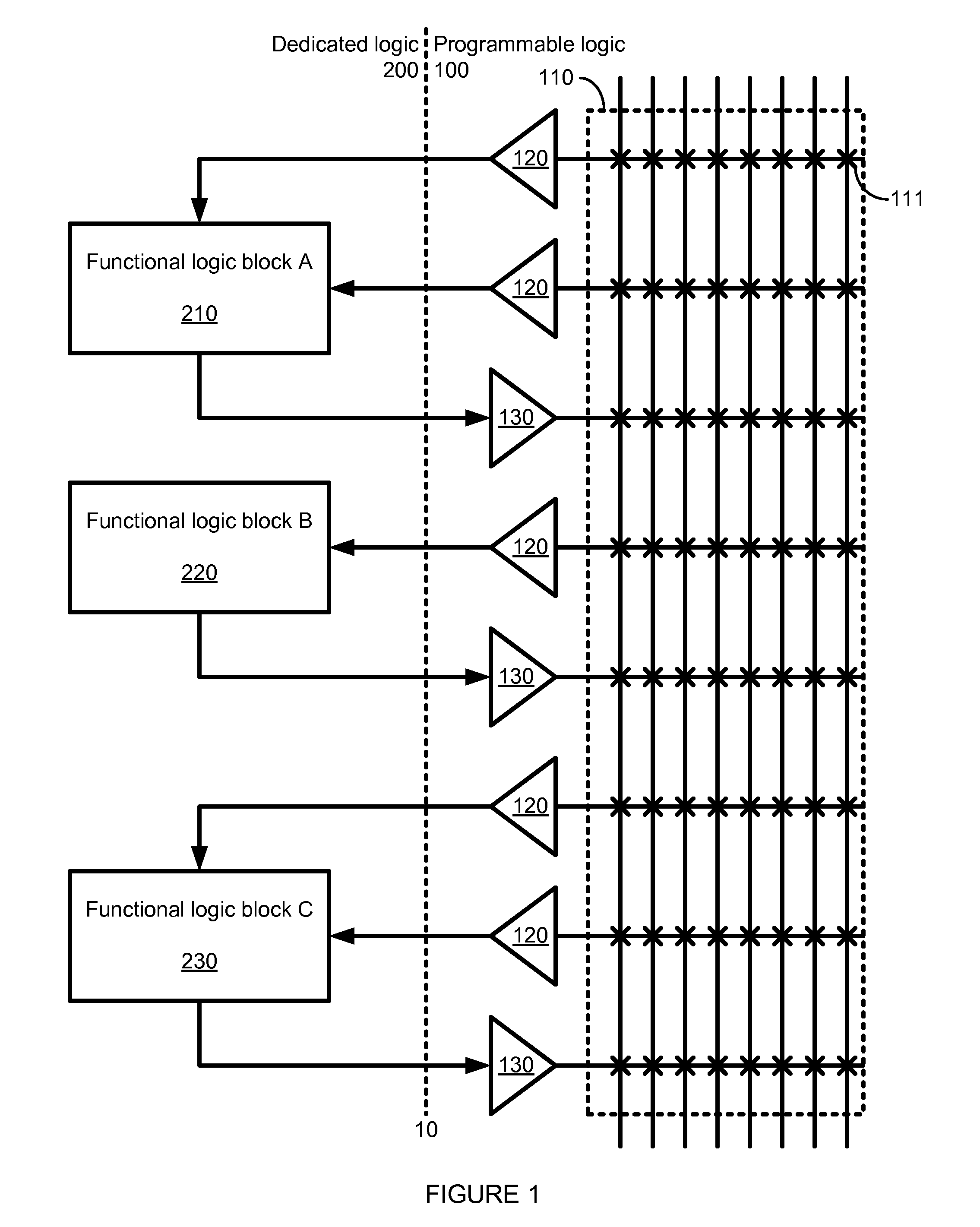

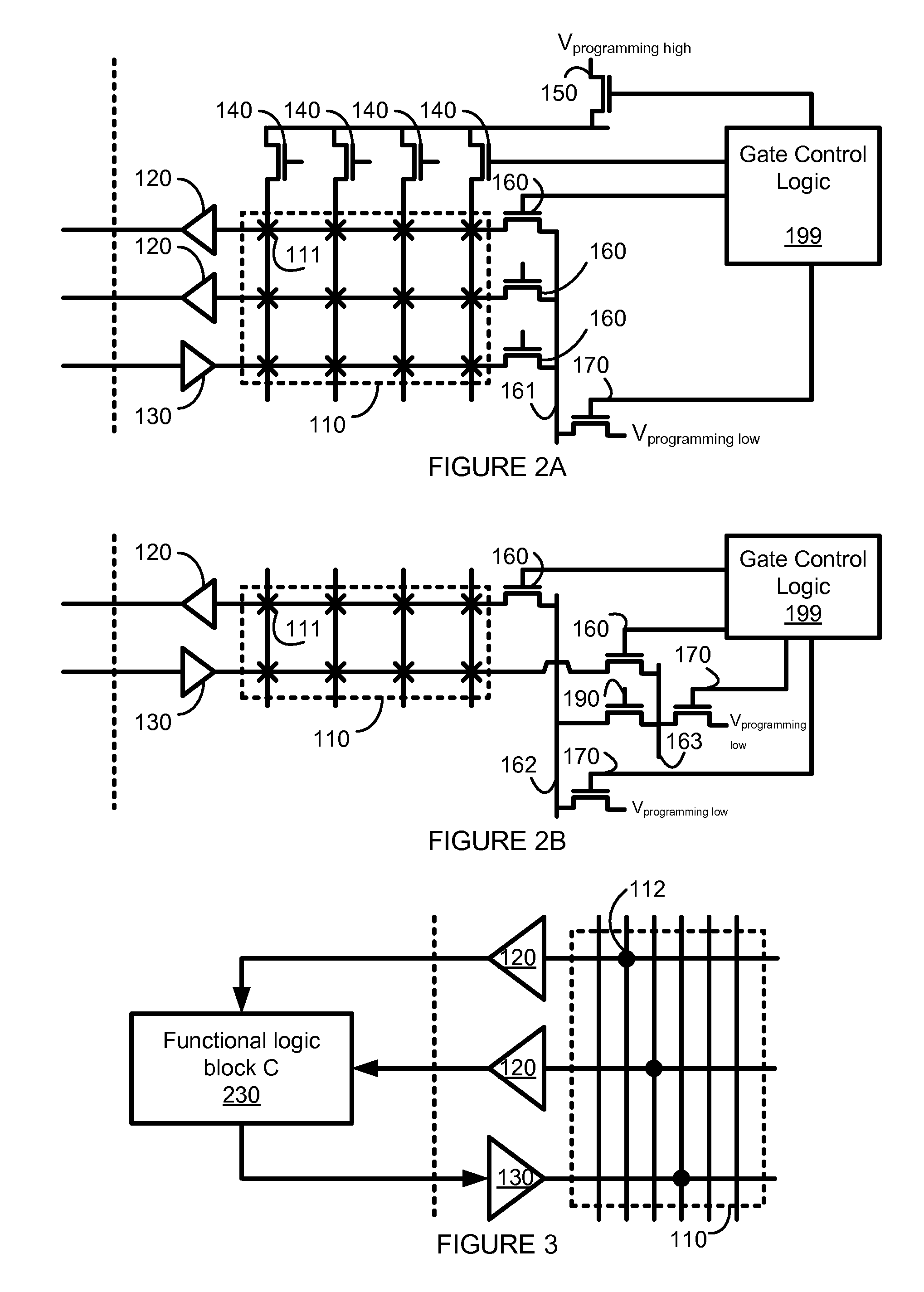

FPGA programming structure for ATPG test coverage

Testing of combinatorial logic in a programmable device is provided by routing input and / or output test values as signals from and back to dedicated logic through programming circuitry in programmable logic. Some embodiments of the present invention provide for a method for testing functional logic block of an application-specific standard product (ASSP) in a programmable logic device, the method comprising: storing an input value into a register; passing the input value from the register to combinatorial logic; producing an output value from the combinatorial logic; passing the output value from the combinatorial logic to the register; saving the output value in the register; and reading the output value out of the register.

Owner:QUICKLOGIC

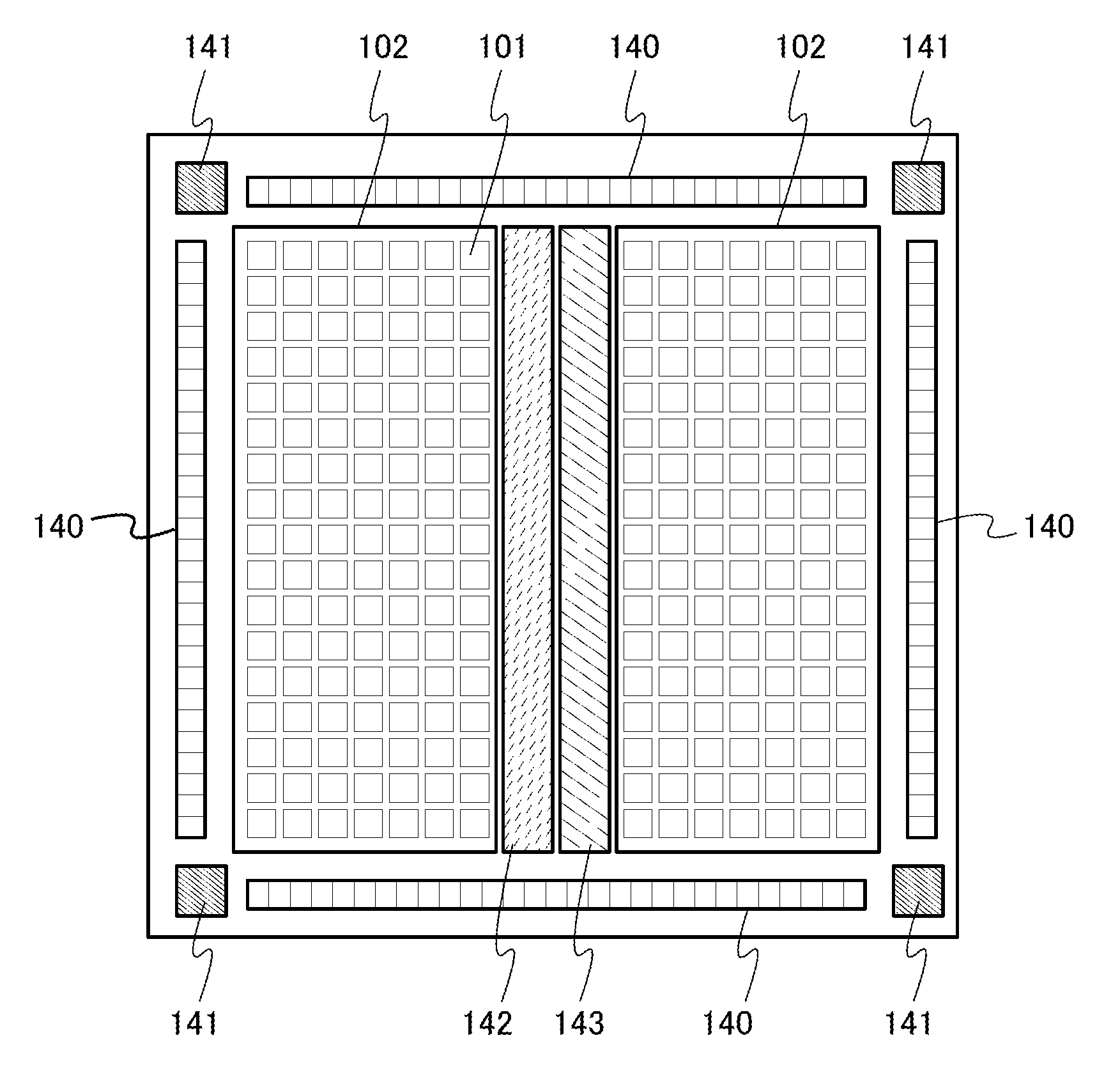

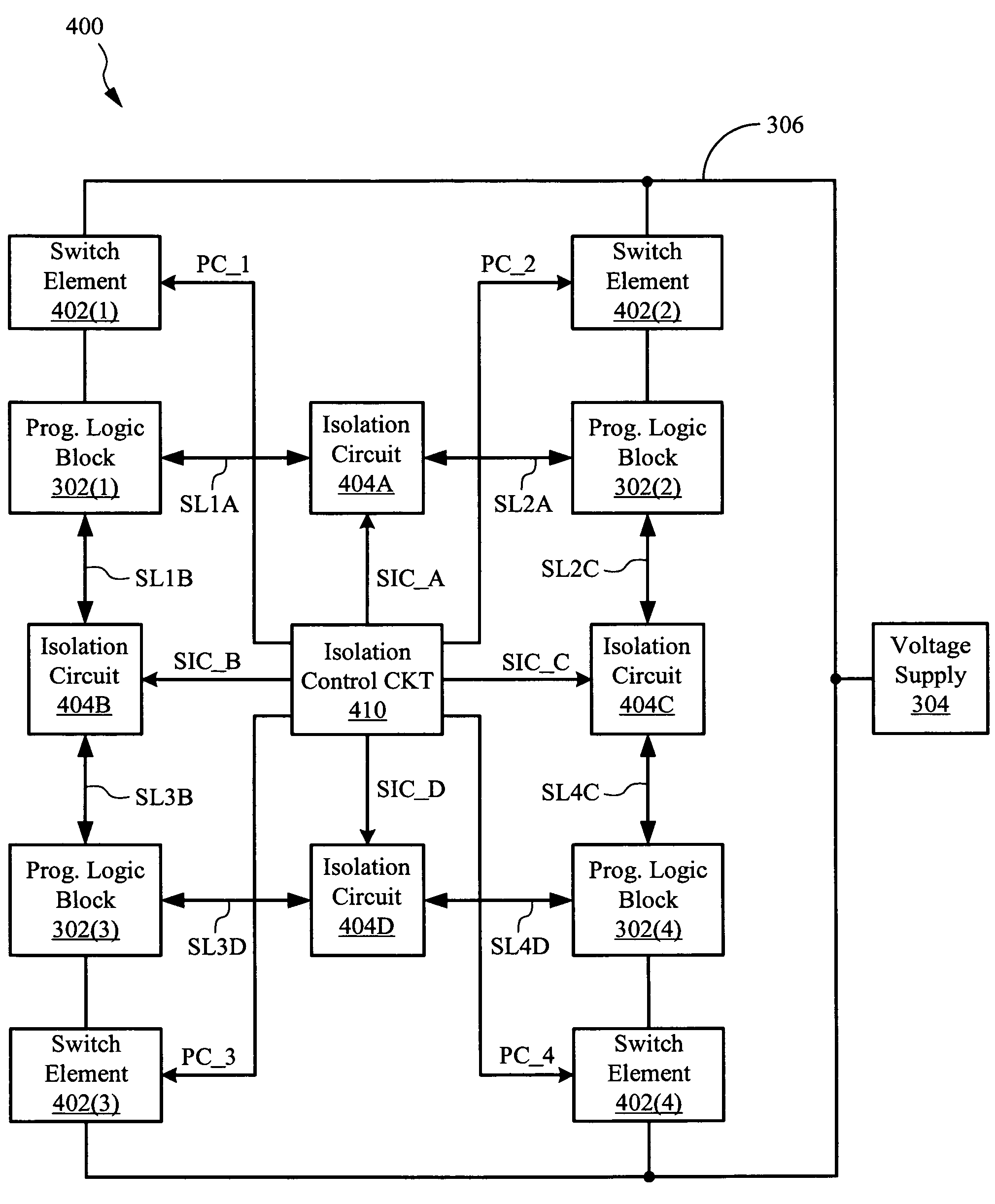

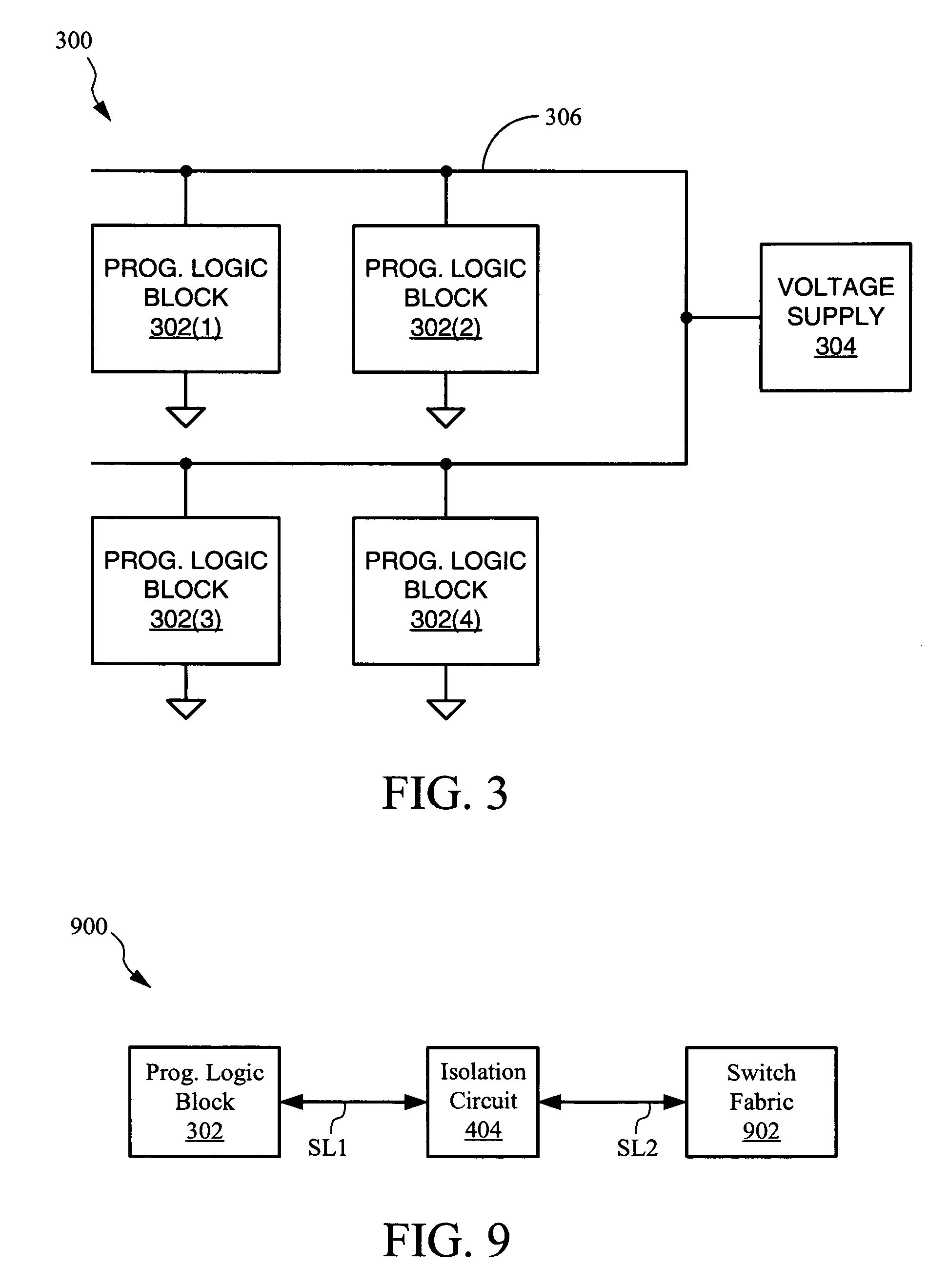

Low power zones for programmable logic devices

ActiveUS7498839B1Reduce static power consumptionDisabling unused or inactive resourcesTransistorSemiconductor/solid-state device detailsProgrammable logic deviceInvalid Data

An integrated circuit device such as a PLD is divided into a plurality of logic blocks, each including one or more resources of the device. The device includes a plurality of switch elements and a number of signal isolation circuits. The switch elements selectively disable corresponding logic blocks to reduce power consumption, and the signal isolation circuits selectively isolates corresponding logic blocks to prevent the transmission of invalid data from disabled logic blocks to enabled logic blocks.

Owner:XILINX INC

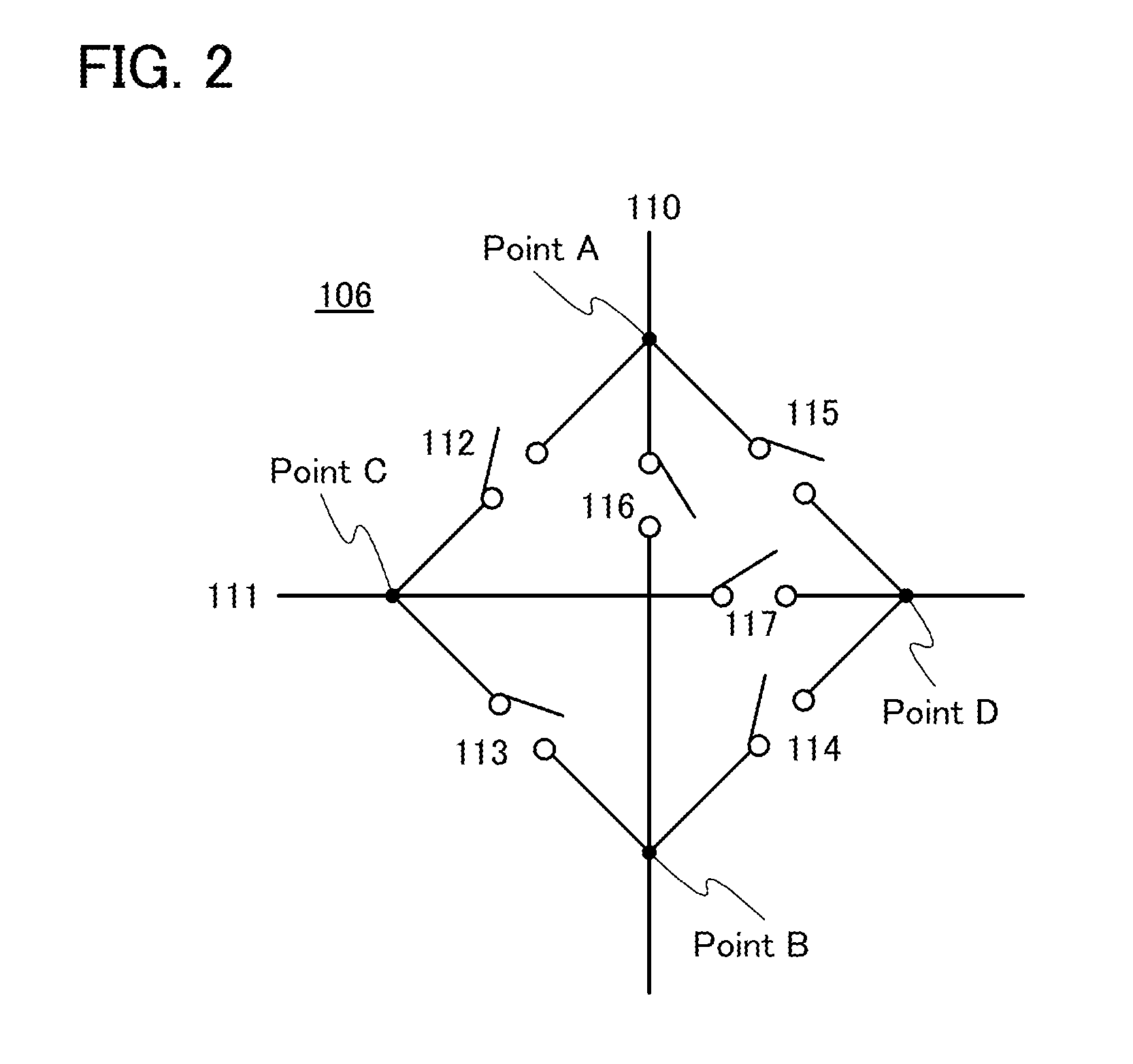

Programmable logic device

InactiveUS8476927B2Short startup timeEasy to integrateSolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic deviceErasable programmable logic device

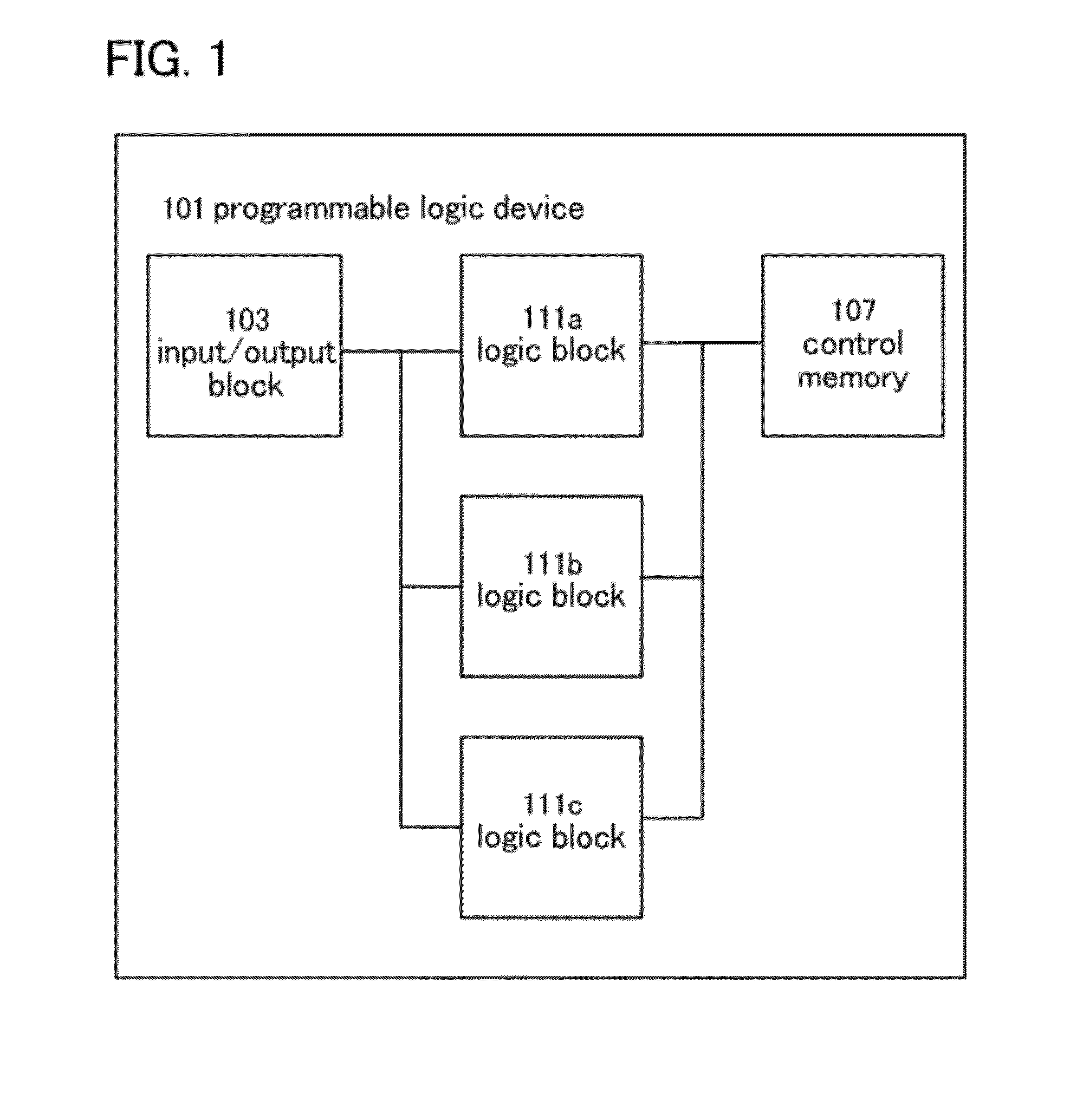

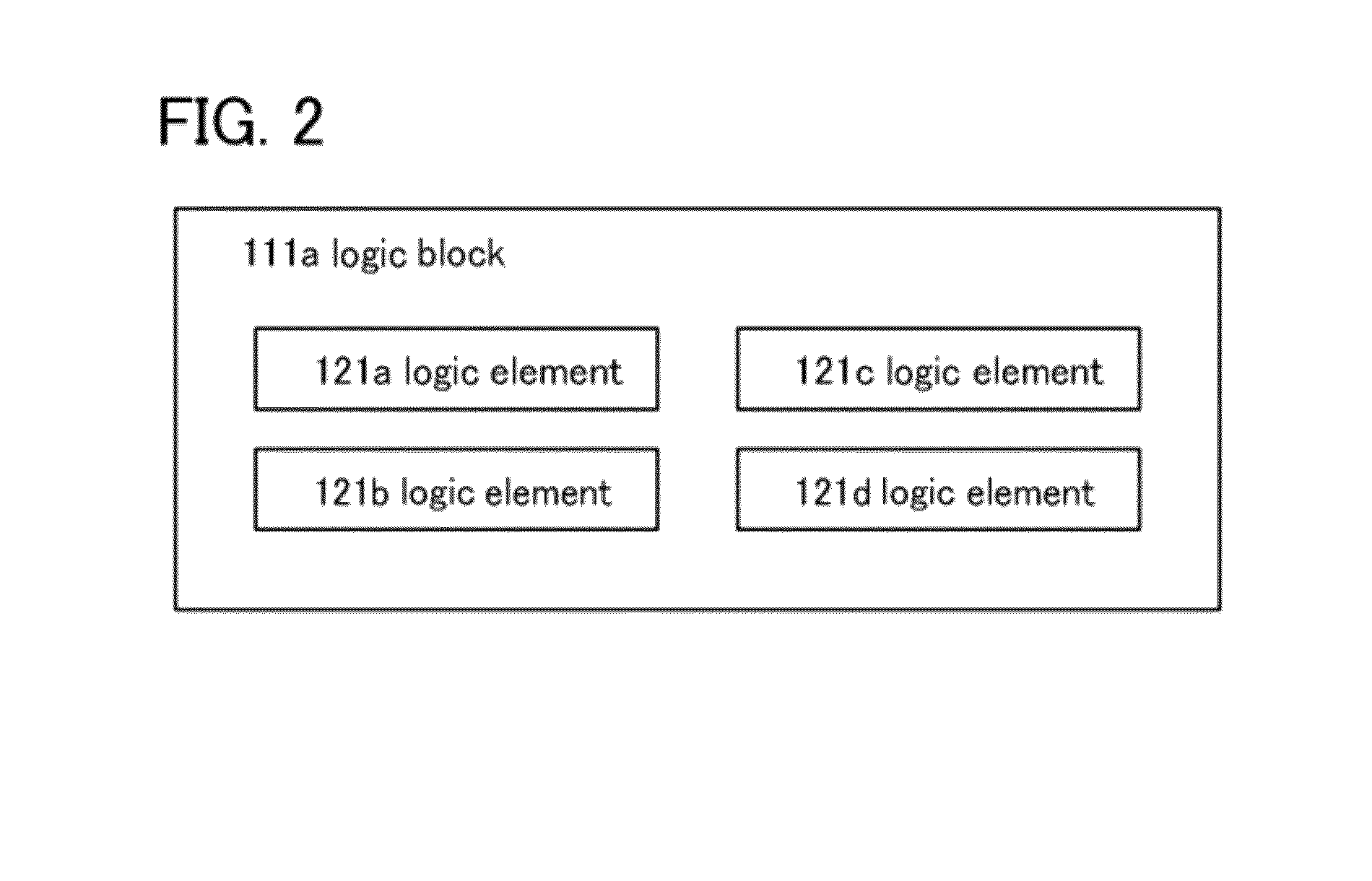

An object of the present invention is to provide a programmable logic device which has short start-up time after supply of power is stopped, is highly integrated, and operates with low power. In a programmable logic device including an input / output block, a plurality of logic blocks each including a logic element, and a wiring connecting the plurality of logic blocks, the logic element has a configuration memory for holding configuration data and a look-up table including a selection circuit. The configuration memory includes a plurality of memory elements each of which includes a transistor whose channel region is in an oxide semiconductor film and an arithmetic circuit provided between the transistor and the selection circuit. Configuration data is selectively changed and output by the selection circuit in accordance with an input signal.

Owner:SEMICON ENERGY LAB CO LTD

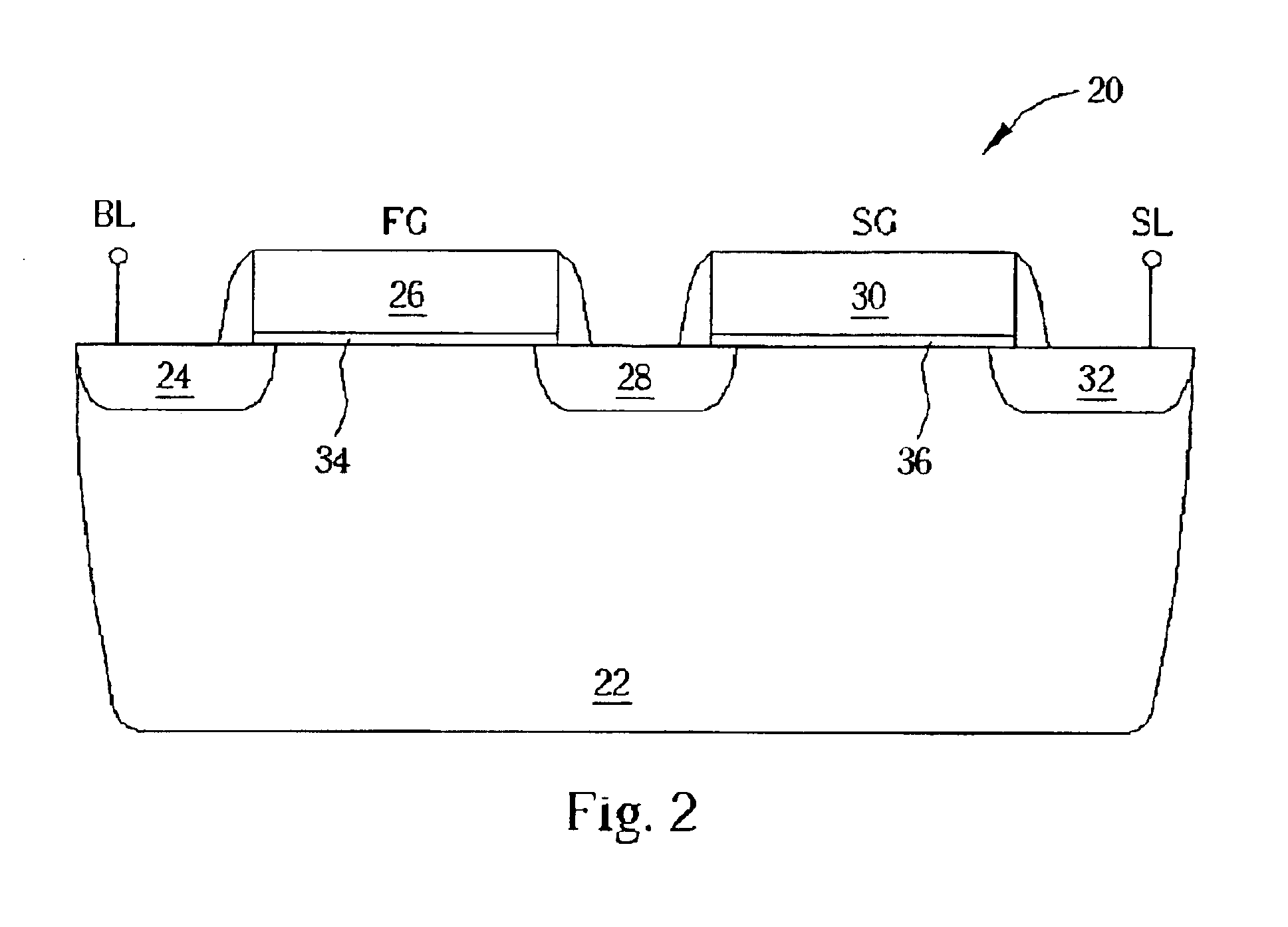

Method for operating N-channel electrically erasable programmable logic device

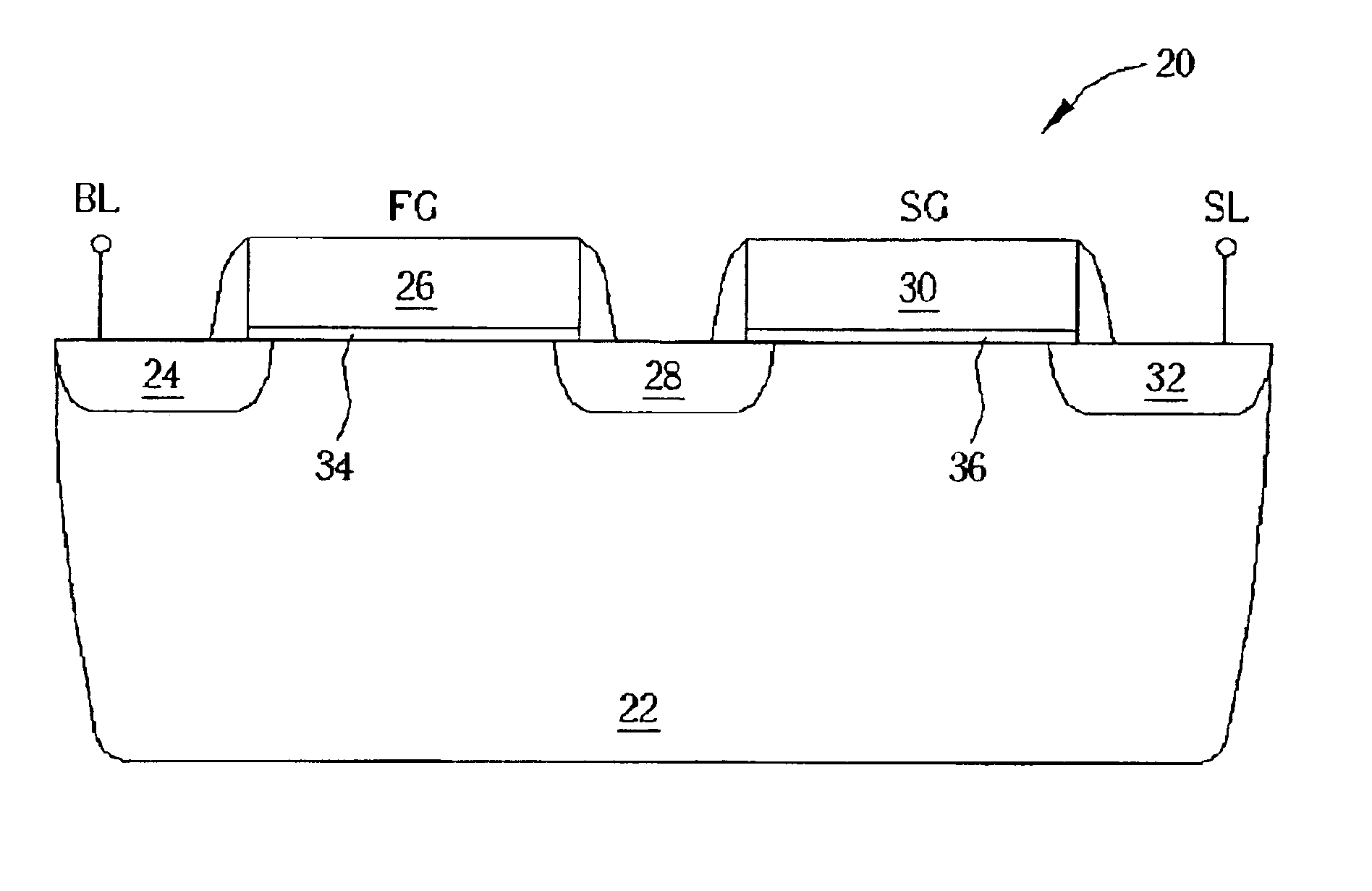

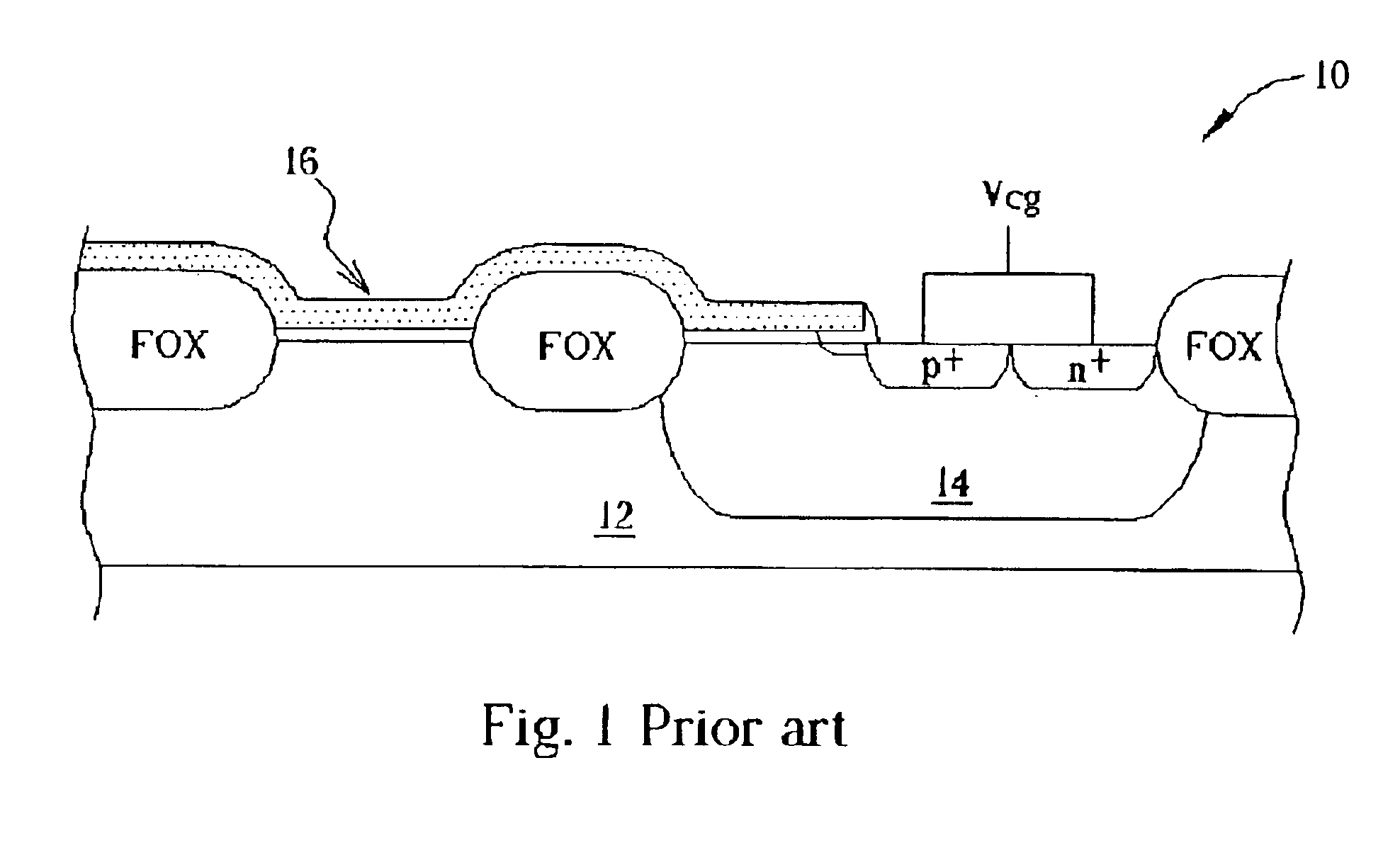

InactiveUS6842374B2TransistorSolid-state devicesProgrammable logic deviceErasable programmable logic device

An electrically erasable programmable logic device (EEPLD) contains a P-type substrate. A first N-type doped region is disposed in the P-type substrate. A first gate, which is used to store data, overlies the P-type substrate and is adjacent to the first N-type doped region. A second N-type doped region is laterally disposed in the P-type substrate. The second N-type doped region is also adjacent to the first gate. A second gate, which acts as a select gate or select gate of the EEPLD, overlies the P-type substrate and is adjacent to the second N-type doped region. A third N-type doped region is disposed in the P-type substrate. The third N-type doped region is adjacent to the second gate. By Applying a sufficient voltage on the first N-type doped region (VBL), and changing a select gate voltage (VSG) or the third N-type doped region voltage (VSL) applied on the second gate of the EEPLD, the operation of the EEPLD can be selectively implemented either under a channel hot hole (CHH) program mode or a channel hot electron (CHE) erase mode.

Owner:EMEMORY TECH INC

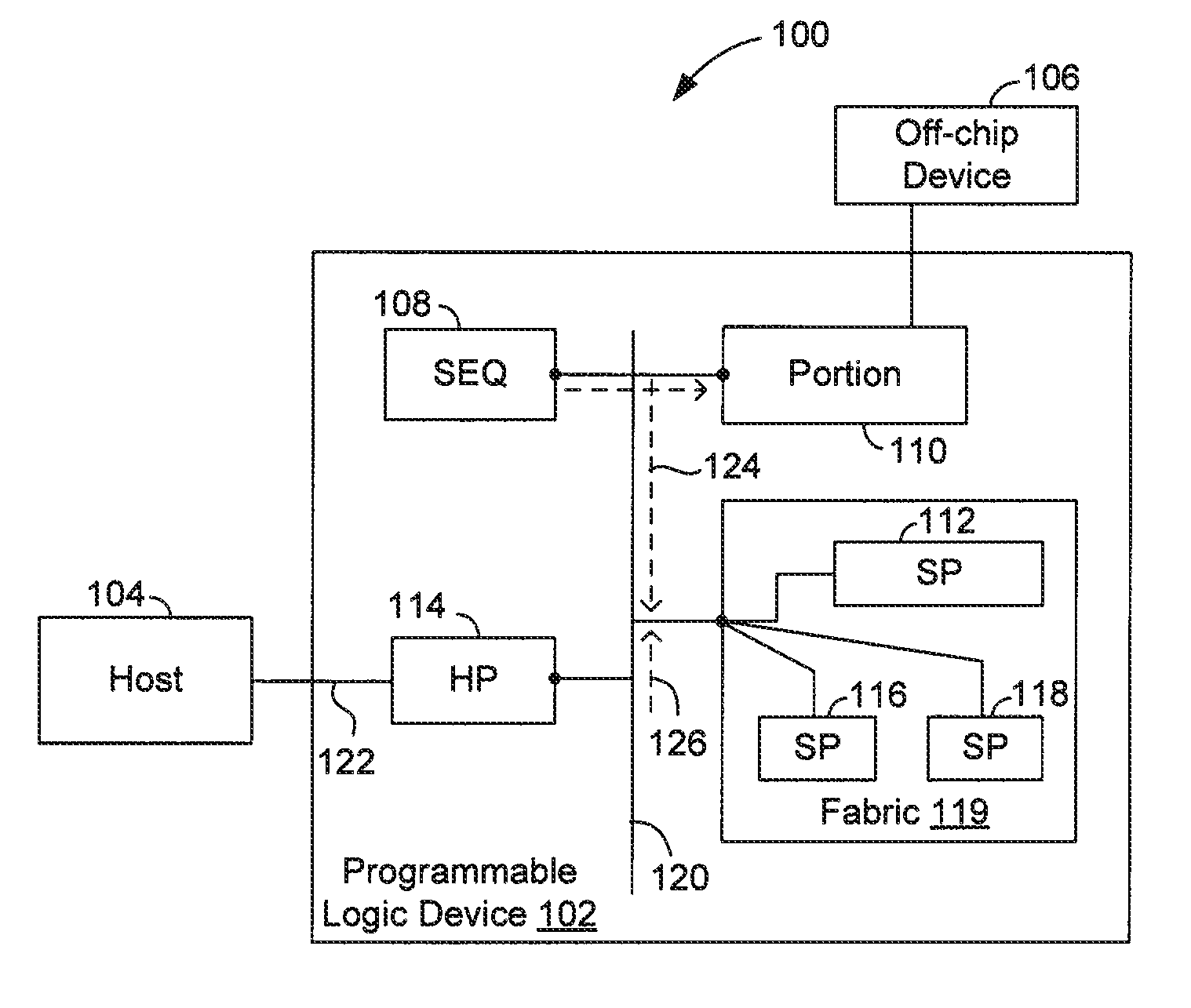

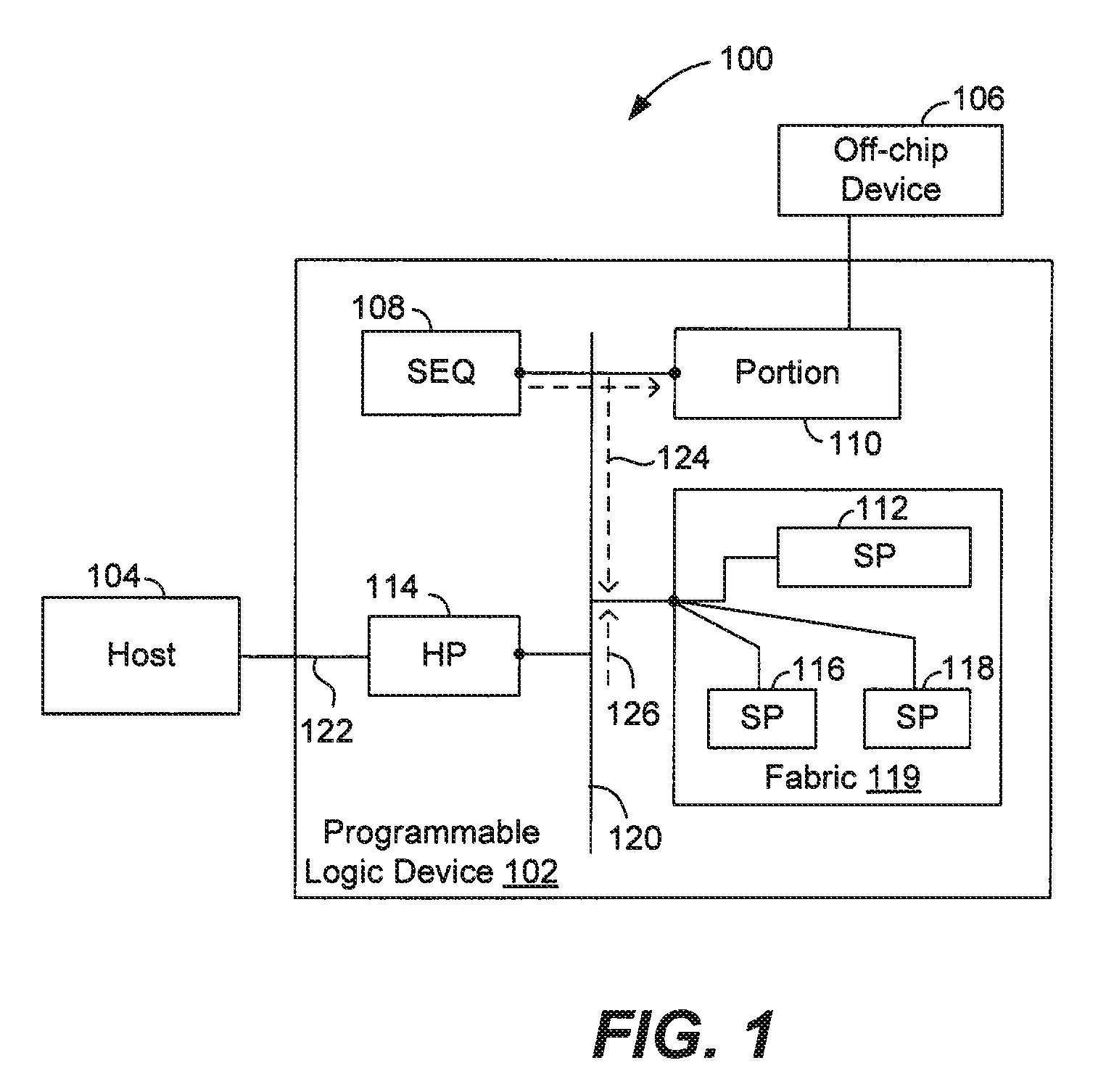

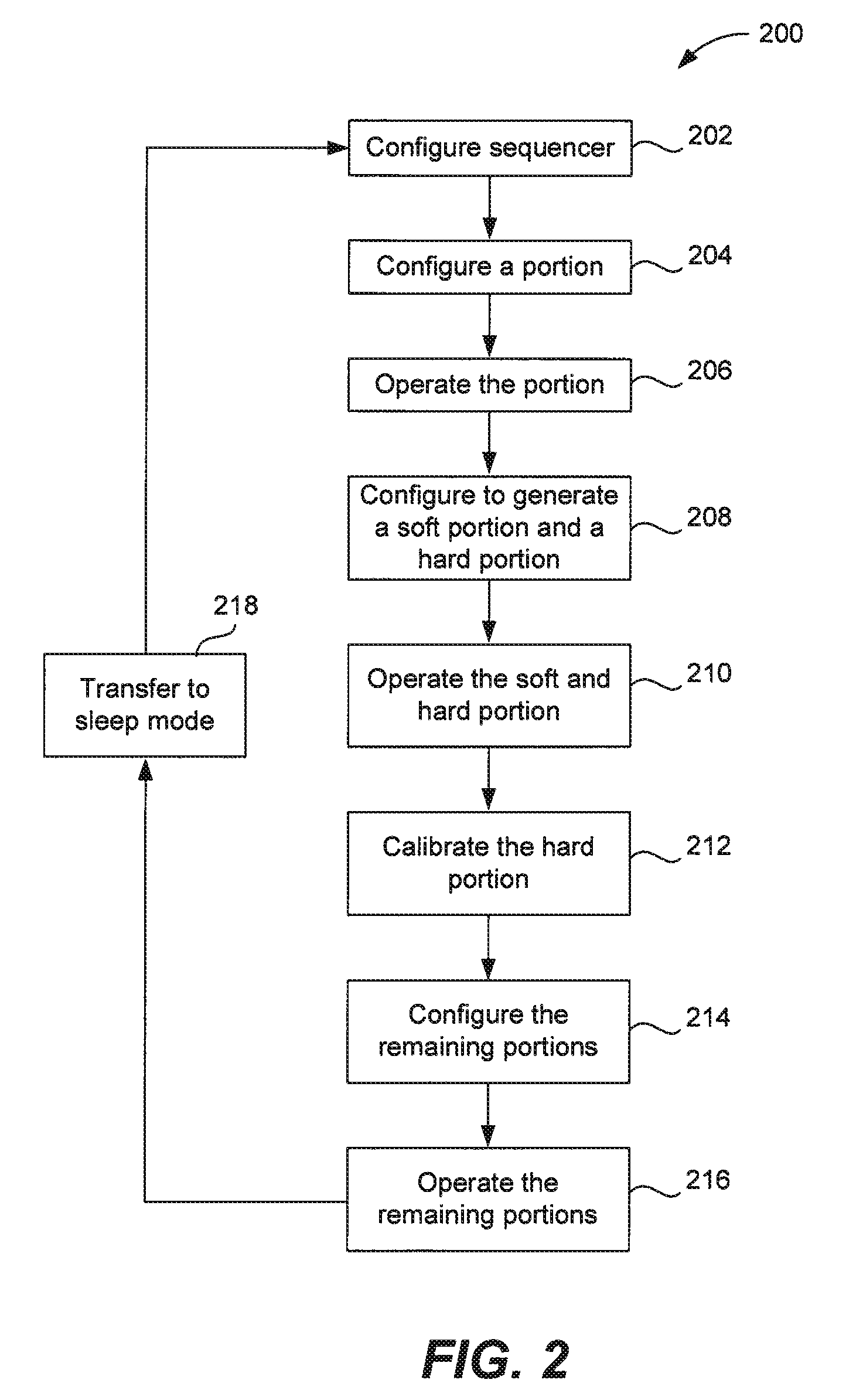

Systems and methods for flexibly configuring a programmable logic device

ActiveUS8664975B1CAD circuit designSpecial data processing applicationsIntellectual propertyProgrammable logic device

Systems and methods for flexibly configuring one or more intellectual property (IP) blocks of a programmable logic device are described. The methods include configuring and operating a first portion of the programmable logic device before configuring a remaining portion of the programmable logic device. By operating the first portion before configuring the remaining portions, various timing constraints including power-up timing constraints can be met by the programmable logic device.

Owner:ALTERA CORP

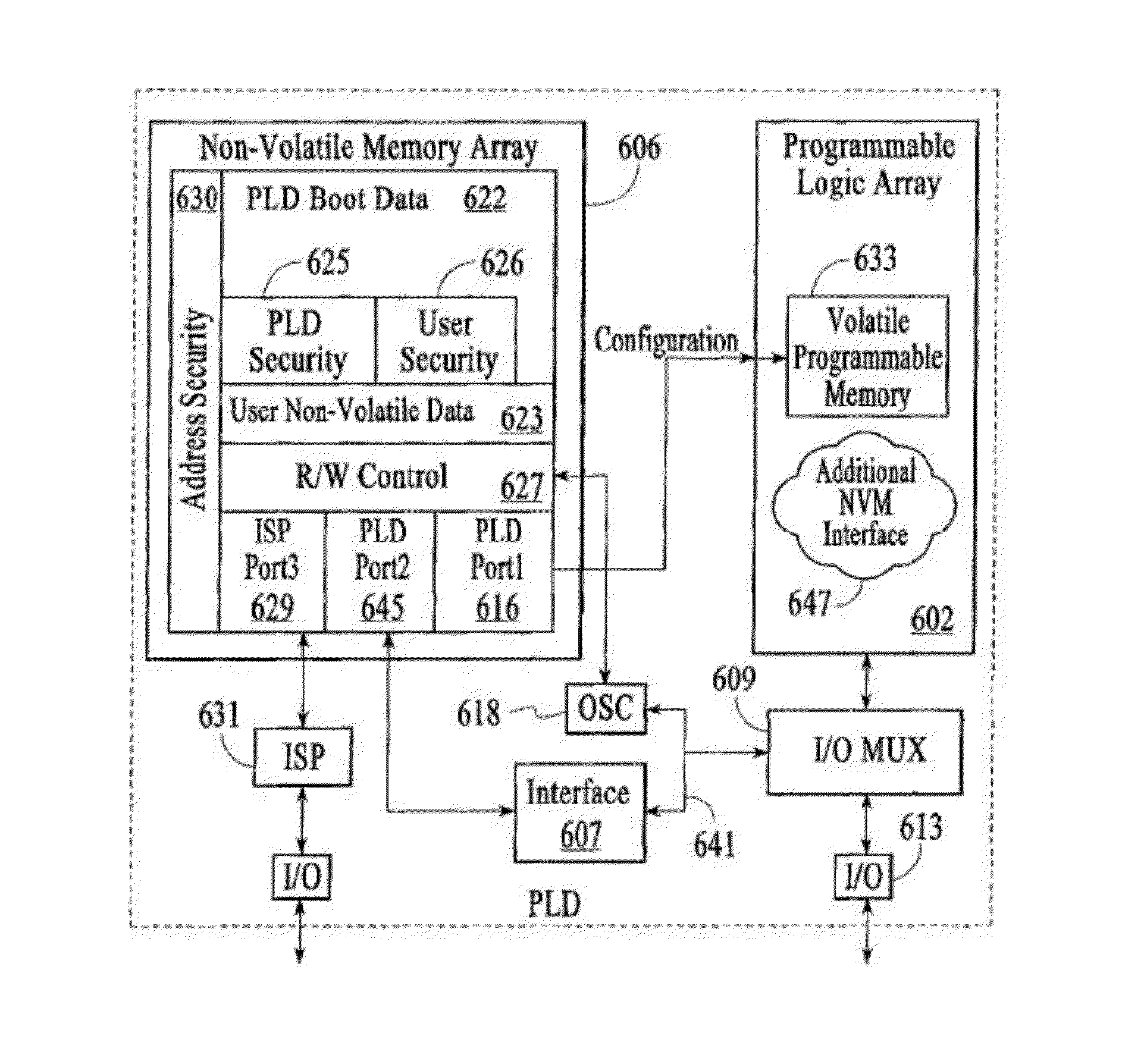

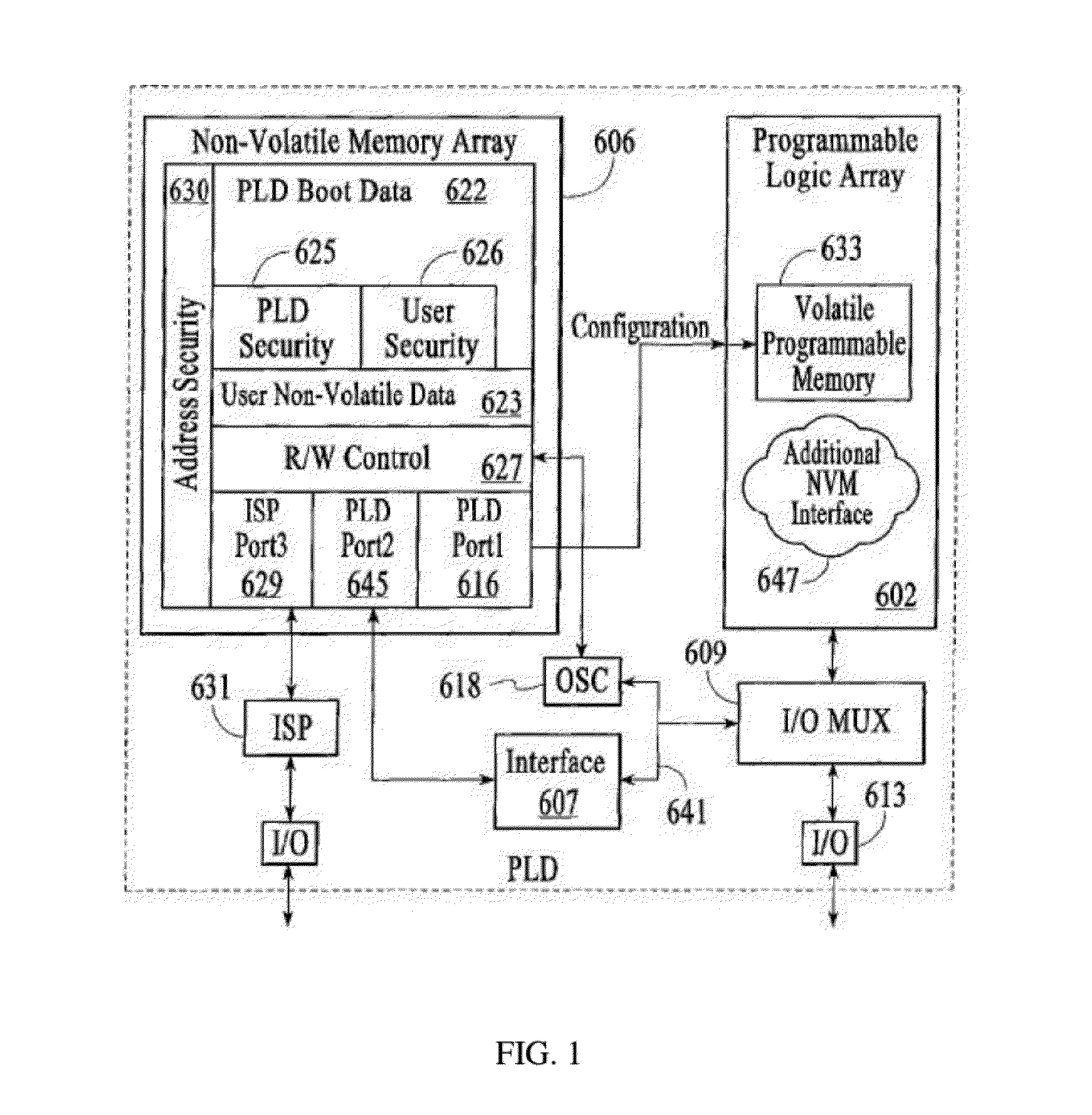

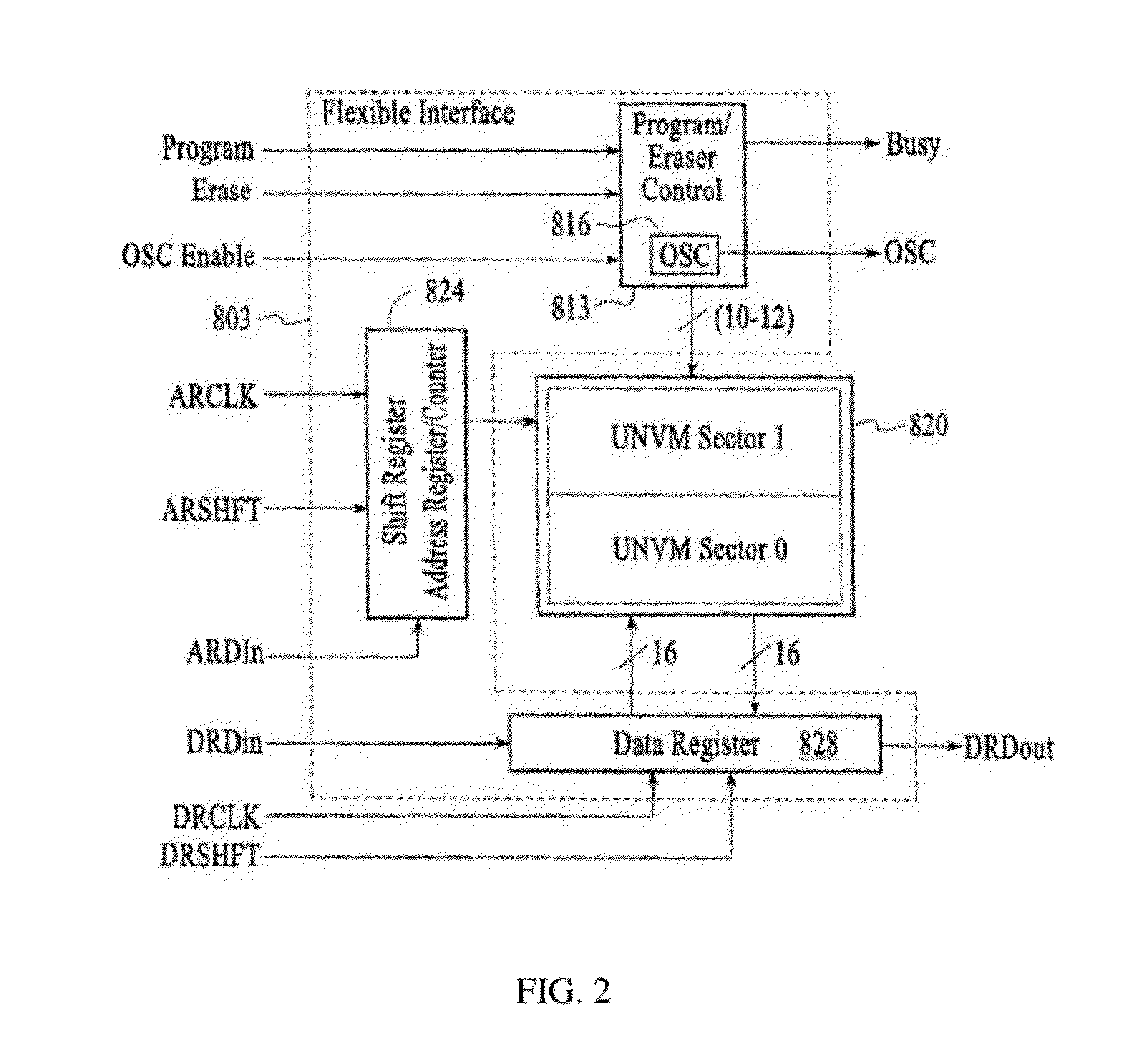

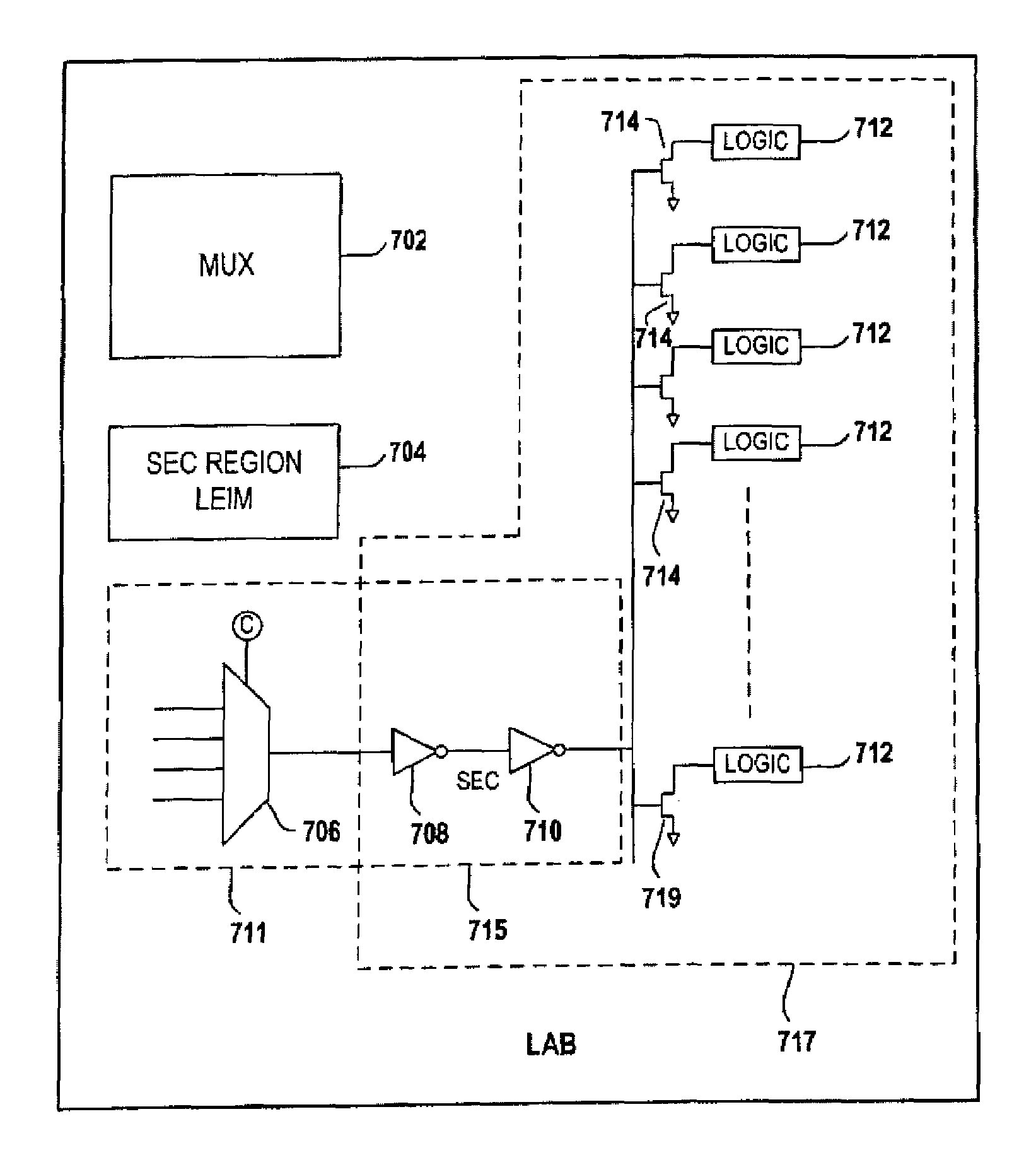

Programmable Logic Device With On-Chip User Non-Volatile Memory

ActiveUS20160274816A1Easy to useLow costInput/output to record carriersDigital computer detailsControl signalErasable programmable logic device

The present invention discloses a programmable logic device with on-chip user non-volatile memory, comprising: a programmable logic array, which is a user programmable logic array and comprises a SRAM array and a logic block array with an interface; the SRAM array is used to store configuration data to control the logic block array in real time, therefore, the logic block can be formed to perform the function a user desires; a non-volatile memory block, comprising one or more segments storing configuration data and one or more segments storing user data which is used during FPGA's normal operation after configuration; the non-volatile memory block has only one interface, and the non-volatile memory block connects to a programming controller through the interface; a programming controller, which can randomly access the non-volatile memory through a data bus, an address bus, and corresponding control signals.

Owner:GOWIN SEMICON CORP LTD

Method of reducing leakage current using sleep transistors in programmable logic device

ActiveUS7518399B1Reduce leakage currentMinimize leakage currentPower reduction by control/clock signalSolid-state devicesProgrammable logic deviceErasable programmable logic device

A programmable logic device (PLD) having minimal leakage current for inactive logic blocks is provided. The PLD includes an array of logic blocks. Among the array of logic blocks, one of the array of logic blocks monitors the level of activity of each of the remaining logic blocks. The level of activity may be monitored by observing the input and output pin of the logic blocks. The PLD further includes a plurality of driven wires defining a routing pattern between the array of logic blocks. When one of the array of logic blocks detect inactivity in any one of the remaining logic blocks for a certain duration, the one of the array logic blocks transmits a signal invoking a sleep mode for the inactive logic blocks. A sleep transistor with a threshold voltage level that is capable minimizing the leakage current is associated with each of the remaining block. The gate of the sleep transistor receives the signal transmitted by one of the array logic blocks and the signal switches off the sleep transistor.

Owner:TAHOE RES LTD

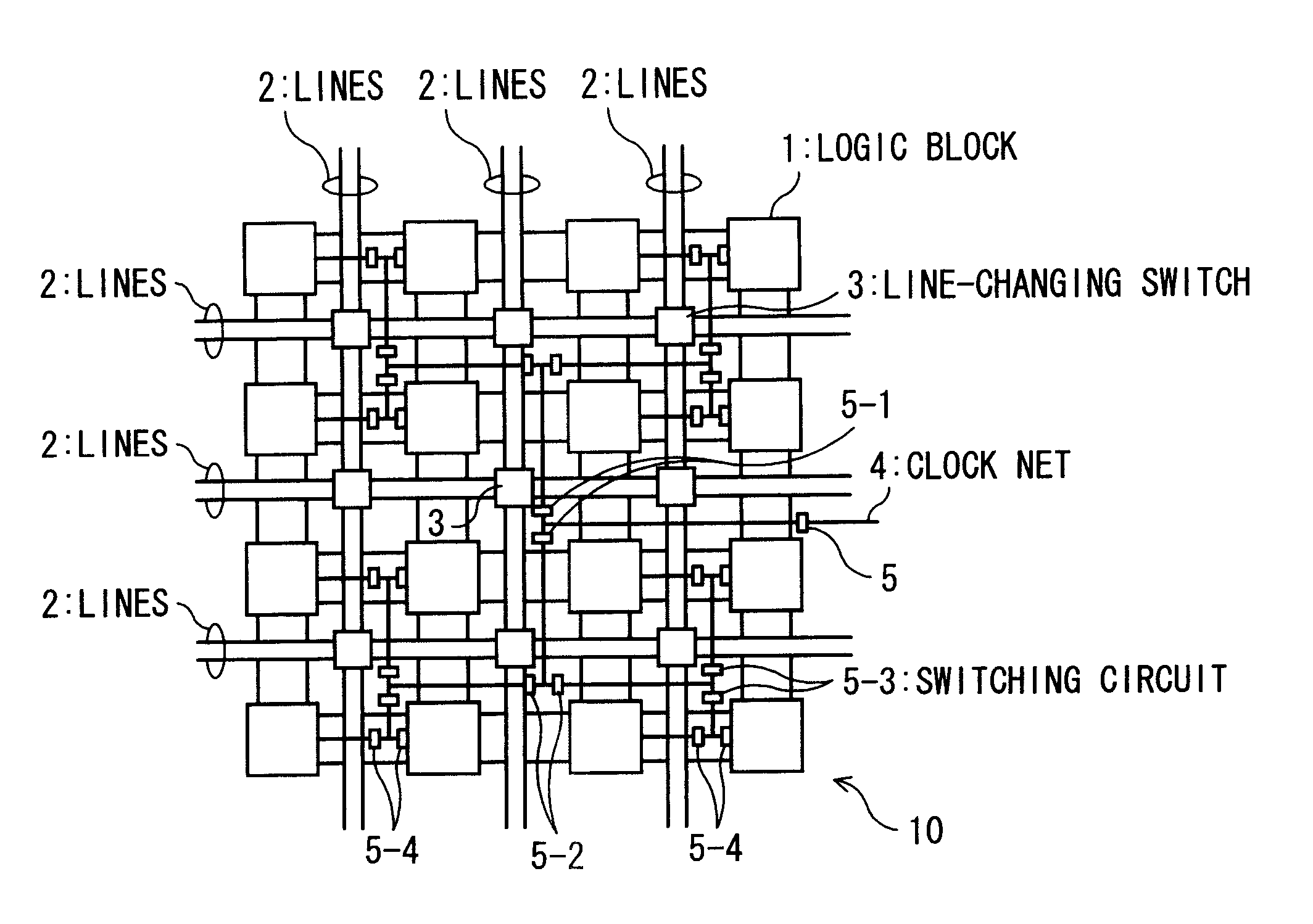

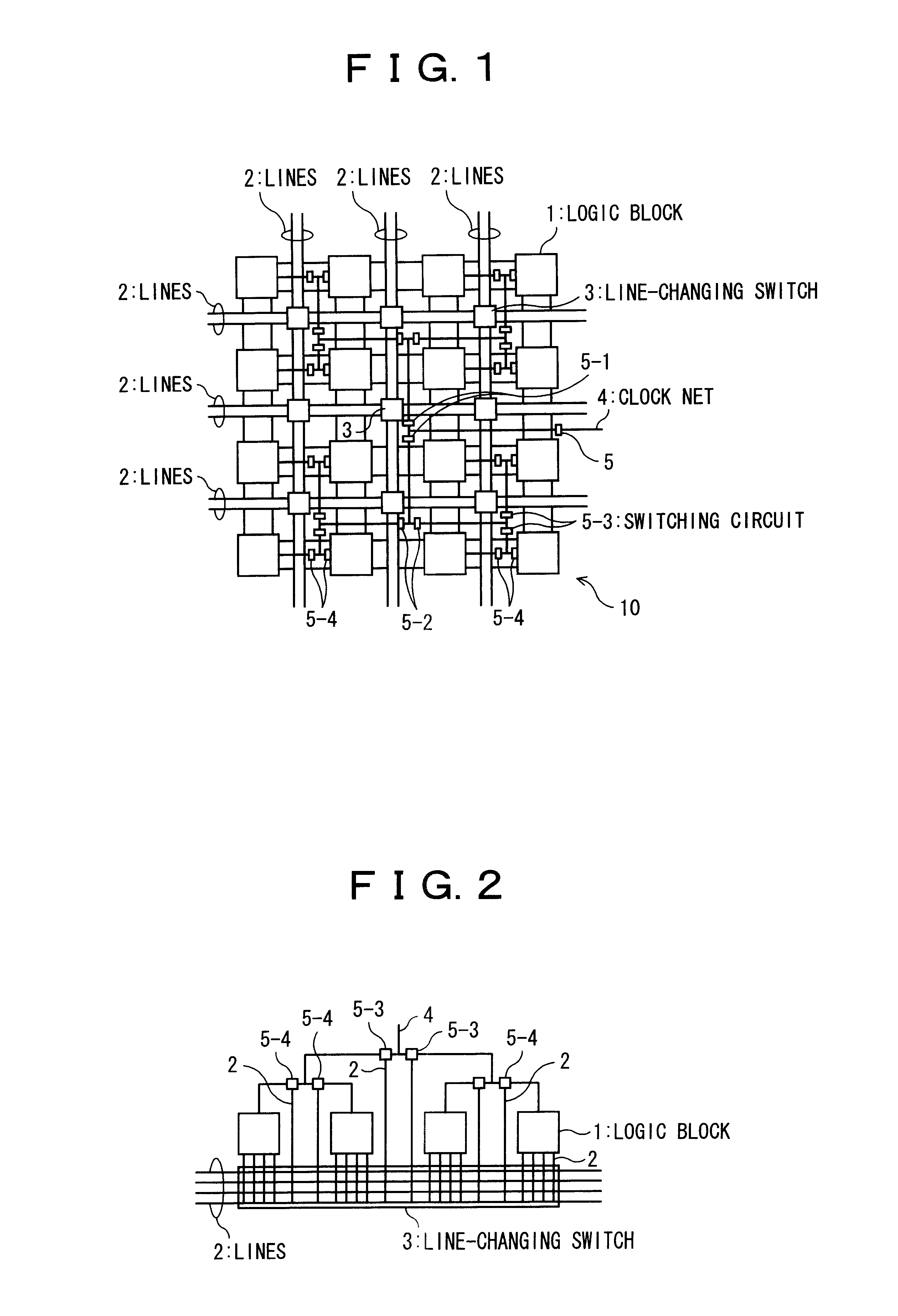

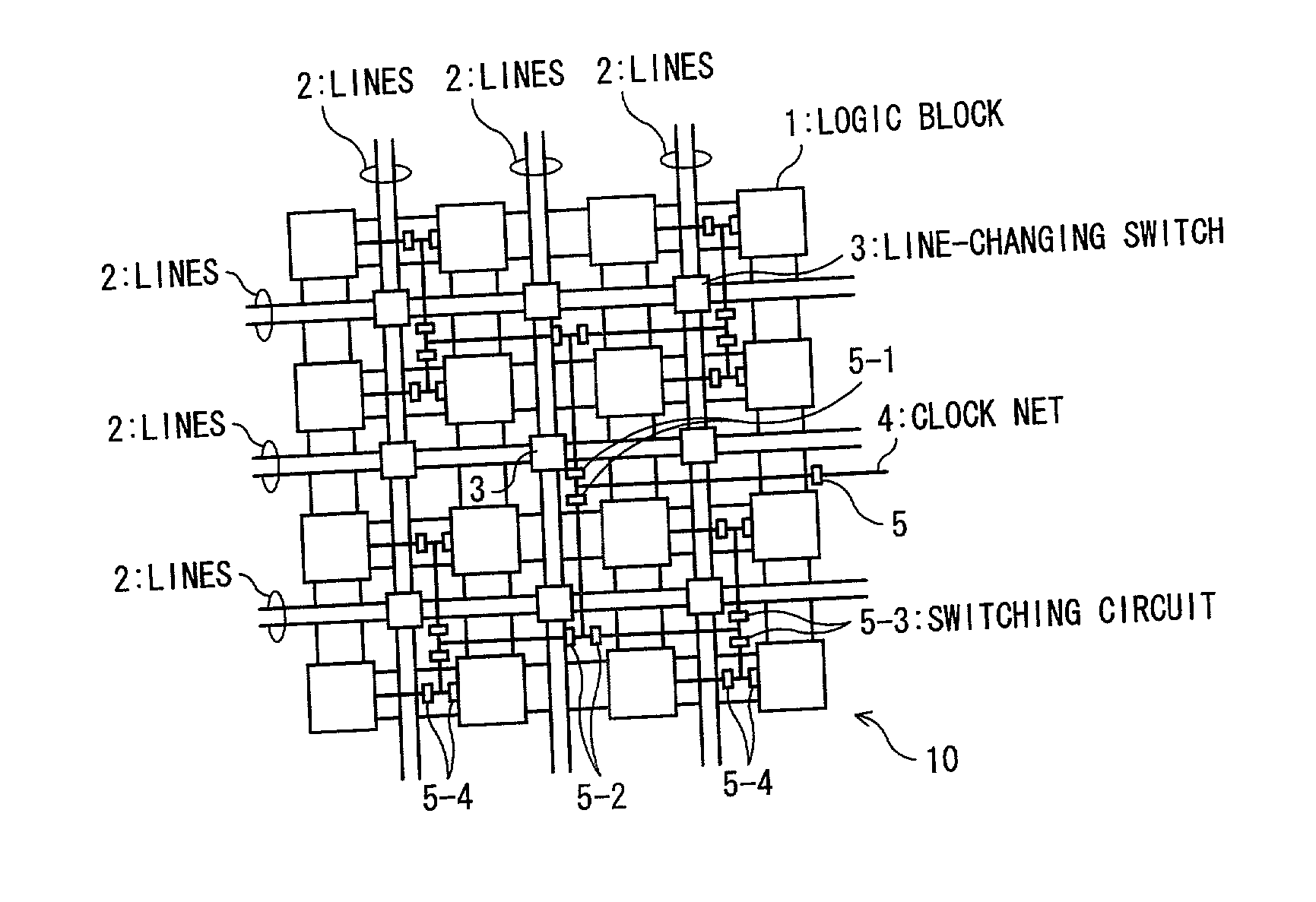

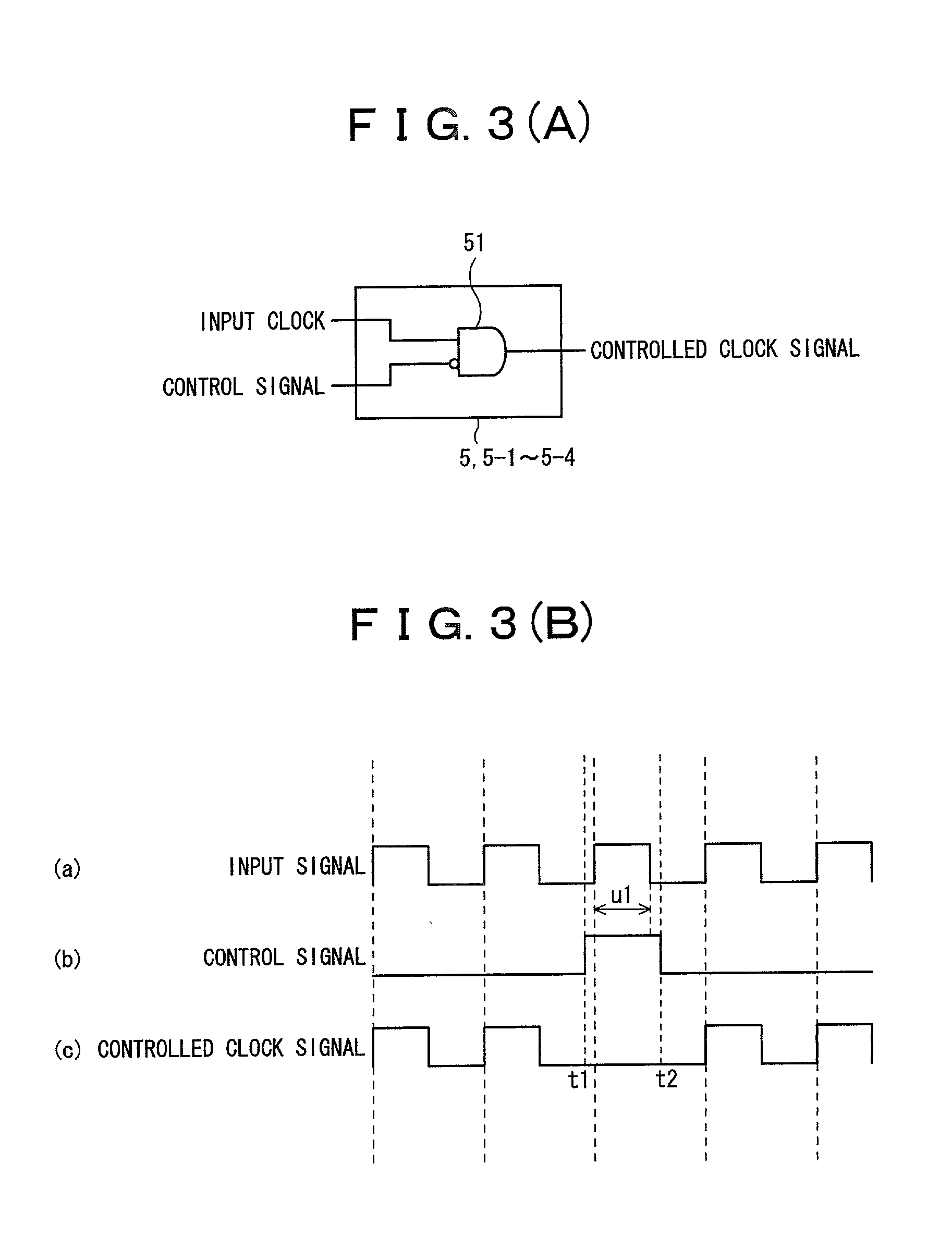

Programmable logic device and method of controlling clock signal thereof

InactiveUS6703859B2Solid-state devicesSemiconductor/solid-state device manufacturingProgrammable logic deviceErasable programmable logic device

An object of the present invention is to provide a programmable logic device which intends to reduce electric power consumption or heat generation sufficiently as a whole device while preventing a clock skew from being generated and retaining a processing speed of the device. To this end, according to the present invention, there is provided a device including logic blocks for carrying out logical operation, lines for connecting the logic blocks, line-changing means for changing the state of lines connecting the logic blocks by programming, a clock net for supplying a clock signal to each of the logic blocks, and clock control means for dynamically controlling switching between a clock signal supply mode and a clock signal stop mode for each logic block so that at least one non-active logic block of the logic blocks can be stopped from being supplied with the clock signal.

Owner:FUJITSU LTD

Programmable logic device and method of controlling clock signal thereof

InactiveUS20030107400A1Solid-state devicesSemiconductor/solid-state device manufacturingProgrammable logic deviceErasable programmable logic device

An object of the present invention is to provide a programmable logic device which intends to reduce electric power consumption or heat generation sufficiently as a whole device while preventing a clock skew from being generated and retaining a processing speed of the device. To this end, according to the present invention, there is provided a device including logic blocks for carrying out logical operation, lines for connecting the logic blocks, line-changing means for changing the state of lines connecting the logic blocks by programming, a clock net for supplying a clock signal to each of the logic blocks, and clock control means for dynamically controlling switching between a clock signal supply mode and a clock signal stop mode for each logic block so that at least one non-active logic block of the logic blocks can be stopped from being supplied with the clock signal.

Owner:FUJITSU LTD

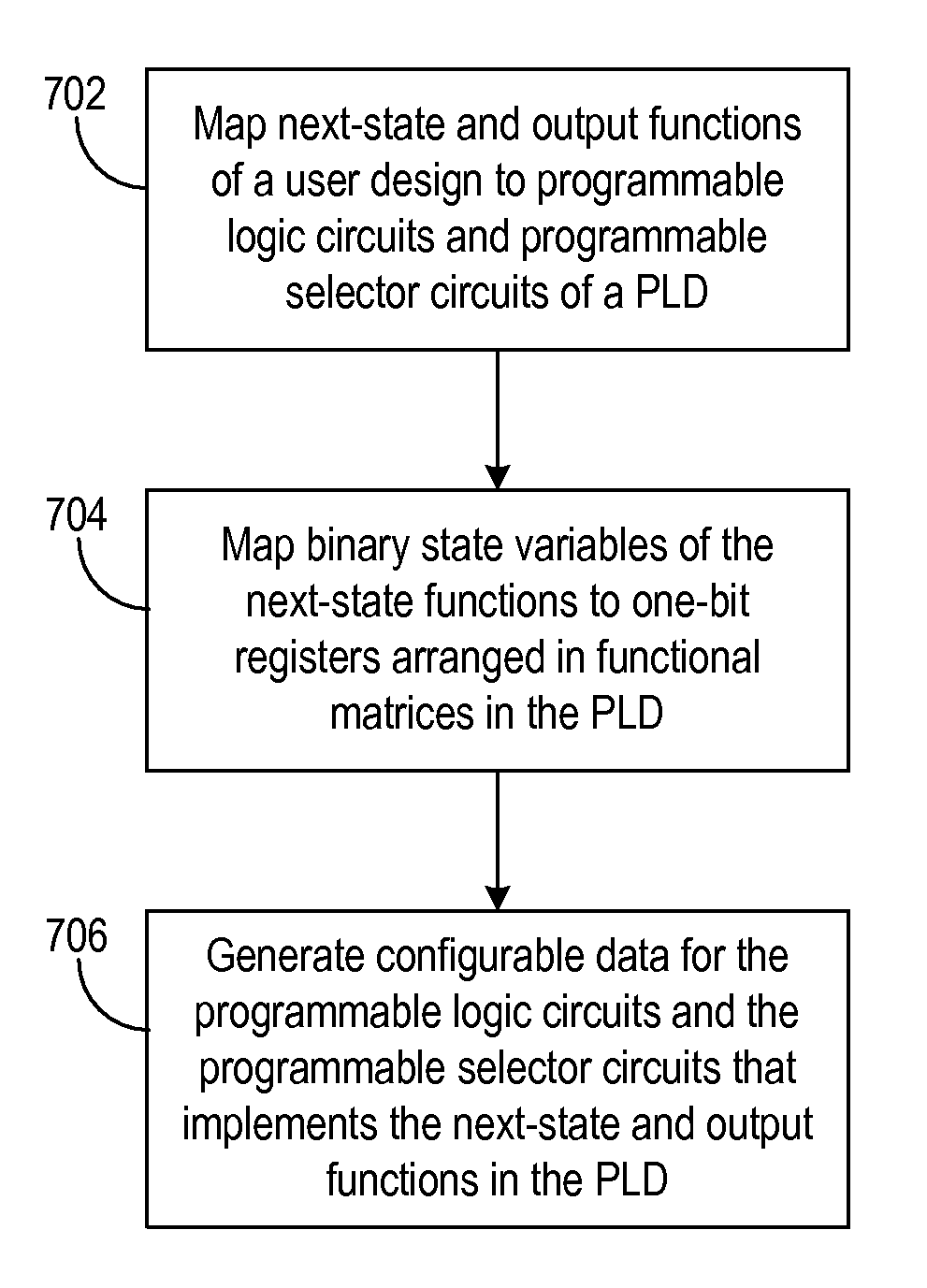

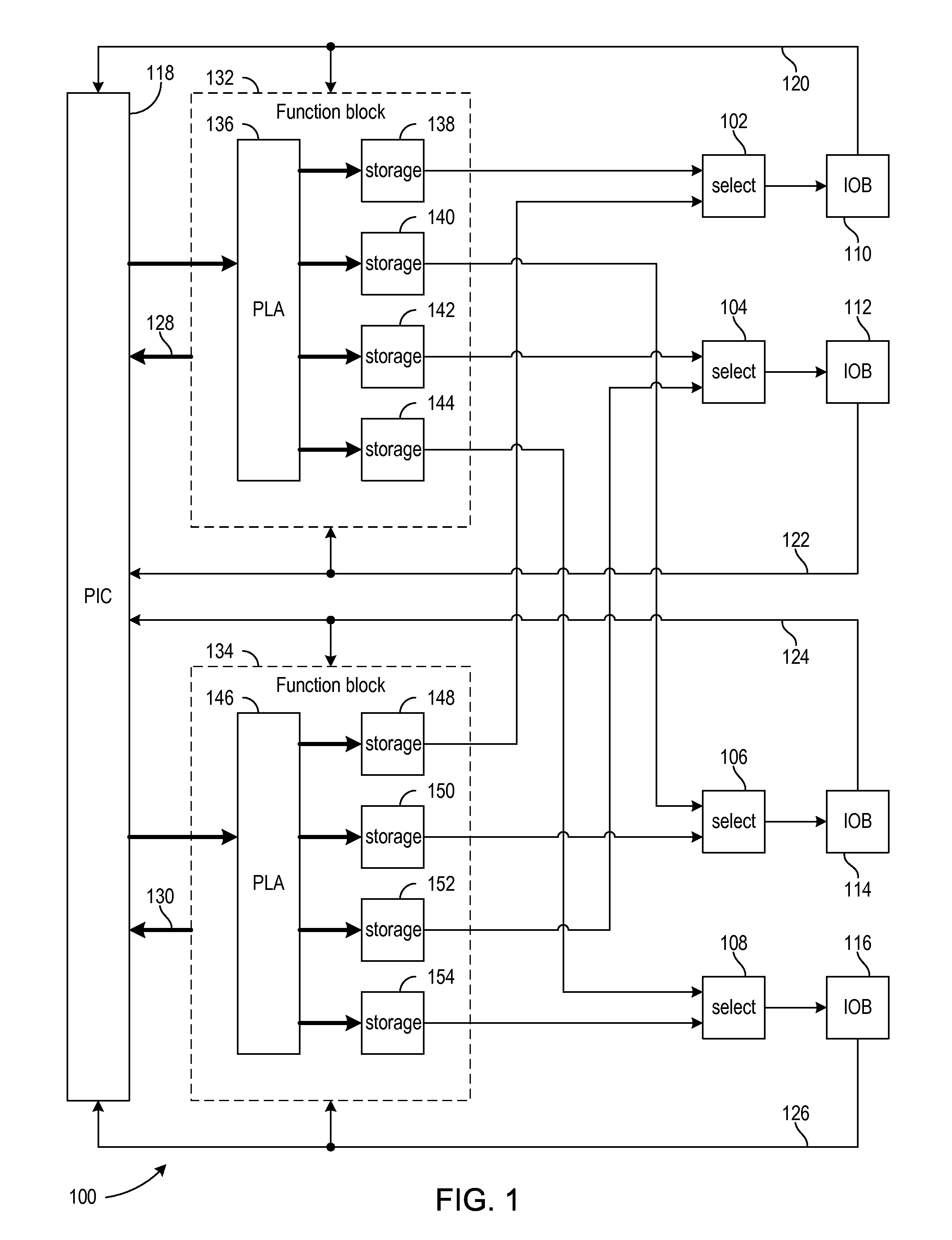

Programmable logic device having a programmable selector circuit

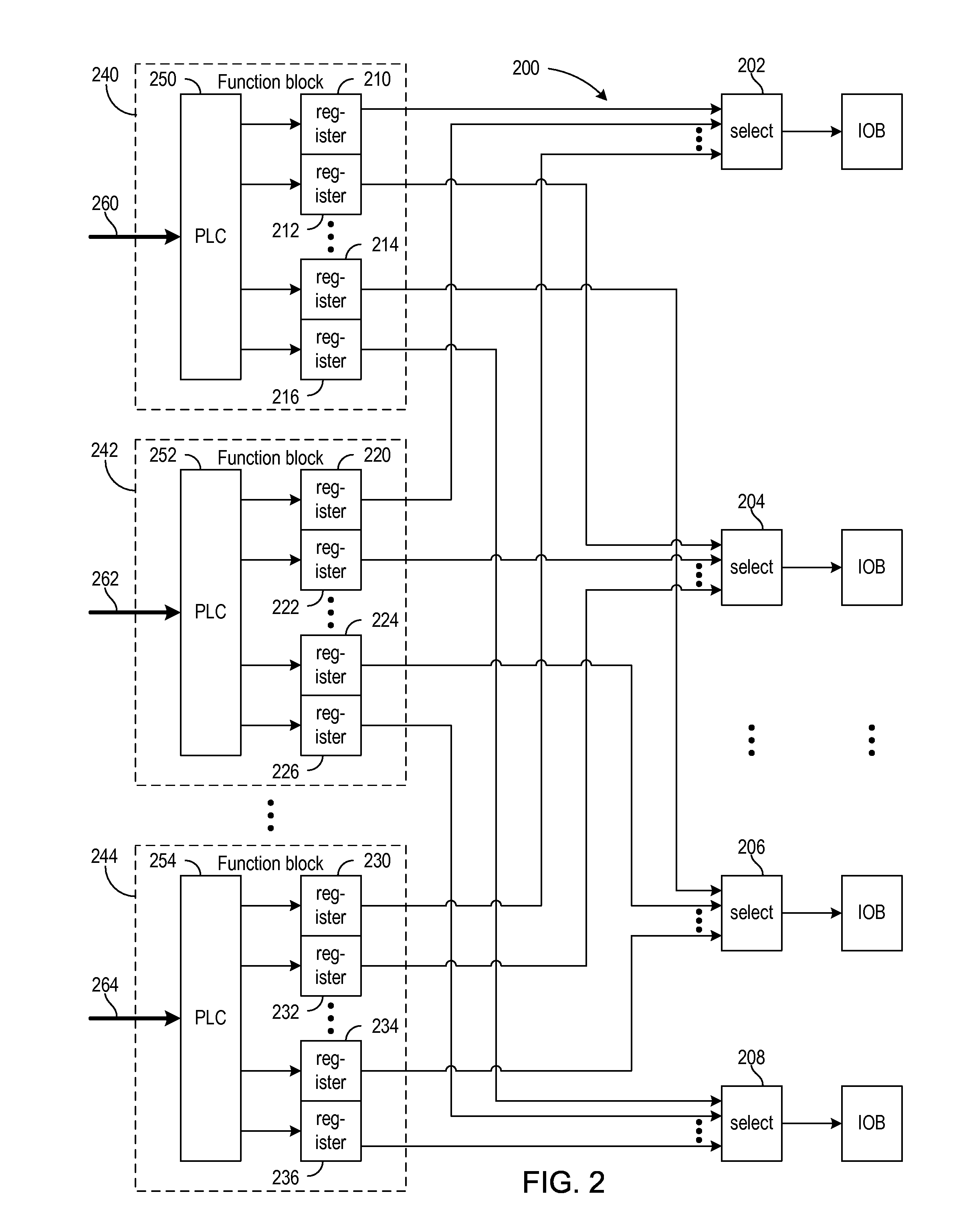

ActiveUS7620929B1Special data processing applicationsLogic circuits using elementary logic circuit componentsProcessor registerProgrammable logic device

A PLD is configurable to efficiently implement a wide variety of user functions. The PLD includes a programmable interconnect circuit, programmable logic circuits, one-bit registers, selector circuits, and input / output blocks. The programmable interconnect circuit is configurable to connect the signal lines of its output ports to the signal lines of its input ports. The programmable logic circuits are configurable to implement a programmable function generating one-bit signal values from a respective output port of the programmable interconnect circuit. The one-bit registers store a respective one of these one-bit signal values. The programmable selector circuits are each coupled to output ports of a plurality of the one-bit registers, with each of these one-bit registers coupled to a respective one of the programmable logic circuits. The programmable input / output blocks are each coupled to an output port of a respective programmable selector circuit and to a respective input port of the programmable interconnect circuit.

Owner:XILINX INC

Prototype verification device for programmable logic devices

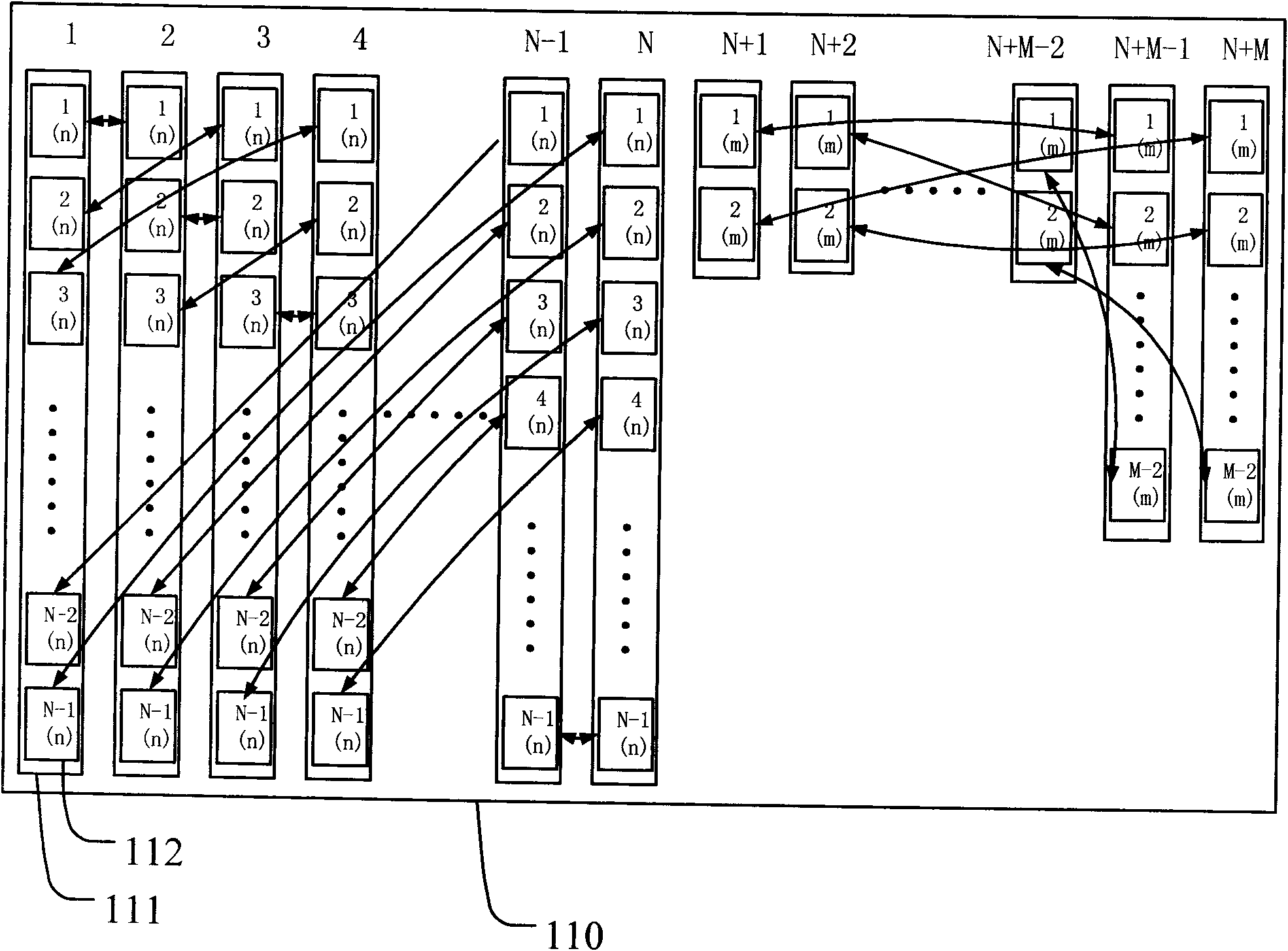

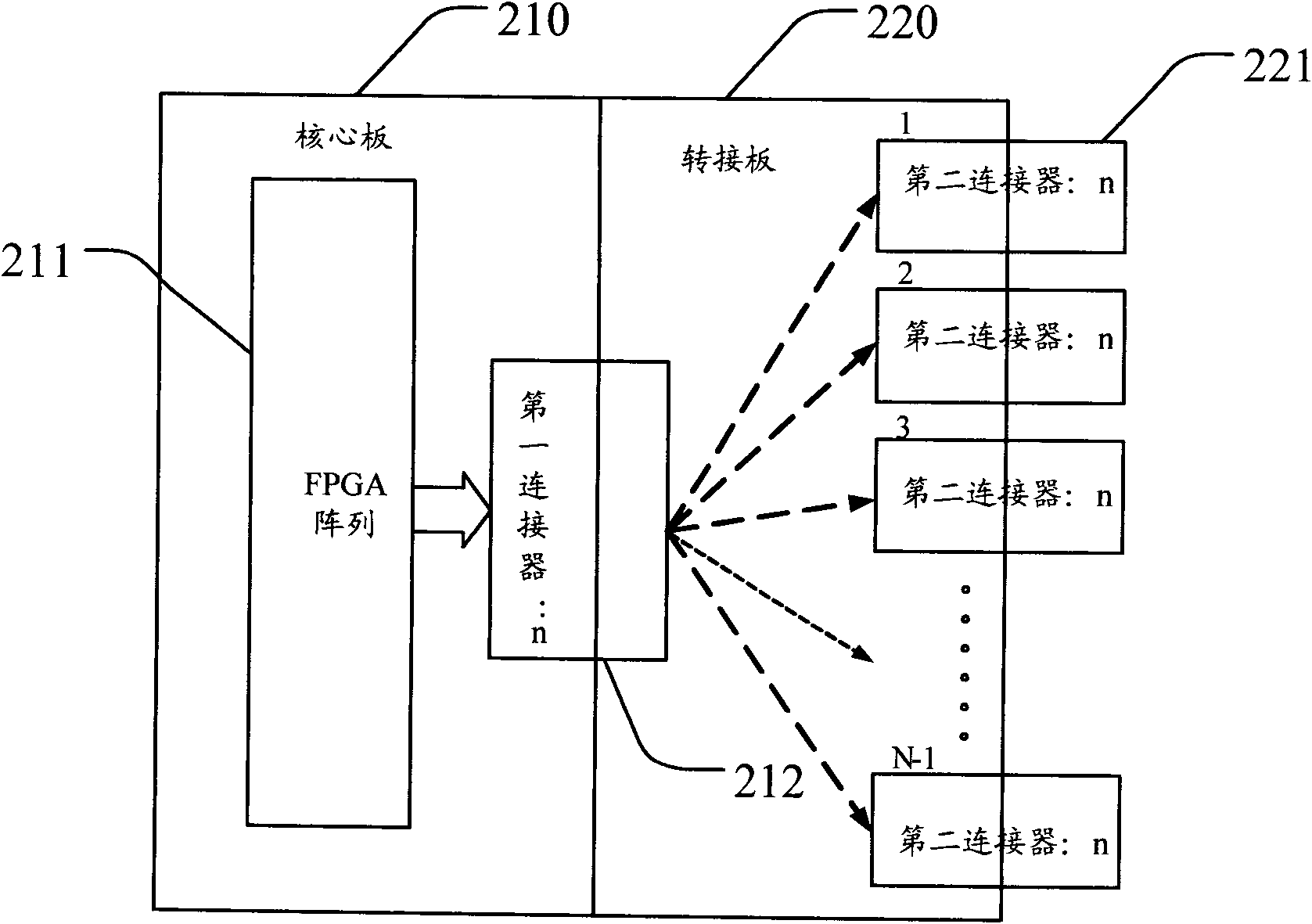

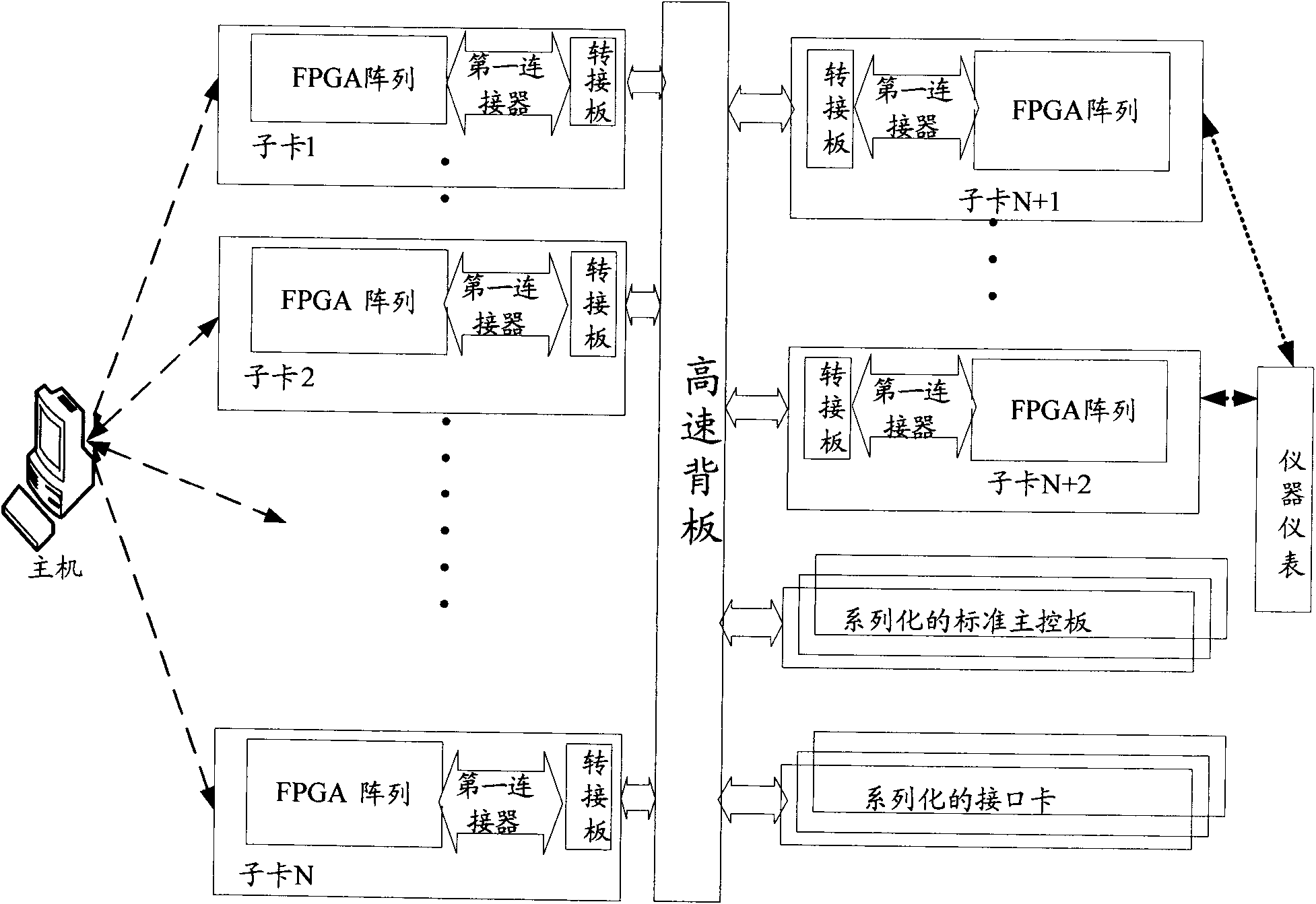

ActiveCN102402474AFlexible connectionQuick buildFunctional testingProgrammable logic deviceModularity

The invention relates to a prototype verification device for programmable logic devices. The prototype verification device comprises a back plate, at least two card slots connected to the back plate, and sub-cards inserted into the card slots, wherein the at least two sub-cards are connected through the back plate; each sub-card comprises a core plate and an adapter plate which are connected through a first connector; the adapter plate is connected to the back plate; the core plate is provided with a programmable logic device array; and the programmable logic device arrays on the at least two sub-cards are connected through the adapter plates, which are connected to the back plate, of the at least two sub-cards. The prototype verification device for the programmable logic devices has a modular and open extensible framework, the core plates can be in flexible connection with the back plate through the adapter plates according to the requirement, and a testing device is quickly constructed according to different requirements, so that one verification device is suitable for testing various chips, and cost is saved.

Owner:SANECHIPS TECH CO LTD

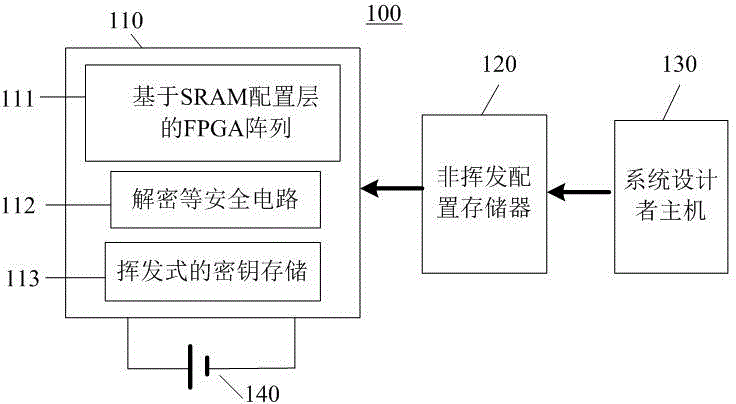

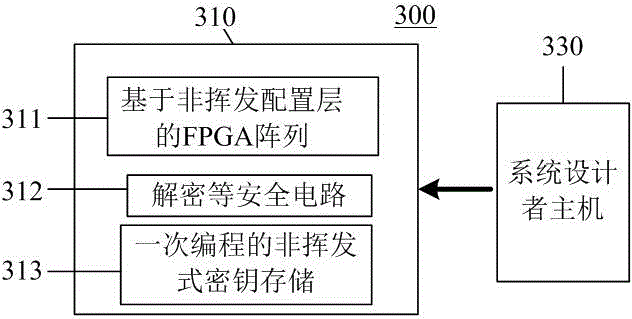

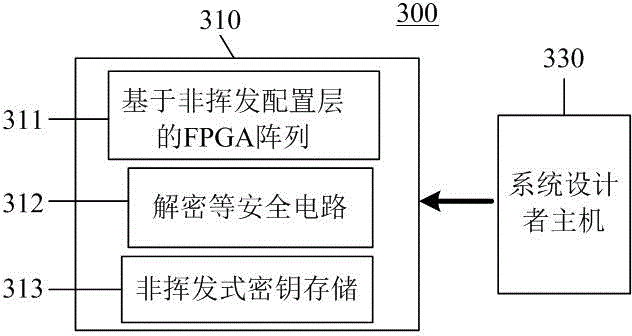

Programmable logic device enabling configuration data flows to be high in safety

ActiveCN104615953AAvoid attacks such as interception and stealingAvoid attacks such as reverse engineeringInternal/peripheral component protectionData streamRandom access memory

The invention belongs to the technical field of programmable logic devices, and particularly relates to a programmable logic device enabling configuration data flows to be high in safety. The programmable logic device comprises a programmable logic array based on an SRAM configuration layer, a non-volatile scratchpad memory, a security mechanism control circuit, a configuration control circuit, an interface module and other modules; the non-volatile scratchpad memory can comprise multiple partitions for storing different data, such as configuration data, secret keys and authentication tags, the non-volatile scratchpad memory further comprises a write-protect circuit, and the write-protect circuit can provide different write-protect control strategies according to the different partitions on the non-volatile scratchpad memory; the non-volatile scratchpad memory specially comprises a resistance type random access memory and other non-volatile memories capable of being compatible with logic processes. The programmable logic device enabling the configuration data flows to be high in safety can prevent the configuration data flows from being stolen and loaded maliciously and enable the configuration data flows to have other security features in the storage and transmitting processes.

Owner:FUDAN UNIV

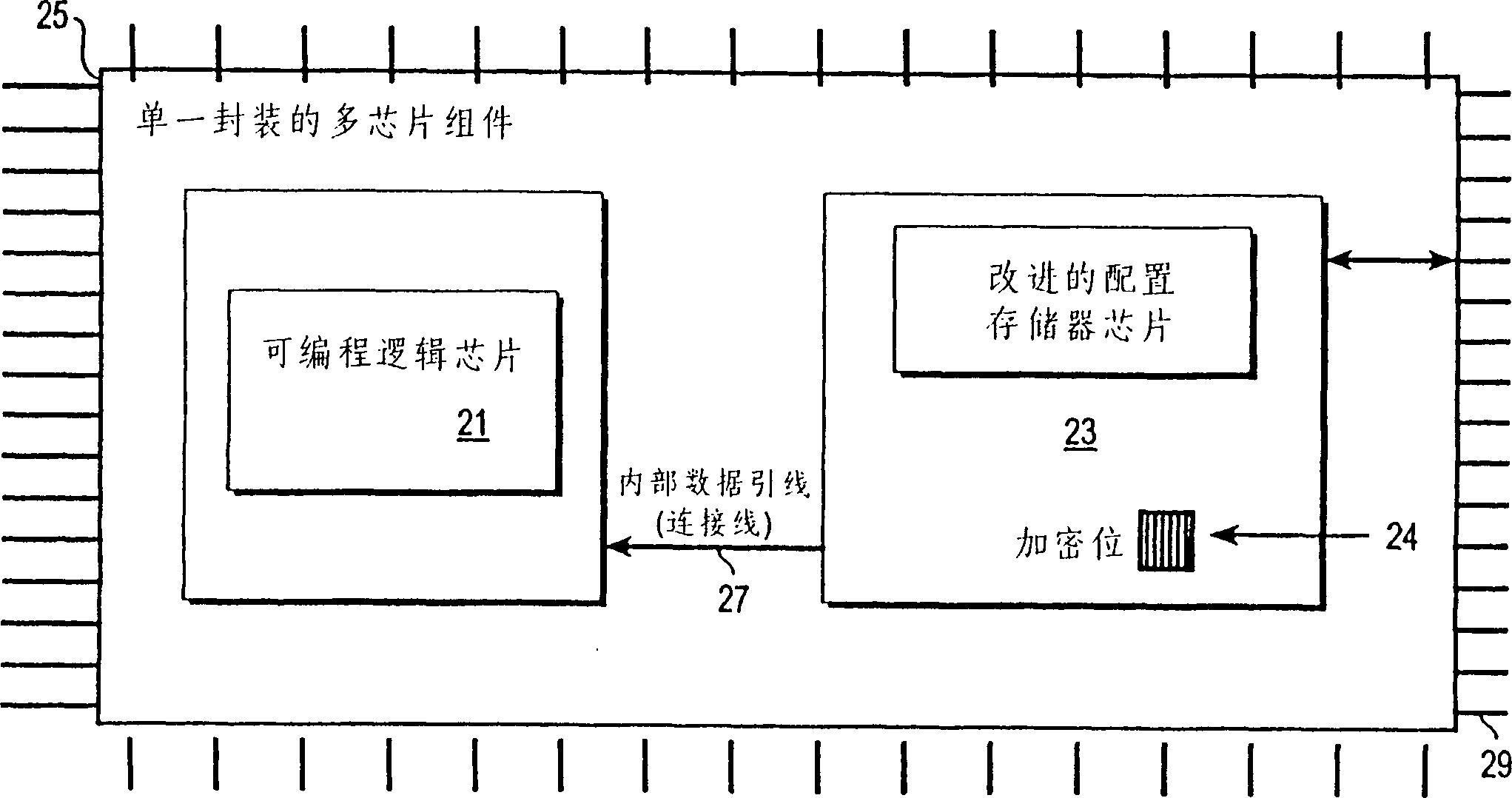

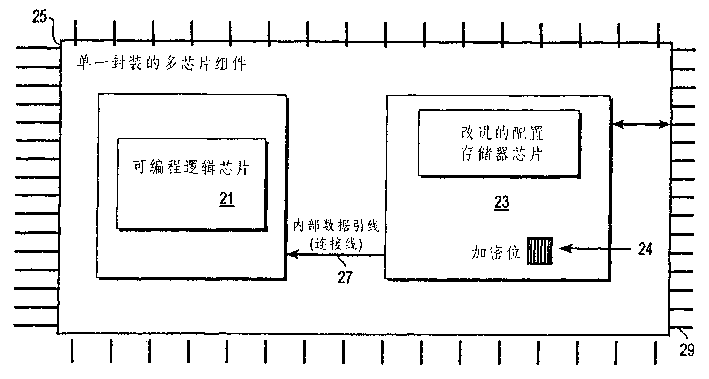

Secure programmable logic device

InactiveCN1444799AAvoid readingRead-only memoriesUnauthorized memory use protectionMemory chipProgrammable logic device

A programmable logic chip (21) and configuration memory chip (23) are both mounted in a multi-chip module (25) to form a single package. The configuration memory has an encryption bit (24). When it is in the first state, the readback of the configuration data in the memory chip can be programmed through the external leads (29) of the package. When the encryption bit is in the second state, Only the erase command can communicate with the memory chip through the external lead. The internal data transmission link (27) provided between the memory chip and the programmable logic chip can only be activated when the encryption bit is in the second state and the memory chip is in readback mode, thereby allowing configuration data to be loaded at power-on into the logic chip.

Owner:ATMEL CORP

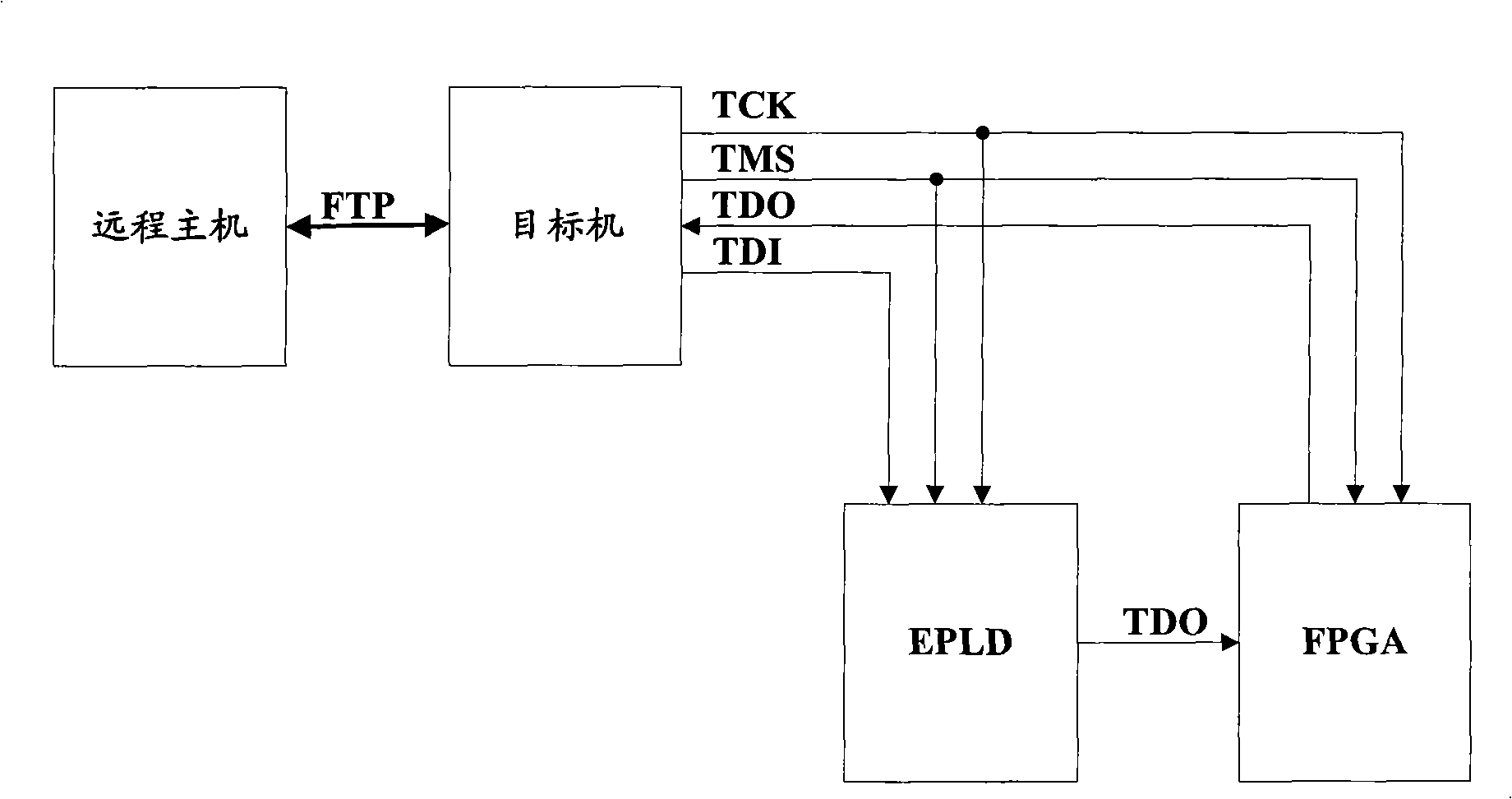

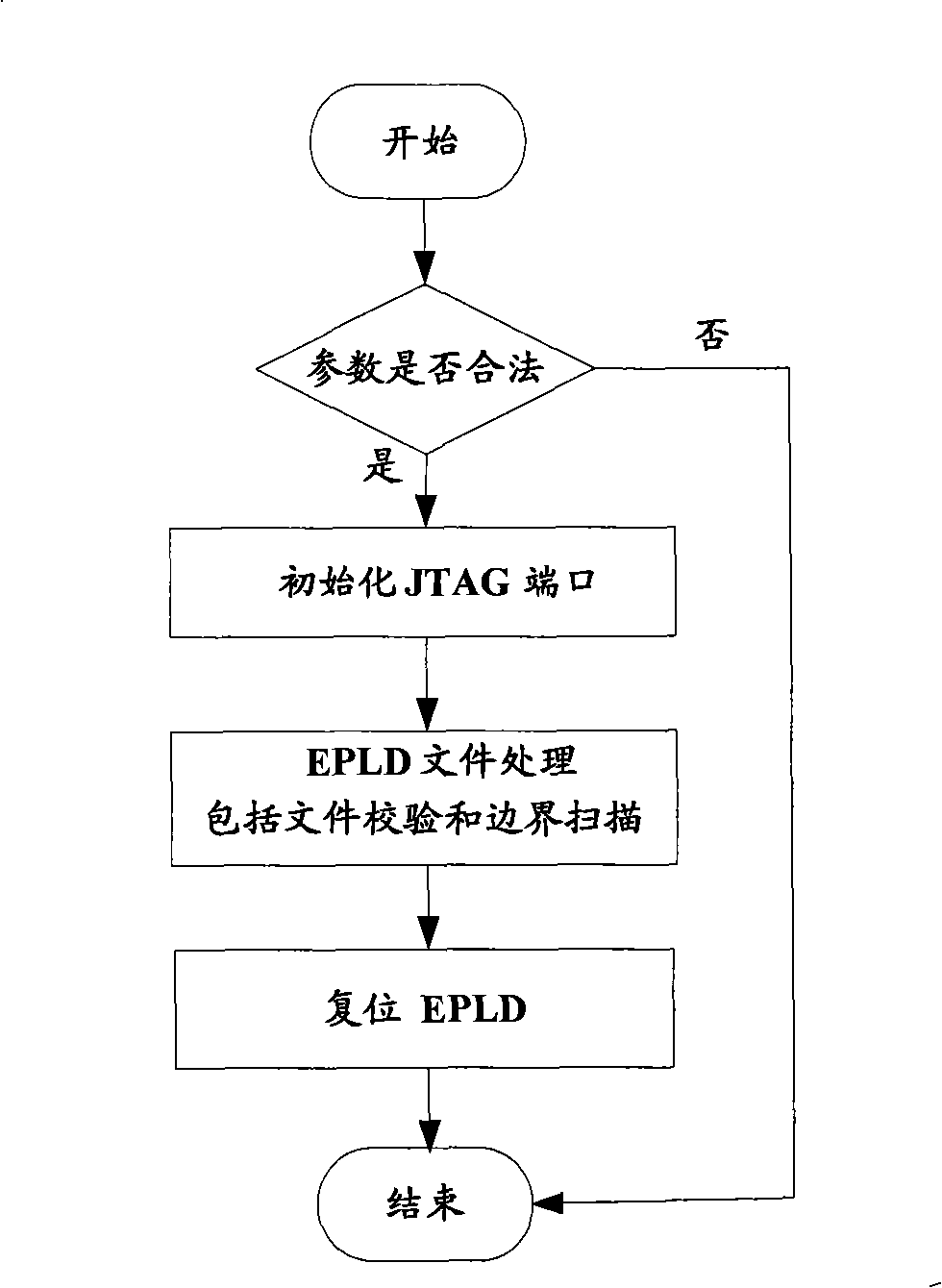

Method for remote downloading erasable programming logic device EPLD

InactiveCN101493770AEasy maintenanceEasy to upgradeProgram loading/initiatingRandom access memoryErasable programmable logic device

The invention provides a method for remotely downloading an erasable programmable logic device (EPLD), which is characterized in that an output / input interface IO of a CPU is used for simulating download signals of a Joint Test Action Group (JTAG), a pre-compiled EPLD program file is downloaded to a flash memory FLASH of a system through a file transfer protocol, then the EPLD file stored in FLASH is read through the CPU and copied to the random-access memory (RAM) of the system, and the EPLD file is downloaded into the EPLD through a JTAG bus. The method can remotely download EPLD which forms a JTAG link with a FPGA, and uses a JTAG port to download the JTAG and the FPGA.

Owner:ZTE CORP

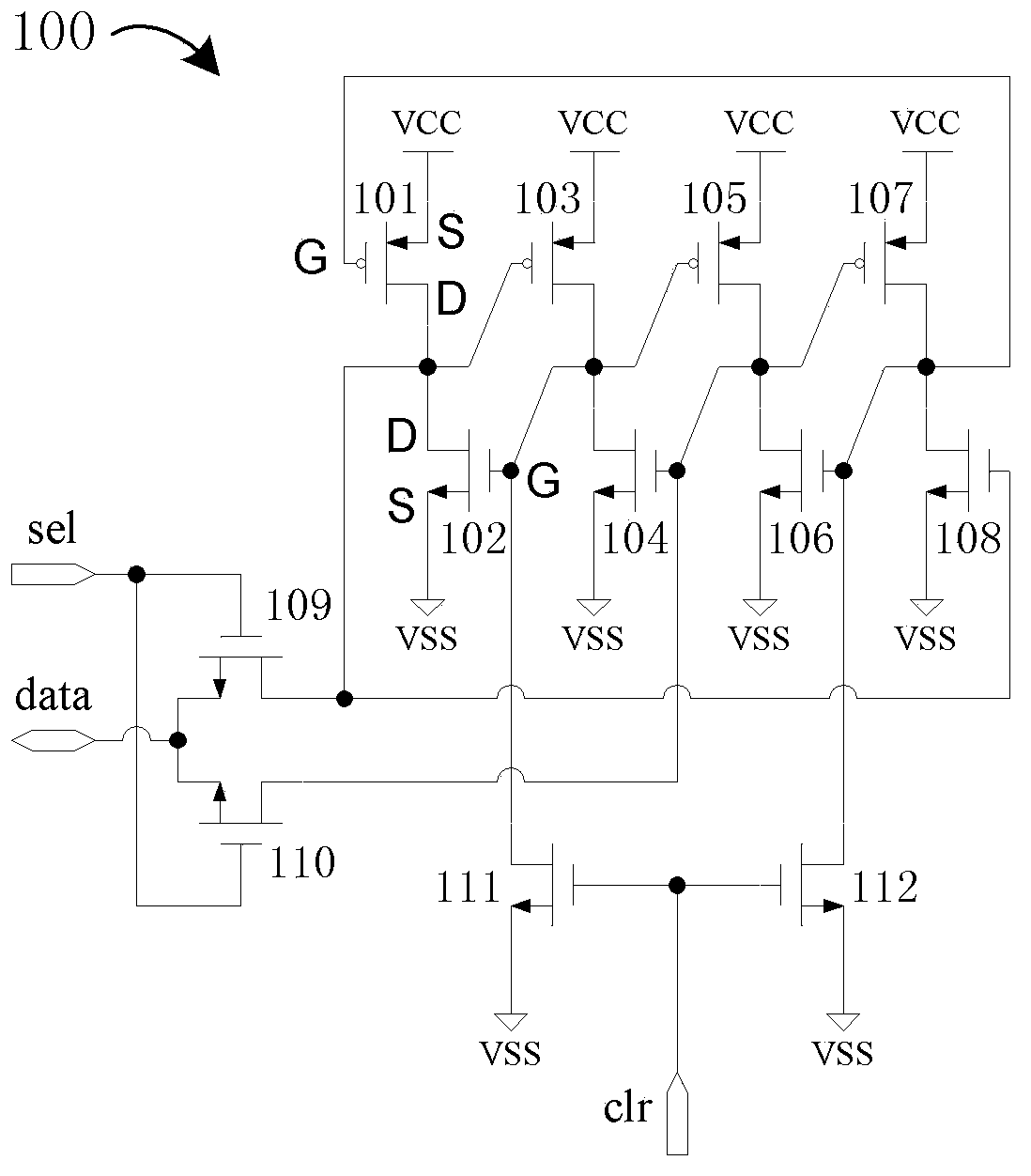

Two-module redundancy configuration memory unit circuit used in programmable logic device

ActiveCN103632715AIncrease flip thresholdMeet configuration requirementsDigital storageProgrammable logic deviceErasable programmable logic device

A disclosed two-module redundancy configuration memory unit circuit used in a programmable logic device comprises a four-level interlocking memory unit consisting of four PMOS tubes and four NMOS tube, tow transmission tubes and two reset tubes. The two-module redundancy configuration memory unit circuit is capable of satisfying the configuration requirements of the programmable logic device by employing MOS tubes as less as possible, and improving the single event upset resistant threshold value of the programmable logic device.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

Volatile memory elements with elevated power supply levels for programmable logic device integrated circuits

ActiveCN101356584AImprove performanceReduce signal degradationSolid-state devicesDigital storageProgrammable logic deviceErasable programmable logic device

Integrated circuits are provided that have volatile memory elements. The memory elements produce output signals. The integrated circuits may be programmable logic device integrated circuits containing programmable core logic including transistors with gates. The core logic is powered using a core logic power supply level defined by a core logic positive power supply voltage and a core logic ground voltage. When loaded with configuration data, the memory elements produce output signals that are applied to the gates of the transistors in the core logic to customize the programmable logic device. The memory elements are powered with a memory element power supply level defined by a memory element positive power supply voltage and a memory element ground power supply voltage. The memory element power supply level is elevated with respect to the core logic power supply level.

Owner:INTEL CORP

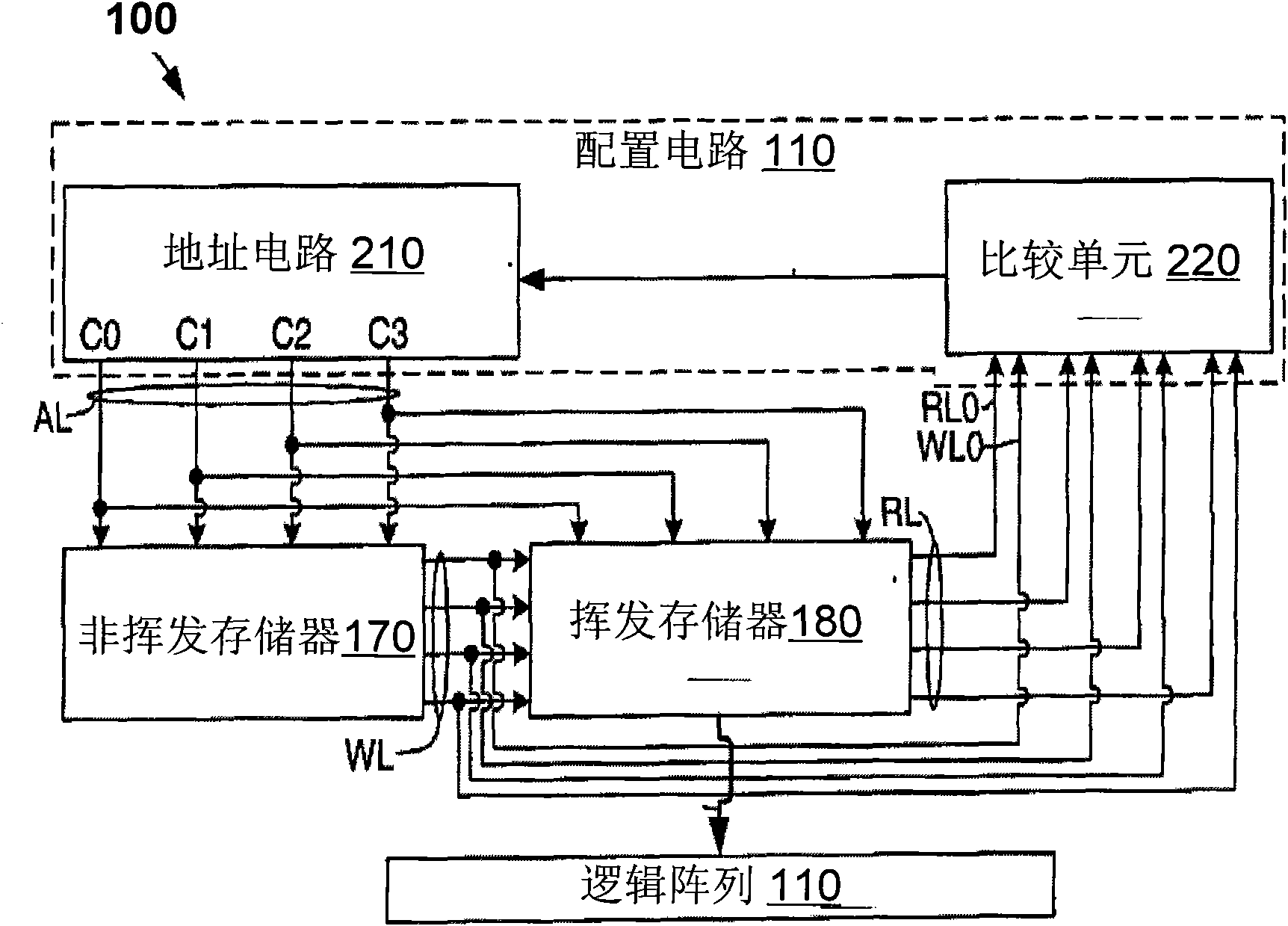

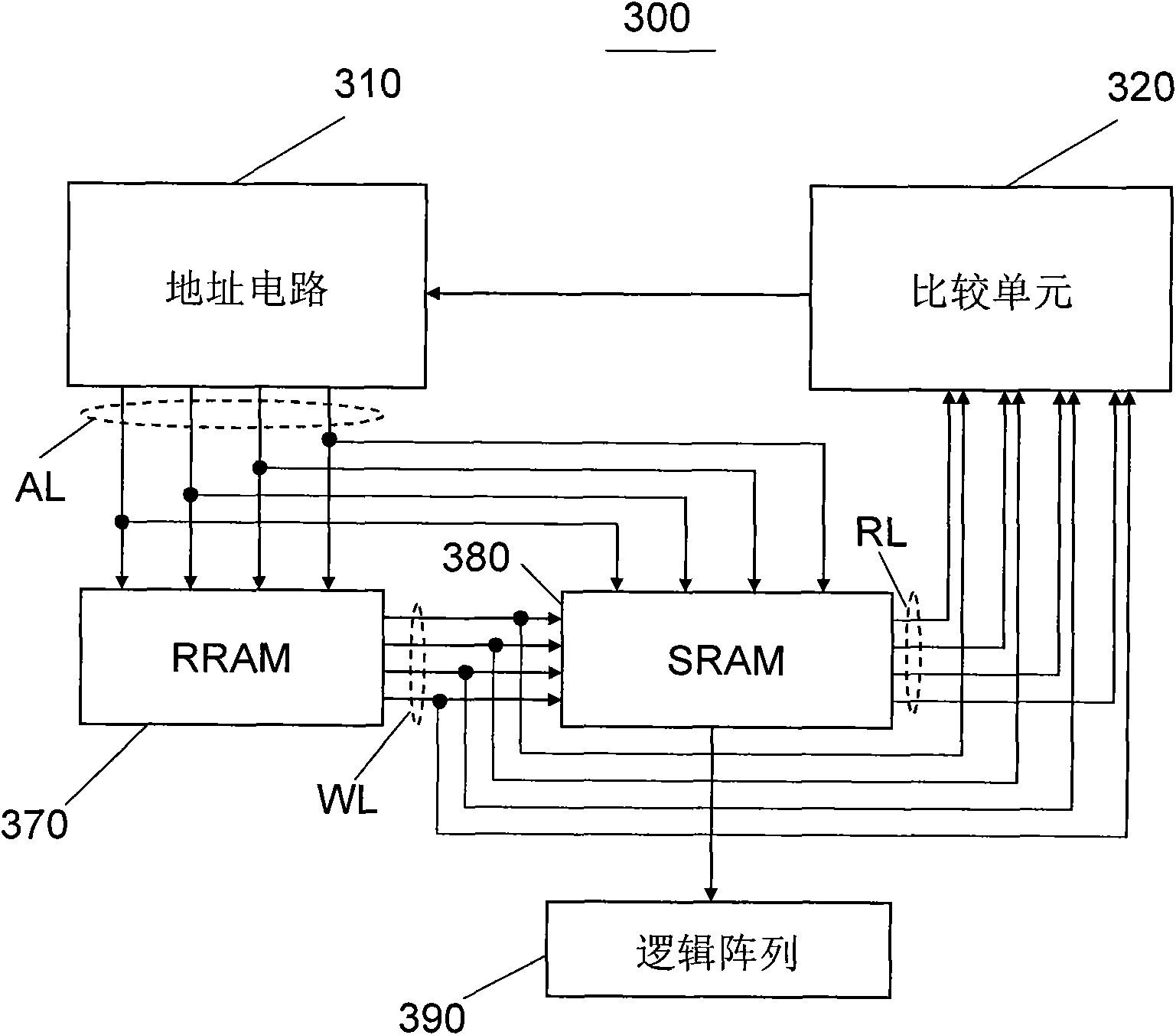

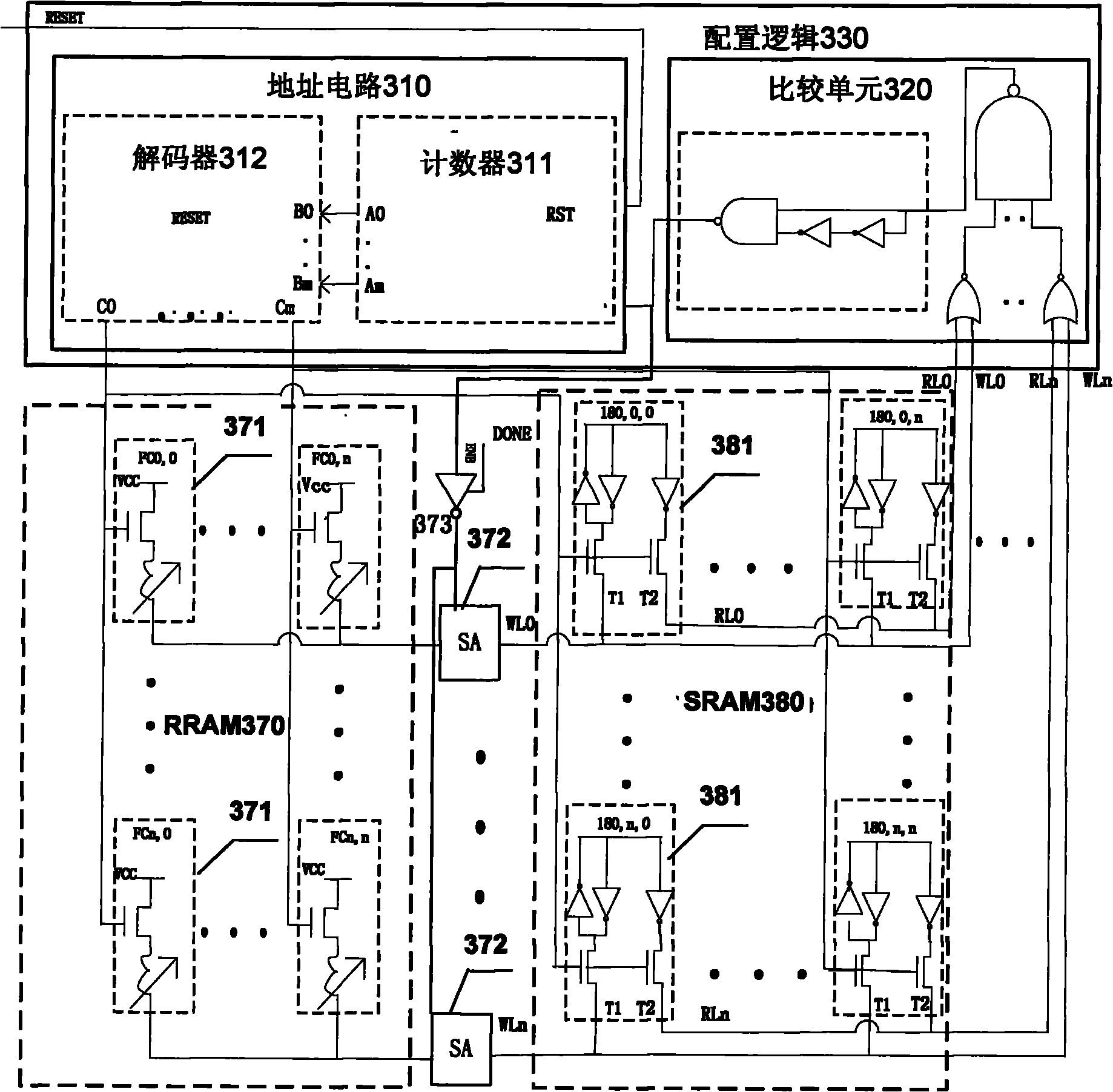

Single chip structured programmable logic device with resistance random access memory (RAM) module

InactiveCN102169711AAnti-radiation hasRadiation Hardness AchievedDigital storageStatic random-access memoryField programmable logic devices

The invention belongs to the technical field of programmable logic device and particularly discloses a programmable logic device. The programmable logic device comprises an address circuit module (310), a comparison unit (320), an SRAM (Static Random Access Memory) module (380), a logic array (390) and a resistance RAM module (370) which is used for overcoming the soft error rate in the SRAM module, wherein the resistance RAM module realizes single chip integration with the address circuit module, the comparison unit, the SRAM module and the logic array. The programmable logic device not only can overcome the SER (Symbol Error Rate) problem in the SRAM, but also has the characteristics of single chip, small size, radiation resistance, low power consumption and low cost.

Owner:FUDAN UNIV

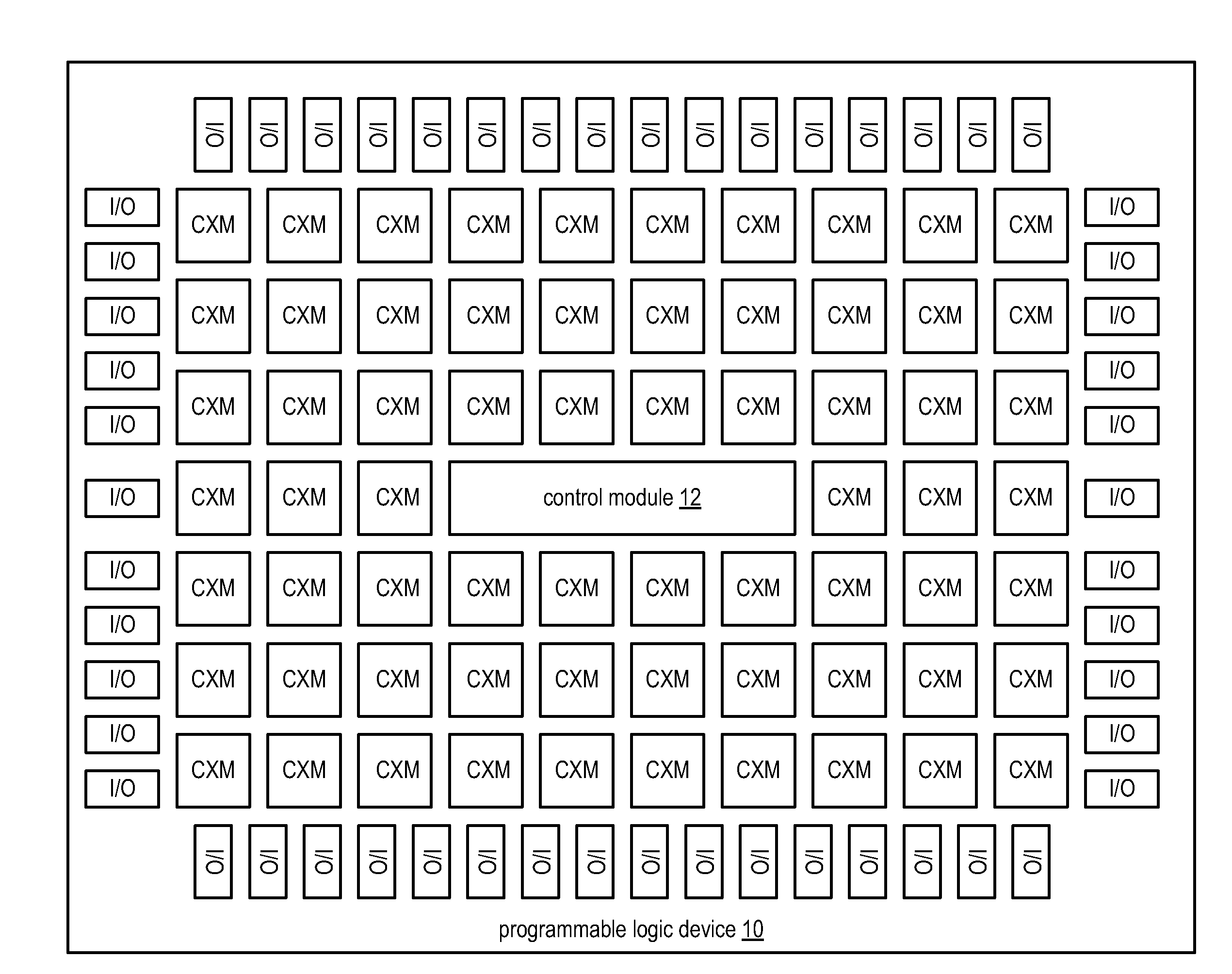

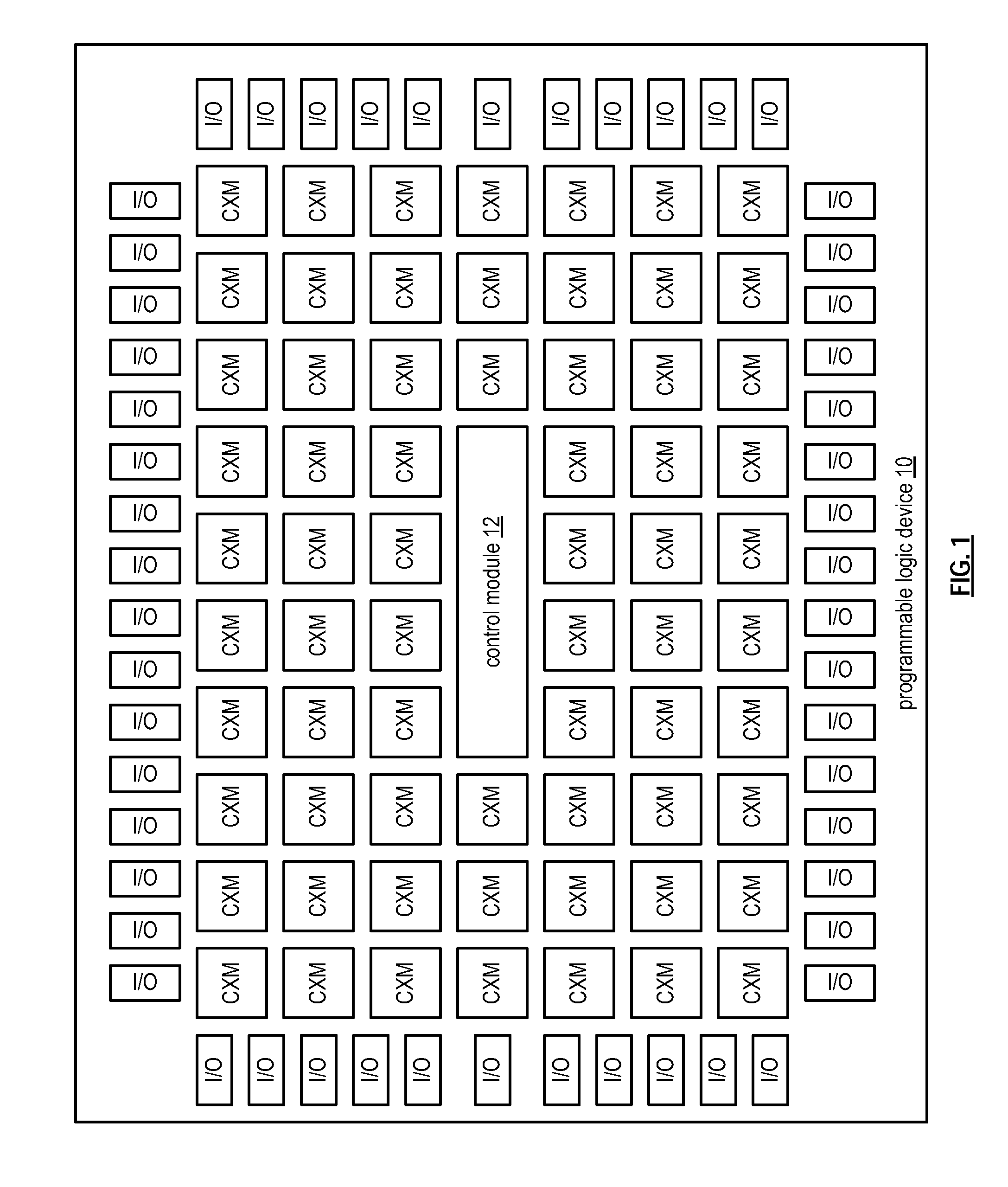

Wireless programmable logic device

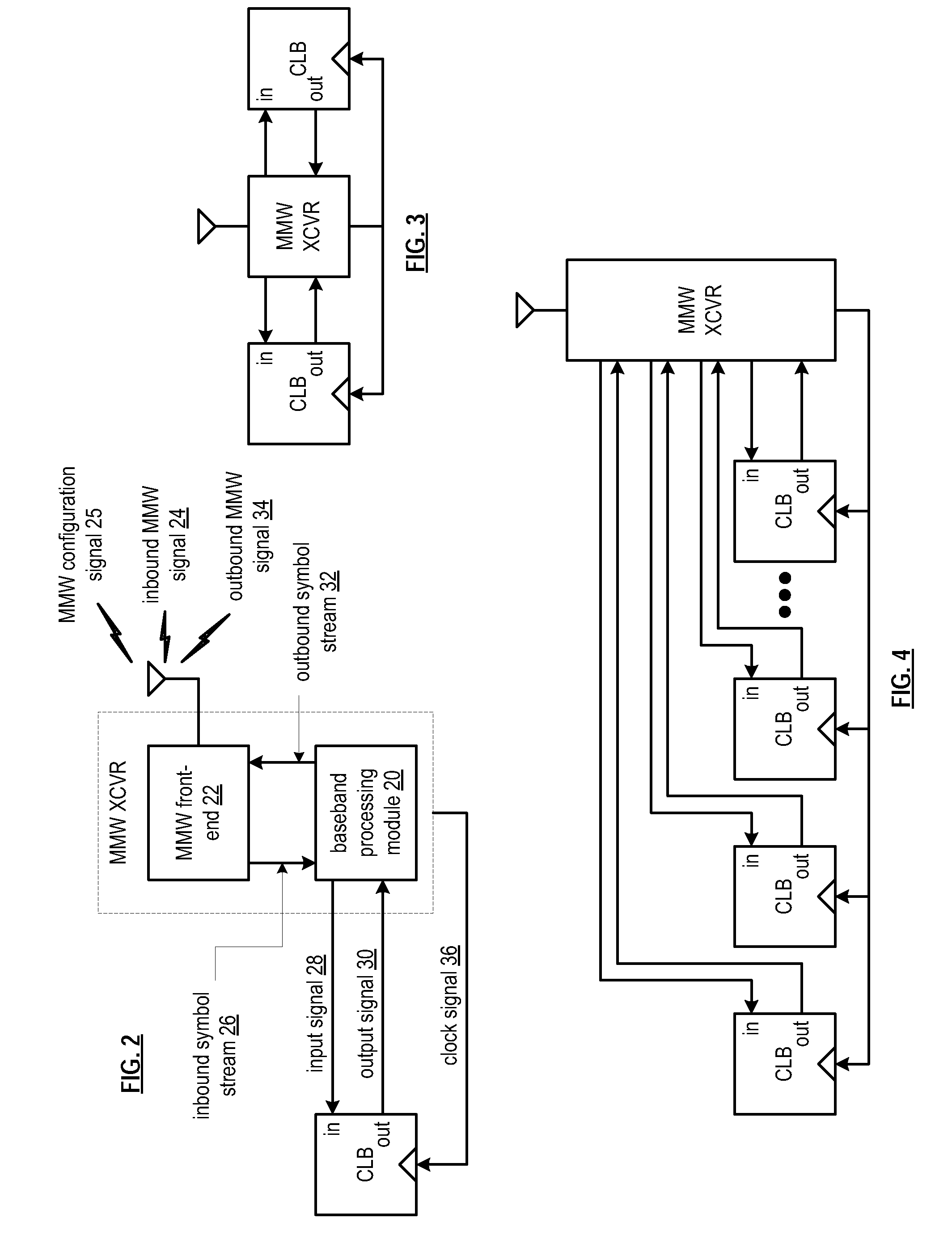

InactiveUS20090196199A1Data switching by path configurationSubstation equipmentProgramming languageTransceiver

A programmable logic device includes a control module, a plurality of input / output modules, and a plurality of configurable logic and millimeter wave (MMW) transceiver modules (CXM). The control module is operable to: receive a programming instruction; identify a set of the plurality of CXMs based on the programming instruction; identify at least one of the plurality of input / output modules based on the programming instruction; determine configuration of the set of the plurality of CXMs and the at least one of input / output modules in accordance with the programming instruction; and allocate wireless communication resources of the programmable logic device to support the configuration of the set of the plurality of CXMs and the at least one of the plurality of input / output modules.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

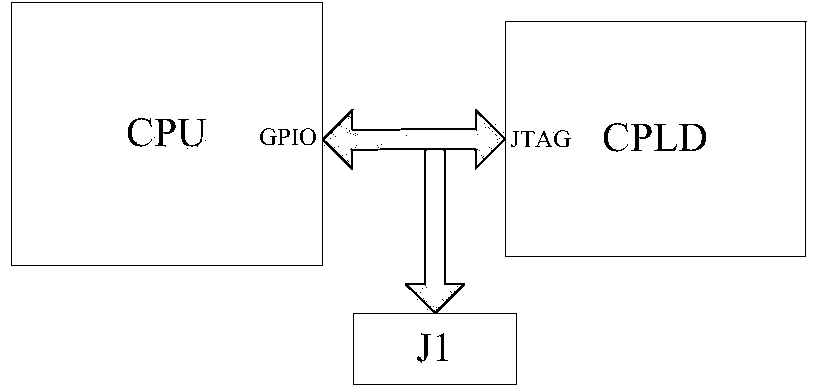

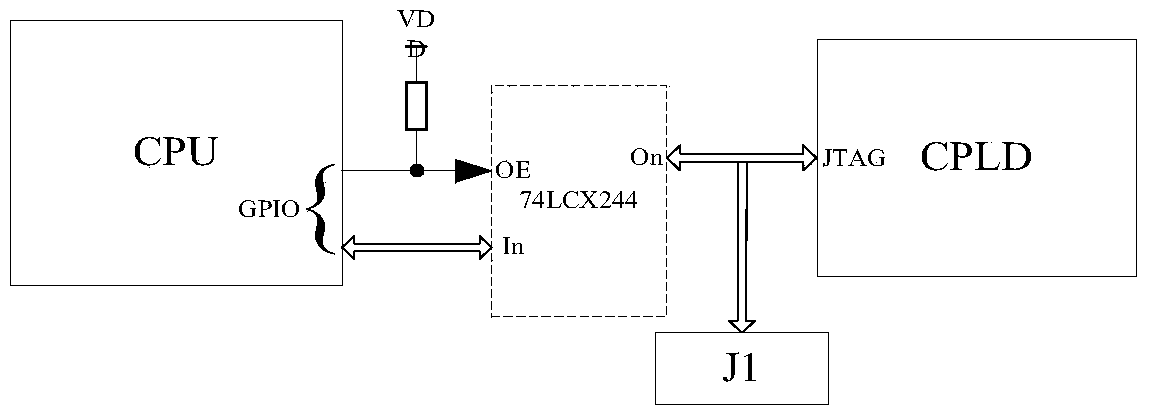

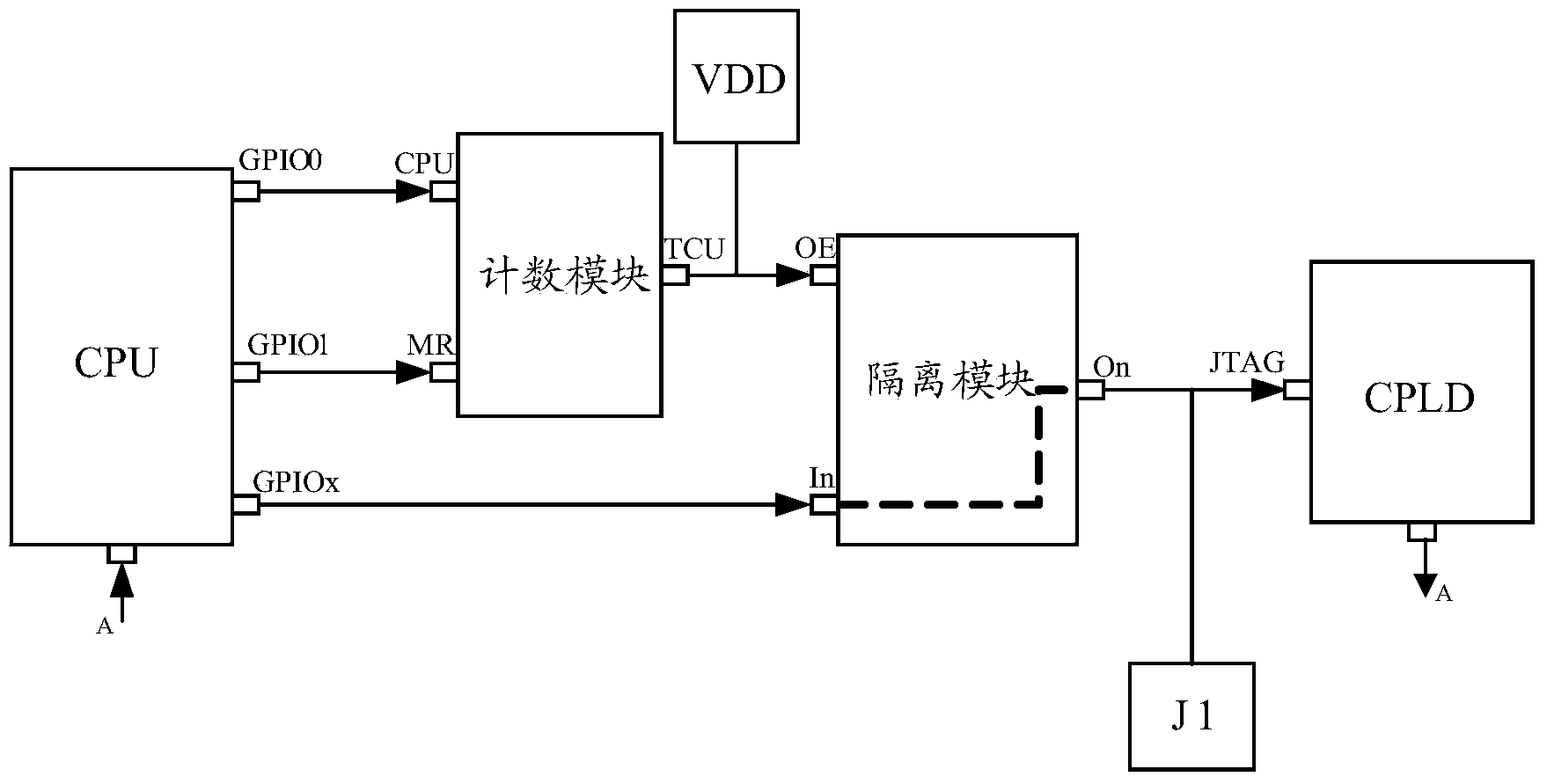

Device and method for mounting CPLD (complex programmable logic device) chip

The invention discloses a device and a method for mounting a CPLD (complex programmable logic device) chips. The device and the method have the advantages that only a low-cost counting module is additionally arranged between a CPU (central processing unit) and an isolation module, so that time sequences of special JTAG (joint test action group) interfaces can be assuredly simulated by GPIO (general purpose input / output) pins of the CPU no mater whether GPIO ports are in high-level states or low-level states or high-impedance states when the CPU is powered on and reset, and the CPLD chip can be reliably mounted for upgrading / updating software.

Owner:NEW H3C TECH CO LTD