Device and method for mounting CPLD (complex programmable logic device) chip

A chip and counting module technology, applied in the field of devices for loading CPLD chips, can solve problems such as conflicts, and achieve the effect of reliable loading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

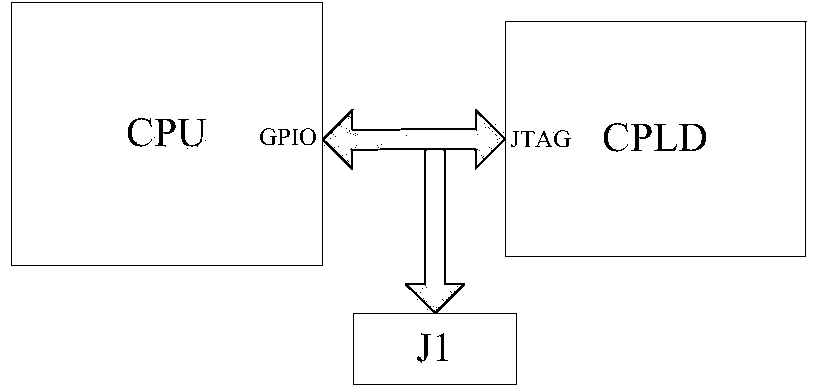

Problems solved by technology

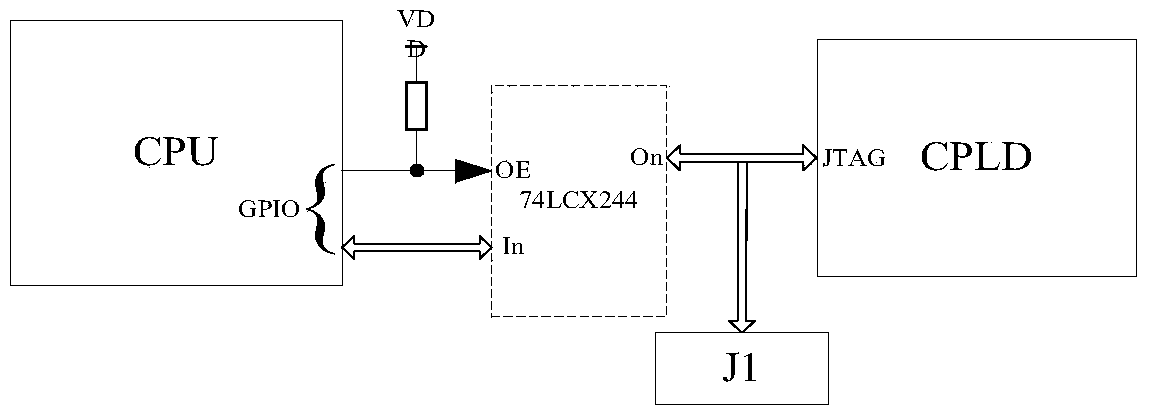

Method used

Image

Examples

Embodiment Construction

[0035] In order to make those skilled in the art more clear and understandable, the technical solution of the present invention will be clearly and completely described below in conjunction with exemplary embodiments of the present invention.

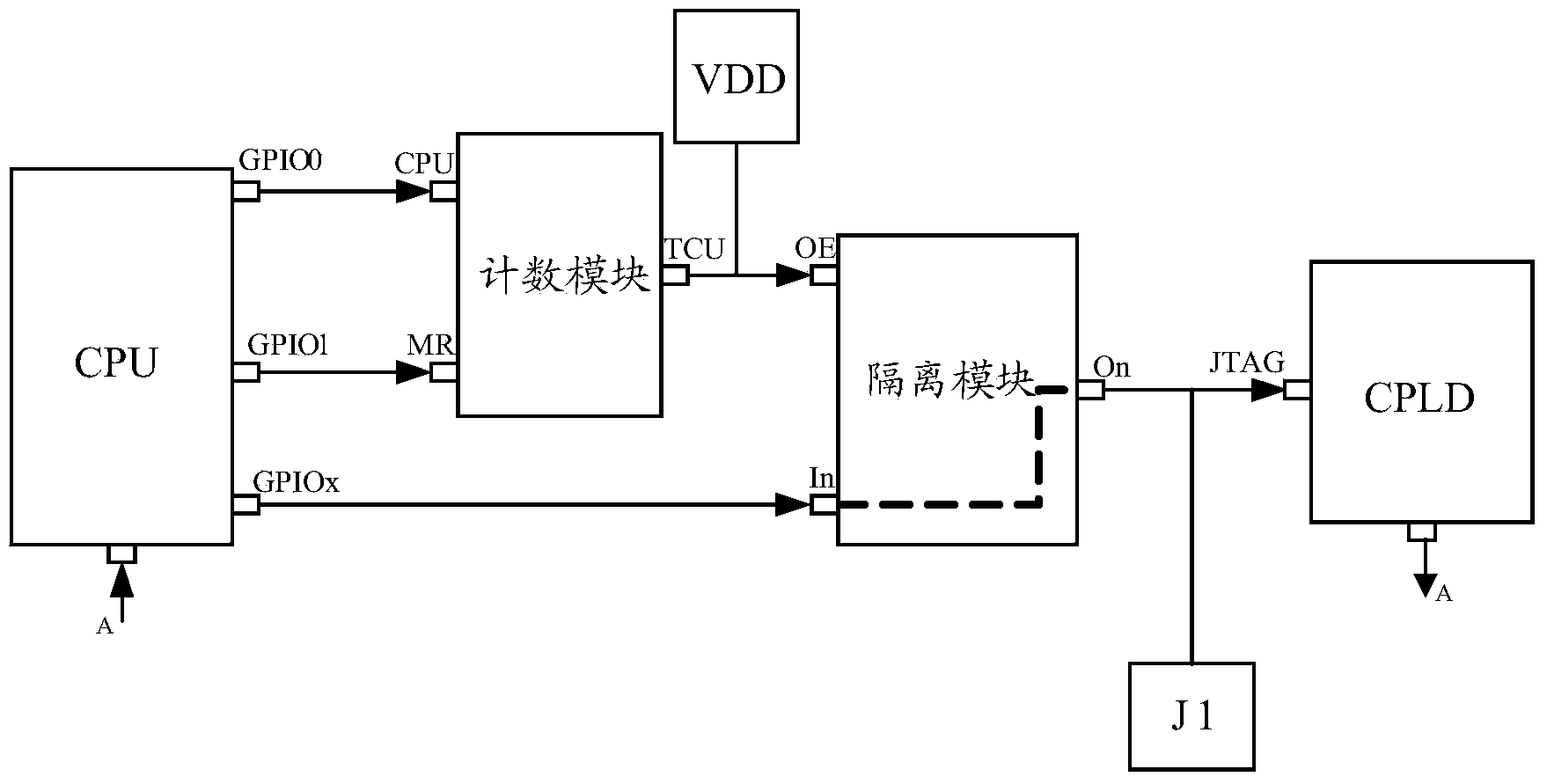

[0036] Such as image 3 As shown in FIG. 1 , it is a schematic diagram of hardware connection for loading a CPLD chip provided by an exemplary embodiment of the present invention. In this figure, the special JTAG interface for loading the CPLD chip software is respectively connected to the isolation pin ON of the isolation module and the loading socket J1; the isolation module is connected to the GPIOx pin of the CPU through the input pin In, and connected to the counting pin through the control pin OE The overflow pin TCU of the module receives the count overflow signal from the counting module. When the count overflow signal is received, the control isolation pin ON is in a low-impedance state, so that the GPIOx pin of the CPU can sim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More