Patents

Literature

59 results about "Field programmable logic devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

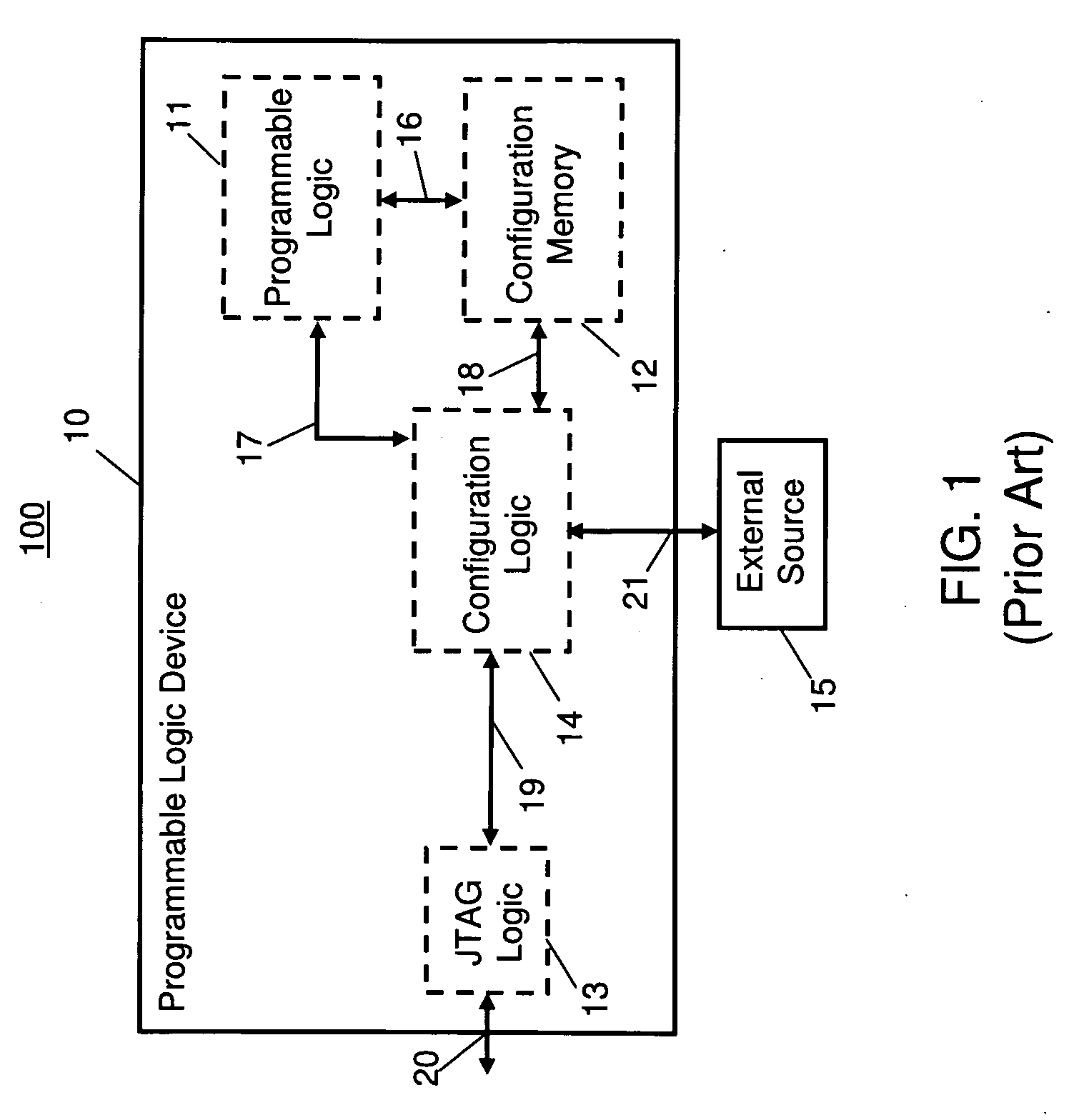

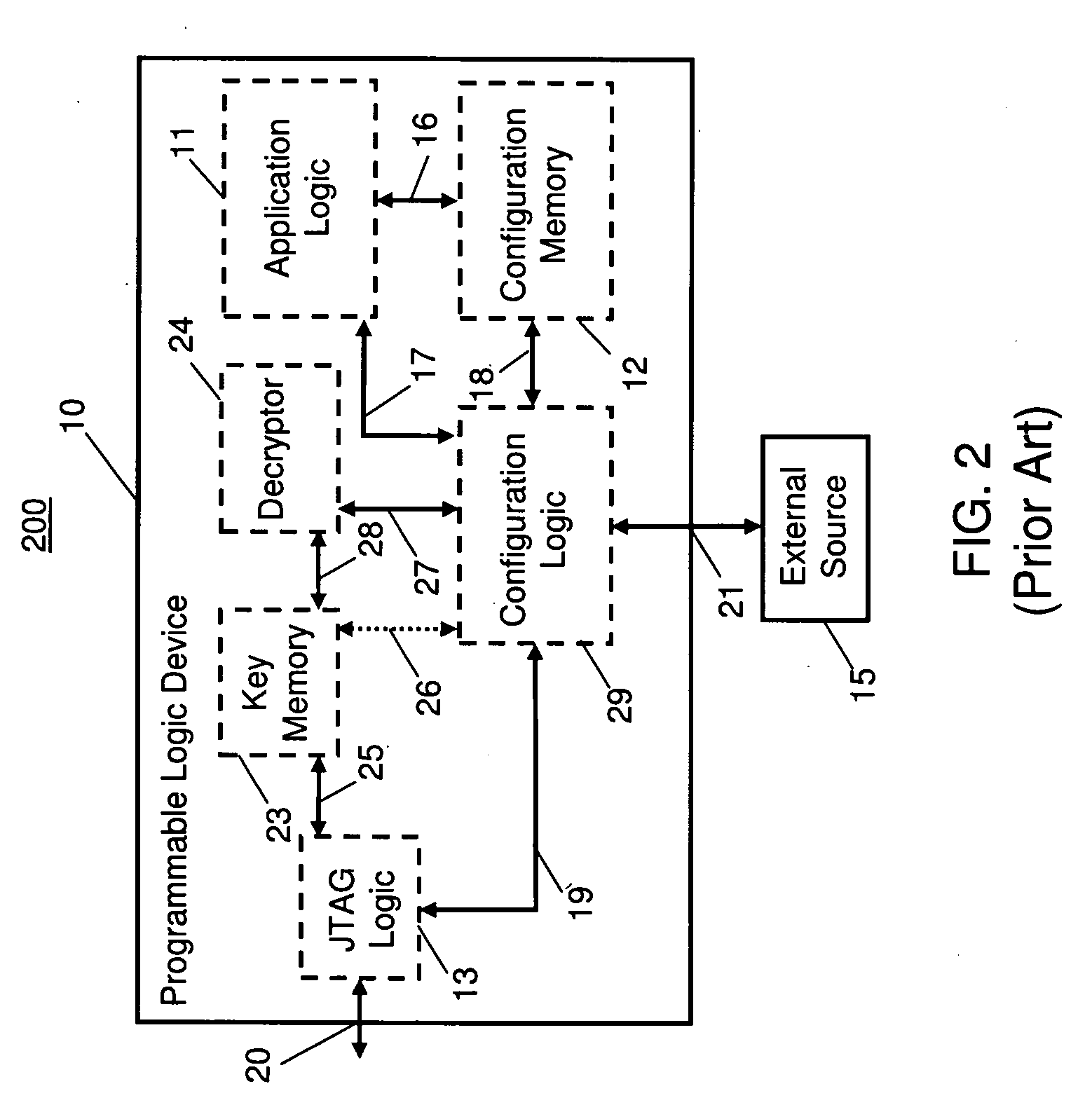

Programmable Logic. There are many types of Programmable Logic Devices (PLDs), beginning with simple combinations of digital logic that are integrated on one chip. Complex Programmable Logic Devices (CPLDs) and Field Programmable Gate Arrays (FPGAs) are general-purpose semiconductor devices that can be programmed after shipping.

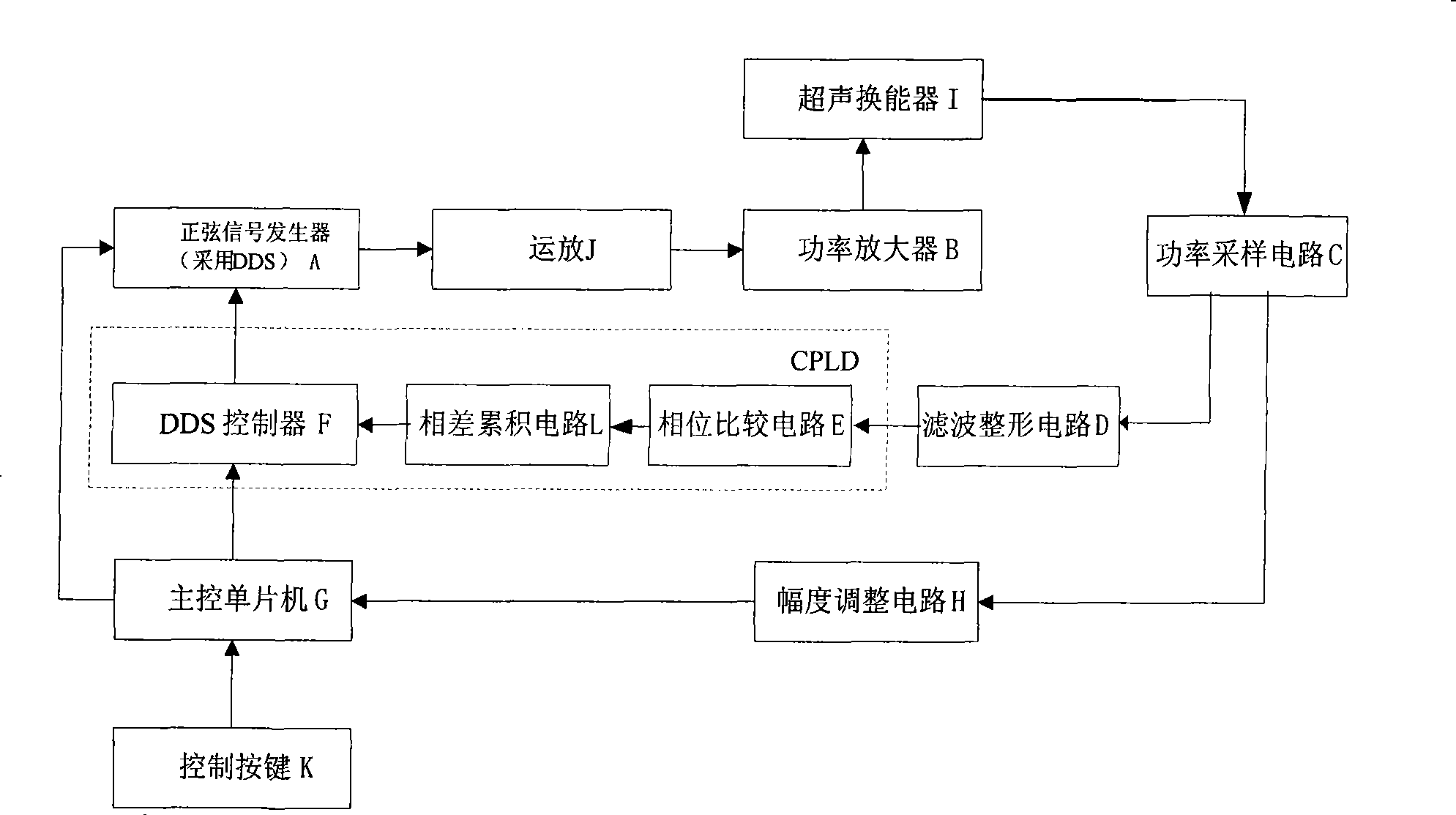

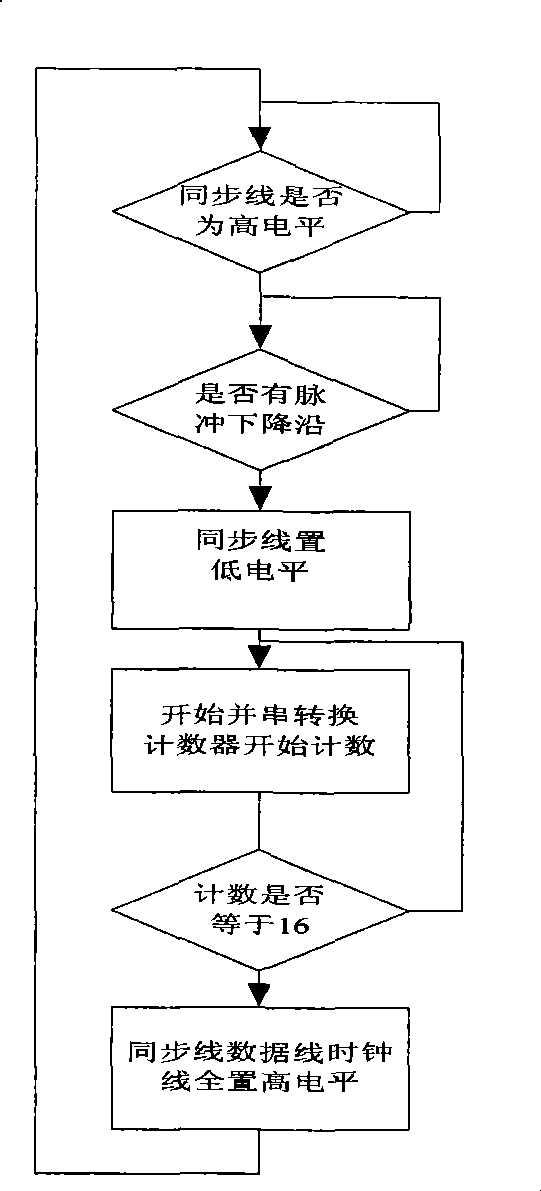

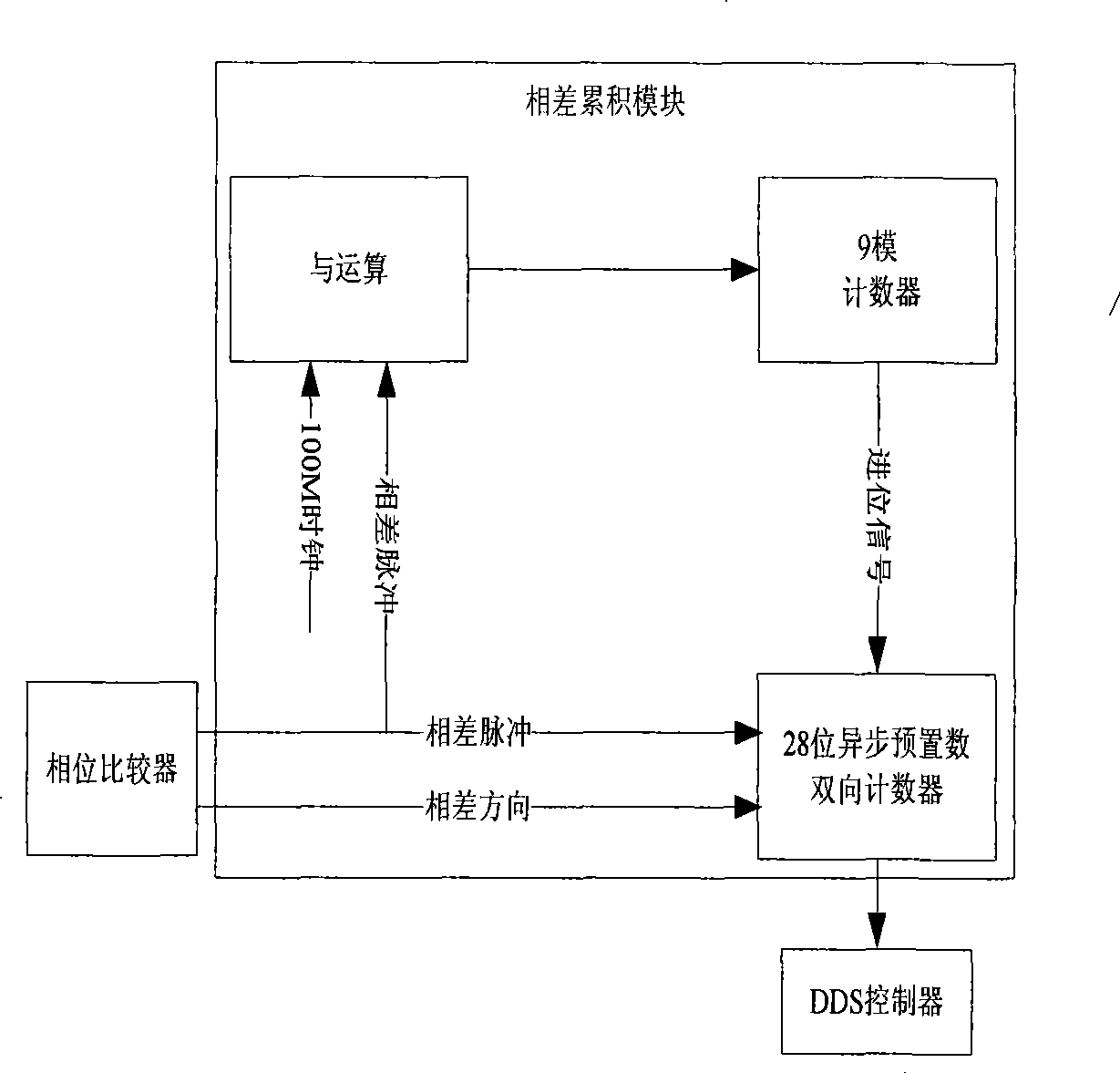

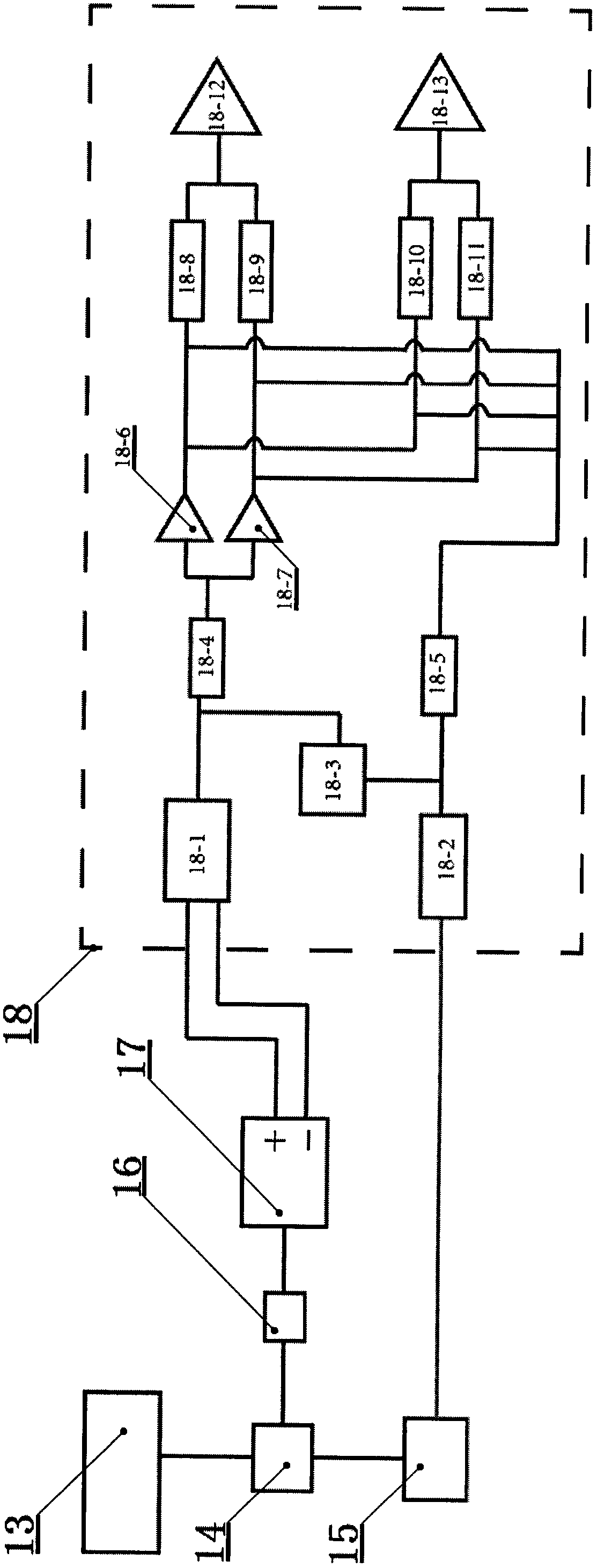

Automatic frequency tracking method of supersonic transducer and system thereof

ActiveCN101468347ARealize digital controlWork reliablyMechanical vibrations separationLogical elementUltrasonic sensor

The invention relates to an automatic frequency tracking method and a system for an ultrasonic transducer. A direct digital frequency synthesizer is used as a signal source, wherein the direct digital frequency synthesizer can be an independent integrated chip and also be achieved by the method that a digital part of a DDS is integrated in a site programmable logical element FPGA and then a digital-analog converter is additionally added. The design of the invention adopts a frequency sweeping and tracking policy, and an automatic frequency controller achieved by the programmable element controls the output frequency of the DDS according to a feedback signal sampled from the self transducer end so as to achieve the full digitization automatic frequency tracking and ensure that the ultrasonic transducer work near a resonance point all the time to obtain the optimal efficiency. A phase comparator utilizes a trigger to give out the arriving time difference of two riser edge signals of two input signals I ph and V ph aiming to the sensitive characteristics of the riser edge signals, and the sequence of the riser edge signals of the two input signals I ph and V ph is given out by a Dirrect pin.

Owner:BEIJING ANHEJIALIER TECH CO LTD

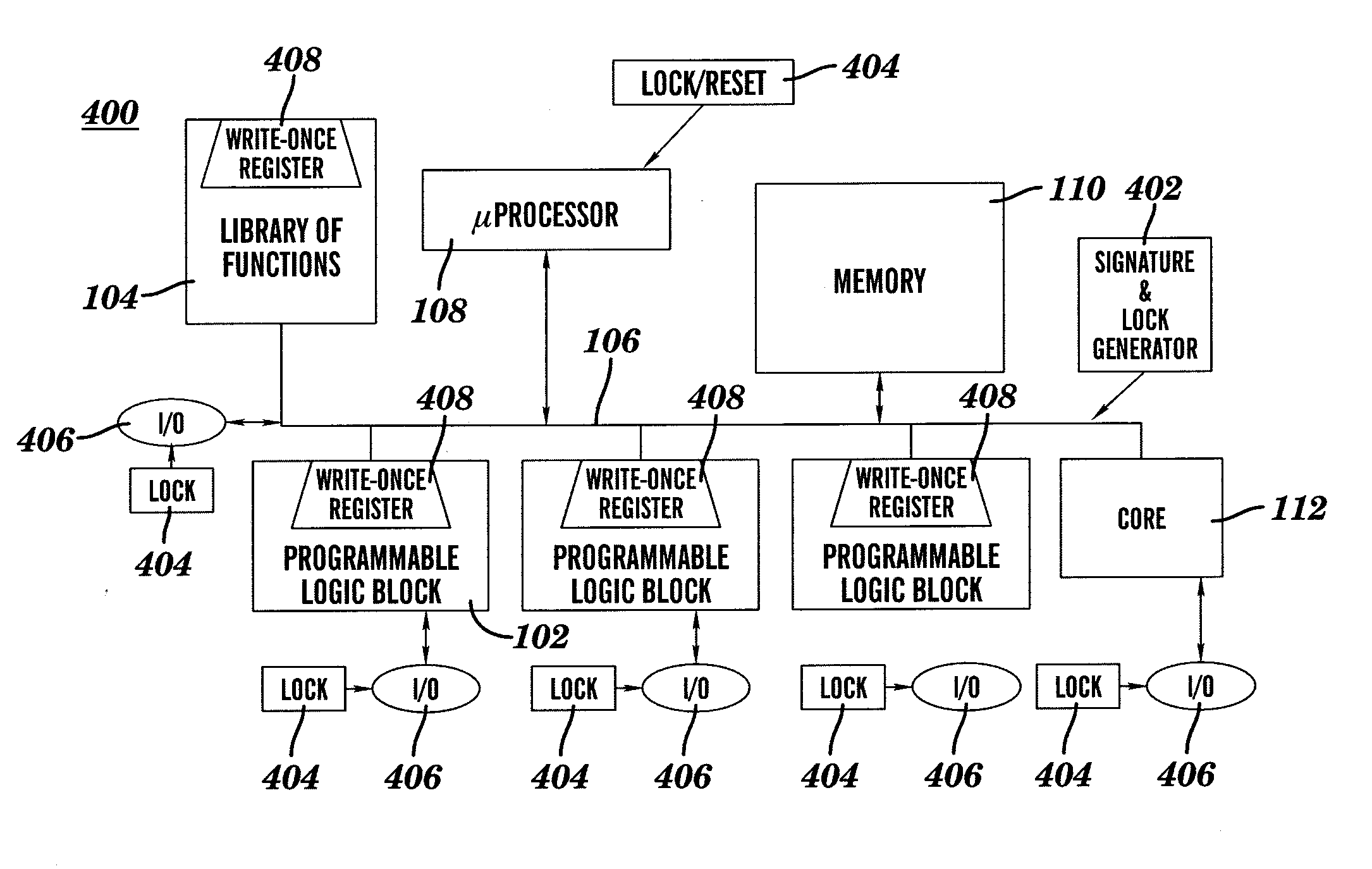

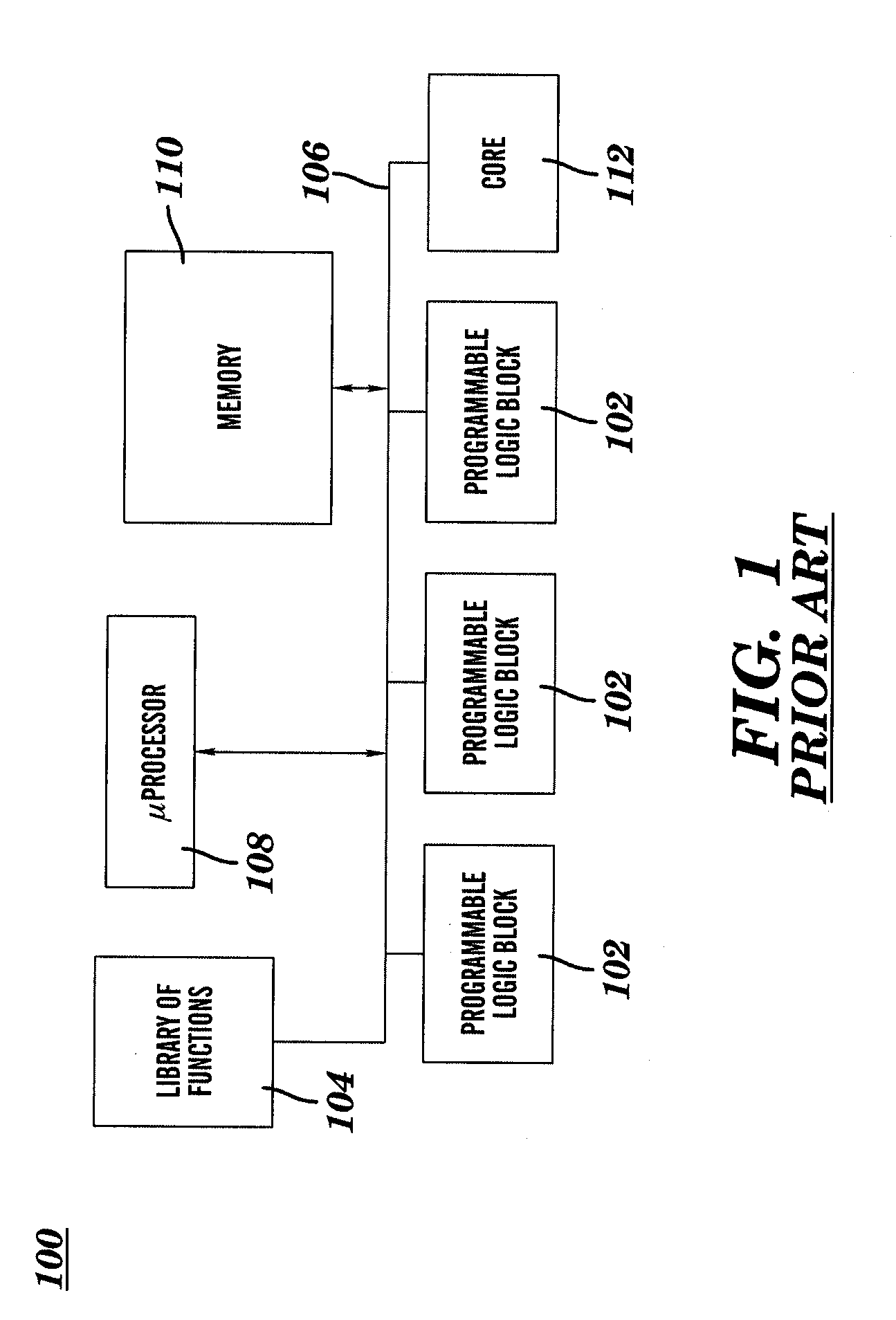

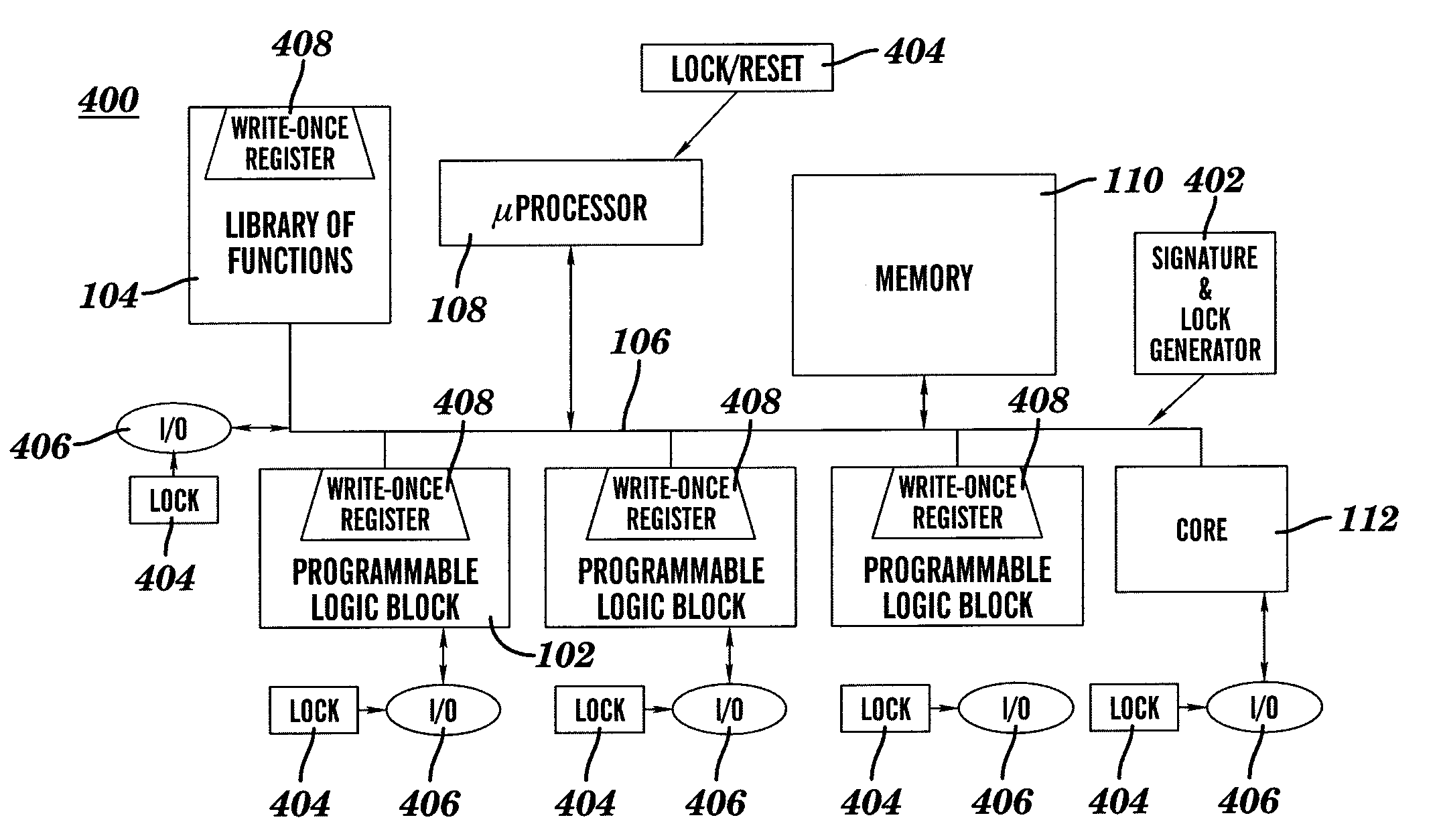

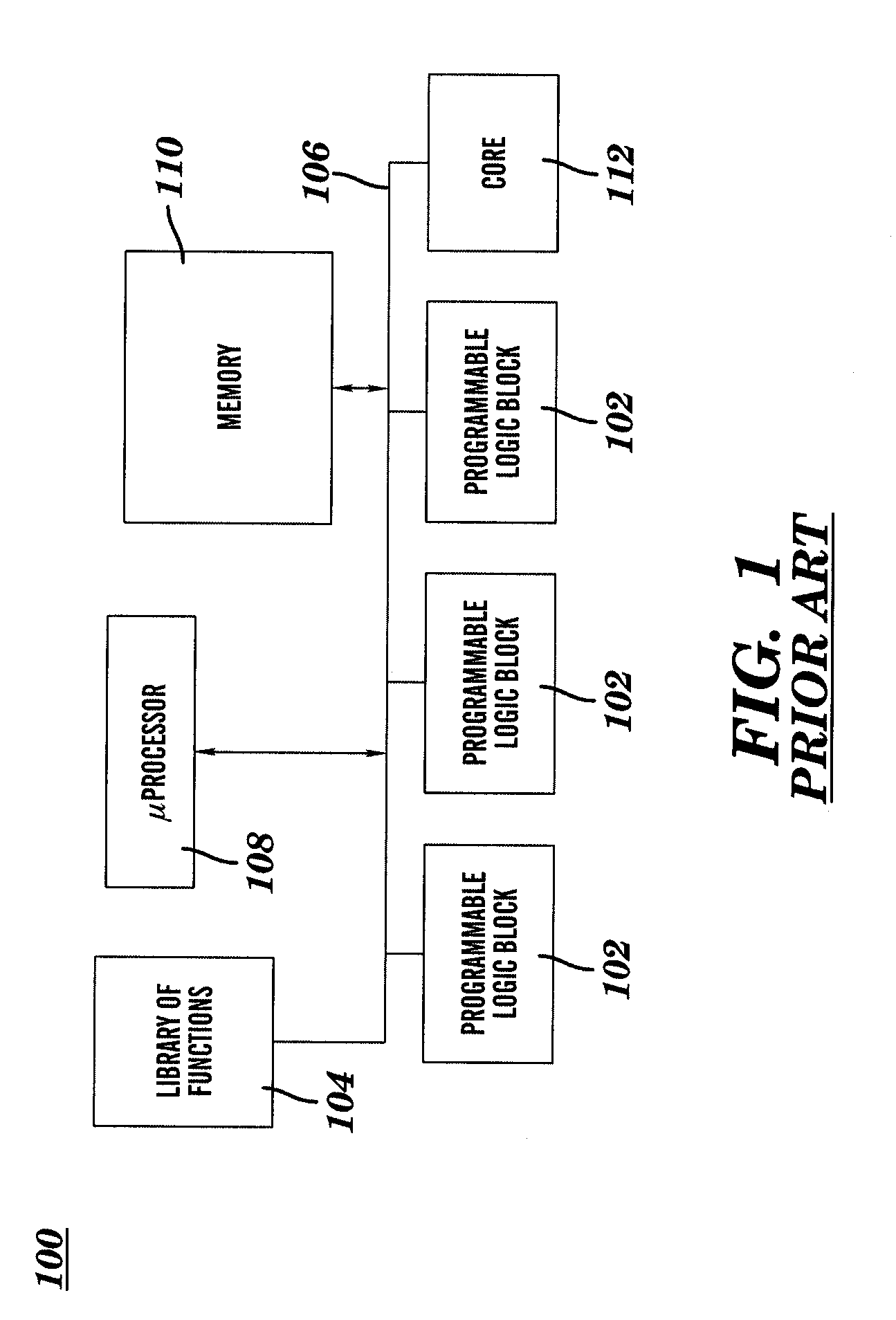

Method for system level protection of field programmable logic devices

InactiveUS20050278551A1Avoid accessDigital data processing detailsUser identity/authority verificationField programmable logic devicesProgrammable logic device

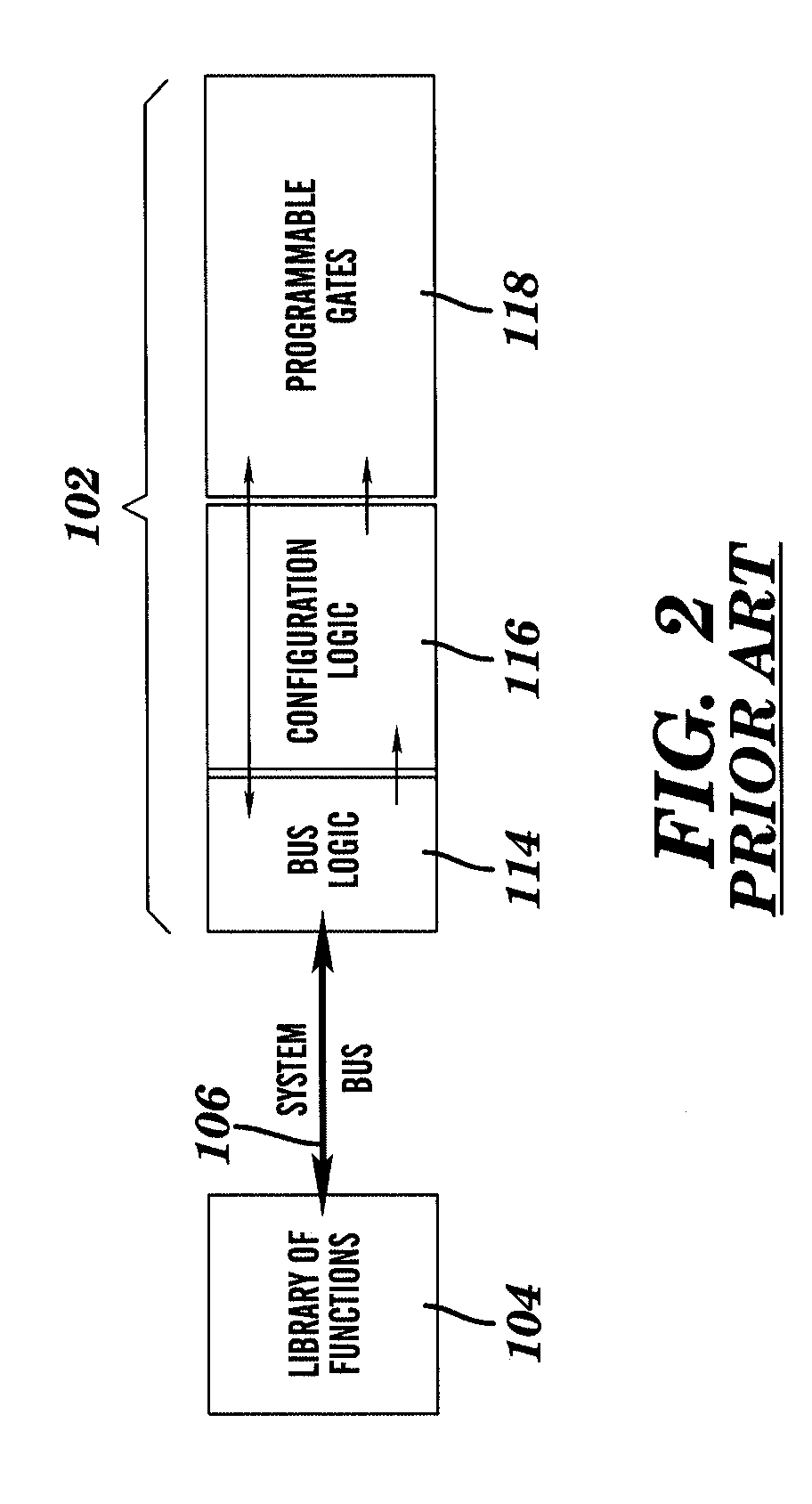

A method for protecting a dynamically reconfigurable computing system includes generating an encoding signature and passing the encoding signature, through a system level bus, to at least one field programmable logic device and to a function library included within the system. The function library contains a plurality of functions for selective programming into the at least one field programmable logic device. A lock is generated so as to prevent external resources with respect to the system from accessing the encoding signature during the passing thereof.

Owner:IBM CORP

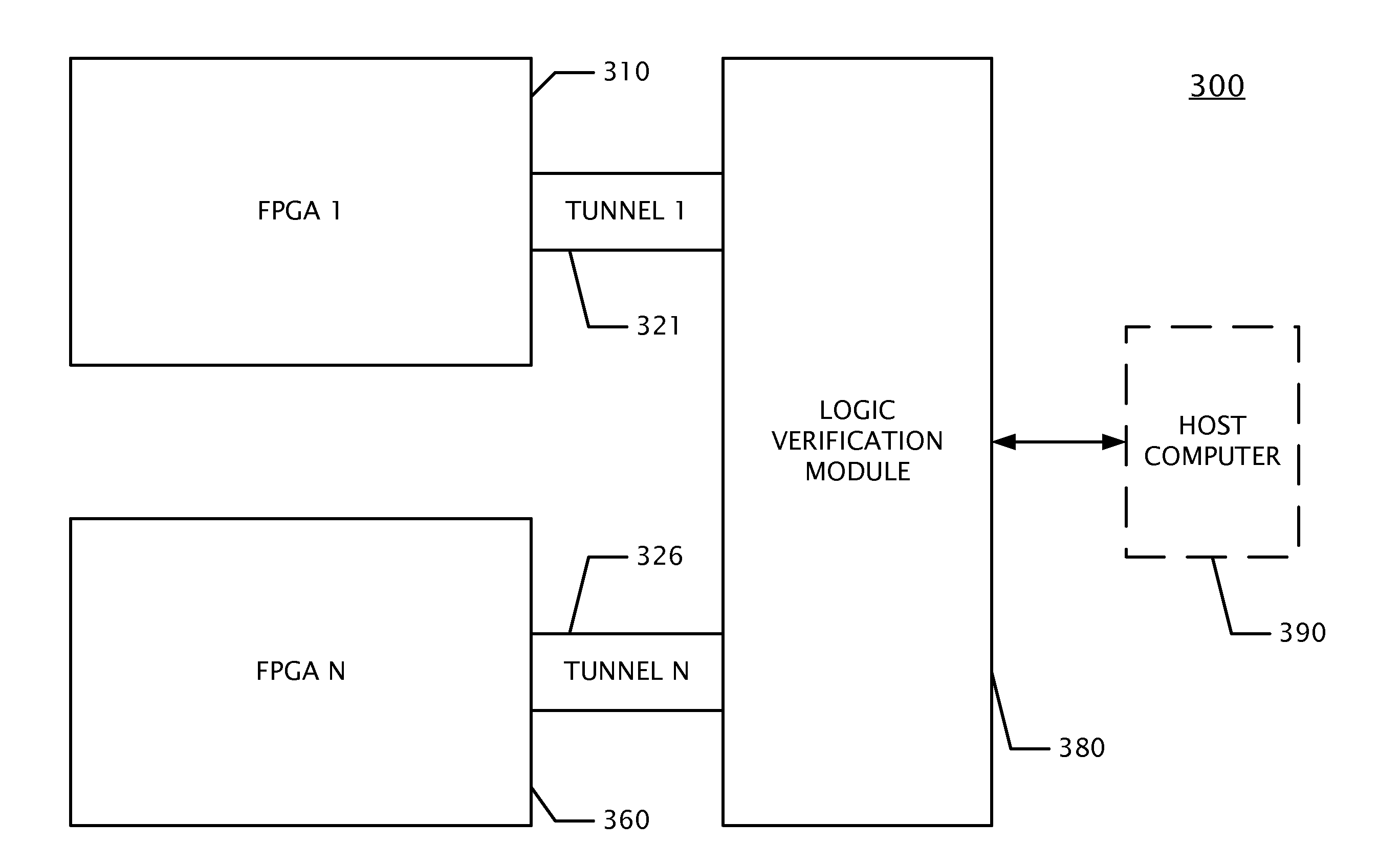

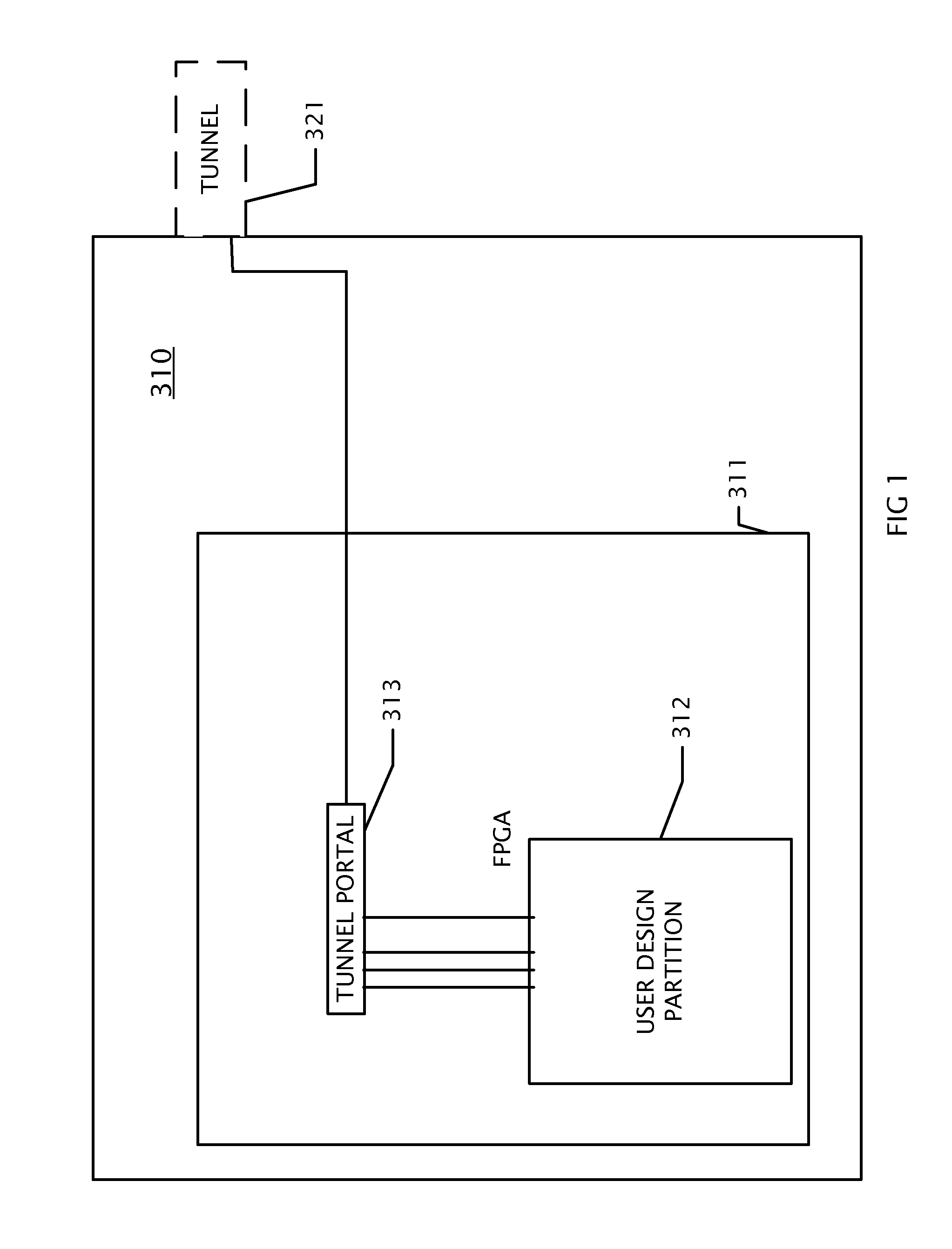

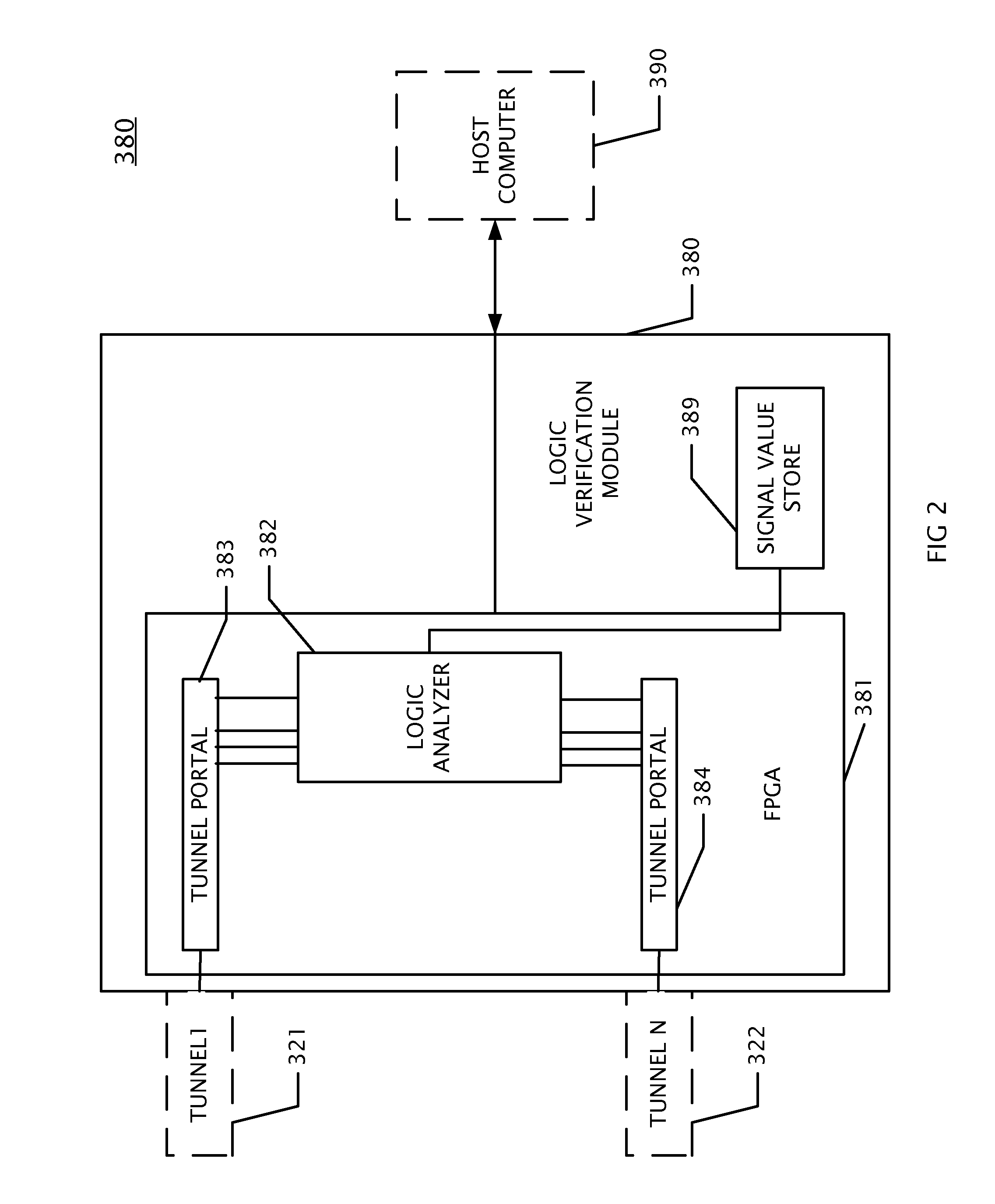

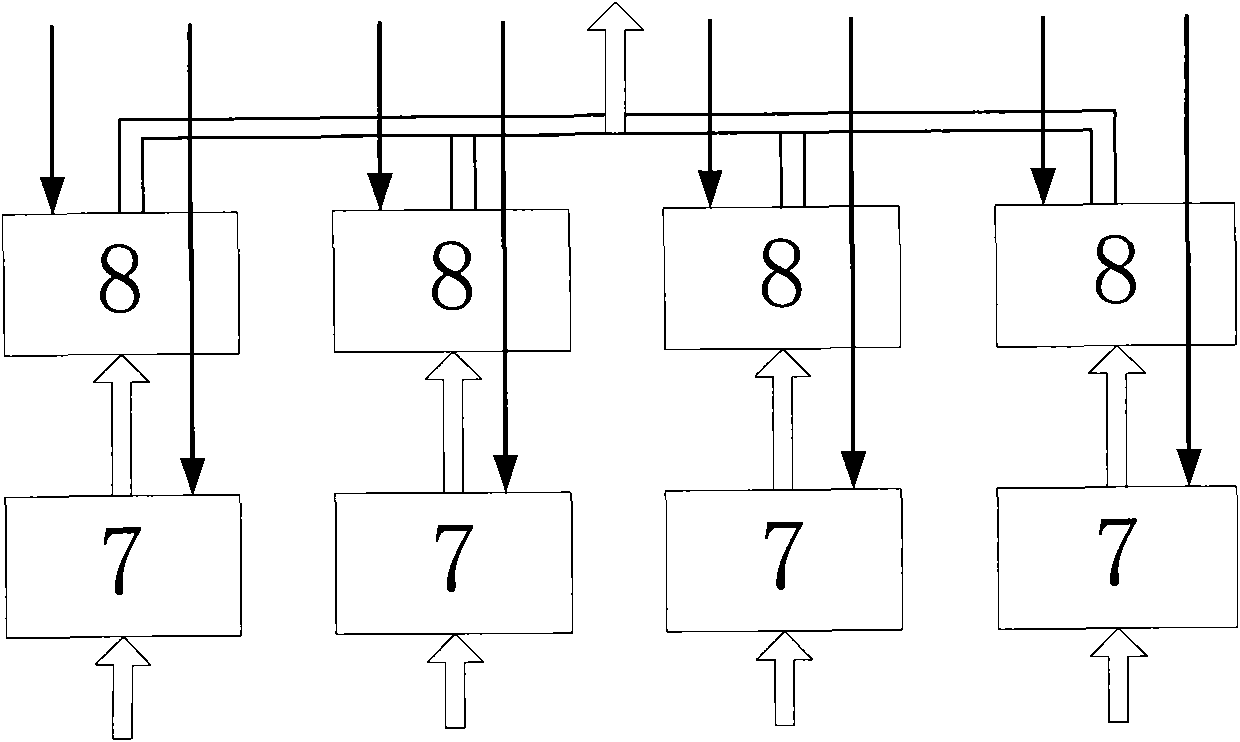

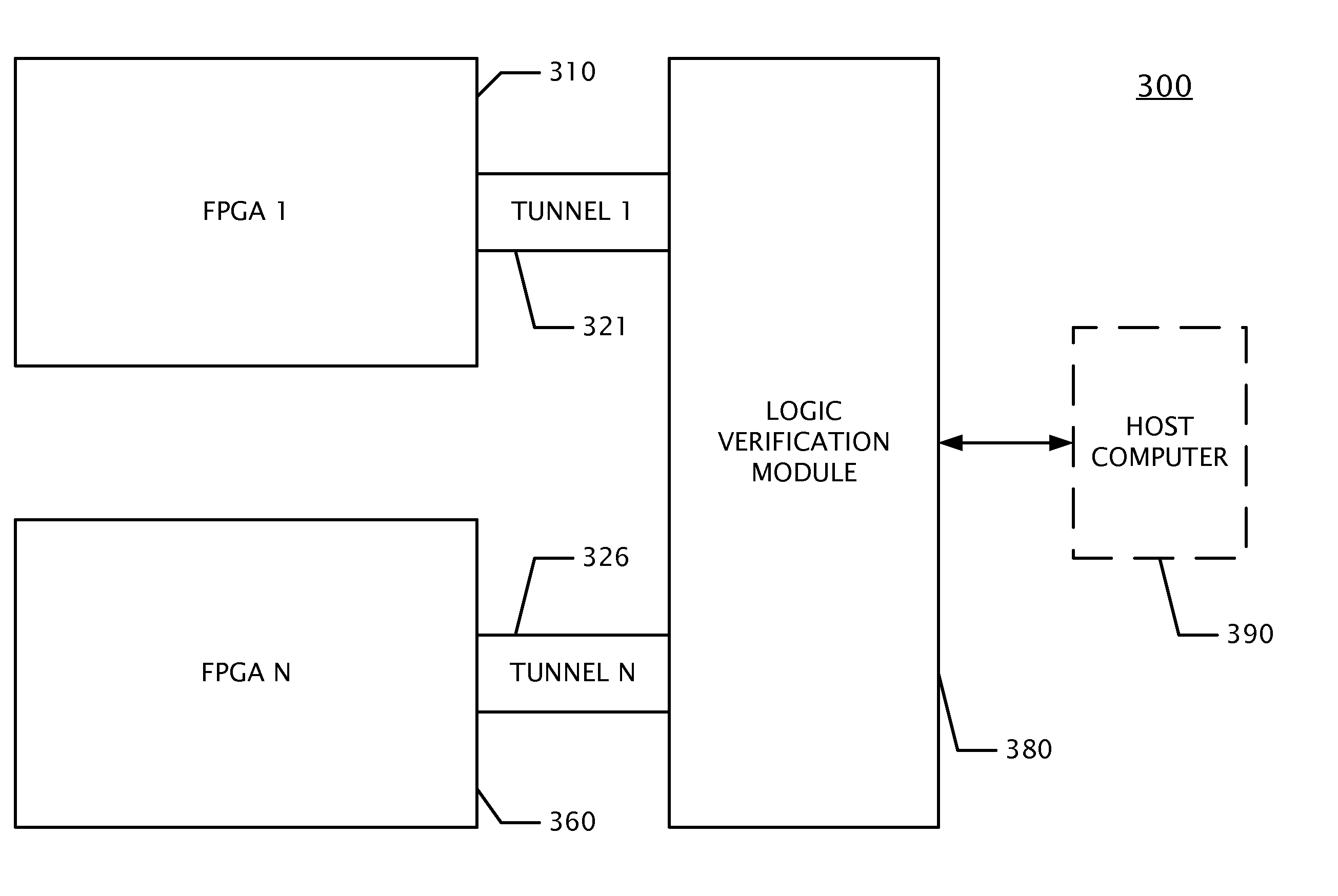

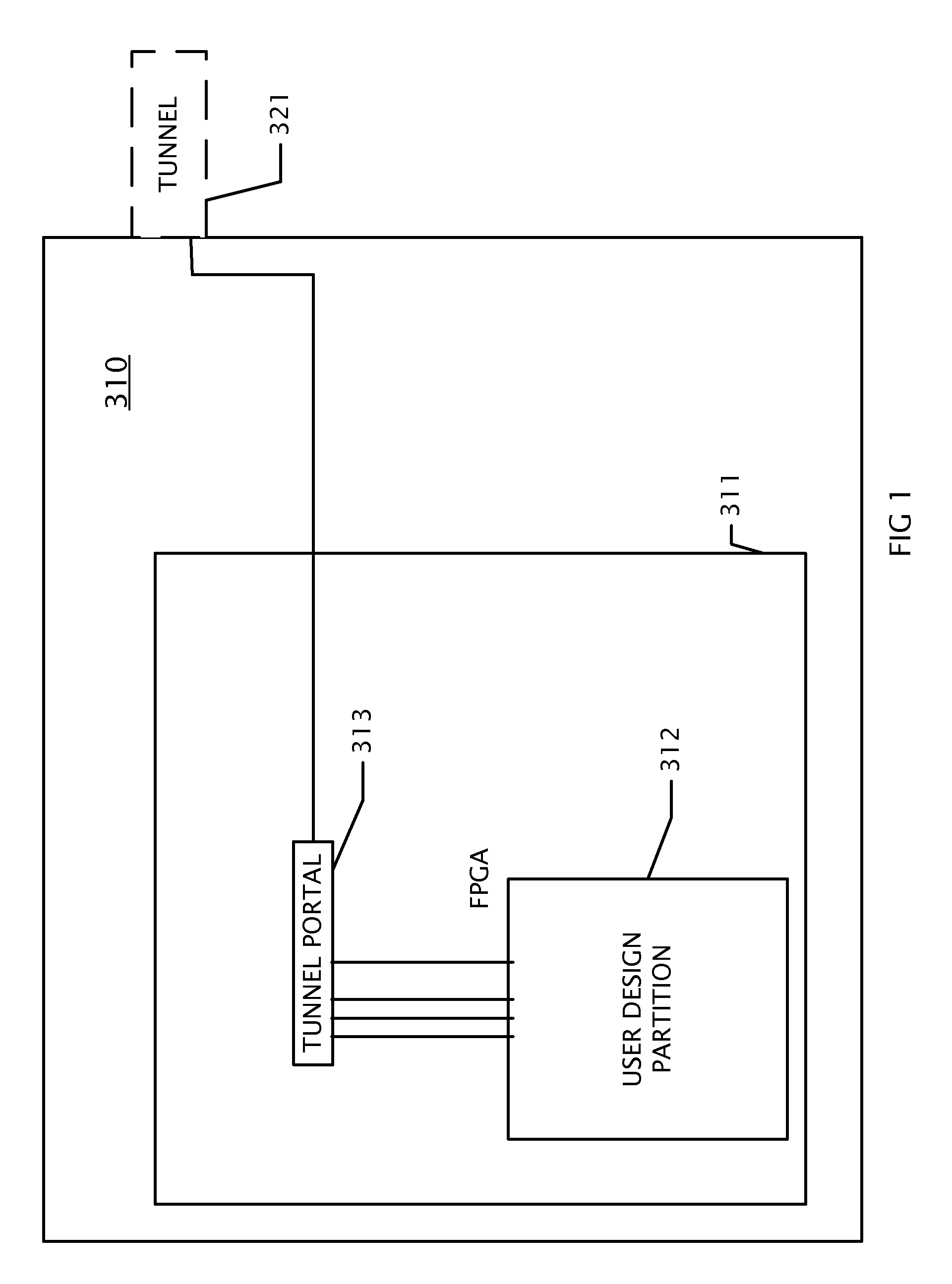

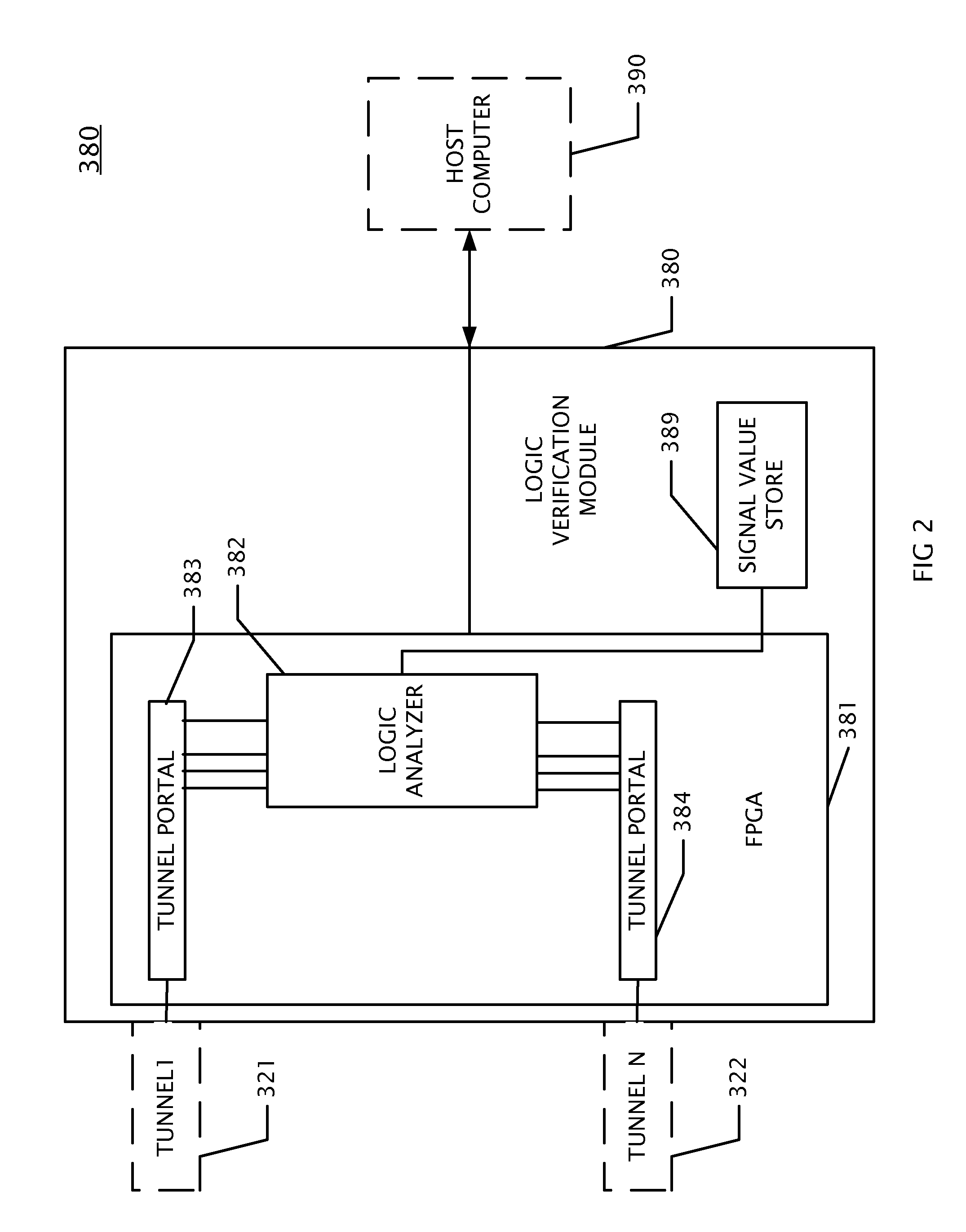

Logic verification module apparatus to serve as a hyper prototype for debugging an electronic design that exceeds the capacity of a single FPGA

ActiveUS20120290993A1Detecting faulty computer hardwareCAD circuit designComputer architectureField programmable logic devices

A apparatus and a system and method to operate the above provide a reconfigurable platform for emulating and debugging a user design which exceeds the capacity of a single field programmable logic device (FPGA). The method and system facilitates design and emulation of a system-on-a-chip type user design. The netlist of a user design may be included with logic value tunneling circuits in an emulation using a platform including a number of field programmable devices. A verification module apparatus provides a hyper prototype for debugging an electronic design that exceeds the capacity of a single FPGA. A verification module provides access to a plurality of attached FPGAs by means of Logic Value Tunneling Transmitters and Receivers which deliver many signals over few pins.

Owner:S2C LTD

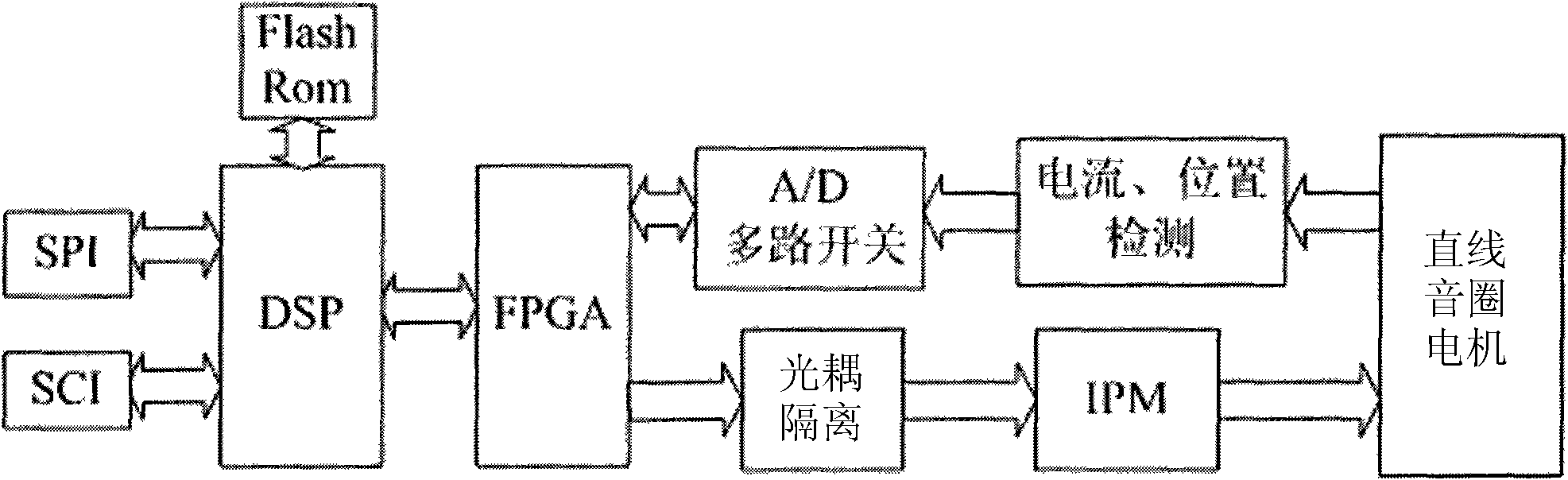

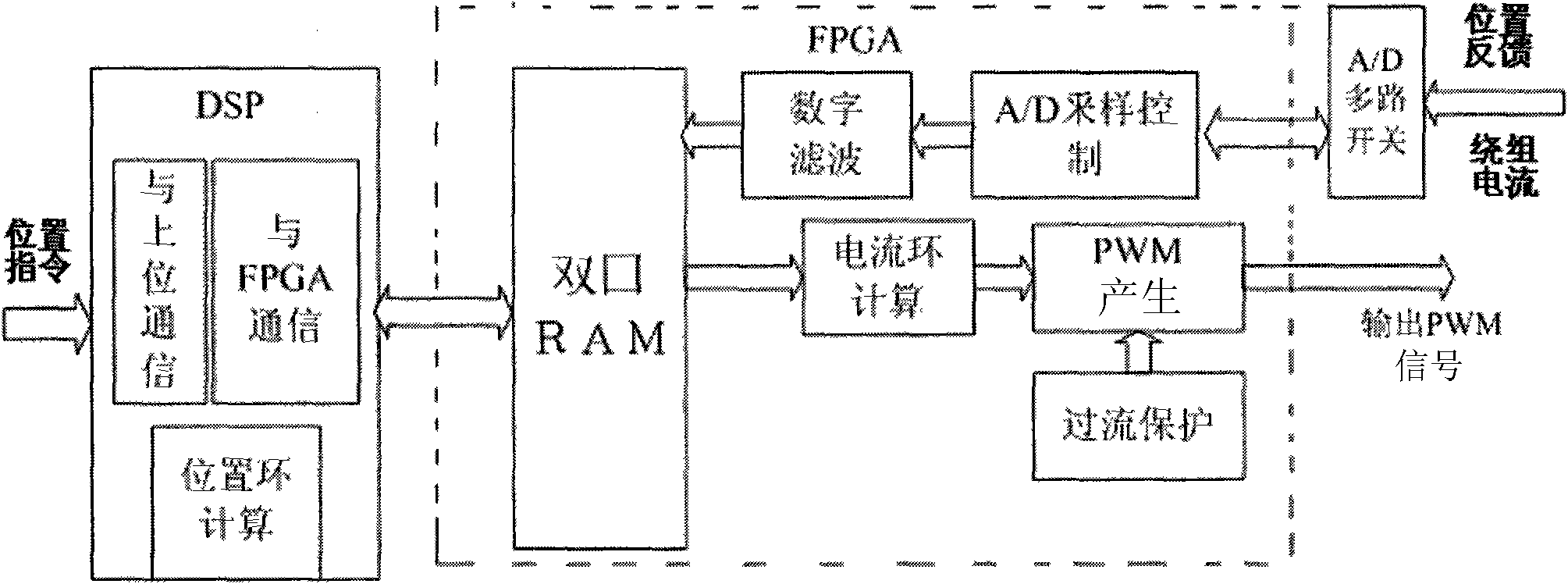

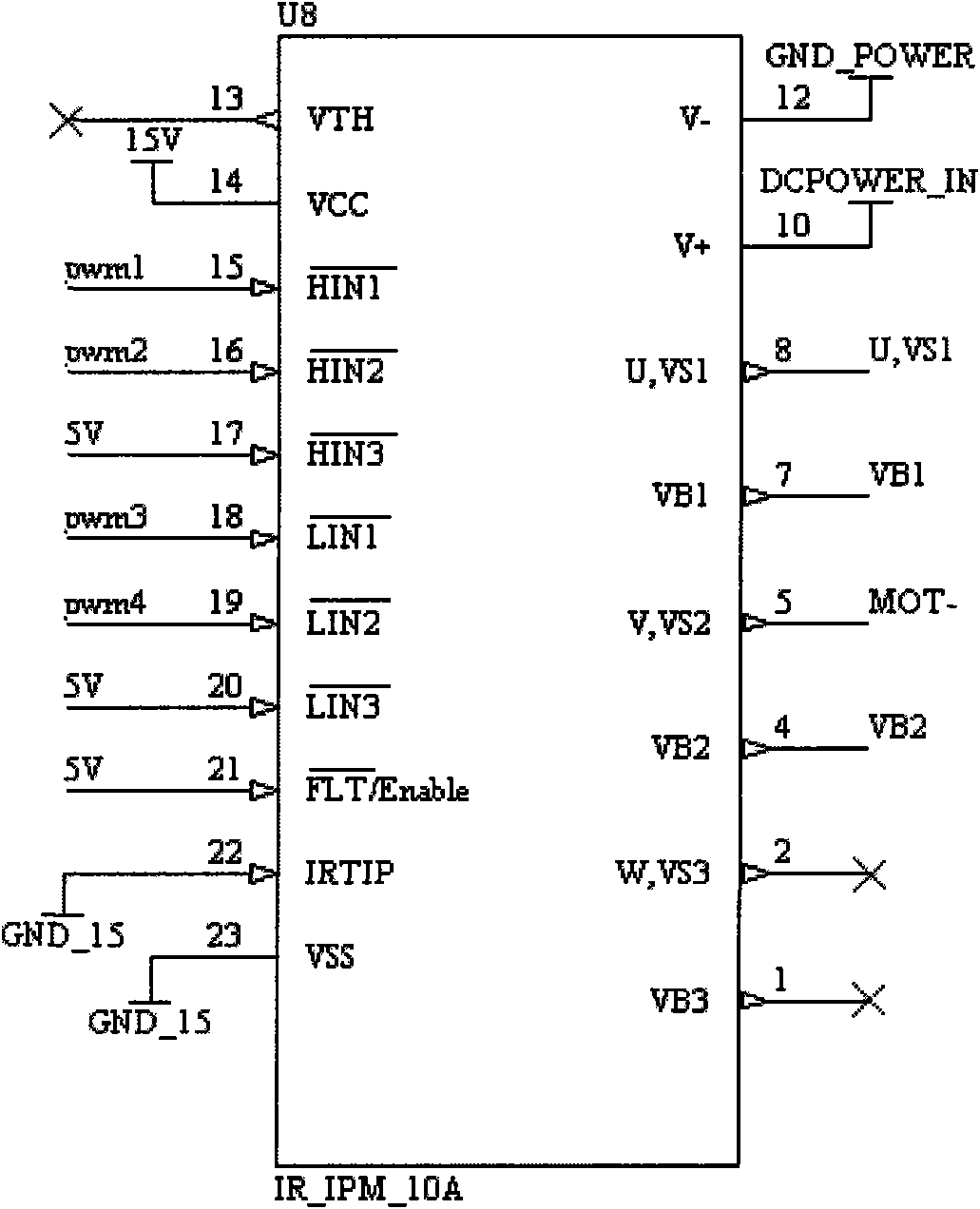

Full digital driving controller of permanent magnetic linear voice coil motor used for direct driving valve

InactiveCN101576745AIncrease sampling rateHighly integratedAC motor controlElectric motor controlExtensibilityField programmable logic devices

The invention relates to a full digital driving controller of a permanent magnetic linear voice coil motor used for a direct driving valve, consisting of three parts: a digital controller, a power circuit and a signal detection circuit; the digital controller circuit comprises a 32-bit floating point DSP, a field programmable logic device FPGA and an external Flash ROM; the power circuit comprises a high-speed optical coupling isolation circuit, and an H-bridge power main circuit consisting of intelligent power modules IPM; the signal detection circuit comprises an A / D converter, a multi-path analogue switch, a Hall current sensor used for detecting the moving coil winding current, a non-contact eddy current displacement sensor used for detecting the position of the moving coil and an amplification and active power filter circuit for analogue signals. The full digital driving controller of the permanent magnetic linear voice coil motor used for the direct driving valve has the advantages of high integration, good extensibility, high reliability, high frequency response and high precision.

Owner:BEIHANG UNIV

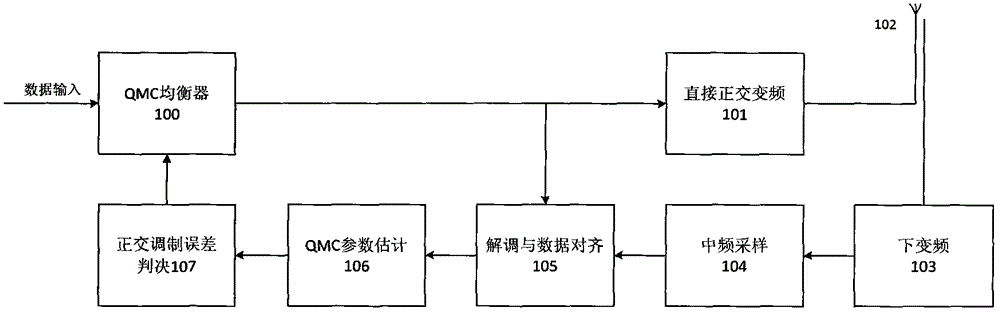

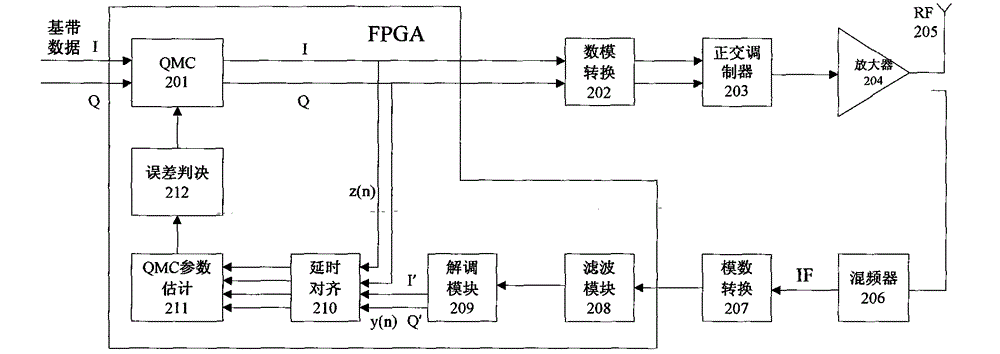

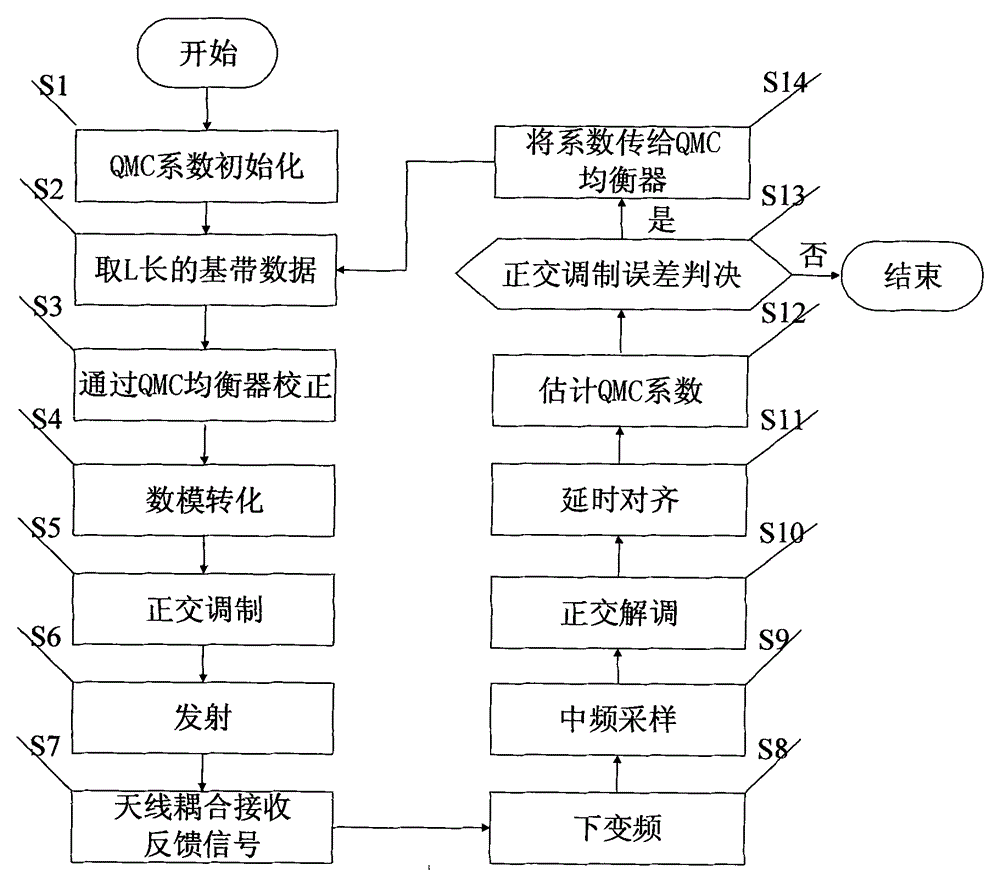

Self-adaptive direct quadrature variable-frequency modulation error correction method

ActiveCN104486273ASuppress image interferenceEliminate LO LeakageTransmitters monitoringTransmitter/receiver shaping networksField programmable logic devicesIntermediate frequency

The invention discloses a self-adaptive direct quadrature variable-frequency modulation error correction method. The method creates a new quadrature modulation error model, and puts forward a self-adaptive QMC (Quadrature Modulation Compensation) algorithm for direct quadrature variable-frequency modulation error correction on the basis of the model. Through antenna coupling and down-conversion mixing, by obtaining a feedback signal after intermediate-frequency high-speed sampling, a quadrature modulation error inverse distortion coefficient is estimated after the feedback signal and a transmission signal are aligned, and self-adaptive correction is implemented in a numeric field programmable logic device FPGA (field programmable gate array). The self-adaptive direct quadrature variable-frequency modulation error correction method can efficiently and accurately inhibit local oscillator leakage caused by direct-current bias and image interference caused by I / Q amplitude and phase imbalance, and has important significance for self-adaptive direct quadrature variable-frequency modulation error correction.

Owner:COMMUNICATION UNIVERSITY OF CHINA

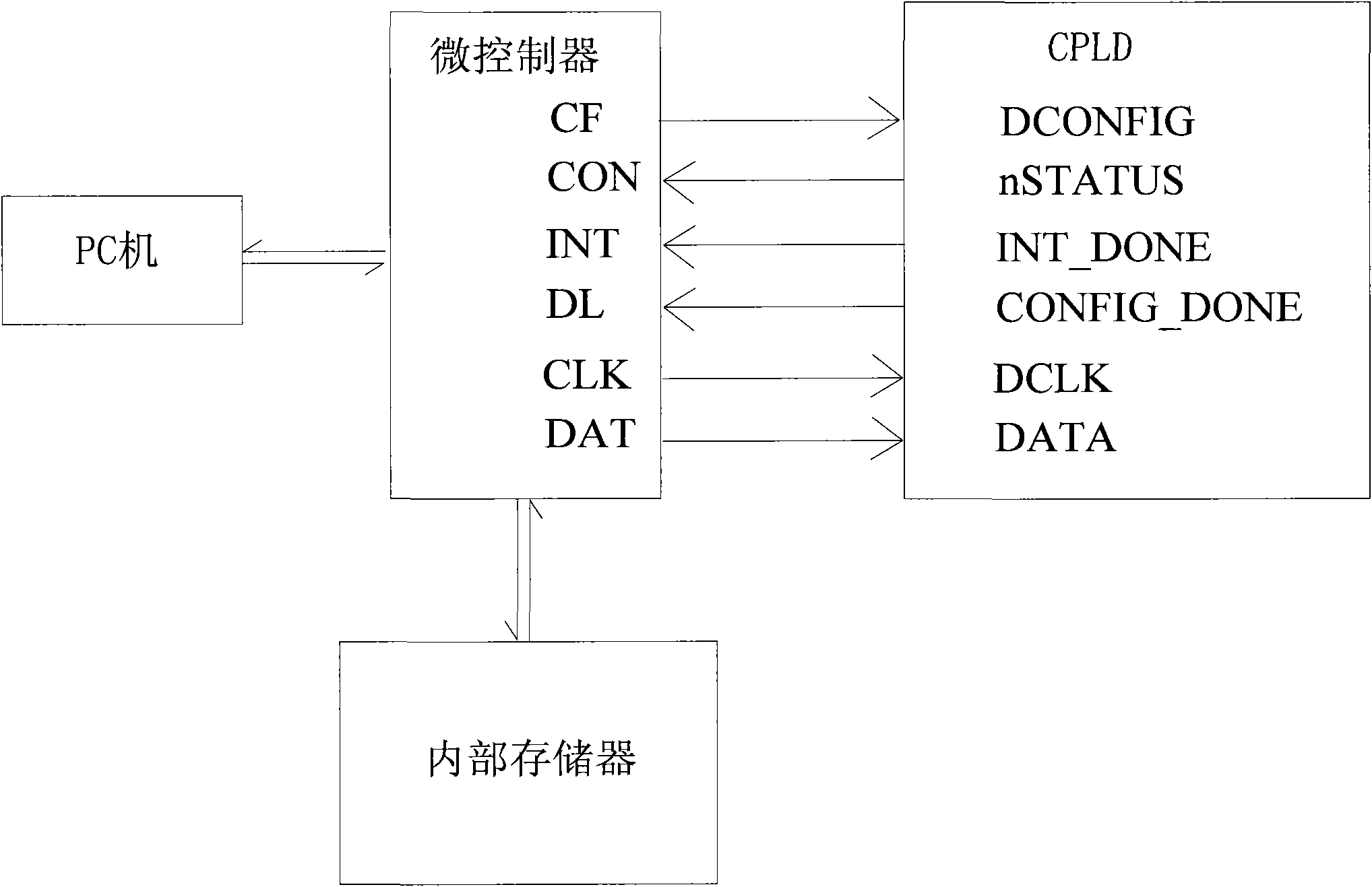

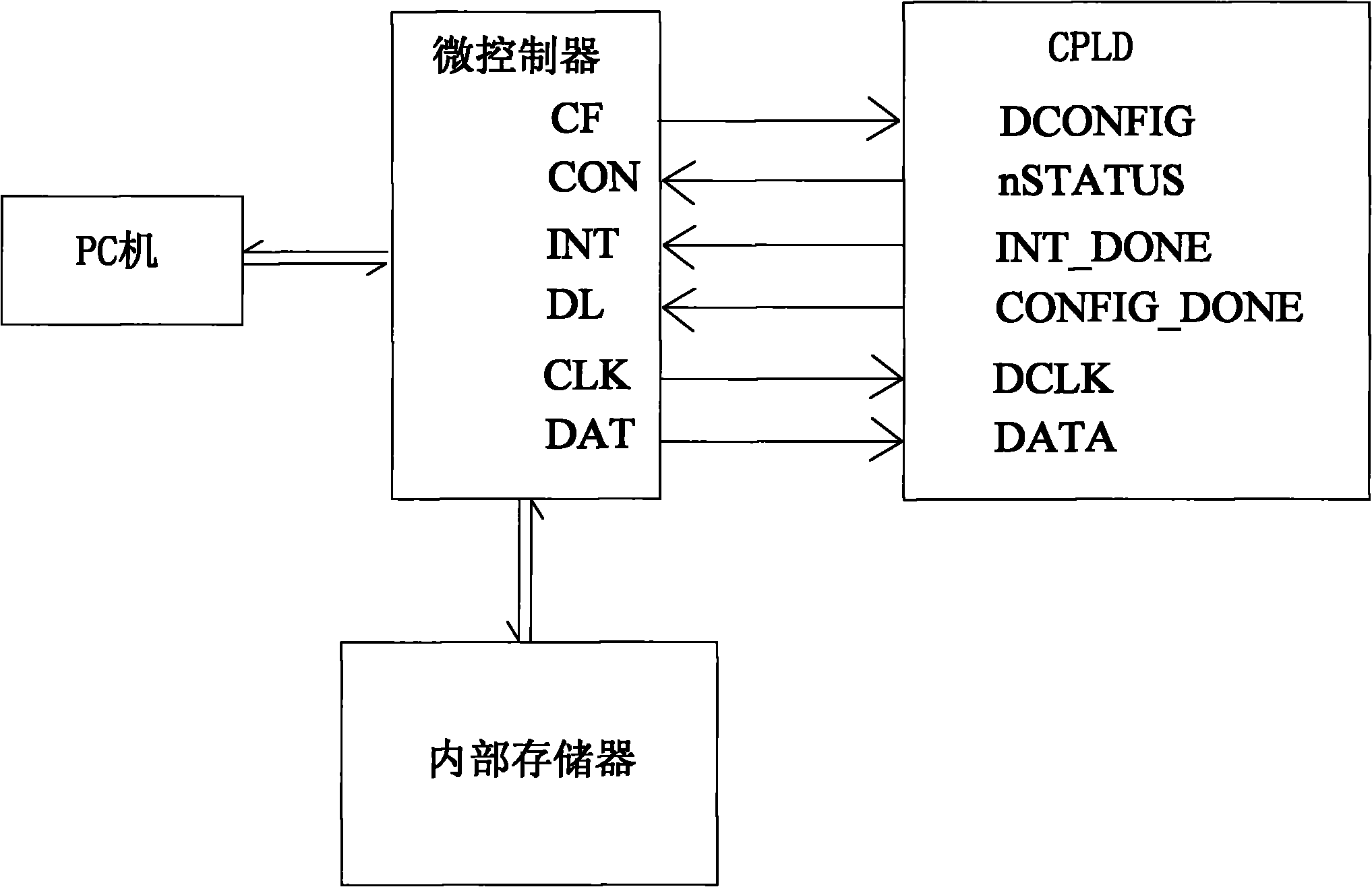

Device for upgrading firmware of field programmable logic device and method thereof

InactiveCN101826025ATroubleshoot broken tech issuesRealize the logic functionProgram loading/initiatingMicrocontrollerField programmable logic devices

The invention discloses a device for upgrading the firmware of a field programmable logic device, which comprises a microcontroller and a host connected with the microcontroller, and is characterized in that the microcontroller is connected with the field programmable logic device in a passive serial mode, after the host sends a firmware upgrading instruction, the microcontroller reads in the firmware upgrading data and configures the firmware upgrading data for the field programmable logic devices in passive serial mode. When upgrading the CPLD firmware, the device is simple to operate, and not only can eliminate the hardware problems caused by artificially welding or inserting / pulling the chip CPLD, but also can avoid the inconvenience caused by using the ISP.

Owner:TAICANG T&W ELECTRONICS CO LTD

High-speed image compression method and device based on optimally quantized wavelet sub-band interlacing

InactiveCN102833546AReduce resource usageHigh speedTelevision systemsDigital video signal modificationData streamField programmable logic devices

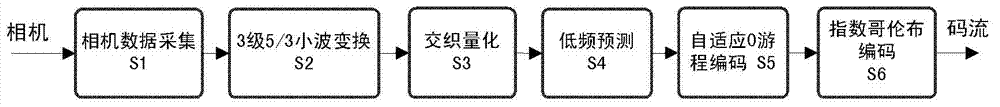

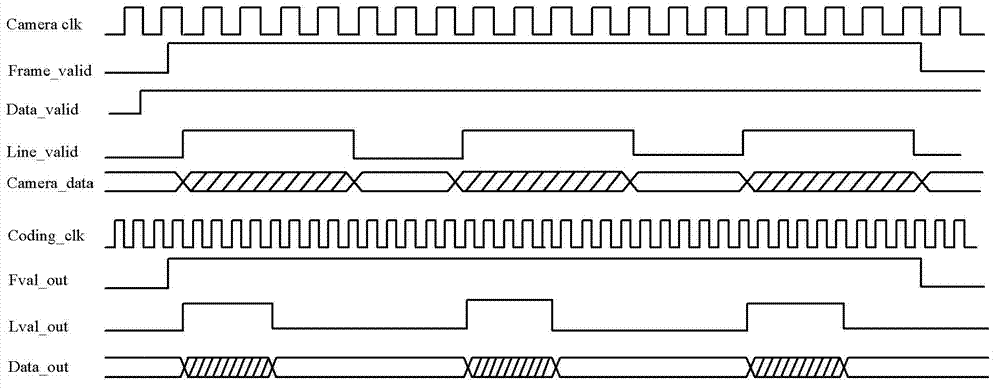

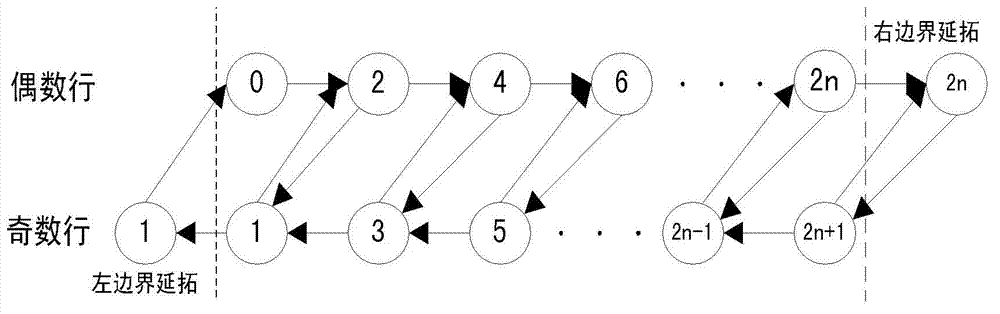

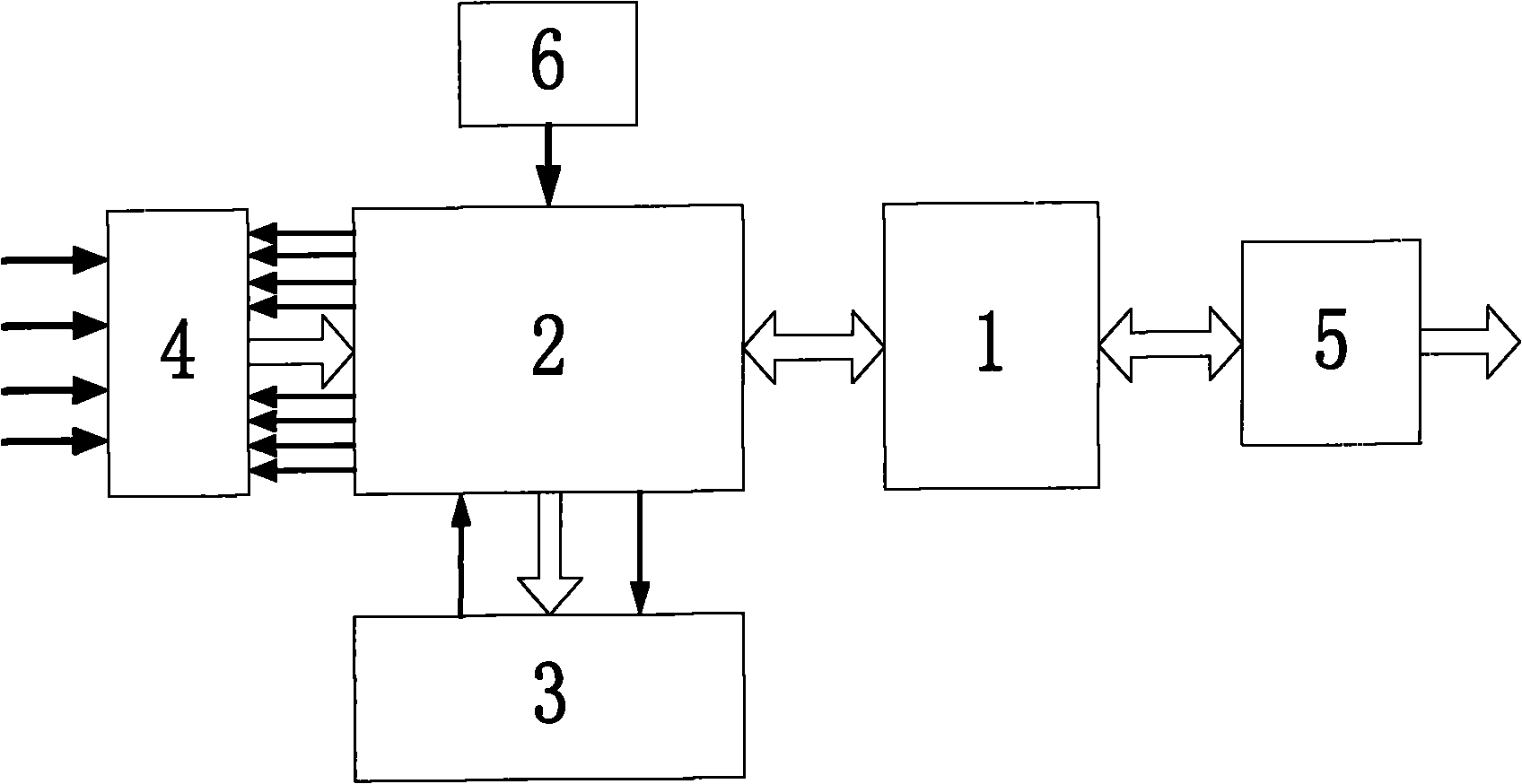

The invention relates to a high-speed image compression method based on optimal wavelet sub-band interlacing, which comprises the following steps of: acquiring CCD (Charge Coupled Device) camera data and carrying out 3-level wavelet transform on the CCD camera data; converting parallel sub-band data subjected to the wavelet transform into a sub-band interlaced serial data stream and carrying out optimal quantization; predicating quantized lowest frequency wavelet sub-band data by using a JPEG-LS (Joint Photographic Experts Group-Lossless Standard) algorithm; and carrying out run-length coding and exponential-Golomb coding on the quantized and predicated data to obtain a final code stream of an acquired image. The invention also provides a compression device. According to the image compression method and device, the whole process of image data acquisition, coding and transmission can be achieved by only using a single-chip field programmable logic device, the compression ratio can be adjusted by a quantization step and the throughput of single-channel data can reach 350 MSPS (Million Samples Per Second).

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

DDS-based Doppler compensation device in real-time water sound communication

InactiveCN101777939AImprove applicabilityHigh output frequency accuracyRadio transmissionMulti-frequency code systemsField programmable logic devicesProcessing core

The invention discloses a DDS-based Doppler compensation device in real-time water sound communication. An analogue-to-digital conversion circuit at the front end of a communication processing plate is connected with a universal I / O port of a field programmable logic device FPGA in a parallel interface mode through a group of data buses; a signal processing chip DSP serving as a processing core chip is connected with the FPGA through the data buses of EMIFA interfaces in and out of the chip; a chip selection wire, a reading control wire and partial address wires of an EMIFA interface are connected with the universal I / O interface of the FPGA; 10 / 100Mb / s Ethernet comprising a DSP for interconnecting networks controls an external network interface circuit; and a frequency synthesis module is connected with the universal I / O interface of the FPGA through a group of data buses and reading control wires of the DDS. The device can well compensate the Doppler frequency shift in the real-timewater sound communication in real time with high precision, and has the characteristics of high output frequency precision, real-time Doppler communication, strong applicability, high speed, stability and flexible application.

Owner:HARBIN ENG UNIV

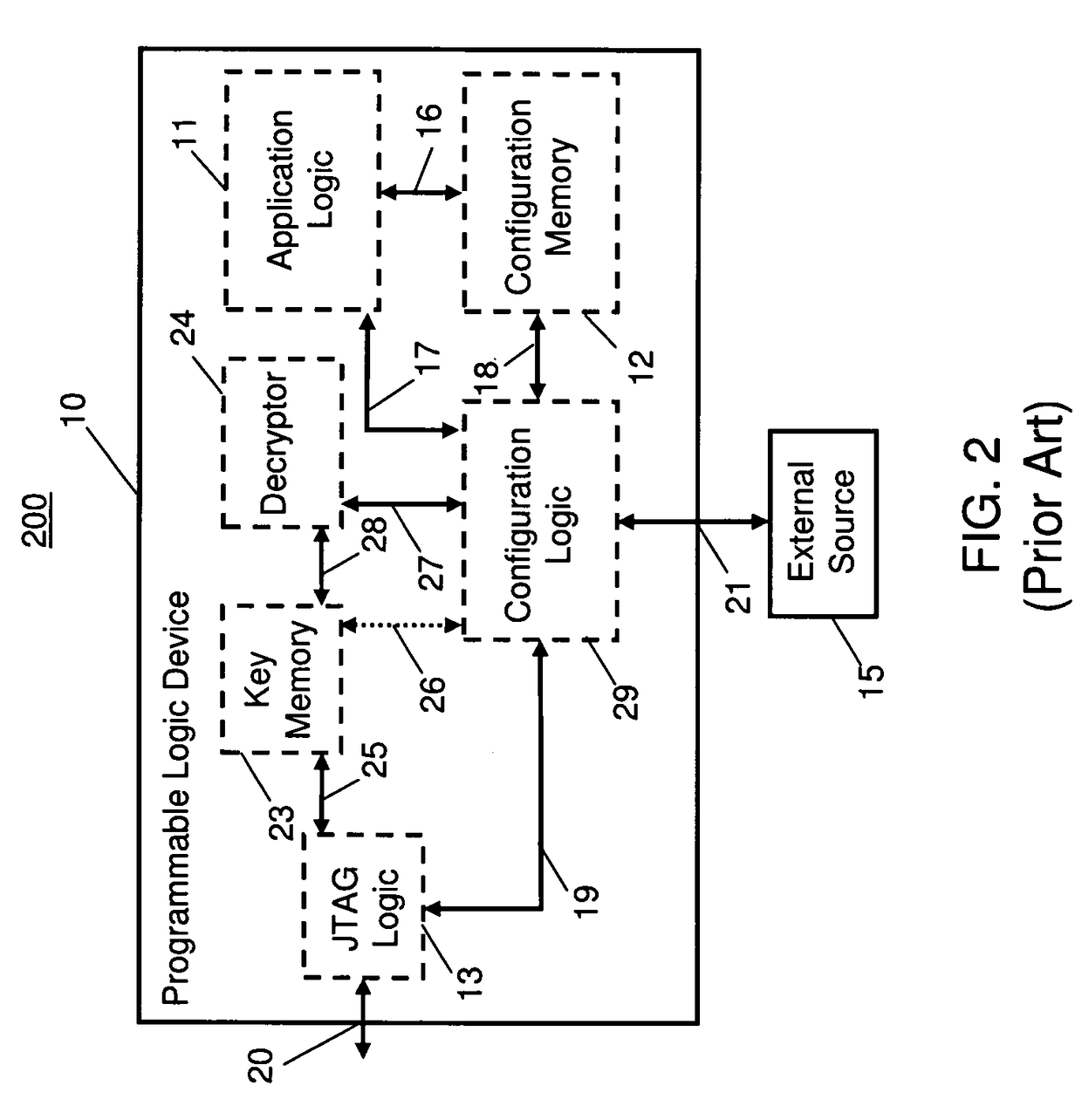

Method for system level protection of field programmable logic devices

InactiveUS7512813B2Multiple keys/algorithms usageMemory loss protectionField programmable logic devicesProgrammable logic device

A method for protecting a dynamically reconfigurable computing system includes generating an encoding key and passing the encoding key, through a system level bus, to at least one field programmable logic device and to a function library included within the system. The function library contains a plurality of functions for selective programming into the at least one field programmable logic device. A lock is generated so as to prevent external resources with respect to the system from accessing the encoding key during the passing thereof.

Owner:INT BUSINESS MASCH CORP

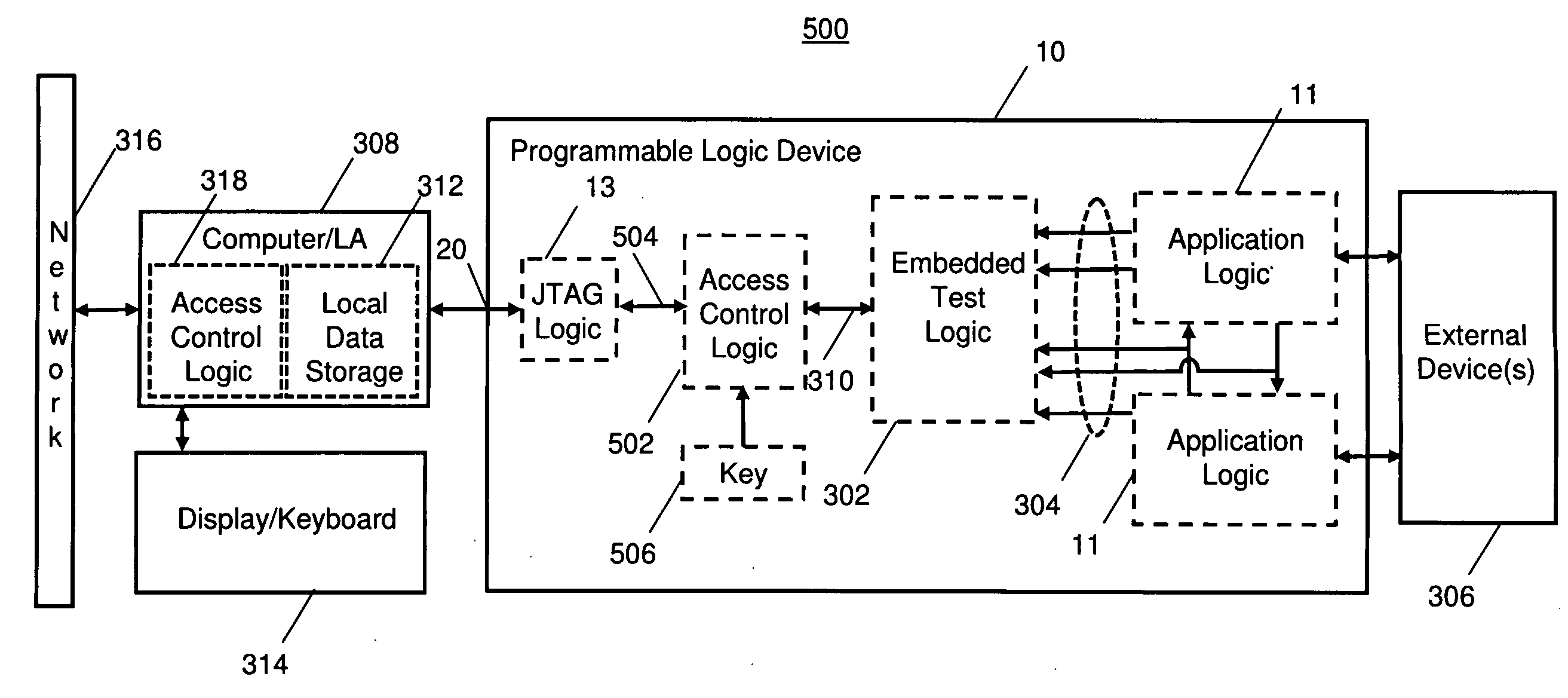

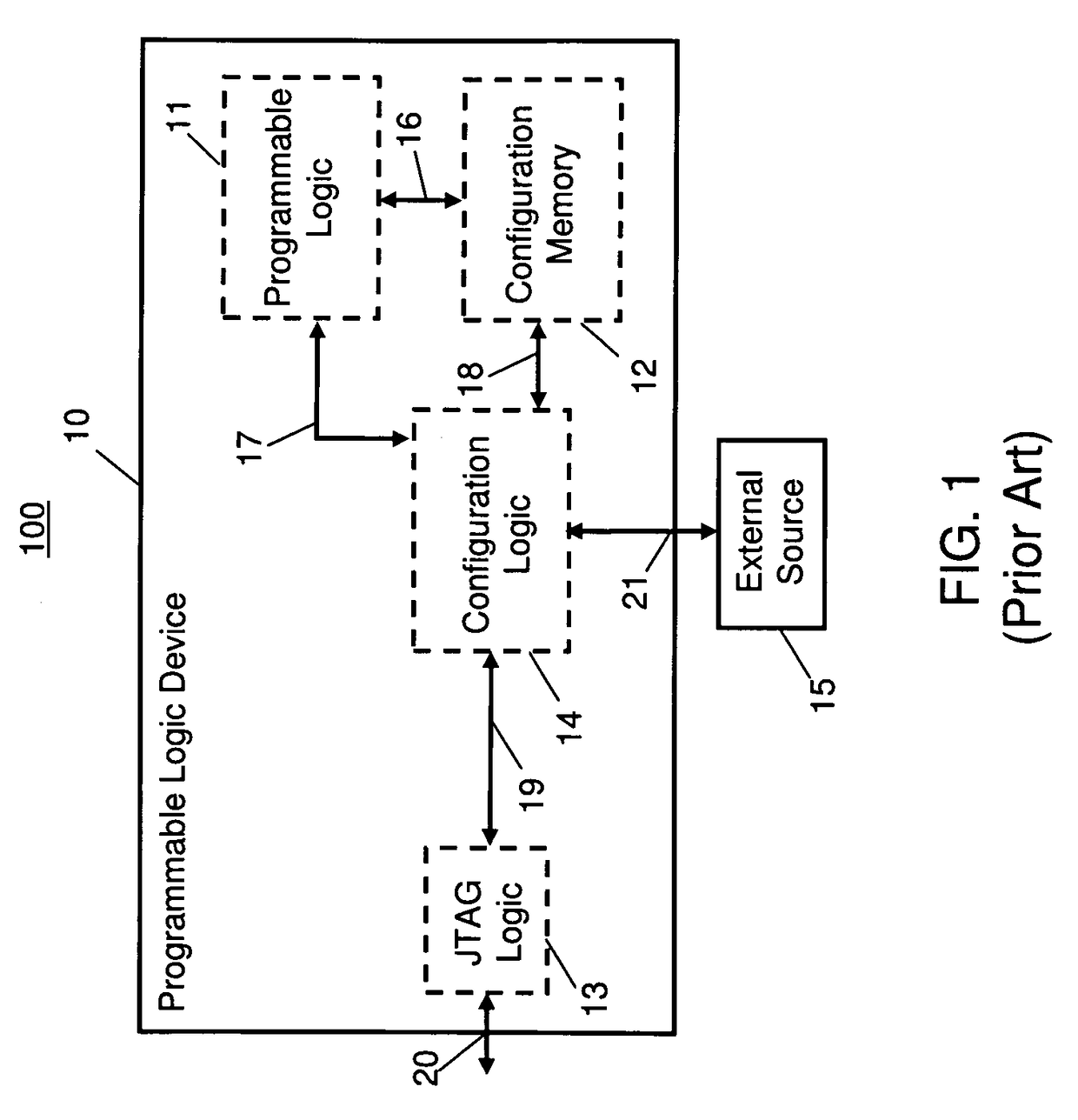

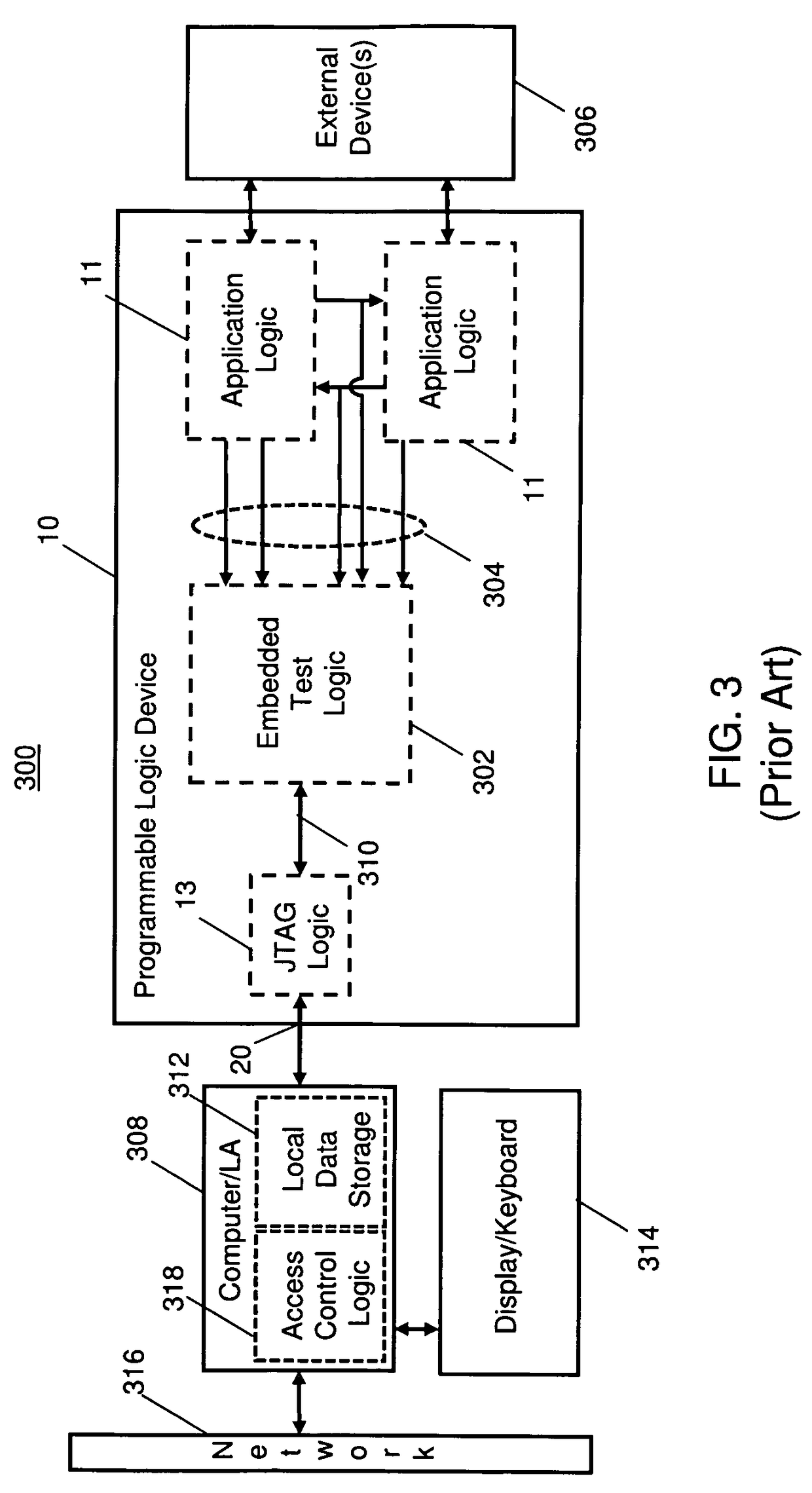

Programmable logic device having an embedded test logic with secure access control

InactiveUS20100141295A1Electrical testingUnauthorized memory use protectionField programmable logic devicesProgrammable logic device

An improved configuration for a programmable logic device and an improved method for configuration of a programmable logic device are provided. A programmable logic device such as field programmable logic device is configured to include an application logic, an embedded test logic that monitors the application logic, and an access control logic that grants access to an external device to embedded test data provided that an access control requirement is met that is based upon a key stored in a memory and information received from the external device.

Owner:INTUITIVE RES TECH

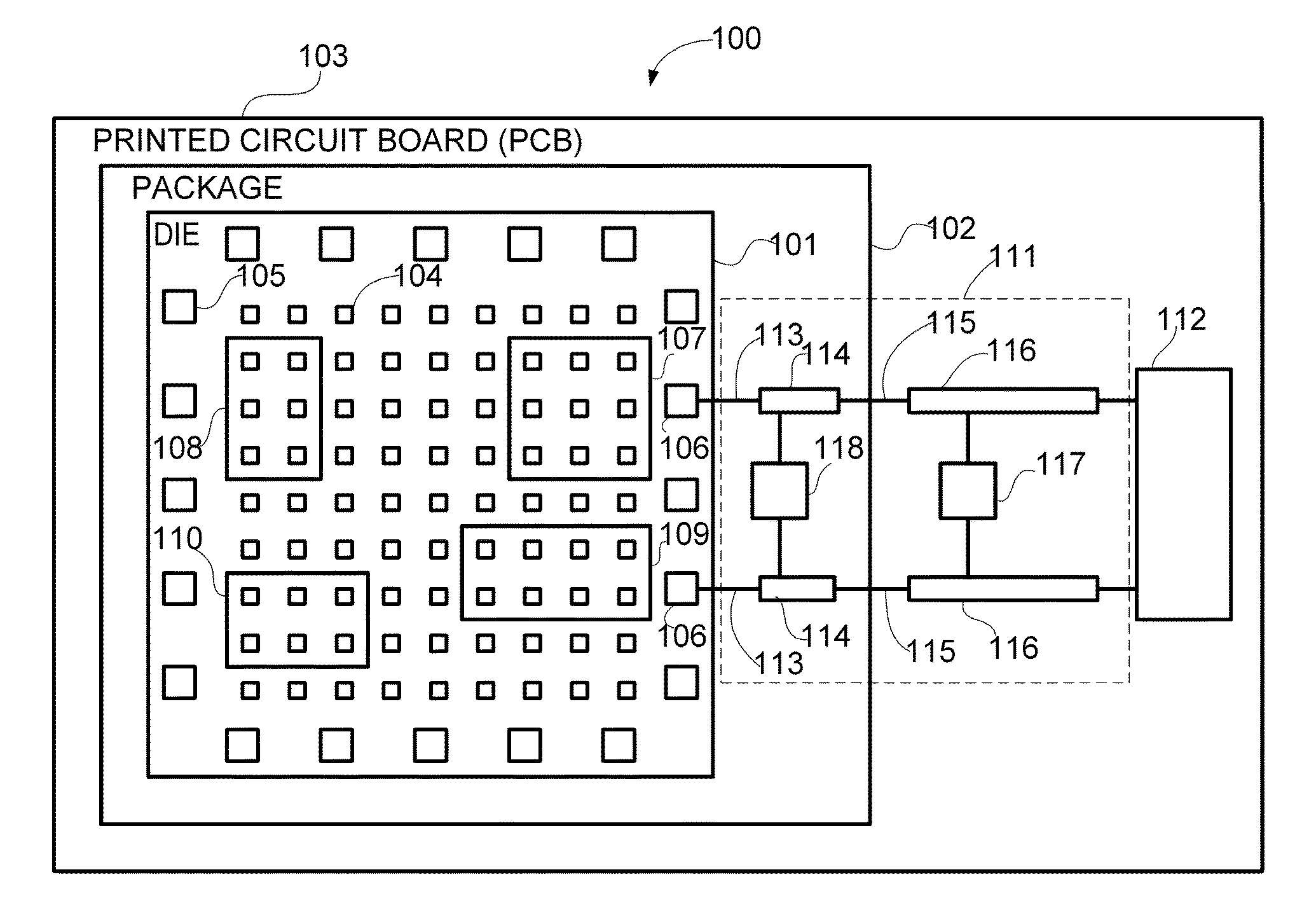

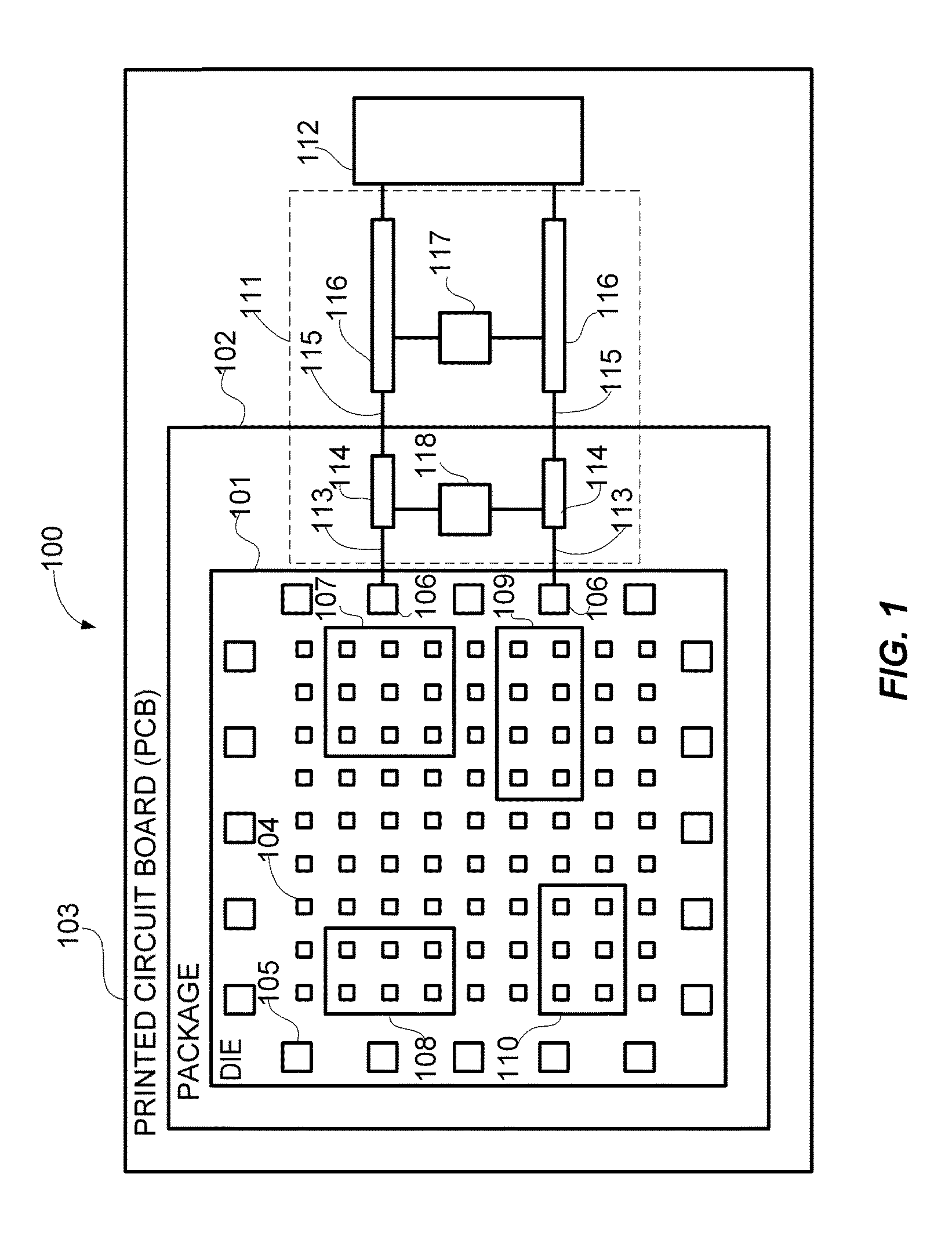

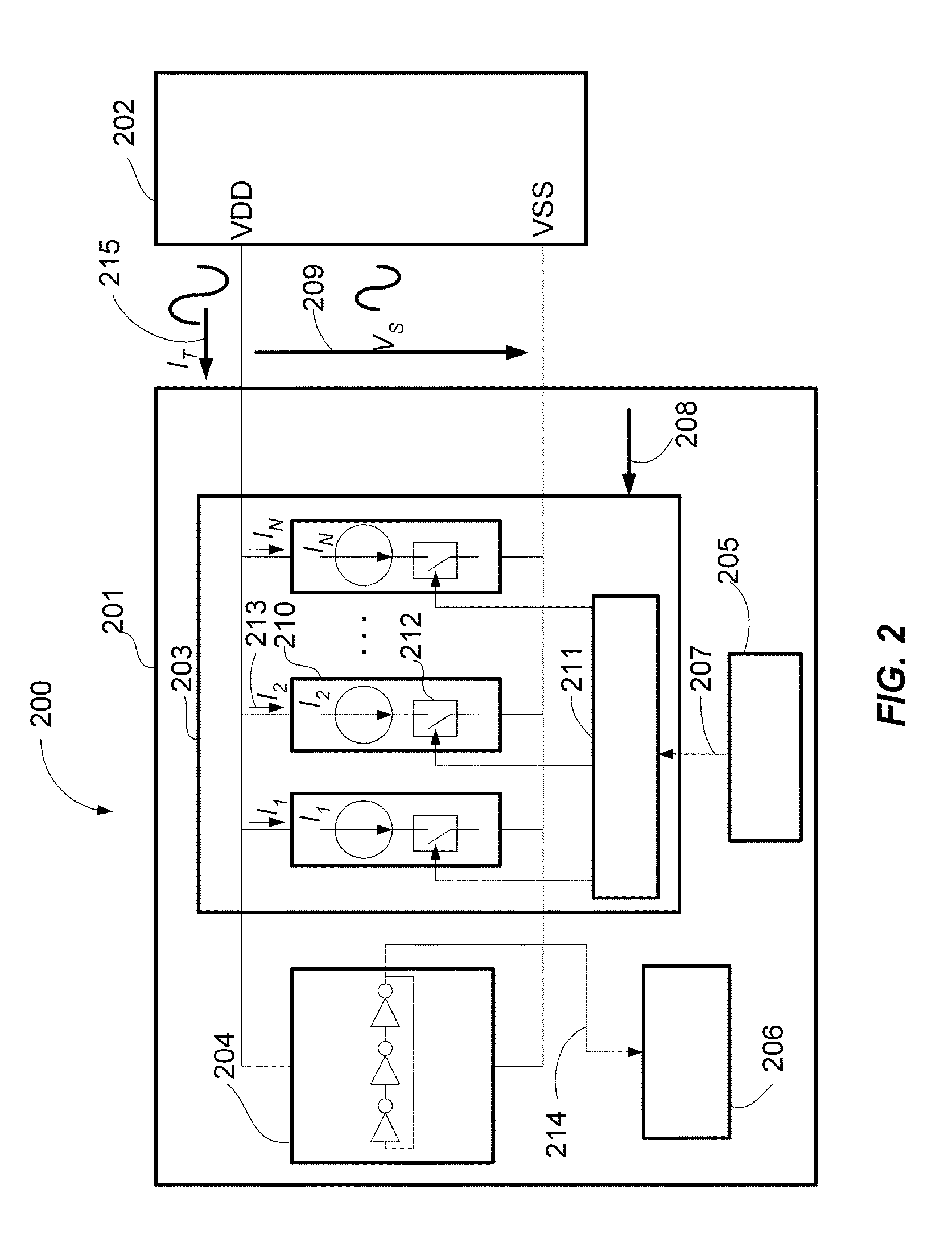

Method and system for measuring the impedance of the power distribution network in programmable logic device applications

ActiveUS20130030741A1Low costReduce power consumptionResistance/reactance/impedenceElectrical testingField programmable logic devicesProgrammable logic device

On-die measurement of power distribution impedance frequency profile of a programmable logic device (PLD), such as field programmable gate array (FPGA) or complex programmable logic device (CPLD), is performed by configuring and using only logic blocks resources commonly available in any existing programmable logic device, without the need of built-in dedicated circuits. All measurements are done inside the programmable logic device without the need of external instruments. The measurement method can be used during characterization to select decoupling capacitors or for troubleshooting existing systems, after which the programmable logic device may be reconfigured to perform any other user-defined function.

Owner:NOISECOUPLING LLC

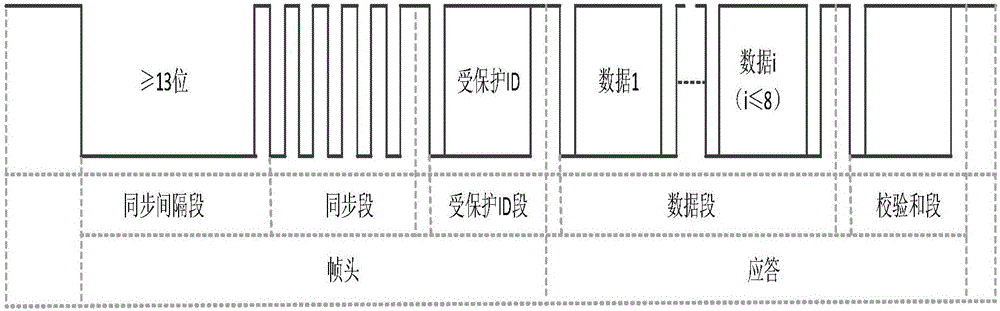

LIN bus decoding, triggering and analyzing technology

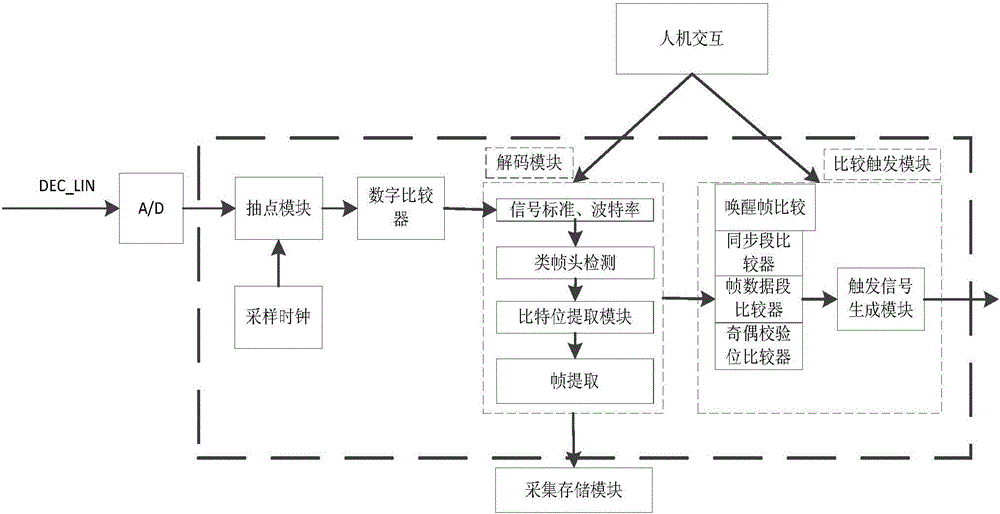

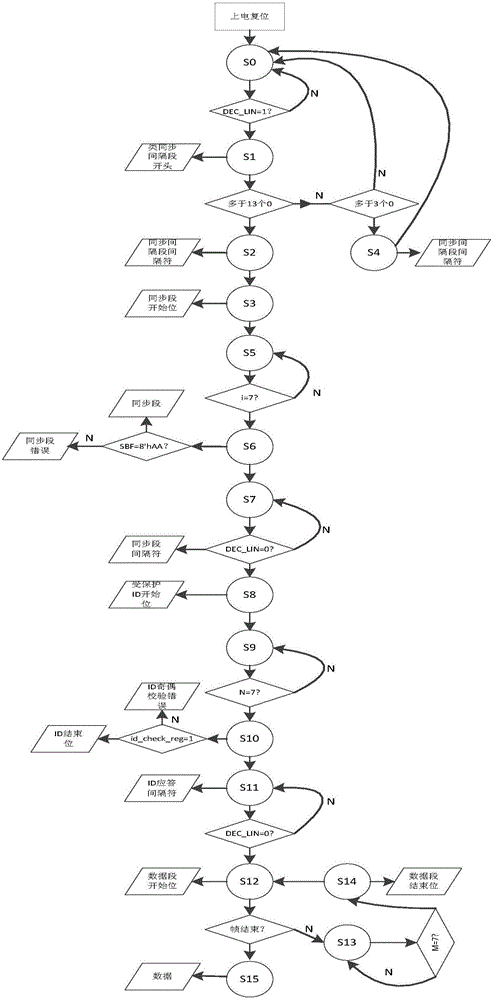

InactiveCN106021165AEasy to analyzeSimple methodElectric digital data processingField programmable logic devicesAnalysis method

The invention provides an LIN bus decoding, triggering and analyzing method, and relates to a technology which can be used for decoding data transmitted by LIN buses in real time, setting different triggering conditions according to users so as to carry out triggering on correct positions, and summarizing information of all frames in an acquisition range into an event list. Aiming at the disadvantages in the prior art, the method adopts a hardware decoding technology, so that the real-time decoding of a plurality of buses can be realized, the decoding speed is high and the efficiency is high; and only one field programmable logic device is required so that the cost is low. The method for analyzing and triggering LIN buses is simple and low in cost; the analysis and triggering for a plurality of LIN buses can be realized at the same time; and analysis can be carried out on LIN bus signals with any Baud rate so that the universality is strong.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

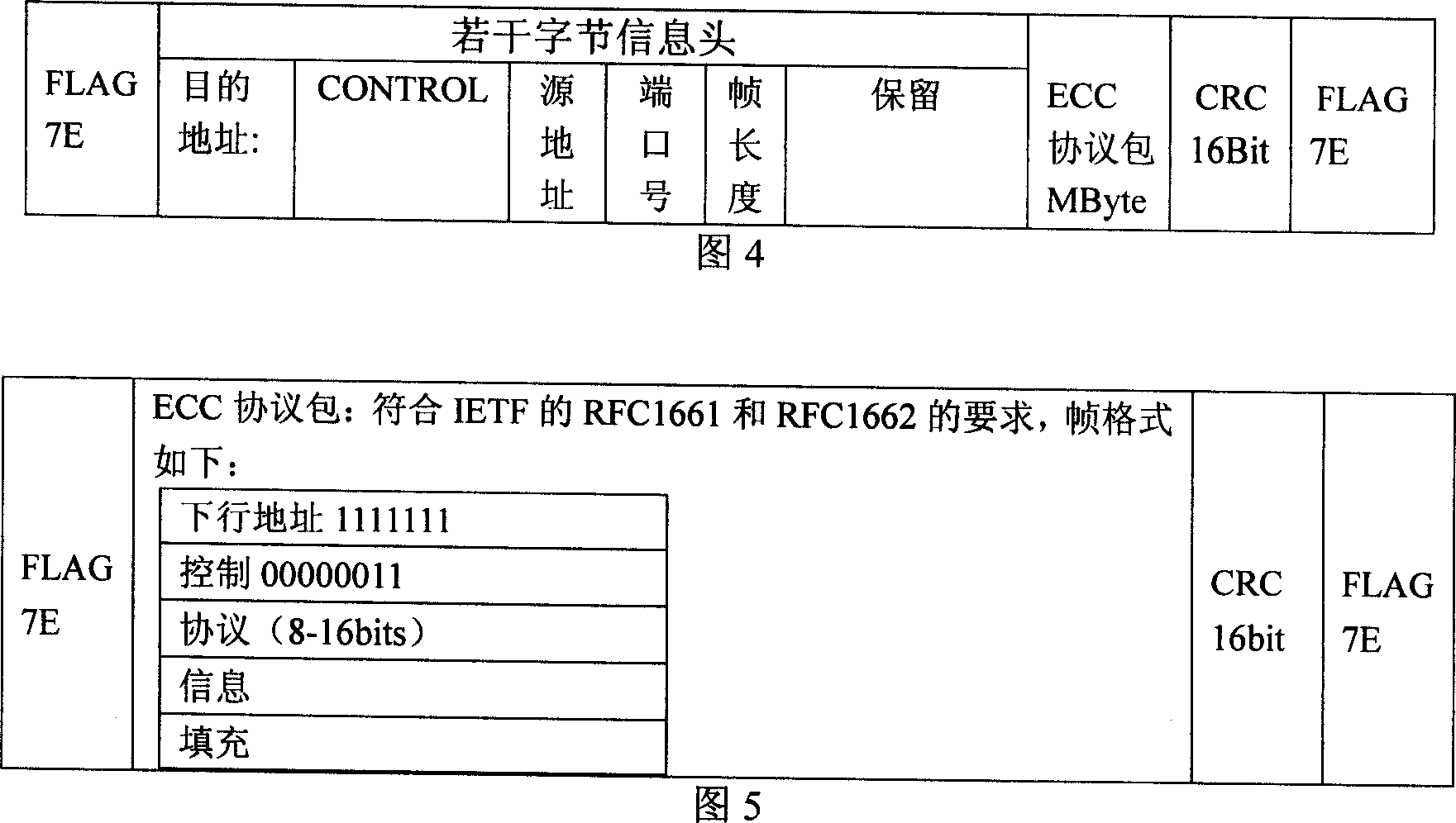

Realizing device for embedded control path communication using FPGA completing optic transmission device

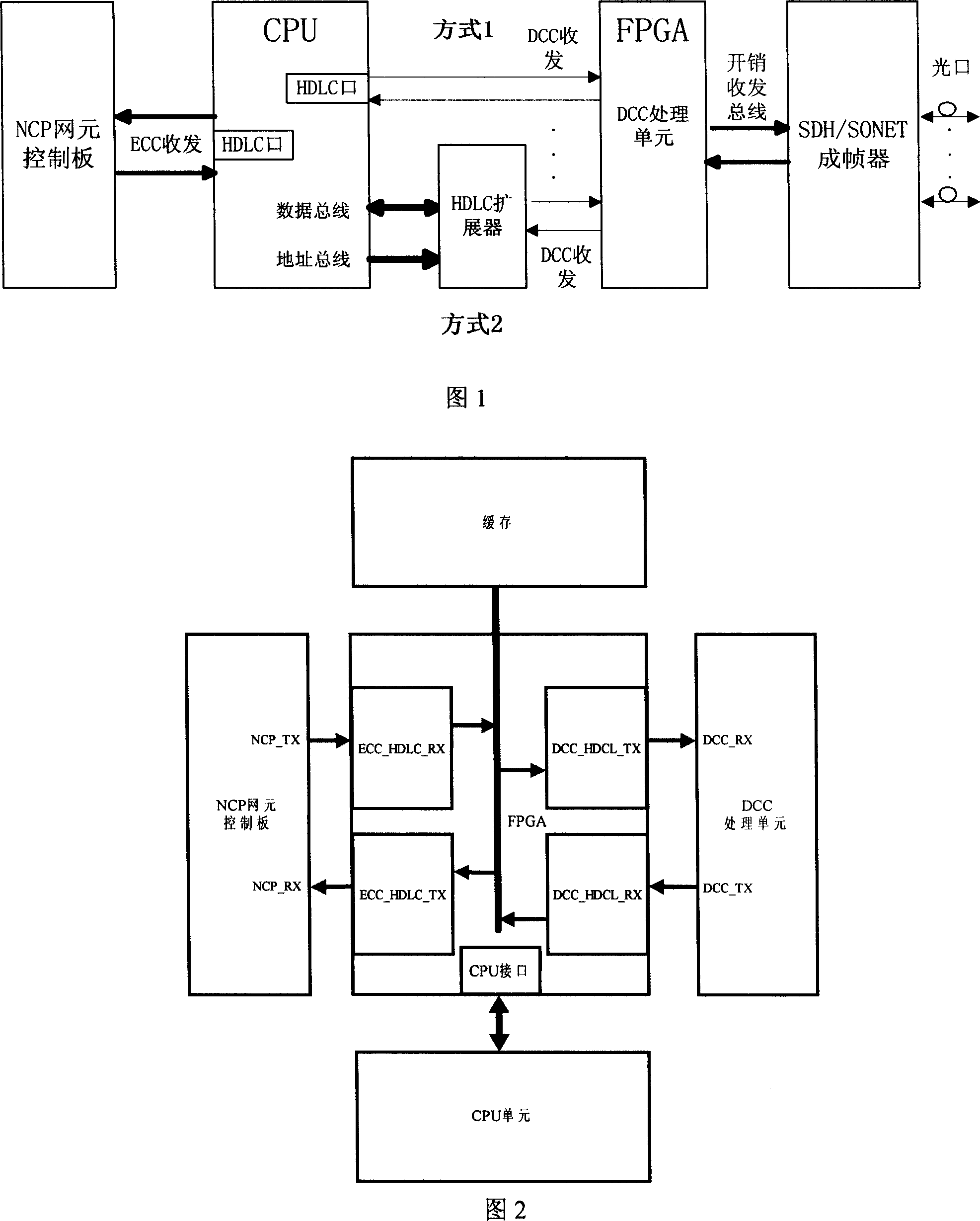

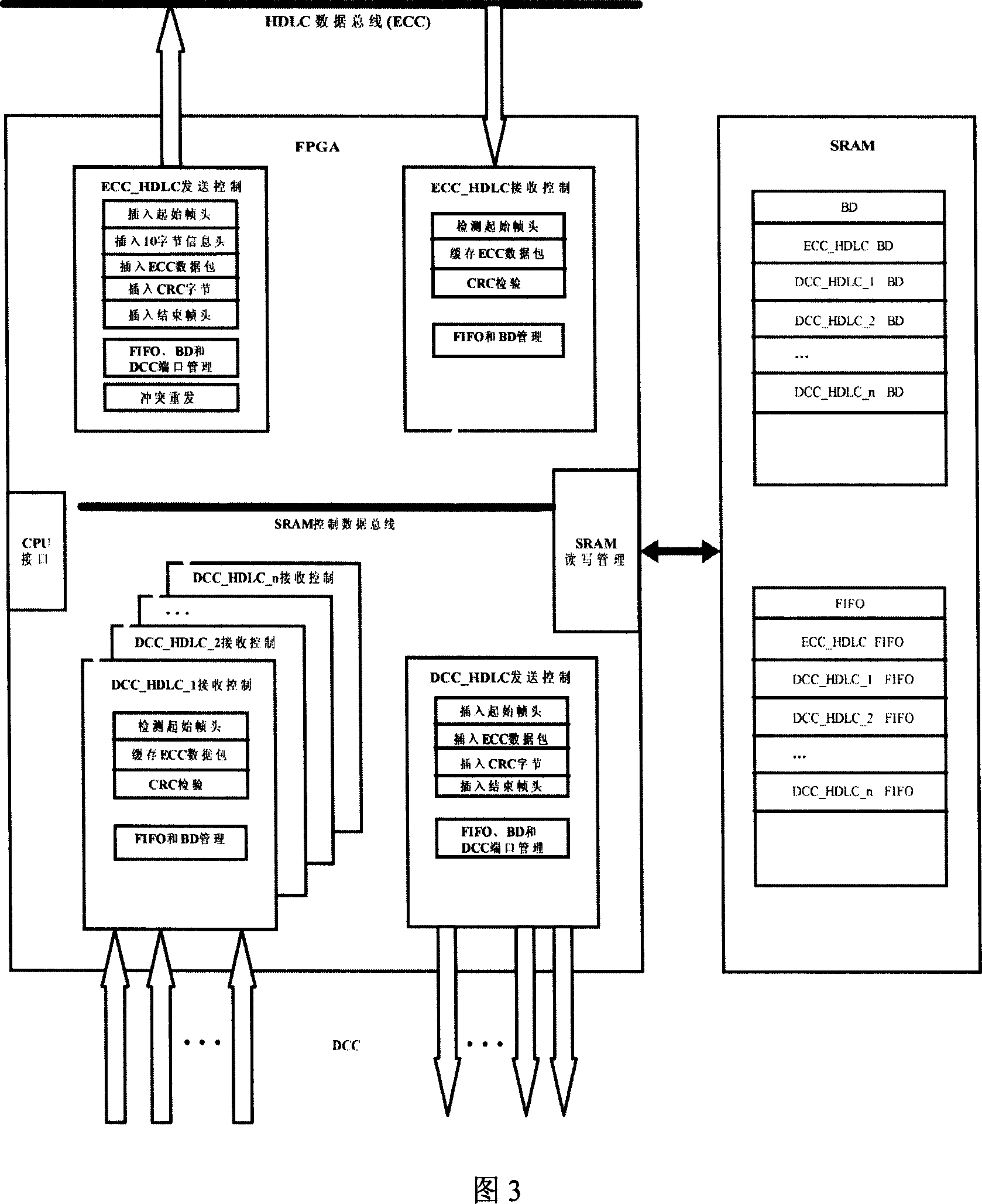

ActiveCN1988501AFree resourcesImprove stabilityData switching networksProtocol processingField programmable logic devices

The invention discloses an ECC communication device between the two equipments for using field programmable logic device (FPGA) to realize optical transmission (SDH / SONET). The invention proposes the ECC communication device for using FPGA hardware to process SDH / SONET automatically, through the effective FPGA logic design, the veneer CPU only need to complete some initialization operation of FPGA, the rest tasks of the agreement processing are completed by the FPGA hardware automatically. The invention solves those technical problems, such as CPU overloading in the traditional way, no real-time to complete the conversion from DCC protocol to ECC protocol and easy ECC communication blocking, and raises ECC communications stability of the fiber transmission network.

Owner:ZTE CORP

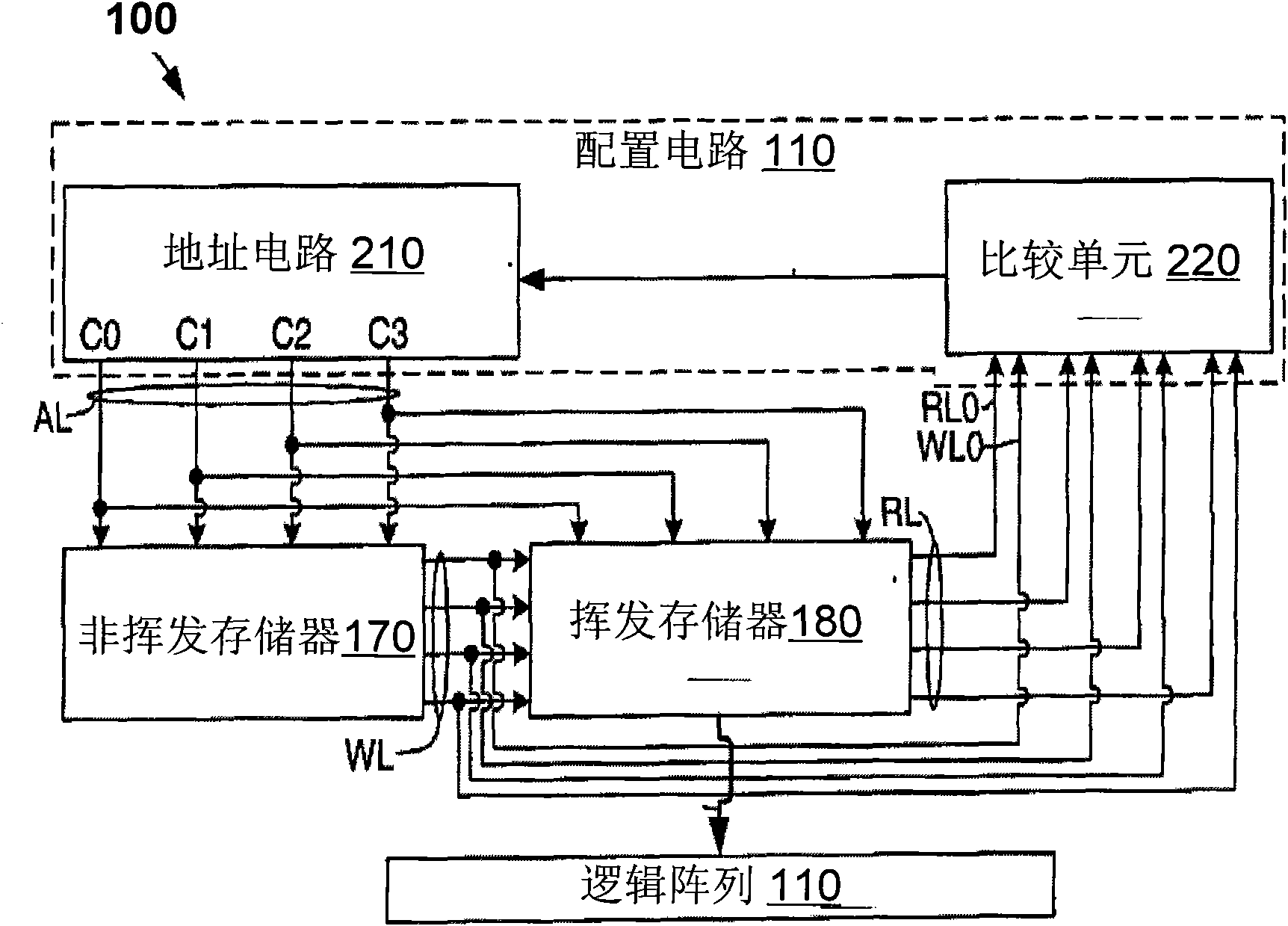

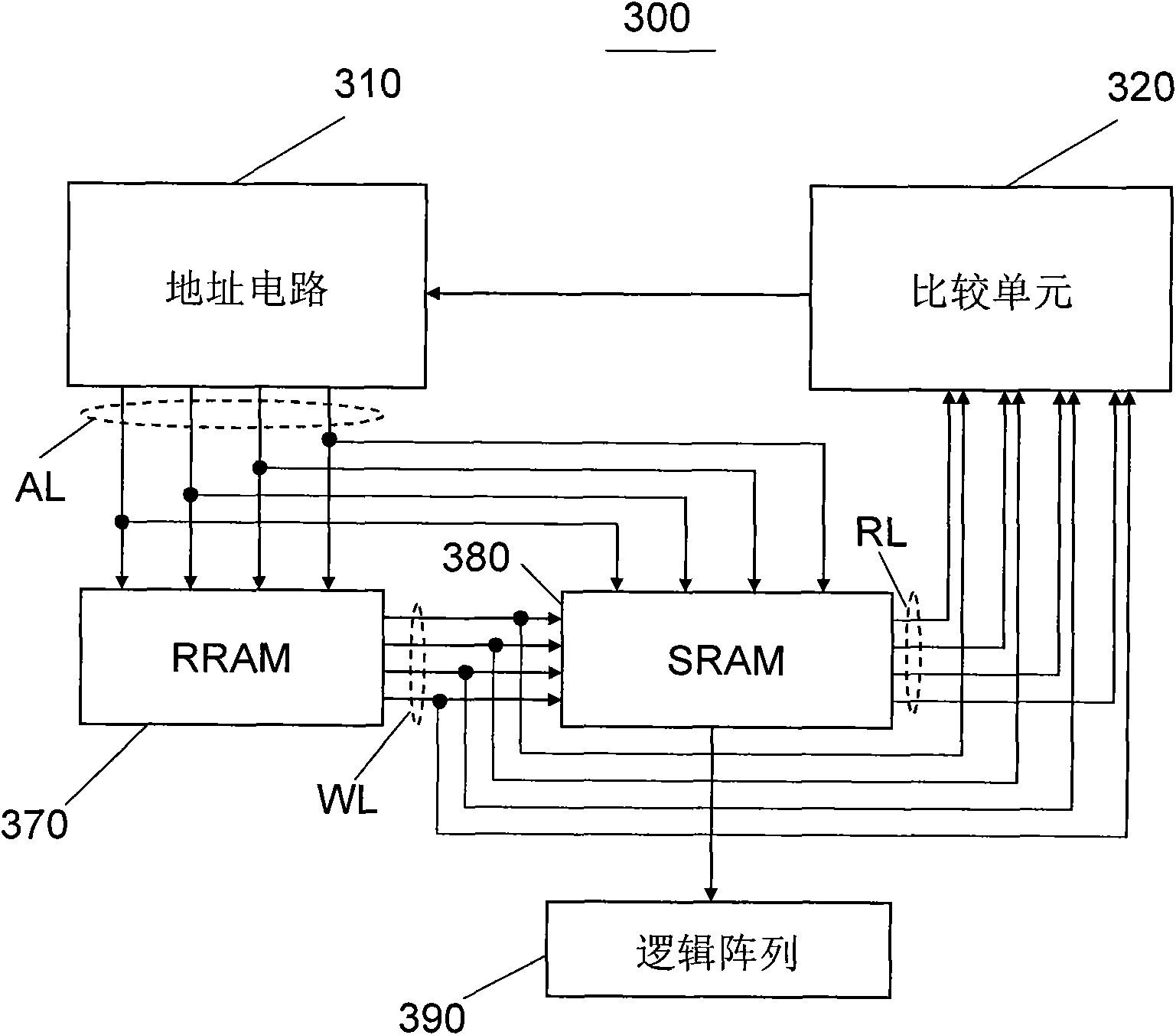

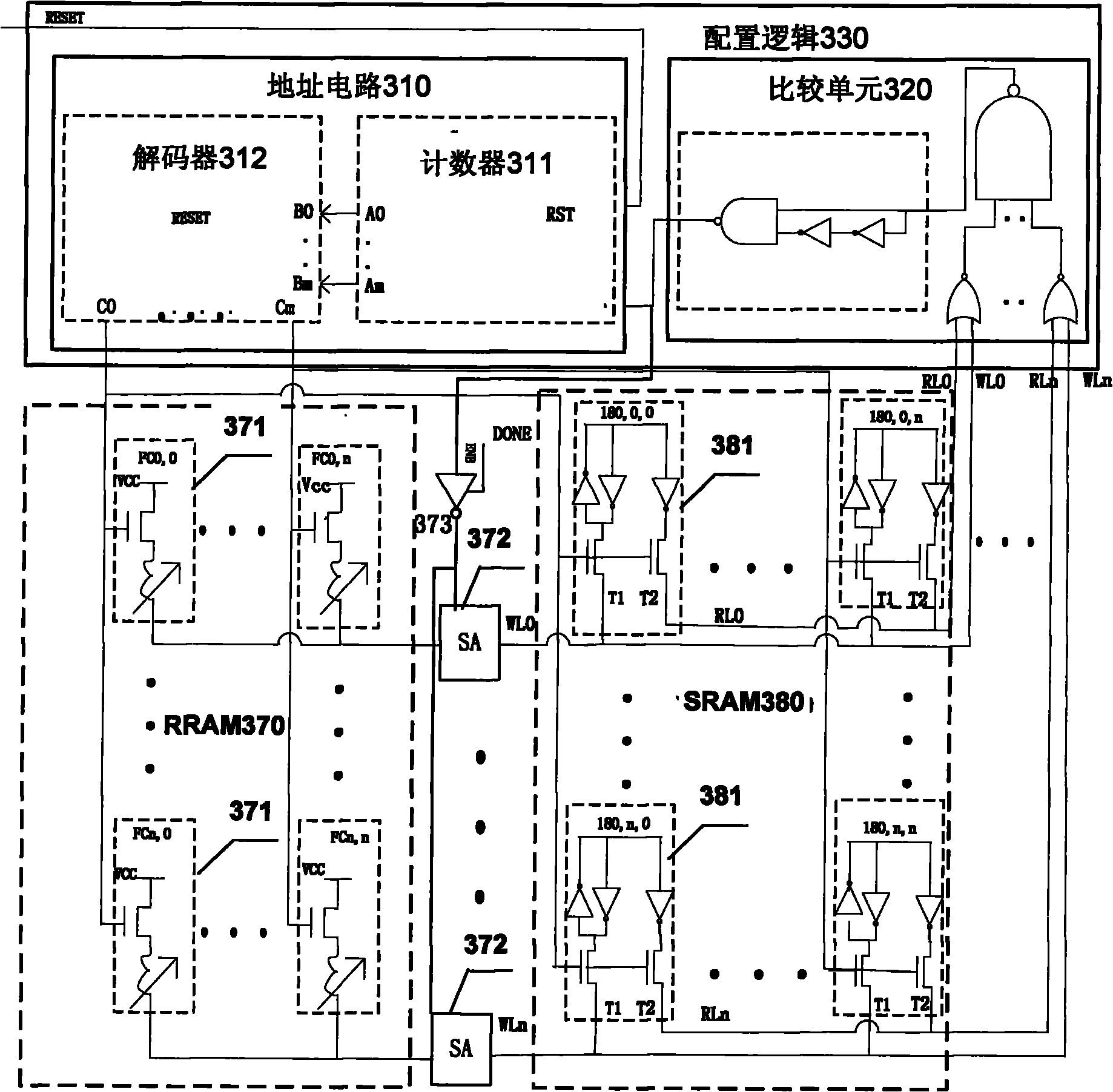

Single chip structured programmable logic device with resistance random access memory (RAM) module

InactiveCN102169711AAnti-radiation hasRadiation Hardness AchievedDigital storageStatic random-access memoryField programmable logic devices

The invention belongs to the technical field of programmable logic device and particularly discloses a programmable logic device. The programmable logic device comprises an address circuit module (310), a comparison unit (320), an SRAM (Static Random Access Memory) module (380), a logic array (390) and a resistance RAM module (370) which is used for overcoming the soft error rate in the SRAM module, wherein the resistance RAM module realizes single chip integration with the address circuit module, the comparison unit, the SRAM module and the logic array. The programmable logic device not only can overcome the SER (Symbol Error Rate) problem in the SRAM, but also has the characteristics of single chip, small size, radiation resistance, low power consumption and low cost.

Owner:FUDAN UNIV

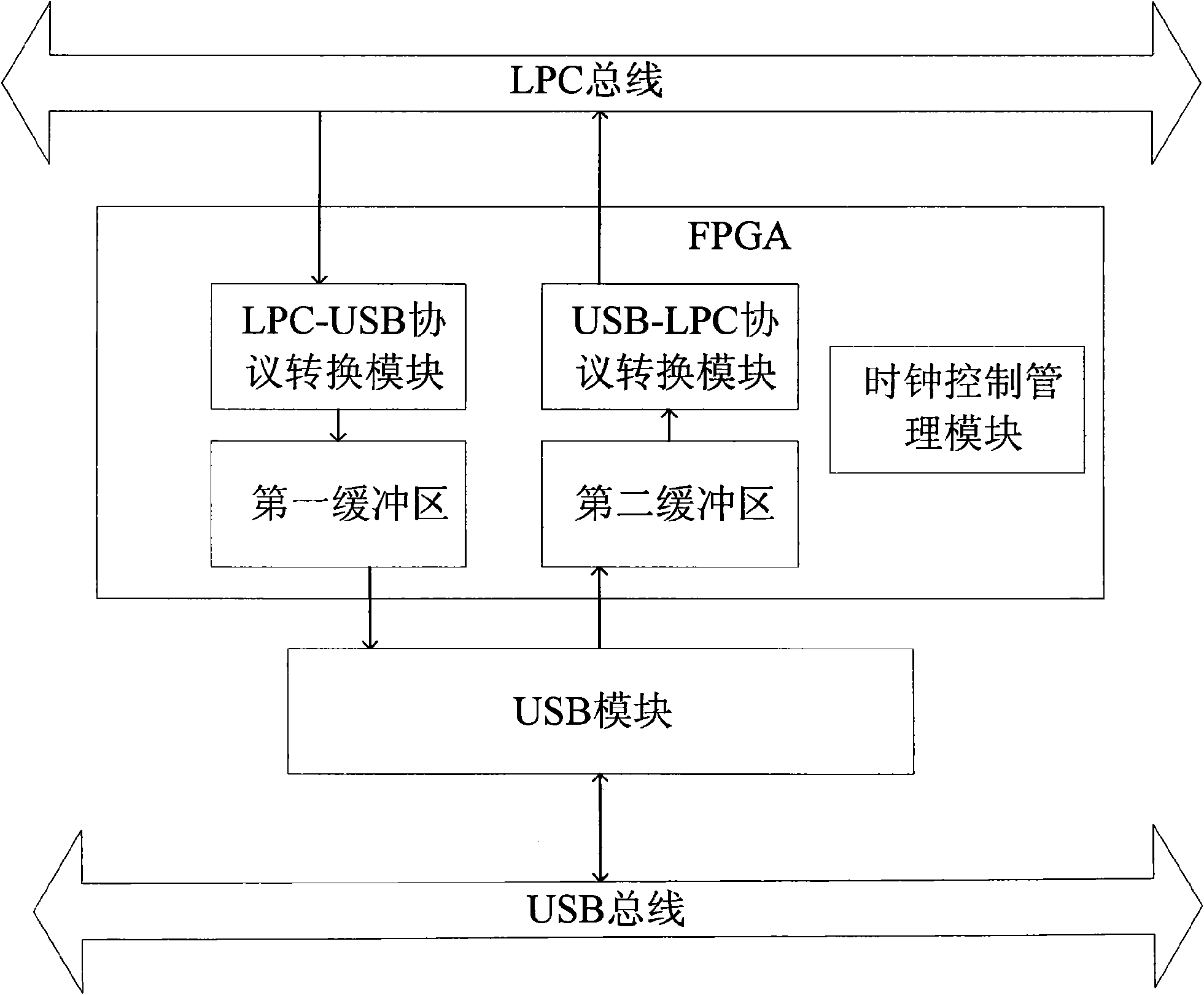

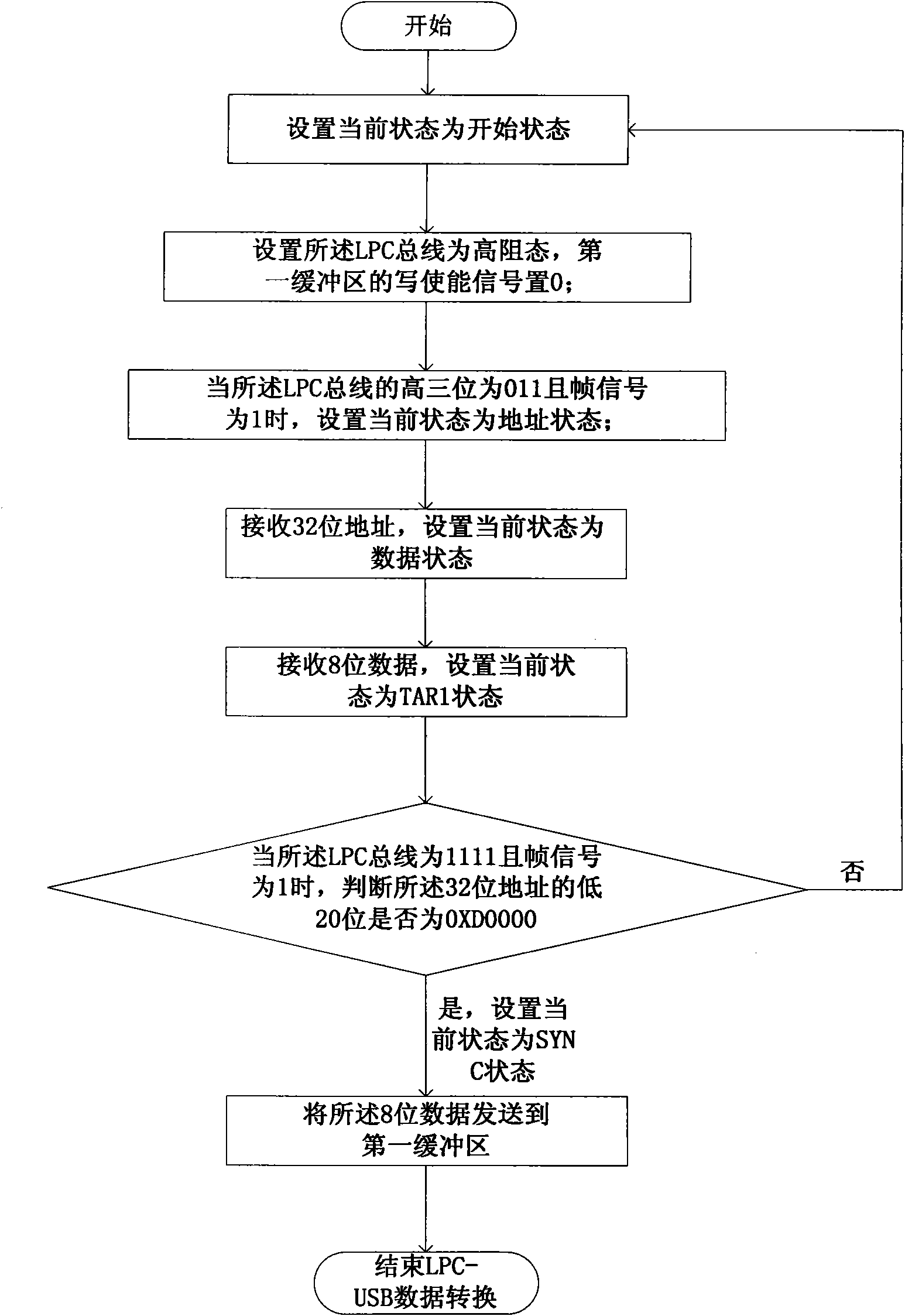

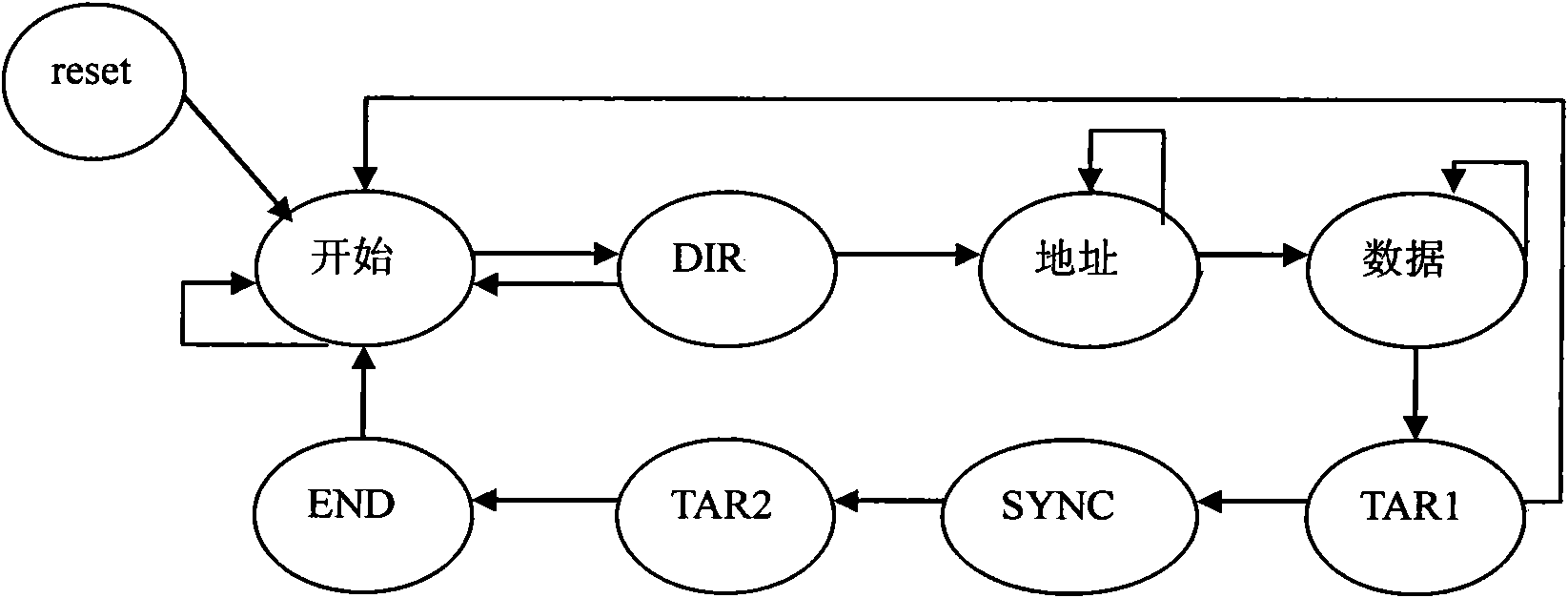

Device for achieving LPC-USB two-way communication by using FPGA and data conversion method of LPC-US and USB-LPC

ActiveCN101655825AReduce areaEasy to integrateEnergy efficient ICTEnergy efficient computingField programmable logic devicesLeast cost

The invention relates to a device for achieving LPC-USB two-way communication by using an FPGA and a data conversion method. The device comprises an LPC bus, a USB bus, a field programmable logic device and a USB module, wherein the field programmable logic device finishes the protocol conversion and transmission from LPC data to USB data from the LPC bus to the USB bus, and finishes the protocolconversion and transmission from the USB data to the LPC data from the USB bus to the LPC bus. The device achieves the full-duplex communication of the LPC bus and the USB bus by using the FPGA so asto satisfy certain special application occasions and solve the problems of the short-range communication of two or more computers without the help of other media. The device adopts a scheme with the FPGA and a USB control chip, and two FIFOs are arranged in the FPGA to replace an external FIFO so as to achieve high integration, and an integrated circuit board is manufactured to have the minimum area, the lowest power consumption and the least cost. Besides, the device uses the characteristic of occupying fewer ports of the FIFO to ensure that FIFO only occupies an address space of less than 2bits in a PC, thereby greatly saving the address space. Simultaneously, the device uses the characteristic of parallel high speed of the FPGA so that the scheme can satisfy the high-speed full-duplexcommunication.

Owner:深圳市九牛一毛智能物联科技有限公司

Programmable logic device having an embedded test logic with secure access control

InactiveUS7906983B2Electrical testingUnauthorized memory use protectionField programmable logic devicesProgrammable logic device

An improved configuration for a programmable logic device and an improved method for configuration of a programmable logic device are provided. A programmable logic device such as field programmable logic device is configured to include an application logic, an embedded test logic that monitors the application logic, and an access control logic that grants access to an external device to embedded test data provided that an access control requirement is met that is based upon a key stored in a memory and information received from the external device.

Owner:INTUITIVE RES TECH

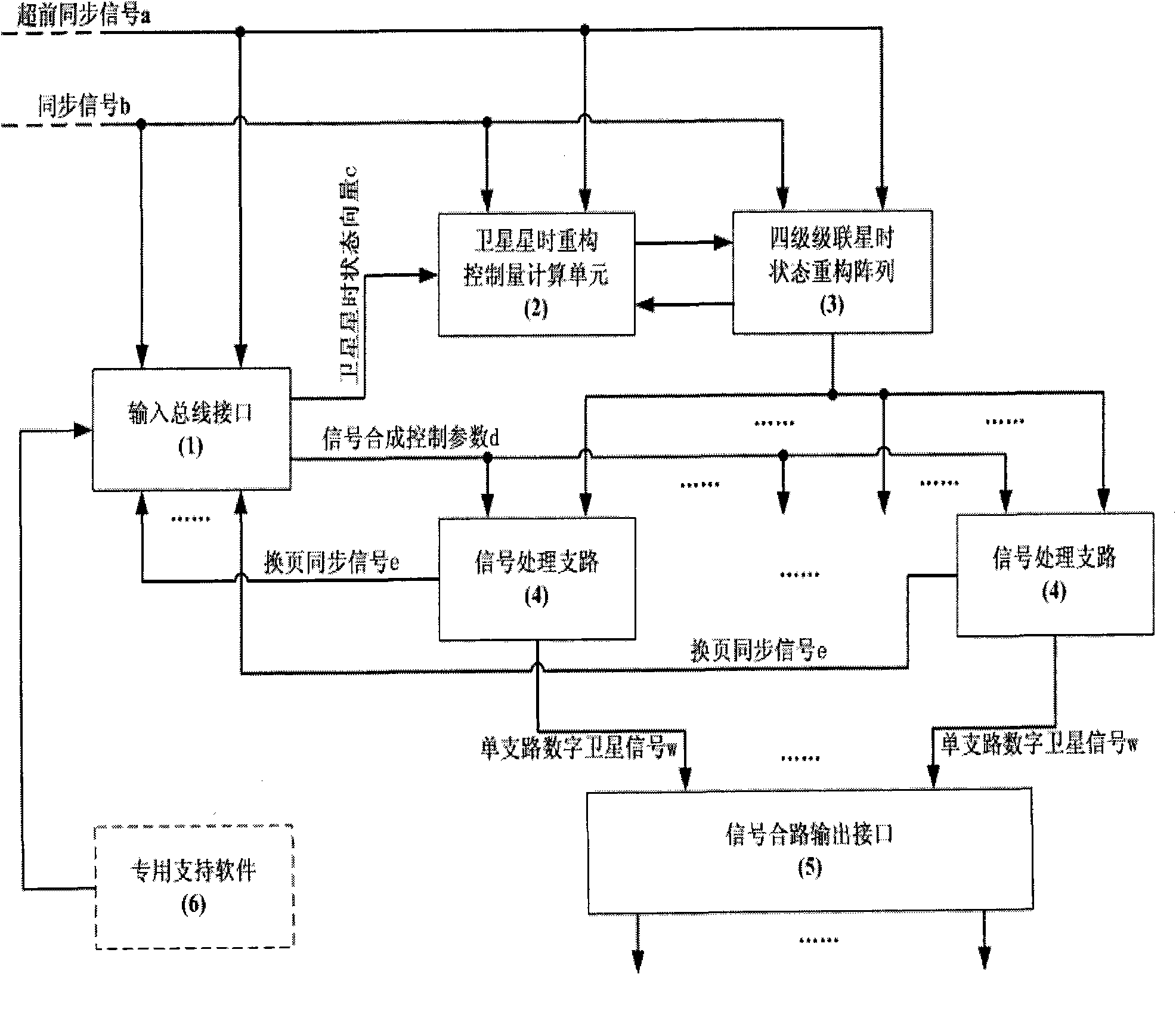

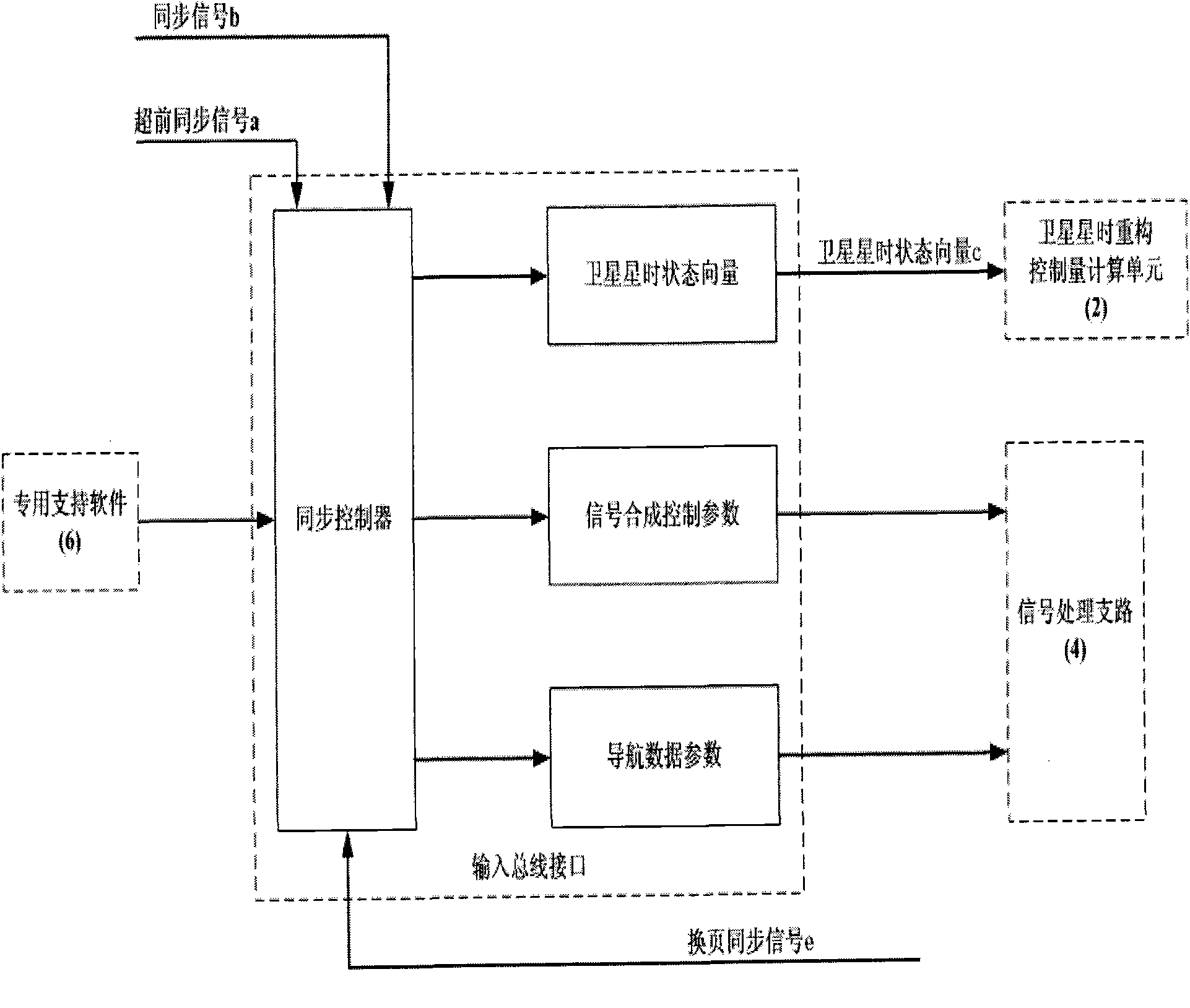

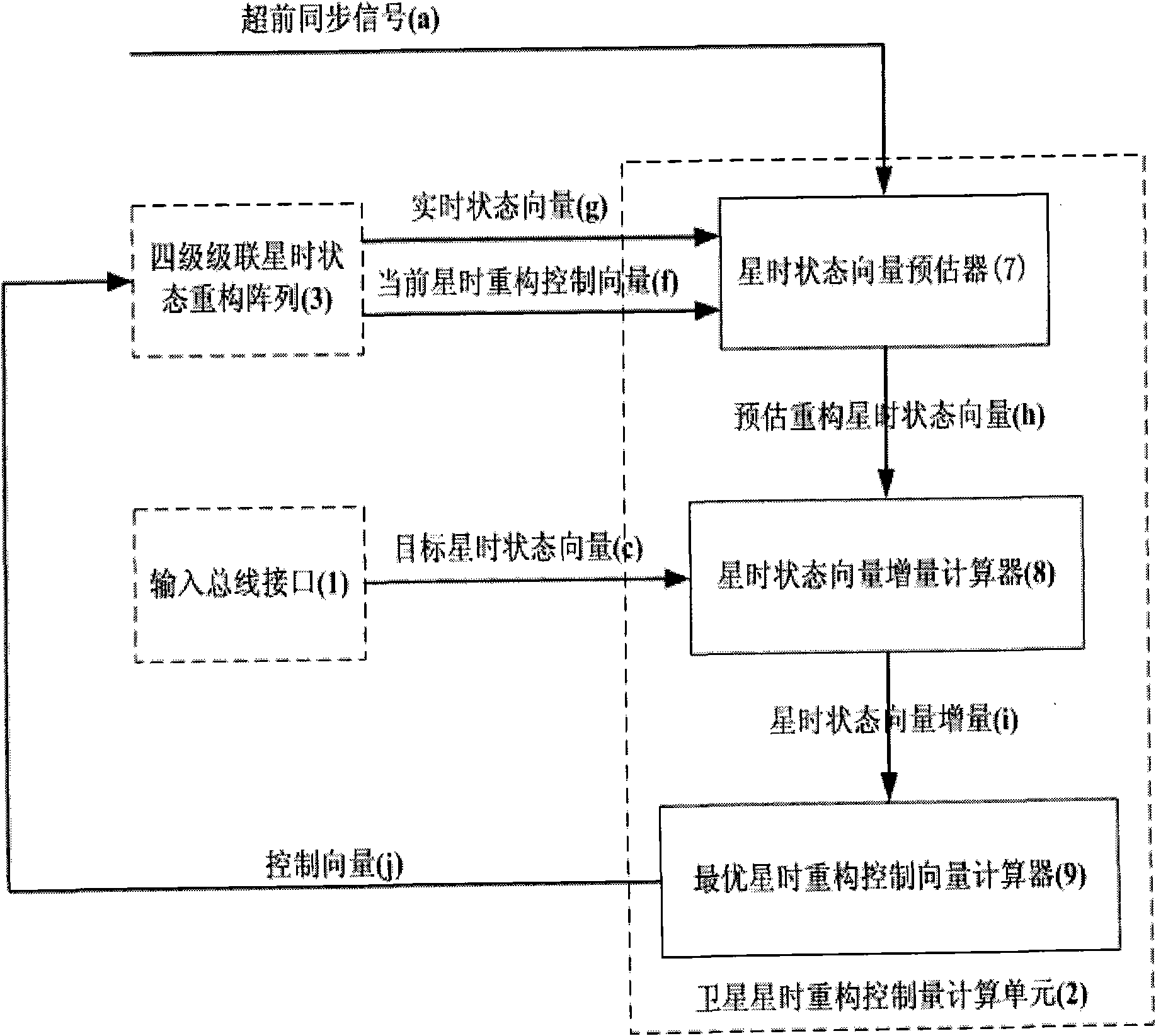

General simulated satellite broadcast signal synthesizer based on satellite star-time reconstruction

ActiveCN102122986AImprove reconstruction accuracyImprove performanceSatellite broadcast receivingSatellite radio beaconingNatural satelliteField programmable logic devices

The invention relates to a general simulated satellite broadcast signal synthesizer based on satellite star-time reconstruction, which is provided with a hardware circuit and special support software which are capable of realizing designed functions through a super-large-scale field programmable logic device, wherein the hardware circuit consists of an input bus interface, a satellite star-time reconstruction control quantity calculating unit, a four-stage cascaded star-time status reconstruction array, a signal processing branch and a signal combination output interface; and the special support software is shown in a form of a header file, a library or a target code and embedded into the specific simulator software of a satellite navigation system. Compared with the prior art, the general simulated satellite broadcast signal synthesizer based on the satellite star-time reconstruction has the advantages that: the support to a hardware processing unit for the multi-path signal real-time reconstruction of a single satellite and corresponding calculation software is provided; the real-time reconstruction of a multi-satellite signal environment of the conventional navigation system can be supported by multi-unit parallel integrated processing; and the functions of each branch of the general satellite star-time reconstruction and a broadcast satellite signal synthesizer can be configured flexibly or combined arbitrarily according to a user requirement.

Owner:PLA SECOND ARTILLERY ENGINEERING UNIVERSITY

Logic verification module apparatus to serve as a hyper prototype for debugging an electronic design that exceeds the capacity of a single FPGA

ActiveUS8356272B2Detecting faulty computer hardwareCAD circuit designComputer architectureField programmable logic devices

A apparatus and a system and method to operate the above provide a reconfigurable platform for emulating and debugging a user design which exceeds the capacity of a single field programmable logic device (FPGA). The method and system facilitates design and emulation of a system-on-a-chip type user design. The netlist of a user design may be included with logic value tunneling circuits in an emulation using a platform including a number of field programmable devices. A verification module apparatus provides a hyper prototype for debugging an electronic design that exceeds the capacity of a single FPGA. A verification module provides access to a plurality of attached FPGAs by means of Logic Value Tunneling Transmitters and Receivers which deliver many signals over few pins.

Owner:S2C LTD

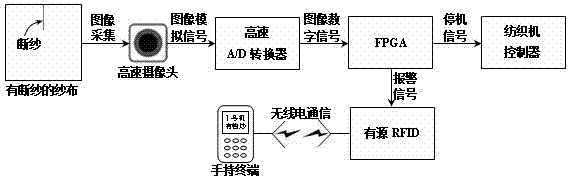

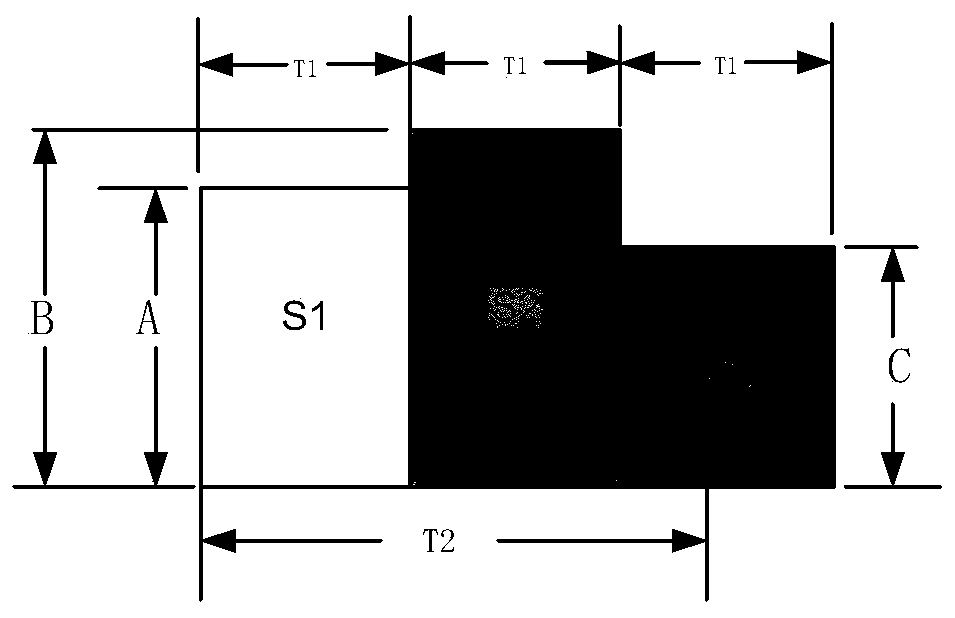

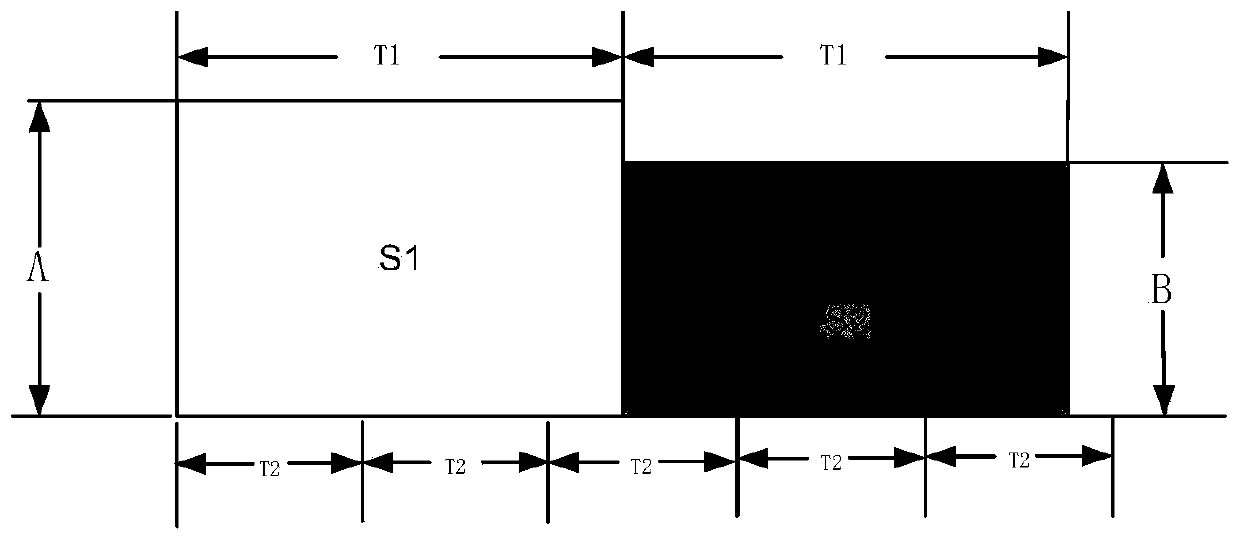

Broken yarn detection method based on video signal processing

The invention belongs to the field of signal detection and processing in textile industry and relates to a broken yarn detection method for looms. The broken yarn detection method for looms overcomes the defects in the existing broken yarn detection, and uses area means instead of point means, so that broken yarn detection is more accurate and reliable. A system of broken yarn detection comprises a high-speed camera, a high-speed A / D (analog / digital) converter, FPGAs (field programmable logic devices), an active RFID (radio frequency identification device), a handheld terminal and the like. Pictures of gauze are captured by the high-speed camera, the high-speed A / D converter is used for sampling and analog-digital conversion for image analog signals, image data are rapidly analyzed and processed by FPGA technology, signals are output to stop a loom according to processing results, and wireless alarm signals are transmitted to the handheld terminal through the active RFID.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

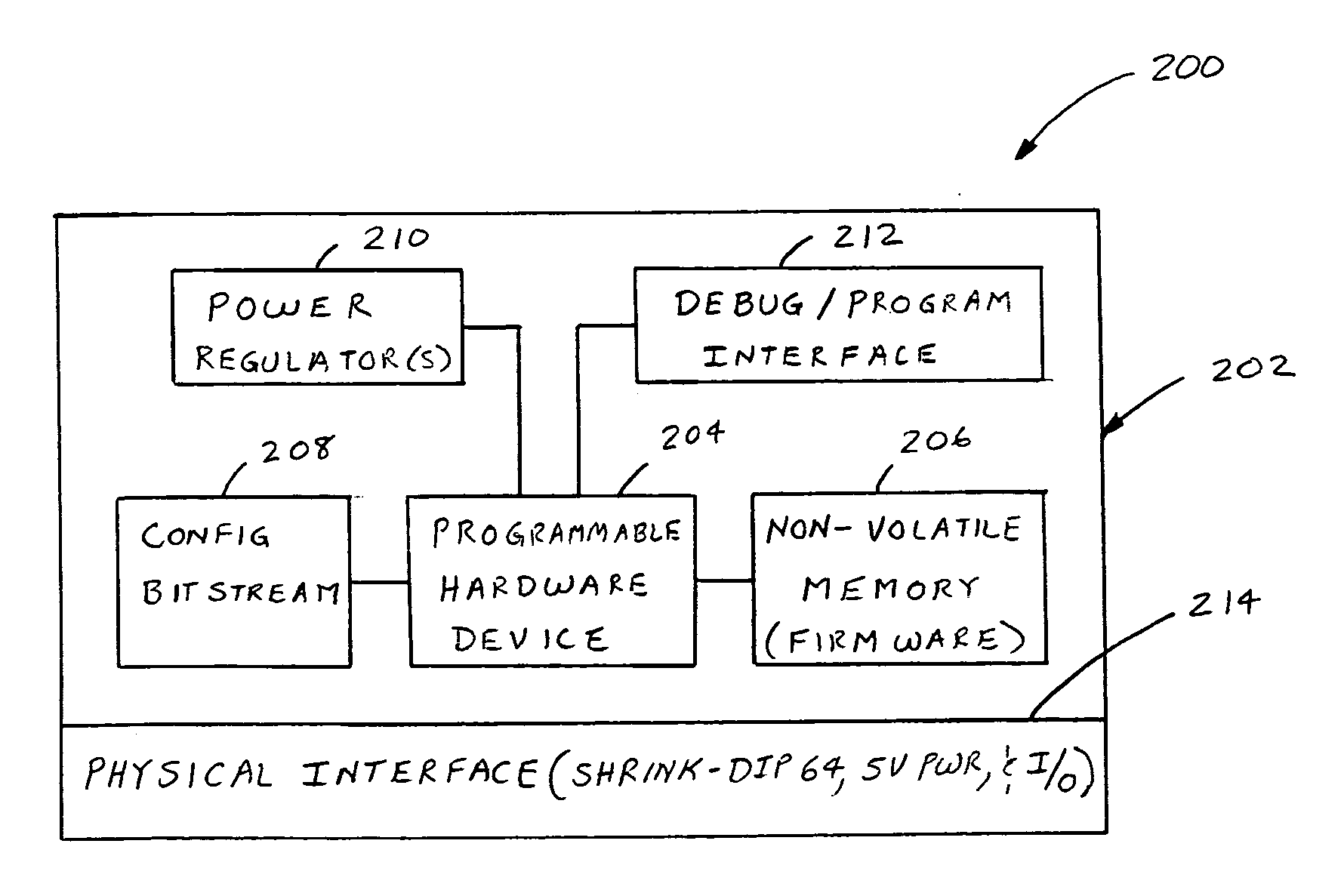

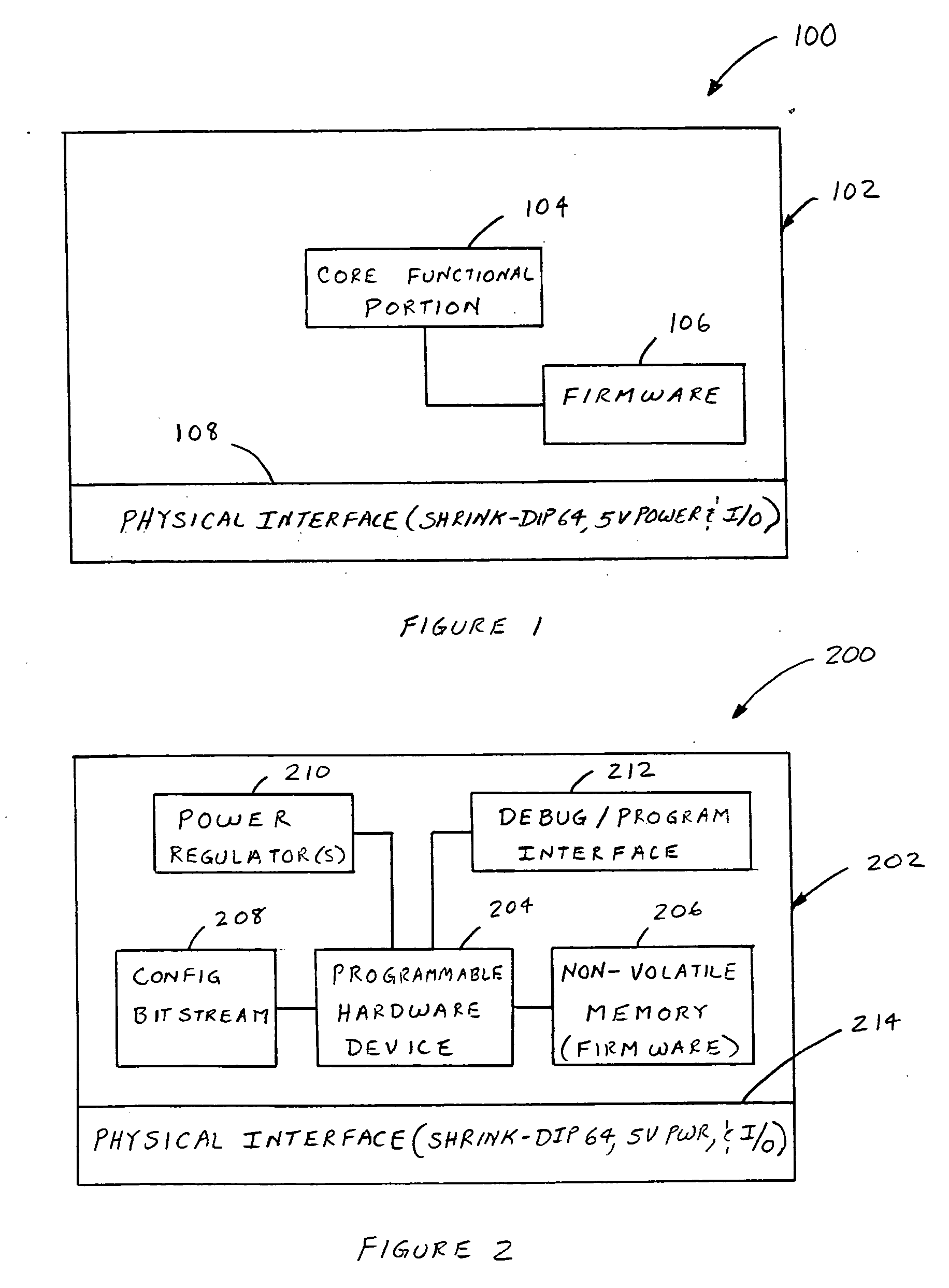

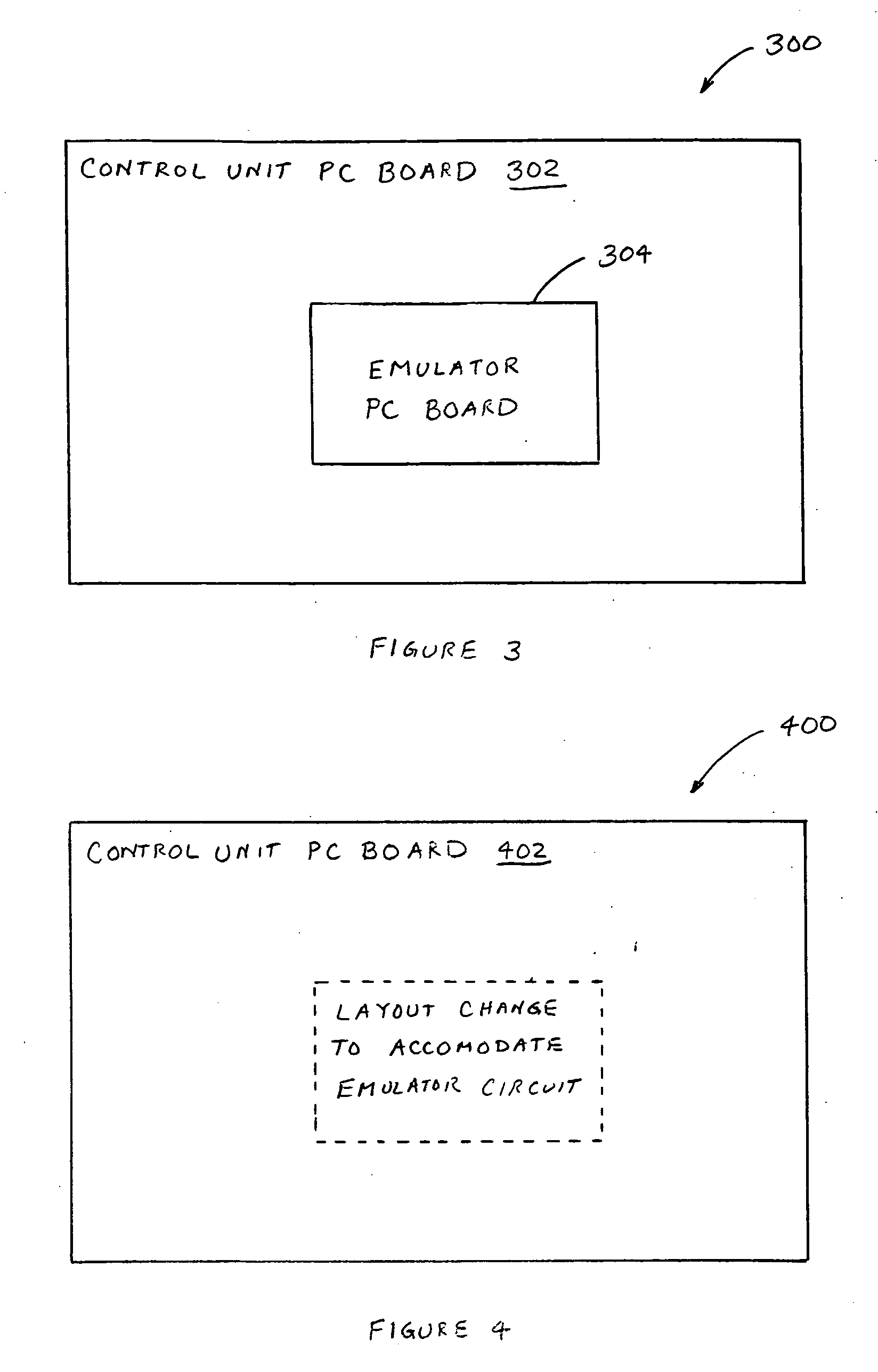

System and method for dealing with component obsolescence in microprocessor-based control units

InactiveUS20060282254A1Error detection/correctionSoftware simulation/interpretation/emulationField programmable logic devicesComplex programmable logic device

A method of dealing with a microprocessor used in a first vehicle system control unit becoming obsolete. The method comprises providing a second vehicle system control unit for performing substantially the same operation as that of the first vehicle system control unit, wherein the second vehicle system control unit includes a microprocessor emulation unit having a programmable hardware device adapted to emulate the operation of the core functional portion of the microprocessor. The programmable hardware device may comprise a field programmable gate array (FPGA) device, a field programmable logic device (FPLD), a programmable logic array (PLA), a mask programmable logic device (MPLD), a programmable array logic (PAL) device, or a complex programmable logic device (CPLD). The microprocessor emulation unit may include substantially the same firmware and physical interface of the obsolete microprocessor.

Owner:BAYERISCHE MOTOREN WERKE AG

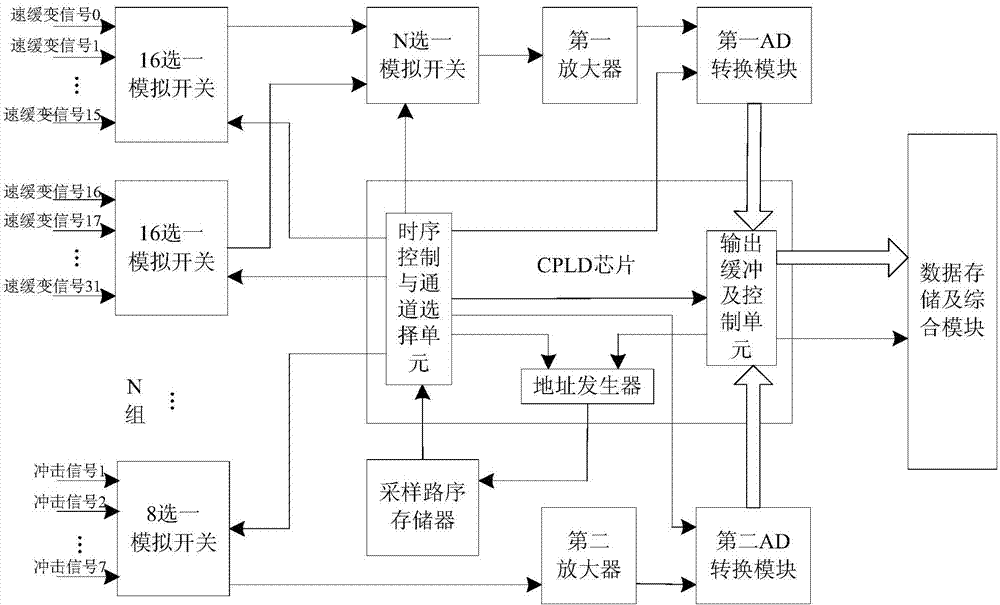

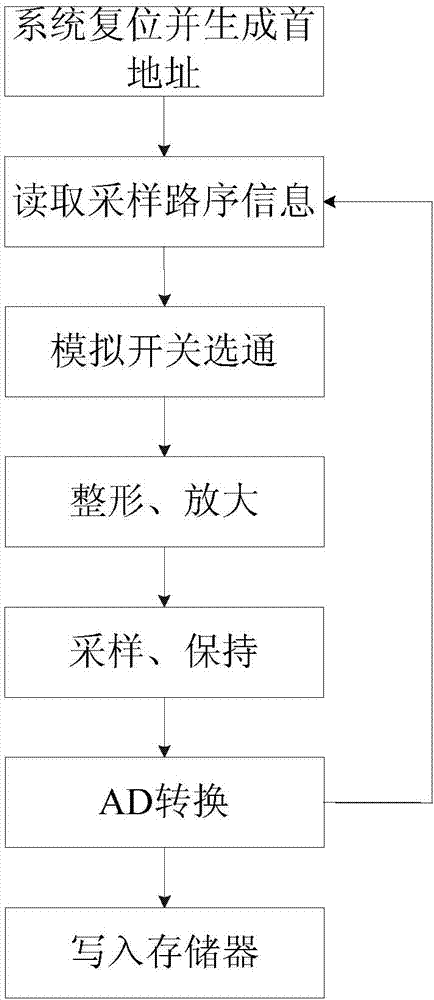

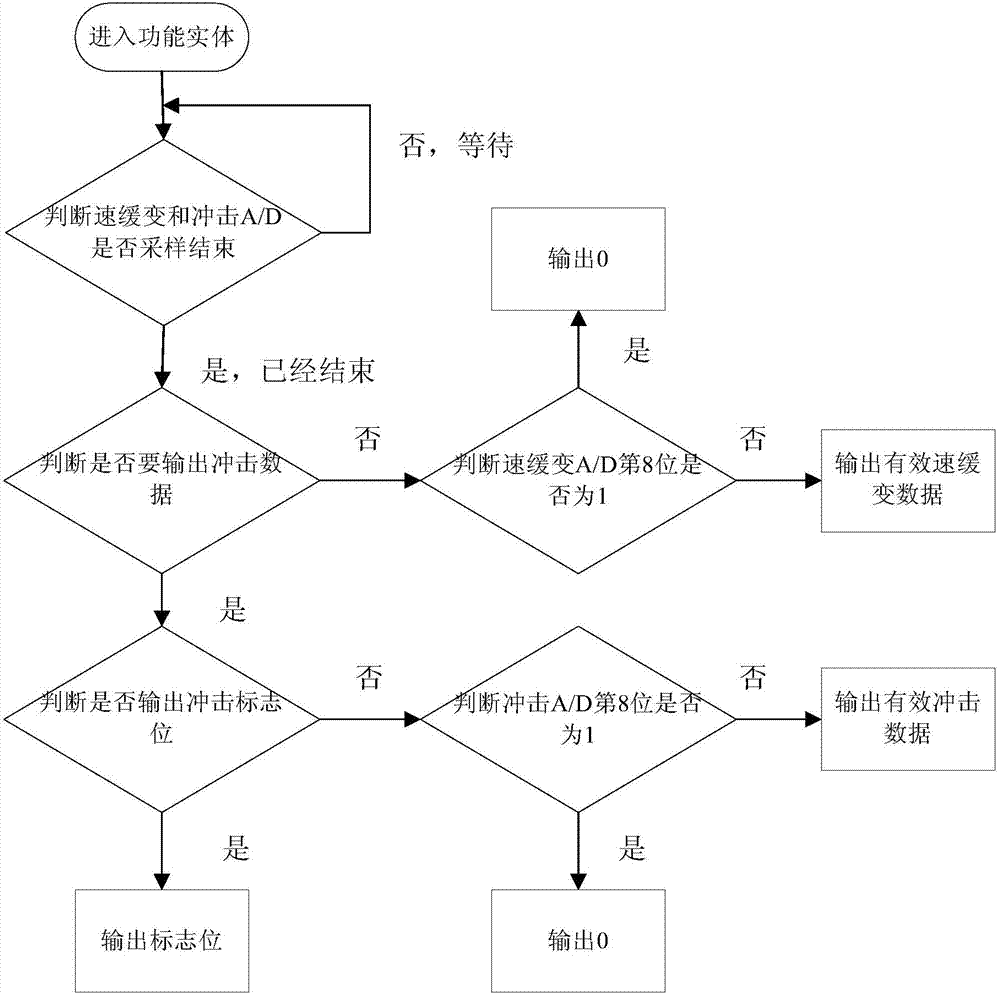

Speed-grading and impact signal flexible collecting method

ActiveCN104121828AReduce complexityReasonable arrangementSelf-propelled projectilesField programmable logic devicesAdaptive design

The invention provides a speed-grading and impact signal flexible collecting method. Multiple channels of programmable-control analog switches are in parallel connection or cascaded connection to achieve the purpose of gating and collecting super-multiple channels of signals. An on-site programmable logic device is utilized to previously set the gating sequence of the multiple channels of signals and the gating ranges of the switches to achieve a flexible data collecting method. Thus, the work efficiency of a remote measuring system is greatly improved. Meanwhile, by means of a flexible design method, a collecting circuit can be designed adaptively according to different requirements. Compared with traditional circuit measurement, the application universality of the speed-grading and impact signal flexible collecting method is improved.

Owner:BEIJING INST OF ASTRONAUTICAL SYST ENG +1

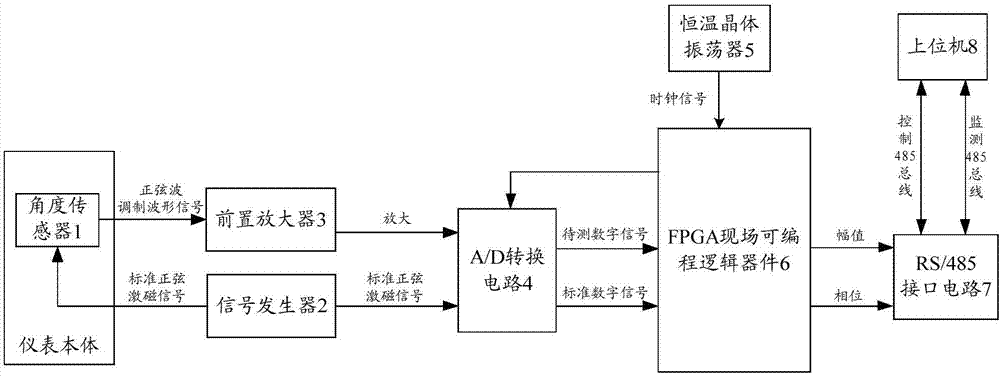

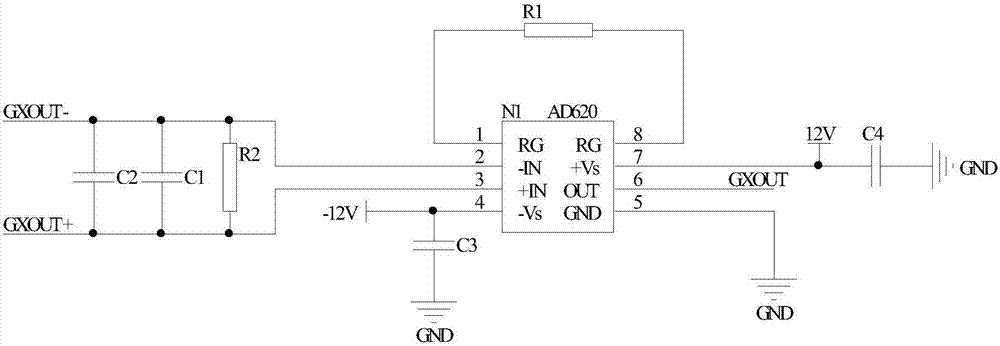

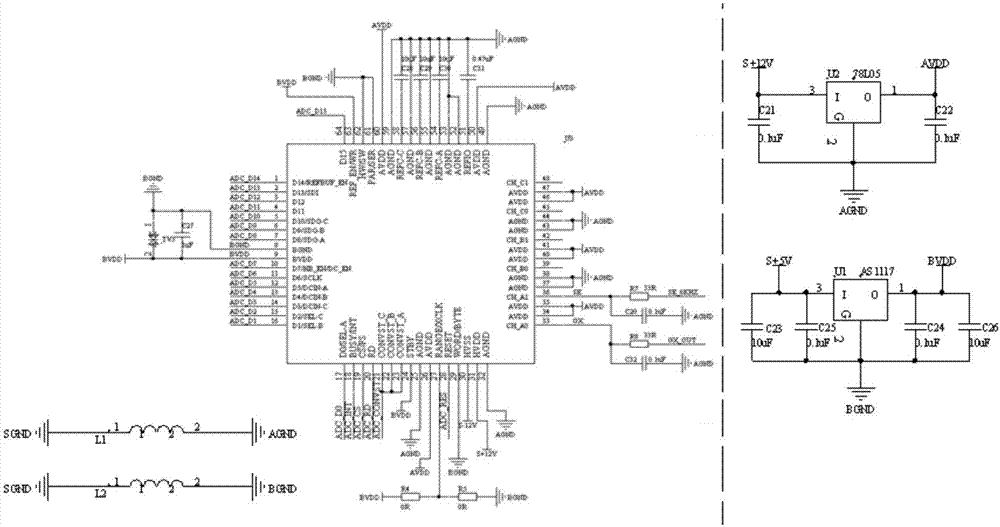

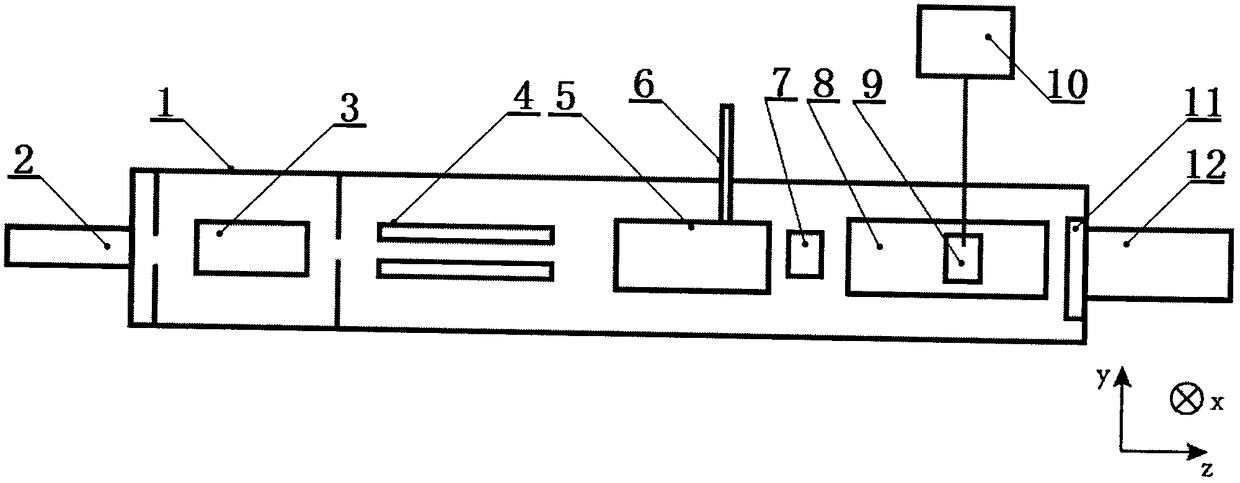

Digital demodulation system for three-floated gyroscopes

ActiveCN107247437AFast digital demodulationEliminate driftProgramme control in sequence/logic controllersField programmable logic devicesPhysics

The invention discloses a digital demodulation system for three-floated gyroscopes, which comprises an angle sensor, a signal generator, a preamplifier, an A / D conversion circuit, a constant-temperature crystal oscillator, an FPGA field programmable logic device, an RS / 485 interface circuit, and a principal computer. The angle sensor is used for loading a collected signal to be measured on a standard sine excitation signal generated by the signal generator to form a sine wave modulation waveform signal. The preamplifier is used for amplifying the signal. The A / D conversion circuit is used for performing analog-to-digital conversion on the signal to get a digital signal to be measured and a standard digital signal. The FPGA field programmable logic device is used for calculating the digital signal to be measured according to the standard digital signal and outputting the calculation result to the principal computer through the RS / 485 interface circuit. Through the system of the invention, fast and high-precision digital demodulation of a to-be-measured signal collected by the angle sensor is realized.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES

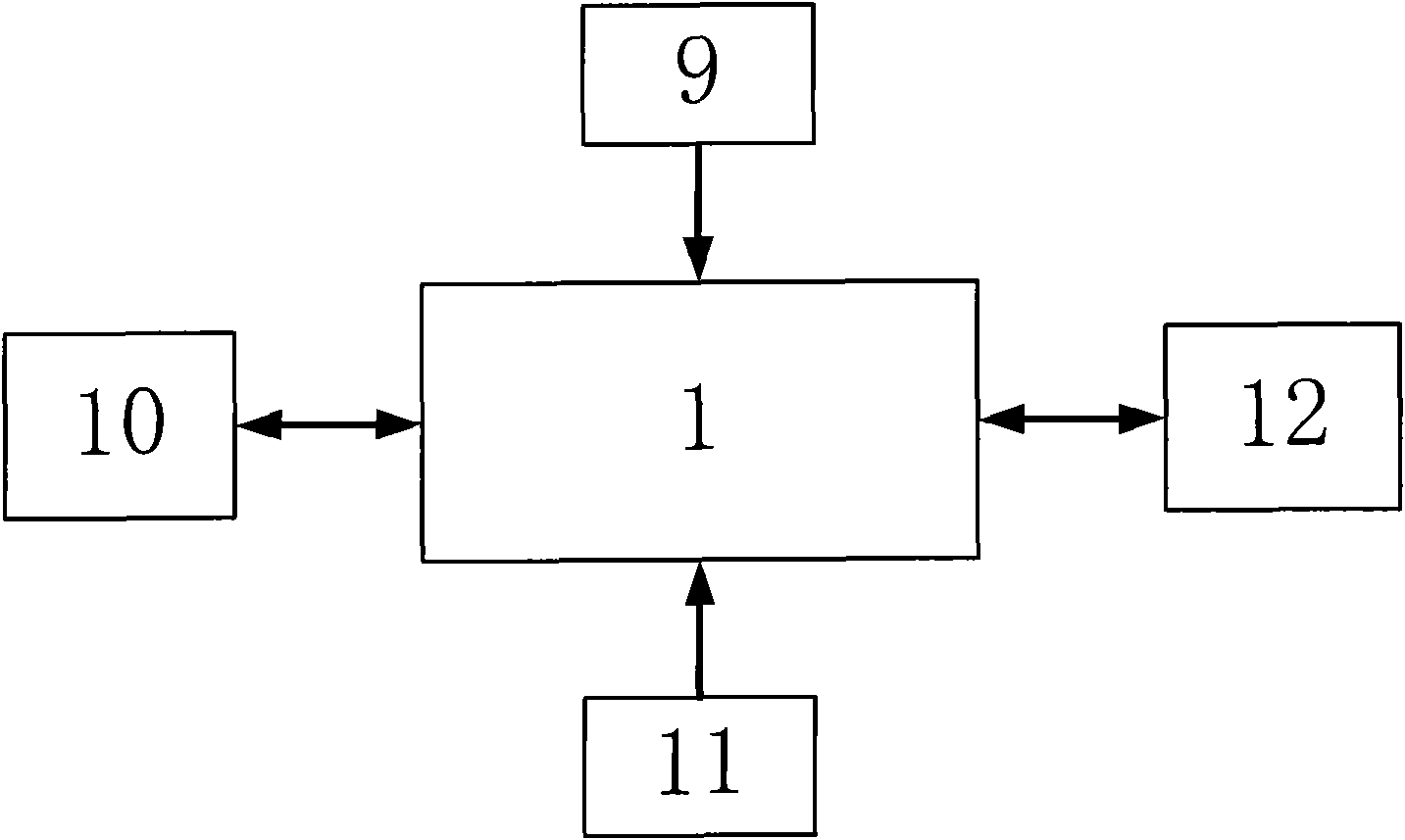

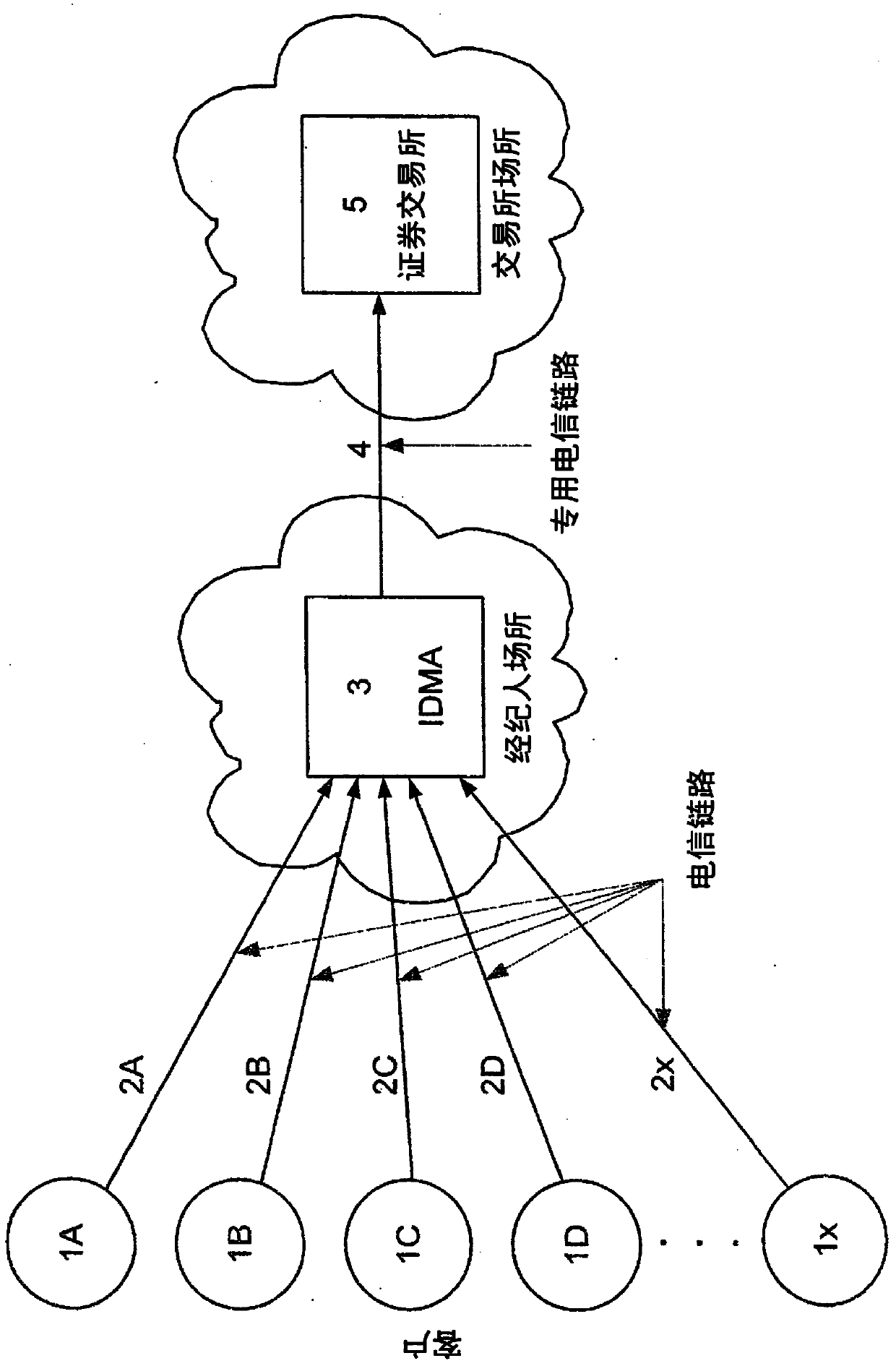

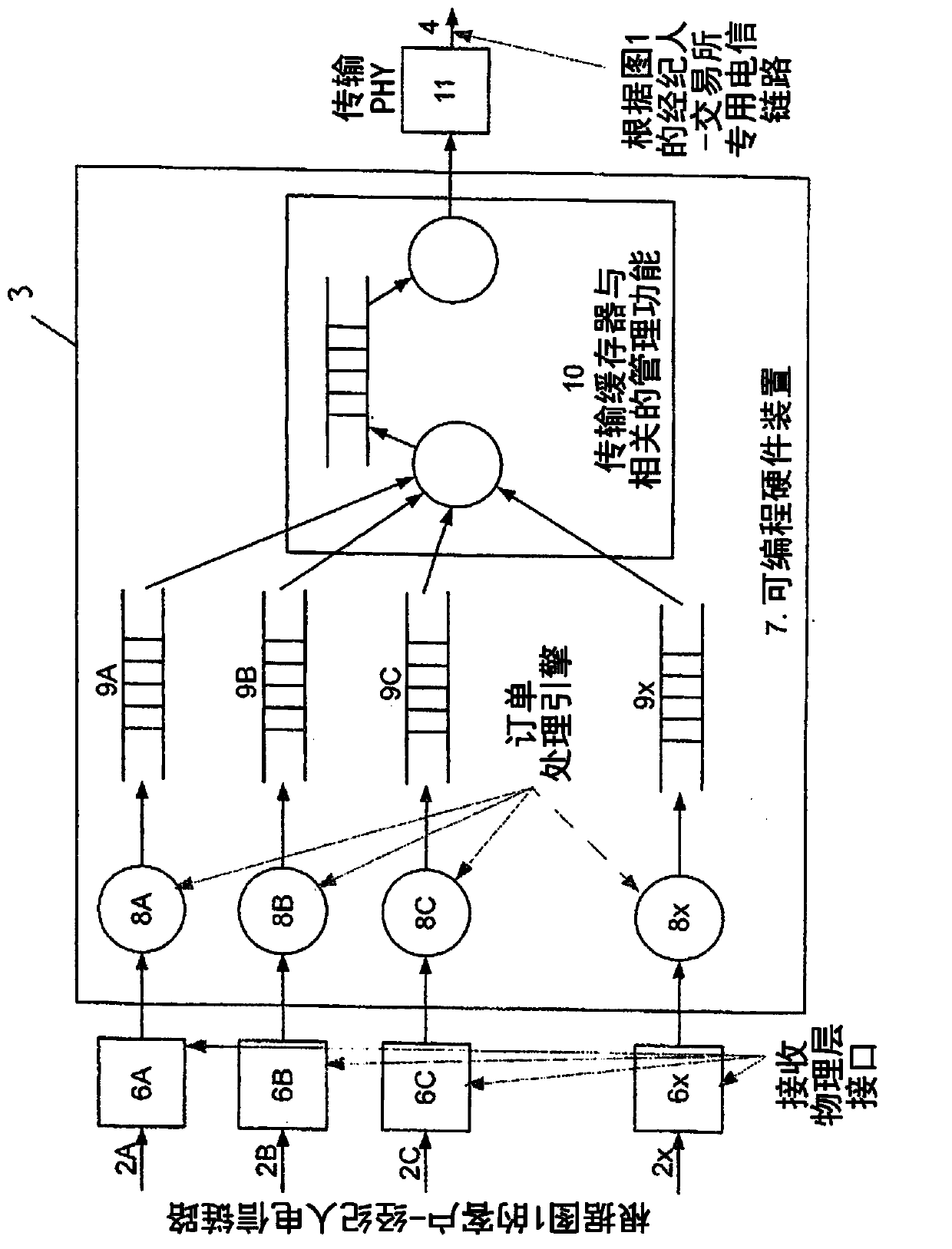

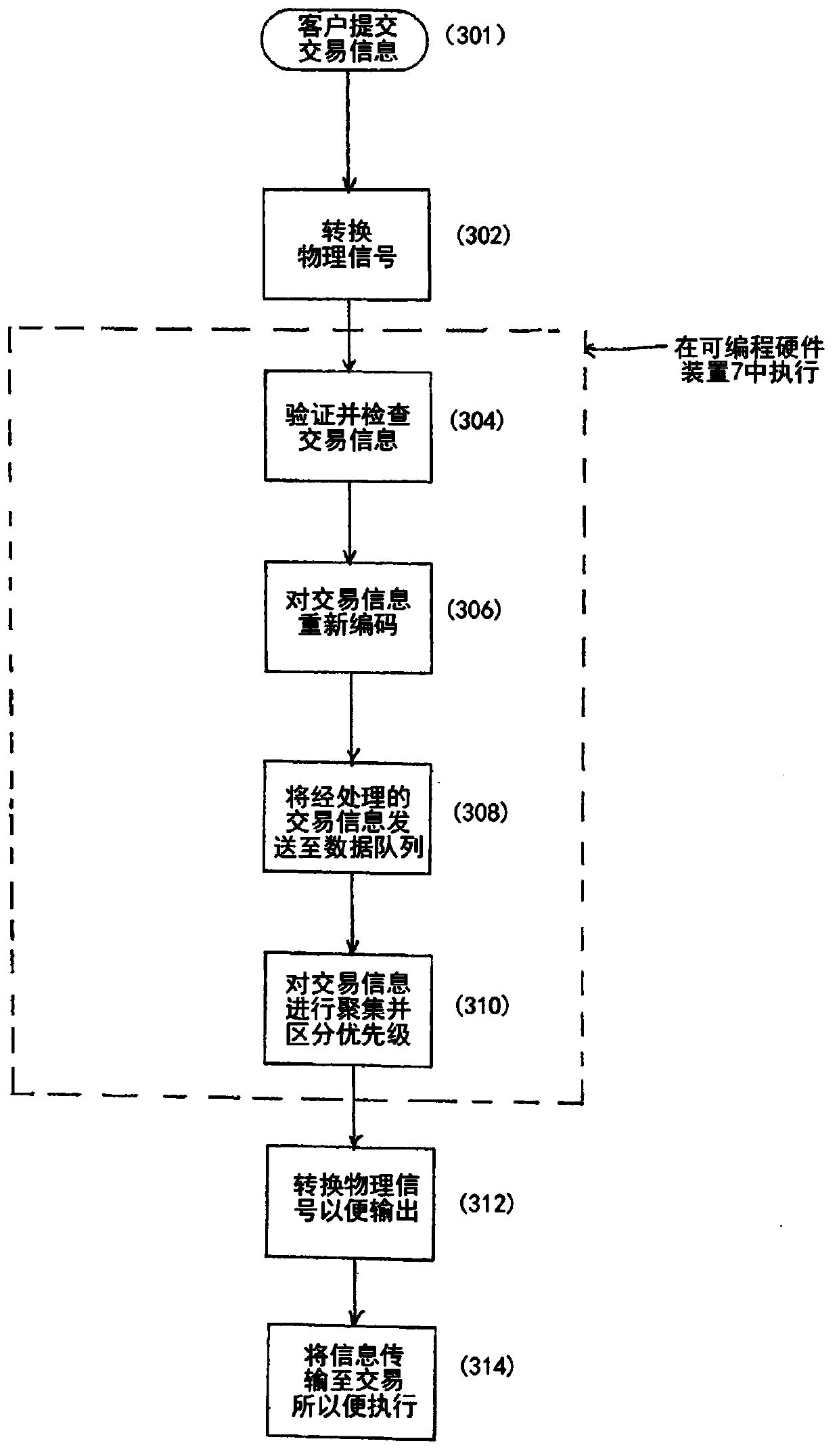

A market access system and method

The present invention relates to a broker's market access system for use in processing orders for transmission to a market exchange. General purpose computing systems, with appropriate operating systems and application software typically implement broker's market access systems. In this invention, the market access system is implemented by dedicated hardware in the form of programmable logic devices, such as field programmable logic devices, for speeding processing of client orders. In an embodiment, the dedicated hardware comprises an architecture including order processing engines arranged to parallel process multiple client orders.

Owner:ZOMOJO

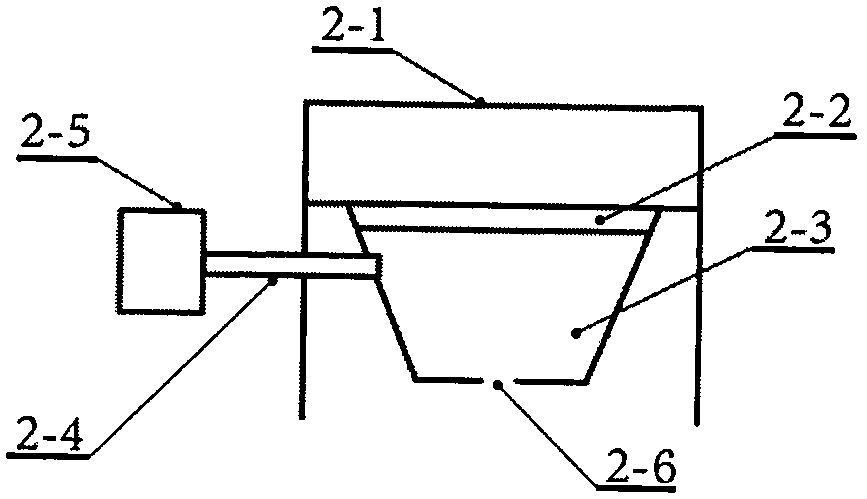

Device for studying macromolecular ion photoelectron spectrum

PendingCN108801922ARich varietyAnalysis by thermal excitationField programmable logic devicesMass ratio

The invention relates to the field of spectrochemistry, and relates to a device for studying a macromolecular ion photoelectron spectrum. The device comprises a vacuum cavity, a droplet ejector, an ion buncher, a quadrupole mass filter, an ion trap, an air inlet, an exit lens, a shield cover, a speed imaging disk, a laser, a multi-channel disk, a detector, a computer, an input / output module, fieldprogrammable logic device, a digital-to-analog conversion module, a high-voltage power supply, a drive circuit and a vacuum pump set. A method of resonance of a drive unit and liquid is utilized to eject droplets; a vibration direction of the drive unit is parallel to a droplet ejecting direction, so that the device can form uniform droplets with relatively small size, has no special requirementfor a solvent, does not need to apply a high voltage to the solution during ejection, is applicable to a wider range of macromolecular species, utilizes a digital trapezoidal waveform voltage to drivethe quadrupole mass filter, obtains a charge-to-mass ratio spectrum by scanning the frequency, can measure particles with a relatively large charge-to-mass ratio, can minimize harmonics in the voltage, and obtains a relatively high signal resolution.

Owner:JINHUA VOCATIONAL TECH COLLEGE

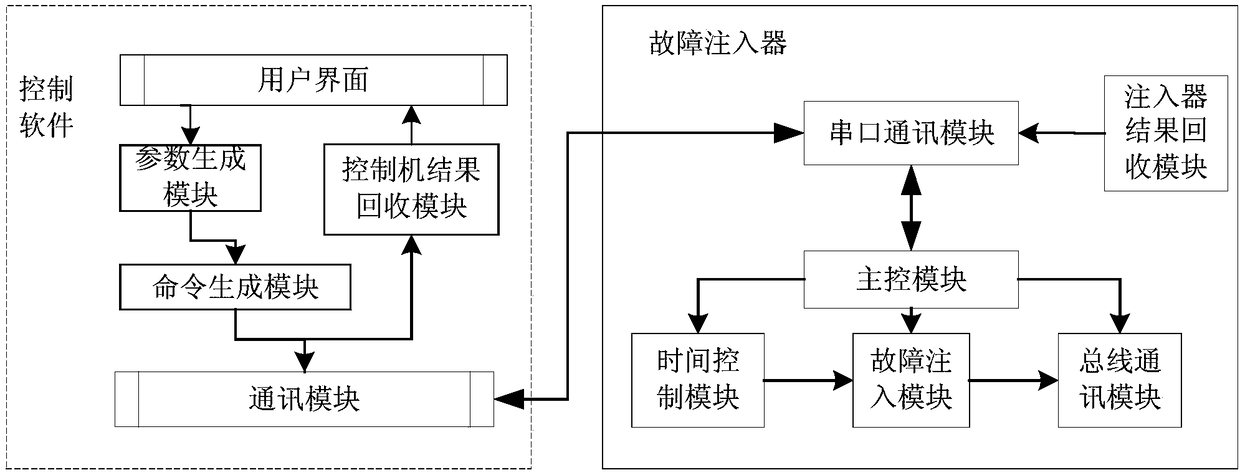

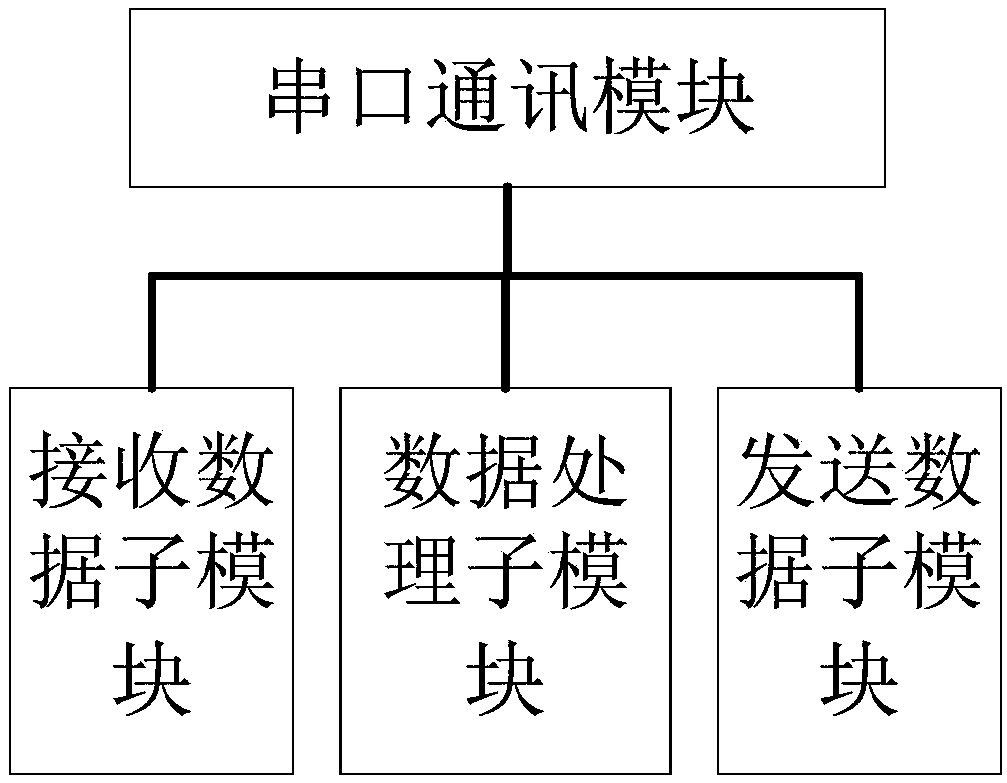

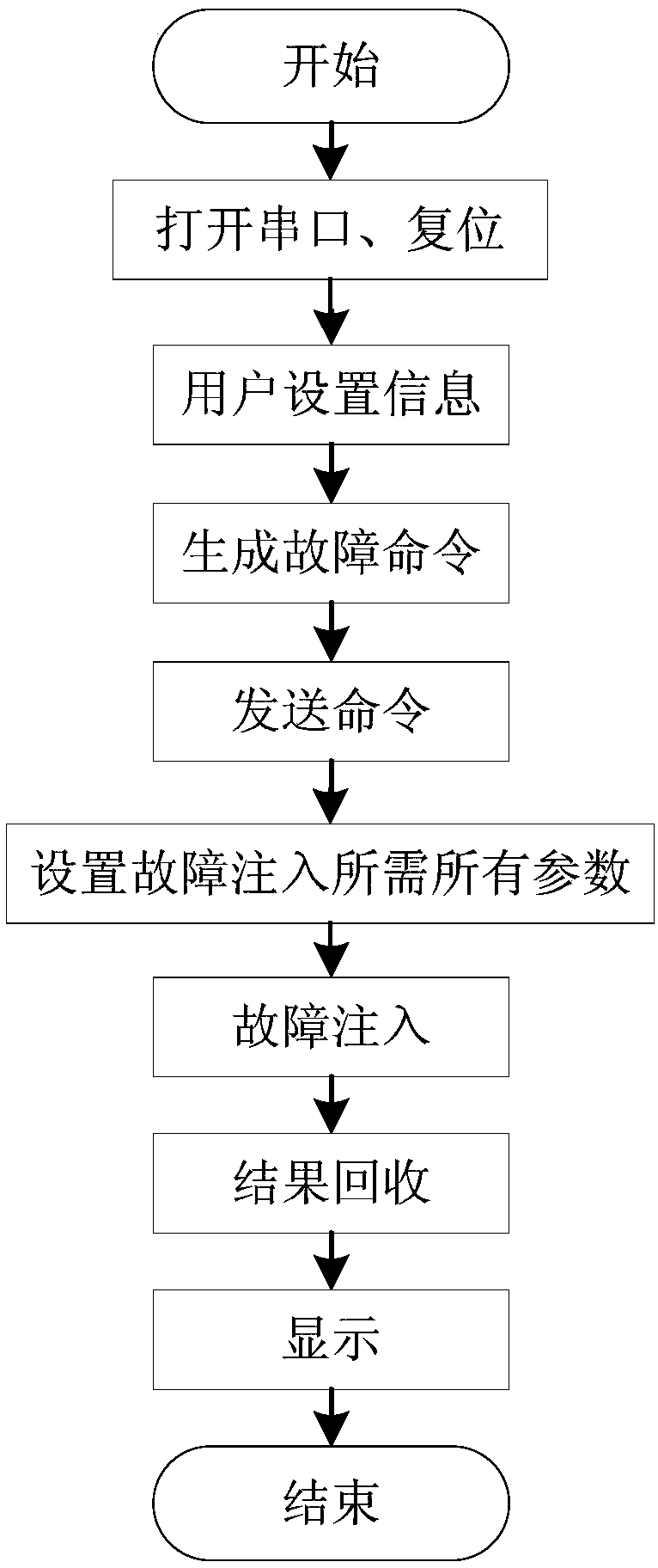

Fault simulation system and method for serial bus

ActiveCN108958997APromote generationVerify reliabilityFunctional testingFaulty hardware testing methodsInjection resultField programmable logic devices

The invention provides a fault simulation system and method for a serial bus, and belongs to the technical field of computer reliability evaluation. The fault simulation system for the serial bus in the invention comprises a control machine and a fault injector; the control machine generates a fault command according to user requirements, sends the fault command to the fault injector, receives aninjection result and a target system state fed back by the fault injector, and feeds back the injection result and the target system state to a user; and the fault injector sets all parameters required by fault injection according to the fault command from the control machine by adoption of a field programmable logic device FPGA, injects a fault into data after receiving the data from the serial bus, sends the modified data to the serial bus, and returns the obtained injection result and the target system state to the control machine. By means of the fault simulation system and method for theserial bus in the invention, the problem that the real-time property is low when the existing bus fault injection is used for verifying the reliability of a computer can be solved; and the fault simulation system and method for the serial bus in the invention can be used for bus fault simulation.

Owner:HARBIN INST OF TECH

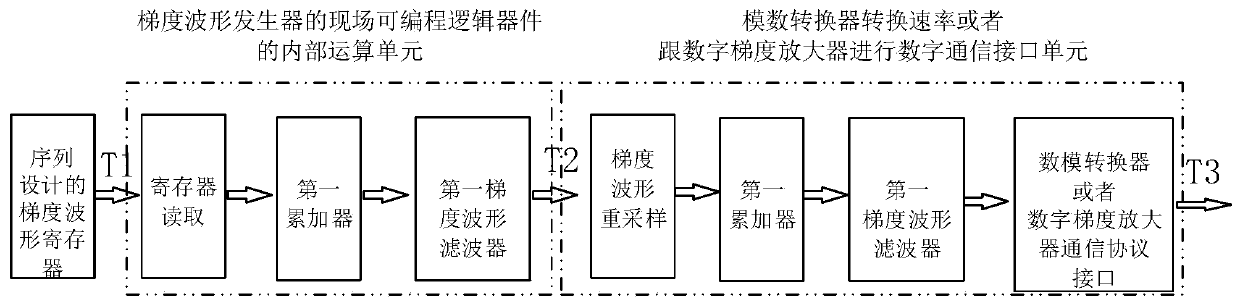

Gradient waveform rate automatic adaptive output method and magnetic resonance system

ActiveCN111521963AConsistent gradient area accuracyMeasurements using NMR imaging systemsField programmable logic devicesEngineering

The invention discloses a gradient waveform rate automatic adaptive output method and a magnetic resonance system, and are applied to the technical field of computers, the problem that the gradient waveform signal rate of magnetic resonance sequence design in the prior art cannot be flexibly configured according to magnetic resonance application is solved. According to the invention, a nuclear magnetic resonance sequence design gradient waveform rate is matched into an analog-to-digital converter conversion rate of a gradient waveform signal generator or a uniaxial gradient waveform signal data transmission rate of a digital communication interface with a digital gradient amplifier; the gradient waveform rate is designed according to the nuclear magnetic resonance sequence; the technical effects that the method is not restrained by the internal operation rate of a field programmable logic device of the gradient waveform signal generator, and meanwhile the conversion rate of an analog-to-digital converter of the gradient waveform signal generator or the uniaxial gradient waveform signal data transmission rate of a digital communication interface with a digital gradient amplifier cannot be restrained are achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

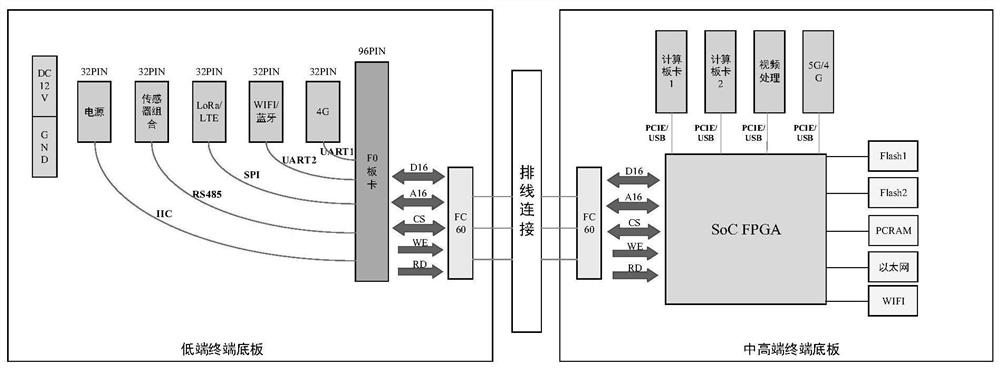

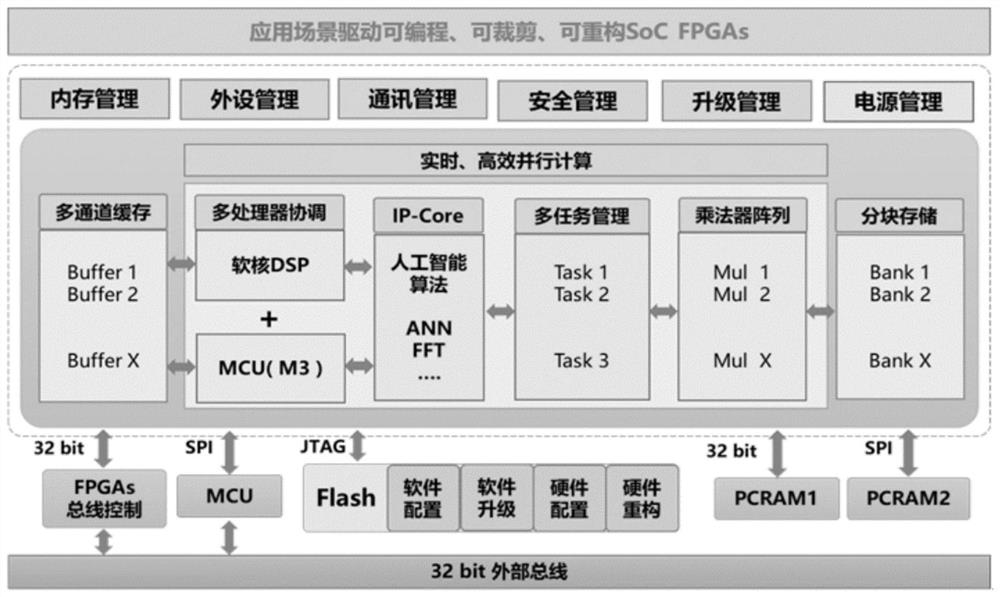

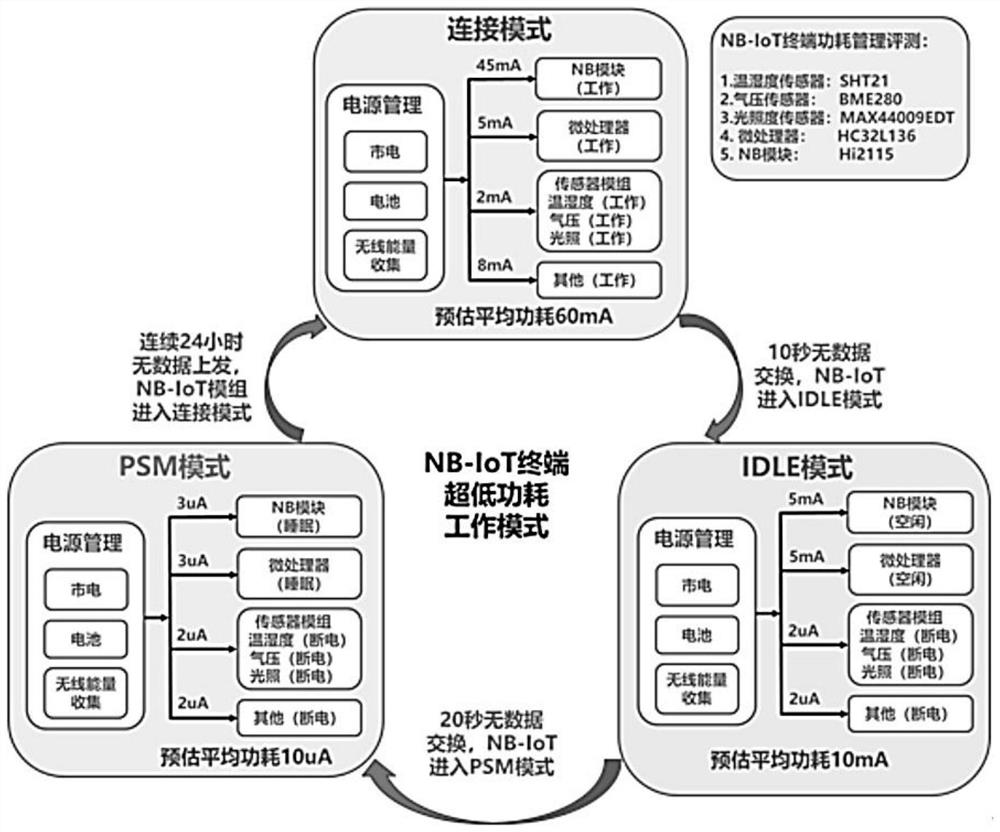

Platformized intelligent terminal system and implementation method thereof

ActiveCN112003909AWith perceptionWith operationTransmissionInformation processingComputer architecture

The invention discloses a platformized intelligent terminal system and an implementation method thereof. The platformized intelligent terminal system comprises open source instruction set architecturebased on a reduced instruction set (RISC-V) principle and a mainboard with a micro control unit (MCU), a field programmable logic device (Soc FPGA) of a system on chip, a high-speed computing board card, a sensor combination, a wireless communication module, a wired communication module and a power supply module, wherein the medium-low speed wired communication module, the wireless communicationmodule and the sensor combination are respectively connected with the mainboard and the SoC FPGA, the SoC FPGA is connected with the mainboard through a flat cable, and the SoC FPGA is connected withthe computing board card through PCIE. According to the platformized intelligent terminal system and the implementation method thereof, the platformized multi-type intelligent terminal system which isreconfigurable and programmable in software and hardware and autonomously adapts to multiple application scenes is constructed, so that the information processing capability of the terminal is improved; and the MCU+FPGA+PCRAM architecture is adopted, an electric energy management technology for low-power-consumption operation of the intelligent terminal is provided, and efficient data processingand low-power-consumption operation are integrated.

Owner:SHANGHAI JIAO TONG UNIV

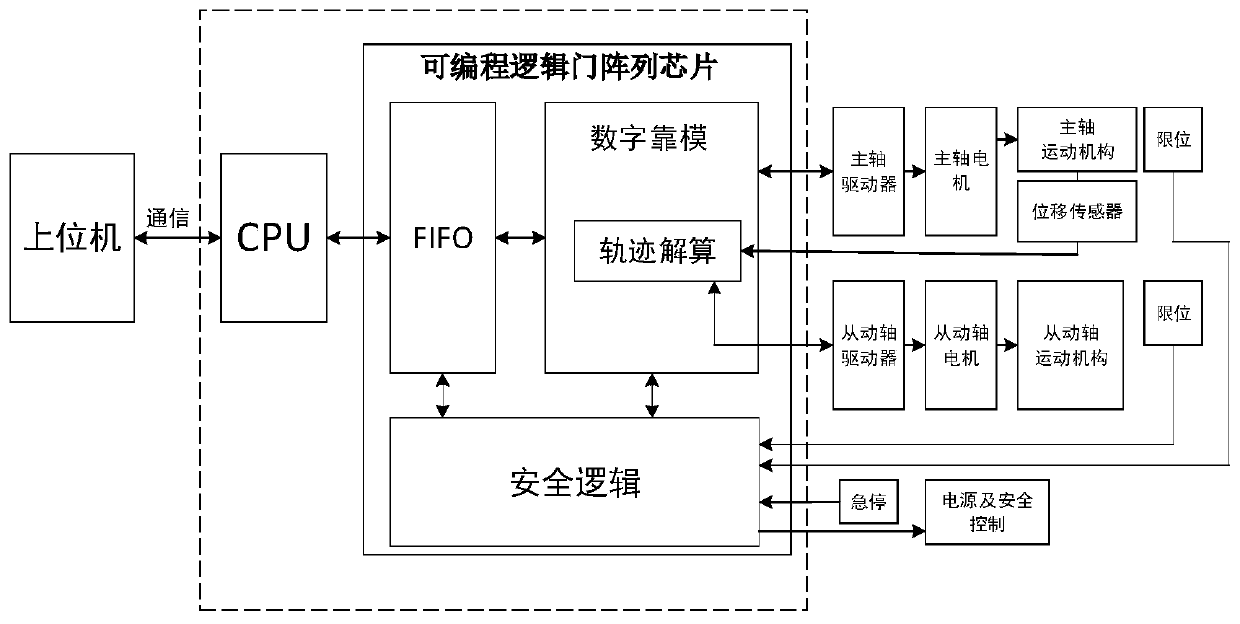

Digital profiling control system and method based on programmable logic device

InactiveCN110579997AImprove stabilityImprove reliabilityProgramme control in sequence/logic controllersField programmable logic devicesControl system

The invention discloses a digital profiling control system and method based on a programmable logic device. The system comprises an FIFO unit, a digital profiling unit and a safety logic unit which are achieved based on the programmable logic device. Both the digital profiling unit and the safety logic unit are in communication connection with an external host through the FIFO unit, and the safetylogic unit is in communication connection with the digital profiling unit; the digital profiling unit is used for completing control output and state information reading of a main shaft and a drivenshaft to realize linkage control over the main shaft and the driven shaft; and the safety logic unit is used for collecting and processing information related to machine tool safety, to realize safetycontrol. Linkage control over the main shaft and the driven shaft is achieved through the field programmable logic device in a hardware control mode, safety signals such as limiting signals and emergency stop signals of the main shaft and the driven shaft are collected and processed, control over emergency stop, power failure and the like is achieved, and the profiling stability and reliability are improved.

Owner:MIANYANG WEIBO ELECTRONICS

Intelligent electromechanical motion controller combined on single board

InactiveCN106707827AImprove reliabilityImprove performanceProgramme controlComputer controlDigital signal processingField programmable logic devices

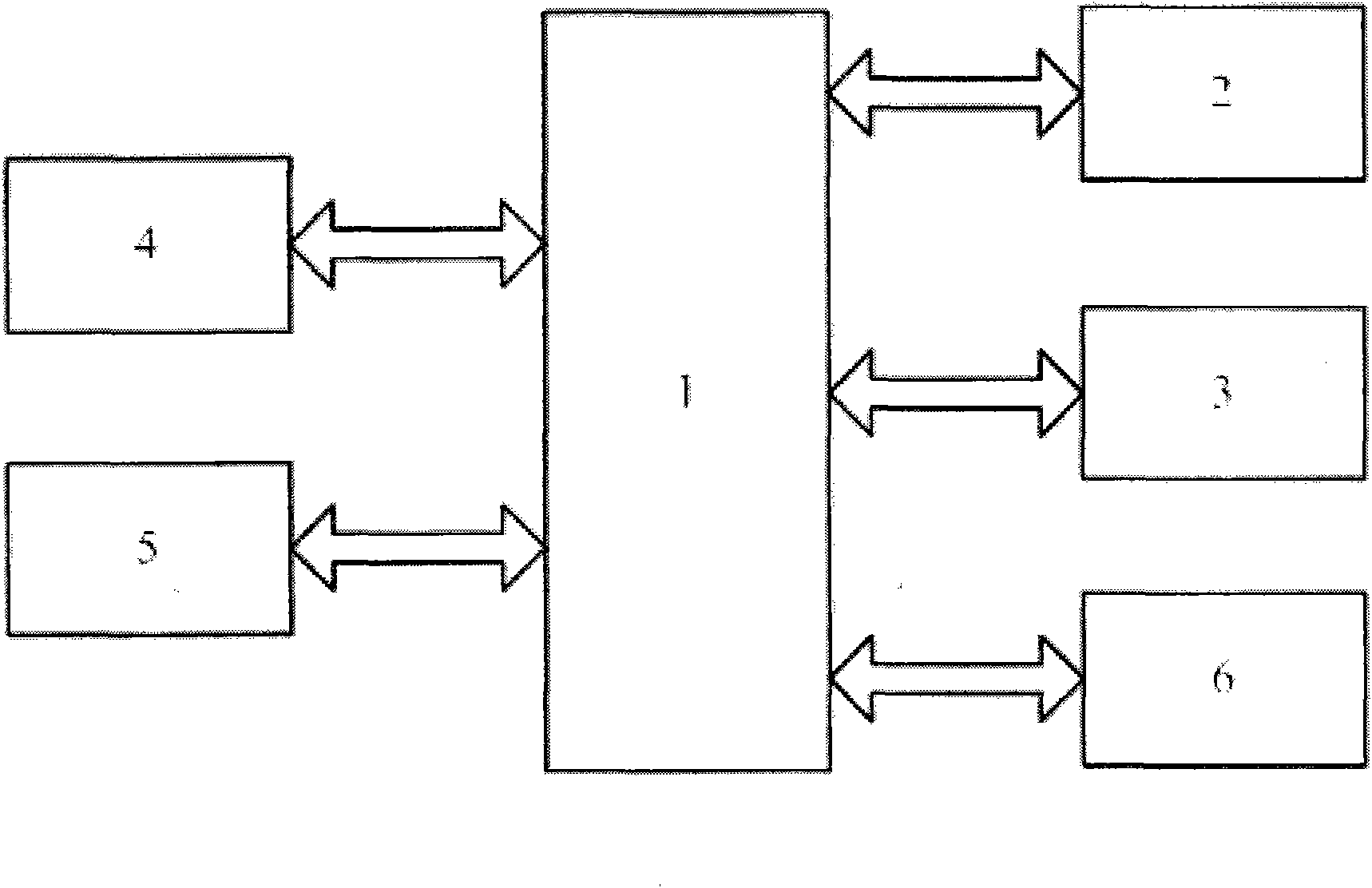

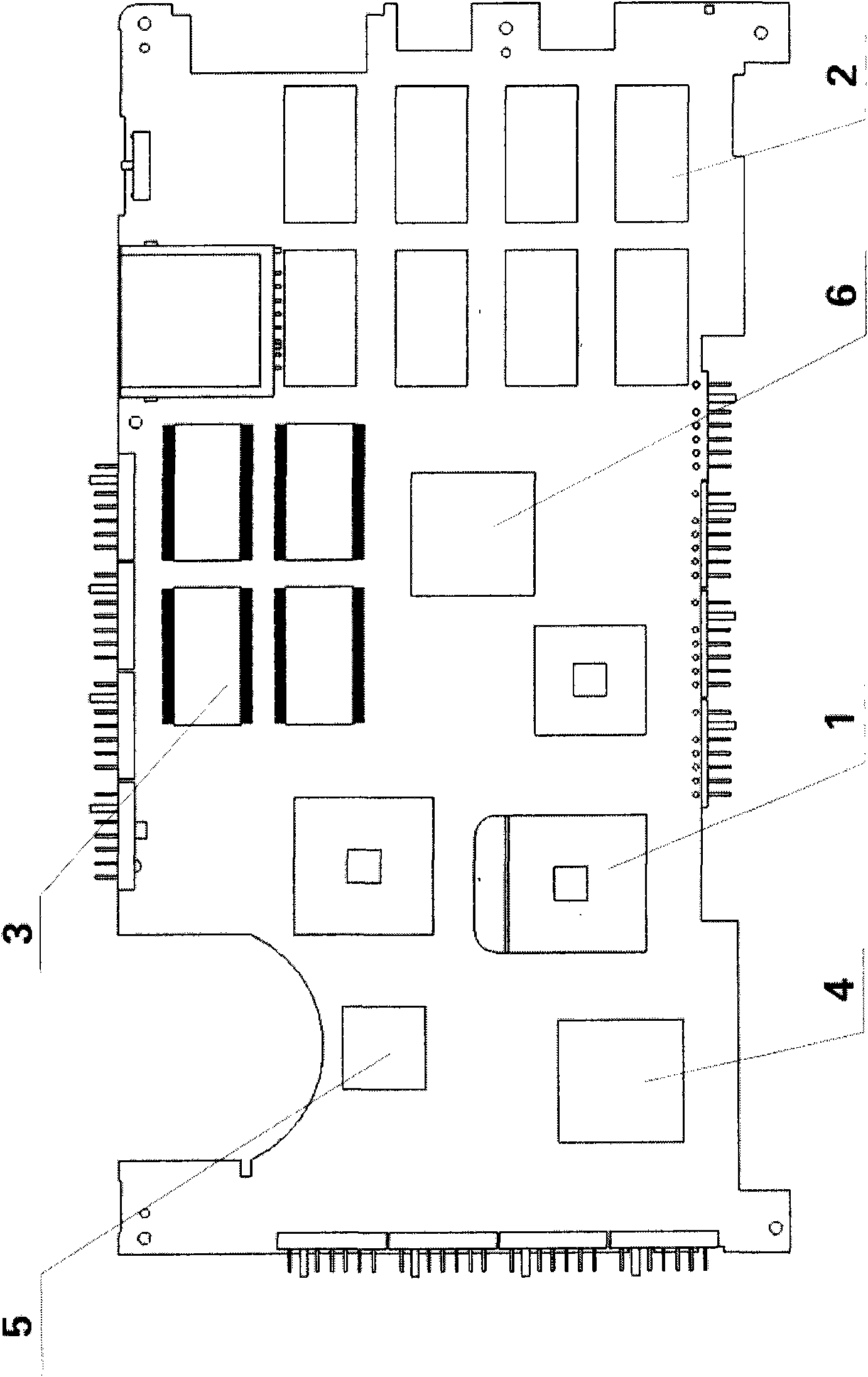

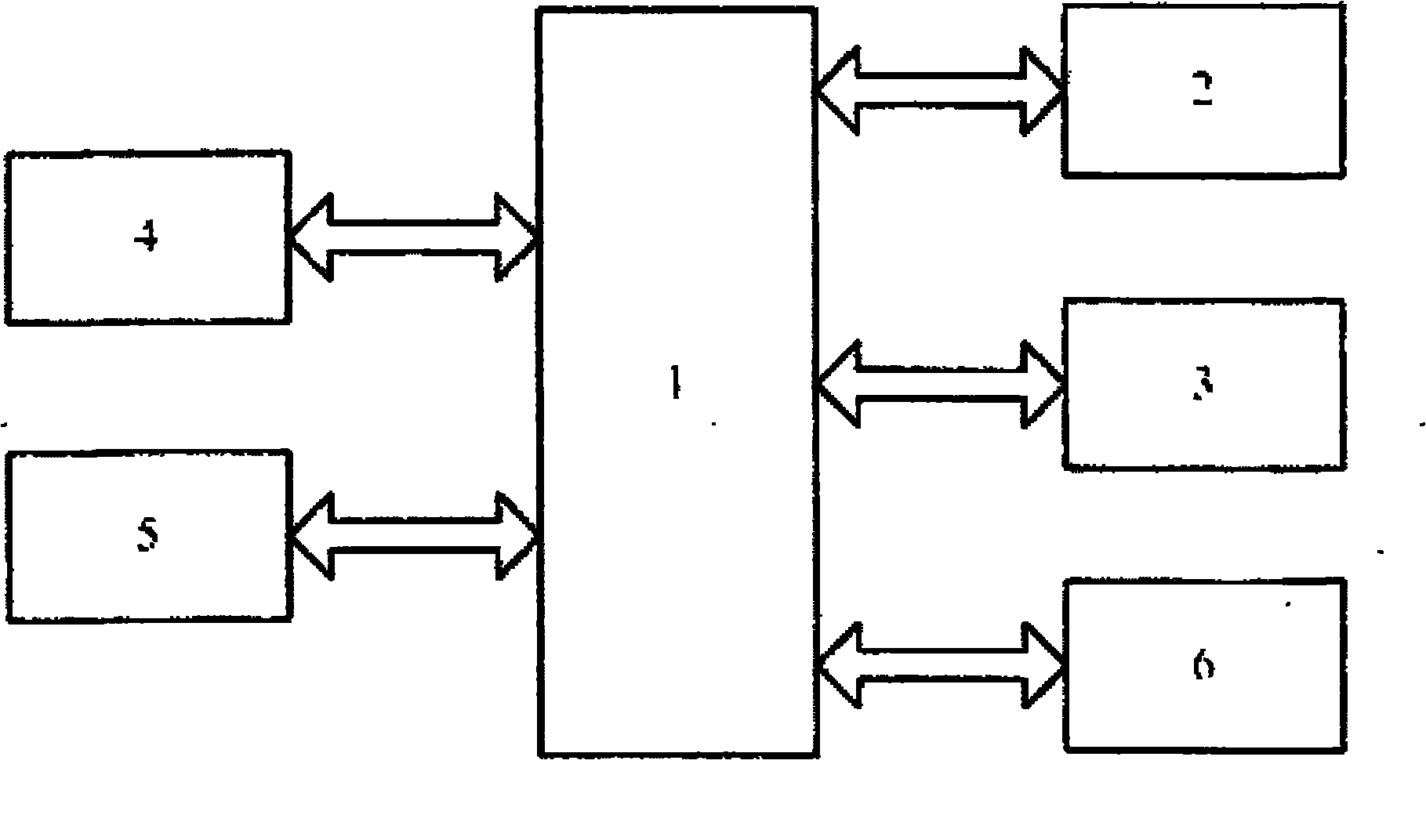

The invention discloses an intelligent electromechanical motion controller combined on a single board, and belongs to the technical field of electromechanical motion controllers. The intelligent electrochemical motion controller comprises an X86 central processing unit serving as a main CPU, a memory, a solid-state electronic disk, a digital signal processor (DSP), a field programmable logic device FPGA, a real-time Ethernet controller and the like; the components are all welded and connected on a single circuit board and integrally combined or integrated with the single board to form the intelligent electrochemical motion controller; the high-performance universal X86 processor is used as a core and matched with advanced hardware or software integration; various hardware which needs to be combined on the single board is arranged on the circuit board by welding; and the intelligent single-board machine has the advantages of high overall reliability, abundant software and hardware resources, convenient information integration, high degree of standardization, high intelligent performance and good application and popularization prospect so as to be worthy of being applied and popularized in the electromechanical industry.

Owner:重庆德秋建设工程有限公司

Intelligent electromechanical motion controller combined on single board

InactiveCN101819428AImprove reliabilityImprove performanceNumerical controlDigital signal processingField programmable logic devices

The invention discloses an intelligent electrochemical motion controller combined on a single board, and belongs to the technical field of the electromechanical motion controller. The intelligent electrochemical motion controller comprises an X86 central processing unit serving as a main CPU, a memory, a solid-state electronic disk, a digital signal processor (DSP), a field programmable logic device FPGA, a real-time Ethernet controller and the like; the components are all welded and connected on a monolithic circuit board and integrally combined or integrated with the single board to form the intelligent electrochemical motion controller; the high-performance universal X86 processor is used as a core and matched with advanced hardware or software integration; various hardware which needs to be combined on the single board is arranged on a circuit board by welding; and the intelligent single-board machine has the advantages of high overall reliability, abundant software and hardware resources, convenient information integration, high degree of standardization, high intelligent performance and good application and popularization prospect so as to be worthy of being applied and popularized by the electromechanical industry.

Owner:ACCUPOWER ELECTRONIC TECH CO LTD OF TAIYUAN