Prototype verification device for programmable logic devices

A programming logic and prototype verification technology, applied in the field of programmable logic device prototype verification devices, can solve the problems of waste of resources, difficult to expand, and low reuse rate, and achieve the effect of saving costs and reducing the risk of verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

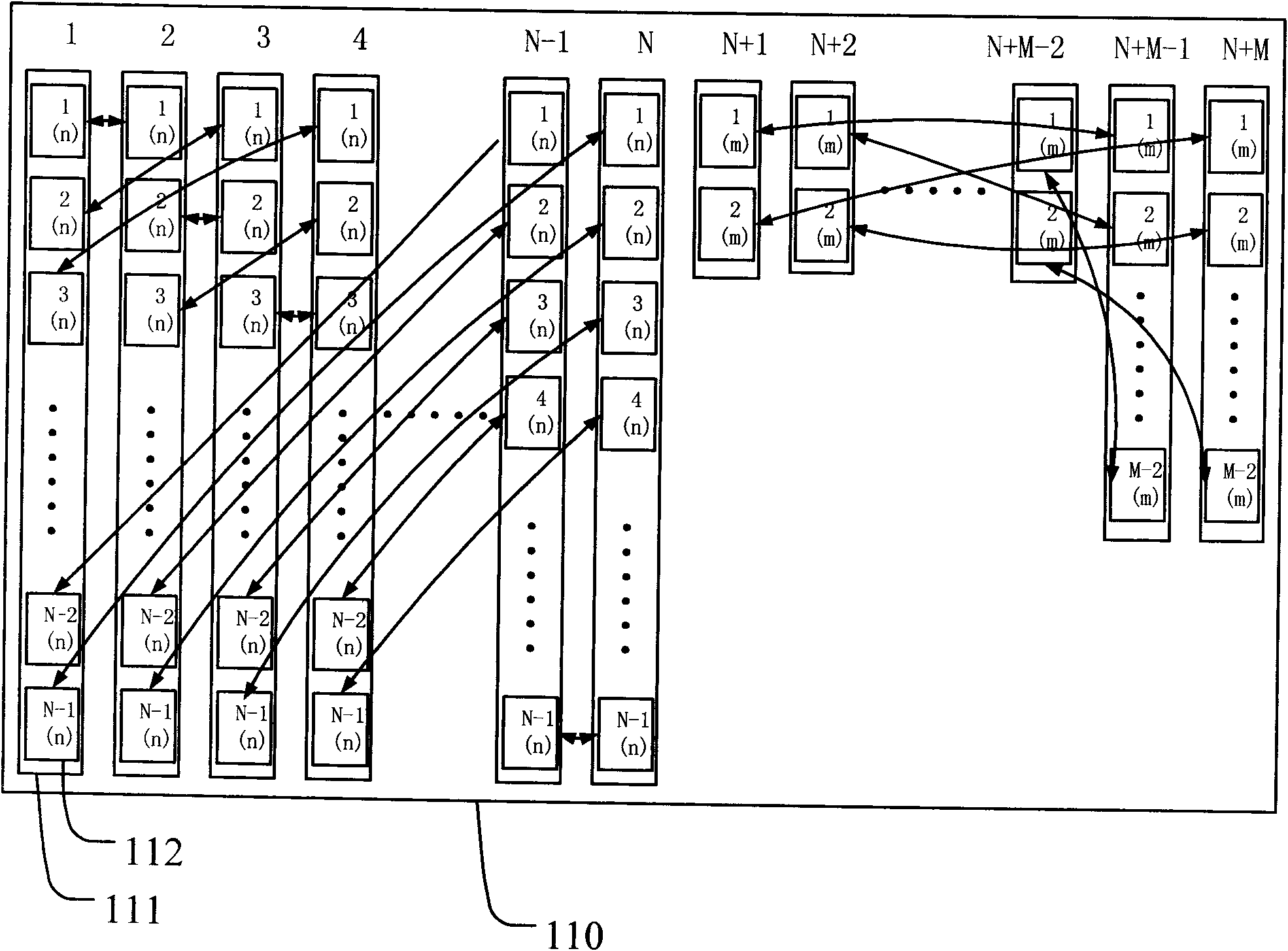

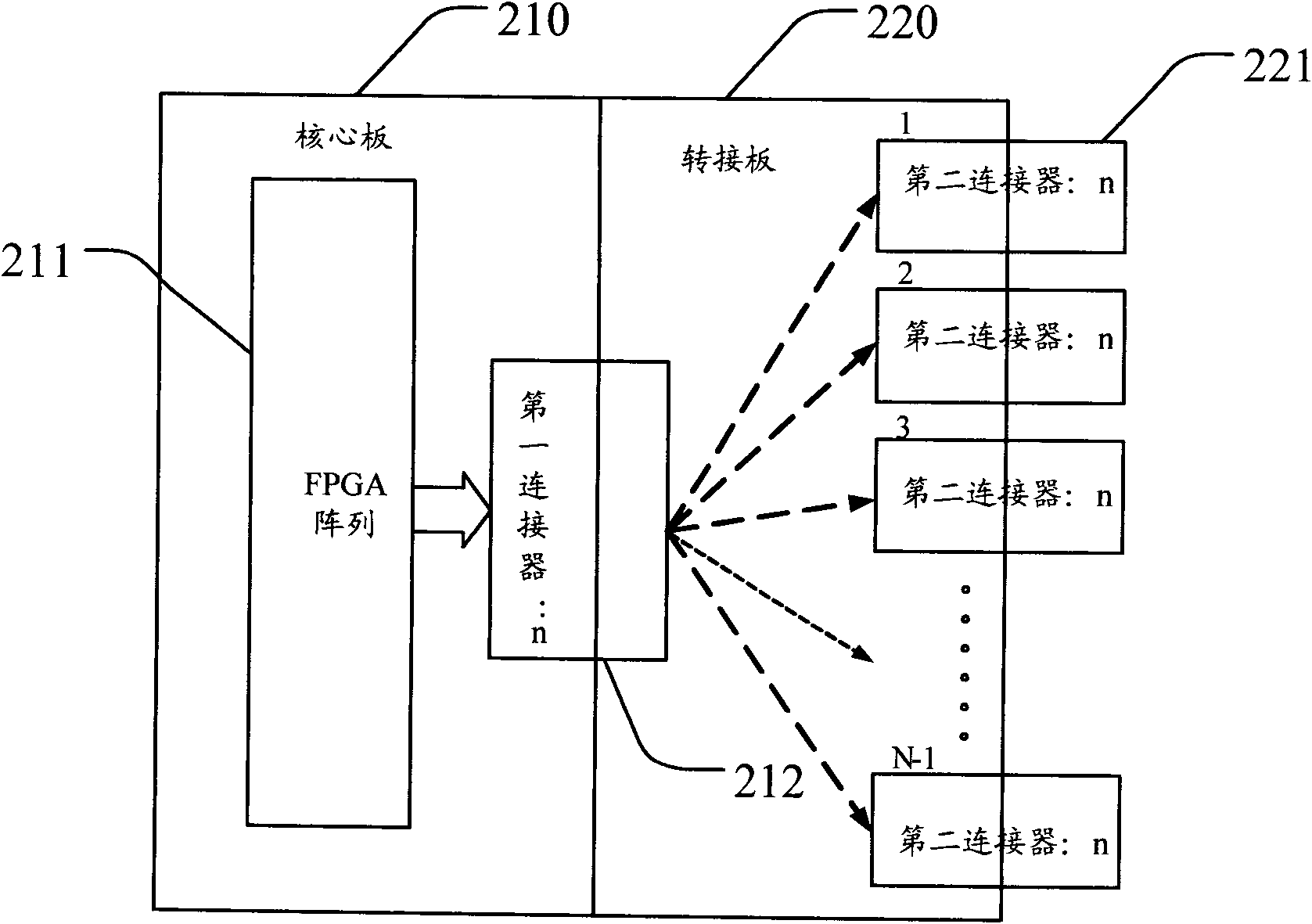

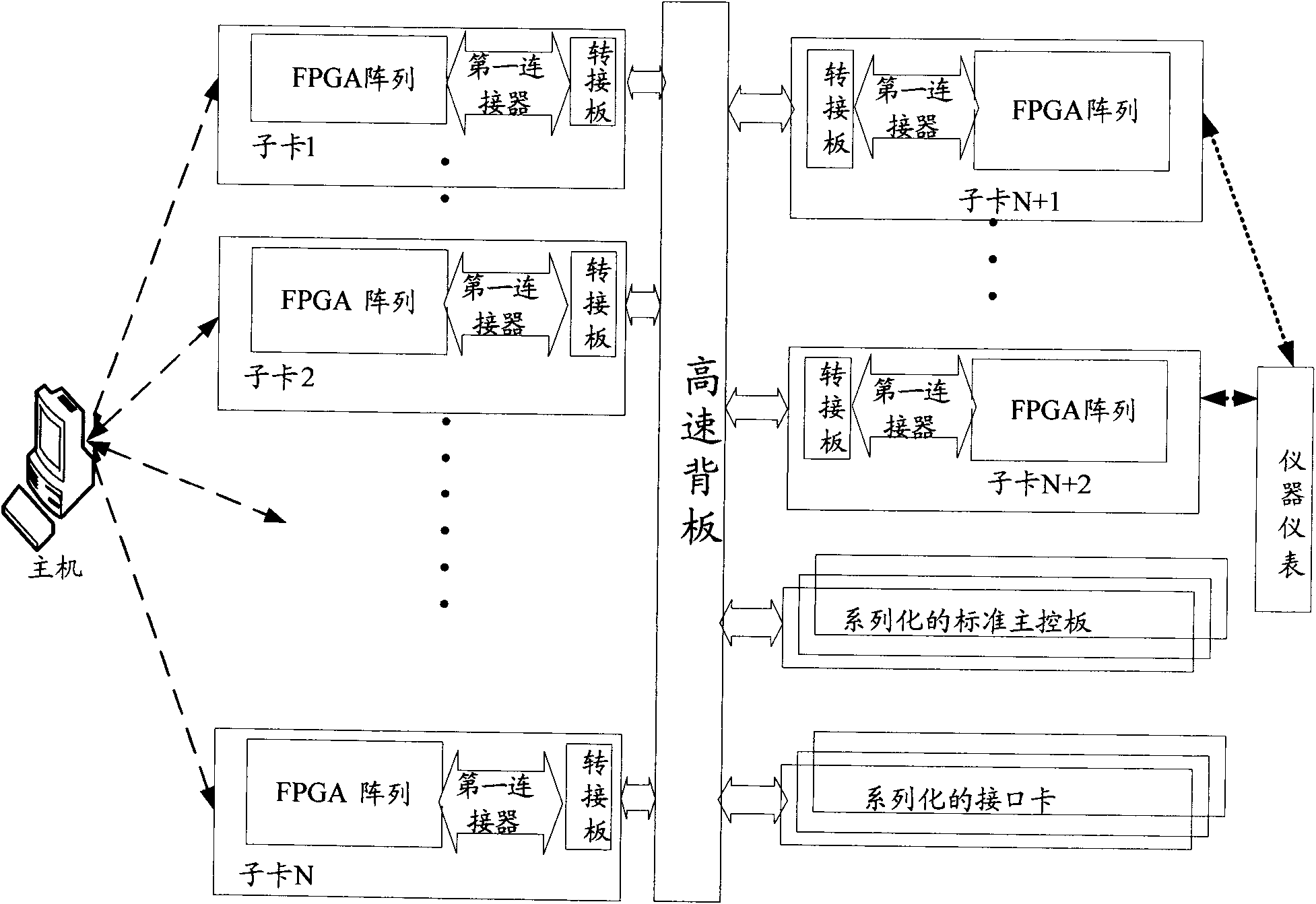

[0024] An embodiment of the present invention provides a programmable logic device prototype verification device, such as image 3 As shown, the device includes a backplane (a high-speed backplane in this embodiment), at least two card slots 111 arranged and connected to the backplane, and a daughter card inserted into the card slots 111, image 3 Among them are N+2 sub-cards, the sub-card 1, sub-card 2...sub-card N, etc. are connected to each other through the high-speed backplane, wherein: sub-card 1...sub-card N signal Connect to the host, subcard N+1, and subcard N+2 are connected to instru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More