Patents

Literature

76 results about "FPGA prototype" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Field-programmable gate array prototyping (FPGA prototyping), also referred to as FPGA-based prototyping, ASIC prototyping or system-on-chip (SoC) prototyping, is the method to prototype system-on-chip and application-specific integrated circuit designs on FPGAs for hardware verification and early software development.

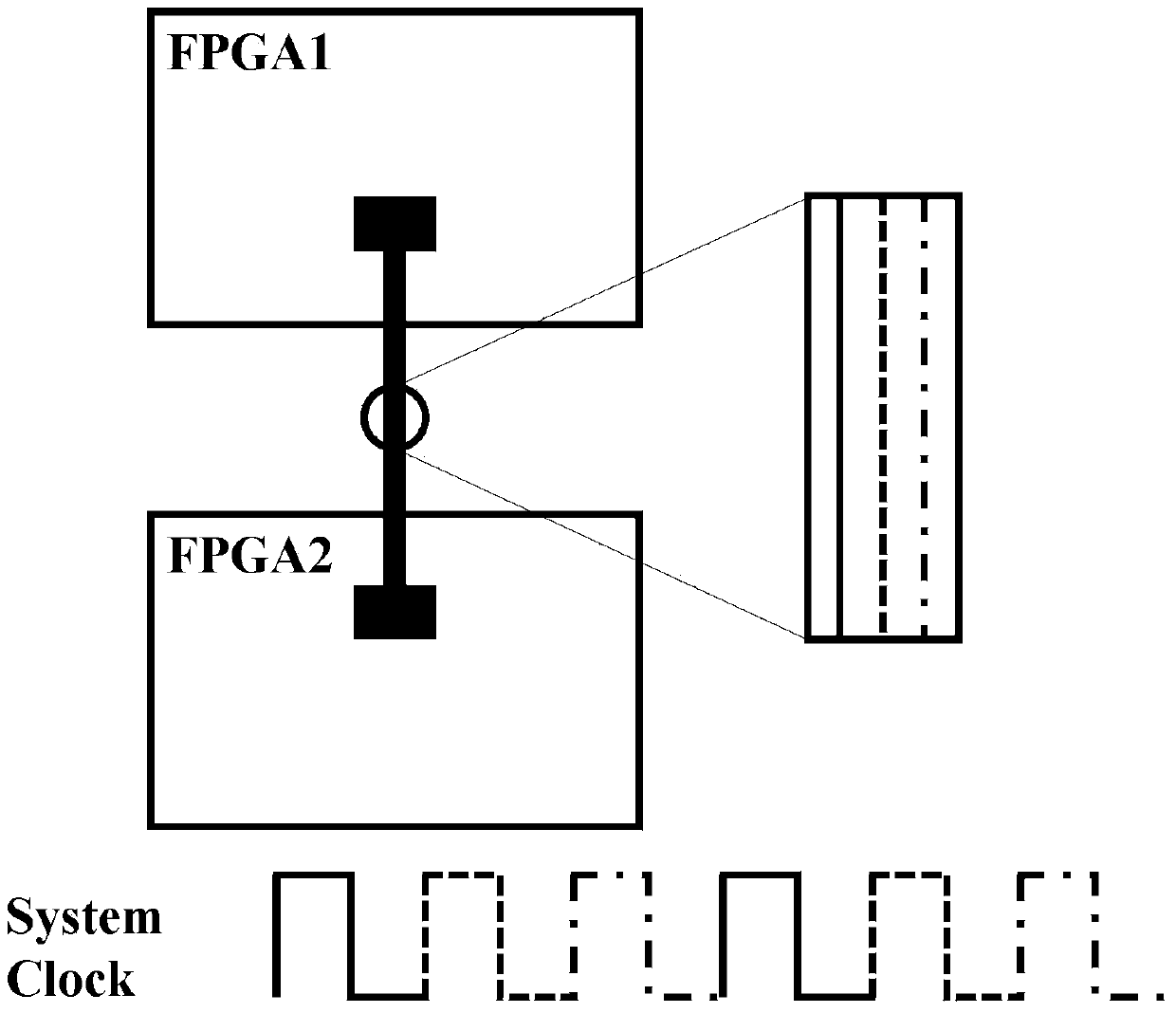

Clock synchronous device and system for Field Programmable Gate Array (FPGA) prototype test plate piling

ActiveCN103105889ASimple designImprove clock synchronization efficiencyFunctional testingGenerating/distributing signalsTime delaysMultiplexer

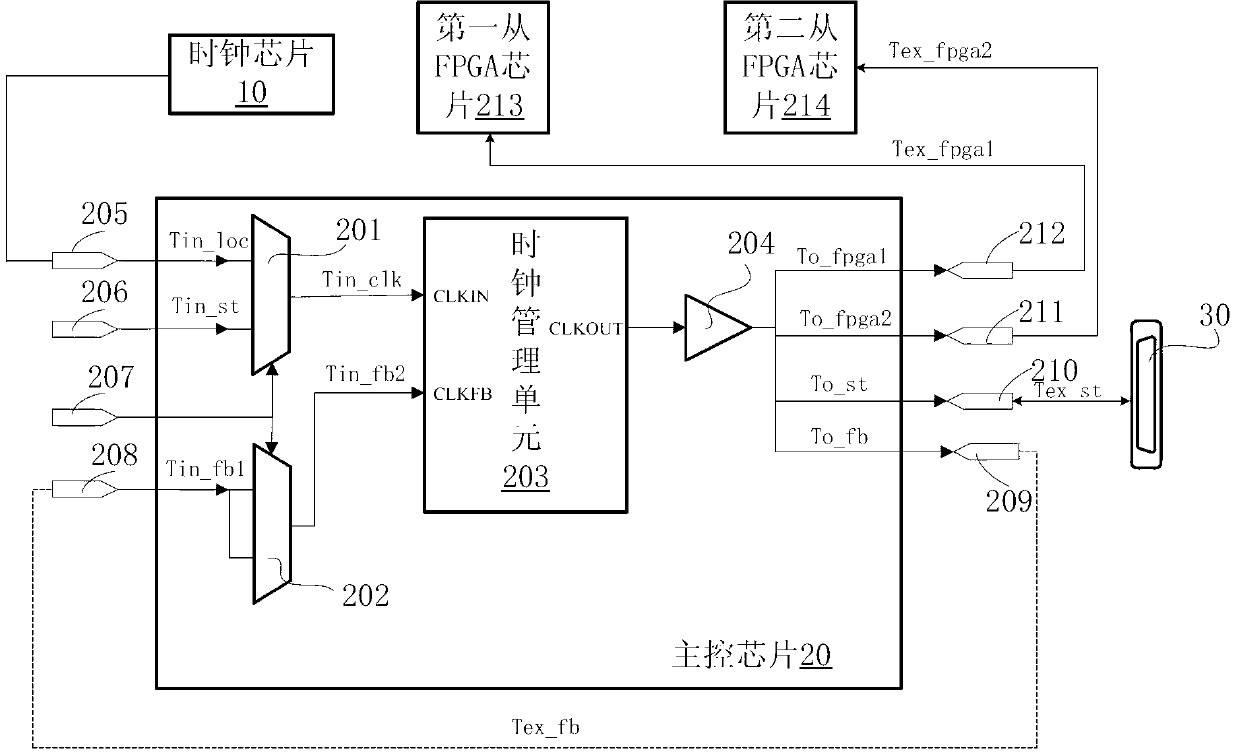

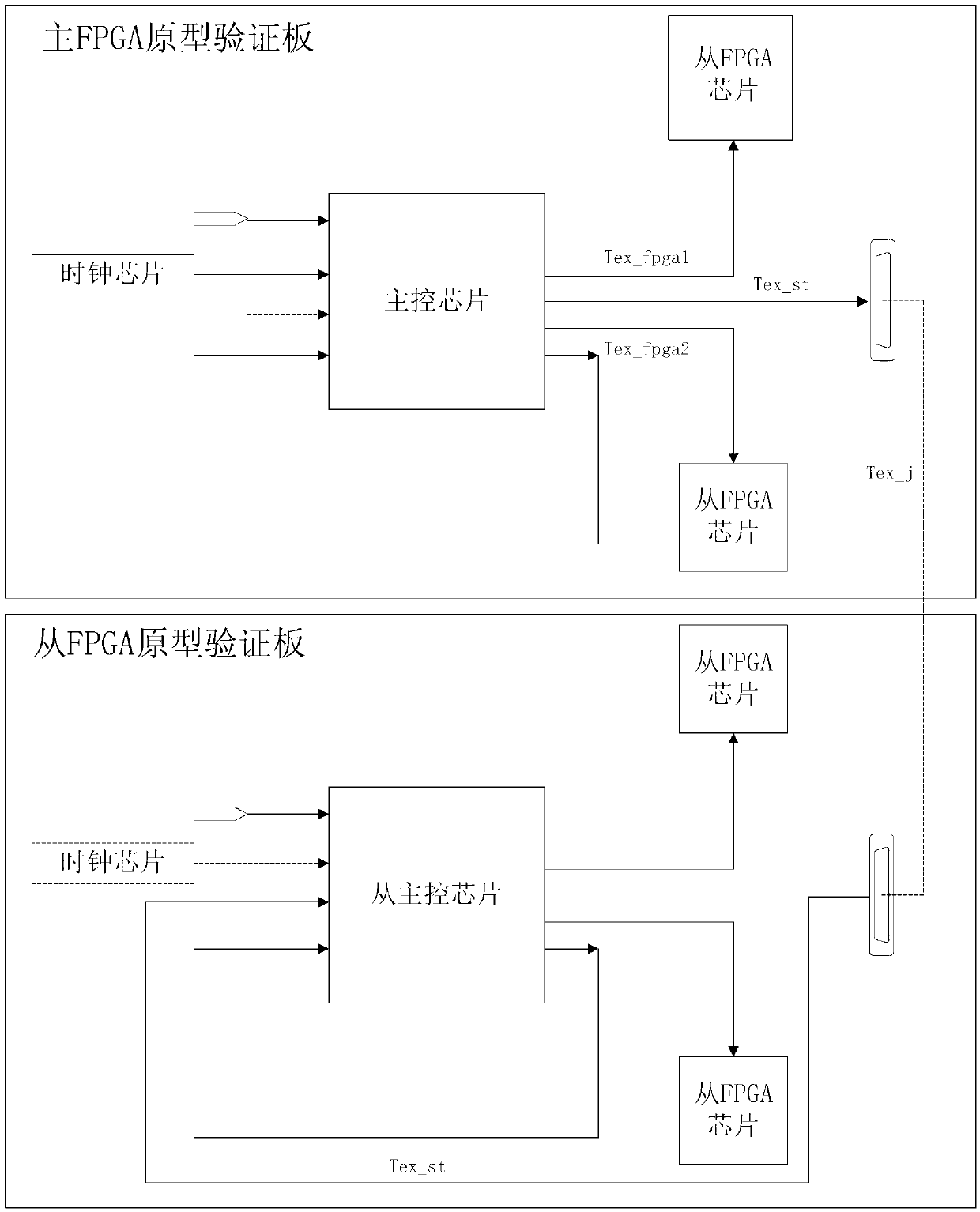

The invention discloses a clock synchronous device and a system for Field Programmable Gate Array (FPGA) prototype test plate piling, wherein the clock synchronous device for FPGA prototype test plate piling comprises a clock chip, a master control chip, at least one slave FPGA chip and at least one high-speed connector, wherein the main control chip further comprises a first data selector, a second data selector, a clock management unit and a global clock buffer. The master chip comprises a local clock input pin, a piling clock input pin, a selective signal input pin, a selective signal input pin, a feedback clock input pin, a slave FPGA clock synchronization clock signal output pin, a feedback clock synchronization clock signal output pin and a high-speed connector synchronization clock signal output pin. The clock synchronous device and the system for FPGA prototype test plate piling utilize a master control chip inner lock phrase loop to feed back, the time delay of a master control chip inner routing is equal to the corresponding routing time delay of an outer PCB plate, and the clocks which are output to all slave FPGA chip are enabled to achieve synchronization.

Owner:杭州乔微电子科技有限公司

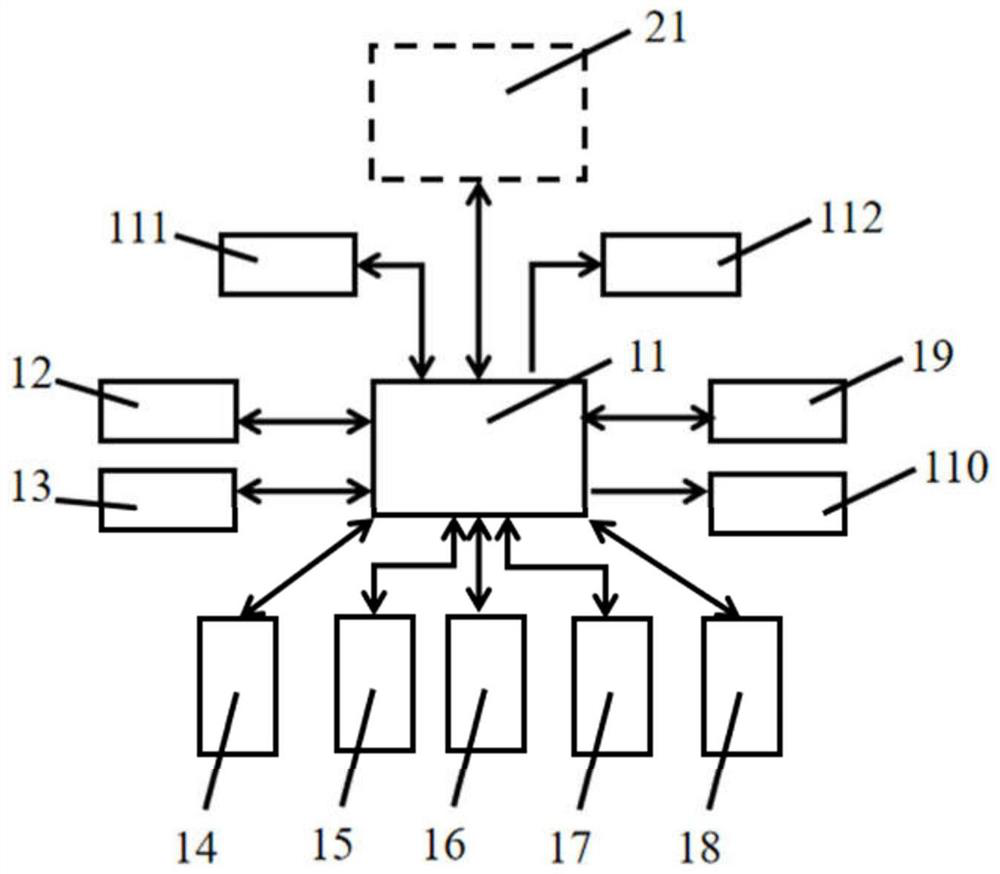

Field-programmable gate array (FPGA) prototype verification clock device

ActiveCN102306034AConvenient verificationEfficient verificationGenerating/distributing signalsResource utilizationSource-synchronous

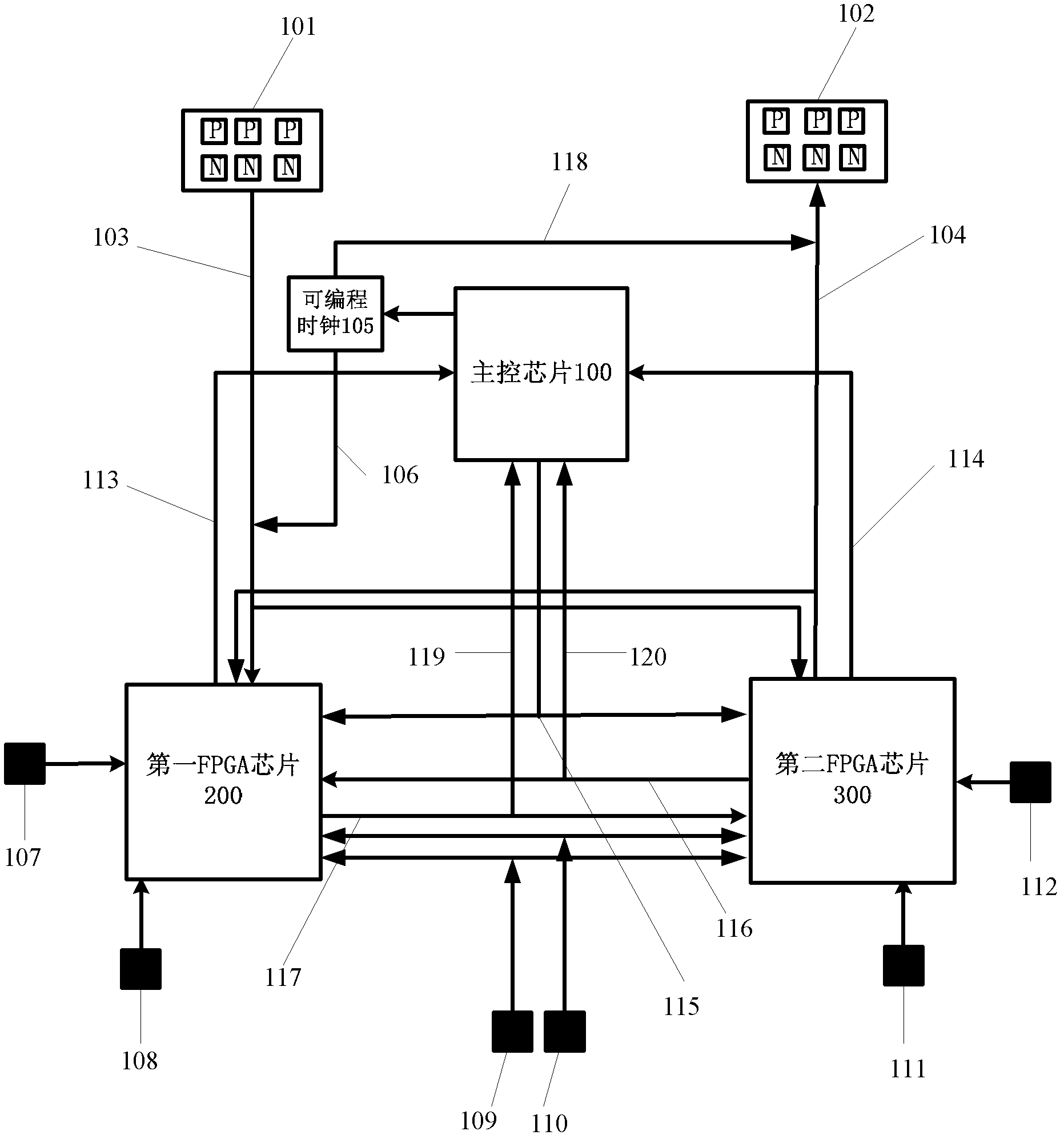

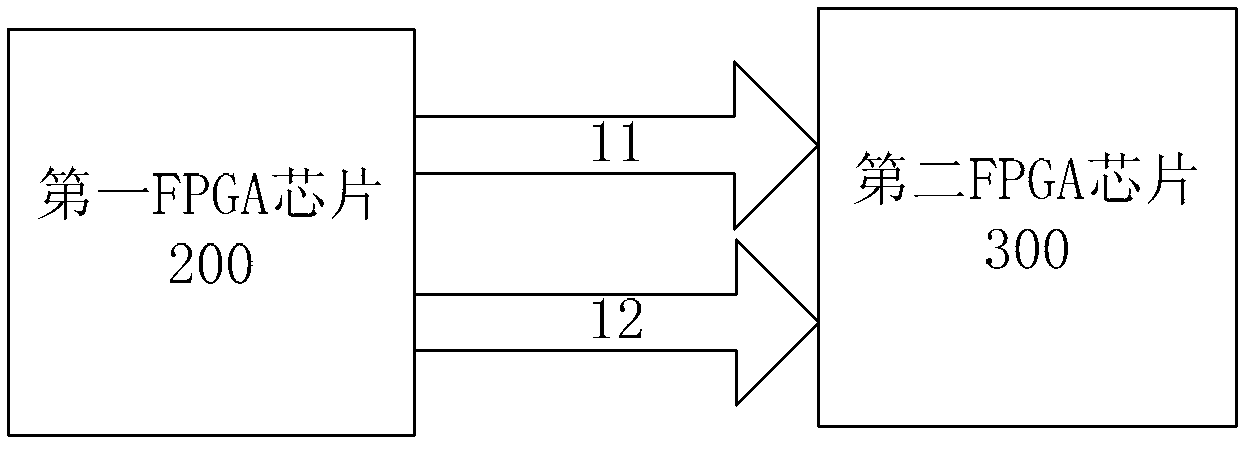

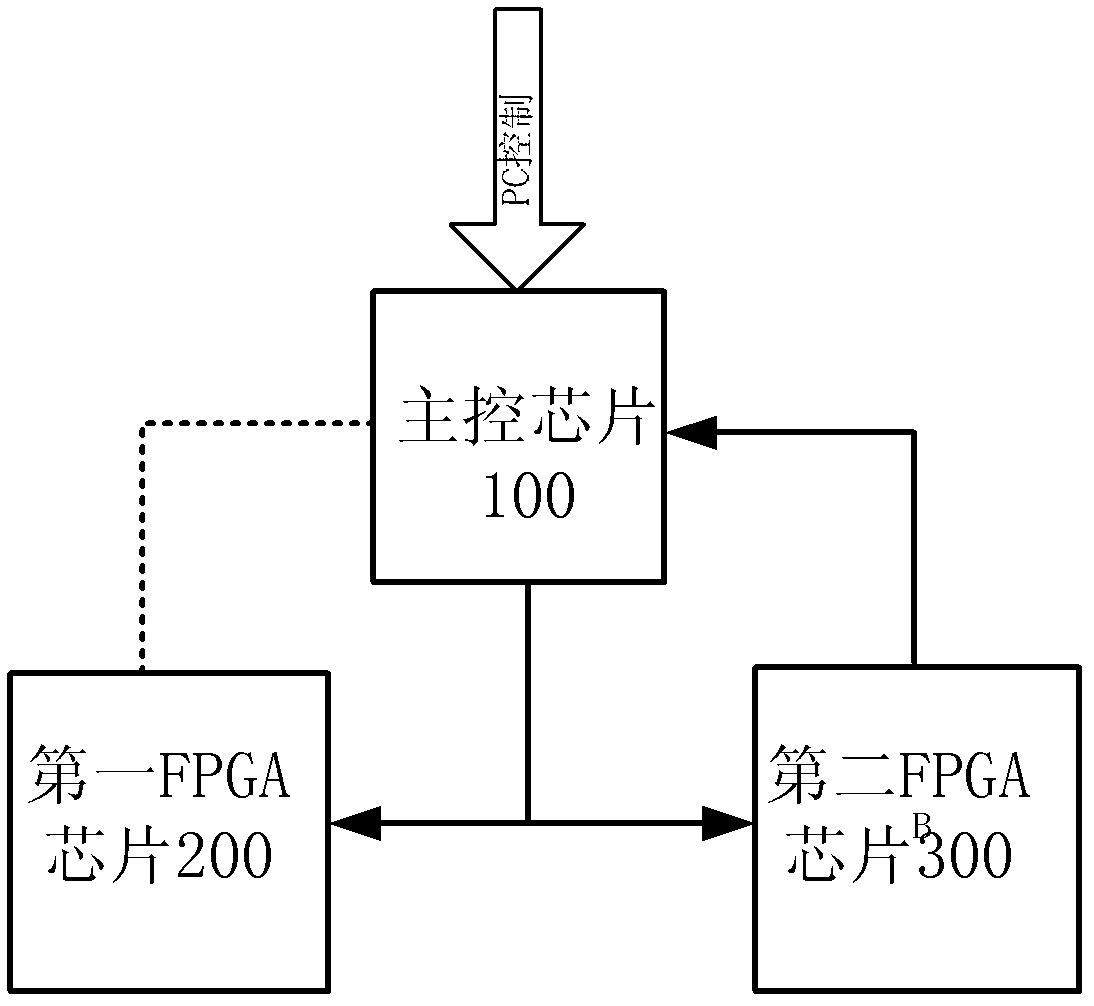

The invention provides a field-programmable gate array (FPGA) prototype verification clock device, and relates to the field of FPGA prototype verification. The device comprises a master control chip, a first FPGA chip, a second FPGA chip, an external clock input / output circuit which is connected with the first FPGA chip and the second FPGA chip simultaneously, an internal programmable clock circuit of which one end is connected with the master control chip and the other end is connected with the first FPGA chip and the second FPGA chip respectively, an external direct-insert crystal oscillator circuit which is directly connected with the first FPGA chip or the second FPGA chip or the first FPGA chip and the second FPGA chip simultaneously, a source synchronous clock circuit which points from the first FPGA chip to the second FPGA chip, and / or a source synchronous clock circuit which points from the second FPGA chip to the first FPGA chip, and a feedback clock circuit which is used for introducing the feedback clock of the first FPGA chip or the second FPGA chip into the master control chip and introducing the adjusted clock into the first FPGA chip and the second FPGA chip. The device realizes the centralized management of various clocks and maximizes a system clock resource utilization rate.

Owner:无锡亚科鸿禹电子有限公司

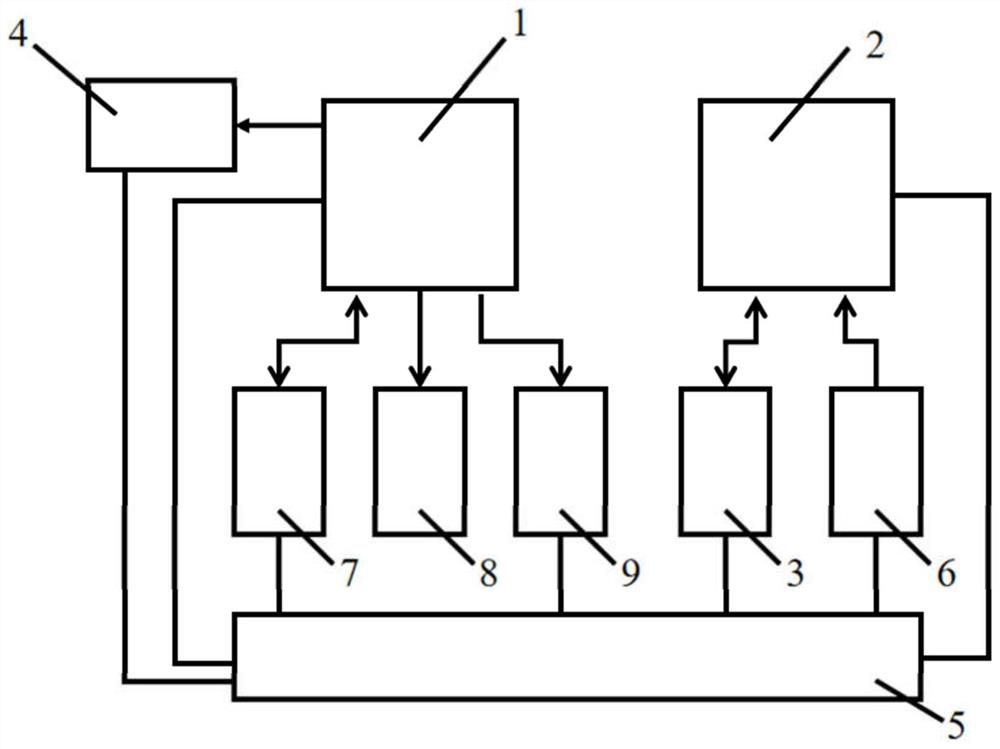

Bus control device for field-programmable gate array (FPGA) prototype verification system

ActiveCN102306131AConvenient verificationLow costElectric digital data processingData streamMode control

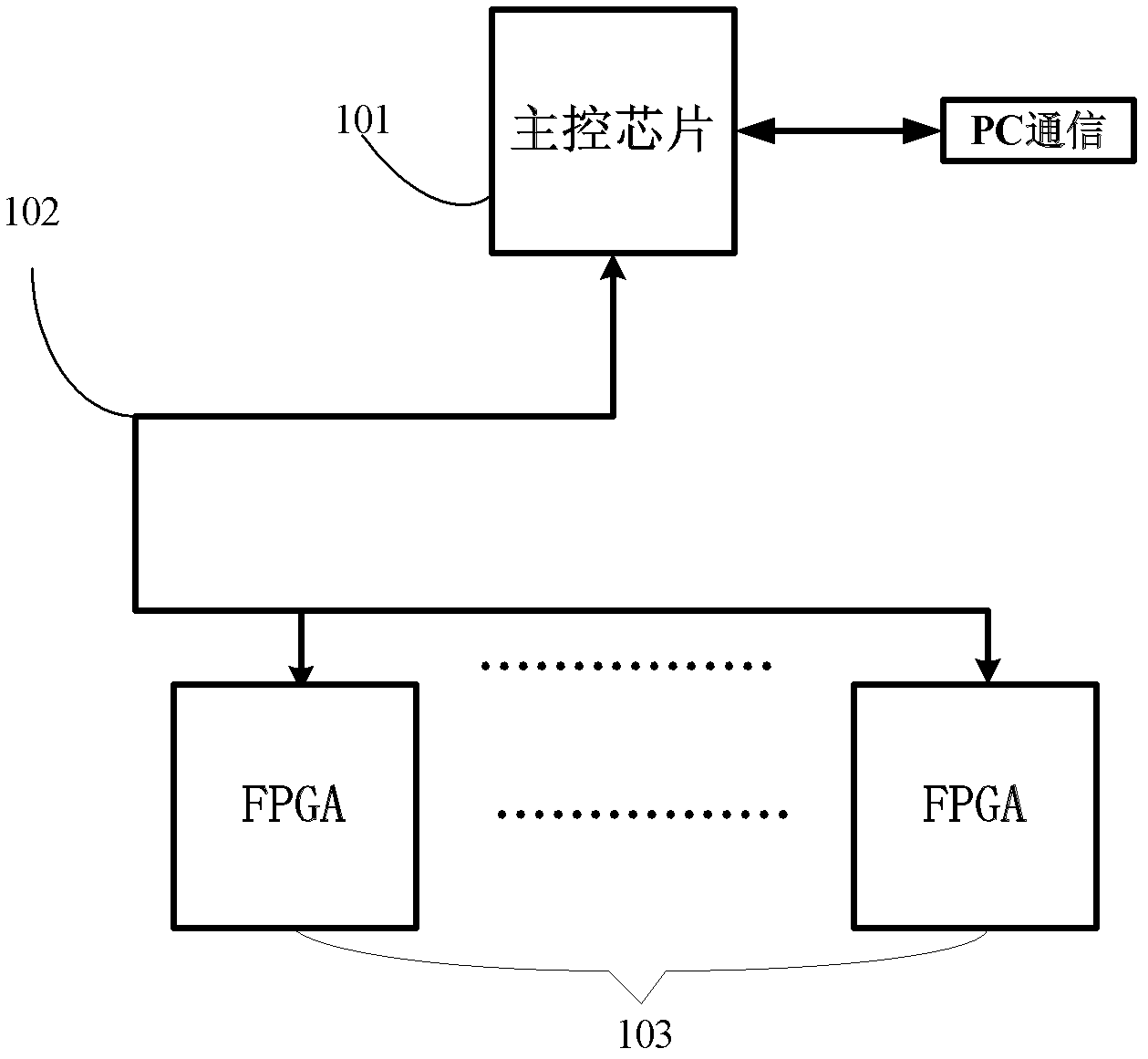

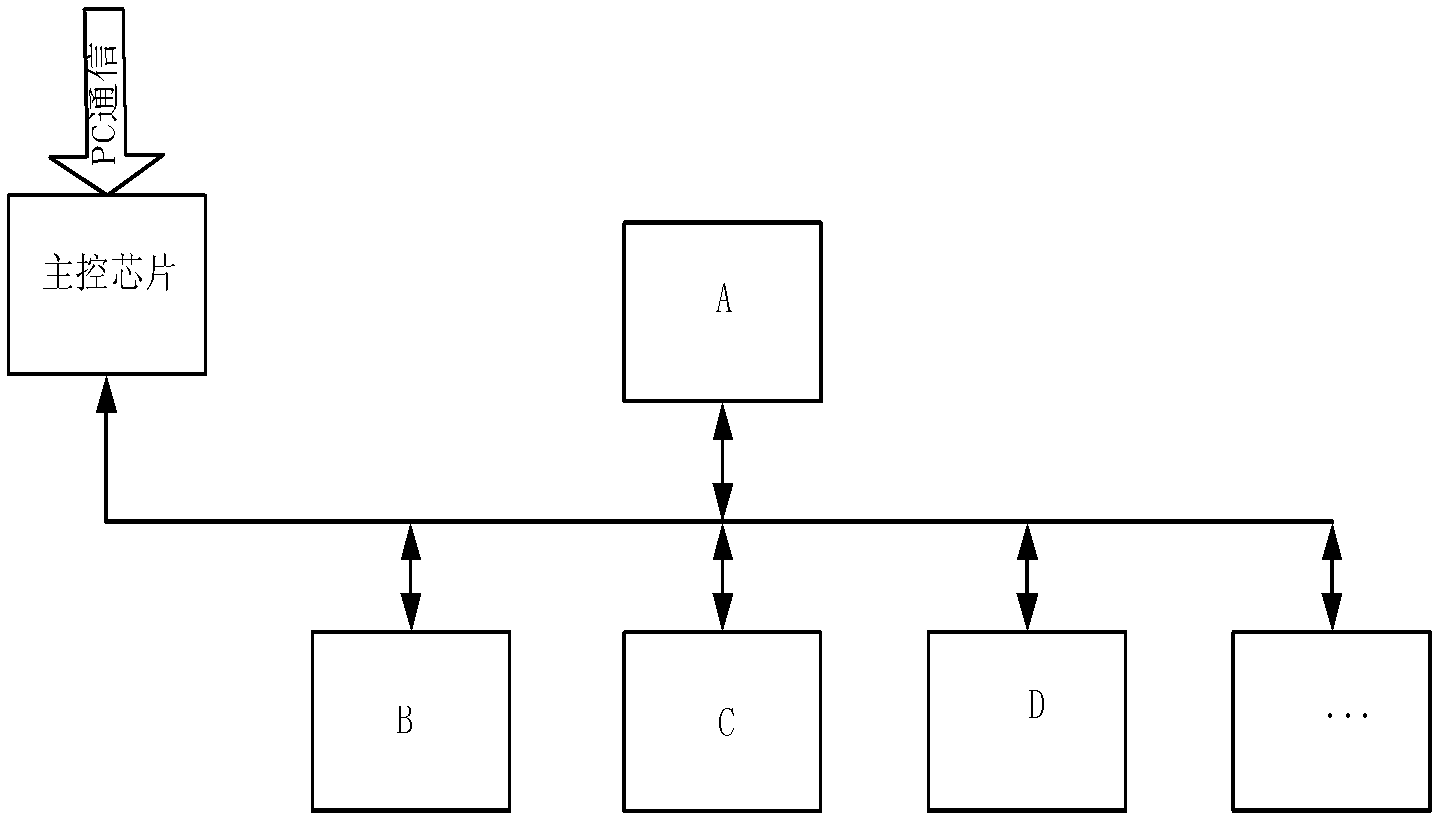

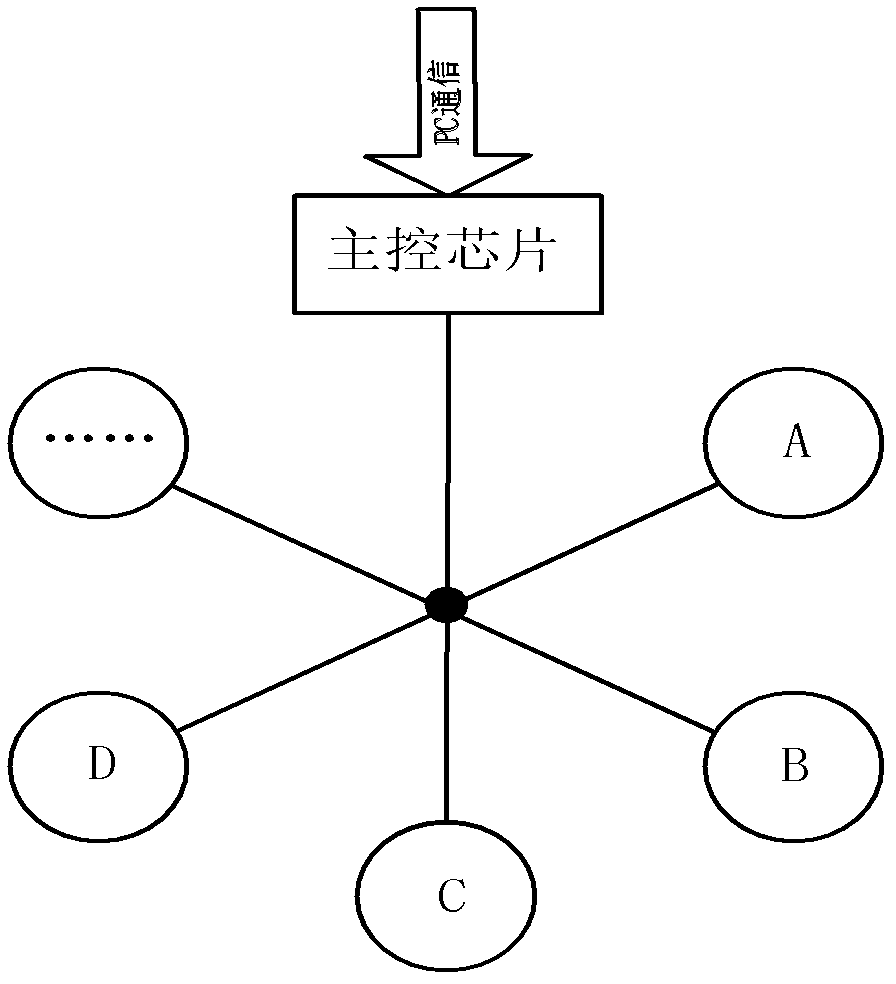

The invention provides a bus control device for a field-programmable gate array (FPGA) prototype verification system, and relates to the field of FPGA prototype verification. The device comprises a master control chip, a HyperBus and a plurality of slave FPGA chips, wherein the master control chip is connected with the plurality of slave FPGA chips through the HyperBus; the HyperBus comprises a mode control line; the master control chip comprises a master mode control module, a master data transceiving module and a master data stream monitoring module; and each slave FPGA chip comprises a slave mode control module and a slave data transceiving module. In the device, the master control chip is connected with the HyperBus (HyperSilicon Bus), adjusts the state of the mode control line according to a mode control instruction, or sets the working mode of a system bus by manually setting the state of the mode control line in an initial state, so that a multibus working mode is operated in the same system, great convenience is brought to the FPGA prototype verification, cost is reduced, and the HyperBus provides a good system communication and control path particularly for HyperBus-based secondary development.

Owner:无锡亚科鸿禹电子有限公司

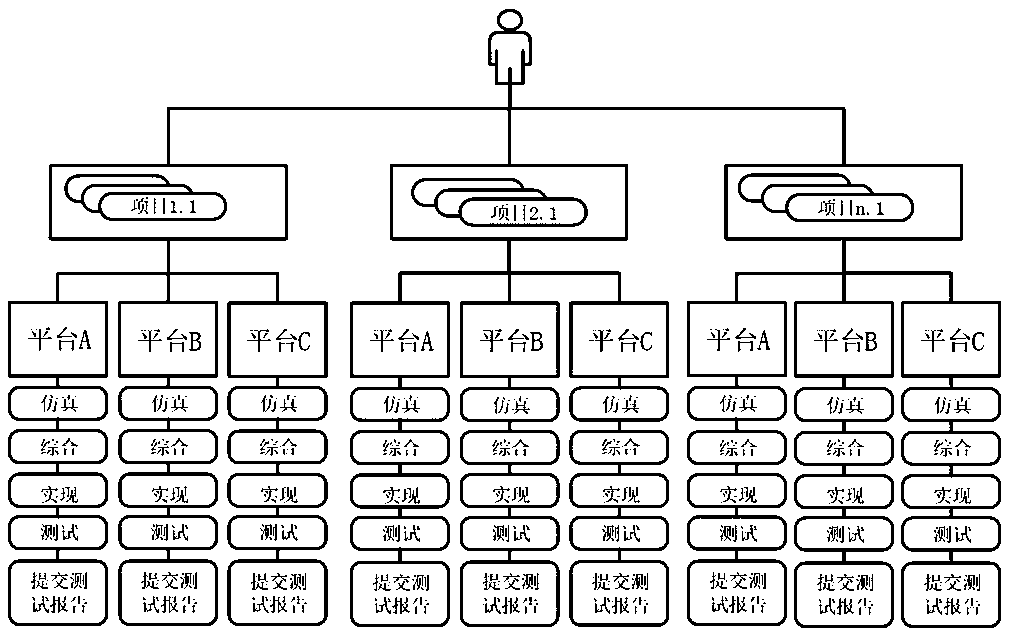

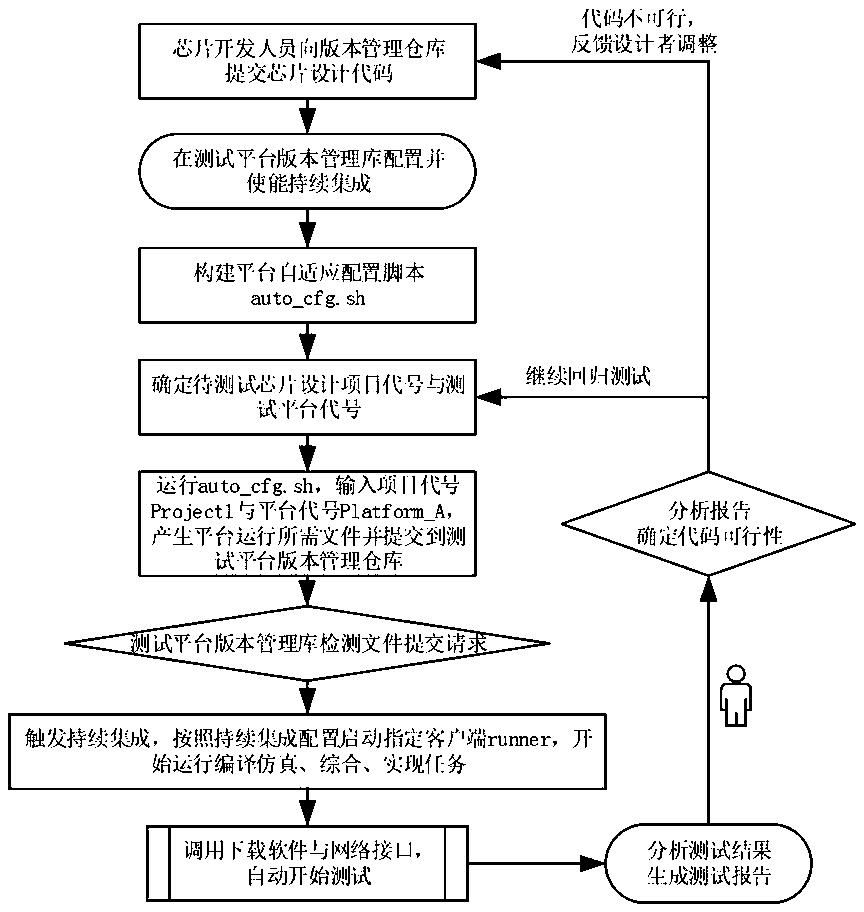

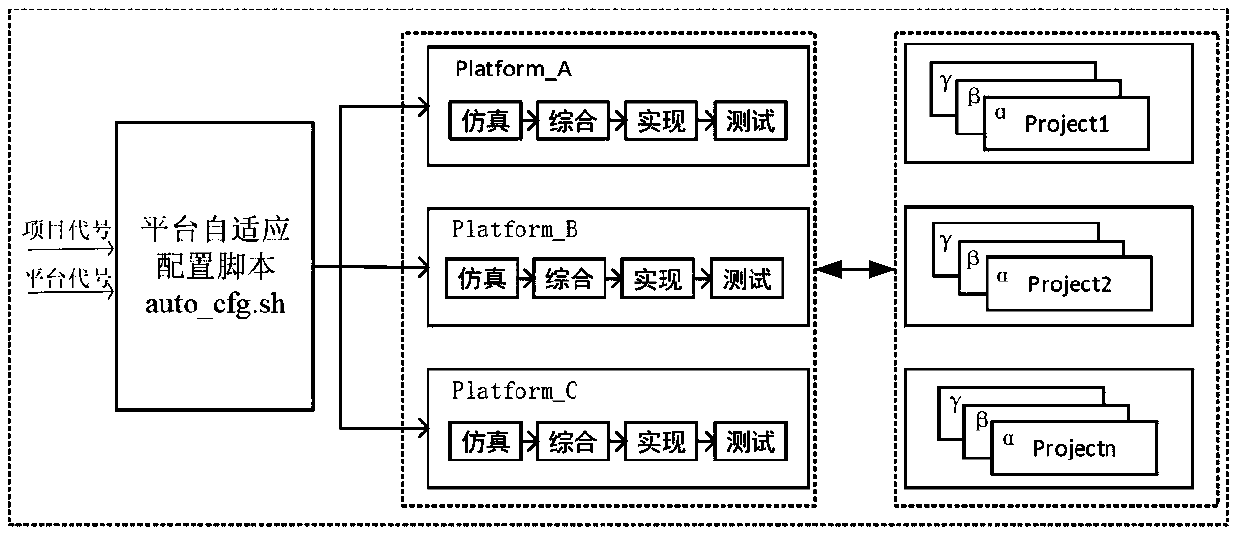

Multi-project and multi-platform self-adaptive chip design FPGA prototype verification method and system

ActiveCN111400119ASupport for automated verificationReduce interventionDetecting faulty computer hardwareCAD circuit designContinuous integrationSoftware engineering

The invention discloses a multi-project and multi-platform self-adaptive chip design FPGA prototype verification method and system. The method comprises the following steps: executing multi-project and multi-platform initialization, determining a project code of chip design, using a tested platform code, generating a file list and a parameter file required by running of a corresponding project library and a platform environment library, and submitting the file list and the parameter file to a version management warehouse of a corresponding test platform; triggering the continuous integration tool to start the client according to the script to perform compilation simulation, integration, realization and generation of a test report, and uploading the test report to a version management warehouse. According to the invention, a plurality of chip design projects and a plurality of FPGA prototype verification platform environments are coupled together; verification developers are supported to flexibly switch between a plurality of projects and a plurality of verification platforms in one version management library, and the FPGA prototype verification automation process of the specified project and the specified platform can be quickly completed only through a small amount of configuration.

Owner:PHYTIUM TECH CO LTD

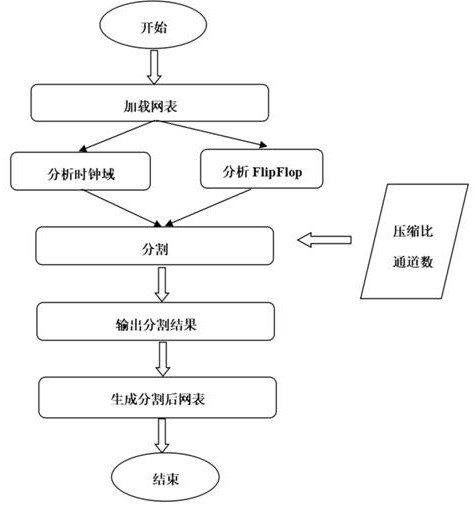

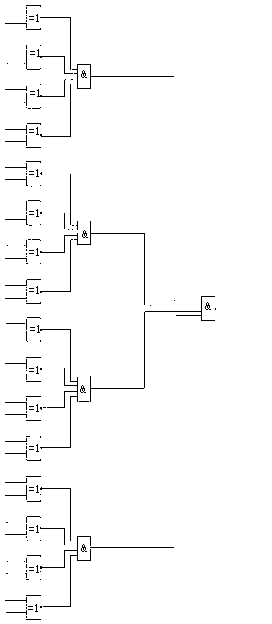

Software segmentation method based on FPGA logic

ActiveCN112183002AGood segmentation resultCAD circuit designSpecial data processing applicationsClock rateSoftware engineering

The invention belongs to the technical field of electronic computer software application, and particularly relates to a software segmentation method based on FPGA logic. The method comprises a FlipFlop and FPGA analysis step, a compression ratio presetting step and a segmentation step. Processing of related constraints such as clock domain grouping, FlipFlop and compression ratio which influence IC circuit operation is added into a traditional minimum cut algorithm based on resource weight, so that the operation clock frequency constraint of an IC circuit system can be met in a multi-FPGA prototype system segmentation process, an obtained segmentation result enables the whole IC circuit to be better in operation performance, correct in function and stable in work.

Owner:S2C

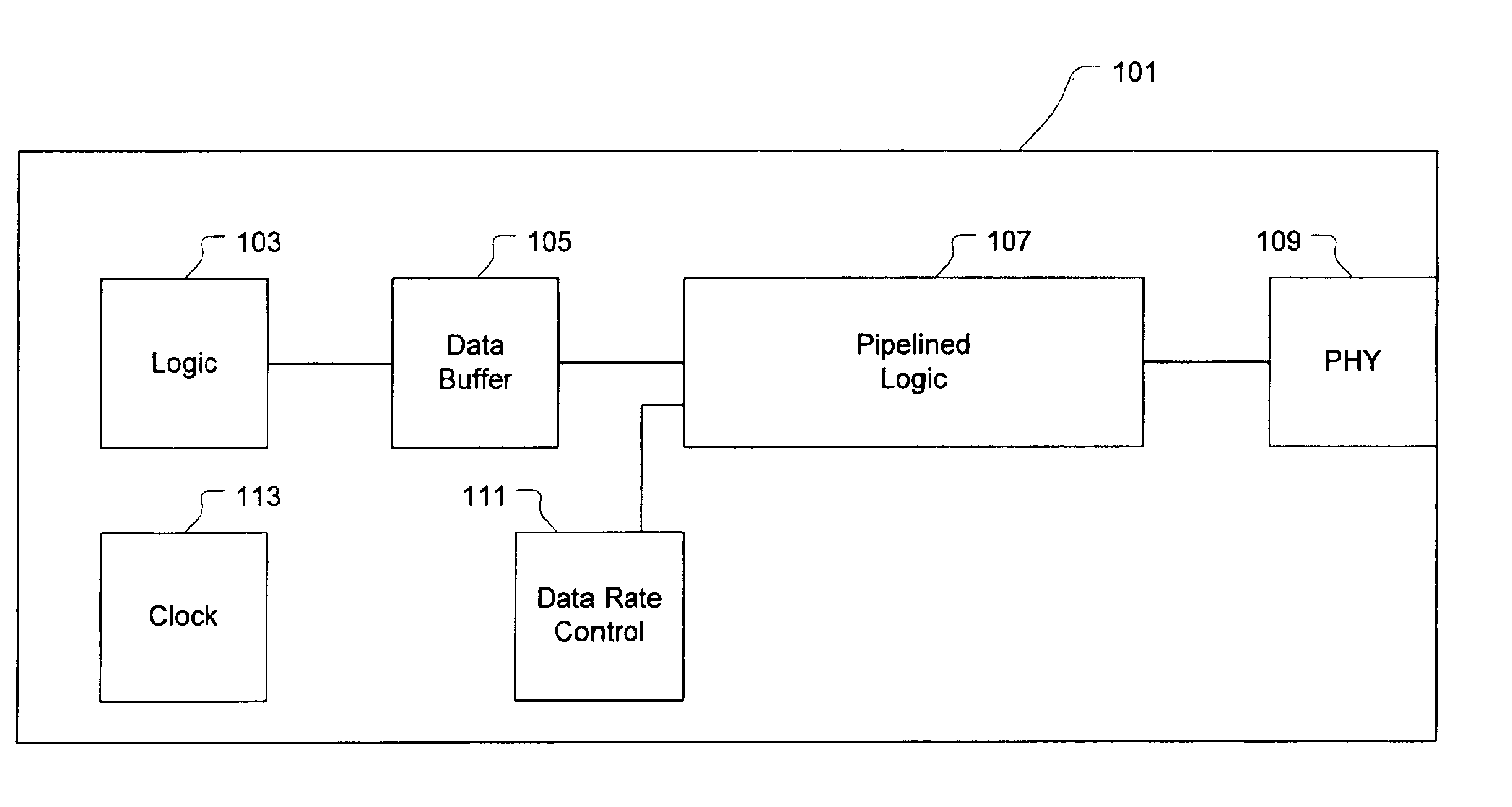

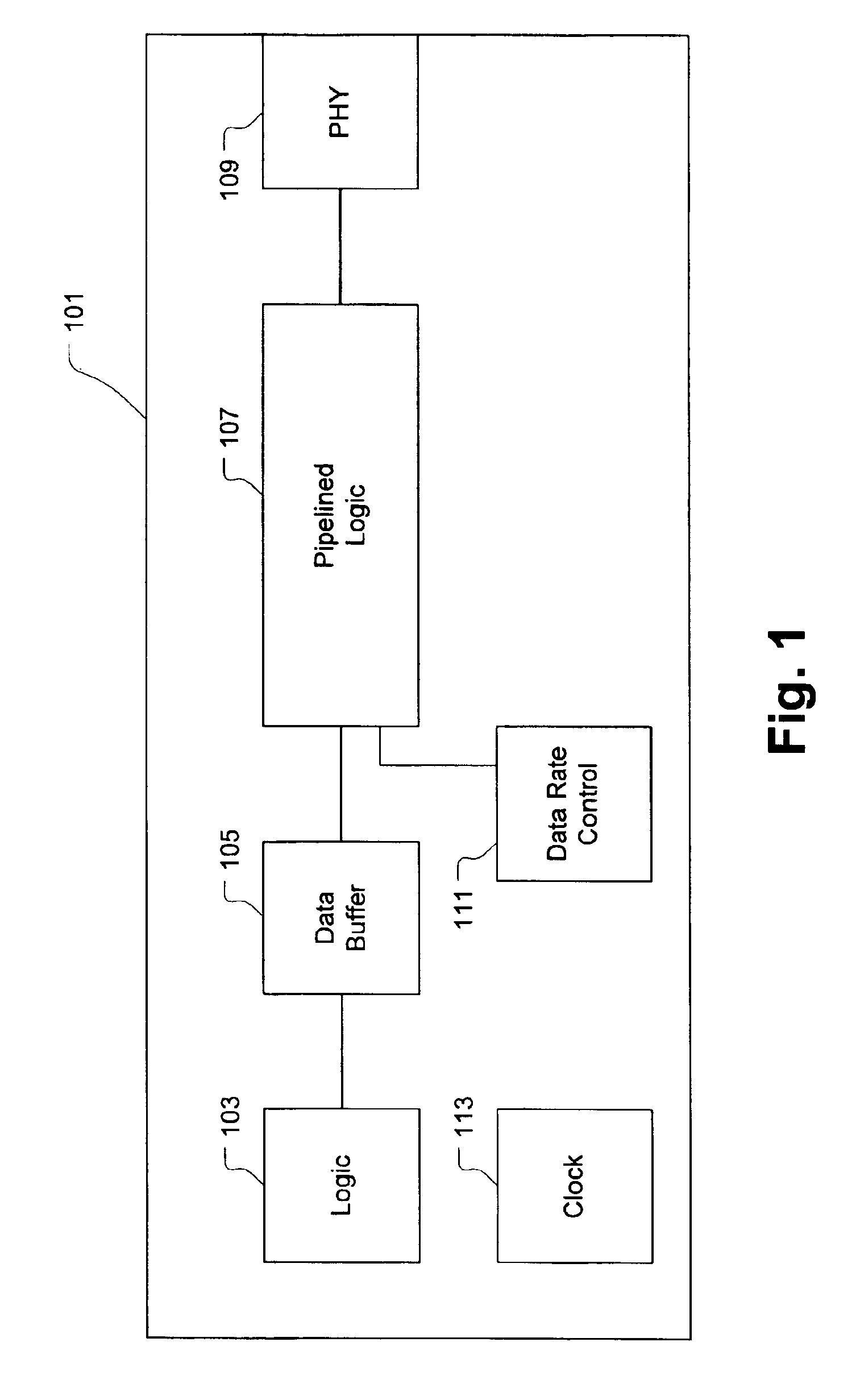

Method and apparatus for controlling data output frequency

Broadly speaking, a method and corresponding apparatus is provided for controlling a data output rate of an electronic device. More specifically, the method and corresponding apparatus enables an equivalent data output rate to be obtained from each of an ASIC and an FPGA prototype of the ASIC while maintaining equivalent logic between the ASIC and the FPGA prototype. A validity bit is attached to each output data signal in accordance with each cycle of a clock signal. The validity bit provides an indication as to whether the associated data signal should be processed (i.e., transmitted as output) normally. Only valid output data signals as identified by their validity bit value are transmitted. Thus, the validity bit values associated with successive data signals can be defined to generate a particular data output rate.

Owner:ADAPTEC +1

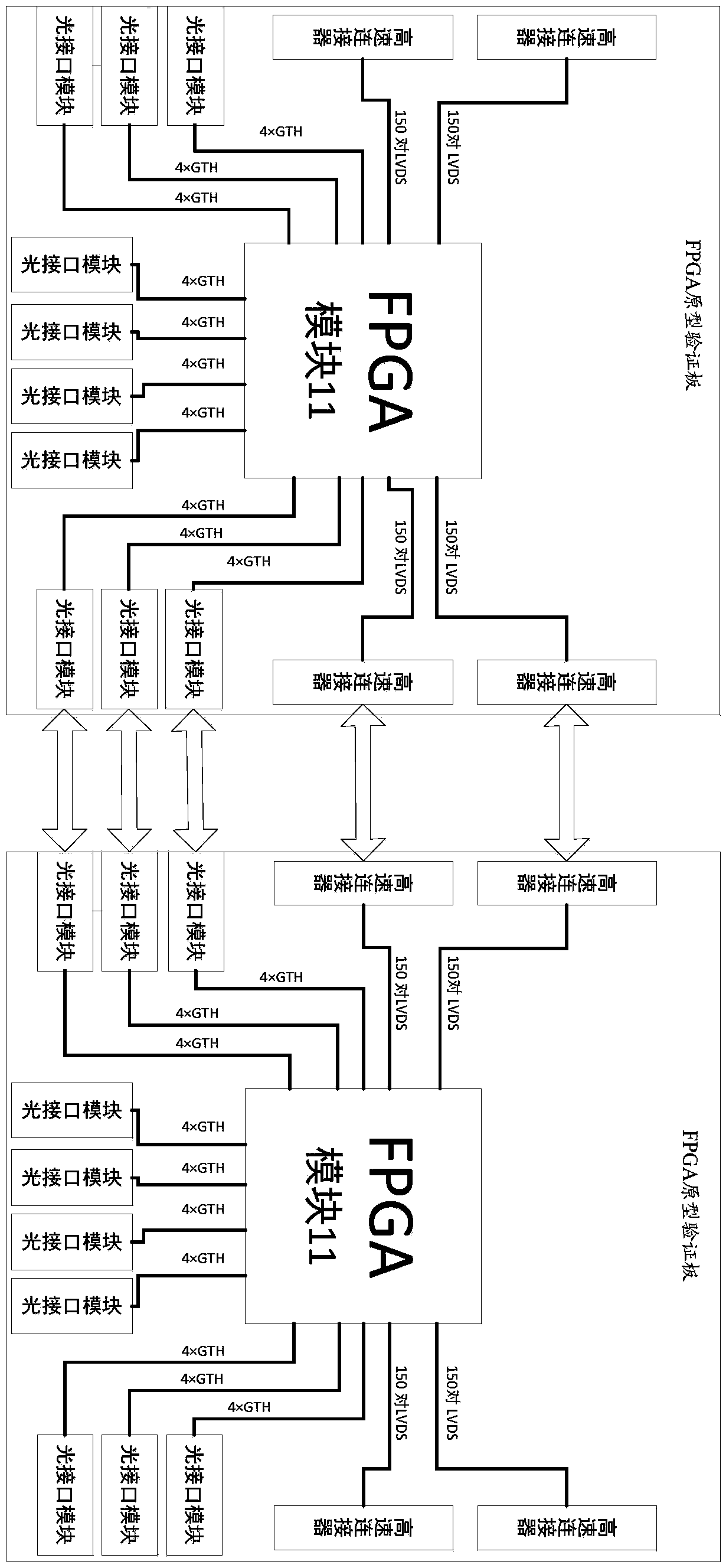

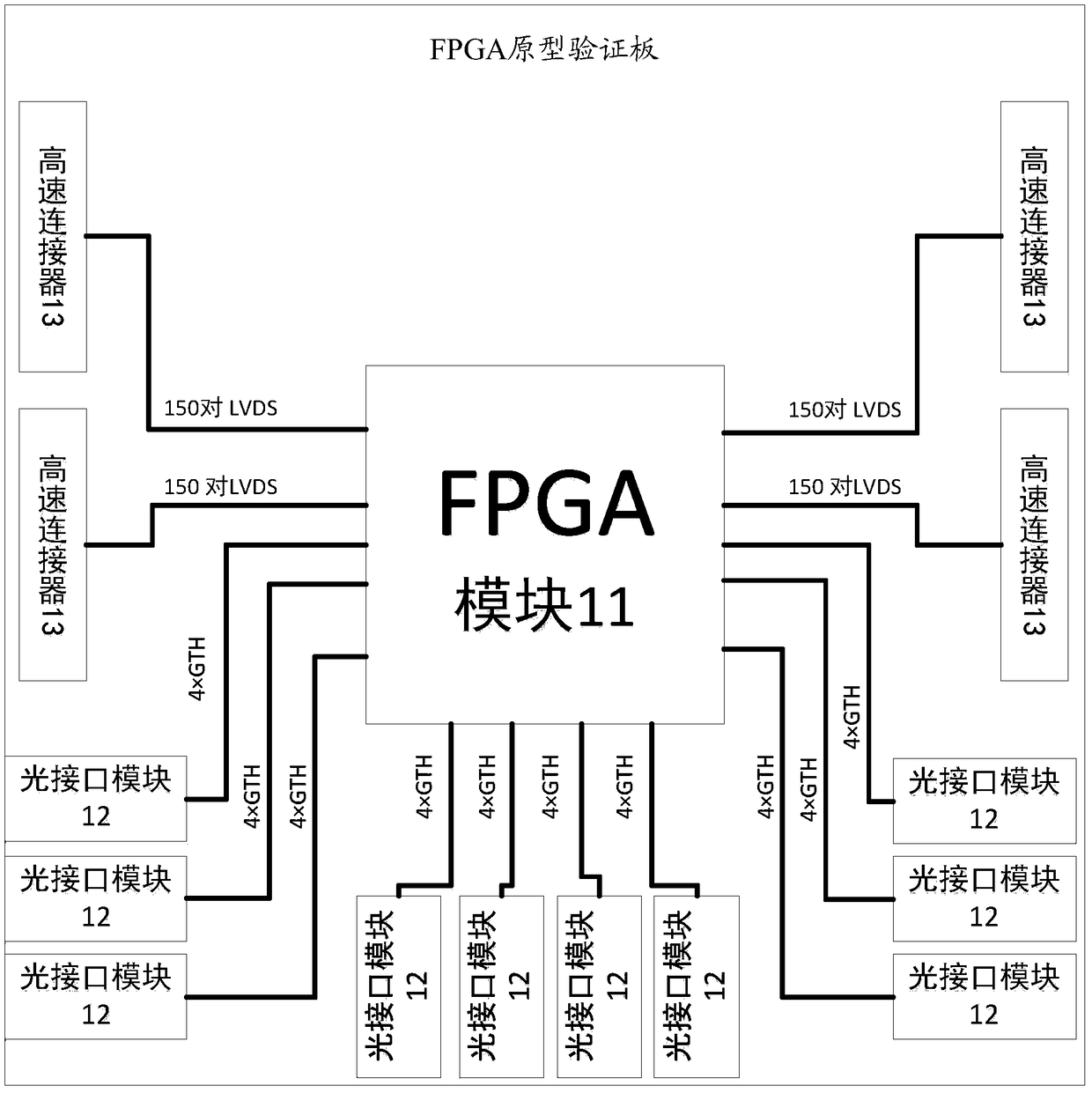

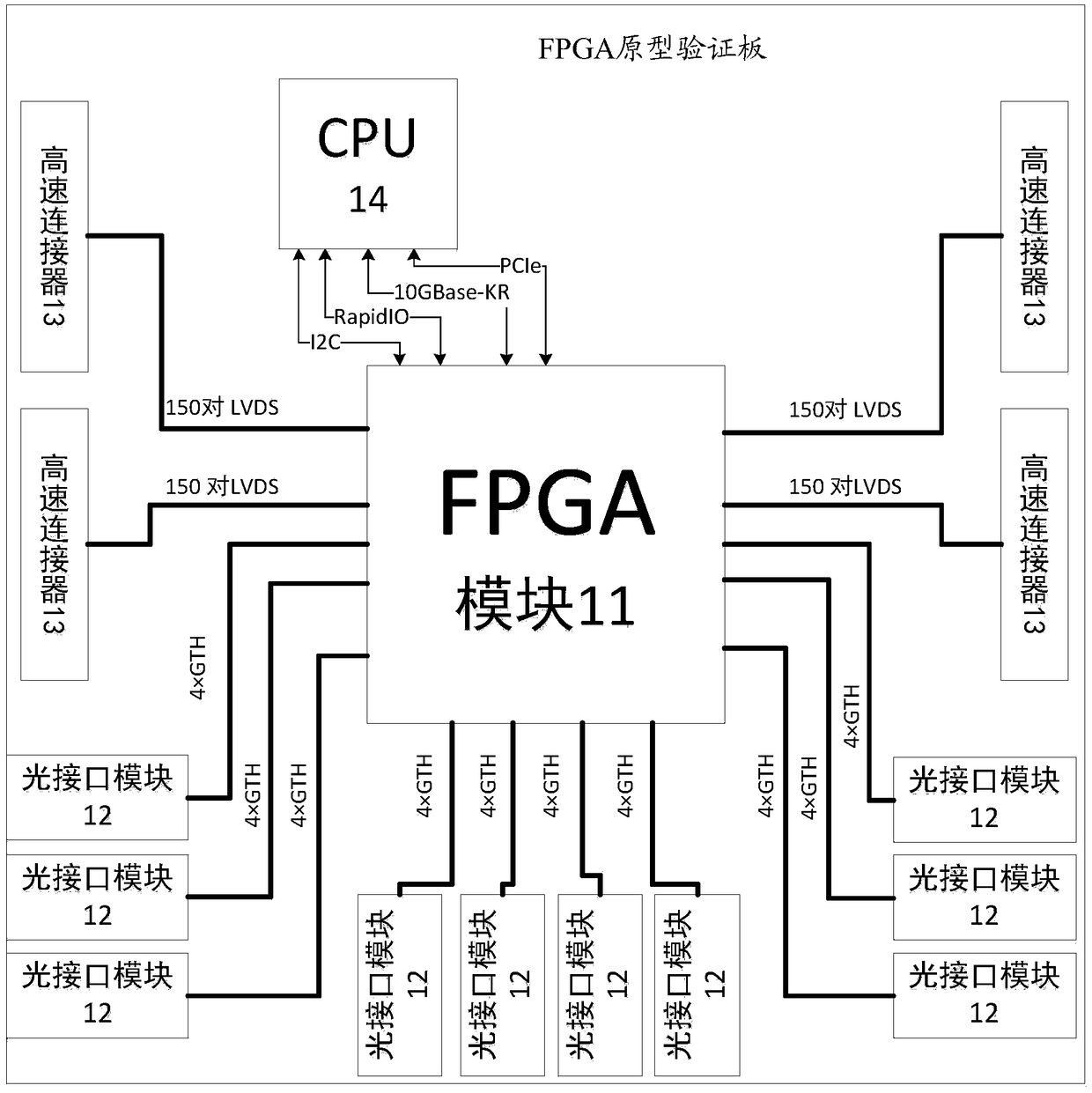

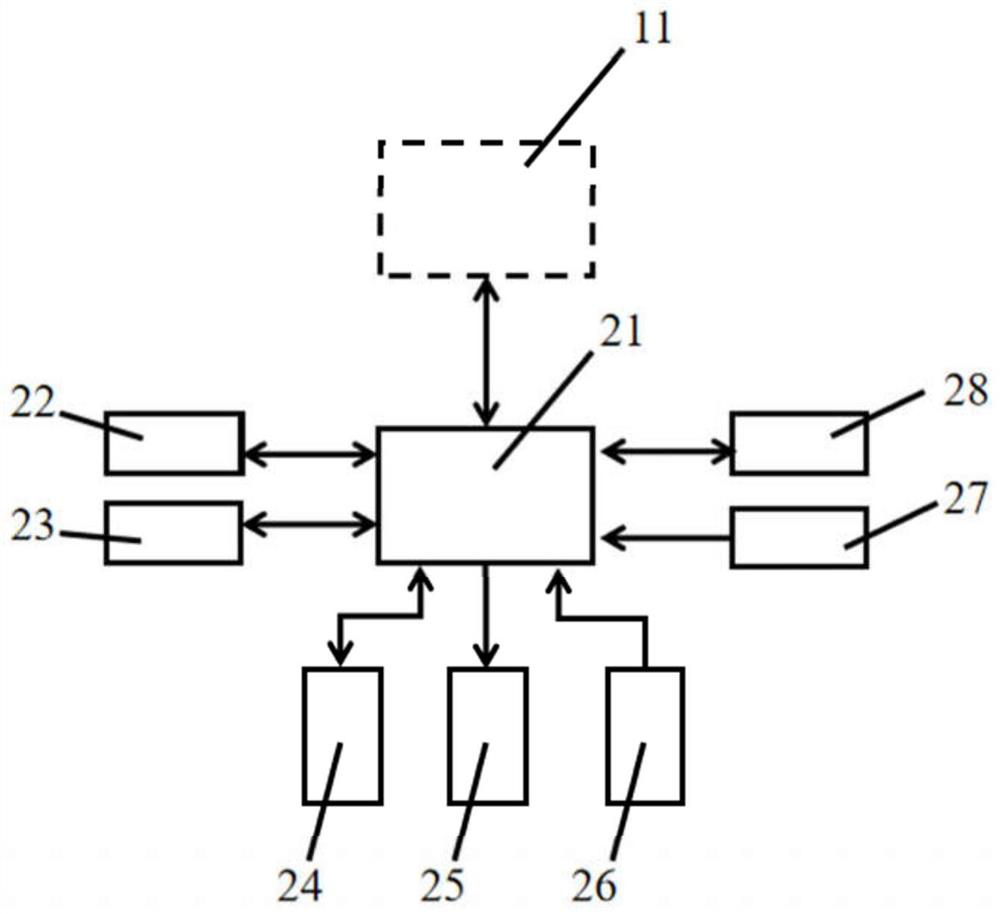

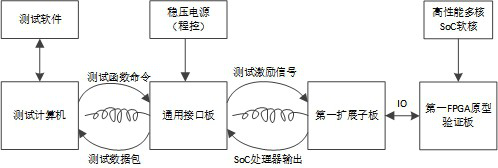

FPGA prototype verification system

PendingCN109190276AEasy to verify experimentsSolve the disadvantages of fewCAD circuit designSpecial data processing applicationsComputer moduleInterconnection

The invention provides an FPGA prototype verification system. The FPGA prototype verification system comprises at least two cascaded FPGA prototype verification boards. The I / O port of the high-speedconnector of the FPGA prototype verification board of the previous stage is connected with the I / O port of the high-speed connector of the FPGA prototype verification board of the next stage. The I / Oport of the optical interface module of the preceding FPGA prototype verification board is connected with the I / O port of the optical interface module of the subsequent FPGA prototype verification board. Through the high-speed connector and the optical interface module, the board-level cascading can be flexibly carried out, thereby facilitating some large-scale module or whole-chip prototype verification experiments, and the technical effect that the available interconnection interface is greatly improved to solve the shortcoming of the existing scheme that the interconnection interface is few.

Owner:天津市滨海新区信息技术创新中心 +1

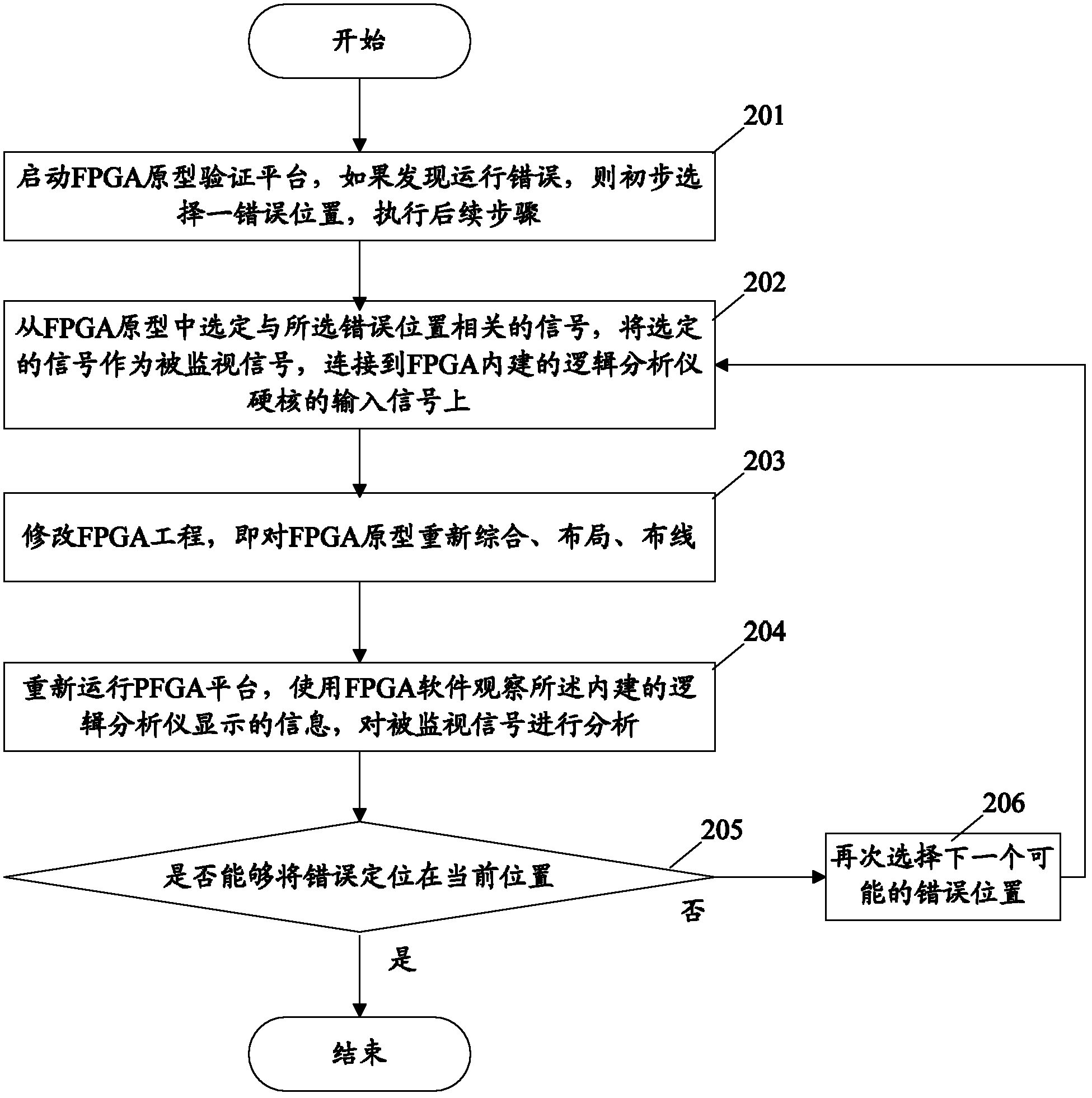

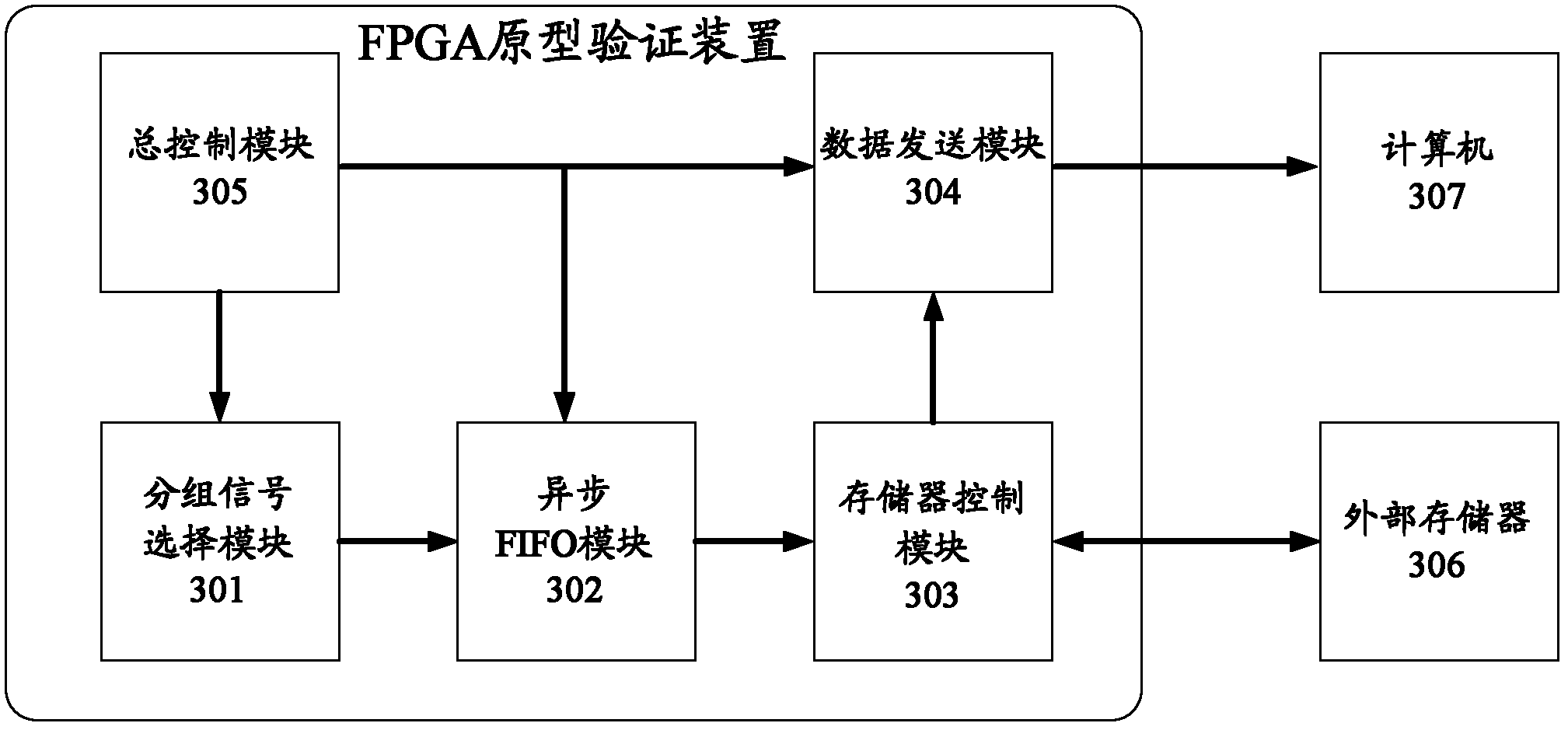

Field programmable gate array (FPGA) prototype verification device and method

ActiveCN102855338AShorten the timeEasy to operateSpecial data processing applicationsVisibilityExternal storage

The invention discloses field programmable gate array (FPGA) prototype verification device and method. The device comprises a packet signal selection module, an asynchronous first in first out (FIFO) module, a memory control module, a data transmission module and a main control module, wherein an input end of the packet signal selection module is connected with at least one packet signal of an FPGA prototype; when an error occurs during the FPGA prototype verification, one of the packet signals is selected from the input end of the packet signal selection module according to a selection instruction to serve as a monitored signal; the packet signal is output to the asynchronous FIFO module to be synchronized into a signal with a speed same as that of the memory control module; the synchronized signal is stored to an external memory by the memory control module and then is read to the data transmission module by the external memory; and the monitored signal is transmitted to an external computer by the data transmission module to carry out data analysis so as to positioning the error. By using the FPGA prototype verification device and method, the operability, the visibility and the efficiency of the FPGA verification can be improved.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

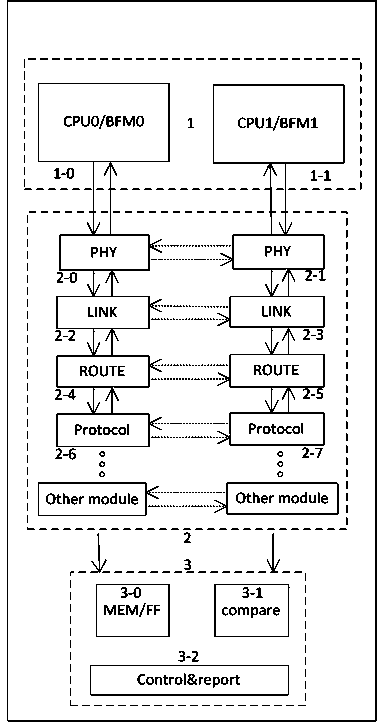

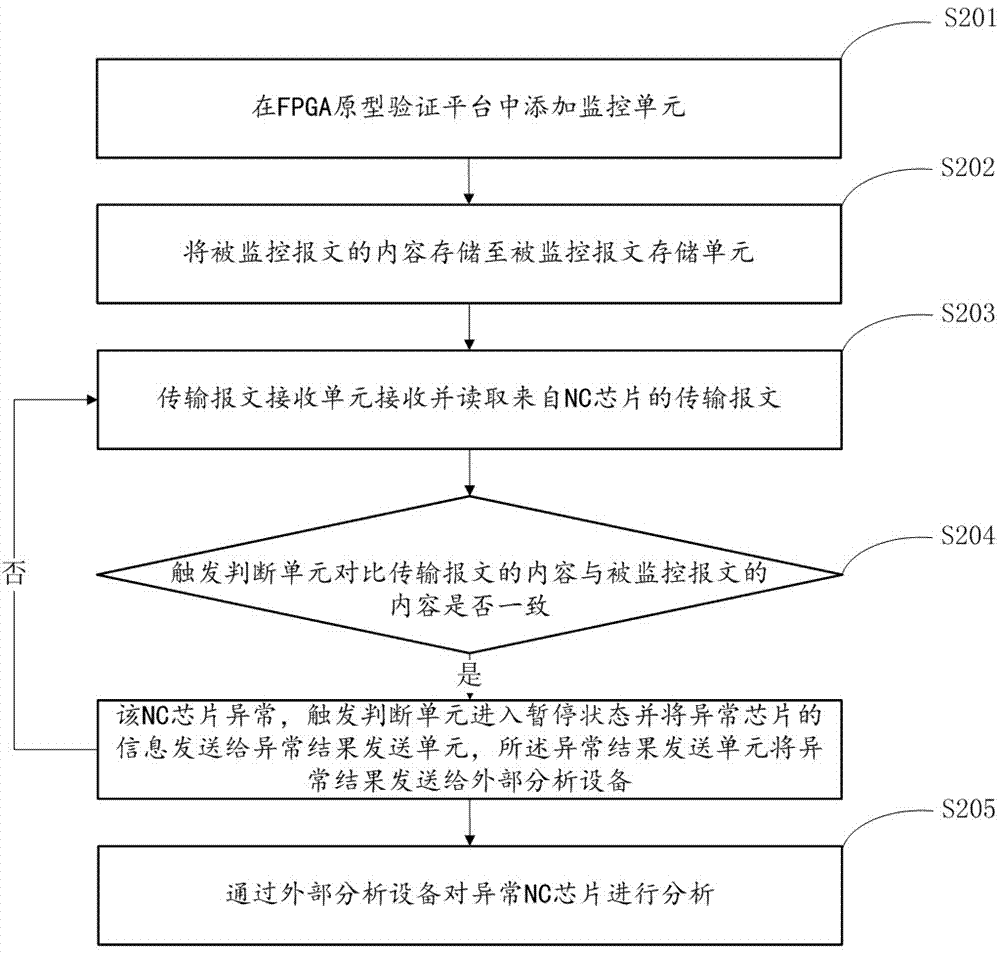

Back-to-back loopback validation method for large-scale interconnection chips based on detection logic addition

ActiveCN103970634AProcessing speedElectronic circuit testingLogical operation testingFPGA prototypeLogisim

The invention provides a back-to-back loopback validation method based on detection logic addition to validate NC interconnection logic through simulation validation and FPGA prototype validation. According to the characteristics that NC messages can be divided according to types and transmitted through channels, the mode of module back-to-back loopback validation and detection logic addition validation is put forward, problems of large data size, low manual validation efficiency and difficult in positioning during simulation validation and FPGA prototype validation of large-scale interconnection logic are solved, and validation results and efficiency are ensured.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

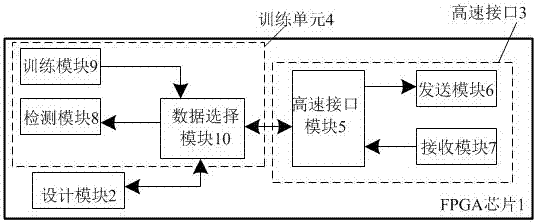

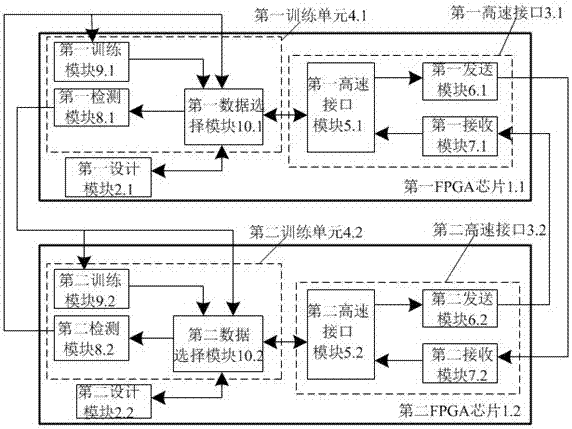

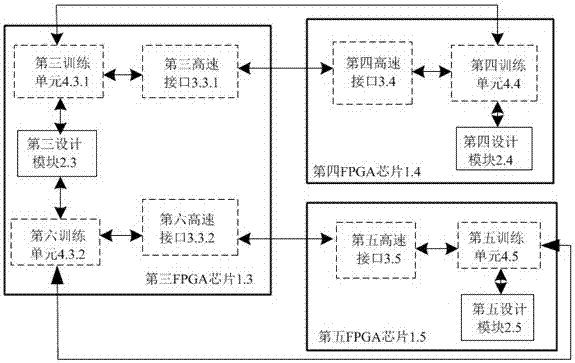

FPGA chip, high-speed interface interconnection system and interconnection achieving method

ActiveCN107480332AIncrease success rateReduce participationCAD circuit designSpecial data processing applicationsData selectionFPGA prototype

The invention relates to an FPGA chip, a high-speed interface interconnection system and an interconnection achieving method. The FPGA chip is characterized by comprising an FPGA chip body, the FPGA chip body comprises a high-speed interface and a training unit, the high-speed interface comprises a high-speed interface module, and the high-speed interface module is connected with a transmitting module and a receiving module; the training unit comprises a data selection module, and the data selection module is connected with a training module and a detection module; the data selection module is connected with a design module; the data selection module is connected with the high-speed interface module; the FPGA chip body and the high-speed interface of at least another one FPGA chip. An automatic interconnection mechanism of the high-speed interface is put forwards, the high-speed interface interconnection success rate is increased, artificial participation is reduced, the debugging process is accelerated, and therefore the FPGA prototype verification period and the chip development period are greatly shortened.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

A shared on-line debugging method based on FPGA prototype verification system

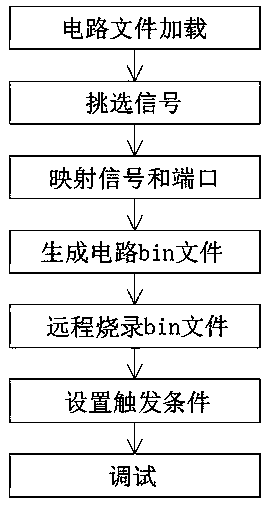

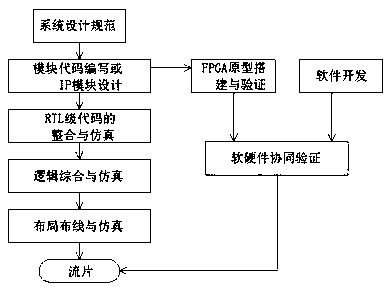

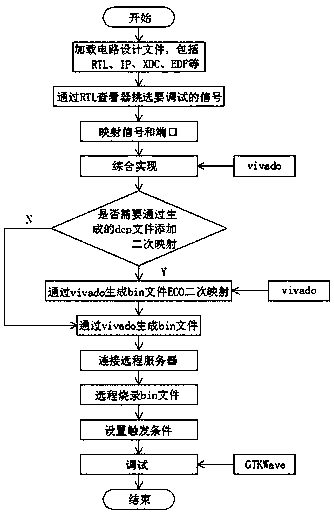

The invention provides a shared on-line debugging method on a prototype verification system based on FPGA. The debugging method comprises: loading circuit files, selecting signals, mapping signals andports, generating circuit bin files, remotely burning the bin files, setting triggering conditions, and debugging. The device of the invention comprises a server end, an FPGA prototype verification board and a client, the server end comprises a server end program, the client includes a client program, the client program provides a visual debugging interface for a user, including RTL code viewing,variable name mapping, secondary mapping in ECO, etc. The invention discloses a shared on-line debugging method based on FPGA prototype verification system, which can improve the usage rate of FPGA prototype verification, reduce the use cost, and greatly improve the debugging speed of circuit design engineer.

Owner:山东芯革电子科技有限公司

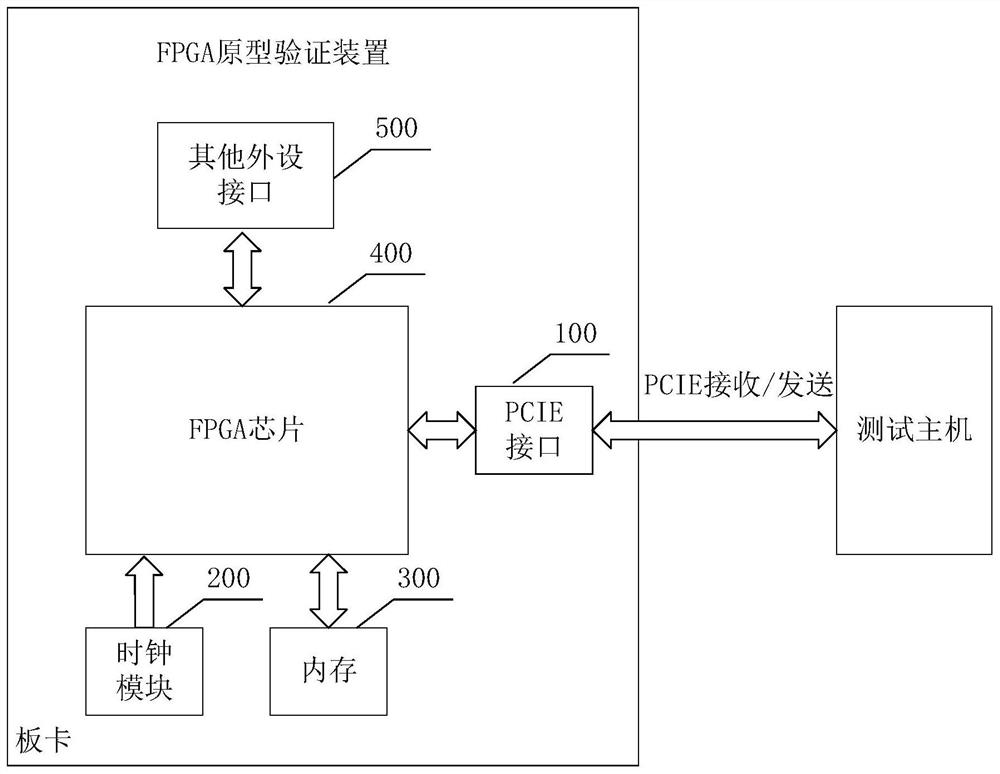

FPGA prototype verification device and method

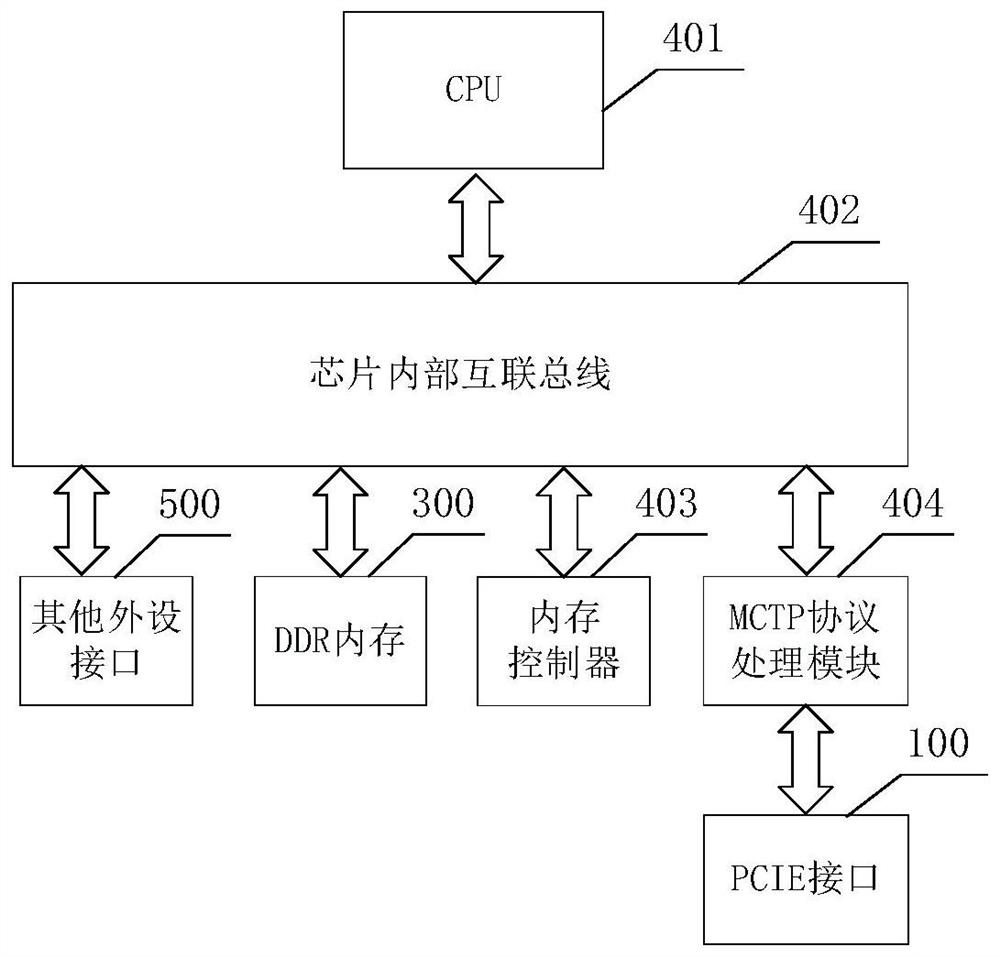

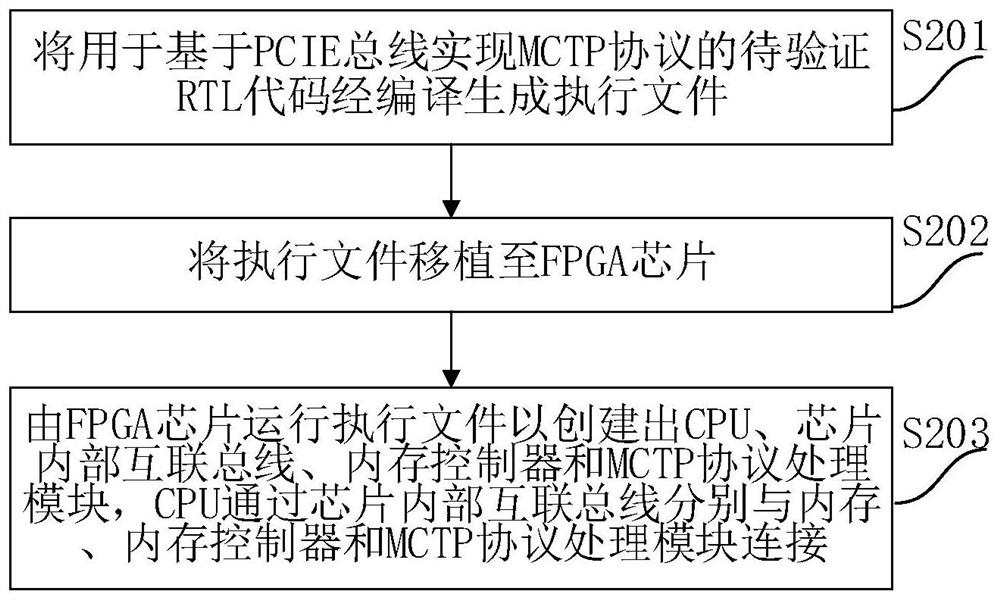

PendingCN113760748ASolve the problem that the timing of the chip cannot be evaluatedImprove the efficiency of functional verificationSoftware testing/debuggingData packComputer architecture

The invention discloses an FPGA prototype verification device and method. The device comprises a PICE interface, a clock module, a memory and an FPGA chip which are arranged on a board card. The method comprises the steps that a to-be-verified RTL code used for achieving an MCTP based on a PCIE bus is compiled to generate an execution file; the execution file is transplanted to the FPGA chip; the FPGA chip creates a CPU, a chip internal interconnection bus, a memory controller and an MCTP processing module by running the execution file, wherein the CPU is connected with the memory and the MCTP processing module through the chip internal interconnection bus; and then MCTP data packet receiving and transmitting verification between the CPU and a test host is carried out through the PCIE interface. According to the invention, a software and hardware verification platform is provided for realizing the MCTP by adopting the PCIE bus, time to market of a product is accelerated, and the research and development cycle of the product is shortened.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

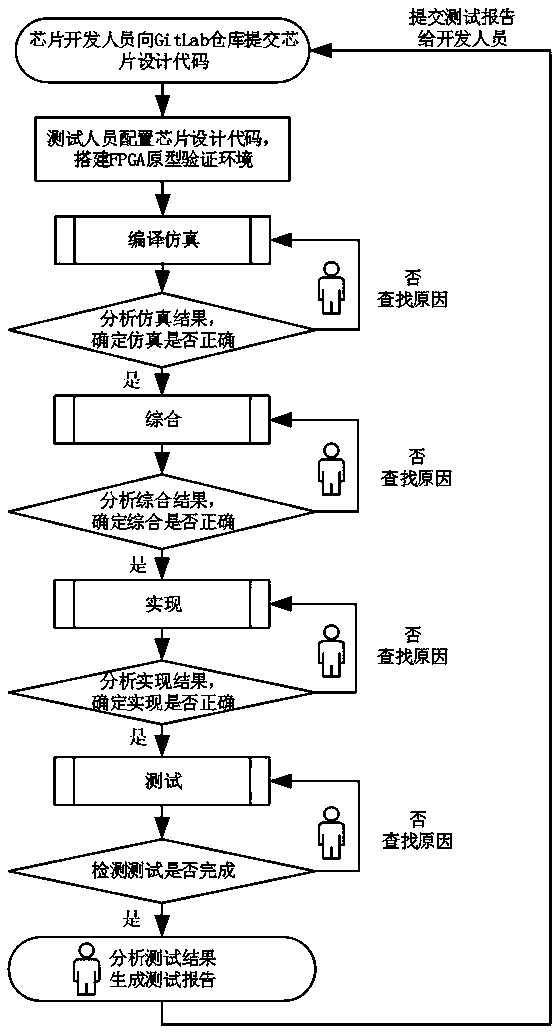

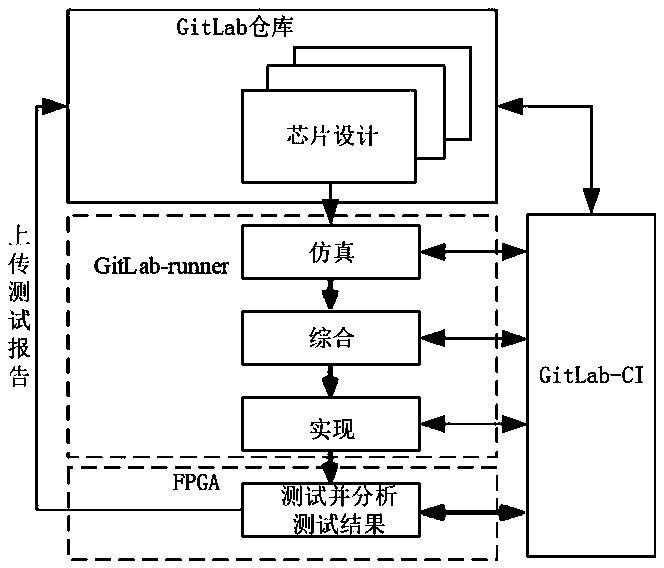

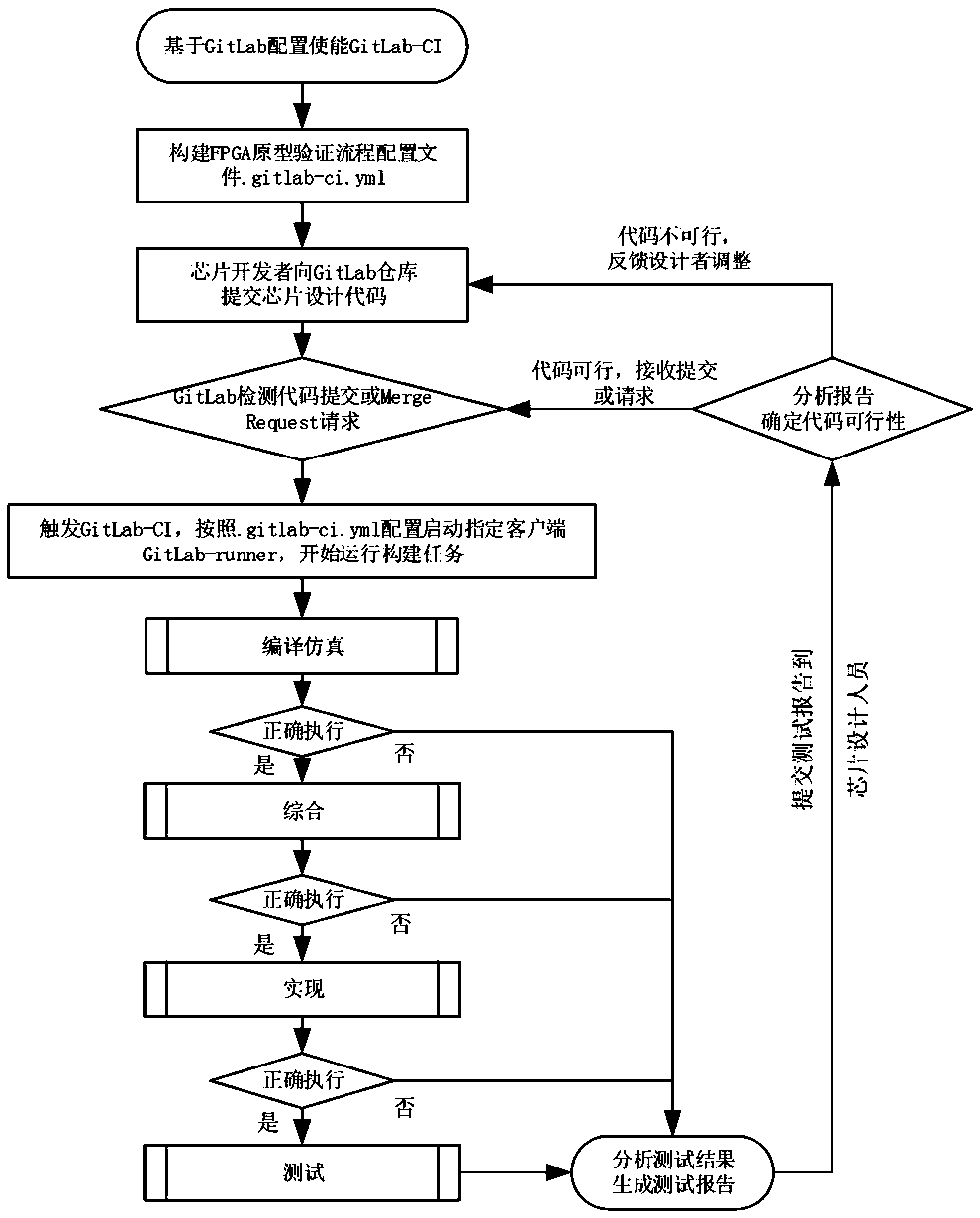

FPGA prototype automatic verification method and system based on GitLab-CI

ActiveCN109101680AImprove efficiencyReduce manpowerCAD circuit designSpecial data processing applicationsContinuous integrationValidation methods

The invention discloses a method and system based on GitLab-CI FPGA prototype automatic verification, the invention adopts a GitLab-CI continuous integration mode, the process of compiling and simulating, synthesizing, realizing, testing, analyzing and submitting test report in the verification process of FPGA prototype is processed automatically. The system includes computer systems, including interconnected GitLab repositories, triggering the continuous integration tool GitLab-CI and at least one client GitLab-Runner. An FPGA board is connected to the client GitLab- runner through a networkinterface. The invention can automatically realize the process of chip code compilation and simulation, synthesis, realization, test, analysis of test result and submission of test report, etc., and has the advantages of reducing waste of manpower and energy and improving the efficiency of prototype verification work.

Owner:PHYTIUM TECH CO LTD

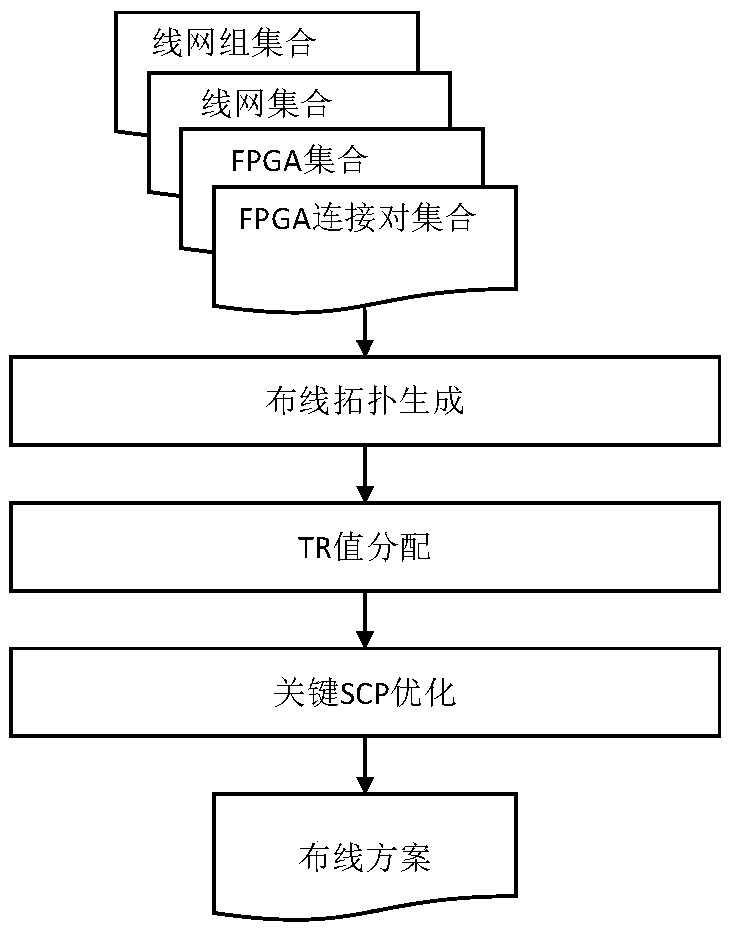

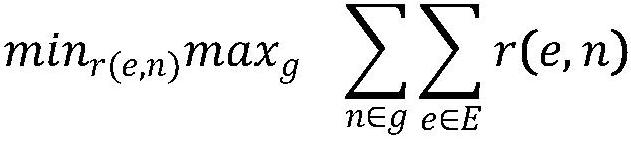

Multi-stage FPGA wiring method for optimizing time division multiplexing technology

ActiveCN111310409AOptimizing Latency OptimizingOptimize inter-chip signal delayMachine learningComputer aided designFPGA prototypeTime-division multiplexing

The invention relates to a multi-stage FPGA (Field Programmable Gate Array) wiring method for optimizing a time division multiplexing technology. The multi-stage FPGA wiring method comprises the following steps: S1, acquiring an FPGA set, an FPGA connection pair set, a wire network set and a wire network set; S2, according to the FPGA set, the FPGA connection pair set, the wire network set and thewire network set, obtaining the wiring topology of the wire network under the condition that TR is not allocated; S3, allocating a corresponding TR to each edge of each wire network according to different time delay conditions of each wire network group; and S4, circularly carrying out TR reduction and edge legalization, iteratively optimizing the wire network group of which the TR value is greater than a preset value, and obtaining an optimal wiring scheme until an iteration termination condition is met. According to the invention, the problems of inter-chip signal delay and wiring of a multi-FPGA prototype system can be optimized.

Owner:FUZHOU UNIV

FPGA prototype verification development board segmentation simulation system and method, medium and terminal

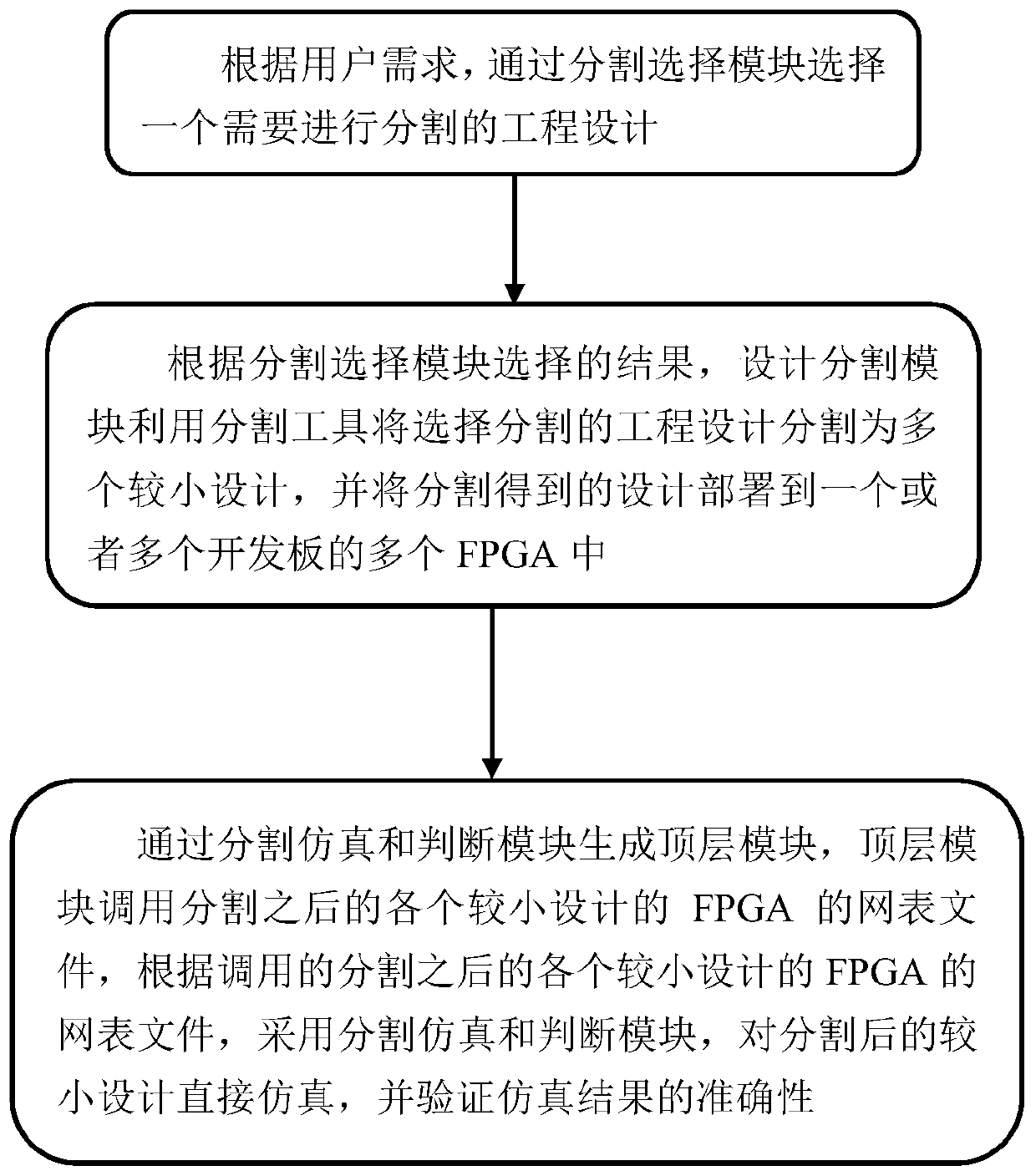

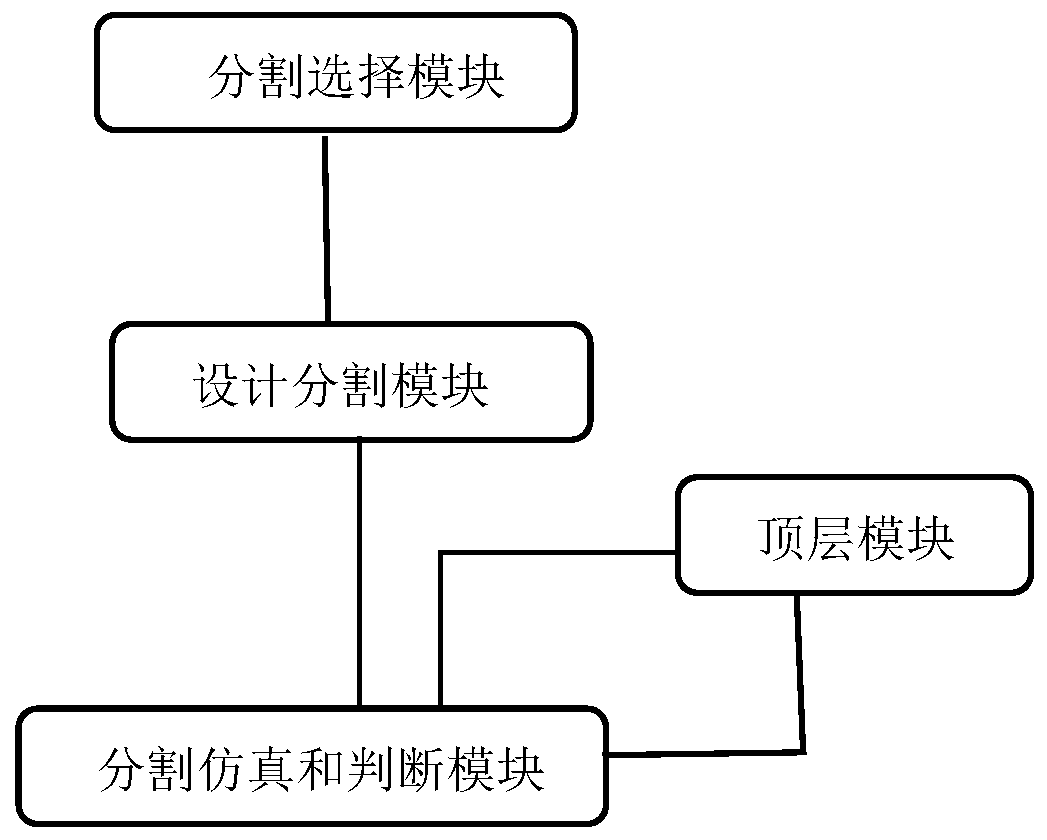

PendingCN110941934ASpeed up the development processComputer aided designSpecial data processing applicationsComputer architectureEngineering

The invention discloses an FPGA prototype verification development board segmentation simulation system and method, a medium and a terminal, and the system comprises: a segmentation selection module which is used for selecting an engineering design needing to be segmented according to the demands of a user; a design segmentation module which is used for segmenting the engineering design selected to be segmented into a plurality of smaller designs by utilizing a segmentation tool according to a result selected by the segmentation selection module, and deploying the designs obtained by segmentation into a plurality of FPGAs of one or more development boards; a top layer module which is used for calling the segmented netlist files of the FPGAs with the small designs; a segmentation simulationand judgment module which is used for generating the top layer module , directly simulating the partitioned small design according to the netlist file called by the top layer module, verifying the accuracy of a simulation result. The running state of the design can be confirmed in a partitioning design and simulation mode for the large engineering design, and therefore a user can conveniently conduct large-capacity and high-complexity engineering design.

Owner:S2C

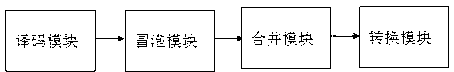

Message filtering system and message filtering method of high-speed interconnection bus

The invention discloses a message filtering system and a message filtering method of a high-speed interconnection bus. The message filtering system comprises a decoding module, a bubbling module connected with the decoding module, a combining module connected with the bubbling module and a converting module connected with the combining module. By the aid of the message filtering system of the high-speed interconnection bus, data transmitted on the high-speed interconnection bus are decoded, effective data messages are kept, invalid information in the data is filtered, and a data stream after filtering is subjected to clock domain conversion by means of asynchronous FIFO (first in first out) and further is converted from a high-frequency clock domain of the high-speed interconnection bus to a lower-frequency clock domain of an FPGA (field programmable gate array) chip core logic, so that requirements on frequency and resources are lowered, the problem about limitation of an FPGA verification system is solved, and design flexibility of the high-speed interconnection bus is improved. By means of reducing risks and difficulty of an FPGA prototype system, a product verification cycle is shortened, and the success rate of chip putting is increased.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

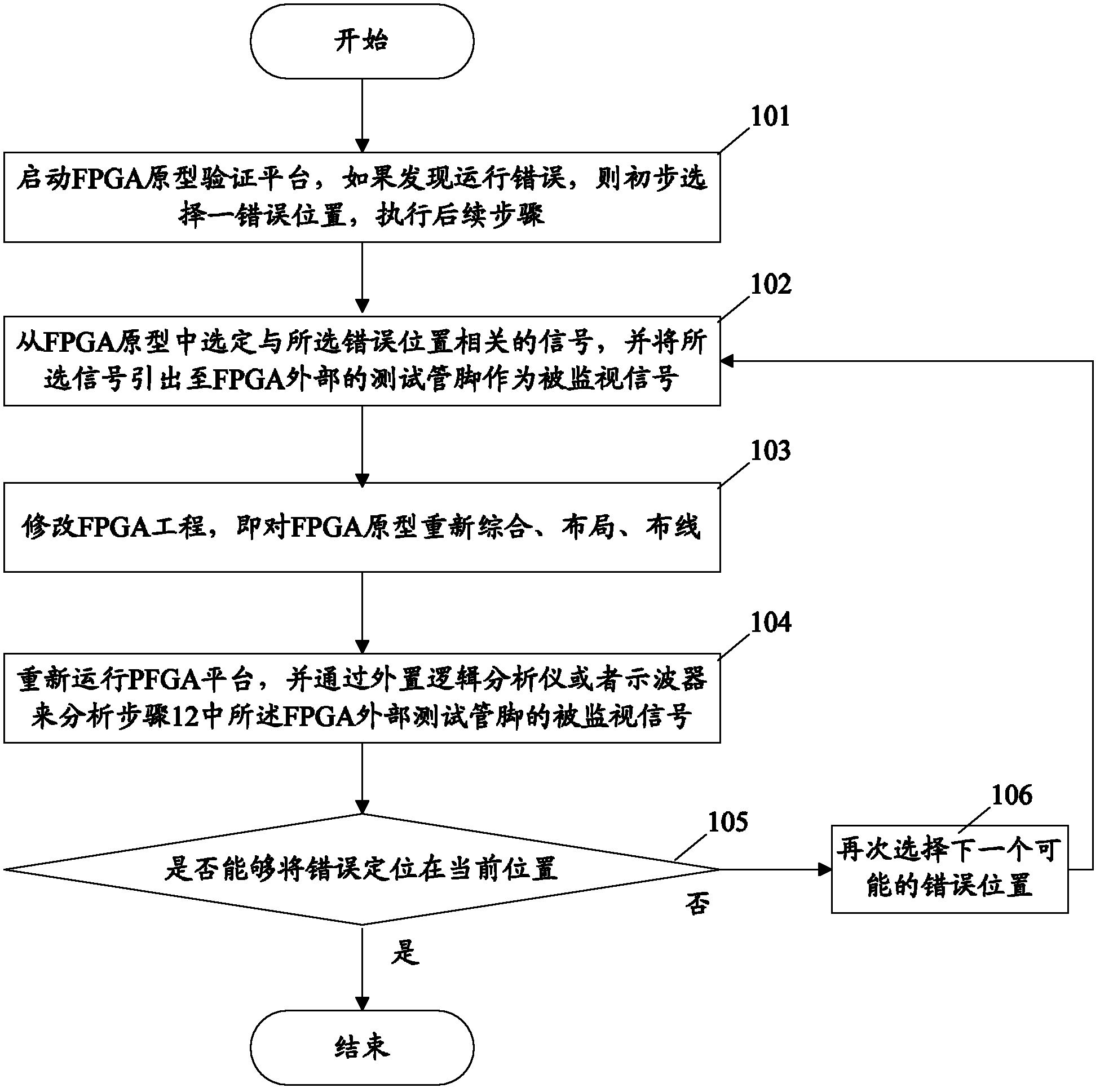

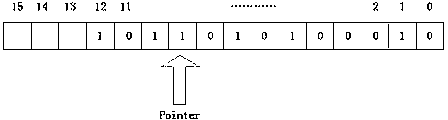

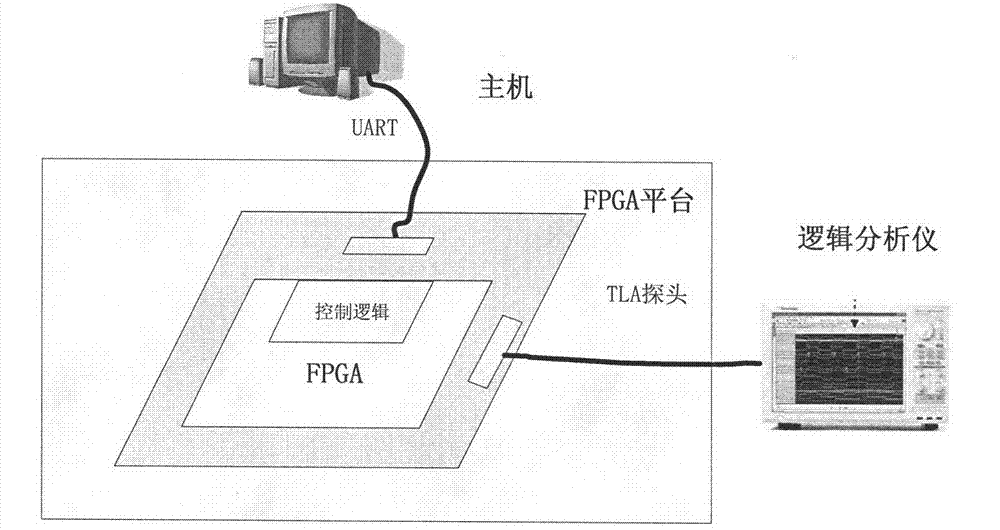

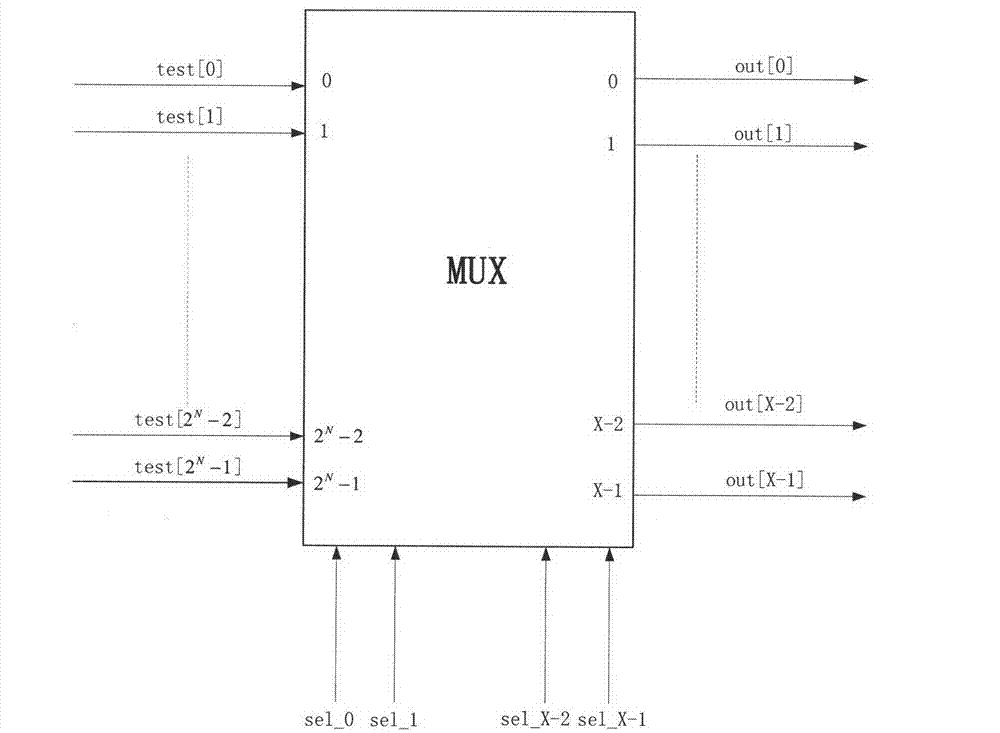

Debugging method for large-scale field programmable gate array (FPGA) design

The invention provides a debugging method for large-scale field programmable gate array (FPGA) design, and mainly aims to provide a relatively general debugging method. By the debugging method, the time of debugging an FPGA prototype is saved, and the efficiency of debugging the FPGA prototype is improved. The main theory is that a redundant control logic is designed; and a main machine end configures a corresponding register of the control logic through operation of a universal asynchronous receiver / transmitter (UART), so that an external test pin is selectively connected to a signal to be tested in a certain FPGA chip. By the method, the structure is simple; the method is easy to implement; the external test pin can test a plurality of inner signals to be tested of the FPGA chips; and during test, the inner signals to be tested of certain FPGA chips can be freely selected, and the signals are not required to be grouped in advance.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

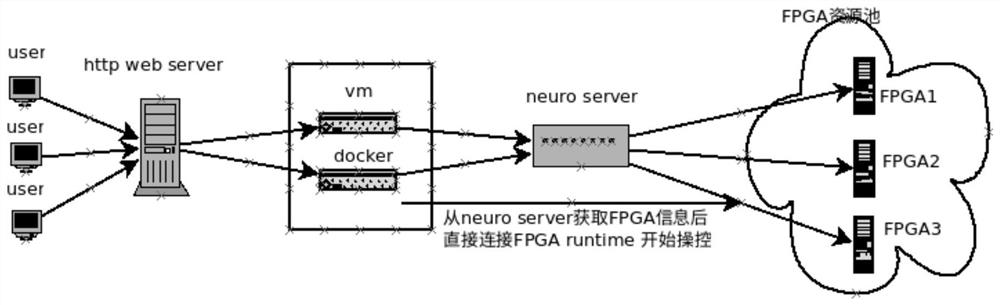

Cloud service platform system and method for FPGA prototype verification

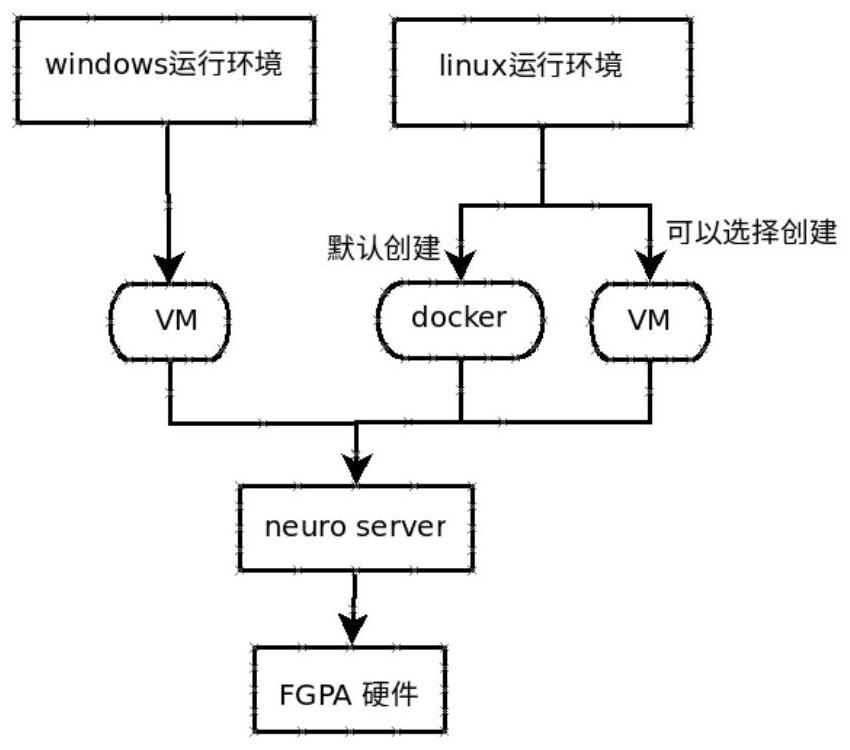

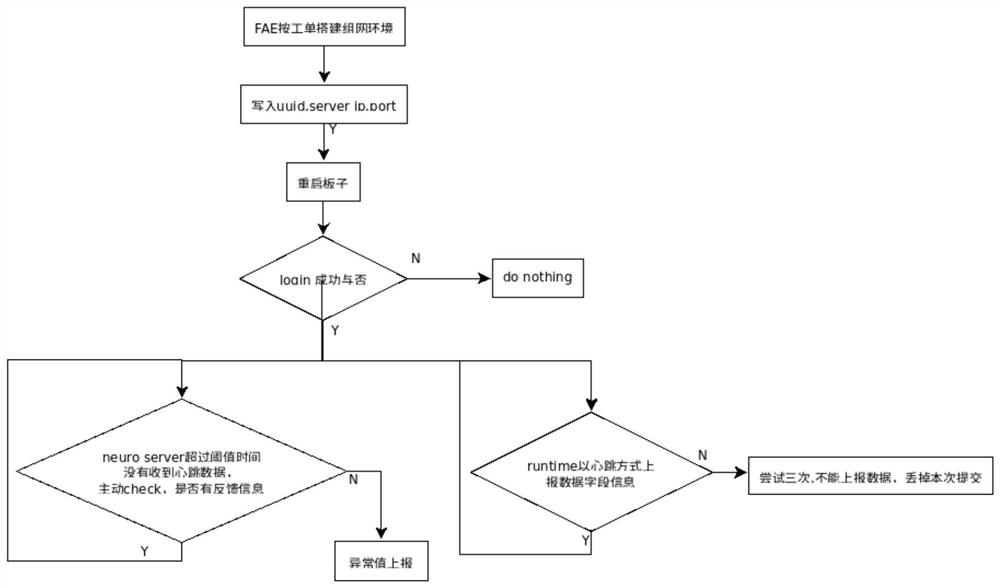

ActiveCN112181745AShort cycleReduce development costsDetecting faulty computer hardwareSoftware testing/debuggingFPGA prototypeMiddleware

The invention provides a cloud service platform system and method for FPGA prototype verification, and the system comprises a Web server unit, a VM virtual machine unit and a Neuro server unit which are in communication connection with one another, and the Web server unit is configured to provide a serial port for the remote operation of a user; the VM virtual machine unit is configured to providean os carrier for a user to operate FPGA equipment; the Neuro server unit is configured to manage FPGA resources and service communication credentials between each piece of FPGA equipment and the VMvirtual machine unit. A unified hardware platform and middleware are provided at the cloud, and the development and deployment cost of the accelerator can be greatly reduced.

Owner:S2C

FPGA prototype verification platform for digital micromirror device driving chip

ActiveCN111711804ARealize adaptive dynamic expansionEasy to usePicture reproducers using projection devicesComputer hardwareGate array

The invention discloses an FPGA prototype verification platform for a digital micromirror device driving chip. The platform comprises an FPGA programmable gate array ZYNQ subsystem, an FPGA programmable gate array Kintex subsystem, a capacitive touch screen, a daughter board part, a power supply part, a camera, a color wheel module, a UHP lamp module and a high-power LED module. High requirementsof chip verification can be met, and moreover, the platform is suitable for intelligent development of the projection market. According to the invention, self-adaptive dynamic expansion of hardware resources can be realized, and the platform can be applied to various occasions such as super-large-scale chip prototype verification, intelligent projection chip prototype verification, remote networkvideo projection chip prototype verification and the like. The platform has the advantages of being small in size, complete in function, excellent in performance, high in developability and the like,and easy, convenient and rapid use experience is brought to users.

Owner:EAST CHINA NORMAL UNIVERSITY

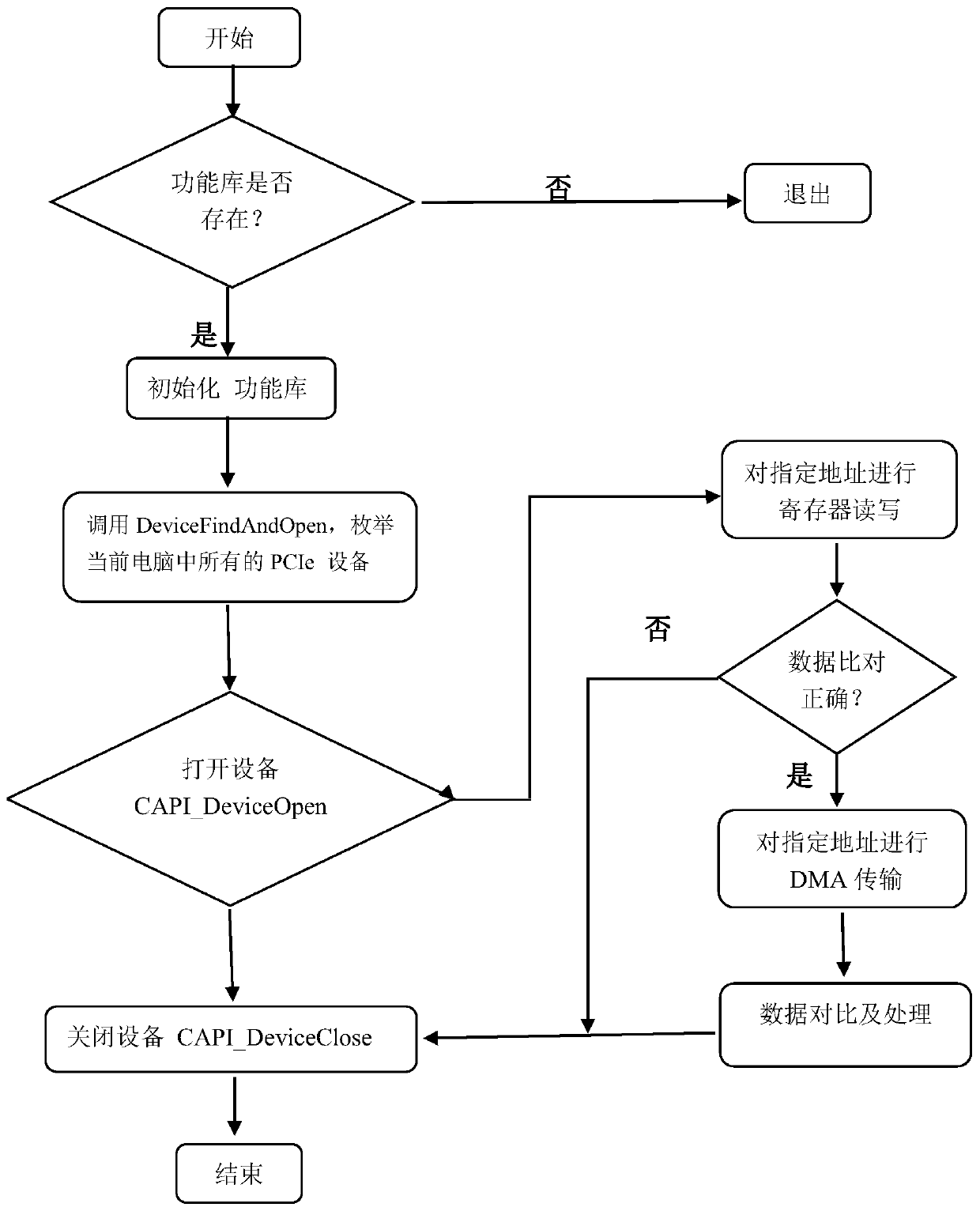

High-speed transmission method based on PCIE interface, storage medium and terminal

ActiveCN111045964AImprove test coverageAccelerate Design VerificationElectric digital data processingComputer hardwareEquipment finding

The invention discloses a high-speed transmission method based on a PCIE interface, a storage medium and a terminal, and the method comprises the steps: judging whether a function library exists in anFPGA prototype verification development board or not, and initializing the function library after judging that the function library exists; calling a device to search and open an interface, enumerating all PCIe devices in the current terminal, and opening an equipment CAPI; carrying out register reading and writing on the designated address, then, judging whether data comparison is correct or notaccording to a reading and writing result, if so, carrying out DMA transmission on the designated address, carrying out comparison and processing on the data, and then, turning off the equipment CAPI; and if the data comparison result is judged to be wrong, directly closing the equipment CAPI and stopping transmission, so that a large amount of data can be transmitted between a host and a prototype at a high speed, the real-time test is approached, the user design can be executed at a hardware speed, the design verification is accelerated, the test coverage of FPGA prototype verification is increased, and the problems proposed in the background technology can be effectively solved.

Owner:S2C

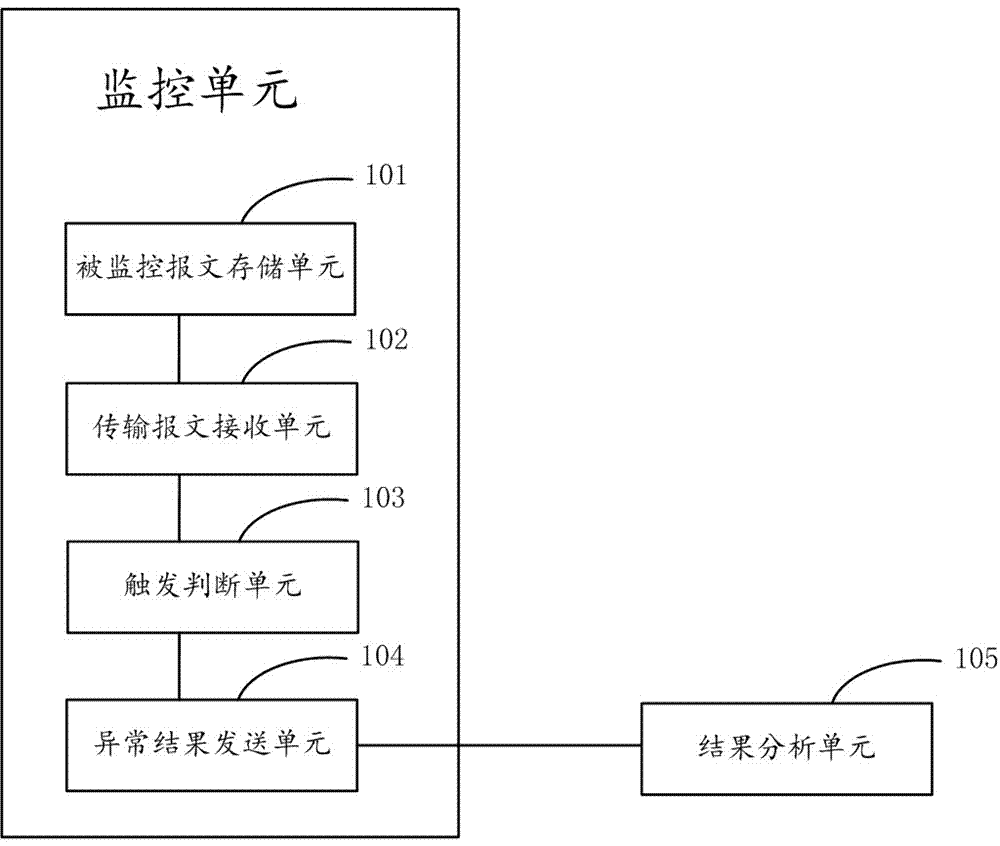

Device and method for increasing FPGA prototype verification efficiency

ActiveCN106919748AImprove verification efficiencyQuick analysisCAD circuit designSpecial data processing applicationsComputer hardwareFPGA prototype

The invention relates to the technical field of chip prototype verification and especially relates to a device and method for increasing FPGA prototype verification efficiency. The invention discloses a device for increasing the FPGA prototype verification efficiency. The device comprises a monitoring unit. The monitoring unit further comprises a monitored message storage unit, a transmission message receiving unit, a trigger judgment unit and an abnormal result sending unit, wherein the monitored message storage unit is used to store contents of a monitored message; the transmission message receiving unit is used to receive and read a transmission message from an NC chip; and the trigger judgment unit is used to judge whether contents of the transmission message are consistent with the contents of the monitored message. The invention also discloses a method for increasing the FPGA prototype verification efficiency. By the invention, a chip design department can analyze and position problems rapidly, and the verification efficiency of an FPGA prototype platform can be increased greatly.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

Design segmentation method for multiple FPGAs

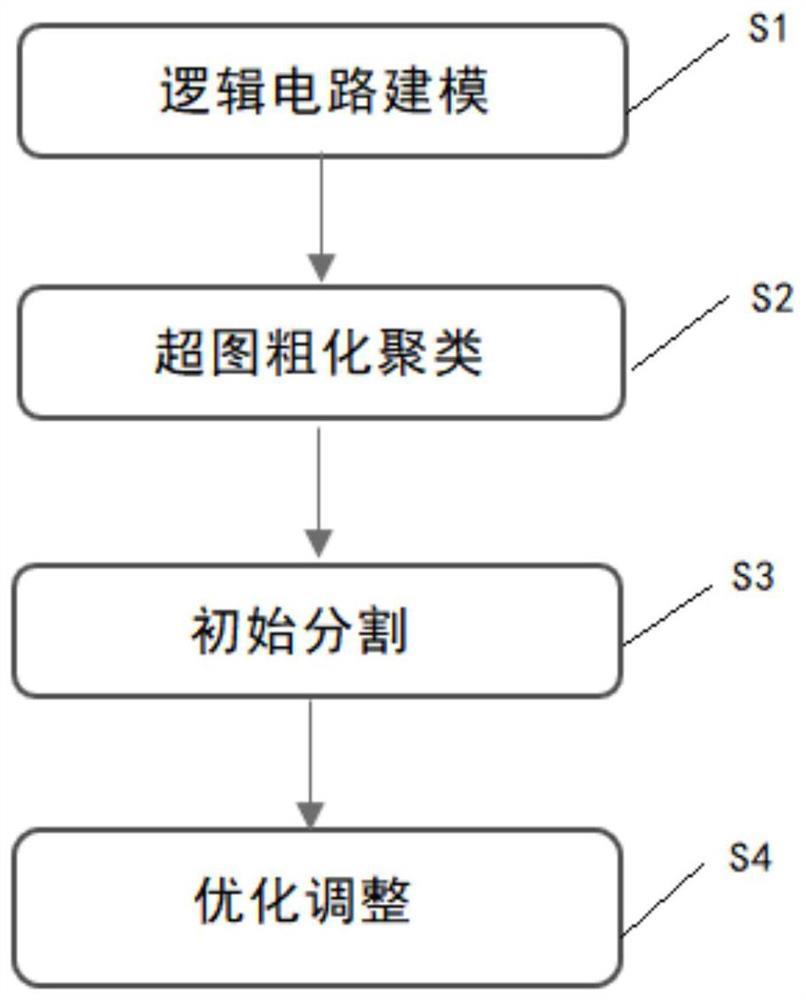

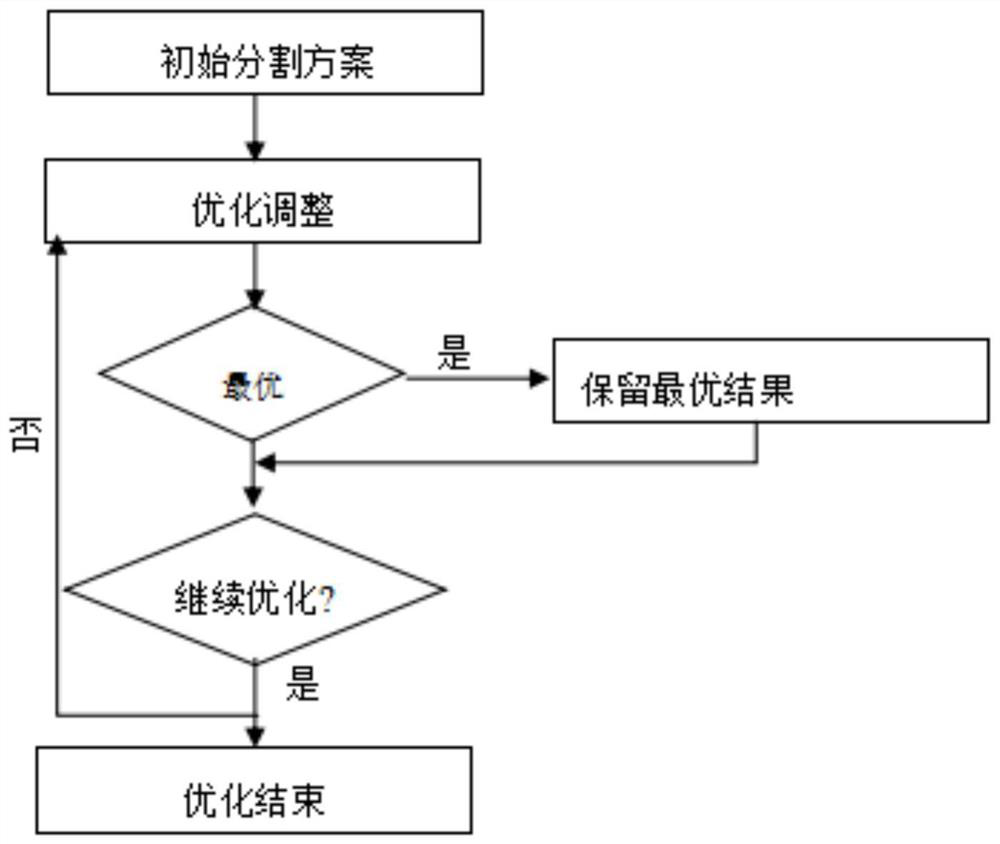

ActiveCN112183007AGood segmentation resultCAD circuit designConstraint-based CADGreedy algorithmHypergraph

The invention discloses a design segmentation method for multiple FPGAs, and relates to the technical field of chip logic design. The method comprises the steps that S1, a logic circuit is modeled into a hypergraph: configuring grouping interconnection size resources and cutting grouping balance factors S2, supergraph coarsening: aggregating closely connected vertexes together to construct a sub-graph; S3, initial segmentation: traversing clusters without a connection relationship by using a greedy algorithm rule according to the sizes of partitions and a cutting grouping balance factor of theclustered sub-graphs, and allocating the clusters to different partitions; and S4, optimization adjustment: calculating the movable vertex income according to an FM algorithm, performing adjustment,and optimizing the cutting size. An optimal segmentation result can be obtained under the condition that interconnection constraint rules among the FPGAs are met in the segmentation process of the multi-FPGA prototype system.

Owner:S2C

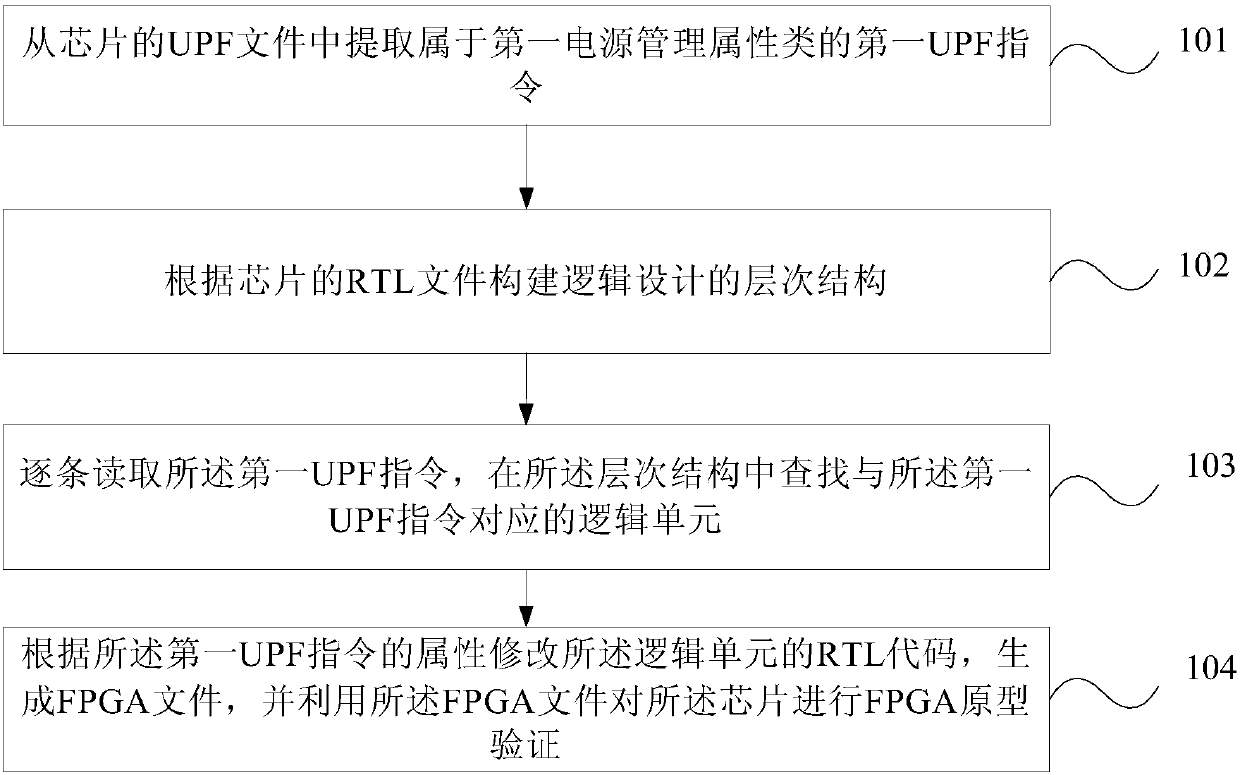

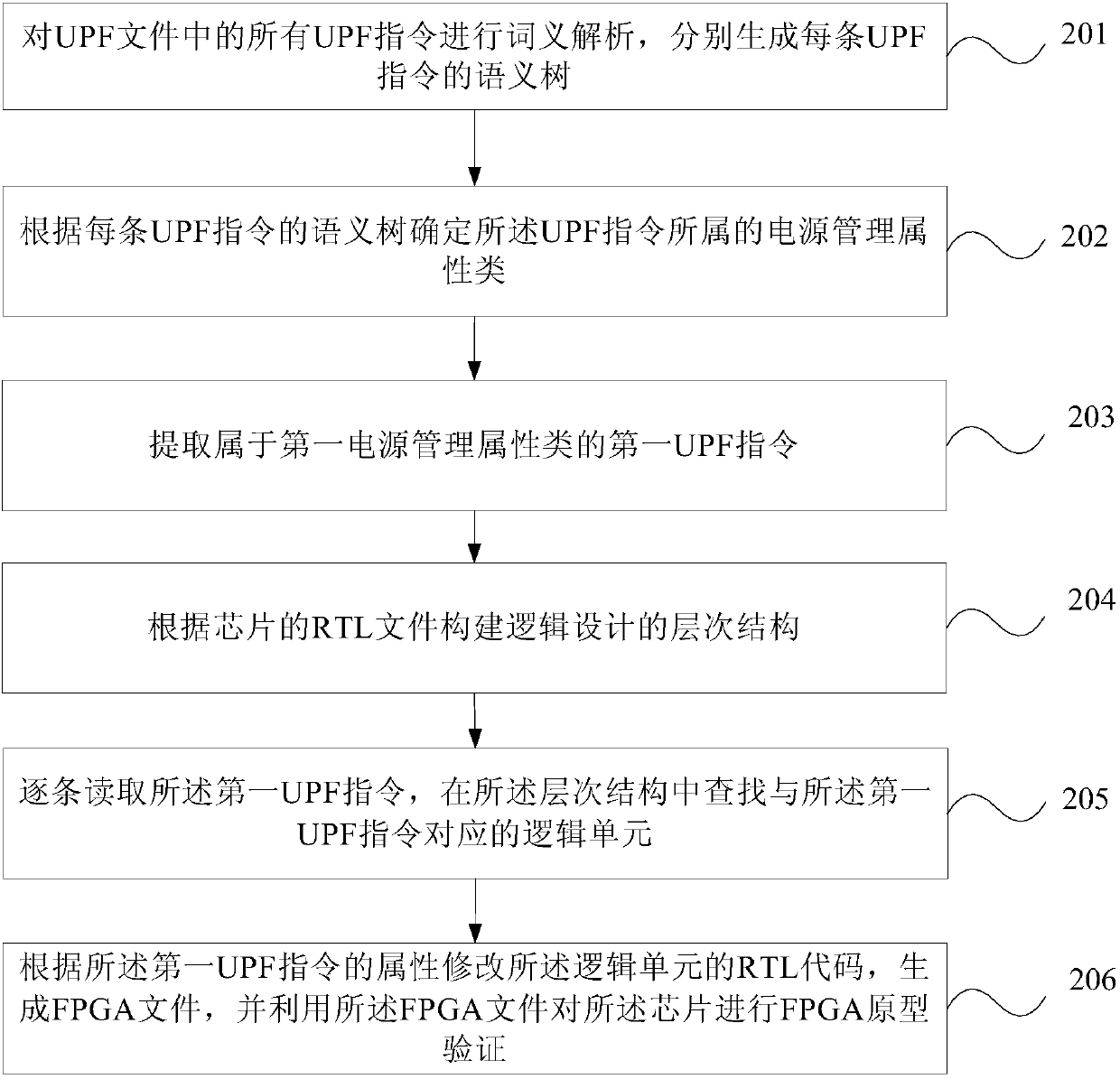

Method and device of FPGA (Field-Programmable Gate Array) prototype verification on chip

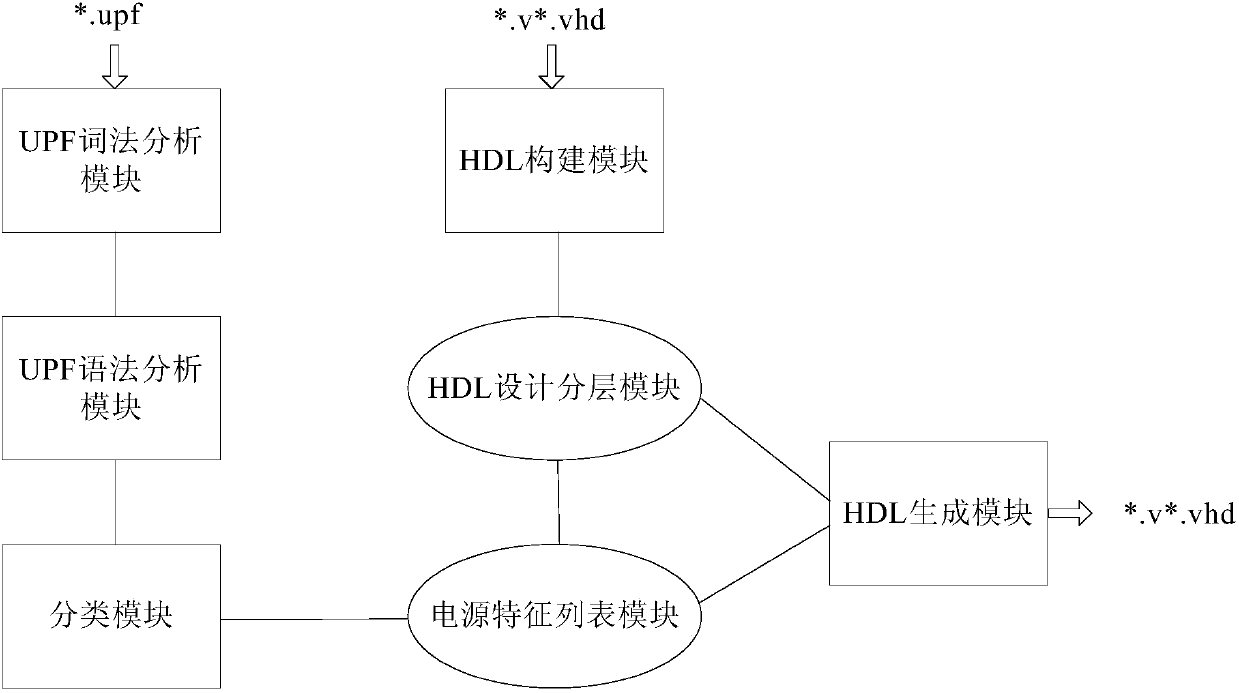

The embodiment of the invention provides a method and a device of FPGA (Field-Programmable Gate Array) prototype verification on a chip. The method of FPGA prototype verification on the chip of the invention includes: extracting first UPF (Unified Power Format) instructions, which belong to a first power management attribute class, from a UPF file of the chip; constructing a hierarchical structureof logic design according to an RTL (Register Transfer Level) file of the chip; reading the first UPF instructions one by one, and finding logic units, which correspond to the first UPF instructions,in the hierarchical structure; and modifying RTL code of the logic units according to attributes of the first UPF instructions, generating an FPGA file, and utilizing the FPGA file for FPGA prototypeverification on the chip. According to the embodiment of the invention, power management behaviors in an integrated circuit (IC) can be simulated on a conventional FPGA, logic behaviors of the FPGA are enabled to be consistent with the integrated circuit, and a valid reference basis is provided for chip design.

Owner:HISENSE VISUAL TECH CO LTD

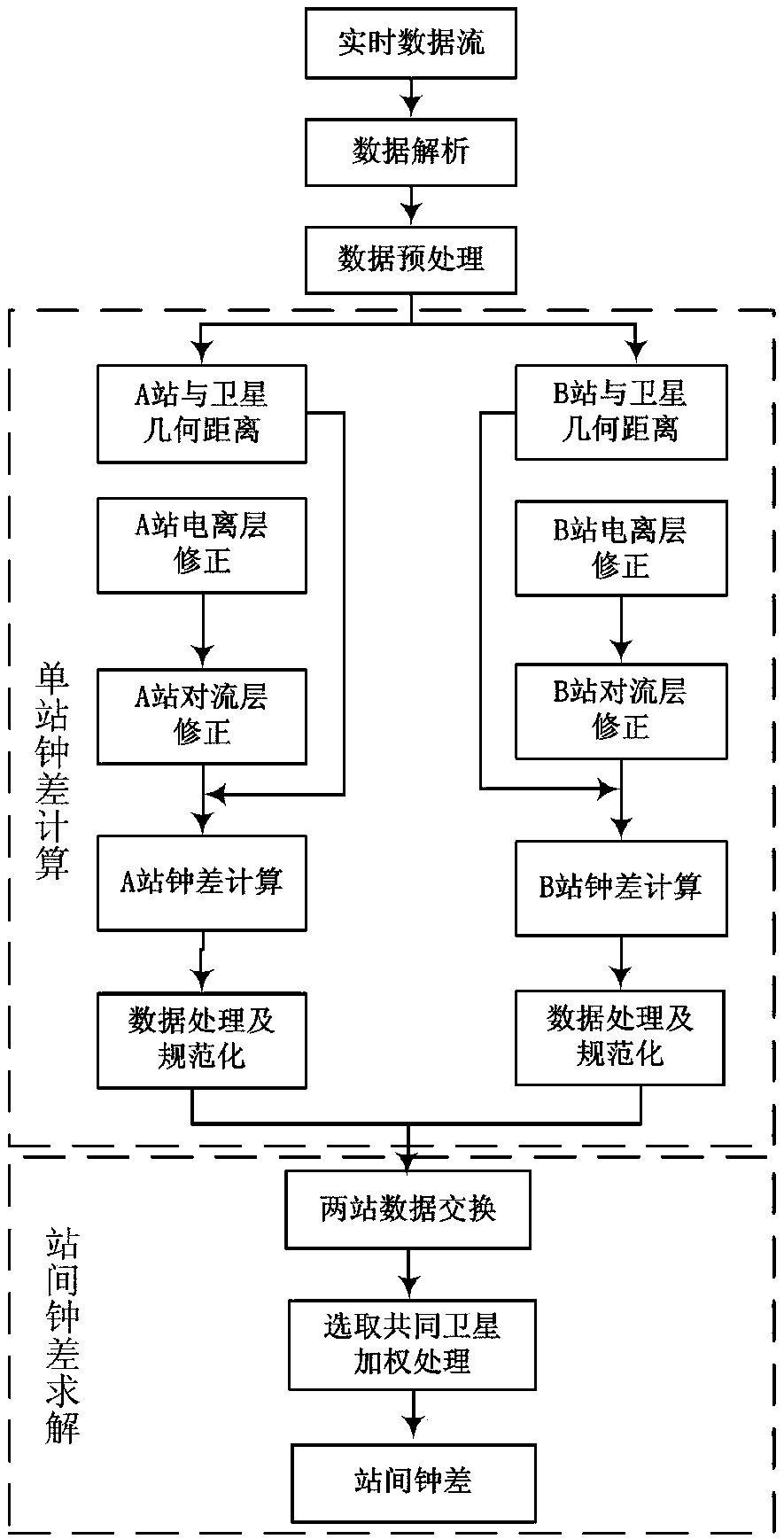

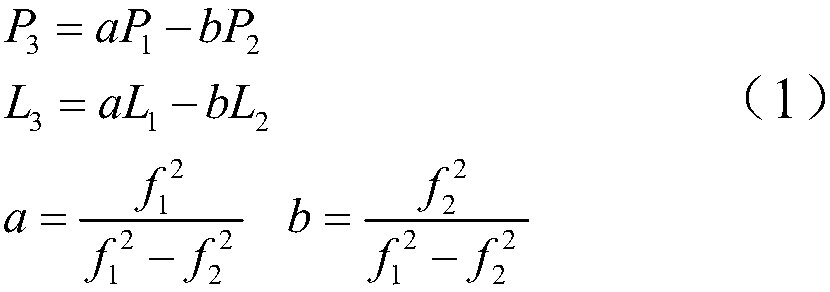

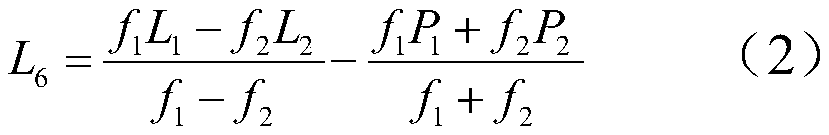

Embedded long distance real time GPS common view time comparison method

InactiveCN108680930ASolve the problem of time synchronization between different stationsSolve the modular problemSatellite radio beaconingFPGA prototypeDistance based

The invention aims to solve the long distance based GPS common view time comparison technical demands, and discloses an embedded long distance real time GPS common view time comparison method; based on a FPGA prototype board card, the method can embed a GPS common view time comparison algorithm into a DSP, thus realizing time comparison in real time; the main task contains GPS common view and single machine synergy; the method can ensure to stably output a clock error result without increasing operation complexity and space complexity, thus realizing inter-station time synchronization within thousands of kilometers.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

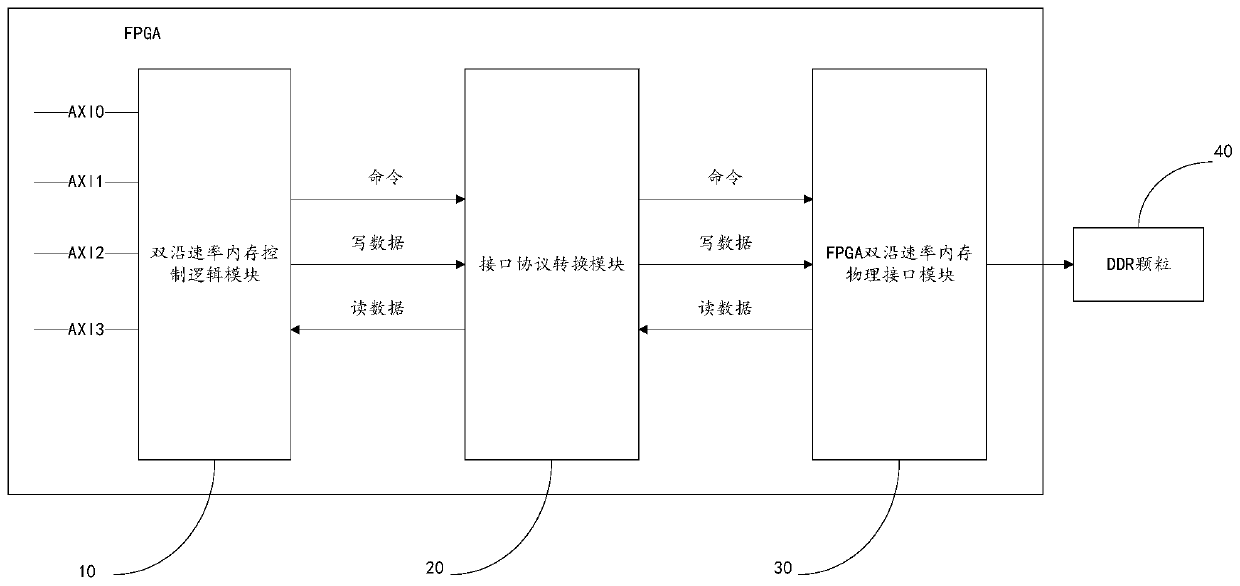

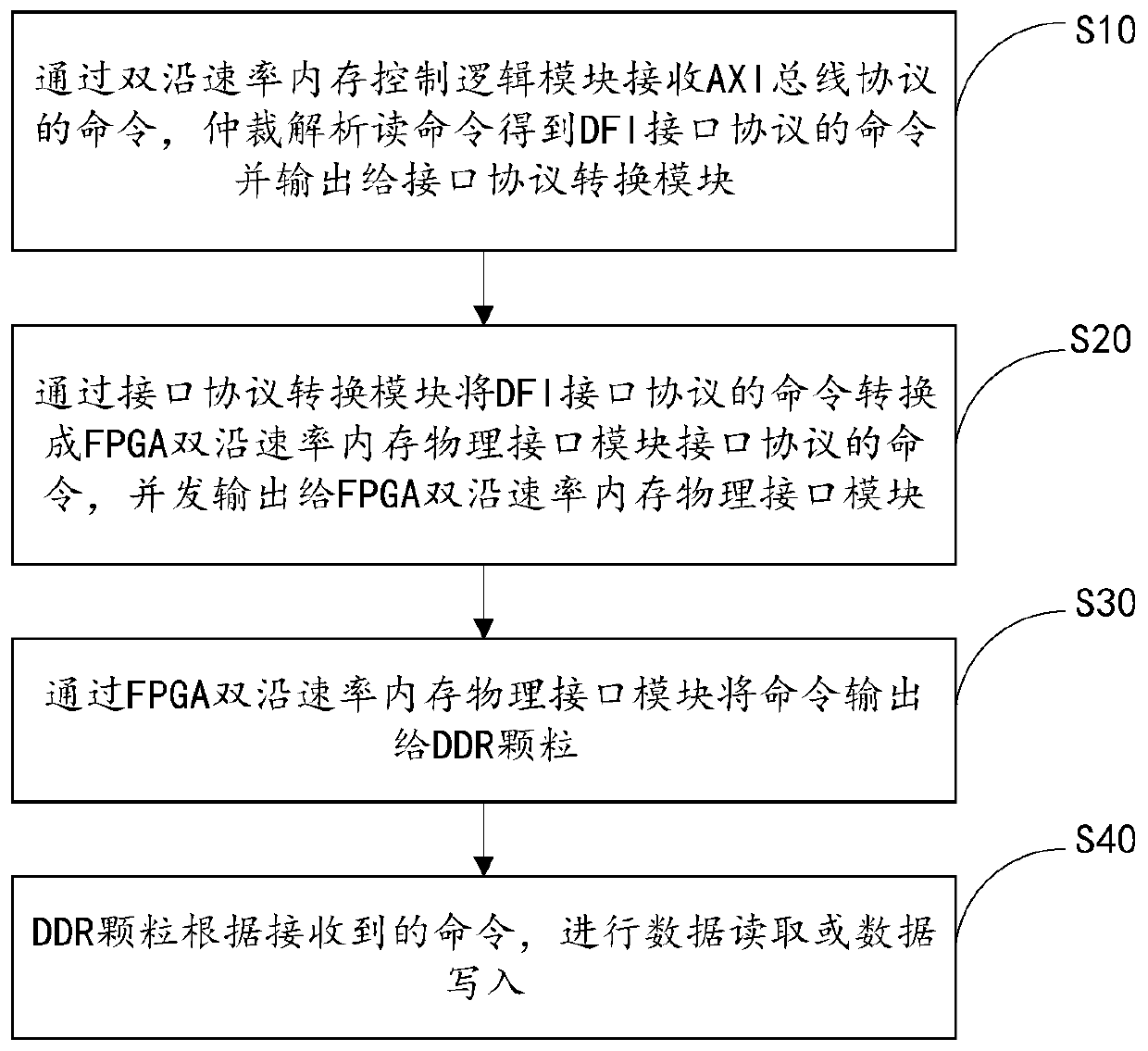

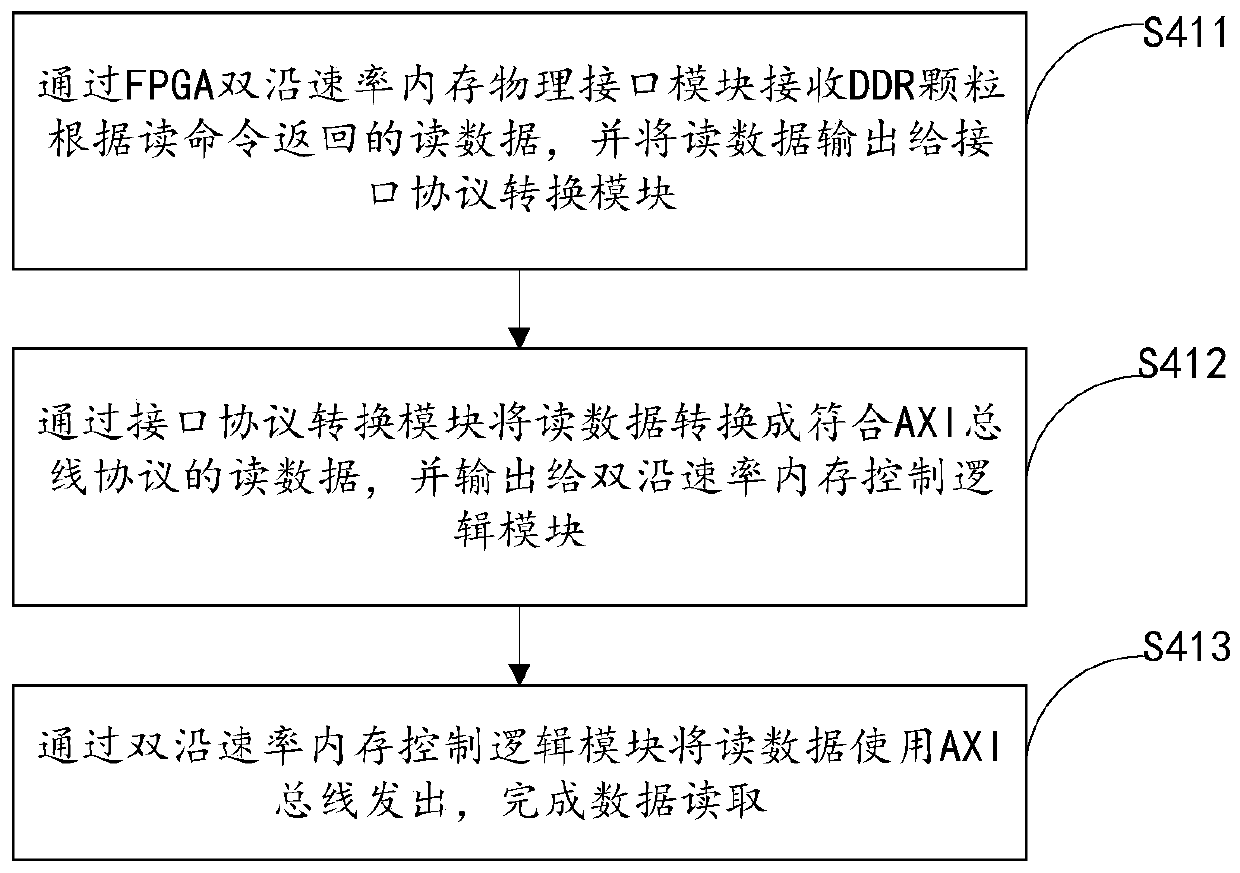

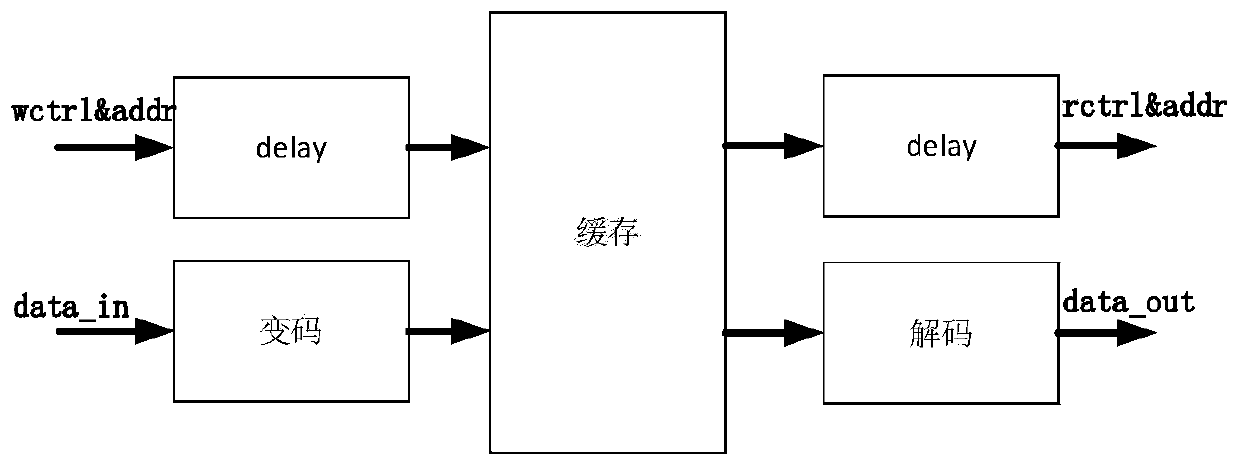

Device and method for verifying DDR by using FPGA prototype of SOC of solid state disk, computer equipment and storage medium

InactiveCN111475437AIncrease flexibilityLow costElectric digital data processingComputer architectureInterface protocol

The invention relates to a device and a method for verifying DDR by using an FPGA prototype of a SOC of a solid state disk, computer equipment and a storage medium. The device comprises the FPGA, wherein a double-edge-rate memory control logic module, an interface protocol conversion module and an FPGA double-edge-rate memory physical interface module are arranged in the FPGA, and DDR particles are connected to the FPGA double-edge-rate memory physical interface module; the double-edge-rate memory control logic module is used for outputting command data of a standard bus protocol consistent with the ASIC to the interface protocol conversion module; the interface protocol conversion module is used for converting the command data into command data of an interface protocol of the FPGA double-edge rate memory physical interface module and sending the command data; and the FPGA double-edge rate memory physical interface module is used for sending the received command data to the DDR particles. According to the device and the method, the FPGA double-edge-rate memory physical interface module sends the data to the DDR particles, the double-edge-rate memory control logic module of the ASICcan be verified on the FPGA, the flexibility is high, and the cost is lower.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

White box instrumentation FPGA prototype verification method for integrated circuit safety function

ActiveCN110865936AReduce the probability of false triggeringDoes not improve functionalitySoftware testing/debuggingCAD circuit designComputer hardwareComputer architecture

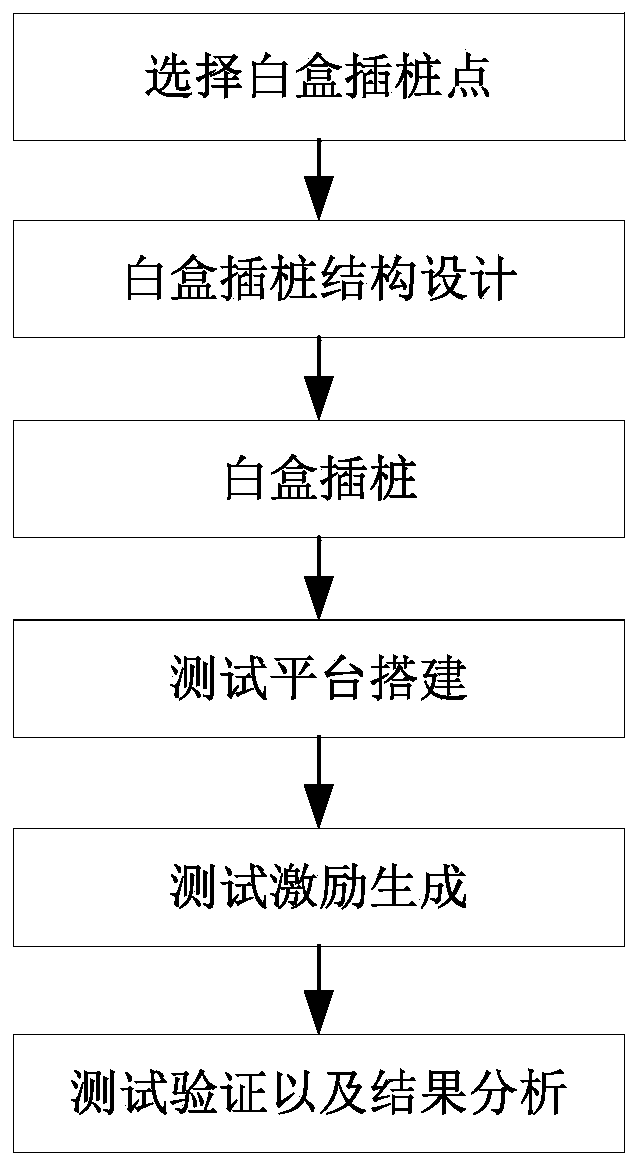

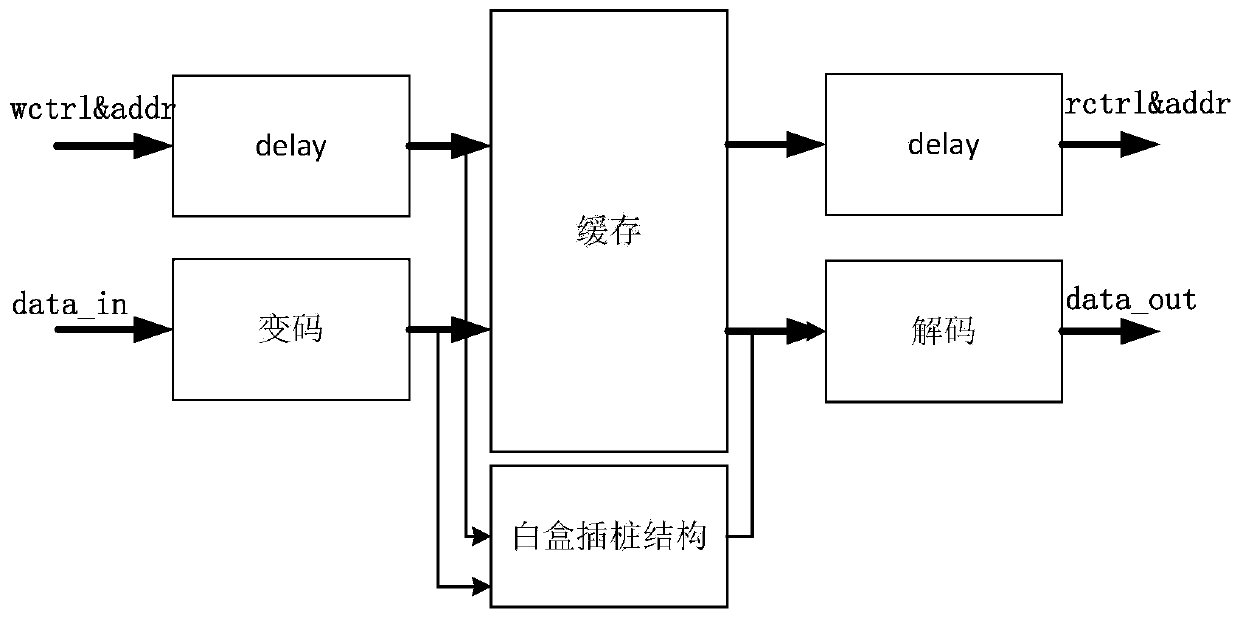

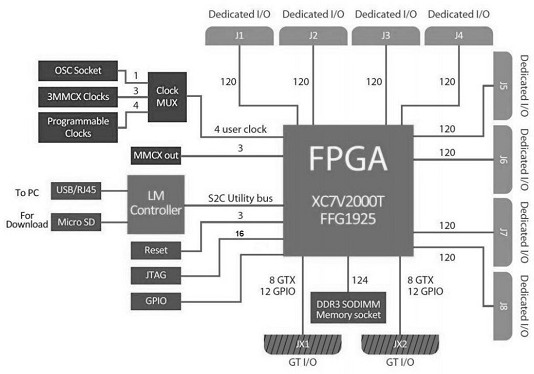

The invention belongs to the technical field of integrated circuit design verification, and discloses a white box instrumentation FPGA prototype verification method for an integrated circuit safety function. The white box instrumentation FPGA prototype verification method comprises the steps: 1, selecting a white box instrumentation point of an FPGA prototype verification system according to a logic structure of an integrated circuit safety function protection module; 2, designing a white box pile inserting structure; 3, inserting the designed instrumentation structure into a white box instrumentation point of an FPGA prototype verification system, and performing macro definition on the instrumentation structure at the white box instrumentation point; 4, building a test platform; 5, generating test excitation; and 6, injecting the test excitation into the built test platform, and performing test verification. According to the white box instrumentation FPGA prototype verification method, the instrumentation code can run on the FPGA prototype without influencing the functions of the RTL, and the security of the integrated circuit can be visually reflected, i.e., the defense effect for the instrumentation hardware Trojan horse, the vulnerability or the backdoor is achieved.

Owner:PLA STRATEGIC SUPPORT FORCE INFORMATION ENG UNIV PLA SSF IEU

SoC software and hardware collaborative verification system and method based on FPGA prototype

PendingCN114611445AAvoid designSpeed up the verification processComputer aided designSpecial data processing applicationsTest efficiencyComputer architecture

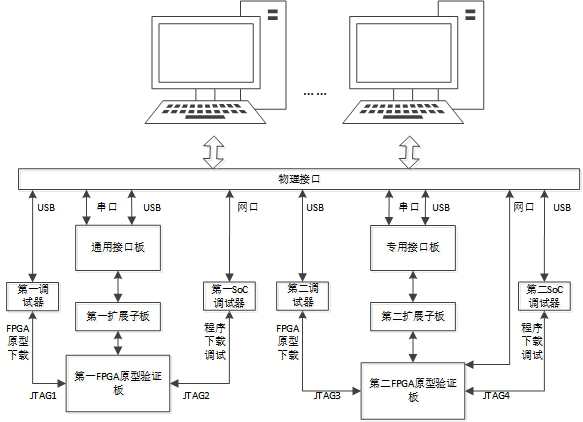

The invention discloses an FPGA prototype-based SoC software and hardware collaborative verification system and method. The system comprises a plurality of computers, at least a first set of FPGA prototype verification platform connected to the plurality of computers through physical interfaces, and at least a second set of FPGA prototype verification platform connected to the plurality of computers through physical interfaces. Two sets of FPGA prototype verification platforms are arranged, the high-performance SoC interface classification test operation is met, the first set of FPGA prototype verification platform is used for universal interface switching test verification, the second set of FPGA prototype verification platform is used for special interface switching test verification, a modular design thought is adopted, the cooperative verification method based on the FPGA prototype is improved, and the test efficiency is improved. The system and the method provided by the invention are high in reusability, repeated development of a plurality of systems is avoided, the verification progress before chip tape-out is greatly improved, and the integration time of software and hardware is shortened.

Owner:北京轩宇空间科技有限公司

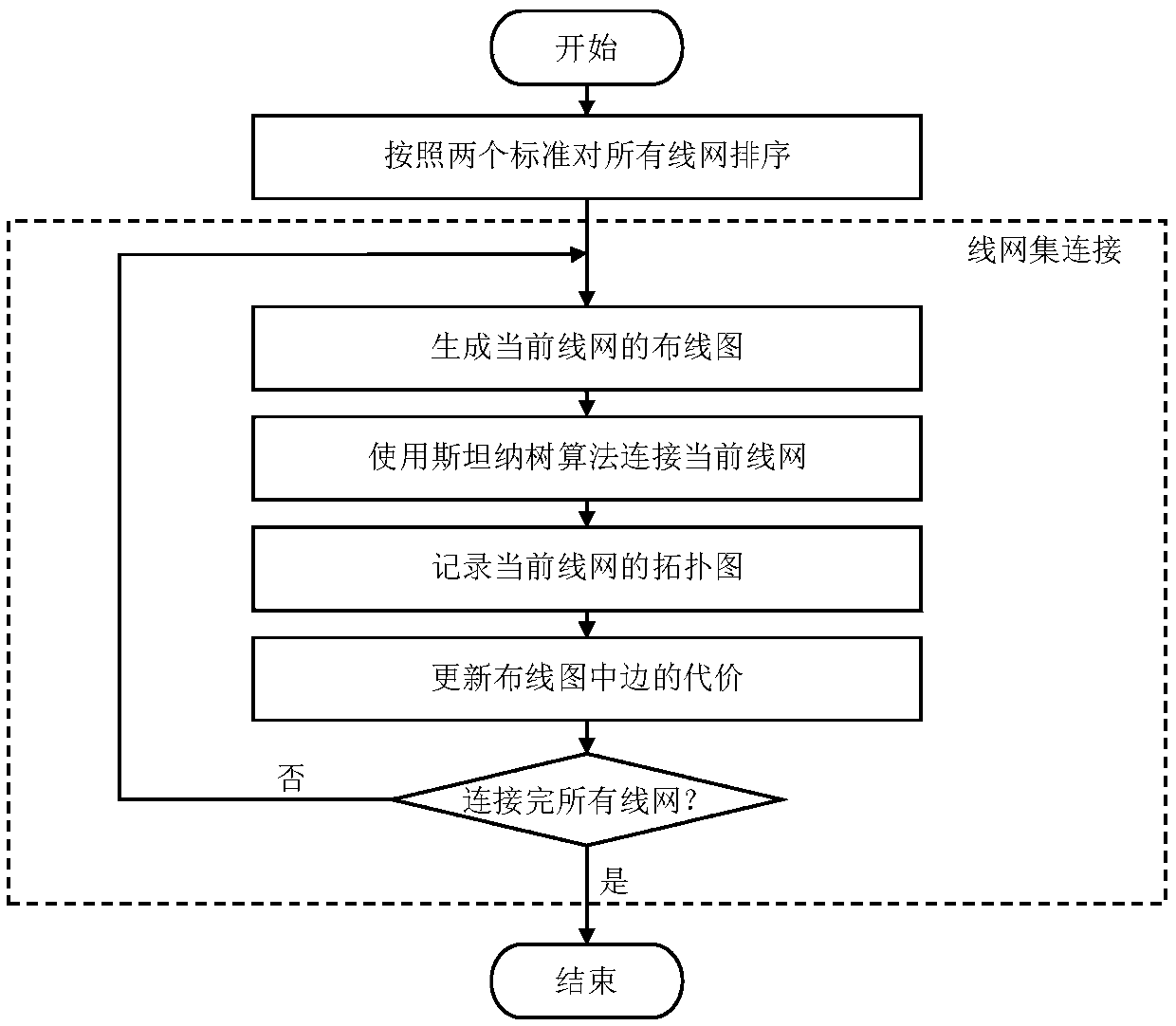

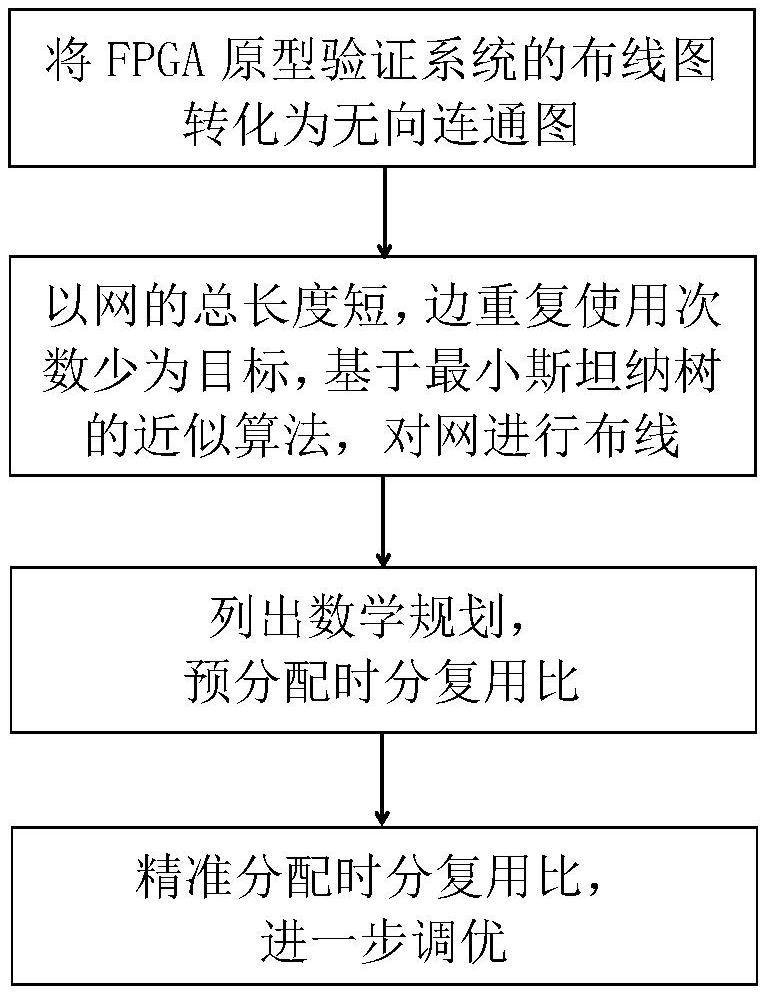

Wiring method of FPGA prototype verification system

PendingCN113392615AImprove performanceShorten the lengthConstraint-based CADSpecial data processing applicationsComputer hardwareWiring diagram

The invention discloses a wiring method of an FPGA prototype verification system. The wiring method comprises the following steps: converting a wiring diagram of the FPGA prototype system into an undirected connected diagram; taking the short total length of the network and the small number of times of repeated use of edges as targets, and performing wiring on the network based on an approximation algorithm of a minimum Steiner tree; according to the wiring condition and the constraint condition of the network, listing a mathematical plan, and pre-allocating a time division multiplexing ratio; accurately distributing the time division multiplexing ratio, and carrying out further tuning. According to the method, the FPGA prototype system can be successfully wired, and the group with the largest negative effect in all the groups is minimized, so that the system delay is greatly reduced, and the performance of the whole FPGA system is improved.

Owner:NANJING NORMAL UNIVERSITY

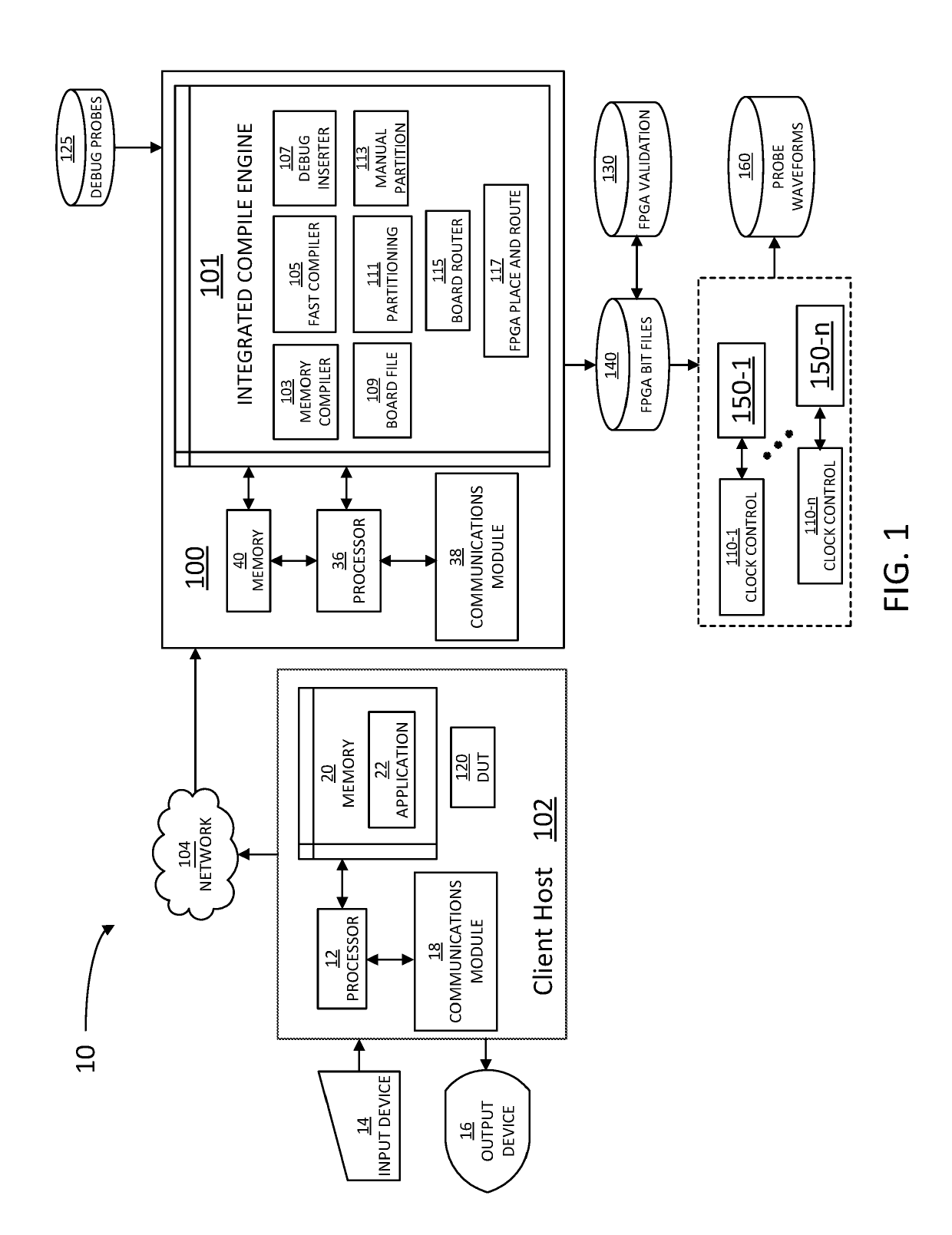

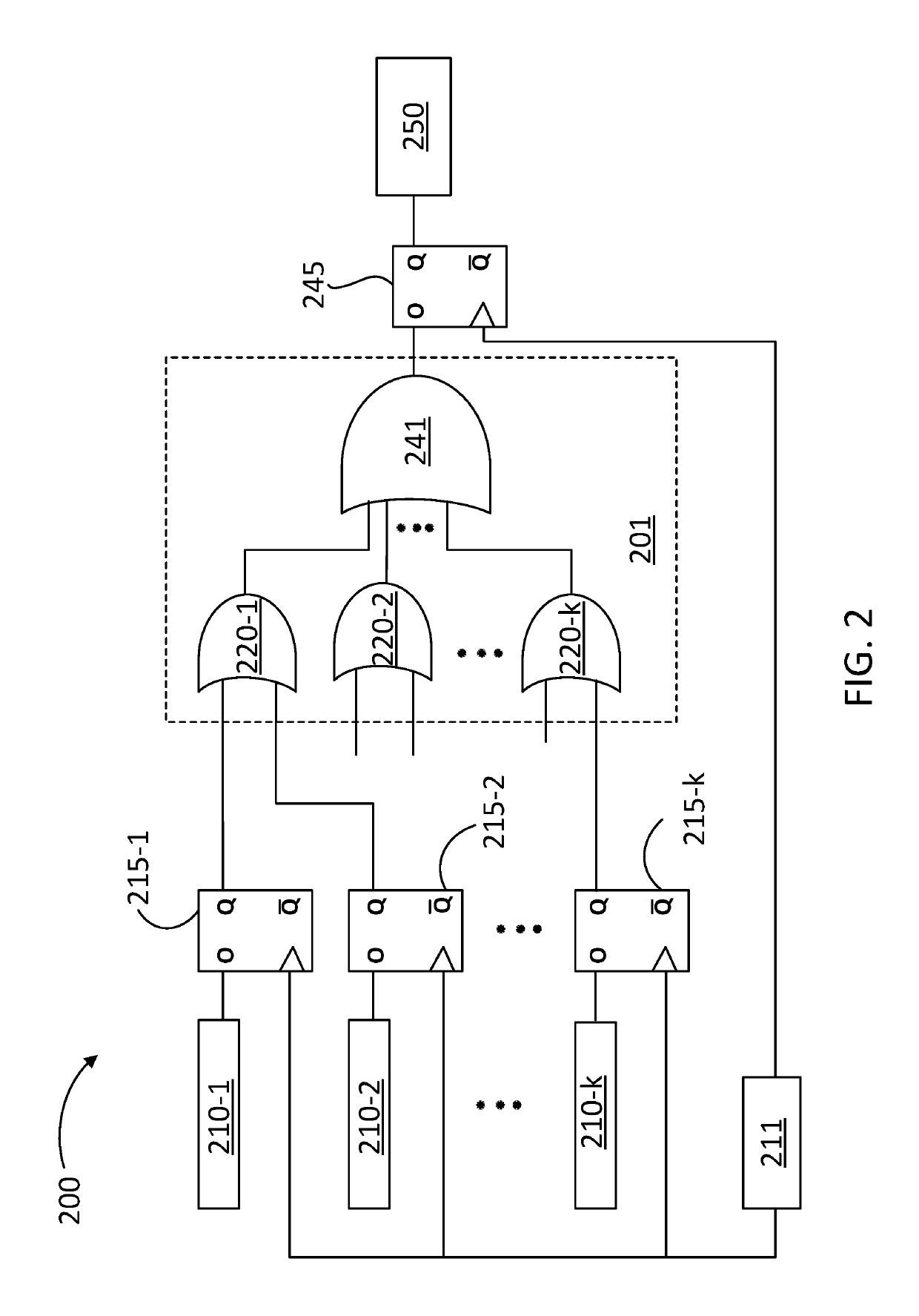

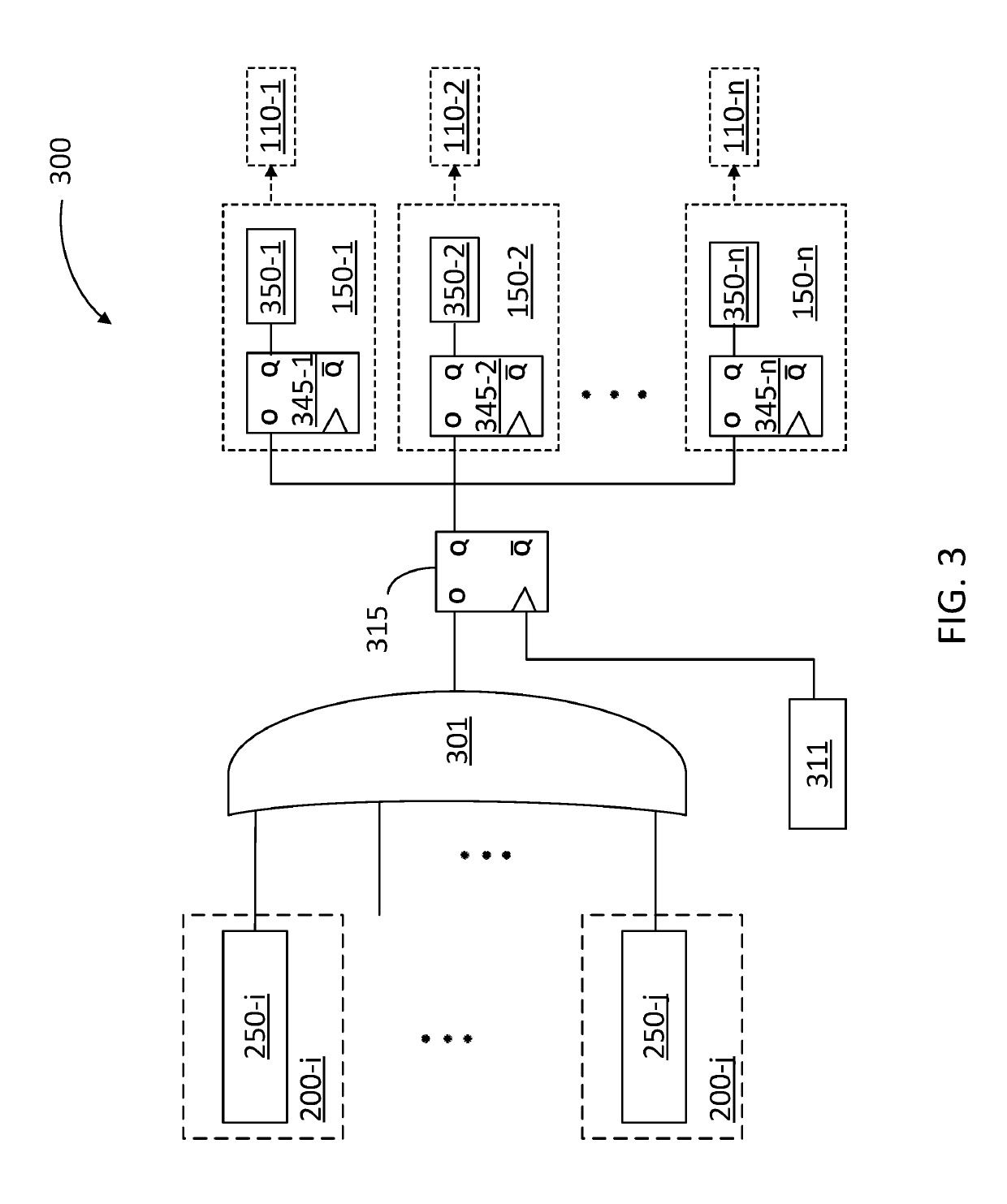

Support for multiple user defined assertion checkers in a multi-FPGA prototyping system

ActiveUS10489534B1Accurate conditionCAD circuit designSpecial data processing applicationsComputer architectureControl signal

A method is provided that includes selecting an assertion checker for a design under test. The design under test includes hardware and firmware for a system on a chip, the method including instantiating the assertion checker in a compilation file, annotating the compilation file to define an assertion control signal for the assertion checker, and selecting one of a DISABLE or an ENABLE definition for the assertion control signal. The method also includes configuring a clock in a prototyping platform to stop when the assertion control signal is enabled in the assertion checker and a logic condition for the assertion control signal is satisfied in the prototyping platform. A system and a computer readable medium including instructions to perform the above method are also provided.

Owner:CADENCE DESIGN SYST INC

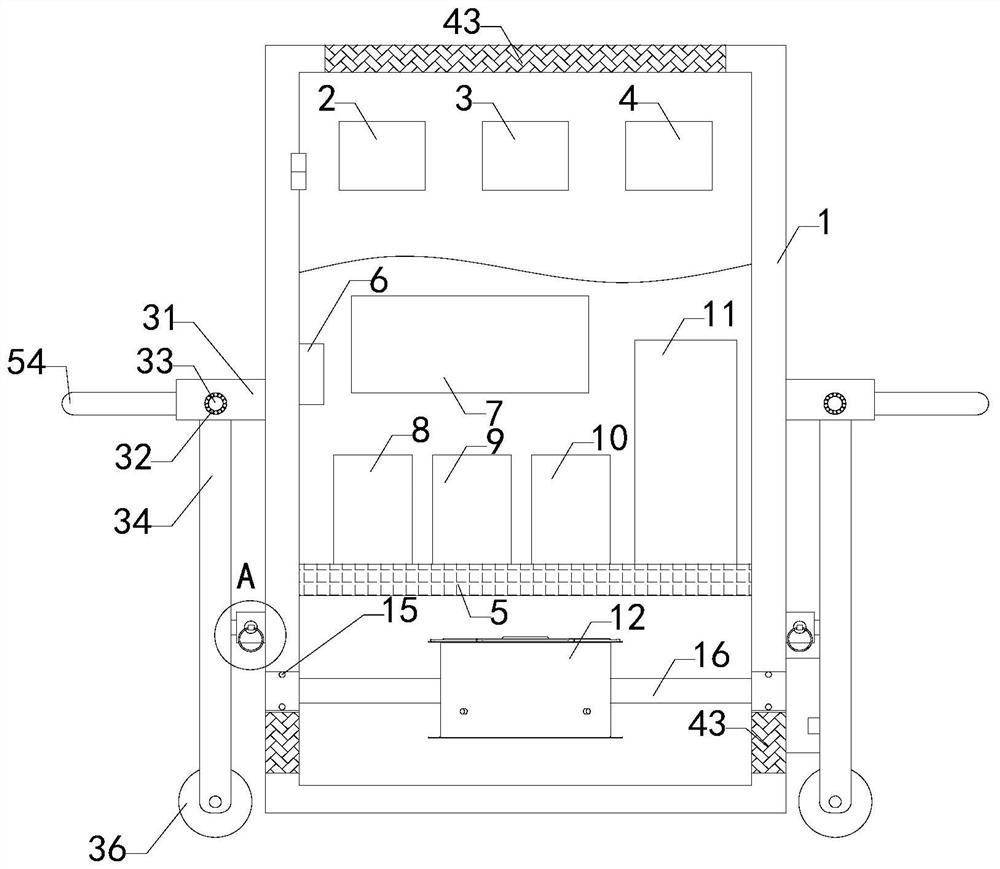

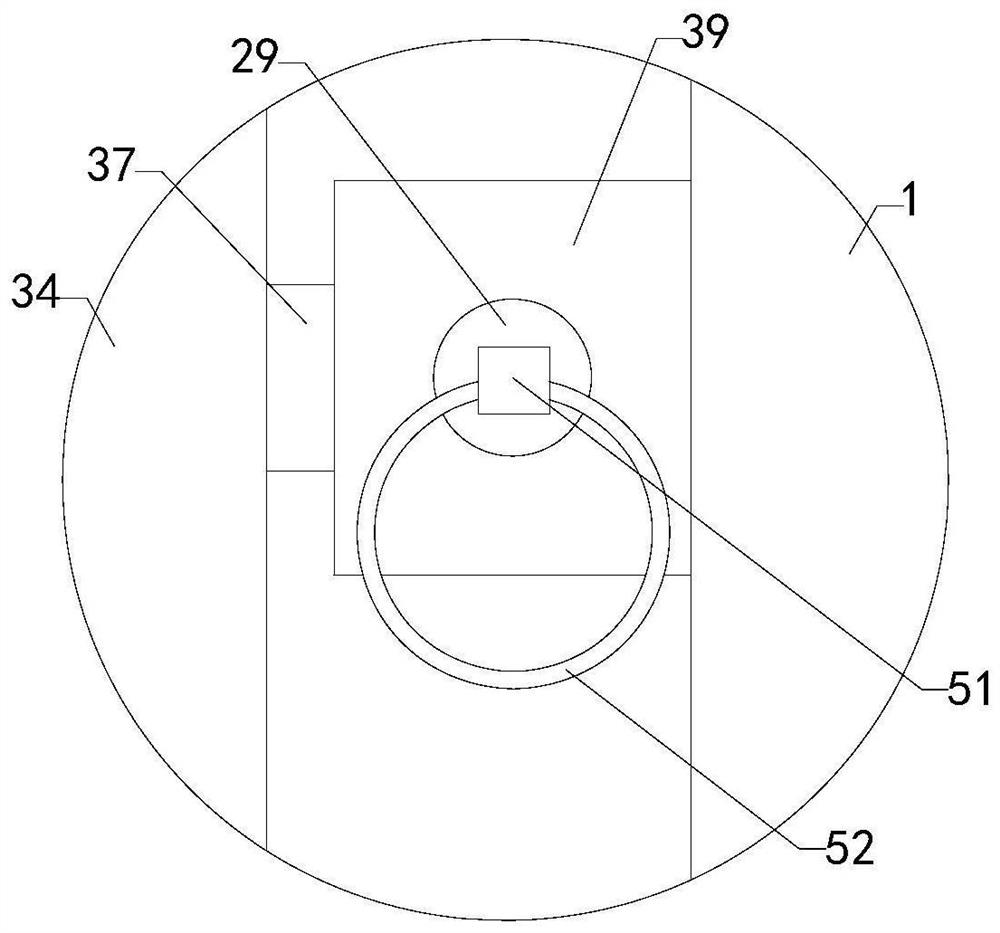

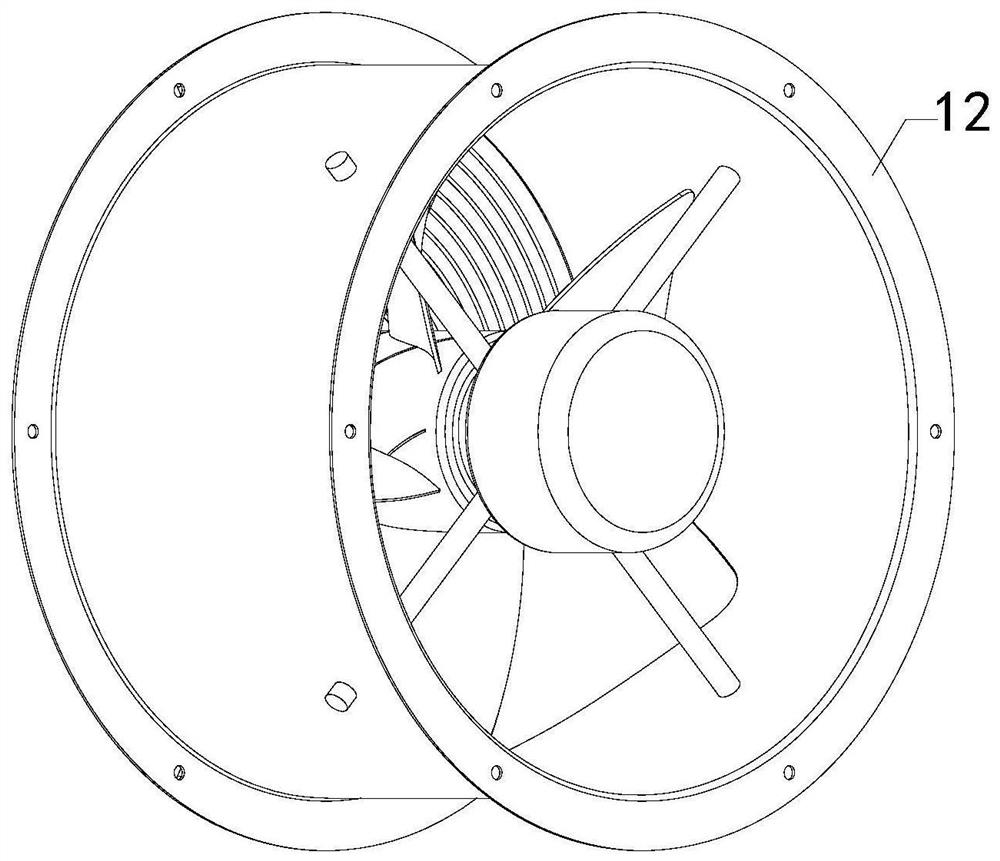

Power supply monitoring device of FPGA prototype verification system

ActiveCN112384049AEasy to moveReduce lossCircuit arrangementsCasings/cabinets/drawers detailsEngineeringFPGA prototype

The invention relates to the technical field of FPGA accessory devices, in particular to a power supply monitoring device of an FPGA prototype verification system. The device is simple in structure, improves the heat dissipation performance and mobility of the power supply monitoring device, and reduces the use limitation. The device comprises a shell. An output voltage display meter, an alternating current output voltage display meter and a direct current output voltage display meter are arranged on the shell, the shell is hollow, a hollow partition plate is arranged in the shell, and a temperature detection device, a power supply device, a direct current distribution protector, an alternating current distribution protector, a dual-power converter and a UPS host are arranged on the partition plate. The device further comprises an axial flow fan, a reciprocating lead screw and a guide rod. First bearings are arranged in the lower half areas of the left side wall and the right side wallof the shell correspondingly, a left rotating shaft and a right rotating shaft are arranged at the left end and the right end of the axial flow fan correspondingly and connected with inner rings of the two sets of first bearings correspondingly, a box body is arranged on the right side wall of the shell, and the right end of the right rotating shaft extends into the box body. A gear is arranged at the right end of the right spindle.

Owner:SHANGHAI TECHN INST OF ELECTRONICS & INFORMATION