White box instrumentation FPGA prototype verification method for integrated circuit safety function

A technology for prototype verification and safety functions, applied in CAD circuit design, electrical digital data processing, instruments, etc., to achieve the effect of simple and easy to see test results, improve code function and performance risks, and ensure accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further explained below in conjunction with accompanying drawing and specific embodiment:

[0044] The integrated circuit security function protection module refers to the functional module that can defend against the existence of hardware Trojan horses, loopholes or backdoors in the integrated circuit functional modules. These hardware Trojan horses, loopholes or backdoors can cooperate with the attacker to send code words from the outside to cooperate with the attack function module to achieve the attack effect. .

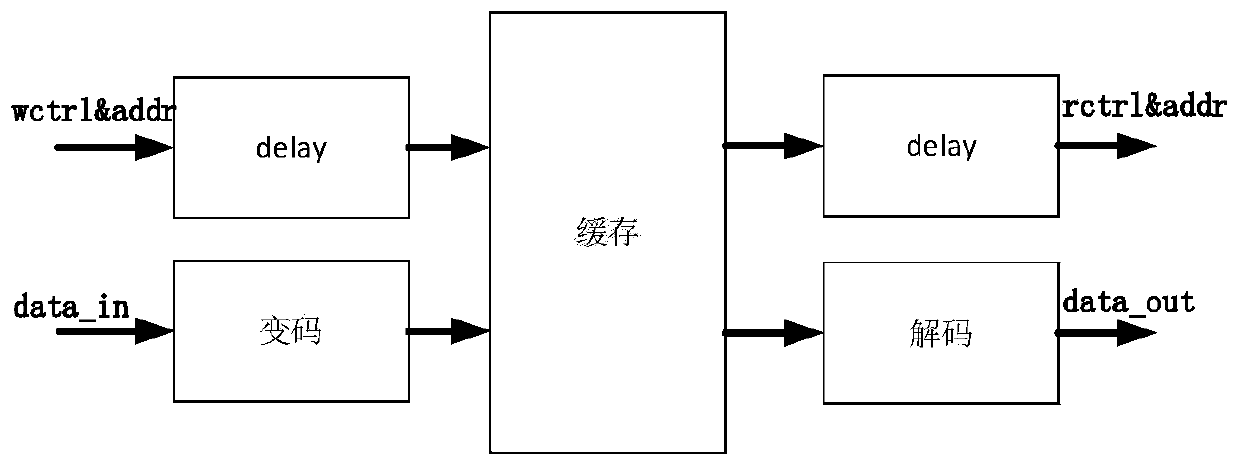

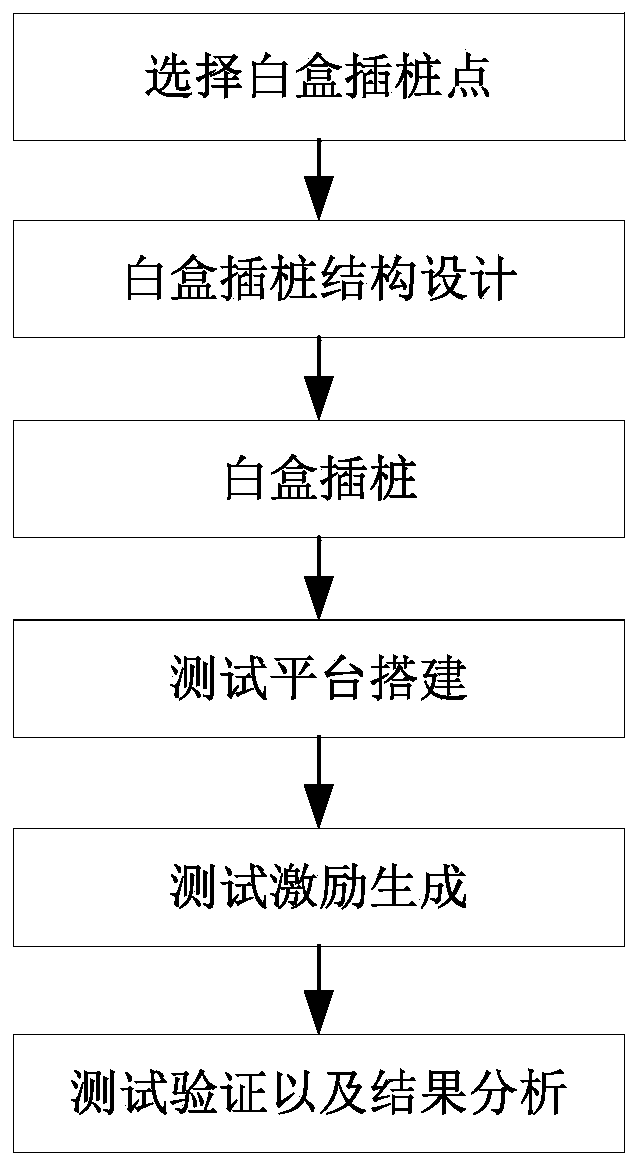

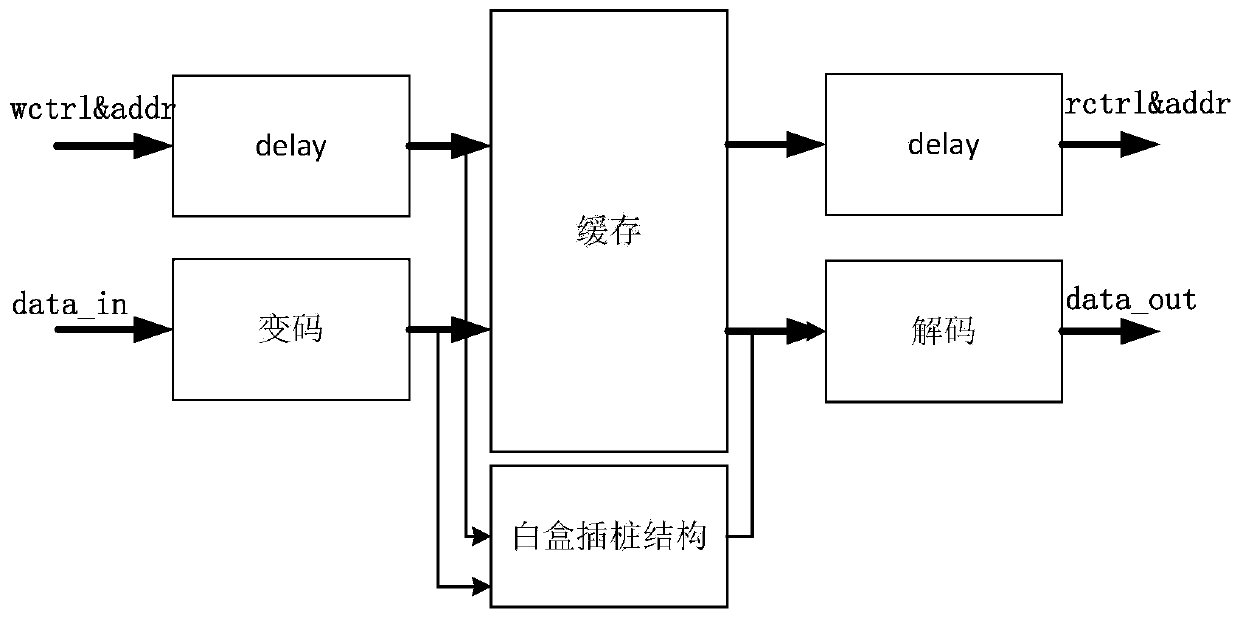

[0045] This implementation is carried out by taking the white-box instrumentation test of the switching chip de-collaboration module as an example. The de-coordination module is a code-changing and decoding module inserted into the cache module, which can effectively scramble user data and prevent attackers from The caching module triggers. The relationship between the coordination module and the cache module of the switching...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More