FPGA prototype automatic verification method and system based on GitLab-CI

An automatic verification and prototype technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve the problems of reducing the overall efficiency of prototype verification, time-consuming and labor-intensive, limited number of testers and work efficiency, etc., to reduce Waste of manpower and energy, improve efficiency, and improve the effect of overall efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

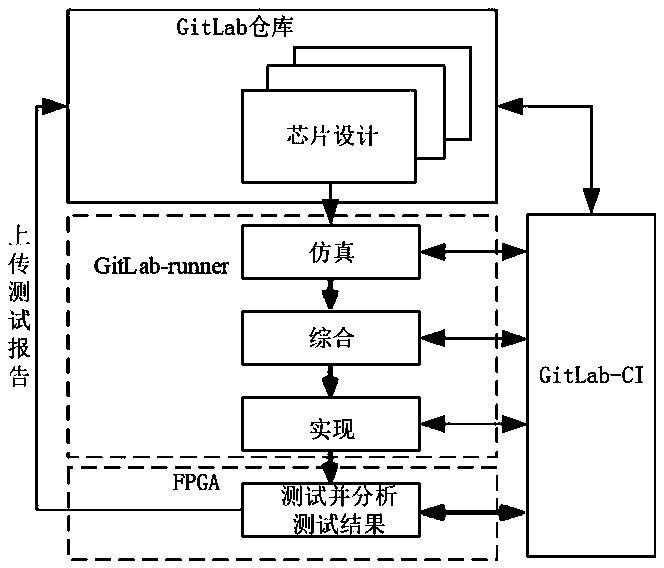

[0024] like figure 2 As shown, the FPGA prototype automatic verification method based on GitLab-CI of the present invention needs to use the version management system GitLab (GitLab warehouse), the continuous integration tool GitLab-CI, the client GitLab-runner and the FPGA prototype verification board, and through the GitLab code warehouse The management terminal enables continuous integration of GitLab-CI, and the chip testers build an automatic process configuration script .gitlab-ci.yml to execute the GitLab-CI-based FPGA prototype automatic verification method of the present invention.

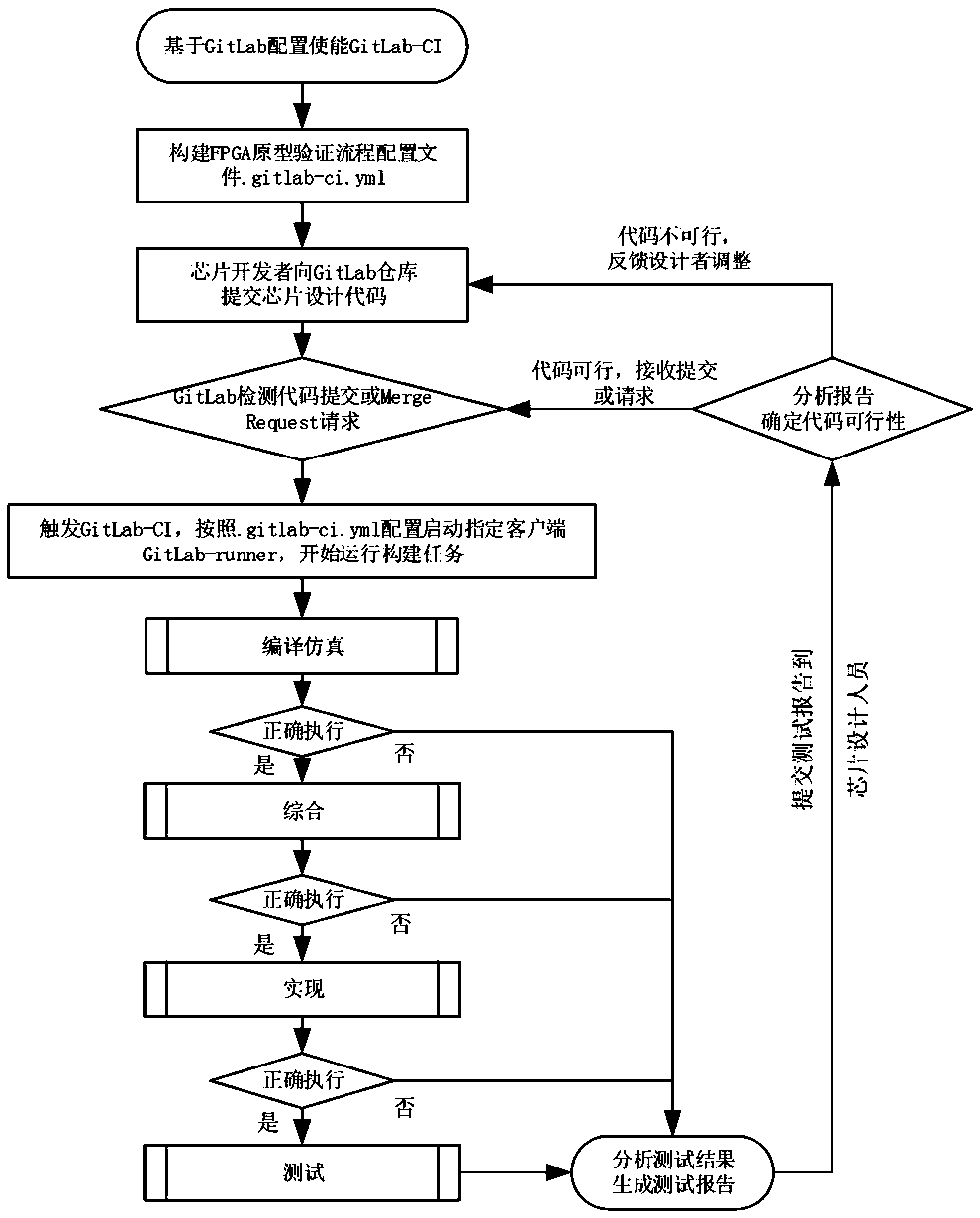

[0025] like image 3 As shown, the implementation steps of the FPGA prototype automatic verification method based on GitLab-CI in this embodiment include:

[0026] 1) Detect the code submission and Merge Request sent by the chip developer to the GitLab warehouse. If the code submission or Merge Request sent by the developer to the GitLab warehouse is detected, jump to the next step;

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More