Message filtering system and message filtering method of high-speed interconnection bus

An interconnection bus and message filtering technology, which is applied in data transformation, instrumentation, electrical digital data processing, etc., can solve the problems of inability to achieve high-speed interconnection bus clock frequency, bus frequency FPGA chip logic frequency mismatch, etc., to improve film casting The effect of success rate, shortened verification cycle, and improved design flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the objectives, technical solutions and advantages of the present invention clearer, the following further describes the present invention in detail with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

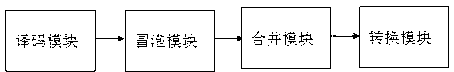

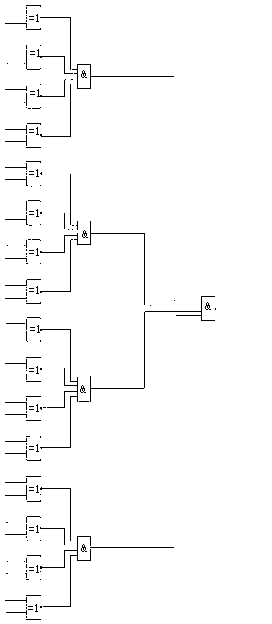

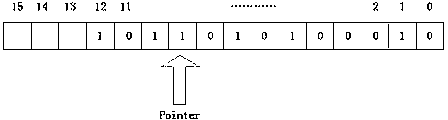

[0029] Such as figure 1 As shown, a message filtering system for a high-speed interconnected bus of the present invention includes a decoding module, a bubbling module connected to the decoding module, a merge module connected to the bubbling module, and a conversion module connected to the merge module. Among them, the decoding module decodes the parallel data on the receiving end of the bus according to the message encoding defined by the point-to-point connection protocol, and uses a separate mark to mark whether each message is valid; the bubbling module parallels the bus according to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More