FPGA chip, high-speed interface interconnection system and interconnection achieving method

A high-speed interface and interconnection system technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as easy failure, difficult debugging, chip design transplanted to a single FPGA chip, etc., to improve the success rate , Speed up the debugging process and shorten the chip development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be described in detail below with reference to the accompanying drawings and specific examples. The following examples are to explain the present invention, but the present invention is not limited to the following embodiments.

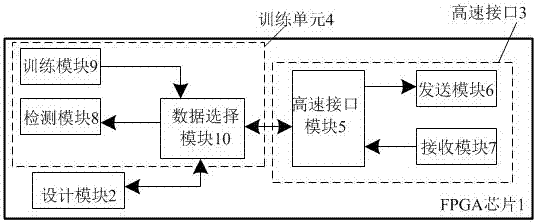

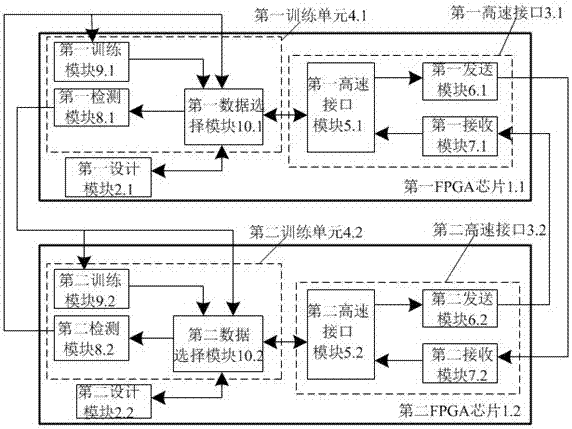

[0042] like figure 1 As shown, an FPGA chip provided in this embodiment includes a high-speed interface 3 and a training unit 4, the high-speed interface 3 includes a high-speed interface module 5, and the high-speed interface module 5 is connected with a sending module 6 and a receiving module 7;

[0043] The training unit 4 includes a data selection module 10 , the data selection module 10 is connected with the training module 9 and the detection module 8 ; the data selection module 10 is connected with the design module 2 ; the data selection module 10 is connected with the high-speed interface module 5 .

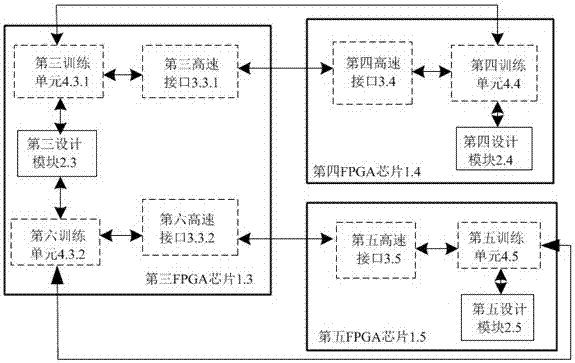

[0044] There are several high-speed interfaces 3 , and the number of training units 4 is the same as the number...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More