Device and method for increasing FPGA prototype verification efficiency

A prototype verification and efficiency technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as difficult positioning, wide verification process, and high complexity of chip design, and achieve the effect of improving verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

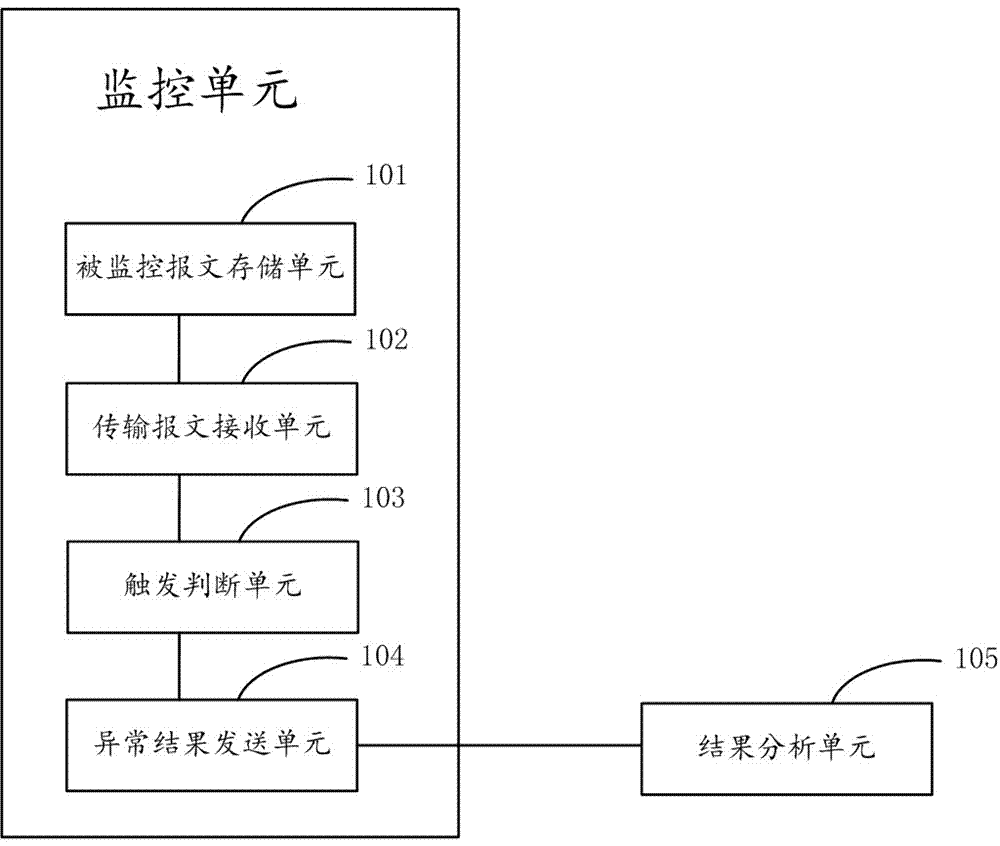

[0028] Please refer to figure 1 , A device for improving the efficiency of FPGA prototype verification, the device comprising: a monitoring unit, the monitoring unit further comprising: a monitored message storage unit 101, a transmission message receiving unit 102, a trigger judgment unit 103, and an abnormal result sending unit 104 ,among them:

[0029] The monitored message storage unit 101 is used to store the content of the monitored message;

[0030] The transmission message receiving unit 102 is configured to receive and read the transmission message from the NC chip;

[0031] The trigger judgment unit 103 is used to compare whether the content of the transmission message is consistent with the content of the monitored message. If they are consistent, the NC chip is abnormal, the trigger judgment unit 103 enters the pause state, and sends the information of the abnormal chip to Abnormal result sending unit 104, the abnormal result sending unit 104 sends the abnormal result to...

Embodiment 2

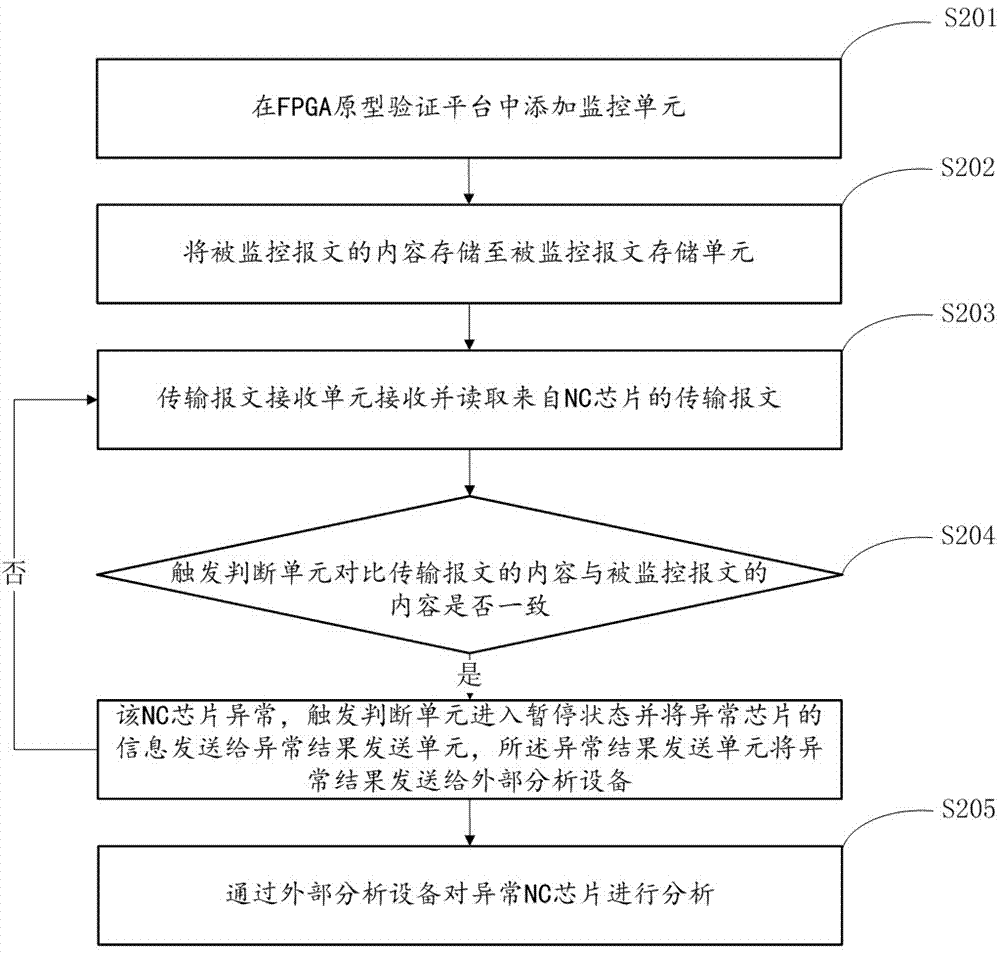

[0036] Please refer to figure 2 , A method to improve the efficiency of FPGA prototype verification, including the following steps:

[0037] Step 201: Add a monitoring unit to the FPGA prototype verification platform. The monitoring unit includes: a monitored message storage unit, a transmission message receiving unit, a trigger judgment unit, and an abnormal result sending unit;

[0038] Step 202: Store the content of the monitored message in the monitored message storage unit;

[0039] Step 203: The transmission message receiving unit receives and reads the transmission message from the NC chip;

[0040] Step 204: The trigger judgment unit compares whether the content of the transmitted message is consistent with the content of the monitored message. If they are consistent, the NC chip is abnormal, the trigger judgment unit enters the pause state, and the information of the abnormal chip is sent to the abnormal result sending unit , The abnormal result sending unit sends the abnor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More