FPGA prototype verification development board segmentation simulation system and method, medium and terminal

A prototype verification and simulation system technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems, design cannot be accommodated alone, and results cannot be understood, so as to speed up the development process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

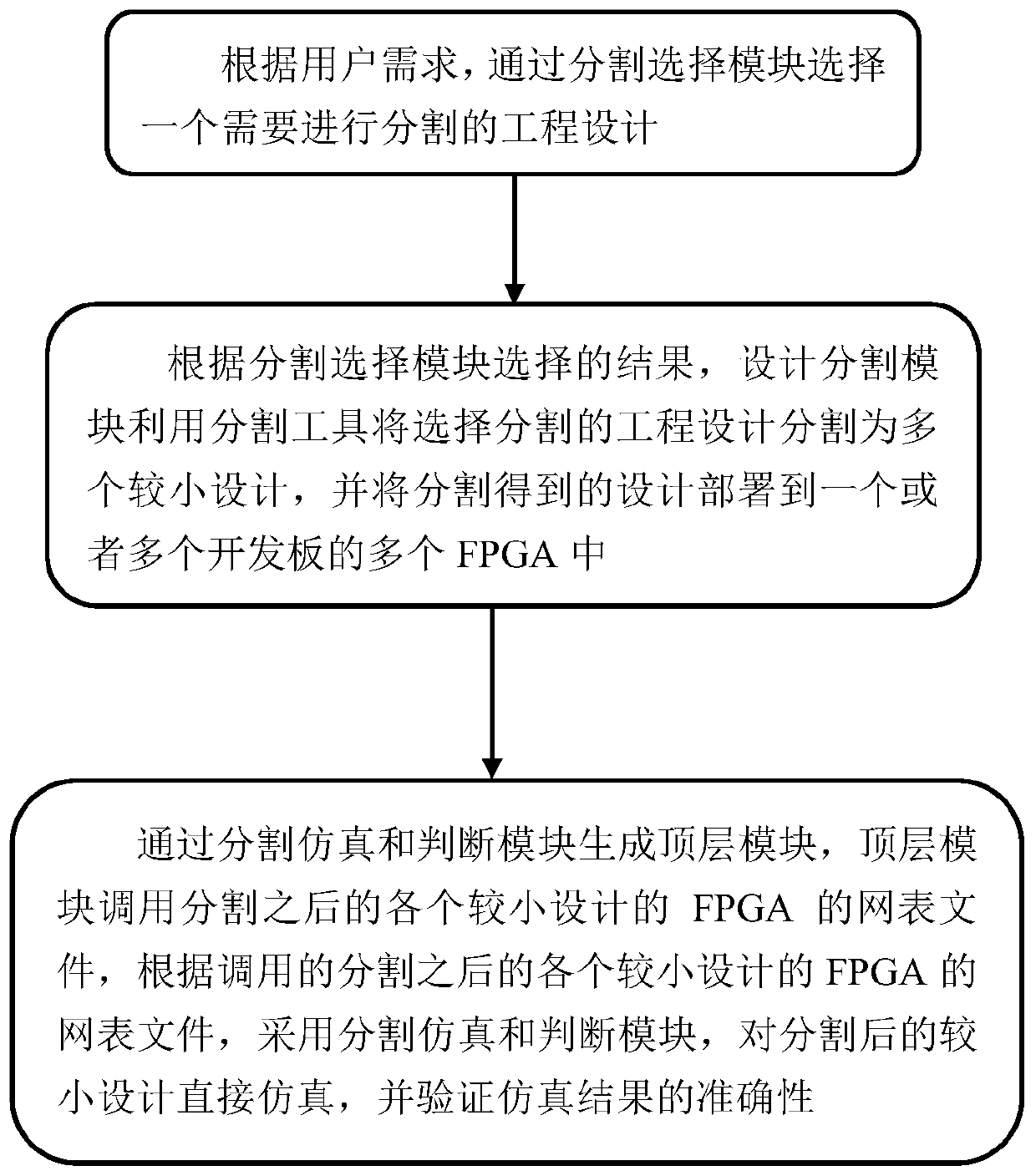

[0027] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

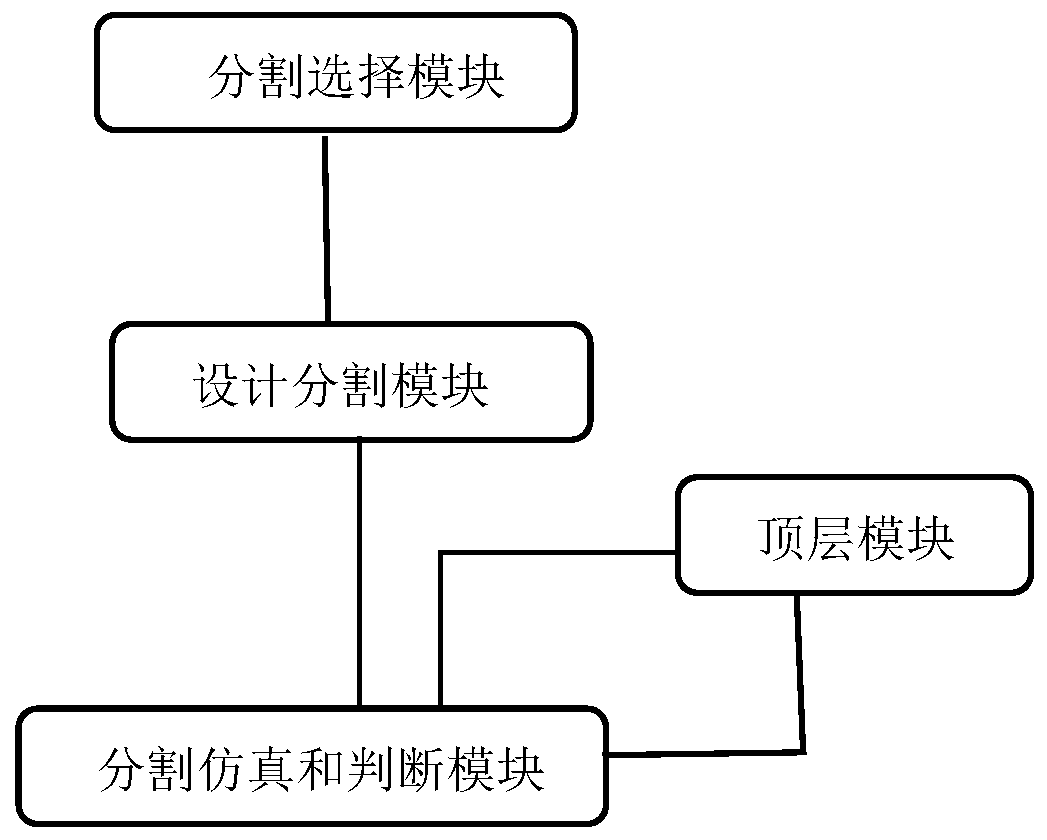

[0028] Such as figure 2 As shown, the invention provides a kind of FPGA prototype verification development board segmentation simulation system, comprising:

[0029] The segmentation selection module is used to select an engineering design that needs to be divided according to user requirements;

[0030] The design segmentation module is used to divide the selected engineering design into multiple smaller designs by using the segmentation tool according to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More