FPGA prototype verification system

A prototype verification and port technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as insufficient support for large-scale data exchange, small number of interconnection interfaces, etc., to facilitate module or full-chip prototype verification experiments , Solve the effect of less interconnection interface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

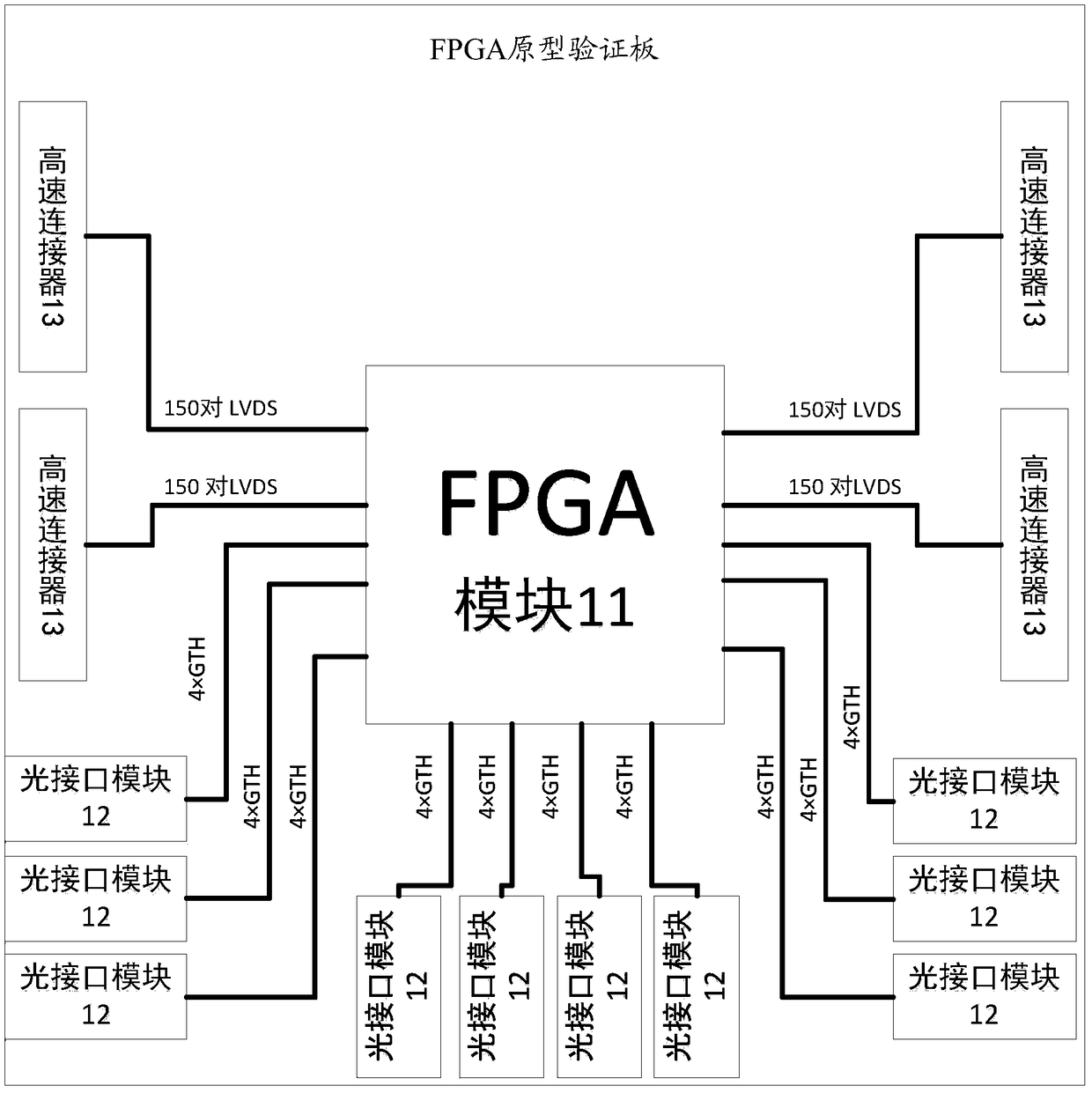

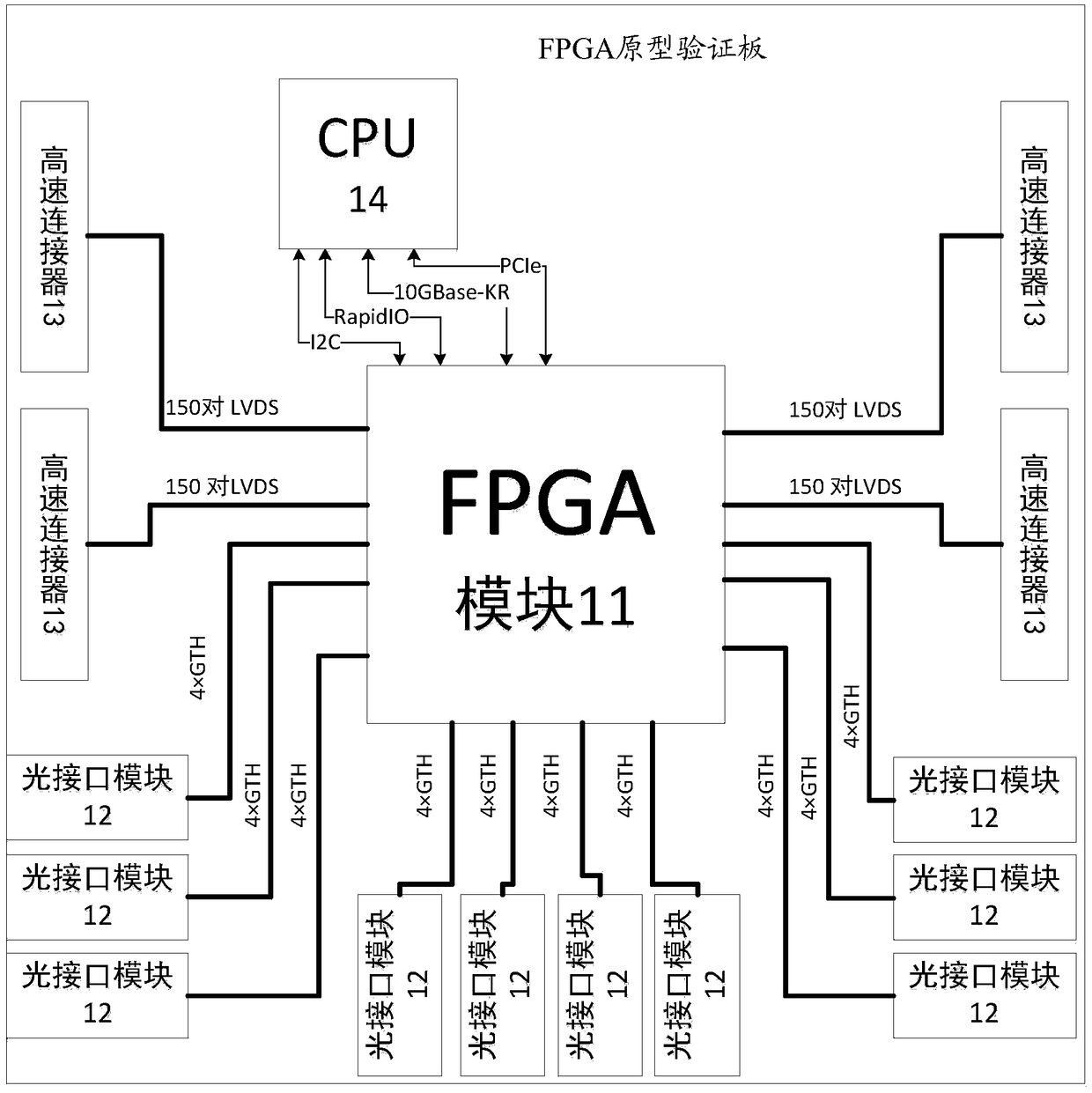

[0033] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions of the present invention will be clearly and completely described below in conjunction with the accompanying drawings. Obviously, the described embodiments are part of the embodiments of the present invention, not all of them. the embodiment. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

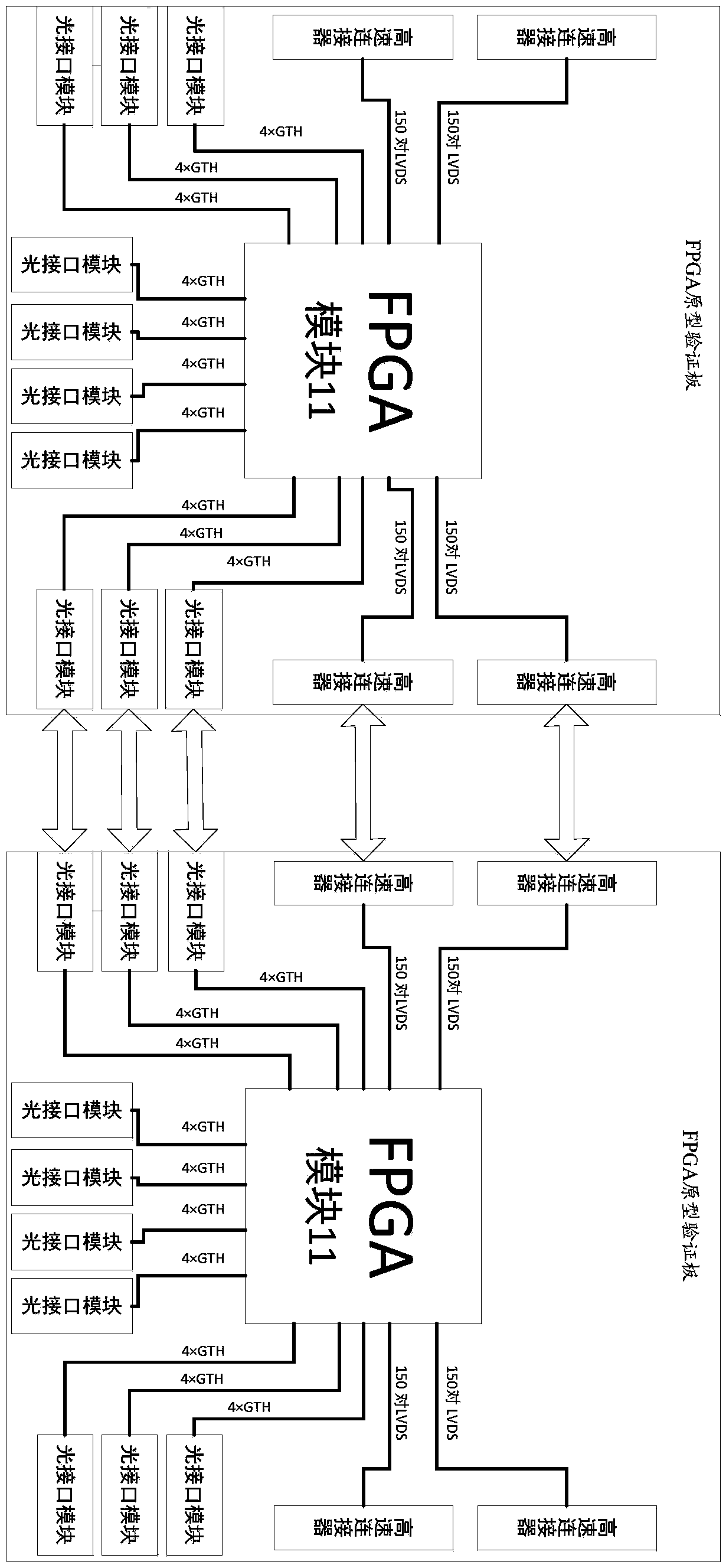

[0034] In the current FPGA verification system, the number of interconnection interfaces between each two FPGA chips is relatively small, which is not enough to support large-scale data exchange. For example, the VU440 cascade verification board needs to meet the basic requirements of resources and interfaces in a single exchange verification scenario. At the same time, due to the la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More