Debugging method for large-scale field programmable gate array (FPGA) design

A debugging method and large-scale technology, applied in the direction of measuring devices, instruments, measuring electronics, etc., can solve the problems of long signal time, limited data acquisition and storage depth, waste of time and cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be described in detail below with reference to the accompanying drawings.

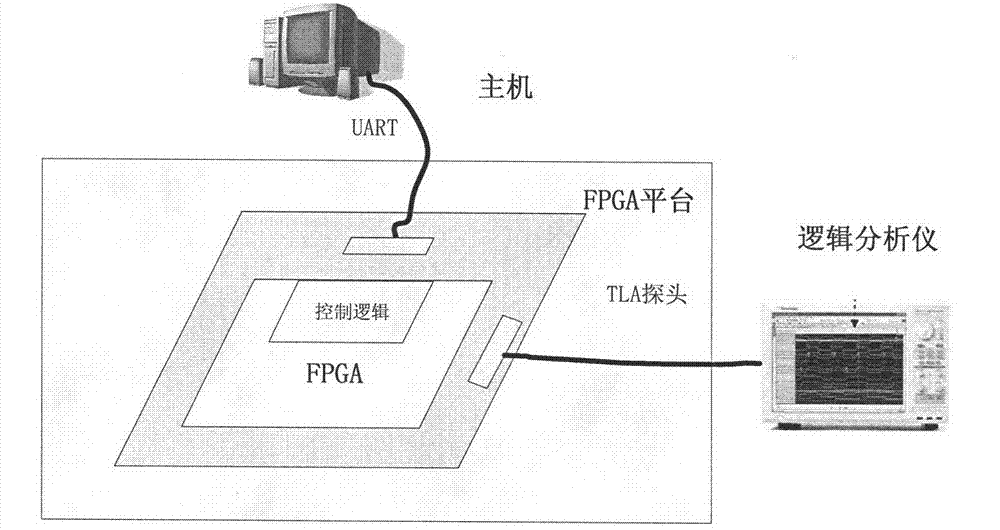

[0016] The invention provides a debugging method suitable for large-scale FPGA design, the main purpose is to improve the debugging efficiency on the FPGA prototype, reduce the test cost, and realize the selection of an external test pin to any internal signal to be tested. The main principle is to operate the control logic inside the FPGA through the host UART interface to realize the connection between the internal signal to be tested and the external test pin.

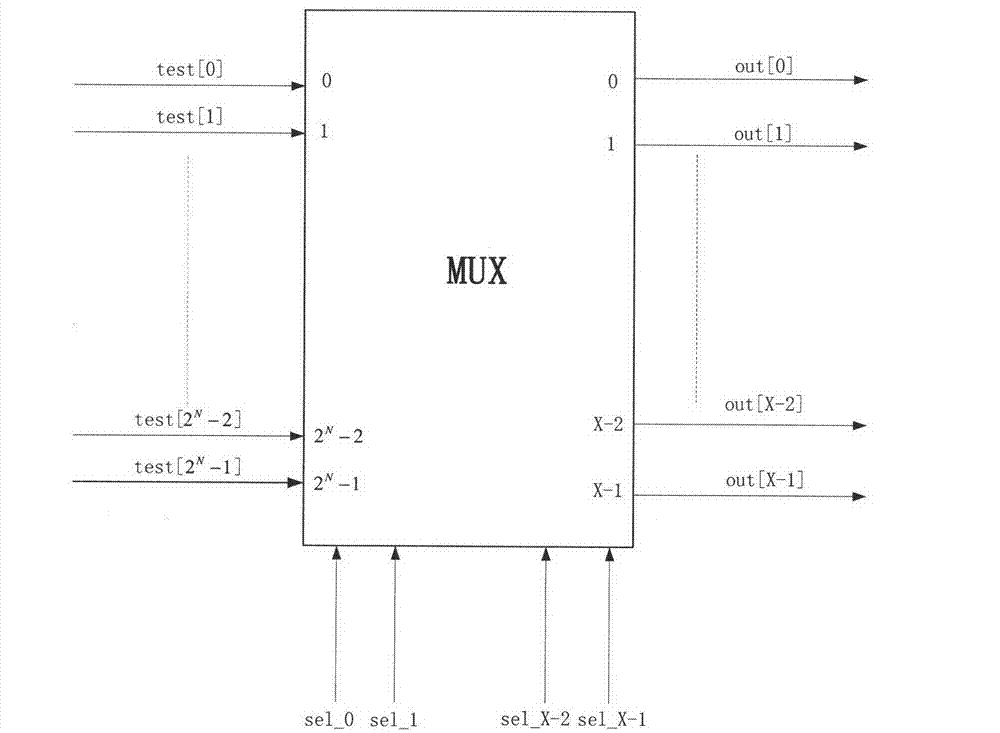

[0017] First, the internal signal to be tested needs to be set up in advance, assuming there are 2 N If you want to observe the signal, you need to set these 2 in advance in the design. N Each signal is set as the internal signal to be tested and connected to the control logic inside the FPGA.

[0018] Control logic input is 2 N The output is connected to the external test pins. Assuming that the number o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More