SoC software and hardware collaborative verification system and method based on FPGA prototype

A technology of software and hardware collaboration and prototype verification, applied in the fields of instruments, calculations, electrical digital data processing, etc., to achieve the effect of improving verification progress, reducing workload, and shortening integration time

Pending Publication Date: 2022-06-10

北京轩宇空间科技有限公司

View PDF0 Cites 2 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

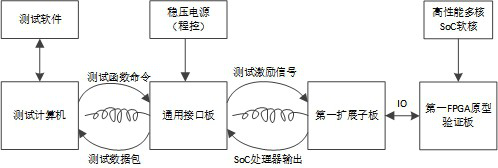

The first FPGA prototype verification platform is used for general interface transfer test verification;

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment 1

Embodiment 2

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

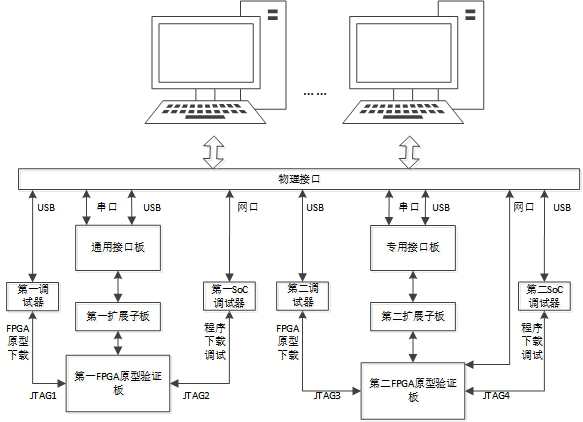

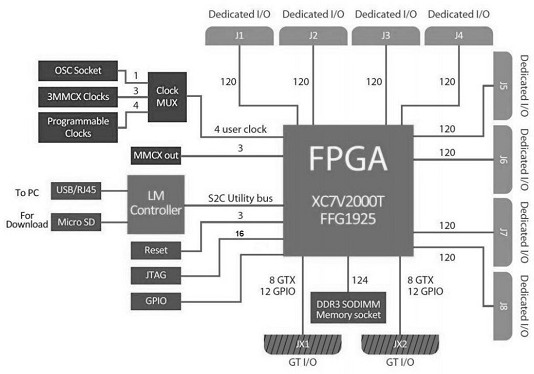

The invention discloses an FPGA prototype-based SoC software and hardware collaborative verification system and method. The system comprises a plurality of computers, at least a first set of FPGA prototype verification platform connected to the plurality of computers through physical interfaces, and at least a second set of FPGA prototype verification platform connected to the plurality of computers through physical interfaces. Two sets of FPGA prototype verification platforms are arranged, the high-performance SoC interface classification test operation is met, the first set of FPGA prototype verification platform is used for universal interface switching test verification, the second set of FPGA prototype verification platform is used for special interface switching test verification, a modular design thought is adopted, the cooperative verification method based on the FPGA prototype is improved, and the test efficiency is improved. The system and the method provided by the invention are high in reusability, repeated development of a plurality of systems is avoided, the verification progress before chip tape-out is greatly improved, and the integration time of software and hardware is shortened.

Description

Technical field [0001] The invention involves the field of IC simulation verification, and especially involves the FPGA -based SOC software and hardware collaborative verification system and methods. Background technique [0002] In SOC design, software and hardware collaborative verification is to run software on the simulated hardware model in front of the chip stream to ensure that there is no hardware design defect.Software and hardware collaborative verification is a verification technology developed for SOC technology. The main purpose is to verify the functions and timing of SOC chip software and hardware interfaces, solve the problem of SOC software and hardware, and develop and develop and develop in advance before chip flow.Debug application software to shorten the development cycle of the entire project. [0003] At present, software and hardware collaboration verification methods mainly include two categories: collaborative verification based on the simulation platfor...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G06F30/331G06F30/398

CPCG06F30/331G06F30/398

Inventor 王红霞刘鸿瑾王宏张绍林李宾王小波牟宁马远航宋佳伟付宝玲

Owner 北京轩宇空间科技有限公司