Wiring method of FPGA prototype verification system

A prototype verification and wiring method technology, applied in the field of FPGA prototype verification system wiring, can solve problems such as signal delay increase, FPGA prototype system performance degradation, and large delay ratio.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0047] Table 1 is the common parameter meaning of the present invention:

[0048] Table 1 parameter description

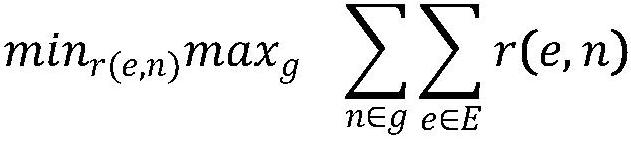

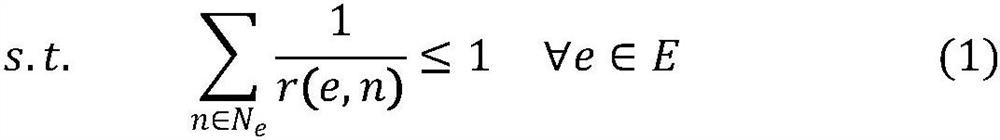

[0049] symbol meaning G A collection of all groups g group N A collection of all the nets n net E A collection of all connections between FPGAs e Connection between FPGAs V A collection of all FPGAs v Single FPGA r(e, n) Time division multiplexing ratio allocated when network n uses edge e

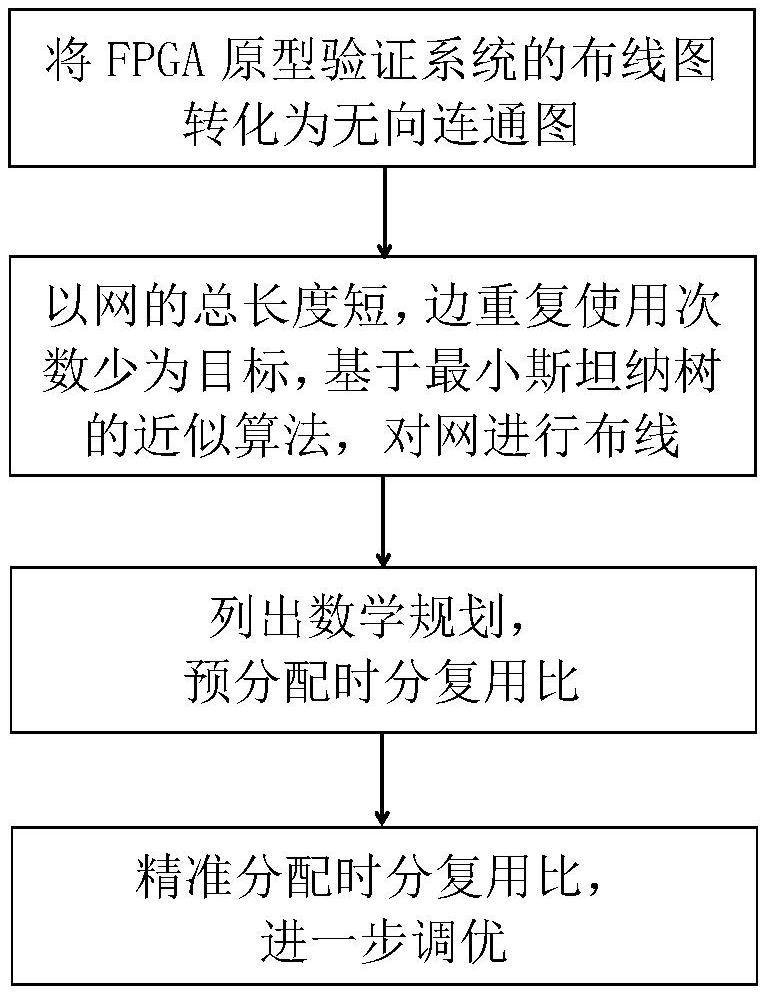

[0050] The present invention proposes a wiring method of FPGA prototype verification system, such as figure 1 As shown, it specifically includes the following steps:

[0051] Step 1: Convert the wiring diagram of the FPGA prototype system into an undirected connected graph.

[0052] Transform the wiring diagram of the FPGA prototype system into an undirected connected graph G(V, E), reco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More