Field-programmable gate array (FPGA) prototype verification clock device

A clock device and prototype verification technology, applied in the field of FPGA prototype verification, can solve problems such as system resource waste, logic timing tightening, poor stability, etc., and achieve the effect of maximizing the utilization of system clock resources, realizing clock management, and convenient verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the above objects, features and advantages of the present application more obvious and understandable, the present application will be further described in detail below in conjunction with the accompanying drawings and specific implementation methods.

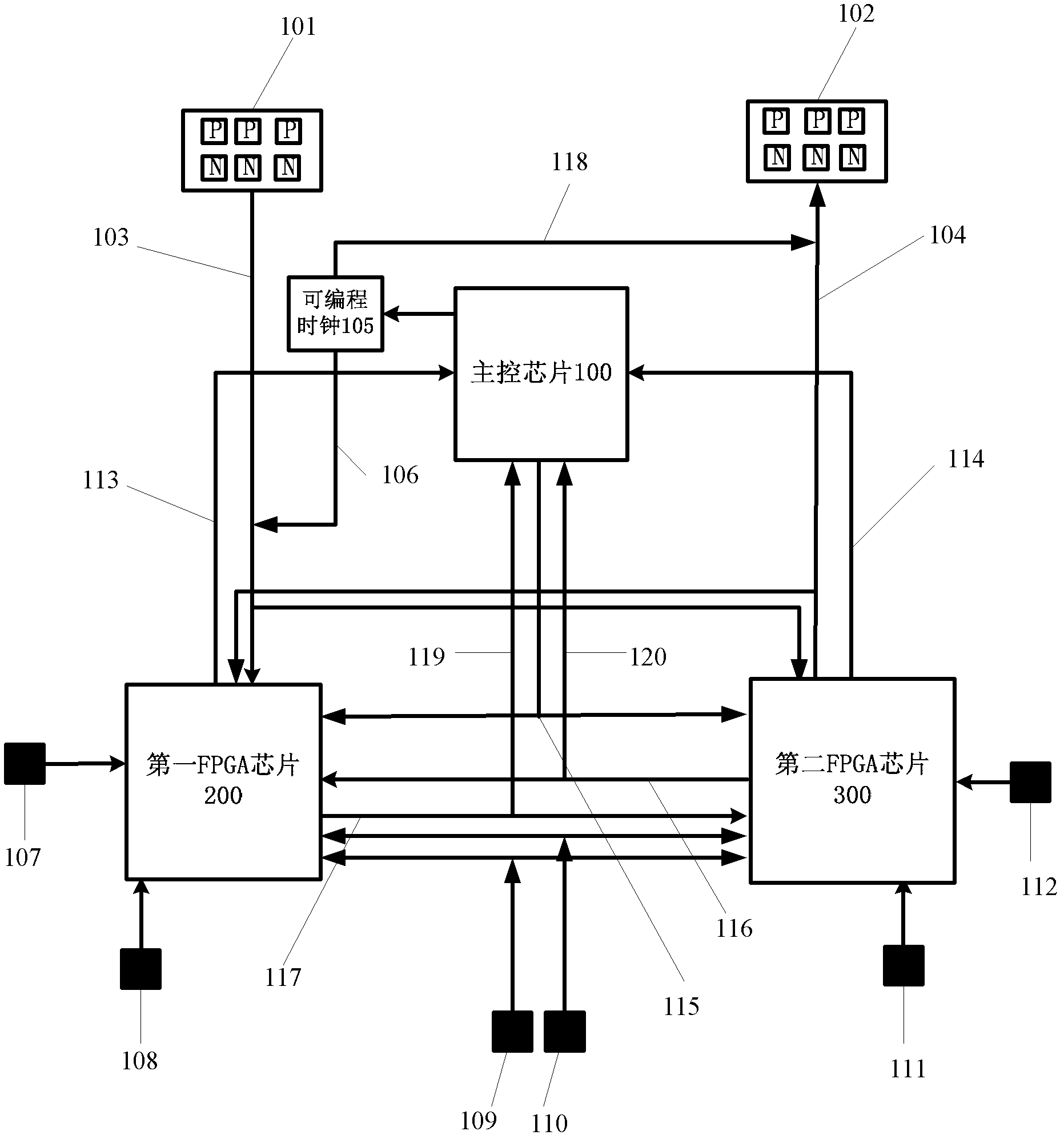

[0031] refer to figure 1 , which shows a schematic structural diagram of a circuit of a preferred FPGA prototype verification clock device of the present application.

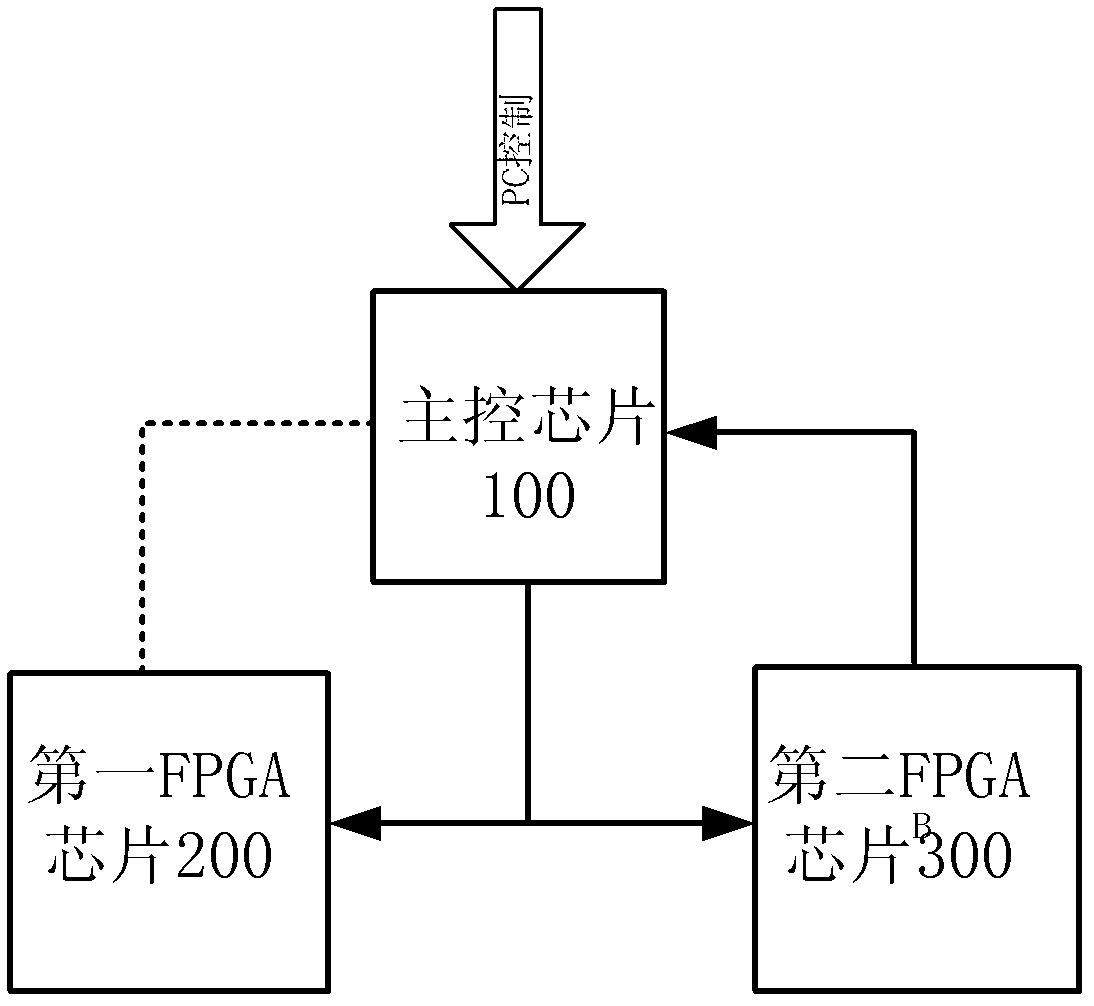

[0032] Such as figure 1 , the present application includes a main control chip 100, a first FPGA chip 200, and a second FPGA chip 300;

[0033] And an external clock input and output circuit connected to the first FPGA chip 200 and the second FPGA chip 300 at the same time;

[0034] One end is connected to the main control chip 100, and the other end is respectively connected to the internal programmable clock circuit of the first FPGA chip 200 and the second FPGA chip 300;

[0035] Directly connected to the first FPGA chip 200, or the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More