Patents

Literature

60results about How to "Minimizes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

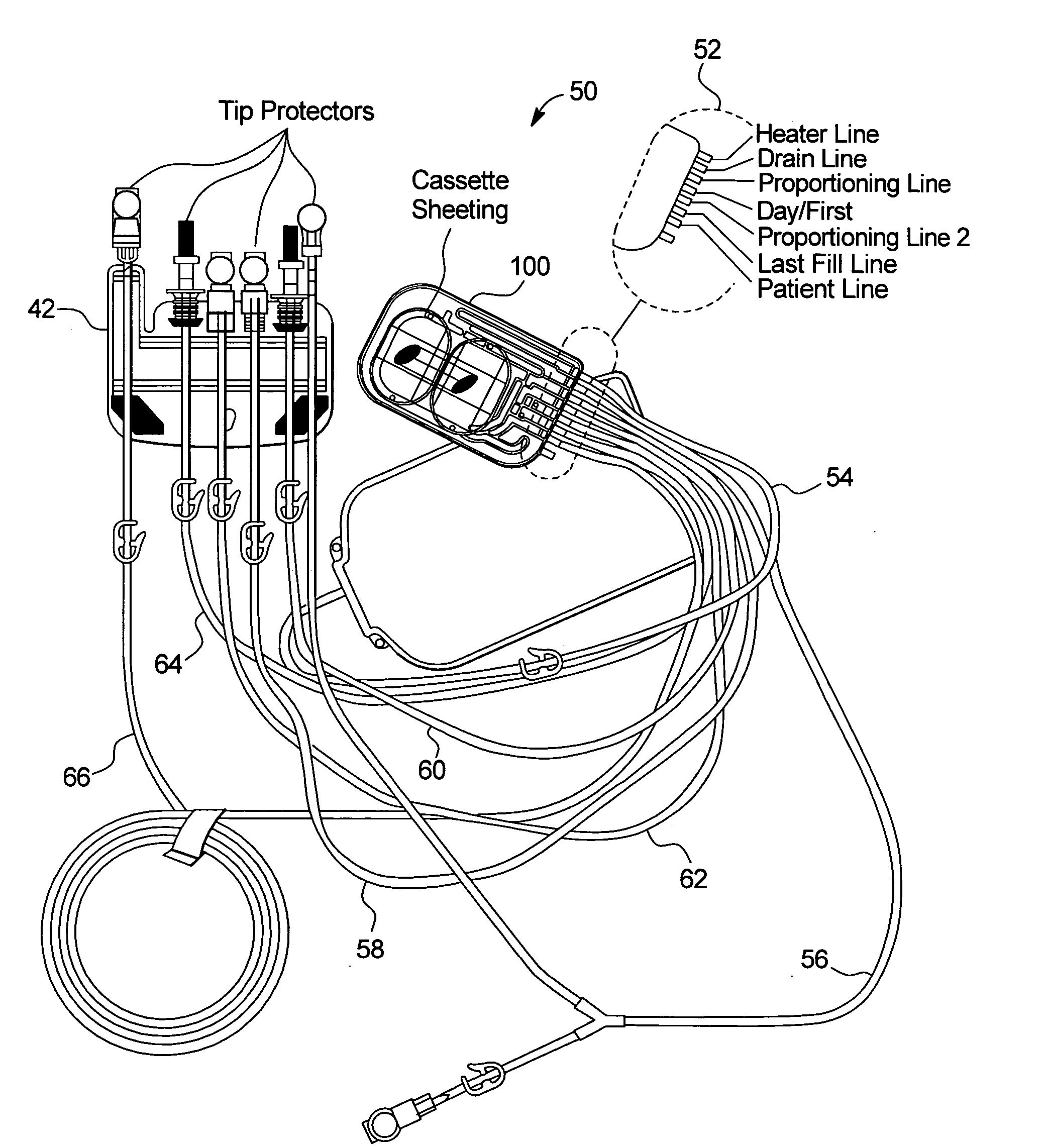

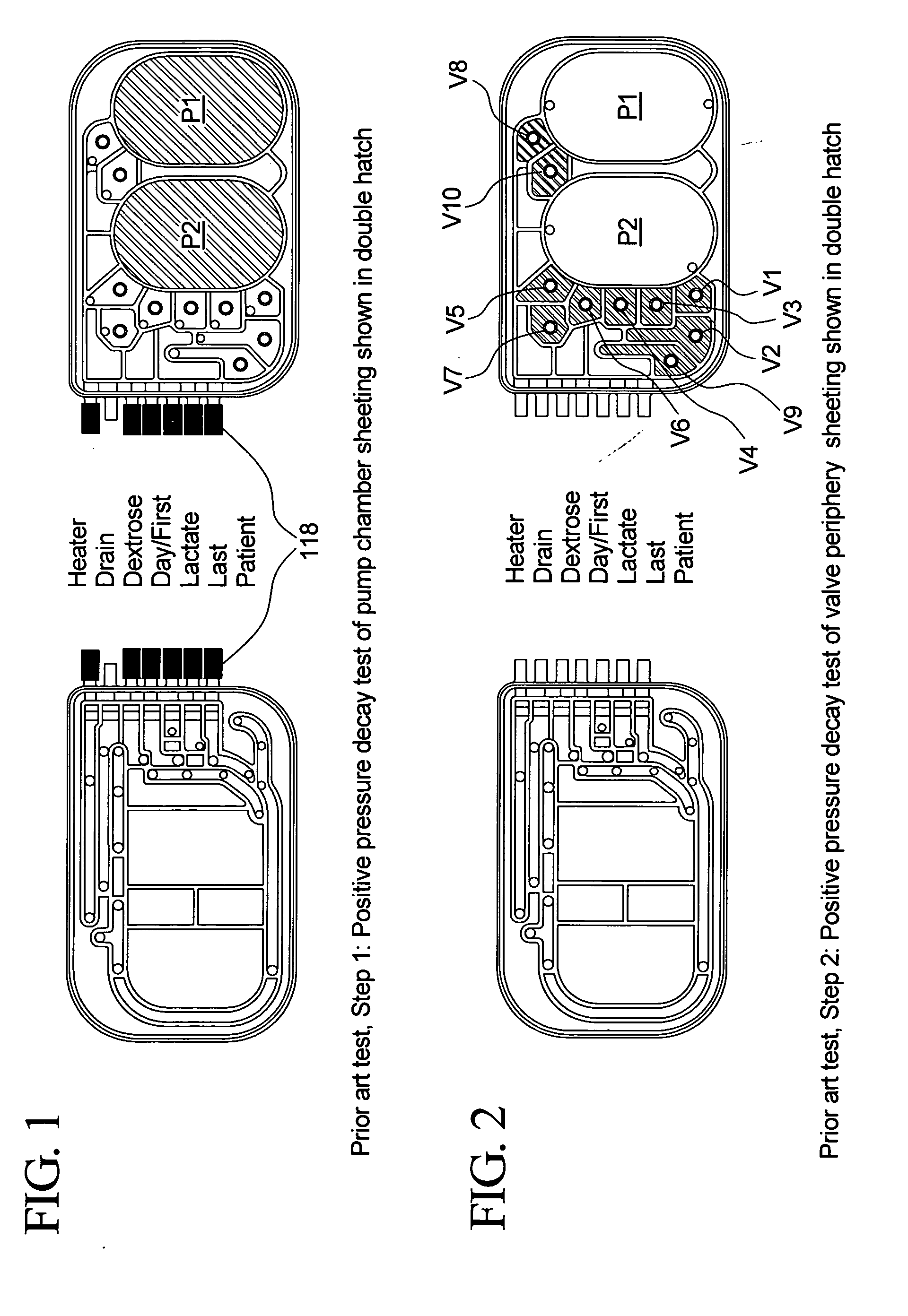

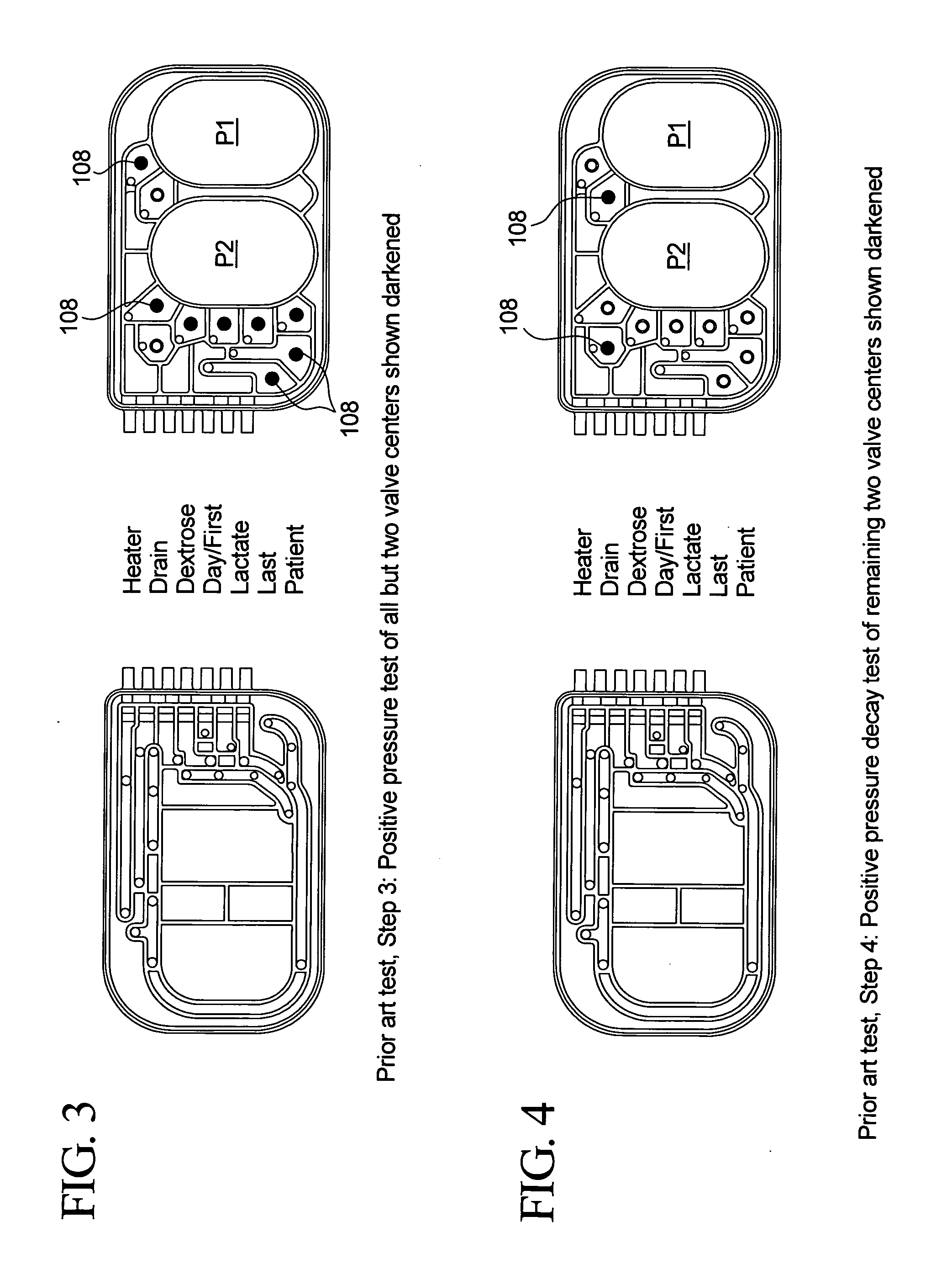

Priming, integrity and head height methods and apparatuses for medical fluid systems

ActiveUS20050126998A1Less timeLeakage is detectedDetection of fluid at leakage pointOther blood circulation devicesDelivery systemFluid system

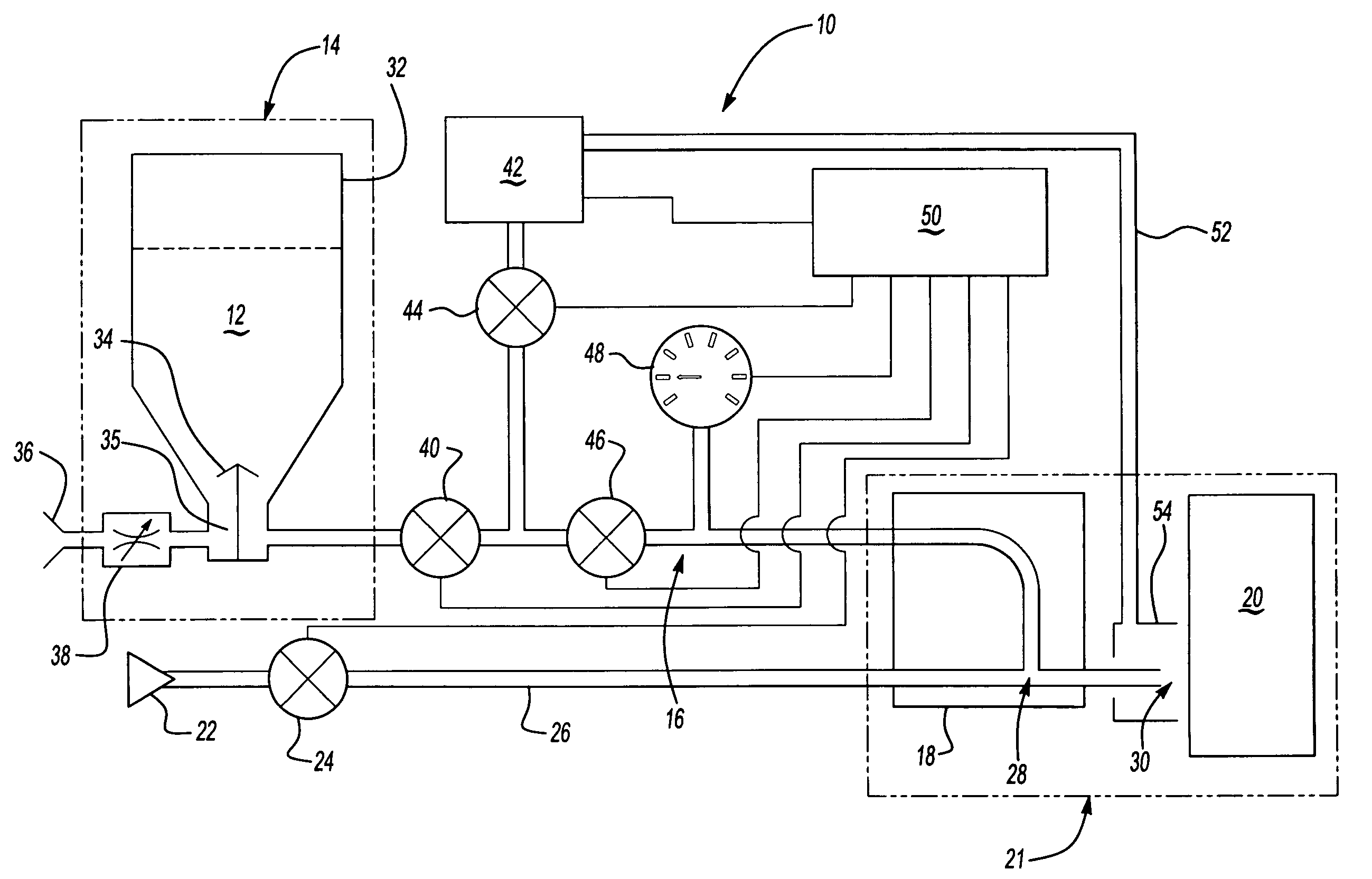

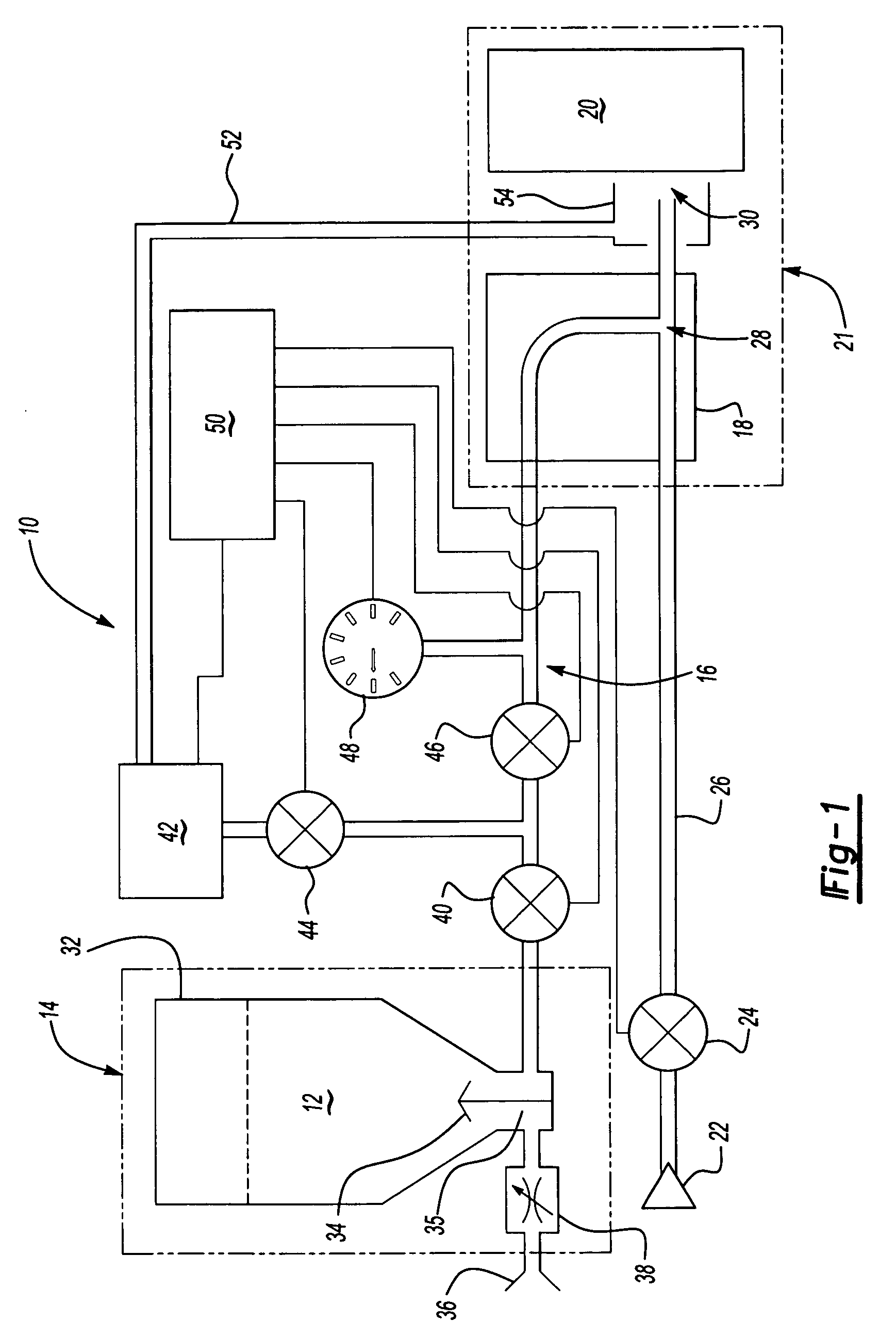

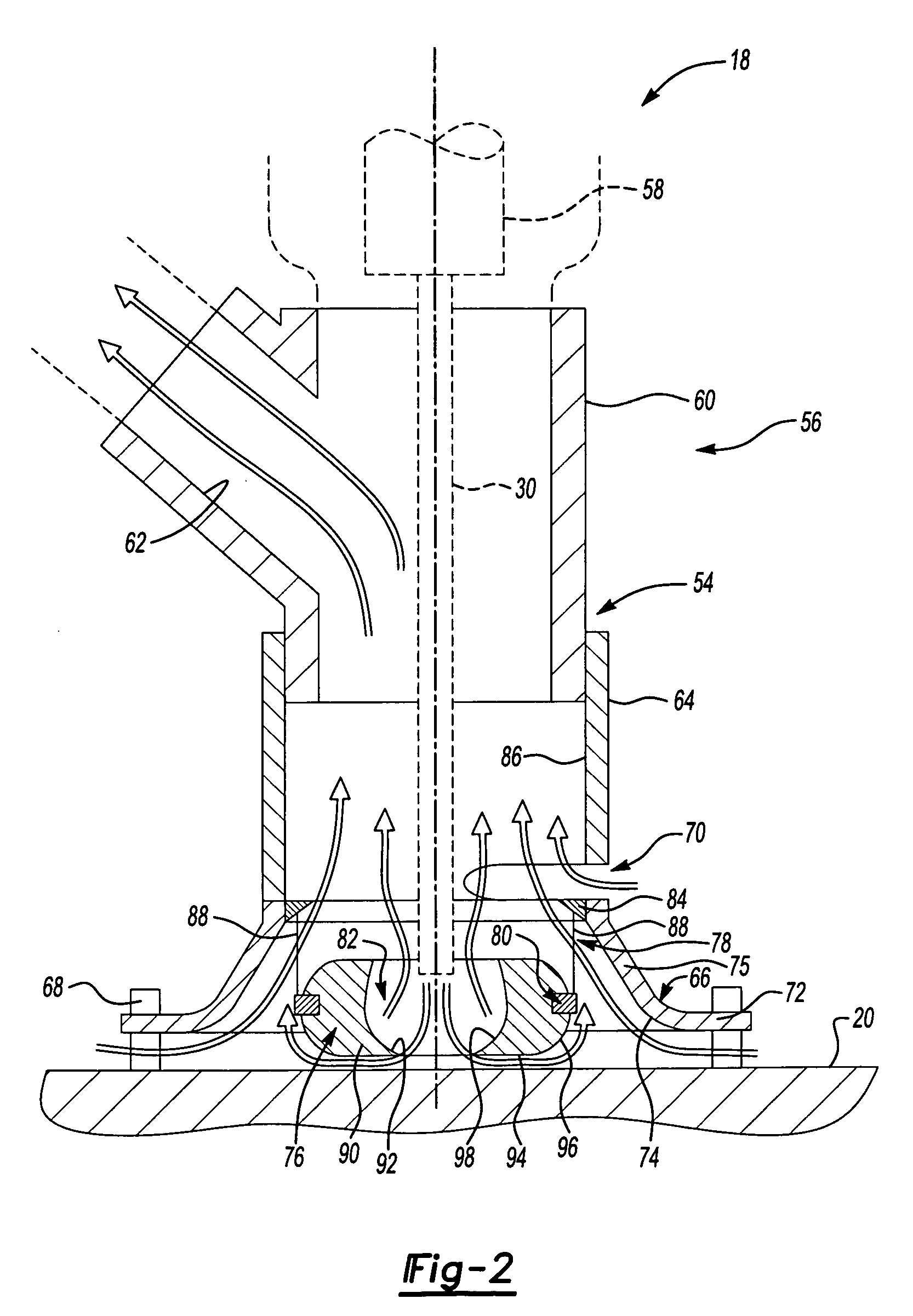

Improved integrity test, priming sequence and bag height detection tests, apparatuses and methods for a medical fluid delivery system are provided. The integrity test includes a plurality of air pressure decay tests, using positive and negative pressure. The priming sequence includes pumping fluid through a portion of a patient line to be primed to overcome air in the line and other potential obstacles. The head height test measures a pressure build-up or drop-off within a pump chamber of a membrane pump. The measured pressure corresponds to a head height between a fluid supply and the pump or between the pump and a fluid drain. A determination is made whether the corresponding head height is acceptable.

Owner:BAXTER INT INC +1

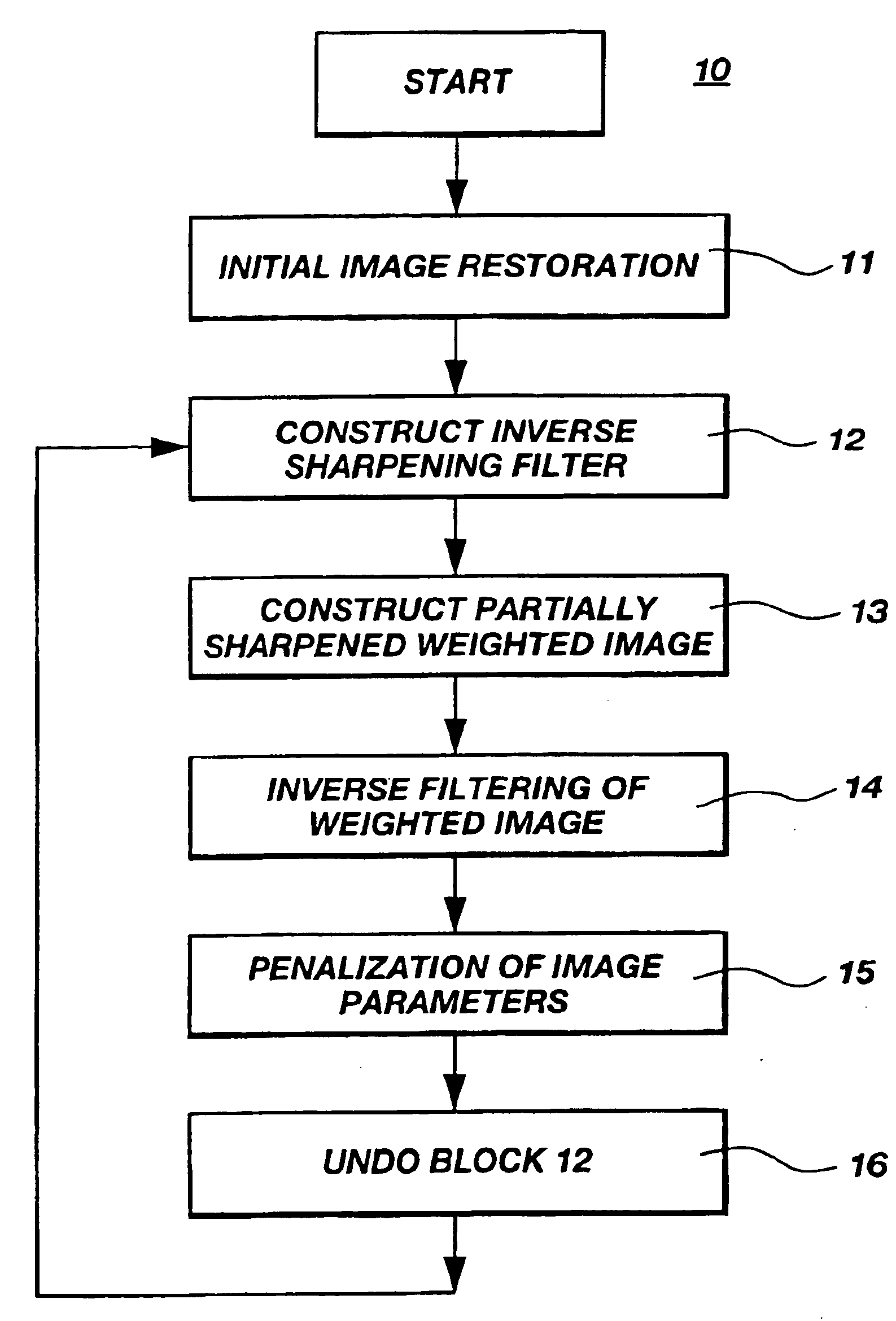

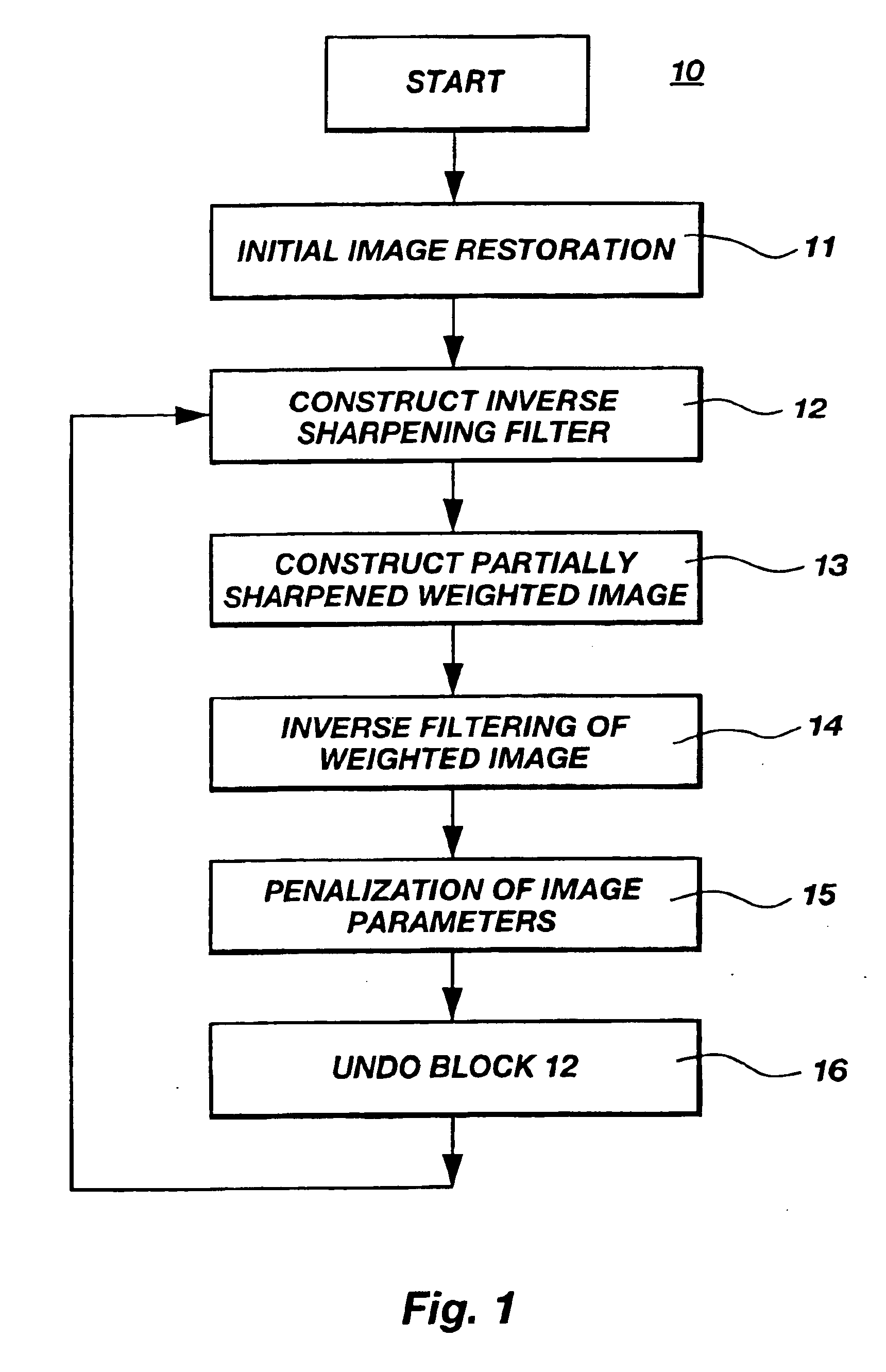

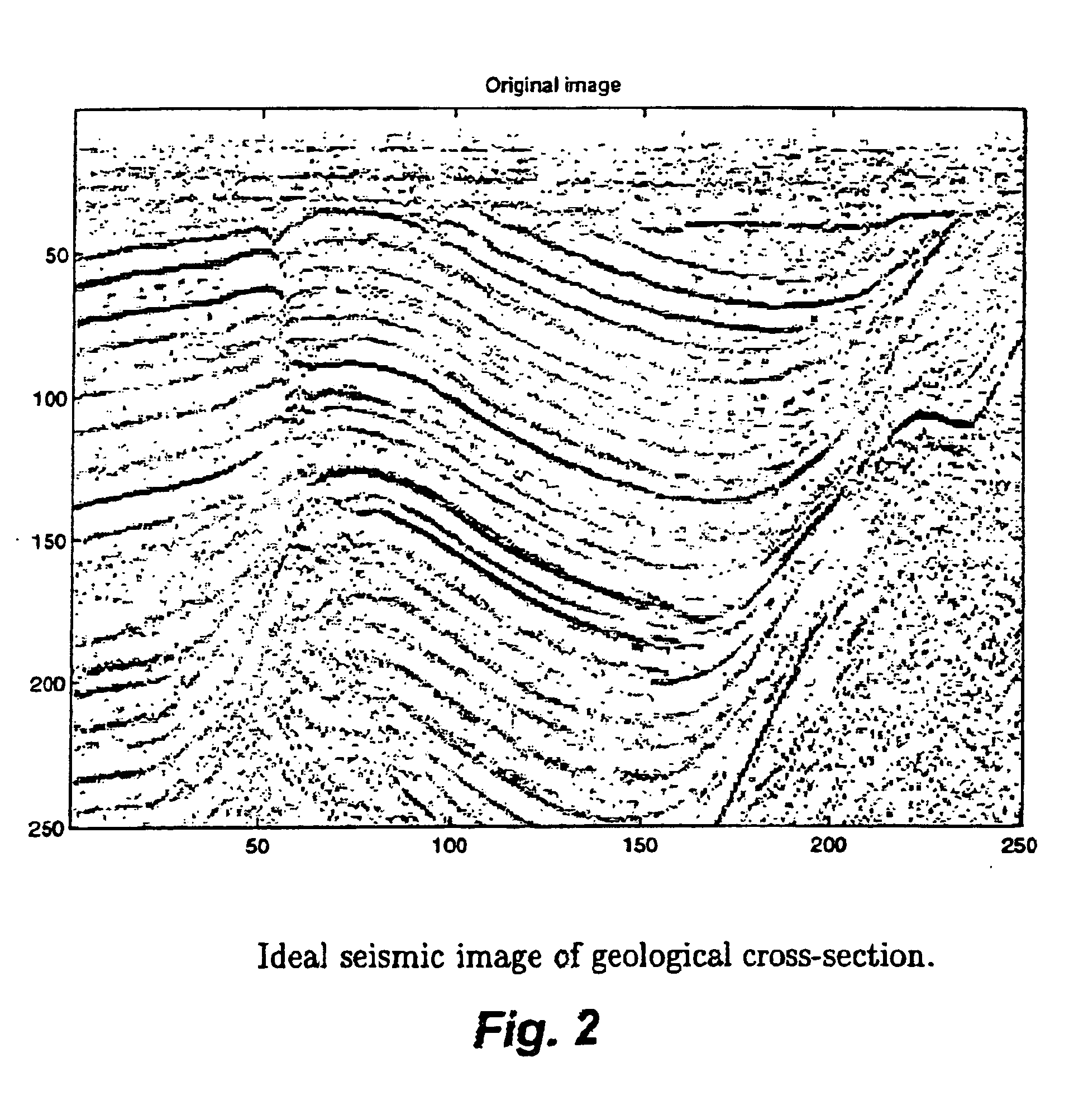

Method of digital image enhancement and sharpening

InactiveUS6879735B1MinimizesImage enhancementImage analysisRadiographic Image EnhancementPresent method

A method of digital image enhancement and sharpening (11, 12) which may be applied to restoration of blurred digital images of arbitrary origin. The method uses a specially formulated constraint (15) to reconstruct the original images. In particular, the constraint of the present method minimizes the area where strong image parameter variations and discontinuities occur. This new constraint is called a minimum gradient support (MGS) constraint. The MGS constraint generates a stable sharp solution of the linear ill-posed image restoration equation with an arbitrary blurring operator.

Owner:UNIV OF UTAH RES FOUND

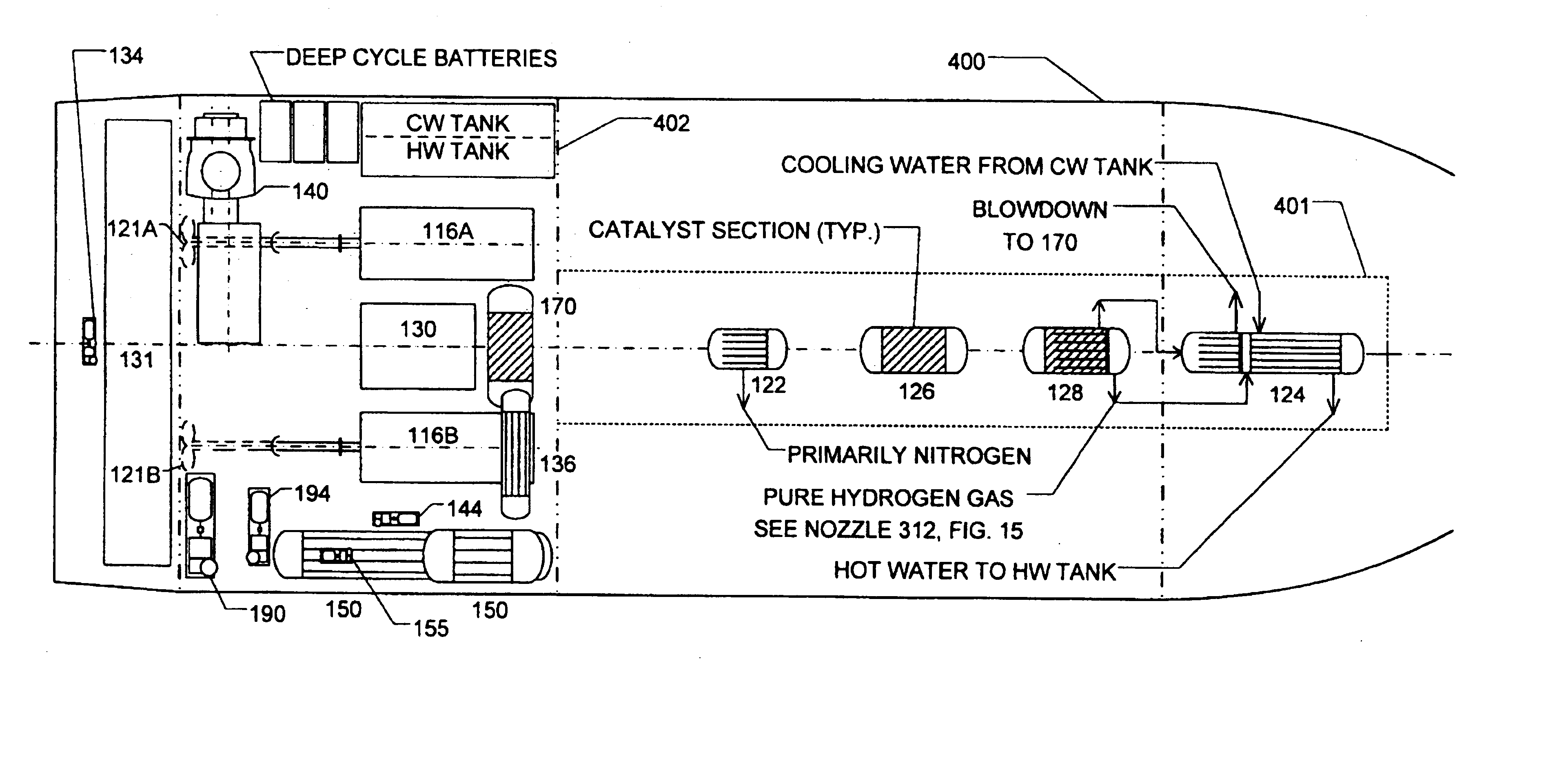

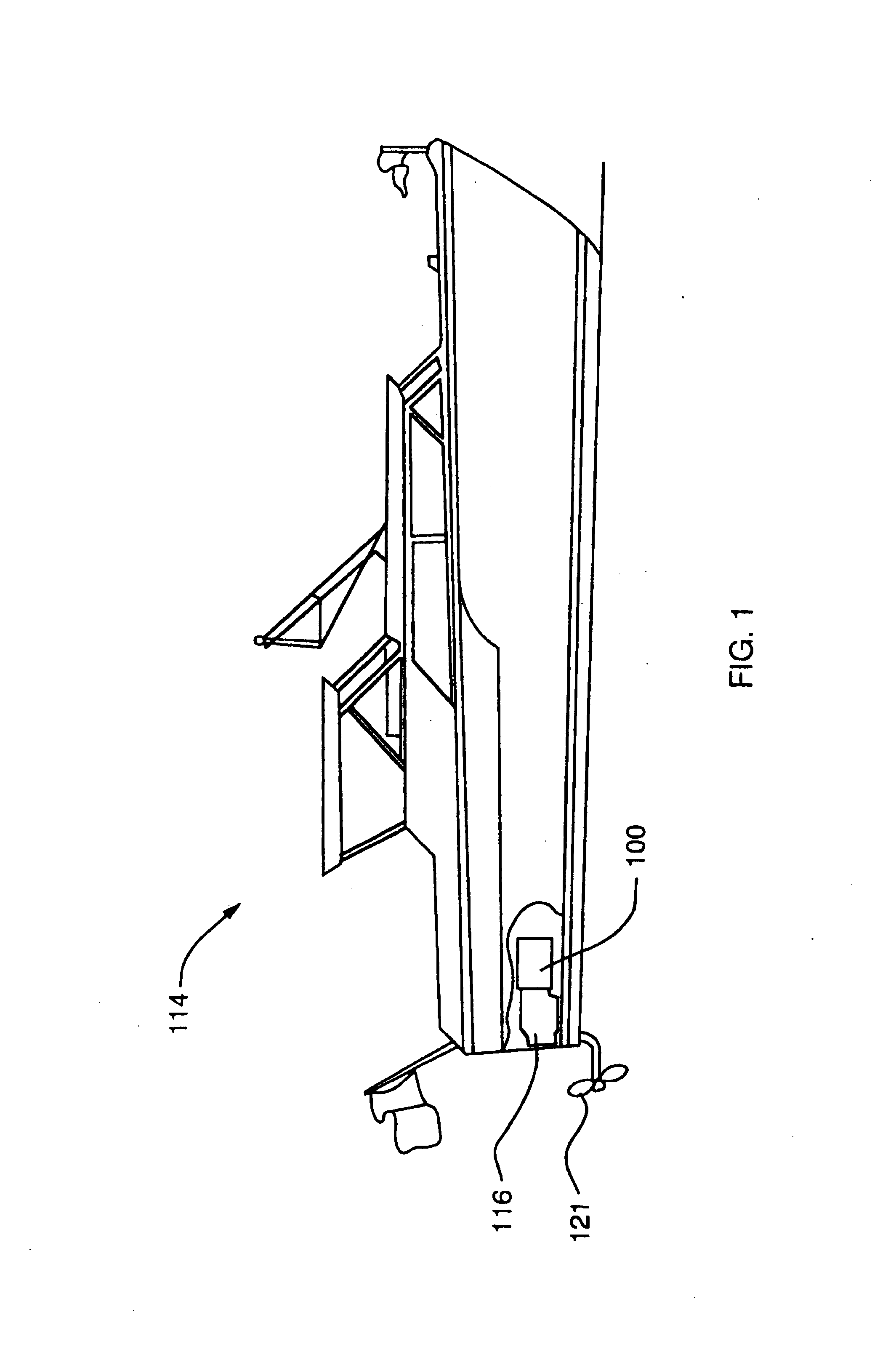

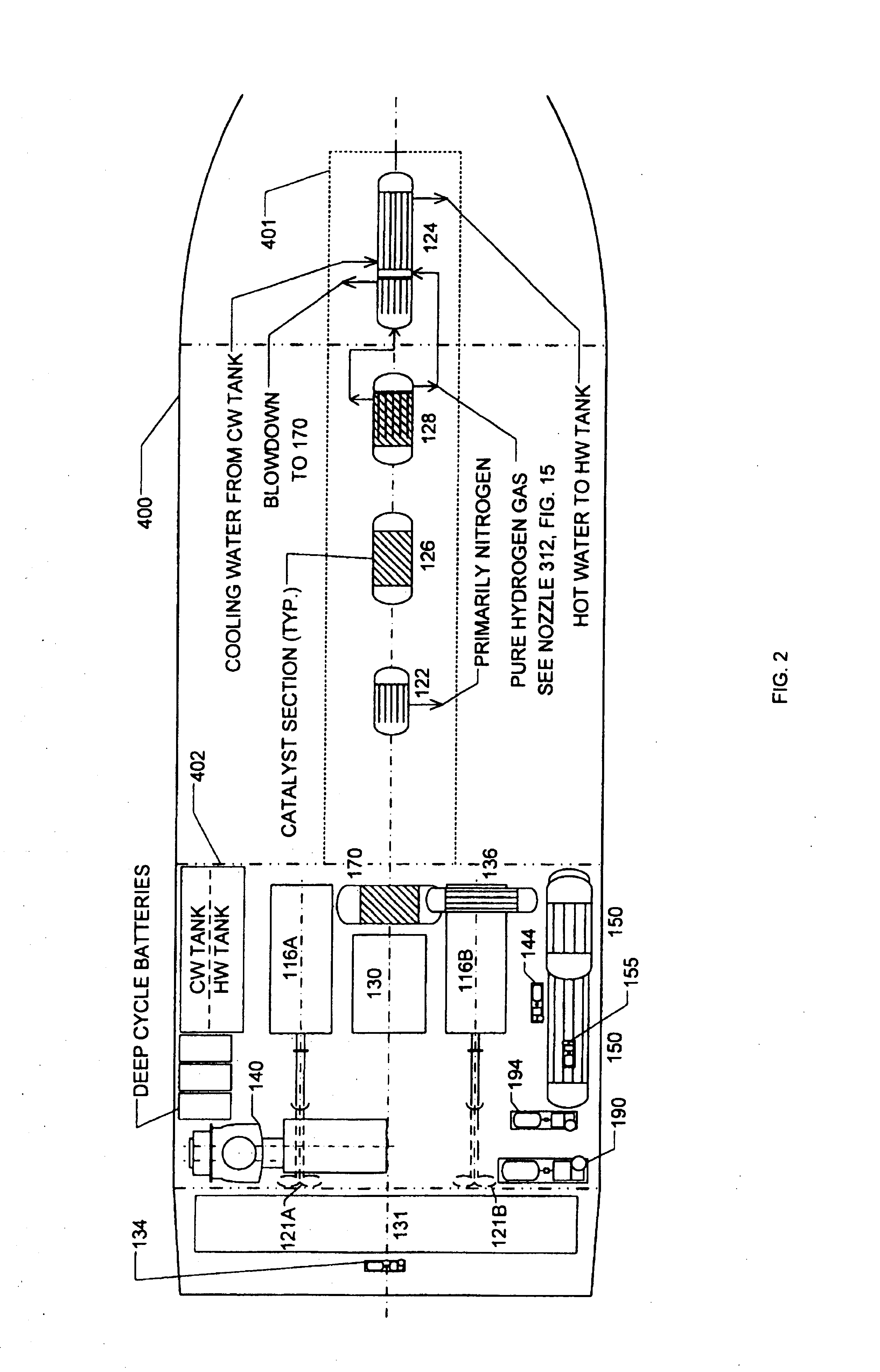

Fuel cell system with integrated fuel processor

InactiveUS20070122667A1MinimizesMaximize heat utilizationHydrogenOxygen/ozone/oxide/hydroxideBiodieselWater balance

A fuel cell system with fuel processor for integration with a marine vessel propulsion system. The system includes an auto thermal reactor that is the fuel processor for producing hydrogen from a fuel source. The fuel source is preferably ethanol or biodiesel or a mixture thereof, but can also be a sulfur containing fuel like petrodiesel of JP-8. The system further includes a gas-water shift reactor for further production and concentration of the hydrogen from the auto thermal reactor output. The system also includes a hydrogen permeable membrane separator for generating suitable quantities of essentially pure hydrogen to the fuel cell. The system also includes an oxygen permeable membrane separator for concentrating oxygen and reducing nitrogen to improve the partial pressure of hydrogen in subsequent fuel processing steps. The system contemplates the use of a Polymer Electrolyte Membrane (PEM) fuel cell. The system minimizes preheating of catalysts or other components to the extent just needed to initiate the fuel processor. To that end, heat sources and sinks of the system and associated usage systems are matched so as to minimize heat collection, storage and distribution systems. Water is recycled within the system to the extent necessary to maintain a water balance in the fuel processor and the fuel cell stack(s). The system includes cooling of the fuel cell stack(s) and integrated heat recovery with exothermic and endothermic catalysts. The fuel processor / fuel cell system components are configured to conform to and take advantage of the available space and limitations, such as the space constraints and opportunities associated with a marine vessel.

Owner:KELLEY RICHARD H

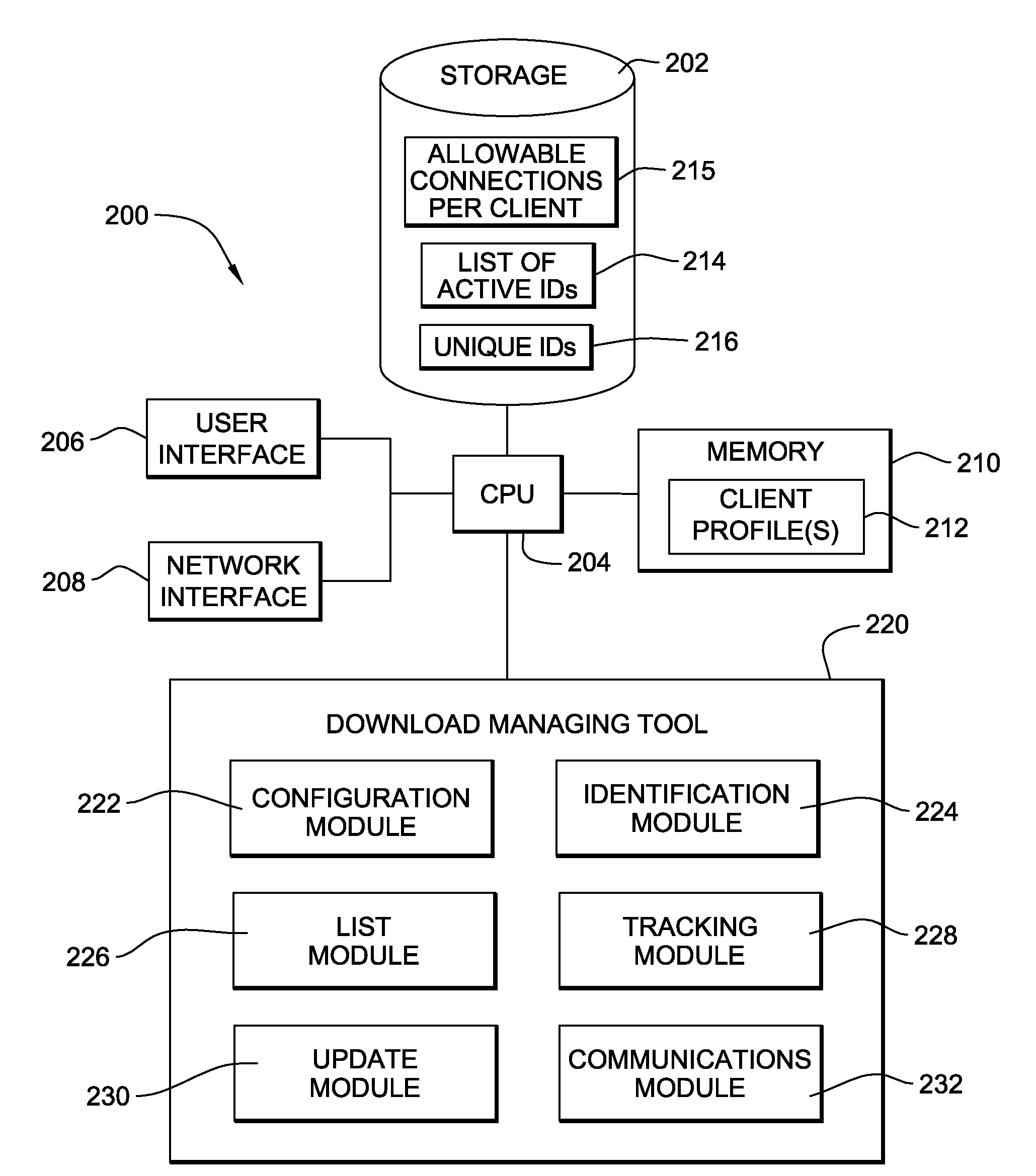

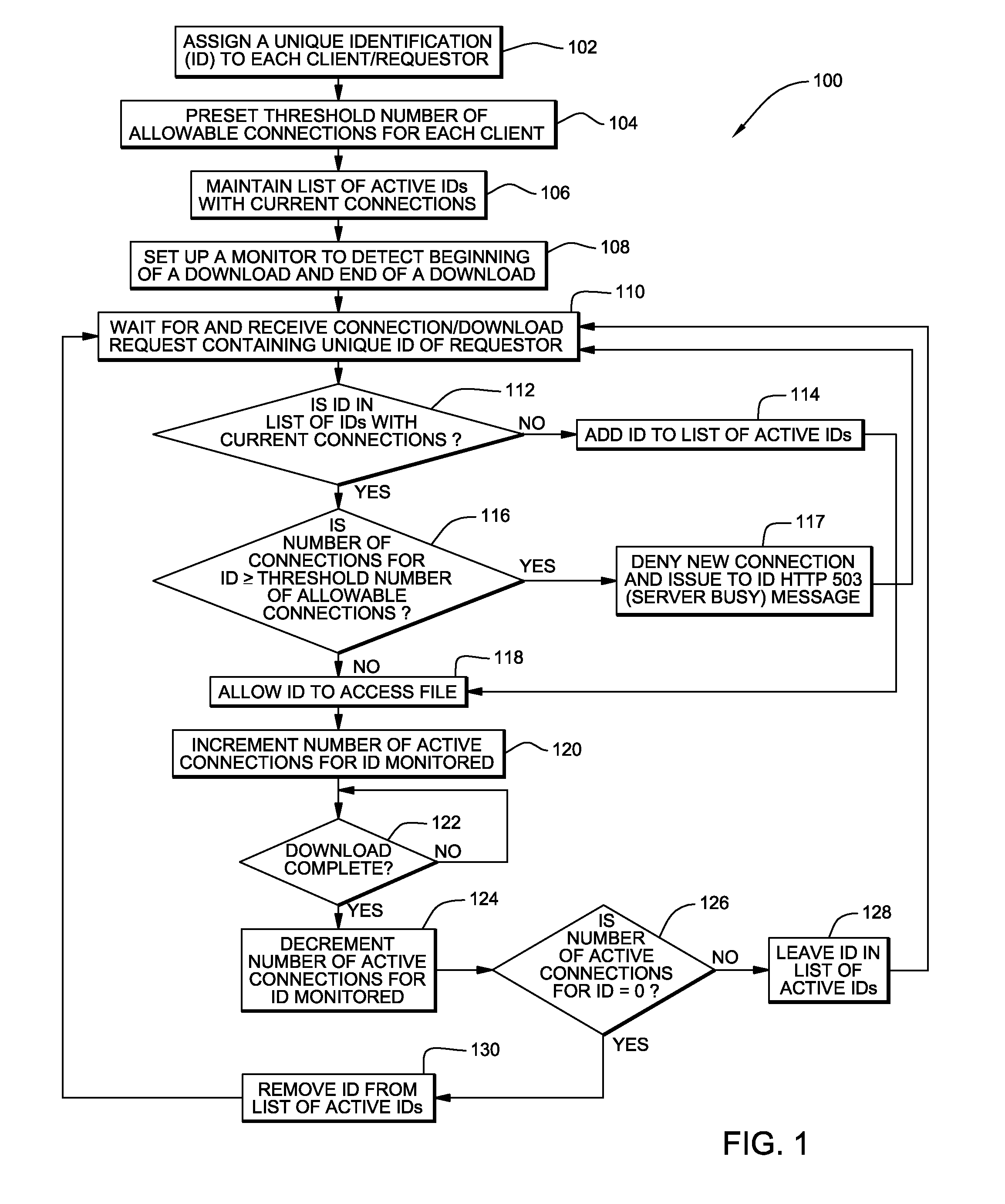

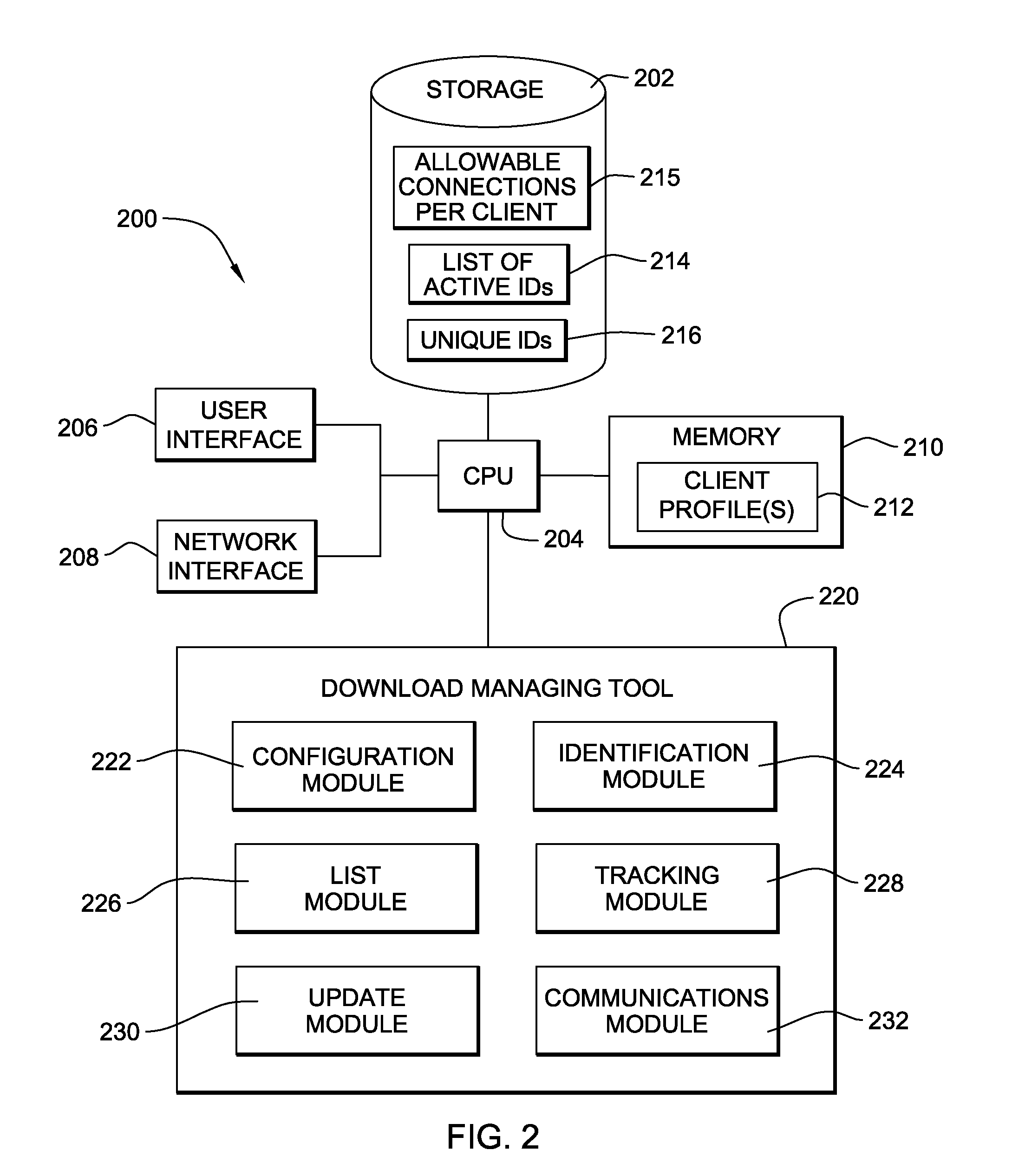

Method, system and program product for managing download requests received to download files from a server

InactiveUS20090024991A1MinimizesProgram loading/initiatingTransmissionClient-sideDistributed computing

A method, system and program product for managing downloads of files from a server. The method includes presetting, using a tool, a threshold number of allowable connections for each client requesting connections to download files from a server. The method further includes identifying, using the tool, a client requesting one or more connections to download a file and tracking, using the tool, whether or not the client has exceeded the threshold number of allowable connections preset. If the client has not exceeded the threshold number of allowable connections preset, allowing the one or more connections up to the threshold number of allowable connections preset for the client to download the file from the server and if the client has exceeded the threshold number of allowable connections preset, preventing the client from connecting to the server, such that overloading of the server with too many simultaneous active connections is minimized.

Owner:KYNDRYL INC

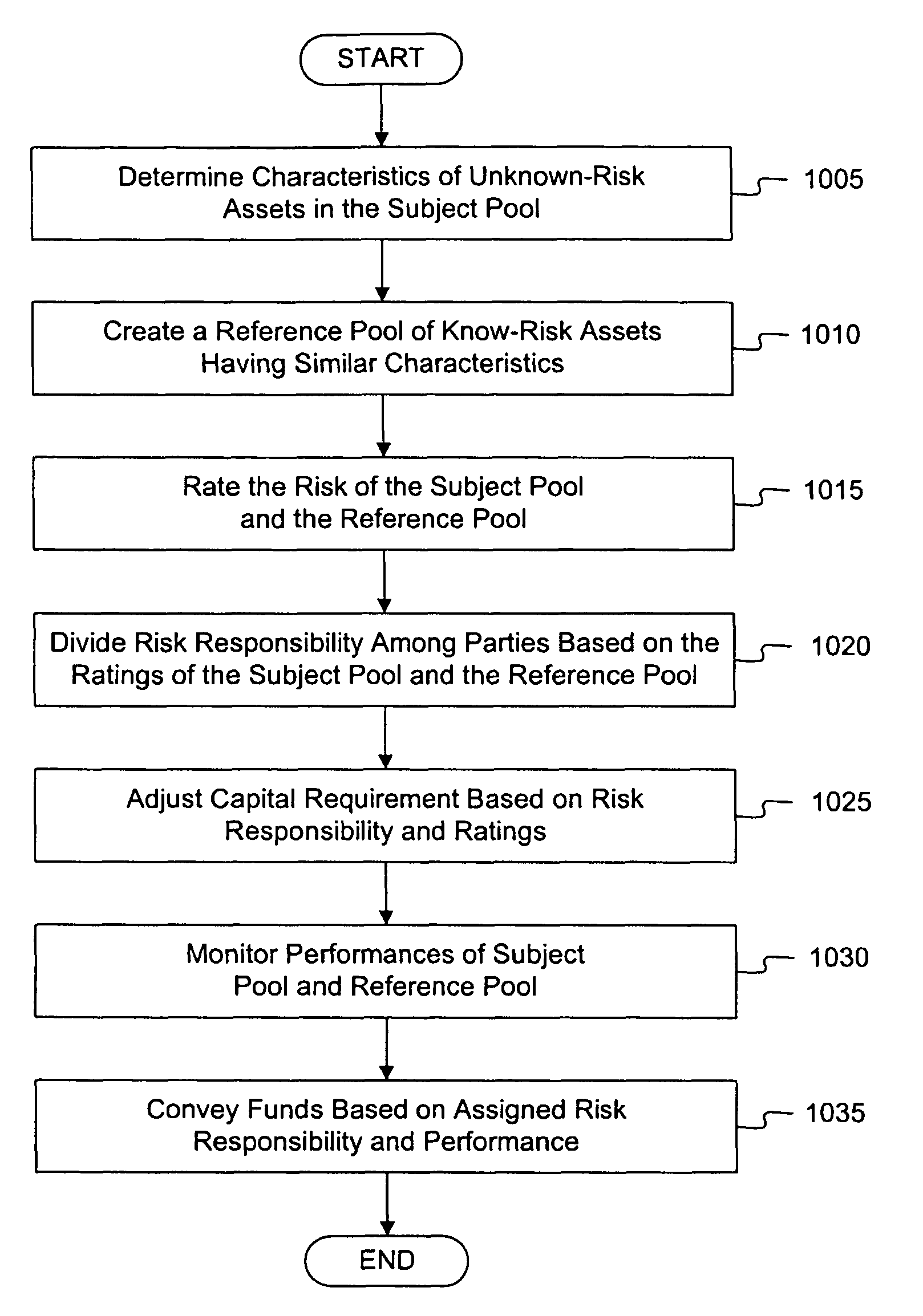

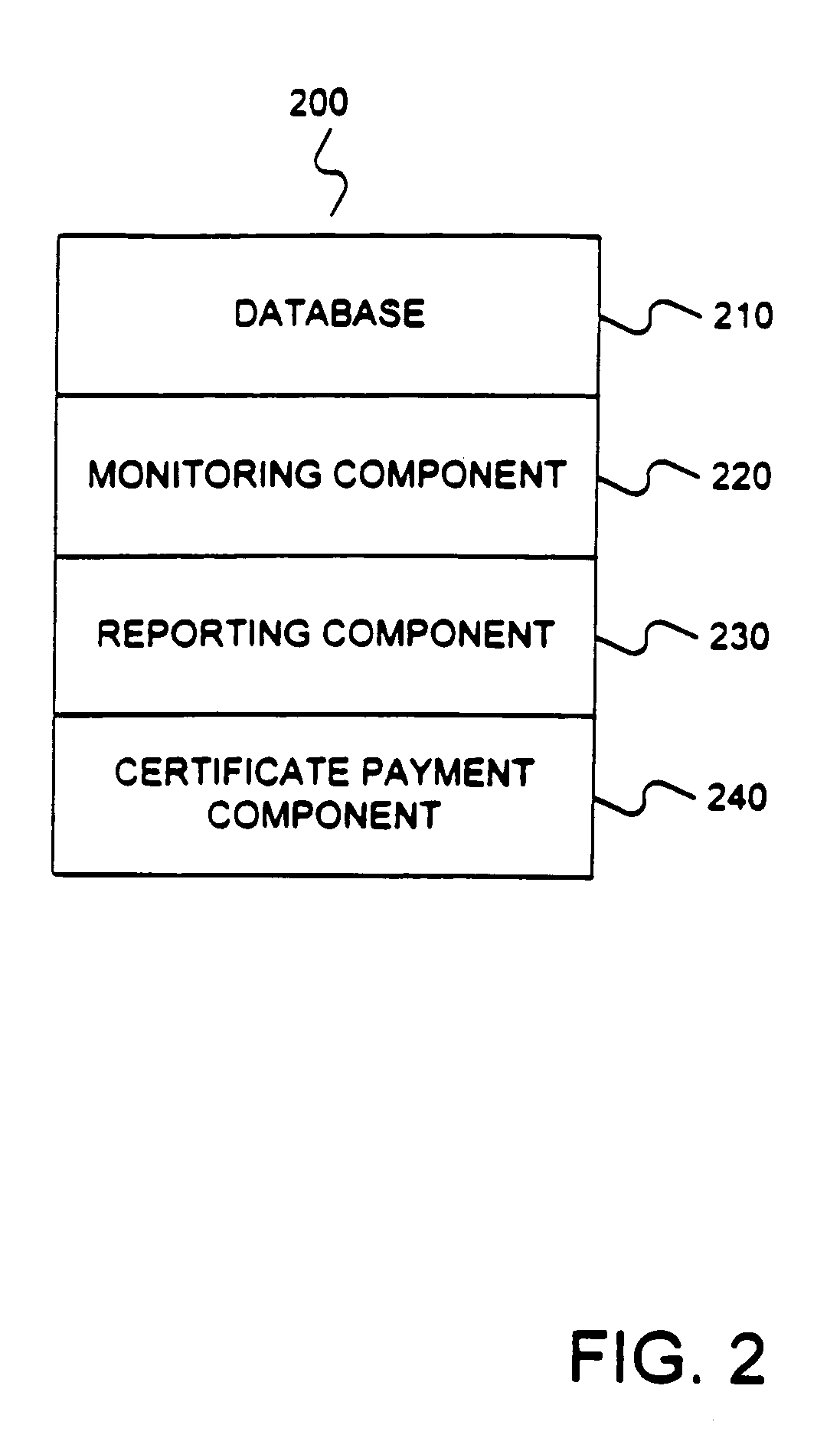

Risk-based reference pool capital reducing systems and methods

Embodiments consistent with the present invention provide a credit enhancement structure for risk allocation between parties that minimizes the regulatory capital reserve requirement impact to an institution subject to capital reserve requirement. A subject pool of assets held by the institution, such as a pool of loans, is rated to determine its risk levels. Based on the rated risk levels, a guarantor party agrees to be responsible for a portion of the risk associated with the pool of assets, which may define the maximum risk exposure of the institution holding the asset pool. The risk-rated capital reserve requirements are applied to the asset pool based on the risk level rating and the guarantor's agreed upon risk responsibility such that the institution holds a reduced amount of reserve capital compared to what it would otherwise be required to hold.

Owner:HEUER JOAN D +6

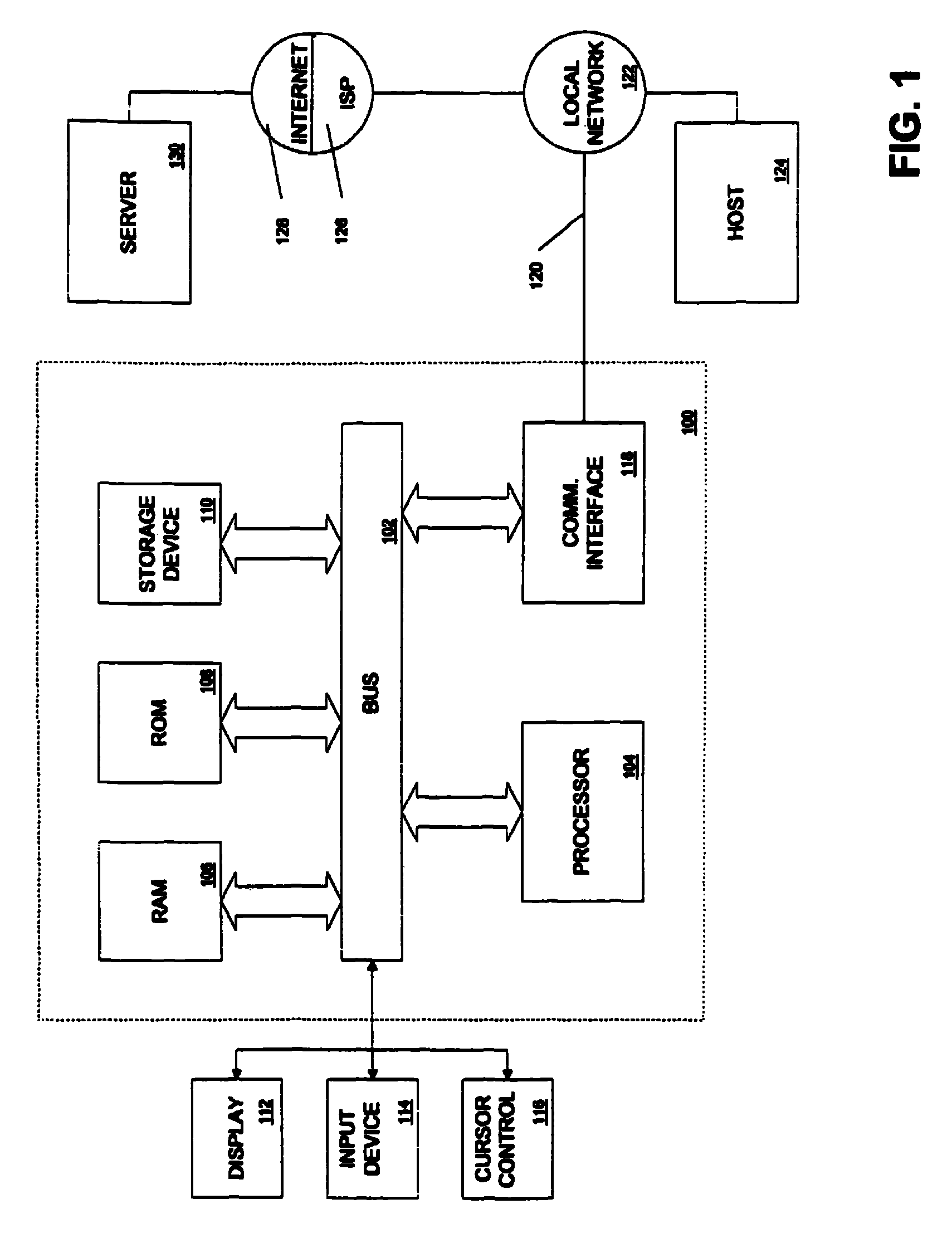

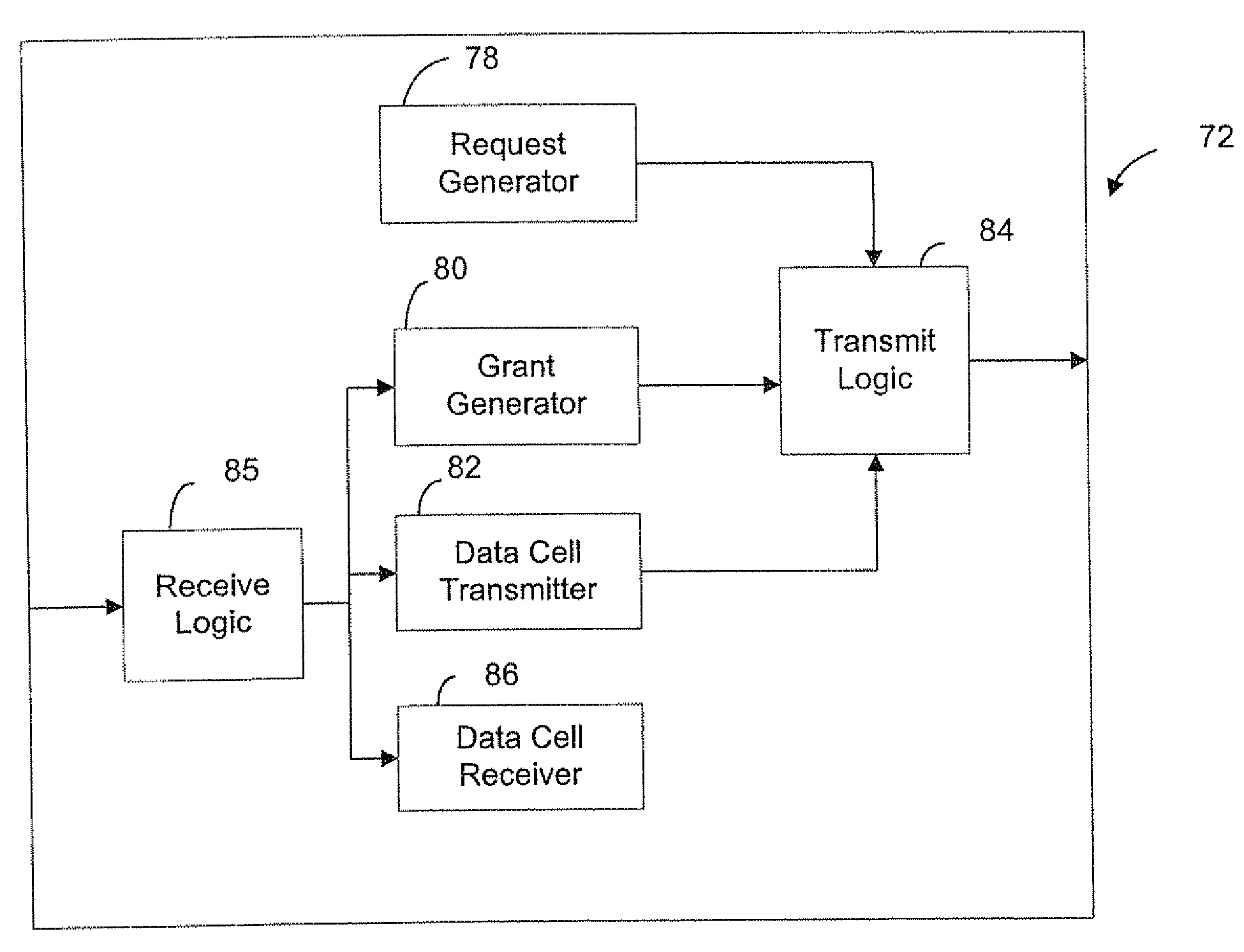

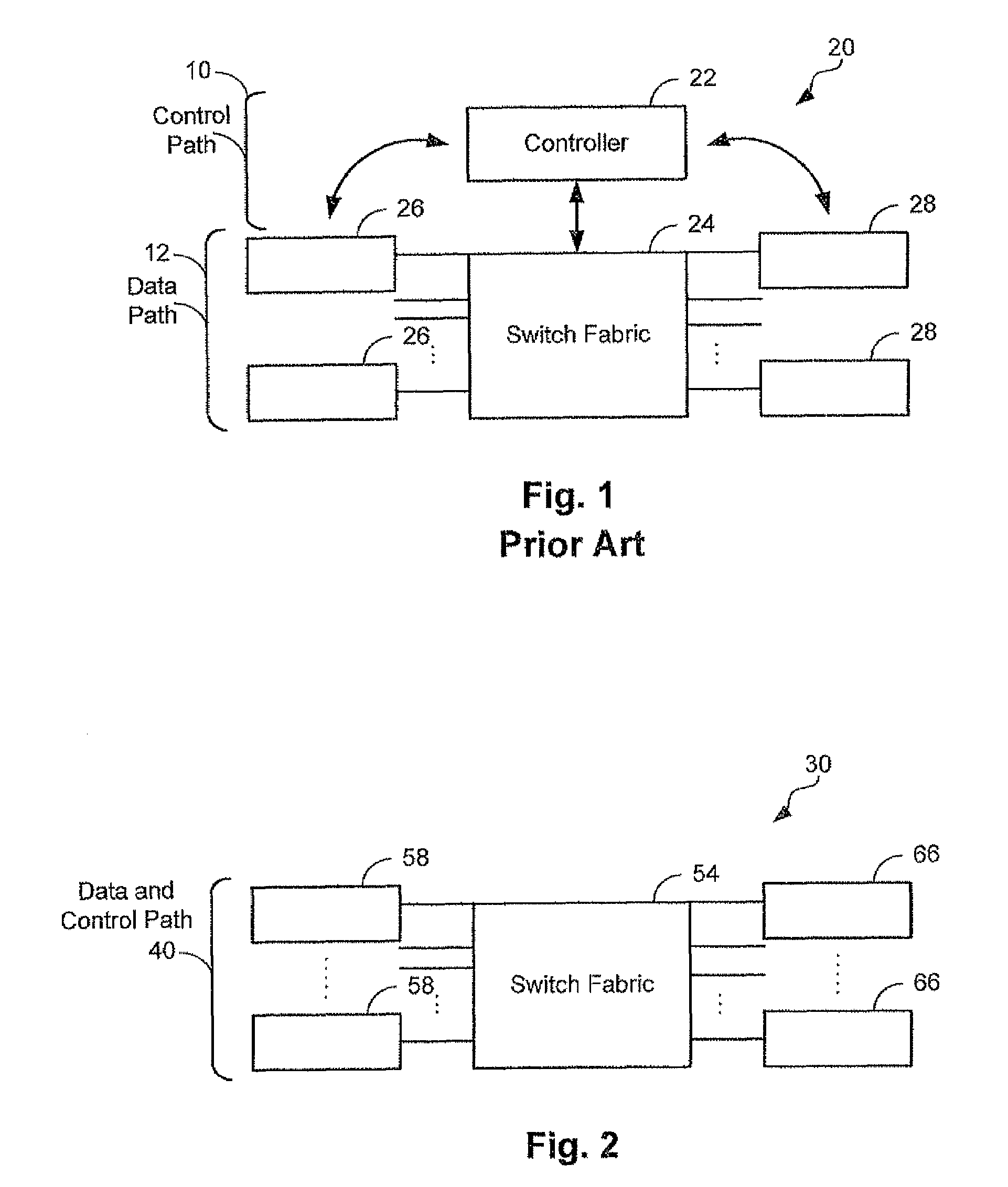

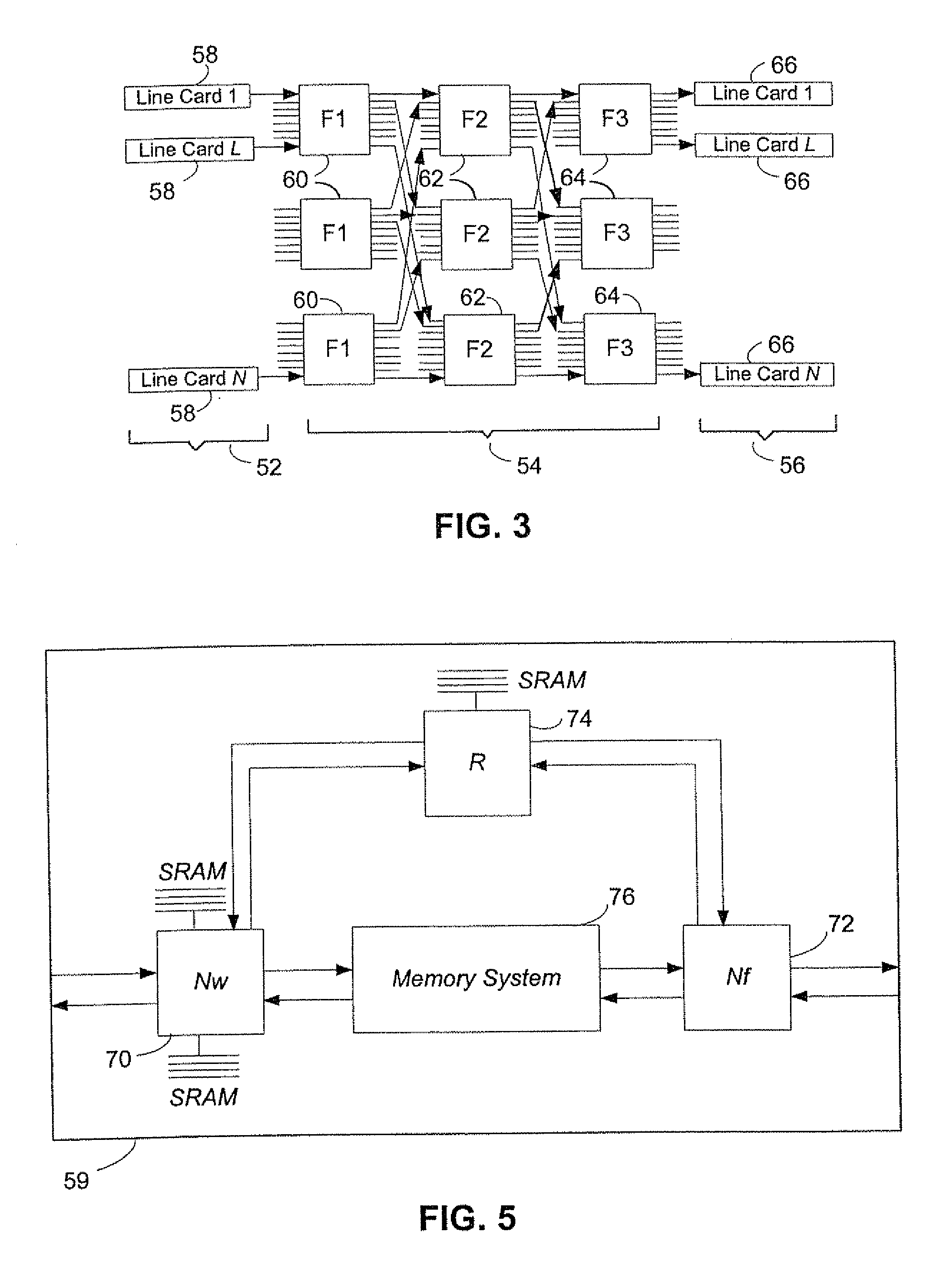

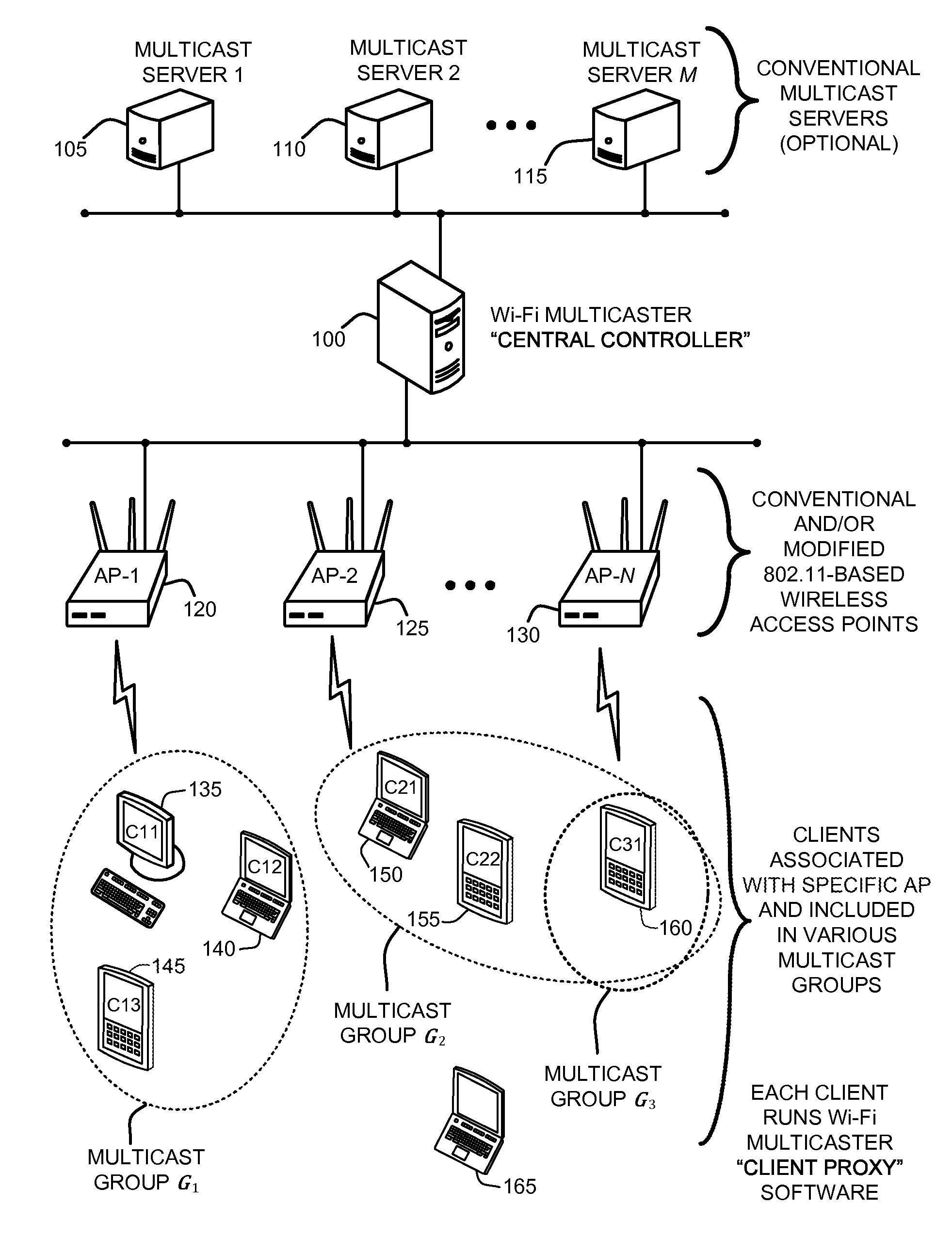

Switching device

InactiveUS7342887B1MinimizesLess storageError preventionTransmission systemsComputer hardwareLine card

A switching device in a network system for transferring data includes one or more source line cards, one or more destination line cards and a switching fabric coupled to the source line cards and the destination line cards to enable data communication between any source line card and destination line card. Each source line card includes a request generator to generate a request signal to be transmitted in order to obtain an authorization to transmit data. Each destination line card includes a grant generator to generate and send back a grant signal to the source line card in response to the request signal received at the destination line card to authorize the source line card to transmit a data cell to the destination line card.

Owner:JUMIPER NETWORKS INC

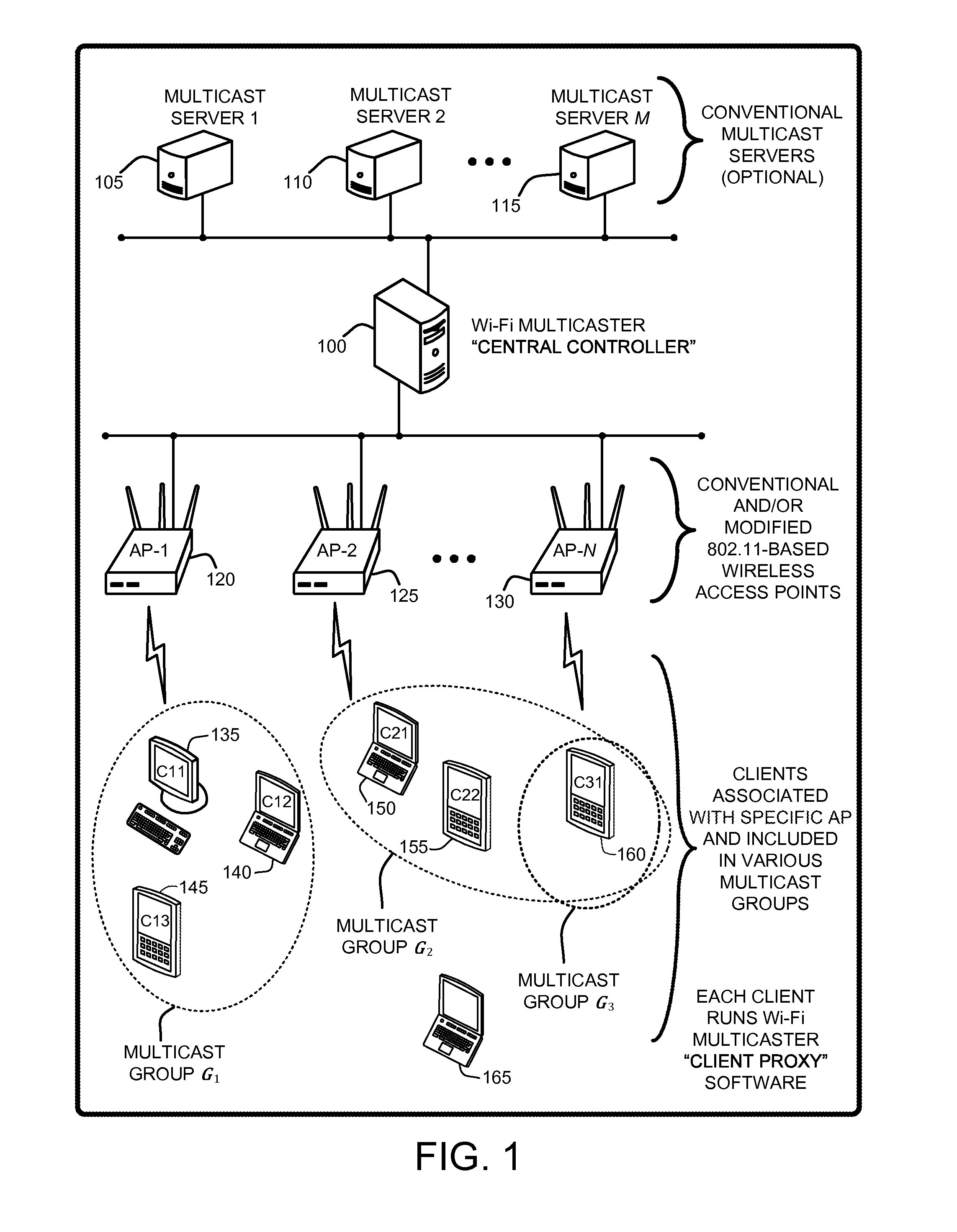

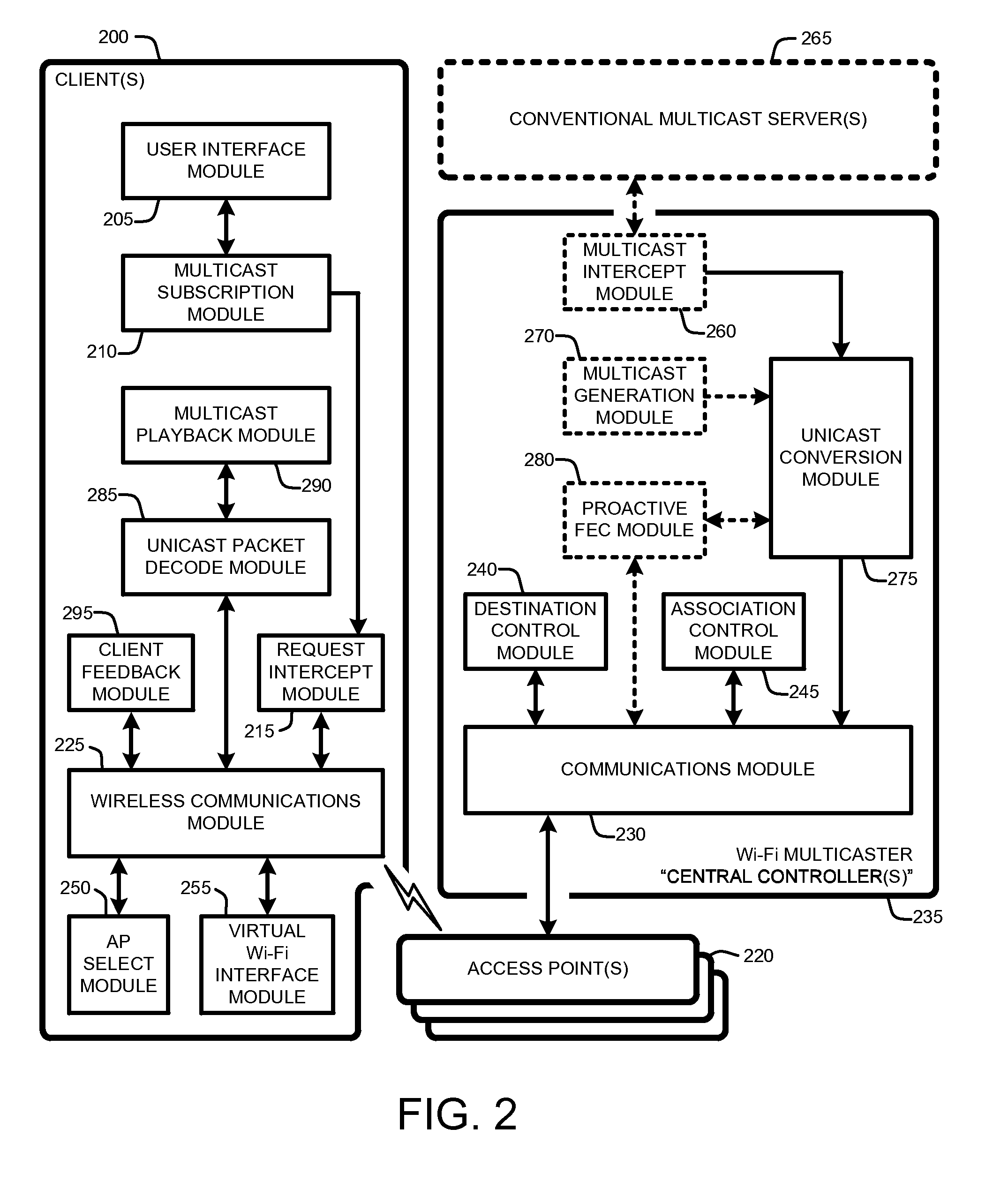

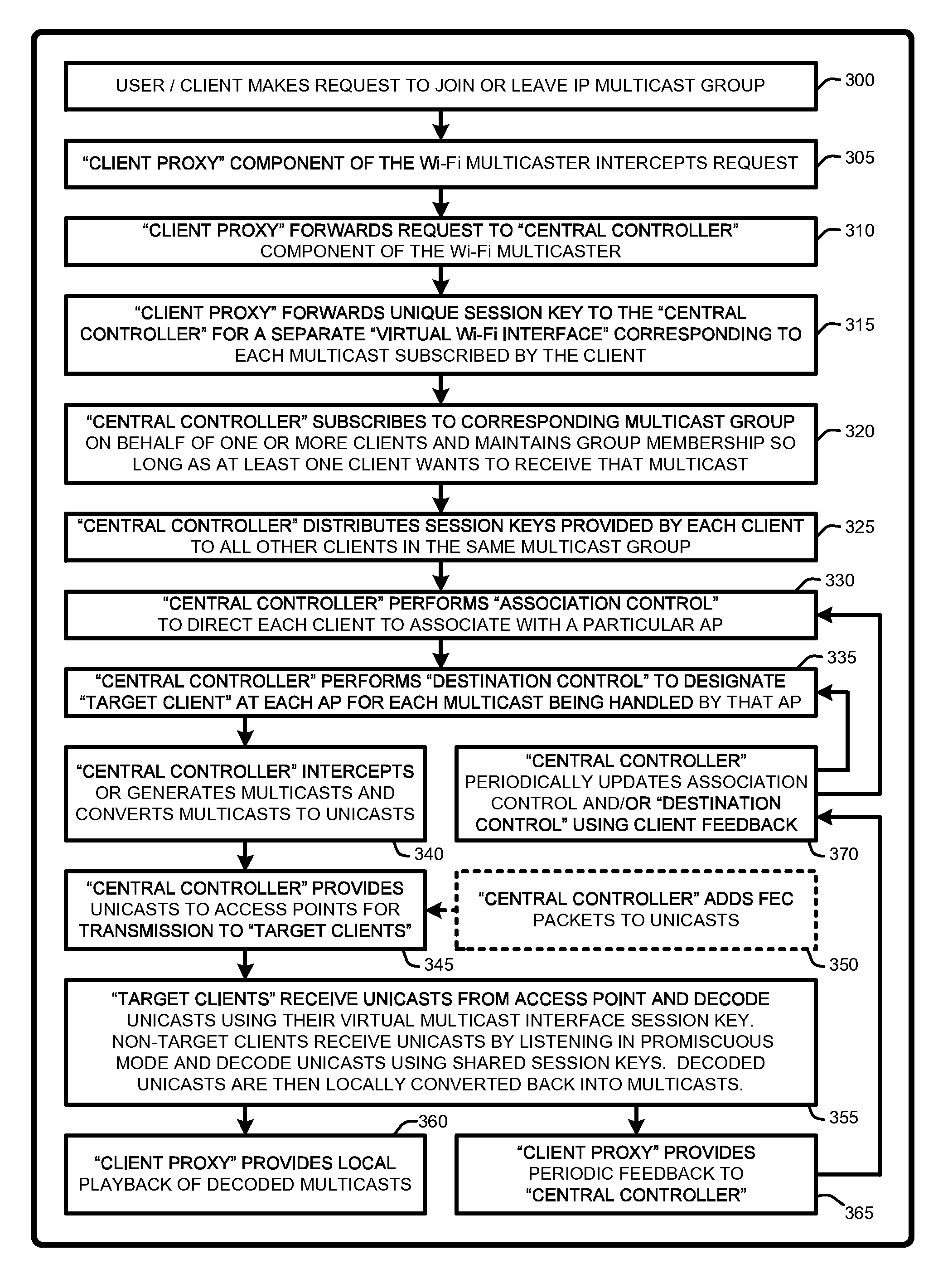

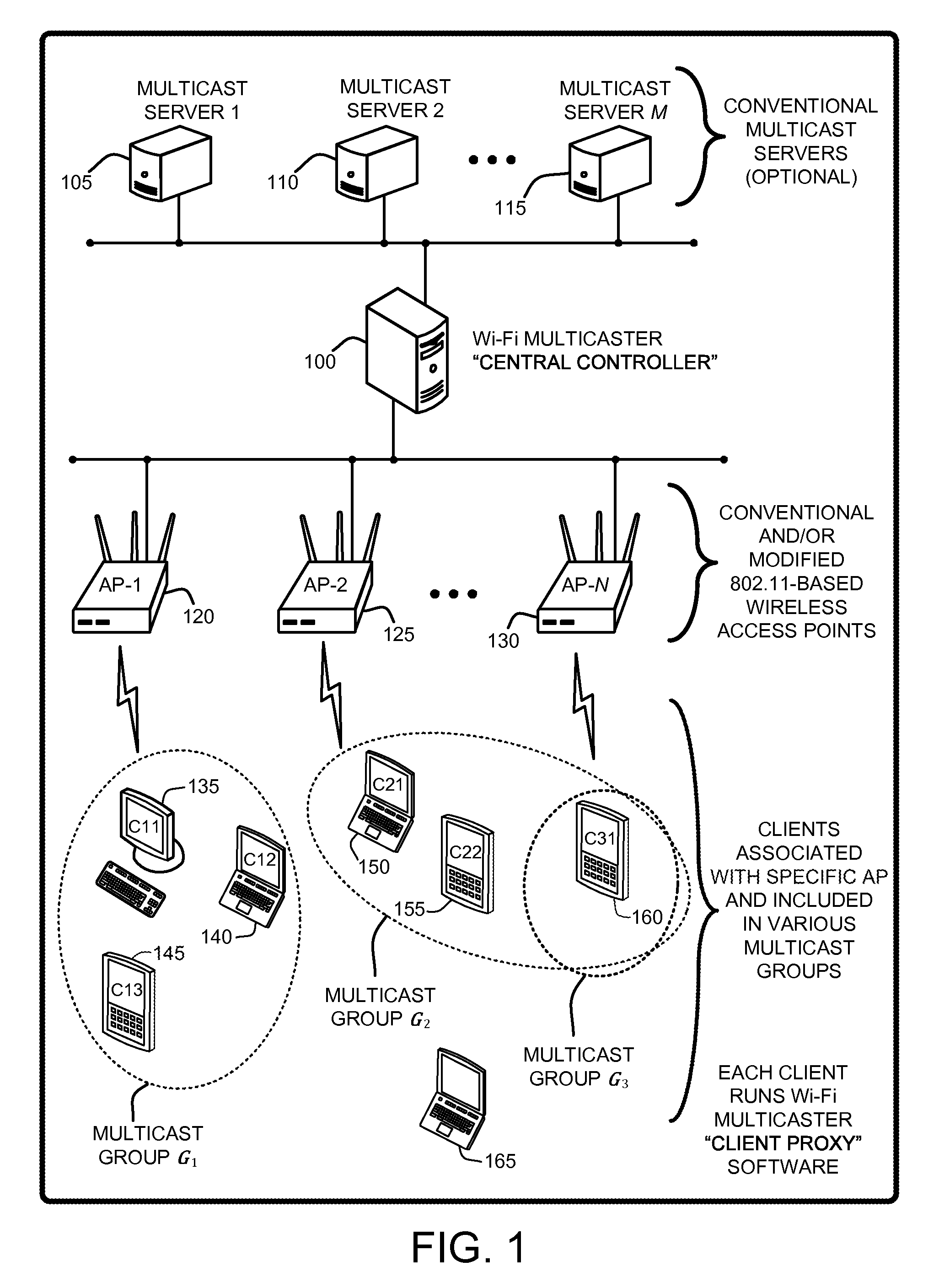

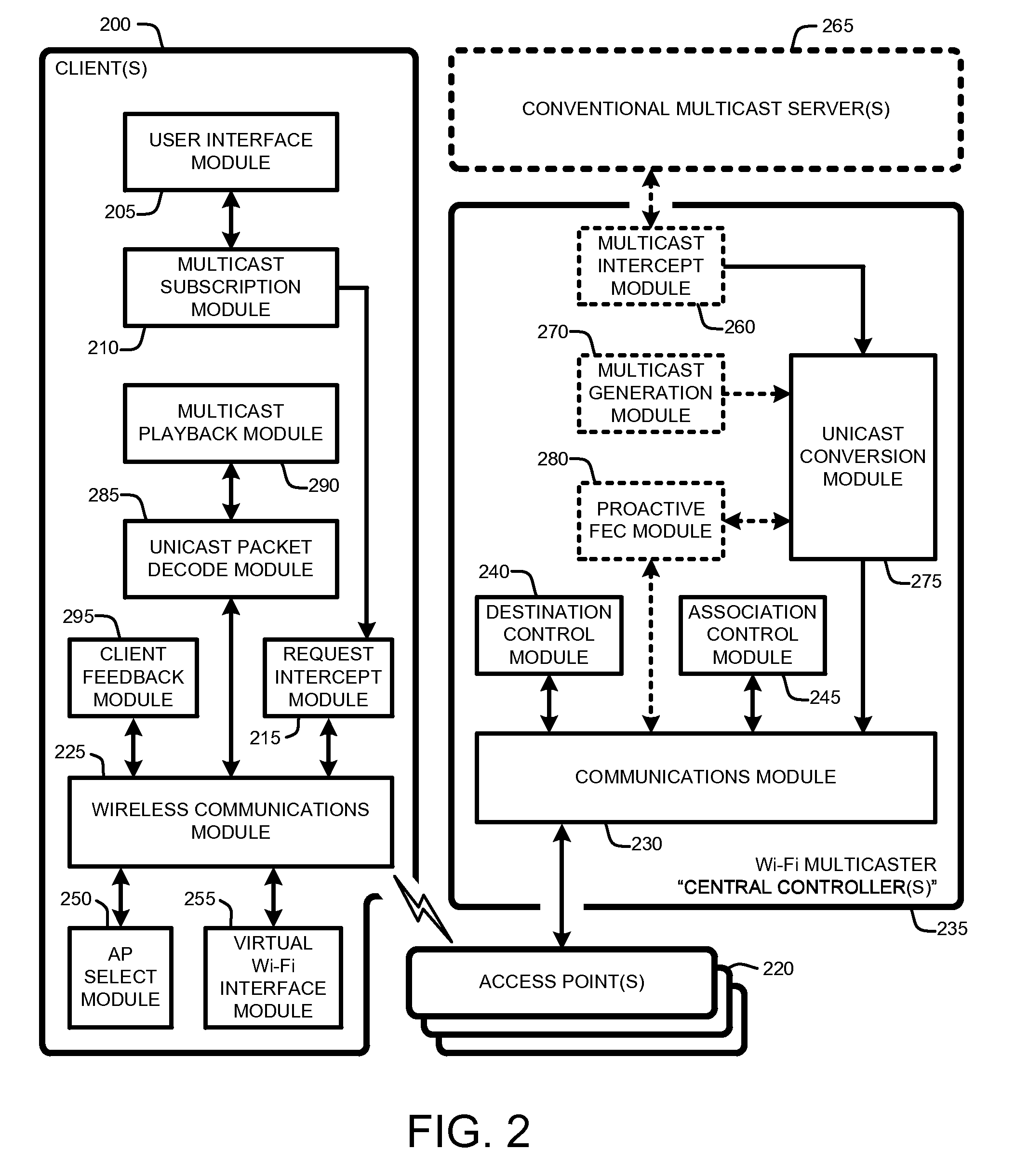

EFFICIENT AND RELIABLE MULTICAST OVER A Wi-Fi NETWORK

ActiveUS20110211517A1Reduce lossesLittle overheadError prevention/detection by using return channelBroadcast specific applicationsWi-FiPacket loss

A “Wi-Fi Multicaster” provides a practical and efficient Wi-Fi multicast system for environments having potentially large numbers of Wi-Fi clients. Significantly, the Wi-Fi Multicaster does not require any changes to the 802.11 protocol, or to the underlying Wi-Fi infrastructure. In various embodiments, the Wi-Fi Multicaster uses pseudo-broadcast, and augments it with destination control, association control and optional proactive FEC (forward error correction) to improve multicast performance. More specifically, the Wi-Fi Multicaster system converts multicast packets to targeted unicast transmissions. To minimize the amount of airtime consumed, the Wi-Fi Multicaster uses destination control in combination with various algorithms for association control. Further, in various embodiments, the Wi-Fi Multicaster includes an adaptive, proactive FEC scheme to reduce overall packet losses. Finally, to overcome the challenges posed by encryption protocols such as 802.1x, the Wi-Fi Multicaster uses a “virtual multicast interface” that allows clients to “share” a common key for each multicast.

Owner:MICROSOFT TECH LICENSING LLC

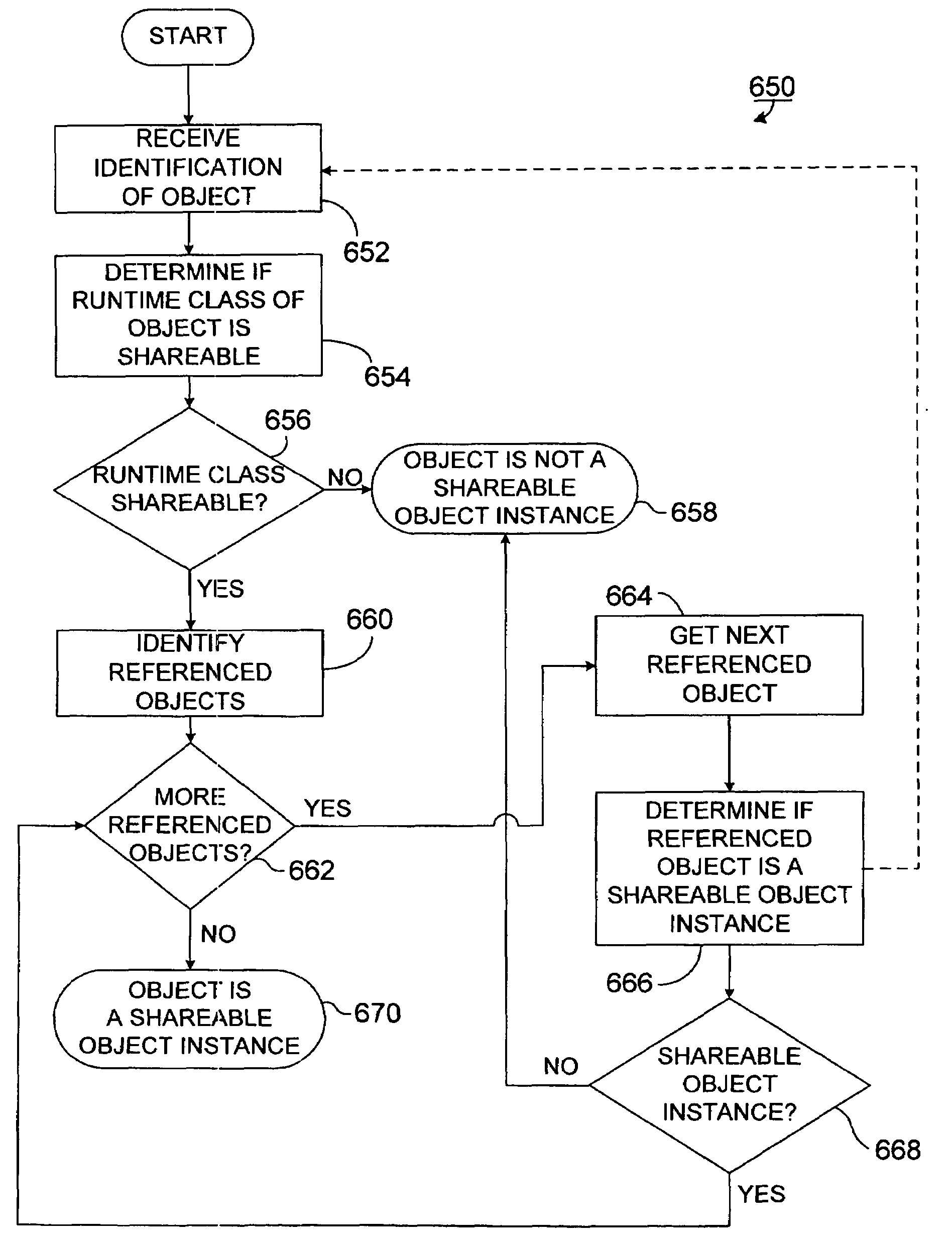

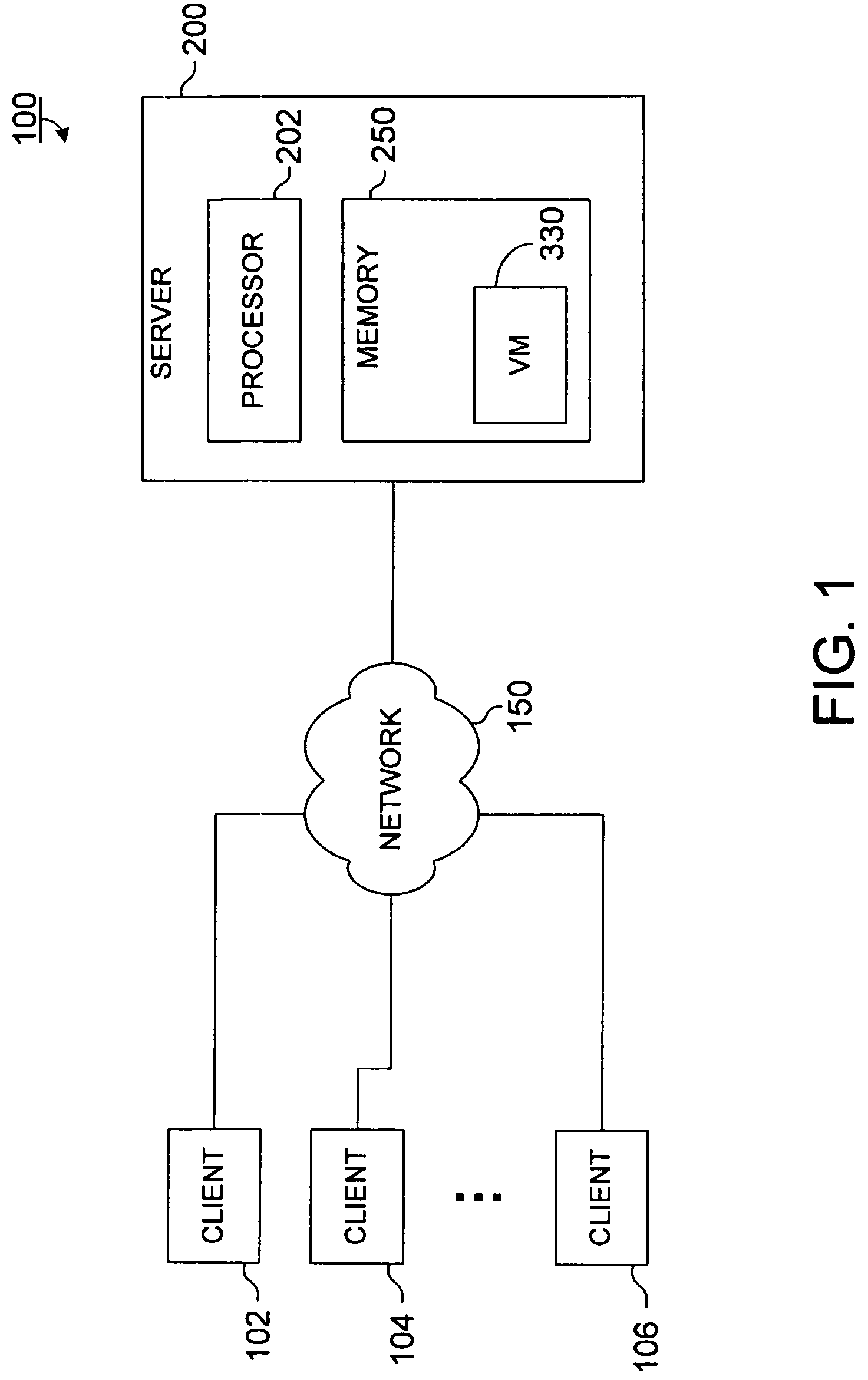

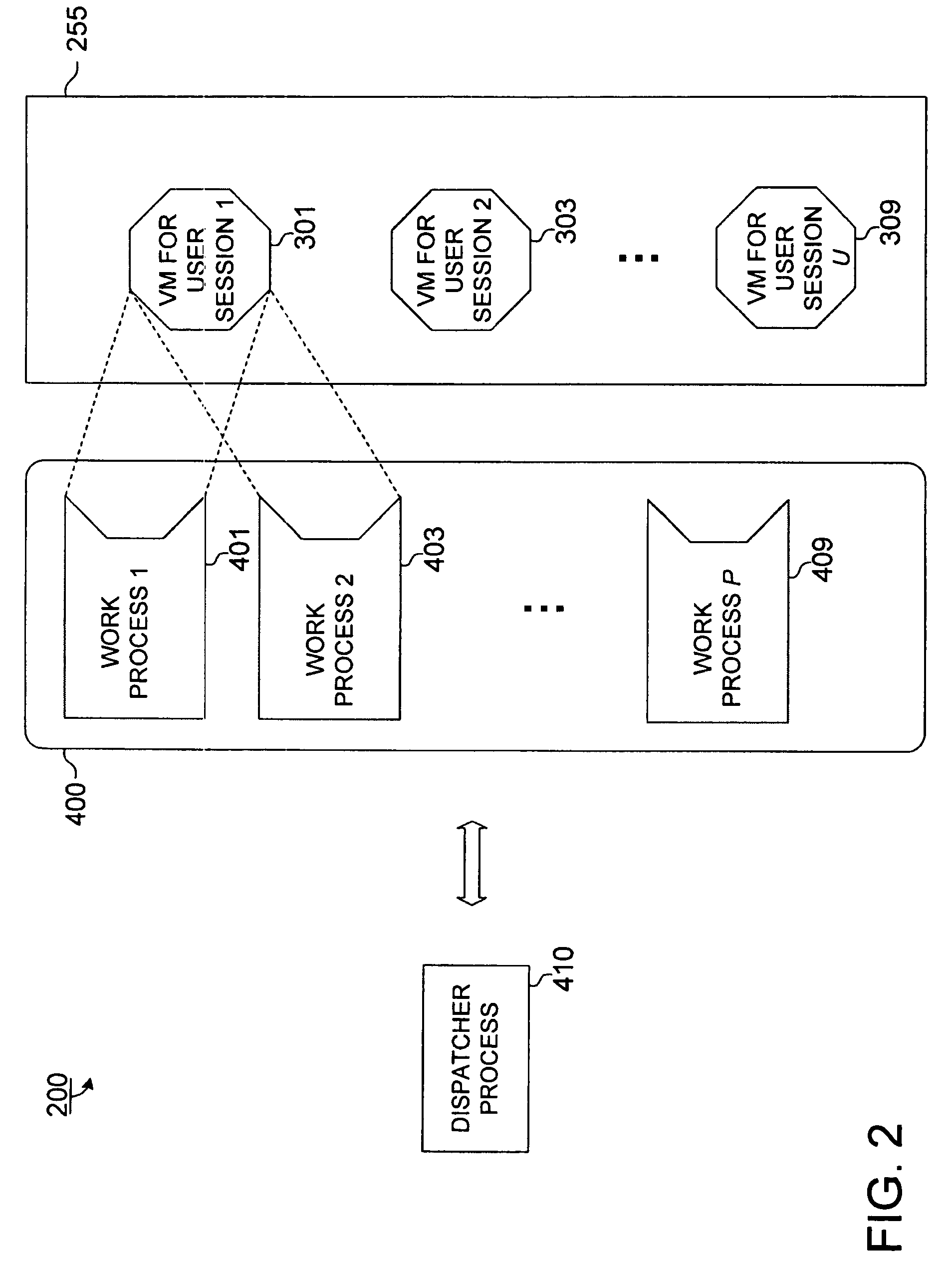

Sharing objects in runtime systems

ActiveUS7415704B2Limited accessAvoid dataMultiprogramming arrangementsSpecific program execution arrangementsComputerized systemSerialization

Methods and apparatus, including computer systems and program products, for sharing data objects in runtime systems. An identification of a first data object in a first runtime system is received. The first data object references zero or more referenced data objects. A shared closure of data objects, which consists of the first data object and a transitive closure of the referenced data objects, is identified, and a determination is made as to whether the shared closure of data objects is usable in a second runtime system. In some implementations, determining whether a shared closure is usable in a second runtime system includes determining whether each data object in the shared closure is serializable without execution of custom code, or determining whether the runtime class of each object instance in the shared closure is shareable. Using shared closures to share objects between runtime systems can provide isolation between user sessions.

Owner:SAP AG

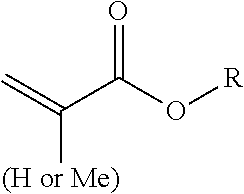

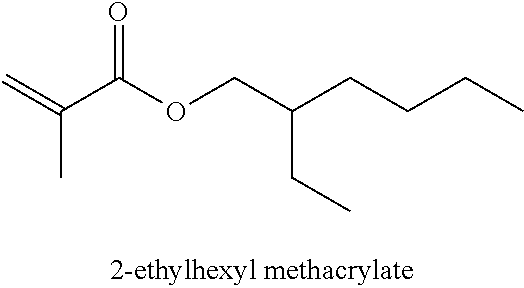

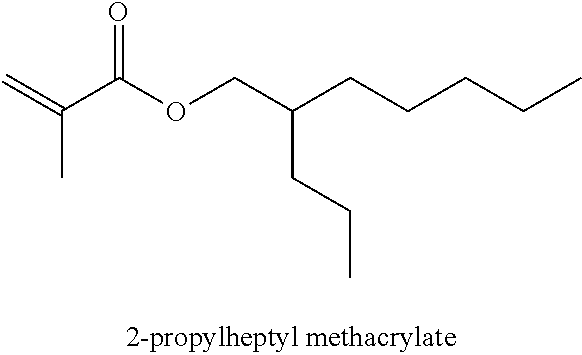

Lubricant composition having improved non-newtonian viscometrics

ActiveUS20120245068A1Preventing and minimizingImproves low temperature non-Newtonian viscometricsAdditivesViscosity indexBase oil

A lubricant composition having improved non-Newtonian viscometrics includes at least 85 weight percent of a base oil and 1 to 15 weight percent of a lubricant additive. The additive itself includes 10 to 80 weight percent of a diluent oil and 30 to 80 weight percent of a random co-polymeric viscosity index improver. The viscosity index improver is the free-radical polymerization product of at least 5 to 15 weight percent methyl methacrylate and 5 to 95 weight percent of a C8-C10 alkyl (meth)acrylate. The additive is formed using a method that includes the step of providing the diluent oil, the methyl methacrylate, the C8-C10 alkyl (meth)acrylate, and a free-radical initiator. The method also includes the steps of flowing the diluent oil into a reactor, flowing the methyl methacrylate and the C8-C10 alkyl (meth)acrylate into the reactor independently from the free-radical initiator, and flowing the free-radical initiator into the reactor.

Owner:BASF AG

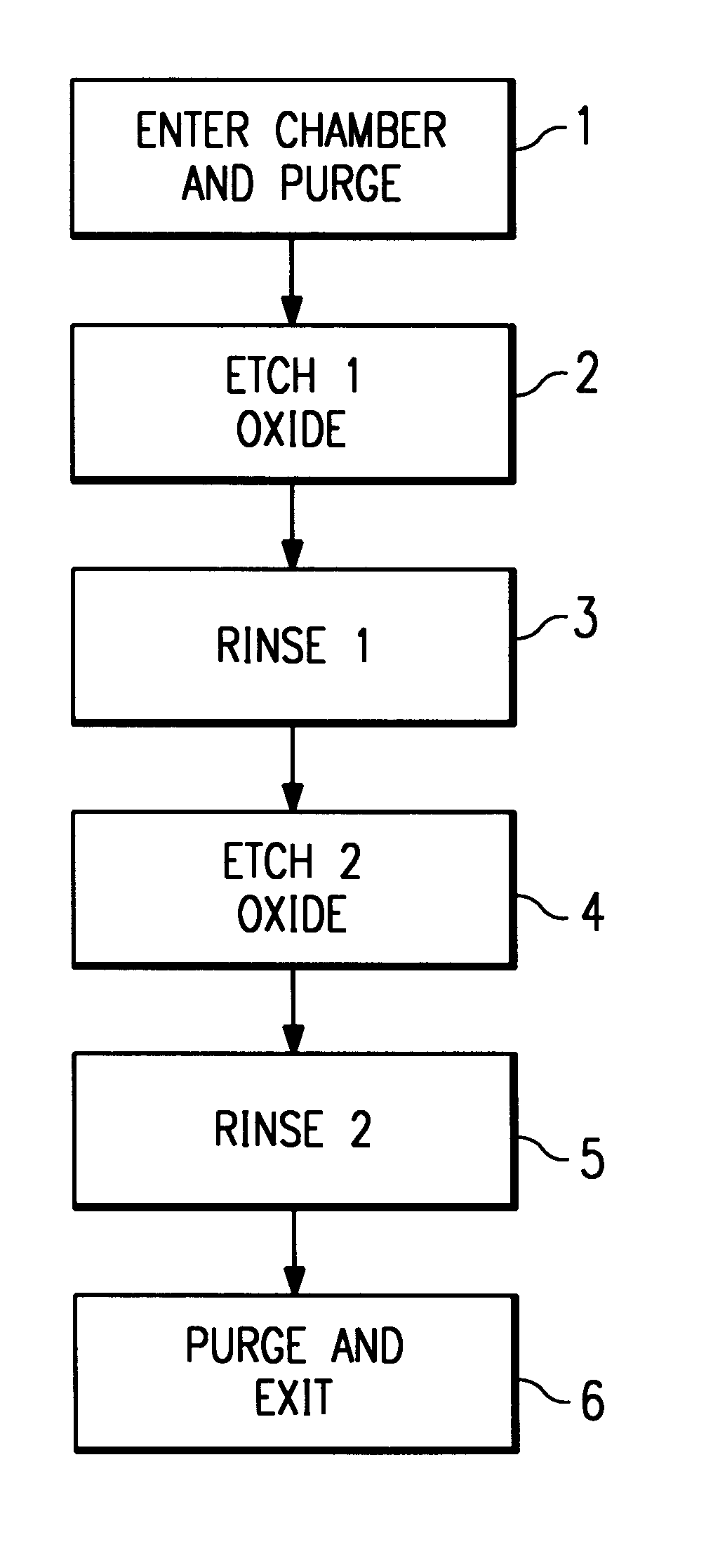

Two step oxide removal for memory cells

InactiveUS6174817B1Reduce particlesMinimizesTransistorSolid-state devicesHydrofluoric acidWater vapor

Hydrofluoric acid (HF) mixed with water and often buffered with ammonium fluoride is a standard silicon dioxide wet etchant which is followed by a rinse. An improved silicon dioxide etch is vapor HF which may be followed by a water vapor rinse. The invention discloses a further improved silicon dioxide etch. Following an initial exposure to vapor HF for oxide removal, a first insitu water rinse occurs. A second exposure to vapor HF then occurs and is followed by a second insitu water rinse. Water, rather than water vapor, aids in freeing particles from the wafer surface. During both the water rinses, the wafer may be rotated at increasing speeds to aid in sweeping particles from wafer surface. The process may be practiced in a commercially available reactor and is suitable for ULSI devices having complex topographies, such as, for example, 64 megabit DRAMs employing crown type memory cells.

Owner:TEXAS INSTR INC

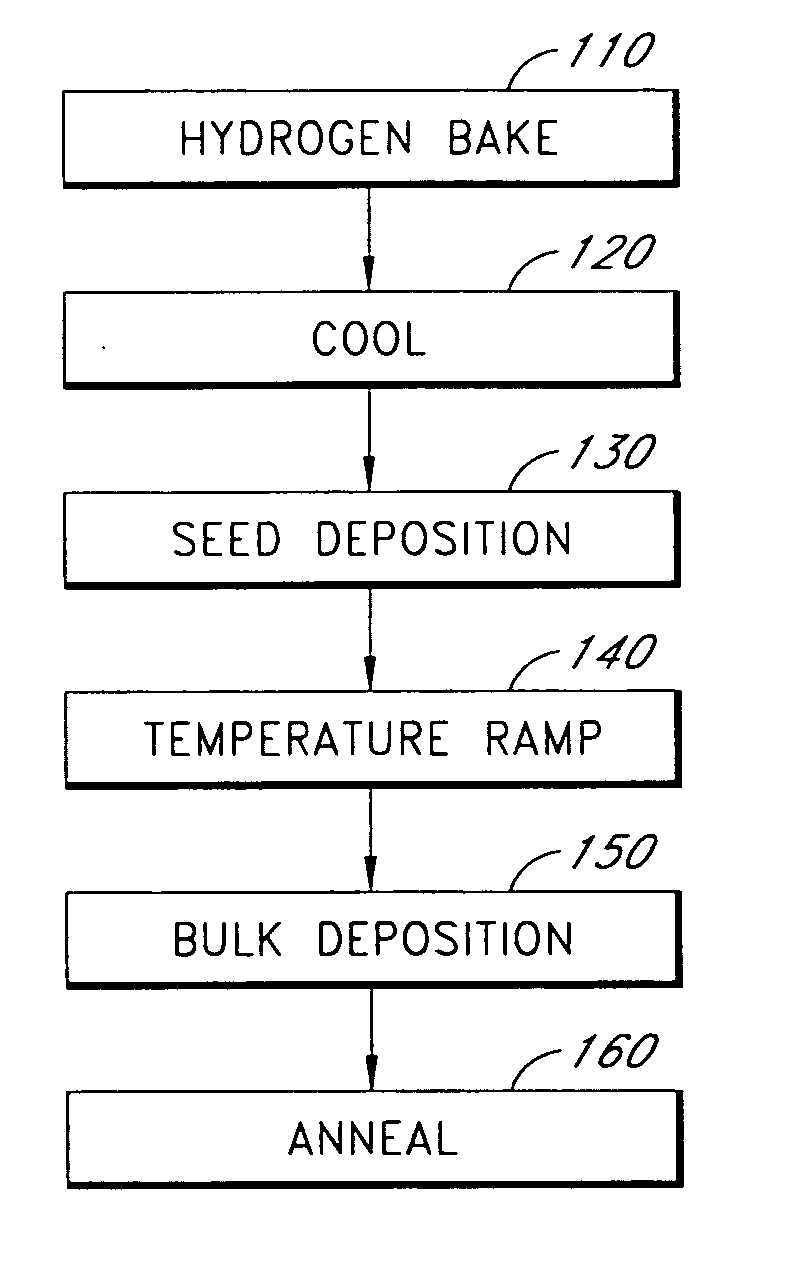

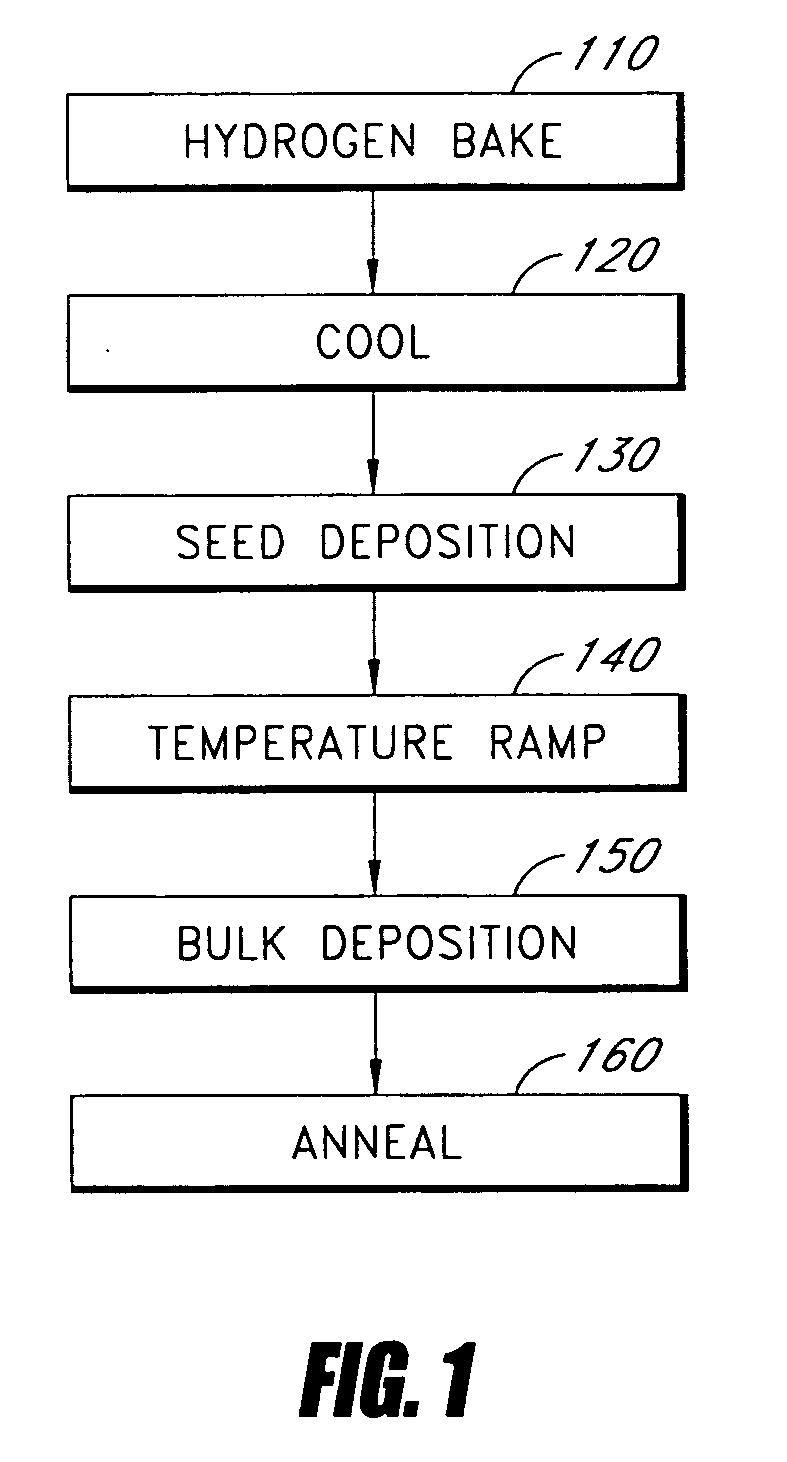

Germanium deposition

ActiveUS20050191826A1MinimizesExcessive surface roughnessPolycrystalline material growthSemiconductor/solid-state device manufacturingReaction chamberMonolayer

A method comprises, in a reaction chamber, depositing a seed layer of germanium over a silicon-containing surface at a first temperature. The seed layer has a thickness between about one monolayer and about 1000 Å. The method further comprises, after depositing the seed layer, increasing the temperature of the reaction chamber while continuing to deposit germanium. The method further comprises holding the reaction chamber in a second temperature range while continuing to deposit germanium. The second temperature range is greater than the first temperature.

Owner:ASM IP HLDG BV

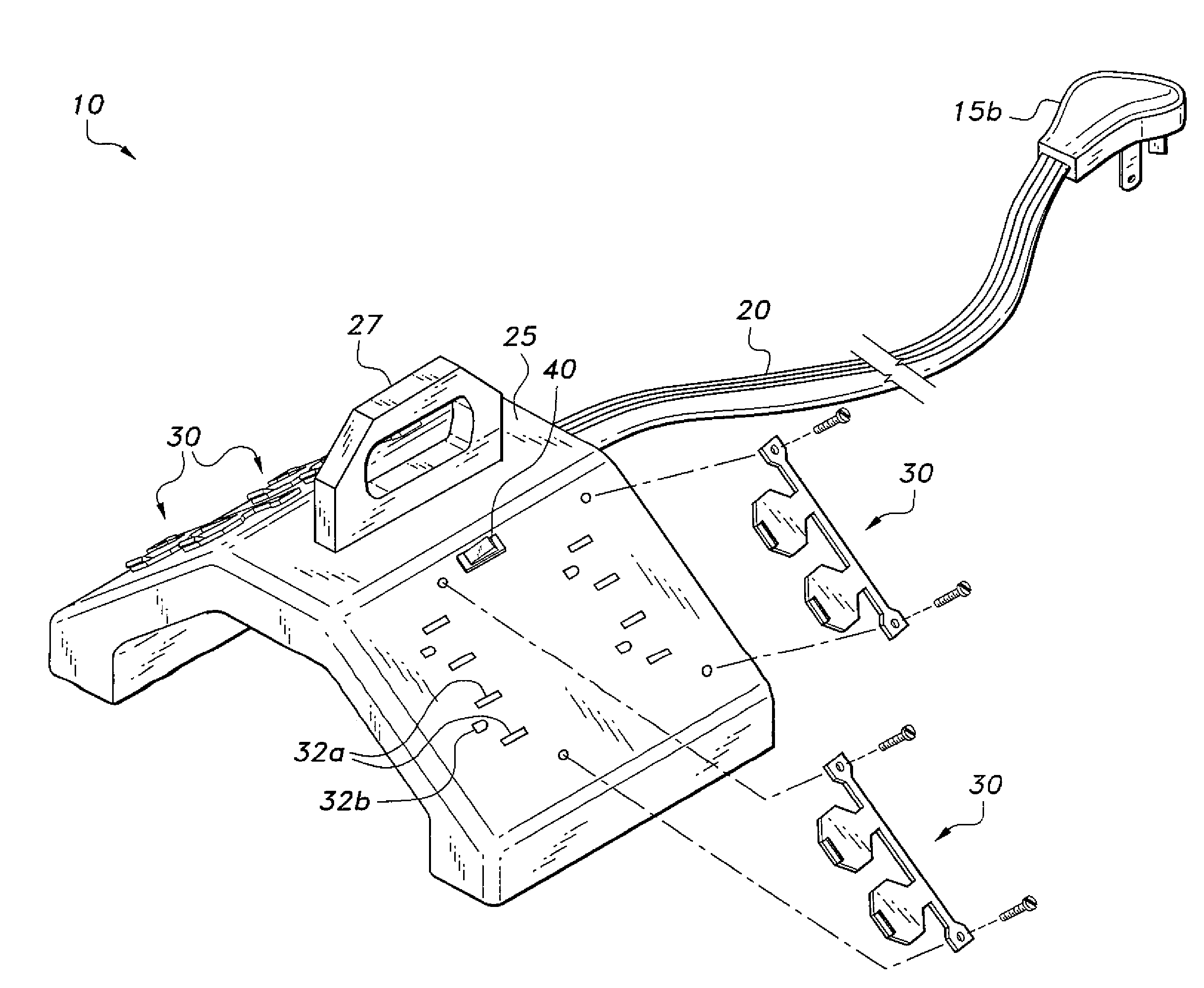

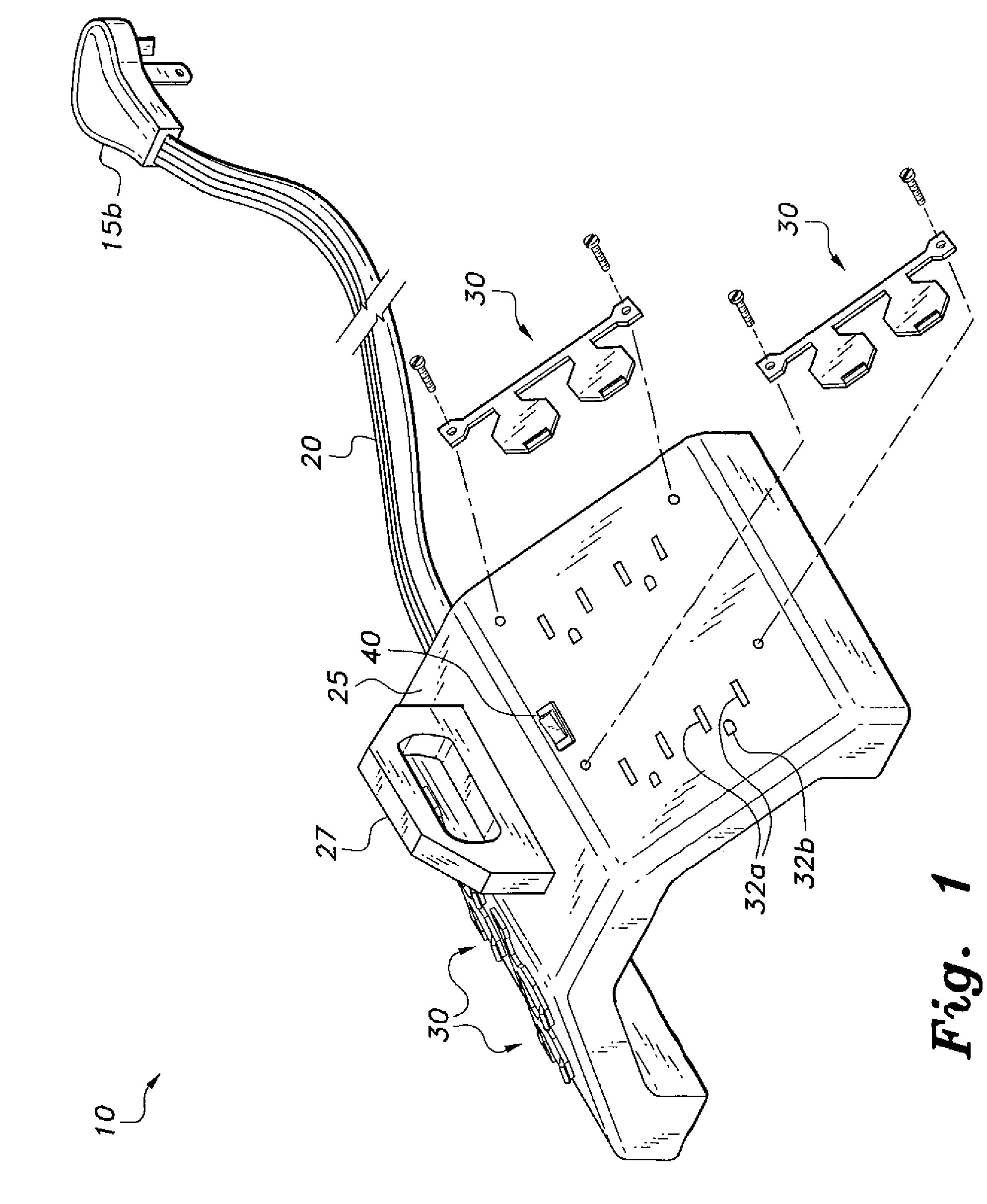

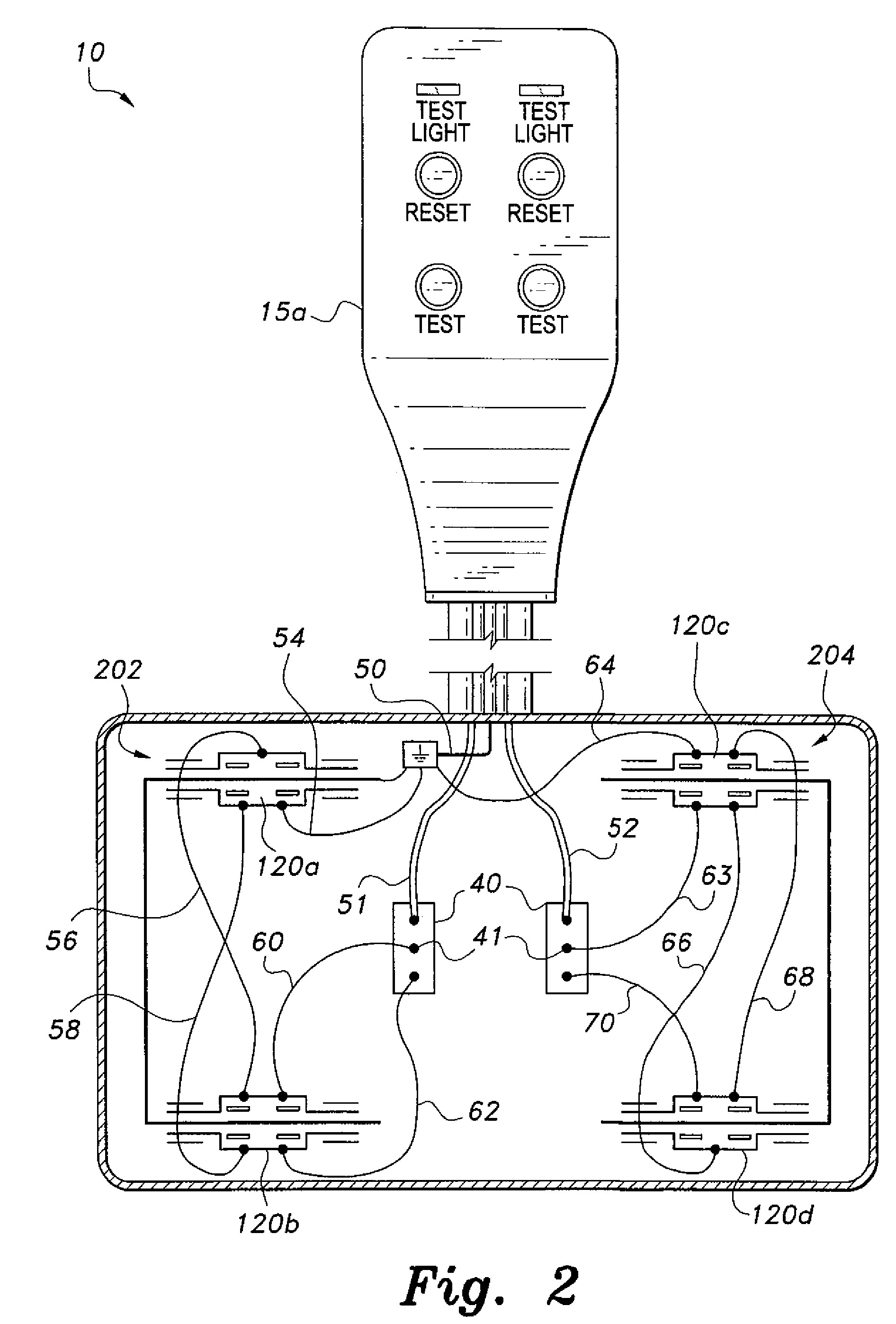

Portable electrical power box

ActiveUS8292657B2MinimizesPrevent overloadDc network circuit arrangementsTwo pole connectionsPortable powerElectric wire

Owner:SINGH JAGDEO

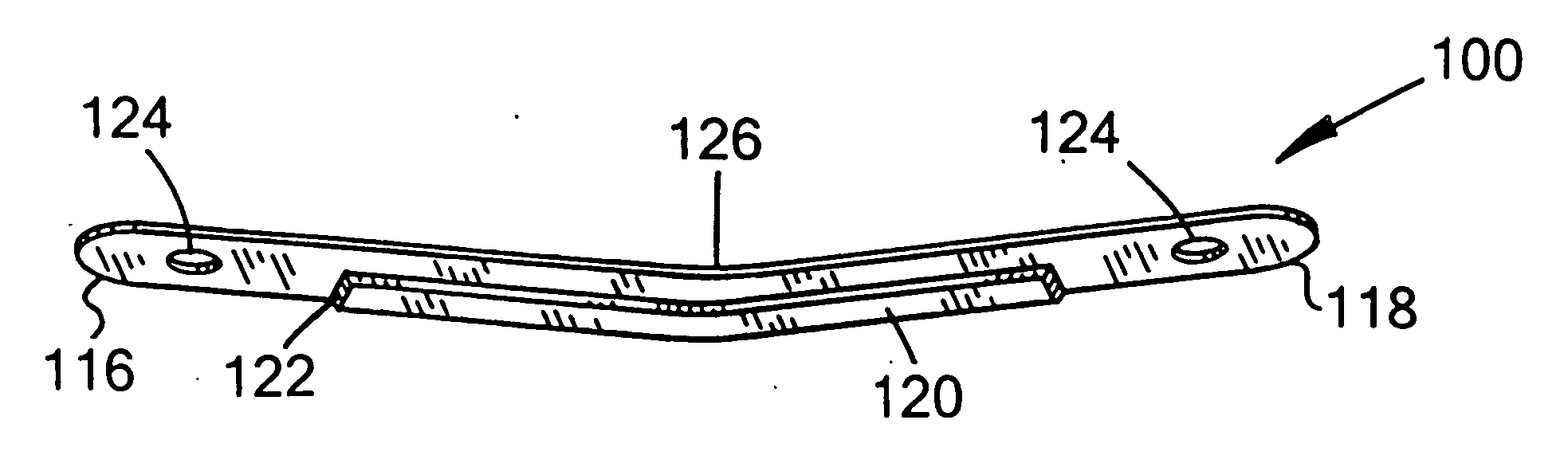

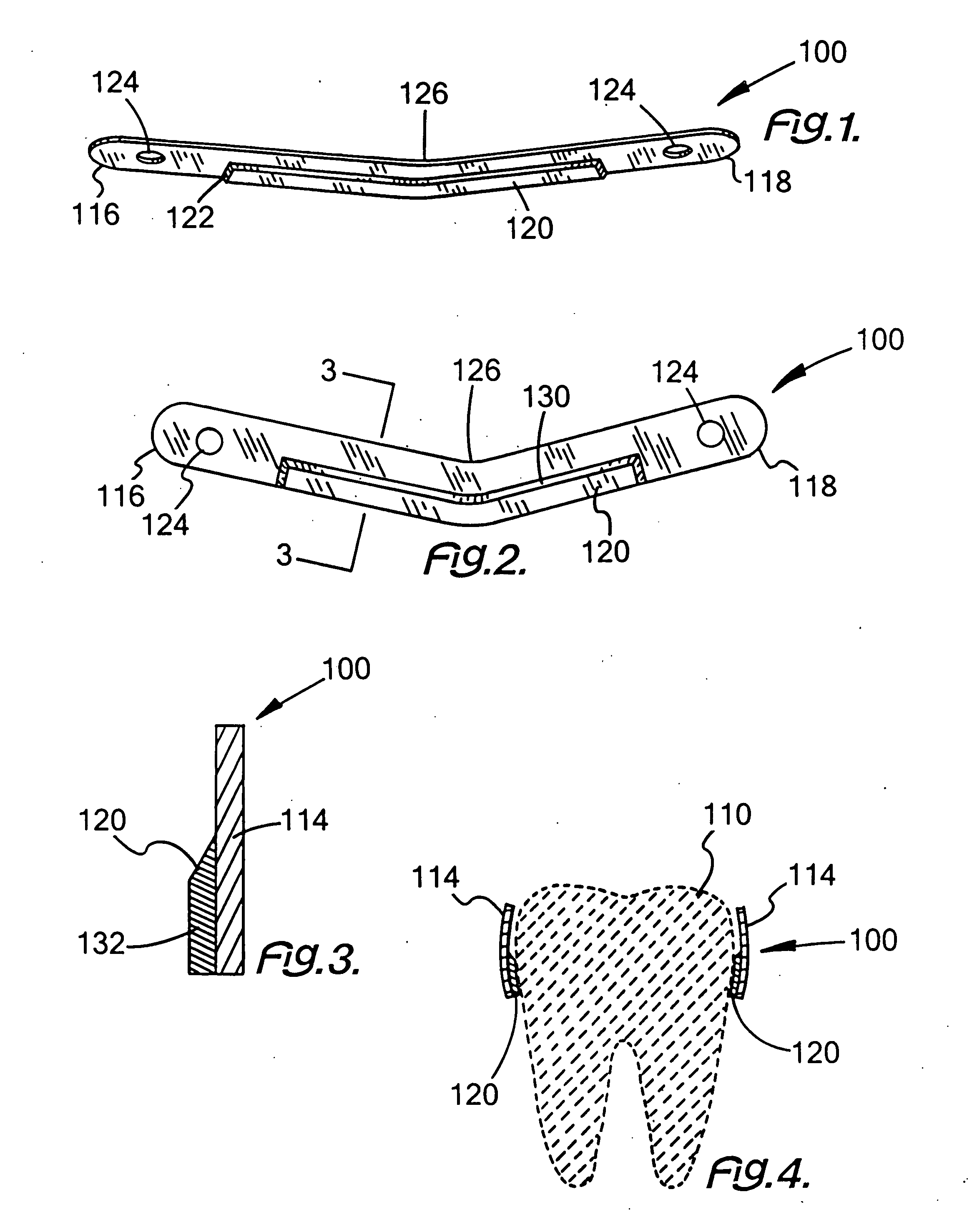

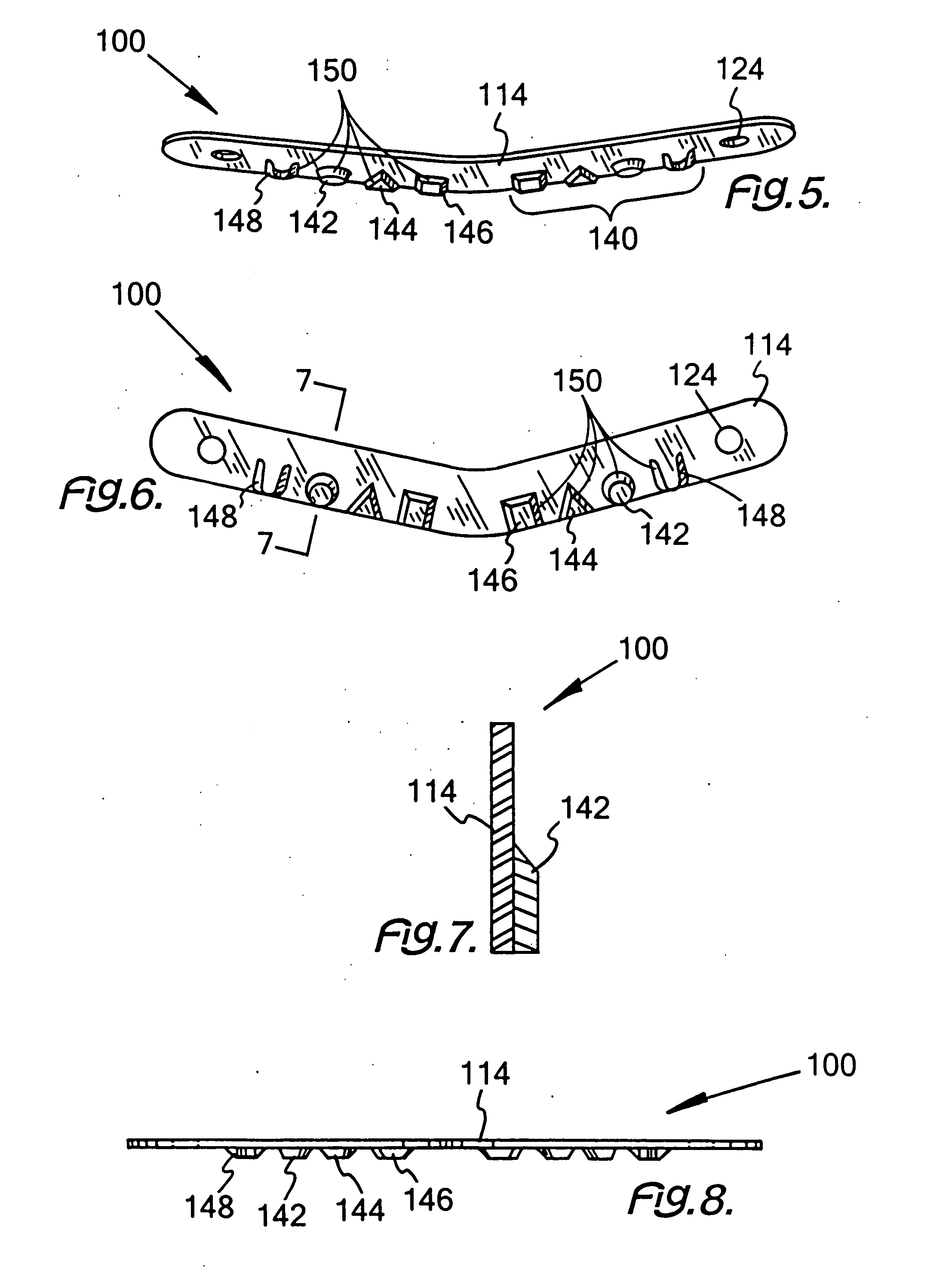

Dental matrix band seal in combination with a matrix band

InactiveUS20050221255A1Eliminate the problemReduces and eliminates capillary actionTeeth cappingDental aidsCapillary actionDental treatments

A coated matrix band or coated separating strip for use in dentistry eliminates capillary action between a tooth and the matrix band due to the coating while the tooth is being filled, while at least one aperture in the matrix band assists with removal of the matrix band from the tooth, after the filling is complete. The improvement in the coated matrix band or coated separating strip is a coating applied to the surface thereof in order to minimize the ingress of fluid between the tooth and the device as the tooth is being filled. At least one aperture therein assists with the removal from the tooth after the filling is complete.

Owner:HARADEN WILLIAM J +1

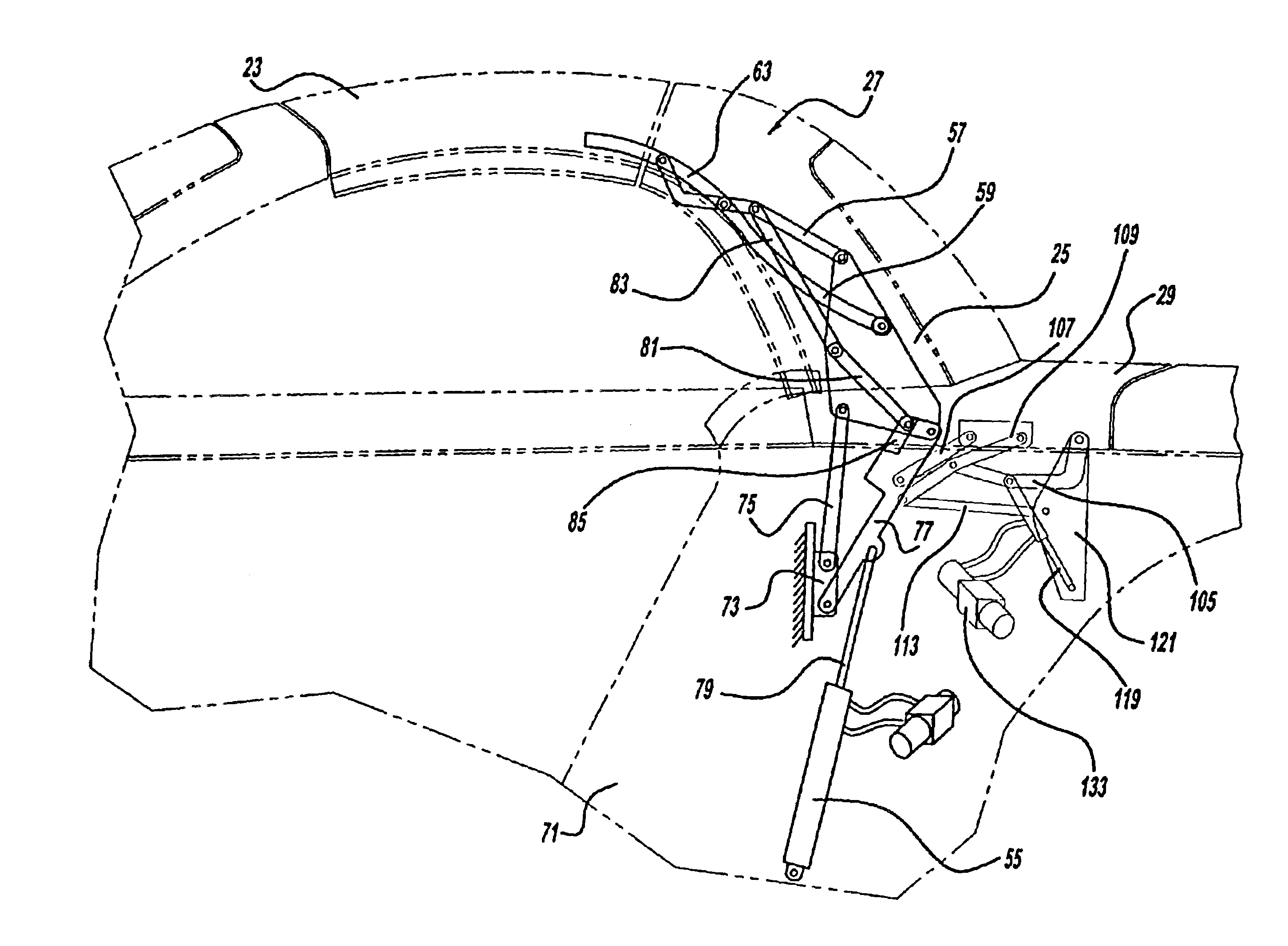

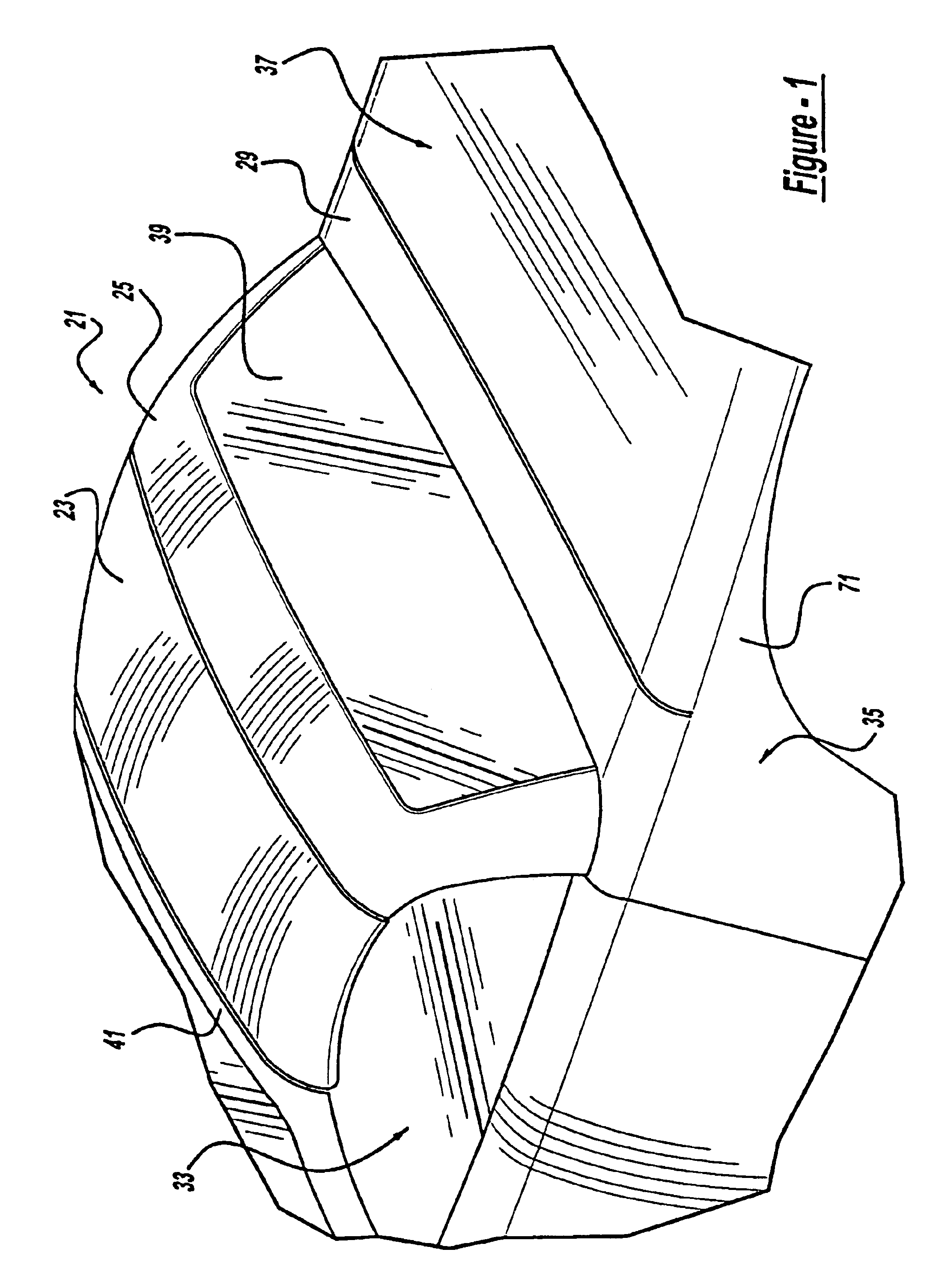

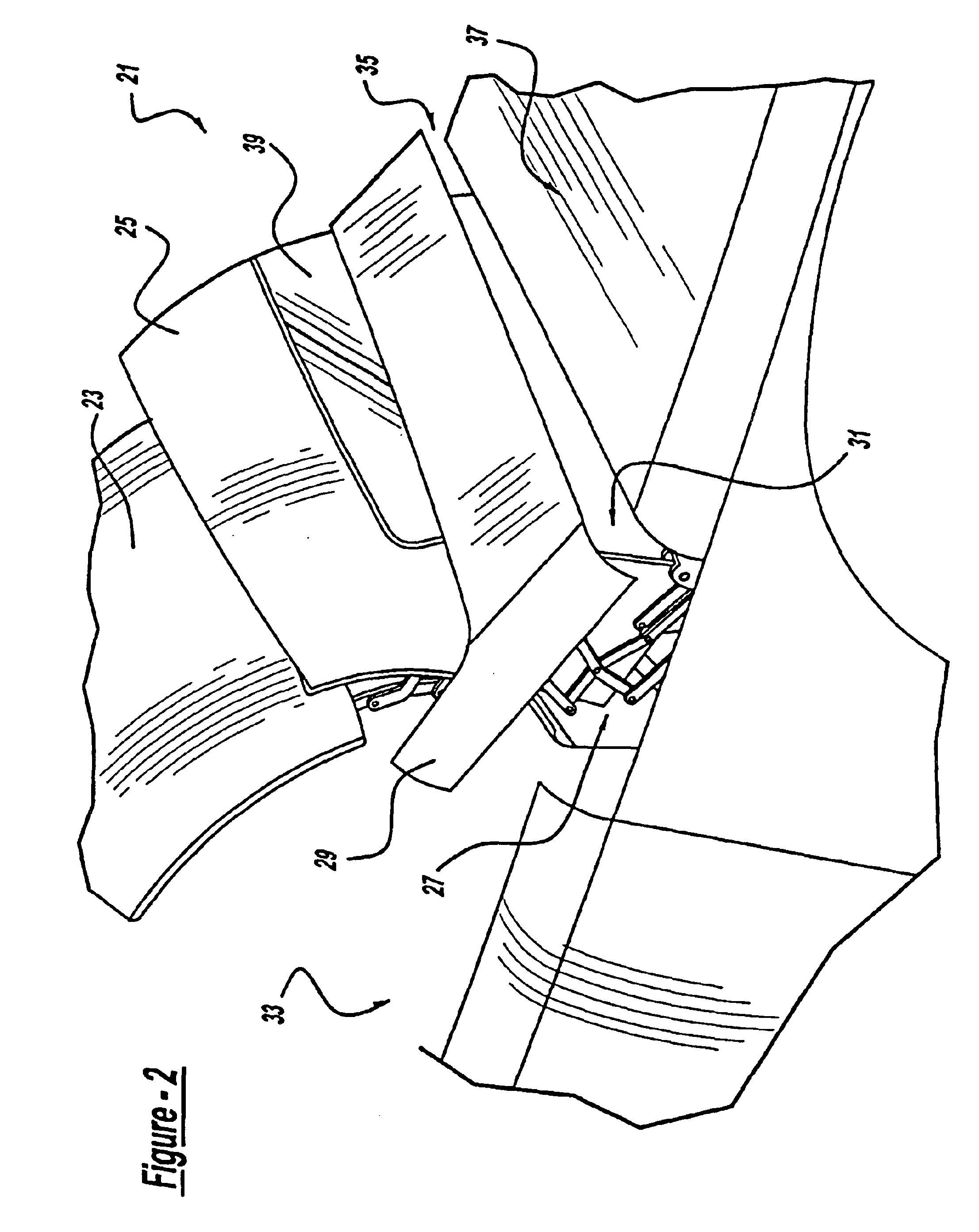

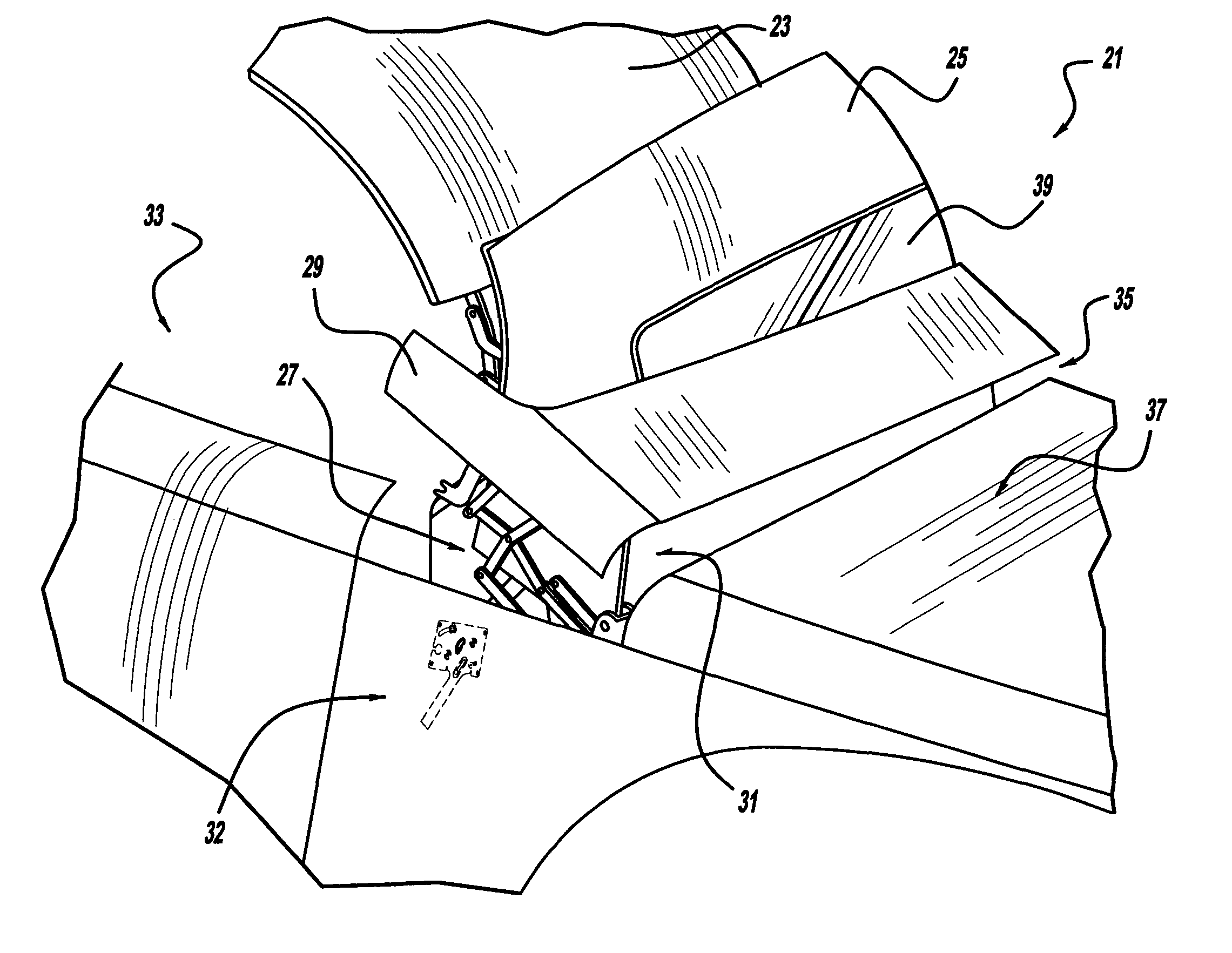

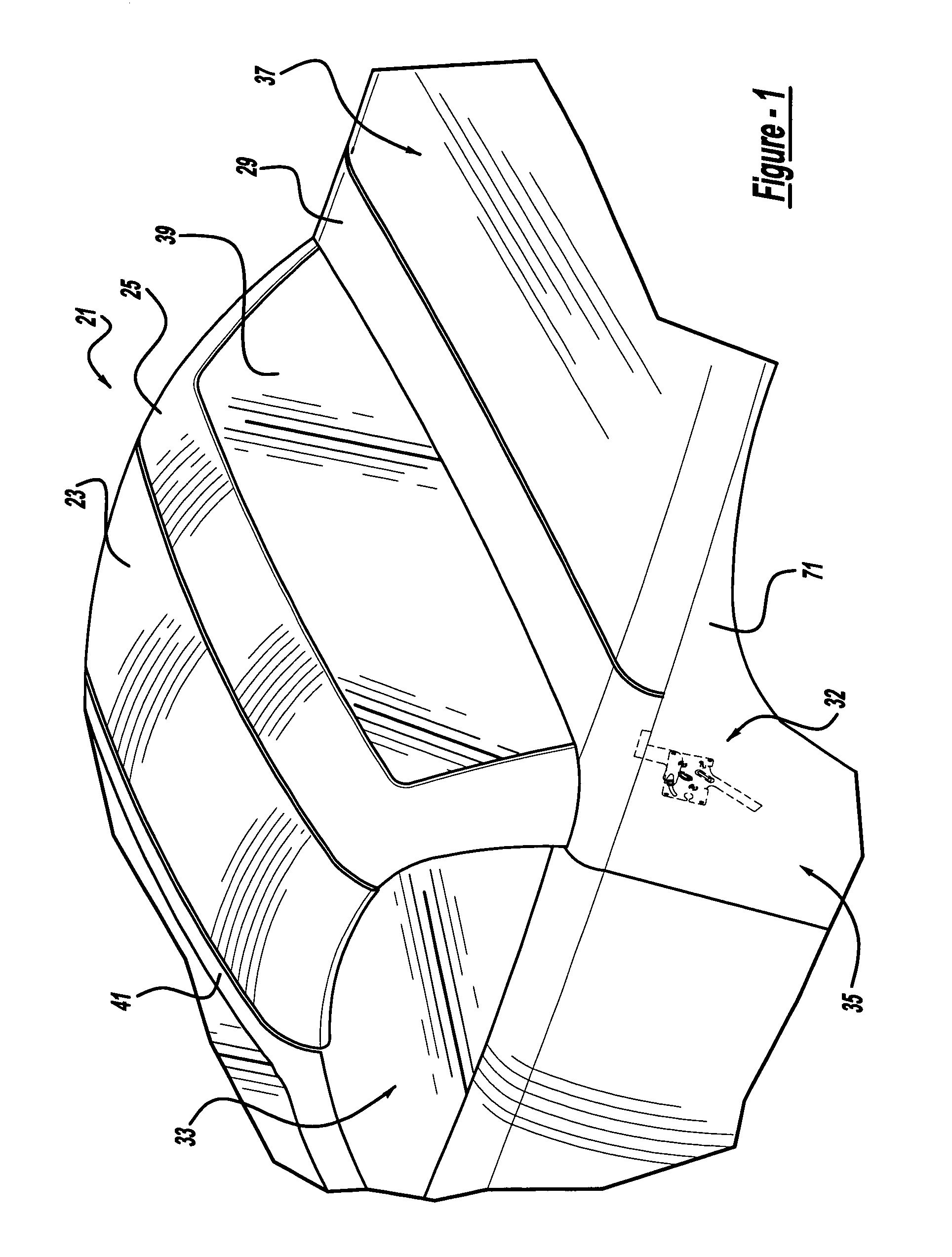

Hard-top convertible roof system

InactiveUS6866325B2MinimizesLess-costly to assembleEngine sealsVehicle sealing arrangementsEngineeringActuator

A convertible roof system includes a front roof section, a rear roof section, an automatically power actuator and a linkage mechanism. In another aspect of the present invention, the front and / or rear roof sections are rigid, hard-top roofs. A further aspect of the present invention provides that the outside surfaces of the roofs have a generally vertical orientation when in their open and retracted positions.

Owner:SPECIALTY VEHICLE ACQUISITION

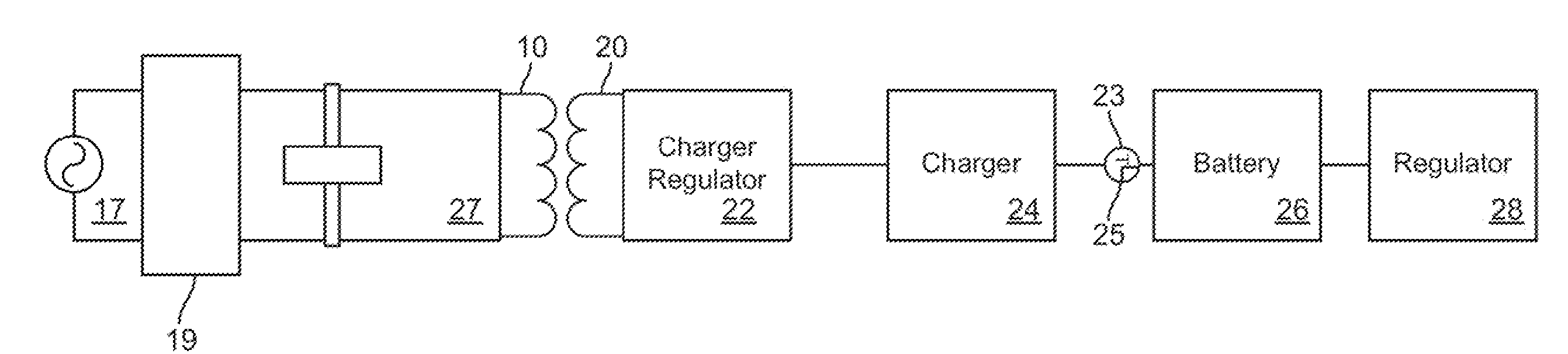

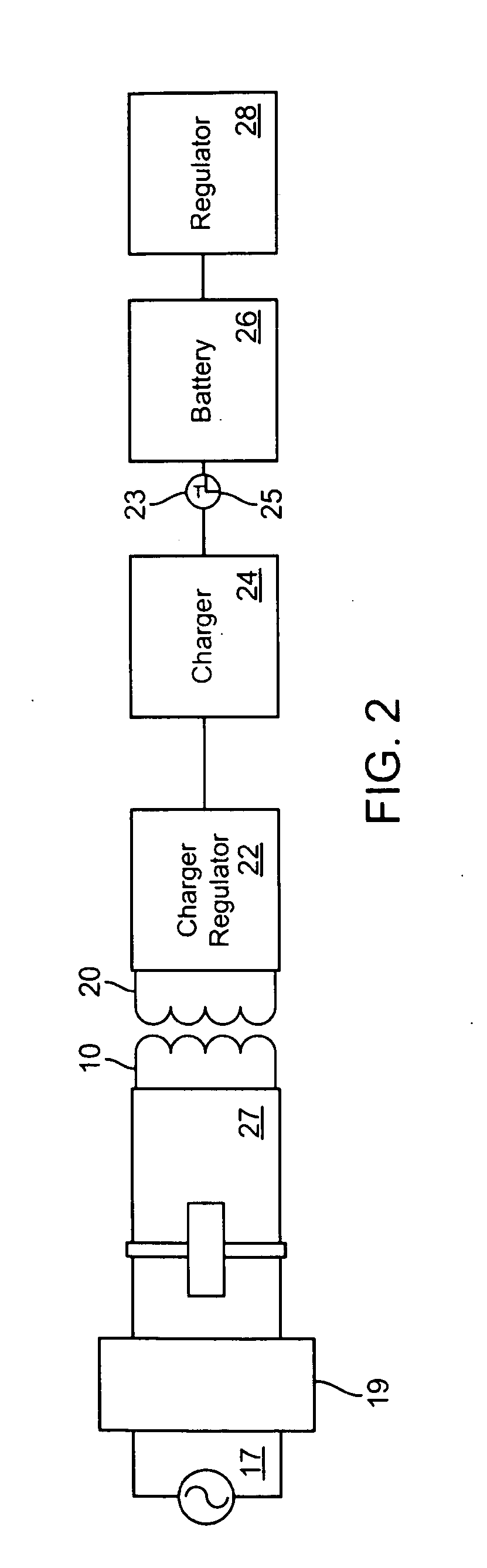

Intra-oral charging systems and methods

InactiveUS20100194333A1Avoid shortingEasy to operate-usersBatteries circuit arrangementsTransformersEngineeringBattery charger

Systems and methods are disclosed for charging an intra-oral apparatus includes an intra-oral appliance having an appliance charger coil defining a first portion of an electromagnetic loop; and a charger base having a base charger coil defining a second portion of the electromagnetic loop, wherein the appliance charger coil and the base charger coil in combination transfer energy for inductive charging.

Owner:SOUNDMED LLC

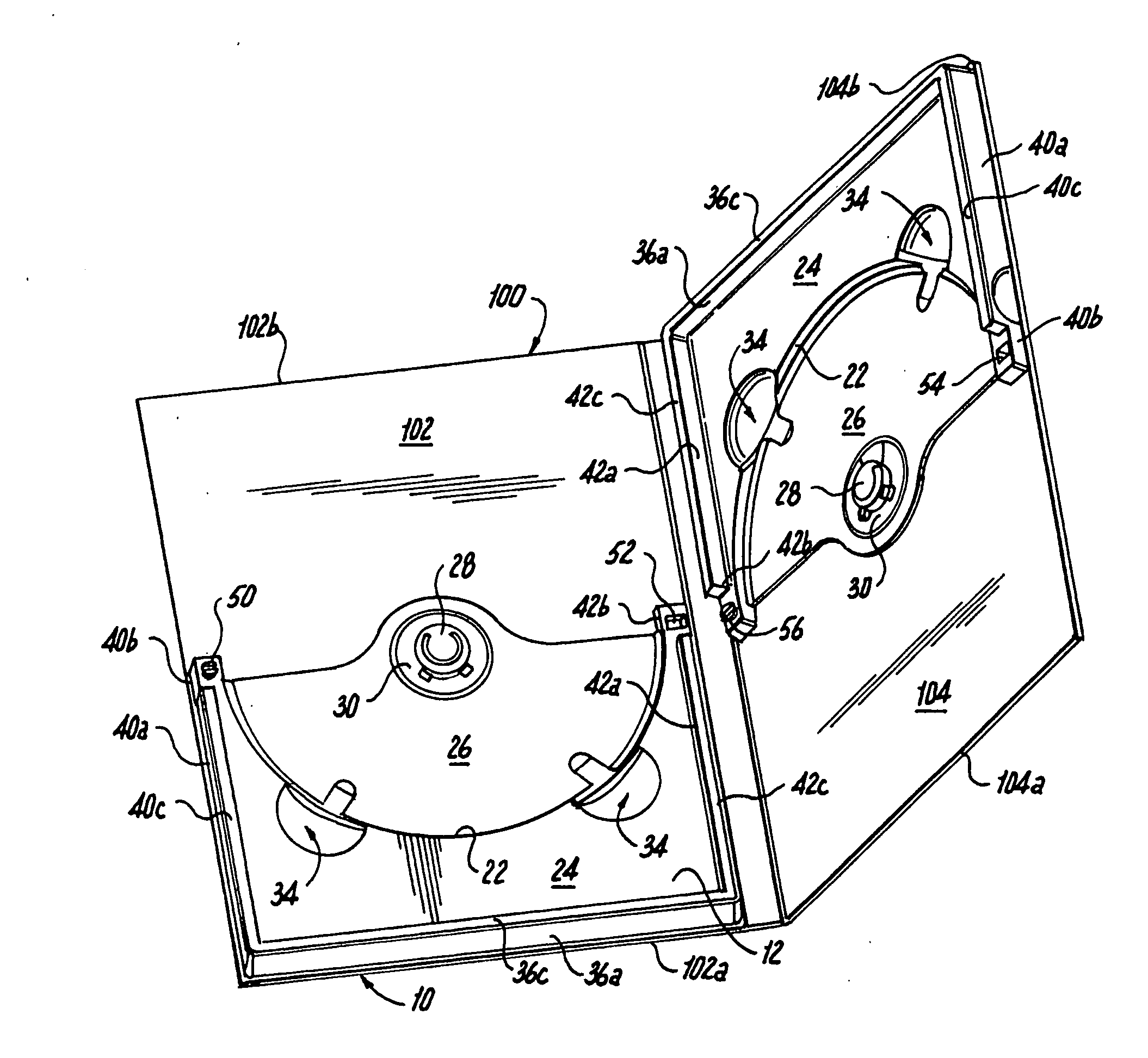

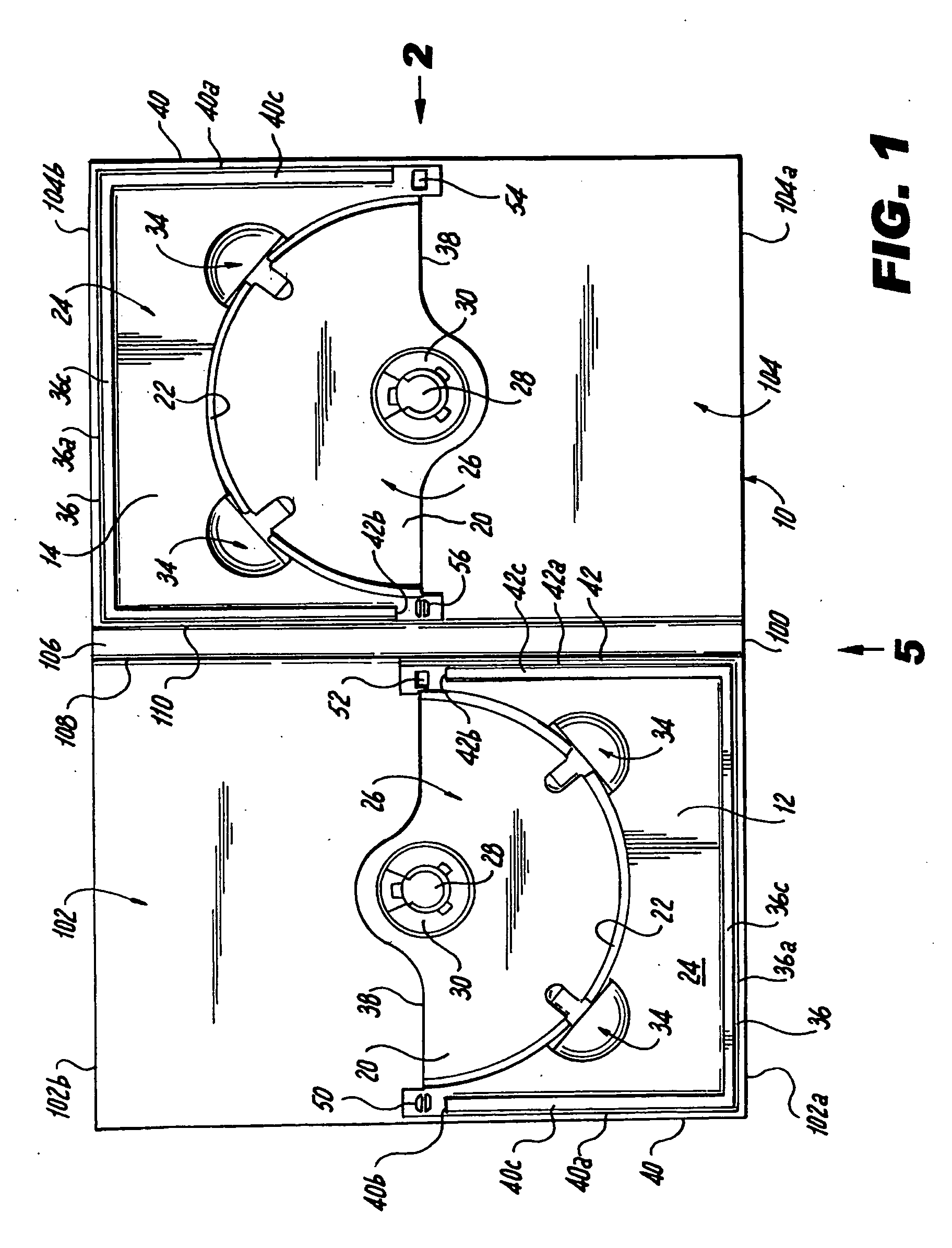

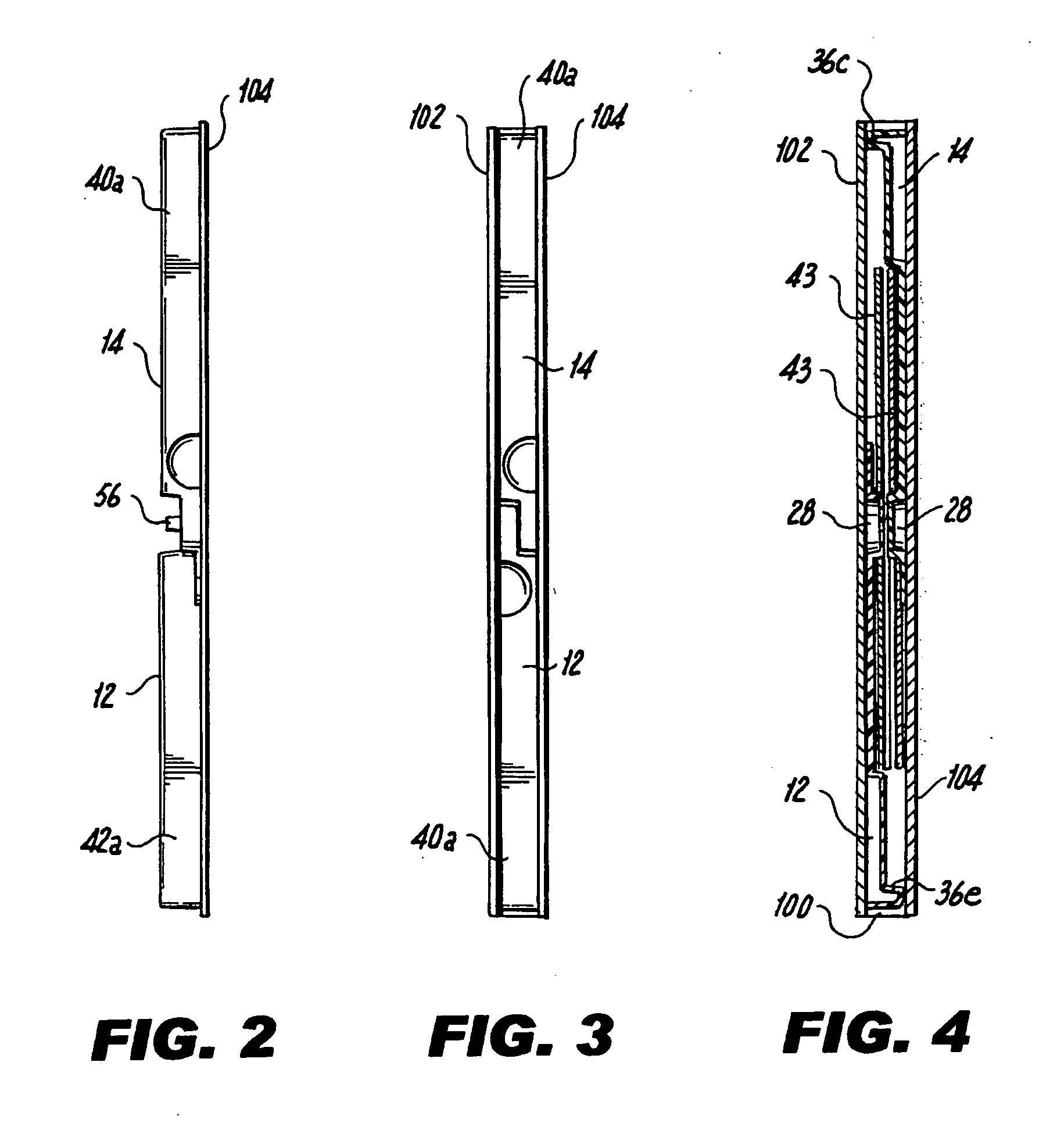

Package with aligned discs on opposite covers

A package for housing two discs including a cover forming an elongated spine panel with first and second opposing panels extending therefrom such that the opposing panels selectively rotate between open and closed postions. First and second partial trays attach to the first and second opposing panels, respectively, and are laterally spaced so that when closed, the thickness of the package is approximately equal to that of one of the trays. Each partial tray has a planar surface forming a periphery and a recess, a rosette near a first side of the tray for engaging a central aperture to retain a disc within the recess and a spacing rim upstanding from the planar surface. The spacing rim is U-shaped so that in the closed position, the spacing rims do not overlap.

Owner:MEADWESTVACO CORP

Vacuum nozzle for spray system

InactiveUS20060081174A1Efficient drawingMinimizing turbulent flowLiquid surface applicatorsVacuum evaporation coatingVisibilityEngineering

A cold spray system includes a spray nozzle for depositing material onto a substrate. A collection assembly at least partially surrounds the spray nozzle for vacuuming undepositive material and gases in the work area. The collection assembly includes a transparent collection tube at an end portion of the collection assembly to provide visibility to the work area. The collection assembly includes a shield having a flange that extends radially outwardly from the collection assembly and is generally parallel to a substrate. An angled portion of the shield extends from the collection assembly. A radius portion adjoins the flange and the angled portion. A ring is spaced between the spray nozzle and the shield. An inner surface of the ring deflects material that typically would otherwise not become adhered to the substrate back into the collection assembly to minimize the material that must be vacuumed at the substrate. A curved surface of the ring extends from a surface spaced from the substrate toward the shield to provide a smooth transition for materials flowing along the substrate back into the collection assembly.

Owner:DOBEN LTD

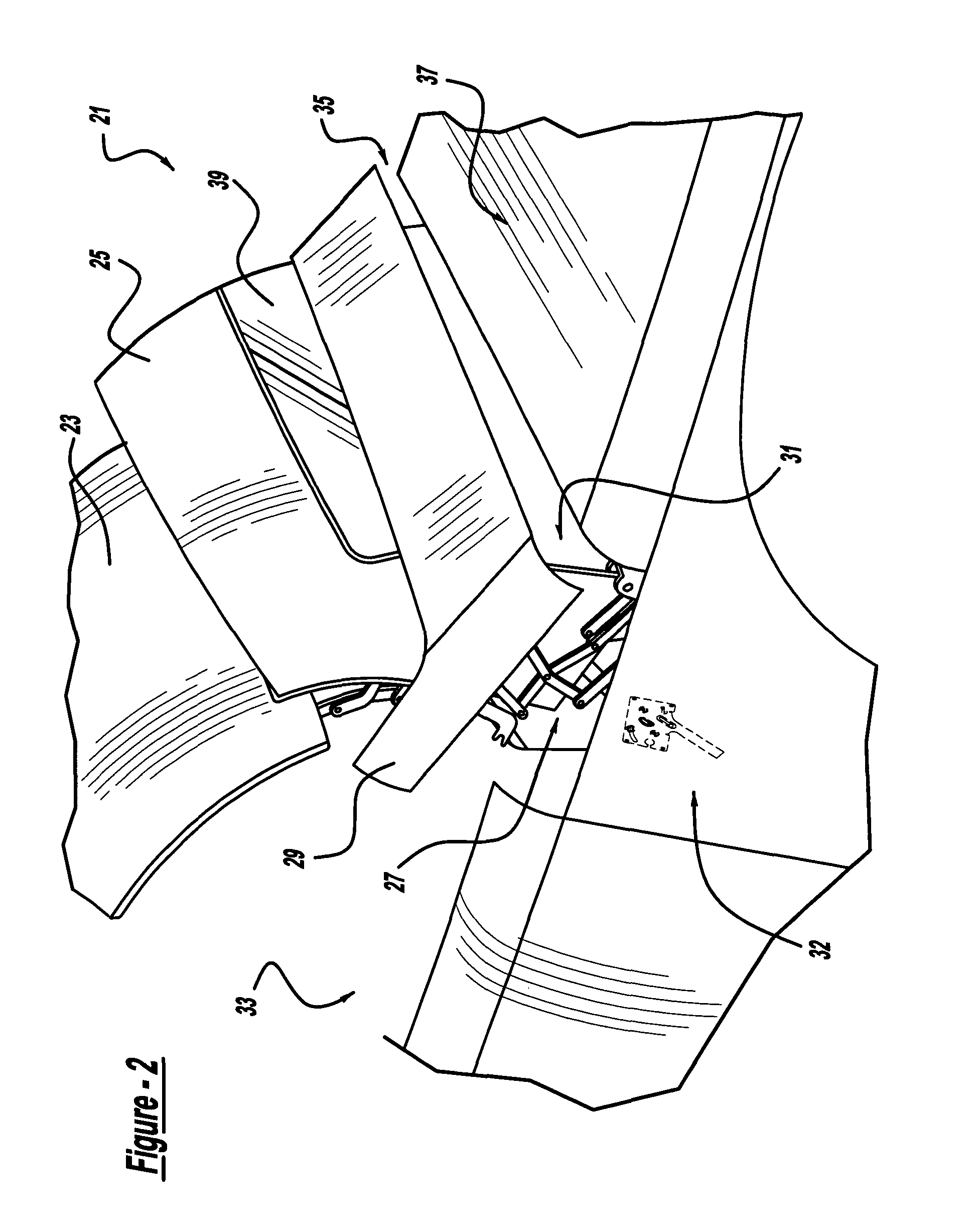

Latch for an automotive vehicle having a convertible roof

InactiveUS7140666B2MinimizesMinimal intrusionEngine sealsVehicle sealing arrangementsMotorized vehicleMechanical engineering

A latching system for an automotive vehicle having a convertible roof is provided. In another aspect of the present invention, front and / or rear convertible roof sections are rigid, hard-top roofs. A further aspect of the present invention system provides a latch which secures a generally rigid tonneau cover.

Owner:VALMET AUTOMOTIVE

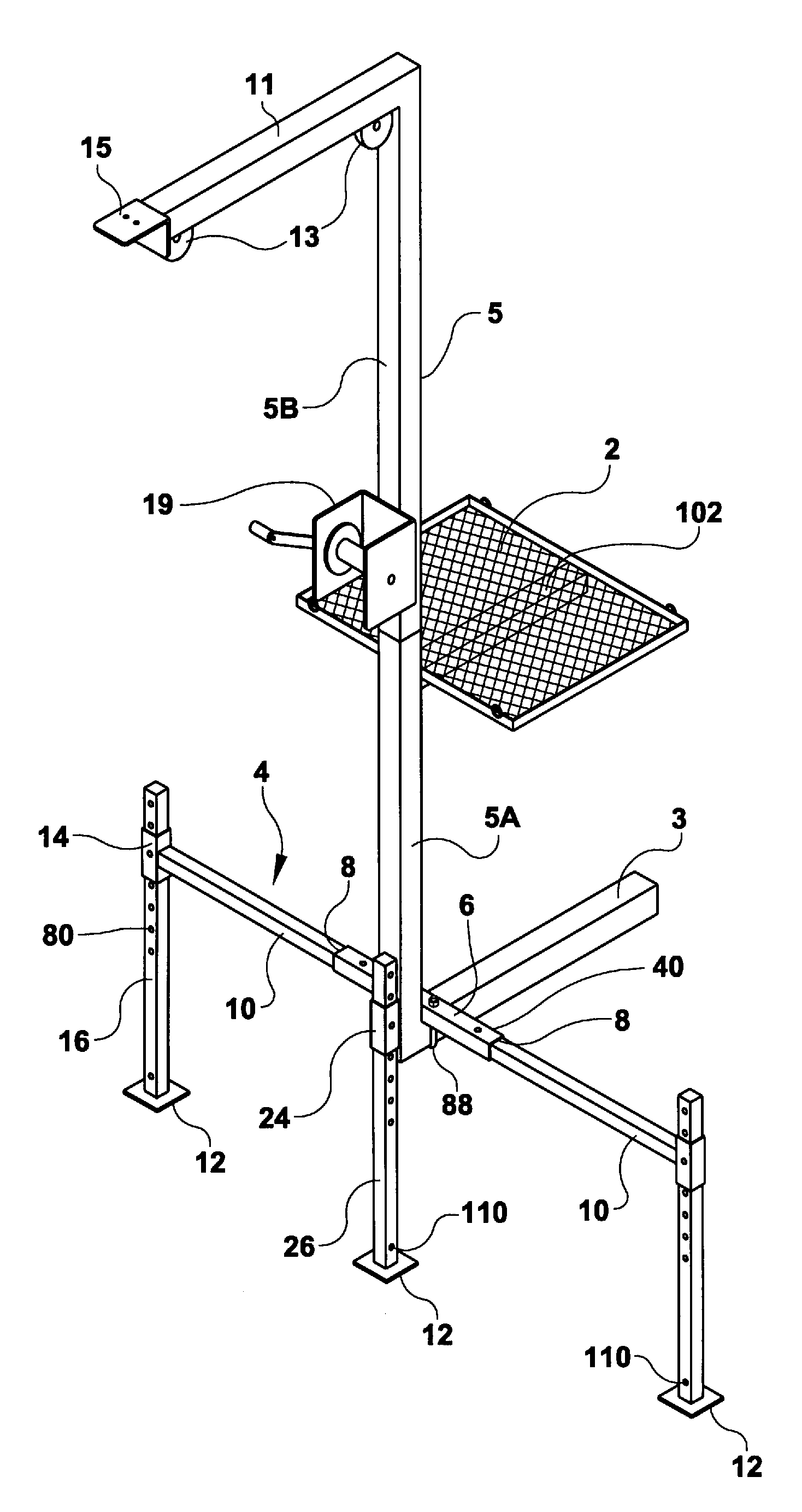

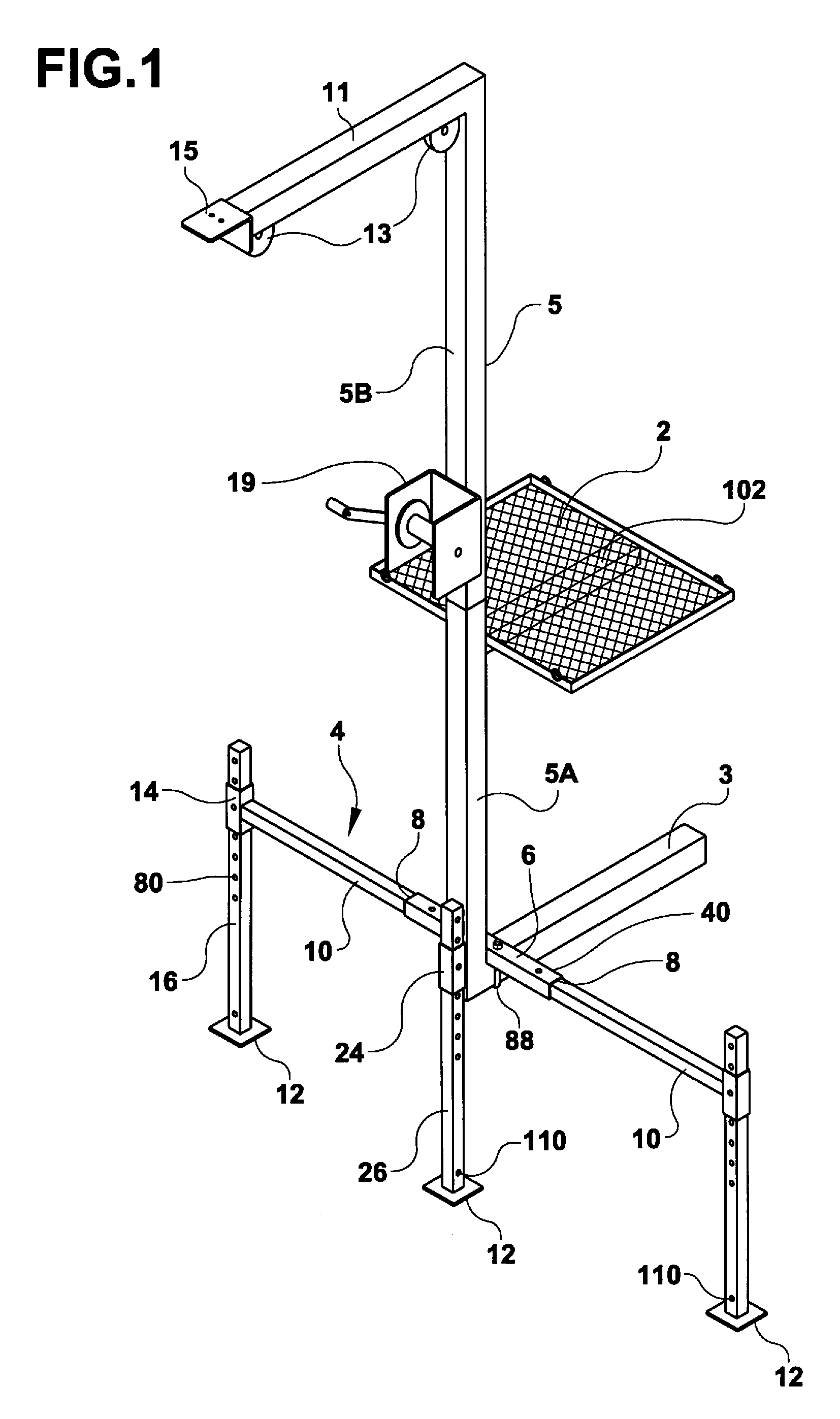

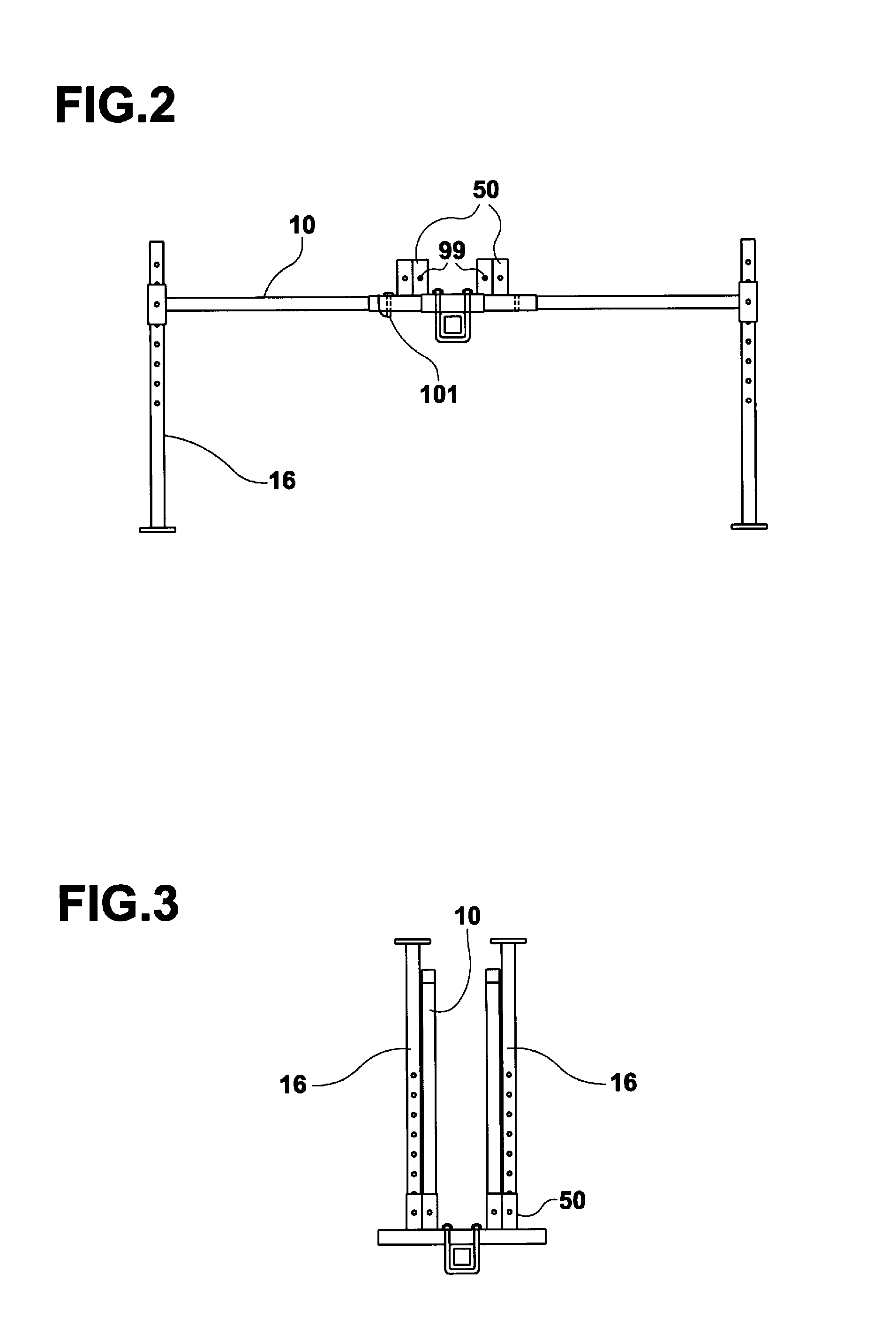

Deer hoist for an all terrain vehicle

InactiveUS7544032B1Compact storageAdd supportLoading/unloading vehicle arrangmentSuperstructure subunitsEngineeringLandform

A deer hoist for an all terrain vehicle includes a transverse mounting bar adapted to be attached to a trailer hitch drawbar on the vehicle. A beam vertically extends from the mounting bar and has a horizontal arm extending therefrom. A brake wench mounted on the vertical beam operates a cable along a plurality of pulleys disposed on the horizontal arm. A gambrel is secured to a distal end of the cable for suspending a deer. A width and height adjustable outrigger assembly is attached to the transverse mounting bar to prevent the all terrain vehicle from toppling when a load is placed on the hoist. The outrigger assembly can be conveniently disassembled and stored on the hoist when not in use. The hoist also includes an accessory rack and light for remote use.

Owner:SCOTT JR EARL

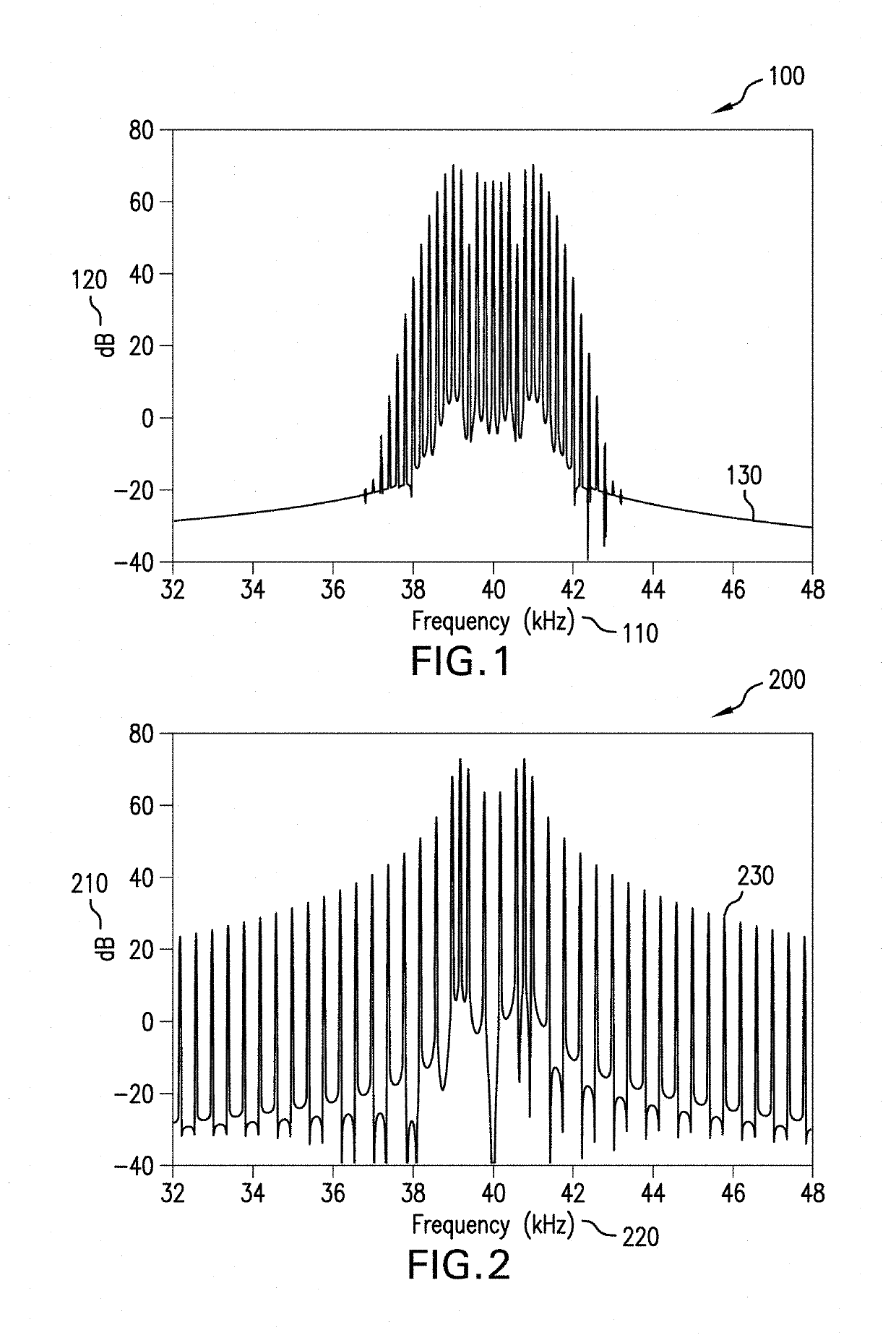

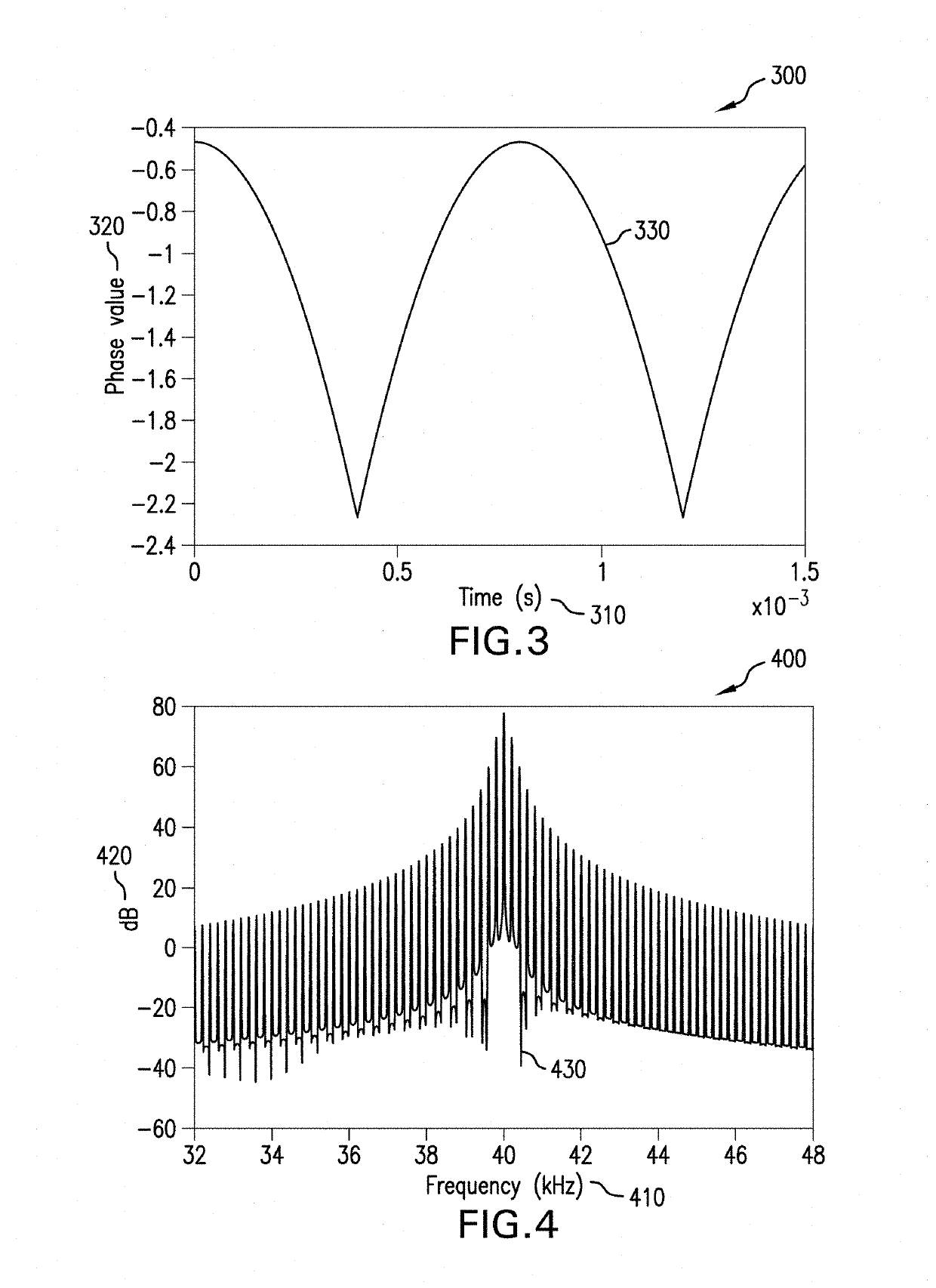

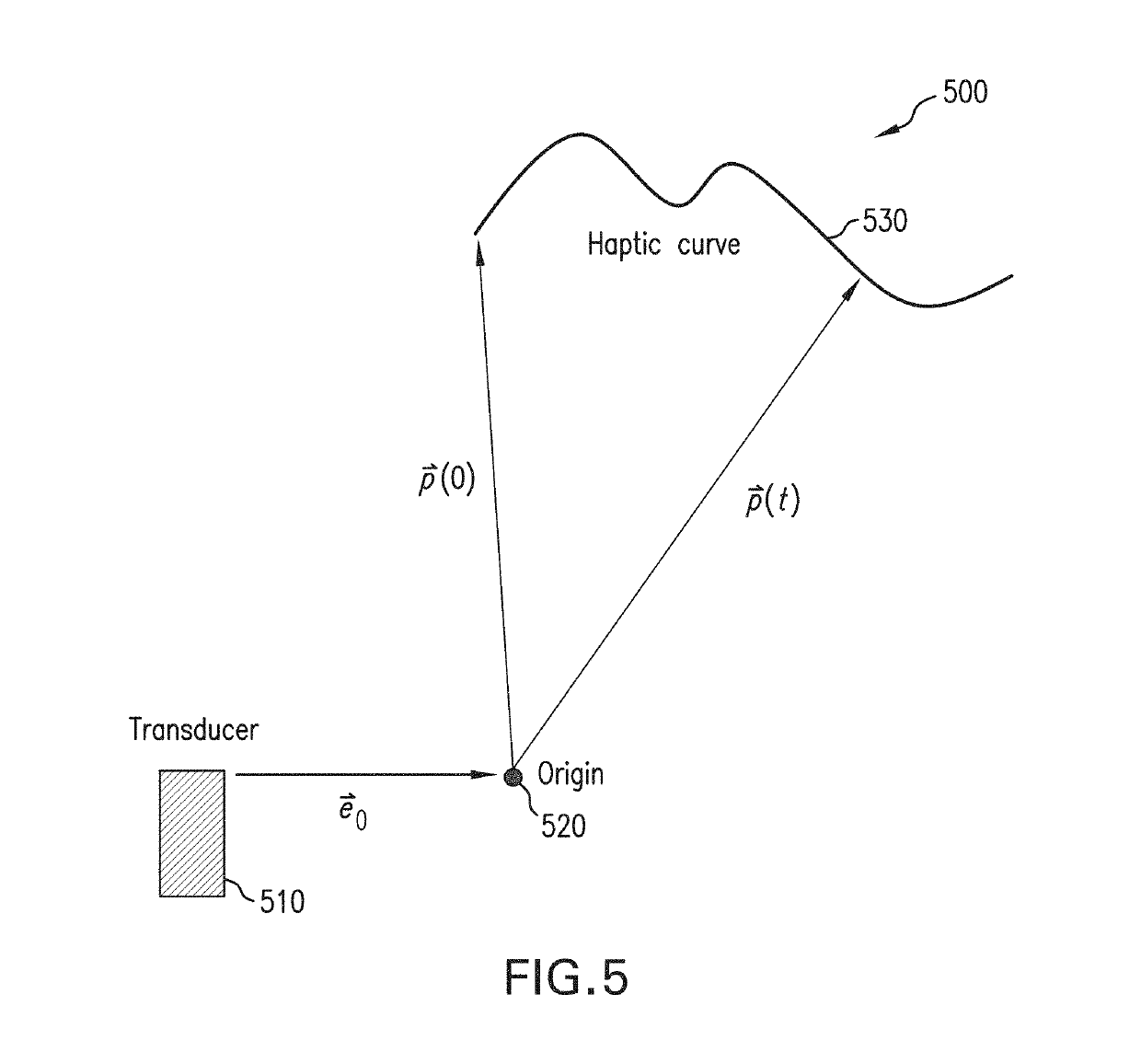

Minimizing Unwanted Responses in Haptic Systems

PendingUS20190197842A1MinimizesMinimizes unwanted parametric audioTactile signalling systemsSound producing devicesConvolutionEngineering

Disclosed are methods to manipulate a given parametrized haptic curve in order to yield a smooth phase function for each acoustic transducer which minimizes unwanted parametric audio. Further, the impulse response of a haptic system describes the behavior of the system over time and can be convolved with a given input to simulate a response to that input. To produce a specific response, a deconvolution with the impulse response is necessary to generate an input.

Owner:ULTRAHAPTICS IP LTD

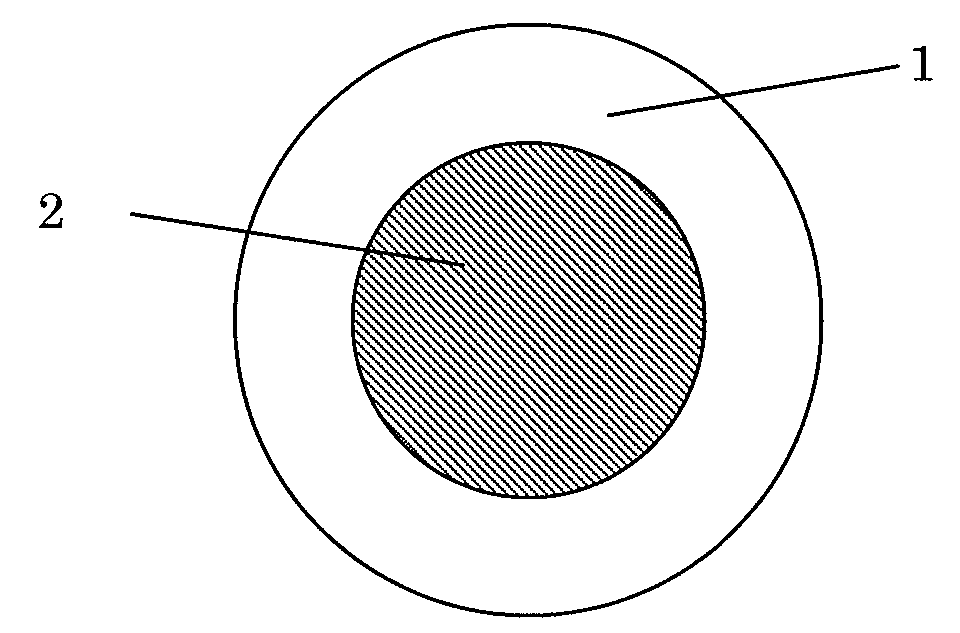

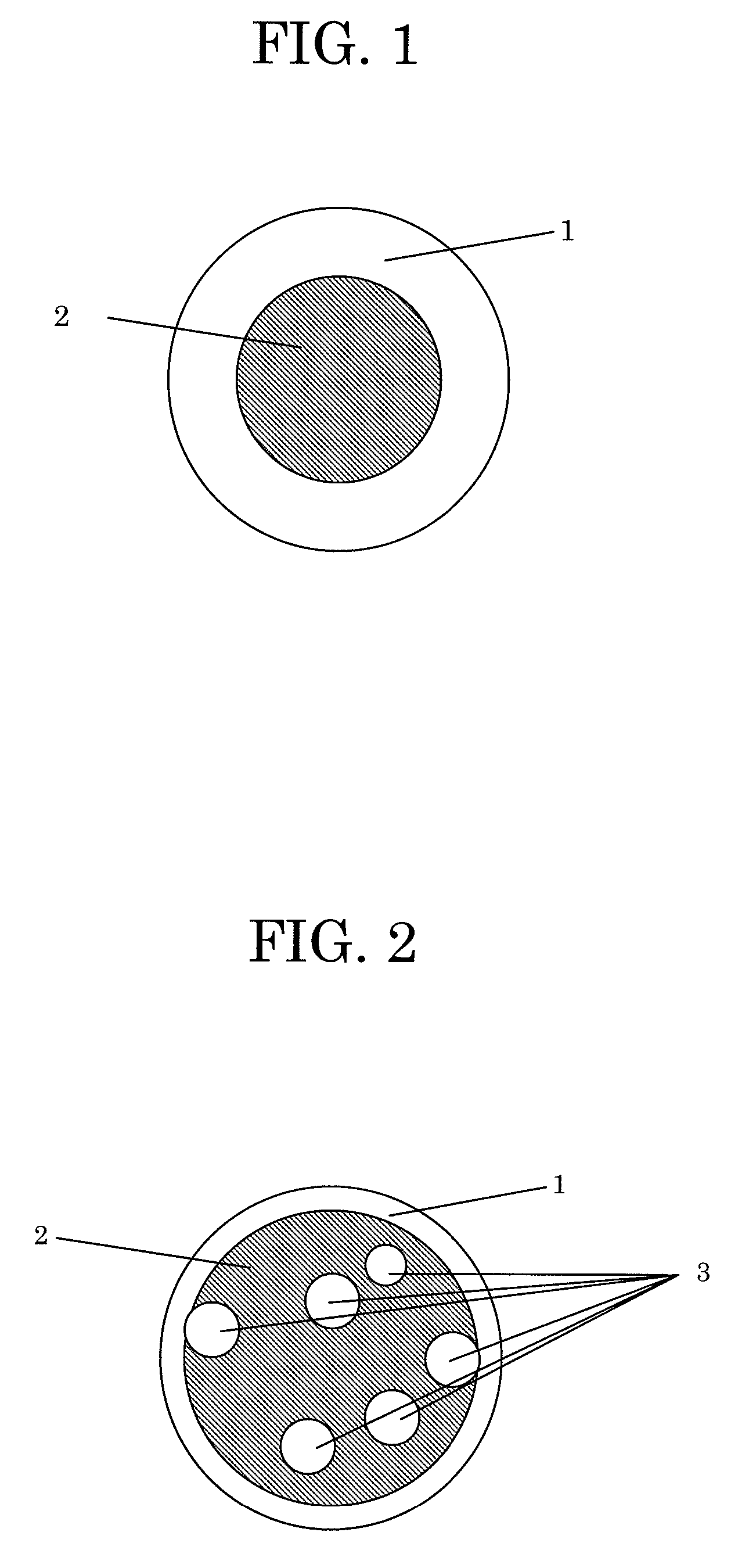

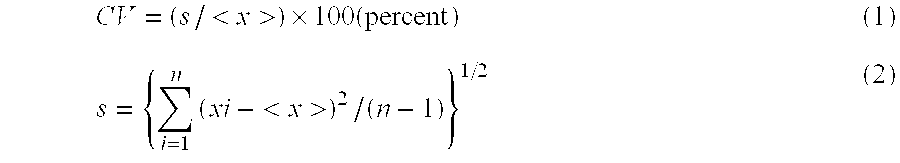

Heat-expandable microspheres and a process for producing the same

ActiveUS20090176098A1Efficient productionGood thermal expansion performanceSynthetic resin layered productsCellulosic plastic layered productsMicrosphereBoiling point

A method that heat-expandable microspheres includes the use of a shell of thermoplastic resin and a non-fluorine blowing agent encapsulated therein having a boiling point not higher than the softening point of the thermoplastic resin. The method includes a step of dispersing an oily mixture containing a polymerizable component, the blowing agent, and a polymerization initiator containing a peroxydicarbonate in an aqueous dispersing medium to polymerize the polymerizable component contained in the oily mixture. The resultant heat-expandable microspheres have a shell which is less apt to become thinner than its theoretical value, contain minimum amount of resin particle inside their shell, and have excellent heat-expanding performance.

Owner:MATSUMOTO YUSHI SEIYAKU

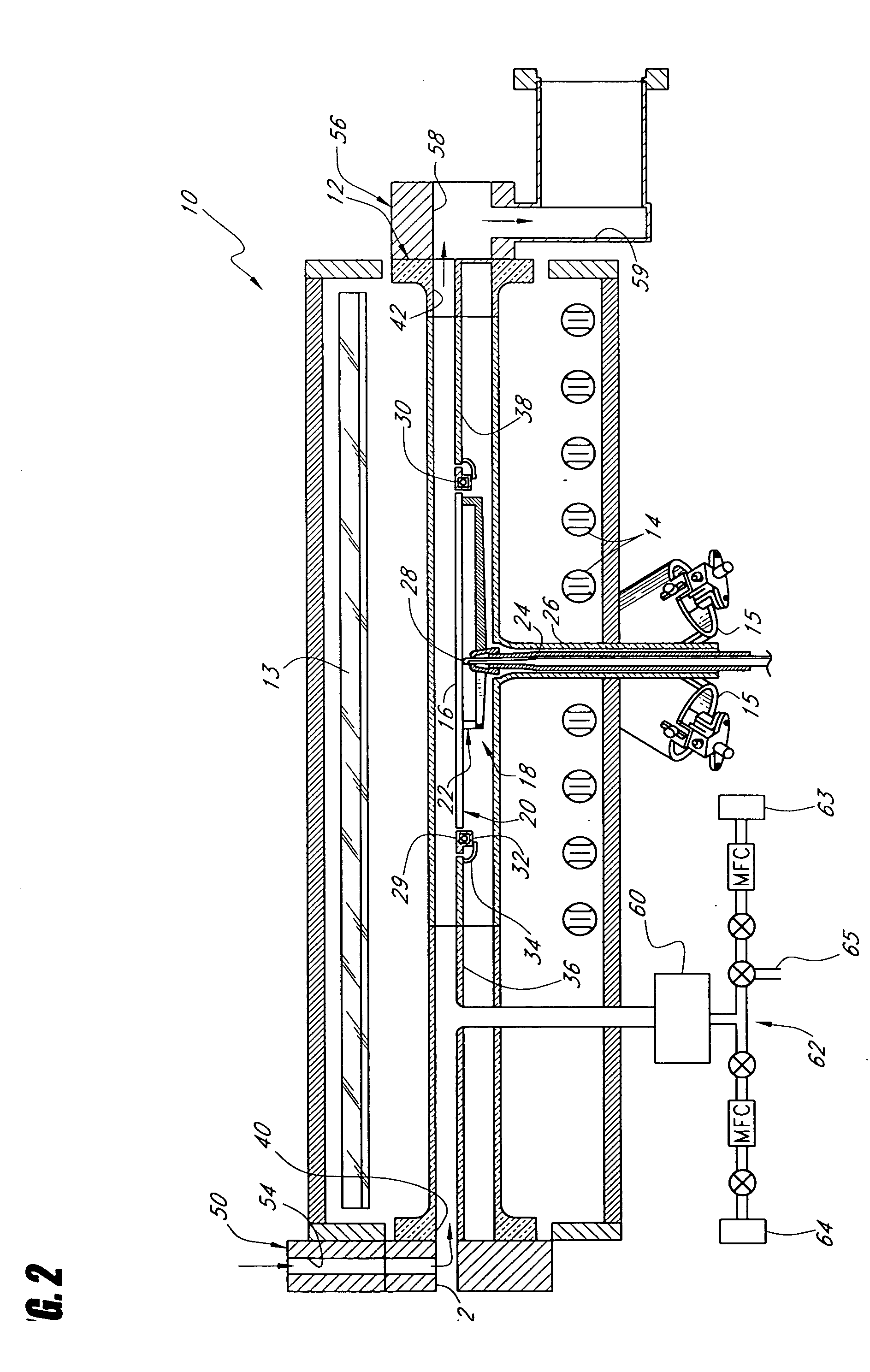

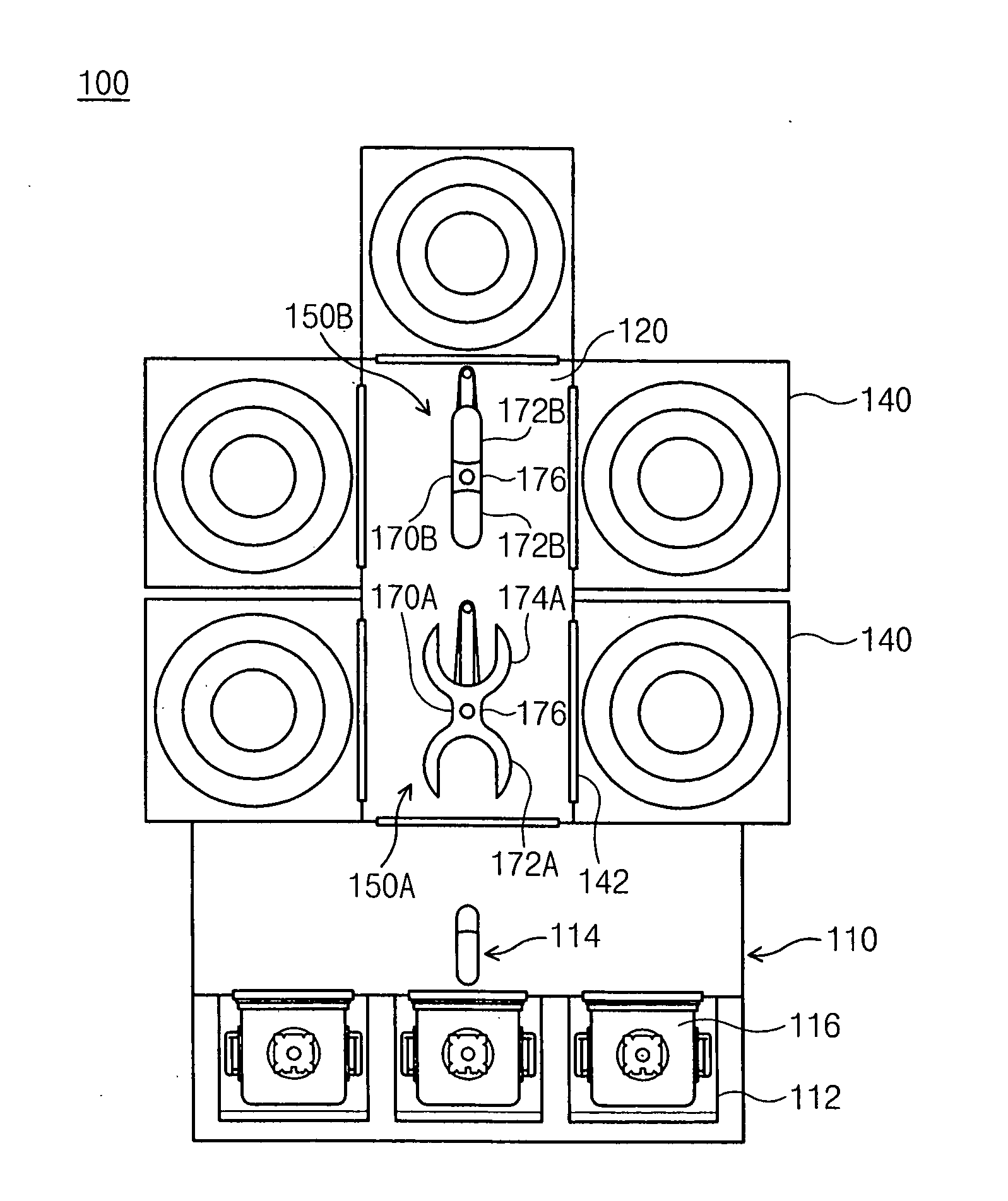

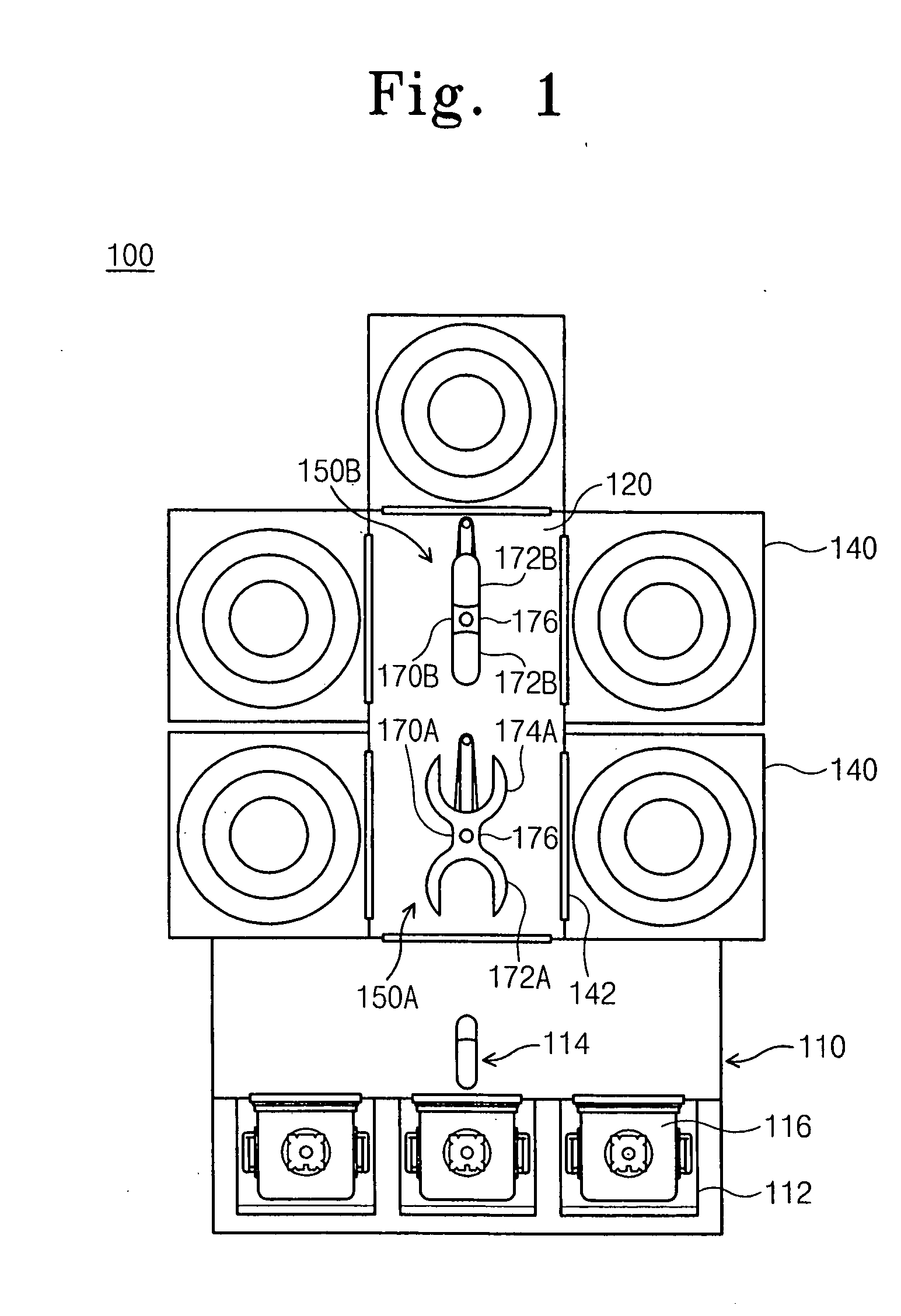

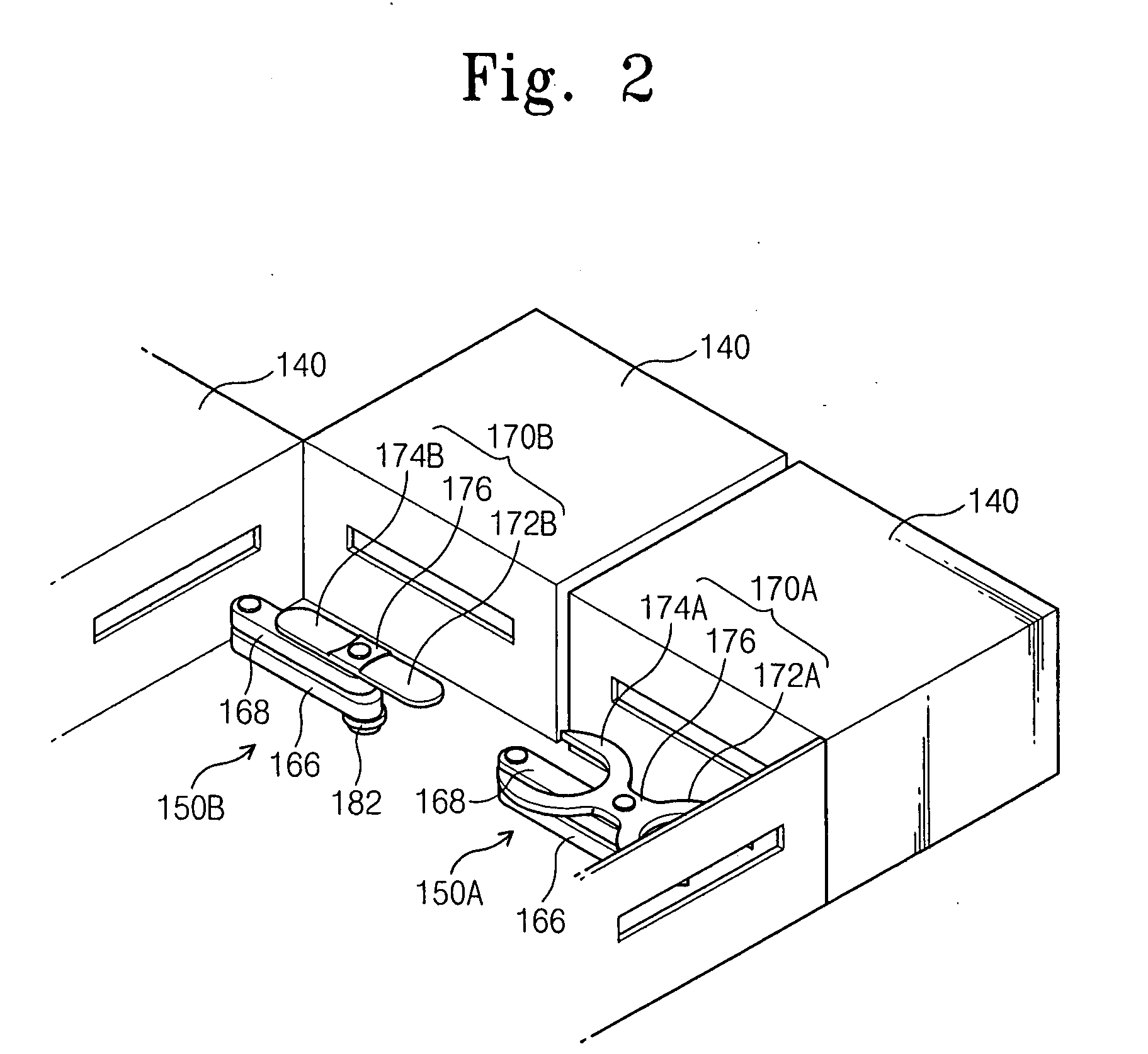

Multi-chamber system

InactiveUS20050111936A1MinimizesMinimizing equipmentSemiconductor/solid-state device manufacturingStorage devicesMechanical engineeringRobot

A multi-chamber system includes an index station at which one or more substrate cassettes are placed, a transfer passageway having one end adjacent the index station, at least one process chamber disposed alongside the transfer passageway, and at least one substrate transfer robot disposed in the transfer passageway for receiving a substrate from the index station and by which the substrate is transferred to each process chamber. The multi-chamber system has a minimal footprint. Furthermore, the system can be easily expanded. In addition, the substrate transfer robot(s) may have a blade including two substrate supports so that the time required for moving a substrate through the system is minimized.

Owner:SAMSUNG ELECTRONICS CO LTD

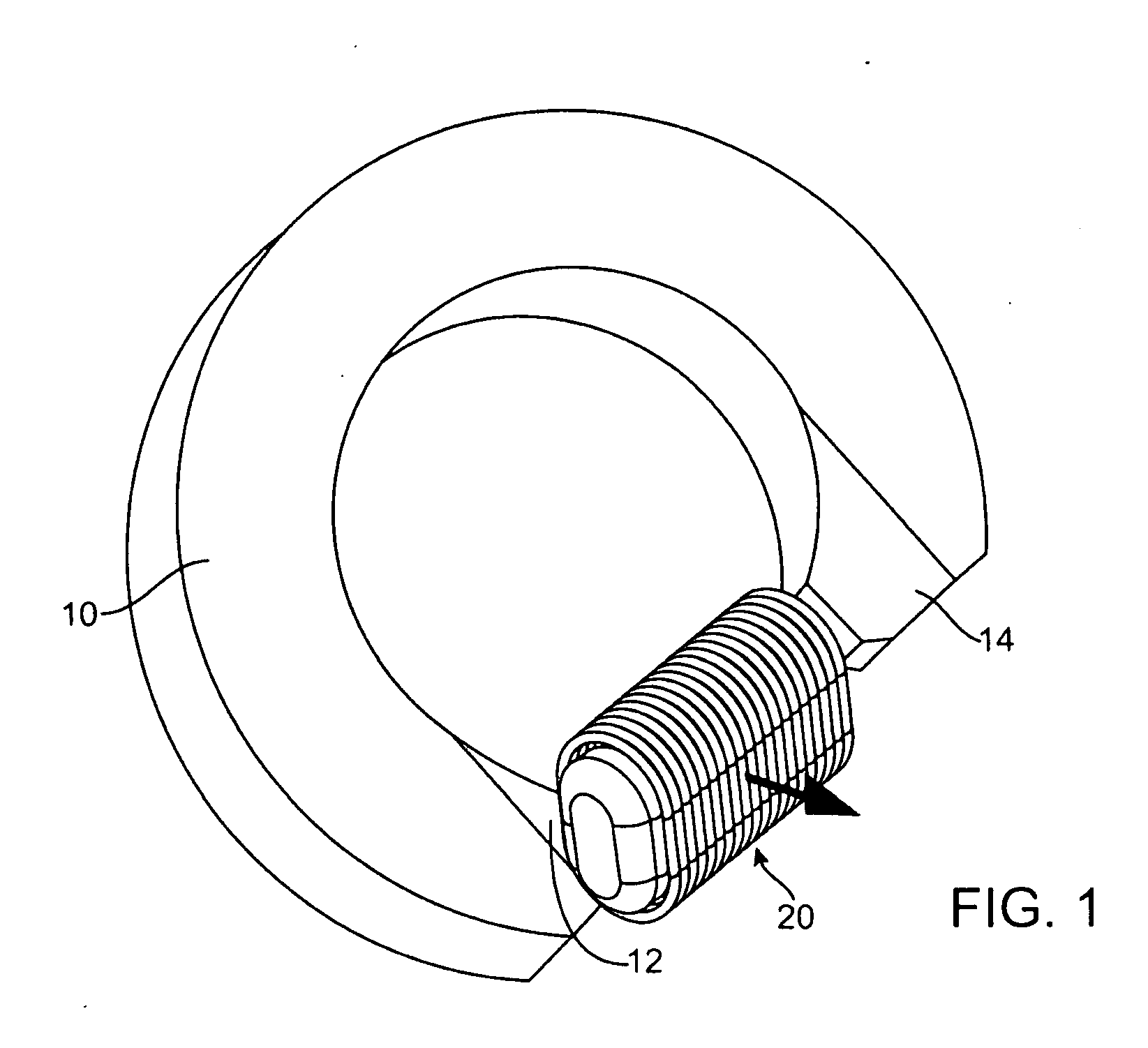

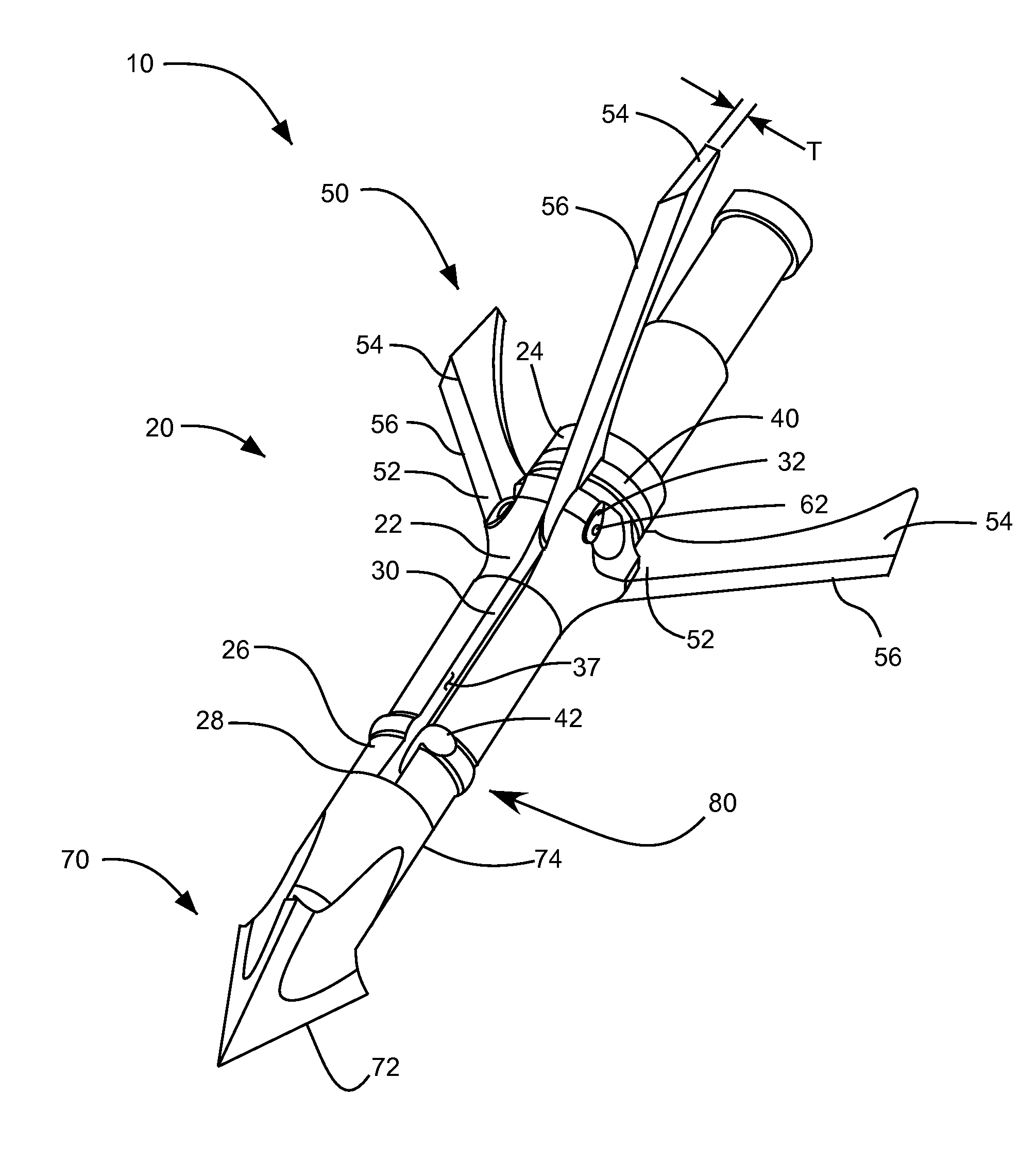

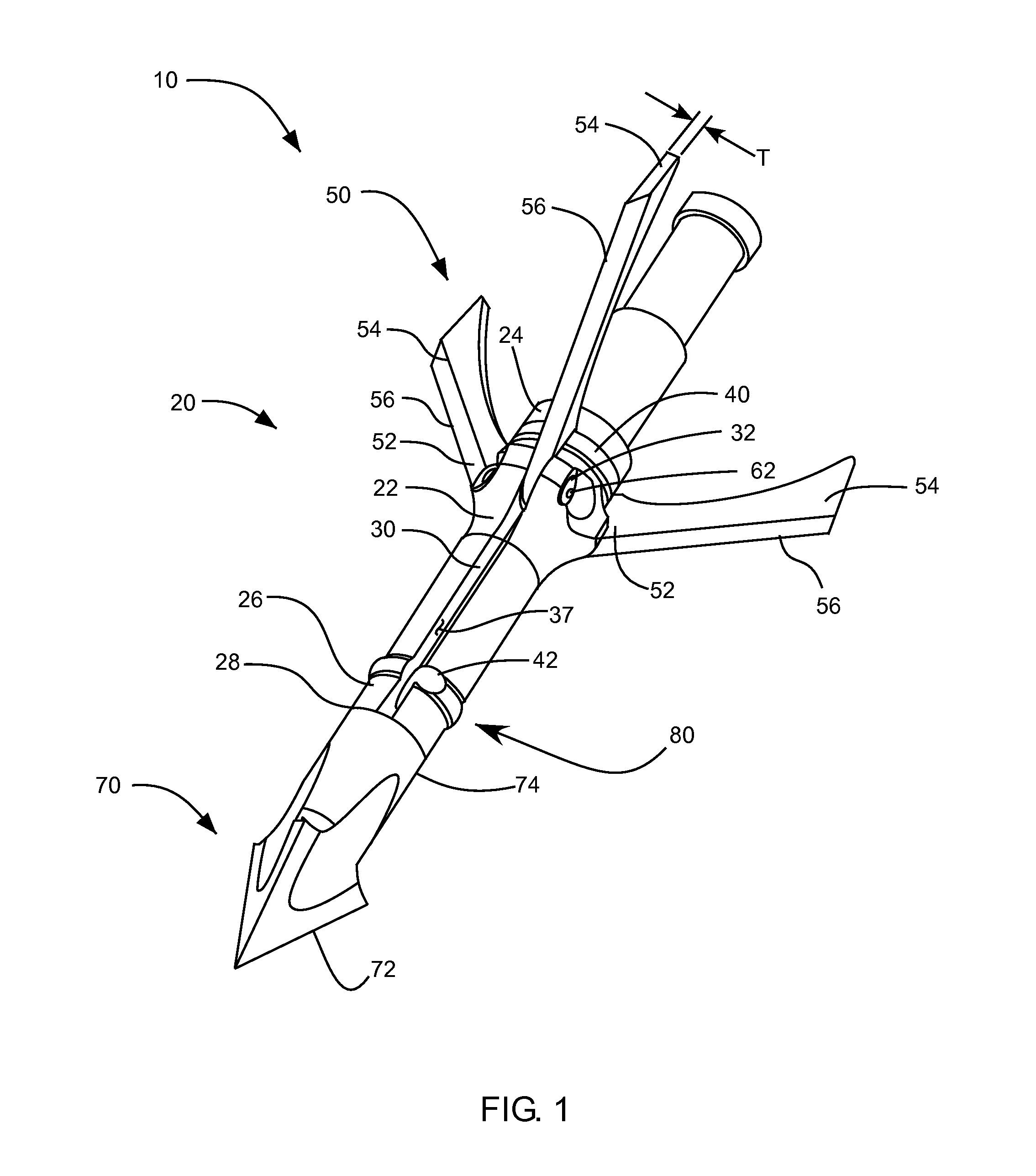

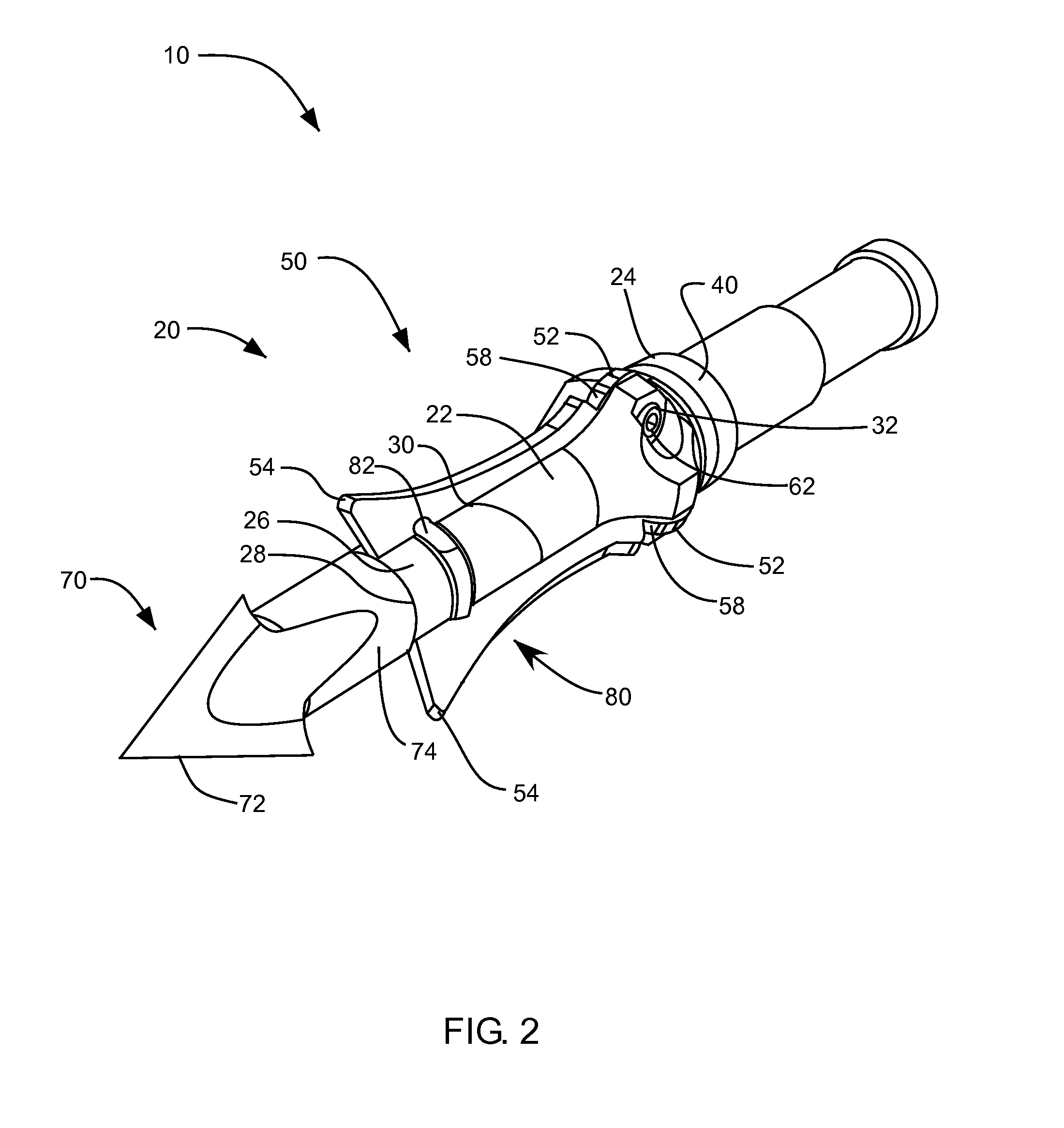

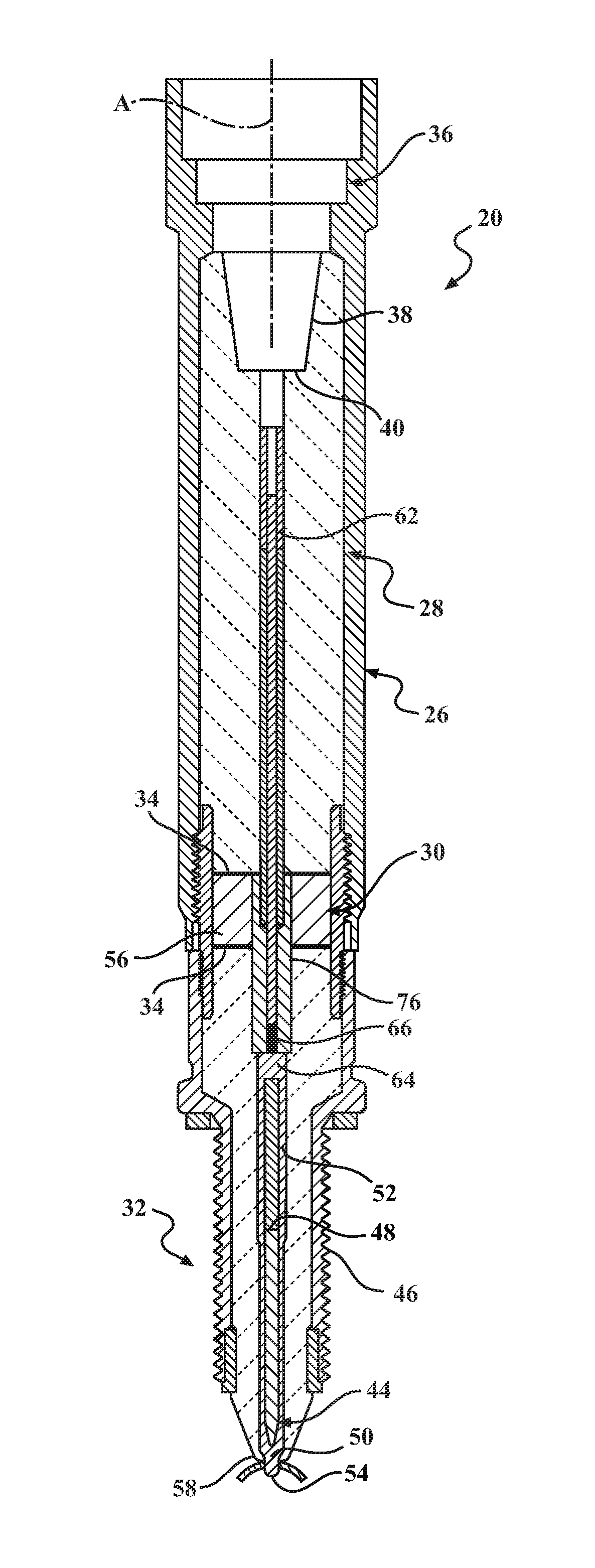

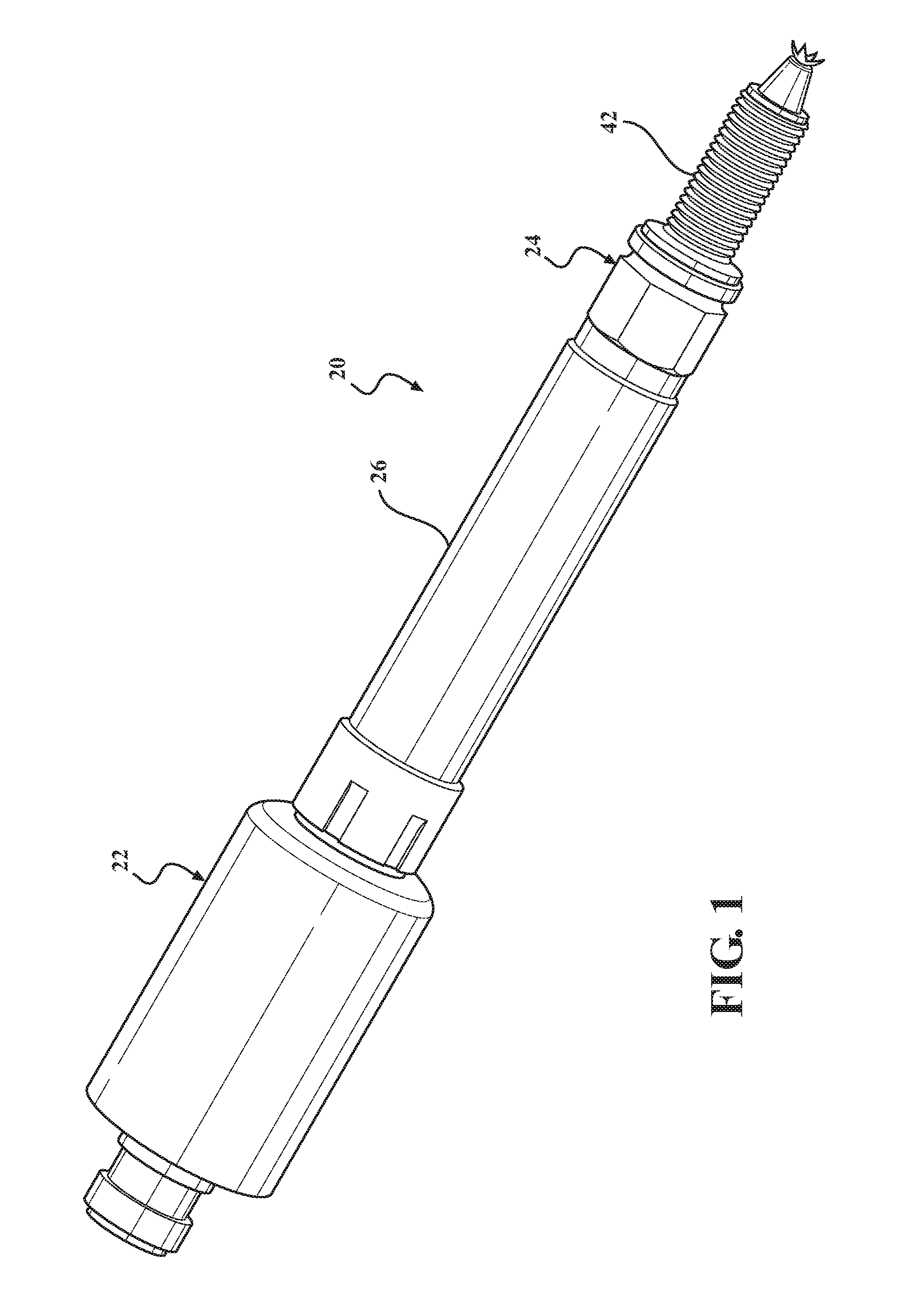

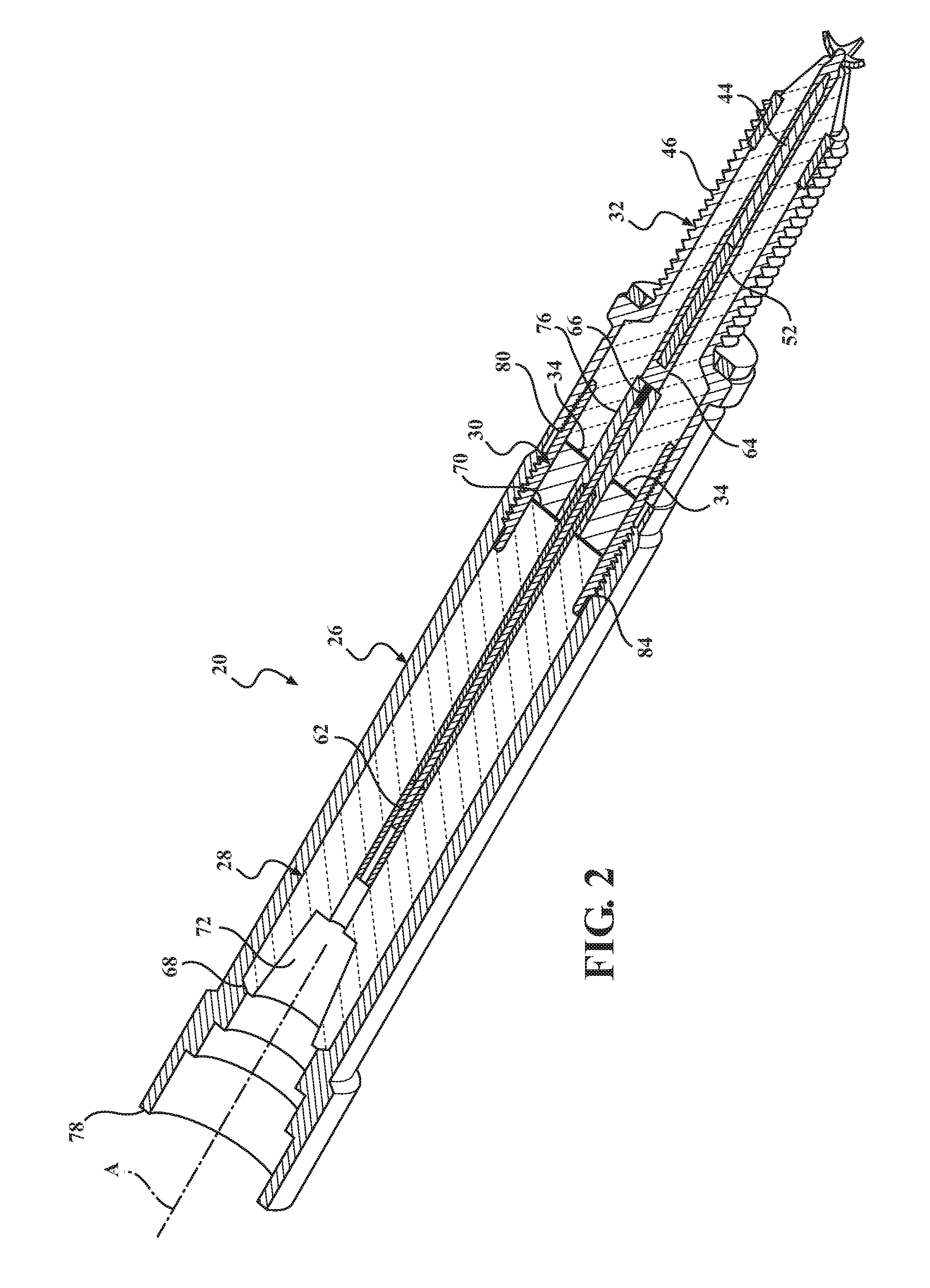

Broadhead arrow tip and associated methods

InactiveUS20140194234A1MinimizesReduce manufacturing complexityThrow gamesArrowsEngineeringMechanical engineering

Owner:MILES CHRISTOPHER RAY

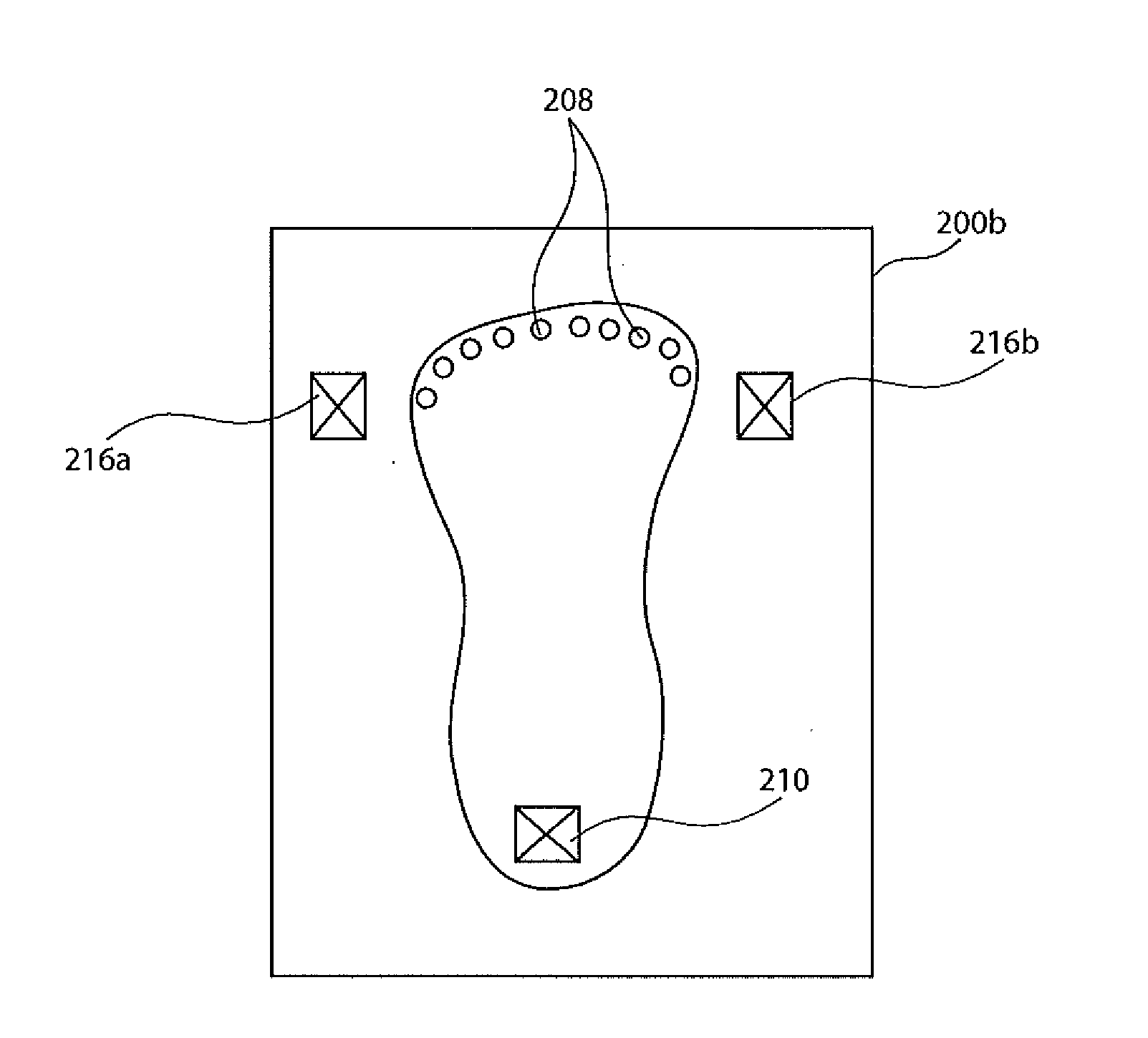

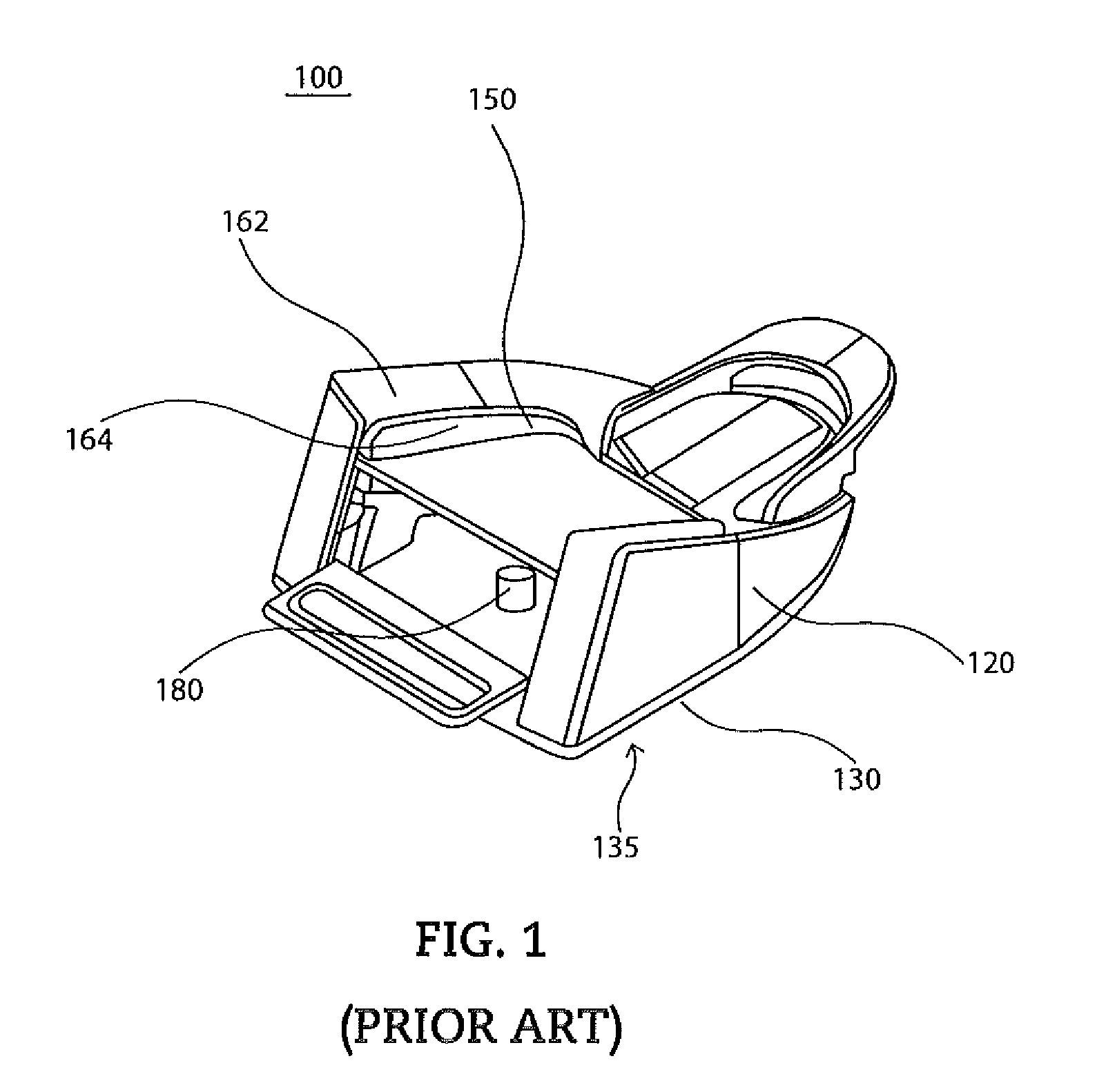

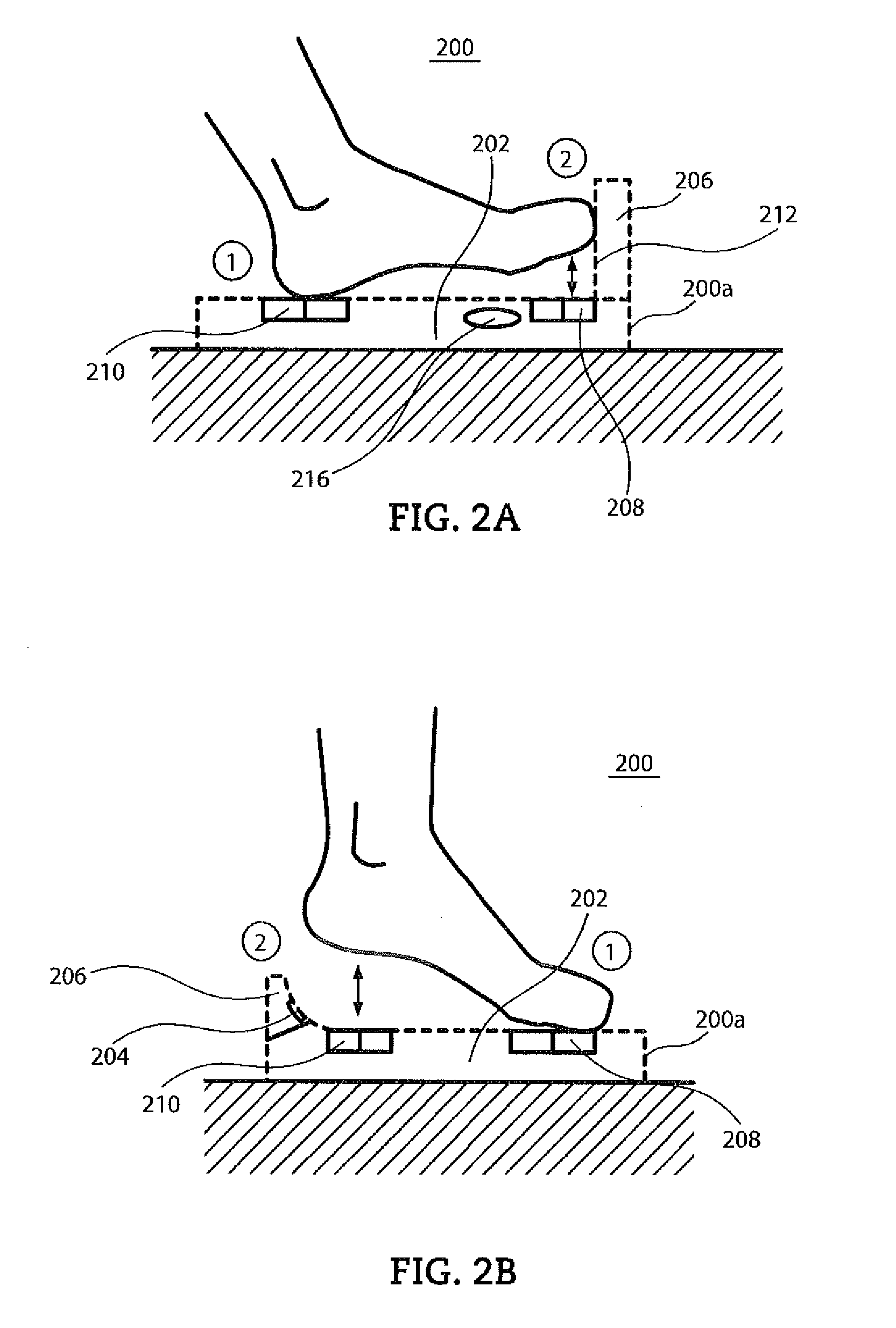

Foot pedal system and apparatus

InactiveUS20140378986A1Reduce mechanical failureImprove ergonomicsEye surgerySurgical manipulatorsEngineeringSurgical instrument

A phacoemulsification system and method, and a foot pedal device, system and method. The devices, systems and methods may include a console comprising a plurality of modes for at least one physically associated surgical instrument, and a foot pedal communicatively associated with said console and suitable for varying ones of the plurality of modes. The foot pedal may include a foot pedal base, and at least two electronically actuated sensors physically associated with the foot pedal base, communicatively connected to the console, and suitable for receiving physical indications of variations in ones of the plurality of modes.

Owner:JOHNSON & JOHNSON SURGICAL VISION INC

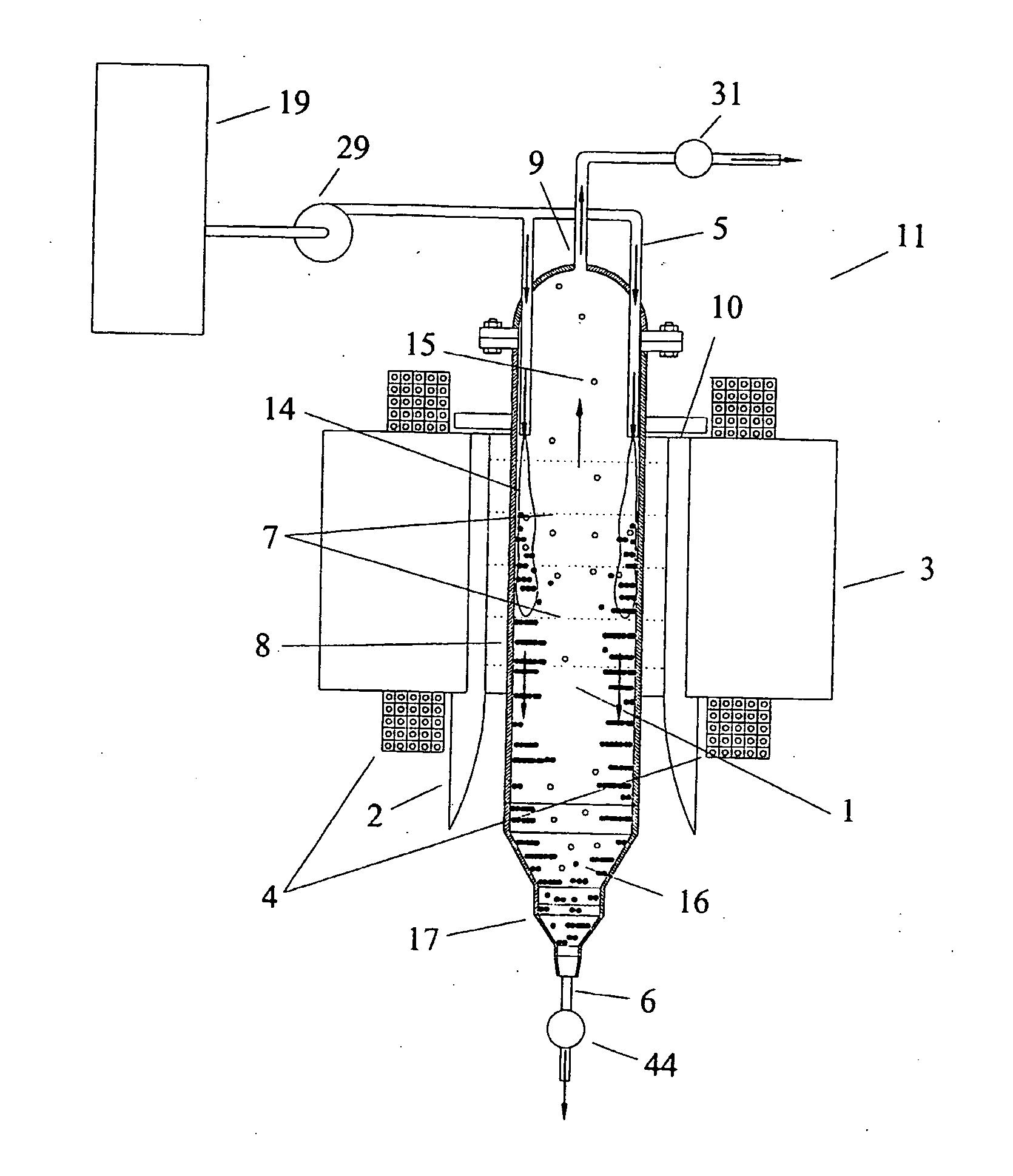

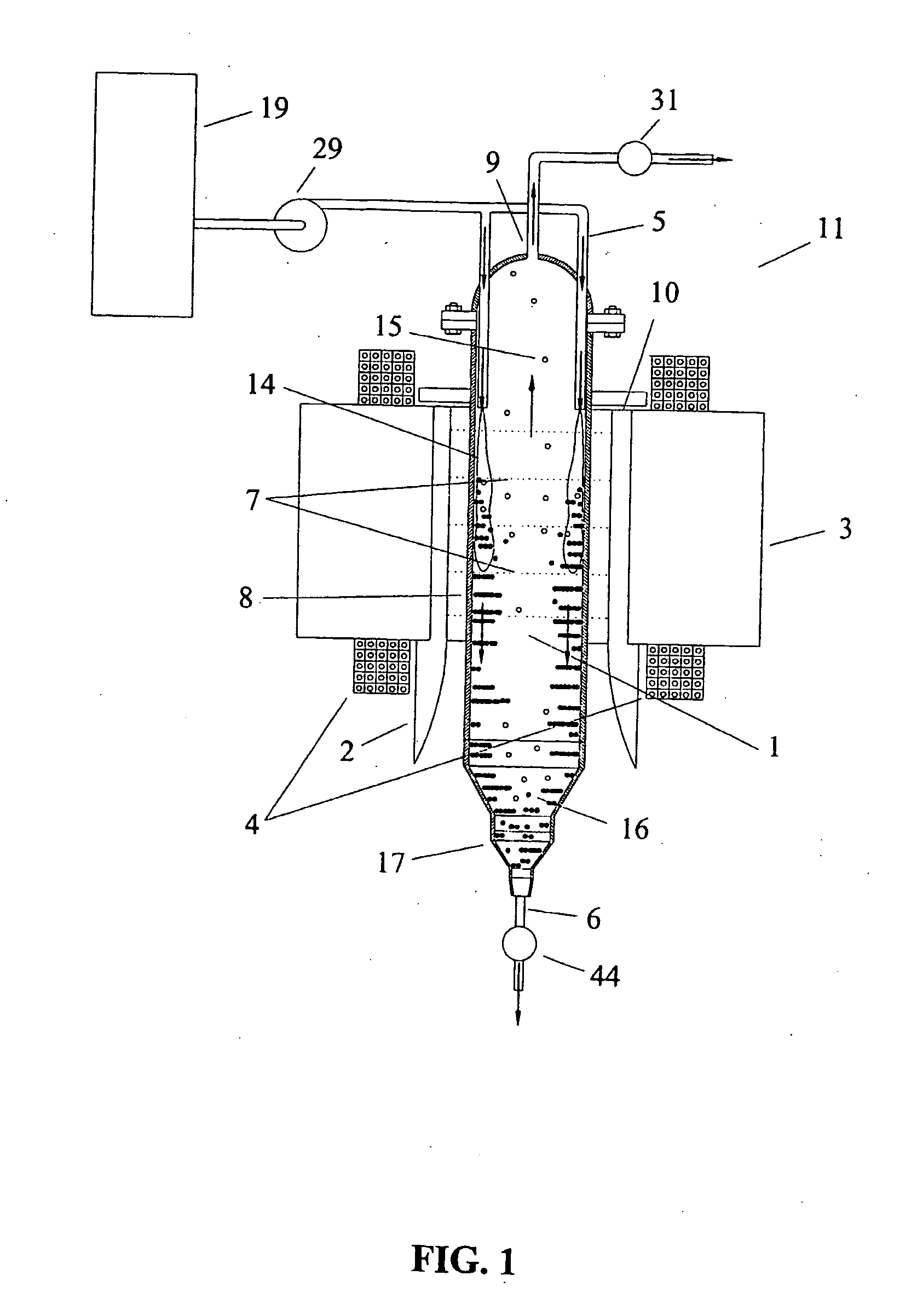

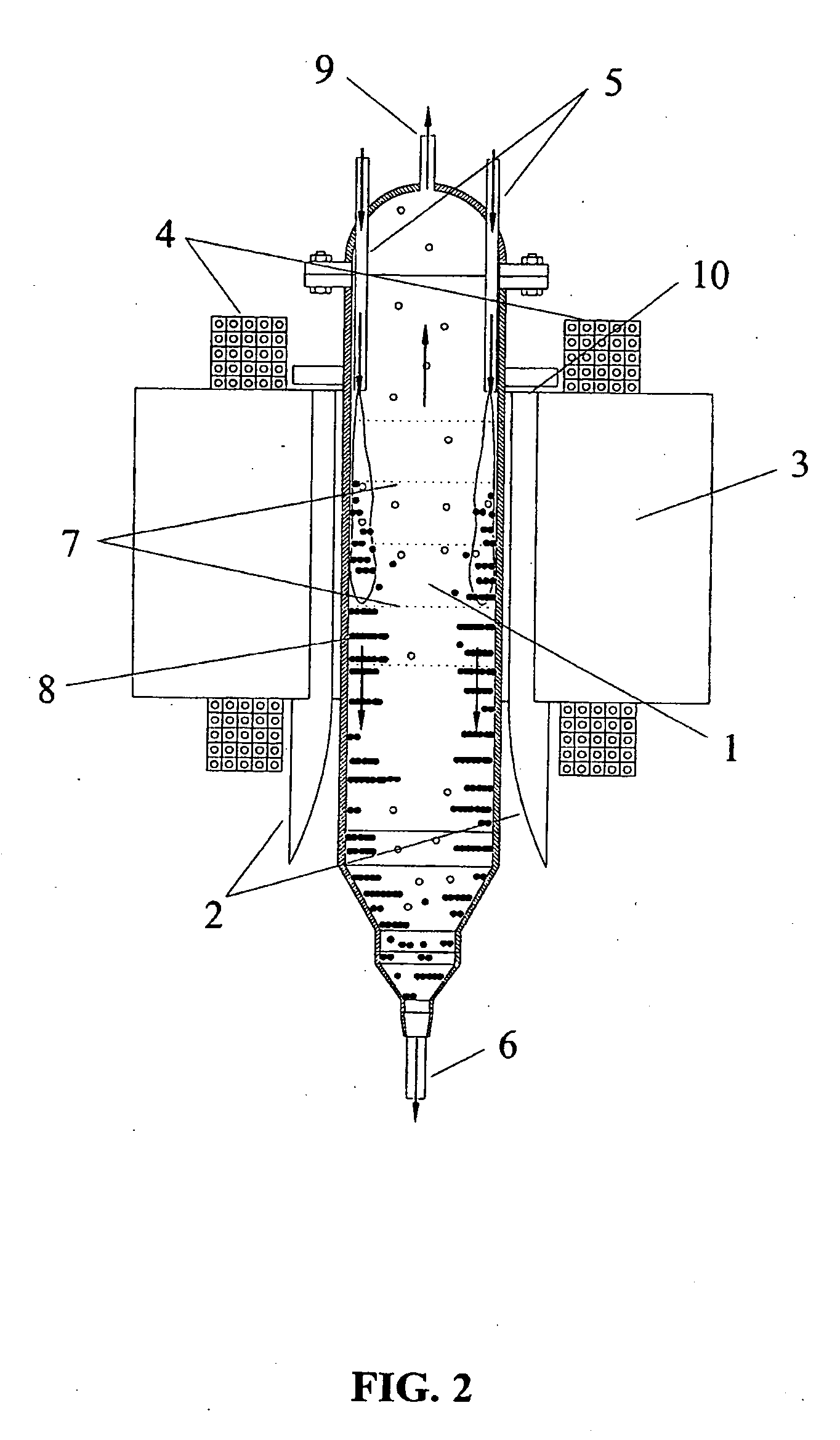

Apparatus and method for continuous separation of magnetic particles from non-magnetic fluids

InactiveUS20100200511A1Avoid stickingMinimize impactSettling tanks feed/dischargeWater/sewage treatment by magnetic/electric fieldsNon magneticMolecular physics

Owner:RES USA LLC

Efficient and reliable multicast over a Wi-Fi network

ActiveUS8411608B2Improve multicast performanceImprove performanceError prevention/detection by using return channelBroadcast specific applicationsWi-FiPacket loss

A “Wi-Fi Multicaster” provides a practical and efficient Wi-Fi multicast system for environments having potentially large numbers of Wi-Fi clients. Significantly, the Wi-Fi Multicaster does not require any changes to the 802.11 protocol, or to the underlying Wi-Fi infrastructure. In various embodiments, the Wi-Fi Multicaster uses pseudo-broadcast, and augments it with destination control, association control and optional proactive FEC (forward error correction) to improve multicast performance. More specifically, the Wi-Fi Multicaster system converts multicast packets to targeted unicast transmissions. To minimize the amount of airtime consumed, the Wi-Fi Multicaster uses destination control in combination with various algorithms for association control. Further, in various embodiments, the Wi-Fi Multicaster includes an adaptive, proactive FEC scheme to reduce overall packet losses. Finally, to overcome the challenges posed by encryption protocols such as 802.1x, the Wi-Fi Multicaster uses a “virtual multicast interface” that allows clients to “share” a common key for each multicast.

Owner:MICROSOFT TECH LICENSING LLC

Corona suppression at the high voltage joint through introduction of a semi-conductive sleeve between the central electrode and the dissimilar insulating materials

ActiveUS20170025824A1Relieve pressureMinimizesSparking plugs manufactureCorona dischargeIgnition coilCorona discharge

A corona ignition assembly comprising a plurality of different insulators disposed between an ignition coil assembly and firing end assembly is provided. A high voltage center electrode extends longitudinally between an igniter central electrode and the ignition coil assembly. A high voltage insulator formed of a fluoropolymer surrounds the high voltage center electrode, and a firing end insulator firing of alumina surrounds the igniter central electrode. A sleeve formed of a semi-conductive and complaint material, such as silicone rubber with conductive filler, is disposed radially between the electrodes and adjacent insulators. The sleeve fills air gaps and minimizes the peak electric field within the corona igniter assembly. The sleeve is able to prevent unwanted corona discharge, and thus extends the life of the materials and directs energy to the firing end.

Owner:TENNECO INC

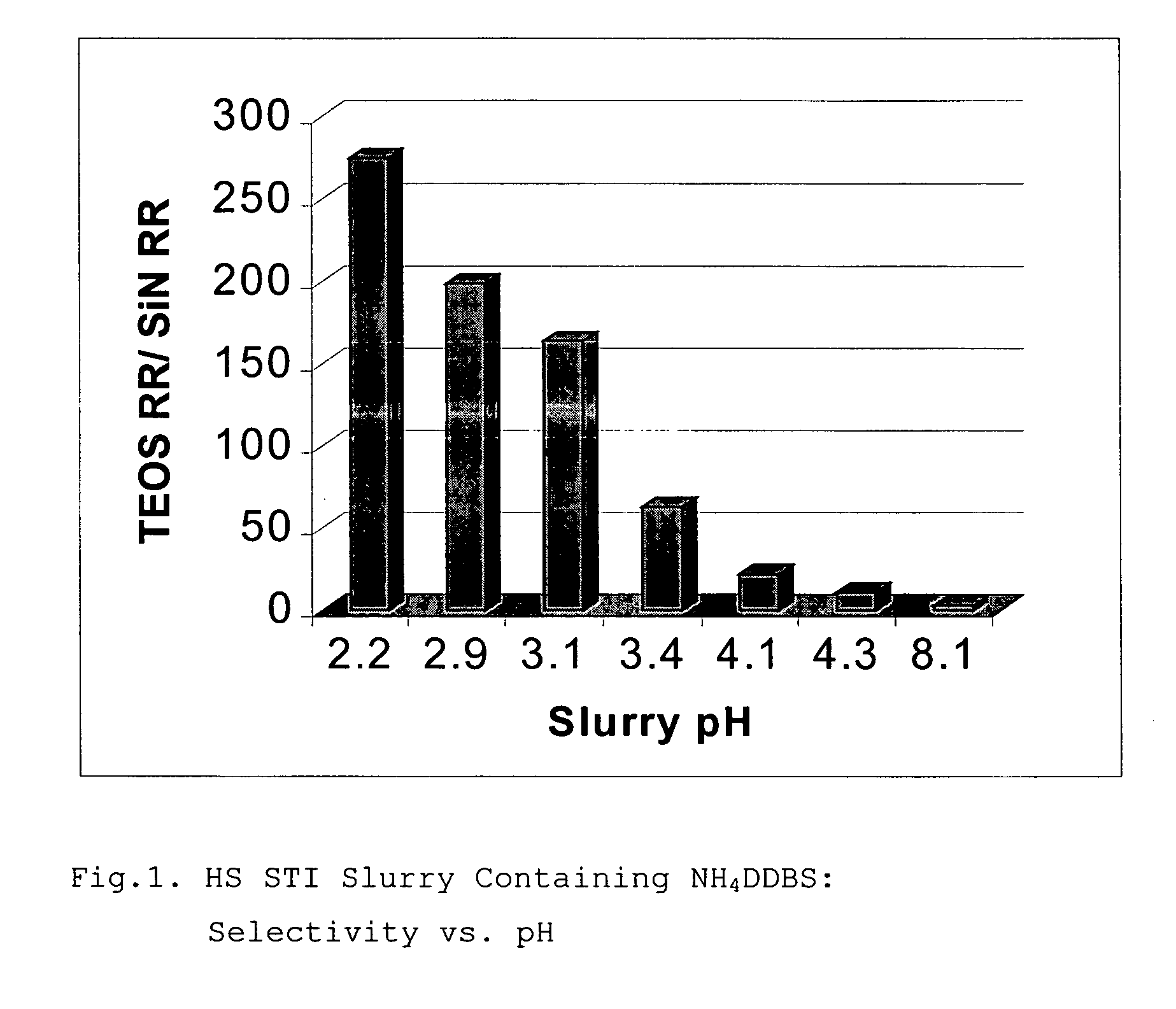

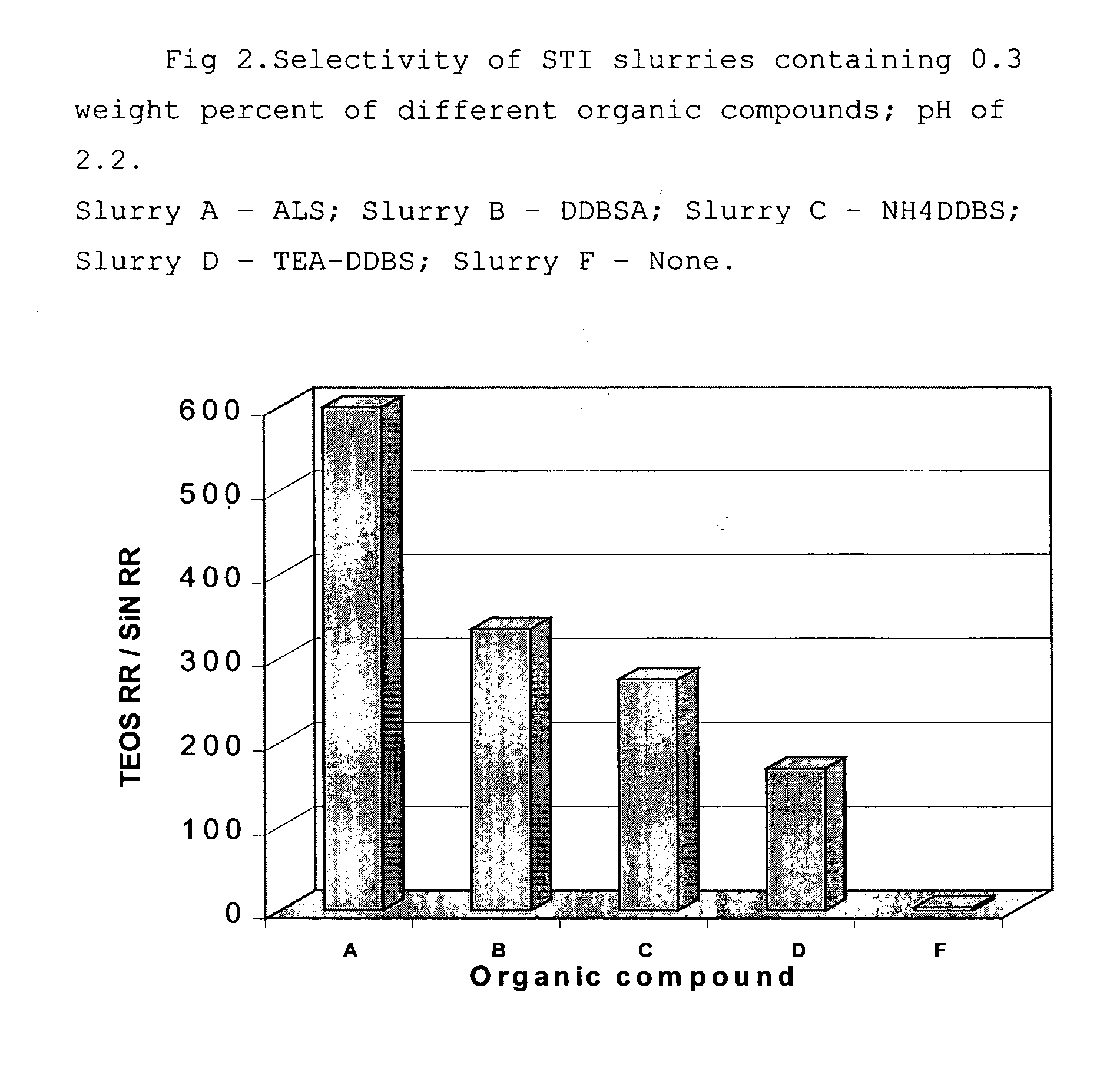

High selectivity colloidal silica slurry

InactiveUS20050113000A1MinimizesOther chemical processesSemiconductor/solid-state device manufacturingColloidal silicaColloid

Provided is a novel high selectivity aqueous slurry composition method of utilizing same. The composition includes non-modified silica based abrasive particles in an amount of about 5 to about 50 weight percent, and an organic compound in an amount of about 0.001 to about 2.0 weight percent in an aqueous solution, wherein the silicon oxide to silicon nitride selectivity ratio ranges from about 50 to about 700.

Owner:AKZO NOBEL CHEM INT BV

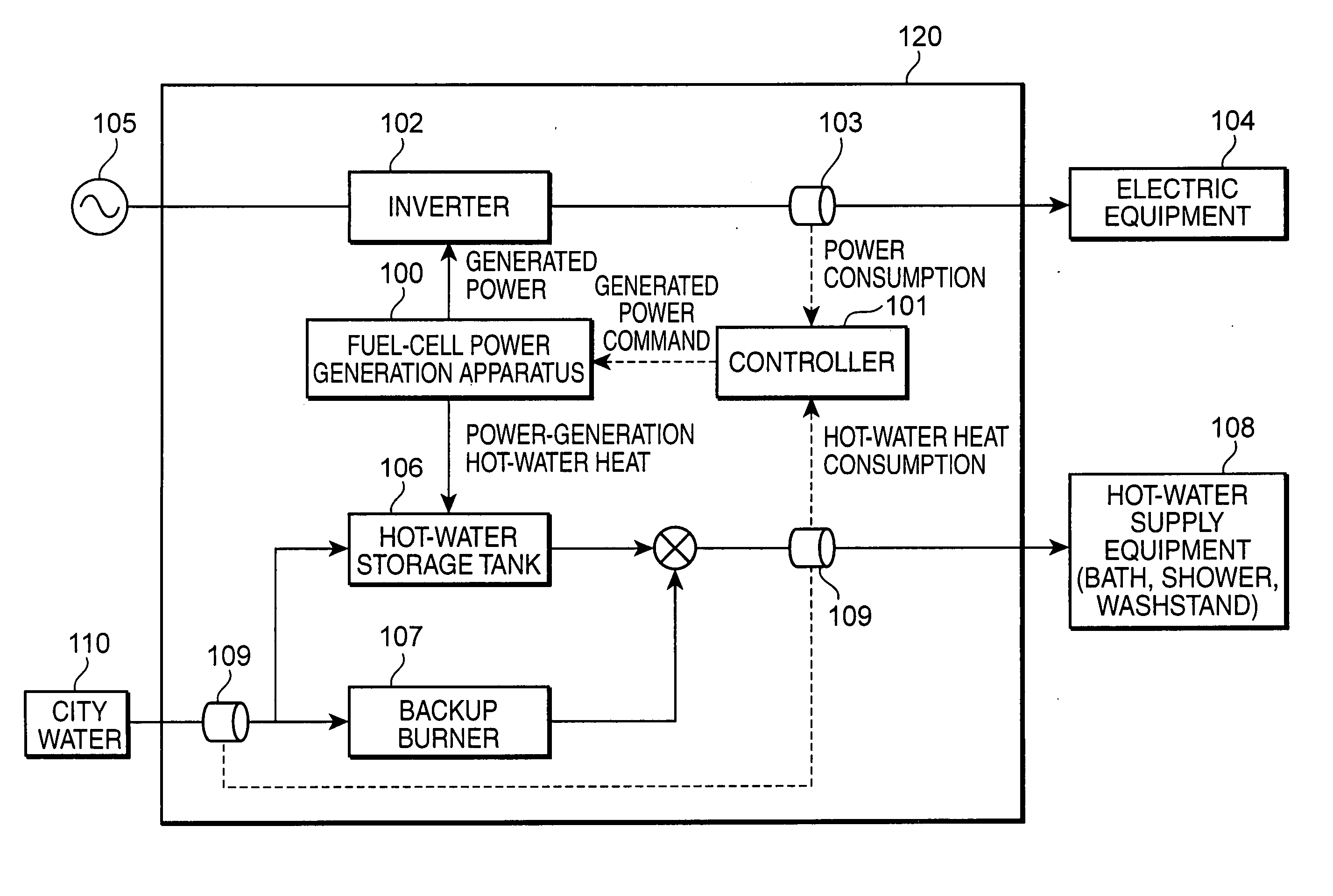

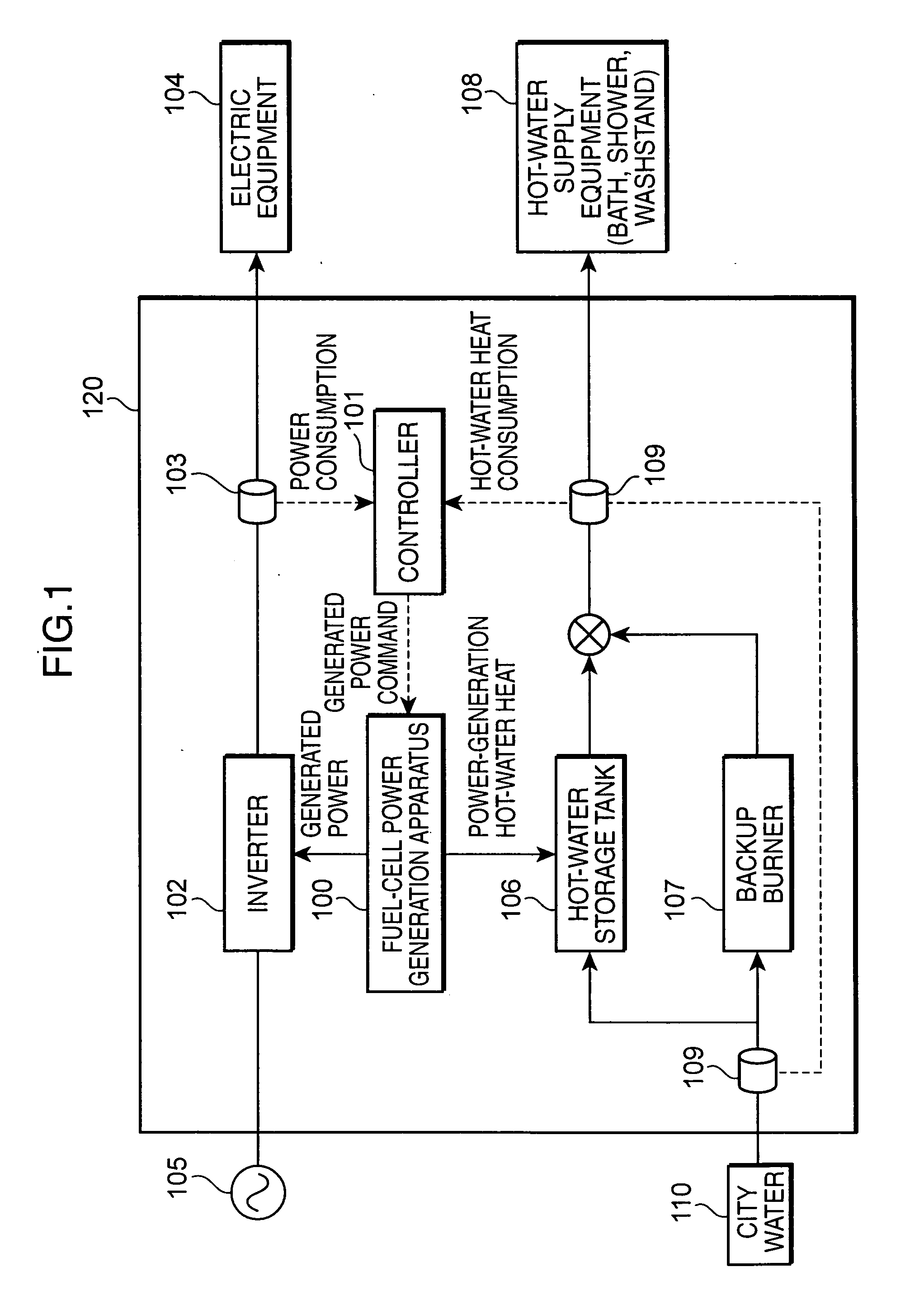

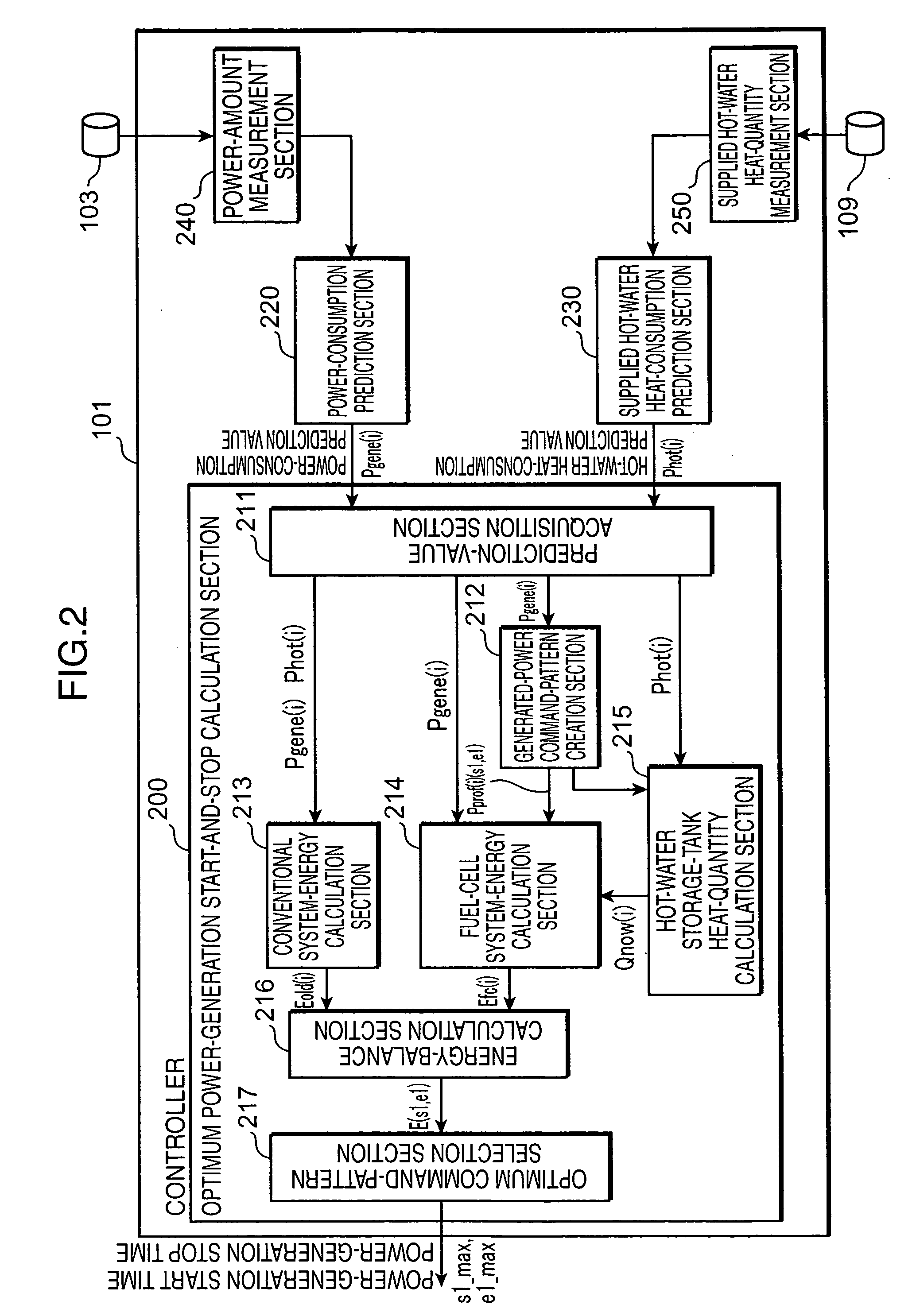

Control Unit For Fuel-Cell Power Generation Apparatus, And Control Method, Control Program And Computer-Readable Record Medium With Control Program For The Same

InactiveUS20080038604A1MinimizesEasy to operateFluid heatersEnergy efficient heating/coolingStart timeElectrical devices

A control unit is provided which is capable of operating a fuel-cell power generation apparatus efficiently according to a power consumption and a supplied hot-water heat consumption which are different in each home, and realizing the saving of energy. A generated-power command-pattern creation section 212 creates a plurality of generated-power command patterns which are obtained from a combination of a start time and a stop time of the fuel-cell power generation apparatus, based on a power-consumption prediction value; a hot-water storage-tank heat-quantity calculation section 215 calculates a stored hot-water heat quantity for a predetermined period in a hot-water storage tank, based on a supplied hot-water heat-consumption prediction; a fuel-cell system-energy calculation section 214 calculates fuel-cell system energy which indicates the energy of a fuel required in hot-water supply equipment and electricity required in electric equipment when the fuel-cell power generation apparatus is operated in each generated-power command pattern; and in terms of the fuel-cell system energy in each of the plurality of generated-power command patterns, an optimum command-pattern selection section 217 operates the fuel-cell power generation apparatus in the generated-power command pattern which minimizes the fuel-cell system energy.

Owner:PANASONIC CORP

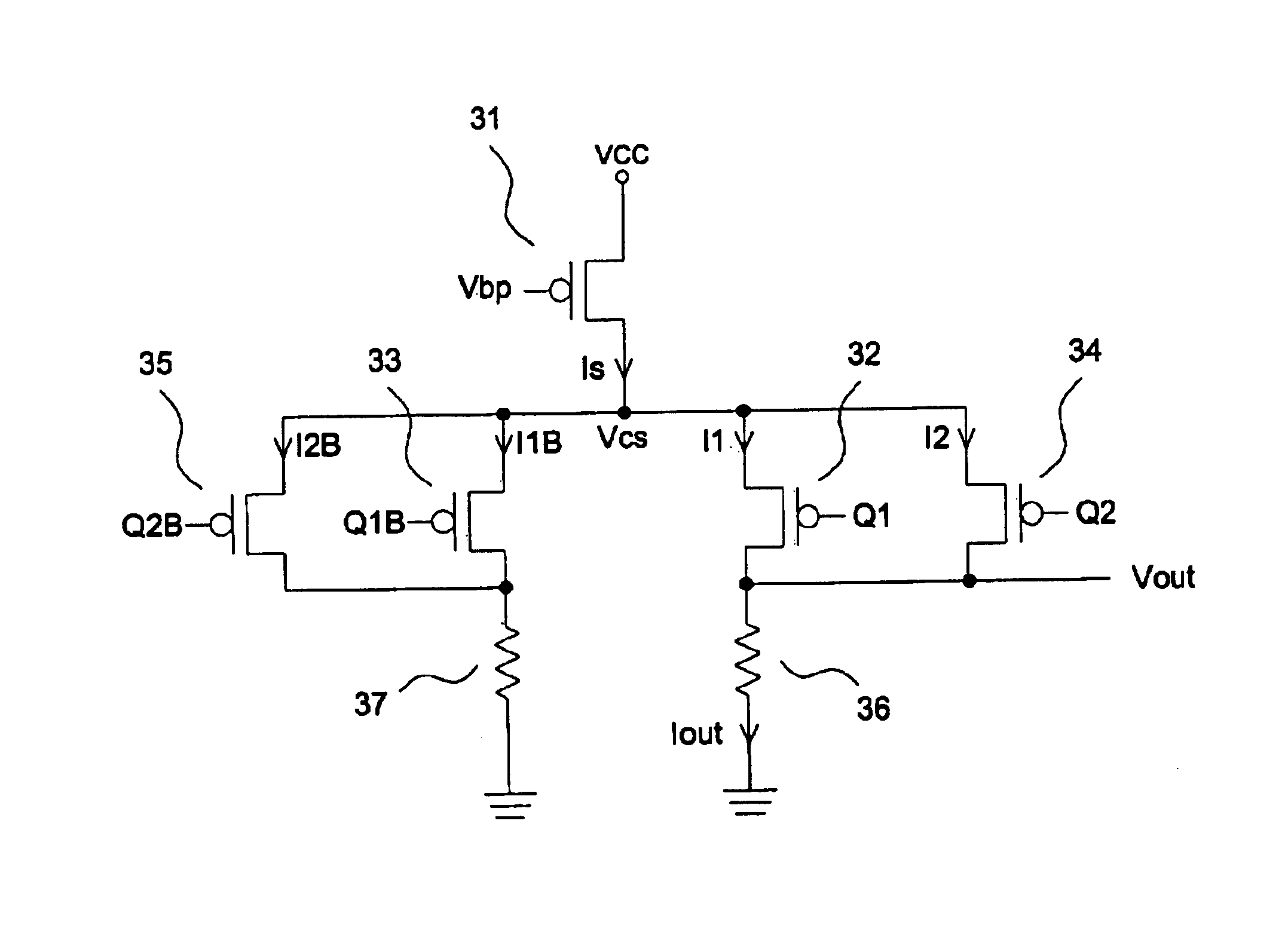

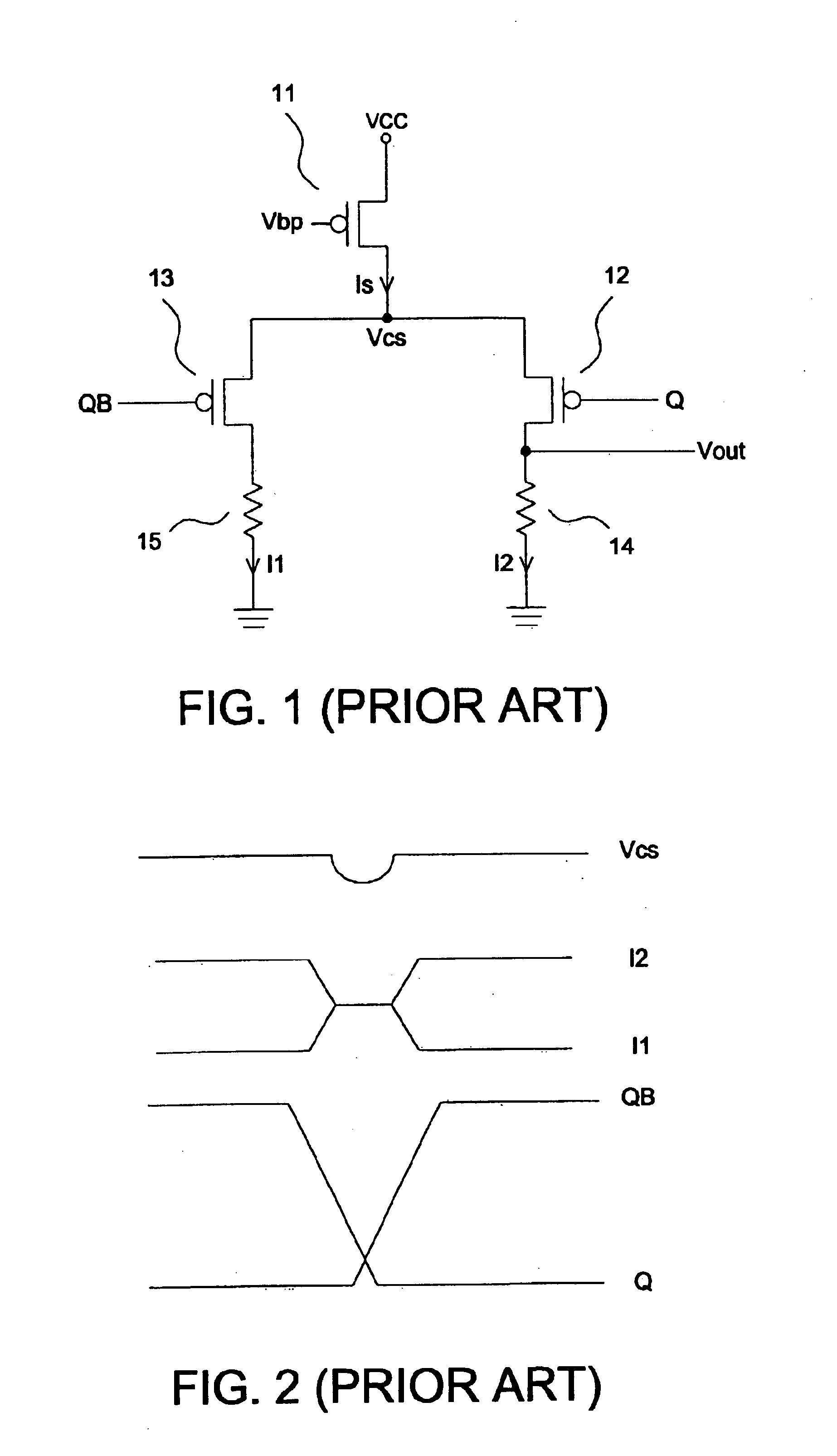

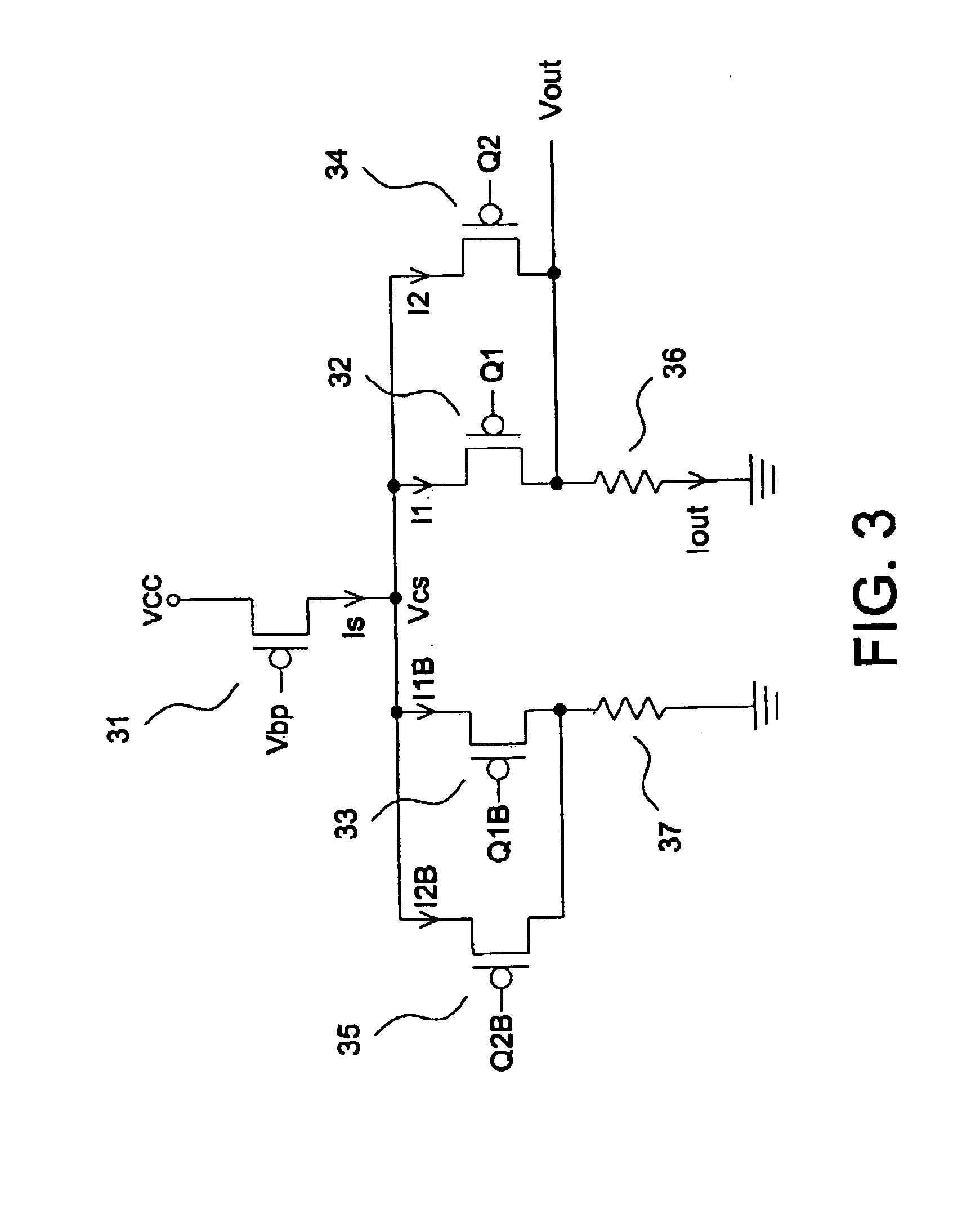

DAC cell circuit

ActiveUS6844835B2Settling fastMinimizesElectric signal transmission systemsDigital-analogue convertorsMOSFETDigital analog converter

A digital-analog converter (DAC) cell circuit. The circuit includes a current source, a first resistor, a second resistor, a first MOSFET, a second MOSFET, a third MOSFET and a forth MOSFET. The first MOSFET has a source and a drain connected to the current source and the first resistor, respectively, and a gate receiving a first control signal. The second MOSFET has a source and a drain connected to the current source and the second resistor, respectively, and a gate receiving a second control signal. The third MOSFET has a source and a drain connected to the source and drain of the first MOSFET, respectively, and a gate receiving a third control signal. The fourth MOSFET has a source and a drain connected to the source and drain of the second MOSFET, respectively, and a gate receiving a fourth control signal. The third control signal is a signal delayed of the first signal and the forth control signal is a signal delayed of the second signal. The delayed control signal can be used to control the slew rate of current DAC cell, thus reduce the package inductance induced L di / dt noise. Also it can be used to reduce the voltage fluctuations during current switching so as to get fast settling current.

Owner:MEDIATEK INC