Patents

Literature

2871 results about "Signal selection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

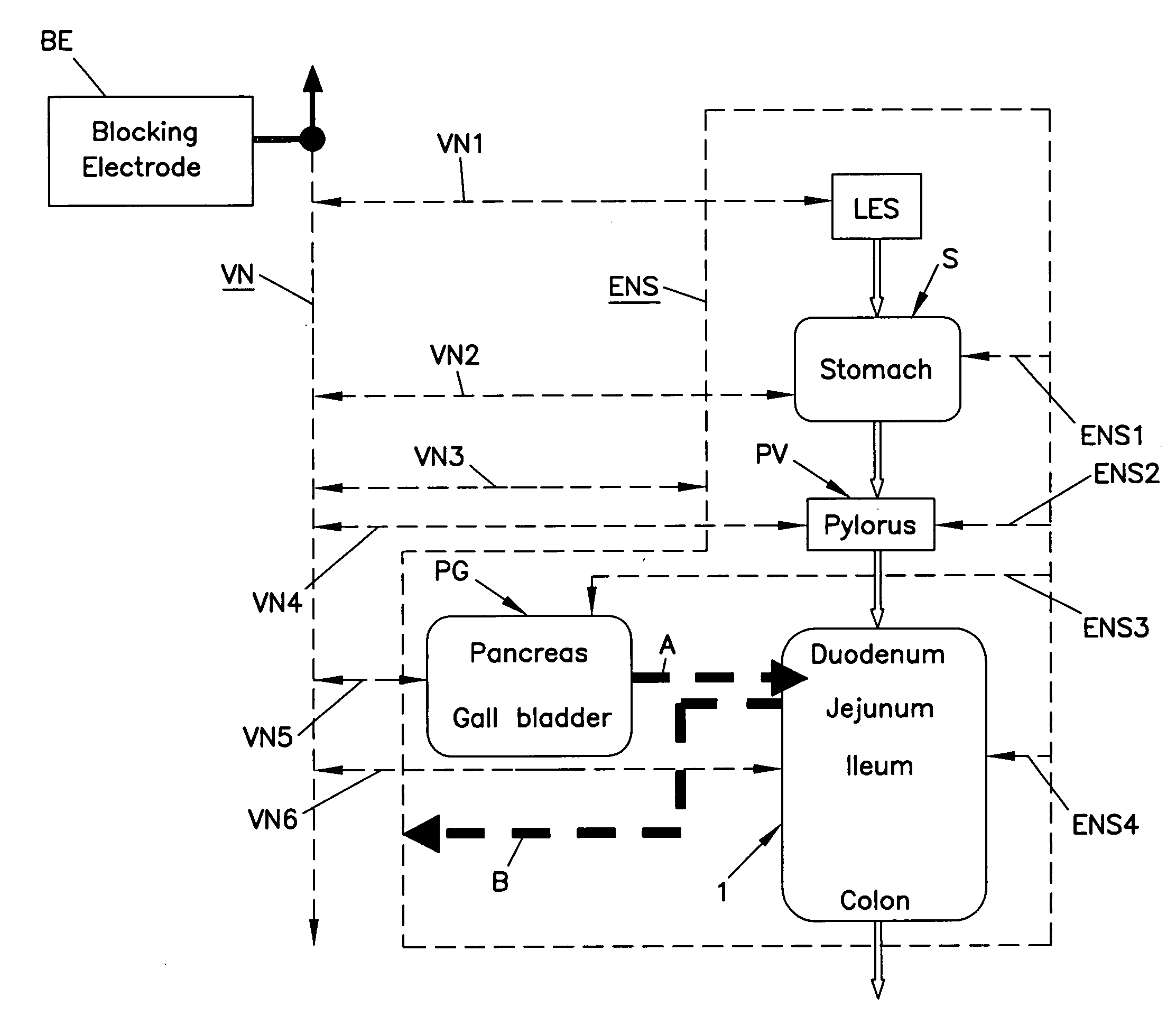

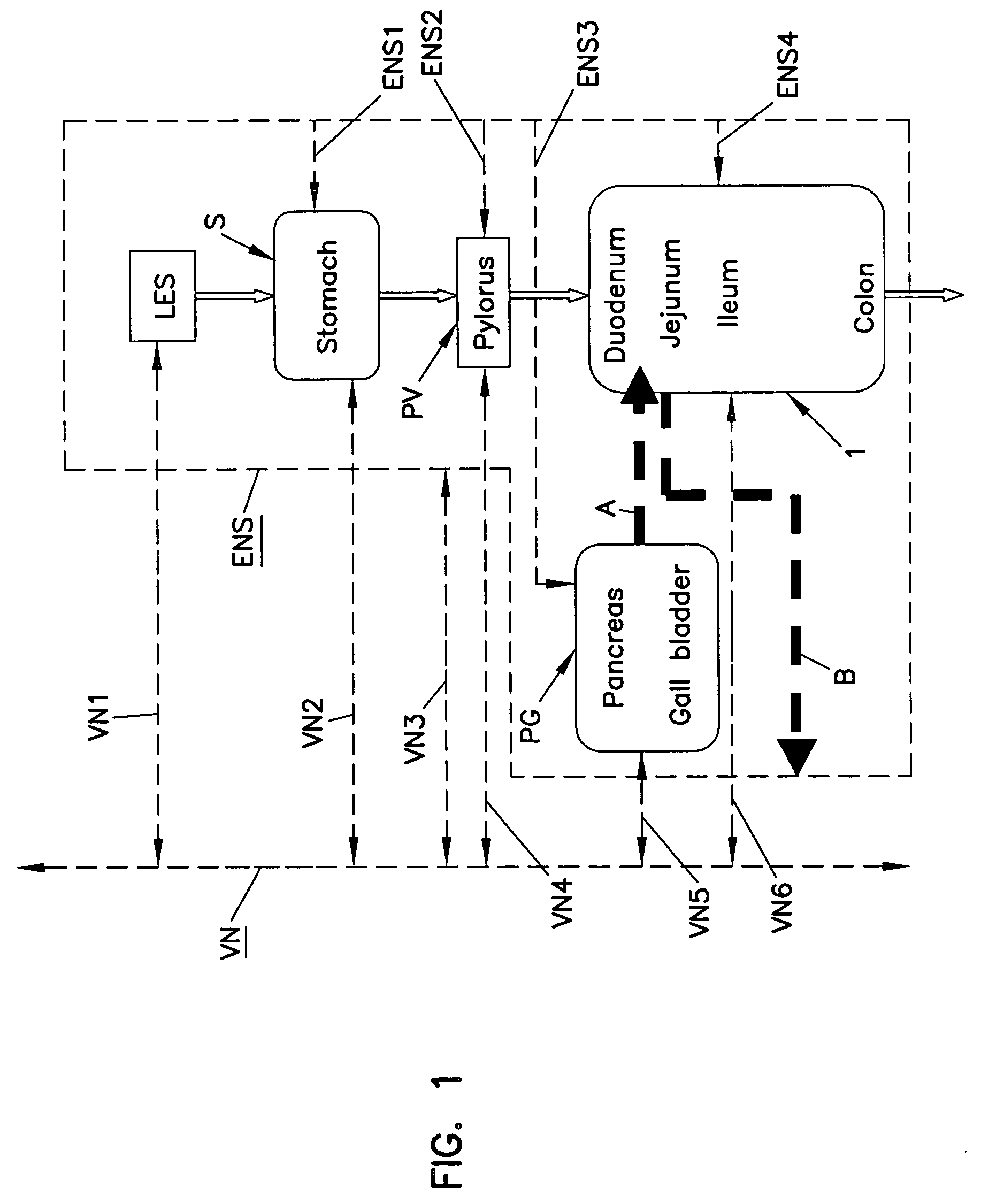

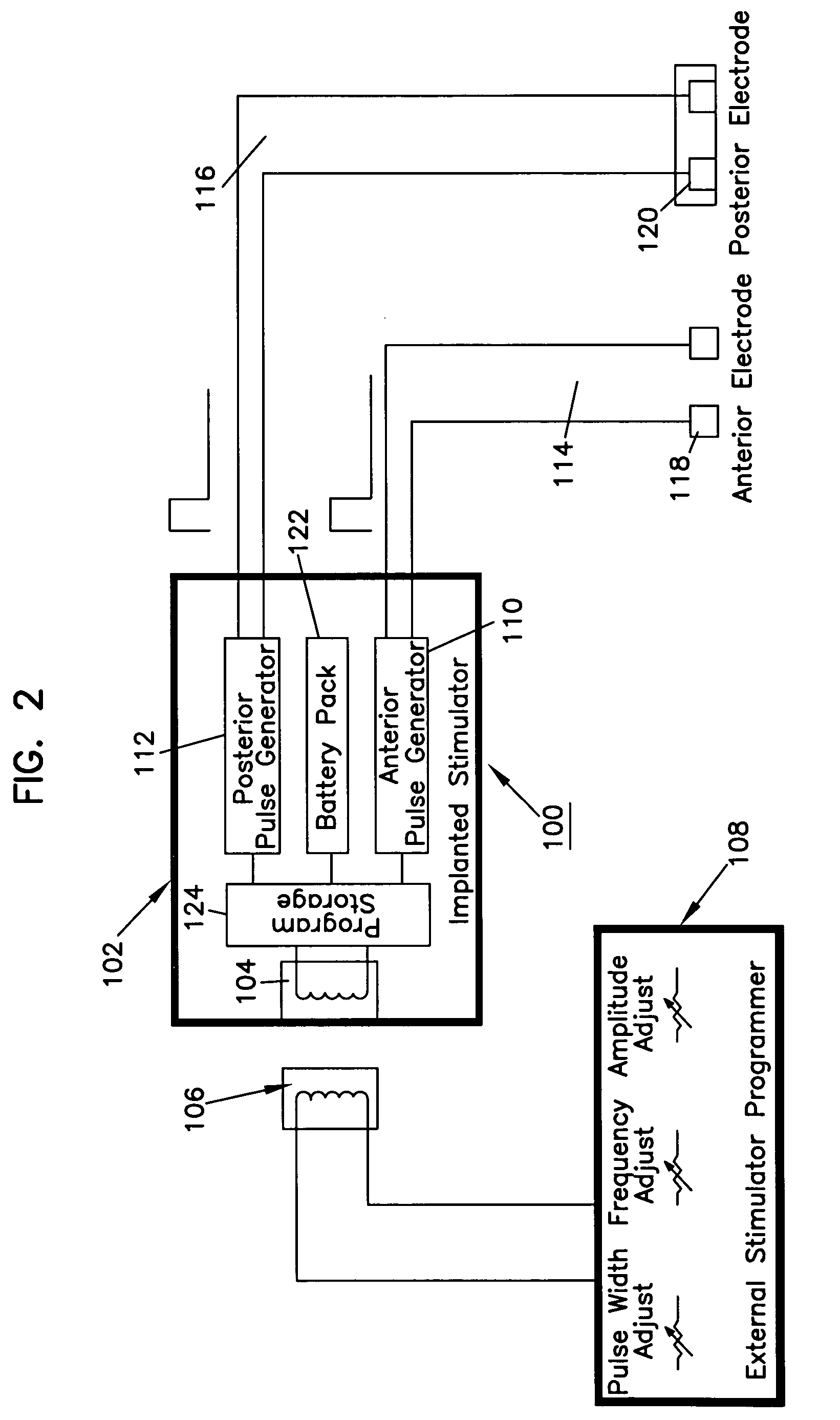

Controlled vagal blockage therapy

A method for treating at least one of a plurality of disorders characterized at least in part by vagal activity includes positioning an electrode around a body organ innervated by the vagus. An electrical signal is applied to the electrode to modulate vagal activity. The electrical signal is applied at a frequency selected for the signal to create a neural conduction block to the vagus with the neural conduction block selected to at least partially block nerve impulses on the vagus. The application of the electrical signal is discontinued. The application of the signal and the discontinuing of the signal are repeated with durations of the discontinuing and the application selected to treat the disorder.

Owner:RESHAPE LIFESCIENCES INC

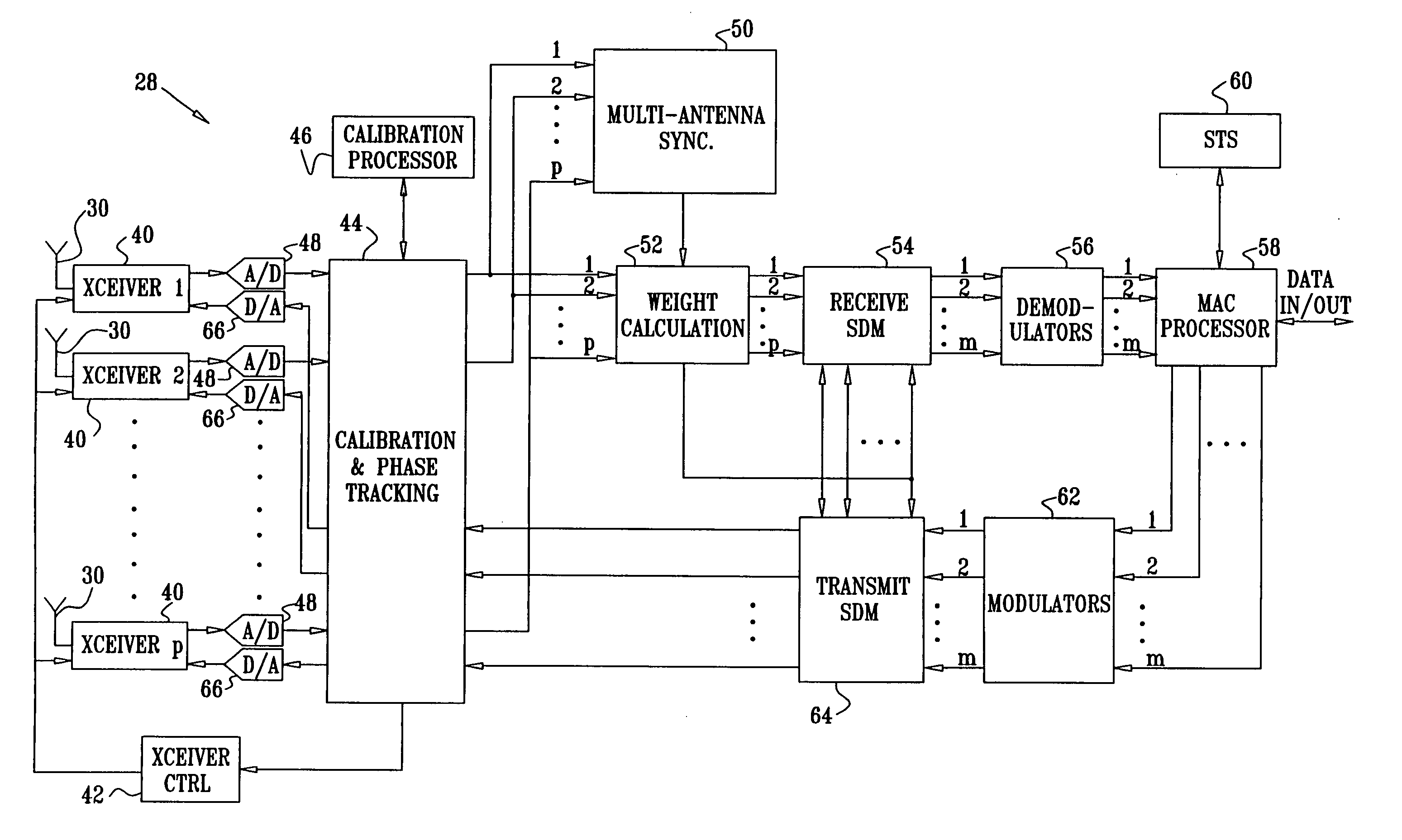

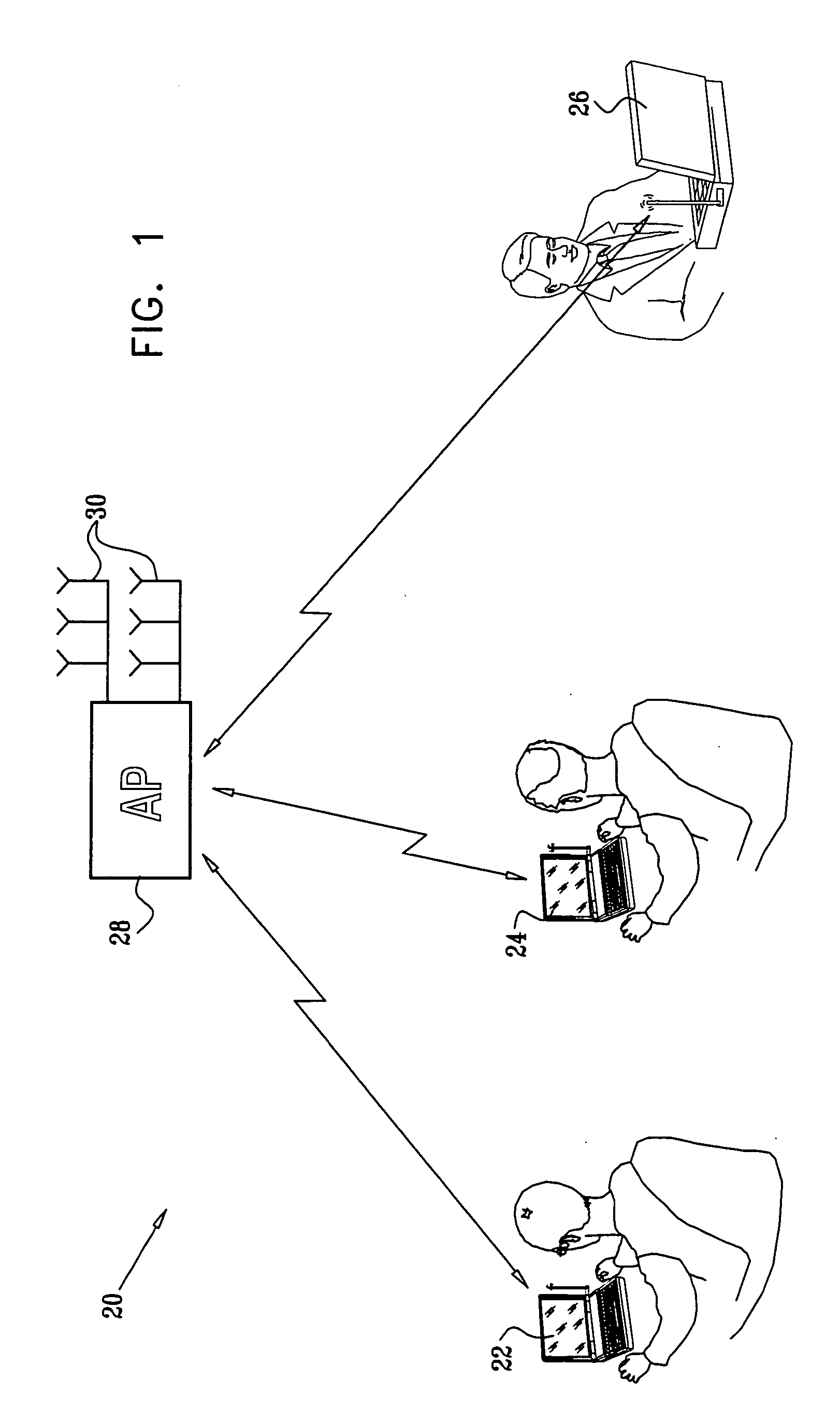

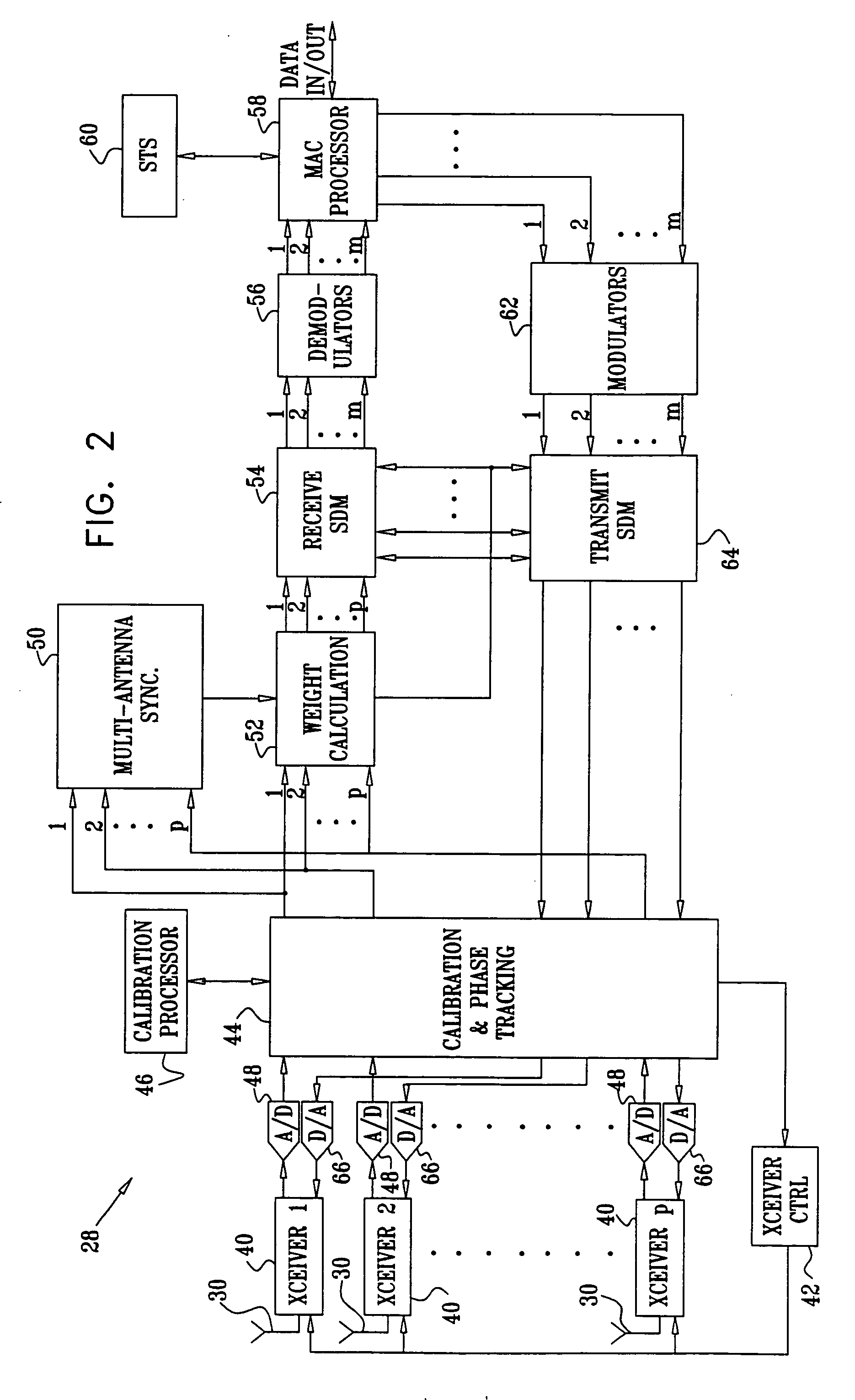

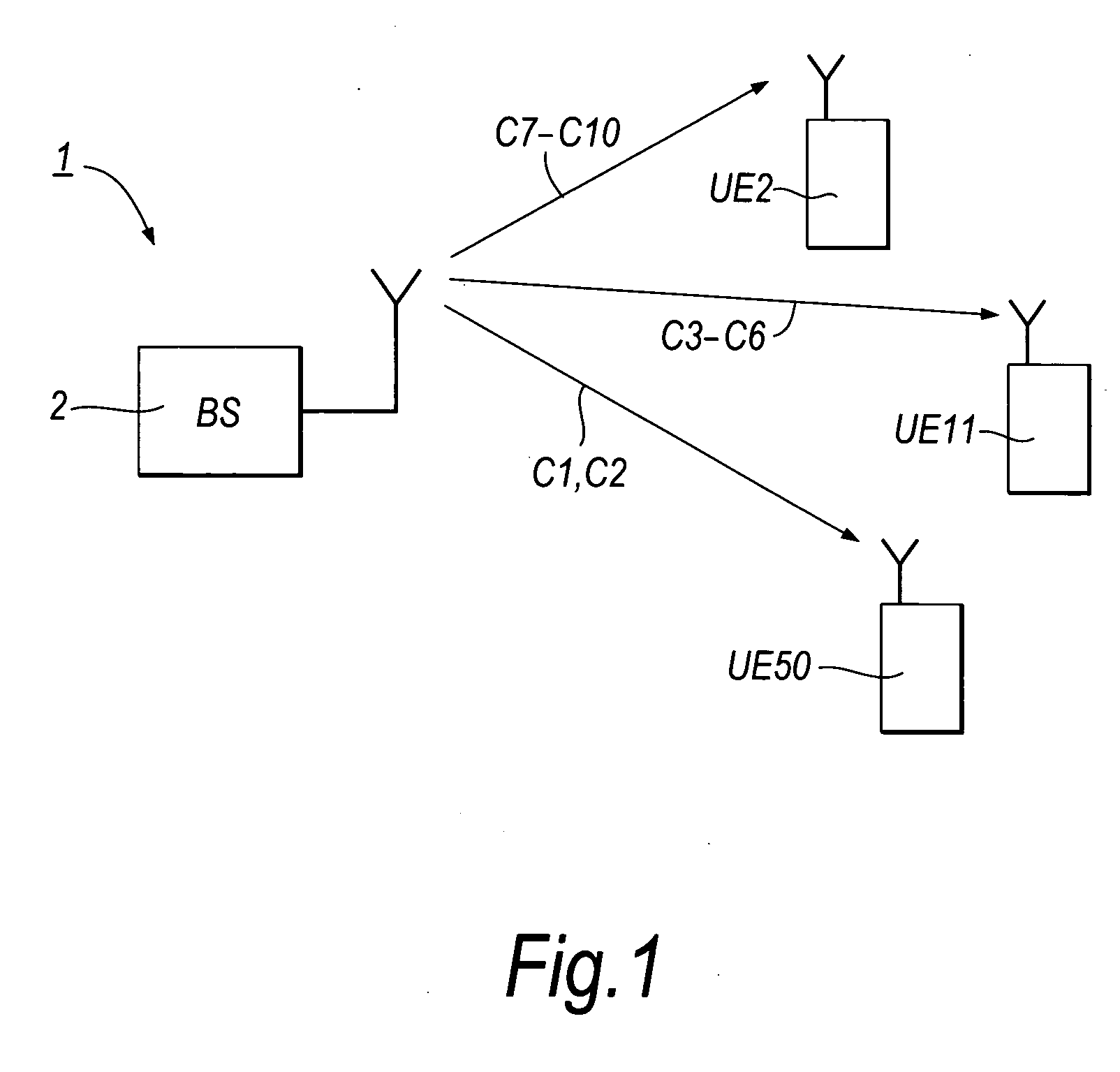

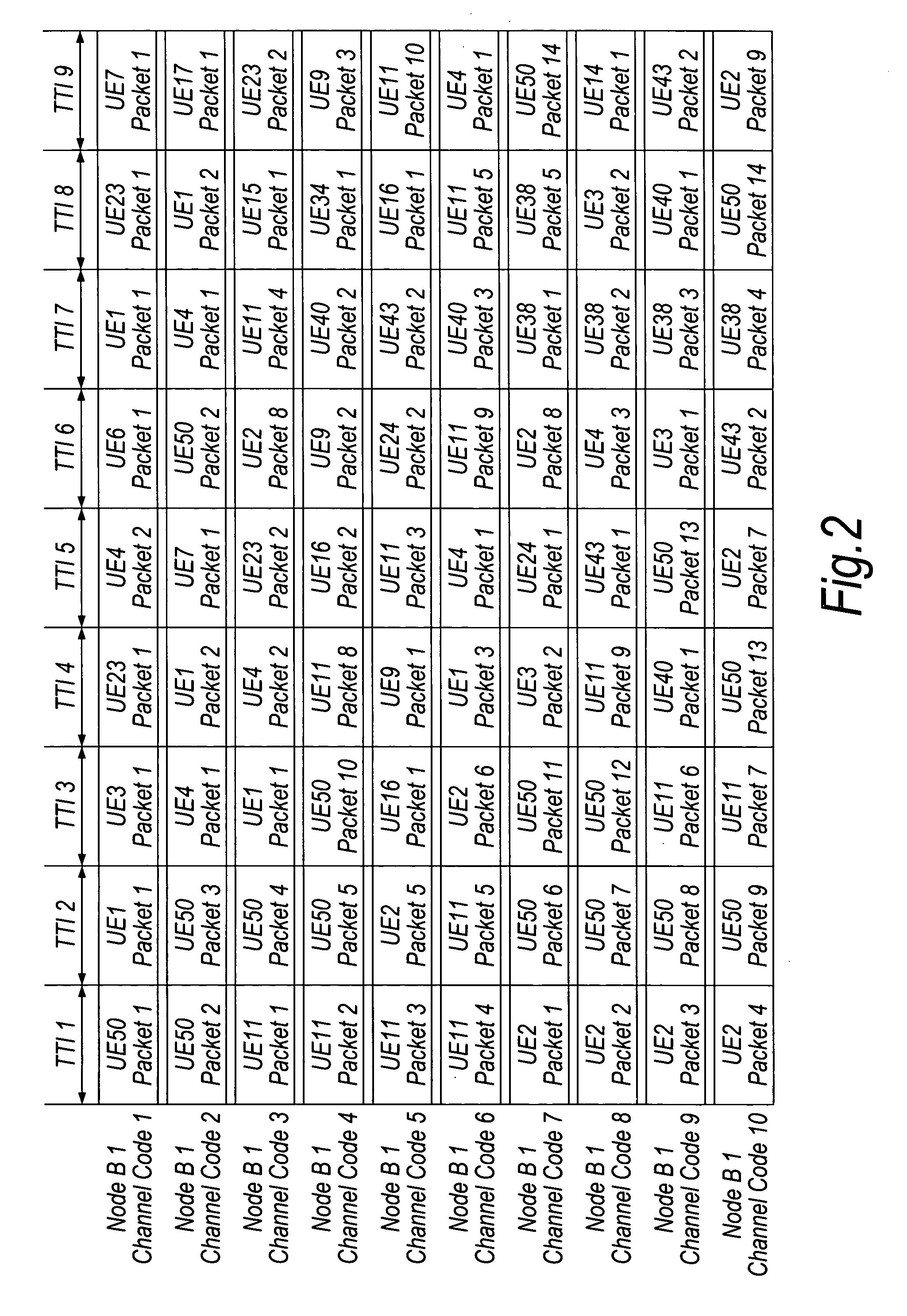

WLAN capacity enhancement using SDM

ActiveUS20050047384A1Increase capacityMaximize signal powerNetwork traffic/resource managementNetwork topologiesSignal responseTelecommunications

A method for communication over a wireless local area network (WLAN) includes receiving uplink signals from a plurality of stations in the WLAN. Responsively to the uplink signals, a set of the stations is selected for inclusion in a spatial multiplexing group. Downlink signals are transmitted simultaneously to the stations in the set using spatial division multiplexing (SDM).

Owner:WAVION

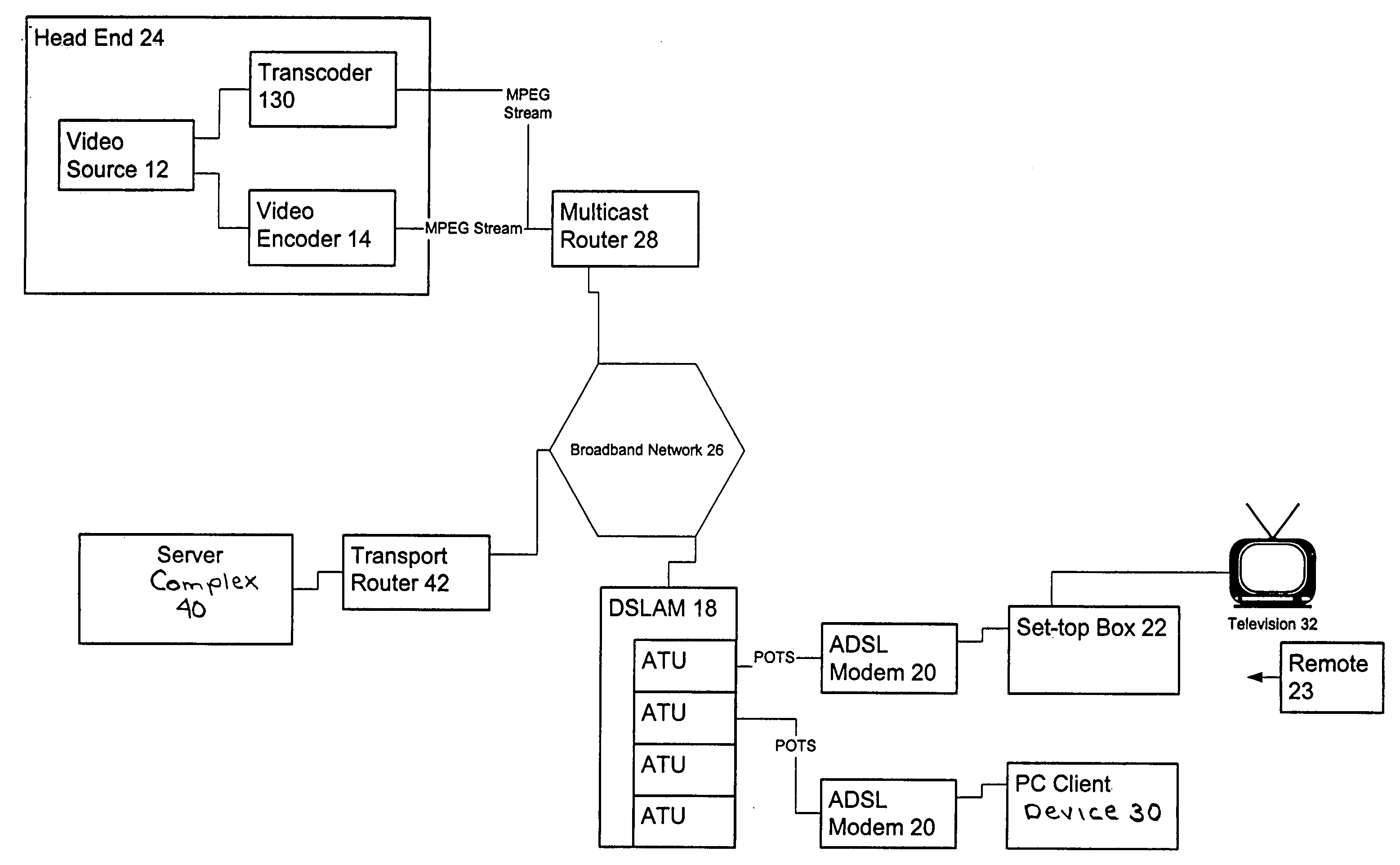

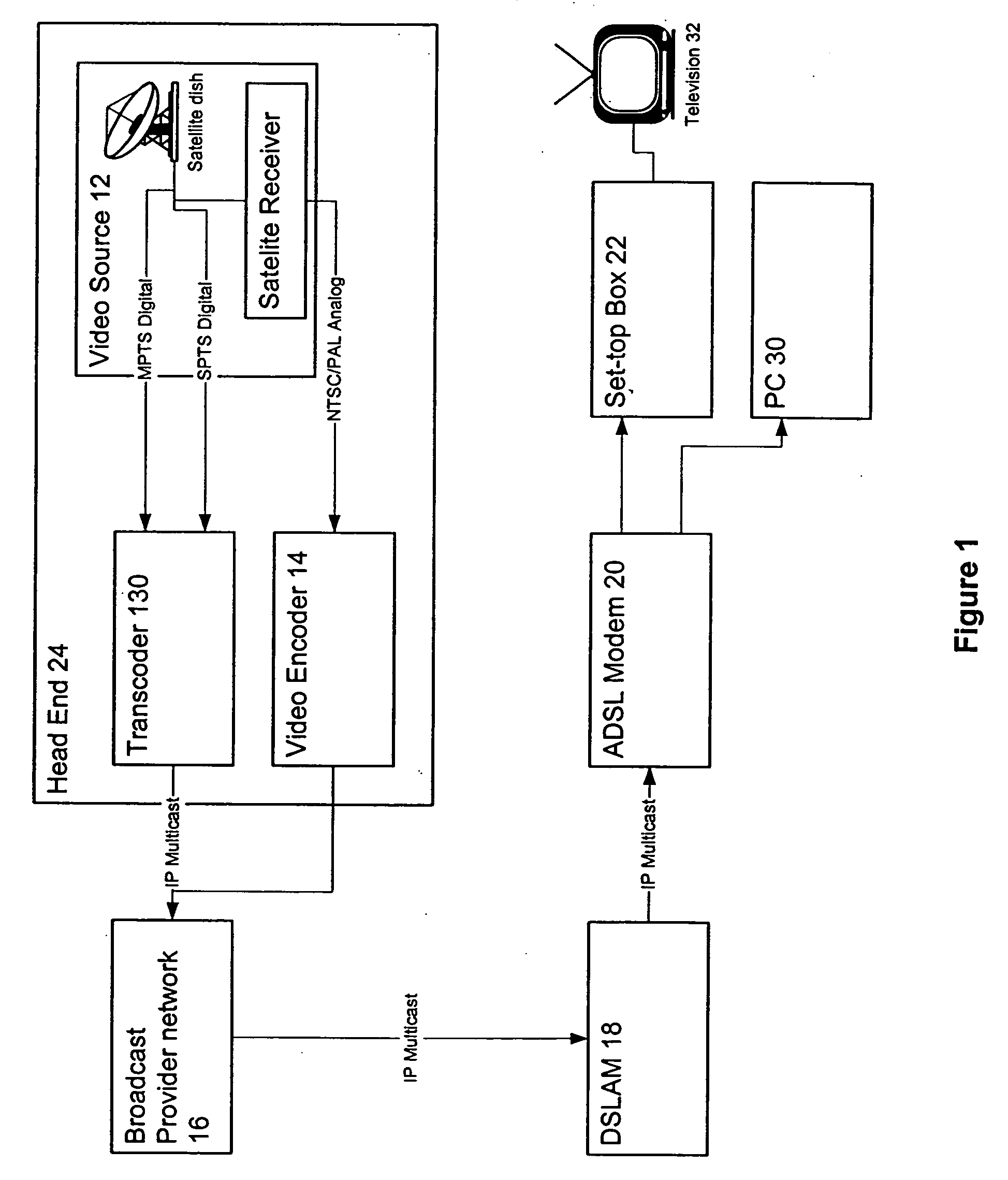

Digital interactive delivery system for TV/multimedia/internet

InactiveUS20050028206A1Television system detailsAnalogue secracy/subscription systemsSignal onIP multicast

Owner:IMAGICTV

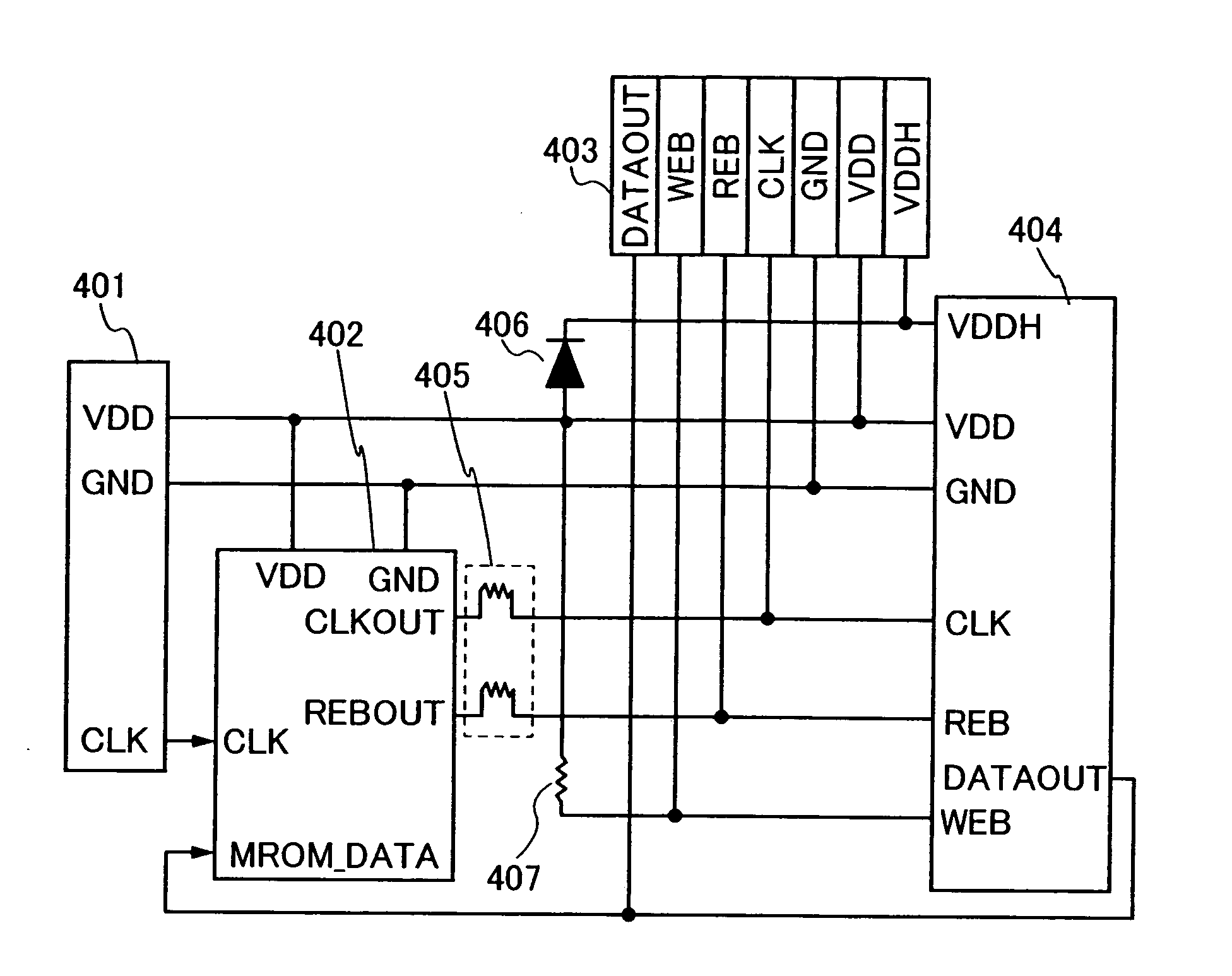

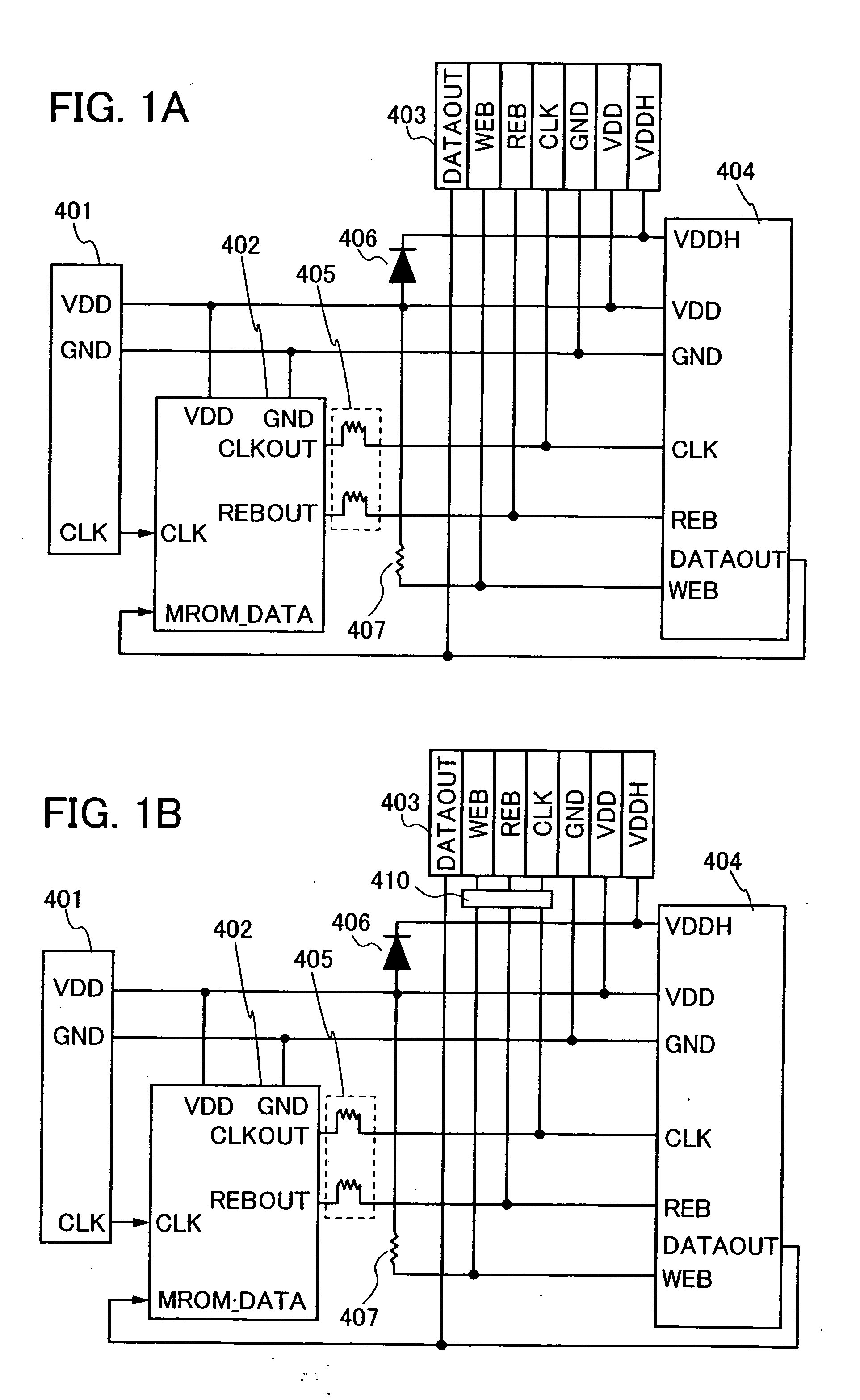

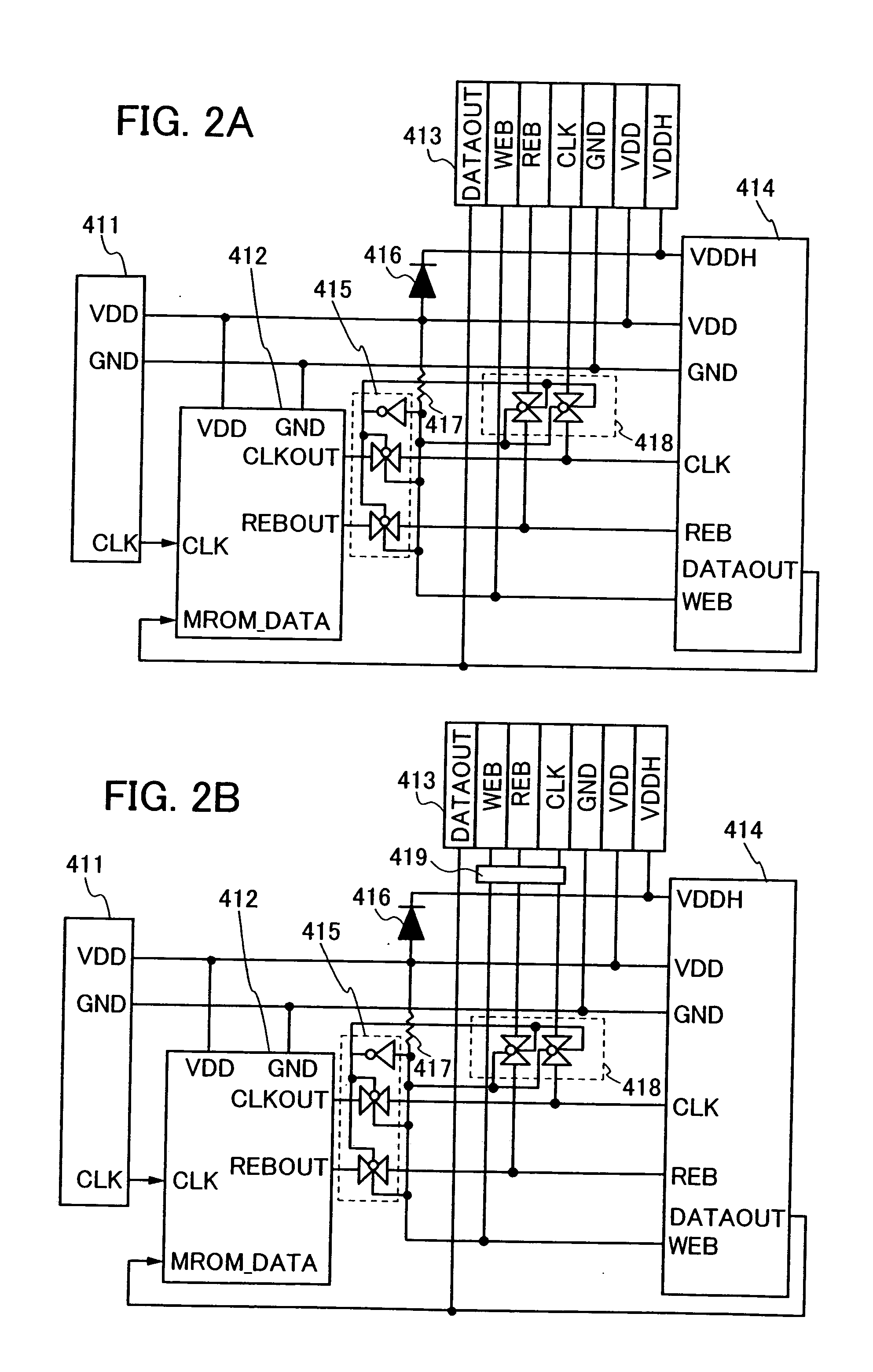

Semiconductor device and operating method thereof

InactiveUS20070123189A1Lower unit costReduce memory areaNanoinformaticsSolid-state devicesOrganic memoryBit line

In an organic memory which is included in a radio chip formed from a thin film, data are written to the organic memory by a signal inputted with a wired connection, and the data is read with a signal by radio transmission. A bit line and a word line which form the organic memory are each selected by a signal which specifies an address generated based on the signal inputted with a wired connection. A voltage is applied to a selected memory element. Thus writing is performed. Reading is performed by a clock signal or the like which are generated from a radio signal.

Owner:SEMICON ENERGY LAB CO LTD

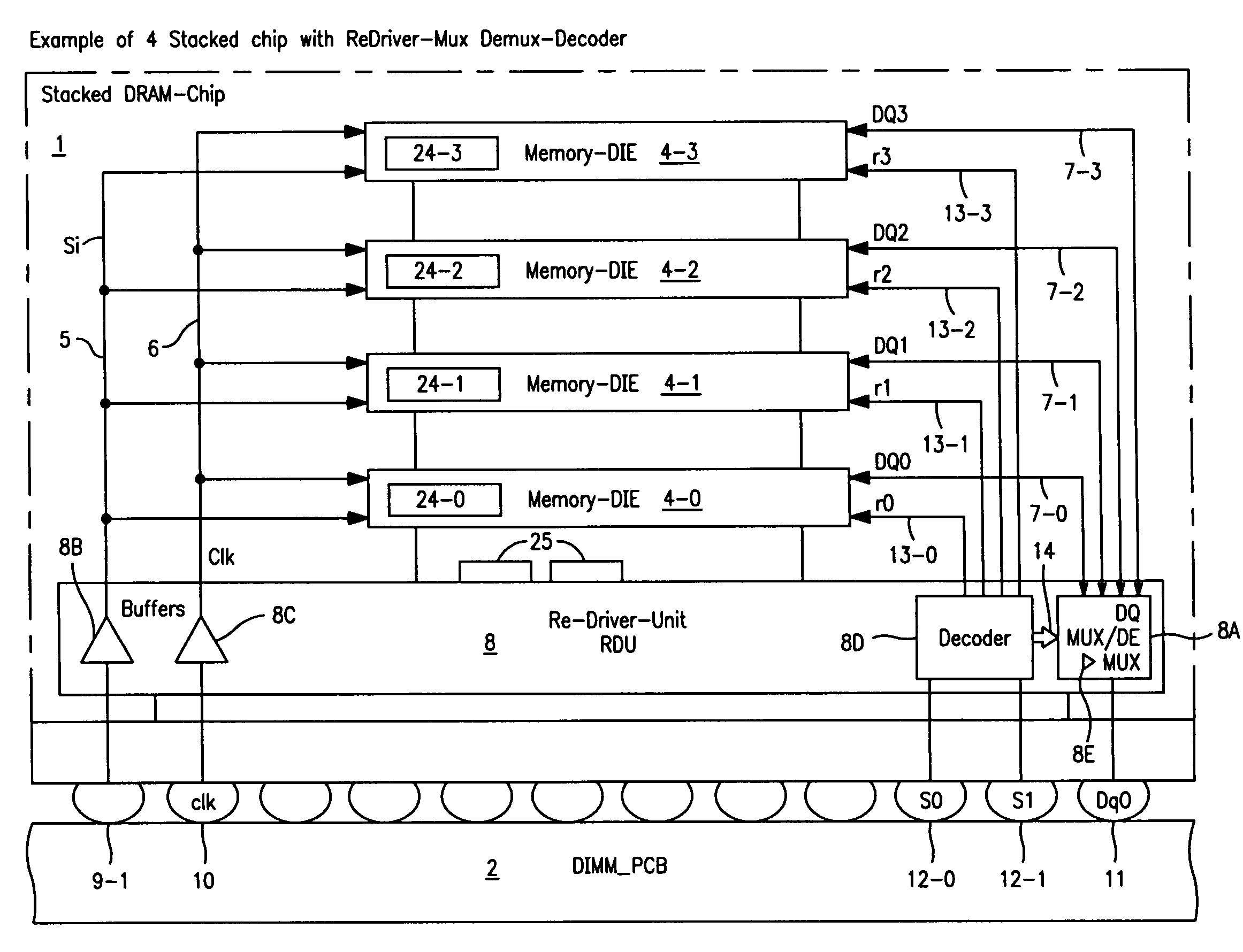

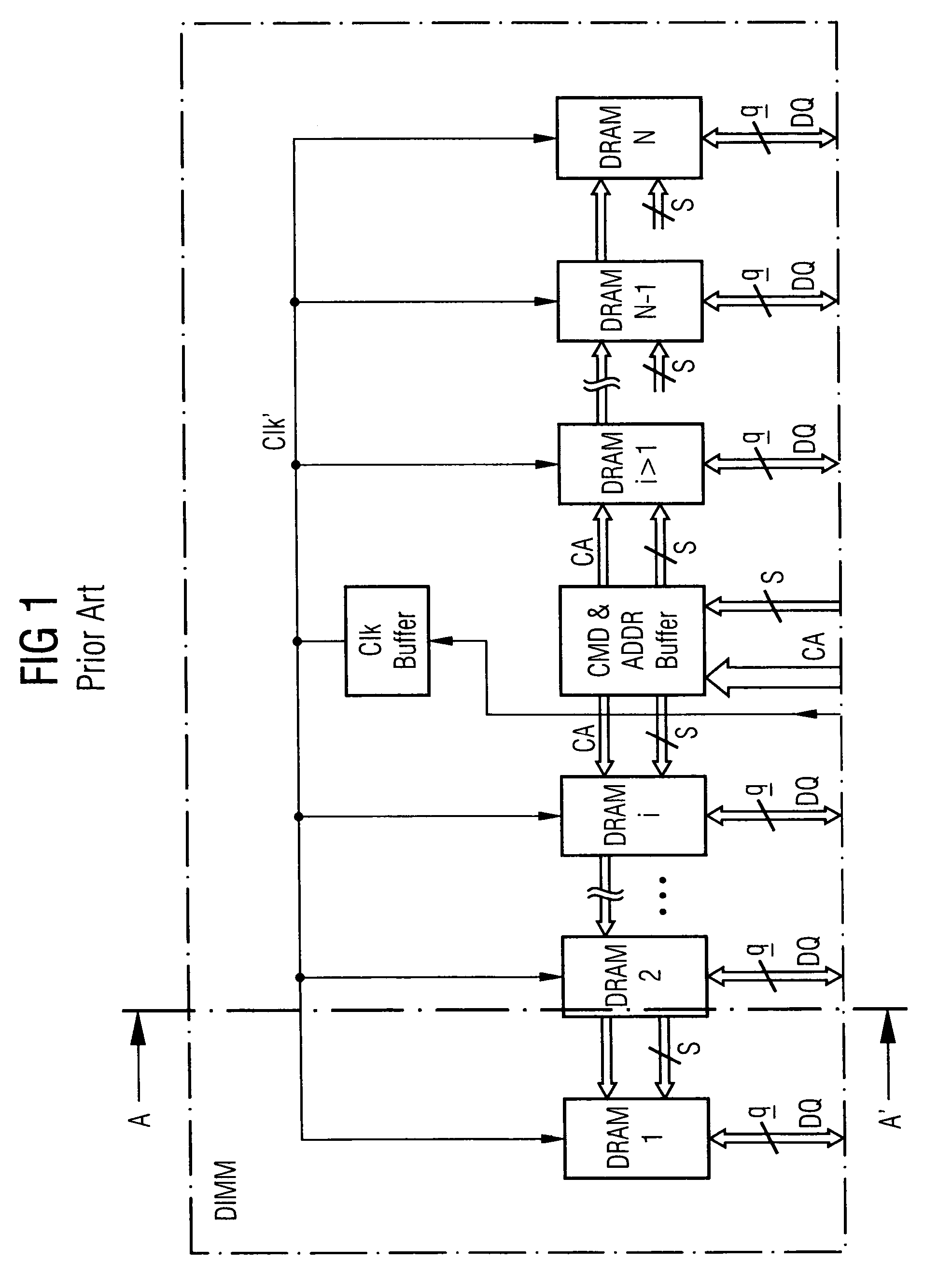

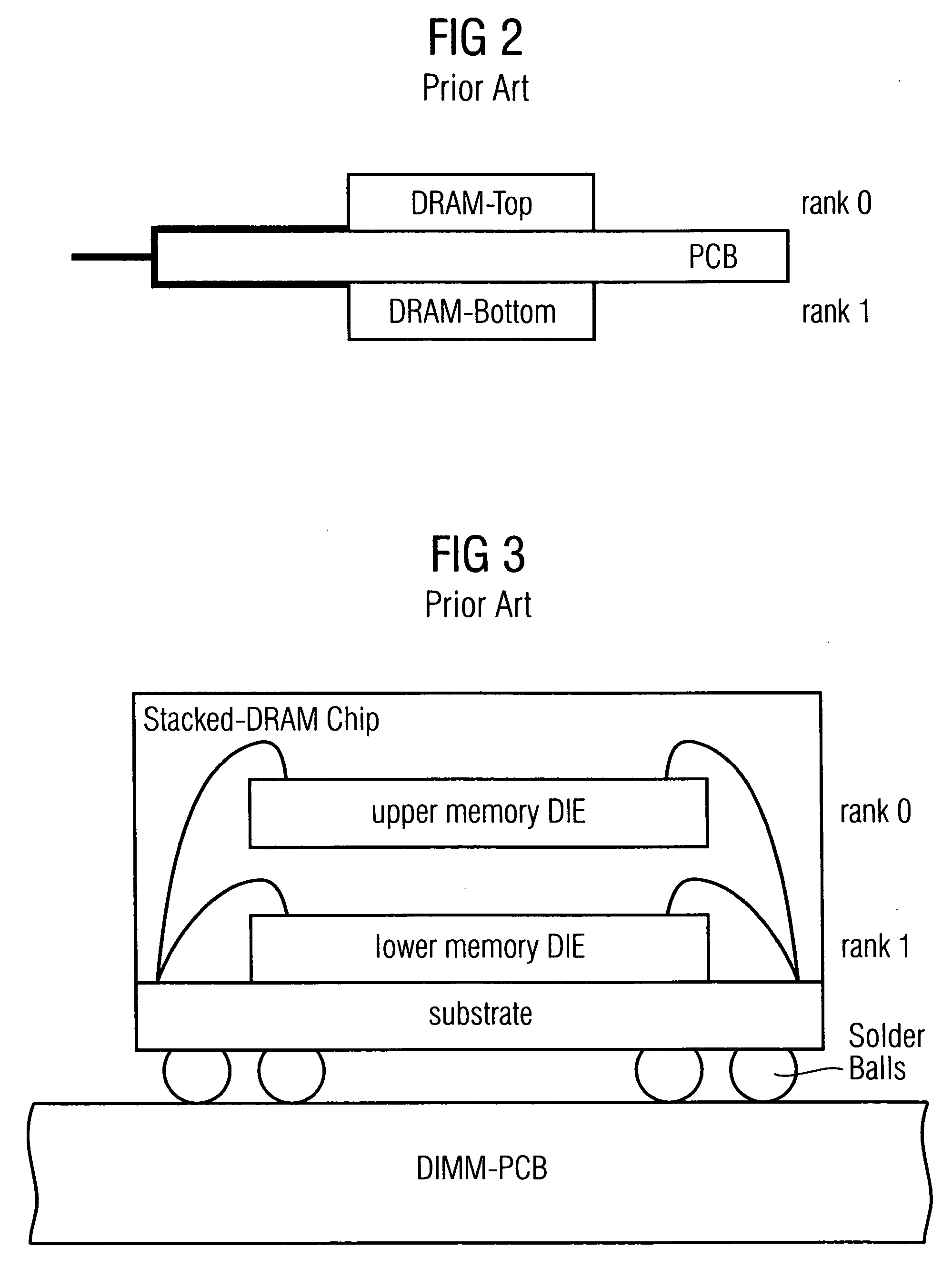

Stacked DRAM memory chip for a dual inline memory module (DIMM)

ActiveUS7200021B2Increase the number ofSmall sizeSemiconductor/solid-state device detailsNanoinformaticsInternal memoryMemory chip

A stacked DRAM memory chip for a Dual In Line Memory Module (DIMM) is disclosed. According to one aspect, the DRAM memory chip comprises at least four stacked DRAM memory dies. Further, the memory dies are each selectable by a corresponding internal memory rank signal. Each memory die comprises an array of memory cells. A common internal address bus is provided for addressing the memory cells and is connected to all stacked DRAM memory dies. Internal data buses are provided for writing data into the memory cells and reading data out of the memory cells of the DRAM memory dies. An integrated redriving unit comprises buffers for all internal address lines provided for driving external address signals applied to address pads of the DRAM memory chip. A multiplexer / demultiplexer switches the internal data lines of the selected DRAM memory die. A memory rank decoder selects a corresponding memory die.

Owner:POLARIS INNOVATIONS LTD

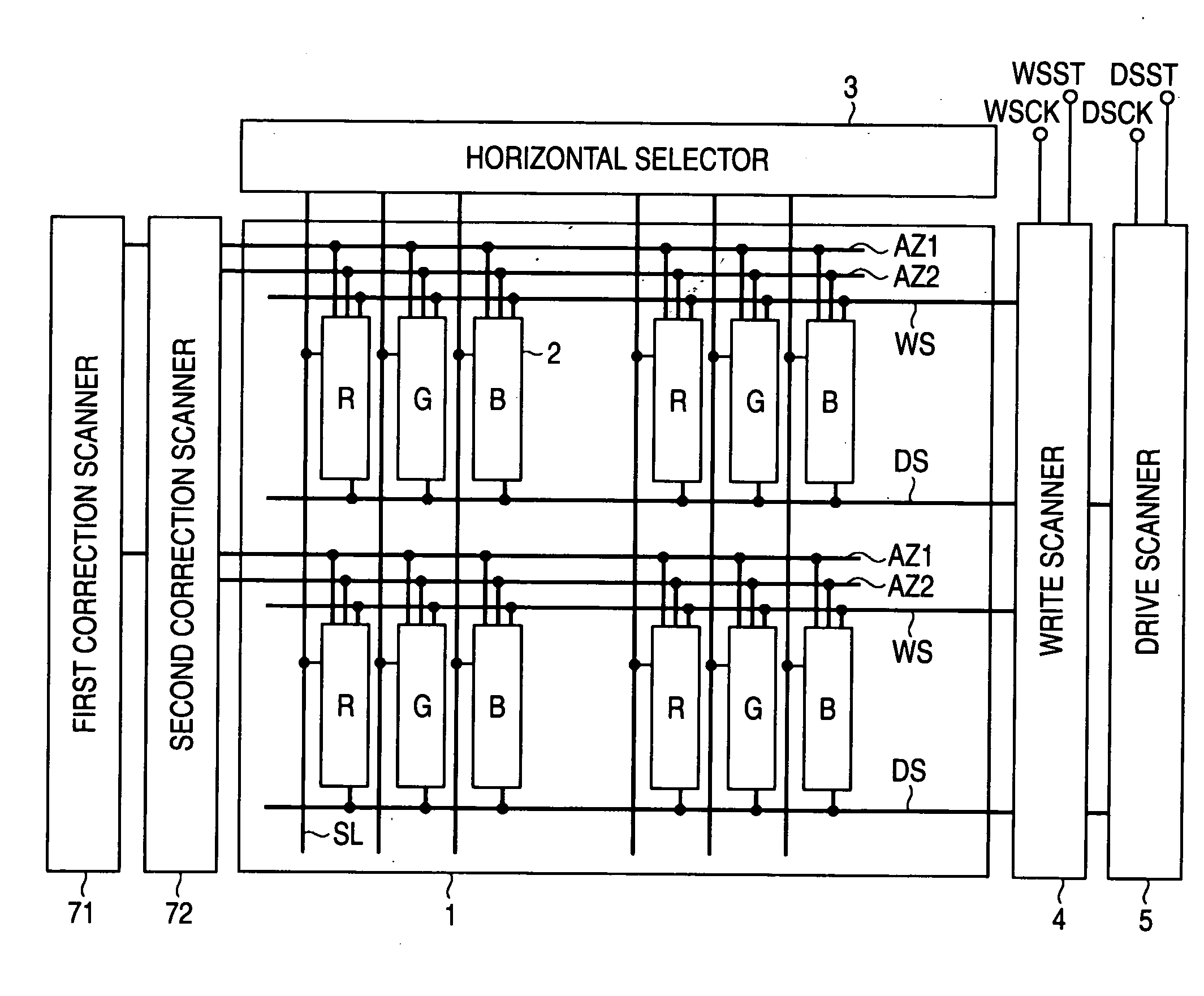

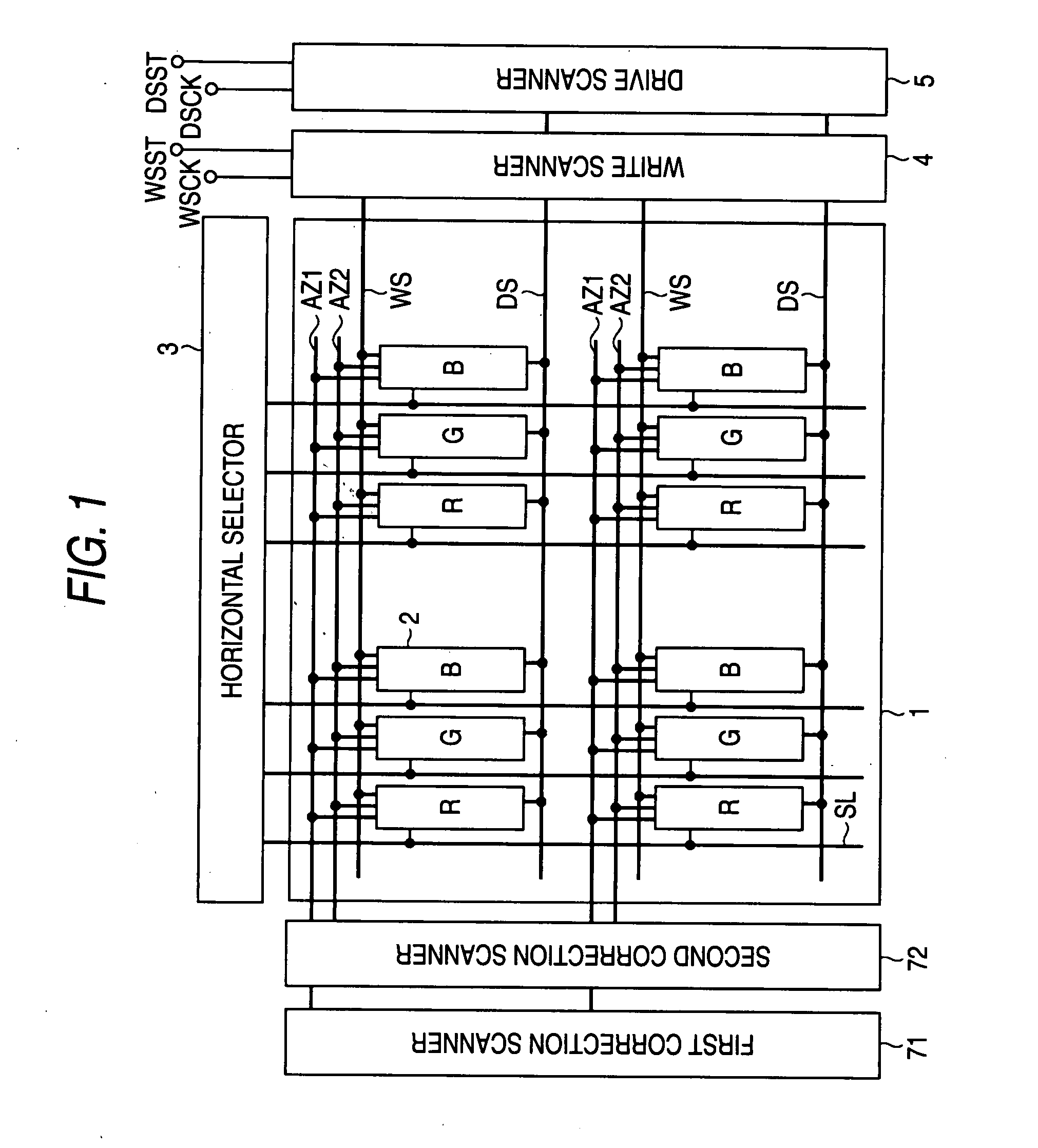

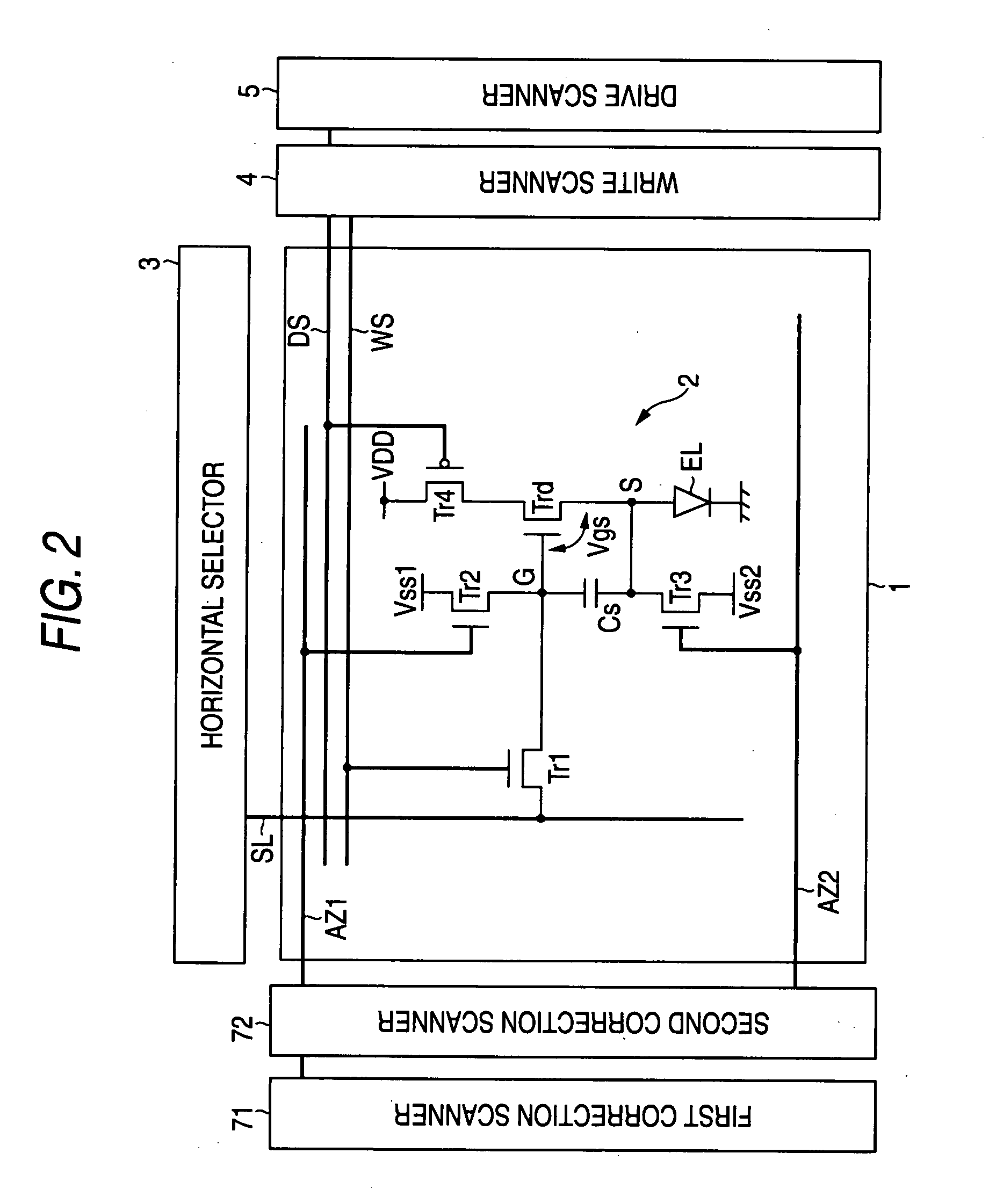

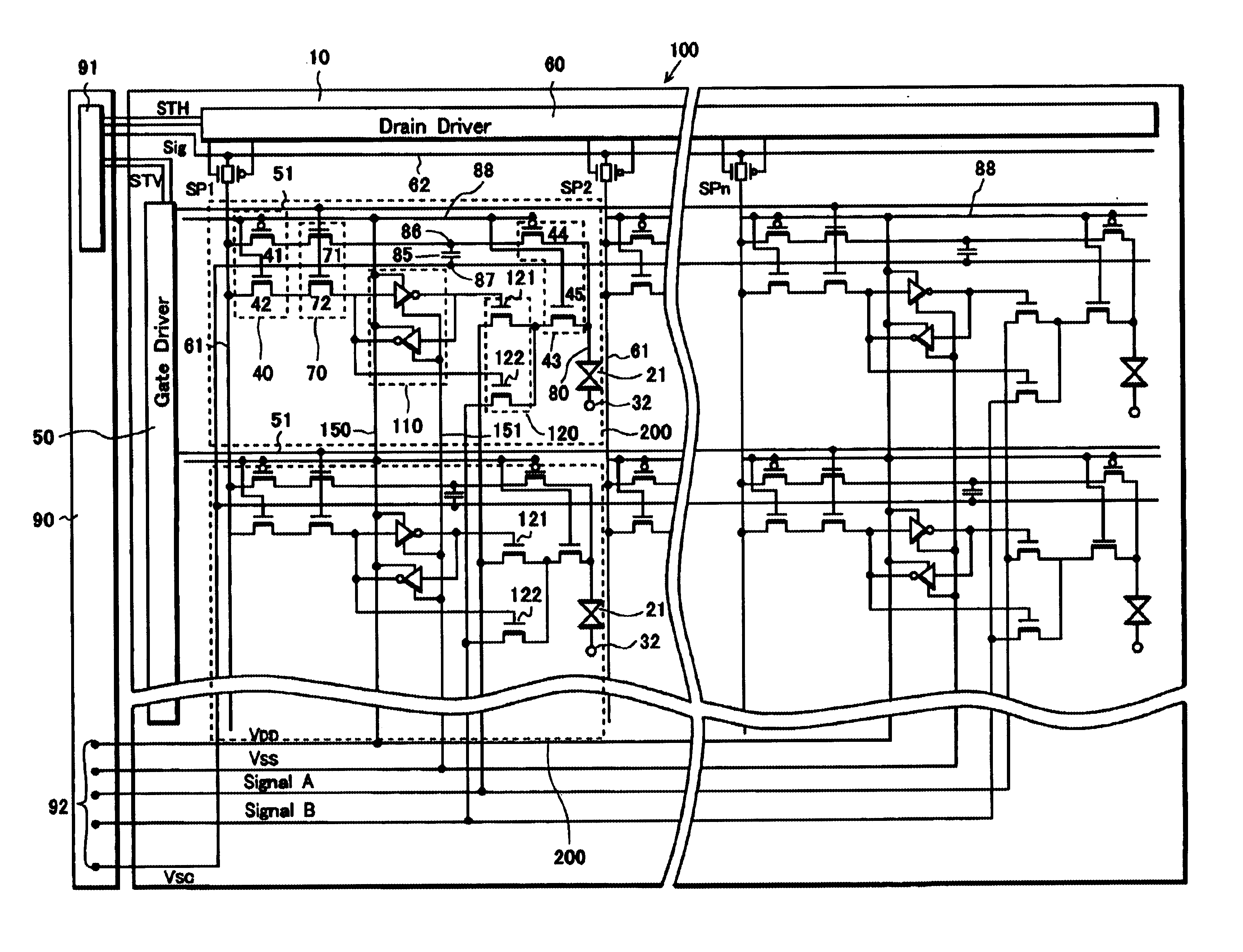

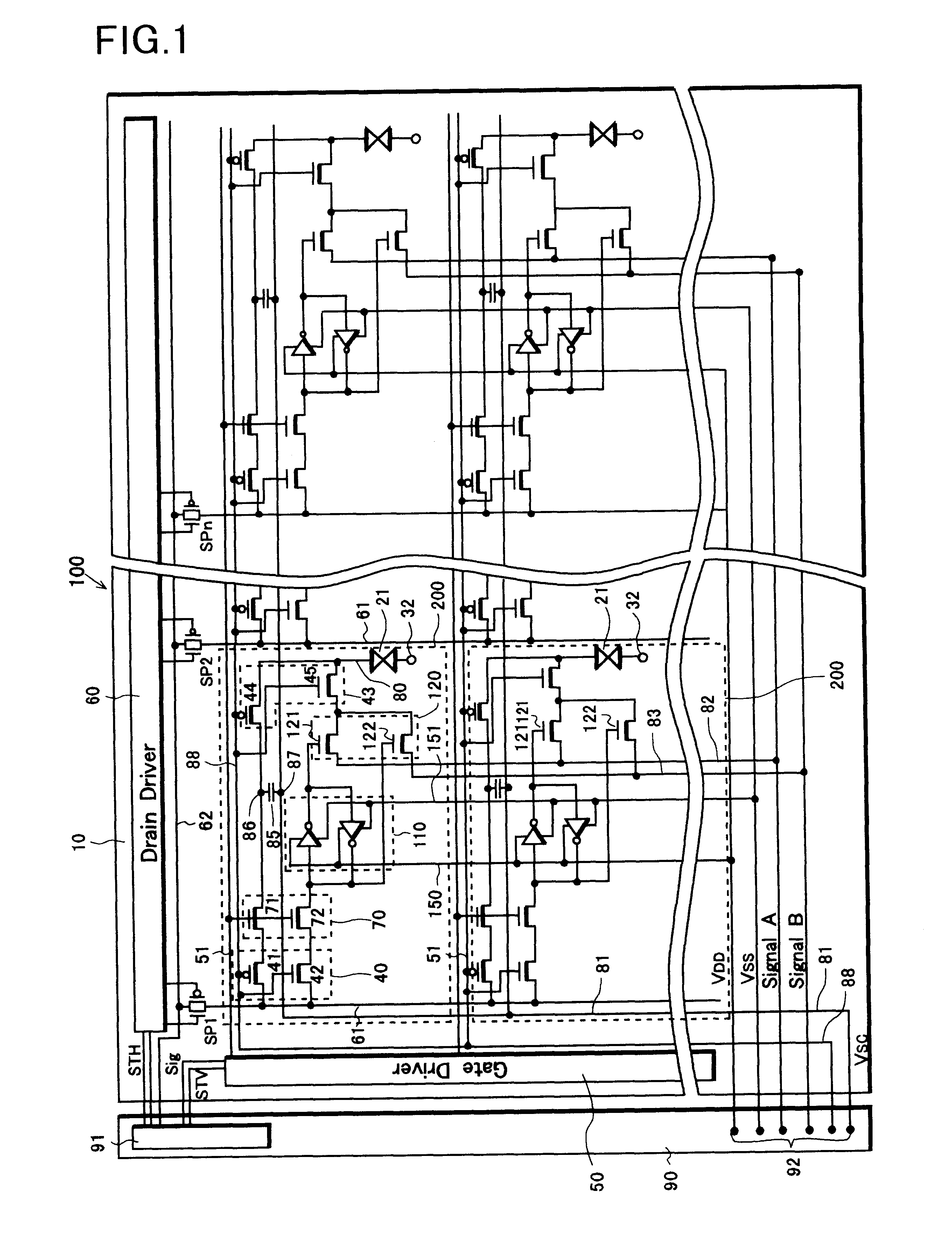

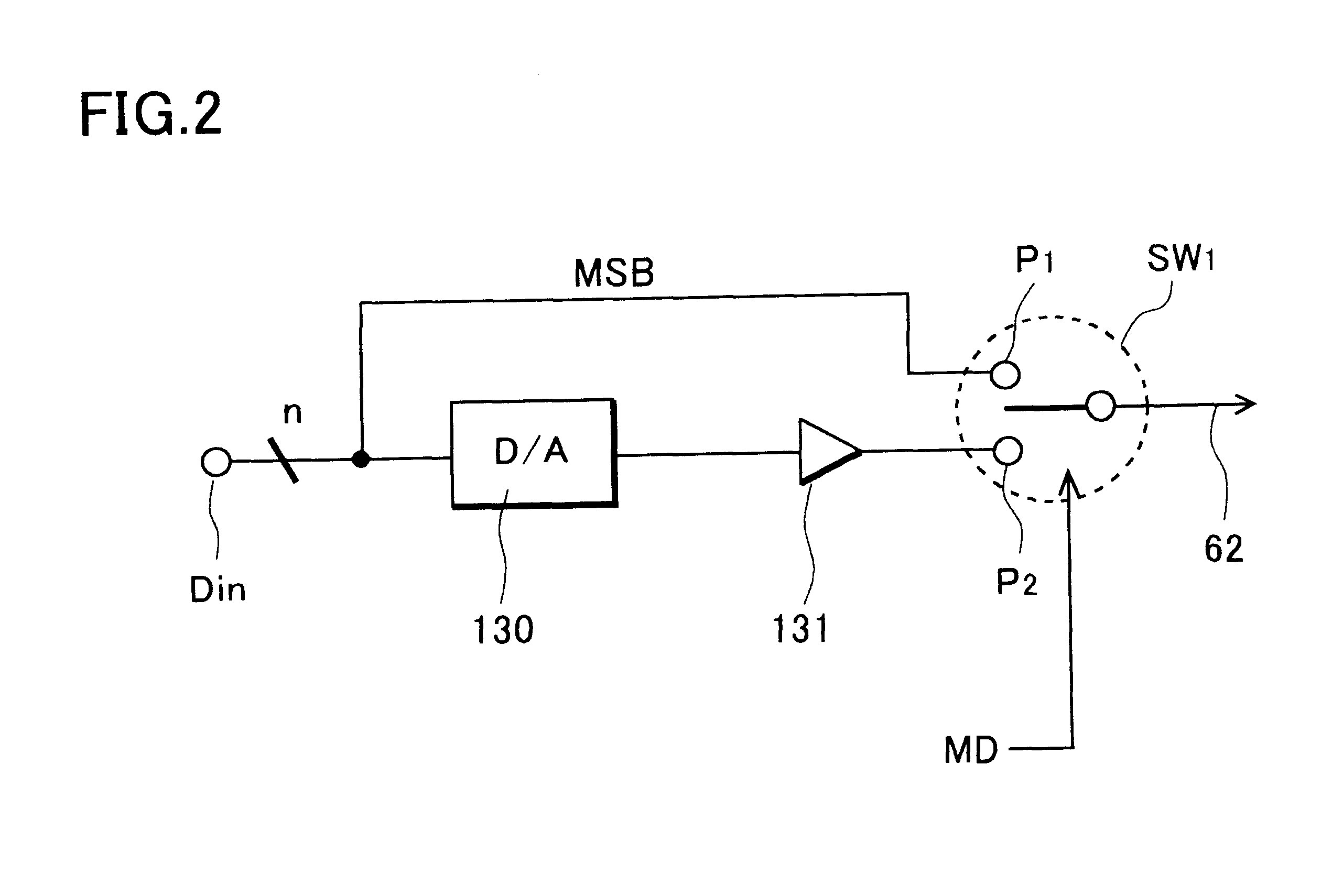

Display device and electronic equipment

ActiveUS20080042948A1Amount of signal becomes smallReduce semaphoreElectrical apparatusStatic indicating devicesScan lineControl signal

A display device is disclosed. The display device includes: a pixel array part; and a drive part that drives the pixel array part. The pixel array part includes row-wise first scan lines and second scan lines, column-wise signal lines, pixels arranged in a matrix form on parts where the lines intersect, and power supply lines and ground lines that supply power to the respective pixels. The drive part includes a first scanner that sequentially supplies first control signals to the respective first scan lines and line-sequentially scans the pixels in units of rows, a second scanner that sequentially supplies second control signals to the respective second scan lines according to the line-sequential scan, and a signal selector that supplies video signals to the column-wise signal lines according to the line-sequential scan.

Owner:JOLED INC

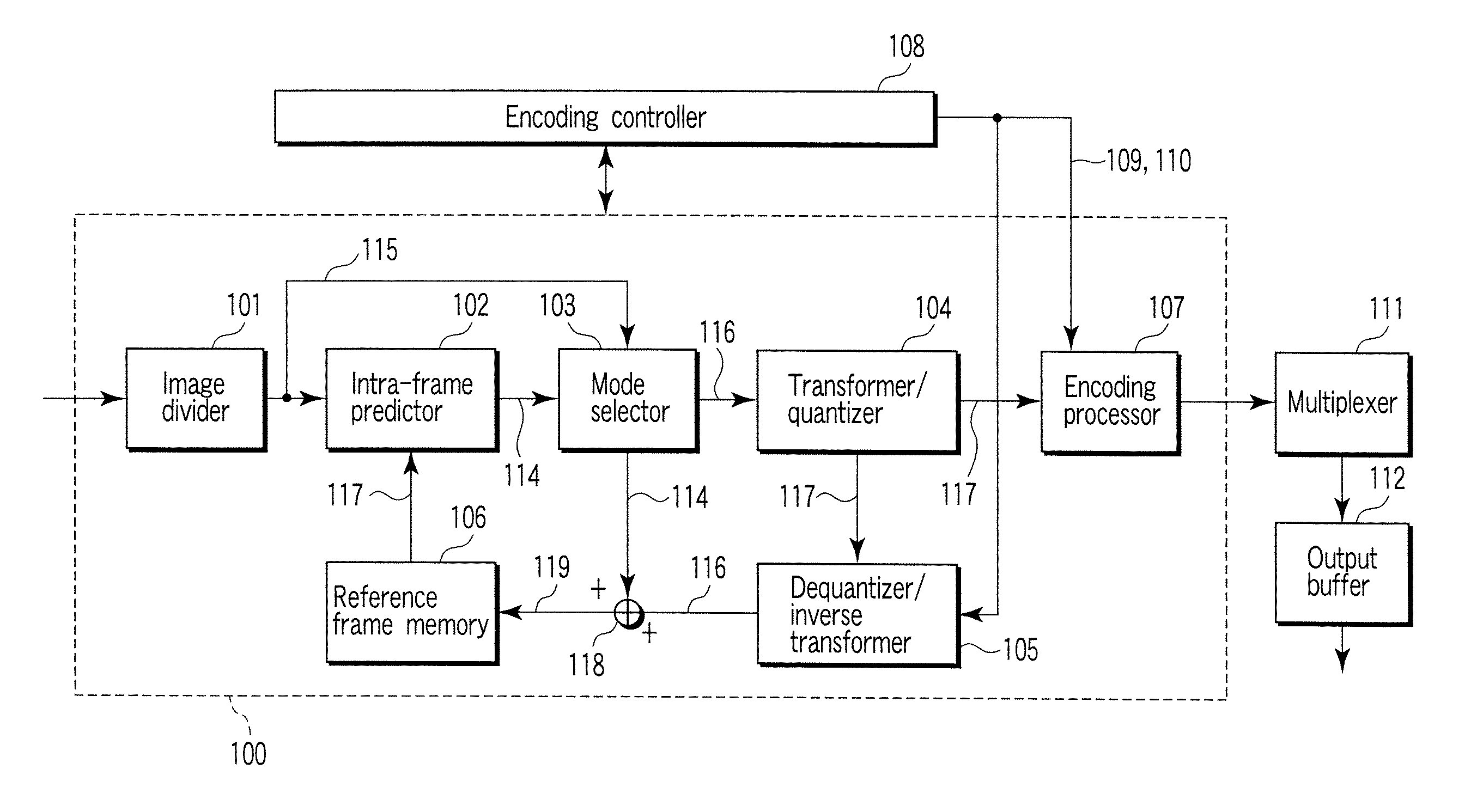

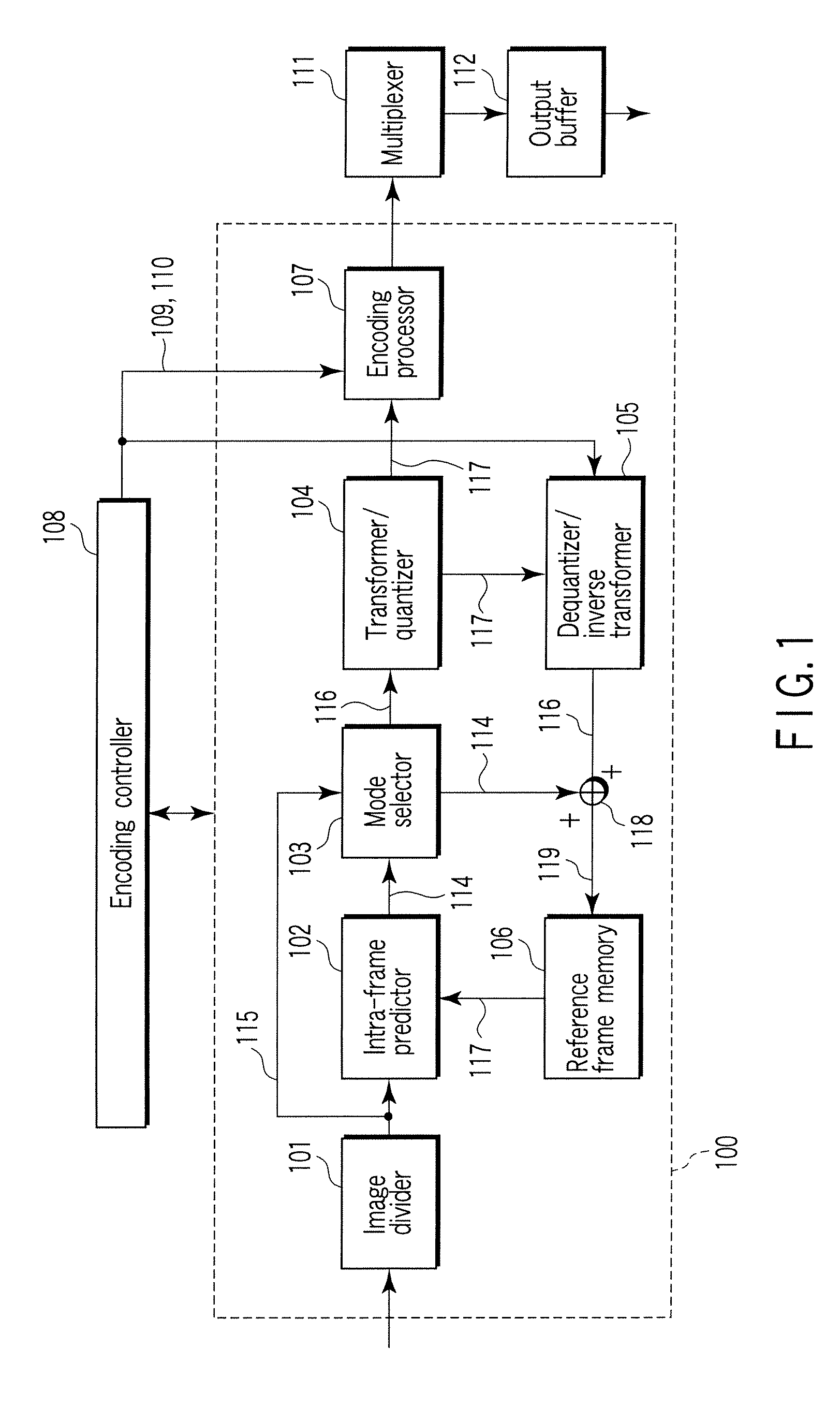

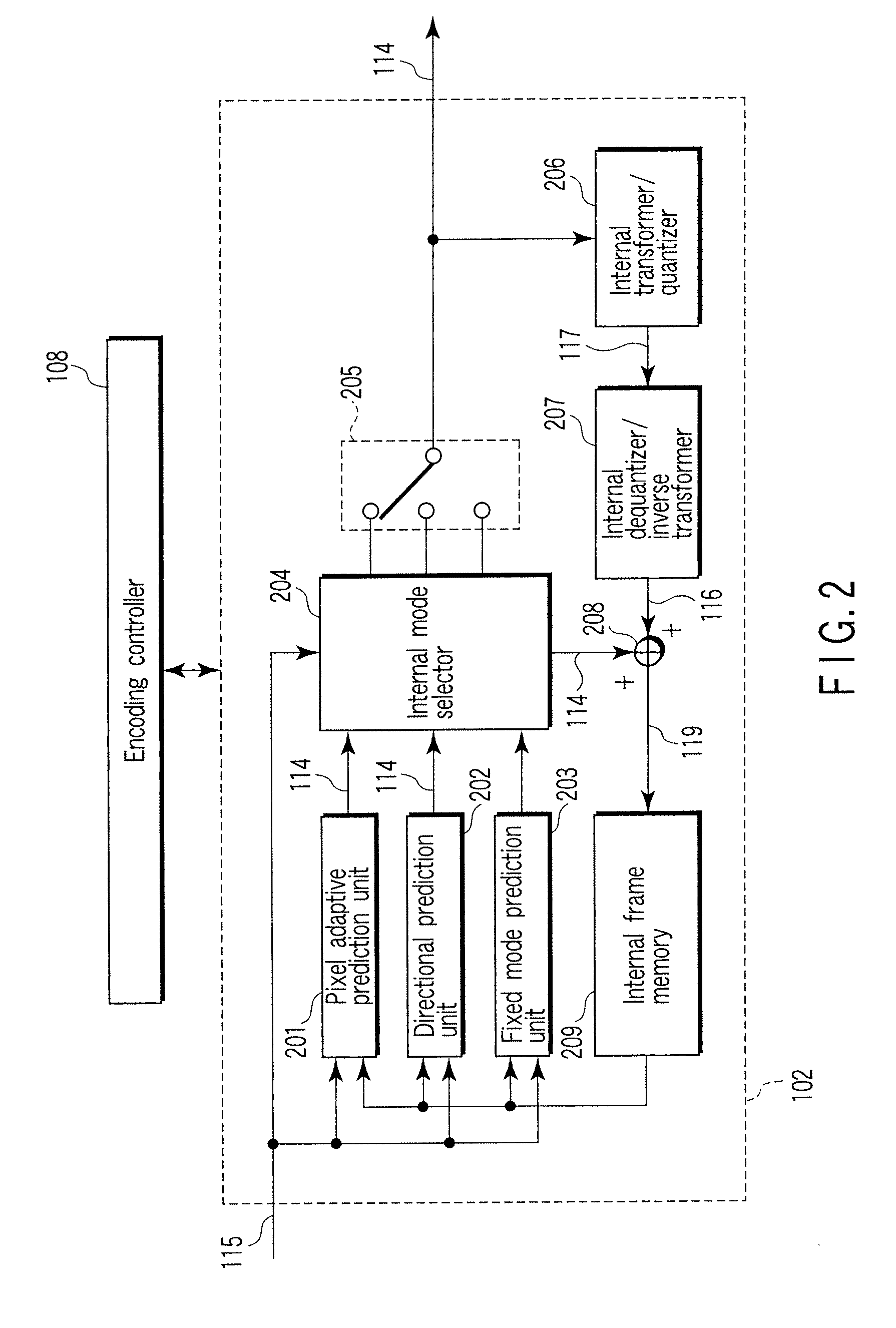

Image encoding/image decoding method and image encoding/image decoding apparatus

InactiveUS20070121731A1Color television with pulse code modulationColor television with bandwidth reductionAlgorithmImage signal

An image coding method includes dividing an input picture into a plurality of pixel block signals, performing intra prediction for extrapolating or interpolating a prediction pixel using reference pixels changed in number according to a distance between the prediction pixel and a reference pixel in plural prediction modes each representing a prediction direction, generating a predictive image signal by extrapolating or interpolating the prediction pixel, calculating a prediction error signal from the pixel block signal and the predictive image signal, selecting one prediction mode of the plural prediction modes using the prediction error signal, and performing entropy-coding using the prediction error signal based on the selected prediction mode.

Owner:KK TOSHIBA

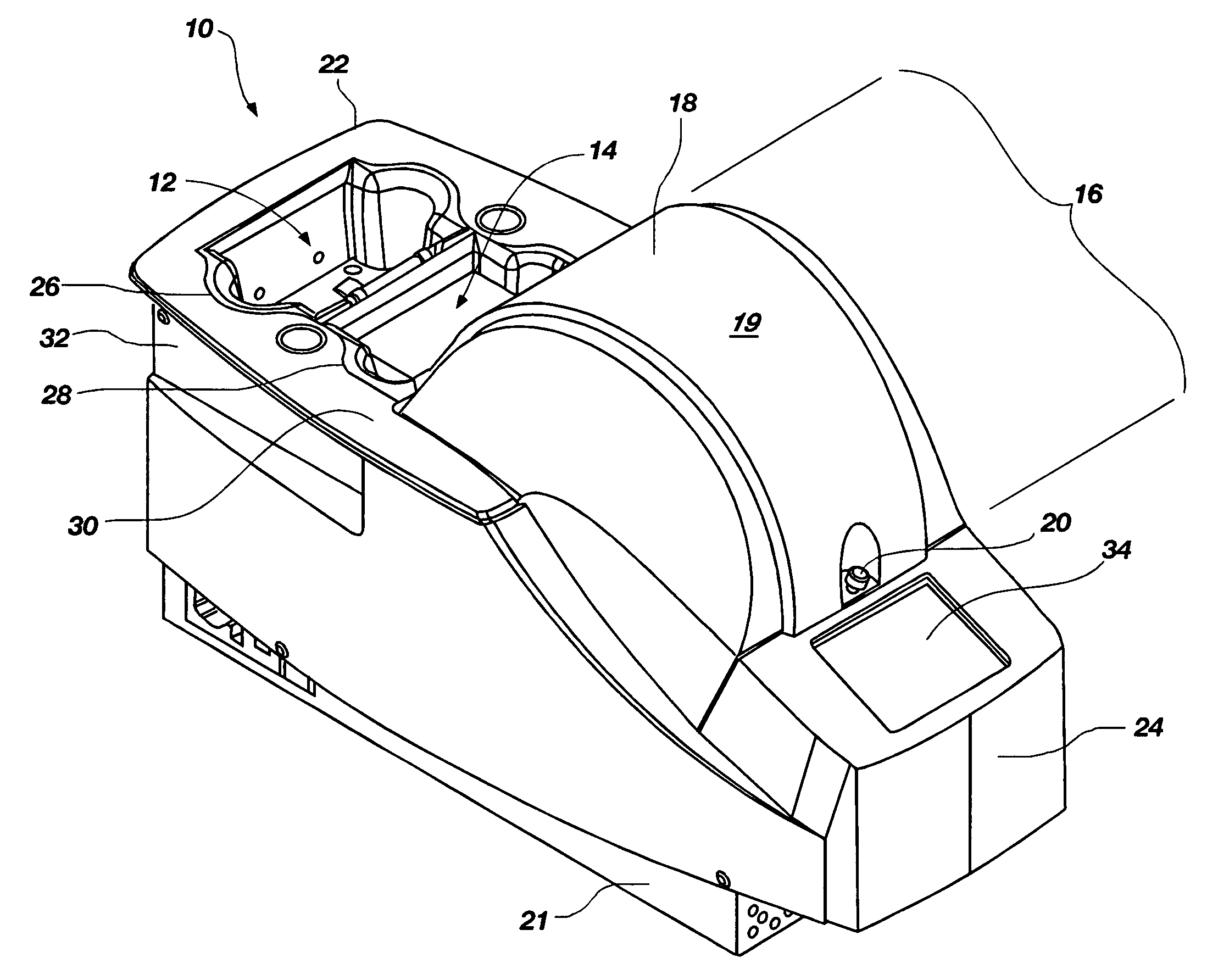

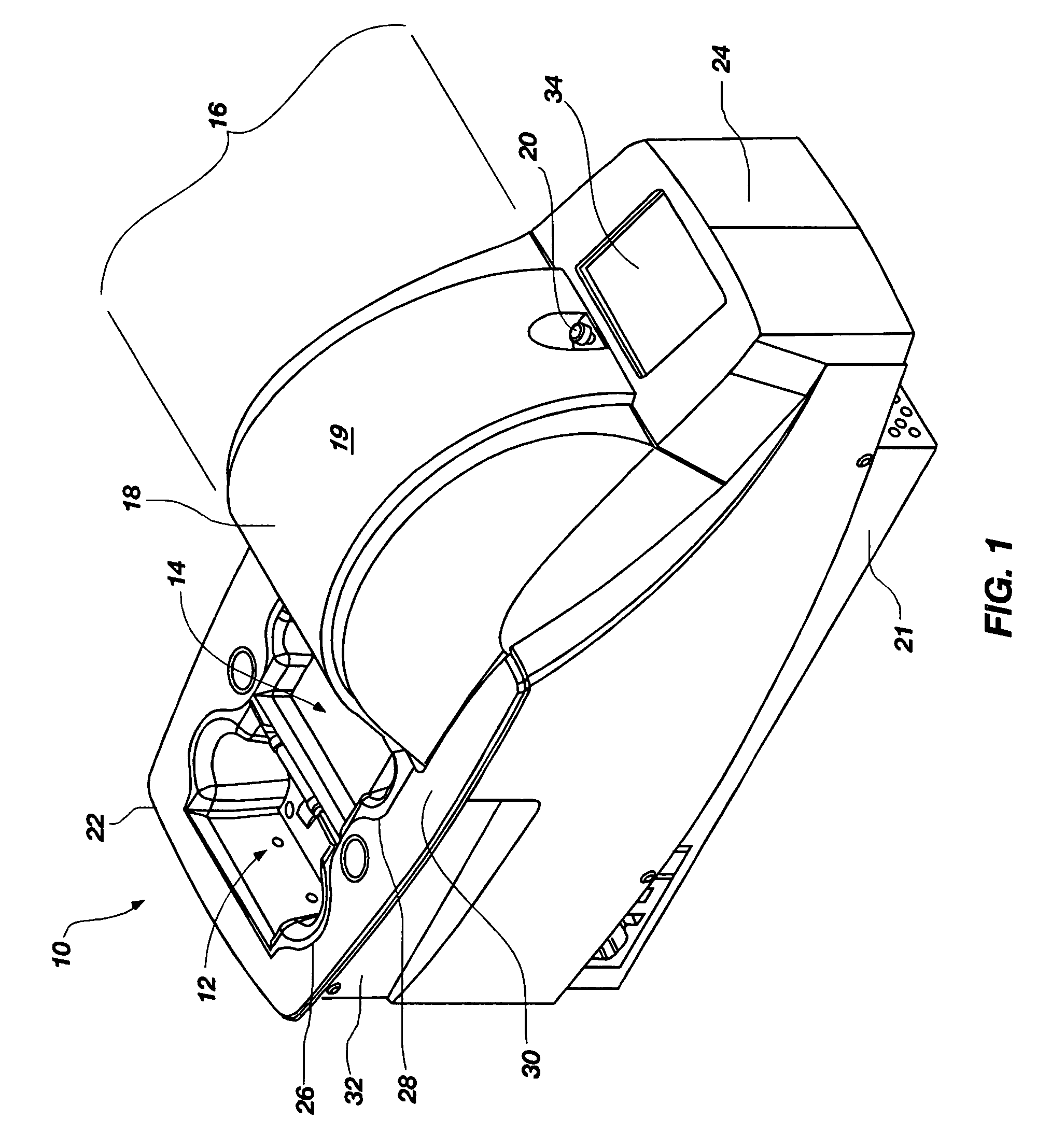

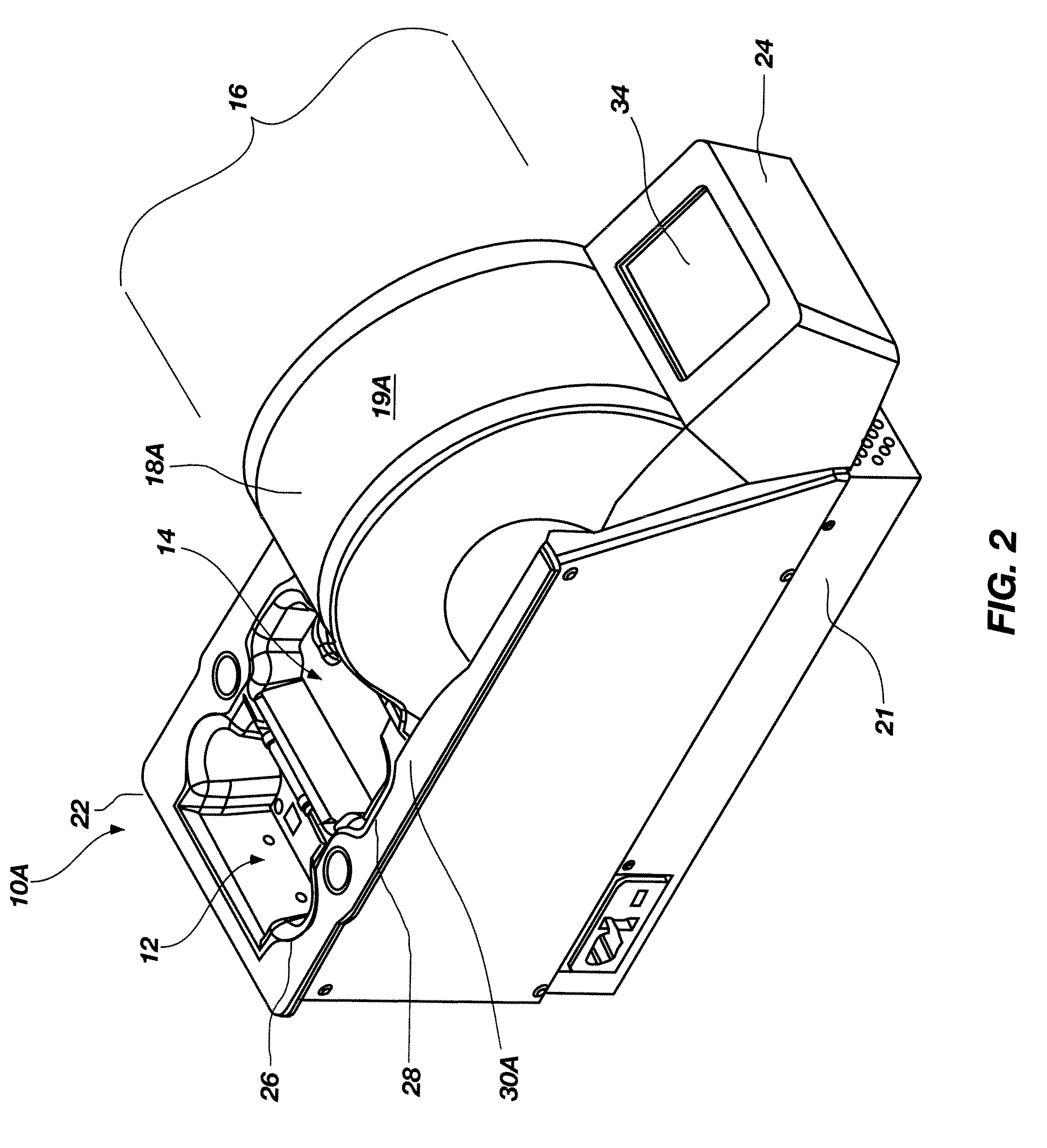

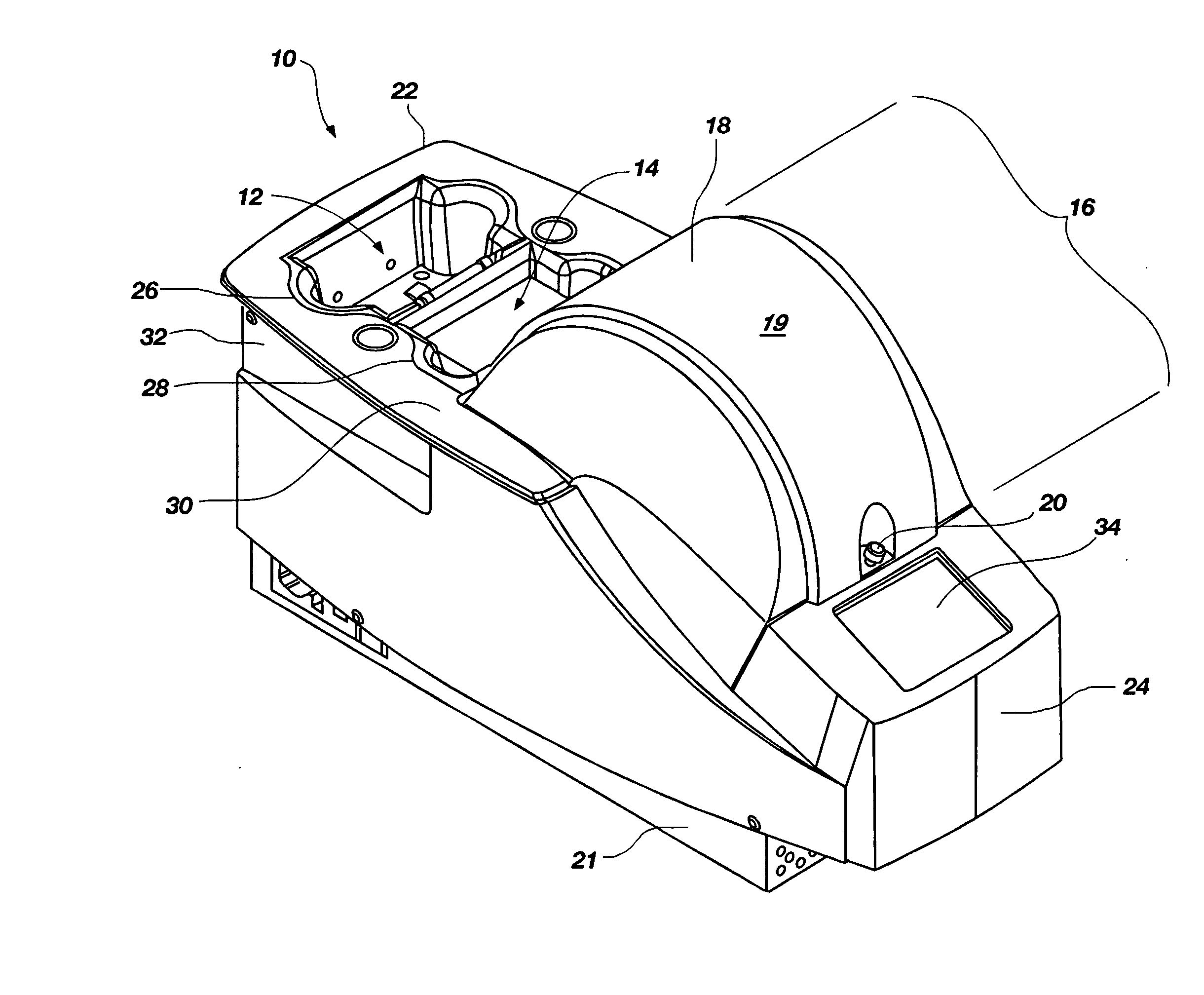

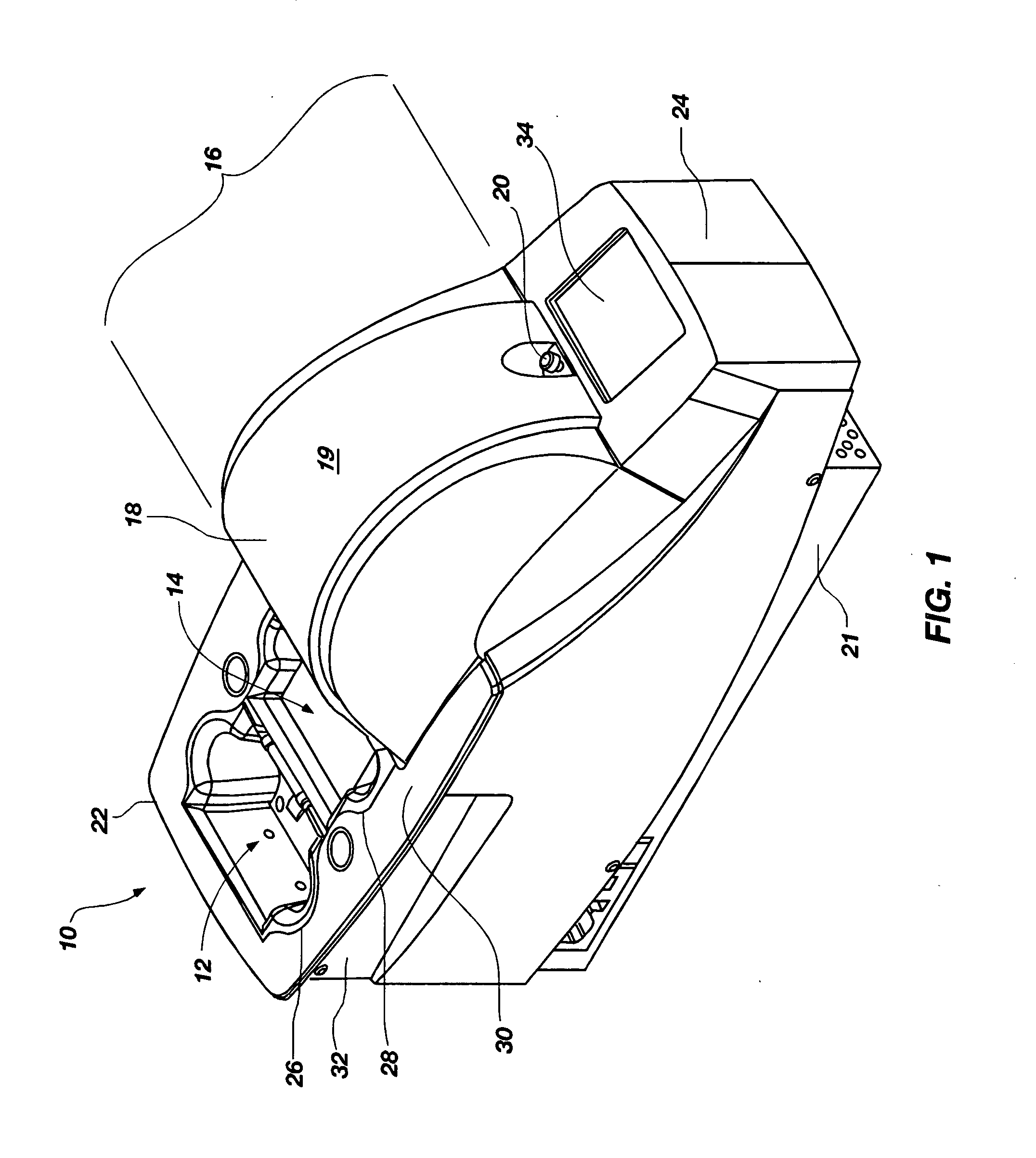

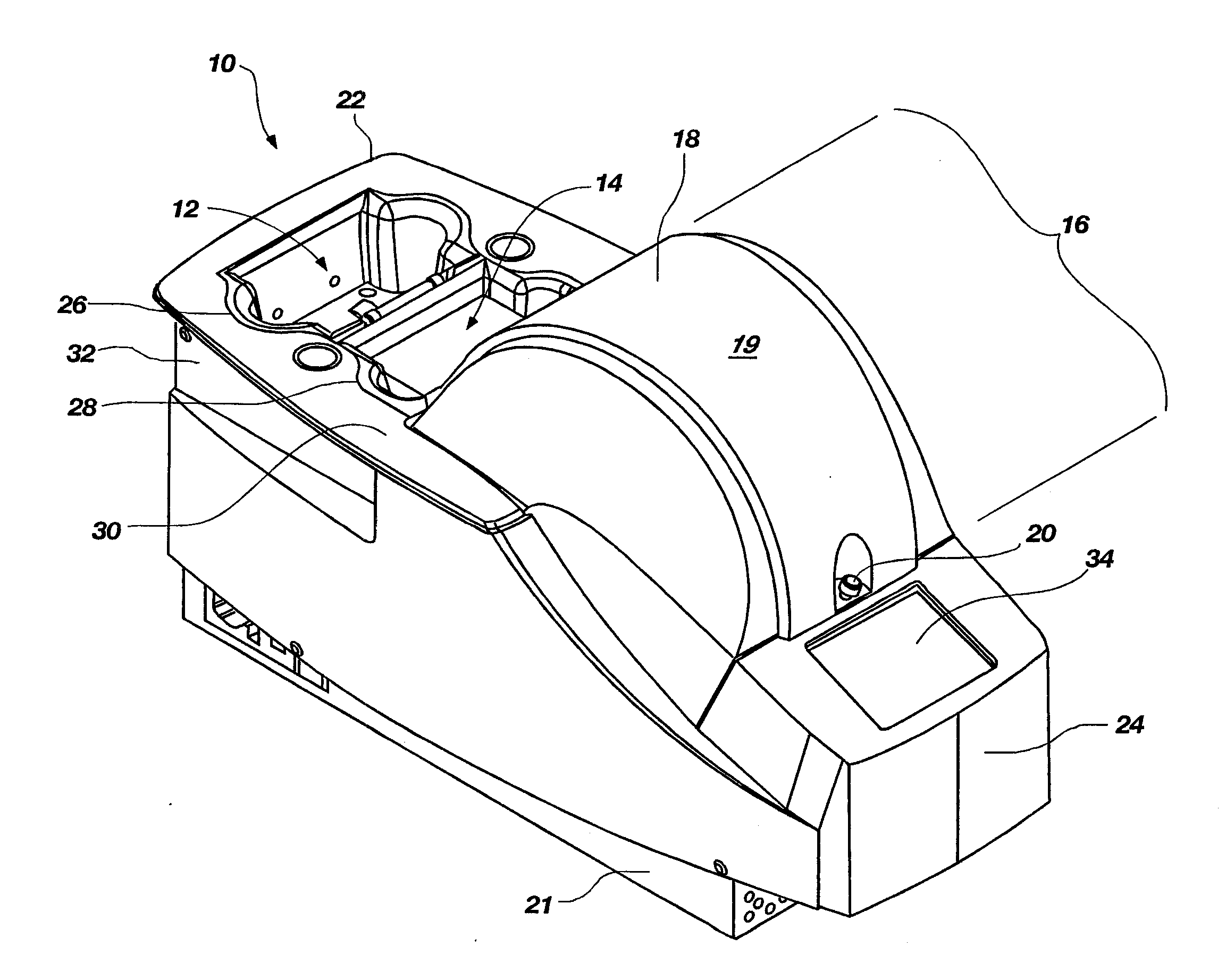

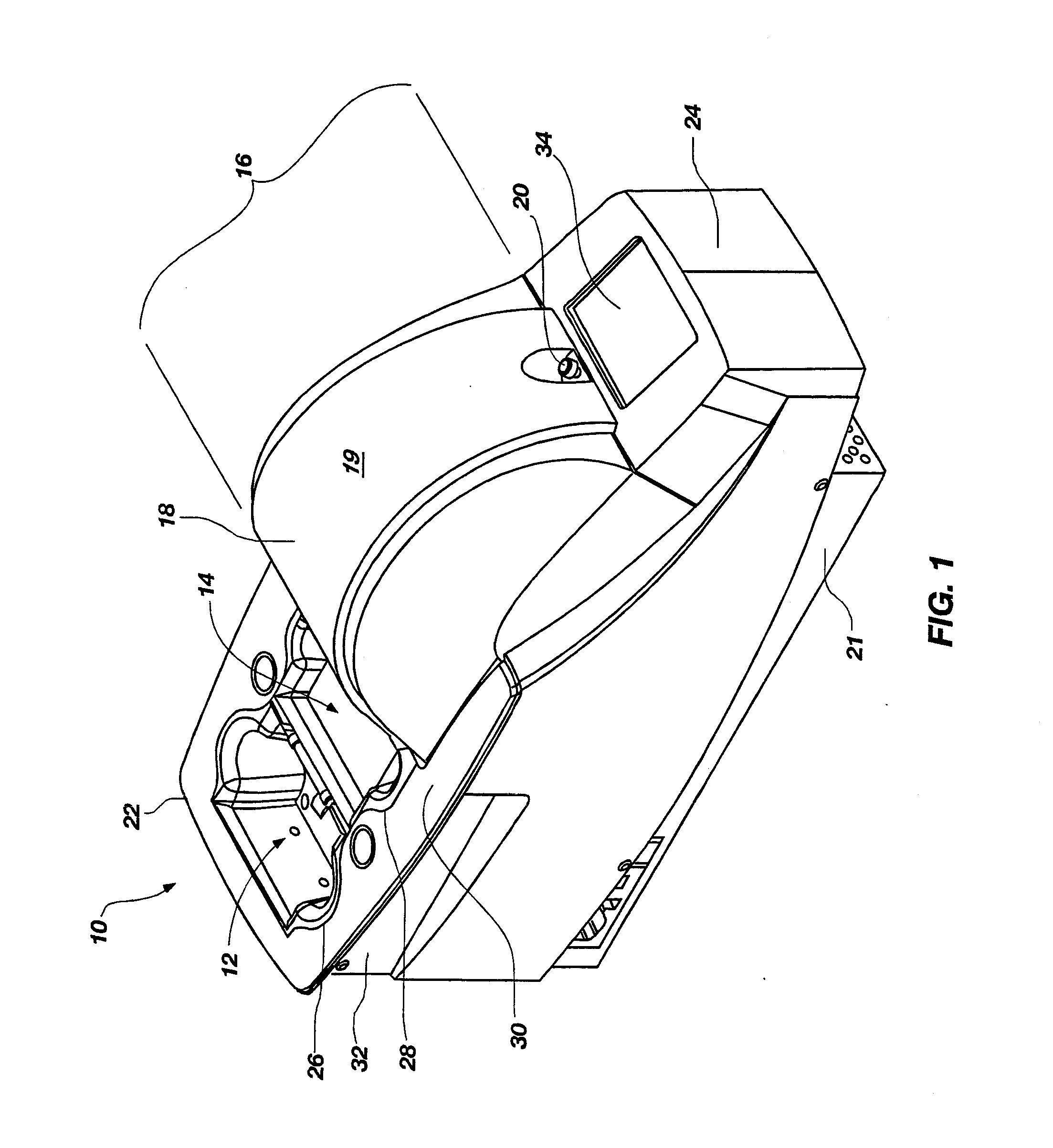

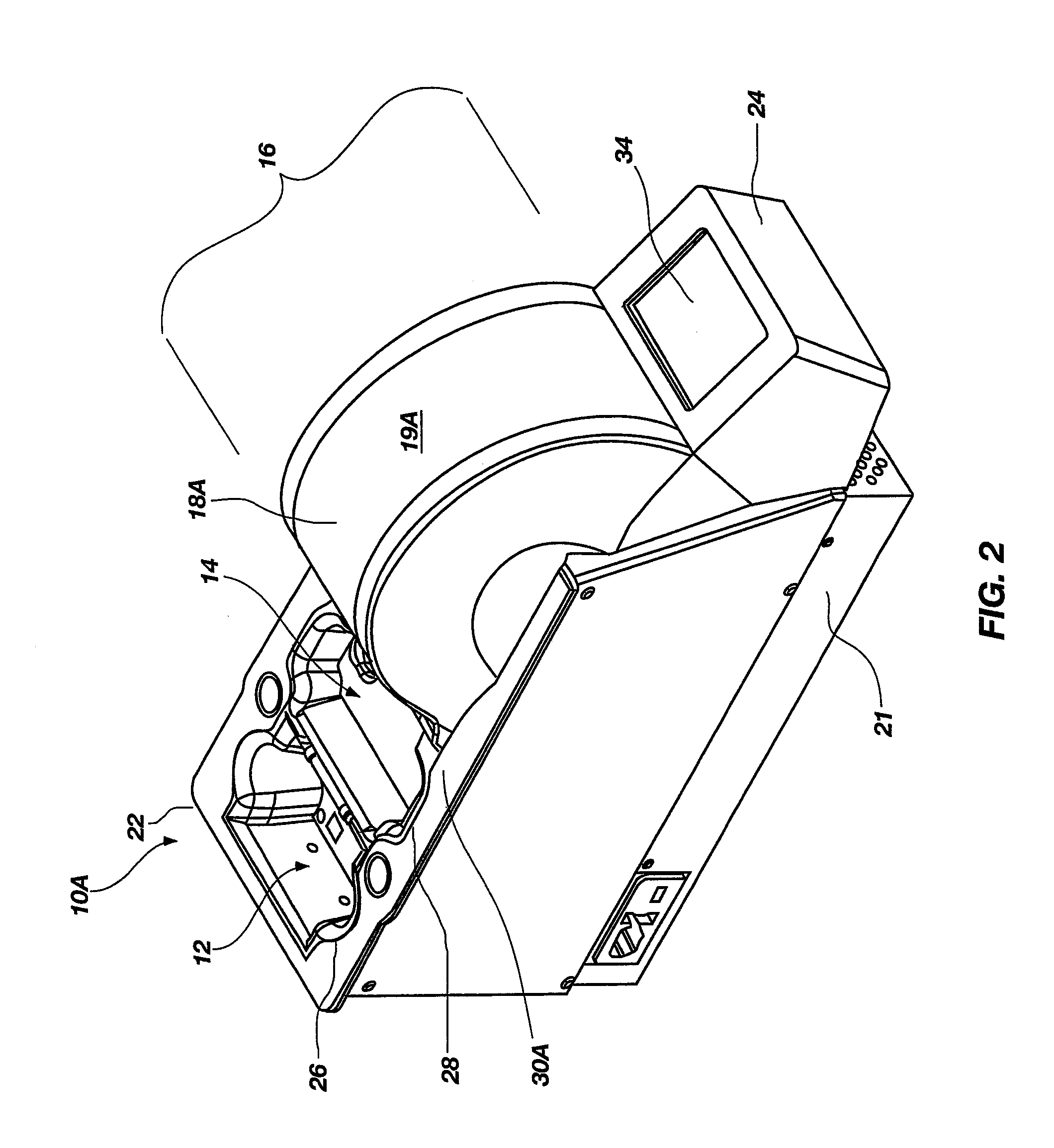

Card handling devices and methods of using the same

A card handling device includes a sensing system for identifying cards handled thereby. A control system may be configured to selectively control an infeed system, a storage system, and / or an output system of the device in response to a signal received from the sensing system, and to enable a user to selectively perform one or more of a shuffling operation, a sorting operation, and a dealing operation using the device. A card handling device may be configured to dispense randomly arranged hands, prearranged hands, randomly arranged decks, or prearranged decks.

Owner:LNW GAMING INC

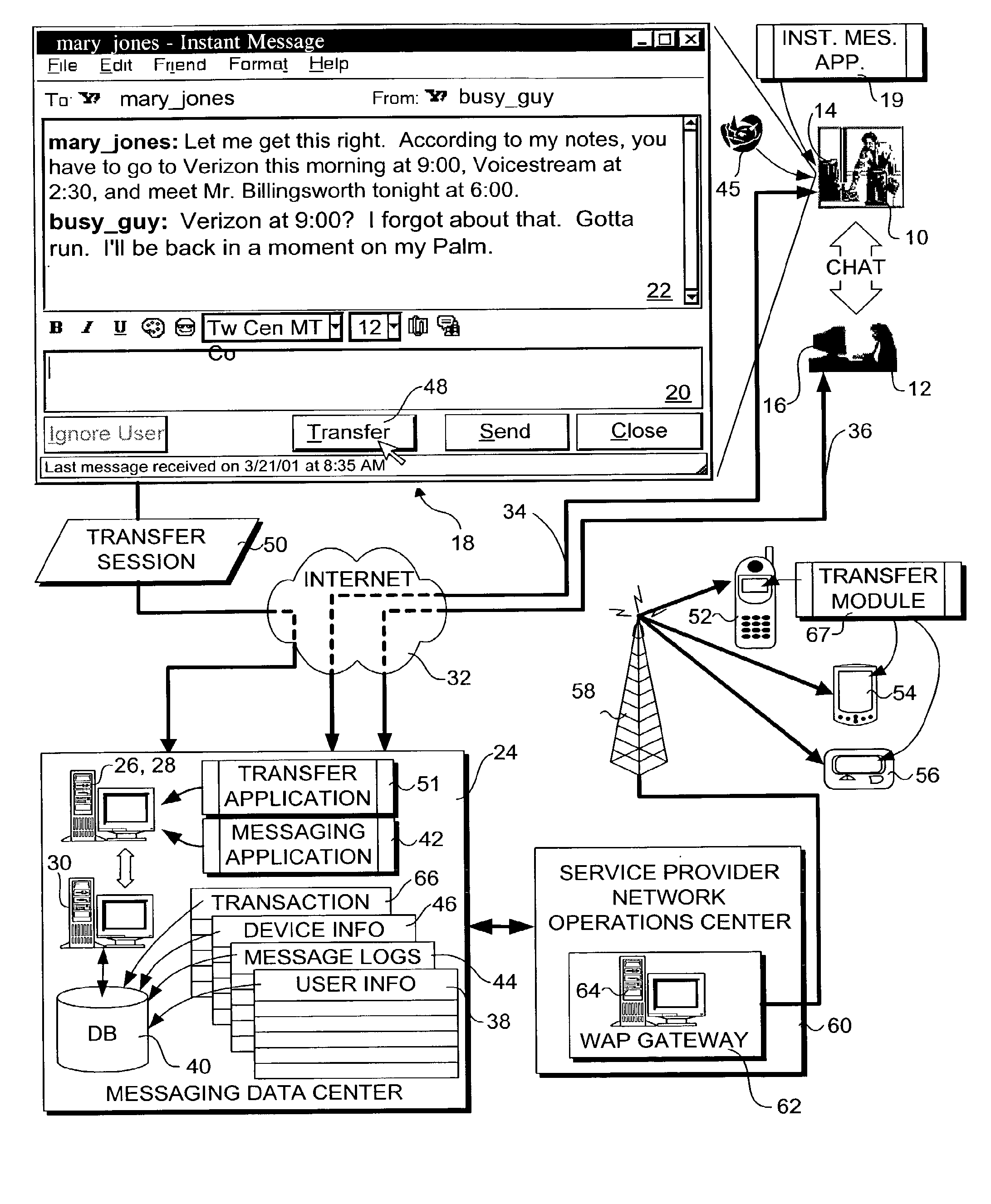

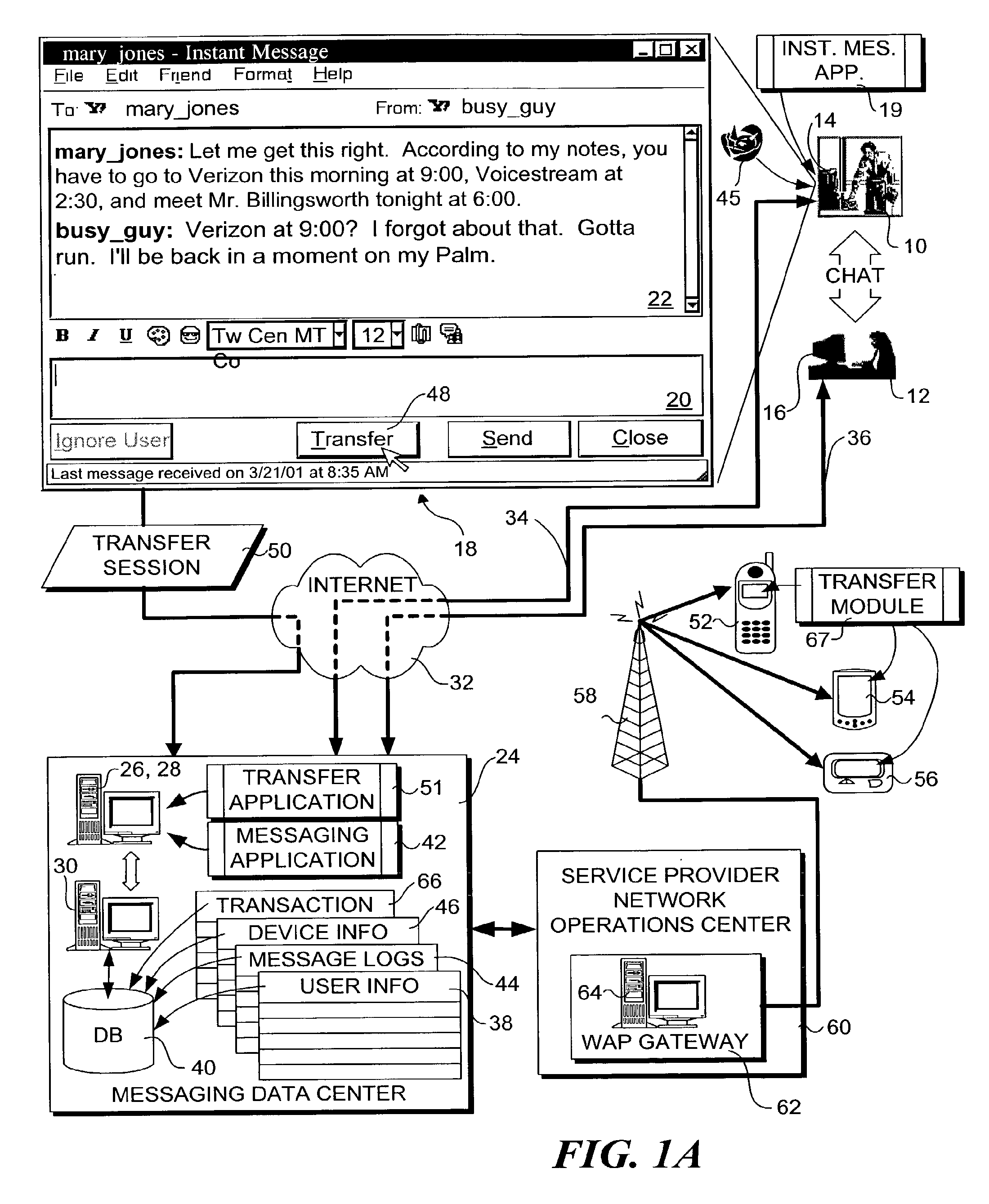

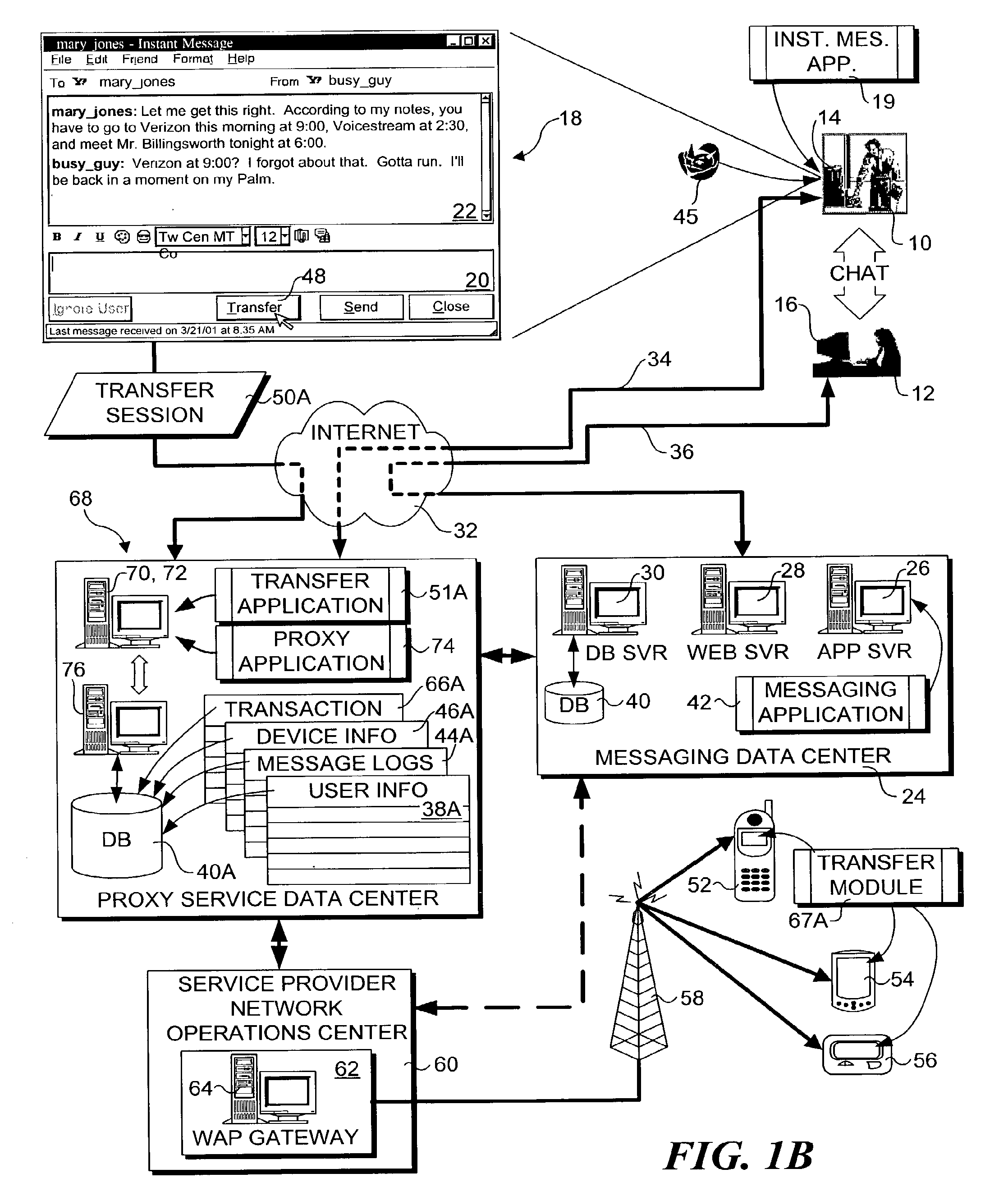

Transferring sessions between devices

InactiveUS20090138606A1Multiple digital computer combinationsTransmissionComputer SessionPersonal computer

Methods and apparatus for transferring a communication and computer session between devices. A user launches a communication session on a first device, such as a personal computer. The user may then selectively transfer the communication session to another device, such as a wireless device, through activation of a triggering signal. In response, the context of the communication session is determined as it is being performed on the first device, including a type of the communication session. The communication session is then transferred to the second device by launching a new communication session on the second device and transferring the context of the communication session corresponding to the first device to the new communication session on the second device. The communications session is continued via use of the first device as a proxy for the second device.

Owner:CONTEMPORARY DISPLAY LLC

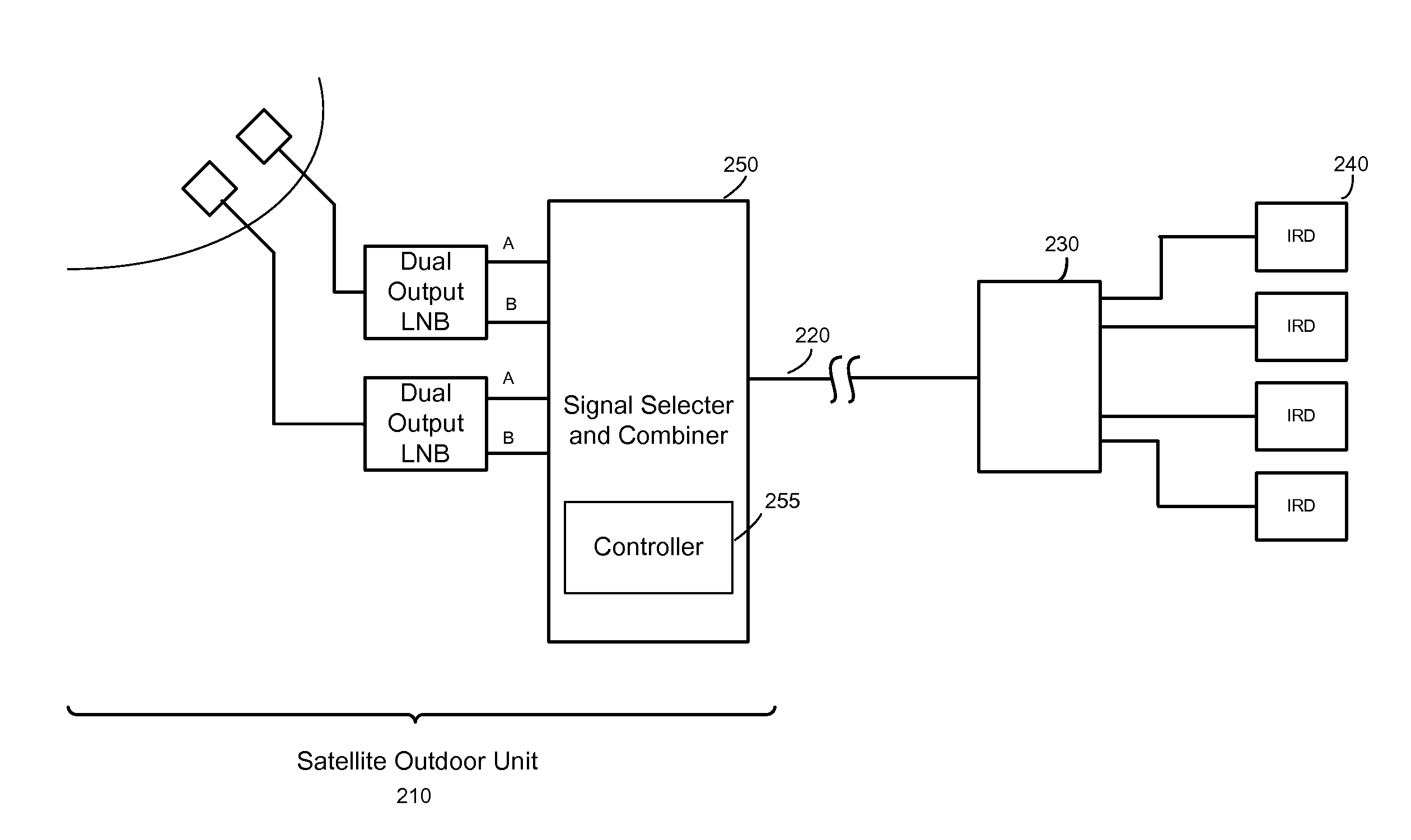

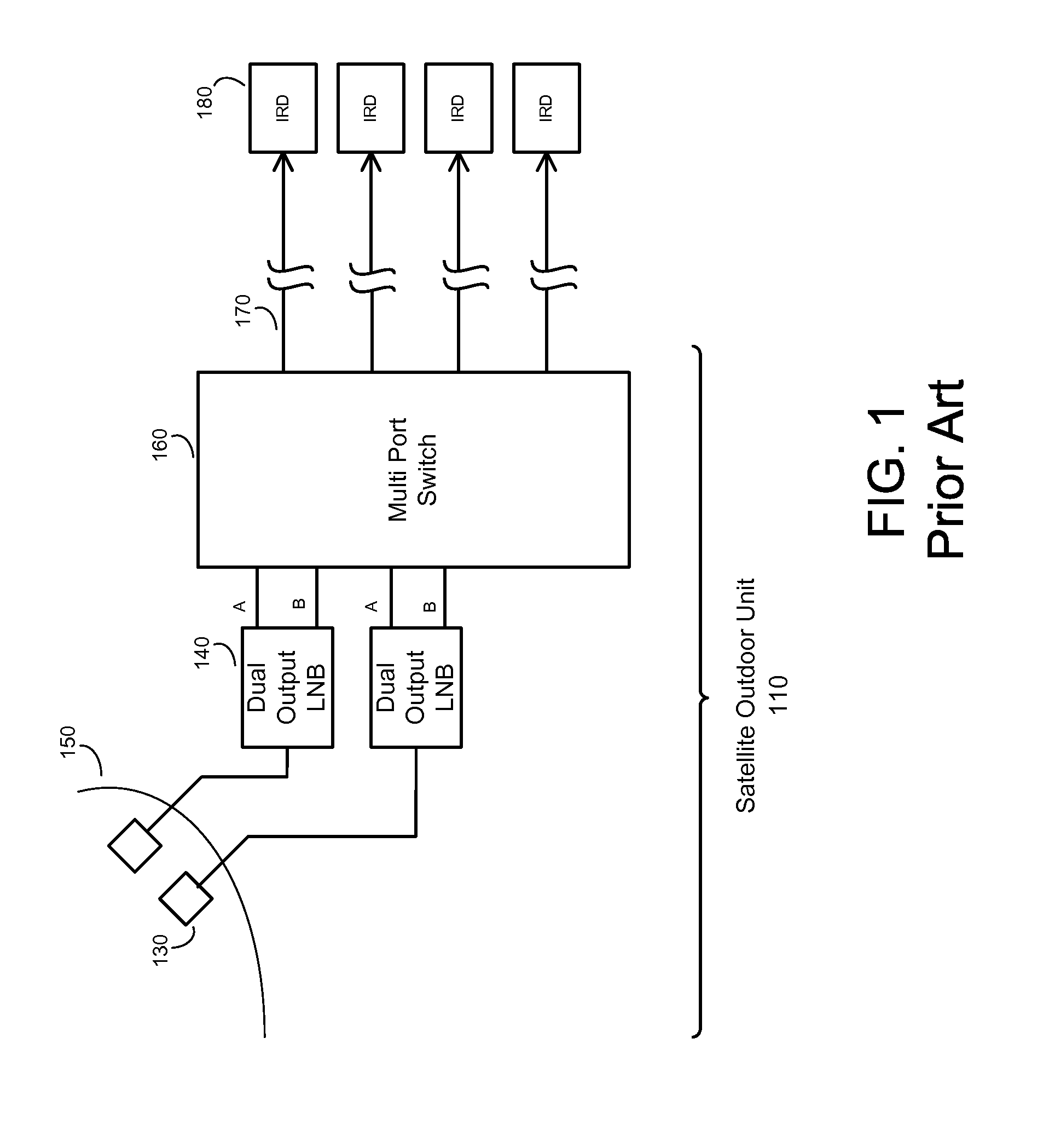

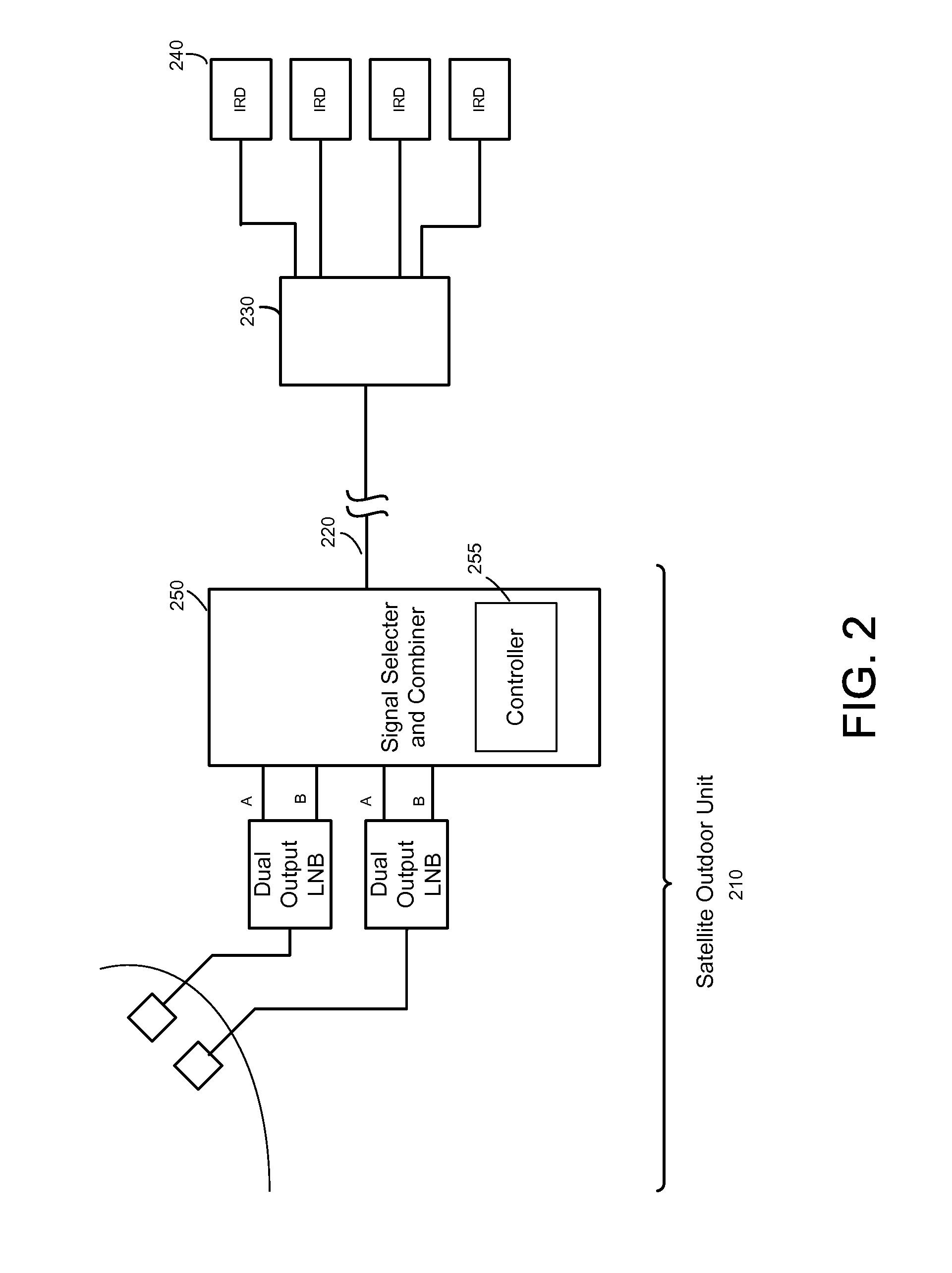

Signal selector and combiner for broadband content distribution

ActiveUS7130576B1Eliminates cross point switchEliminates the cross point switchSatellite broadcast receivingGHz frequency transmissionContent distributionBroadband

In a satellite receiving system, program channels are selected from one or more broadband signals and combined with other selected channels and transmitted from a first unit, for example an outdoor unit, to a second unit, for example a gateway, server, or set-top box, using a single cable. Channels can be selected by digitizing the broadband signal then digitally filtering to isolate the desired channels. The outputs of several LNBs can be selected and combined into one signal. Multiple set-top boxes can receive independent signals over a single cable from the outdoor unit.

Owner:ENTROPIC COMM INC

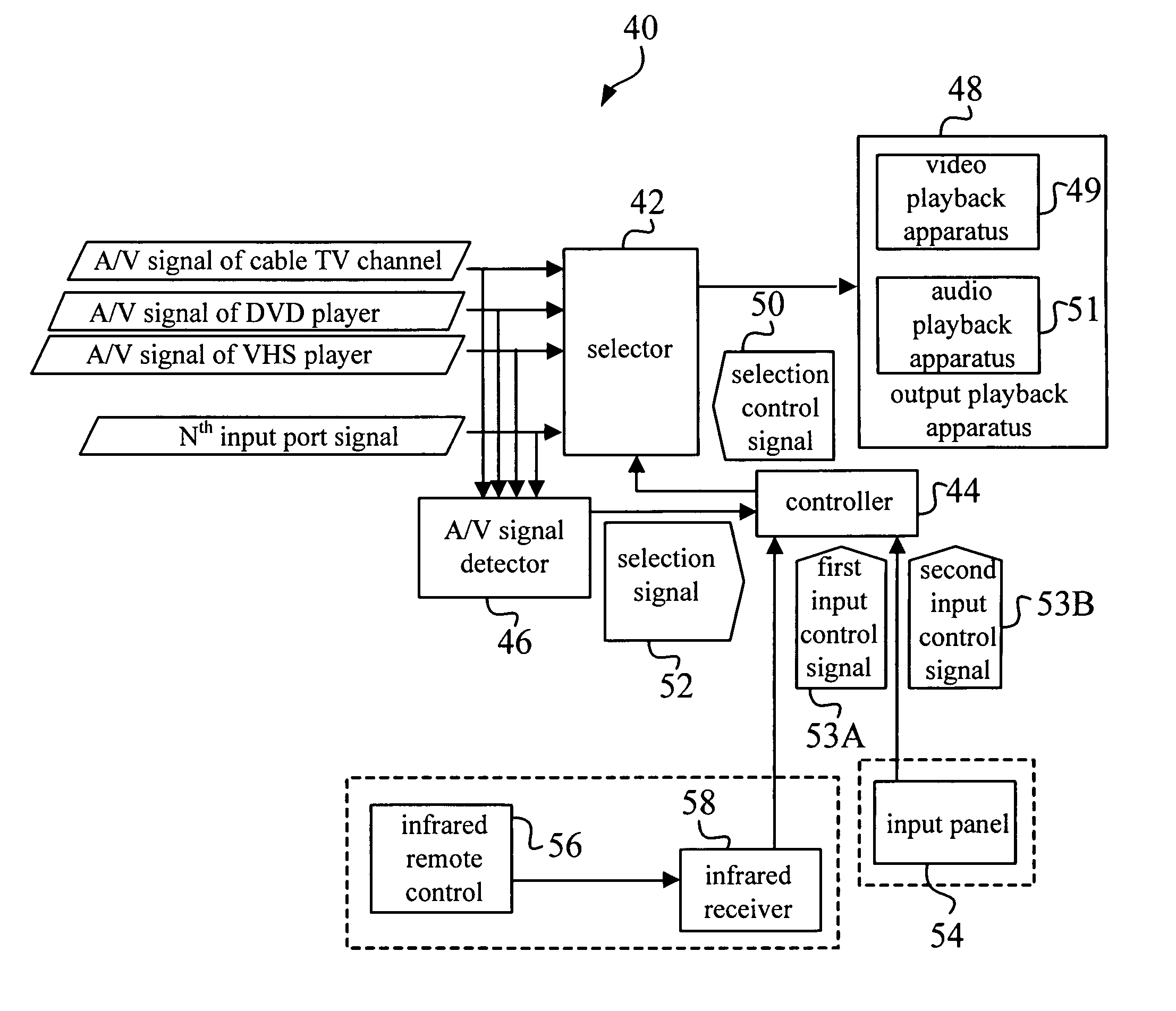

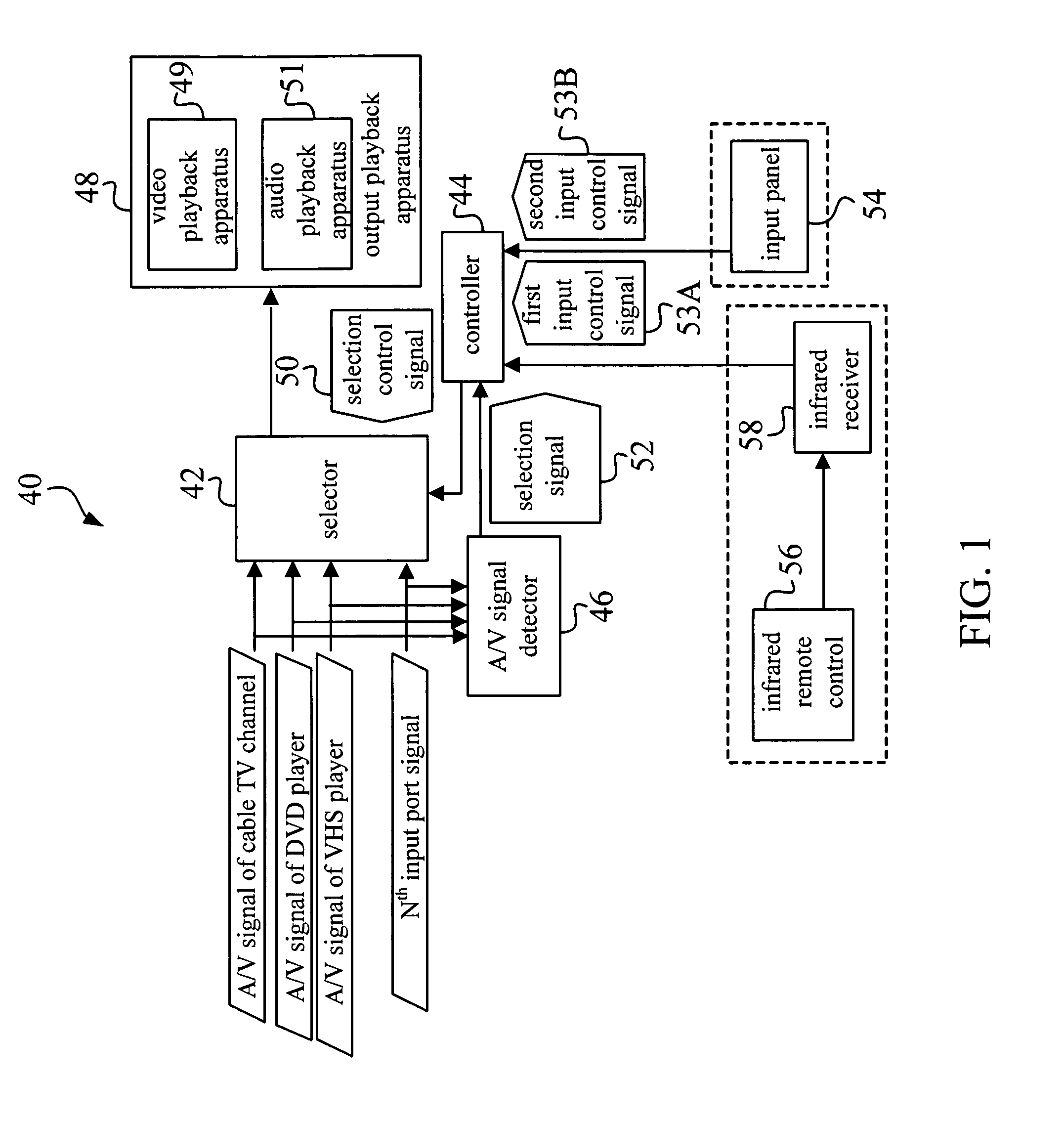

Multimedia processing system capable of auto-detecting multimedia signals to facilitate selecting and method of the same

InactiveUS20050154766A1Avoid difficult choicesTelevision system detailsDigital data processing detailsComputer hardwareControl signal

A multimedia processing system includes a selector, an output playback apparatus, a controller, and an A / V signal detector. The selector has a plurality of input ports for receiving multimedia signals and for selecting and outputting one of the multimedia signals according to a selection control signal. The output playback apparatus is used for playing the multimedia signal outputted by the selector in the output playback apparatus. The controller is used for generating the corresponding selection control signals to the selector. The A / V signal detector is used for detecting whether the input ports of the selector have received a newly inputted multimedia signal. When a newly inputted multimedia signal is detected, the A / V signal detector outputs a specific selection signal to the controller, so the controller subsequently generates the corresponding selection control signal to the selector for selecting and outputting the newly inputted multimedia signal to the output playback apparatus.

Owner:MEDIATEK INC

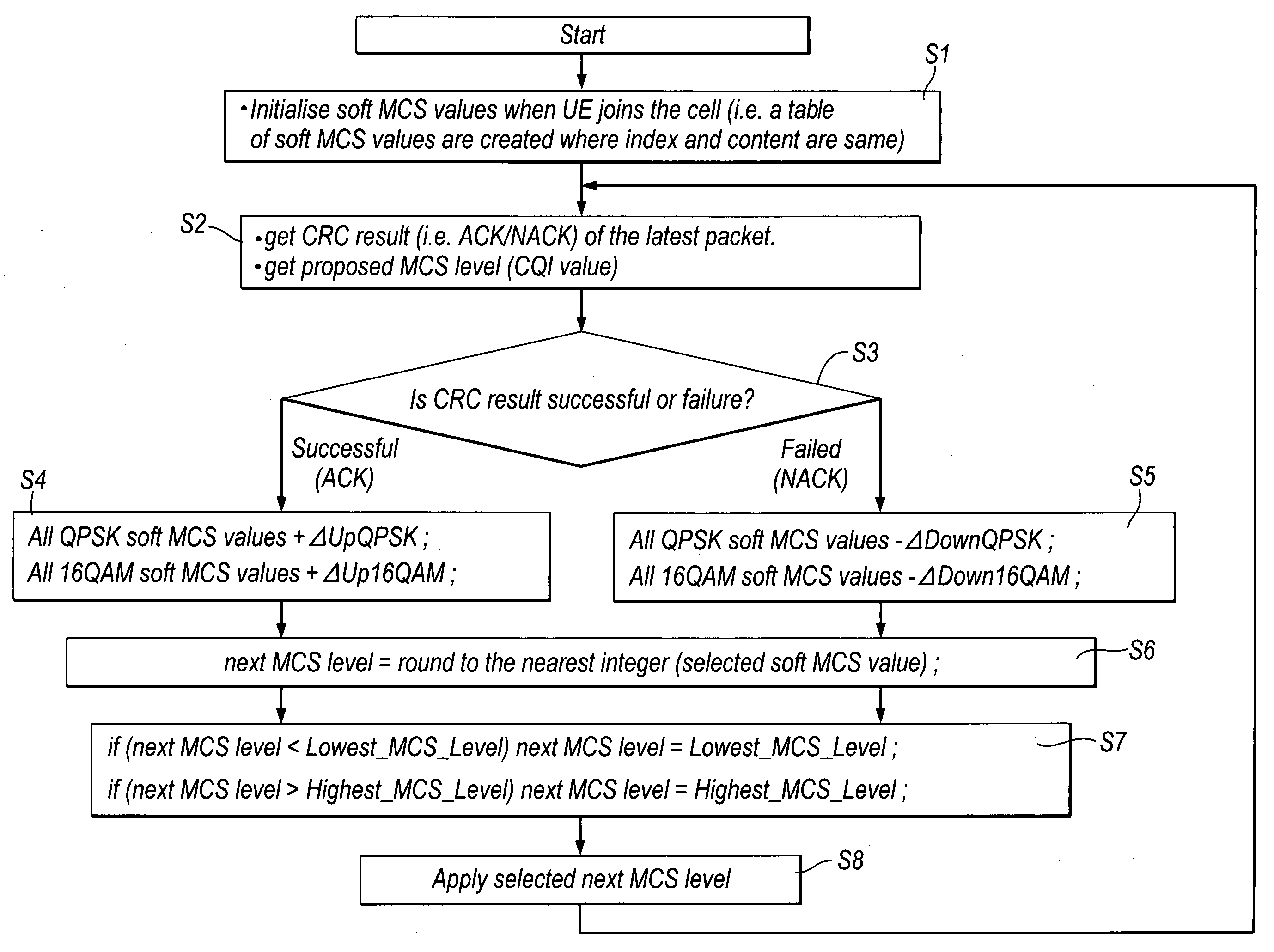

Adaptive modulation and coding

InactiveUS20050025254A1Improve accuracyChoose simpleAmplitude-modulated carrier systemsCode division multiplexEngineeringSelf adaptive

In an adaptive modulation and coding method one or more adjustable values are created (S1), each corresponding to at least one of a plurality of available modulation and coding levels applicable to a signal transmitted from a transmitter to a receiver, and each representing a change to the level(s) to which it corresponds. One or more of said adjustable values is / are adjusted in dependence upon whether or not the signal is received successfully by the receiver (S2-S5). One of said available modulation and coding levels is selected (S6-S8) to apply to the signal based on such an adjustable value. Such a method can enable the appropriate modulation and coding level to be selected even when the path and channel conditions vary. The method is applicable to selecting modulation and coding levels in a high-speed downlink packet access system of a wireless communication network.

Owner:FUJITSU LTD

Card handling devices and methods of using the same

A card handling device includes a sensing system for identifying cards handled thereby. A control system may be configured to selectively control an infeed system, a storage system, and / or an output system of the device in response to a signal received from the sensing system, and to enable a user to selectively perform one or more of a shuffling operation, a sorting operation, and a dealing operation using the device. A card handling device may be configured to dispense randomly arranged hands, prearranged hands, randomly arranged decks, or prearranged decks.

Owner:LNW GAMING INC

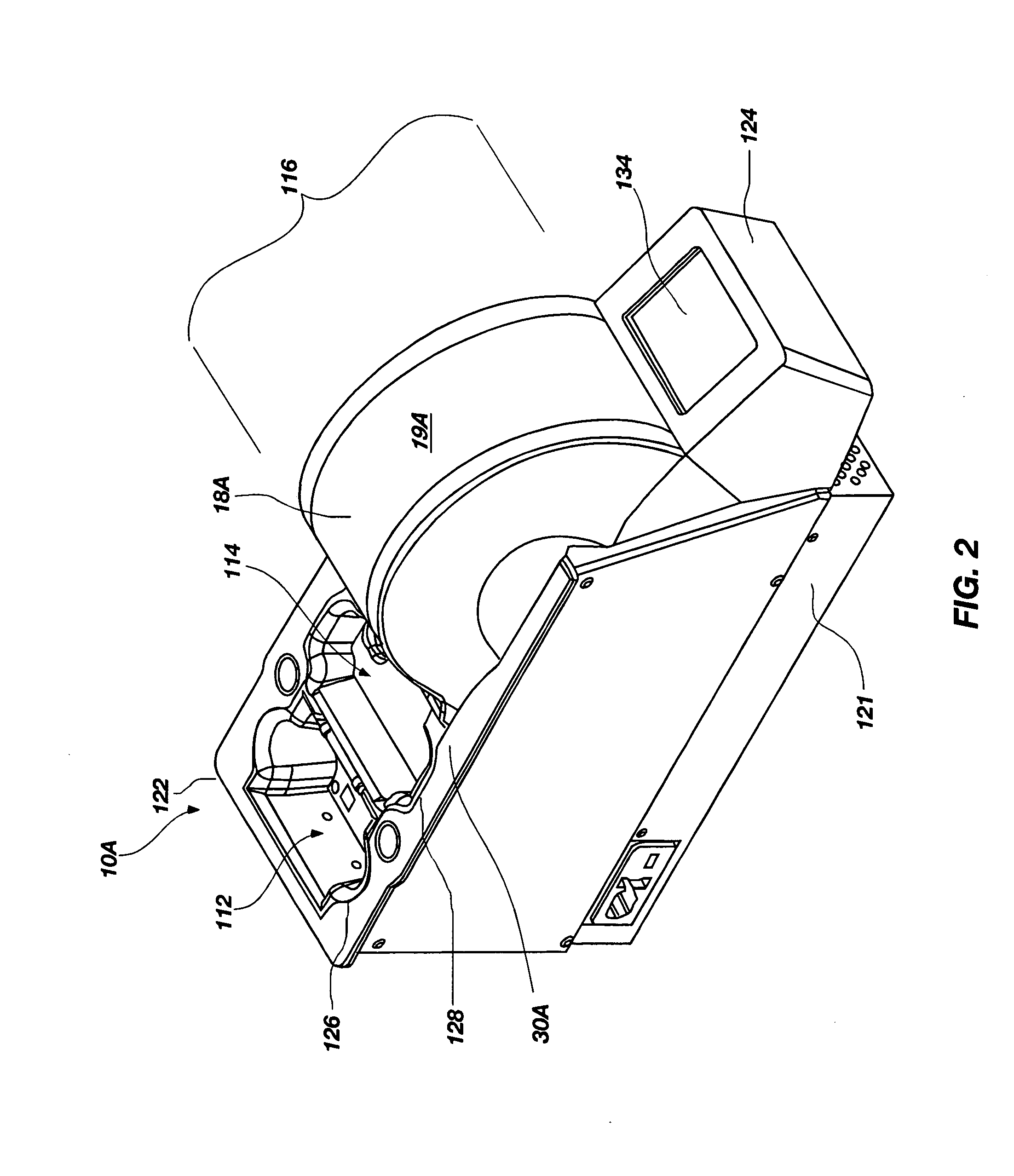

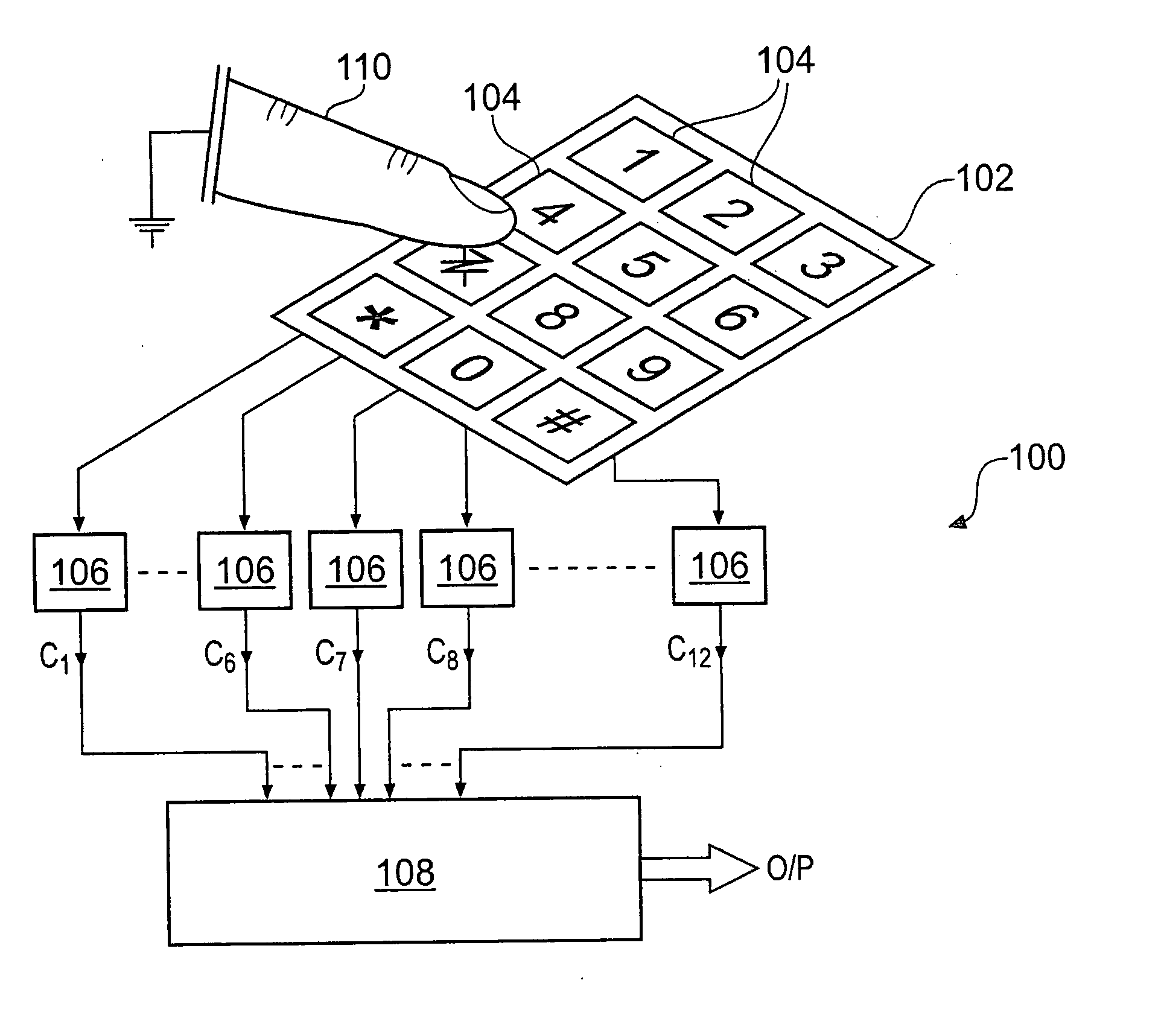

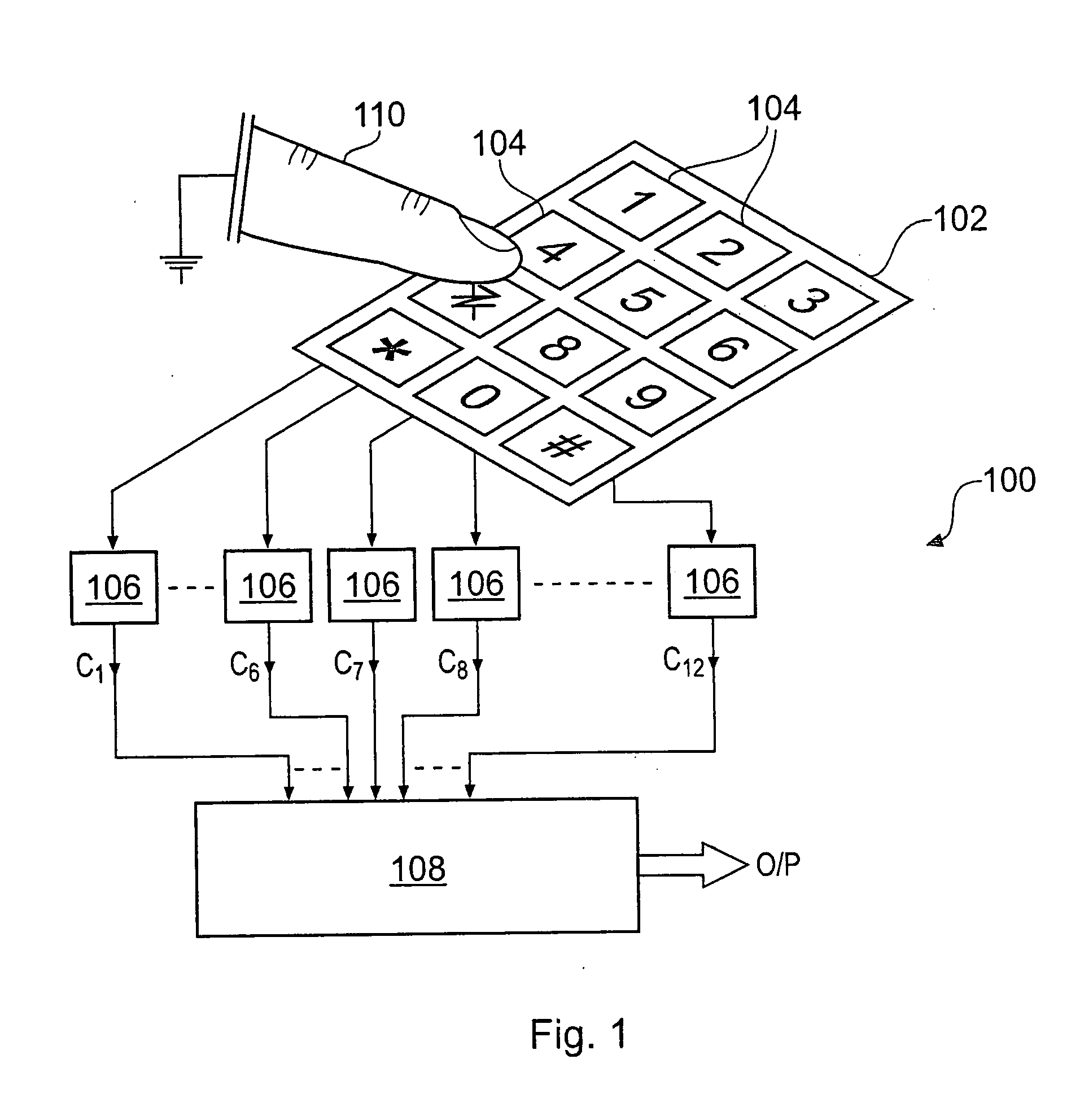

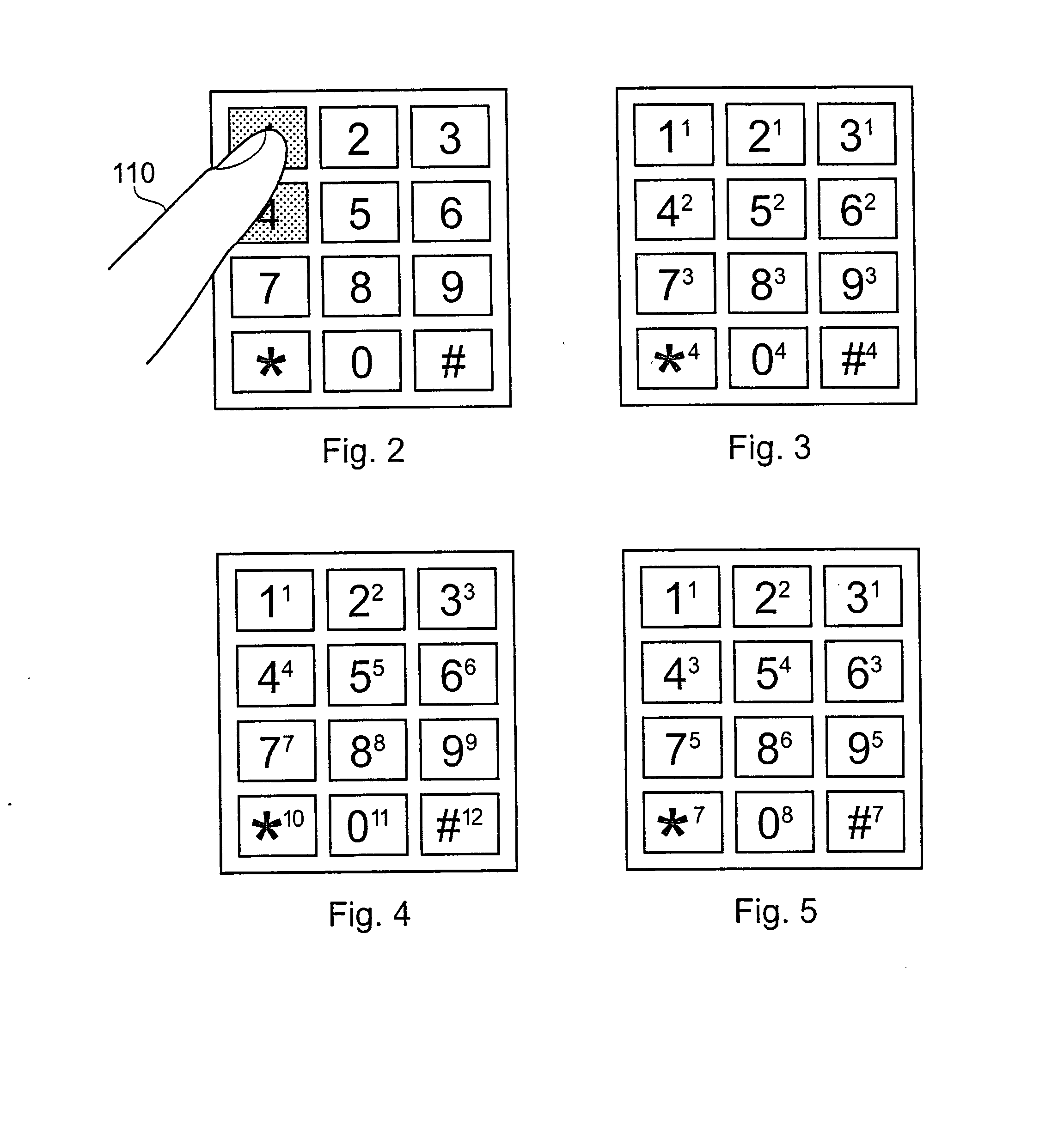

Capacitive Keyboard with Position Dependent Reduced Keying Ambiguity

InactiveUS20070273561A1Reduce ambiguitySignal strength value can be enhancedElectronic switchingInput/output processes for data processingHuman–computer interactionCapacitance transducer

Owner:NEODRON LTD

Display device

InactiveUS6853371B2Reduce signal linesLess spaceCathode-ray tube indicatorsNon-linear opticsHigh densityDisplay device

Within one pixel element 200, two display circuits corresponding to the analog display mode and the digital display mode are disposed such that they are adjacent to each other. One of these two display circuits can be selected through the circuit selection circuits 40 or 43. Since the high voltage power line 150 of the retaining circuit 110, which is used under the digital display mode, also performs as the signal selection line 88, it is possible to have the high density integration of the pixel element 200. Also, the bias voltage Vsc supplied through the selection storage capacitor line 81 is same as the signal A. Therefore, the storage capacitor line 81 is connected to the drain of the TFT 122 of the signal selection circuit 120 so that the signal line 82 for supplying the signal A can be omitted. Thus, the high-density integration of the pixel element 200 can be achieved.

Owner:SANYO ELECTRIC CO LTD

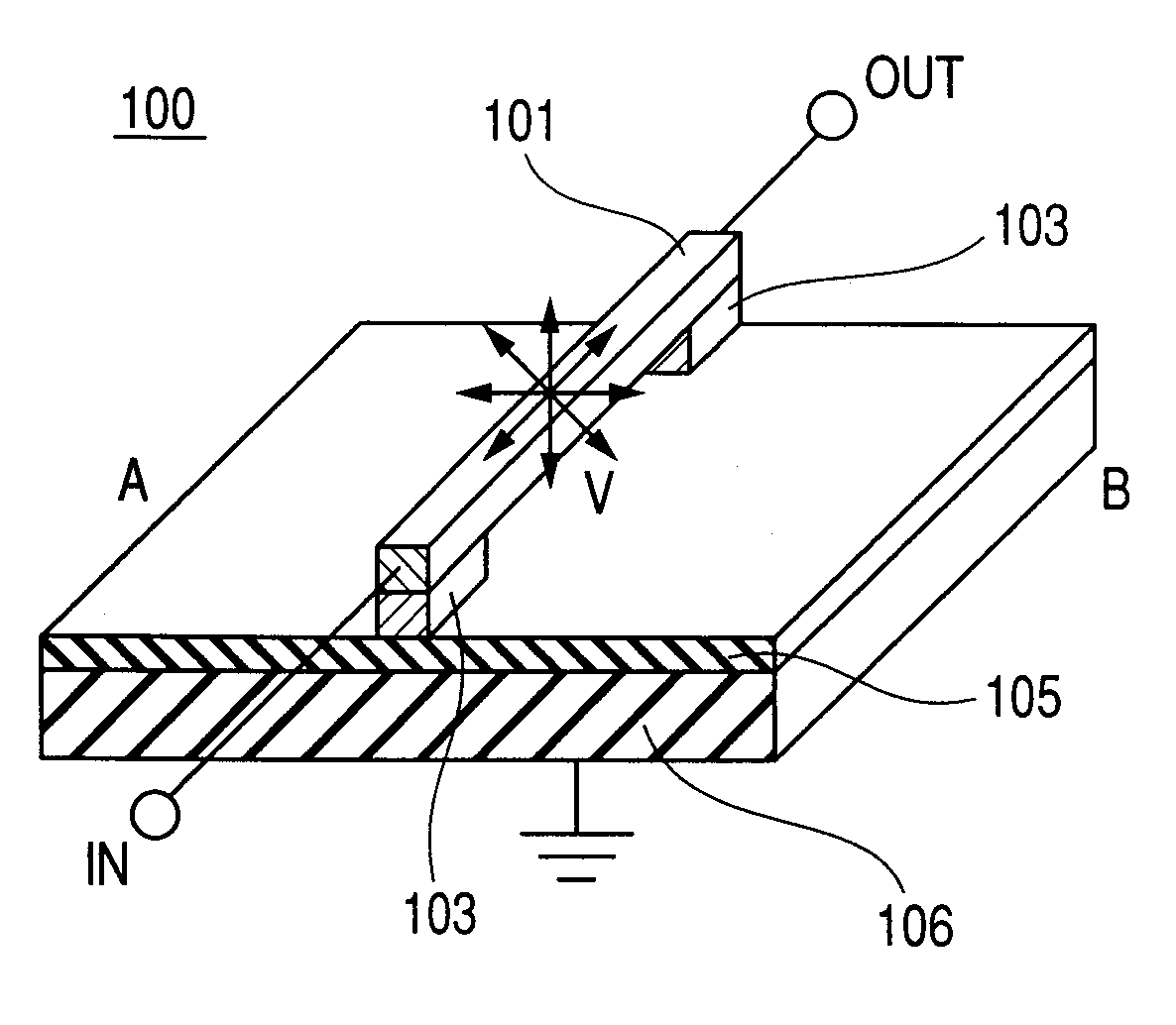

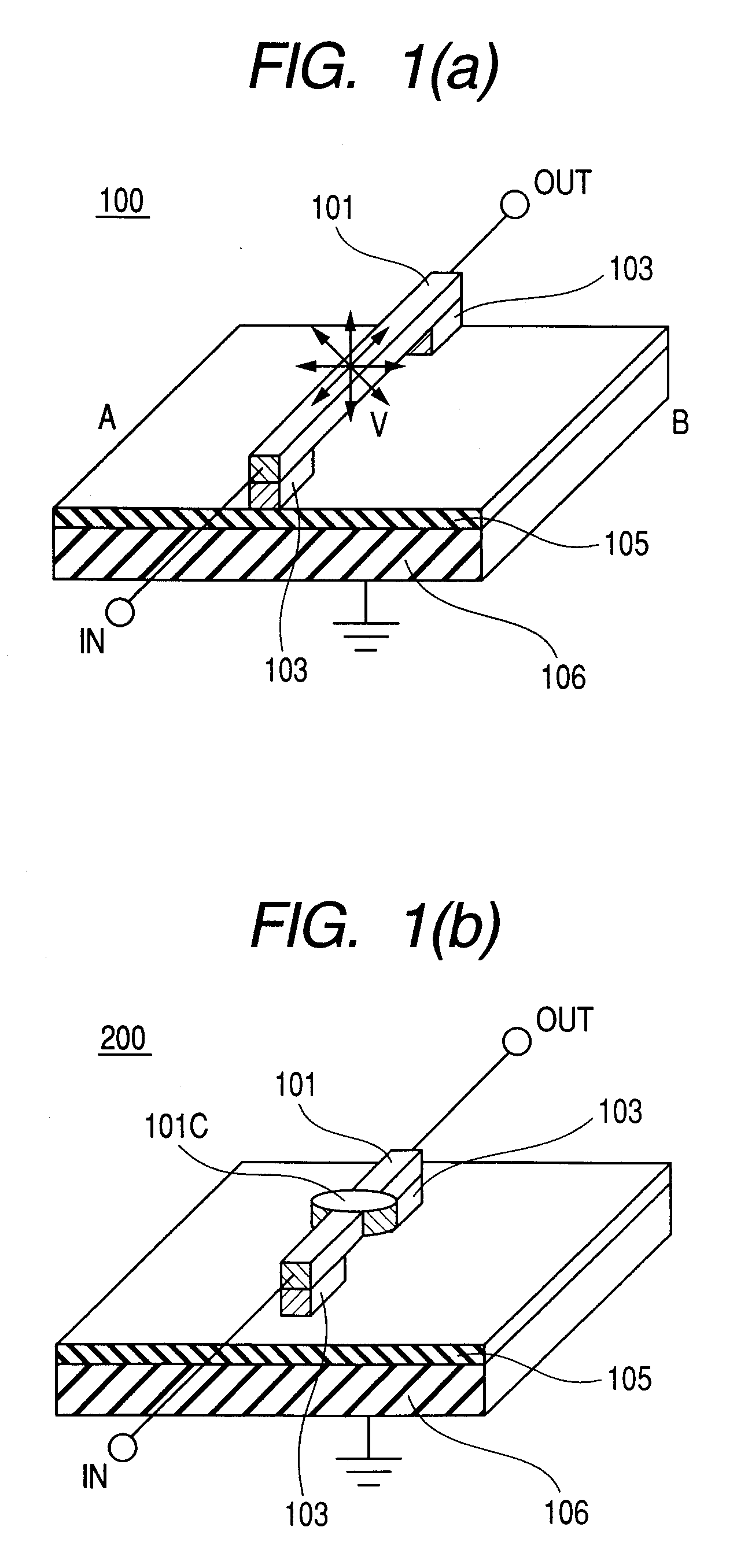

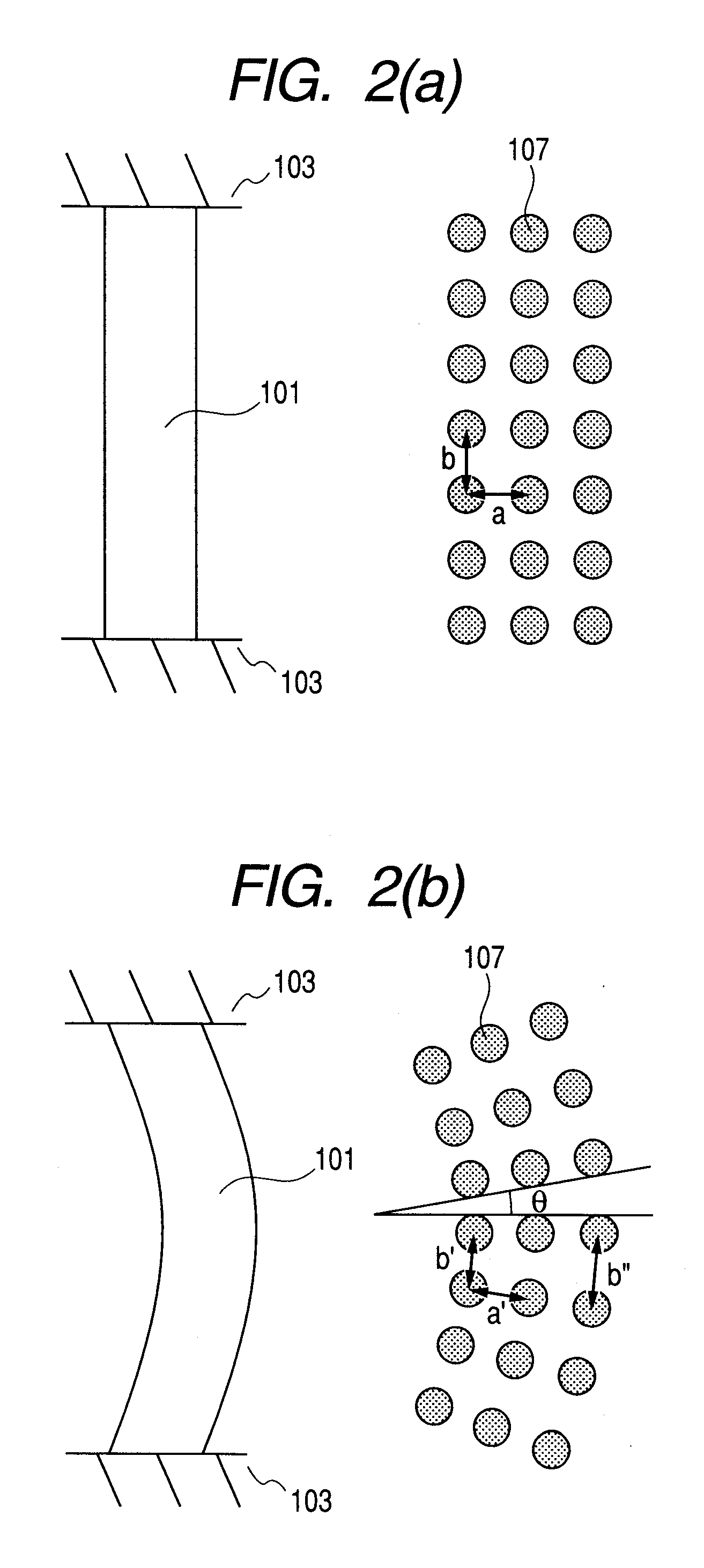

Electric machine signal selecting element

InactiveUS20070164839A1Simple structureLow costImpedence networksPiezoelectric/electrostrictive devicesElectric machineMiniaturization

To provide an electromechanical signal selection device which can be miniaturized and highly integrated and which can selectively output only a signal of a predetermined frequency without providing any sensitive vibration sensing mechanism, and electric equipment using the electromechanical signal selection device. A micro-vibrator serving as a resonator is provided. The micro-vibrator can be excited by an external force to excite vibration of the micro-vibrator. A material whose physical property is changed in accordance with a structural change is used as the micro-vibrator. Thus, a sensitive electromechanical signal selection device is obtained.

Owner:PANASONIC CORP

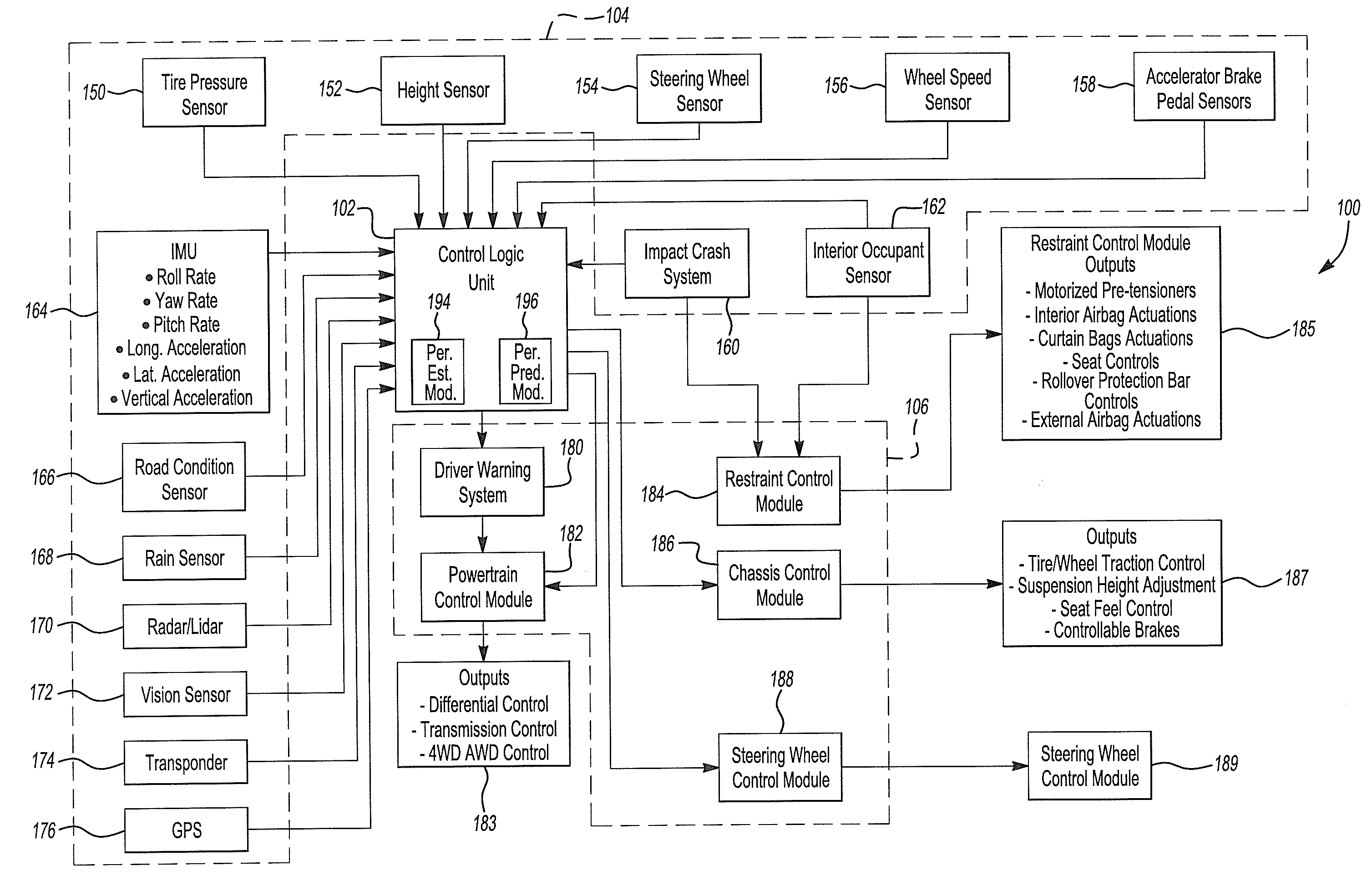

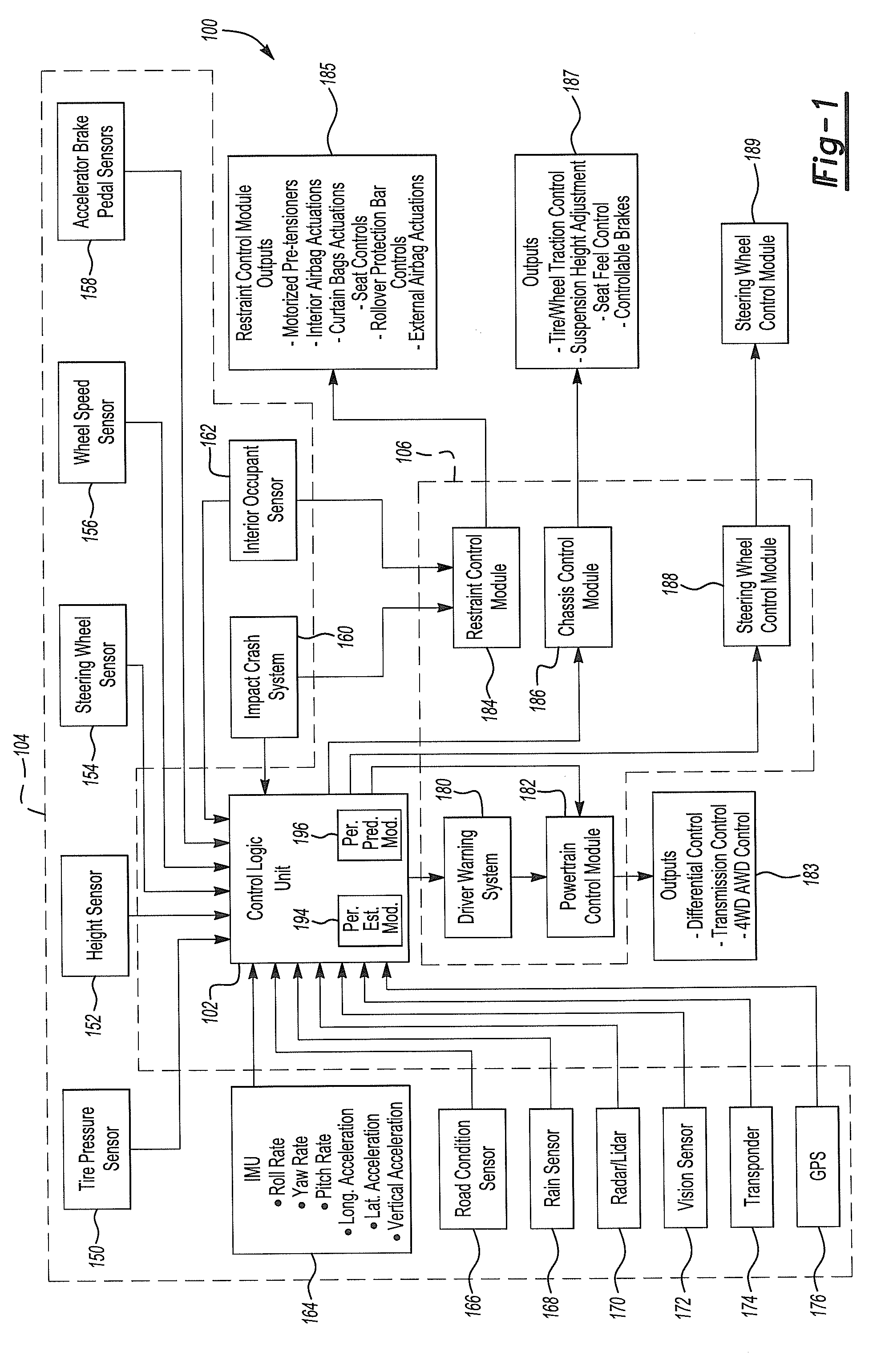

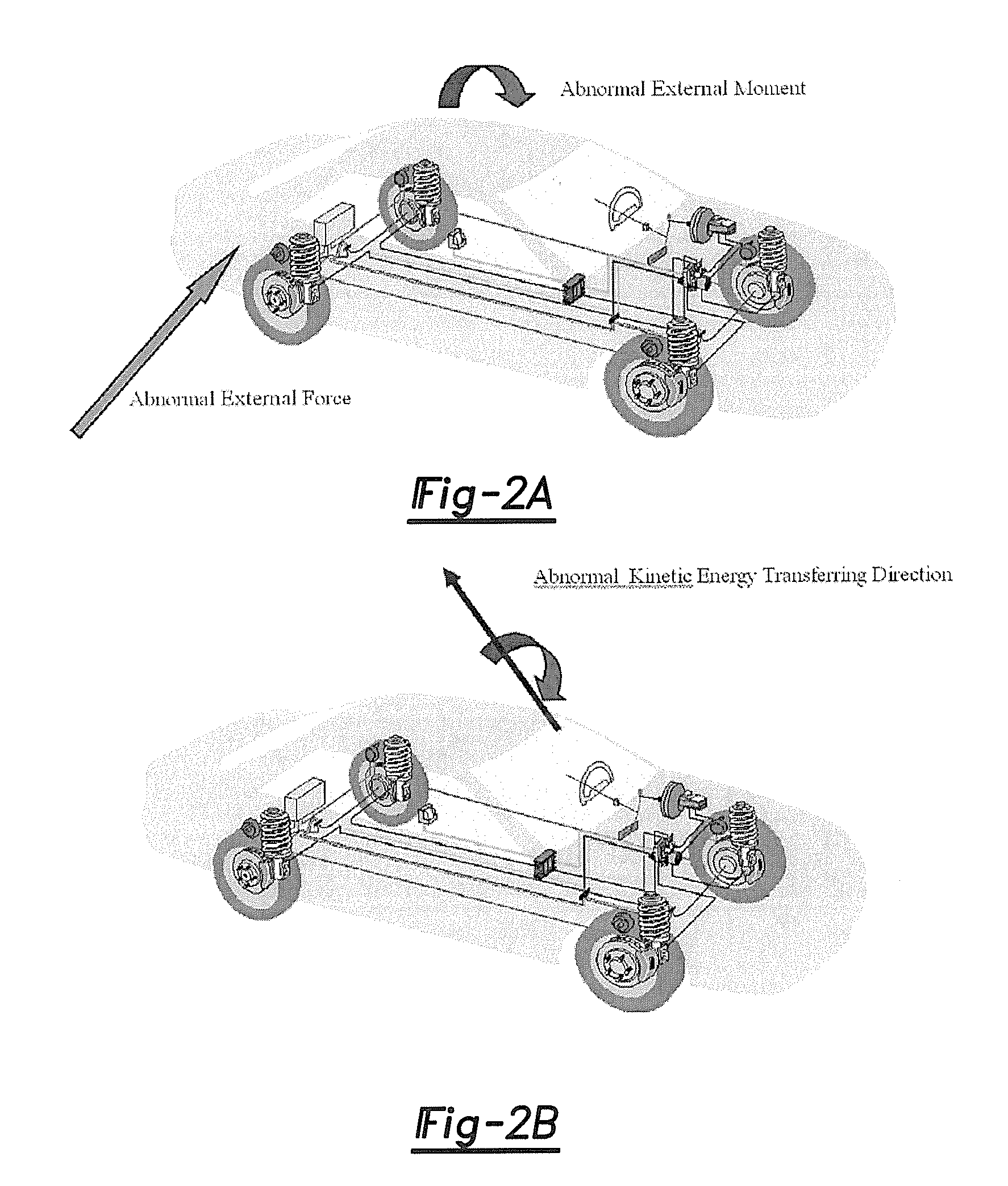

Active safety system

InactiveUS20080147277A1Minimize damageEasily damagedDigital data processing detailsPedestrian/occupant safety arrangementActive safetyControl system

According to one embodiment, an active safety control system for a driver of a vehicle is provided when the vehicle is in a first perturbed state. The system generally includes a plurality of sensors, an actuation system and a controller. The plurality of sensors are operable to generate signals which indicate that the vehicle is in the first perturbed state. The actuation system is adapted to change driving conditions of the vehicle. The controller is configured to selectively control the actuation system in response to the signals without driver intervention to change the driving conditions of the vehicle to regain control of the vehicle after the vehicle has entered the first perturbed state.

Owner:FORD GLOBAL TECH LLC

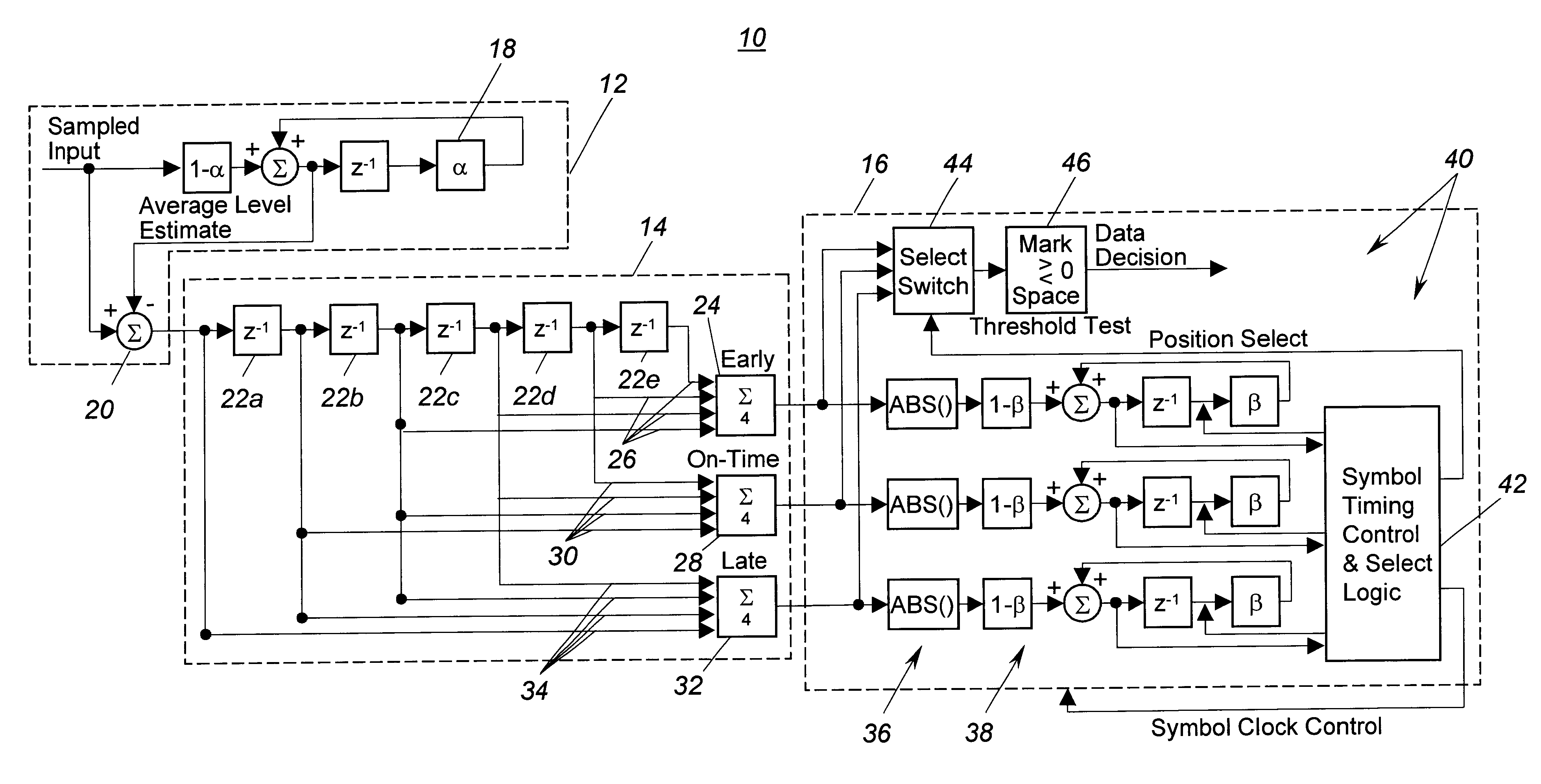

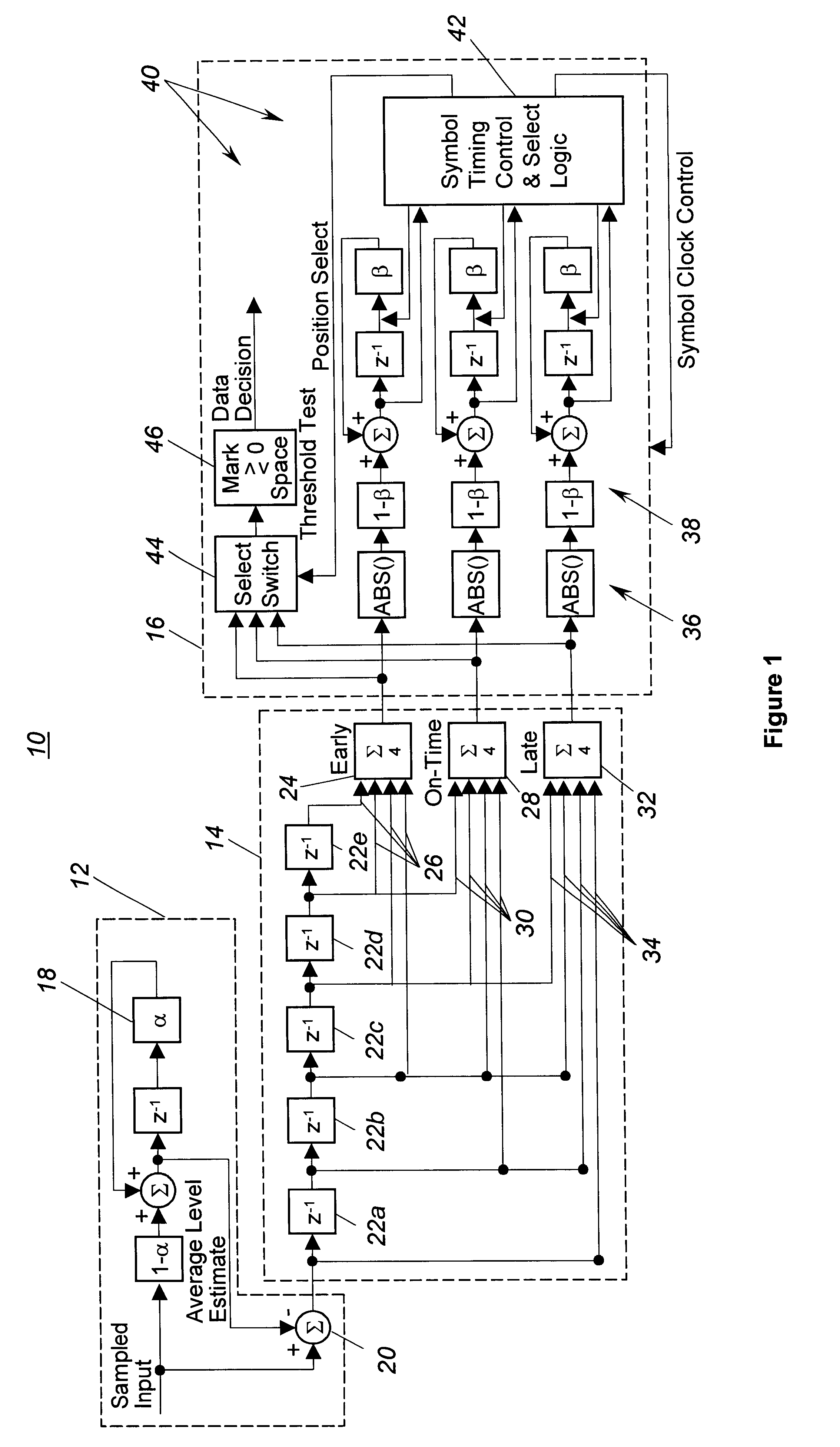

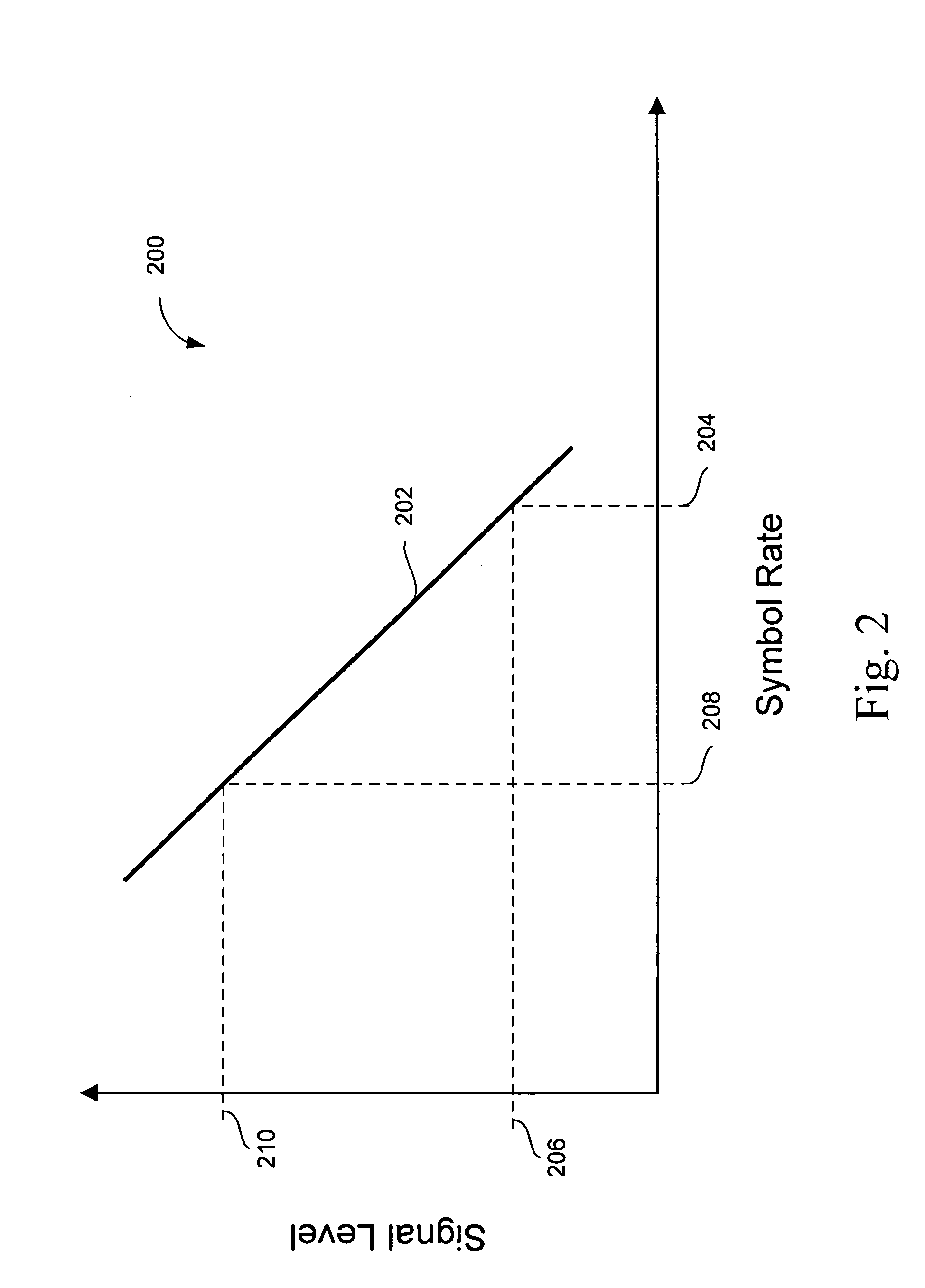

Early/on-time/late gate bit synchronizer

InactiveUS6792059B2Eliminates excessive memory bufferEliminates control logicTime-division multiplexAmplitude-modulated carrier systemsTime gateSymbol rate

A bit synchronizer for a digital receiver system accounts for loss of bit synchronization due to transmission phenomena. The bit synchronizer includes a DC level estimator for converting a sampled digital signal having a bit rate and a sampling rate into a level-adjusted signal. A delay module generates a first timing signal, a second timing signal, and a third timing signal based on the level-adjusted signal. The timing signals correspond to early, on-time, and late sampling windows. The control module generates an output signal based on the timing signals such that the transmit and receive bit timing are synchronized. In one embodiment, the control module has an absolute value stage, an integration stage, and a signal selector. The signal selector is able to select between the timing signals, adjust the symbol rate to re-center the on-time gate, and memory swap to maintain correct averaging operations.

Owner:NORTHROP GRUMMAN SYST CORP

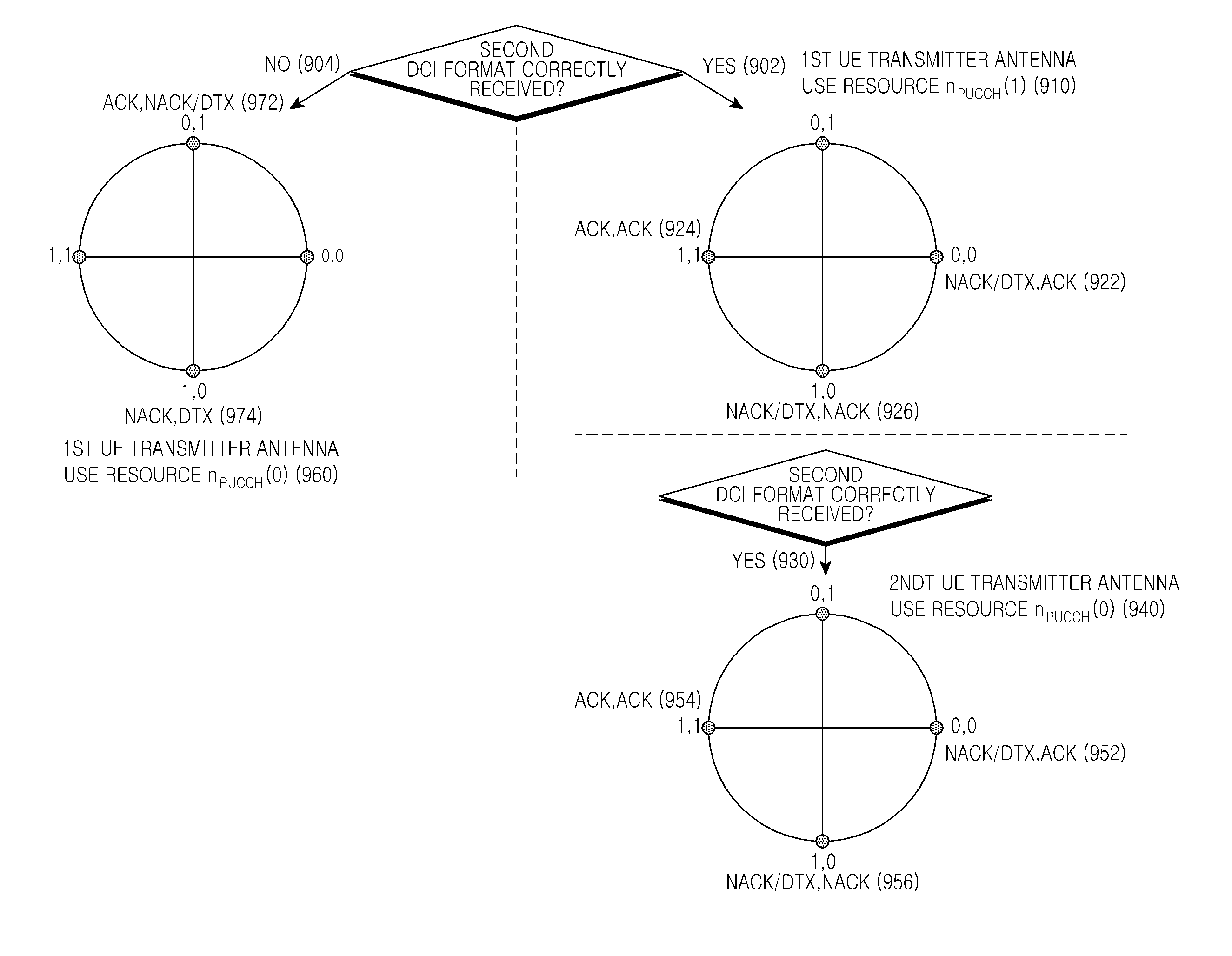

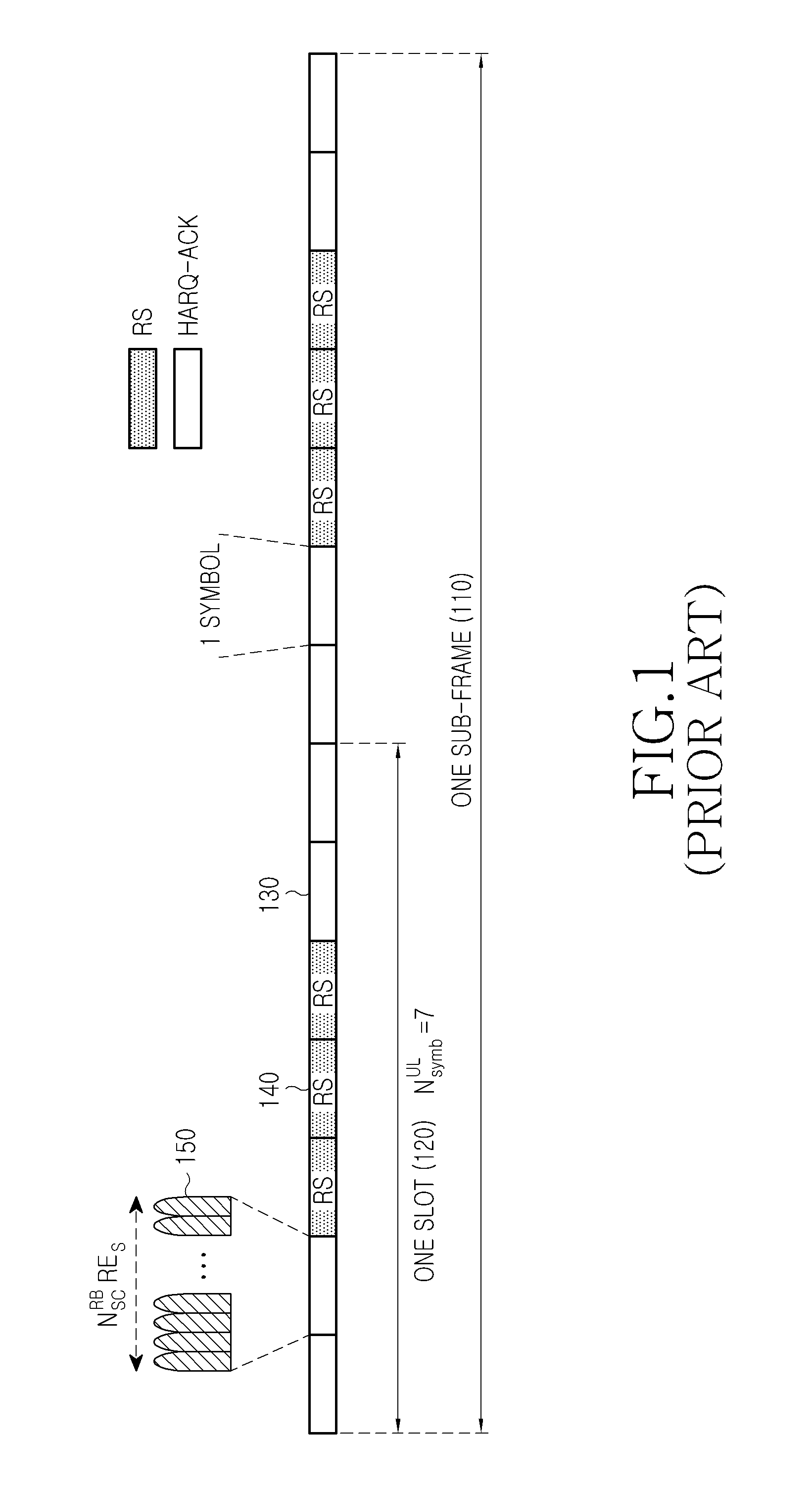

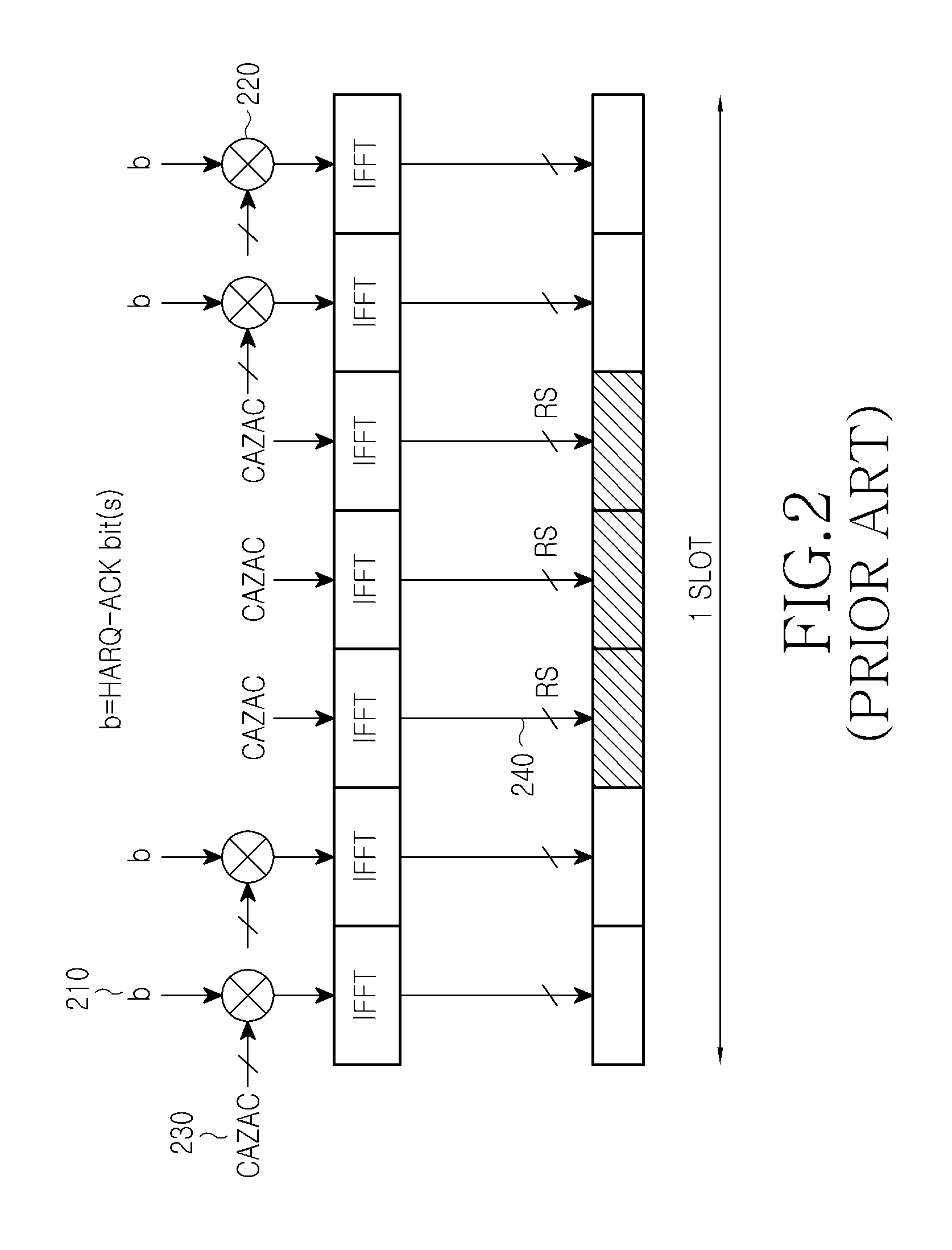

Transmission diversity and multiplexing for harq-ack signals in communication systems

A method and apparatus are described for a User Equipment (UE) to transmit in a control channel ACKnowledgement signals associated with a Hybrid Automatic Repeat reQuest process (HARQ-ACK signals) in response to receiving Transport Blocks (TBs) transmitted from a base station. The UE conveys the HARQ-ACK information by selecting one resource from multiple resources in the control channel and by selecting a constellation point of the modulation scheme for the HARQ-ACK signal. Transmission diversity is supported using different control channel resources that are already available to the UE without configuring additional resources. Design principles are described to optimally map the HARQ-ACK information to control channel resources and modulation constellation points for a Time Division Duplex (TDD) system and for a Frequency Division Duplex (FDD) system.

Owner:SAMSUNG ELECTRONICS CO LTD

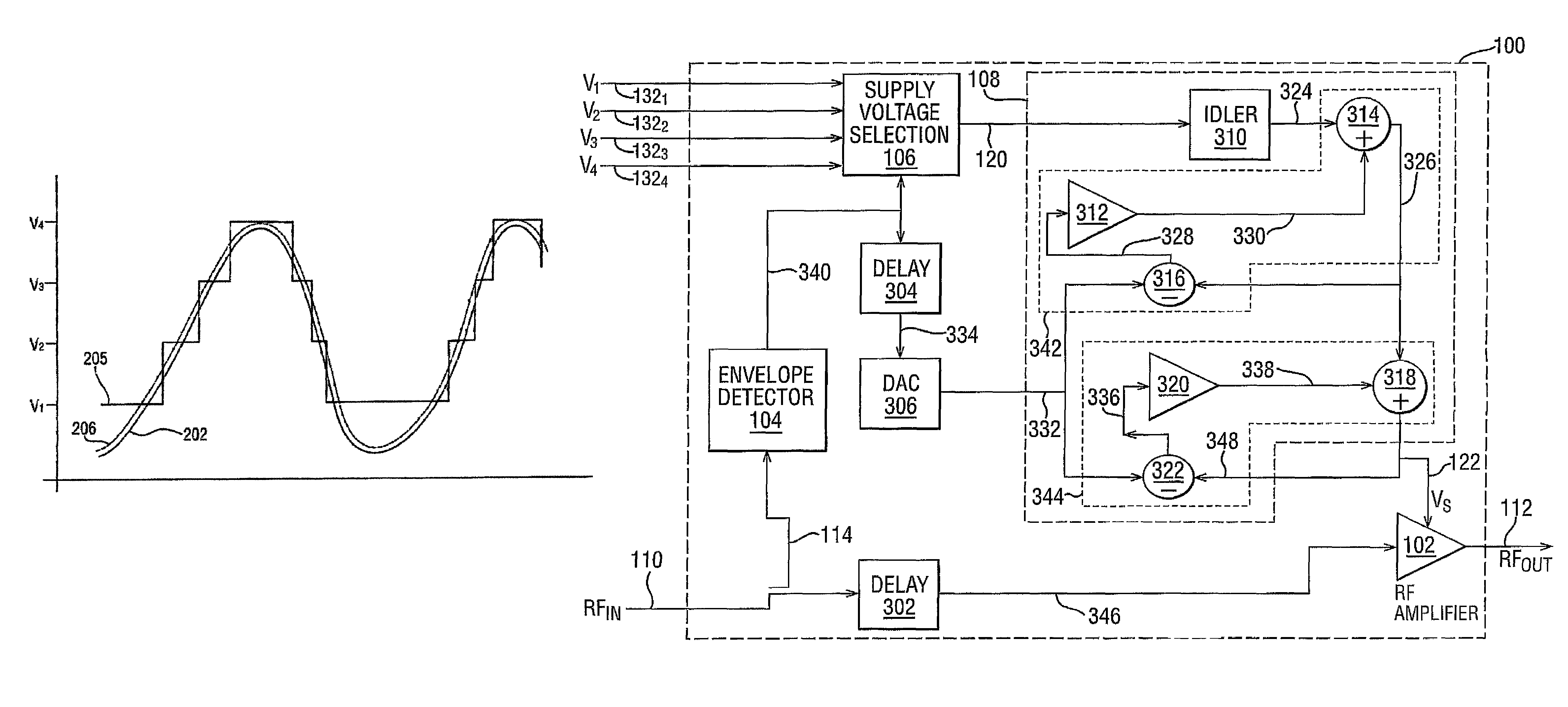

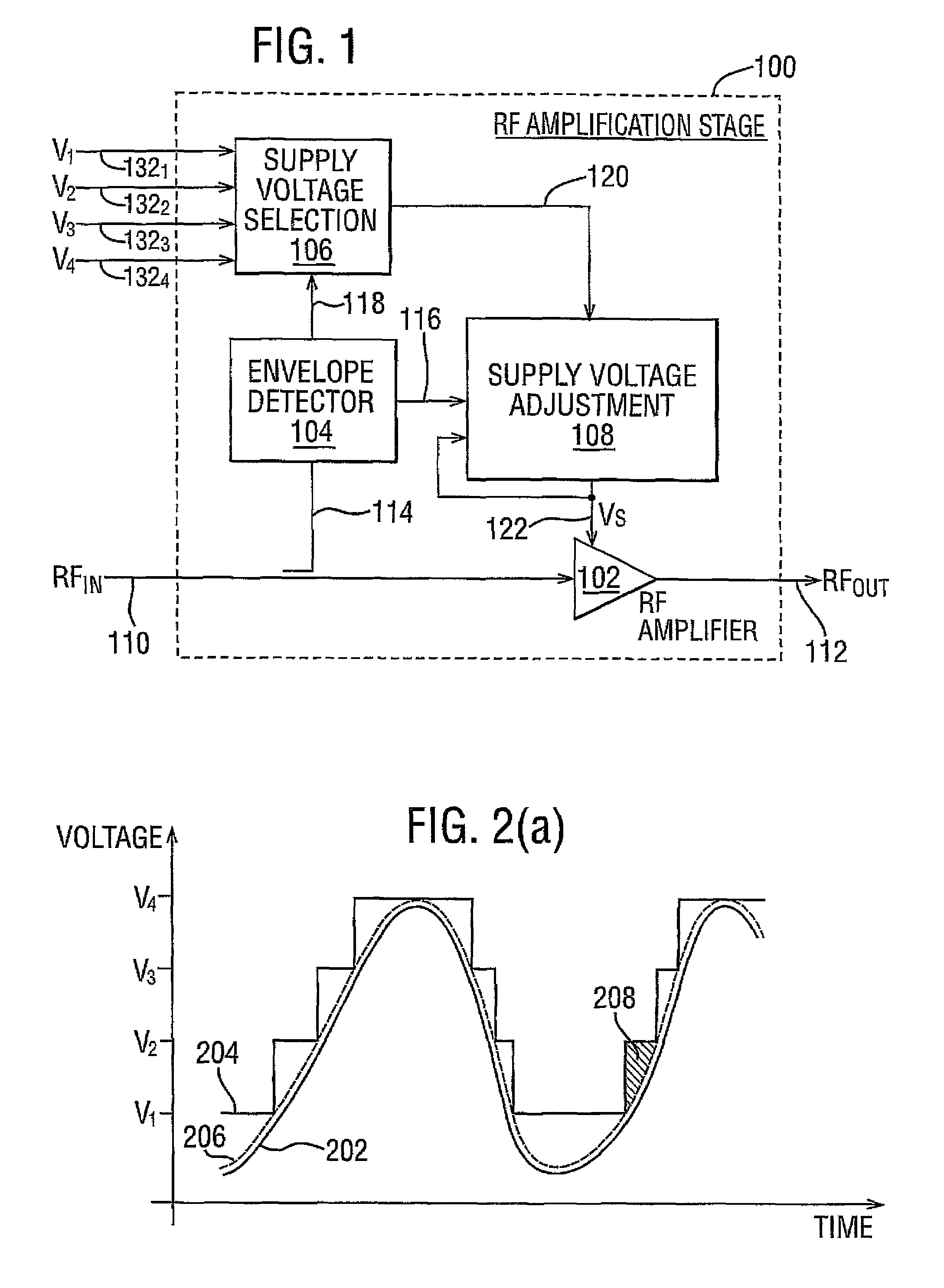

High efficiency amplification

InactiveUS7482869B2Fast corrective loopWide bandwidthHigh frequency amplifiersGain controlAudio power amplifierSignal envelope

A radio frequency amplification stage including an amplifier for receiving an input signal to be amplified and a power supply voltage; and a power supply voltage stage for supplying said power supply voltage, including a circuit for providing a reference signal representing the envelope of the input signal; a circuit for selecting one of a plurality of supply voltage levels in dependence on the reference signal; and a circuit for generating an adjusted selected power supply voltage, including an ac amplifier for amplifying a difference between the reference signal and one of the selected supply voltage level or the adjusted selected supply voltage level, and a summer for summing the amplified difference with the selected supply voltage to thereby generate the adjusted supply voltage.

Owner:SNAPTRACK

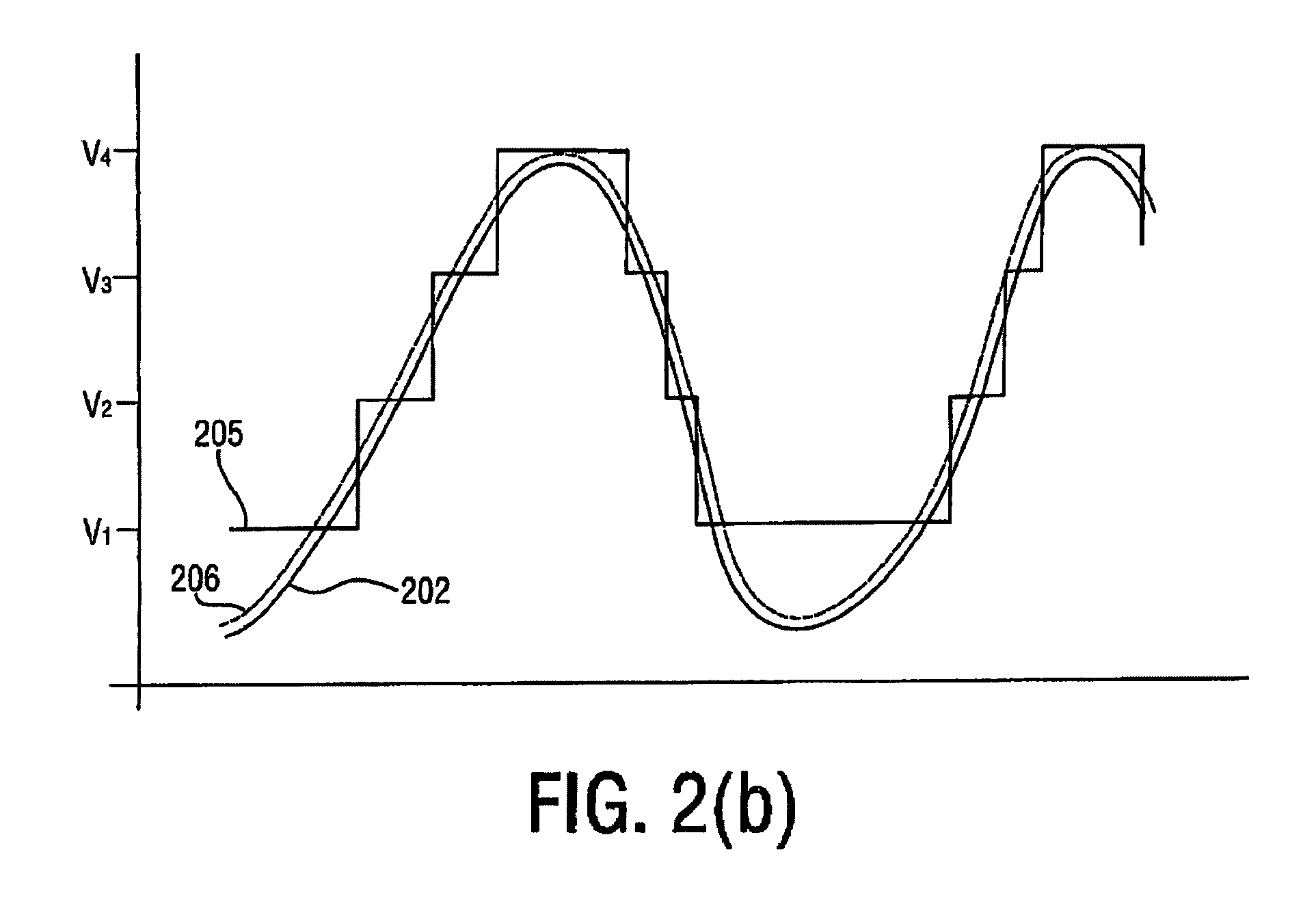

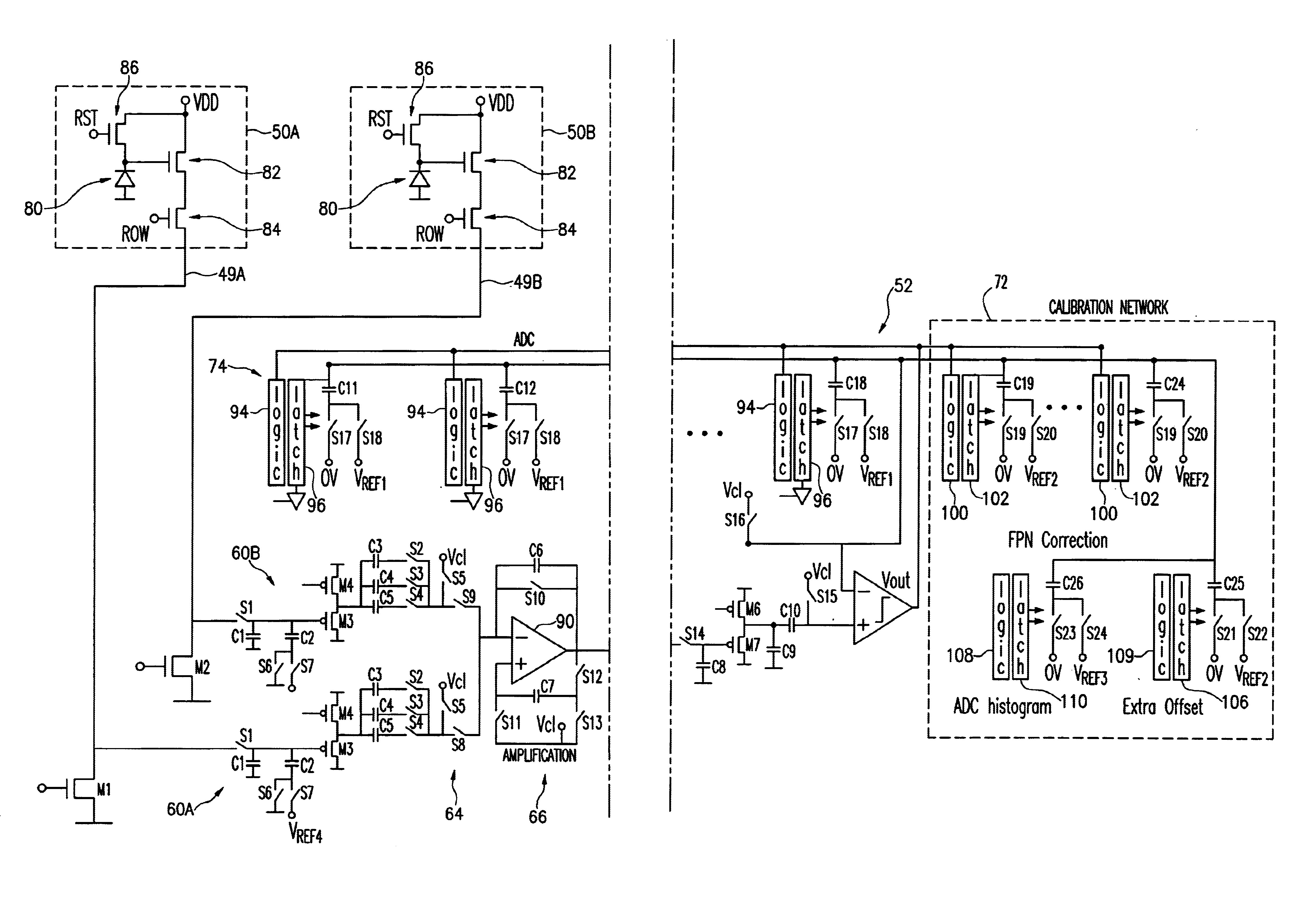

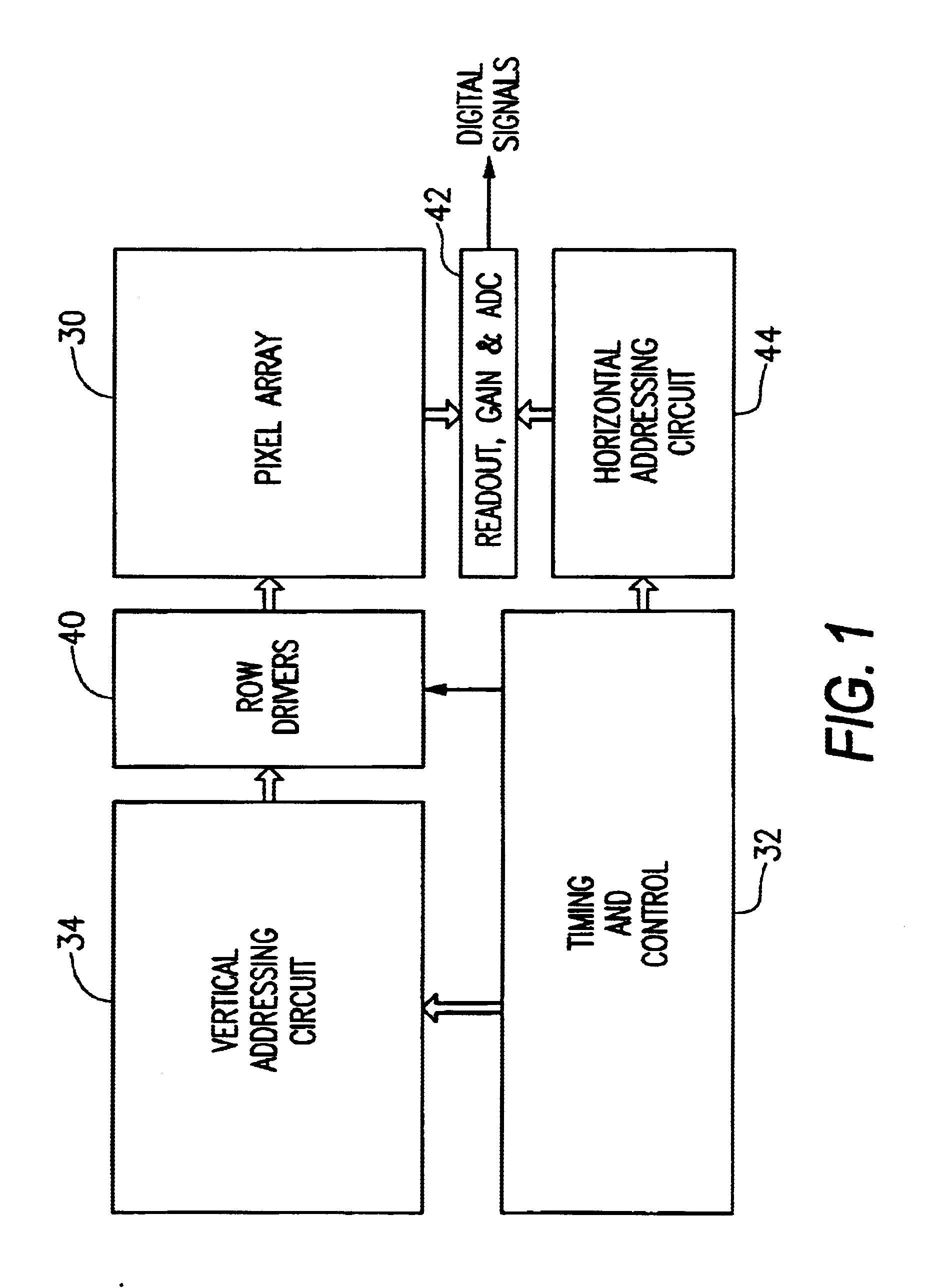

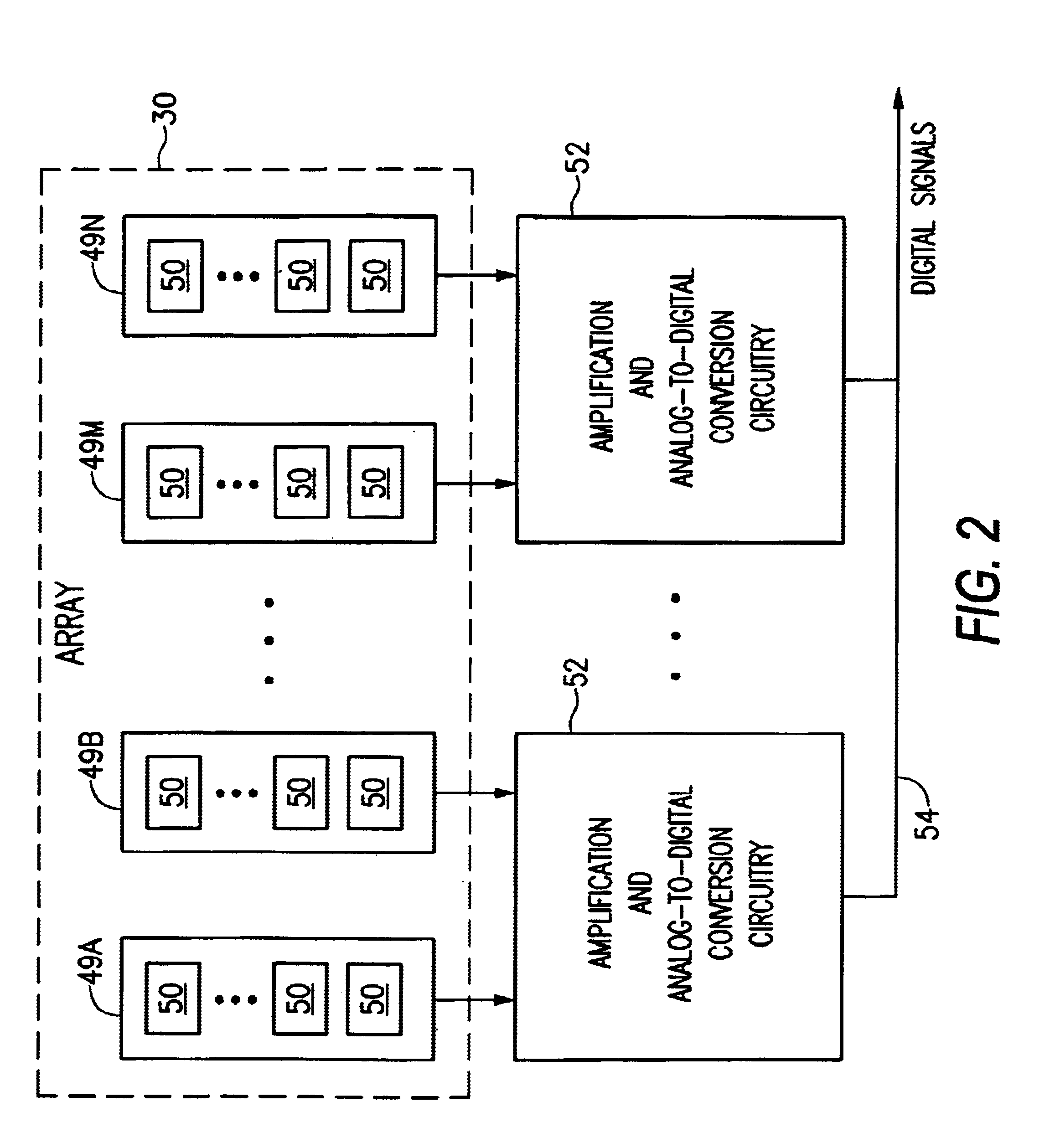

Readout circuit with gain and analog-to-digital a conversion for image sensor

InactiveUS6885396B1Increase parallel structureAttenuation bandwidthTelevision system detailsElectric signal transmission systemsSensor arrayCMOS sensor

A CMOS imager includes an array of active pixel sensors, wherein each pixel is associated with a respective column in the array. The imager also includes multiple circuits for reading out values of pixels from the active sensor array. Each readout circuit can be associated with a respective pair of columns in the array and can include first and second sample-and-hold circuits. The first and second sample-and-hold circuits are associated, respectively, with first and second columns of pixels in the array. Each readout circuit also includes an operational amplifier-based charge sensing circuit that selectively provides an amplified differential output signal based on signals sampled either by the first sample-and-hold circuit or the second sample-and-hold circuit. The readout circuit also has an analog-to-digital converter for converting the differential output to a corresponding digital signal using a successive approximation technique. Use of the readout circuit can increase the parallel structure of the overall chip, thereby reducing the bandwidth which each readout circuit must be capable of handling.

Owner:APTINA IMAGING CORP

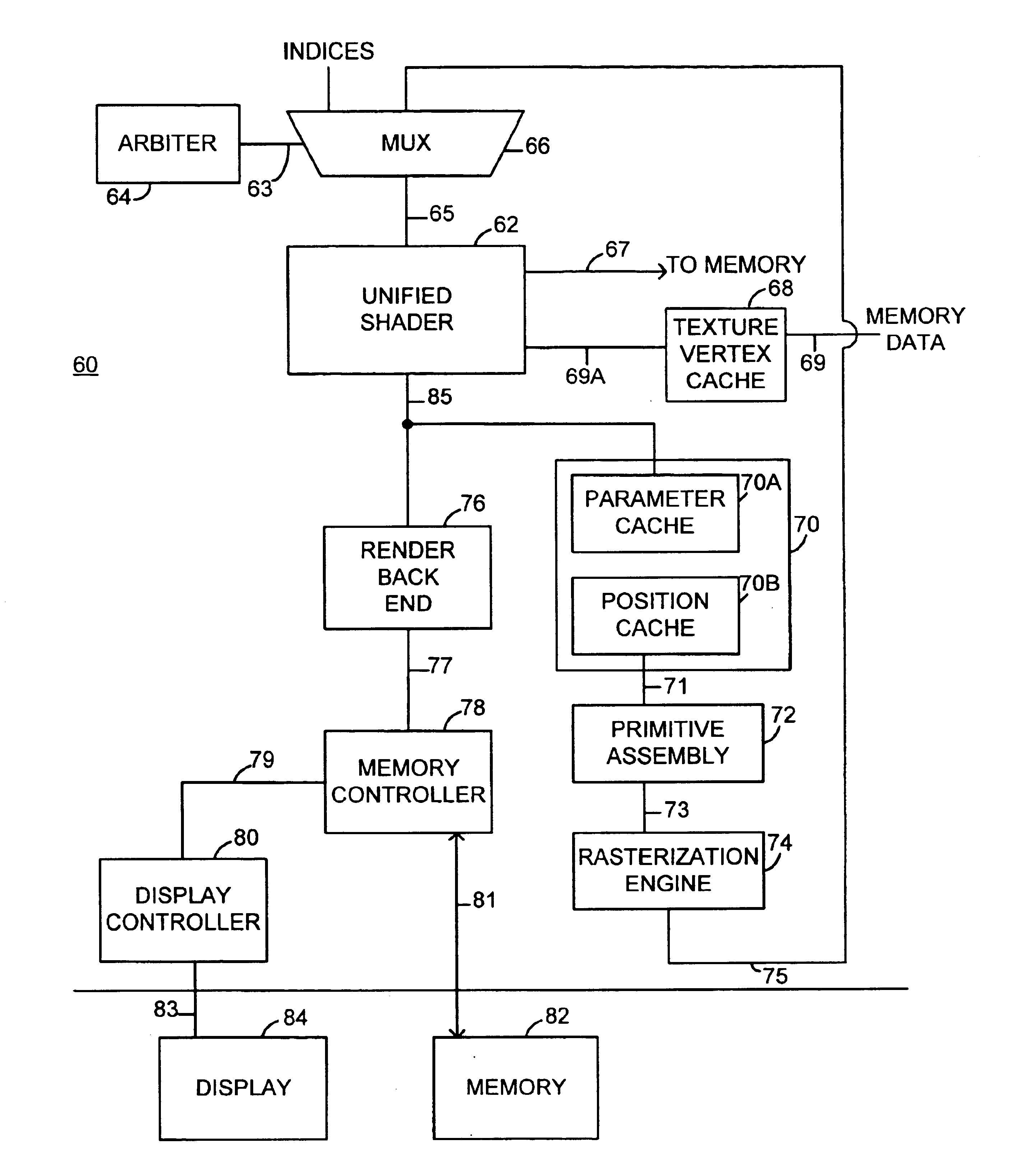

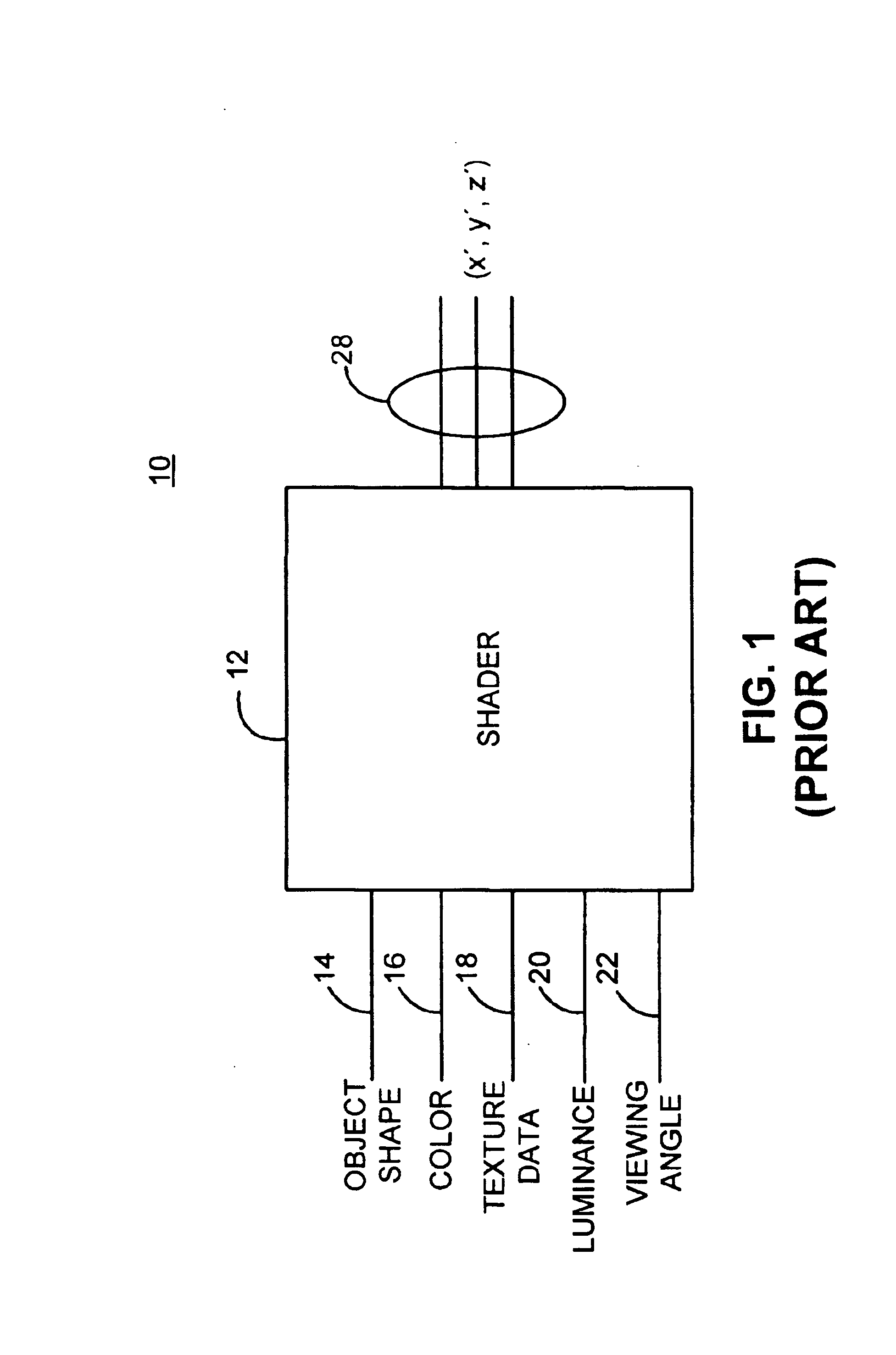

Graphics processing architecture employing a unified shader

ActiveUS6897871B1More computationally efficientFlexiblyDigital computer detailsCathode-ray tube indicatorsControl signalLogical operations

A graphics processing architecture employing a single shader is disclosed. The architecture includes a circuit operative to select one of a plurality of inputs in response to a control signal; and a shader, coupled to the arbiter, operative to process the selected one of the plurality of inputs, the shader including means for performing vertex operations and pixel operations, and wherein the shader performs one of the vertex operations or pixel operations based on the selected one of the plurality of inputs. The shader includes a register block which is used to store the plurality of selected inputs, a sequencer which maintains vertex manipulation and pixel manipulations instructions and a processor capable of executing both floating point arithmetic and logical operations on the selected inputs in response to the instructions maintained in the sequencer.

Owner:ATI TECH INC

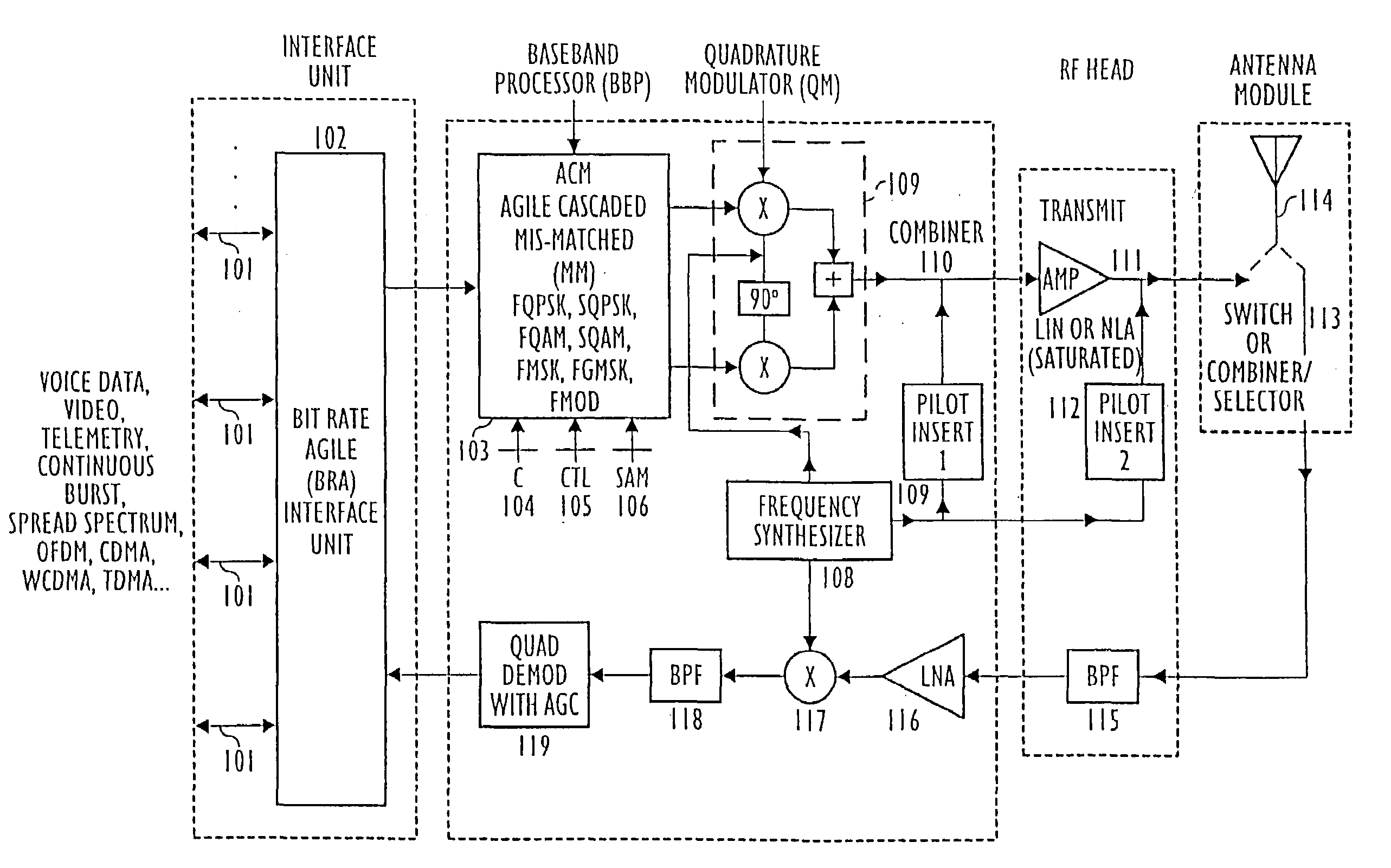

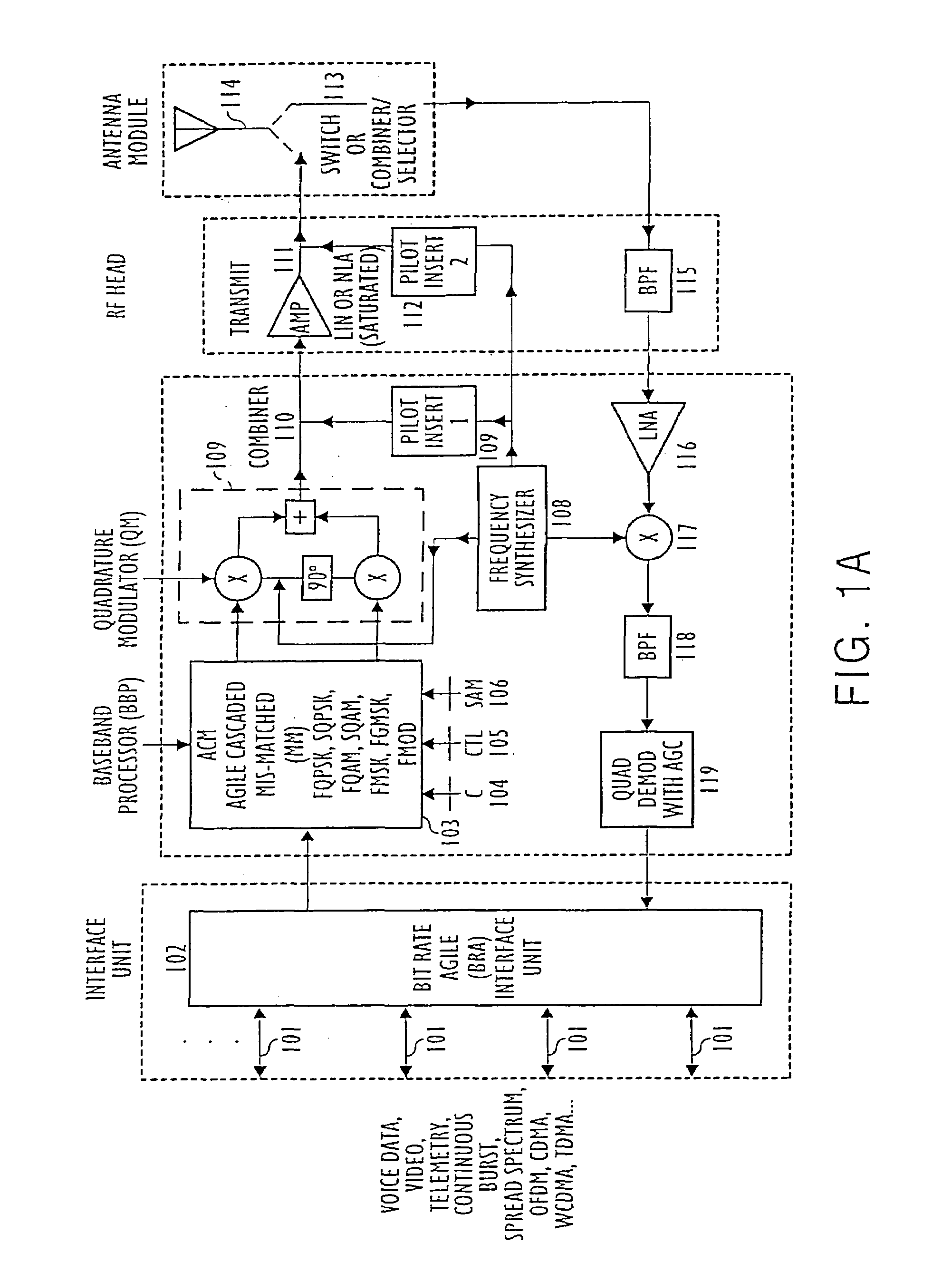

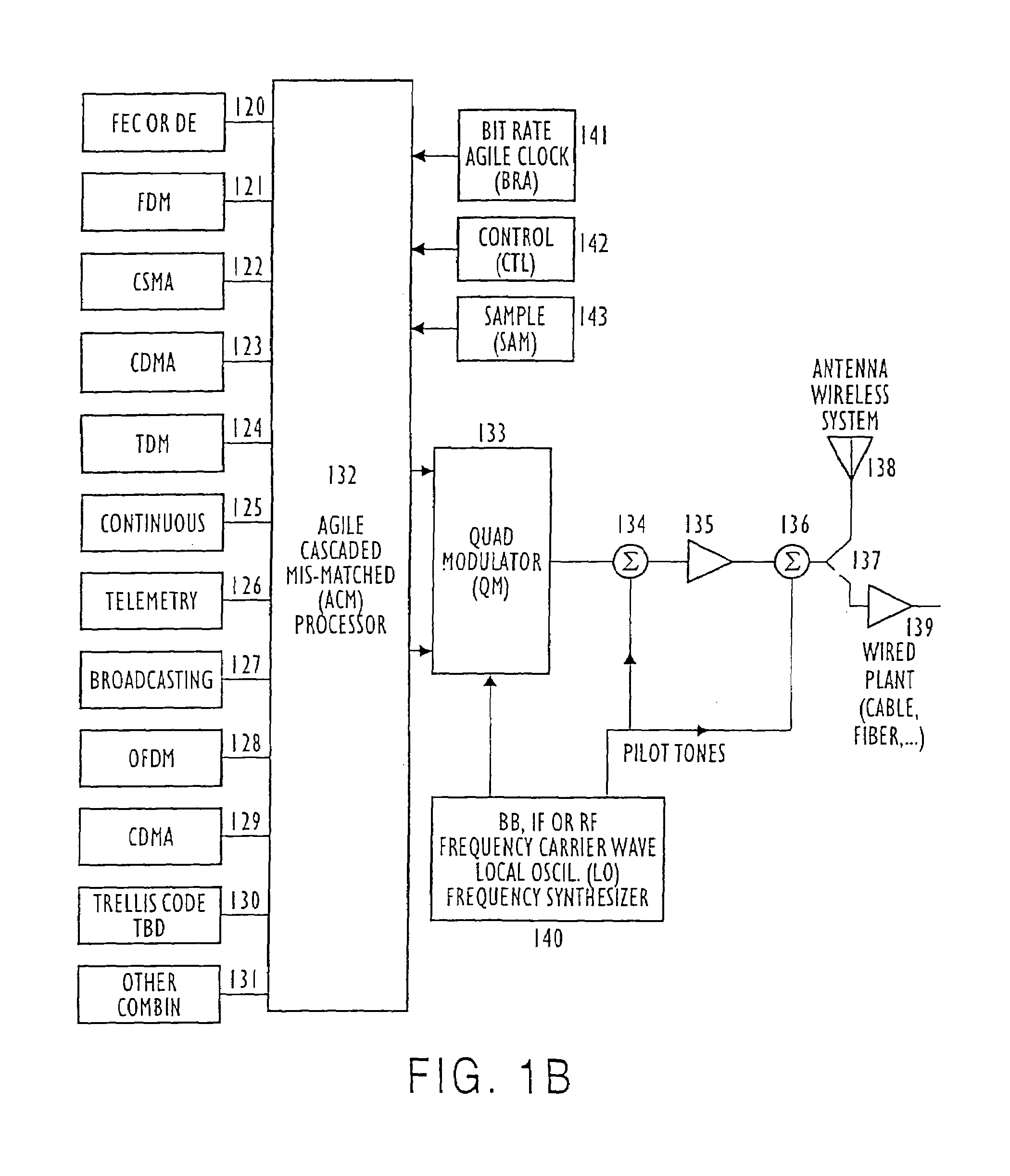

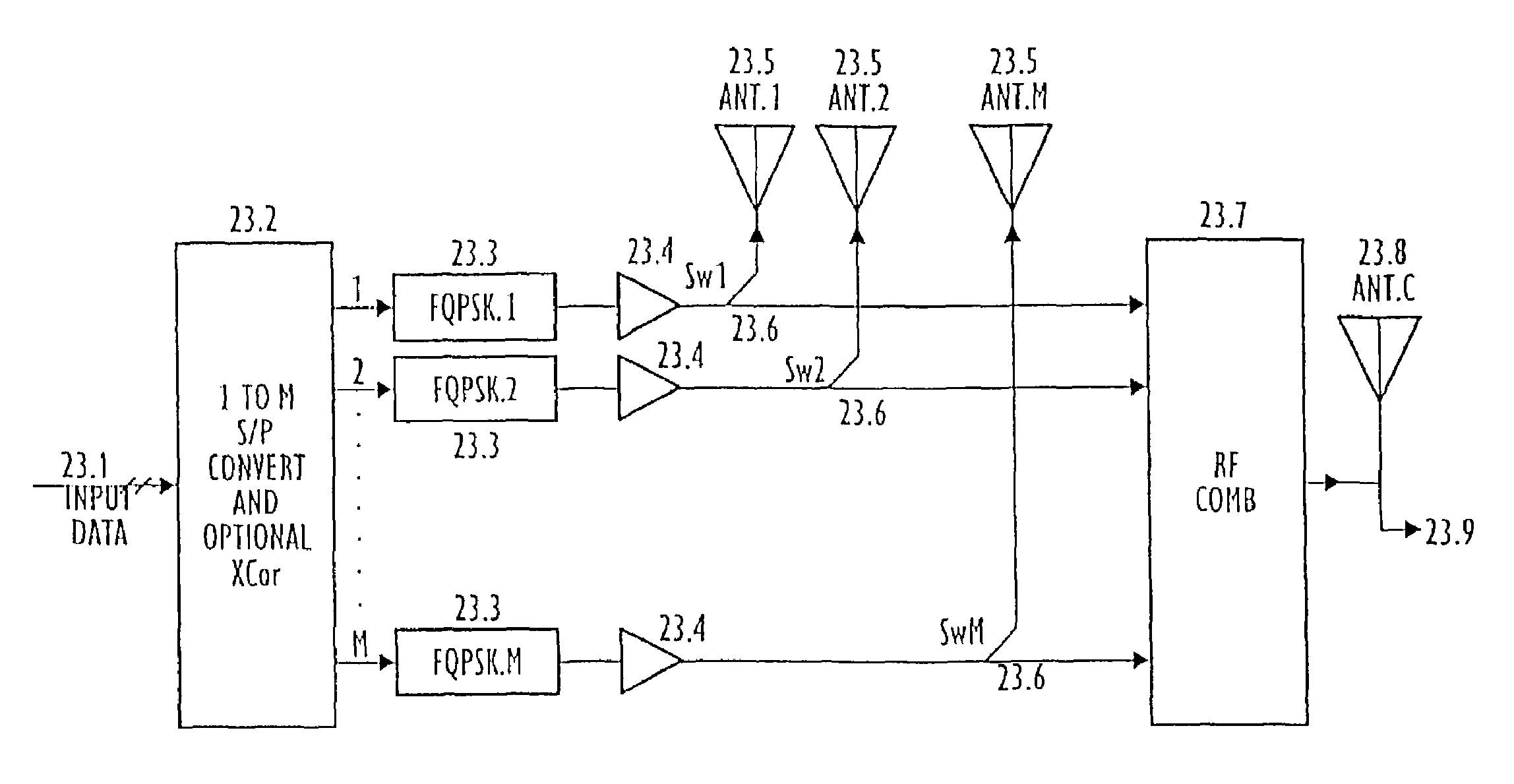

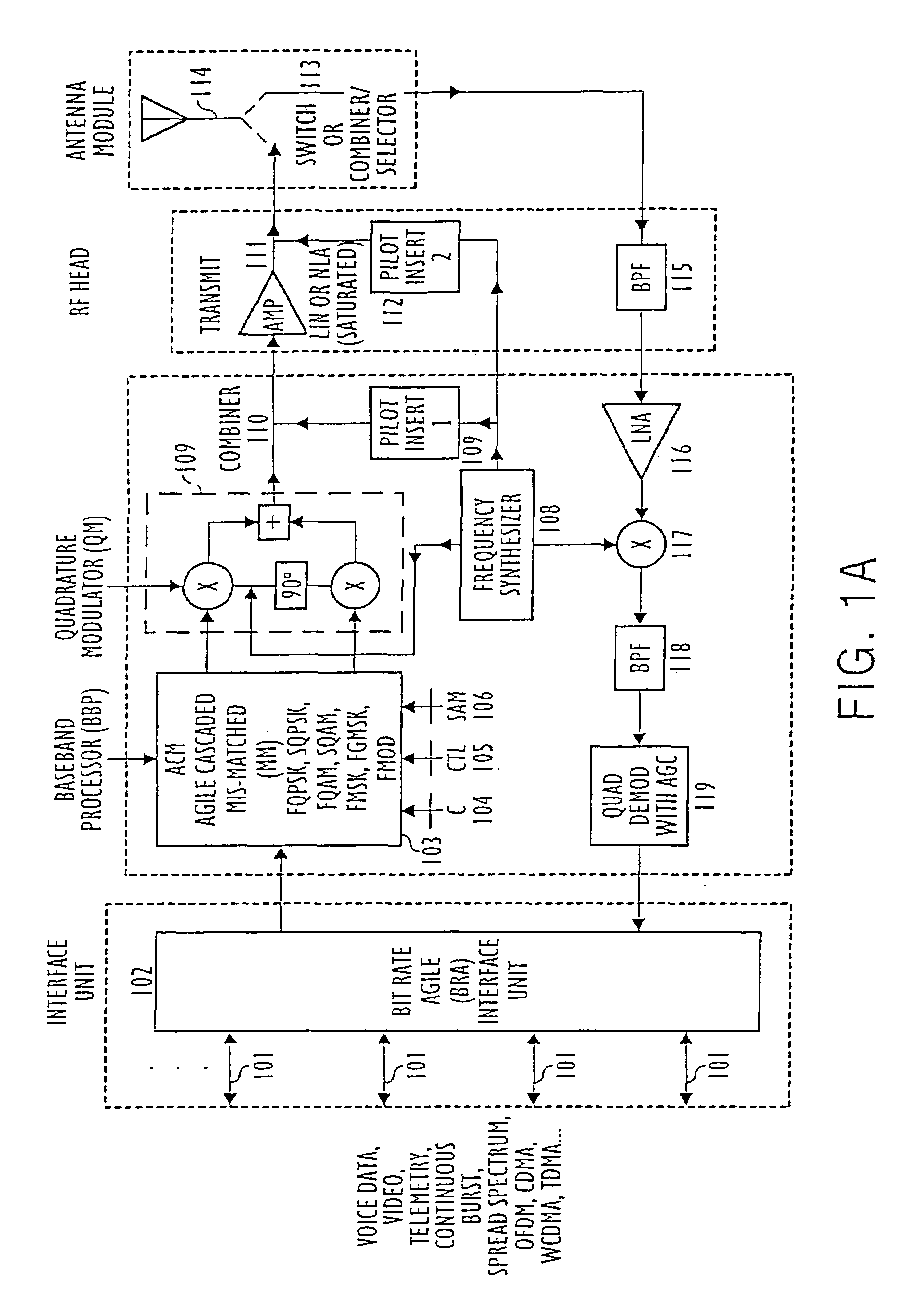

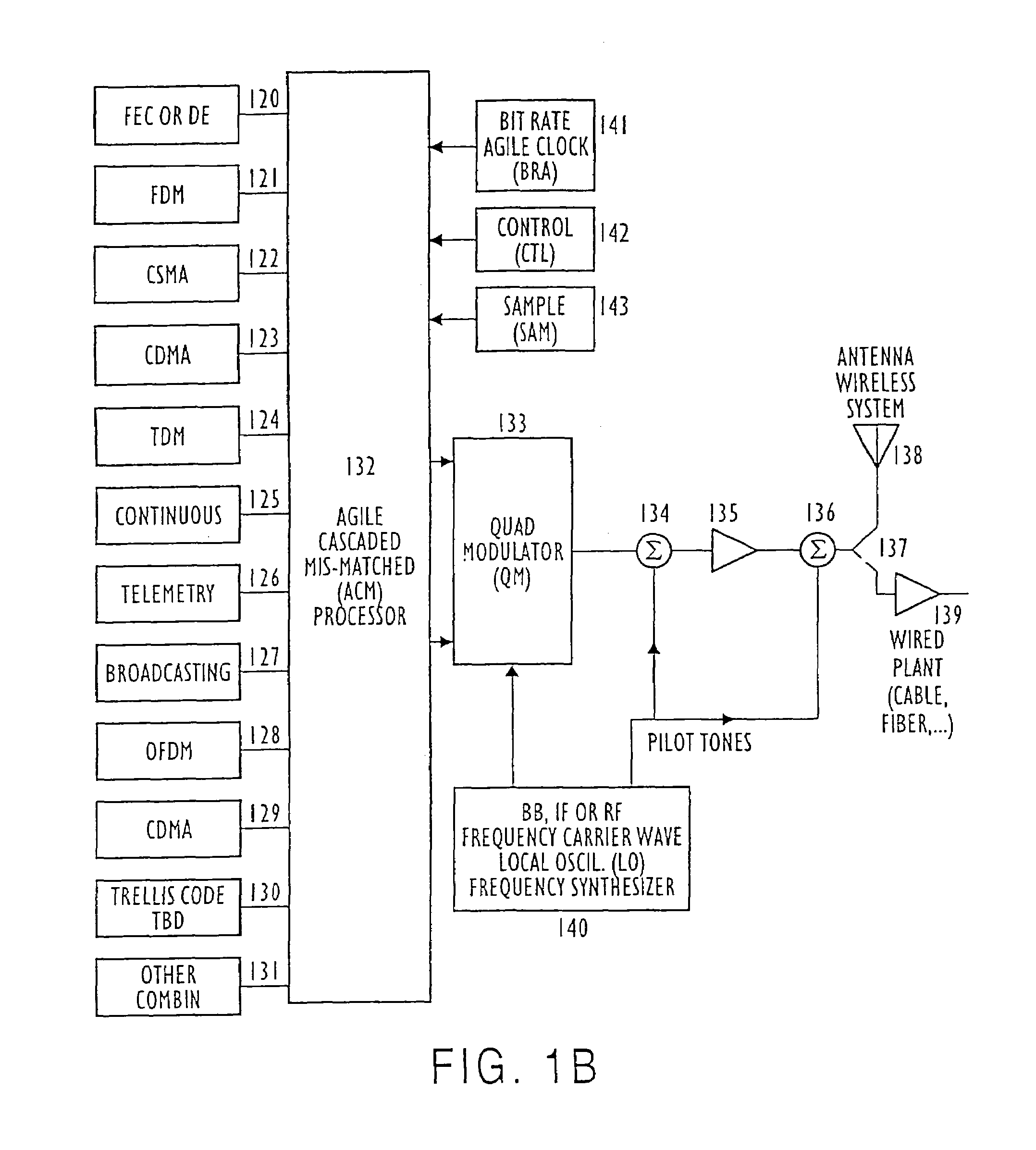

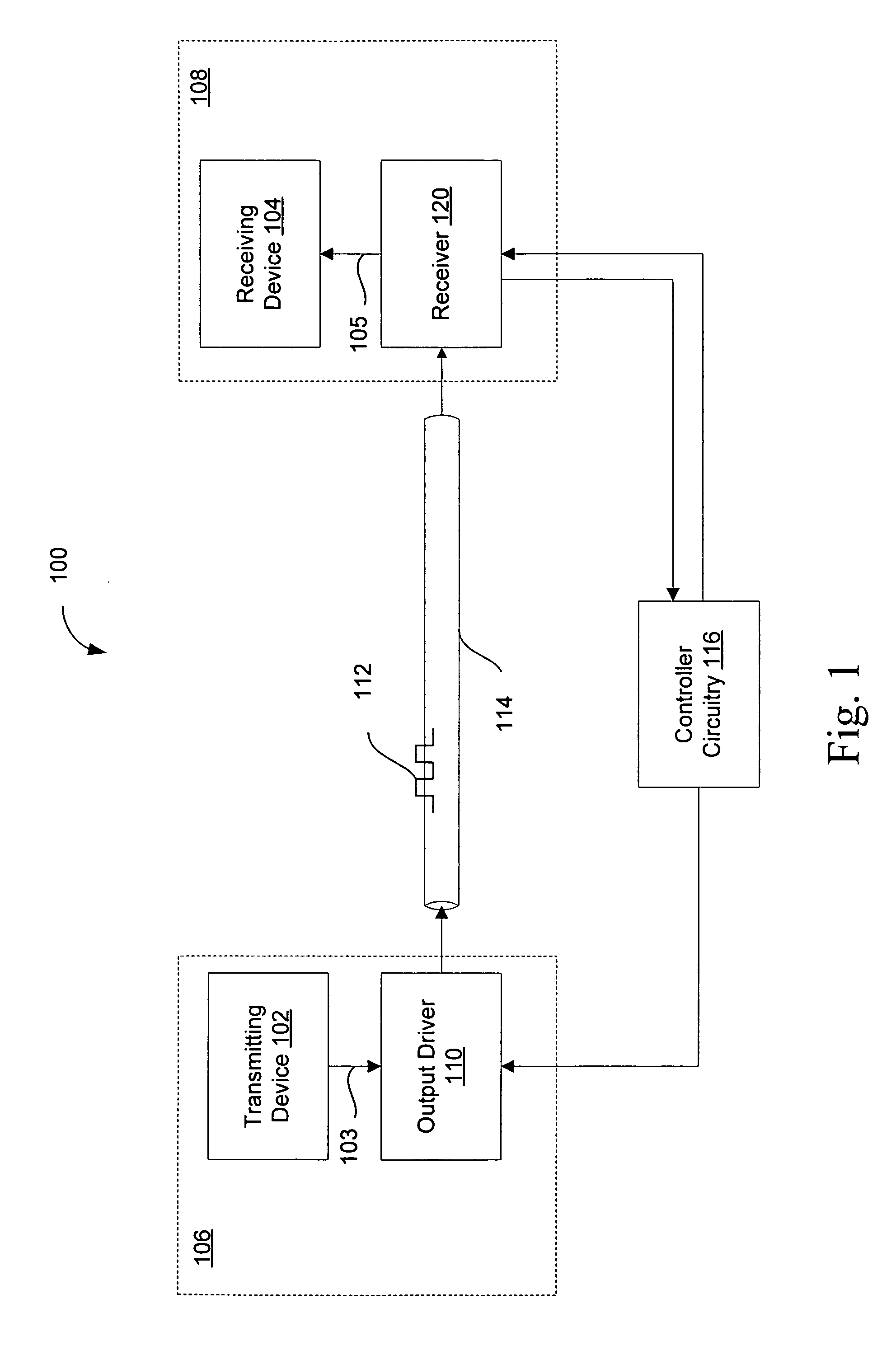

Modulation and demodulation format selectable system

InactiveUS7133456B2Improve efficiencyImprove performanceEnergy efficient ICTError preventionQuadrature modulatorModem device

Modulation Demodulation (Modem) Format Selectable (MFS) and Code Selectable (CS) systems for new generations of wireless systems, including third generation “3G”, spread spectrum systems, CDMA,W-CDMA and GSM, OFDM systems having different bit rates, that is having bit rate selection or bit rate agile( BRA) operation. MFS and Code Selectable (CS) systems connected to one or more modulators, one or more transmit amplifiers and one or more antennas. The transmitted signals are received by single or multiple receivers and demodulators.Shaped Time Constrained Signal(TCS) wavelet processors and bit rate agile Long Response (LR) filters provide shaped Time Constrained Signal (TCS) waveforms / filtered signals in in-phase(I) and quadrature-phase(Q) baseband channels to one or more Quadrature Modulators(QM) connected to the baseband signal processing network. A control processor and signal selection device selects one or more of the baseband signals and provides these signals through one or more quadrature modulators(QM) having the same or different radio frequency(RF) signals for amplification by one or more amplifiers. A selection device for selecting a Linearly and / or a Non-Linearly Amplified (NLA) modulated signal is provided and the selected amplified signal is provided to one or more transmit antenna systems or to one or more transmission media.

Owner:WI LAN INC

Spread spectrum, cross-correlated and filtered modulated systems

InactiveUS7110433B2Improve efficiencyImprove performanceEnergy efficient ICTError preventionSpread spectrumBaseband

Spread Spectrum baseband signals, in-phase and quadrature-phase cross-correlated baseband signals and other filtered baseband signals connected to modulators for providing modulated signals. Modulator selection for modulated signal selection or for multiple modulated signals provided to one or more antennas for signal transmission.

Owner:WI LAN INC

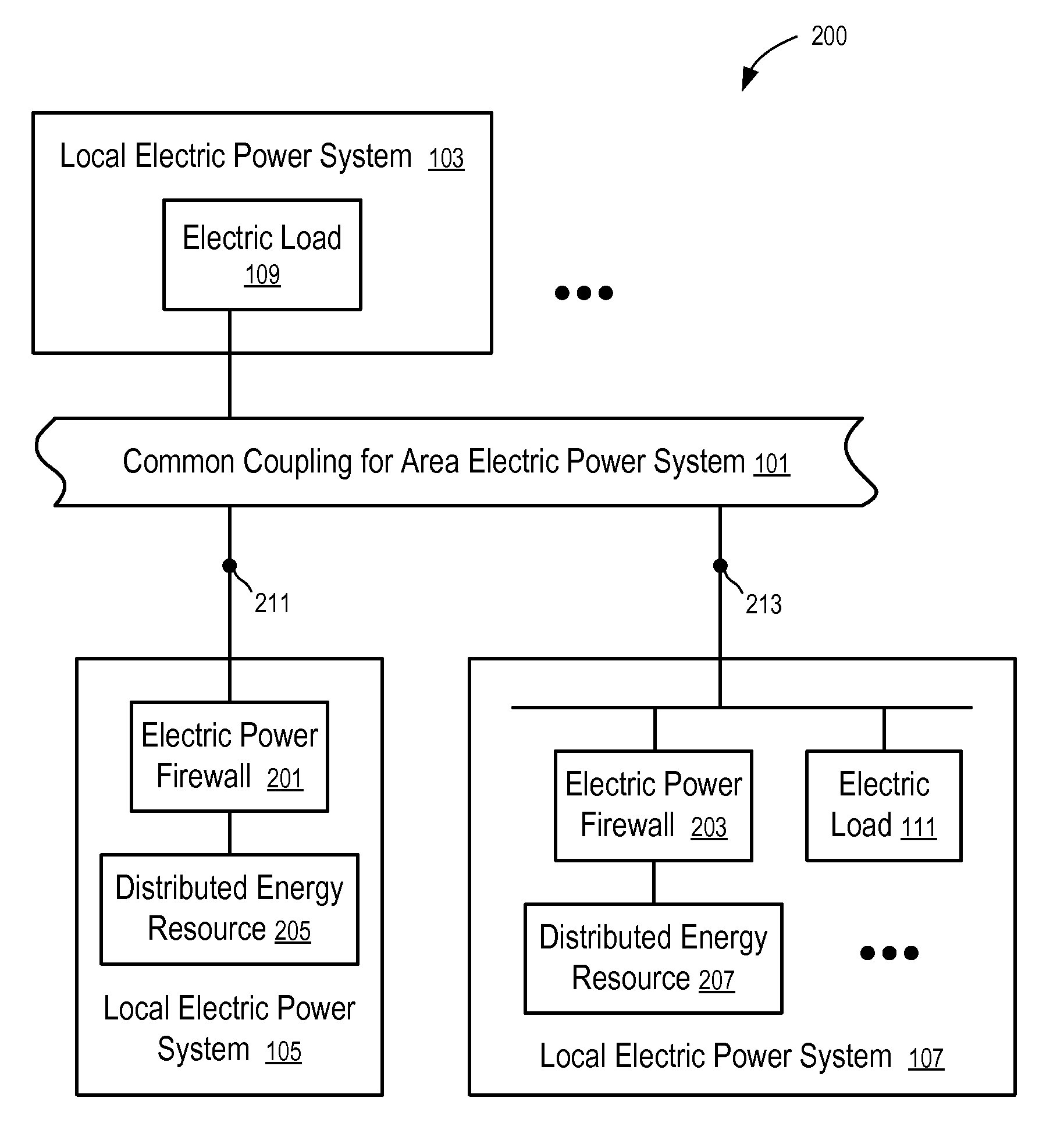

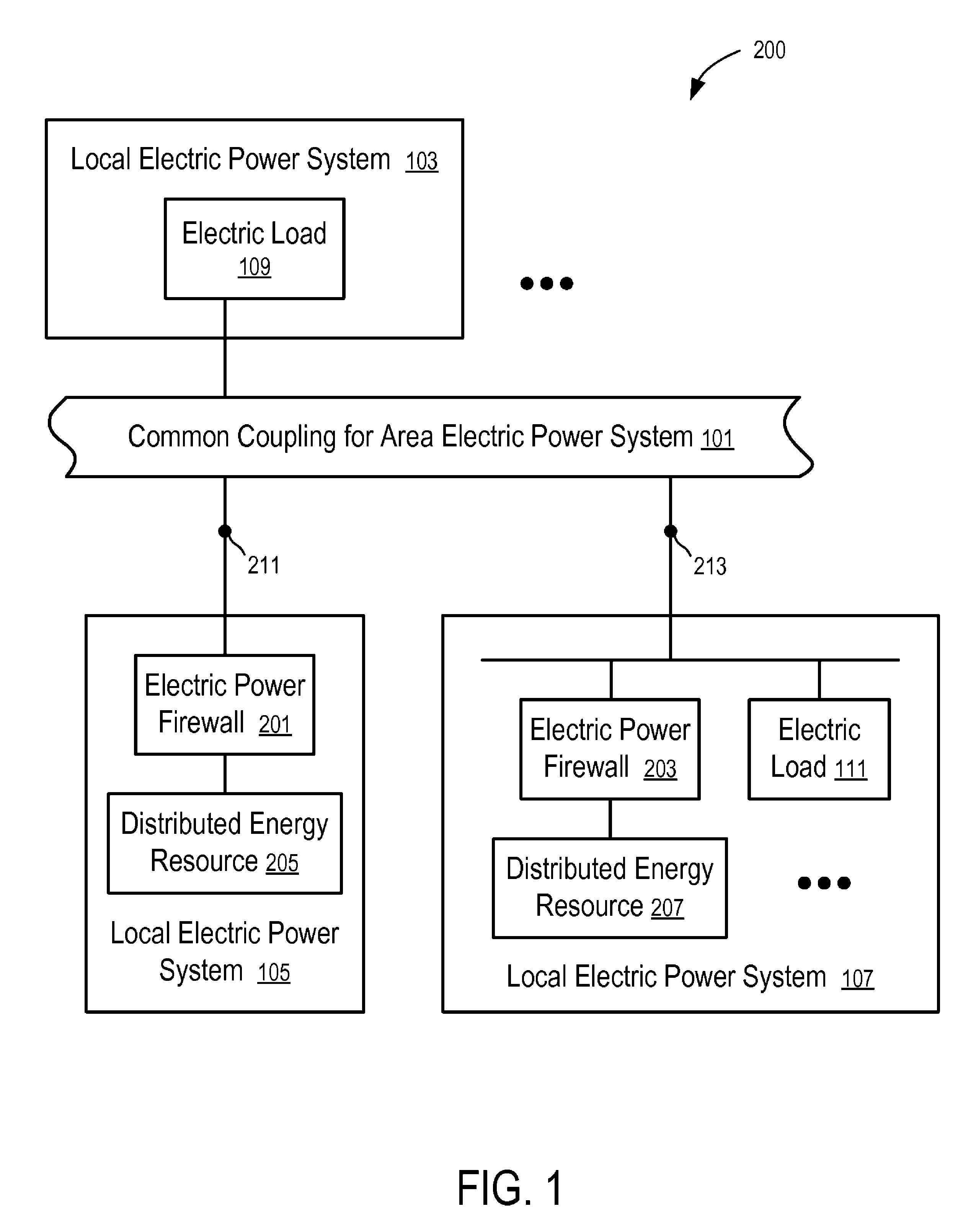

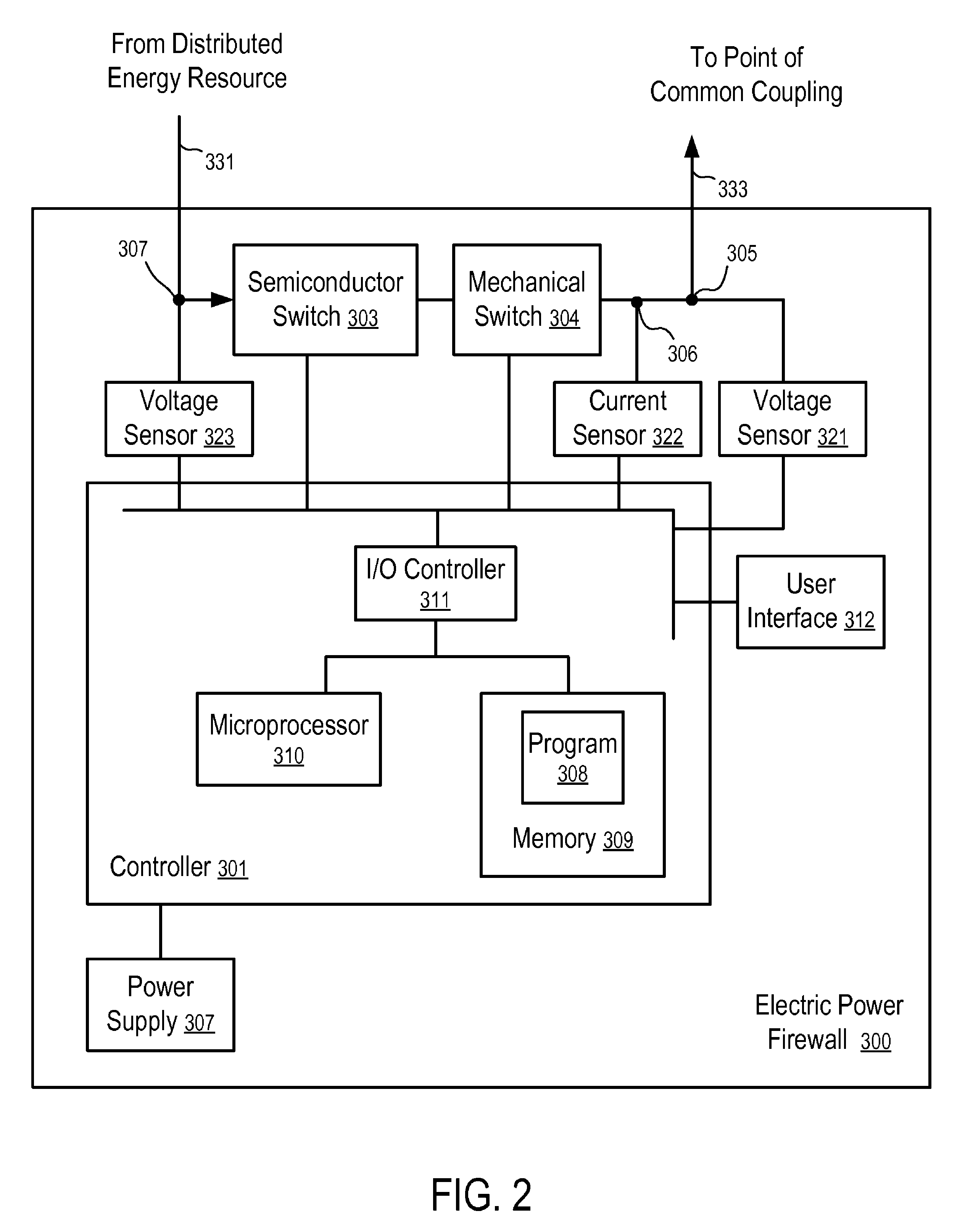

Apparatuses and methods to connect power sources to an electric power system

ActiveUS7898112B2Dc network circuit arrangementsBatteries circuit arrangementsElectric power systemEngineering

Apparatuses and methods to firewall distributed energy sources. In one aspect, an apparatus includes: a first connector configured to interface with a distributed energy source; a second connector configured to interface with a connection point of an electric power system; at least one switch coupled between the first connector and the second connector; at least one sensor coupled with the switch; and a controller coupled with the at least one switch, the controller to use the at least one switch to selectively connect or disconnect an electric path between the first connector and the second connector based on signals from the at least one sensor.

Owner:NEWLIGHT CAPITAL LLC

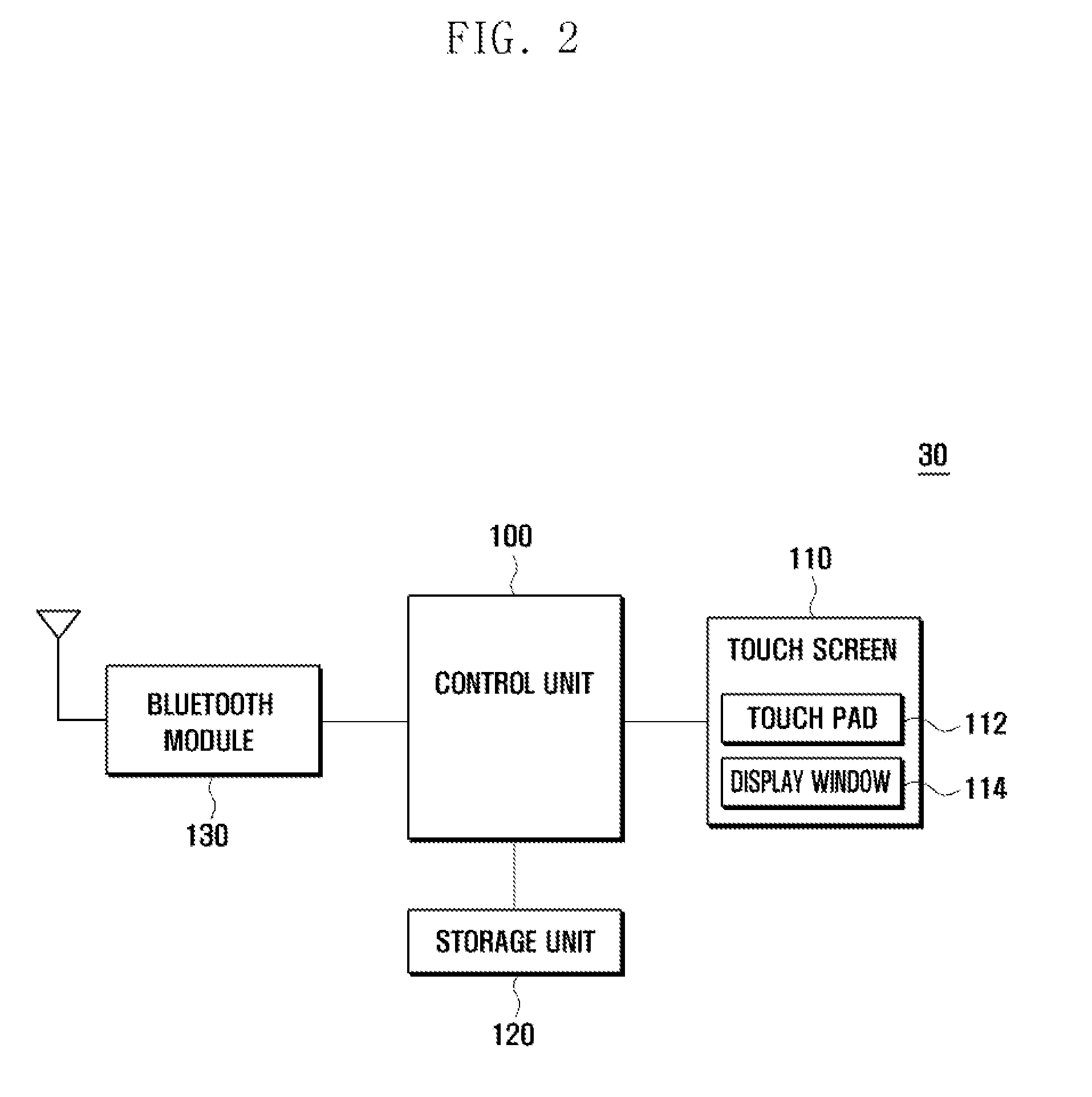

System and method for connecting bluetooth devices

InactiveUS20100304674A1Easy to buildConveniently generatedNetwork topologiesConnection managementBluetoothComputer science

A system and method for connecting Bluetooth devices are provided. The system includes a first device comprising a Bluetooth module, a relay terminal for transmitting information regarding the first device selected by a touch signal together with a Bluetooth connection request, and a second device for receiving the Bluetooth connection request and device information from the relay terminal, for analyzing the received Bluetooth connection request and the device information, and for transmitting a Bluetooth connection response accepting the request to the first device. The information includes an address of the first device and a name of the first device.

Owner:SAMSUNG ELECTRONICS CO LTD

Card handling devices and methods of using the same

A card handling device includes a sensing system for identifying cards handled thereby. A control system may be configured to selectively control an infeed system, a storage system, and / or an output system of the device in response to a signal received from the sensing system, and to enable a user to selectively perform one or more of a shuffling operation, a sorting operation, and a dealing operation using the device. A card handling device may be configured to dispense randomly arranged hands, prearranged hands, randomly arranged decks, or prearranged decks.

Owner:BALLY GAMING INC

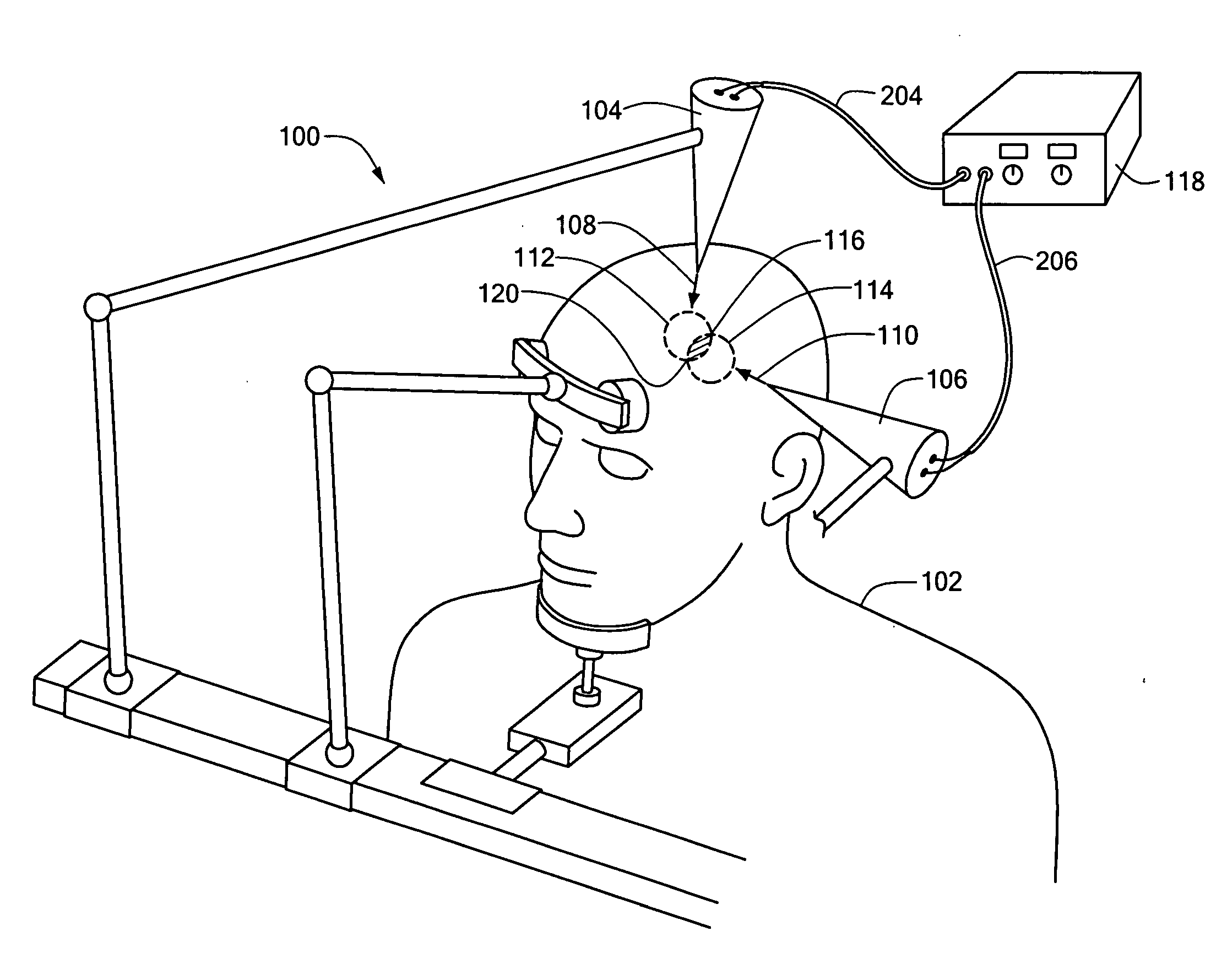

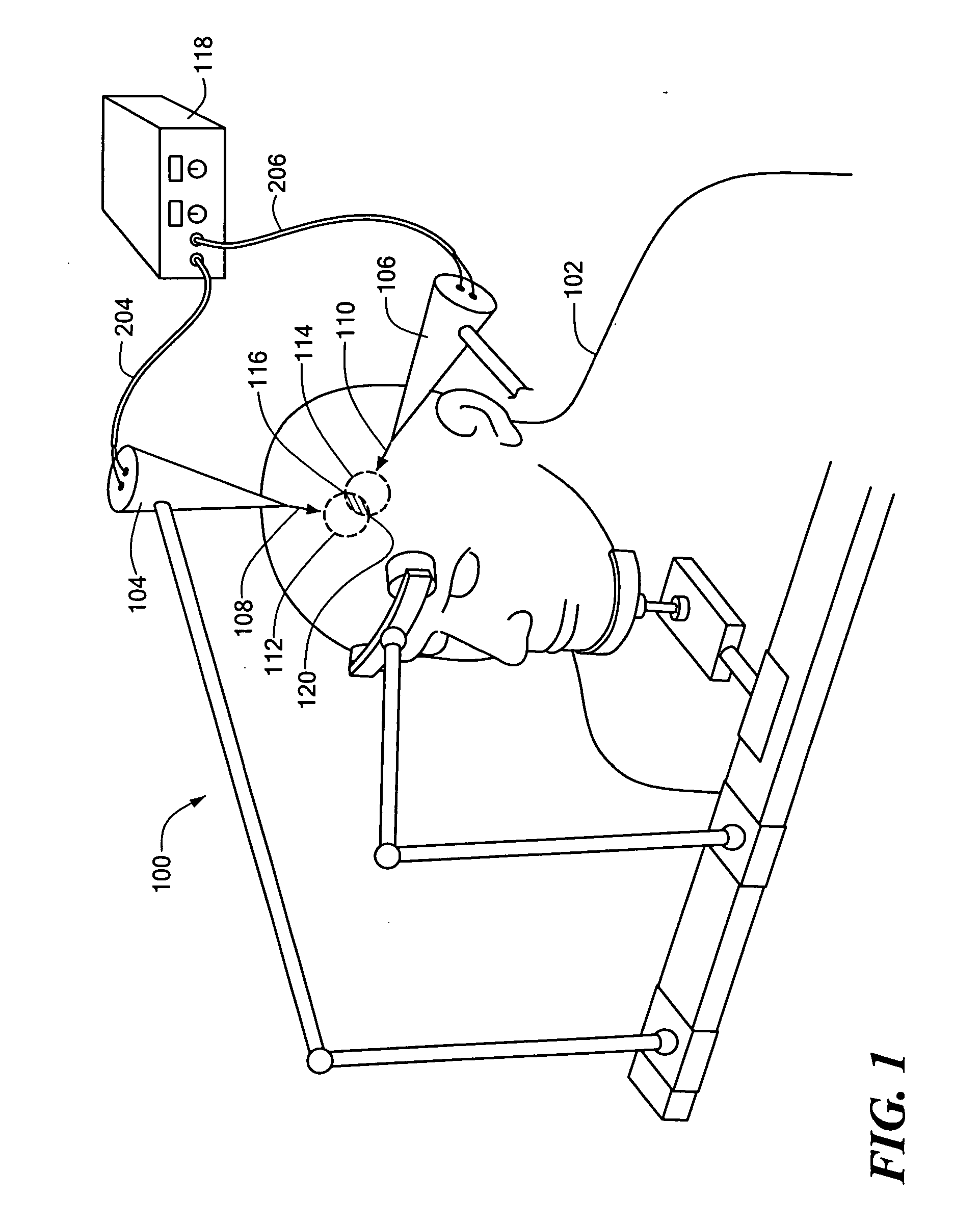

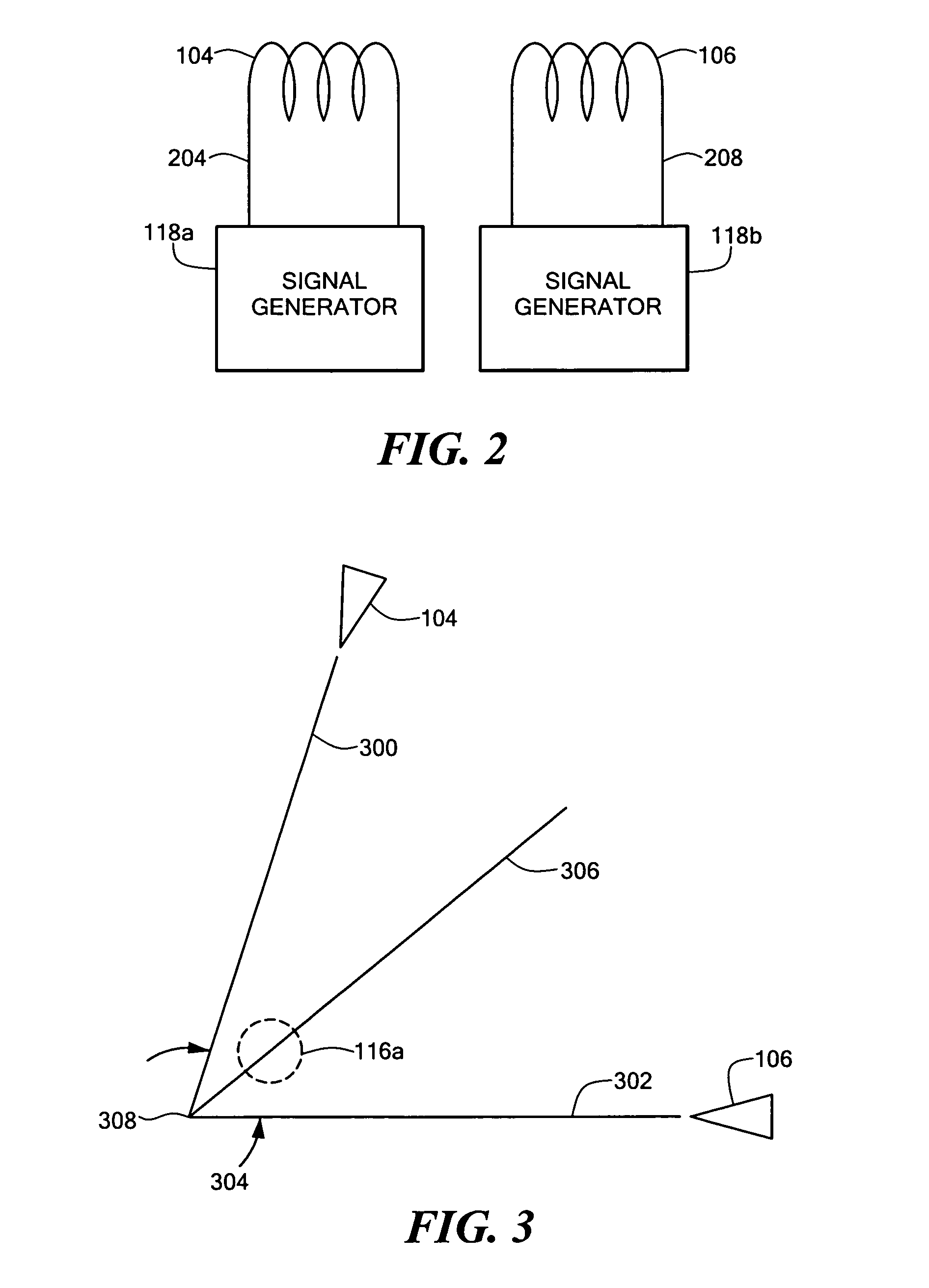

Magnetic stimulator

InactiveUS20060199992A1Deep penetrationElectrotherapyMagnetotherapy using coils/electromagnetsElectricityElectrical conductor

At least two coils deliver at least two time-varying magnetic fields to a target region within a body. The coils are oriented such that the magnetic fields create intersecting electric fields in the target region. The magnetic fields operate at different frequencies and thus produce a beat frequency signal where the electric fields intersect. The frequencies are chosen so a time-varying electric field, or a current induced by a time-varying magnetic field, alternating at the beat frequency would stimulate excitable tissue located in the target region. Some embodiments utilize a novel coil, which includes a first conductor and at least one second conductor electrically connected to the first conductor at a point. The second conductor extends from the point of connection with the first conductor to a location spaced from the first conductor. At least a portion of the second conductor adjacent the point of connection with the first conductor is non-parallel to the first conductor.

Owner:EISENBERG SOLOMONR +1

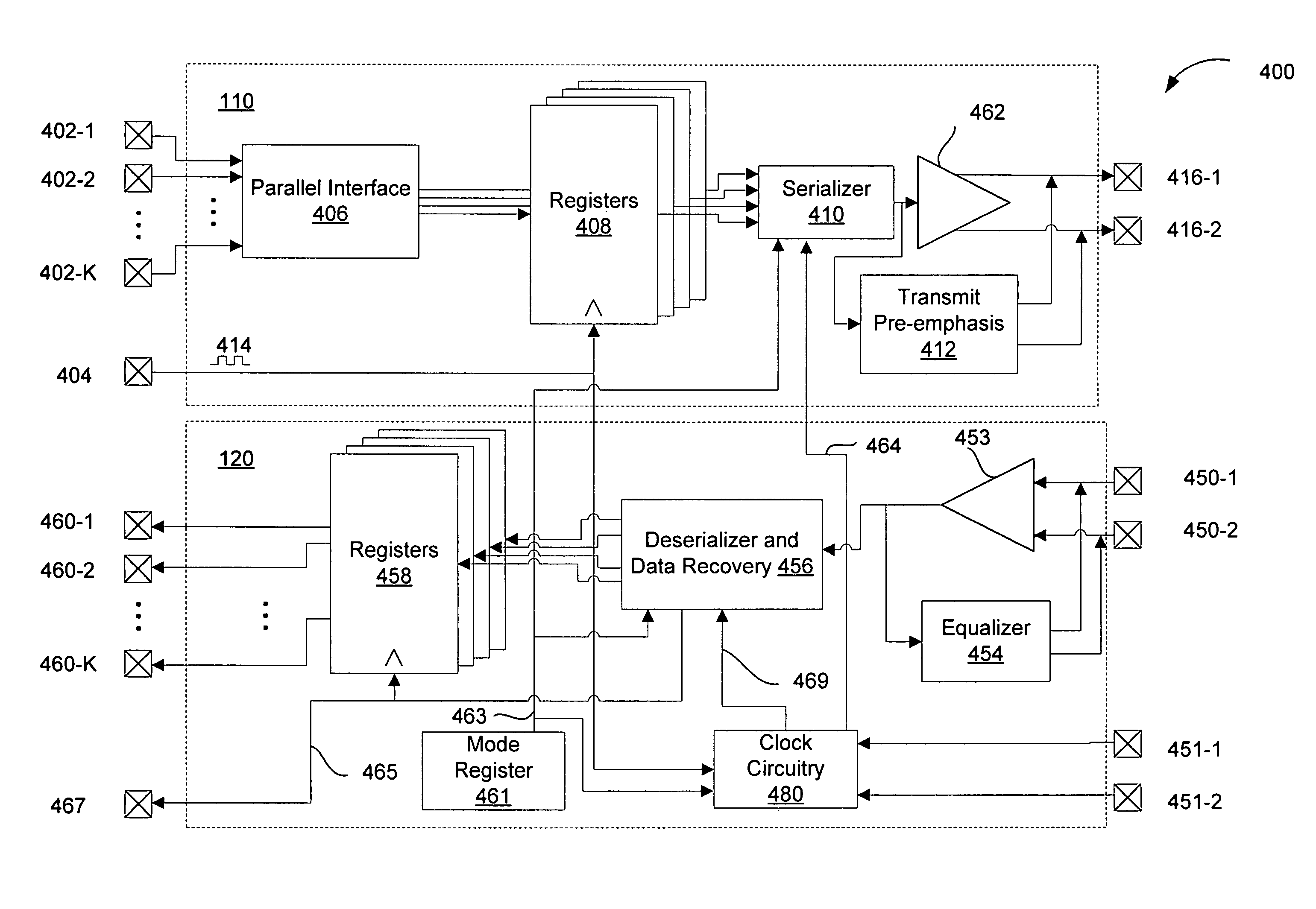

Transparent multi-mode PAM interface

ActiveUS20050089126A1Amplitude-modulated carrier systemsAmplitude-modulated pulse demodulationState variationData rate

Provided are a method and apparatus for high-speed, multi-mode PAM symbol transmission. A multi-mode PAM output driver drives one or more symbols, the number of levels used in the PAM modulation of the one or more symbols depending on the state of a PAM mode signal. Additionally, the one or more symbols are driven at a symbol rate, the symbol rate selected in accordance with the PAM mode signal so that a data rate of the driven symbols in constant with respect to changes in the state of the PAM mode signal. Further provided are methods for determining the optimal number of PAM levels for symbol transmission and reception in a given physical environment.

Owner:RAMBUS INC

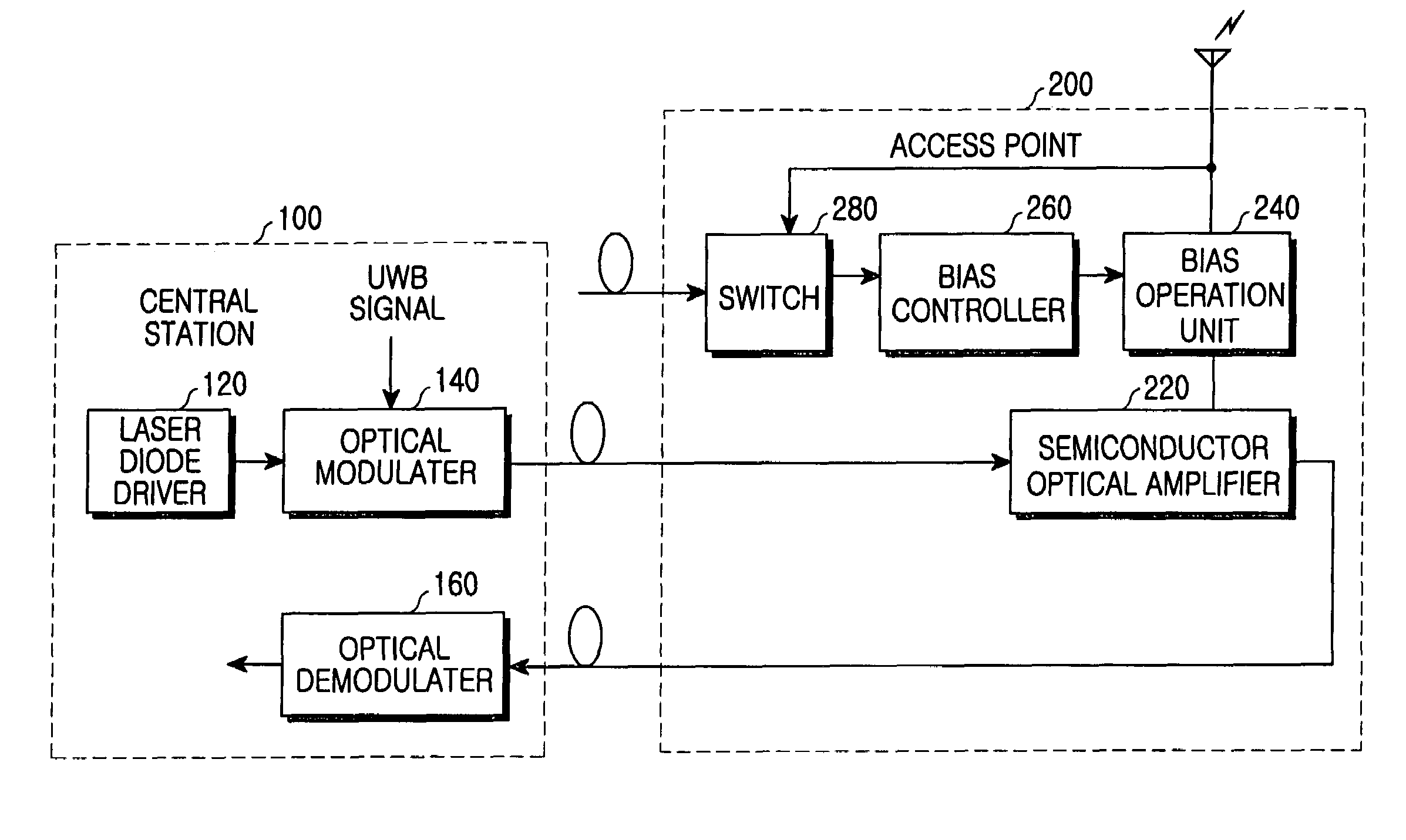

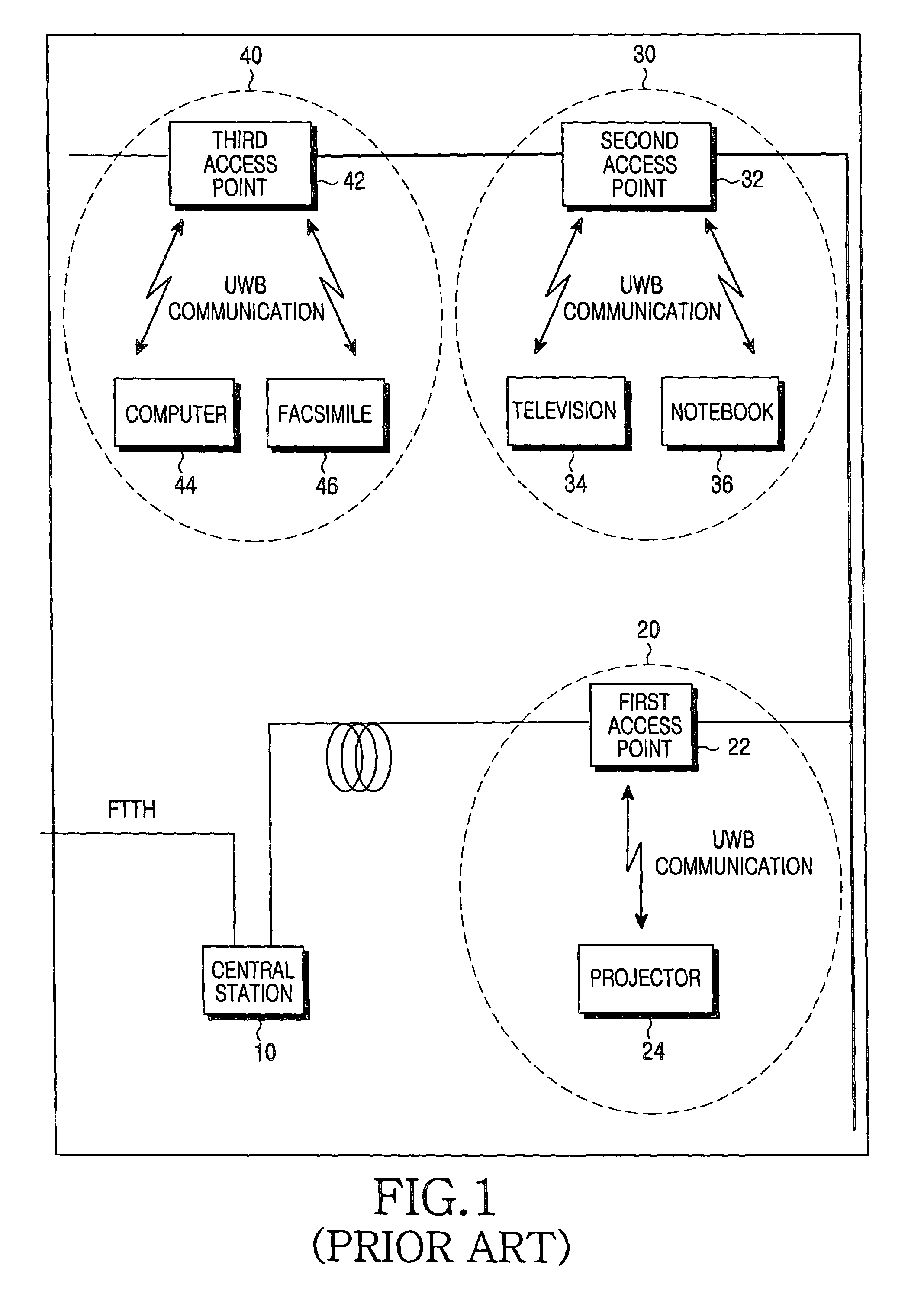

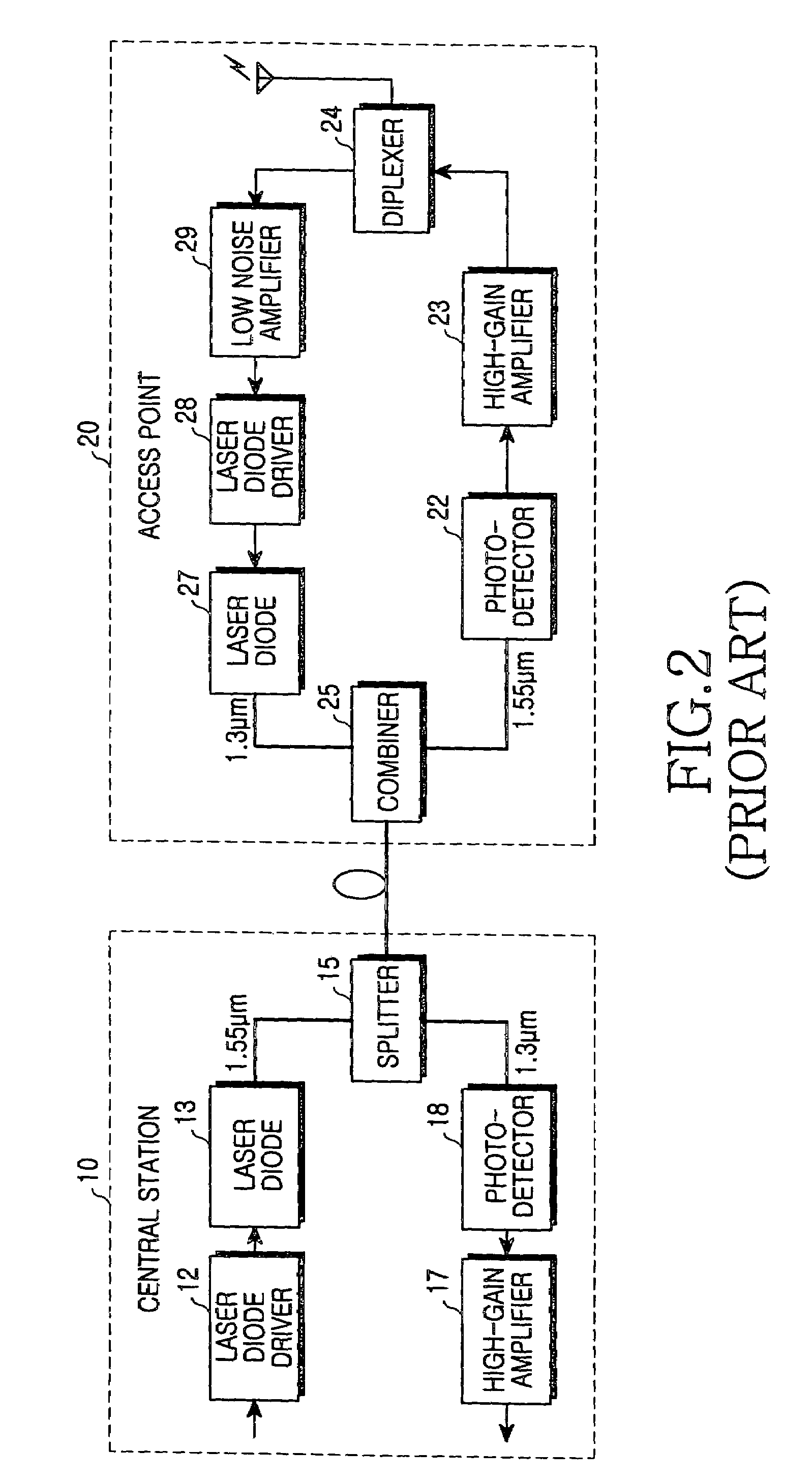

Access point for constructing optical fiber-based high-speed wireless network system

InactiveUS7349633B2Small sizeReduce manufacturing costTime-division optical multiplex systemsNetwork topologiesModulation functionNetworked system

An access point in an optical fiber-based high-speed optical wireless network is disclosed. The access point includes an antenna for receiving communication requirement signals, a switch for selectively outputting a corresponding signal according to the communication requirement signals, a bias control unit for selectively outputting bias current with variable intensity according to whether an output of the signal from the switch exists or not, on the basis of a threshold current; a bias operation unit for outputting input signals to the antenna when an input bias current is smaller than the threshold current and for outputting signals received by the antenna when an input bias current is larger than the predetermined threshold current, and a semiconductor optical amplifier for selectively performing an optical detection function of converting optical signals, which have been received through a first optical fiber from an central station, into electrical signals and sending the converted electrical signals to the bias operation unit, when a current smaller than the threshold current is input to the bias operation unit, and an optical modulation function of transmitting signals output from the bias operation unit through a second optical fiber to the central station, when a current larger than the threshold current is input to the bias operation unit.

Owner:SAMSUNG ELECTRONICS CO LTD